# Voltage Balancing of DC Capacitors in Chain-Link STATCOMs

Jan Kheir

Master of Engineering

Electrical and Computer Engineering Department

McGill University

Montreal,Quebec

2014-07-23

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Master of Engineering

©Jan Kheir, 2014

#### **ACKNOWLEDGEMENTS**

I would like to thank Dr. Ambra Sannino for giving me the opportunity of doing my thesis work in the R&D department at ABB FACTS. I would also like to thank Mr. Greger Fasth who has made this possible by allowing me to share my time between work and study. I would like to thank Mr. Mauro Monge and Mr. Jean-Philippe Hasler. Their supervision and guidance has been essential. Finally, I would like to thank professor Boon-Teck Ooi for accepting me as his student, and for encouraging me from the very beginning.

#### ABSTRACT

Modular Multilevel Converters (MMC) have become an interesting alternative to other converter topologies for Static synchronous Compensator (STATCOM) applications due to the modularity of their design and to their increased effective switching frequency which reduces the harmonics on the AC side. The drawback is that these converters have a large number of DC capacitors whose voltages have to be controlled independently. This becomes particularly important when the converter is required to operate during unbalanced conditions. The purpose of this thesis is therefore to define the problem of DC capacitor voltage balancing in MMC based STATCOMs, and to solve this problem for four different STATCOM topologies. A comparison of the advantages and disadvantages of each converter topology is then performed, and the proposed control schemes are implemented and tested using Matlab/Simulink.

### ABRÉGÉ

Les convertisseurs modulaires multiniveaux (MMC - de l'anglais : Modular Multilevel Converter) deviennent une alternative intéressante aux topologies de convertisseurs conventionnelles pour des applications de compensateurs synchrones statiques (STATCOM - de l'anglais : Static Synchronous Compensator) grâce, entre autres, à leur conception modulaire ainsi qu'à leur fréquence effective de commutation élevée qui réduit les harmoniques générées. L'inconvénient des convertisseurs à topologie MMC est qu'ils comportent un grand nombre de condensateurs CC dont les tensions doivent être contrôlées de façon indépendante. Ceci devient particulièrement important lorsque ces convertisseurs doivent opérer dans des conditions débalancées. L'objectif de cette thèse est donc de comprendre le problème qu'est le débalancement des tensions CC dans les STATCOM de type MMC et de résoudre ce problème pour quatre topologies différentes. Une comparaison des avantages et des inconvénients de chaque topologie de convertisseur sera faite, et les algorithmes de contrôle dévelopés seront réalisés et testés à l'aide de Matlab/Simulink.

# TABLE OF CONTENTS

| ACK                         | NOW                              | LEDGEMENTS i                                           |  |  |  |  |  |

|-----------------------------|----------------------------------|--------------------------------------------------------|--|--|--|--|--|

| ABS                         | TRAC                             | Tii                                                    |  |  |  |  |  |

| ABR                         | ÉGÉ                              |                                                        |  |  |  |  |  |

| LIST                        | OF T                             | ABLES vii                                              |  |  |  |  |  |

| LIST                        | OF F                             | IGURES                                                 |  |  |  |  |  |

| LIST                        | OF A                             | BBREVIATIONS xi                                        |  |  |  |  |  |

| 1                           | Introd                           | uction                                                 |  |  |  |  |  |

| 2                           | STAT                             | COM Principles and Applications                        |  |  |  |  |  |

|                             | 2.1<br>2.2                       | STATCOM Principles                                     |  |  |  |  |  |

| 3 Voltage Source Converters |                                  |                                                        |  |  |  |  |  |

|                             | 3.1<br>3.2                       | Principles of a Basic Voltage Source Converter         |  |  |  |  |  |

| 4                           | The P                            | roblem of DC Capacitor Voltage Balancing               |  |  |  |  |  |

| 5                           | Delta-Coupled Chain-Link STATCOM |                                                        |  |  |  |  |  |

| 6                           | Ungro                            | unded Wye-Coupled Chain-Link STATCOM                   |  |  |  |  |  |

| 7                           | Groun                            | ided Wye-Coupled Chain-Link STATCOM                    |  |  |  |  |  |

| 8                           | Furthe                           | er Optimization to Increase STATCOM Output             |  |  |  |  |  |

|                             | 8.1<br>8.2<br>8.3<br>8.4<br>8.5  | Defining a Degree of Freedom                           |  |  |  |  |  |

|                             | 8.6                              | Example of Results With and Without the Optimization 4 |  |  |  |  |  |

| 9    | Unbalance Between Cells in a Given Phase 4                           |                                                     |                                                    |  |  |  |

|------|----------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|--|--|--|

| 10   | Double Wye-Coupled Chain-Link STATCOM with Half-Bridge Cells . 49    |                                                     |                                                    |  |  |  |

| 11   | Comp                                                                 | parison of Chain-Link STATCOM Topologies            | 56                                                 |  |  |  |

|      | 11.1<br>11.2<br>11.3<br>11.4<br>11.5                                 | Delta-Coupled STATCOM                               | 57<br>60<br>63<br>64<br>64                         |  |  |  |

| 12   | Imple                                                                | ementation of Control Strategies in Matlab/Simulink | 65                                                 |  |  |  |

|      | 12.1<br>12.2<br>12.3                                                 | Converter Modeling                                  | 65<br>67<br>68<br>69<br>69<br>72                   |  |  |  |

| 13   | Simul                                                                | lation Results                                      | 74                                                 |  |  |  |

|      | 13.1<br>13.2<br>13.3<br>13.4                                         | Phase to Phase Fault with no STATCOM                | 74<br>76<br>78<br>81<br>81<br>82<br>83<br>84<br>85 |  |  |  |

| 14   | Concl                                                                | lusion                                              | 86                                                 |  |  |  |

| 15   | Futur                                                                | re Work                                             | 89                                                 |  |  |  |

| Refe | erences                                                              |                                                     | 90                                                 |  |  |  |

| A    | Symmetrical Components                                               |                                                     |                                                    |  |  |  |

| В    | Differential Mode and Common Mode Extraction for Scalar Quantities 9 |                                                     |                                                    |  |  |  |

| С | Netw  | ork Unbalances                                    |

|---|-------|---------------------------------------------------|

|   | C.1   | Network Unbalances During Faults                  |

|   |       | C.1.1 Grounded Network                            |

|   |       | C.1.2 Ungrounded Network                          |

|   | C.2   | Network Unbalances During Normal Operation        |

|   |       | C.2.1 Transmission Line Unbalanced Impedances 113 |

|   |       | C.2.2 Unbalanced loads                            |

|   | C.3   | Summary                                           |

| D | Activ | e and Reactive Power Flow                         |

# LIST OF TABLES

| <u>Table</u> |                                                |  |  |  |  |  | <u>r</u> | age |

|--------------|------------------------------------------------|--|--|--|--|--|----------|-----|

| 3–1          | Valid switch combinations in a full-bridge VSC |  |  |  |  |  |          | 15  |

| 11–1         | Summary of STATCOM topology comparison .       |  |  |  |  |  |          | 64  |

| C-1          | Summary of Voltage Unbalances Due to Faults    |  |  |  |  |  |          | 117 |

#### LIST OF FIGURES

| Figure |                                                                                                                                                        | page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2-1    | Two bus network with active/reactive power flow                                                                                                        | 7    |

| 2-2    | Typical STATCOM single-line diagram                                                                                                                    | 8    |

| 2–3    | Simple STATCOM control scheme for positive sequence voltage control                                                                                    | 9    |

| 2-4    | Simple Phase-Locked Loop                                                                                                                               | 10   |

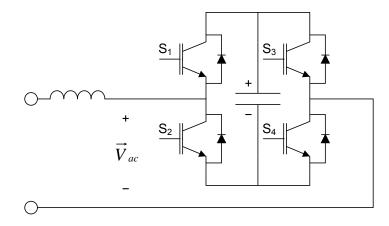

| 3-1    | Single-phase, full-bridge voltage source converter                                                                                                     | 15   |

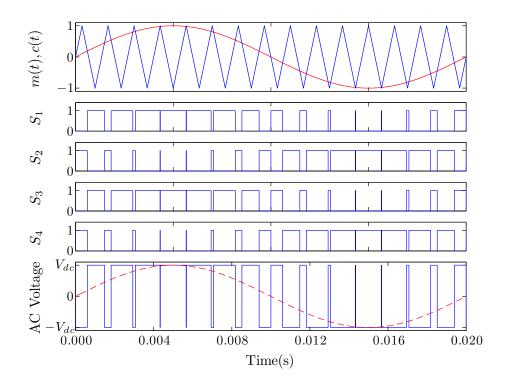

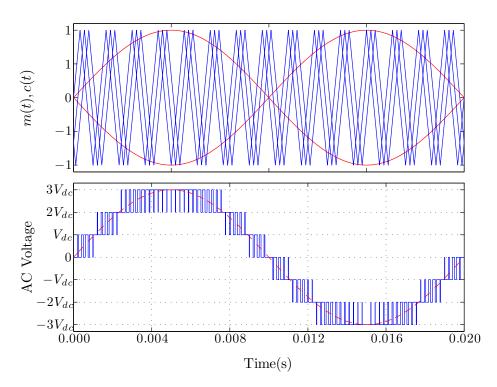

| 3-2    | SPWM for a full-bridge bipolar switching VSC                                                                                                           | 16   |

| 3-3    | SPWM for a full-bridge uni-polar switching VSC                                                                                                         | 17   |

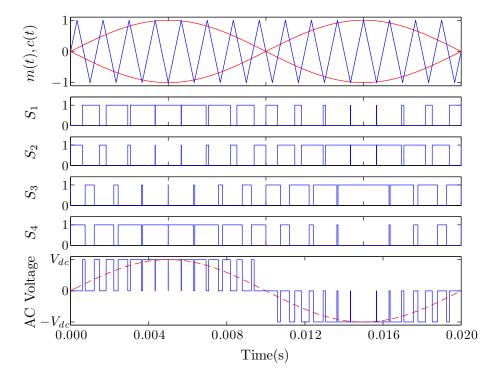

| 3-4    | Modular Multilevel Converter based chain-link VSC                                                                                                      | 18   |

| 3–5    | SPWM for a full-bridge uni-polar switching MMC chain-link VSC using three cells                                                                        | 19   |

| 5-1    | Delta-Coupled Chain-Link STATCOM                                                                                                                       | 26   |

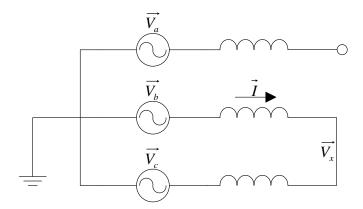

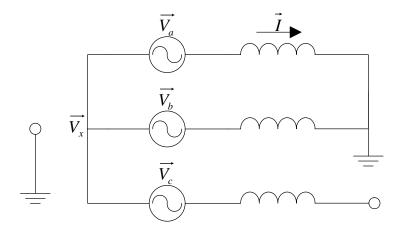

| 6–1    | Ungrounded Wye-Coupled Chain-Link STATCOM                                                                                                              | 31   |

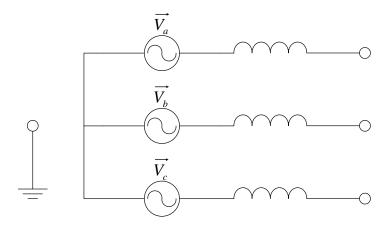

| 7–1    | Grounded Wye-Coupled Chain-Link STATCOM                                                                                                                | 34   |

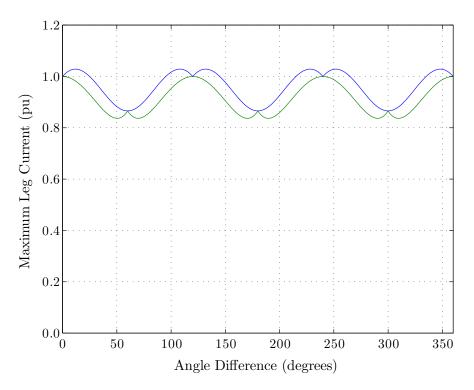

| 8-1    | Optimization of leg currents using common mode active power flow                                                                                       | 45   |

| 10-1   | Un-grounded Double Wye-Coupled Chain-Link STATCOM                                                                                                      | 50   |

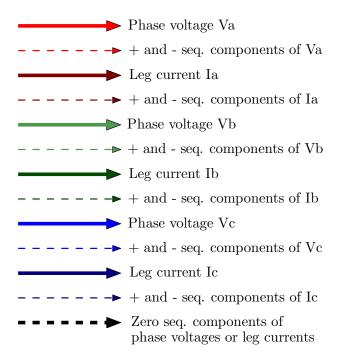

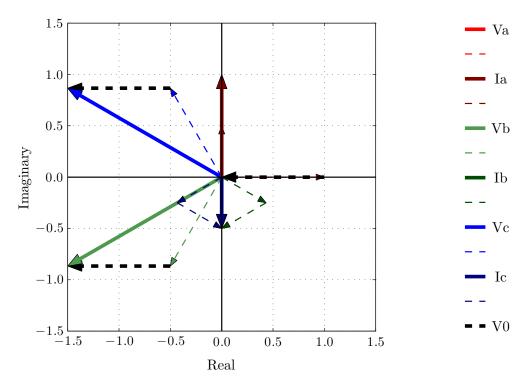

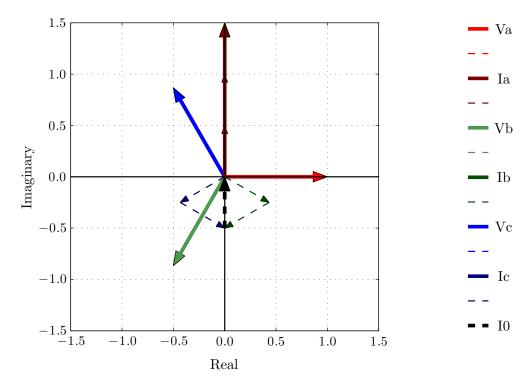

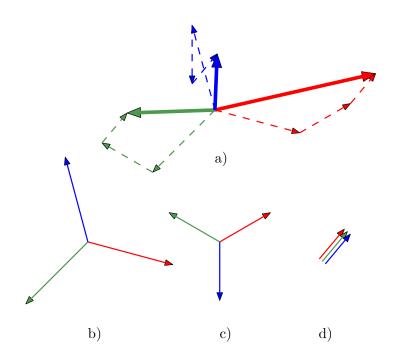

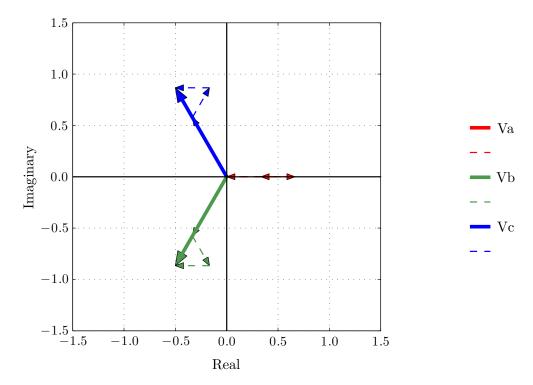

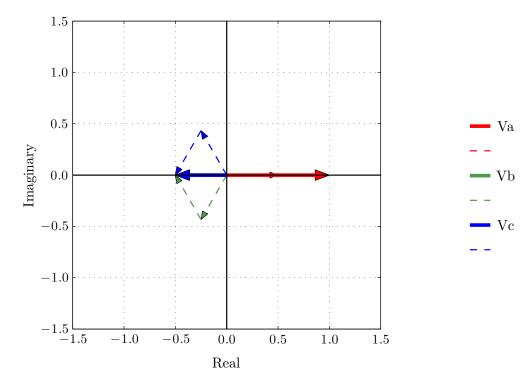

| 11–1   | Legend for interpreting phasor diagrams                                                                                                                | 57   |

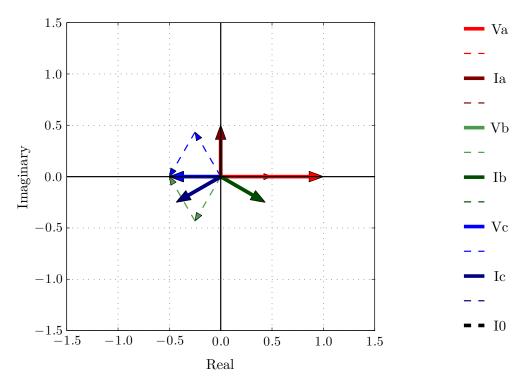

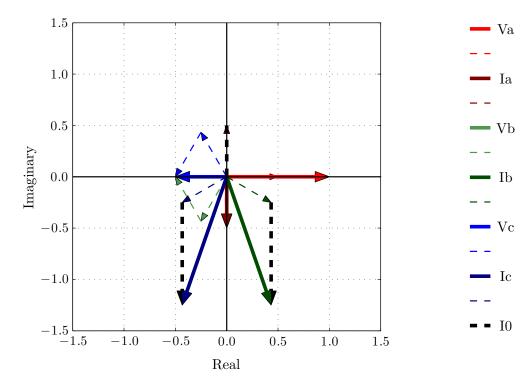

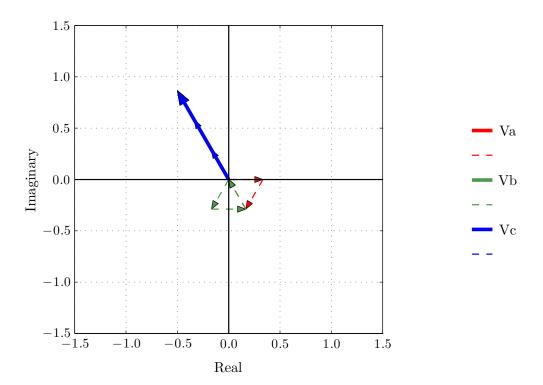

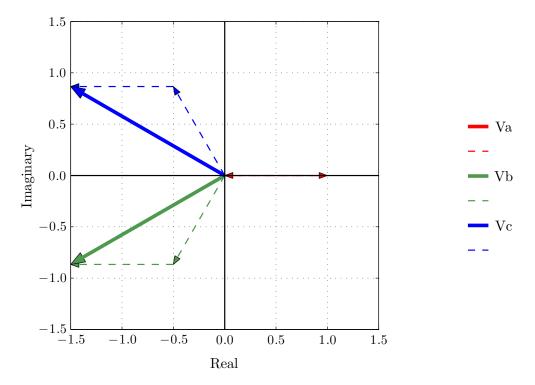

| 11–2   | Phase Voltages and Positive Sequence Leg Currents in a Delta-<br>Coupled STATCOM During a Phase to Phase Fault                                         | 58   |

| 11–3   | Phase Voltages and Positive Sequence Leg Currents in a Delta-<br>Coupled STATCOM During a Phase to Phase Fault with Zero<br>Sequence Current Injection | 59   |

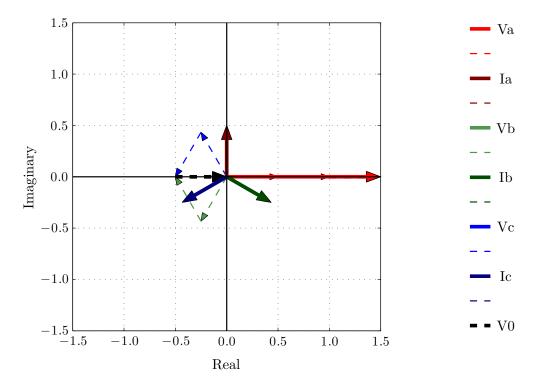

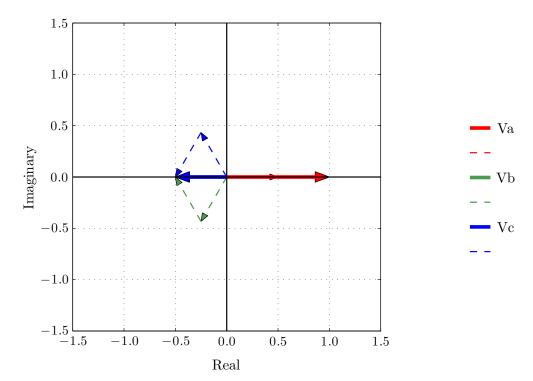

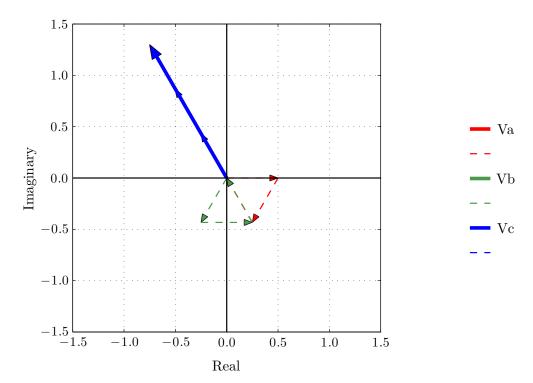

| 11–4 Phase Voltages and Positive Sequence Leg Currents in a Wye-<br>Coupled STATCOM During a Phase to Phase Fault with Zero<br>Sequence Voltage Injection | 60 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 11–5 Positive Sequence Phase Voltages and Unbalanced Leg Currents in a Wye-Coupled STATCOM                                                                | 61 |

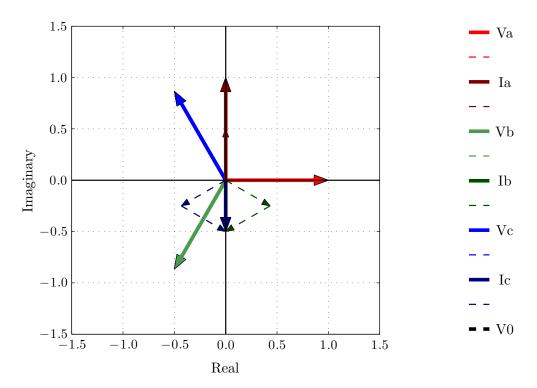

| 11–6 Positive Sequence Phase Voltages and Unbalanced Leg Currents in a Wye-Coupled STATCOM with Zero Sequence Voltage Injection                           | 62 |

| 11–7 Positive Sequence Phase Voltages and Unbalanced Leg Currents in a Delta-Coupled STATCOM with Zero Sequence Current Injection                         | 63 |

| 12–1 Test circuit used in $Matlab/Simulink$ simulations                                                                                                   | 65 |

| 12–2 Simplified test circuit used in $Matlab/Simulink$ simulations                                                                                        | 66 |

| 12–3 Modeling of converter cells as controllable voltage sources                                                                                          | 66 |

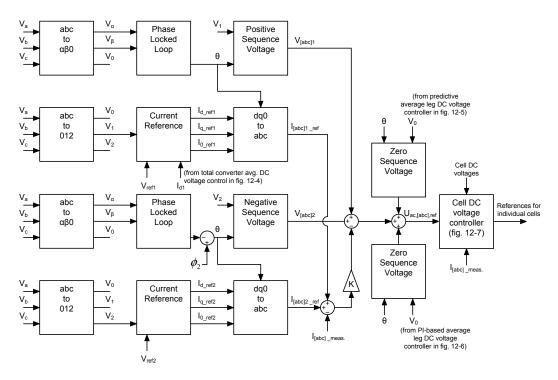

| 12–4 Full controls of the STATCOM                                                                                                                         | 68 |

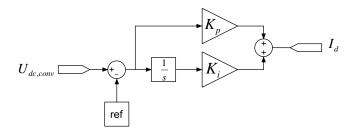

| 12–5 Control loop for total converter average DC voltage                                                                                                  | 69 |

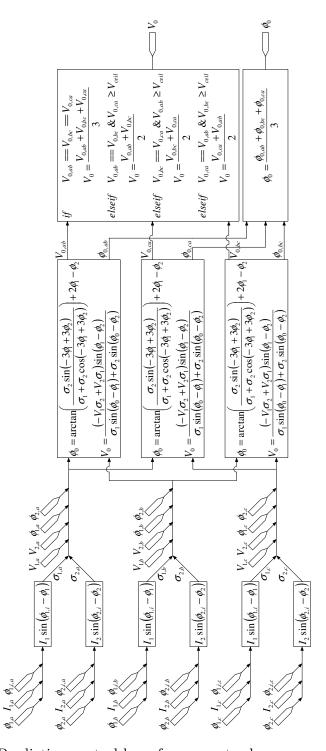

| 12–6 Predictive control loop for converter leg average DC voltage                                                                                         | 70 |

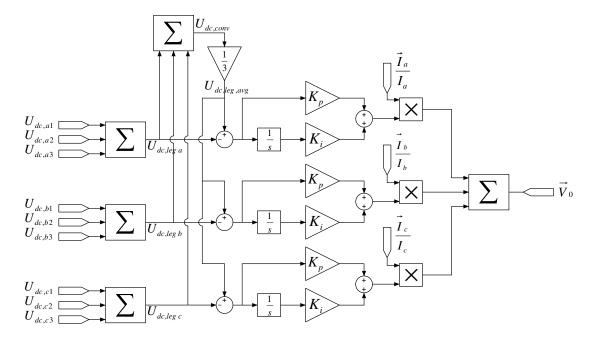

| 12–7 PI control loop for converter leg average DC voltage                                                                                                 | 71 |

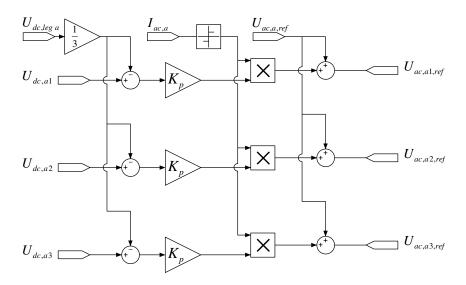

| 12–8 Control loop for converter cell voltage (phase a)                                                                                                    | 72 |

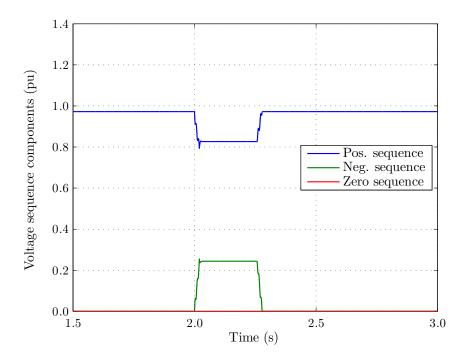

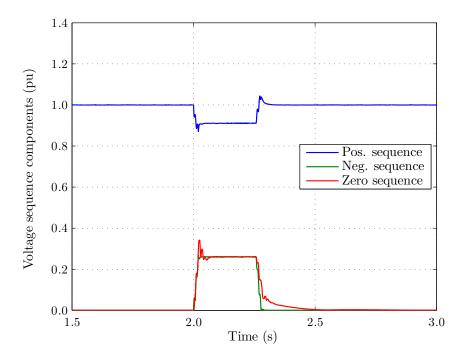

| 13–1 Sequence voltages (STATCOM inactive)                                                                                                                 | 75 |

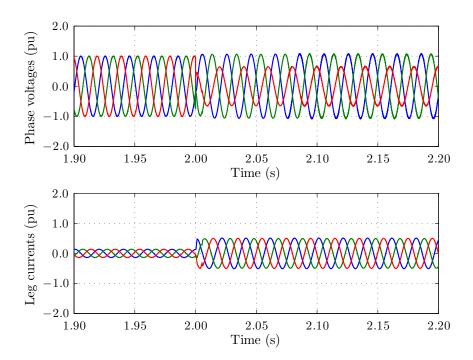

| 13–2 Phase voltages and currents (STATCOM inactive)                                                                                                       | 75 |

| 13-3 Sequence voltages (STATCOM active but no DC voltage control) .                                                                                       | 76 |

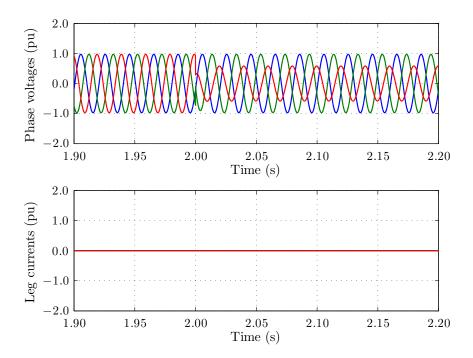

| 13–4 Phase voltages and currents (STATCOM active but no DC voltage control)                                                                               | 77 |

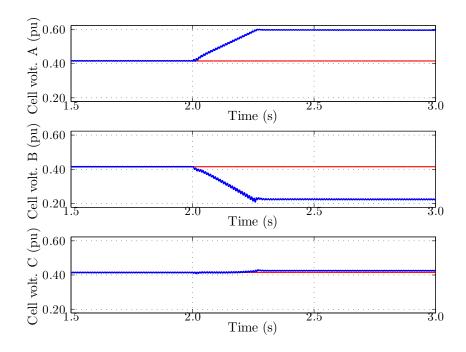

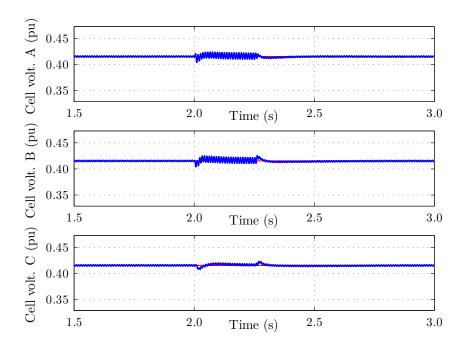

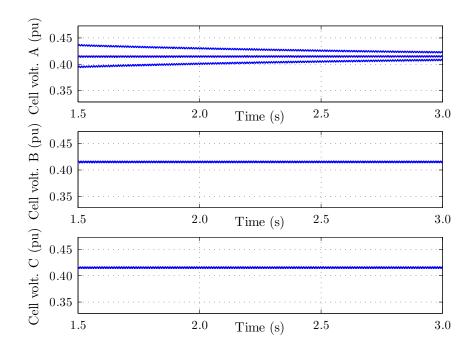

| 13–5 Cell voltages (STATCOM active but no DC voltage control)                                                                                             | 78 |

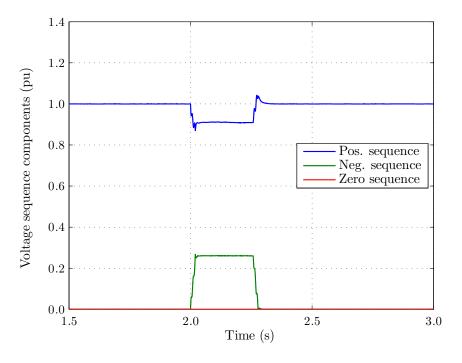

| 13–6 Sequence voltages (STATCOM active and DC voltage control enabled)                                                                                    | 79 |

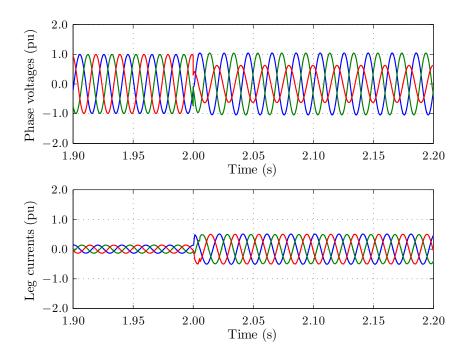

| 13–7 Phase voltages and currents (STATCOM active and DC voltage control enabled)                                                                          | 80 |

| 13–8 Cell voltages (STATCOM active and DC voltage control enabled) .                                                                                      | 80 |

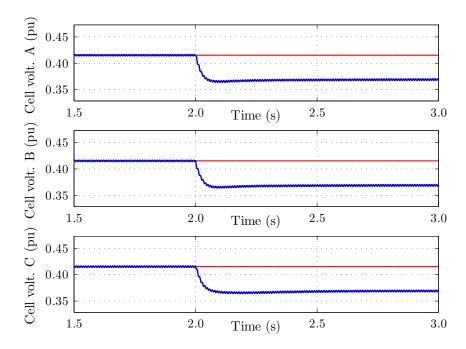

| 13–9 Cell voltages after a step in total converter avg. DC voltage reference                                                                              | 81 |

| 13–10 Cell voltages (PI controller for leg avg. DC voltage disabled)                                                                                      | 82 |

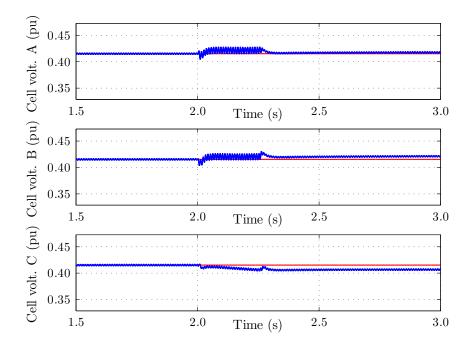

| 13–11 Cell voltages (Predictive leg avg. DC voltage controller disabled) . 83      |

|------------------------------------------------------------------------------------|

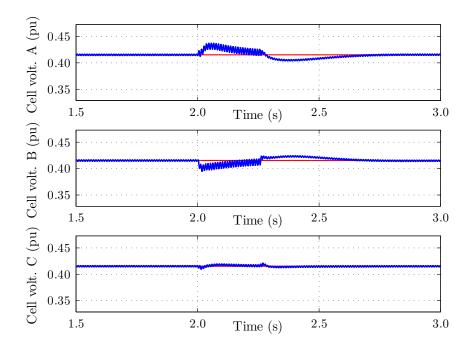

| 13–12 Unbalanced cell voltages within the same phase (phase A) 85                  |

| A-1 Symmetrical components                                                         |

| C–1 Grounded Net                                                                   |

| C–2 Phase voltages during a single phase to ground fault in phase a 102            |

| C-3 Phase voltages during a two phase to ground fault in phases a and b 103        |

| C–4 Phase to Phase fault in a grounded network                                     |

| C–5 Phase voltages during a phase to phase fault between phases b and c $105$      |

| C–6 Ungrounded Network                                                             |

| C–7 Phase voltages during a single phase to ground fault in phase a 108            |

| C–8 Two-Phase to Ground Fault in an Ungrounded Network 109                         |

| C-9 Phase voltages during a two phase to ground fault in phases a and b 110        |

| C–10<br>Phase voltages during a phase to phase fault between phases b and c<br>112 |

| C–11 Typical three-phase transmission line                                         |

| D-1 Transmission line and active/reactive power flow                               |

|                                                                                    |

#### LIST OF ABBREVIATIONS

AC: Alternating Current

DC: Direct Current

FACTS: Flexible Alternating Current Transmission Systems

HVDC: High Voltage Direct Current

IGBT: Integrated Gate Bipolar Transistor

KCL: Kirchhoff's Current Law

KVL: Kirchhoff's Voltage Law

MMC: Modular Multilevel Converter

PI: Proportional-Integral

PLL: Phase Locked Loop

PWM: Pulse Width Modulation

SPWM: Sinusoidal Pulse Width Modulation

STATCOM: Static Synchronous Compensator

SVC: Static var Compensator

TCSC: Thyristor Controlled Series Capacitor

VSC: Voltage Source Converter

#### CHAPTER 1 Introduction

With the ever increasing need for energy, many power transmission networks are reaching their limits. Building new transmission lines could possibly alleviate this problem, but the associated cost is extremely high, and the level of urbanization in many regions often makes this impossible. One possible solution is to optimize existing networks.

Given that networks need a stability margin in order to cope with transient events, the power transmission capabilities cannot be increased up to the thermal limits of lines and transformers. However, if the size and severity of these transient events can be reduced, the necessary margin can also be reduced, and more transmission capability can be obtained from the same network.

Several devices can be used in order to improve network transient stability. One such device is the Static Synchronous Compensator or STATCOM as it will be referred to from here on. In addition to improving network transient stability, STATCOMs can also be used for voltage support and to improve power quality in many industrial processes. Utilities impose strict power quality requirements on industries, and the costs associated with the penalties for not fulfilling these requirements are quite high. Therefore, STATCOMs are often a worthwhile investment for large industrial customers.

For these reasons, much research in the field of STATCOM technologies has occured in the last decades, and the arrival of new converter topologies has generated new challenges and created the need for more sophisticated control strategies. One of these innovations has been the advent of modular multilevel converters (MMC). MMC based topologies have many advantages over other converter topologies, namely the modularity of the design, but also the increased effective switching frequency which reduces the harmonics on the AC side. However, this modularity comes at a cost: The increased complexity of the system requires more sophisticated controls.

One of the main differences with MMC based converters is that they are composed of many modules or cells which each have a DC capacitor. This means that several DC voltages need to be controlled. For a STATCOM application under normal conditions with balanced phase voltages and currents, the converter provides only reactive power. However, in unbalanced conditions, the converter will supply/absorb unbalanced active power. In other words, each phase will supply/absorb a different amount of active power. This flow of active power changes the DC capacitor voltages, and this is of course not sustainable. The purpose of this thesis is therefore to define the problem of DC capacitor voltage balancing in MMC based STATCOMs, and to solve this problem for four different STATCOM topologies. A comparison of the advantages and disadvantages of each converter topology is then performed.

Chapters 2 and 3 of this thesis are dedicated to giving a brief overview of the basic purpose of STATCOMs as well as the operating principles of Voltage Source Converters (VSCs).

Chapter 4 presents a detailed explanation of the problem of capacitor DC voltage balancing. The flow of active power into the STATCOM legs is separated

into common mode active power flow and differential mode active power flow. It is then explained that the common mode active power flow can be easily controlled by setting the correct angle between the positive and negative sequence current references and the positive and negative sequence voltages present on the network. The control of differential mode active power flow requires additional controls which are specific to the converter topology. The subsequent chapters describe the four STATCOM topologies which are studied in this thesis, and the applicable methods for differential mode active power flow control are developed.

One solution applicable to all topologies that are evaluated in this thesis is to control the voltage of each cell locally. This is done by comparing the cell voltage to a reference, and modifying the switching pattern of each cell in order to change the time during which each cell is conducting. By doing so, it is possible to control the average energy absorption of each cell over a switching cycle and therefore control the voltage of each cell. Such methods are for example described in [18], [21] and [22]. A similar method is used in this thesis and is described in chapter 9 and in section 12.3.3. The difference is that in this thesis, localized control for each cell is not the only method used. It is used as part of a scheme of nested control loops. The reason is that these localized methods rely on the detection of an error in DC voltage. The additional control loops used here rely on measured network voltages and STATCOM currents in order to anticipate DC voltage drift caused by unbalanced operation. These methods anticipate the error and take corrective measures in order to prevent it. They are therefore different from methods which rely on the detection of an error.

These additional methods are however dependant on the converter topology. For a single wye-coupled or delta-coupled converter supplying positive sequence currents to a network with unbalanced voltages, it is possible to impose a negative-sequence current that will cancel the flow of active power. Such methods are used, for example, in [5], [14] and [20]. This is not a preferred solution as the negative sequence currents increase the unbalance condition in the network. Furthermore, this method imposes a restriction on the operating range of the STATCOM. Indeed, it is not possible to provide any wanted positive sequence currents and negative sequence currents simultaneously as they are related by the need to cancel active power flow.

Chapter 6 presents another solution for the wye-coupled converter which is to impose a zero-sequence voltage on the neutral point of the converter. Such a method is presented in [19]. A similar method is developed in this thesis, with the difference that the calculation of the zero sequence voltage is simplified. This method does not create additional unbalance in the network, and is flexible in the sense that positive-sequence currents and negative sequence currents can be chosen somewhat independently. It can be shown that it is not always possible to find a finite zero-sequence voltage that will cancel the flow of active power if both a negative sequence current and a positive sequence current need to be supplied. Furthermore, this method requires that the converter be rated for a much higher voltage than the nominal system voltage.

Chapters 5 and 7 present the methods applicable to a delta-coupled converter or a wye-coupled converter with a neutral current path respectively. Both of these methods are based on the use of a zero-sequence current. A similar method to the ones which are developed in these chapters are also described in [4], [5] and [20] but again, the method presented for calculating the zero-sequence current reference produced by the converter assumes balanced leg currents, and is therefore not a general method. Moreover, the methods presented in this thesis are developed

based on the calculation of a differential power vector which is simpler and less cumbersome than the method described in [4], [5] and [20]. The zero-sequence current method does not require the converter to be overrated from a voltage perspective, however, it does require a higher current rating. It can also be shown for this method that it is not always possible to find a finite zero-sequence current that will cancel the flow of active power if both a positive sequence voltage and a negative sequence voltage are present in the network. This method also relies on the existence of a zero-sequence current path which requires the use of additional components such as a grounding transformer in the case of a wye-coupled converter.

Chapter 8 then explains how the exchange of common mode active power flow between the positive sequence and the negative sequence can be used in order to minimize the STATCOM leg currents and effectively increase the available reactive power output of the converter.

Chapter 9 gives a brief explanation of one more cause of DC capacitor unbalance which is the drift of cell DC voltages due to the non-ideal nature of components and switching patterns. A solution to this problem based on individual control of each cell is presented. This method is applicable regardless of the converter topology, and is used in conjunction with the common mode active power control and the differential mode active power control. Other methods such as selective swapping are described in [12]. The advantage of the method presented in this thesis is that it can be implemented locally for each cell and does not require centralized control.

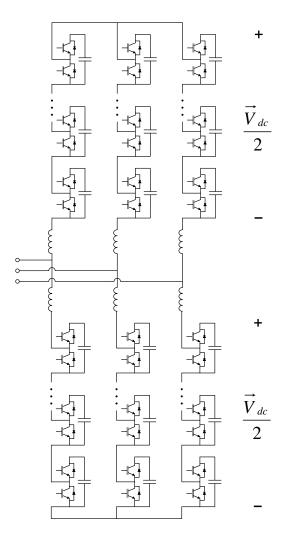

Chapter 10 presents a fourth converter topology. This converter is composed of two wye-coupled converters with their neutral points connected together (or not). This type of converter configuration is used in the latest non-traditional HVDC applications [9]. A control scheme for DC capacitor voltage balancing is

presented in [13], but this control scheme requires the existence of a path for neutral current. In this thesis, it is shown that for this converter configuration, all methods described previously are applicable, but there also exists another method. Indeed, it is possible to use DC currents to cancel the active power flow. Due to the fact that this method relies on DC quantities, it can be shown that there always exists a finite solution that will cancel the active power flow. However, it also requires a converter with a higher current rating. It will also be shown how combining these methods may result in a reduction of the converter stresses. However, due to its topology the double-wye coupled converter requires more leg reactors and DC capacitors than the single wye-coupled converter, and is therefore more expensive and has a larger footprint.

Chapter 11 presents a brief comparison of the advantages and disadvantages of each of the converter topologies. The comparison is mainly done on the basis of limitations of the operating ranges due to the necessity of balancing DC voltages. The cost and complexity of each topology are also briefly mentioned.

Chapter 12 presents one proposed implementation of the methods described above for a simple STATCOM containing three cells per phase. This implementation is directly scalable for a converter with more cells.

Chapter 13 presents the results of simulations which were performed in order to validate that the DC voltage control methods function correctly.

## CHAPTER 2 STATCOM Principles and Applications

The STATCOM, is one member of the large family of Flexible AC Transmission Systems Controllers (FACTS Controllers). In simple terms, the STATCOM is a shunt device which acts as a voltage source by controlling the amount of reactive power it absorbs or generates. This chapter briefly explains what STATCOMs are used for, and how they operate from a system point of view.

#### 2.1 STATCOM Principles

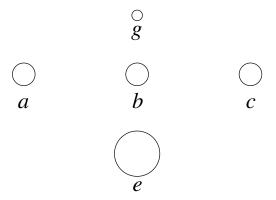

Starting from a two bus network such as the one shown in figure 2–1, one can derive the following equations for active and reactive power flow. The derivation

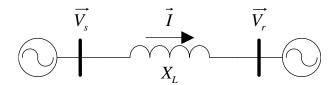

Figure 2–1: Two bus network with active/reactive power flow

is presented in appendix D and assumes that the angle between the sending end voltage and the receiving end voltage  $\delta$  is small.

$$P_r \approx -\frac{V_r V_s \delta}{X_L} \tag{2.1}$$

$$Q_r \approx \frac{V_r V_s}{X_L} - \frac{V_r^2}{X_L} = \frac{V_r (V_s - V_r)}{X_L}$$

(2.2)

As demonstrated by equation (2.2), if one assumes that  $V_s$  is constant, then changing  $Q_r$  will mainly have an impact on  $V_r$ . In the network of figure 2–1, the

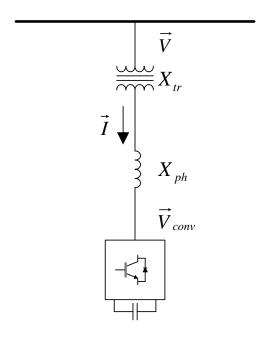

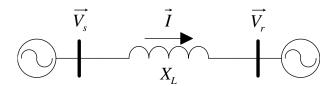

impedance  $X_L$  can be split into two parts. The first part can represent a Thevenin equivalent network together with the source  $V_s$ , and the second part can represent the combined transformer reactance and phase reactance of a STATCOM where the source  $V_r$  represents the converter. A schematic of a STATCOM is shown in figure 2–2. If the system is taken in per-unit, the transformer leakage inductance is

Figure 2–2: Typical STATCOM single-line diagram

lumped with the phase inductance of the STATCOM to form  $X_{stat}$ . If pure reactive power flow is assumed, the following relations can then be stated:

$$I = \frac{V - V_{conv}}{X_{stat}} \tag{2.3}$$

$$Q = \frac{1 - \frac{V_{conv}}{V}}{X_{stat}} V^2 \tag{2.4}$$

If  $V_{conv}$  is larger than V, the reactive power becomes negative and the STATCOM is therefore behaving as a capacitor. On the other hand, if  $V_{conv}$  is smaller than V, the reactive power becomes positive and the STATCOM is then behaving as a

reactor. In reality, a small amount of active power can flow into the STATCOM under certain conditions, and this will be dealt with in the subsequent chapters.

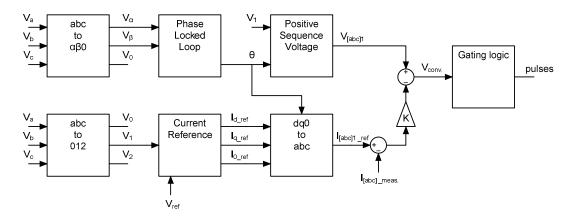

A simple control scheme is presented in figure 2–3 to control the positive sequence voltage at the STATCOM busbar. The busbar voltages are measured and

Figure 2–3: Simple STATCOM control scheme for positive sequence voltage control

transformed to the  $\alpha\beta0$  reference frame by applying the following transformation:

$$\begin{bmatrix} \vec{V}_{\alpha} \\ \vec{V}_{\beta} \\ \vec{V}_{0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} \vec{V}_{a} \\ \vec{V}_{b} \\ \vec{V}_{c} \end{bmatrix}$$

(2.5)

This transformation is also called the Clarke transformation [6], and for reference purposes, the inverse Clarke transformation is:

$$\begin{bmatrix} \vec{V}_a \\ \vec{V}_b \\ \vec{V}_c \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} & 1 \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} & 1 \end{bmatrix} \begin{bmatrix} \vec{V}_\alpha \\ \vec{V}_\beta \\ \vec{V}_0 \end{bmatrix}$$

(2.6)

The Clarke transformation is basically a projection of the three-phase quantities onto two orthogonal axes where the  $\alpha$  axis is in phase with phase a of the rotating three-phase system.

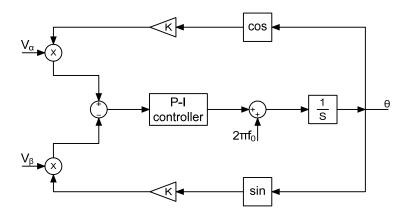

In order to obtain the positive sequence voltage and the d-q frame so as to implement the controls, it is necessary to acquire the argument  $\theta = \omega t + \phi$  of the a-phase voltage. Along the upper path of figure 2–3, the a-b-c frame voltages are transformed to the  $\alpha\beta0$  frame using equation 2.5 and then passed to the Phase Locked Loop (PLL) of figure 2–4 which acquires the argument  $\theta = \omega t + \phi$ . The design of a phase-locked loop is fairly complex in the sense that its behaviour must be optimized according to several design criteria such as the desired response time, the range of frequencies to which it must be able to latch on to, the behavior in the presence of a negative sequence component as well as the behavior in the presence of harmonics to name a few. A simple phase-locked loop is shown in figure 2–4. Once the angular position  $\theta$  is extracted by the PLL, it is used to reconstruct the

Figure 2–4: Simple Phase-Locked Loop

positive sequence voltage component of the phase voltages. This is simply done by implementing the following equation:

$$v_{a1}(t) = V_1 sin(\theta) \tag{2.7}$$

$$v_{b1}(t) = V_1 \sin(\theta - \frac{2\pi}{3})$$

(2.8)

$$v_{c1}(t) = V_1 \sin(\theta - \frac{4\pi}{3}) \tag{2.9}$$

In parallel to this, the phase voltages are also transformed into their sequence components using the following equation.

$$\begin{bmatrix} \vec{V}_0 \\ \vec{V}_1 \\ \vec{V}_2 \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 1 & 1 & 1 \\ 1 & a & a^2 \\ 1 & a^2 & a \end{bmatrix} \begin{bmatrix} \vec{V}_a \\ \vec{V}_b \\ \vec{V}_c \end{bmatrix}$$

(2.10)

where a is equal to  $e^{j\frac{2\pi}{3}}$ .

Equation (2.10) is derived in Appendix A. For a STATCOM application of positive sequence voltage support such as the one described here, the magnitude of the positive sequence current is computed based on the difference between the measured positive sequence voltage magnitude and the desired reference. The currents are computed in the dq0 reference frame and then transformed into the abc reference frame using equation 2.12 which is the inverse of the dq0 transformation. The dq0 transformation is:

$$\begin{bmatrix} I_d \\ I_q \\ I_0 \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta - \frac{4\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{4\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} I_a(t) \\ I_b(t) \\ I_c(t) \end{bmatrix}$$

(2.11)

and the inverse of the dq0 transformation is:

$$\begin{bmatrix} I_a(t) \\ I_b(t) \\ I_c(t) \end{bmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) & 1 \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) & 1 \\ \cos(\theta - \frac{4\pi}{3}) & -\sin(\theta - \frac{4\pi}{3}) & 1 \end{bmatrix} \begin{bmatrix} I_d \\ I_q \\ I_0 \end{bmatrix}$$

(2.12)

The dq0 is also a projection of the three-phase quantities onto two orthogonal axes where the d and q axes are orthogonal to each other, but this time they rotate at the same angular velocity  $\theta = \omega t$  as the three-phase quantities. The d axis is in phase with phase a of the three-phase system at t = 0 and at every cycle. One

reason for using a current reference in the dq0 reference frame is that by using the angle  $\theta = \omega t$  of the three-phase voltages produced by the PLL, the d component of the current then corresponds to a three-phase quantity which is in phase with the three-phase voltages. Similarly, the q component of the current corresponds to a three-phase quantity in quadrature with the three-phase voltages. In the dq frame, the active and reactive power are therefore:

$$P = V_d I_d + V_a I_a \tag{2.13}$$

$$Q = V_d I_q - V_q I_d \tag{2.14}$$

When the PLL is locked on to phase a,  $V_q = 0$ . Therefore:

$$P = V_d I_d \tag{2.15}$$

$$Q = V_d I_q \tag{2.16}$$

In other words, the d component of the current carries only active power whereas the q component of the current carries only reactive power. Since the desired operation of the STATCOM is to exchange only reactive power with the network, the reference current needed to support the positive sequence voltage should only have a q component. Once the current reference is transformed from the dq0 reference frame to a three-phase quantity, the measured phase currents are subtracted from it, the result is scaled by a proportional gain, and then subtracted from the positive sequence voltage which was reconstructed earlier. The result becomes the voltage reference that the converter will follow.

#### 2.2 STATCOM Applications

The uses for STATCOMs and shunt compensation in general are multiple. In the context of transmission networks, they are often used for:

- End of line voltage support in order to prevent voltage instability. An example of this would be for voltage support at a load center in the event of load fluctuations or loss of one of several feeders.

- Improvement of transient stability, an example of which would be to provide fast dynamic voltage support during faults in order to avoid loss of synchronism of generators.

- Power oscillation damping in poorly damped power systems. Disturbances in poorly damped networks will have the tendancy to create mechanical oscillations in the rotors of generators, thus changing the voltage angle and creating oscillations in the active power transmitted.

In addition to the applications stated above, other applications exist which are more specific to industrial processes. These include:

- Flicker compensation for loads with a very stochastic behavior. An example of this would be flicker compensation for arc furnaces.

- Low order harmonic cancellation. STATCOMs being devices with a very fast response time, they are capable of cancelling the first few harmonic orders created by non-linear loads.

- Compensation of load unbalances. As will be seen in later chapters, STAT-COMs are capable of generating unbalanced currents. This property can be used to compensate for unbalanced three-phase loads.

Additional information and more detailed explanations about some of these applications can be found in [10], [15] and [16]. The following chapter explains how the actual converter is implemented, and how it operates.

# CHAPTER 3 Voltage Source Converters

This chapter explains what a Voltage Source Converter is, and describes how several of them can be connected to create a Modular Multilevel Converter (MMC).

#### 3.1 Principles of a Basic Voltage Source Converter

The conventional thyristor, used in several FACTS devices such as the Static Var Compensators (SVC) or the Thyristor-Controlled Series Capacitors (TCSC) can be triggered to turn-on at any point on the half-cycle of voltage waveform during which the device is positively biased. However, the turn-off cannot be controlled. The device can only stop conducting once the current flowing through it goes to zero. Other devices such as the Integrated Gate Bipolar Transistor (IGBT) have both turn-on and turn-off capability. These devices therefore enable new converter concepts which can have significant cost and performance advantages [17]. One such converter type is the voltage source converter (VSC). The VSC concept can be applied to single-phase or multi-phase converters using either half-bridges or full-bridges. A single-phase, full bridge VSC is presented in figure 3-1. This converter is presented here in more detail because it is the building block of the STATCOMs which will be discussed in subsequent chapters. The VSC is composed of one DC capacitor, one series AC reactor, as well as four switches and four antiparallel diodes. Since the DC voltage never changes polarities, anti-parallel diodes are sufficient to ensure operation in all four power quadrants. The four switches offer sixteen different on/off combinations. However, it is clear that closing both switches of the same leg at the same time, that is 1 and 2 or 3 and 4, would result in a short circuit across the capacitor which is of course undesireable. Eliminating

Figure 3–1: Single-phase, full-bridge voltage source converter

all switch combinations which include two switches of the same leg being closed at the same time, as well as all four combinations where only one switch is closed (which are of no use), five combinations of interest remain. These combinations are given in table 3–1. The last combination is valid, but is of no great interest

Table 3–1: Valid switch combinations in a full-bridge VSC

| $S_1$ | $S_2$ | $S_3$ | $S_4$ | Voltage at terminals |

|-------|-------|-------|-------|----------------------|

| 1     | 0     | 0     | 1     | $+V_{dc}$            |

| 0     | 1     | 1     | 0     | $-V_{dc}$            |

| 1     | 0     | 1     | 0     | 0                    |

| 0     | 1     | 0     | 1     | 0                    |

| 0     | 0     | 0     | 0     | Open Circuit         |

since it simply results in the converter being idle. The other four combinations are of more interest because by alternately changing between them, the voltage across the VSC terminals can be made to follow an AC voltage reference. This is done through the process of Sinusoidal Pulse Width Modulation (SPWM).

The full-bridge VSC can operate with two switching schemes; either bipolar switching or uni-polar switching. Bipolar switching requires that diagonal switch pairs always have the same state, meaning that the converter can only operate

using the two first switch combinations. Uni-polar switching on the other hand, allows for the use of all four switch combinations.

The principle of SPWM is that the sinusoidal reference m(t) is compared to a triangular waveform c(t) called the carrier. In the bipolar switching scheme, when m(t) > c(t), switches 1 and 4 are on and switches 2 and 3 are off. When m(t) < c(t), switches 1 and 4 are off and switches 2 and 3 are on. Assuming that

Figure 3–2: SPWM for a full-bridge bipolar switching VSC

the DC capacitor is large enough so that the DC voltage remains constant, and that the frequency of c(t) is much higher than that of m(t), the average of the AC voltage over one switching period is equal to the duty cycle times the DC voltage. This situation is illustrated in figure 3–2. In the unipolar switching scheme, the on/off states of switches 1 and 2 are generated in exactly the same way as for the bipolar switching scheme. The on/off states of switches 3 and 4 are generated by

comparing -m(t) with c(t). when -m(t) < c(t), switch 4 is on and switch 3 is off. When -m(t) > c(t), switch 4 is off and switch 3 is on. This situation is illustrated in figure 3–3. The major advantage of the uni-polar switching scheme over the

Figure 3–3: SPWM for a full-bridge uni-polar switching VSC

bipolar scheme is that the generated waveform is a much better approximation to the reference waveform. The result is much lower harmonic distortion.

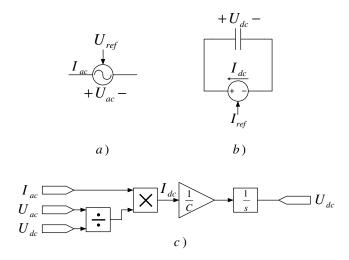

It should be noted that although this converter allows four quadrant operation, the flow of active power is restricted to exactly the amount necessary to replace the converter losses and maintain the DC capacitor voltage. Indeed, since the DC buses are not connected to a generator or load, a larger flow of active power would result in a change in DC capacitor voltage. In this configuration, the VSC is therefore more suitable for a STATCOM application since in this case, the converter supplies/absorbs reactive power.

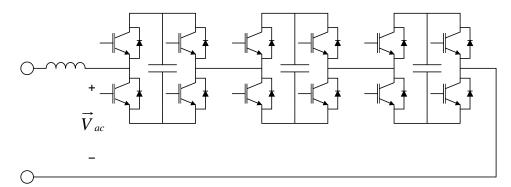

#### 3.2 Modular Multilevel Converter

The full-bridge VSC with uni-polar switching as described in the previous section cannot be used for applications with high voltages since the withstand capability of the switching devices is in the order of a few kilovolts. Furthermore, the AC-side voltage waveform at the output of the VSC of figure 3-1 has a fairly high harmonic content. A solution to the latter problem could be to increase the carrier frequency and therefore the switching frequency. This would indeed generate less lower order harmonics from the switching itself, however, this would also increase switching losses to an undesirable level. A better solution to the two problems stated above is to connect several VSCs in series. The result is that the total required AC voltage is then shared between several cells, and by staggering the switching pattern of the cells, it becomes possible to obtain an effective switching frequency which is much higher, thus obtaining a cleaner waveform. This type of converter is referred to as a chain-link Modular Multilevel Converter (MMC) due to the fact that it is composed of several identical cells (or modules) connected in a chain. An example of such an MMC based chain-link VSC with three cells is presented in figure 3–4. It should be noted that a single AC reactor is necessary

Figure 3–4: Modular Multilevel Converter based chain-link VSC

for the entire converter due to the series connection. It is also worth noting that

in theory, any number of cells can be connected in series. In order to achieve the staggering of the switching patterns, each cell uses the same AC reference, but the triangular carriers are shifted by an angle

$$\phi_{c,n} = \frac{\pi}{N}(n-1) \tag{3.1}$$

where  $\phi_{c,n}$  is the phase shift applied to the carrier of cell n, and N is the total number of series connected cells in the chain. Figure 3–5 shows the shifted triangular carriers as well as the resulting AC waveform for N=3.

Figure 3–5: SPWM for a full-bridge uni-polar switching MMC chain-link VSC using three cells

For the case of the single VSC in the previous section, the DC voltage on the capacitor had to be at least as high as the maximum AC voltage waveform to be reproduced in order to avoid overmodulation. In the case of the chain-link converter, it is the sum of all DC voltages that has to be at least as high as the maximum

AC voltage waveform to be reproduced. This clearly shows the suitability of the MMC chain-link converter for high voltage applications. Not surprisingly, the total number of voltage levels that can be reproduced is proportional to the number of cells.

$$n_{levels} = 2N + 1 \tag{3.2}$$

The AC waveform presented in figure 3–5 is a much better approximation to the AC reference than the AC waveforms in figures 3–2 and 3–3. By increasing the number of cells in a given converter, the harmonic content of the AC waveform is reduced to a point where AC harmonic filters may no longer be required. The following chapter will describe one of the problem which MMC based STATCOMs are faced with when operating in unbalanced network conditions.

# CHAPTER 4 The Problem of DC Capacitor Voltage Balancing

The STATCOM described as a three phase voltage source in chapter 2 can be constructed by using individual MMC-based VSCs such as the one shown in figure 3–4 for each phase. Several different topologies can be acheived by connecting the VSCs in different ways. For example, two of the simplest and more intuitive topologies are the wye-coupled converters, where each phase of the STATCOM is connected phase-to-ground, and the delta-coupled converters, where each phase of the STATCOM is connected phase-to-phase. Variants of these topologies as well as other topologies also exist. However, all of them suffer from the same problem which is DC capacitor voltage unbalance. The present chapter will describe the problem, and the subsequent chapters will present the main converter topologies of interest as well as the applicable solutions for balancing these DC capacitor voltages.

As explained earlier, except for the active power needed to replace the losses in the converter, a STATCOM should only exchange reactive power with the network. A larger (or smaller) exchange of active power would result in a change of the DC voltages of the capacitors since these DC buses are floating. For now, and until section 12.1, converter losses will be neglected in order to simplify the explanation. Therefore, under normal operation in a network having only a positive sequence voltage, it can be assumed that the STATCOM will generate a positive sequence current which is either purely capacitive or purely inductive (or zero). However, in unbalanced conditions such as those explained in appendix C, if, for example, the STATCOM is to supply positive sequence reactive power, it will also

supply/absorb active and reactive power due to the product of positive sequence current with negative sequence and zero sequence voltage. Furthermore, not only will the STATCOM exchange active power with the network, but it will do so in an unbalanced way. That is, the active power flowing in/out of each phase will be different.

In order to quantify and understand how this occurs, let us first consider the general case where STATCOM voltages and currents have positive sequence, negative sequence and zero sequence components ("1", "2" and "0" sub-indices).

$$\vec{V}_a = \vec{V}_{a0} + \vec{V}_{a1} + \vec{V}_{a2} \tag{4.1}$$

$$\vec{V}_b = \vec{V}_{b0} + \vec{V}_{b1} + \vec{V}_{b2} \tag{4.2}$$

$$\vec{V}_c = \vec{V}_{c0} + \vec{V}_{c1} + \vec{V}_{c2} \tag{4.3}$$

$$\vec{I}_a = \vec{I}_{a0} + \vec{I}_{a1} + \vec{I}_{a2} \tag{4.4}$$

$$\vec{I_b} = \vec{I_{b0}} + \vec{I_{b1}} + \vec{I_{b2}} \tag{4.5}$$

$$\vec{I}_c = \vec{I}_{c0} + \vec{I}_{c1} + \vec{I}_{c2} \tag{4.6}$$

The equations above use a simplified notation for the sequence components in each phase quantity. For the full expression of each component, the reader may refer to Appendix A. The active power flowing in each phase is the dot product of voltage and current which gives

$$P = \vec{V} \cdot \vec{I} \tag{4.7}$$

$$= (\vec{V}_0 + \vec{V}_1 + \vec{V}_2) \cdot (\vec{I}_0 + \vec{I}_1 + \vec{I}_2) \tag{4.8}$$

$$= \vec{V}_0 \cdot \vec{I}_0 + \vec{V}_0 \cdot \vec{I}_1 + \vec{V}_0 \cdot \vec{I}_2 + \vec{V}_1 \cdot \vec{I}_0 + \vec{V}_1 \cdot \vec{I}_1 +$$

$$\vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_0 + \vec{V}_2 \cdot \vec{I}_1 + \vec{V}_2 \cdot \vec{I}_2 \tag{4.9}$$

By applying the transformation developed in appendix B to equation 4.9 for all three phases of the STATCOM, it is possible to identify the terms of equation 4.9 which result in a balanced flow of active power, and those which result in an unbalanced flow of active power.

$$\begin{bmatrix} x_{1,diff} \\ x_{2,diff} \\ x_{comm} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} P_a \\ P_b \\ P_c \end{bmatrix}$$

(4.10)

The  $P_a$ ,  $P_b$  and  $P_c$  are the expressions for active power flow into each phase as given by equation 4.9. In equation 4.10, the  $x_{comm}$  term represents the common mode power, that is, the power which is common to all three phases, whereas the  $x_{1,diff}$ and  $x_{2,diff}$  terms represent together the differential mode power, that is, the power which is unbalanced in all three phases. Similar methods for finding the common mode and differential mode quantities of three phase variables are described in [8] and [23]. Applying this to the product of positive sequence voltage and positive sequence current,

$$\begin{bmatrix} P_{a11} \\ P_{b11} \\ P_{c11} \end{bmatrix} = \begin{bmatrix} Re\{V_1 \angle (\phi_{V1}) \cdot I_1 \angle (\phi_{I1})\} \\ Re\{V_1 \angle (\phi_{V1} - \frac{2\pi}{3}) \cdot I_1 \angle (\phi_{I1} - \frac{2\pi}{3})\} \\ Re\{V_1 \angle (\phi_{V1} - \frac{4\pi}{3}) \cdot I_1 \angle (\phi_{I1} - \frac{4\pi}{3})\} \end{bmatrix} = \begin{bmatrix} V_1 I_1 cos(\Delta \phi_{V1I1}) \\ V_1 I_1 cos(\Delta \phi_{V1I1}) \\ V_1 I_1 cos(\Delta \phi_{V1I1}) \end{bmatrix}$$

$$(4.11)$$

we get the following expression for differential mode and common mode power.

$$\begin{bmatrix} x_{1,diff} \\ x_{2,diff} \\ x_{comm} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ V_1 I_1 cos(\Delta \phi_{V1I1}) \end{bmatrix}$$

$$(4.12)$$

As expected, the product of positive sequence voltage and positive sequence current gives only common mode power. Now, applying the same procedure to the product of positive sequence voltage and negative sequence current,

$$\begin{bmatrix} P_{a12} \\ P_{b12} \\ P_{c12} \end{bmatrix} = \begin{bmatrix} Re\{V_1 \angle (\phi_{V1}) \cdot I_2 \angle (\phi_{I2})\} \\ Re\{V_1 \angle (\phi_{V1} - \frac{2\pi}{3}) \cdot I_2 \angle (\phi_{I2} - \frac{4\pi}{3})\} \\ Re\{V_1 \angle (\phi_{V1} - \frac{4\pi}{3}) \cdot I_2 \angle (\phi_{I2} - \frac{2\pi}{3})\} \end{bmatrix} = \begin{bmatrix} V_1 I_2 cos(\Delta \phi_{V1I2}) \\ V_1 I_2 cos(\Delta \phi_{V1I2} + \frac{2\pi}{3}) \\ V_1 I_2 cos(\Delta \phi_{V1I2} - \frac{2\pi}{3}) \end{bmatrix}$$

$$(4.13)$$

we get the following expression for differential mode and common mode power.

$$\begin{bmatrix} x_{1,diff} \\ x_{2,diff} \\ x_{comm} \end{bmatrix} = \begin{bmatrix} V_1 I_2 cos(\Delta \phi_{V1I2}) \\ -V_1 I_2 \left(\frac{1}{2} cos(\Delta \phi_{V1I2}) + \frac{\sqrt{3}}{2} sin(\Delta \phi_{V1I2})\right) \\ 0 \end{bmatrix}$$

(4.14)

The product of positive sequence voltage and negative sequence current gives only differential mode power. In fact, the previous analysis can be done for all the terms in equation 4.9, and the result is that the product of same sequence voltages and currents gives only common mode power whereas the product of different sequence voltages and currents gives only differential mode power.

$$\begin{vmatrix}

\vec{V}_{0} \cdot \vec{I}_{1} \\

\vec{V}_{0} \cdot \vec{I}_{0} \\

\vec{V}_{1} \cdot \vec{I}_{1} \\

\vec{V}_{2} \cdot \vec{I}_{2}

\end{vmatrix} \Rightarrow x_{comm}$$

$$\begin{vmatrix}

\vec{V}_{0} \cdot \vec{I}_{1} \\

\vec{V}_{1} \cdot \vec{I}_{0} \\

\vec{V}_{1} \cdot \vec{I}_{2} \\

\vec{V}_{2} \cdot \vec{I}_{0} \\

\vec{V}_{2} \cdot \vec{I}_{1}

\end{vmatrix} \Rightarrow x_{diff}$$

$$(4.15)$$

The common mode power terms cause a uniform change of capacitor voltage in all phases. This situation can usually be prevented by properly defining the current reference of the STATCOM so that all sequence currents are out of phase by  $\pm \frac{\pi}{2}$  with respect to the voltages of the same sequence. The differential mode power terms on the other hand, cause an unbalanced change of capacitor voltage in each of the phases. Methods for preventing this situation depend on the configuration of the converter, and will be the focus of the subsequent chapters.

# CHAPTER 5 Delta-Coupled Chain-Link STATCOM

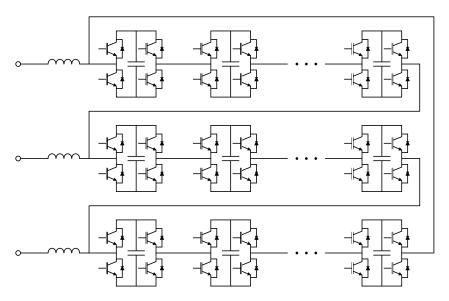

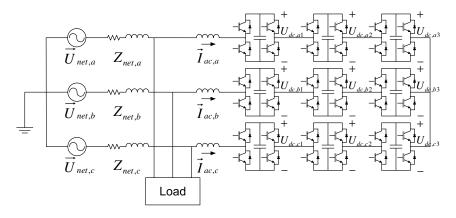

The first topology that is of interest is the delta-coupled chain-link STATCOM. The intent of this chapter is to describe this topology, and to solve the problem of capacitor DC voltage balancing which is described in chapter 4 for this specific topology. A schematic of the delta-coupled chain-link STATCOM is shown in figure 5–1. By delta-coupled, it is implied that the VSCs are connected between

Figure 5–1: Delta-Coupled Chain-Link STATCOM

phases of a three-phase system. The voltage reference developed in figure 2–3 is computed using phase to phase quantities, and is applied to the SPWM algorithm of section 3.2 for all cells of the three phases of the STATCOM in figure 5–1.

The currents and voltages to consider in the calculation of the previous chapter are of course the currents through the converter legs, and the voltages across them. In the case of the delta-coupled STATCOM, the currents are therefore the currents

inside the delta, while the voltages are the phase to phase voltages. This means that positive sequence, negative sequence and zero sequence currents can flow around the delta, however, only positive sequence voltages and negative sequence voltages are present across the legs since zero sequence voltages are eliminated due to the delta-connection. Equation 4.9 therefore reduces to

$$P = \vec{V}_1 \cdot \vec{I}_0 + \vec{V}_1 \cdot \vec{I}_1 + \vec{V}_1 \cdot \vec{I}_2 +$$

$$\vec{V}_2 \cdot \vec{I}_0 + \vec{V}_2 \cdot \vec{I}_1 + \vec{V}_2 \cdot \vec{I}_2$$

(5.1)

Considering a case where the following positive and negative sequence voltages are present while the STATCOM is providing positive sequence currents and negative sequence currents,

$$\vec{V}_1 = V_1 \angle \phi_1 \tag{5.2}$$

$$\vec{V}_2 = V_2 \angle \phi_2 \tag{5.3}$$

it is possible to choose

$$\vec{I}_1 = I_1 \angle \left(\phi_1 \pm \frac{\pi}{2}\right) \tag{5.4}$$

$$\vec{I}_2 = I_2 \angle \left(\phi_2 \pm \frac{\pi}{2}\right) \tag{5.5}$$

in order to ensure that

$$\vec{V}_1 \cdot \vec{I}_1 = 0 \tag{5.6}$$

$$\vec{V}_2 \cdot \vec{I}_2 = 0 \tag{5.7}$$

However, it cannot be guaranteed in all conditions that

$$\vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_1 = 0 \tag{5.8}$$

From equation 5.1 and from the fact that the STATCOM is delta-coupled, it is interesting to notice that another degree of freedom is available. That is, a zero sequence current reference can be imposed on the STATCOM which will not influence the phase currents outside the delta. However, inside the delta, this current can be used to cancel the effect of the remaining unbalance terms. In other words, the idea is to chose  $\vec{I_0}$  so that

$$\vec{V}_1 \cdot \vec{I}_0 + \vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_0 + \vec{V}_2 \cdot \vec{I}_1 = 0 \tag{5.9}$$

A different approach to the one developed here is used in [4] where an expression for  $\vec{I_0}$  is defined using space vectors for an application where a delta-coupled STAT-COM is compensating for an asymmetrical load. This is a specific case where only the differential power term  $\vec{V_1} \cdot \vec{I_2}$  needs to be cancelled. However, the space vector approach becomes somewhat cumbersome when trying to solve the general case of equation 5.9. The power vector approach is more suitable for deriving a full expression for  $\vec{I_0}$  in the general case.

In order to solve for  $\vec{I}_0$ , equation 5.9 can be rewritten in the following form:

$$Re \begin{pmatrix} \vec{V}_1 \vec{I}_0^* & \begin{bmatrix} 1 \\ a^2 \\ a \end{bmatrix} + \vec{V}_2 \vec{I}_0^* & \begin{bmatrix} 1 \\ a \\ a^2 \end{bmatrix} \end{pmatrix} = -Re \begin{pmatrix} \vec{V}_1 \vec{I}_2^* & \begin{bmatrix} 1 \\ a \\ a^2 \end{bmatrix} + \vec{V}_2 \vec{I}_1^* & \begin{bmatrix} 1 \\ a^2 \\ a \end{bmatrix} \end{pmatrix}$$

(5.10)

To obtain equation 5.10, equation 5.9 was expressed for each of the three phases, and the terms were reorganised so that the three rows of equation 5.10 represent the active power in each of the three phases. It is then possible to solve for  $\vec{I}_0$ . Indeed, there are two unknowns which are the magnitude and the phase of the zero sequence current. It is therefore required to solve two of the three rows of equation 5.10. In other words, since equation 5.10 contains only differential mode active power terms, if the active power flow is cancelled in two phases, it will

necessarily be zero in the third phase as well. Solving for example the first and second rows, one gets:

$$I_0 = \frac{\left(-V_1 I_2 sin(\phi_{2,i} - \phi_2) + V_2 I_1 sin(\phi_{1,i} - \phi_1)\right) sin(\phi_1 - \phi_2)}{V_1 cos(\phi_1 - \phi_0) + V_2 cos(\phi_2 - \phi_0)}$$

(5.11)

$$\phi_0 = -\arctan\left(\frac{V_1 + V_2\cos(-3\phi_1 + 3\phi_2)}{V_2\sin(-3\phi_1 + 3\phi_2)}\right) + 2\phi_1 - \phi_2 \tag{5.12}$$

The subscripts i in 5.11 denote that the angle in question is the angle of the current phasor. The other angles are related to the voltage phasors. The latter equations are valid only if sequence currents are orthogonal to the corresponding sequence voltages as described in equations 5.2 to 5.5. Therefore, the first two sine terms in the numerator of equation 5.11 simplify to  $\pm 1$  depending if the sequence currents are inductive or capacitive with respect the sequence voltages. In order to simplify the notation here and in further chapters, the following quantities will be defined:

$$\sigma_1 = I_1 sin(\phi_{1,i} - \phi_1) \tag{5.13}$$

$$\sigma_2 = I_2 sin(\phi_{2,i} - \phi_2) \tag{5.14}$$

Equation 5.11 then become:

$$I_0 = \frac{(-V_1\sigma_2 + V_2\sigma_1)\sin(\phi_1 - \phi_2)}{V_1\cos(\phi_1 - \phi_0) + V_2\cos(\phi_2 - \phi_0)}$$

(5.15)

Also, looking at equations 5.11 and 5.12, it is clear that the magnitude of the zero sequence current becomes zero for  $\phi_1 - \phi_2 = 0$  or  $\pi$ . However, this solution does not solve equation 5.9 and can therefore be considered degenerate. In fact, the first row of equation 5.10 becomes degenerate for  $\phi_1 - \phi_2 = 0$  or  $\pi$ , the second row becomes degenerate for  $\phi_1 - \phi_2 = -\frac{2\pi}{3}$  or  $\frac{\pi}{3}$  and the third row becomes degenerate for  $\phi_1 - \phi_2 = \frac{2\pi}{3}$  or  $\frac{5\pi}{3}$ .

In other words, each of the three equations becomes degenerate for a different angle difference between positive and negative sequence voltages. Referring to table C-1 in appendix C, the reader will realise that several fault cases result in an angle difference  $\phi_1 - \phi_2$  which causes one of the equations to become degenerate. Hence, in order to have a robust system which gives a correct solution in all conditions, all three combinations of two equations must be solved simultaneously. In that way, at least two of the three solutions will be correct at all times.

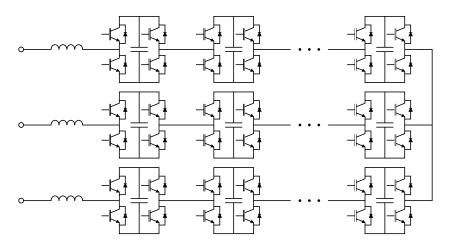

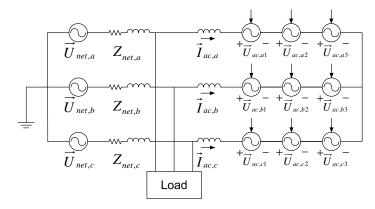

# CHAPTER 6 Ungrounded Wye-Coupled Chain-Link STATCOM

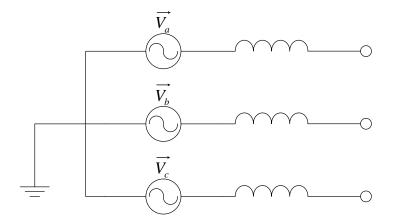

It is also possible to connect the single-phase chain-link VSCs to create an ungrounded wye-coupled STATCOM such as the one shown in figure 6–1. The current chapter describes this topology, and solves the problem of capacitor DC voltage balancing specific to this topology. The individual converter legs are con-

Figure 6–1: Ungrounded Wye-Coupled Chain-Link STATCOM

nected between the phase voltage and a floating neutral point. This means that a method analogous to the zero sequence current method of the previous chapter can be used in this case by applying a zero sequence voltage on the converter neutral point. Equation 4.9 therefore reduces to

$$P = \vec{V}_1 \cdot \vec{I}_1 + \vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_1 +$$

$$\vec{V}_2 \cdot \vec{I}_2 + \vec{V}_0 \cdot \vec{I}_1 + \vec{V}_0 \cdot \vec{I}_2$$

(6.1)

The zero sequence voltage can then be chosen such that the sum of all unbalanced active power terms is zero. In other words, the idea is to chose  $\vec{V}_0$  so that

$$\vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_1 + \vec{V}_0 \cdot \vec{I}_1 + \vec{V}_0 \cdot \vec{I}_2 = 0 \tag{6.2}$$

In order to solve for  $\vec{V}_0$ , equation 6.2 can be rewritten in the following form:

$$Re \begin{pmatrix} \vec{V}_0 \vec{I}_1^* & 1 \\ a \\ a^2 \end{pmatrix} + \vec{V}_0 \vec{I}_2^* & 1 \\ a \end{pmatrix} = -Re \begin{pmatrix} \vec{V}_1 \vec{I}_2^* & 1 \\ a \\ a^2 \end{pmatrix} + \vec{V}_2 \vec{I}_1^* & 1 \\ a^2 \\ a \end{pmatrix}$$

(6.3)

where each of the three rows represents the application of equation 6.2 in each of the three phases. It is then possible to solve for  $\vec{V}_0$ . Indeed, there are two unknowns which are the magnitude and the phase of the zero sequence voltage. It is therefore required to solve two of the three rows of equation 6.3. Solving for example the first and second rows, one gets:

$$V_0 = \frac{(-V_1\sigma_2 + V_2\sigma_1)sin(\phi_1 - \phi_2)}{\sigma_1 sin(\phi_0 - \phi_1) + \sigma_2 sin(\phi_0 - \phi_2)}$$

(6.4)

$$\phi_0 = \arctan\left(\frac{\sigma_2 \sin(-3\phi_1 + 3\phi_2)}{\sigma_1 + \sigma_2 \cos(-3\phi_1 + 3\phi_2)}\right) + 2\phi_1 - \phi_2 \tag{6.5}$$

As in the previous chapter, the latter equations are valid only if sequence currents are orthogonal to the corresponding sequence voltages as described in equations 5.2 to 5.5. The definitions of  $\sigma_1$  and  $\sigma_2$  are given in 5.13 and 5.14 respectively.

Also, looking at equations 6.4 and 6.5, it is clear that the magnitude of the zero sequence voltage becomes zero for  $\phi_1 - \phi_2 = 0$  or  $\pi$ . However, this solution does not solve the power balance equation 6.2. This solution can therefore be considered degenerate. In fact, the first row of equation 6.3 becomes degenerate

for  $\phi_1 - \phi_2 = 0$  or  $\pi$ , the second row becomes degenerate for  $\phi_1 - \phi_2 = -\frac{2\pi}{3}$  or  $\frac{\pi}{3}$  and the third row becomes degenerate for  $\phi_1 - \phi_2 = \frac{2\pi}{3}$  or  $\frac{5\pi}{3}$ .

In other words, each of the three equations becomes degenerate for a different angle difference between positive and negative sequence voltages. Referring to table C-1 in appendix C, the reader will realise that several fault cases result in an angle difference  $\phi_1 - \phi_2$  which causes one of the equations to become degenerate. Hence, in order to have a robust system which gives a correct solution in all conditions, all three combinations of two equations must be solved simultaneously. In that way, at least two of the three solutions will be correct at all times.

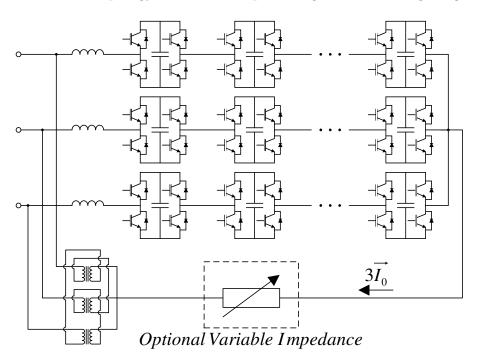

# CHAPTER 7 Grounded Wye-Coupled Chain-Link STATCOM

It is also possible to connect the single-phase chain-link VSCs to get a grounded wye-coupled STATCOM such as the one shown in figure 7–1. The current chapter describes this topology, and solves the problem of capacitor DC voltage balancing specific to this topology. The neutral point is grounded through a grounding

Figure 7–1: Grounded Wye-Coupled Chain-Link STATCOM

transformer, and the grounding path allows for a zero sequence current to flow. If the grounding path impedance is assumed to be negligible, the only contribution to the zero sequence voltage at the neutral point comes from the zero sequence voltage already present in the network (if any). In other words, the neutral is still floating with respect to ground and thus, no zero sequence voltage appears across the valves. This means that this converter is similar to the delta coupled converter of chapter 5, and equations 5.11 and 5.12 could still apply with the slight modification that the voltages to be controlled are the phase to ground voltages.

In practice however, the grounding path impedance is not negligible. This is due to the non-zero impedance of the grounding transformer, but it can also be due to the fact that a series impedance may be purposely added. In this case, the flow of zero sequence current will create a zero sequence voltage at the neutral point where the relation is:

$$\vec{V}_0 = 3Z_n \vec{I}_0 \tag{7.1}$$

The factor three arises from the fact that each phase contributes a current  $\vec{I_0}$  to the neutral current. The neutral impedance  $Z_n$  is a complex number representing the grounding path impedance. This grounding path impedance may be defined in three ways:

- Only grounding transformer impedance

- The sum of grounding transformer impedance and fixed series impedance

- The sum of grounding transformer impedance and variable series impedance. The first two cases are similar in the sense that the neutral path impedance has a fixed value. For the following derivation, a fixed neutral path impedance is assumed and  $Z_n$  will be expressed in polar coordinates as  $Z_0 \angle \zeta$ . Due to the existence of both a zero sequence voltage and a zero sequence current, all terms of equation 4.15 are present. In order to have no unbalanced active power flow, the following condition

must be met:

$$Re \begin{pmatrix} \vec{V}_{1}\vec{I}_{0}^{*} & 1 \\ \vec{V}_{1}\vec{I}_{0}^{*} & a^{2} \\ a \end{pmatrix} + \vec{V}_{2}\vec{I}_{0}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + \vec{V}_{0}\vec{I}_{1}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + \vec{V}_{0}\vec{I}_{2}^{*} & 1 \\ a \\ a^{2} \end{pmatrix}$$

$$= -Re \begin{pmatrix} \vec{V}_{1}\vec{I}_{2}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + \vec{V}_{2}\vec{I}_{1}^{*} & 1 \\ a \\ a^{2} \end{pmatrix}$$

$$(7.2)$$

Equation 7.2 can be simplified by using 7.1 to either solve for  $\vec{I_0}$  or  $\vec{V_0}$ . Solving for  $\vec{I_0}$  will result in the following expression:

$$Re \begin{pmatrix} \vec{V}_{1}\vec{I}_{0}^{*} & 1 \\ \vec{V}_{1}\vec{I}_{0}^{*} & a \end{pmatrix} + \vec{V}_{2}\vec{I}_{0}^{*} & 1 \\ a \\ a \end{pmatrix} + 3Z_{n}\vec{I}_{0}\vec{I}_{1}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + 3Z_{n}\vec{I}_{0}\vec{I}_{1}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + 3Z_{n}\vec{I}_{0}\vec{I}_{2}^{*} & 1 \\ a \\ a^{2} \end{pmatrix}$$

$$= -Re \begin{pmatrix} \vec{V}_{1}\vec{I}_{2}^{*} & 1 \\ a \\ a^{2} \end{pmatrix} + \vec{V}_{2}\vec{I}_{1}^{*} & a^{2} \\ a \end{pmatrix}$$

$$(7.3)$$

Note that the three rows of 7.2 and 7.3 are simply stating that the sum of the terms resulting in unbalanced active power flow must be zero for each of the three phases. It is then possible to solve for  $\vec{I_0}$  in a similar way as in chapter 5. The result is:

$$I_0 = \frac{(-V_1\sigma_2 + V_2\sigma_1)\sin(\phi_1 - \phi_2)}{3Z_0\sigma_1\sin(\zeta + \phi_0 - \phi_1) + 3Z_0\sigma_2\sin(\zeta + \phi_0 - \phi_2) + V_1\cos(\phi_1 - \phi_0) + V_2\cos(\phi_2 - \phi_0)}$$

(7.4)

$$\phi_{0} = -\arctan\left(\frac{(3Z_{0}\sigma_{1}sin(\zeta)+V_{1})-3Z_{0}\sigma_{2}cos(\zeta)sin(-3\phi_{1}+3\phi_{2})+(3Z_{0}\sigma_{2}sin(\zeta)+V_{2})cos(-3\phi_{1}+3\phi_{2})}{3Z_{0}\sigma_{1}cos(\zeta)+3Z_{0}\sigma_{2}cos(\zeta)cos(-3\phi_{1}+3\phi_{2})+(3Z_{0}\sigma_{2}sin(\zeta)+V_{2})sin(-3\phi_{1}+3\phi_{2})}\right) + 2\phi_{1} - \phi_{2}$$

$$(7.5)$$

As in the previous chapter, the latter equations are valid only if sequence currents are orthogonal to the corresponding sequence voltages as described in equations 5.2 to 5.5. The definitions of  $\sigma_1$  and  $\sigma_2$  are given in 5.13 and 5.14 respectively. Also, as in the two previous chapters, all three combinations of two rows in equation 7.3 should be solved in parallel in order to ensure that a non-degenerate solution is found.

Unless there is a source or sink of active power in the neutral path, the neutral path impedance can be assumed to be purely reactive. This means that:

$$Z_n = Z_0 \angle \zeta = Z_0 \angle \pm \frac{\pi}{2} \tag{7.6}$$

and the equations above simplify to:

$$I_{0} = \frac{(-V_{1}\sigma_{2} + V_{2}\sigma_{1})sin(\phi_{1} - \phi_{2})}{\pm 3Z_{0}\sigma_{1}cos(\phi_{0} - \phi_{1}) \pm 3Z_{0}\sigma_{2}cos(\phi_{0} - \phi_{2}) + V_{1}cos(\phi_{1} - \phi_{0}) + V_{2}cos(\phi_{2} - \phi_{0})}$$

(7.7)

$$\phi_0 = -\arctan\left(\frac{(\pm 3Z_0\sigma_1 + V_1) + (\pm 3Z_0\sigma_2 + V_2)\cos(-3\phi_1 + 3\phi_2)}{(\pm 3Z_0\sigma_2 + V_2)\sin(-3\phi_1 + 3\phi_2)}\right) + 2\phi_1 - \phi_2$$

(7.8)

Note that the  $(\pm)$  signs in equations 7.7 and 7.8 correspond to the two solutions generated by the  $(\pm)$  sign in the expression for the angle of  $Z_n$ .

If a variable impedance such as an additional single phase MMC-based voltage source converter like the one presented in figure 3–4 is connected in series in the neutral path, the zero sequence voltage and the zero sequence current become independent. Indeed, equation 7.2 can be solved by choosing  $\vec{V}_0$  and  $\vec{I}_0$  separately, and choosing the neutral path impedance to be equal to:

$$Z_0 \angle \zeta = \frac{1}{3} \frac{\vec{V}_0}{\vec{I}_0} \tag{7.9}$$

The result is that an optimal combination of  $\vec{V}_0$  and  $\vec{I}_0$  can be chosen to minimize leg voltages and currents. To solve the power balance equation using both the zero sequence voltage and the zero sequence current, it is necessary to define how much of the unbalance compensation should be done by each of the zero sequence quantities. One way of defining this is to use the valve voltage rating. Indeed, it is possible to use the zero sequence voltage method to the extent where the valve voltage reaches its rated value. The remaining balancing is then done using the zero sequence current method, and the necessary neutral path impedance is calculated as per equation 7.9. The first step is therefore to calculate the required zero sequence voltage as if only that method was used. This amounts to solving equation 6.3. Once this is done, the angle of the zero sequence voltage is kept fixed and the amplitude is recomputed so that the resulting leg voltage magnitudes remain smaller than the maximum allowed leg voltage  $V_{max}$ . That is, writing the expression for the line to neutral voltage across the converter legs, where the neutral point is taken as the converter neutral before the variable neutral path impedance:

$$\vec{V}_{conv} = \vec{V}_0 \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} + \vec{V}_1 \begin{bmatrix} 1 \\ a^2 \\ a \end{bmatrix} + \vec{V}_2 \begin{bmatrix} 1 \\ a \\ a^2 \end{bmatrix}$$

$$(7.10)$$

the individual phase voltages can be written as:

$$\vec{V}_a = 1V_0 e^{(j\phi_0)} + 1V_1 e^{(j\phi_1)} + 1V_2 e^{(j\phi_2)}$$

(7.11)

$$\vec{V}_b = 1V_0 e^{(j\phi_0)} + a^2 V_1 e^{(j\phi_1)} + aV_2 e^{(j\phi_2)}$$

(7.12)

$$\vec{V}_c = 1V_0 e^{(j\phi_0)} + aV_1 e^{(j\phi_1)} + a^2 V_2 e^{(j\phi_2)}$$

(7.13)

The inequality condition can then be solved for each phase. For example, the inequality condition for phase a is:

$$\|\vec{V}_a\| = \|V_0 e^{(j\phi_0)} + V_1 e^{(j\phi_1)} + V_2 e^{(j\phi_2)}\| \le V_{max}$$

(7.14)

Solving for the amplitude of  $\vec{V}_0$ :

$$V_{0} \leq -\left(V_{1}cos(\phi_{0} - \phi_{1}) + V_{2}cos(\phi_{0} - \phi_{2})\right)$$

$$\pm \sqrt{\left(V_{1}cos(\phi_{0} - \phi_{1}) + V_{2}cos(\phi_{0} - \phi_{2})\right)^{2} - \left(V_{1}^{2} + V_{2}^{2} + 2V_{1}V_{2}cos(\phi_{1} - \phi_{2}) - V_{max}^{2}\right)}$$

(7.15)

Negative solutions for  $V_0$  are then discarded since the angle of  $\vec{V}_0$  has already been defined. The smallest solution from all three phases is taken as the largest allowed  $V_0$ . Finally, the remaining unbalance is cancelled by solving equation 7.2 for  $\vec{I}_0$ . The neutral path impedance required to achieve this is calculated using equation 7.9.

#

It is possible to do some additional optimization in order to increase the STAT-COM output while remaining within the constraints of leg current and voltage ratings. The following derivation is done for the delta-coupled STATCOM topology. However, this method also applies directly to the wye-coupled STATCOM with grounded neutral, and could apply to the wye-coupled STATCOM with floating neutral by modifying the equations to consider  $\vec{V}_0$  instead of  $\vec{I}_0$ .

## 8.1 Defining a Degree of Freedom

In the general case for the delta-coupled STATCOM, the voltages across the legs and the currents in the legs are:

$$\vec{V}_a = \vec{V}_{a1} + \vec{V}_{a2} \tag{8.1}$$

$$\vec{V}_b = \vec{V}_{b1} + \vec{V}_{b2} \tag{8.2}$$

$$\vec{V}_c = \vec{V}_{c1} + \vec{V}_{c2} \tag{8.3}$$

$$\vec{I}_a = \vec{I}_{a0} + \vec{I}_{a1} + \vec{I}_{a2} \tag{8.4}$$

$$\vec{I_b} = \vec{I_{b0}} + \vec{I_{b1}} + \vec{I_{b2}} \tag{8.5}$$

$$\vec{I_c} = \vec{I_{c0}} + \vec{I_{c1}} + \vec{I_{c2}} \tag{8.6}$$

The active power flowing in each phase is the dot product of voltage and current which gives

$$P = \vec{V} \cdot \vec{I} \tag{8.7}$$

$$= (\vec{V}_1 + \vec{V}_2) \cdot (\vec{I}_0 + \vec{I}_1 + \vec{I}_2) \tag{8.8}$$

$$= \vec{V}_1 \cdot \vec{I}_0 + \vec{V}_1 \cdot \vec{I}_1 + \vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_0 + \vec{V}_2 \cdot \vec{I}_1 + \vec{V}_2 \cdot \vec{I}_2$$

(8.9)

and as explained in the previous chapters, these terms can be divided as follows

$$\begin{vmatrix}

\vec{V}_{1} \cdot \vec{I}_{1} \\

\vec{V}_{2} \cdot \vec{I}_{2}

\end{vmatrix} \Rightarrow P_{comm}$$

$$\begin{vmatrix}

\vec{V}_{1} \cdot \vec{I}_{0} \\

\vec{V}_{1} \cdot \vec{I}_{2} \\

\vec{V}_{2} \cdot \vec{I}_{0} \\

\vec{V}_{2} \cdot \vec{I}_{1}

\end{vmatrix} \Rightarrow P_{diff}$$

(8.10)

In order to prevent DC capacitor voltage unbalance, it is necessary that the sum of these terms be zero. In the existing method, the positive sequence current and positive sequence voltage are forced to be orthogonal in order to ensure that

$$\vec{V}_1 \cdot \vec{I}_1 = 0 \tag{8.11}$$

The same reasoning applies to the negative sequence current. It should be orthogonal to the negative sequence voltage so that

$$\vec{V}_2 \cdot \vec{I}_2 = 0 \tag{8.12}$$

A zero sequence current is then imposed inside the converter delta such that the sum of the differential power terms is zero.

$$\vec{V}_1 \cdot \vec{I}_0 + \vec{V}_1 \cdot \vec{I}_2 + \vec{V}_2 \cdot \vec{I}_0 + \vec{V}_2 \cdot \vec{I}_1 = 0$$

(8.13)