# SABLEWASM: A STATIC COMPILER AND RUNTIME FOR WEBASSEMBLY

Hongji Chen, School of Computer Science McGill University, Montreal August, 2021

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of

Master of Computer Science

©Hongji Chen, 2021

### Abstract

WebAssembly is a relatively new language, introduced to improve the performance of compute-intensive workloads in web-based applications. It offers a compact binary bytecode intended to allow for fast compilation and improved optimization opportunities over dynamic web languages like JavaScript. These properties, however, also make it an interesting target for static execution, enabling web code to run outside of a browser as well as within it. In this thesis, we describe *SableWasm*, a static, multi-pass compiler system that translates sandboxed WebAssembly applications to native shared libraries. Our work covers several different aspects of compiler design. First, we provide an efficient and extensible WebAssembly module parsing and validation framework, with improved execution speed and memory footprint compared to the reference baseline. We then define a middle-level intermediate representation and build an analysis and transformation framework. We explore several classic data-flow analyses, such as dominatortree construction within the framework, and additionally identify several WebAssembly specific optimization opportunities, which we address through custom transformation passes. SableWasm also incorporates several in-progress extension proposals including the SIMD vector operation extension. Optimized intermediate code is then converted to native code through a backend implementation with the help of the LLVM compiler framework and a runtime that enables C/C++ programs to interact with the WebAssembly module directly. Finally, we evaluate SableWasm by benchmarking against several well-known testing suites and observe performance improvement compared to the baseline implementation.

# Abrégé

WebAssembly est un langage relativement nouveau, introduit pour améliorer les performances des charges de travail gourmandes en calcul dans les applications Web. Il offre un bytecode binaire compact destiné à permettre une compilation rapide et des opportunités d'optimisation améliorées par rapport aux langages Web dynamiques comme JavaScript. Ces propriétés, cependant, en font également une cible intéressante pour l'exécution statique, permettant au code Web de s'exécuter à l'extérieur d'un navigateur ainsi qu'à l'intérieur de celui-ci. Dans cette thèse, nous décrivons *SableWasm*, un système de compilateur statique multi-passes qui traduit les applications WebAssembly en bac à sable en bibliothèques partagées natives. Notre travail couvre plusieurs aspects différents de la conception d'un compilateur. Premièrement, nous fournissons un cadre d'analyse et de validation de module WebAssembly efficace et extensible, avec une vitesse d'exécution et une empreinte mémoire améliorées par rapport à la ligne de base de référence. Nous définissons ensuite une représentation intermédiaire de niveau intermédiaire et construisons un cadre d'analyse et de transformation. Nous explorons plusieurs analyses de flux de données classiques, telles que la construction d'arbres dominants dans le cadre, et identifions en outre plusieurs opportunités d'optimisation spécifiques à WebAssembly, que nous abordons via des passes de transformation personnalisées. SableWasm intègre également plusieurs propositions d'extension en cours, y compris l'extension d'opération vectorielle SIMD. Le code intermédiaire optimisé est ensuite converti en code natif via une implémentation backend à l'aide du framework de compilateur LLVM et d'un runtime qui permet aux programmes C/C++ d'interagir directement avec le module WebAssembly. Enfin, nous évaluons SableWasm en comparant plusieurs suites de tests bien connues et observons une amélioration des performances par rapport à la mise en œuvre de base.

## Acknowledgements

First, I would like to extend my deepest gratitude to Professor Clark Verbrugge. The work would not have been possible without his support and advice, especially during a global pandemic. Second, I would like to thank Professor Laurie Hendren for her guidance in the field of compiler design in my early days as an undergraduate student. Finally, I would like to thank my colleagues and friends, especially my Sable lab mates, for their encouragement throughout the entire thesis journey.

# **Table of Contents**

|   | Abs  | tract                               | i    |

|---|------|-------------------------------------|------|

|   | Abr  | égé                                 | ii   |

|   | Ack  | nowledgements                       | iii  |

|   | List | of Figures                          | vii  |

|   | List | of Tables                           | 7iii |

| 1 | Intr | oduction                            | 1    |

|   | 1.1  | Contribution                        | 2    |

|   | 1.2  | Thesis outline                      | 4    |

| 2 | Bacl | kground                             | 6    |

|   | 2.1  | Emscripten and Asm.js               | 6    |

|   | 2.2  | WebAssembly                         | 9    |

|   | 2.3  | WebAssembly Extensions              | 13   |

|   | 2.4  | WebAssembly System Interface (WASI) | 16   |

|   | 2.5  | LLVM Compiler Infrastructure        | 18   |

| 3 | Fror | ntend                               | 23   |

|   | 3.1  | Bytecode Parser                     | 23   |

|   | 3.2  | WebAssembly Bytecode Representation | 26   |

|   | 3.3  | WebAssembly Bytecode Validation     | 29   |

|   | 3.4  | Performance Evaluation              | 31   |

| 4 | Mid  | dle-level Intermediate Representation                              | 35  |

|---|------|--------------------------------------------------------------------|-----|

|   | 4.1  | MIR Module Entities                                                | 38  |

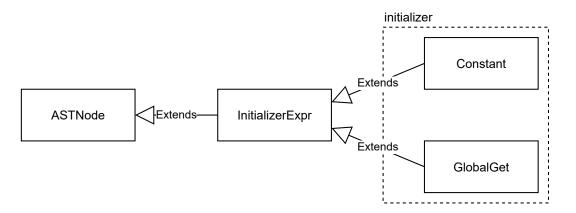

|   | 4.2  | MIR Initializer Expressions                                        | 41  |

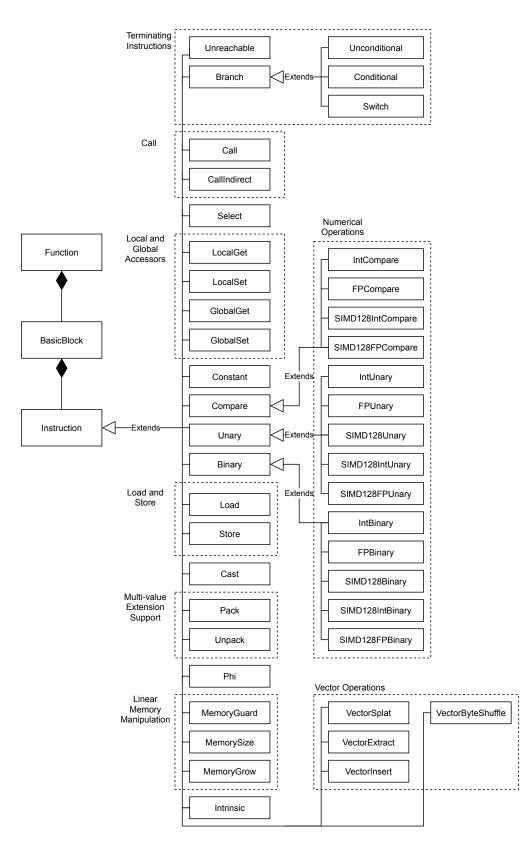

|   | 4.3  | MIR Instructions                                                   | 43  |

| 5 | Mid  | dle-level Intermediate Representation Translation and Optimization | 52  |

|   | 5.1  | Translating WebAssembly to MIR                                     | 52  |

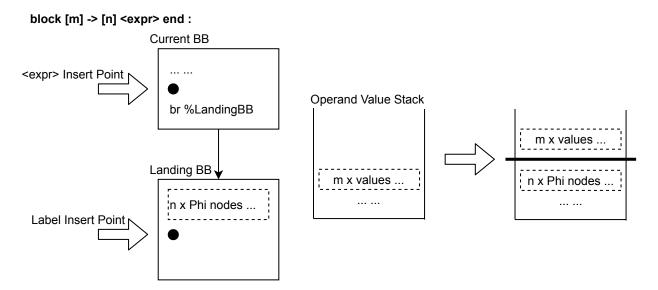

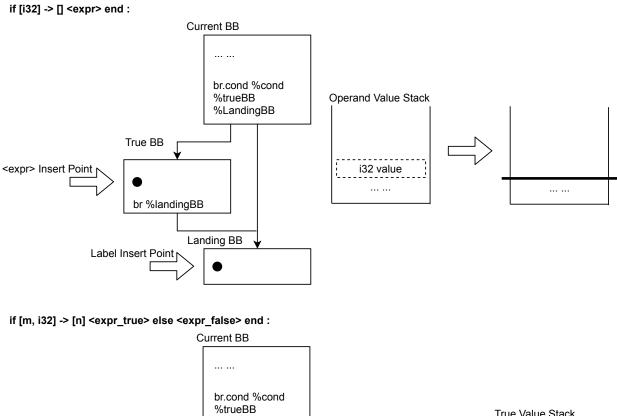

|   |      | 5.1.1 Structured-Control-Flow Construct                            | 53  |

|   |      | 5.1.2 Instruction Reduction                                        | 58  |

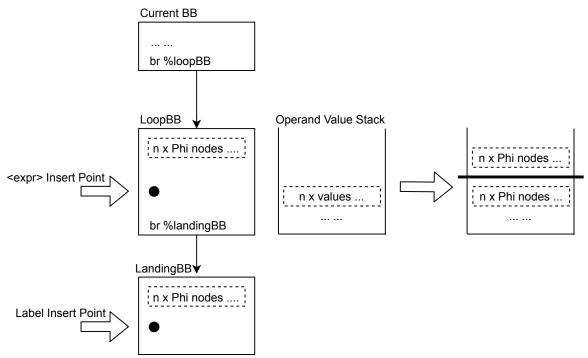

|   | 5.2  | Analysis Framework                                                 | 64  |

|   |      | 5.2.1 Dominators and Dependence                                    | 65  |

|   |      | 5.2.2 Control-Flow Graph Simplification                            | 67  |

|   |      | 5.2.3 Type Inference                                               | 71  |

| 6 | Bac  | kend and Runtime                                                   | 75  |

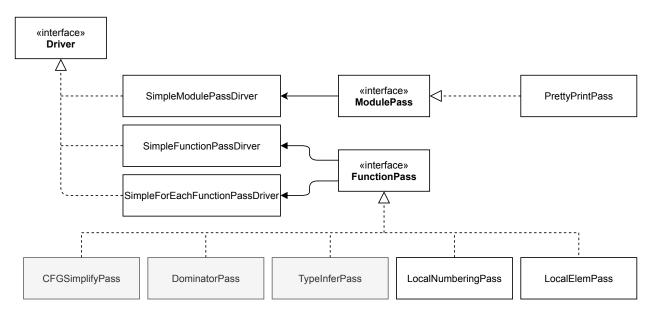

|   | 6.1  | Instance Layout                                                    | 75  |

|   | 6.2  | WebAssembly Entities                                               | 79  |

|   | 6.3  | Code Generation                                                    | 85  |

|   | 6.4  | Interface with C/C++                                               | 91  |

| 7 | Eva  | luation                                                            | 95  |

|   | 7.1  | Experiment Setup                                                   | 95  |

|   | 7.2  | RQ1: How does SableWasm perform compare to others?                 | 99  |

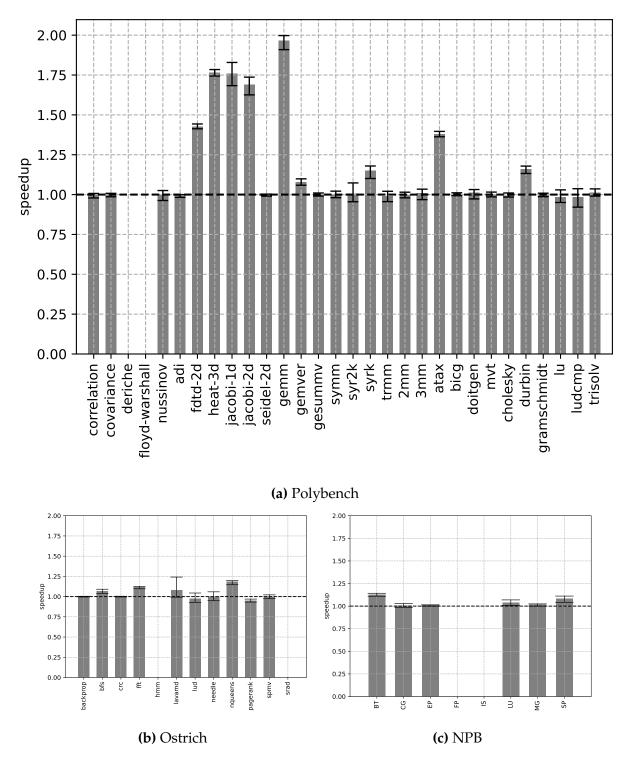

|   | 7.3  | RQ2: Does optimization over input modules matter?                  | 111 |

|   | 7.4  | RQ3: How much does SIMD extension improve in performance?          | 114 |

| 8 | Rela | ated Work                                                          | 118 |

| 9 | Futi | are Work and Conclusion                                            | 123 |

# **List of Figures**

| 1.1 | The SableWasm compiler and runtime                | 2  |

|-----|---------------------------------------------------|----|

| 2.1 | Adler 32 in C, asm.js and text-format WebAssembly | 8  |

| 2.2 | A illustration of WASI                            | 17 |

| 2.3 | A illustration of LLVM compilation pipeline       | 19 |

| 2.4 | Adler 32 in LLVM                                  | 20 |

| 3.1 | SableWasm parser                                  | 24 |

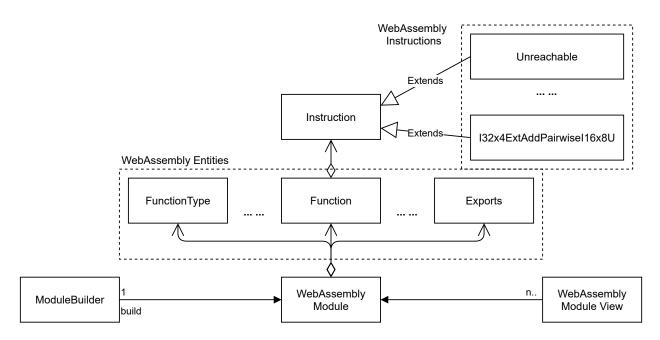

| 3.2 | SableWasm bytecode representation                 | 27 |

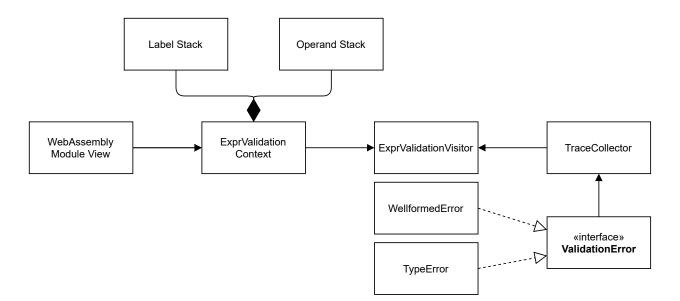

| 3.3 | SableWasm validation pass                         | 29 |

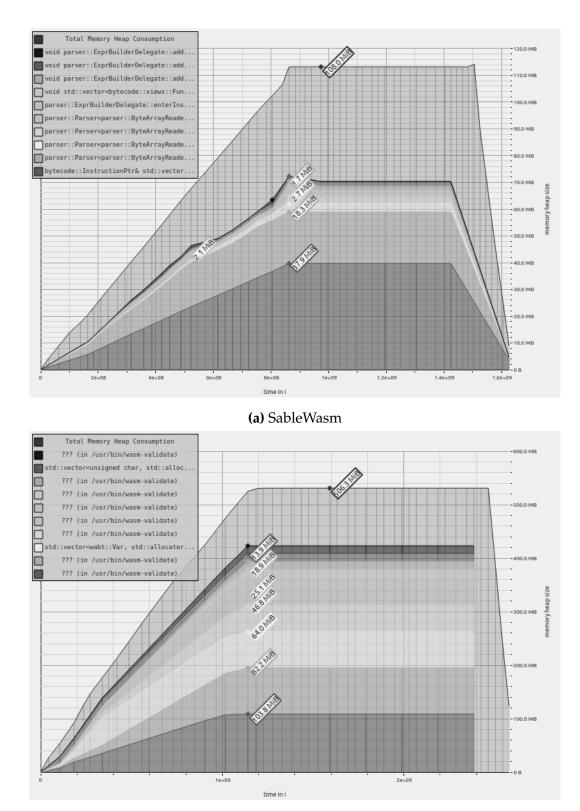

| 3.4 | Frontend memory footprint comparison              | 32 |

| 4.1 | Fibonacci in translated SableWasm MIR             | 37 |

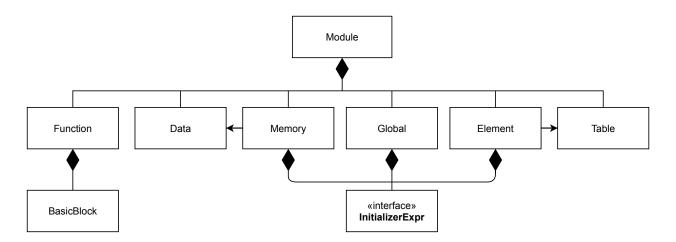

| 4.2 | SableWasm MIR Module-level entities               | 38 |

| 4.3 | SableWasm MIR Initializer Expression              | 41 |

| 4.4 | SableWasm MIR Instructions                        | 44 |

| 5.1 | WebAssembly block translation pattern             | 53 |

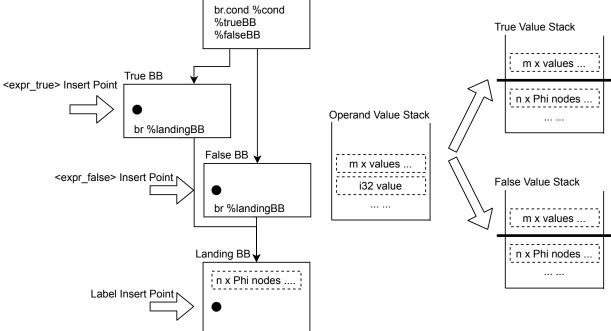

| 5.2 | WebAssembly if translation pattern                | 55 |

| 5.3 | WebAssembly loop translation pattern              | 57 |

| 5.4 | SableWasm MIR Analysis and Optimization Framework | 65 |

| 5.5 | Control-flow graph simplification example         | 68 |

| 5.6 | Control-flow graph simplification result          | 71 |

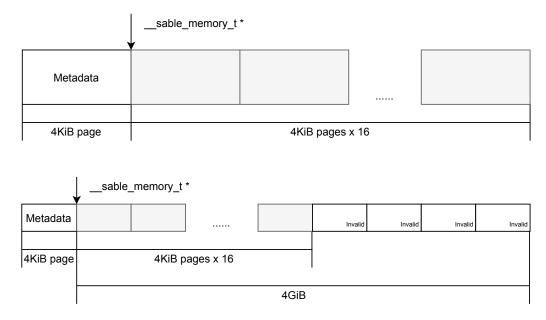

| 6.1  | SableWasm WebAssembly instance                                          |

|------|-------------------------------------------------------------------------|

| 6.2  | SableWasm WebAssembly linear memory                                     |

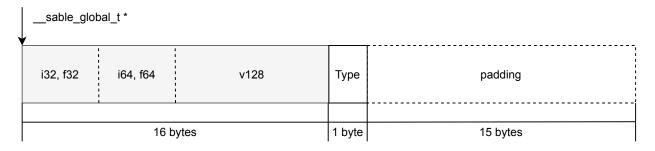

| 6.3  | SableWasm WebAssembly linear global                                     |

| 6.4  | Simple C++ SableWasm loader function                                    |

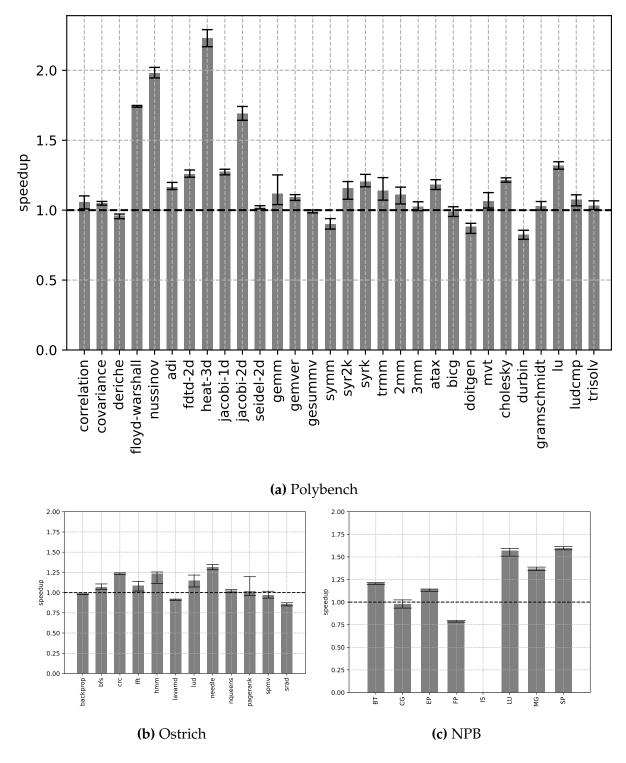

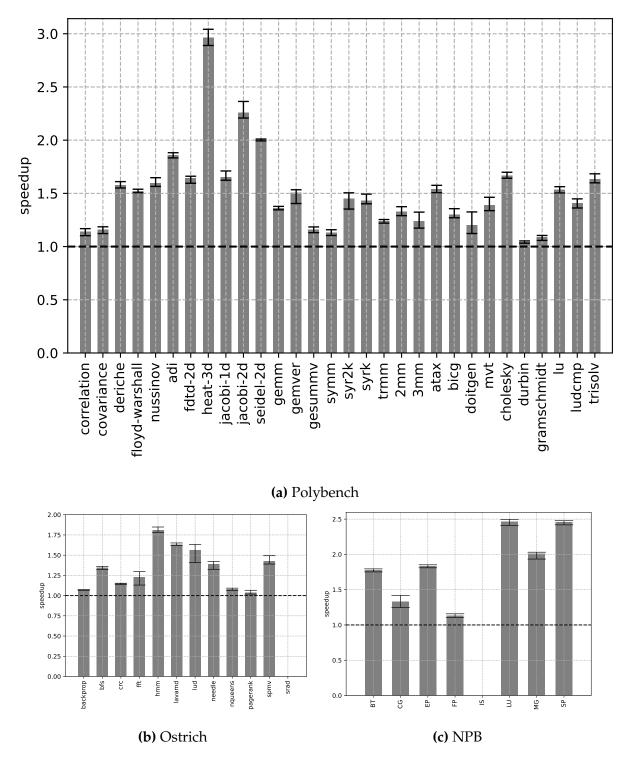

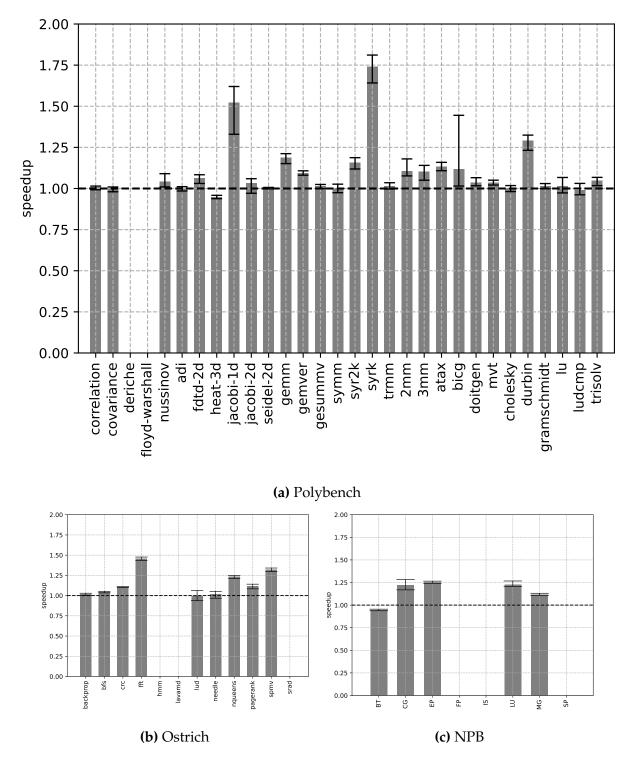

| 7.1  | Benchmarks with naive (-00) on Wasmtime                                 |

| 7.2  | Benchmarks with naive (-00) on Wasmer (Cranelift)                       |

| 7.3  | Benchmarks with naive (-00) on Wasmer (LLVM)                            |

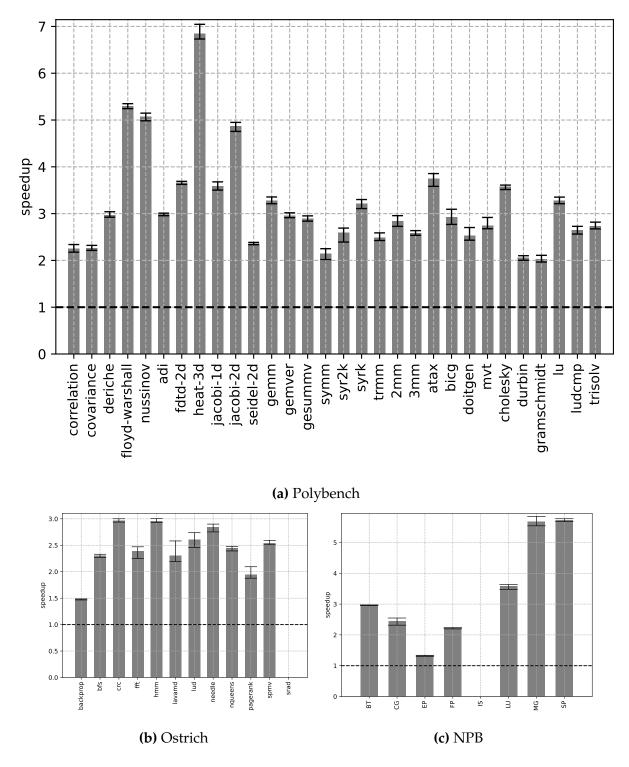

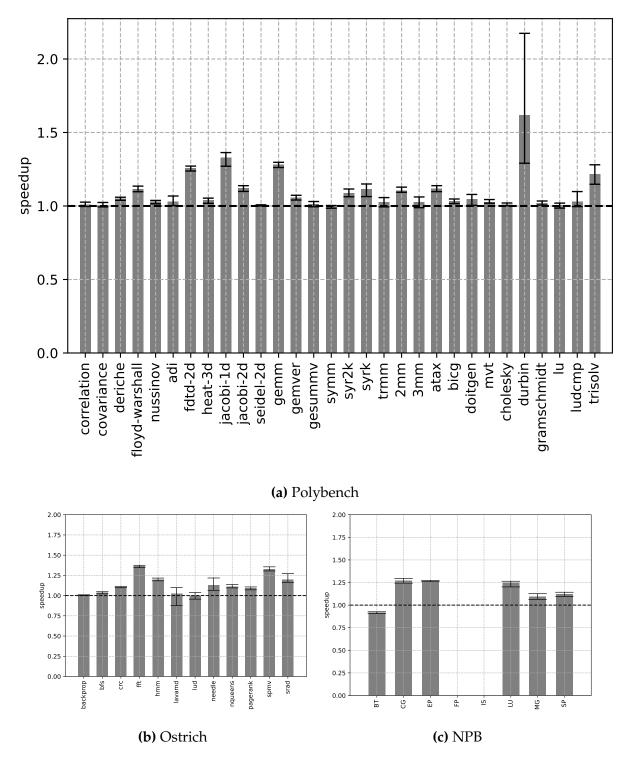

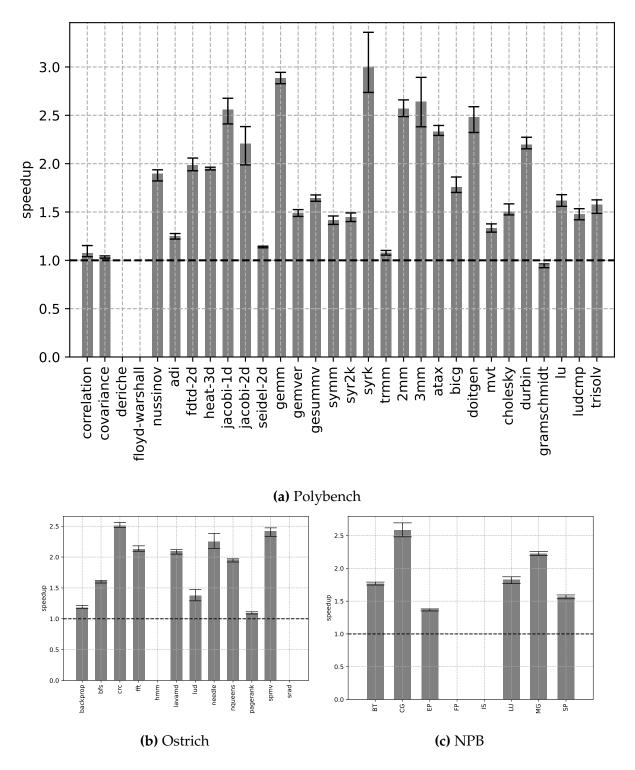

| 7.4  | Benchmarks with optimized (-03) on Wasmtime                             |

| 7.5  | Benchmarks with optimized (-03) on Wasmer (Cranelift)                   |

| 7.6  | Benchmarks with optimized (-03) on Wasmer (LLVM)                        |

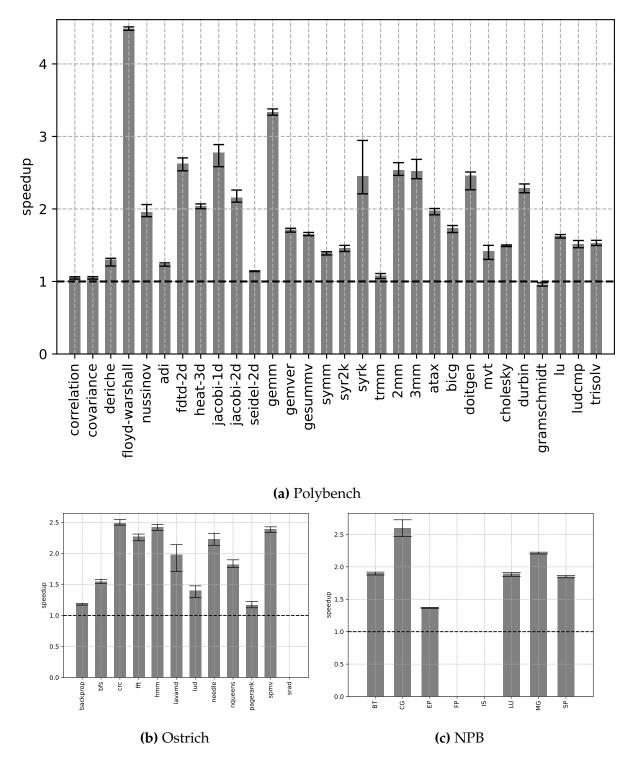

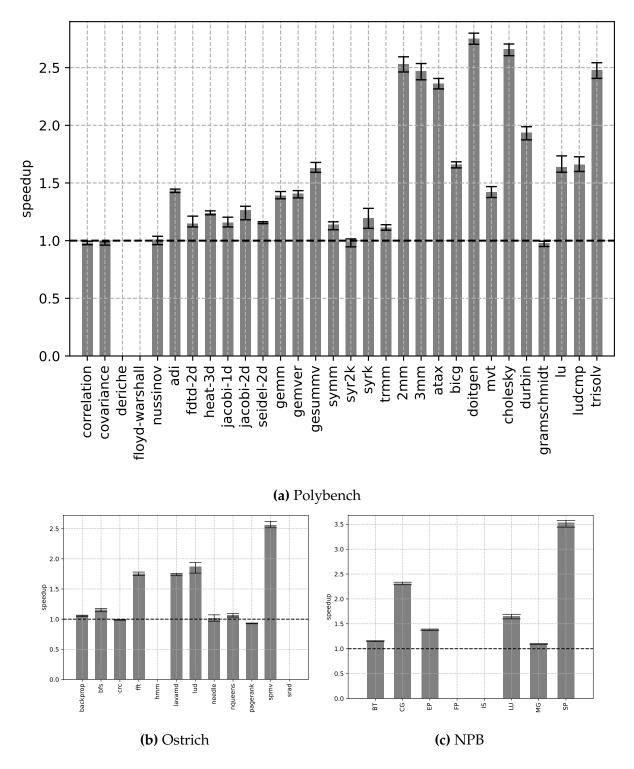

| 7.7  | Benchmarks with SIMD extension (-03 -msimd128) on Wasmtime 108          |

| 7.8  | Benchmarks with SIMD extension (-03 -msimd128) on Wasmer (Cranelift)109 |

| 7.9  | Benchmarks with SIMD extension (-03 -msimd128) on Wasmer (LLVM) . 110   |

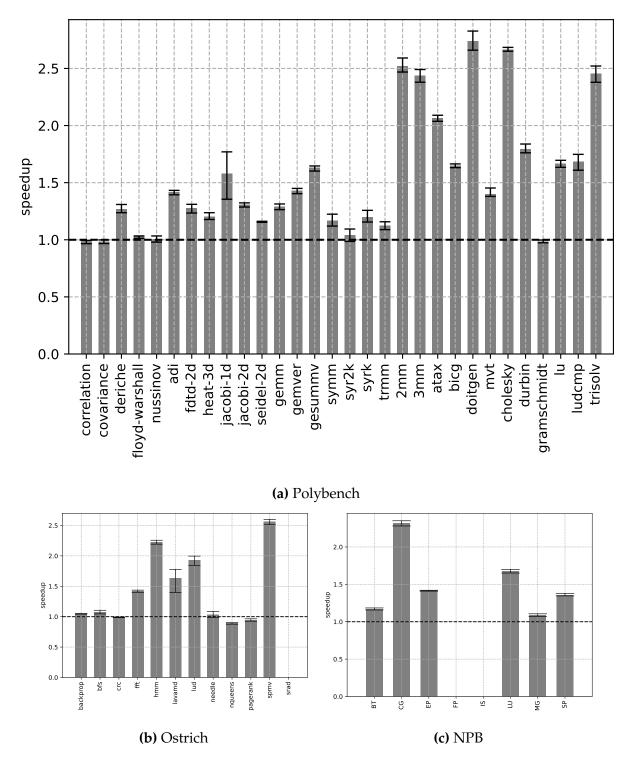

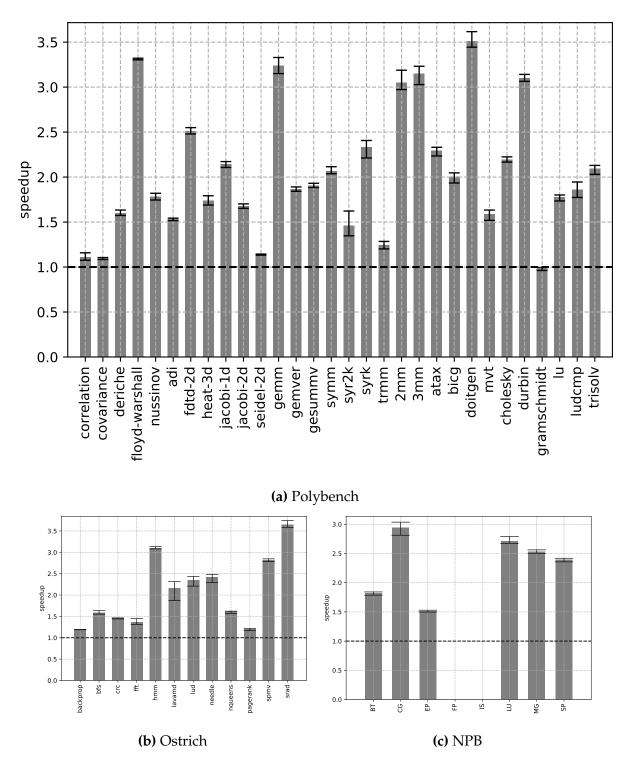

| 7.10 | Comparision between optimized and naive input modules                   |

| 7.11 | Polybench gemm benchmark kernel                                         |

| 7.12 | Comparision between SIMD-enabled and optimized input modules 115        |

| 7.13 | Polybench gemm code snippet                                             |

# **List of Tables**

| 3.1 | Frontend execution speed comparison                       | 33  |

|-----|-----------------------------------------------------------|-----|

| 6.1 | SableWasm shared libraries exported symbols               | 79  |

| 6.2 | SableWasm runtime builtin functions for linear memory     | 81  |

| 6.3 | SableWasm runtime builtin functions for indirect table    | 83  |

| 7.1 | the Polyhedral benchmark suite (Polybench)                | 96  |

| 7.2 | the Ostrich benchmark suite (Ostrich)                     | 97  |

| 7.3 | the NAS parallel benchmark suite (NPB)                    | 98  |

| 7.4 | Geometric mean of speedups compare to Wasmtime and Wasmer | 111 |

## Chapter 1

### Introduction

Web-based applications have grown in popularity in recent years. From the early days of simple web applets to current full-blown programs, their codebase's complexity and size has grown rapidly. Due to the design of most browsers, programmers have to choose JavaScript or its dialects to implement them. This approach is quite successful; however, it still leaves several problems unsolved. First, JavaScript is a scripting language and employs many dynamic features that prevent backend runtime environment from efficient execution, such as dynamic typing. Additionally, when porting existing applications to JavaScript, especially those with a large codebase where manually translating source code line-by-line is not feasible, a nontrivial source-to-source compiler is needed due to the structural difference between native binaries and JavaScript source codes.

To address these problems, the WebAssembly working group was established in 2017 and proposed a new standard for distributing applications over the Internet. WebAssembly focuses on safety, performance, portability and module compactness. These properties also make it an interesting target for static execution, enabling sandboxed applications outside of browsers. Although WebAssembly started as an intermediate format for distributing compiled programs over the Internet, it is not limited to the Web. The WebAssembly working group, in its famous WebAssembly introduction paper [8], also shows that WebAssembly can serve as an open standard for embedding in a multi-

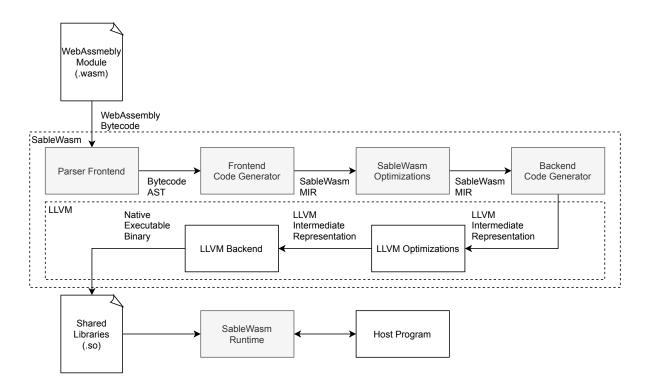

Figure 1.1: The SableWasm compiler and runtime

contexts environment. To this end, the WebAssembly community further designed the WebAssembly System Interface (WASI), which provides a standardized interface for WebAssembly modules to access native features such as the file system.

WebAssembly is also an evolving language. Although the WebAssembly community has published the minimum viable product (MVP) WebAssembly, the community is still actively proposing and experimenting with new language features, such as exception handling and garbage collection. These additional language features are proposed in language extension proposals that modify the current WebAssembly specification syntactically and semantically. Thus, a well-designed WebAssembly runtime environment system should be modular and extensible, leaving space for future design changes.

### 1.1 Contribution

This thesis aims to design and implement a runtime environment that enables WebAssembly to run outside of the browser. To this end, this thesis makes three major contributions.

Figure 1.1 illustrates the SableWasm compiler and runtime system. We mark our contributions in this thesis as shaded boxes in the figure.

Implementing a WebAssembly runtime system Our first contribution is a standalone WebAssembly runtime environment with support for the WebAssembly System Interface (WASI). We first start by implementing a custom extensible parser frontend for WebAssembly binary format, shown as the 'Parser Frontend' in figure 1.1. We then define a 'middle-level' representation (MIR) for SableWasm. To match modern hardware, Sable-Wasm MIR is a register-based *control flow graph* representation of the program, while, on the other hand, WebAssembly operates over a stack-based virtual machine. Hence, translating between them is nontrivial. Therefore, we design and implement a frontend code generator that lowers WebAssembly bytecode into SableWasm MIR, shown as the 'Frontend Code Generator' in figure 1.1. SableWasm MIR plays a critical role in the Sable-Wasm system. First, it provides a middle ground where we implement an extensible and straightforward optimization framework. With the help of the framework, we experiment with several analyses and optimizations on SableWasm MIR. Second, SableWasm MIR also separates the frontend from the backend. Currently, we implement an ahead-oftime (AOT) compiler backend using the LLVM compiler infrastructure [15], shown as the 'Backend Code Generator' in figure 1.1. However, there are several challenges when lowering SableWasm MIR into LLVM intermediate representation. For example, SableWasm MIR, similar to WebAssembly bytecode, utilizes several abstract high-level concepts such as linear memory and indirect function calls. These operations cannot be trivially mapped to LLVM instructions and require runtime library support. Hence, the last component of SableWasm is a runtime library that provides builtin runtime functions for the generated modules and defines an easy-to-use interface for the host system, shown as the 'Sable-Wasm Runtime' in figure 1.1.

Adding support for WebAssembly extensions Our second contribution in this thesis is to experiment and adopt several in-progress WebAssembly language extensions. Sable-

Wasm is designed to be extensible and currently implements four post-MVP WebAssembly features. The most interesting one among them is perhaps the fixed-width SIMD operation extension which defines vector-based operations that can operate on multiple data simultaneously, packed into special vector registers and supported by modern hardware. The SIMD extension in WebAssembly introduces one additional value type and approximately 240 new instructions to the specification. As we have discussed earlier in this section, SableWasm MIR provides a middle ground where we perform optimization on the program. Therefore, we would like to keep the size of the SableWasm MIR instruction set simple. To achieve this goal, we carefully design a set of reduction patterns in the frontend code generator that significantly reduce the number of instructions needed. We also generalize our backend code generator that targets LLVM by emitting corresponding vector operation instructions.

**Evaluating system performance** Our last contribution in this thesis is to investigate how SableWasm performs and the factors that affect the performance. Here we focus on three research questions: First, how does SableWasm perform comparing to other existing WebAssembly runtime implementations? Second, does optimization over the input WebAssembly modules affect SableWasm's overall performance? Finally, does the SIMD operation extension bring performance improvement to the system? To answer these questions, we analyze the performance of three well-known benchmark suites, Polybench [36], Ostrich [9], and NPB [33]. We also examine generated LLVM intermediate representations in SableWasm to search for factors contributing to the slow down in the system.

### **1.2** Thesis outline

This thesis consists of nine chapters in total, including the introduction chapter. Chapter 2 discusses the background information that helps the understanding rest of the thesis. It first presents the motivation for WebAssembly and WebAssembly System Interface (WASI), followed by a brief overview of the LLVM intermediate representation. Chapter 3 to chapter 6 discusses the design of implementation of the SableWasm system. Chapter 3 starts with presenting the custom extensible and efficient parser frontend for WebAssembly binary format. Chapter 4 continues the discussion of SableWasm by describing Sable-Wasm MIR's design. Chapter 5 discusses the code generating strategies used when lowering WebAssembly bytecode to SableWasm MIR and the optimization framework. Chapter 5 also presents several optimization passes we experimented with the framework, such as control flow graph simplification and type inference. Chapter 6 illustrates the last component of SableWasm, the LLVM backend and the runtime support library. In chapter 7, we investigate the performance of SableWasm by presenting benchmark results and discussing several possible theories for the slowdown. Finally, chapter 8 discusses related work and chapter 9 presents our conclusion along with future work.

## Chapter 2

### Background

This chapter provides background information that helps to understand the thesis. We first revisit the rise of *asm.js* and its toolchain, *Emscripten*, followed by an introduction to *WebAssembly* and its standardized *WebAssembly System Interface* (WASI). Finally, we will give a brief overview of the LLVM compilation framework.

### 2.1 Emscripten and Asm.js

In the past decade, web-based applications are gaining popularity, and due to the design of most browsers, programmers tend to choose JavaScript or its dialects to implement them. One natural problem is how to compile programs that target the native platform to run over the internet. Making the situation more challenging, programs with a large codebase, such as games requiring complex video and physical computation, are nearly impossible to translate line-by-line manually. In 2010, Alon Zakai started the first attempt at translating source code that targets native platforms into JavaScript [34]. After two years of development, he published Emscripten that translates LLVM intermediate representation into asm.js, a JavaScript subset [37]. An asm.js program shares a similar programming model to that which one would expect on the native platform. The detailed asm.js specification is available on the official website <sup>1</sup>. We will visit several critical features in asm.js with examples in figure 2.1 (page 8). These examples are implementations of the Adler-32 hashing algorithm used in ZLib compression library [4] <sup>2</sup>, in both C and its corresponding generated asm.js with Emscripten.

**Function prologue and type annotation** JavaScript is a dynamically typed language. Hence, a proper implementation needs to verify the types of variables when needed. Although several optimization techniques can eliminate some of the checks and improve the execution performance, such language features can still incur a significant performance loss. Asm.js adds type annotations to function parameters and expressions to address this problem. In figure 2.1b, Emscripten generates parameter annotations for parameters  $0_1$  and  $0_2$  at line 2 and line 3 respectively. The trailing bitwise 'or' operation against zero hints that both arguments are integral values since bitwise operations are only defined for integral values in JavaScript. Emscripten also annotates float-point numbers with the unary positive operation, '+', which we do not show in the example. A system that supports asm.js directly can quickly recover the type information from the annotations, which, in theory, can improve both the compilation and execution performance. On the other hand, for a system that does not recognize asm.js, the program above is still a valid JavaScript program, and the type annotations ensure the correct semantics for numeric operations.

**Control flow** LLVM employs a register-based intermediate representation with a *control flow graph* (CFG). However, JavaScript uses structured control flow and does not allow arbitrary jump statements similar to one would expect in C. Hence, when translating LLVM IR to asm.js, Emscripten mimics the branch instructions between basic blocks in the generated code with JavaScript control-flow statements. Emscripten uses a pattern-based translation and classifies control flow changes into three categories. In figure 2.1b,

<sup>&</sup>lt;sup>1</sup>asm.js specification: http://asmjs.org/spec/latest/

<sup>&</sup>lt;sup>2</sup>Revisiting Fletcher and Adler Checksums:

http://www.zlib.net/maxino06\_fletcher-adler.pdf

```

1

uint32_t adler32(void const *buffer_, size_t length_) {

2

3

uint8_t const *buffer = (uint8_t const *)buffer_;

uint32_t a = 1;

4

uint32_t b = 0;

for (size_t i = 0; i < length_; ++i) {

a = (a + buffer[i]) % 65521;</pre>

5

6

7

b = (a + b) \% 65521;

8

}

9

return (b << 16) | a;

10

}

```

```

(a) C

```

```

function $adler32($0_1, $1_1) {

1

2

$0_1 = $0_1 | 0;

3

1_1 = 1_1 = 1_1;

4

var \$2_1 = 0, \$3_1 = 0, \$4_1 = 0;

5

3_1 = 1;

6

if ($1_1)

7

while (1)

{

8

$3_1 = (HEAPU8[$0_1 + $2_1 | 0] + $3_1 >>> 0) % 65521 | 0;

9

$4_1 = ($4_1 + $3_1 >>> 0) % 65521 | 0;

10

$2 1 = $2 1 + 1 | 0;

if (($2_1 | 0) != ($1_1 | 0)) { continue }

11

12

break;

13

14

$2_1 = $4_1 << 16;

15

}

16

return $2_1 | $3_1;

17 }

```

```

(b) asm.js

```

```

(type $t0 (func (param i32 i32) (result i32)))

(func $adler32 (export "adler32") (type $t0)

2

3

(local $10 i32) (local $11 i32)

456789

get_local $p1

if $I0

(set_local $11 (i32.const 1))

loop $L1

(i32.rem_u

(i32.add

10

(get_local $11)

11

(i32.load8_u (get_local $p0)))

12

(i32.const 65521))

13

. . .

. . .

14

end

15

(i32.or

16

(i32.shl (get_local $10) (i32.const 16))

17

(get_local $11))

18

return

19

end

20

i32.const 1)

21

(memory $memory (export "memory") 2)

```

(c) Text-format WebAssembly

Figure 2.1: Adler 32 in C, asm.js and text-format WebAssembly

we demonstrate two of the three control-flow structures, *if* and *loop*, at line 6 and line 7 respectively. Asm.js also has a third control flow structure, *block*, which we do not show in the example. A *block* structure is similar to a *loop* structure and can be translated to a while loop with an always-false condition. A branch instruction referring to the *block* is equivalent to a break statement in this case. WebAssembly adopts a similar design, and we will revisit this in the later section with more details.

**Byte array as heap** Emscripten uses multiple typed array views that share a single underlying byte array buffer to simulate the heap in a native programming model. In figure 2.1b, the asm.js example uses HEAPU8, an unsigned byte view over the byte array at line 8, to access the data passed by the pointer via the first argument. Asm.js also offers other array views such as HEAPI32 and HEAPF32 which allows programs to access 32-bit signed integers and single-precision floating-point numbers on the heap. This technique also inspires the linear memory design in WebAssembly, which we will discuss later in the chapter with more details.

Emscripten is quite successful. Experiment results show that it can port most of the C/C++ programs of non-trivial code size to the web with approximately 50-67% of native performance <sup>3</sup> without any missing significant features.

#### 2.2 WebAssembly

Although Emscripten with asm.js is successful, there are still several problems that remain unaddressed. One of them is the parsing overhead. As asm.js is a strict subset of JavaScript, parsing the generated program is a non-trivial task due to the complexity of JavaScript grammar. Additionally, because Emscripten emits generated programs in asm.js, the output size grows significantly faster than the native binary. Another problem regards the generated programs' safety, especially when running an untrusted module

<sup>&</sup>lt;sup>3</sup>Alon Zakai's presentation on Emscripten at CppCon: https://kripken.github.io/mloc\_emscripten\_talk/cppcon.html

received over the internet. In 2017, the WebAssembly community established and proposed a new standard for distributing programs over the internet to address these problems. The design of WebAssembly focuses on safety, performance, portability, and compactness. The introduction paper describes the detailed structure, validation rules [35], and execution semantics of WebAssembly [8]. Here we will only visit some of the key points that help understand the rest of the thesis. In figure 2.1c we also present a simple WebAssembly program that implements the Adler32 hashing.

Module structure WebAssembly modules can have four different kinds of entities: functions, indirect tables, linear memories, and globals. Modules are also able to import and export entities by names. In figure 2.1c, we define a *function* and a *linear memory* and export them under name adler32 and memory respectively. WebAssembly functions can define an arbitrary number of local variables and a possibly empty sequence of instructions as the body. All instruction operates over an implicitly declared stack. The control-flow will return from the function by either a return instruction or reaching the end of the body. WebAssembly linear memories have bounds consisting of a pair of integers, representing the lower bound and upper bound respectively, <sup>4</sup> in units of 16-KiB pages. In figure 2.1c, at line 21, we defined a linear memory with a minimal size of 32-KiB. WebAssembly linear memory can also associate with zero or multiple *data* segments. Each data segment contains a constant evaluated expression, representing the initialization offset, and a sequence of bytes that the runtime environment will copy from. WebAssembly indirect tables are similar to linear memories, but they store function pointers instead of bytes. A *indirect table* has a type that consists of an upper and lower bound similar to *linear memory*, as well as a function type indicating the type of the function pointers allowed <sup>5</sup>. WebAssembly tables also introduce their initializer, *element* segments. The *element* segment is similar to the *data* segment, but it initializes function pointers instead of bytes.

<sup>&</sup>lt;sup>4</sup>The upper bound is optional

<sup>&</sup>lt;sup>5</sup>Currently, the function type must be funcref which is a union type of all possible function types.

Another difference between linear memories and indirect tables is that indirect tables are immutable after initialization to ensure the module's safety <sup>6</sup>.

**Linear memory** Similar to asm.js, WebAssembly programs can access one or multiple *linear memories*<sup>7</sup>. The memory is unmanaged, and it is the program's responsibility to handle the layout correctly. The program can grow the *linear memory* if needed via the memory.grow instruction; however, the runtime environment is not obligated to increase the *linear memory*. The program can check the result of the command via the instruction's return value. Asm.js also allows the growth of the heap byte array. However, due to the limitations of JavaScript, this operation is usually quite expensive, as there is no efficient realloc algorithm provided in JavaScript, and it requires allocating a byte array with a larger capacity and copying byte-by-byte. WebAssembly specification does not impose requirements on the time complexity of growing the linear memory, yet it encourages any implementation to avoid copying. Unlike native heap memory, there is no alignment requirement on load-store instructions; i.e., load-store can start at any byte in the memory with the probable additional cost for unaligned access. However, there are boundary checks applied to the linear memory. Any out-of-bound access will result in a runtime panic. Additionally, WebAssembly specification requires any runtime environment implementation to zero-initialize the linear memory.

Indirect table Asm.js represents function pointers using first-class function values, thanks to JavaScript. However, in WebAssembly, every entity is referred to with indices representing references, and value types only consist of integral types and floating-point types <sup>8</sup>. Hence, we need something creative to implement the function pointers in WebAssembly. The solution utilizes one special instruction call\_indirect and indirect tables. During module initialization, the runtime environment will initialize the indirect table according to the *element* section. Each call\_indirect instruction associates with an in-

<sup>&</sup>lt;sup>6</sup>This is subject to change in the reference type extension

<sup>&</sup>lt;sup>7</sup>In the current version of WebAssembly, at most one linear memory is allowed within a single module <sup>8</sup>WebAssembly may introduce more primitive value types in the future.

dex and an expecting type. The runtime environment will perform both a validity check on the index and a type check against the expecting type. Unlike the linear memory, the indirect table is not growable at runtime and is currently immutable once the initialization phase is complete. An indirect table does not limit the function pointers stored to be internal functions nor even WebAssembly functions. The function pointer can even be a host native function; many runtime environment implementations utilize this feature to register native call-back functions to WebAssembly modules.

**Structured control flow** Another WebAssembly's key feature is the structured control structure. Unlike the native binary and most of the bytecode representations that utilize labels and offsets, WebAssembly has structured control flow instructions and classifies them into three categories, block, if and loop, similar to asm.js. Each control flow instruction can optionally associate with a value type, representing the change on the operand stack once the control block exits <sup>9</sup>. A *block* control flow is perhaps the simplest structure. It introduces a label index to the context. The label is only referable within the *block* construct by indices. If a branch instruction refers to the block's label, the runtime environment will redirect the control flow as if it reaches the *block*'s end. An *if* control flow is similar to the *block* control flow with two significant differences. One is that it will implicitly consume a 32-bit integer from the stack and choose the branch accordingly. The other difference is that it can optionally have a *false* branch. If the *false* branch is missing, the runtime environment will redirect the control flow to reach the if's end, similar to the block control flow structure. The last control flow structure is loop. The only difference between the *loop* control structure and *block* structure is when a branch instruction refers to it. When a branch instruction refers to a *loop* block, the runtime environment will redirect the control flow to the *loop*'s beginning instead of the end. In the figure 2.1c, we present

<sup>&</sup>lt;sup>9</sup>WebAssembly multivalue extension relaxes the requirement and allows structured control instruction to have a function type. If a control instruction associate with a function type, the parameter types refer to the value consumed from the operand stack and result types refer to the value added to the operand stack.

the *if* structure on line 5, and *loop* structure on line 7. The example does not contain a *block* structure, but there is no difference between it and a *loop* structure at the syntax level.

Generally speaking, WebAssembly's performance, compared to its native counterpart, varies significantly from test case to test case. On the browser side, WebAssembly can finish most test cases within 10% slower than the native version and all test cases within two times slower [8]. Another test shows similar results for most test cases, except one case is 2 times to 3.4 times slower than native, depending on the input size [12]. For generated code size, the community introduction paper claims 85.3% compare to native implementations. WebAssembly is not only successful in the field of Web-based applications. It also defines a portable format for distributing programs over the internet, similar to what we have seen in Java and its virtual machine. GraalVM now has its interpreter for WebAssembly modules, TruffleWasm [28], and can execute WebAssembly modules with impressive performance with only 4% slower than WebAssembly reference implementation in most of the cases, and even 4% faster in PolybenchC.

#### 2.3 WebAssembly Extensions

In the previous section, we presented the core part of WebAssembly published by the community in late 2016 as a minimal viable product (MVP). Although the WebAssembly MVP is powerful enough to host most of the applications [20], there still exists room for improvement. These post-MVP proposals enhance the functionality of WebAssembly by introducing new instructions or modifying existing module constructs. For example, MVP WebAssembly has no support for exception handling. Thus, when compiling programs implemented in C++, users need to turn off the compiler's exception feature explicitly. The exception handling post-MVP extension addresses the problem by introducing a special try block, which enables user-defined stack unwinding. Most post-MVP extensions are still in the early stage of development and may merge into core WebAssembly in the future. This project implemented several post-MVP features such as integral value

sign extension, non-trapping floating-point conversion, multivalue semantics, and fixedwidth SIMD vector operation. In this section, we will quickly visit these post-MVP feature extensions.

Integral value sign extension MVP WebAssembly only has 32-bit and 64-bit integral values. However, many programming languages support integers with a smaller width. Thus, implementing short integral values in WebAssembly is quite awkward. To alleviate the problem, MVP WebAssembly has instructions that can perform load and store of 8-bit and 16-bit integers with signed or zero extension semantics. However, what if one already has a short integer on the stack and would like to perform a sign extension? Unfortunately, there are no immediate solutions. One possible work-around is to store the value to the linear memory and then sign extend with the load instruction's help, which is quite expensive. The sign extension proposal introduces new instructions that perform the stack then performs the sign extension to the operand as if the operand is an 8-bit integer. The proposal also introduces similar instructions for 64-bit integers.

**Non-trapping float-to-int conversion** MVP WebAssembly offers floating-point-to-integer conversion with implicit range checks to fulfill the no-undefined behaviour design goal of the language. If the desired integer type cannot accurately represent the floating-point value, the runtime environment should trap. However, in most other languages, such as LLVM, the conversion yields an undefined result without trapping in such scenarios. Thus, if one wants to simulate the conversion between floating-point and integers faithfully, an if block with manual checks is usually required. This proposal introduces saturated value conversion to address the problem. If the desired integer type cannot represent the resulting number, the instruction employs saturated semantics. More specifically, if the floating-point value is more significant than the maximum representable value of the integer type, the maximum value is returned, and the same holds in the case of value

underflow. This extension also lays the foundation of SIMD vector operations to achieve more hardware-like semantics, which we will see later in this section.

Multivalue The multivalue proposal focuses on two aspects of WebAssembly, the function return value and the types of structured-control-flow constructs. In MVP WebAssembly, the function can have at most one return value. The proposal generalizes the function type by allowing functions to return multiple return values. For structured-control-flow constructs, MVP WebAssembly requires that any instructions within the construct cannot consume stack values outside of the stack frame. Additionally, the construct can put at most one value onto the stack when it exists. One advantage of having such strict rules on structured-control-flow constructs is that the validation rule is trivial, and the runtime system can compute the stack height with minimal effort. However, this has its drawbacks. For example, this method causes the bloat of local variables. When entering a structured-control-flow construct, the program needs to push all the values it may need to the local variables, then load them back to the stack later, which is quite expensive. The multivalue proposal relaxes such constraints by allowing the control-flow-construct to have a function type. Function types' parameter types indicating the type of values that the construct will consume, and the result types hint at the type of values that will be pushed onto the stack.

**SIMD vector operations** Single-instruction-multiple-data (SIMD) is a powerful tool for implementing high-performance programs. Many modern compilers, such as GCC, have auto-vectorization analysis and transformation to automatically rewrite scalar codes in parallel form [23]. Before WebAssembly, many attempts have been made to implement SIMD operations over the internet, most notably, SIMD.js<sup>10</sup>. The design of the SIMD vector operation proposal is based on the design of SIMD.js. Currently, the proposal focuses on 128-bit vector operation, which is widely available on different hardware architectures such as SSE [27], and ARM Neon [11]. The proposal introduces a new value type v128

<sup>&</sup>lt;sup>10</sup>https://hacks.mozilla.org/2014/10/introducing-simd-js/

representing a 128-bit vector. Note that the vector type does not contain any knowledge about the element type and how to interpret the lane, which is the number and the type of elements packed into a single vector, depends on the instruction. The SIMD vector operations proposal takes instructions from the intersection among different hardware architectures to ensure the module's portability. For example, i32x4.add will interpret both operands as packed 32-bit integers and perform lane-wise addition between them, while f64x2.sqrt will interpret its operand as a packed double-precision floating-point numbers. Most of the instructions are a direct generalization of the scalar operations in MVP WebAssembly. One notable difference is the floating-point conversion semantics. In MVP WebAssembly, the conversion will trap in the case of overflow or underflow. In contrast, in the SIMD vector proposal, packed floating-point value conversions follow similar semantics to those defined in the non-trapping float-to-int conversion proposal.

### 2.4 WebAssembly System Interface (WASI)

In the previous section, we introduce WebAssembly as a new format for delivering programs over the internet. The question then arises: can we push WebAssembly beyond the browser? On the other hand, if we want to compile the native program into WebAssembly, how do we translate operating-system-specific commands, such as file access? Taking a step further, how do we ensure the safety of the generated program? In the early days of development, Emscripten generates JavaScript glue code that mimics the operating system syscalls. However, this ad-hoc solution results in messy and nonportable code.

To address these problems, the WebAssembly community started the process of standardizing the system interface for modules <sup>11</sup>. The WASI interface design focuses on two aspects, portability and safety, following the WebAssembly design philosophy. The interface is still under active development at the time of thesis writing. In this project, we implement the interface functions only if they are needed while designing the backend

<sup>&</sup>lt;sup>11</sup>WASI initial announcement:

https://hacks.mozilla.org/2019/03/standardizing-wasi-a-webassembly-system-interface/

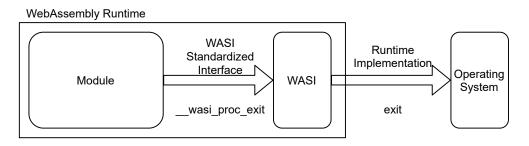

Figure 2.2: A illustration of WASI

library to be extensible. The official API documentation provides a detailed view on the design of the interface <sup>12</sup>. Figure 2.2 gives a general illustration of the relationship among the WebAssembly module, the runtime environment, and WASI. Here we will focus on several key points of the design.

WASI ABI model WASI classifies modules into two categories, *commands* and *reactors*. A *command* module has a single entry function, namely \_start and all the other exported functions are hidden from the user. On the other hand, a *reactor* module has an optional initialization function named \_initialize. If the initialization function is present, the runtime environment is obligated to invoke such a function before calling others. The runtime environment may invoke either the start or initializer function once during a module's lifetime. Additionally, every WASI-compatible model needs to export a linear memory under the name \_memory, and all addresses referred by modules are offsets within this linear memory. Similarly, modules will also export an indirect table under the name \_\_indirect\_function\_table. The runtime environment will pass function pointers through the indirect table. Additionally, WASI requires the runtime environment to provide all WASI API under module name wasi\_snapshot\_preview1<sup>13</sup>.

**Sandbox** As we described above, WASI API follows WebAssembly's design philosophy, safety, performance, portability, and compactness. WASI modules execute under a

<sup>&</sup>lt;sup>12</sup>WASI API documentation:

https://github.com/WebAssembly/WASI/blob/main/phases/snapshot/docs.md

<sup>&</sup>lt;sup>13</sup>This will change in the future, as WASI is still in the standardization phase.

capability-based security system to ensure the safety of the host environment. The host runtime system will provide a sandboxed environment for each model. For example, for file system access, WASI standard library C works with a virtual file system for each module with the help of libpreopen <sup>14 15</sup>.

**Non-invasive and extensible** In our discussion above, one may notice that a WASIcompatible module is also a valid WebAssembly module on its own. WASI does not introduce new instructions or sections to the module; instead, it provides additional functionalities through imported external functions. The design of WASI is also highly extensible and split into separate modules. Currently, the WASI working group focuses on developing the core part that provides most of the POSIX interface, but it may add additional features in the future.

### 2.5 LLVM Compiler Infrastructure

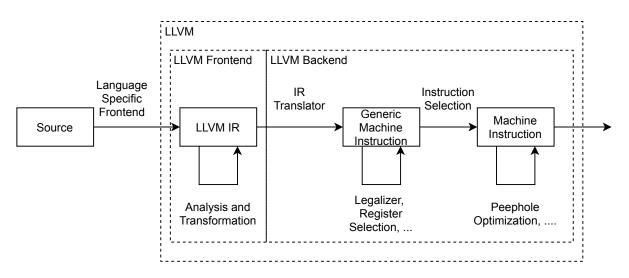

The last section of this chapter briefly overviews the compiler pipeline design and LLVM compilation framework. Designing a robust and efficient compiler in terms of both generated code and compilation speed is challenging. The LLVM compiler framework [15] alleviates the problem by introducing a standardized intermediate representation (IR) between the compiler frontends and backends. Backend developers can target their analysis and transformations on the IR instead of specializing in different languages. On the other hand, frontend developers can translate the source language into the IR and expect the backend to support multiple target platforms with efficient code generation. Figure 2.3 illustrates the LLVM compilation pipeline. In this project, we are more interested in the frontend of the framework. The LLVM official documentation and tutorial provide full details of their intermediate representation <sup>16</sup>. Here we will only discuss several major

<sup>&</sup>lt;sup>14</sup>libpreopen: https://github.com/musec/libpreopen

<sup>&</sup>lt;sup>15</sup>In the more recent version of WASI libc, libpreopen is no longer required.

<sup>&</sup>lt;sup>16</sup>LLVM Language Reference Manual: https://llvm.org/docs/LangRef.html

Figure 2.3: A illustration of LLVM compilation pipeline

differences between LLVM IR and WebAssembly that help understand the thesis. We also provide an implementation of Adler-32 hashing in LLVM IR generated with Clang in figure 2.4.

**Register-based IR against stack-based IR** In WebAssembly, all instructions operate over an implicitly declared stack. For example, in figure 2.1c at line 20, a 32-bit integer constant instruction, i32.const, will push the constant value on the stack, and a 32-bit add instruction, i32.add will pop two values off the stack as left-hand-side and right-hand-side operands accordingly, then push the sum onto the stack. On the other hand, LLVM utilizes a register-based IR, which is more similar to what one would expect on a native machine. In figure 2.4, each value for example, %0, %1, etc is a virtual register. Later in the backend, the register allocation pass will map the virtual registers into physical registers using register allocation algorithms.

**Control flow, basic block, and**  $\phi$  **instruction** As we saw in previous sections, WebAssembly has specialized instructions to manage the program's control flow. On the other hand, LLVM took a more traditional approach to the problem. In 1991, researchers from IBM introduced *static single assignment* (SSA) form to ease the difficulty of writing program analysis and transform passes [2]. In SSA, each value has its definition exactly once, and

```

1

define i32 @adler32(i8* %0, i64 %1) {

2

2:

3

%3 = icmp eq i64 %1, 0

4

br i1 %3, label %6, label %10

5

6

; preds = %10

4:

7

%5 = shl nuw i32 %20, 16

8

br label %6

9

10 6:

; preds = %4, %2

11

%7 = phi i32 [ 1, %2 ], [ %18, %4 ]

%8 = phi i32 [ 0, %2 ], [ %5, %4 ]

12

13

%9 = or i32 %8, %7

14

ret i32 %9

15

16

; preds = %2, %10

10:

17

%11 = phi i64 [ %21, %10 ], [ 0, %2 ]

18

%12 = phi i32 [ %20, %10 ], [ 0, %2 ]

19

%13 = phi i32 [ %18, %10 ], [ 1, %2 ]

20

\$14 = getelementptr inbounds i8, i8 * \$0, i64 \$11

21

%15 = load i8, i8* %14, align 1

22

%16 = zext i8 %15 to i32

23

%17 = add nuw nsw i32 %13, %16

24

%18 = urem i32 %17, 65521

25

%19 = add nuw nsw i32 %18, %12

26

%20 = urem i32 %19, 65521

27

%21 = add nuw i64 %11, 1

28

%22 = icmp eq i64 %21, %1

29

br i1 %22, label %4, label %10

30

}

```

Figure 2.4: Adler 32 in LLVM

hence, the use-definition chain (UD chain) is trivial to compute. The UD chain presents the relationship between variable declarations and variable-uses in a graph. It helps the analysis pass to efficiently pinpoint the variables and identify if the variable declaration is necessary. However, in most programs, this information needs to be merged from different control-flows; for example, in a for-loop, the loop counter may be defined in the loop initialization and on each loop iteration. The SSA introduces a special instruction,  $\phi$  instruction, explicitly marking the merge of definitions from different execution paths. LLVM adopts this design principle in its intermediate representation. In figure 2.4 we have multiple  $\phi$  instructions. For example, at line 11 and 12, value %7 and %8 represent *a* and *b* accordingly. We know that *a* and *b* initialized to 0 and 1 upon entry and updated on each iteration from our C implementation. In the generated LLVM IR, these merges induce  $\phi$  instructions. For *a* (%7), if the control flow is from the beginning of the function, we set its value to 1, and on the other hand, if the control flow is from the loop iteration, we update its value accordingly. The different paths inducing a  $\phi$  instruction are indicated by basic block numbers. A basic lock groups the maximum number of instructions without control flow transfer. At line 11, we see the  $\phi$  instruction merges the definition coming from the %2 which is the entry block and %4. Additionally,  $\phi$  instructions must appear before any other instructions within the same basic block, as they model the merging of values and do not have any execution semantics.

Memory and load-store instruction The last significant difference between WebAssembly and LLVM IR is on the memory and its related instructions. As we discussed earlier, a WebAssembly module can have access to multiple linear memories <sup>17</sup>. One might confuse WebAssembly's linear memory with the concept of address space in LLVM IR. LLVM IR associates each address with an integer value, namely, the address space. However, unlike linear memory in WebAssembly, which has no difference between one and another, the LLVM backend interprets the address space differently for various architectures. For example, in the PTX backend, a backend target for Nvidia GPUs, the implicit address space 0 refers to traditional main RAM, and address space 4 represents the address shared by both main RAM and GPU RAM<sup>18</sup>. For most architectures, the implicit address space is the only address space available to the programmer. Another difference between WebAssembly and LLVM IR is in the design of load-store instructions. Load store instructions in both languages have an attribute of alignment. However, LLVM IR interprets this attribute differently from WebAssembly. In WebAssembly, the alignment attribute acts as a hint to the runtime environment. If the alignment hint is unsuitable, the runtime environment should still proceed under a possible penalty in the performance. However, in LLVM IR, the alignment attribute is a requirement. Any memory access that violates

<sup>&</sup>lt;sup>17</sup>In the current version of WebAssembly, only one linear memory is allowed per module <sup>18</sup>An introduction for PTX backend:

https://llvm.org/devmtg/2011-11/Holewinski\_PTXBackend.pdf

the alignment attribute will result in undefined behaviour, usually a runtime panic. A load-store instruction in LLVM IR with alignment set to one will never fail. However, it will be significantly less efficient as the backend will likely generate byte-wise load and concatenation instructions.

We visited some of the background information that helps with understanding the thesis in this chapter. The next chapter will start from the beginning of the system implementation, the WebAssembly parsing and validation frontend.

## Chapter 3

### Frontend

This chapter describes the frontend of SableWasm. The frontend consists of two parts, the bytecode parser and the validation pass. WebAssembly is a continuously evolving language, and its community might add new instructions in the future. Hence, the design of the parser and the bytecode validation phase closely follows WebAssembly's specification and is modular to ensure the framework's extensibility. Additional functionalities are provided via a read-only view of the module structure. The design of the parser and the validation phase focuses on performance, both in execution time and memory footprint.

#### 3.1 Bytecode Parser

One of WebAssembly's binary format design goals is to be simple to parse. Although open-source bytecode parsing and validation libraries have become available at this point, such as WABT<sup>1</sup> provided by the WebAssembly community, there was no suitable library at the time when the project starts. Thus, for SableWasm, we implemented our bytecode parsing frontend instead. The bytecode parser consists of three components: the bytesource reader, WebAssembly bytecode parser and the parser delegate. This section will

<sup>&</sup>lt;sup>1</sup>WebAssembly Binary Toolkit: https://github.com/WebAssembly/wabt.git

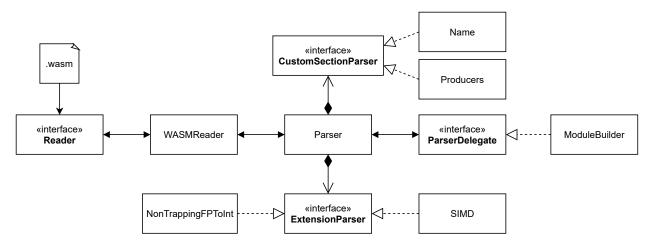

Figure 3.1: SableWasm parser

give a brief description of each component, and figure 3.1 presents a general illustration of the parser design.

**Byte-source reader** The byte-source reader consists of two parts, the byte-buffer reader and the WebAssembly reader. The byte-buffer reader provides essential functionalities such as reading and skipping ahead. Additionally, the byte-buffer reader also needs to support rewind and enforce an end-of-stream barrier. Any out of bound access, either beyond the barrier or if the byte stream is exhausted, will signal via exceptions. On the other hand, the WebAssembly reader provides a richer interface to the parser, such as the ability to decode LEB-128 encoded integers and parse WebAssembly value types. The WebAssembly reader is also responsible for validating the result before passing it to the parser. In the case where the result is invalid, the reader throws exceptions similar to the byte-buffer reader.

**WebAssembly parser** WebAssembly parser is the kernel part of the parsing framework. As we discussed earlier in this chapter, one of the primary design goals of the framework is its extensibility. Hence, the SableWasm parser is modular and consists of three parts: the parser core, the custom section parser and the instruction extension parser. The grammar for the WebAssembly binary representation is quite simple, and therefore, the parser core implements a simple top-down recursive descent parser with a single byte look-ahead.

*Custom sections* are a special section defined in the WebAssembly standard. They are essentially a binary data chunk tagged with a string name. How to interpret the binary data can be different in each case. These custom sections can either be standardized by the community or defined as specific to a toolchain. In this project, we implement two custom sections standardized by the WebAssembly working group, namely Name section and Producer section. The Name section gives human-readable names to functions and their local variables that help with program debugging. The specification does not require these names to be the same as the import or export names. There is no direct support for more detailed debug information encoding in WebAssembly at the time of thesis writing; however, extensions are working on this problem, such as DWARF for WebAssembly<sup>2</sup>. The *Producer* section is relatively simple. It only encodes information about the toolchain that generates the module, such as the toolchain name and version. All custom section parsers in SableWasm are derived from the base class CustomSection. The parser core will dispatch the binary chunk to the corresponding custom section parser based on the name tag. Each custom section parser manages its results and does not communicate to the parser delegate directly.

Instruction extension parsers focus on another different aspect of the WebAssembly module. In the background section, we have visited several extensions that merged with the WebAssembly specification. A quick reminder, WebAssembly extensions can insert or modify the instructions defined in the minimum-viable-product (MVP) specification. The SableWasm WebAssembly parser employs instruction extension parsers to address this problem. When the parser intends to parse an instruction, it will iterate over all its instruction extension parsers in a chained manner. If the instruction opcode is not recognized by any registered instruction extension parser nor in the minimum-viable-product specification, the parser will signal the error by throwing an exception. An instruction

$<sup>^{2}</sup> DWARF \ for \ Web Assembly: \ \texttt{https://yurydelendik.github.io/webassembly-dwarf/}$

extension parser can also override the default behaviour for MVP instructions by handling instructions early, though, in the current version of WebAssembly, no extensions modify the semantics of these instructions. In this project, we implement two instruction extension parsers, the non-trapping-float-to-int conversion parser and SIMD parser, which handles the instructions introduced by the extensions as their names suggest.

**Parser delegate** The last part of the SableWasm WebAssembly bytecode parser is the parser delegate. The parser delegate and the parser core directly implement the typical delegation pattern seen in many other projects, separating the parsing logic from the heavy lifting of module construction. One can implement a validation pass at this level without module construction. However, in this project, we implement our bytecode validation pass after the module construction, giving space for further projects focusing on bytecode-level transformation. We will discuss the implementation of such a validation pass later in the chapter.

In this section, we gave a brief overview of the parser framework introduced in Sable-Wasm. In the next section, we will discuss the WebAssembly bytecode representation used in the project and several techniques to improve the performance and ensure flexibility.

### 3.2 WebAssembly Bytecode Representation

The WebAssembly specification provides compact representations in both binary and text formats [8], and might subject to change in the future. In SableWasm, we implement our bytecode representation as close to the specification as possible. Hence, in the future, if the community alters the specification, we can straightforwardly update the bytecode representation without introducing extra complexity. In figure 3.2, we present an illustration of the bytecode representation used in SableWasm. The WebAssembly bytecode representation in SableWasm consists of three layers: the module, the entities, and the

Figure 3.2: SableWasm bytecode representation

instructions, which we will discuss in detail later in this section. Compared to the representation given in the WebAssembly specification, the only difference we have is the Function. The standard WebAssembly bytecode representation splits the function section into two different sections, *function* and *code*, to achieve its one-pass validation goal. The *function* section contains the type of all functions defined in the module, similar to function declarations in other programming languages. Later in the module, the *code* section defines them. On the other hand, in SableWasm, we merge these two sections into a single Function object. A Function in SableWasm bytecode representation contains both its type and body definition.

**WebAssembly module view** The WebAssembly module structure only serves as a storage container for the bytecode representation and itself does not provide an interface to the user, except by retrieving entities by index. Additionally, the WebAssembly standard binary format focuses more on compactness instead of usability, which leads to complexity when retrieving the information. For example, to avoid duplication, the function types are stored in their own section, namely, the *type* section. Later in the module, any reference to the type becomes indices within this section. Another example is entity indices. The WebAssembly specification requires that every import entry in the *import* section implicitly introduces an index in its corresponding class. These indices should come before any definition introduced in the module. These two rules suggest that to retrieve an entity by index, one should first iterate over all the imports and then locate the entity accordingly, which is a relatively expansive operation. To address these problems, we implement a read-only view of the WebAssembly module that caches the indices and provides additional features.

**Instructions** SableWasm takes a traditional 'abstract syntax tree' approach to bytecode instruction representation. The frontend represents each instruction using a corresponding class derived from a common base class, namely Instruction, and an expression with a vector of instruction pointers. One observation is that the heap memory usage grows rapidly, as each instruction requires a unique heap-allocated object, which is not optimal. In WebAssembly, instructions operate over an implicitly defined stack, and for most of the operations, there are no operands attached to them. For example, F32x4Nearest has no operand; it will pop a value from the stack, treat it as a vector of packed single-precision floating-point values, round them to the nearest integer, and finally push the result back to the stack. From the bytecode representation point of view, there is no difference between multiple instances of the same instruction. Hence, we use pointers that point to object singletons to represent instructions without operands to reduce memory consumption. However, this introduces a problem in distinguishing a pointer that points to an object from one referring to an actual heap-allocated object which requires memory deallocation. To address this problem, we use tagged pointers. For a non-heap allocated singleton object, we tag the least significant bit in the pointer with zero; and on the other hand, we tag that of a heap-allocated object pointer with one. Later, we only need to examine the pointer's least significant bit within the destructor and deallocate memory when needed. With tagged pointer techniques, we can significantly

Figure 3.3: SableWasm validation pass

reduce the memory needed to store the bytecode representations while maintaining their polymorphic nature. As less memory allocation is needed, we also observe performance improvement in terms of execution time, which we will later see in this chapter.

This section gave an overview of the bytecode representation used in SableWasm and several techniques to improve its performance. In the next section, we will move to the validation pass implementation in SableWasm.

# 3.3 WebAssembly Bytecode Validation

The WebAssembly specification defines detailed static validation rules both for wellformedness and type-soundness. Similar to the parser framework, we implement our validation pass as close to the specification as possible. If there are changes to the specification in the future, we can adopt them with minimal effort. The validation pass implementation consists of three parts: the validation context, the validation visitor, and the trace collector as illustrated in figure 3.3. Later in the section, we will give a brief introduction to each of the components. The detailed validation rule, both well-formedness and type-soundness, are listed in the WebAssembly introduction paper [8], and a separate paper that focuses on validation [35]. Note that these two papers only present the validation rules for the minimum viable product (MVP) WebAssembly and each extension may modify the specification. The additional validation rules introduced by the extensions adopted by SableWasm are relatively trivial. Hence, we will not give a detailed description here, and one should consult the extension proposals for detailed information.

**Validation context** The validation context implements the context defined in the WebAssembly specification. It provides an easy way for the validation visitor to access the WebAssembly entities' declarations. The validation context itself does not perform any error signalling. The validation context also manages the operand stack and the label stack. The operand stack stores the type information gathered from the instruction within the expression while the label stack keeps track of the signatures of the control flow structures. The operand stack also records the requirements generated from type variable sequences and checks if there are contradictions among them.

**Validation visitor** The validation visitor is the core driver part of the validation pass. It implements all the validation rules for each instruction and derives from the visitor template. In the current state of implementation, the design of the validation visitor is not modular, and hence, if additional instructions are added to the project later, direct modification is required. The validation visitor also handles all the error signalling. However, it does not construct the error objects by itself. The task is deferred to the trace collector. For most of the instructions, the validation rule is quite simple, involves only popping and pushing values to the operand stack. Currently, the validation visitor will stop at the first error it encounters due to the WebAssembly validation rules' design.

**Trace collector** The last part of the validation pass implementation is the trace collector. It locates the position of the instruction that currently undergoes validation. It first keeps track of the section where the instruction lives with an enumeration and uses a stack to track how to locate it. Every time the validation visitor enters a nested construct such

as if, block or loop, it pushes the construct to the site stack and pops when a nested expression finishes validation. If the validation visitor locates an error, the trace collector will build the error by moving the trace stack into the error object.

In this section, we presented the validation pass implementation in SableWasm. In the next section, we will perform some experiments to evaluate the system's performance in terms of both execution speed and memory footprint.

# 3.4 **Performance Evaluation**

This section presents the performance benchmark comparison between the SableWasm parser frontend and the WebAssembly binary toolkit (WABT) offered by the WebAssembly community group. The benchmarks focus on both the execution time and memory footprint. We will first present the benchmark setup and then evaluate the data collected from the experiment.

**Benchmark setup** Experiments were performed on a server with a six-core Intel Core processor at 3.7 GHz standard clock frequency and an L3 cache of 12MiB. The server runs Ubuntu 18.04 with Linux kernel version 4.15.0 and 32GiB of memory. For the benchmark subject, we choose Pyodide <sup>3</sup>, a WebAssembly implementation of Python 3.8. The project has reasonable complexity, and the size of the module is quite significant, which reduces the measurement errors during the benchmark. The WebAssembly binary toolkit (WABT) we used during the benchmark is version 1.0.23, and we perform module validation with its wasm-validate command. This command should parse the WebAssembly module, construct an internal bytecode representation, and finally perform a validation pass over it. This procedure is similar to what we used in the SableWasm frontend. For the execution speed experiment, we time the execution speed with the shell builtin time command. We perform ten runs for each implementation in total and then compute the

<sup>&</sup>lt;sup>3</sup>Pyodide project: https://github.com/pyodide/pyodide

**(b)** WABT

Figure 3.4: Frontend memory footprint comparison

average execution speed. For memory footprint, we use the Massif tool provided by Valgrind [22]. Massif is a heap profiler that collects heap memory usage throughout a program lifetime, which we will use to compare two implementations.

**Benchmark result** We will go over the finding over the execution speed first and then analyze the memory footprint. Table 3.1 gives the result of the execution speed benchmark. The data is relatively consistent over a total of ten runs, where the SableWasm frontend achieves around 1.5x to 1.7x speedup compared to wasm-validated provided by WABT. On average, the SableWasm frontend is 1.6x times faster than WABT's implementation.

| Run     | SableWasm | WABT  | Speedup |

|---------|-----------|-------|---------|

| Run #1  | 0.311     | 0.523 | 1.682   |

| Run #2  | 0.308     | 0.511 | 1.659   |

| Run #3  | 0.307     | 0.511 | 1.664   |

| Run #4  | 0.329     | 0.513 | 1.559   |

| Run #5  | 0.336     | 0.520 | 1.548   |

| Run #6  | 0.317     | 0.534 | 1.685   |

| Run #7  | 0.315     | 0.518 | 1.644   |

| Run #8  | 0.335     | 0.522 | 1.558   |

| Run #9  | 0.311     | 0.513 | 1.650   |

| Run #10 | 0.335     | 0.574 | 1.713   |

| Average | 0.320     | 0.524 | 1.635   |

Table 3.1: Frontend execution speed comparison

On the topic of memory footprint, figure 3.4a and figure 3.4b shows the memory consumption trace for SableWasm and WABT, respectively. As we can see from the figures, SableWasm consumes approximately 108MiB at peak while WABT uses around 506MiB, suggesting a 4.6x reduction in memory footprint. More specifically, SableWasm spends about 38MiB for bytecode representation, and WABT takes roughly 64MiB, indicating a 1.7x reduction for bytecode representation only. Note that in SableWasm's heap memory trace, we can accurately determine the memory consumption of bytecode representation using debug symbols. However, this is not the case for WABT, where the debug information is stripped from the executable. In this experiment, we estimate the memory consumption for bytecode representation via the vector that contains the opcode.

Overall the SableWasm frontend implementation performs better than WABT in terms of both execution speed and memory footprint. Of course, SableWasm is a static compiler that will only perform parsing and validation at compile-time and does not affect the overall execution time for emitted executables. However, in the future, if one would like to implement a just-in-time (JIT) style compiler, the SableWasm parsing and validation frontend can effectively improve the response time of the JIT compiler.

We visited the design and implementation of the SableWasm frontend, which takes care of parsing, validating and constructing a bytecode representation in this chapter. In the next chapter, we will move to the next phase in the SableWasm compilation pipeline, the middle-level intermediate representation.

# Chapter 4

# Middle-level Intermediate Representation

This chapter describes SableWasm's middle-level intermediate representation (MIR), which has a critical role in the entire compilation pipeline. The MIR acts as a middle ground between the WebAssembly bytecode frontend and various possible backends. Currently, SableWasm only implements one backend that utilizes the LLVM compilation framework, but adding more backend support should not require significant modification on the MIR. It also implements an analysis and transformation framework where we perform several optimizations over the MIR. We will first go over the overall design of the MIR, and later move to the translation rules and analysis framework in the chapter 5.

In the previous chapters, we covered the design of WebAssembly bytecode. A quick reminder, WebAssembly is a stack-based intermediate representation (IR) where all instructions operate over an implicitly declared operand stack. There are several advantages of a stack-based IR. Perhaps the most important one is its portability. A stack-based IR makes fewer assumptions on the machine than a register-based one. One can even provide an implementation for a hypothetical device with only one register. Another advantage is the code size. Experiments show that, in general, a stack-based IR is smaller in size than its corresponding registered version [30]. When designing a binary format that ships executables over the internet, the stack-based IR seems to be a better choice for WebAssembly.

Nevertheless, there are no silver bullets: a stack-based IR design also has its drawbacks. One of them is the difficulty faced when performing code analysis and transformation over the module. As for each instruction, its operands implicitly come from the stack; the value use-definition relationship between instructions is not apparent to the analysis, and recovering such connection between instructions from the IR is not a trivial task.

On the other hand, we have the register-based intermediate representation, commonly abstracted to assume an infinite number of registers and requiring a register allocation algorithm to map them to actual, physical registers. For each instruction in register-based IR, it has its operand encoded in the instruction. Hence, the use-definition relationship will become explicit to the analysis and transformation.

The main design goal for SableWasm MIR is to provide an analysis platform for the entire compiler system. Thus, we implement our MIR as an infinite register machine. We also take a traditional approach in various other aspects. For example, instead of using the structured control flow similar to what WebAssembly offers, we use *control-flow graphs* (CFGs) to represent the relationship between basic blocks. The SableWasm MIR is also in *single static assignment* (SSA) form [2], as covered in the background chapter. The design for instruction and module-level entities in SableWasm MIR is quite similar to what WebAssembly instruction offers. One can view the SableWasm MIR as a mixture of the target LLVM intermediate representation and the source WebAssembly bytecode. We also adopt several design features from LLVM IR into MIR, such as automatically managed use-site lists, which provide each AST node with an efficient way to access their use sites. In SableWasm MIR, all elements are derived from the base class ASTNode which implements these features that are helpful later in MIR analysis and transformation.

```

1 @export memory

2 memory %memory:0 : {min 2}

3

4 table %table:0 : {min 1, max 1} funcref

5

6 global %global:0 : var i32 = i32 66560

7

8 function %fibonacci : [i32] -> [i32] {

9 {(arg)%0:i32}

10 # pred = \{\}

11 %entry:

%1 = local.get (arg)%0

12

13

br.table %BB:1 0:%BB:2 1:%BB:0

14

15 #pred = {%entry}

16 %BB:0:

%2 = const i32 1

17

18

br %exit

19

20 # pred = \{ % entry \}

21 %BB:1:

22

%3 = local.get (arg)%0

23

\$4 = \text{const i32} - 1

24

%5 = int.add %3 %4

25

%6 = call %fibonacci(%5)

%7 = local.get (arg)%0

26

27

88 = const i 32 - 2

28

%9 = int.add %7 %8

29

%10 = call %fibonacci(%9)

30

%11 = int.add %6 %10

31

local.set (arg) %0 %11

32

br %BB:2

33

34 #pred = {%BB:1, %entry}

35 %BB:2:

36

%12 = local.get (arg)%0

37

br %exit

38

39 #pred = {%BB:2, %BB:0}

40 %exit:

41

%13 = phi i32 [%2, %BB:0] [%12, %BB:2]

42

ret %13

43

44 }

```

Figure 4.1: Fibonacci in translated SableWasm MIR

Figure 4.2: SableWasm MIR Module-level entities

Figure 4.1 shows a simple function that calculates Fibonacci numbers with a recursive method in SableWasm MIR. With the help of the figure, we will go through the detailed design of SableWasm later in the chapter. We will first present the module-level entity and their initializer expressions, such as functions, then move to the design of each instruction defined in MIR.

# 4.1 MIR Module Entities

SableWasm module-level entities are the top-level elements in a translation module. They are direct implementations of the WebAssembly module entities defined in the specification. Figure 4.2 presents a general illustration of the SableWasm module-level entities. In this section, we will cover the design of each entity and compare it with its WebAssembly correspondent. All SableWasm module-level entities can optionally have import and export annotates, except data and element. These annotations correspond to the import and export entries defined in the WebAssembly specification.