National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your Re.: Votre releience

Our life - Notice reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

**AVIS**

If pages are missing, contact the university which granted the degree.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# FPGA Driven Synthesis Employing a Self-Testing VLSI Controller Implementation as a Case Study

Betina K. Hold, (Bachelor Eng 1988)

McGill University, Montreal

November 1994

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file. Votre reference

Our file Notice retaining

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS.

L'AUTEUR A ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THY SIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION.

L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

ISBN 0-612-05453-5

1.

#### SHORTENED TITLE OF THESIS

FPGA Driven Synthesis Employing a Self-Testing VLSI Controller

## Abstract

As the complexity of VLSI circuits increases and the time to market requirements become more stringent, the demands on the designer aggrandize while the challenges of achieving specified performance intensify. The skill of rapidly producing functional circuits for intrasystem testing and prototyping is essential to the electronic market. Tools which aid the designer, thereby quickening the design cycle are indispensable. However, the methodologies employed by these tools, though maturing, still necessitate amelioration, as shall be shown through a conceivable case study.

Rapid prototyping in numerous digital application domains are served by synthesis and FPGA technology. Embedded controller systems touch one application area. The study of particular design examples can provide information on the current status of tools, their algorithms, and available hardware architectures and consequently furnish a list of deficiencies and efficacious enhancements towards further, automatically generated implementations. In fact, subsequent to in depth research into FPGA architectures, synthesis algorithms, and digital design techniques, one example application was realized. This particular case study lead to proposed specifications supporting foundations for an "Application Specific Design and Synthesis System", and their necessity particularly when design time is critical and real-time responses are in demand.

This thesis formulates, and implements an automotive Anti-lock Brake System (ABS), reporting on it's design simulation, synthesis, and eventual layout steps, from which extensions are drawn towards digital controllers onto FPGA technology, and the potential migration of the design onto ASIC technology. Implementation/environment fine-tuning of embedded controllers as such necessitate quickly prototyped circuit realizations. Examination of its functionality, real-time response, implementation, and testability is performed in an

attempt to measure the usefulness of higher level design entry facilities such as VIIDL in a rapid prototyping environment. Continuous on-line testing is included using aperiodic sample injections where the resultant generated values are compared to signatures known a priori, without compromising functionality. The achievable area and timing aid in the determination of the efficiency of the process and provide fuel for an FPGA and/or ASIC migration path for eventual implementation. Commentaries and generalized methodologies are assembled from the design's simulation, synthesis and layout utilizing VIIDL and FPGAs, illustrating CAD tool capabilities/requirements/limitations, with respect to real-time synthesis and rapid prototyping of general controller applications involving asynchronous elements.

# Résumé

La complexité grandissante des circuits VLSI et la réduction de leurs échéances de mise en marché imposent une productivité croissante aux concepteurs dans le but de rencontrer les critères de performance demandés. L'expertise requise pour la production rapide de circuits prototypes complets et de prototypes fonctionnels en guise de substitution aux composantes non-conçues d'un système est essentielle aux tests de la phase de développement d'un produit du marché de l'électronique. Des outils sous forme de logiciels sont devenus indispensables pour accélérer le processus de conception. Cependant, bien que ces outils aient atteint un certain niveau de maturité, ils ont plusieurs défaillances qui doivent être améliorées. Cette constatation fera l'objet d'un cas d'étude pratique présenté dans cette thèse.

La conception rapide de prototypes dans plusieurs applications du domaine de l'électronique numérique emploient la synthèse digitale et les tableaux de portes logiques programmables (FPGA). Les contrôleurs digitaux encastrés à leurs systèmes représentent une telle application. L'examen de concepts digitaux pratiques fournira des données importantes sur l'efficacité de la synthèse, des algorithmes, et des architectures digitales disponibles à l'intérieur des outils en plus d'indiquer des voies menant à l'amélioration de la performance de ces mêmes outils. En effet, à la suite de recherches approfondies sur les architectures FPGA, les algorithmes de synthèse and la conception digitale, un exemple d'application à été conçu. Ce cas d'étude particulier à conduit à la proposition de justifications supportant la base dans le Domaine d'Application Spécifique (CSDAS) En particulier, la nécessité du CSDAS sera argumentée pour les produits ayant de courtes échéances de conception et les systèmes à reaction temporelle critique.

Cette thèse utilise la spécification d'un système de freins anti-blocage (ABS) pour illustrer le processus de simulation, synthèse, et la mise en circuit de contrôleurs digitaux sur des FPGAs. En outre, la transformation possible de ces contrôleurs sur des circuits intégrés à application spécialisée (ASIC) est discutée. Les multiples étapes de raffinement dans la conception de contrôleurs digitaux encastrés requièrent la disponibilité rapide de circuits prototypes. Dans le cas du contrôleur ABS, la qualité des outils de haut niveau d'abstraction, comme VHDL, est mesurée seton les opérations fonctionnelles de l'implémentation résultante, la rencontre des contraintes de performance temporelles, et la capacité du circuit à être verifié pour son bon fonctionnement.

Un méchanisme d'auto-vérification apériodique est intégré au système. Des vecteurs tests sont injectés dans le circuit et les réponses du système sont alors comparés aux signatures obtenues a priori d'un circuit sans défauts. Les tests se produisent de façon continuelle pendant l'opération normale du circuit et ce sans compromettre aucune des ses fonctions. La surface de silicium requise et la performance temporelle des circuits synthétisés contribuent à l'analyse de l'efficacité des outils de synthèse. De plus, ces données fournissent un cheminement vers l'implémentation éventuelle du contrôleur sur un FPGA ou un ASIC. D'autres résultats, acquis à partir d'outils sur le langage VHDL et de synthèse sur les FPGAs, génèrent des observations additionnelles. Ces résultats provenant de simulations, de synthèse et de mise en circuit démontrent les exigences, les limitations et les capacités des outils de conception assistée par ordinateur par rapport à la synthèse de contrôleurs ayant des composantes asynchrones et la rencontre de leurs contraintes temporelles.

# Acknowledgements

The work presented has been supported partly by the Natural Sciences and Engineering Research Council of Canada (NSERC), by Dr. V. K. Agarwal, with the aide of the facilities of the McGill's Microelectronics and Computer Systems Laboratory (MACS) and the tools and workshops of the Canadian Microelectronics Corporation (CMC).

From a professional perspective, I would like take this opportunity to thank my supervisor, Prof. Vinod K. Agarwal for allowing me to pursue this area of study, for providing me with the means to accomplish whatever tasks were necessary, and for supporting my attendance to several conferences and workshops. I would also like to express thanks to Professor Bhatt for his co-supervision and continuous proof-reading of all my papers and thesis outlines. Owing to the strength of inter-university bonds, gratitude also goes to Professor Cerny, Université de Montréal, for offering me a chance to pursue PhD studies in an interesting and closely related field. And last, but definitely not least, I would like to thank Jindrich Zejda (Jindra) for his help in proof-reading and giving focus to this thesis, the fruit of my efforts.

On a personal note, I would like to express my sincere thanks to my parents, Anton and Anita Hold for their constant support and understanding throughout my Bachelor's and Master's, François Lambert for bearing with me, for providing unix administrative advice and for helping organize the figures and the final thesis format, and to my family, Markus and Susan Hold for understanding that I would resume my existence as an available family member once the never-ending days of lab-life would be finished. Je remercie Eric Masson pour son aide, ses réponses détaillées et bien pensées, sa traduction de l'abstract et son support moral, and Jacek Slaboszewicz, our indispensable system administrator for providing me with a superb working environment, and so many answers. I would also like to mention Mike Toner for his aide in scanning in the FPGA pictures, and most of all for his listening ear, his advising and his boosting. And lastly, I thank MOSAID Technologies Inc., my new employers, for offering me work in my preferred field of interest and providing that last incentive to finish.

# Contents

| Λ | bstr | net                                                                      | ì   |

|---|------|--------------------------------------------------------------------------|-----|

| R | ésun | né                                                                       | iii |

| A | ekno | wledgements                                                              | v   |

| 1 | Inti | roduction                                                                | 1   |

|   | 1.1  | Background to the Real-time Controller Design and Synthesis onto FPGAs . | 2   |

|   | 1.2  | Design Issues, Models, and Tools                                         | 5   |

|   | 1.3  | Motivation and Research Goals                                            | 7   |

|   | 1.4  | Author's Specific Contribution                                           | 8   |

| 2 | Coı  | stroller Implementation Fundamentals                                     | 10  |

|   | 2.1  | Theory behind the Controller Design and Implementation                   | 10  |

|   |      | 2.1.1 System Dynamics Definitions                                        | 11  |

|   |      | 2.1.2 Asynchronous vs Synchronous Design and their Synthesis             | 11  |

|   |      | 2.1.3 Control System Commonalities with Respect to Synthesis             | 13  |

|   | 2.2  | Automated and FPGA Specific Synthesis                                    | 15  |

|   |      | 2.2.1 Synthesis Fundamentals                                             | 17  |

|   |      | 2.2.2 Controller Synthesis Techniques                                    | 19  |

|   | 2,3 | FPGAs: Technology of the Times                     | 2()  |

|---|-----|----------------------------------------------------|------|

|   |     | 2.3.1 FPGA Classification and Architectures        | 21   |

|   |     | 2.3.2 FPGA Propitions Technology-specific Features | 26   |

|   |     | 2.3.3 Delay Modeling and Estimation                | 27   |

|   |     | 2.3.4 Technology Considerations                    | 28   |

|   | 2.4 | VIIDL for Design Entry                             | 29   |

|   | 2.5 | Evaluation of Synthesis Quality                    | 30   |

|   | 2.6 | Testability Measures                               | 31   |

| 3 | Cor | troller and FPGA Design Considerations             | 33   |

|   | 3.1 | Requirements for Optimal Controller Design         | 33   |

|   | 3.2 | FPGA Design Flow                                   | 3-1  |

|   | 3.3 | VHDL Constructs                                    | 35   |

|   | 3.4 | The Testable Design                                | 37   |

|   |     | 3.4.1 Fault-Detecting and Fault-Tolerant Designs   | 39   |

|   |     | 3.4.2 Test Circuitry Evaluation Criteria           | -[(] |

|   | 3.5 | Design Procedures                                  | -11  |

| 4 | The | ABS Control Model                                  | 43   |

|   | 4.1 | ABS Dynamics                                       | 43   |

|   |     | 4.1.1 Motivation for ABS Design and Implementation | 43   |

|   |     | 4.1.2 The ABS Functional Model                     | 44   |

|   |     | 4.1.3 ABS Design Specifications and Structure      | 46   |

|   |     | 4.1.4 The Self-Testing Design                      | 52   |

|   | 4.2 | Design Engineering and Mechanics                   | 54   |

|   |     | 4.2.1 Tooling of Design                            | 5.5  |

|   |     | 4.2.2   | Preamble and Approximations for an ABS Realization                  | 56  |

|---|-----|---------|---------------------------------------------------------------------|-----|

| 5 | FPC | GA Syr  | nthesis                                                             | 61  |

|   | 5.1 | The F   | PGA Design Cycle                                                    | 61  |

|   |     | 5.1.1   | Tuning an Application to FPGA Structures                            | 62  |

|   |     | 5.1.2   | Encoding Primitives                                                 | 64  |

|   | 5.2 | FPGA    | Implementation of ABS                                               | 66  |

|   |     | 5.2.1   | Control Circuitry                                                   | 66  |

|   |     | 5.2.2   | Self-testing Circuitry                                              | 70  |

|   |     | 5.2.3   | Simulations                                                         | 74  |

|   |     | 5.2.4   | Timing Considerations                                               | 75  |

|   | 5.3 | Synthe  | sis                                                                 | 77  |

|   |     | 5.3.1   | Implementation Specifics and Results                                | 77  |

|   |     | 5.3.2   | VHDL Synthesis and Tool Support                                     | 82  |

|   |     | 5.3.3   | FPGA Design Specifics                                               | 84  |

| 6 | Des | ign and | d Synthesis Methodologies                                           | 88  |

|   | 6.1 | Well-C  | onstructed Procedures for FPGA Conceptualization and Implementation | 90  |

|   |     | 6.1.1   | FPGA-Specific Hardware Considerations                               | 91  |

|   |     | 6.1.2   | VIIDL Encoding Styles                                               | 92  |

|   |     | 6.1.3   | Design Problems: FPGA Solutions                                     | 94  |

|   |     | 6.1.4   | FPGA Test Philosophy                                                | 98  |

|   | 6.2 | FPGA    | Synthesis Issues and Proposed Solutions                             | 100 |

|   |     | 6.2.1   | FPGA Structures and Design Methodologies                            | 102 |

|   |     | 6.2.2   | Design Entry and VHDL                                               | 103 |

|   |     | 6.2.3   | Synthesis/Layout Suggestions                                        |     |

|   |     |         |                                                                     |     |

|    |       | 6.2.4  | Functional Self-Checking    |               | <br><i>.</i> | 109   |

|----|-------|--------|-----------------------------|---------------|--------------|-------|

|    |       | 6.2.5  | Mapping onto FPGAs          | • • • • • • • | <br>         | 110   |

| 7  | Clos  | ing Re | emarks                      |               |              | 111   |

|    | 7.l   | Accom  | plishments and Results      | • • • • • • • | <br>         | 111   |

|    | 7.2   | Conclu | sions                       |               | <br>         | 112   |

| Bi | bliog | raphy  |                             |               |              | 116   |

| A  | ABS   | 5 Theo | ry, Notation, and Dynamics  |               |              | 122   |

| В  | Exa   | mples  | of VHDL Code                |               |              | 130   |

| C  | Syn   | thesis | and Supporting Libraries    |               |              | 140   |

|    | C.1   | FPGA   | Library Motivation          | • • • • • • • | <br>         | . 141 |

|    | C.2   | Existi | ng Concepts                 |               | <br>         | . 143 |

|    | C.3   | Propo  | sed Library Component Types |               | <br>         | . 145 |

|    | CA    | Synth  | osis Tool Functionality     |               |              | 146   |

# List of Figures

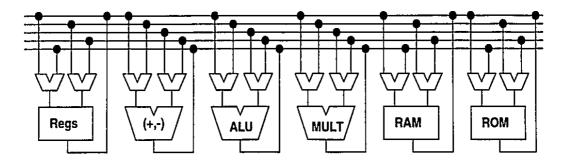

| 2.1 | Typical datapath components and their interconnections                                                                                                                                                                                                                                                                                                                             | Į5 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

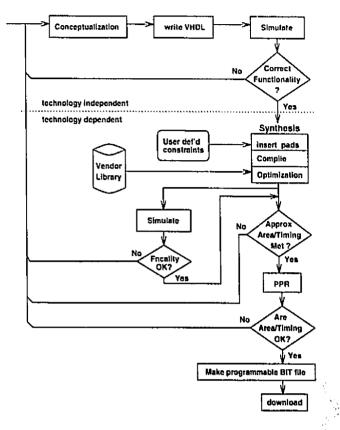

| 2.2 | FPGA design flow chart for VHDL design and implementation                                                                                                                                                                                                                                                                                                                          | 16 |

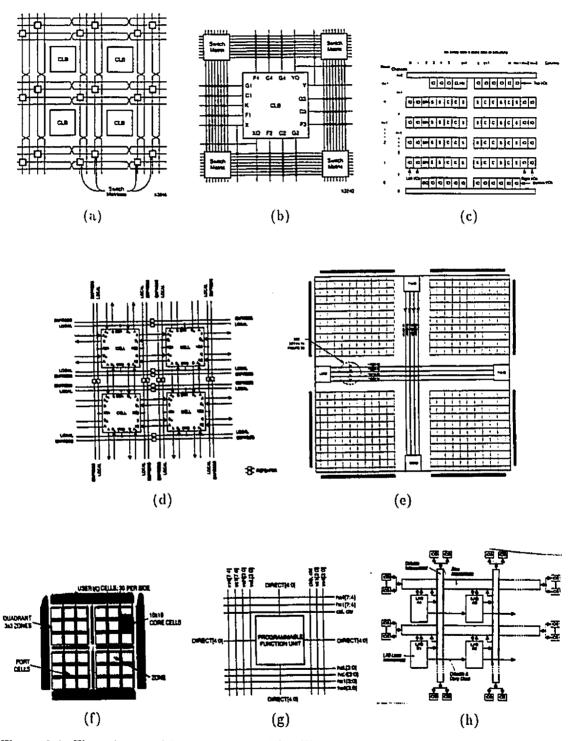

| 2.3 | Floorp'ans and Interconnects: (a) Xilinx's Double-Length Lines, (b) Xilinx's Adjacent Single-Length Lines, (c) Actel's Generalized Floor Plan of ACT 3 Device, (d) Atmel's Cell-to-Cell and Bus-to-Bus Connections, (e) AT&T's Interquad Routing, (f) Motorola's MPA1036, (g) AT&T's Single PLC View of Inter-PLC R-Nodes and (h) Altera's FLEX 8000 Device Interconnect Resources | 23 |

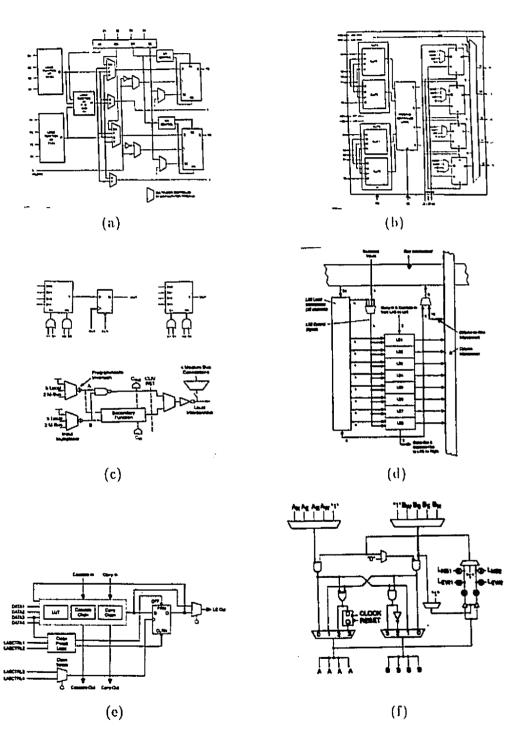

| 2.4 | FPGA Logic block architectures: (a) Xilinx'x XC4000 Configurable Logic Block, (b) AT&T's Simplified FPU Diagram, (c) Actel's S-Module & C-Module Diagram (top), Motorola's Core cell (bottom) (d) Altera's Logic Array Block (LAB), (e) Altera's FLEX 8000 Logic Element (LE) and (f) Atmel's Cell Structure                                                                       | 24 |

| 3.1 | Design flow for VHDL design and implementation using Xilinx FPGAs                                                                                                                                                                                                                                                                                                                  | 36 |

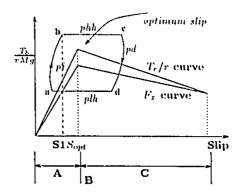

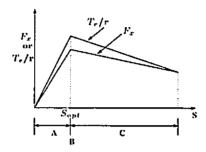

| 1.1 | Piecewise linear approximation of the tire-road characteristic and the desired path to follow under the ABS Control Loop.                                                                                                                                                                                                                                                          | 46 |

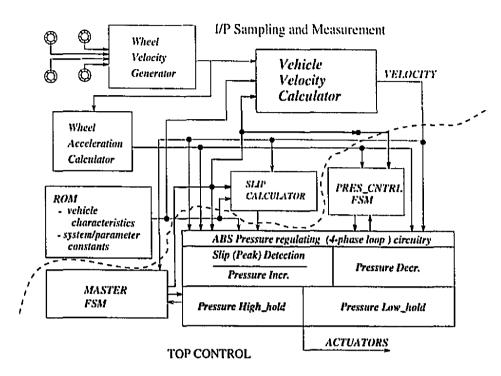

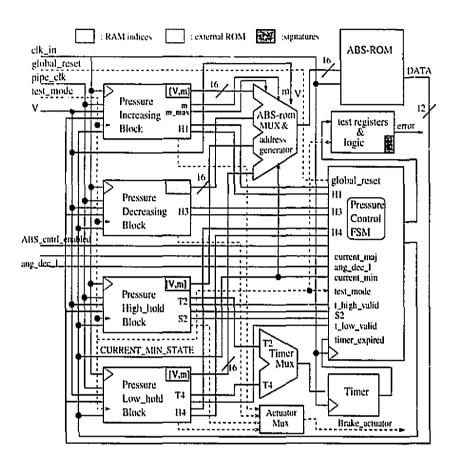

| 1.2 | Block diagram of ABS Controller: Top Level                                                                                                                                                                                                                                                                                                                                         | 48 |

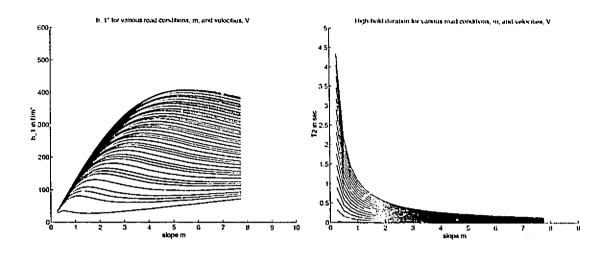

| 4.3 | Thresholds for various road conditions and a range of vehicle velocities                                                                                                                                                                                                                                                                                                           | 56 |

| 4.4 | Time duration to maintain brake pressure in the high and low holding states                                                                                                                                                                                                                                                                                                        | 56 |

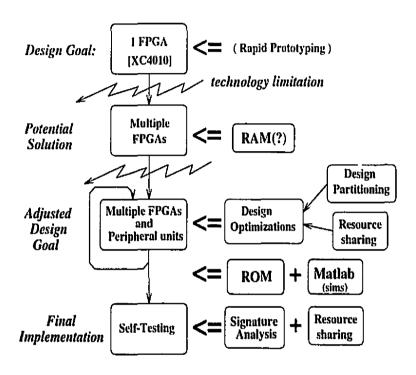

| 5.1 | FPGA design steps and realization cycle                                                                                                                                                                                                                                                                                                                                            | 63 |

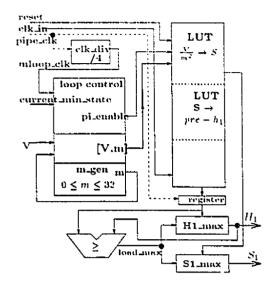

| 5.2  | Block diagram implementation of the pressure increasing state,                                               | 68  |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 5.3  | Synopsys' synthesized version of the pressure increasing state and its calculations                          | 68  |

| 5.4  | Implementation of Pressure control Blocks                                                                    | 69  |

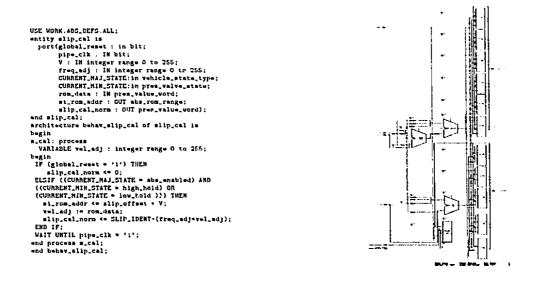

| 5.5  | VIIDL code for slip calculation                                                                              | 70  |

| 5.6  | CLB representation of slip calculation                                                                       | 70  |

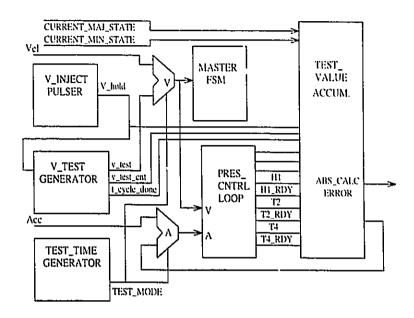

| 5.7  | Self-testing circuitry added to the pressure control block                                                   | 72  |

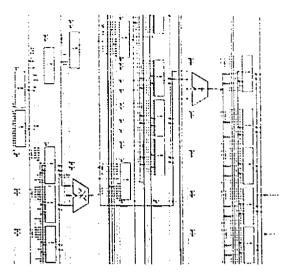

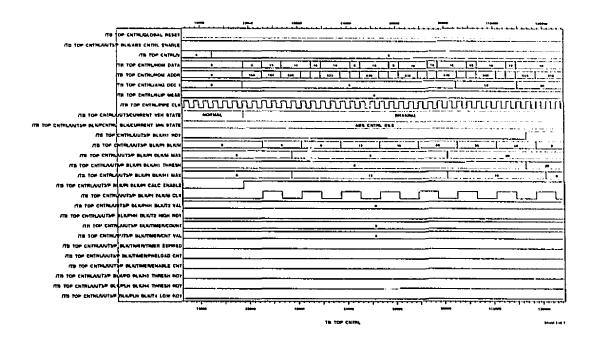

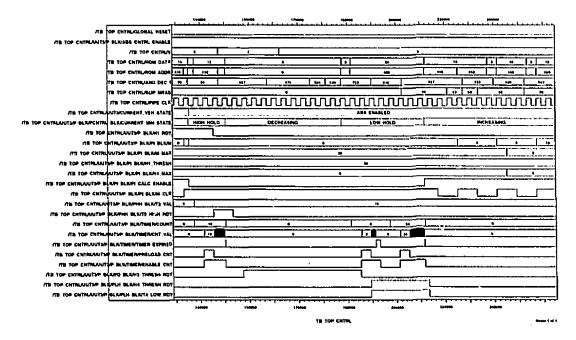

| 5.8  | Simulation results: Timing diagram of start-up and Normal to Braking transition of 4-phase ABS control loop  | 76  |

| 5.9  | Timing Diagram cont'd: high hold - decreasing - low hold - increasing transition of 4-phase ABS control loop | 76  |

| 5.10 | VHDL transformation from asynchronous code to implementable synchronous sequential code                      | 85  |

| A.1  | Piecewise linear approximation of the tire-road characteristic                                               | 123 |

## Chapter 1

## Introduction

In the 1940's the first electronic, programmable, general-purpose computer, the ENIAC, a breakthrough in its time, occupied an area 100 feet long, 8.5 feet high by several feet wide. Simple design took weeks, programming was manual, accompanied by cable connections and setting of switches, a task which took from half an hour to an entire day. Along analogous lines, in the 1990's, automatic design tools are flourishing and programmable hardware exists which can be reconfigured for an application in a matter of minutes occupying about I square inch of area. Hardware has evolved, circuit densities are increasing, permissible prototyping times have diminished, and tools which aid circuit realization have correspondingly been unfolded. From stand alone compilers and schematic entry packages, complete frameworks exist which take the designer and his/her specifications from design entry to implementation. But the questions arises, how efficient are they and is their maturity attainable? Additionally, as circuits grew larger and larger, testability became an issue, requiring controllable and observable in-circuit viewpoints. Ensuring that the resultant functionality of the hardware meets the original specifications upon fabrication and after in system utilization are difficult and grow notably with increasing circuit complexities. Conceptualization thus forth embodies testability, alongside design with its ever increasing constraint lists.

Controller designs were selected for the analysis as they represent a well-known and largely encompassing application domain. Furthermore, conjoining them with FPGA (Field Programmable Gate Array) technology, offers an alternative solution to the current micro-controller-software implementations. This additional motivation demands the assurance or surpassing of previously attained real-time effects while maintaining the ease of design en-

coding, re-encoding, compilation and testing for both faults and fine-tuning.

It is proposed in this dissertation that an investigation of hardware and software elements could produce a set of design, synthesis, testing, and implementation methodologies and recommendations for the electronics engineer and consequently facilitate future conceptualizations. Enhancements are proposed suggesting favorable evolutionary paths bridging the methodologies developed today with ones to be used tomorrow. Precluding an exclusive research-oriented study, an engineering approach to explore such hardware/software facilities/limitations was employed, utilizing case studies -specify it, build it, test it, and document and evaluate the steps undertaken. Tangible results could then be obtained, re-used, and then extrapolated to general circuit realizations and systems, and be labeled as application specific design methodologies forming the groundwork for Application Specific Design, Synthesis and Layout (ASDSL).

This engineering approach envelops the above methodologies employing technology of the times, which we refer to as Integrated Circuit (IC) technology, two of which are FPGAs and Synthesis tools. A schema, to optimize their exercise by designers in similar, future design and module undertakings, is developed, the evolution of which is best formulated through "hands-on" experimentation. Notwithstanding, the development of FPGA design and synthesis techniques requires analysis of their architectures and the tools which realize their circuits.

### 1.1 Background to the Real-time Controller Design and Synthesis onto FPGAs

The time-to-market expediency has invigorated the search for rapid circuit a..d system implementations with limited risks. FPGAs serve as excellent prototyping devices and additionally provide expeditious solutions in selected application areas. The evolution of FPGAs from Masked Programmable Gate Arrays (MPGAs) and Programmable Logic Devices (PLDs) must encompass not only architectural advances but must incite a proficiency in Electronic Design Automation, (EDA) tools as well. This thesis examines the above utilizing VHDL for design entry and separate tools for synthesis and layout onto FPGAs. Specification of timing and area constraints cannot be entered for a design in VHDL format, hence real time

constraints must be entered through a synthesis tool. Not all tools address this issue very well, many of them relying on the design - simulate iterative process.

Real-time implies an ability to respond to the fastest rate of arrival of the input events. Digital controller applications exhibit real-time qualities when their outputs are generated as soon as possible after the inputs are available within their sampling time interval. Real-time cannot be quantified in terms of time limits or intervals as individual system response times are highly application dependent. Furthermore, real-time control systems must be reliable, possess error detection capabilities and exhibit some kind of fault recovery mechanism such as an ability to restart or shut itself down. Traditionally, redundancy must also be built into the overall control system. Success in its design and implementation hinges on achieving this real time response utilizing a given technology. One of the motivations of this thesis is to explore applicability of FPGAs in real-time controller applications.

Some elements from Houpis and Lamont, [2], which receive attention in our design are: real-time task concurrency, synchronization, coordination and scheduling, response time, sectioning of internal and external timing (sampling), resource allocation, fault/error recovery, restart and system shutdown, and self testing. Though system controllers require control and data-path circuits and are most often of a synchronous nature, asynchronous factors do exist demanding, in some cases, particular treatment. Data-path logic includes operations for buffering, multiplexing, control, and data processing. Typical circuits require multiplexers, registers, buffers, FIFOs, counters, accumulators, ALUs, adders/subtracters/comparators, and are synchronous. The asynchrony emanates from the need to respond to externally sampled input and to realize the on-line self-testing mechanisms.

An ABS controller is one example of an embedded application class. A vehicle in motion is a complex, nonlinear and time varying system responding to its asynchronous environment. An ABS controller requires data from this vehicular system and its environs. Optimal control techniques and theories can provide suitable strategies for digital design and implementation, but the on-line computing requirements become excessive and somewhat time prohibitive. Hence, to obtain "real-time" responses, various assumptions, and simplifications of the ideal theoretic equations and models must frequently be proposed to reduce the on-line computing requirements while still retaining correct functionality.

Part of the implemented design comes from Kuo and Yeh [8], who describe mathematically a four-phase brake pressure control loop. No previous hardware implementation onto FPGAs for this theory is known to date, fueling the motivation for its selection for realization. Preliminary constraints entail ABS controller response time requirements which should surpass the human response time, in the order of milliseconds, while allocating adequate time to its actuators and test circuitry in addition to satisfying FPGA area and size limitations.

Rapid prototyping is one of the virtues resulting from FPGA technology. FPGAs present more restrictions to the design automation tool, while offering more flexibility to the designer. Their Logic block structures exhibit larger granular diversity than present ASICs with their gate granularity. Low level structures are fixed and a prelaid interconnection schema for routing signals and connecting blocks already exist, ready for circuit design or customization through the FPGA programmable capabilities. The resulting overhead suggests a need for circumventions and shortcuts using crafty approximations to achieve efficient utilization of the hardware. For an ABS controller, some of these include linearizing the tire-road friction versus slip dynamics about certain operating points and considering a simpler optimization problem. The vehicle velocity is assumed constant for short time intervals so that computations can complete their execution producing valid and current results. To further minimize the on-line computing time while maintaining precision, external (to the FPGA) hardware availability is assumed in the form of Read Only Memory (ROM). Quick to program, they can store large amounts of precalculated data, and competently complement the FPGA.

An additional goal of this thesis is to evaluate the applicability of FPGA technology in safety critical real-time applications. This study focuses on timing and fault/error detection in an FPGA environment. In the event of sudden braking and slippage under hazardous road conditions, the vehicle must respond quickly enough to regulate brake pressure to achieve optimal braking and steering. Should an error in operation occur, the ABS controller should be disabled to avoid incorrect braking interference and to guarantee safety of the driver.

Integrating all these elements through a case study, is an all-encompassing, difficult task. The specification and design of real-time systems not only requires extensive analysis, but also relies on modeling and simulation in order to develop the desired confidence in achieving system performance requirements before circuit realization. Even so, it is impossible to validate that the system performance requirements are achieved for all possible inputs given

the system resources. This applies to all of pre- and post-layout, and in-system renditions of the controller. Hence the need for intelligent designer controlled testing and validation are still necessary. Additionally, the shortcuts and design approximations which are required in the implementation phases must also be justified and accepted, a task which can be done through "special" simulations and mathematical analysis.

High level design languages provide a standard medium for communicating design data. VHDL was selected for design entry based on its ease of implementation, general acceptance and standardization, and its capability of allowing a designer to specify circuits at varying levels of abstraction. VHDL possesses traditional hierarchical level descriptions yet adds behavioral descriptions and user defined attributes. Though currently not the best for synthesis, as it was originally written for simulation purposes, VHDL is a good refinement of a hardware specification language which carries a potential for an efficient design entry method to evolving synthesis tools. Occasionally misleading in simulation, a clear understanding of the event-driven VHDL simulator will result in proper interpretation of results.

For vehicles with ABS, it is estimated that the quantity of some models will easily surpass 1000 units so that eventual migration to ASICs is feasible and thus considered in addition to FPGA implementation. The results of VHDL synthesis are judged on how well the timing requirements are met, testability, and the FPGA chip count required to implement the design, all of which affect the choice for possible migration to a smaller ASIC die.

### 1.2 Design Issues, Models, and Tools

Modeling a system's dynamics for eventual hardware implementation is analogous to writing a film script based on an existing novel. The director/designer must be able produce the best possible movie/design given the script/specifications and the actors/tools available. The actors/tools are interchangeable and replaceable while the script/specification provides the blueprints and fuels the strategy.

Circuit design embodies four main tasks: modeling, implementation encompassing both hardware and software elements, modification, and validation. Constraints are inherent to each task initially directing the synthesis process and ultimately to check correctness of the circuits realization. Modeling from initial specification consists of three elements: structur-

ing. encoding, and constraining. Structuring refers to the subdivision or organization of a design/application into smaller sub-blocks for design entry/definition. It also incorporates hierarchical organization, the number of levels of which depend on the original description. Encoding specifies how a design is entered into a Computer Design Aided(CAD) tool, for further processing such as simulation or synthesis. Constraining refers to the individual goals associated with each block or groups of blocks. Encoding and constraining depend on the choice of modeling language or library block representations and the implementation facilities whereby a subset of these elements, some general, some customized, are used.

An original description of a system for eventual modeling can come in several formats. Textual, pictorial, programming-oriented, mathematical, and petri-net or FSM type descriptions, to name a few, are common. The eventual modeling of the system described in this thesis was developed from textual descriptions and mathematical equations. The design platform for the realization of the above specification, focuses on VHDL descriptions and models as the avenue for design entry. The availability of hardware and software in the university environment rendered Xilinx XC4010 FGPAs as the chosen technology for circuit implementation, and Synopsys as the chosen tool for "automated circuit creation".

Accepting that there exist numerous paths from mathematical formulations to synthesis and eventual FPGA layout, we embarked on a search for mathematical formulas, or control dynamics which are better suited for FPGA implementation. Some useful approximations, optimizations, and implementation short-cuts have been unearthed through the construction of an ABS controller, and can be applicable to general controller applications.

In perspective, the focus of this dissertation rests on the exploration of VHDL design issues for FPGA synthesis of controller type applications using CAD tools. Constraint specifications, which are an integral constituent of any design tasks, can be used to direct synthesis and ultimately to check correctness of the circuits realization. Capabilities and limitations of the many facets in a design cycle, were sought to ultimately propose improvements in the areas of FPGA architecture, design entry, simulation, synthesis, and routing. These can then be formulated into a methodology for design and synthesis onto FPGA technology with particular emphasis on controller type applications, in attempt to parallel the functions of the traditional designer via automation. Producing a high performance and area efficient design meeting all constraints is an aspiration of designer and hence automation process

as well. Additionally, the analysis of testability procedures and their usefulness in FPGA implementations shall be performed.

### 1.3 Motivation and Research Goals

With the advent of programmable hardware, FPGA technology has since emerged. Avoiding costs and risks of traditional gate array design methodologies is one avenue towards which FPGAs can be directed. Exploration of the capabilities of such a hardware implementation is best performed through a design example, realized onto the technology, after which verification of timing and area can be done by the designer. The example chosen for realization, is that of an ABS Controller, which exhibits the desired application features, such as FSM control, synchronous and asynchronous functionality, datapath calculations, and embedded system circuit. Additionally, such an exercise will verify FPGA technology real-time capabilities in a safety critical control environment.

From a design entry and tool interpretation point of view, traditional schematic entry is less ambiguous than HDL encoding, as direct library-component matching during synthesis is possible and somewhat explicit. However, a fair amount of research remains to be done in order to resolve and produce an optimized and synthesized design with respect to VHDL and FPGAs, especially with commercial tools and the ever evolving FPGA architectures. Particularly, much work remains in exploiting technology specific FPGA architectures and pre-designed blocks (hard macros), and exploring synthesis, and design methodologies. Synthesis requires extensive design space exploration schemes and itself is an NP-hard problem. Creating an optimal implementation is, consequently, not a certainty and heuristics shall continuously be sought.

FPGAs are vendor and family specific possessing distinct architectures better adapted to certain design styles, or "niches". This thesis reports on one such niche by documenting the design process from specification to technology mapping.

Before embarking with background material, let us reiterate our goals:

• To explore VHDL design issues for FPGA synthesis of controller type applications using CAD tools. This embraces scrutiny of limitations and observance of features and

capabilities.

- To evaluate the suitability of CAD tools for such a design.

- To gauge the applicability of FPGA technology in safety critical real-time applications..

Likewise, our achievements can be summarized as follows:

- The development of a methodology for design and synthesis onto FPGA technology with particular emphasis on data-path/controller type applications. These applications revolve around processing externally received data in a controlled and ordered manner.

- Analysis of testability procedures, their feasibility and their usefulness in FPGA technology.

- List of limitations/capabilities of commercial synthesis tools.

- The implementation of a self-testing ABS controller onto FPGAs, based on recent four phase control loop theory and self-designed, complementary surrounding blocks and connecting logic.

- Realization of a controller onto programmable technology so that prototyping and in-system testing can be achieved with minimal cost.

- Presentation of an alternative solution to the traditional implementation of controller applications onto microprocessors and program memory (RAM:random accessible memory).

### 1.4 Author's Specific Contribution

The originality of this thesis stems not from an individual specific contribution but from an embodiment of diverse contributions fueling strategies and suggesting approaches and amelioration in future design and synthesis undertakings. Synthesis issues and algorithms from all levels -system level down to logic and boolean levels— were researched along with the numerous tools, both commercial and non-commercial. Considerable time was spent researching all available FPGA architectures, their construction blocks, special features and their synthesis tools, as well as implicit basics such as digital design techniques, programmable logic, synchronous and asynchronous systems, and Moore and Mealy machines. In addition, the extrinsic area of automotive mechanics and electronics was investigated to arrive at an implementable specification of an ABS Controller. A brief mention of all researched elements is included, and further details can be found from the extensive reference list located in the

bibliography. Subsequent to the research phase, the experimental phase ensued. The ABS Controller was specified and refined, succeeded by its encoding, simulation, synthesis, and eventual routing and layout. Results were then accumulated and interpreted, followed by the formulation of design methodologies and their documentation.

Briefly, the thesis is organized as follows: Chapter 2 presents background information and includes past work in the area of application specific synthesis. Chapter 3 introduces design and experimental methodologies and evaluation criteria. The Anti-lock Brake System (ABS) dynamics, the hardware specifications encompassing the self-testing features, are recited in Chapter 4, whereas implementation details, synthesis and layout results along with FPGA design strategies are located in Chapter 5. Ensuite, Chapter 6 summarizes and generalizes the approaches and methodologies used throughout the design and synthesis case study, with regard to VHDL controller design onto FPGA technology. Finally, concluding remarks are presented in Chapter 7. Additional ABS definitions, derivations and explanations are given in Appendix A, while sample VHDL code is available in Appendix B describing some interesting encoding styles for datapath/controller implementations. Lastly Appendix C touches briefly on synthesis needs, tools and supporting libraries and their structures as related to FPGAs, which is an important area of study encompassing entire new domains of research.

## Chapter 2

# Controller Implementation Fundamentals

The ideal synthesis tool will explore the largest design space and build an efficient design conforming to all user constraints. A comprehensive and complete design space exploration, or the study of various possible designs from a cost-performance trade-off perspective becomes more difficult at higher levels of design abstraction. Fixed hardware features useful for timely realizations may add proportionate limitations further complicating the synthesis process. Application-specific synthesis techniques or methodologies, provide inherent advantages, [48], and researchers have in the past investigated specific classes of circuits such as microprocessors, DSP Systems and control/datapath based methodologies. This thesis focuses on controller systems, yet many of the methodologies presented are applicable or can be extended to other application domains.

### 2.1 Theory behind the Controller Design and Implementation

Control system design characteristics, entry methods and implementation technology merit some introduction. For synthesis to be acceptable in tightly constrained systems, these three elements must be well understood by the designer and intelligently administered and processed by the tool, as will be seen in Chapters 5 and 6.

#### 2.1.1 System Dynamics Definitions

A system is a synergistic combination of components which perform a specific objective. A component is a single functioning, atomic, unit of this system. A dynamic system is one where the present output depends on the past input, and as a result, the output changes with time [1]. A real-time system is one where the present output depends on the past input, and as a result, the output changes quickly enough so as to effect correct responses in the surrounding system, within the specified time. Modeling time and translating events and durations in time to hardware are difficult problems to address in synthesis, yet happen to be essential in the calculations of several real-time controller systems. Hence, having tools that correctly model such behavior on the chosen technology is imperative.

System design begins with a prediction of its performance and behavior. Such prediction is based on a mathematical description of the system's dynamic characteristics, called a mathematical model. For physical systems, differential equations are used for these mathematical models. System dynamics deals with the mathematical modeling and response analysis of dynamic systems. Linear and non-linear systems are modeled by linear and non-linear differential equations respectively. Due to the mathematical difficulty involved with non-linear systems, they are often linearized about the operating point. Many hydraulic and pneumatic systems exhibit non-linear relationships amongst their variables.

### 2.1.2 Asynchronous vs Synchronous Design and their Synthesis

Sequential circuits are composed of gates, flip-flops and latches interconnected in some complex configuration. A synchronous circuit employs an independent, periodic clock signal to synchronize its internal changes of state, whereas an asynchronous circuit does not. Set, reset, and interrupt signals occurring sporadically characterize such asynchronous circuits. State changes occur in direct response to signal changes on primary input lines, and different memory elements can change state at different times. This can give rise to critical race conditions which must be avoided. Asynchronous circuits offer substantial benefits in the design of digital control units or sequencers, particularly when many of the actions of the control units are based on externally generated signals that are not guaranteed to be correlated to an available clock signal [41].

The development of asynchronous design techniques for synthesis are beneficial in control systems where input events occur haphazardly, and in interfacing components where handshaking occurs or the individual blocks are not synchronized to a common clock. Asynchronous methods are also exercised for module or system interfacing. Request-acknowledge (negative acknowledge) protocol of the four-cycle or two-cycle type communications requires asynchronous procedures and careful circuit realization. Starting from as early as [42] and [41], where a "one-hot" row assignment and one feedback variable restriction was suggested for circuit synthesis, asynchronous control unit implementations were being analyzed. Simulation of asynchronous systems using HDLs is commonplace, [34], however the research invested in its implementation has not yet reached commercial tool levels. Control applications in complex embedded systems, such as the ABS realization, would benefit from such a tool.

The approach to partition the specification and then employ different synthesis tools for algorithmic and interface parts [44] is feasible, but not the integrated solution sought after. It assumes clock availability, a synchronous design and focuses solely on handshaking, omitting sampling and response time issues which are vital for asynchronous designs. An ideal synthesis tool would permit modularization at a functional rather than at a timing level, so that a language such as VHDL could specify order and time of events with simple sequential and "if ... then ..." statements. However, as advances in asynchronous synthesis currently undergoing research are not yet readily available in commercial synthesis tools, designers are forced to either a manual approach or a synchronous approach<sup>1</sup>. If the timing issues can be solved with the switching speed of the technology, then clocks can be used and an asynchronous design can and is most often transformed into a synchronous design. Alternatively, a synthesis tool and particular designer encoding can result in asynchronous circuits. The Design Compiler  $^{TM}$  by Synopsys can process VIIDL which results in asynchronous type components, however, their realized behavior is not guaranteed to work as simulated. Certain elements are not allowed, and others are processed without guaranteeing correctness or immunity from hazards or race conditions. Designer discretion is advised and the automatic synthesis may not provide any advantage. Ultimately, more flexibility and

<sup>&</sup>lt;sup>1</sup>append a fast-enough clock to the circuit and synchronize the entire design, inputs, handshaking and actuator control signal generation to the clock

more refined synthesis are expected in newer tool versions, while it is still understood that manual synthesis options must remain.

#### 2.1.3 Control System Commonalities with Respect to Synthesis

Control systems can be divided into datapath and control logic blocks, the latter of which is often realized in the form of finite state machines (FSMs). FSMs prevail, due to the facility of depicting states of operation for tasks such as data processing or response generation and their transitions which effectually sequences the sub-tasks and applies order to them. FSMs comprise sequential elements for current (past) state storage and combinational logic for the determination of the next state. Datapath reflects the flow of data in a system under the management of control units such as sequencers or FSMs. Datapath infers a chain of operations which will be executed on one or several words of data of some pre-defined length. Again, both combinational and sequential logic are required for circuit materialization.

Typical control-type applications involve tasks such as sampling, data-processing, buffering, multiplexing, ordering and decision-making, and response generation. Functionality at the periphery is associated with analog circuits whereas data processing is often associated with digital circuits. Sampling often requires an analog-digital (A/D) interface, just as response generation will implicate digital-analog conversion. Data-processing leads to datapath/register-ALU-mux based hardware while decision making encompasses straightforward boolean type logic and combinational gate level logic. Typical datapath and control circuits are transformed into components such as: adders, subtracters, accumulators, counters, multiplexers, register files, FIFO buffers, three-state buffers, and busses.

Several facets exist within a digital control system; control laws (algorithms), hardware implementation, the conversion between analog and digital signal domains, the system performance, and the sampling process [2]. In continuous control systems, all system variables are continuous signals, regardless of whether the system is linear or not. The generation of a control model to be realized as a digital information processing device is of primary importance [2], and it is why much time was alloted to develop these models and why Chapter 4 is devoted to the specification of the example control system selected and employed.

Previously proposed techniques for synthesis of control systems involving FSM and dat-

apath structures [38], [44], [40] assume a similar succession of steps; the compilation of the input behavior into an intermediate graph representation<sup>2</sup> followed by synthesis tasks such as scheduling, unit selection, functional, storage and interconnection binding, and control generation. From an HDL starting point, such as VHDL, many lack specific guidelines in the use of timing constructs for synthesis, such as after and wait statements, since they have simulation semantics for scheduling future events or for suspending simulation execution. In synthesis these constructs have ambiguous semantics, without specific guidelines.

Control logic activates functional units, component blocks in a schematic and entity blocks in VHDL, in the datapath according to a given schedule. Synthesis of control logic is important because it affects the control flow of operations and hence directly impacts the overall performance of the resulting hardware [40]. Control logic can be implemented as microcode sequences (software solution) or finite state machines (hardware solution). With VHDL this would implicate explicitly encoding FSMs via process statements, as shown in Appendix B, or via wait statement sequences, Section 3.3.

Ψ,

Due to the common nature of control applications, their decomposition and subsequent realization leads to a communal set of logic and circuit elements. Typical datapath components such as adders, ALUs, registers, and interconnection units are used to realize operations such as +,-,\*,/,>,<,=,&,--, to retrieve and store their operands, and to connect them via multiplexors. FSMs, which control the multiplexers, registers, bus drivers, ALUs, etc., materialize themselves through registers and combinational logic. Figure 2.1 illustrates simple datapath components with a bus-mux interconnection system. Due to the inherent nature of the four phase control loop which dominates the ABS controller design, notably complex calculations were required in short times. It was determined that they could be best realized through look up tables (LUTs) implemented in a ROM. Hence a ROM is included in addition to RAM and registers as datapath memory elements.

Efficient VHDL synthesis elicits a proximate coupling of VHDL to these components, which in turn must evoke an adroit *mapping* between them and FPGA inherent structures. Further discussion of VHDL design issues appears in Chapter 3, Section 3.3.

<sup>&</sup>lt;sup>2</sup>often a dataflow graph (DFG) and a data structure, or control flow graph (CFG) for control flow

Figure 2.1: Typical datapath components and their interconnections

### 2.2 Automated and FPGA Specific Synthesis

The realm of synthesis embodies four main elements, the available hardware, a set of design styles or mechanisms, tools and designer. An FPGA architecture base can be multiplexor, gate, LUT, or PLA oriented. Design styles such as pipe-lined, data-path and FSM, random logic, or highly memory dependent, will have their corresponding components implemented with varying levels of efficiency on the uniquely structured FPGAs. Subsequently some FPGA types from different vendors or families better suit certain applications. Software tools link the designer to the hardware and attempt to perform automatic synthesis and map a supposedly generically entered design to the FPGA technology. Yet just as different design types will, and should, be diversely implemented on FPGAs, they also tend to adjust themselves to different design compilers and methods of encoding. Accommodation to the tools and hardware can be equated to manual synthesis, and results in customizations, which is often disadvantageous. By and large, there will always remain a certain amount of designer synthesis with its level dependent on the available tool suites and on the quality of final implementation specified by the design constraints.

In addition to the above, it is viewed that further classifications reside in the design and tool analysis; the front end, the design constraint specification capabilities, the synthesis algorithms and heuristics, the layout tools and their tool specific constraint inclusion capabilities, the available technology libraries for simulation and synthesis, and the testability features. While we capture the FPGA Design flow in Figure 2.2, a technology specific design flow shall be described in Chapter 3, Section 3.2. Certain simulation phases are optional

Figure 2.2: FPGA design flow chart for VHDL design and implementation

such as the block which appears after the synthesis step. Decision nodes are present in the design flow indicating that a step was performed and requires a positive confirmation before proceeding to the next step. Without confirmation re-conceptualization must be done. Two such tests are those for validation of correct functionality, and verification for correct timing and acceptable area. The remaining steps involve design partitioning and mapping to logic blocks, actual placement or selection of on chip blocks, and routing, collectively referred to as PPR(Partition, Place and Route). The layout version includes more accurate delay values permitting more precise validations of the implemented circuit. As soon as the layout version is acceptable, it can be transformed into a bit file specifically encoded for the technology chosen, and then downloaded onto the programmable gate array.

#### 2.2.1 Synthesis Fundamentals

A taxonomy for design automation, the Y-chart, introduced by Gajski [38] consists of three different domains: the behavioral domain, the structural domain, and the physical domain. Each domain embodies numerous levels from the transistor level to the system level description which manages items such as CPUs and memory elements. The ultimate goal of design automation is to automate the transformation of a specification given at the highest level of abstraction in the behavioral domain into a description at the lowest level in the physical domain [38]. Software systems which provide this transformation are called silicon compilers. Contingent to the level of design entry, a corresponding synthesis procedure will be employed. Our ultimate focus was on high-level synthesis where a behavioral description at the algorithmic level would serve as the starting point. In effect, encoding and implementation began with higher level specifications but terminated with the inclusion of register-transfer level synthesis where initial design descriptions were in terms of elements such as ALUs, registers, multiplexers, etc. VHDL, the choice for design entry is applicable to all these levels of description.

Synthesis embodies a diverse set of algorithms, many of which are NP hard. The purpose of utilizing high level methods of design entry are manifold: the reduction of design effort and design time, the creation of circuits which are correct the first time, correctness by construction, thus eliminating the need for time consuming engineering changes and redesign. Design specification and synthesis tools should be uniform so that VHDL sections which are behaviorally described, structurally written or asynchronously encoded can be compiled as a conglomerate with at most different algorithms being applied automatically to their synthesis. Aside from the type and level of the systems description, constraints on the design behavior weigh heavily in importance during the synthesis process. They serve to guide the synthesis algorithms toward feasible realizations in terms of performance, costs, testability, reliability, and other physical restrictions [38].

Controller VHDL synthesis issues and datapath synthesis algorithms are addressed in [44], [46], [38], [43], [40], and [48], to list a few. Interface behavior specification where synchronization and handshaking, and inter-process timing issues were addressed through "special" VHDL subsets, is discussed in [45] and [44] with a more thorough discussion of

synthesis algorithms found in [46]. Their first step generates a data flow graph (DFG) and a data structure for the control flow for a coherent intermediate representation on which to perform the design transformation to realization. Along similar lines, an algorithm for the allocation of functional units from RT component libraries for the abstract operations within a behavioral description is presented in [43]. The synthesis steps flow from HDL input parsed to a CDFG, to an RT Data Flow Graph, and finally to the RT structures and instantiations. Further mention of a variety of interface representations, and strategies for allocation of library components and scheduling of operations are given comprehensive narrations by Gajski, Michel, and DeMicheli, in [38], [39], and [40] where they cover an extensive range of synthesis algorithms. A common element with these algorithms is that they are well developed in theory, sometimes implemented, but their integration in commercial FPGA synthesis tools from a VIIDL entry point, is not readily advanced nor well-documented. To exemplify such a situation, Synopsys, a leading edge synthesis tool, cannot yet manipulate high level behavioral descriptions, cannot guarantee functional timing with behavioral encoded process statements, contains a strict VHDL subset and still requires RTL level descriptions including planned register inferences and explicit clock circuitry encoding. It does however contain an FSM Compiler<sup>TM</sup> to create highly optimized FSM structures and encodings, whereas no such design specific tool exists for datapath/control type circuit implementations.

In an FPGA environment, an automatic design tool, will similarly transcend levels of circuit representations during its synthesis algorithms, the number of which depends on the design entry format. Higher levels of input descriptions abstract the user from low level FPGA component considerations, and produce correct<sup>3</sup>, but not so efficient circuit realizations. Low level synthesis, which requires FPGA block structure knowledge, can process register transfer level blocks via algorithms in closer proximity to the hardware, and will produce more efficient FPGA realizations. Regardless of the front end, the final objective is to minimize the number of Logic Blocks (LBs) and I/O Blocks (IOBs) in the final circuit when either area or timing constraints, or both, are under regard.

Descending the FPGA synthesis ladder, ultimately yields a technology mapping endpoint where the design description, which has been reduced to logic level equation format, is mapped to the arrays of equal blocks and special feature elements. Specifically, boolean logic

<sup>&</sup>lt;sup>3</sup>as per vendor/designer measure and criteria, not as per verification

equations are transformed into programmed logic blocks. A number of such LUT technology mappers exist including: Chortle [26], mis-pga [27], [28], Asly, Hydra, Xmap, and VISMAP. All of these map a Boolean network into a circuit of K-input LUTs, attempting to minimize either the total number of LUTs or the number of levels of LUTs in the final circuit. Recent work by Murgai, [29], has included mention of FPGA mapping of sequential circuits. Two approaches are discussed: (i) mapping combinational logic and flip-flops together or (ii) mapping combinational logic and flip-flops separately. Ascending the synthesis ladder towards higher levels of design entry demands additional algorithms and better strategies at each level to produce a favorable FPGA implementation.

#### 2.2.2 Controller Synthesis Techniques

As a precedent, control systems have often been implemented on various computing engine based machines such as microcontrollers/microprocessors, transputers, and larger computing systems. Software was written, compiled and then executed and tested on the hardware. Algorithmic modifications inducing implementation alterations could be performed easily and repeatedly. The lack of speed and the difficulty with ensuring testability and reliability are two disadvantages which accompany this approach. Room for performance enhancements always exists, and correct operation was often assured through multiplicity of microprocessor and its associated RAM. ASIC implementation offers a hardware solution and increased execution speeds but lack in the ease of design alterations, improvements, and upgrades. FPGAs, on the other hand, present a favorable alternative in offering both the speed of hardware and the re-programmability of software. Much has been written about software approaches to controller applications [2], and many software packages exist to simulate controller type applications. Performance can be measured, operation can be tested in-system, but testability and reliability are difficult to build into a single processor. Our aim was to approach controller applications from a hardware viewpoint, analyze the feasibility of design refinement and performance attainment, and introduce a form of concurrent testability employing FPGAs as the hardware solution for circuit materialization.

Rao and Kurdahi [47] proposed a synthesis method which exploits inherent characteristics of a particular class of VLSI systems, to build efficient models or abstractions which simplify the synthesis process. *Modeling* or *abstracting* the problem domain is unlike alternative tech-

niques which concentrate on the development of complicated heuristics for decision making in the various synthesis stages. We suggest analogous modeling at the design entry stage, such that additional effort is spent with design specification and entry, and present a case study to support our proposals and exemplify the extraction of common features and design stages in the design process of a class of applications. We define class regularity extraction as the exception of templates to serve as library elements, synthesis and design flow steps, or aggregated design constructs for applications which exhibit particular uniformity and comparableness. This inherent regularity in description and in design methodology should be exploited in FPGA synthesis to furnish better implementations and reduce design time.

### 2.3 FPGAs: Technology of the Times

An engineering approach in research demands implementation in addition to pure research. One known implementation of and ABS controller was by BOSCII [9] where a microcontroller was used in conjunction with some RAM, supporting a datapath, and this precision of 10 bits of data. In our case, the technology of the times encumbers FPGAs, VHDL and commercially available synthesis and layout tools. Constant evolution of the tools must follow the architectural changes for them to remain useful. One of the intents of this thesis is to recommend some refinements to the tools. It is also accepted that at publishing date, many of the suggestions may already be implemented, never hardware structures will exist and new tool versions will be released.

FPGAs are changing the world of ASIC design by providing fast turnaround and negligible non-recurring engineering costs. But they suffer from lower logic density and speed compared to Masked Programmable Gate Arrays (MPGAs) because the programmable switches used for logic configuration and routing take up more space and produce higher resistances and capacitances than metal wires.

At present, FPGAs have emerged as the prevailing solution to the traditional timeto-market and risk problems in the electronics industry, because they provide immediate manufacturing and very low-cost prototypes. The final structure can be directly configured by the end user without the need for IC fabrication facilities. FPGAs combine the user programmability of a Programmable Logic Device (PLD) and the scalable and flexible interconnection structure of an MPGA. These attributes complement the design environment, by allowing on-site implementation and immediate testing in either a workbench test-jig or the destination embedded system. Synthesis tools can accommodate design changes for exploration of alternatives rather quickly so that altered circuits can be downloaded in minutes, and multiple implementations can be tested without any additional hardware costs.

Similar to ASICs, FPGAs can be used for some higher density circuit needs such as: random logic, glue logic, interface units, embedded controller systems of varying levels of granularity, small to medium sized computing machines, and for decoder or sequencer logic, to list a few.

#### 2.3.1 FPGA Classification and Architectures

An FPGA consists of an array of uncommitted elements that can be interconnected in a general way. Each vendor assumes a proprietary name for their two-dimensional array components, but they all possess similar features: they contain a programmable routing structure, they implement multi-level logic, and they are user-programmable, which characterizes them as FPGAs. Logic circuits are designed and realized onto FPGAs by partitioning the logic into individual *logic blocks* and then interconnecting the blocks through a network of switches and multiplexers. The structure and configuration mechanism of the *logic blocks* and the *interconnection resources* vary greatly amongst the individual modern day vendors of FPGAs.

#### FPGA Taxonomies

Four major architecture classifications exist for FPGAs. They are: (i) symmetrical array, (ii) row-based, (iii) hierarchical PLD, and (iv) sea-of-gates [21]. FPGAs can additionally be grouped according to their granularity and programmability. Commonly used structural classifications are: (i) minute-grained such as those with transistor-level programmability, (ii)(a) fine-grained: LUT based, (ii)(b) fine-grained: MUX based, (iii) coarse-grained: Logic Block Based (LUT AND MUX) with higher logic densities, and (iv) large-grained: PLD Based FPGAs. FPGA families of the above types can be found from respective commercial

vendors such as: (i) Crosspoint Solutions, (ii) Xilinx INc., Quick Logic, Actel Inc., Concurrent Logic, (iii)Xilinx Inc., and (iv) Altera.

Fine-grained FPGA architectures have a large number of small logic cells. Due to the higher density of these logic cells on one chip, larger routing channels are necessary to bandle a massive amount of inter-cell connections. Consequently, a higher percentage of the total area is consumed by routing lines than with a large-grained architecture. Large-grained FPGAs architectures have a smaller number of logic blocks and thus have a less dense and more manageable routing channels per chip. Consider the infamous design tradeoffs: for each advantage created, a disadvantage of some sort will result. The above architectures are not optimal since a fixed large grain structure cannot be fully utilized by the mapping software. The more strict/complicated a design, the less case for full utilization of the block, but the less need for routing resources and cluttering of interconnection resources.

#### Floorplans and routing interconnections

Numerous floorplan types exist for the layout of the logic blocks, the 1/O blocks, the extra features and the interconnection networks. Some specific features of some major FPGA manufacturers are shown in Figure 2.3. Both horizontal and vertical, as well as hierarchical routing facilities exist, and vary amongst vendors. Logic blocks can contain say simple 2-input NAND gates, some are complex, and contain multiplexer, LUT or PLA type structures, and most contain flip-flop elements to aid in the implementation of sequential design. The diversity amongst a collection of logic block configurations is illustrated in Figure 2.4. Repeated logic blocks of type (a), (c), (e), and (f) fit into the numerous floorplan varieties. Larger blocks of type (b) and (d) contain smaller blocks and are characterized by hierarchical routing networks such as those in figures 2.3(e) and (h). Located near the periphery and connecting to the routing network are I/O blocks. Varying their internal structures and contents, they can be analogously diverse amongst the numerous FPGA vendors. Their uniqueness arises from the individual bidirectional, register, slew rate, boundary scan, and tristate capabilities of the blocks. Additional details can be found in the corresponding FPGA data books.

The routing architecture of an FPGA, encompassing both the structure and content of

Figure 2.3: Floorplans and Interconnects: (a) Xilinx's Double-Length Lines, (b) Xilinx's Adjacent Single-Length Lines, (c) Actel's Generalized Floor Plan of ACT 3 Device, (d) Atmel's Cell-to-Cell and Bus-to-Bus Connections, (e) AT&T's Interquad Routing, (f) Motorola's MPA1036, (g) AT&T's Single PLC View of Inter-PLC R-Nodes and (h) Altera's FLEX 8000 Device Interconnect Resources

Figure 2.4: FPGA Logic block architectures: (a) Xilinx'x XC4000 Configurable Logic Block, (b) AT&T's Simplified FPU Diagram, (c) Actel's S-Module & C-Module Diagram (top), Motorola's Core cell (bottom) (d) Altera's Logic Array Block (LAB), (e) Altera's FLEX 8000 Logic Element (LE) and (f) Atmel's Cell Structure

the interconnection, incorporates both the wire segments and the programmable switches. Commercially available programmable switches currently in use fall into the following forms: (i) static RAM cells, (ii) anti-fuses, (iii) EPROM transistors, and (iv) EEPROM transistors. Each shares common property two-state configurability: on and off. In (i), programmable connections are made using pass-transistors, transmission gates, or multiplexors which are controlled by SRAM cells. These types of FPGAs must be configured on power-up and exhibit a volatile programming technology. As a consequence, some kind of permanent storage mechanism must exist in the system to charge up the RAM cells. Compared to other techniques, the chip area required by the SRAM approach is relatively large. On the other hand, here is an FPGA which can be re-configured in circuit very quickly. In (ii), the anti-fuse normally resides in a high-impedance state but can be fused into a low-impedance state when programmable and require larger current and voltage driving circuits to program them. Both (iii) and (iv) exhibit programmable capabilities with (iv) offering incircuit re-programmability.

#### Xilinx Architecture

Xilinx FPGAs, our chosen medium for implementation, also known as Logic Cell Arrays (LCAs), consist of an interior matrix of logic blocks and a surrounding ring of I/O interface blocks. Interconnect resources occupy the channels between the rows and columns of logic blocks and between the logic blocks and the I/O blocks. The core of the LCA device is a matrix of identical configurable logic blocks (CLBs). Each CLB contains programmable combinational logic and storage registers, permitting the implementation of both combinational logic and sequential logic. The combinational section of the block is capable of implementing any Boolean function of its input variables, explainable in terms of its LUT-filled structure. Three function generators, several multiplexors, two flip-flops with clock enable circuitry and asynchronous set/reset capabilities, and carry logic for fast arithmetic operations are all housed in the CLBs as can be seen in Figure 2.4(a). Interconnect network containing neighboring, short, and long (global) routing capabilities are illustrated in Figures 2.3(a) and (b). The functions of the LCA configurable logic blocks, and I/O blocks, and their interconnections are defined by a configuration program stored in a on-chip memory, which must be

loaded on power-up. LCA performance is determined by the logic speed, storage elements, and programmable interconnects. These three features are commonly used to characterize the individual FPGA types.