# COLLECTIVE ANALYSIS AND TRANSFORMATION OF LOOP CLUSTERS

by Russell Olsen

School of Computer Science McGill University, Montreal

May 1992

A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

## Abstract

Hardware alone is insufficient to allow high-performance computer systems to become successful; sophisticated compilers are also required. Compilers for systems of this type will achieve their effectiveness, not from any single optimizing transformation, but from advanced program analysis and selective application of many proven code-improving transformations. One such analysis technique which holds promise, especially for FORTRAN-90 applications, is a collective analysis technique developed by Sarkar and Gao which uses graph coloring to determine whether a cluster of loops can be processed in a pipelined manner [SG91]. The loop clusters we consider in this case are those consisting of loops which define arrays and successor loops which use them. When array elements which are generated in one loop are able to be referenced in the same order by successor loops, the loops are compatible for pipelined processing. On a multiprocessor, pipelined processing is accomplished by running the constituent loops on different processors; whereas on a uniprocessor, the loops are fused and intermediate arrays eliminated through a process of collective transformation, itself a process which often creates additional opportunities for code improvement.

In this document we describe enhancements to Sarkar and Gao's loop coloring technique which improve transformation effectiveness of optimizing compilers for uniprocessors; we also describe a minimum-cost partitioning heuristic to achieve efficient transformation in the event a loop cluster contains non-compatible loops. Based upon empirical evidence, we then show the benefit from loop transformation can be substantial, in certain instances resulting in four-fold speedup for certain types of codes. As part of our experiments, we use sample codes for both compatible and non-compatible loop clusters, run on each of three different types high-performance uniprocessors: a RISC workstation, a superscalar workstation, and a mainframe vector processor. Processor and cache simulations are then used to further substantiate our results. Overall, these experiments illustrate the advantages of using collective analysis and transformation within optimizing compilers for each type of machine.

## Résu lé

De nos jours, un support materiel efficace n'est pas suffisant pour assurer qu'un ordr nateur haute-performance ait du succès; l'utilisation de compilateurs sophistiques est aussi nécessaire. Les compilateurs pour ce type de machine dérivent leur efficacité, non pas d'une scule technique d'optimisation, mais bien de l'utilisation d'un ensem ble d'analyses et de transformations. Une approche prometteuse, particulièrement pour les applications écrites en FORTRAN-90, est l'*analyse collective* développee par Sarkar et Gao, approche qui utilise une technique de coloration de graphes dans le but de déterminer si un ensemble de boucles peut être traité à l'aide d'un pipeline [SG91] Les ensembles de boucles que nous allons étudier sont les boucles servant a definir des tableaux de même que celles utilisant les tableaux ainsi définis. Lorsque les elements d'un tableau produits par une boucle sont utilisés, par une autre boucle, dans le même ordre que celui où ils ont été produits, on dit alors que les deux boucles sont computibles vis-à-vis un traitement par pipelme. Dans une machine a plusieurs processeurs, un traitement par pipeline peut être réalisé en exécutant les diverses boucles sur des processeurs différents; par contre, sur une machine à un seul processeur les boucles peuvent être fusionnées et les tableaux intermédiaires peuvent être éliminés grace a un processus de transformation collective, lequel processus peut lui même créer de nouvelles possibilités d'optimisation du code.

Pans ce mémoire, nous décrivons certaines améhorations à la technique de coloration de graphes proposée par Sarkar et Gao dans le but d'améhorer son efficacité pour des machines à un seul processeur, nous décrivons aussi une heuriscique de décomposition à coût minimum dans le cas d'un ensemble de boucles non compatibles. A l'aide de résultats empiriques, nous montrons ensuite que les avantages d'une telle transformation peuvent être substantiels, conduisant, dans certains cas a des programmes quatre fois plus efficaces. Dans le cadre de nos expériences nous util isons des programmes contenant des boucles compatibles ainsi que des boucles non compatibles, chaque programme étant exécuté sur trois types de machines a haute

performance: une station de travail RISC, une station de travail super-scalaire et un processeur vectoriel. Des simulations de processeurs et de mémoires caches sont aussi utilisées pour confirmer nos résultats. De façon générale, ces diverses expériences illustrent les avantages d'utiliser les techniques d'analyse et de tranformation collective.

# Acknowledgements

Few people are able to successfully complete the research required for a Masters these without some type of support and commitment from family, advisors, and friends. I am certainly no exception for along the way there were many people who helped me and to whom I owe so much

First and foremost I gratefully acknowledge the enormous personal sacrifice and unflinching support of my wife Yoshiko. Only those who have actually been around her these past few years could possibly appreciate the countless ways she has improved my life. For cheerfully enduring our many daily hardships and challenge—she is truly deserving herself of honorary degrees, cum laude, in creative financing—survival hying, morale boosting, and motivational counseling. She has been my dearest and closest friend, not just during this past three years, but for all of our many splendid years together, and dearest closest friends I hope we always shall remain

Secondly, I express my deepest appreciation to Prof. Griang Gao. His enduring patience and constant support were major factors keeping me going throughout this arduous ordeal. Foremost he provided me with the incentive I needed to study high performance computer architectures by introducing each new subject in a comprehensible and intellectually stimulating way. through his numerous interesting seminars and many challenging computer architecture courses. CS505, CS605, and CS762. As a result of his careful guidance and continued support throughout these past three years I was gradually, but ultimately, able to acquire both the confidence and expertise required to become a computer science professional, having little or no exposure to this fascinating but complex subject prior to coming to McGill. Prof. Gao is an extraordinary scientist and scholar, a person of enormous ability, vast knowledge, and rare intuition, and he will always have my highest admiration and deepest respect.

I also feel a tremendous debt of gratitude to our very special friends who unhesitantly provided financial assistance to Yoshiko and me when we so desperately needed it Nancy Henry Tack and Nicole Lewis, and Malcom and Jean Short. Then unwavering trust and unbounded generosity will always be remembered and appreciated. Likewise I gratefully acknowledge Prof. Gao's financial support, as well as the financial support of NSERC and BNR.

Next I wish to gratefully acknowledge the contribution made by fellow classmates and members of the Advanced Computers and Program Structures (ACAPS) group at McGull Erik Altman Herbert Hum, Jean-Marc Monti, Chandrika Mukerji Qi Ning, Ravi Shanker Nematollaah Shiri, V.C. Sreedhar, Kevin Theobald. Guy Tremblay, Phillip Wong, and Bob Yates. Their association added immeasurably to the quality of my education, both with respect to my understanding of the subject matter and to my enjoyment in being here. Through their many helpful discussions and our many pleasant gatherings together we have forged friendships which I hope will continue for many years to come. In this same respect, I express sincere gratitude to Shiela Sundaram and Vigay Grey. Their constant encouragement and support throughout this experience was also much appreciated.

I also gratefully acknowledge the significant contributions made by Dr. Vivek Sarkar at IBM Palo. Alto Scientific Center and Radhika Thekkath at University of Washington, since the influence of their research is reflected throughout this document. Likewise, the assistance provided by Erik Altman and Chandrika Mukerp, with the instruction scheduler used during loop-transformation testing, was absolutely vital and deeply appreciated, especially during the hectic latter days of this research when both of these persons were so very busy with priority undertakings of their own.

Last, but cert, only not least, I would be remiss were I not to recognize the substantial contribution of my parents, my daughter Danna, Yoshiko's family, and our many other friends who in their own special individual ways provided the additional encouragement and support necessary to make our stay in Montreal the satisfying and enjoyable experience that it was. Through their correspondence, their telephone calls, and their visits we have grown to appreciate and cherish each of these priceless relationships even more.

# Contents

| A | DSLF                         | act                                           | 1    |  |  |

|---|------------------------------|-----------------------------------------------|------|--|--|

| R | ésun                         | ı <del>é</del>                                | iı   |  |  |

| A | ckno                         | wledgements                                   | iv   |  |  |

| 1 | Inti                         | roduction                                     | 1    |  |  |

|   | 1.1                          | Scope of Research                             | 2    |  |  |

|   | 1.2                          | Thesis                                        | 1    |  |  |

|   | 1.3                          | Overview                                      | 5    |  |  |

| 2 | Ana                          | 8                                             |      |  |  |

|   | 2 1                          | Preprocessing                                 | 9    |  |  |

|   | 2 2                          | Graphical Constructs                          | 11   |  |  |

|   | 2.3                          | Justification and Methodology                 | 16   |  |  |

|   | 2.4                          | Follow-On Transformations                     | 20   |  |  |

|   | 2.5                          | Analysis of Doubly-Nested Loops               | . 23 |  |  |

|   | 2.6                          | Analysis of $k$ -Nested Loops                 | 29   |  |  |

| 3 | Non-Compatible Loop Clusters |                                               |      |  |  |

|   | 3.1                          | Sources of Non-Compatibility                  |      |  |  |

|   |                              | 3.1.1 Properties of Non-Compatible Clusters . | \$ } |  |  |

|   |      | 3.1.2 The Partitioning Method and Refinements | 45  |

|---|------|-----------------------------------------------|-----|

|   | 3 2  | Analysis of Partitioning Effectiveness        | 51  |

| 4 | Rela | ated Research                                 | 58  |

|   | 1 1  | Loop Analysis and Transformation              | 58  |

|   |      | 4.1.1 Loop Compatibility Analysis             | 59  |

|   |      | 112 Buffer Allocation                         | 61  |

|   | 12   | Collective Loop Fusion                        | 63  |

|   |      | 4.2.1 Terminology and Methodology             | ยวั |

|   |      | 4.2.2 Algorithm Complexity                    | ĩ l |

|   |      | 423 A Case of Non-Optimal Partitioning        | 71  |

|   | 1.3  | Other Related Techniques                      | 71  |

| 5 | Rele | evant Code Transformations                    | 76  |

|   | 5.1  | In-Line Expansion                             | 77  |

|   | 5.2  | Normalization                                 | 77  |

|   |      | 5.2.1 Loop Normalization                      | 78  |

|   |      | 5 2 2 Subscript Normalization                 | 79  |

|   | 5.3  | Scalar Renaming                               | 81  |

|   | 5.4  | Direction Reversal                            | 82  |

|   | 5.5  | Loop Interchange                              | 83  |

|   | 5 6  | Node Splitting                                | 83  |

|   | 5.7  | Loop Fusion                                   | 84  |

|   | 5.8  | Array Contraction                             | 86  |

|   | 5,0  | Software Pipelining                           | 87  |

|   | 5 10 | Incidental Transformations                    | 91  |

|   |      | 5 10 1 Loop Untolling                         | 91  |

|   |      | 5 10 2 Instruction Scheduling                 | 93  |

| 6 | Exp                   | periments with Collective Transformation              | 101  |  |  |  |

|---|-----------------------|-------------------------------------------------------|------|--|--|--|

|   | 6.1                   | Umprocessor Experiments .                             | 101  |  |  |  |

|   |                       | 6 1.1 Tests with Compatible Loop Clusters             | 102  |  |  |  |

|   |                       | 6.1.2 Tests with a Non-Compatible Cluster of Loops    | 112  |  |  |  |

|   | 6.2                   | DLX Simulation .                                      | 118  |  |  |  |

|   |                       | 6.2.1 Tests with Compatible Loop Cluster              | 120  |  |  |  |

|   |                       | 6 2 2 Tests with a Non-Compatible Cluster of Loops    | 133  |  |  |  |

|   | 6.3                   | Summary Observations .                                | i 38 |  |  |  |

| 7 | Con                   | nclusions                                             | 142  |  |  |  |

|   | 7 1                   | Achievements                                          | 112  |  |  |  |

|   | 7 2                   | Topics for Further Research                           | 111  |  |  |  |

| A | San                   | iple Code Listings                                    | 145  |  |  |  |

| В | SPARC Architecture    |                                                       |      |  |  |  |

|   | B 1                   | 155                                                   |      |  |  |  |

|   | B 2                   | The SPARC f77 FORTRAN Compiler                        | 157  |  |  |  |

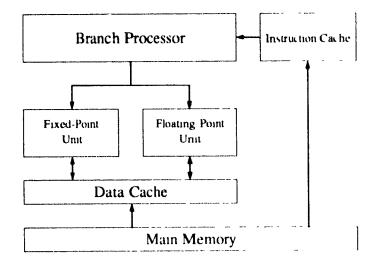

| C | IBM RISC System/6000  |                                                       |      |  |  |  |

|   | C 1                   | Base Architecture                                     | 160  |  |  |  |

|   | C.2                   | C.2 The xlf FOBTRAN Compiler                          |      |  |  |  |

| D | IBM 3090/VF           |                                                       |      |  |  |  |

|   | D.1 Base Architecture |                                                       |      |  |  |  |

|   | D.2                   | VS FORTRAN Compiler                                   | 171  |  |  |  |

|   |                       | D24 Automatic Vectorization .                         | 1,3  |  |  |  |

|   |                       | D 2.2 Additional Factors Affecting Vector Performance | 175  |  |  |  |

| E  | DLX Architecture |                      |   |  |  |   | 176 |     |

|----|------------------|----------------------|---|--|--|---|-----|-----|

|    | E 1              | Base Architecture    |   |  |  |   |     | 176 |

|    | E 2              | The dlxcc C Compiler | • |  |  | • |     | 178 |

| Bi | bliog            | graphy               |   |  |  |   |     | 180 |

# List of Tables

| 6.1  | Performance for a Compatible Loop Cluster                                                    | 106 |

|------|----------------------------------------------------------------------------------------------|-----|

| 6.2  | Speedup for a Compatible Loop Cluster .                                                      | 107 |

| 6.3  | Performance for a Non-Compatible Loop Cluster                                                | 115 |

| 6.4  | Speedup for a Non-Compatible Loop Cluster .                                                  | 116 |

| 6.5  | DLX Performance for a Compatible Loop Cluster, for Integer Arrays                            | 121 |

| 6.6  | Speedup for a Compatible Loop Cluster, using Integer Arrays                                  | 122 |

| 6.7  | DLX Performance for a Compatible Loop Cluster, for Single Precision<br>Floating-Point Arrays | 126 |

| 6.8  | Speedup for a Compatible Loop Cluster using Single-Precision Floating.  Point Arrays         | 127 |

| 6.9  | DLX Performance for a Compatible Loop Cluster, for Double Precision Floating-Point Arrays    | 129 |

| 6.10 | Dinero Cache Performance for a Compatible Loop Cluster                                       | 131 |

| 6.11 | DLX Performance for a Non-Compatible Loop Cluster                                            | 134 |

| 6.12 | Speedup due to Collective Loop Transformation for a Non-Compatible Loop Cluster              | 137 |

| 6.13 | Dinero Cache Performance for a Non-Compatible Loop Cluster                                   | 137 |

| B.1  | SPARC Register Names                                                                         | 150 |

# List of Figures

| 2.1 | Graphic Representation of a Collection of Loops       | 12 |

|-----|-------------------------------------------------------|----|

| 2.2 | An Interference Graph (IG)                            | 14 |

| 2.3 | An Interference Graph after Coloring                  | 20 |

| 2.4 | Loop Collection having Multiple Output Blocks         | 21 |

| 2.5 | A Collection of Typical Two-Dimensional FORTRAN Loops | 25 |

| 2.6 | Phase-1 Analysis of a Two-Dimensional Loop            | 26 |

| 2.7 | Phase-2 Analysis of a Two-Dimensional Loop            | 26 |

| 28  | Phase-3 Analysis of a Two-Dimensional Loop            | 27 |

| 3 1 | Two Non-Compatible Loops                              | 31 |

| 3.2 | A Cluster of Three Non-Compatible Loops               | 32 |

| 3.3 | A Non-Compatible Chain of Loops                       | 34 |

| 3.4 | A Partition of Three Non-Compatible Loops             | 36 |

| 3.5 | A More Complex Cluster of Non-Compatible Loops        | 37 |

| 3 6 | Another Case of Non-Compatible Loops                  | 39 |

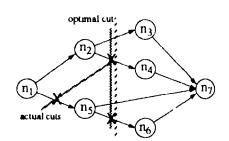

| 3.7 | Optimal Partitioning using Node Capacities            | 44 |

| 3.8 | Multiple-Cut Loop Partitioning                        | 49 |

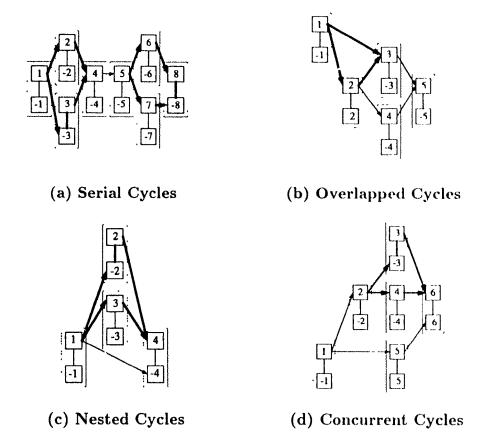

| 3.9 | Examples of Ways Cycles Combine                       | 54 |

| 4.1 | Buffer Allocation for an LCG                          | 61 |

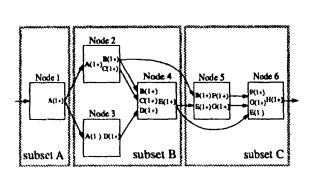

| 4.2 | Sample Collection of Non-Compatible FORTRAN Loops     | 64 |

| 13  | An Example of Cluster Partitioning                    | 66 |

| 4.4 | Another Collection of Non-Compatible FORTRAN Loops .     | 72  |

|-----|----------------------------------------------------------|-----|

| 4.5 | A Case of Non-Optimal Partitioning                       | 73  |

| 4.6 | Non-Optimal and Optimal Partitioning Solutions           | 71  |

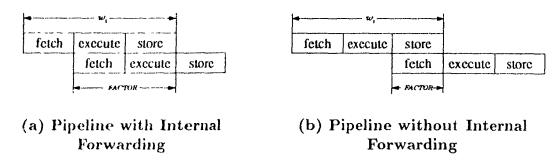

| 5.1 | Software Pipelining                                      | 88  |

| 5.2 | Software-Pipelining w/ Buffering                         | 90  |

| 5.3 | Determining Function-Unit Pipeline Latency               | 96  |

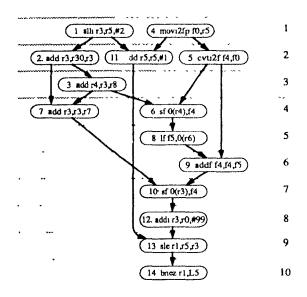

| 5.4 | Shieh-Papachristou Instruction Scheduling                | 98  |

| 5.5 | Shieh-Papachristou Instruction Scheduling Continued      | 99  |

| 6.1 | Transformations of a Compatible Loop Cluster             | 103 |

| 6.2 | Transformations of a Compatible Loop Cluster—Continued . | 101 |

| 6.3 | Transformations of a Non-Compatible Loop Cluster         | 113 |

| C.1 | The IBM RISC System/6000 Architecture                    | 161 |

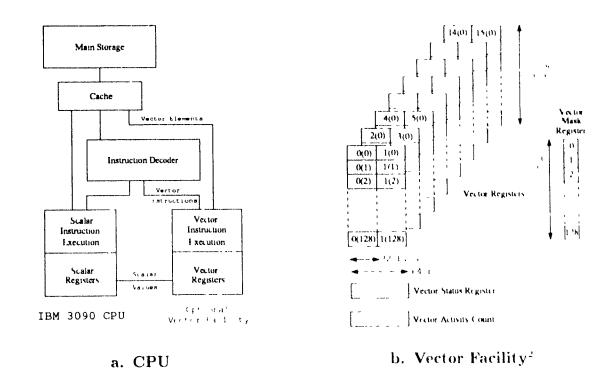

| D.1 | The IBM 3090 CPU and Optional Vector Facility            | 167 |

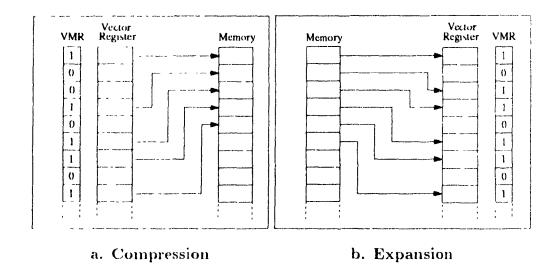

| D 2 | Vector Compression and Expansion                         | 170 |

# Chapter 1

## Introduction

In spite of their great speed, supercomputers today are still not fast enough to solve many of the problems users would like them to be able to solve. As a result, machines of ever increasing computing power are needed, and although more advanced computers are constantly being developed, the introduction of a new machine usually comes at a cost of increased complexity. The reason for this complexity is simple: either machines be made to operate faster or they be made to do more work concurrently. Although clock speeds have been increasing, the potential for further clock-speed increase is limited because of a physical constraint on the rate at which VLSI, and more recently ULSI, logic is able to operate. On the other hand, concurrent processing involves overheads, such as communication and synchronization, which quickly erode the performance benefit which might otherwise accrue from concurrent hardware, especially if the hardware is not effectively managed.

As a consequence, hardware alone is insufficient to allow high-performance computer systems to achieve their full potential; some form of software support is essential, and because of the complexity inherent in controlling program execution on parallel hardware, this software support will necessarily take the form of a highly sophisticated optimizing compiler. Compilers of this type will achieve their effectiveness, not from any single optimizing transformation, but from advanced program analysis and selective application of many proven code-improving transformations, likely requiring much closer programmer interaction than has been required of optimizing compilers in the past.

I.

## 1.1 Scope of Research

The subject of this thesis is a new loop analysis and transformation technique which brings compiler technology closer to meeting the needs of newer high performance computer architectures. In specific terms, the technique provides a way of analyzing loop clusters in which the lead loops define array elements and successor loops use these elements to define yet other arrays. Array computations of this type could easily comprise a large portion of any scientific computation, especially if the application were written in a language such as FORTRAN 90. Consequently, being able to process arrays of this type efficiently is of fundamental importance. When array elements which are generated in one loop are able to be referenced in the same order by successor loops, the loops are compatible for pipelined processing. On a multiprocessor, pipelined processing is accomplished by running the constituent loops on different processors, whereas on a uniprocessor, the loops are fused and intermediate arrays eliminated through a process of collective transformation, a process itself which often creates opportunities for additional code improvement.

By considering clusters as a collection, rather than individually, a compiler is able to identify opportunities for transformation which would not be apparent were the loops considered individually, as in traditional loop optimization. As we show in this document, the benefit from applying a global perspective to loop transformation can be substantial, especially in compiling programs, such as FORTRAN-90 programs, which allow statements in vector notation.

The particular loop analysis methods we evaluate are based upon techniques developed by Sarkar and Gao [SG91]. Gao first raised the issue of collective loop analysis in the context of an *intra-block pipelining* problem, his primary focus being the development of compiler techniques for static dataflow architectures. Later, Sarkar and Gao developed strategies for solving several common subclasses of the problem [Gao86, Gao90, SG91]. Most of these subclasses are reviewed throughout this document. In general, the strategy behind Sarkar and Gao's techniques is to use graph coloring to analyze the suitability of a collection of loops to undergo collective transformation. When a cluster of loops can be found which is compatible, the individual loops can be fused, allowing several follow-on transformations to be performed

The loop transformations employed in identifying and analyzing loop clusters are loop normalization, direction reversal, and loop interchange. Loop normalization transforms the loop-control portion of each loop so that all loops in the cluster have

uniform bounds, step, and direction. Loop reversal, which is often necessary for loop normalization, reverses the order of array element access within a loop body by reversing the indexing function of airay references. This transformation is necessary whenever the direction of a loop is changed. Loop interchange, on the other hand, changes the order of airay referencing by changing the order of nesting of perfectly nested loops. In later chapters, illustrations are given of each of these transformations.

Once a compatible loop cluster is identified, loop transformation is performed to improve program performance. Among the follow-on loop transformations which are used to accomplish this objective are loop fusion, array contraction, and software pipelining. Loop fusion is accomplished by merging statements from several loops, each having the same loop direction, into a single loop body. The effect is to reduce redundant loop control while increasing loop-body size. With a larger loop body, the need for loop unrolling and the effectiveness of instruction scheduling are also effected Without fusion, loop unrolling is often used to increase the number of independent instructions within a loop body, available for instruction scheduling Loop unrolling places statements from several loop iterations within a single iteration, increasing the loop step commensurately. Array contraction transforms array element references to equivalent scalar references. This transformation can only occur if an array element is both produced and consumed within the same loop body 1 Contraction has the effect of eliminating array indexing instructions as well as the associated long-latency loads and stores that accompany such references. At the same time, climination of these array references reduces storage requirements by eliminating the arrays themselves. The impact of array contraction can be substantial, as we will show. Software pipelining is an instruction scheduling technique which through an unrolling process finds a pattern of independent instructions across iterations, all of which can be simultaneously executed if the host machine has sufficient parallelism. Not only does this transformation increase the number of instructions which are concurrently executable, it distances long-latency dependencies which otherwise might stall the hardware execution pipeline. As with the preceding transformations, these transformations too are illustrated in subsequent chapters.

In cases in which loop compatibility does not exict, the constituent loops of a cluster can usually be partitioned into smaller compatible clusters, and follow-on transformations, such as loop fusion, applied to each smaller cluster. In doing so, much of the original benefit from loop fusion can still be achieved. Loop partitioning

<sup>&</sup>lt;sup>1</sup>Wolfe uses the term "array contraction" to refer to the technique for reducing the size of a compiler generated temporary array created as a result of scalar expansion [Wol89]

for loop fusion is the subject of recent research by Gao, Olsen, Sarkar, and Thekkath, and many of the ideas presented in the document derive from their research, although the specific algorithms we employ are slightly different in several instances [GOST92]

#### 1.2 Thesis

The proposition of this thesis is that it is both feasible and beneficial for an optimizing compiler to perform collective loop analysis. To prove this proposition, we first show how collective analysis can be efficiently performed on compatible loop clusters. Our primary focus in this regard is the application of loop analysis to programs written in traditional imperative programming languages, such as FORTRAN, in a uniprocessor setting in which the compiler optimization strategy is to fuse loops within each compatible loop cluster. Although the loop analysis technique we describe applies only to loops with certain restricted classes of array references, these classes include the most common cases that occur in practice, for example, the cases of single dimension and two-dimensional arrays. We also describe a minimum cost partitioning heuristic to achieve efficient fusion in the not so unlikely event the compiler encounters a non-compatible loop cluster. Although a difficult problem to solve, many common cases can be solved efficiently with optimal results, as we will show

Through a series of timing tests on various types of actual uniprocessors, we also show the extent of performance improvement possible from a transformed cluster of compatible loops. We assess the effect of efficient and naive partitioning on a non-compatible loop cluster. For these tests we use a scalar RISC workstation (A 3PARC Server 4/490), a superscalar workstation (An IBM RISC System 6000, Model 550), and a mainframe computer with an attached vector processing facility (An IBM 3090/VF). For each type of machine, loop transformation is shown to be of significant benefit. Moreover, this benefit is shown to be equally important in the case of non-compatible clusters. To further substantiate our results, we replicated our experiments on a scalar processor simulator and a cache simulator. These tests reveal yet additional insights into the effects of the individual transformations, while allowing us to isolate instruction-scheduling effects. Overall our tests confirm that collective loop analysis and transformation can be of substantial benefit in optimizing compilers for the three uniprocessor architectures that were used. Moreover, we produce evidence to suggest that the performance benefit from these transformations, especially array contraction, can be substantial, resulting in a four-fold speedup in

processor performance in certain instances.

#### 1.3 Overview

There are four main parts to this document. The first part describes the process of loop-cluster analysis, first in the case of compatible clusters and then in the case of non-compatible clusters. The second part describes related work on this subject, along with a list of topics for further research. The third part of the document describes essential transformations needed to perform collective loop analysis, along with several common follow-on transformations intended to improve processor performance. This part also describes a number of important related transformations which are used in the fourth part of the document as a basis for performance-test comparison. And, the fourth and final part then describes the results of timing and simulation experiments conducted to evaluate the performance of collective loop transformation. As an addendum to this document, we also include several appendices, the first contains sample code listings used during loop-transformation performance evaluation, and the remaining appendices each provide a brief description of one of the computer architectures and compilers used during the evaluation

Our discussion of loop analysis begins in Chapter 2. In this chapter we first outline the preconcitions under which collective loop analysis can be performed. We then describe a variant of Sarkar and Gao's graph-coloring technique which can be used to determine whether the constituent loops within a loop cluster are compatible for collective transformation. A description of the two principle graphical constructs used during this compatibility analysis is given, along with the basic intuition behind the technique. The two principle constructs we describe are 1) the Loop Communication Graph (LCG) and 2) the loop compatibility Interference Graph (IG). Justification for the loop analysis methodology is then provided along with a detailed description. An example of the analysis of a cluster of non-nested loops is then provided, along with a motivating description of several basic follow-on transformations that might be performed to increase loop-cluster performance. The chapter then continues with an example of another special case, one involving doubly-nested loops, and finally it concludes with a brief description of the strategy for handling clusters of loops which have an arbitrary, but uniform, level of nesting.

In Chapter 3 we examine the not unlikely case in which compatibility does not exist among the loops of a cluster. In this case, compatible subsets of loops must be

identified through a process of cluster partitioning. To motivate our discussion, we first investigate the nature of non-compatibility. Based upon our analysis of some simple situations in which non-compatibility exists, we identify factors which ultimately determine the optimality of cluster partitioning. We then apply our observations to several brief examples which allow us to gain vet a better understanding of the requisite conditions for optimal partitioning. Based upon these examples we derive an efficient heuristic to partition a non-compatible cluster of loops into smaller compatible clusters, using the *flow-augmenting path* algorithm from network flow theory. We then conclude this chapter with a complete description of our methodology and the rational behind it

Chapter 4 describes related research in the area of collective loop transformations. This work is especially important because much of the independent research reported in the previous two chapters derives in one way or another from the research reported here. We begin the chapter with a description of Sarkar and Gao's methodology for collective analysis, describing both its advantages and disadvantages. One important aspect of this particular research is its applicability to multiprocessor situations, a situation we ourselves do not directly address. Next we describe an alternative algorithm for cluster partitioning, called *collective loop fusion*. As part of our description we compare collective loop fusion with the partitioning technique described in Chapter 3. We then follow this description with a brief survey of related research in the area of loop transformation, and finally we list a number of suggested topics for further research.

Chapter 5 contains a discussion of related loop transformations which are essential 1) during the screening process to identify eligible loops, 2) during the analysis process to achieve loop normalization prior to analysis and pipeline compatibility following analysis, and 3) during performance testing, to provide a basis for determining loop transformation effectiveness. Among the transformations discussed in this first category are in-line expansion, normalization, scalar renaming, and node splitting. Transformations which fall into the second category are direction reversal, loop interchange, loop fusion, array contraction, and software pipelining. And, transformations which fall into the third category are instruction scheduling and loop unrolling.

The focus of Chapter 6 is on performance testing. The chapter itself is divided into two parts, the first part discusses timing tests, and the second part, simulation results. For each part we evaluate transformation performance based first upon a compatible loop cluster and then upon a non-compatible cluster. In the first instance we are primarily interested in performance improvement from the respective loop

transformations themselves, while in the second instance we are interested in the impact of alternative partitioning choices. In the second part of the chapter, we use processor and cache simulations to evaluate several factors which could not be easily isolated by timing tests alone, specifically, the impact of instruction scheduling and of cache. We conclude our chapter on performance tests by summarizing key findings, based upon our overall test results.

The final chapter. Chapter 7, is an attempt to tie everything together. In the first part of the chapter we summarize the most significant findings from our research, and the later part we list additional topics we feel might lead to important new results in this area.

As noted previously, we conclude this document with a number of appendices containing material specifically related to the performance testing described in Chapter 6. Appendix A contains sample listings of the code used for the actual timings, and Appendices B to D describe the various architectures and compilers used during both the timing tests and the processor/cache simulations.

# Chapter 2

# Analysis of Loop Clusters

Much of the computation involved in scientific programs occurs within loops which produce or consume large arrays. As a result, being able to handle loops efficiently is of fundamental importance. Much work has been accomplished within the past several years with regard to loop optimization, and many effective techniques have emerged [Ban88, KRP+81, PW86, Wol89, WL91]. These techniques usually focus on reordering statements either to avoid data and control dependences which can stall a hardware execution pipeline or to avoid long latency memory operations. A key point, however, is that since these techniques usually pertain to a single loop nest, their effect is necessarily local.

In this chapter a global analysis technique is described to find a compatible set of loops across a cluster of loops. By compatible we mean there exists a uniform sequence of array references which allows a cluster of loops to be processed in a software pipelined manner. A compatible order might be found from ascending and/or descending loop directions or, in certain circumstances, from the interchange of two levels of loop nesting. We refer the the process of finding a compatible set of loops as collective loop analysis. In general, collective analysis makes use of several common loop transformations, among which are loop normalization, direction reversal, and loop interchange. If loop analysis is successful, in other words, if a compatible set of loops can be found, several other common transformations to improve the loop cluster become possible, as we will show with a series of brief examples—the primary transformations being loop fusion and array contraction. Other code improving transformations, such as software pipelining, loop unrolling, and instruction scheduling, might also be used to further enhance the quality of the overall code, but in order

to focus on the analysis phase of loop processing, we leave description of these latter transformations, along with complete descriptions of the former, until Chapter 5.

Overall, this particular chapter is organized as follows. In the first section we describe relevant conditions, or preprocessing, necessary for collective loop analysis. We also describe the graphic constructs used during compatibility analysis, along with related terminology. We then explain the general rational behind compatibility analysis and describe the technique we use to accomplish this analysis, a technique which is similar, but not identical, to the one proposed by Sarkar and Gao [SG91]. In the section that follows, we give an example of the collective analysis of the common case of non-nested loops. We then cover analysis of doubly-nested loops, and finally, in the last section, we examine extensions of collective loop analysis that are appropriate for other special cases involving higher-level nested loops.

## 2.1 Preprocessing

Several conditions are necessary to qualify loops for analysis, and selection of loops satisfying these conditions forms an integral part of the collective analysis process. In selecting loops, the following restrictions apply:

- 1. The dimensionality of the arrays must be the same for all arrays referenced within the cluster of loops being analyzed.

- 2 The index variable of all loops must increase or decrease by the same constant amount. Usually this amount, called the loop increment, or step, is  $\pm 1$ .

- 3 The loops used to define the arrays must be perfectly nested, and the number of loops within each nest must equal the dimensionality of the arrays being referenced. For example, a code block which performs matrix multiplication on conformable square matrices is disallowed because the calculation of the inner product requires an additional loop, one more than the dimensionality of the participating arrays.

- 4. An index variable can only appear in one subscript position of an array reference. Therefore, references of the type A(I,I+J) (in which I and J are the respective induction variables for a nest of two loops) are disallowed. This condition, that subscripts be uncoupled, also ensures that each reference has the same number of subscripts as there are loops in the surrounding loop nest.

5. Although not essential, another assumption we make is that each array element be defined (that is, stored) only once. This condition, called the *single-assignment rule*, is a common characteristic of functional and applicative languages, such as Haskell and SISAL, and it is implicit in array statements used in FORTRAN 90.

The above criteria restrict the possible type of loops which might be included in a cluster to only those which can be feasibly transformed. These restrictions and other program characteristics make code conditioning essential. The following paragraphs describe some of the conditioning that should occur. First, function in liming should be performed on any function that makes reference to a globally defined array The purpose of in-lining is to collect together as many potential loops as possible This is important because structured programming results in code which uses lots of functions. In lining should be followed by data flow analysis. Intraprocedural flow analysis ensures that scalar variables that are referenced within the loop bodies are not redefined between their use in one loop and their reuse elsewhere in any follow on loop. What intraprocedural flow analysis implies, in this case, is that any code found between eligible loops can be moved out of the way without affecting program correct ness. The next step in collective analysis should be loop normalization. The purpose of normalization is to provide a uniform basis for loop comparison. Normalization consists of 1) setting the loop control within each loop to a range which extends from a lower bound of 1 to an upper bound of N, where N is the adjusted bound, and 2) setting the step to 1. Of course, any changes made to loop parameters also necessitate corresponding changes to index variables used within the respective loop bodies.<sup>1</sup>

Once normalization is completed, loop selection can be performed. Loop selection involves 1) array verification, 2) loop bounds checking, and 3) nesting level checking. Array verification ensures that only those loops which actually produce or consume a globally declared array are included in the cluster. While verification is occurring, subscript coupling could also be checked (Item 3 above). Bounds checking, on the other hand, ensures that the loop upper bound for each loop control statement is the same for all loops under consideration. Lastly, a nesting level check ensures that all loops under consideration have the same level of nesting. As a final phase of preprocessing, local flow analysis should be performed to identify data dependence within loop bodies, dependencies which constrain loop direction, thus preventing direction reversal.<sup>2</sup> Loops which posses data dependencies would then be tagged

<sup>&</sup>lt;sup>1</sup>Loop normalization is described in Chapter 5, Section 5.2.1 (see page 78)

<sup>&</sup>lt;sup>2</sup>Direction reversal is described in Chapter 5. Section 5.4 (see page 82)

as "constrained". Once data flow analysis is completed, the resulting loop cluster selected would be ready for loop compatibility analysis. Compatibility analysis, which is the primary topic of this chapter is described next.

## 2.2 Graphical Constructs

ŕ

To understand the compatibility analysis process, one first must understand the tools, or constructs, used during the process, the two most important constructs employ graphs. Graphs are often used to depict relationships among individual entities in a way which makes a global relationship clear. A case in point is graph coloring. The classic example is the coloring of, say, political regions on a territorial map. Coloring problems such as map coloring are solved using an interference graph. In the case of a map, the regions become nodes and adjacent regional boundaries become arcs. The objective in this case is to color the map interference graph so that no two adjacent nodes are the same color. In general, determining a minimum, or chromatic number, is difficult (an NP-complete problem [PS82]). However, in many situations, coloring heuristics have proven quite practical, as in the case of register allocation [CAC+81].

What Sarkar and Gao discovered is that the analysis of loop clusters can also be converted to a graph coloring problem since an analogous correspondence often exists with respect to the orders in which array elements are defined, or generated, within some loops and the order in which they are used, or consumed, in later loops. The objective of coloring in this particular instance is to find a set of compatible loops which produce and consume array elements in a compatible order which allows array values to flow through a cluster of loops in a manner similar to software pipelining.

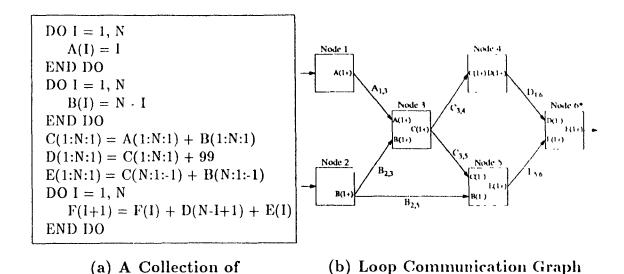

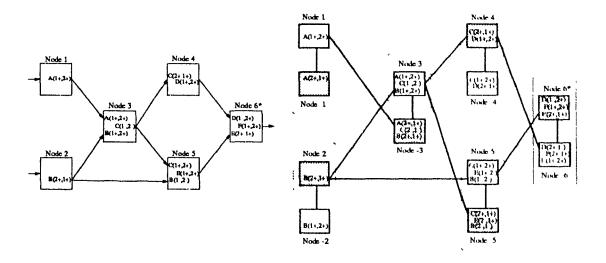

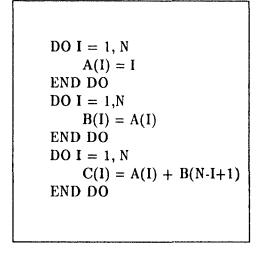

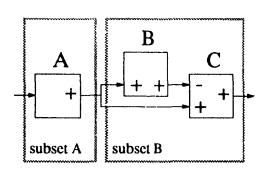

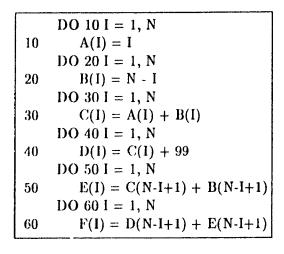

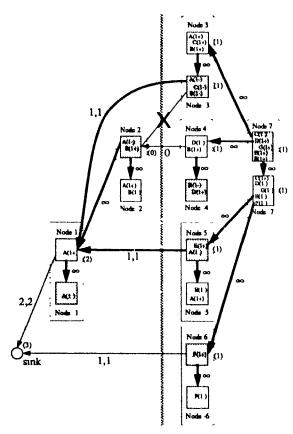

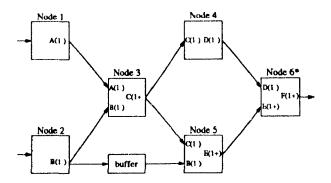

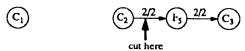

Collective loop analysis begins with the construction of a Loop Communication Graph (LCG). An LCG is a directed multigraph depicting the flow of array values between the code blocks that produce and consume arrays. The "flow" in this case represents flow dependence between assignments to array elements in one code block and the corresponding uses of these elements in follow-on blocks within the loop cluster. Formally, an  $LCG = [N, A \mid A \subseteq N \times N]$ , where  $n \in N$  is a node and  $1 \le n \le |V|$ . A node n in an LCG represents a code block comprised of perfectly nested loops [Wol89]. An arc  $X_{m,n} \in A$  represents the transfer of array elements from a producing code block to a consuming one. Graphically, this transfer is shown by connecting the origin of arc  $X_{m,n}$  to the output port of m corresponding to array X and the terminus of  $X_{m,n}$  to the respective input port of n. An example cluster of

FORTRAN-90 Loops

Figure 2.1: Graphic Representation of a Collection of Loops

(LCG)

loops and corresponding loop communication graph is shown in Figure 2.1 Nodes in an LCG are further specified by a tuple of Array Access Vectors

Each Array Access Vector (AV) is itself a vector of tuples in which the first element of the tuple indicates the correspondence between the subscripts used to access an array and the loops used to generate these subscripts; the second element indicates the direction of the corresponding loop. A direction element can be either positive (increasing) or negative (decreasing). A positive element is indicated by a plus (+), and a negative element, by a minus (-). An AV contains one loop-direction tuple for each subscript in an array. For example, A(2+,1-,3+) describes an array A which is referenced within a three-loop nest in which the outer loop causes the second subscript to decrease, the middle loop causes the first subscript to increase, and the inner loop causes the third subscript to increase. An AV  $n_x = \{(i, \{'+', -'\})^k \mid 1 \leq i \leq k\}\}$  is associated with each input and output port x incident to node n in the LCG, where n is is a loop identifier and k is the depth of loop nesting. When the AV  $n_x$  for an array X which is produced in code block m is paired with the AV  $n_x$  for an array of the same name which is consumed in another code block n the pair form the specification of the arc  $X_{m,n}$  in the LCG. (See Figure 2.1(b))

For certain code blocks the loop direction cannot be reversed because of a data dependence across iterations of the loop. Such a dependence is usually referred to as

a loop-carried dependence. In this case the corresponding node is called a constrained node. The node for the loop-carried dependence created by the assignment statement in the last code block in Figure 2.1 is an example. In an LCG, nodes which are marked with an asterisk refer to constrained nodes, as indicated for Node 6 in Figure (b).

Collective analysis applies to many different loop configurations, each representing a different array-reference sequence; but the methodology we describe considers only two mutually exclusive array-reference sequences at a time. For loops involving vectors (i.e., one-dimensional arrays), the sequence is either ascending or descending loop directions, and for doubly-nested loops that are uniformly ascending, or descending, alternative sequences are determined by interchanging two nested loops within the block, or equivalently, switching the sequence of indices within all access-order vectors of the corresponding block. The way this works is described fully later in the chapter. For now, however, we merely emphasize that only two array-reference orders, or sequences, are allowed at a time, for each block during each phase of loop compatibility analysis, either 1) alternative loop directions or 2) an interchange of two levels of loop nesting. The information about these alternatives is contained in the Interference Graph of the loop cluster used during the particular phase of analysis.

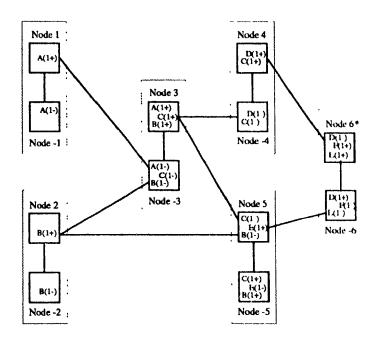

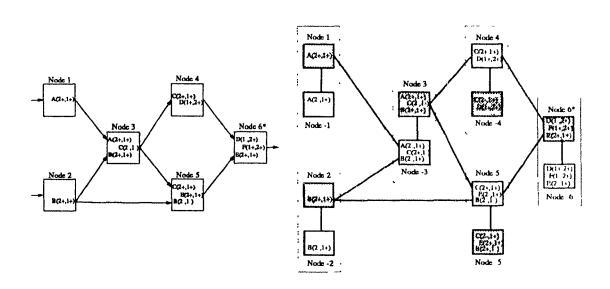

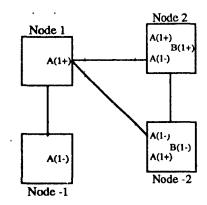

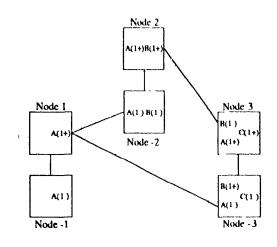

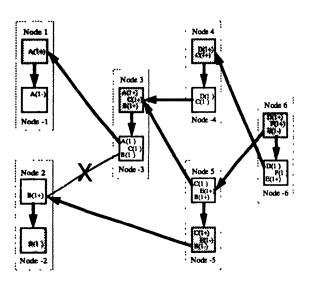

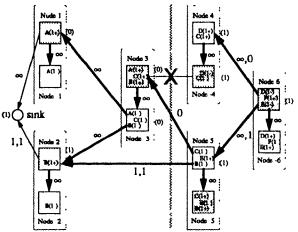

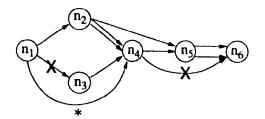

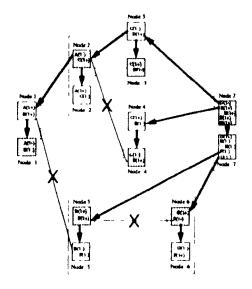

An Interference Graph (IG) is an undirected multigraph having nodes grouped according to blocks, each block being comprised of two nodes: a primary node,  $n^+$ , corresponding to a node in the LCG, with input and output ports matching the respective origins and terminuses of incident arcs to this node, and a compliment node,  $n^-$ , containing a copy of the primary node but with AV elements changed to reflect the alternative array-reference sequence allowed. When loop direction is used as the basis for analysis, the sign of the elements in the AVs are reversed; otherwise, when nesting level is used, corresponding elements in the the AV tuple are switched. For example, the first block, corresponding to Node 1 in the LCG, shown in Figure 2.1(a), consists of two nodes; a primary node  $n_1^+$ , labeled "Node 1" with AV A(1+), and directly below it, a compliment node  $n_1^-$ , labeled "Node -1" with AV A(1-). Formally, an  $IG = [[N, \overline{N}], E : E \in N \times N]$ , where  $[N, \overline{N}]$  is a block,  $n^+ \in N$  and  $n^- \in \overline{N}$  are nodes within a block, for  $1 \le n \le |N|$ . An undirected edge  $X_{m,n}=(m^+,n^\pm)\in E$ , called an interference edge, represents non-compatibility between the order of generation (definition) of array values in one code block and the order of their consumption (use) in another.

Obviously a code block cannot simultaneously process array elements in more than one order at a time. Therefore, to reflect the fact that alternative reference

Figure 2.2: An Interference Graph (IG)

orders represented by the primary and compliment nodes within a block are not simultaneously possible, we attach an interference edge between the two. Likewise, we attach an edge between the output port of a node in one block and input port of a node in another when the two ports reference the same array and the corresponding AVs in the two nodes differ. In this second situation, the edge indicates a situation we would prefer to avoid, since unless the AVs are the same, the array elements which pass between the two nodes, or code blocks, cannot be uniformly passed from one block to the other, as we would like.

Note that not all interference edges need to be attached, since the edges extending from the primary nodes to the nodes in follow-on code blocks provide sufficient interblock compatibility information, by themselves, to allow us to do our analysis. Attaching the corresponding arcs from the complement nodes to follow on blocks therefore becomes unnecessary. For example, notice that, in Figure 2.2, an edge has been attached between Nodes 1 and -3 to indicate non-compatibility in the array-reference orders for AVs A(1+) in Node 1 and A(1-) in Node -3, while no arc was attached between Nodes -1 and 3, even though the non-compatibility of the complement AVs, A(-) and A(+), respectively, is equally valid. The absence of "redundant"

edges from the complement nodes in each block not only reduces the number of linkages which must be made to the graph, but it also simplifies the ensuing analysis, as will become evident

#### Algorithm I Construct an Interference Graph (IG).

input:

An LCG = [N, A] in the form of a linked list; each node in the list corresponds to a code block. The nodes n are each specified by a set of input and output ports,  $n_x$ . Each port refers to an AV for some array X referenced within the block, along with list of connecting nodes m indicating from which node array X was produced or to which m it is being sent.

output:

An  $IG = [[N, \overline{N}], E]$  created from the LCG; each block in the LCG consists of two nodes: a primary node  $n^+$  containing the same input and output ports as corresponding node n in the LCG and a complement node  $n^-$  containing the same input and output ports, but with AV's  $n_x$ ,  $\forall x \in n$ , switched to indicate the alternative array-reference order (see Figure 2.2).

procedure:

Create a complement field in each node.

**FORALL**  $n \in N$  in the LCG

copy n to primary node  $n^+$  and to complement node  $n^-$

FORALL  $n_x \in n^-$

switch the direction of AV elements insert nodes  $n^+$  and  $n^-$  into the graph

Add interference edges.

**FORALL**  $n^+ \in N$

FORALL output ports  $n_x$

IF  $m_x$  for node m specifies the alternate vector attach a link to  $m^{\pm}$  creating  $X_{n+m\pm}$

**ELSE**

attach a link to  $m^{\mp}$ , creating  $X_{n+m\mp}$

## 2.3 Justification and Methodology

Were we to consider all possible array-reference orders possible from a cluster of loops, there would be  $(k! \cdot 2^k)^n$  such possibilities, where n is the total number of AVs used within the code blocks of the loop cluster and k is the level of nesting of these loops Obviously, analysis of so many alternative; at a time would be intractable for all but the simplest loop clusters. However, by restricting analysis to just two orders at a time, say, ascending and/or descending loop direction, problem size is significantly reduced. Moreover, by considering only two alternative orders at a time, we can easily represent any of the  $2^n$  remaining possibilities with a just single IG (again assuming n is the number of AVs). From construction of the IG, we know that neighbor nodes always reflect a complementary array-reference order, and for an overall compatible order to exist, it must consist of orders taken from alternating nodes. Consequently, the IG must be a bipartite graph if a compatible set of loop directions is to exist. Although the number of possibilities can still be very large, we know that there can now be at most two compatible orders for any cluster overall. This fact is what finally makes the problem tractable, since to determine whether a compatible loop ordering exists, we need only determine whether the particular IG under analysis is, in fact, a bipartite graph.

To take advantage of this bipartite property, we look to a few simple notions from graph theory [BM76, Deo74, Har69], and we begin under the premise, based upon our above observations, that an IG is bipartite if, and only if, an overall compatible set of array-reference orders exists. Accepting this fact, it is now easy to show that any bipartite graph is two-colorable (the proof by construction is trivial): Color elements of one partition one color and elements of the remaining partition a second color. Likewise, it follows immediately from the general definition of a spanning tree that the spanning tree induced by an IG represents a minimal connection of nodes within that IG. Therefore our next step to show that every nontrivial (spanning) tree (induced from an IG) is two-colorable.

#### Theorem 2.1 Every nontrivial tree is two-colorable.

proof: (by induction)

basis: Assume T is a tree with two nodes. If one of the nodes is colored with one color, the only remaining node can be colored with a second color

inductive step. Assume T contains n nodes that have already been successfully colored with two colors. If another node is added, regardless of its location, it can always be colored an opposite color to the color of the node to which it is attached.  $\Box$

Once a spanning tree is formed within the IG, we are assured of creating a simple cycle for each of the remaining original arcs added to tree. Fortunately determining whether the cycles formed in this way are themselves two-colorable is quite easy; we merely inspect the origin and terminus of each edge being added, and if the two have different colors, edge insertion can be safely accomplished, preserving the colorability of the graph. If edge insertion is successful for all remaining edges, we know the IG overall is two-colorable, thus confirming the fact that the IG is a bipartite graph and that a set of compatible loops exists. Now to find this order we need only select a set of nodes of the same color. This is because the way we constructed the graph assures us of a direct correspondence between compatible loop configurations and node coloring, that is, we know for a compatible cluster of loops, opposite nodes of every interference edge are both an opposite loop configuration and an opposite color.

The preceding analysis suggests how the determination of loop compatibility can be accomplished. The approach we describe is based upon creating a two-colored spanning tree during a breadth-first walk of the IG, commencing at the output block of a loop cluster. Our particular approach (which is slightly different from the one proposed by Sarkar and Gao) has a special property in that it identifies the least costly non-compatible interference edges to remove whenever no overall set of compatible array-reference orders exits, and it does so efficiently, as we will show in Chapter 3. The cost to which we refer is the cost of referencing elements of an array from memory, and the least-cost edges are those corresponding to arrays that are used by multiple blocks, not just one. The non-compatible edges, if any are found, ultimately form part of a cut-set used to fird compatible clusters of the original cluster which can ultimately be fused, allowing elimination of all arrays except the ones that cross a cluster boundary. We discuss cluster partitioning, in detail in the next chapter.

Again, the basic strategy behind compatibility analysis is to create a two-colored spanning tree during traversal of the IG. We proceed by first identifying and coloring the primary node of the output block of the IG. Then, starting with this node, we traverse the remaining nodes in the graph, in a breadth-first manner. At each node visited during our traversal we examine both the input ports and the port to the complement node within the same block, in each case inspecting the terminus of the interference edge. If the terminus is uncolored, we color it the opposite color of the current node. If, on the other hand, it has already been colored, but the color is

the same as the color of the current node, we note the fact that the cluster is non-compatible and store a reference to the non-compatible interference edge to be used during subsequent cluster-partitioning analysis. After all nodes have been reached, the algorithm stops. Nodes that are of the same color represent a compatible set of loops. Of course, this leaves a choice of the two colorings. One guideline regarding which color nodes to choose is to select nodes that correspond to the color of most of the "primary" nodes, since doing so involves the least follow on direction reversal (the direction-reversal transformation itself will be explained shortly). On the other hand, choosing a color might not be an option at all if the graph contains constrained nodes, since the color of any constrained nodes will uniquely determine the color set which must be used, that is, of course, assuming all constrained nodes are of the same color. Otherwise, if the constrained nodes are not all of the same color, the cluster will not be compatible overall. Our procedure for testing loop compatibility is summarized in the following recursive algorithm:

**Algorithm II** Determine a set of compatible array-reference orders for a cluster of loops, or verify that a compatible set of loops does not exist.

input: An  $IG = [[N, \overline{N}], E]$  in the form of a linked list; each node in the list is either a primary node  $n^+$  or a compliment node  $n^-$  (see Figure 2.2),

A colorset = {color<sub>1</sub>, color<sub>2</sub>}, and a color\_preference which determines the color of the set to be chosen in the event the loop cluster contains constrained nodes; initially color\_preference is undefined,

A checkset which initially contains the primary node of the output block of the cluster; we refer to this node as root, and root color - color,

A nextset =  $\emptyset$ , representing the next level of nodes to visit,

A set of noncompatibles  $= \emptyset$ , which contains any edges identified as having a non-compatible array-reference order with that of its neighbor node (later, we refer to these edges as X-edges), and

A Boolean return value, compatible, with an initial value of true

output: An IG with compatible nodes indicated by the primary color in the color set; however, if any nodes are constrained, the compatible nodes will be those with the same color as the color\_preference.

procedure:

```

FUNCTION colorTree (checkset): compatible

FORALL n \in \text{checkset}

FORALL input arcs X_{mn} and the arc to complement node \overline{n}

IF the terminus m is not colored

color m the opposite color of n

add m to nextset

ELSE IF m is the same color as n

add X_{mn} to noncompatibles

compatible = false

IF m is constrained

IF color_preference has not been set

set color_preference to the color of m

ELSE IF the color of m \neq \text{color\_preference}

add X_{mn} to noncompatibles

compatible = false

IF nextset \neq \emptyset

compatible = colorTree(nextset)

RETURN compatible

```

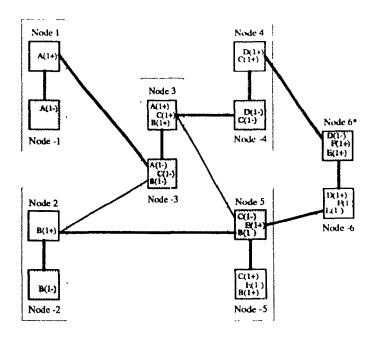

The graph in Figure 2.3 shows the IG in Figure 2.2 after it has been colored using Algorithm II. The dark edges define the spanning tree created during algorithm execution, and the shaded nodes indicate the set of compatible loops. Note that the constraint on Node 6 prevents the unshaded nodes from also forming a alternative set of compatible directions for the respective loops.

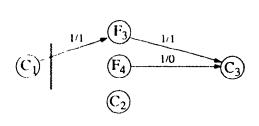

Algorithm II handles situations in which there is only a single output block in the LCG, but situations in which there are multiple output blocks often occur which require a slightly more complex solution, one involving the use of multiple color sets—or rather a different color set for each of the output blocks within the original cluster. In this case, a primary node from each output block is selected to begin the algorithm, and each root node is colored, as in Algorithm II—each with a color from its own respective color set. Then, as before, a depth-first walk is performed beginning from each root. If the LCG is connected (and we can assume that it is), there will come a point where a node is reached that has already been colored, but with a color from a

Figure 2.3: An Interference Graph after Coloring

different color set. When this occurs, the corresponding colors from each of the two sets are henceforth treated as though they were one. Then, should further traversal lead to some later convergence of the two color sets, at the point of terminus checking from some node, the decision whether to add the new edge, or not, will be based upon the initial color-set equivalence established when the color sets first converged. An illustration of the coloring of a loop cluster with two output code blocks is shown in Figure 2.4; the LCG is shown in Figure 2.4(a) and the corresponding IG after coloring is shown in Figure 2.4(b).

### 2.4 Follow-On Transformations

In the last section we described in general terms the collective analysis of the example cluster of loops given in Figure 2.1 (see page 12). To put this analysis into perspective, we now step through the basic actions taken once a compatible set of loop directions have been found. We begin our follow-on description with the coloring shown in Figure 2.2 (page 14). Notice that Node 6 is constrained because of a loop carried dependence of array F. As a result, there is only one set of compatible sequences from

#### (a) Loop Communication Graph

#### (b) Colored Interference Graph

Figure 2.4: Loop Collection having Multiple Output Blocks

which to choose, instead of two as would have been the case had the loop-carried dependence of F not existed. This set is the one indicated by the shaded nodes in the figure—the cluster consisting of Nodes -1, -2, -3, -4, 5, and 6.

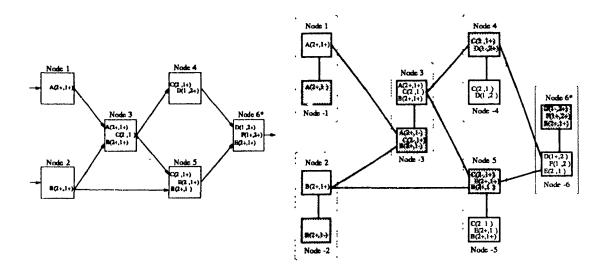

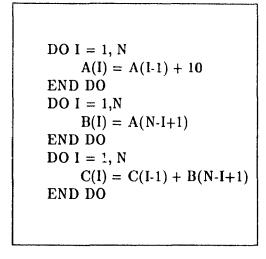

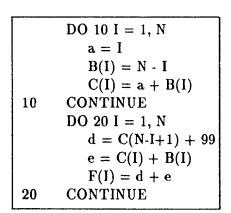

Once the set of compatible nodes have been selected, we apply direction reversal to the loops corresponding to the negative nodes in the set, i.e., the nodes having a negative node number. The basic notion behind direction reversal is merely to substitute N-I+1 for each occurrence of I in the loop body. In this case, applying direction reversal to the first four loops of the normalized code, shown in Figure 2.1, results the transformed code shown at the top of the next page, on the left-hand side. Since normalization ensures uniform loop control and since coloring analysis ensures loop compatibility, we know too that the loops in our example cluster can now be safely fused, as shown at the top of the next page, on the right-hand side.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Direction reversal is described in Chapter 5, Section 5.4 (page 82), and loop fusion is described in Section 5.7 (page 84)

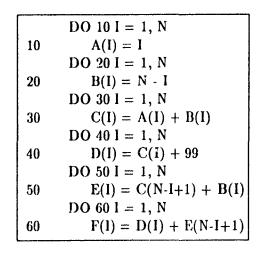

#### After Direction Reversal

# DO I = 1, N A(N-I+1) = N - I + 1 END DO DO I = 1, N B(N-I+1) = N - (N-I+1) END DO C(1:N:-1) = A(1:N:-1) + B(1:N:-1) D(1:N:-1) = C(1:N:-1) + 99 E(1:N:1) = C(N:1:-1) + B(N:1:-1) DO I = 1, N F(I+1) = F(I) + D(N-I+1) + E(I) END DO

#### After Loop Fusion

DO I = 1, N

$$A(N-l+1) = N-l+1$$

$B(N-l+1) = l-1$

$C(N-l+1) = A(N-l+1) + B(N-l+1)$

$D(N-l+1) = C(N-l+1) + 99$

$E(l) = C(N-l+1) + B(N-l+1)$

$F(l+1) = F(l) + D(N-l+1) + E(l)$

END DO

The final transformation, for now anyway, is array contraction, and the following code is the result of applying contraction to the previously transformed code:<sup>4</sup>

#### **Array Contraction**

DO I = 1, N

$$a = N - I + 1$$

$b = I - 1$

$c = a + b$

$d = c + 99$

$e = c + b$

$F(I+1) = F(I) + d + e$

END DO

Notice that array contraction replaced, by a scalar variable, all array references in which an element reference was first produced then later used. For example, A(N-I+1) is replaced by a, and so forth. Since all but the last array was produced then consumed in an element-by-element manner, the need for intermediate arrays, as in the original code, no longer exists. In later chapters we will show that yet additional transformation is not only possible, but, beneficial

The effect of collective transformations, such as these, can be dramatic, loop overhead and memory requirements can be reduced, and most array indexing operations can be eliminated. Moreover, a single larger code block results which facilitates in struction scheduling. In Chapter 5 we describe yet additional transformations which

<sup>&</sup>lt;sup>4</sup>Array contraction is described in Chapter 5, Section 5.8, (page 5.8)

might be performed or which can be affected by collective transformation, and in Chapter 6 we provide experimental evidence to show the extent of performance improvement attributable which is actually realizable on each of several different types of uniprocessor architecture

## 2.5 Analysis of Doubly-Nested Loops

So far we have only discussed the situation involving single-nested loops on onedimensional arrays since this situation is clearly the most intuitive and easiest to handle. The difficulty with multi-nested loops and multi-dimension arrays stems, of course, from the enormous increase in complexity which arises from the many permutations of the levels of loop nesting and loop direction. Whereas in the non-nested case AVs have only two possible orders, in doubly-nested cases there are  $2^2 \cdot 2! = 8$  possible sequences. In spite of this enormous increase in complexity, the basic methodology described in the previous section still applies—that is, with a few appropriate enhancements. Recall from the previous section, our strategy was to identify an alternative, or complementary, set of reference orders for each AV in the loop cluster, and then analyze each of the enumerated possibilities using the graph coloring technique described in Algorithm II. In this section we show how this same methodology can be applied to certain situations involving clusters of doubly-nested loops and two-dimensional arrays.

In the case of doubly-nested loops, the compiler faces essentially three possible possibilities: 1) the direction of all loops are the same across the entire cluster of loops, but the order of the array subscripts in each reference varies, 2) the order of the subscripts are the same across the entire cluster of loops, but the direction of the corresponding loops in the cluster varies, and 3) a combination of these two situations in which both the order of the subscripts and the direction of the loops vary across the cluster of loops.

**CASE 1** The direction of the loops are the same across the cluster of loops, but the order of the subscripts varies.

In this situation, AVs for the arrays referenced within the cluster are either of the form  $array\_name(1+,2+)$  or  $array\_name(2+,1+)$  or they are of the form  $array\_name(1-,2-)$  or  $array\_name(2-,1-)$ . In either situation, the direction of the loops are presumed to be compatible (so no direction transformation is required).

On the other hand, the order of the array subscripts creates the bipartite condition required for two-coloring the IG. In this instance we use Algorithm II, as before, but create the complementary nodes using AVs with a subscript order opposite to the subscript order of the AVs in the primary nodes. Also, instead of using loop reversal, as we did previously, we use loop interchange to align array access orders consistent with the results of the coloring analysis (Leop interchange is described more fully in Chapter 5, Section 5.5)

# **CASE 2** The order of the subscripts are the same across the cluster of loops, but the direction of the loops varies

The AVs in this case are either of the form  $array\_name(l\pm .2\pm)$  or the form  $array\_name(l\pm .2\pm)$ . To analyze these loops, we treat the problem as though it were two separate problems, analyzing the same AV element from each AV as though the referenced arrays were one-dimensional. For example, we might first analyze the directions of the outer loops of the code blocks in the cluster, and if a compatible direction is found, use the results of this analysis to analyze the directions of the inner loops (or visa versa). As in our original examples, the transformation technique used to bring the unaligned loops into alignment is loop reversal

#### **CASE 3** Both the order of the subscripts and the direction of the loops vary.

This last situation is a combination of Case 1 and Case 2. To analyze loop clusters of this type, we first attempt to color the transformed LCG based upon subscript or der, as described in Case 1, and if the coloring is successful, we continue by attempting to color the LCG based upon loop directions, as described in Case 2

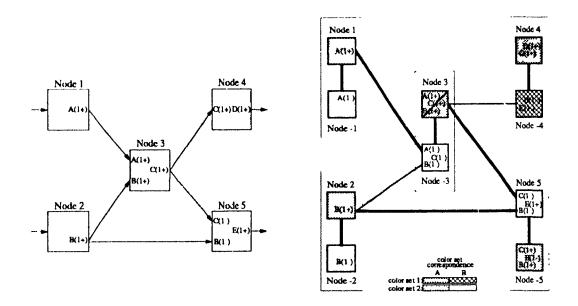

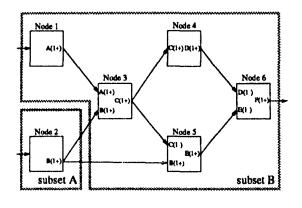

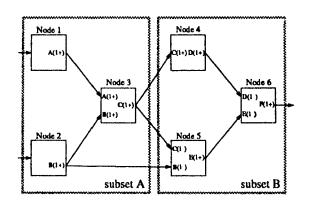

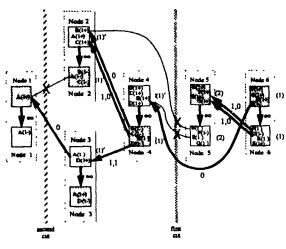

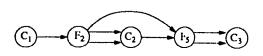

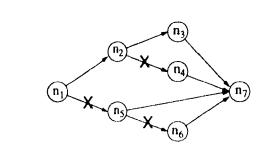

An example of the combined approach is shown in Figures 2.5.2.8. The cluster of doubly-nested loops used in this example are based upon the code segment shown in Figure 2.5. The corresponding LCG for this code is shown in Figure 2.6(a). The loop analyzer of the compiler uses this LCG during the first phase of its analysis to create the IG shown in Figure 2.6(b). Phase-1 analysis is merely the Case 1 analysis, described above. Notice that since the compiler's first attempt at transformation involves loop interchange, the complementary nodes in the Phase 1.1G are composed by copying the primary nodes, which were taken from the LCG, and reversing the of order of their AV elements (as opposed to changing the direction of these elements as was done in the case of non-nested loop clusters). The result of this analysis, a two coloring of the IG, is also reflected in Figure 2.6(b). Although the coloring produces

1

```

DO 10 I = 1, N

DO 10 J = 1, N

A(I,J) = I * J

10

DO 20 I = 1, N

DO 20 J = 1, N

20

B(J,I) = N - I

DO 30 I = 1, N

DO 30 J = 1, N

30

C(N-I+1,N-J+1) = A(I,J) + B(I,J)

DO 40 I = 1, N

DO 40 J = 1, N

D(I,J) = C(J,I) + 99

40

DO 50 I = 1, N

DO 50 J = 1, N

50

E(I,J) = C(I,J) + B(N-I+1,N-J+1)

DO 60 I = 1, N

DO 60 J = 1, N

60

F(I,J) = F(I-1,J) + D(N-I+1,J) + E(J,I)

```

Figure 2 5: A Collection of Typical Two-Dimensional FORTRAN Loops

two sets of nodes: those consisting of shaded boxes and those without, only the first is permissible because Node 6 is constrained by the loop-carried dependence which affects array F. Thus this set of shaded nodes forms the LCG used during the second phase of analysis. The LCG which depicts the results of Phase-1 analysis is shown in Figure 2.7(a).

Since Phase-1 analysis uncovered a compatible arrangement of nestings among the entire cluster, the compiler can proceed to the next phase of analysis. This second phase and the one that follows together form the Case-2 situation described above. During Phase-2 analysis, focus is on finding a compatible set of loop directions for each of the outside loops of the code blocks represented by the nodes of the transformed LCG. Therefore, the complementary nodes of the IG in this case are a copy of the primary nodes from Figure 2.7(a), with the direction of the first element of each AV reversed. The IG reflecting this set of alternative sequences and the resulting two-coloring is shown in Figure 2.7(b). Fortunately, Phase-2 analysis is successful too, so the compiler is able to proceed on to the third and final phase of analysis.

Phase 3 is just Phase 2 performed on the inside loop of each node in the cluster

- (a) LCG prior to Interchange

- (b) IG used for Case-1

Figure 2.6: Phase-1 Analysis of a Two-Dimensional Loop

- (a) LCG prior to Outer-Loop Reversal

- (b) IG used for First Case-2 Transformation

Figure 2.7: Phase-2 Analysis of a Two-Dimensional Loop

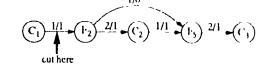

#### (a) LCG prior to Inner-Loop Reversal

#### (b) IG used for Second Case-2 Transformation

Figure 2.8: Phase-3 Analysis of a Two-Dimensional Loop

rather than on the outside node. Using the output from the previous phase, i.e., the LCG shown in Figure 2.8(a), the compiler creates the IG shown in Figure 2.8(b). This time the complementary nodes are created by reversing the direction of the last element of each AV of a corresponding primary node. Phase-3 analysis is also successful, leaving the nodes in the shaded boxes in the IG in Figure 2.8(b) as the final set of nodes from the overall loop pipelining transformation. Again in this last phase, as in the previous one, the transformation required to bring the cluster into alignment is loop reversal.

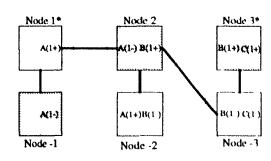

Now that a compatible set of array reference orders is known, it is a straight-forward process to fuse statements into a single code block and then eliminate the intermediate arrays by array contraction, as one done in the case of non-nested loops. To demonstrate this, we continue with the example, using the doubly-nested loops indicated by the shaded boxes in Figure 2.8(b). The retransformed code based upon the preceding analysis is shown at the top of the next page.

#### After Direction Reversal

When loop fusion is applied, the original loop cluster is transformed into the single doubly-nested loop shown below, to the left, and once this is done, all of the array references except the last (the reference to the output array F) are replaced by corresponding scalar variables, as shown on the right.

#### After Loop Fusion

#### After Array Contraction

DO I = 1, N

DO J = 1, N

$$A(J,N-I+1) = (N-I+1) * J$$

$B(J,N-I+1) = 1 - I$

$C(N-J+1,I) = A(J,N-I+1) + B(J,N-I+1)$

$D(N-I+1,J) = C(N-J+1,I) + 99$

$E(J,I) = C(N-J+1,I) + B(J,N-I+1)$

$E(I,J) = F(I-1,J) + D(N-I+1,J) + E(J,I)$

$E(I,J) = F(I-1,J) + D(N-I+1,J) + D(N-I+1,J) + D(N-I+1,J) + D(N-I+1,J)$

Note that in this case, the savings in storage and memory bandwidth is  $5 \cdot n^2$ , where n is the number of loops in the cluster. Again, in addition there are other advantages

derived from increasing code-block size, advantages cited earlier for the non-nested case (see Section 2.4).

### 2.6 Analysis of k-Nested Loops