**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the

text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the copy

submitted. Broken or indistinct print, colored or poor quality illustrations and

photographs, print bleedthrough, substandard margins, and improper alignment

can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and

there are missing pages, these will be noted. Also, if unauthorized copyright

material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning

the original, beginning at the upper left-hand comer and continuing from left to

right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white photographic

prints are available for any photographs or illustrations appearing in this copy for

an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

# Packaging of surface active optoelectronic device arrays

## David Kabal

Department of Electrical Engineering

McGill University

Montréal, Québec

Canada

October, 1997

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the degree of Master of Engineering

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre reference

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-44015-X

# **Abstract**

Requirements of electronic systems are increasing, as the applications for these systems become more complex and require more bandwidth. Optical interconnection can help satisfy these system requirements. In order for an optical interconnect to be successful, system design must satisfy new demands on the packaging of the optically interconnected devices, different from those encountered in packaging electronic interconnects.

This thesis addresses the issues faced in designing the packaging for a two-dimensional array of surface active optoelectronic devices, within the framework of a free-space optically interconnected backplane. Two demonstrator systems' packaging are presented, as well as a general discussion of the issues and constraints involved in the design, assembly and testing of this packaging. These issues include connectivity, bandwidth, thermal management, optomechanical interfacing and space constraints.

The particular optoelectronic devices examined are Quantum Confined Stark Effect (QCSE) modulators and detectors. The impact of temperature sensitivity on these particular devices is examined, and a technique for optimizing their performance at a specific temperature is presented. As a thermal diagnostic aid, as well as a thermal management tool, the design and characterization of an array of temperature sensors integrated into an optoelectronic device array is presented.

# Résumé

En raison de la croissance de leur complexité et de leur besoins en largeur de bande, les exigences des systèmes électroniques deviennent de plus en plus sévères. Les interconnexions optiques promettent de répondre à ces besoins. Afin de réaliser une interconnexion optique, la conception du système doit répondre aux nouvelles contraintes de packaging de dispositifs reliés par l'optique qui sont différentes de celles pour le packaging purement électronique.

Cette thèse aborde les défis à relever au cours de la conception de packaging pour des matrices deux dimensionnelles de composantes optoélectroniques à surface active dans le cadre d'un backplane interconnecté à optique libre. Le packaging pour deux systèmes de démonstration est présenté. Il en suit une discussion sur les considérations et contraintes associées à la conception, au montage et à la vérification de ce packaging. Les considérations comprennent la connectivité, largeur de bande, gestion thermique, interface optomécanique et contraintes de volume.

Les dispositifs optoélectroniques étudiés sont des détecteurs et modulateurs à effet quantique confiné Stark. L'effet sur la performance du système de la sensibilité aux changements de température de ces dispositifs est étudié. Une technique pour optimiser leur performance à une température donnée est aussi mise de l'avant. La conception et l'étude des caractéristiques d'une matrice de senseurs de température intégrée dans une matrice de dispositifs optoélectroniques pour fins de diagnostic thermique est présentée.

# Acknowledgements

I would like to thank the following people, without whom this research would not be possible;

Firstly, I would like to acknowledge Prof. David Plant, my supervisor. Without his invulnerable enthusiasm, invaluable guidance and irrefutably relentless search of funding this research could never have been realized.

Most of the packaging research for the Phase III demonstrator packaging system was conducted as part of a two-person team. Mike Ayliffe handled the optical issues of the packaging as I worked on the electrical, thermal and other aspects of the design. The inevitable area of overlap occured at the optomechanics, where the abstract design met reality. We are jointly reponsibly for this work, and our collaboration was essential to the realization of our designs. A more detailed description of the optomechanical and optical characterization of this work will be published in

due time. It is not simply for our collaboration that I must thank Mike Ayliffe, but also for the almost fantastic ease which changed a half-spoken idea into a deliverable part.

I would also like to thank David Rolston for designing the core and substance of both devices which this thesis talks about: the CMOS-QCSE Workshop Chip and the BiCMOS-QCSE Phase III chip. His advice, inspiration and friendship were invaluable to this thesis.

Mike Venditti is the gracious soul who put up with my relentless nagging and made sure I had all the data I needed on QCSE temperature dependence.

I also thank the following people for their experimentation, simulation, advice and inspiration: Pritha Khurana, Madeleine Mony, Prof. Frank Tooley, and Eric Bernier.

This research was partially funded by the Canadian Institute for Telecommunications Research (CITR) and NorTel.

# **Table of contents**

| 1 Introduction                                           |    |

|----------------------------------------------------------|----|

| 1.1 Motivation                                           |    |

| 1.1.1 Towards a photonic backplane                       |    |

| 1.1.2 Optoelectronic packaging                           |    |

| 1.1.3 Packaging of optoelectronics in optical backplanes |    |

| 1.2 Thesis organisation                                  |    |

| 1.3 Contributions                                        |    |

| 1.4 References                                           | 8  |

| 2 QCSE device packaging                                  | 10 |

| 2.1 Introduction                                         |    |

| 2.1.1 Optoelectronic devices                             | 12 |

| 2.1.2 Optical backplane                                  |    |

| 2.2 Electrical constraints                               |    |

| 2.3 Optical and optomechanical constraints               | 16 |

| 2.4 Thermal issues                                       |    |

| 2.4.3 Temperature optimization of device performance     | 17 |

| Introduction                                             | 17 |

| Optimization procedure                                   | 23 |

| 2.4.4 Thermal management                                 |    |

| 2.5 Manufacturing and reliability                        |    |

| 2.6 Conclusions                                          |    |

| 2.7 References                                           | 28 |

| 3 CMOS-QCSE packaging                                    | 31 |

| 3.1 Introduction                                         |    |

| 3.2 Chip-on-board packaging                              | 31 |

| 3.3 Conclusions                                          |    |

| 3.4 References                                           | 42 |

| 4 BiCMOS-QCSE packaging                                  | 43 |

| 4.1 Introduction                                         |    |

| 4.2 Optical interconnect                                 |    |

| 4.3 Optoelectronic device description                    |    |

| 4.4 Physical design constraints                          |    |

| 4.5 Electrical design constraints                        |    |

| 4.6 Thermal design constraints                           |    |

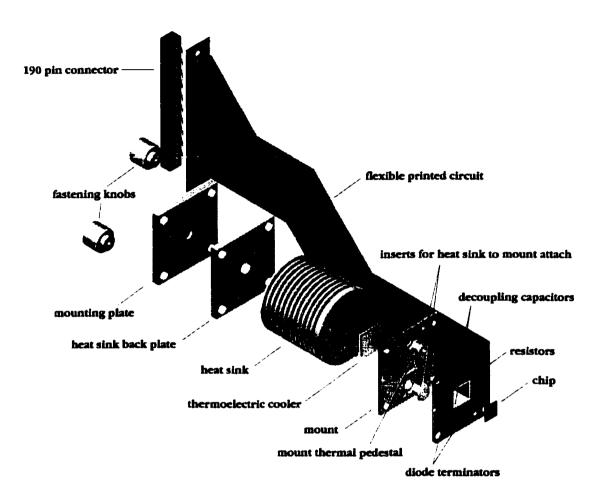

|     | 4.7 General package module description                    | 48 |

|-----|-----------------------------------------------------------|----|

|     | 4.7.1 Chip attach                                         |    |

|     | 4.7.2 Off-chip connectivity                               |    |

|     | Flexible printed circuit                                  |    |

|     | Termination                                               |    |

|     | Decoupling capacitors                                     | 59 |

|     | Thermistor chip                                           |    |

|     | Alignment features                                        |    |

|     | Optomechanical interfacing                                |    |

|     | 4.7.3 Thermal management                                  |    |

|     | 4.8 Characterization of packaging                         |    |

|     | 4.8.4 Thermal characterization                            |    |

|     | 4.8.5 Electrical characterization                         |    |

|     | 4.8.6 Thermal characterization                            |    |

|     | 4.9 Conclusions                                           |    |

|     | 4.10 References                                           |    |

| 5 T | 'emperature sensors                                       | 75 |

|     | 5.1 Introduction                                          |    |

|     | 5.2 Temperature sensor description                        |    |

|     | 5.2.1 Design                                              |    |

|     | 5.3 Experimental setup and temperature calibration        |    |

|     | 5.4 Conclusions                                           |    |

|     | 5.5 References                                            |    |

| 6 C | Conclusions and future work                               | 83 |

| -   | 6.1 Two dimensional optoelectronic device array packaging |    |

|     | 6.2 Future and ongoing work                               |    |

|     |                                                           |    |

# **Chapter 1: Introduction**

# 1.1 Motivation

Requirements of electronic systems are increasing, as the applications for these systems become more complex and require more bandwidth. Electronic systems are now being used in more ways than ever before, and a premium is now placed on the networks that must interconnect these systems. Telecommunications networks must service the bandwidth and connectivity requirements of these electronic systems, evolving to satisfy the increasing needs of a information driven society.

The new performance parameters have changed the purview of the system designer so that the connectivity and speed *between* discrete components and subsystems is becoming a critical area of research, in addition to the performance of these individual components and subsystems. The interconnectivity between these elements is provided by their packaging, and a general packaging hierarchy distinguishes the interconnection levels. The physical layer of a system is composed

of a hierarchy of connectivities: die to die, module to module, board to board and finally subsystem to subsystem. In addition to the interconnections, the physical packaging layer must implement the electrical support and the mechanical structure, including thermal management and the mechanical base upon which a system is built.

As the architectural requirements of the interconnection in a system are expanded, the physical size must remain the same in order to maintain several performance metrics, including speed, latency, reliability, and others. Preservation of compact size ensures new system requirements, as the interconnection density grows higher and more electronics are packed even denser, running at higher speeds and dissipating more power. These requirements will enforce constraints at the backplane level of interconnection (board-to-board) [1], where the highest interconnection density of a system is acheived. The current technological solution, the electronic backplane, is failing to keep pace with the increasing demands placed upon it by increasingly high performance parallel computing and switching systems.

For these reasons, it is apparent that data communication through a photonic interconnect layer can be advantageous, by increasing the overall speed and connectivity of a backplane [2, 3]. For long, medium and short haul telecommunications networks, the jump to photonic interconnects has already been made, and installed fiber optic networks are in use. This jump has yielded tremondous gains in the field of optoelectronic packaging, where the tight

integration of optoelectronic, electronic and optical elements is performed, yielding integrated, commercial packaging solutions that are reliable [1]. These packaging solutions are maturing for optoelectronic/fibre or optoelectronic/lightguide integration.

# 1.1.1 Towards a photonic backplane

At the backplane level, or very short distance communication, photonic interconnects are an emerging technology, and research is starting to demonstrate the potential of this technology towards commercial development. Although guided wave structures can provide nearly lossless transmission for large distances, their applicability to backplanes is limited. These applications are limited by the inherent constraint of fibre and cladding size, limiting the total number of interconnections, and because of their point-to-point nature.

For an optical backplane, another approach has great potential: optically interconnected two-dimensional arrays of optoelectronic devices. The impetus for this development is the potential for bandwith, and particularly, for the large number of channels that the volumetric interconnect that a Free-Space Optically Interconnected (FSOI) Backplane can provide. Current hybrid optoelectronic devices have demonstrated these large number of optical data links operating at high speed [4]. With the availability of devices capable of supporting a volumetric backplane, the effective integration of such devices into an operational interconnect becomes the challenge [5].

Development of the optoelectronic devices that could support a photonic interconnect fabric continues to produce more advanced devices supporting more optical and electrical inputs and outputs, and their speed continues to increase. Hybrid integration of two-dimensional arrays of Quantum Confined Stark Effect modulators and detectors onto CMOS circuitry is a reality, and reliable VCSEL and detector arrays integrated on CMOS circuitry is in progress, with promising applications forthcoming.

The last hurdle in this development cycle is the effective integration of such a device into a system. Such integration will require the successful satisfaction of three fundamental requirements: optomechanical interfacing to the photonic interconnection fabric, electronic interfacing to the photonic interconnect fabric, and optical interconnect design. This work will present one aspect of the interfacing, the electronic and to a smaller extent the optomechanical interfacing required for the construction of an optical backplane.

## 1.1.2 Optoelectronic packaging

Current electronic packaging has advanced to the point where large chips can be interconnected in a hybrid manner, where the delineation between board and chip-level integration and interconnection is blurred. In such a packaging system, chips may be wirebonded or connected using tape bonding to either a module (such as an Multi-Chip-Module), a board (using chip-on-board packaging) or a chip carrier (such as a Ball-Grid-Array, Flatpack, Leaded or Leadless Chip Carrier). The clear

hierarchy of packaging electronic devices has been broken by necessity, as the overhead of the hierarchy proved limiting to either bandwidth or connectivity.

Borrowing from the field of electronic packaging, optoelectronic packaging has advanced steadily [6]. In this field, a smaller subset of practitioners work on the specific problem of packaging two-dimensional arrays of surface-active devices, to interface them to free-space optical interconnects and switching fabrics. Successful examples of integration for two-dimensional device arrays are starting to make the conceptual benefits of free-space optical interconnect into real demonstrators. Starting with standard off-the-shelf electronic packaging used as a basis for optoelectronic packaging, the demands of faster, more dense interconnects have brought more advanced electronic packaging, and packaging unique to optoelectronics, to the field.

# 1.1.3 Packaging of optoelectronics in optical backplanes

This thesis deals with the constraints, challenges and design methodology for packaging two-dimensional arrays of optoelectronic devices. Although the demonstrators presented in this thesis use Quantum Confined Stark Effect (QCSE) modulators and detectors, the approaches used can be applied to emitter based optical interconnections, and many of the goals are shared between the available optoelectronic technologies. These shared goals include high optical and electrical connectivity, thermal stability, and good optomechanical interfacing techniques.

# 1.2 Thesis organisation

This thesis will start with a general statement of the considerations and issues that are vital to the problem of packaging a two-dimensional optoelectronic device array, and discuss the specific application of these issues to the devices under consideration, MOW diodes forming Quantum Confined Stark Effect (QCSE) modulators and P-I-N detectors. Along with the general solutions that have been applied and are currently being applied by researchers in this field, chapter 2 discusses a specific procedure for the optimization of temperature performance for QCSE modulators and detectors. Chapter 3 refines these techniques by application, using a specific demonstrator system to reveal the research and progress in this area. This system was completed in 1996. Chapter 4 is the discussion and application of even more restrictive constraints to a more advanced packaging system that has been completed in 1997. The system demonstrator that this packaging system is integrated into will not be complete until early 1998. Chapter 5 deals with the design and characterization of an array of temperature sensors integrated onto the optoelectronic device whose packaging is discussed in chapter 4. Chapter 6 summarizes the designs, constraints and approaches to the packaging systems for two-dimensional arrays of optoelectronic devices and discusses their applicability in the future.

# 1.3 Contributions

The system demonstrators in this thesis were realized by the combined efforts of a team, the Photonic Systems Group at McGill University. This section tries to quantify the relative contributions of the participants, as well as giving credit where it is due.

In the temperature optimization technique presented in section 2.4.3, the (representative) data presented is the exclusive work of Michael Venditti, who set up the power/photocurrent/voltage/temperature (PIVT) characterization system, developed the computer software necessary to do the scans the author required, and performed the measurements on the optoelectronic devices.

For the system demonstrator packaging presented in chapter 3, the design, assembly and testing of the electrical and thermal aspects, as well as optomechanical characterization, were performed by the author. This included printed circuit design, chip attach assembly, gold-plating of heat spreader, wirebonding, thermal characterization, assembly of package and connector selection. All boards used to test the bandwidth (i.e., connected to the daughterboard) and electrical connectivity were designed by the author with the help of Michael Venditti. The assembly and wirebonding rig was designed by the author, David Rolston and Guillaume Boisset. The mechanics of the three point attach and optical constraints were supplied by Guillaume Boisset. The optoelectronic device was designed by David Rolston.

For the system demonstrator packaging presented in chapter 4, the packaging "team" consisted of the author and Michael Ayliffe. Most of this work is through our

combined design, characterization and testing efforts. Exceptionally, the flexible printed circuit was designed by the author, as well as the printed circuit test board. Michael Ayliffe's future writing will concentrate on the optomechanical interfacing and characterization of the package module, a subject which is notably and unavoidably absent from this work. The assembly and testing of this package module to date were performed by the author, Pritha Khurana and Michael Ayliffe.

The design, layout, and testing for the temperature sensors were performed by the author and Michael Ayliffe.

# 1.4 References

- [1] Frank A.P. Tooley, "Challenges in Optically Interconnecting Electronics," *IEEE Journal of Selected Topics in Quantum Electronics*, April 1996, Vol. 2, No. 1, pp3–13

- [2] H. Scott Hinton, An Introduction to Photonic Switching Fabrics, Plenum Press, 1993

- [3] S. Yu and R. Forrest, "Implementations of smart pixels for optoelectronic processors and interconnection systems II: SEED-based technology and comparison with optoelectronic gates," *Journal of Lightwave Technology*, Vol. 11, XX, pp1670–1680

- [4] Anthony L. Lentine, Keith W. Goossen, J.A. Walker, Leo M.F. Chirovsky, L. Arthur D'Asaro, S.P. Hui, B. J. Tseng, R. E. Leibenguth, J.E. Cunningham, W. Y. Jan, Jen-

Ming Kuo, D. W. Dahringer, D. P. Kossives, D.D. Bacon, Gabriela Livescu, R. L. Morrison, Robert A. Novotny, and D.B. Buchholz, "High-Speed Optoelectronic VLSI Switching Chip with >4000 Optical I/O Based on Flip\_Chip Bonding of MQW Modulators and Detectors to Silicon CMOS," *IEEE Journal of Selected Topics in Quantum Electronics*, April 1996, Vol. 2, No. 1, pp77–83

- [5] David V. Plant, "Constructing a Free-Space Optical Backplane: Challenges and Choices," Technical Digest of *Optics in Computing*, 1997, Vol. 8, pp156–158

- [6] Alan R. Mickelson, Nagesh R. Basavanhally and Yung-Cheng Lee, editors, *Optoelectronic packaging*, John Wiley and Sons, Inc., 1997

# Chapter 2: QCSE device packaging

#### 2.1 Introduction

Providing an integrated packaging solution for a two-dimensional array of surface-active optical devices presents a series of constraints that complicate the employment of standard electronic packaging in systems applications. Through the construction of demonstrator systems, the Photonic Systems Group at McGill University (PSG McGill) has designed, fabricated, and implemented array packaging which uniquely addresses the critical issues associated with successfully integrating two-dimensional optoelectronic device arrays into systems. These system design considerations are: electrical bandwidth, electrical connectivity, thermal management, and optomechanical interfacing.

An overview of the packaging techniques that have been applied to system demonstrators by PSG McGill is presented in Table 2.1. In this chapter, an overview of the constraints inherent to this type of system are presented. In subsequent,

Chapter 2: QCSE device packaging

**Table 2.1: PSG McGill Packaging**

| Year | Optoelectronic<br>device<br>technology | Chip I/O                                                                              |                                                                                                                                                                                                                                  | Aggregate                                                                                                                                                                                                                                                                                    | TE                                                                                                                                                                                                                                                                                                                                                                                         | Thermal                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                        | Electrical                                                                            | Optical                                                                                                                                                                                                                          | optical BW                                                                                                                                                                                                                                                                                   | Cooler                                                                                                                                                                                                                                                                                                                                                                                     | $\theta_{jc}$                                                                                                                                                                                                                                                                                                                                                                                                                              | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1994 | FET-QCSE                               | 40                                                                                    | 32                                                                                                                                                                                                                               | 2.5 GB/s                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 30 °C/W                                                                                                                                                                                                                                                                                                                                                                                                                                    | ~0.5 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1995 | VCSEL/MSM                              | 68                                                                                    | 32                                                                                                                                                                                                                               | 300 MB/s                                                                                                                                                                                                                                                                                     | ·                                                                                                                                                                                                                                                                                                                                                                                          | 55 °C/W                                                                                                                                                                                                                                                                                                                                                                                                                                    | ~0.8 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1995 | CMOS-QCSE                              | 22                                                                                    | 16                                                                                                                                                                                                                               | 8 MB/s                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                            | ~50 °C/W                                                                                                                                                                                                                                                                                                                                                                                                                                   | ~0.15 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1996 | CMOS-QCSE                              | 44                                                                                    | 64                                                                                                                                                                                                                               | 16 MB/s                                                                                                                                                                                                                                                                                      | ~                                                                                                                                                                                                                                                                                                                                                                                          | 7 °C/W                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.5 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1997 | BiCMOS-QCSE                            | 189                                                                                   | 1024                                                                                                                                                                                                                             | 81.9 GB/s                                                                                                                                                                                                                                                                                    | ~                                                                                                                                                                                                                                                                                                                                                                                          | ~3 °C/W                                                                                                                                                                                                                                                                                                                                                                                                                                    | ~5 W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 1994<br>1995<br>1995<br>1996           | Year device technology  1994 FET-QCSE  1995 VCSEL/MSM  1995 CMOS-QCSE  1996 CMOS-QCSE | Year         device technology         Electrical           1994         FET-QCSE         40           1995         VCSEL/MSM         68           1995         CMOS-QCSE         22           1996         CMOS-QCSE         44 | Year         device technology         Electrical         Optical           1994         FET-QCSE         40         32           1995         VCSEL/MSM         68         32           1995         CMOS-QCSE         22         16           1996         CMOS-QCSE         44         64 | Year         device technology         Electrical         Optical         Aggregate optical BW           1994         FET-QCSE         40         32         2.5 GB/s           1995         VCSEL/MSM         68         32         300 MB/s           1995         CMOS-QCSE         22         16         8 MB/s           1996         CMOS-QCSE         44         64         16 MB/s | Year         device technology         Electrical         Optical         Aggregate optical BW         TE Cooler           1994         FET-QCSE         40         32         2.5 GB/s           1995         VCSEL/MSM         68         32         300 MB/s         ✓           1995         CMOS-QCSE         22         16         8 MB/s         ✓           1996         CMOS-QCSE         44         64         16 MB/s         ✓ | Year         device technology         Electrical         Optical         Aggregate optical BW         TE Cooler         resistance θ <sub>jc</sub> 1994         FET-QCSE         40         32         2.5 GB/s         30 °C/W           1995         VCSEL/MSM         68         32         300 MB/s         ✓         55 °C/W           1995         CMOS-QCSE         22         16         8 MB/s         ~50 °C/W           1996         CMOS-QCSE         44         64         16 MB/s         ✓         7 °C/W |

chapters, this overview is refined by a discussion of the packaging techniques that were used in two separate systems (in table 2.1, COB II and III) that were implemented by the Photonic Systems Group. This packaging was designed, modelled, fabricated and demonstrated for board-to-board and backplane optical interconnect applications.

# 2.1.1 Optoelectronic devices

When an optical communication system uses Quantum Confined Stark Effect (QCSE) modulators in reflection mode for transmitting and QCSE detectors for receiving light signals, a unique set of design constraints are imposed on the packaging for that system. In such a system, optical power supply (light) sources are incident on the surface active array. The surface active array introduces a modulation on the power supply beams by altering the absorption of light in the QCSE modulator via an electrical signal applied by transmitter circuitry. This reflected optical signal is directed onto the subsequent array of detectors, which are P-I-N (*P*-doped region, *I*ntrinsic region, *N*-doped region) diodes. The detector translates the received optical signal into a photocurrent, which is amplified and thresholded back to digital (voltage) logic levels by receiver circuitry.

In both of the systems whose packaging is presented in the following chapters, dual rail optical signals were used to represent a single bit of data. With a representative reflectivity difference between high and low states of less than 50% [5], it is desirable to send complementary data, so that the *difference* between two reflected signals can be thresholded by receiver logic. Thus, for these systems, two power

supply beams are reflected by two modulators coupled by their driver logic to produce complementary outputs, and the resulting two optical signals are incident on two detectors where the difference between the resulting photocurrents can be turned into a digital logic level. This arrangement is shown in figure 2.1.

Optical power supply inputs

electrical input transmitter circuit

output

receiver circuit

detectors

Figure 2.1: Dual rail optical interconnect

modulators

# 2.1.2 Optical backplane

For an optical interconnect, an array of these QCSE devices can be hybridly integrated onto the surface of a standard CMOS or BiCMOS chip, using a flip-chipping technique that connects the Silicon substrate of the CMOS or BiCMOS device to the Gallium Arsenide substrate of the QCSE devices, at specific bump-bonding points.

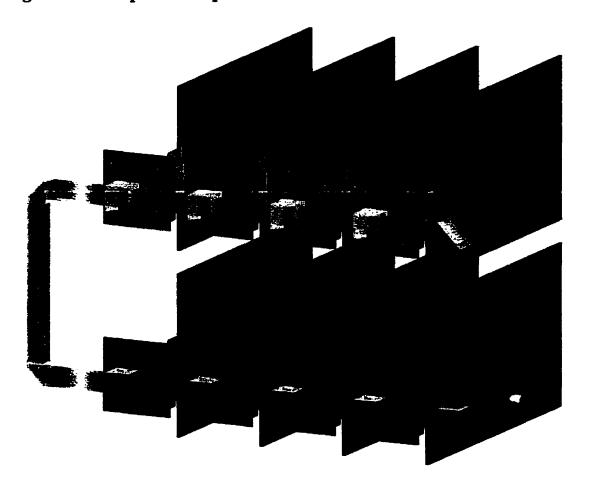

The hybrid device thus integrated can be used as an optical communication node, thereby exploiting the two-dimensional, volumetric nature of the signals as depicted in figure 2.2. This figure ignores the details of the optical interconnection scheme used, but shows a representative application of such an interconnect: to connect printed circuit boards. The details of this optical interconnect and its implications on

Figure 2.2: Optical backplane

the constraints of the packaging system are discussed in section 2.3. The remaining constraints on the packaging fall from the device's thermal dependence, in section 2.4 and the specifics of the electrical connectivity and signal integrity, in the following section (2.2).

# 2.2 Electrical constraints

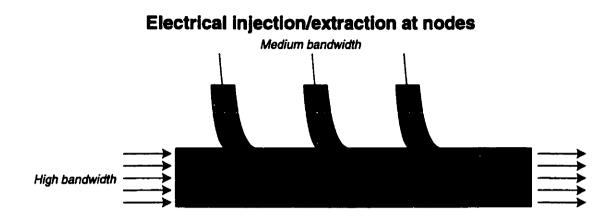

For the system demonstrators in development by the Photonic Systems Group of McGill University, optical nodes in the backplane support the aggregate bandwidth of the entire backplane, and the individual optoelectronic device arrays are required to inject or extract data from this backplane, in what has been referred to as a firehose architecture [6]. This architecture is illustrated in figure 2.3.

Figure 2.3: Firehose architecture

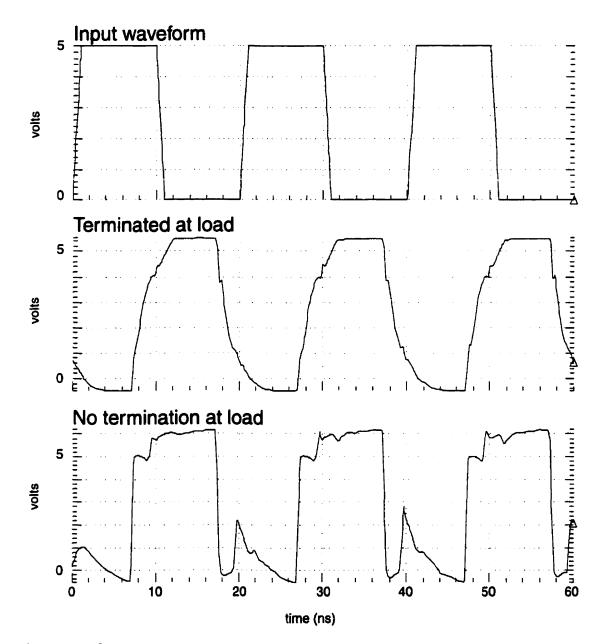

With the firehose architecture, each optoelectronic device is required to support only a medium electronic bandwidth but the entire, high optical bandwidth. This medium electronic bandwidth can still be substantial, and consists, in the Photonic Systems Group incarnation of the optical backplane, of many electrical inputs and outputs, running at speeds of up to 100 Mbit/s. Electrical signal integrity is a serious concern at this speed, and the packaging system must directly address this issue, with impedance control, high-speed, dense connectorization, and adequate termination of electrical signals.

A standard rule-of-thumb that is used to separate low-speed from high-speed packaging problems in the electronics world is the l/6 rule [7]. This rule indicates the demarcation between the transmission line domain and lumped model domain. For example, a 100 MHz digital signal with a rise time or fall time of 1000 ps (1/10).

the cycle width) travelling along a polyimide board with a delay per unit length of 180 ps/in (7 ps/mm) has a rising edge length of:

$$l = \frac{T_R}{D} = \frac{1000 \text{ ps}}{\left(\frac{7 \text{ ps}}{1 \text{ mm}}\right)} = 143 \text{ mm}$$

(2.1)

where D is the delay per unit length, and  $T_R$  is the rise time. For this example, the demarcation between lumped and transmission line models is at 24 mm (l/6). Any trace longer than 24 mm should be treated as if it were a transmission line. For most of the examples presented here, the circuits are significantly longer than the validity that a lumped model permits, requiring a transmission line treatment. In this treatment, termination is necessary to prevent reflections. In the packaging systems presented, the inputs to the optoelectronic device are CMOS inputs, presenting a high impedance to the transmission line, necessitating a termination to prevent an amplitude doubling reflection. Various termination schemes are used, but dominant categories are active Schottky (diode) termination and passive (resistor or resistor and capacitor) termination. Both are present in the Phase III system presented in chapter 4.

# 2.3 Optical and optomechanical constraints

For a packaging system involving an optoelectronic device to be successful, it must interface the optoelectronic device effectively to the optical interconnect. The optical interconnect design, and restrictions on focal length, will generally keep the optoelectronic device in close proximity to optics, forcing tight constraints for

volumes and footprints in the packaging system. The interface itself is clearly also an issue, with the ability to align the optoelectronic device to the optical interconnect a primary concern.

The specific constraints that optomechanical and optical issues form will be introduced in each specific section as they apply to a system demonstrator in chapters 3 and 4.

## 2.4 Thermal issues

This section deals with the thermal issues inherent in a system that uses QCSE modulators and detectors. These devices are temperature sensitive, and a lack of control over each device's temperature could affect system performance. A stepwise optimization procedure to optimize the performance of modulators and detectors is introduced in section 2.4.3.

# 2.4.3 Temperature optimization of device performance

#### Introduction

For a photonic interconnect that utilizes QCSE modulators and detectors in the optical data link, specific optimizations can be performed with regard to the temperature sensitivity. The following section will deal with the temperature dependencies of these devices and suggest an optimization technique.

To introduce the optimization procedure, representative graphs measured from real QCSE modulators and detectors are used. For the data used, the detectors and modulators are identical devices. In a system, these devices would be operated

under different electrical and optical conditions to control their mode of operation.

The optimization technique presented here does not preclude the use of separately designed and fabricated devices for modulators and detectors [5].

The modulators and detectors were both Multiple Quantum Well (MQW) diodes created in Gallium Arsenide by researchers at Nortel Technology (wafer growth) and École Polytechnique de Montréal (processing), and measured using an optical/electrical setup with wavelength, voltage and temperature sweeping capabilities. At each voltage, temperature and wavelength, the output photocurrent of the diode could be measured.

The setup consisted of a monochromator (*Oriel Instruments* MS 257), a DSP lock-in amplifier (*Stanford Research Systems* SR830), temperature controller (*ILX* LDC-3722B), voltage source (*Keithley* 230), optical chopper and microprobes. This setup allowed very small photocurrents to be sampled by probing the active device with microprobes. The photocurrents are isolated from background noise using the optical chopper and lock-in amplifier.

The GaAs devices are tested prior to their hybrid integration onto a CMOS or BiCMOS chip. To do this, the devices are temporarily mounted in a Pin-Grid-Array (PGA) chip carrier cavity alongside a chip thermistor (*Betatherm* 10K3CG2). To control the temperature, a Peltier device (*Marlow Industries* MI1060T) is operated in reverse mode to raise the temperature of the cavity, under the control of the temperature controller. The PGA is mounted on a custom-designed mounting printed circuit, and the monochromator delivers a given wavelength so that the

resulting photocurrent can be measured. The measurement system is under the control of a single Macintosh computer running (*National Instruments*) LabView software.

The wavelength dependency of the quantum efficiency,  $\eta$ , of a detector is an important metric, and the temperature shift of this efficiency versus wavelength is an oft-quoted number; approximately 0.3 nm/°C [5]. In a communications system, specific optimization is needed in order to maximize performance for modulators and detectors at a given wavelength, the system's wavelength, around which all the optical elements are designed. The behaviour of the exciton curve for such a device at wavelengths other than the system wavelength may not be relevant, in this case.

For detectors, the absorption should be maximized for this wavelength, at the operating temperature, for a given bias voltage. For modulators driven by circuit logic, the reflectivity difference should be maximized at this wavelength, at the operating temperature, using two parameters: the bias and the available logic swing.

These dependencies can be summarized as:

$$absorption = 1 - R_{detector}(\lambda, T, V_{bias})$$

(2.2)

where R is the reflectivity, $\lambda$  is the wavelength, T is the temperature,  $V_{bias}$  is the reverse bias voltage.

reflectivity difference =

$$\Delta R_{modulator}(\lambda, T, V_{bias}, \Delta V)$$

(2.3)

where  $\lambda$  is the wavelength, T is the temperature,  $V_{bias}$  is the reverse prebias voltage and  $\Delta V$  is the available logic swing.

In a system, the wavelength is fixed ( $\lambda$  = constant), and frequently the available logic swing is fixed ( $\Delta V$  = constant). If the absorption and the reflectivity difference are independently optimized (maximized) to find the ideal  $V_{bias}$  for each, at any given temperature, the dependencies become:

$$1 - R_{detector}(T) \tag{2.4}$$

$$\Delta R_{modulator}(T)$$

(2.5)

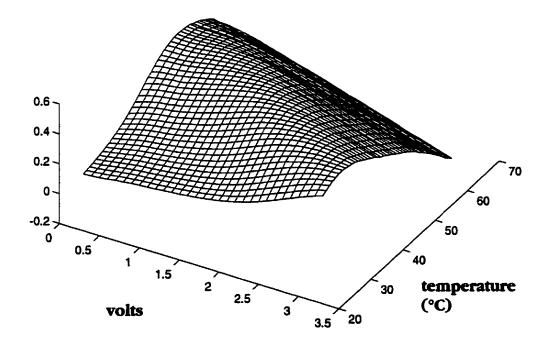

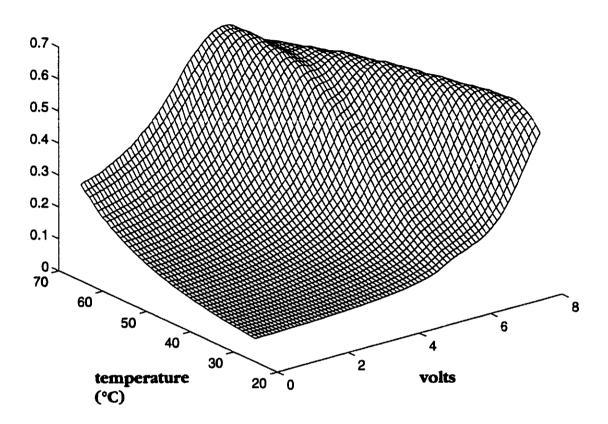

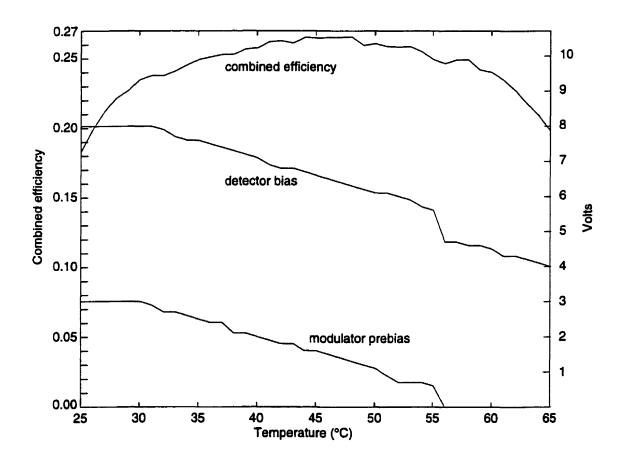

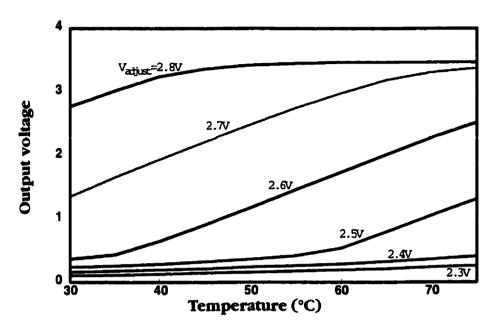

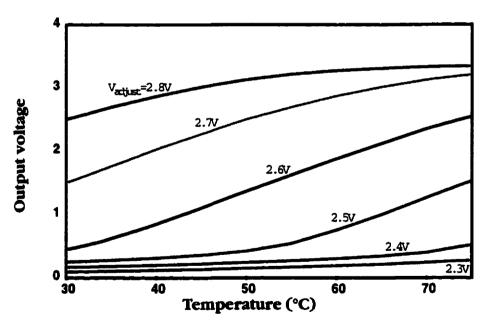

In the following graphs illustrating this optimization,  $\Delta V$  was set to the logic swing of our system, 5 V,  $\lambda$  was set to the operating wavelength of our system, 852.0 nm. The resulting graphs are shown in figures 2.4 and 2.5. For these values, the

Figure 2.4: Modulator reflectivity difference

Figure 2.5: Detector (1-R)

reflectance of the back mirror of the QCSE device (gold) is assumed to be 91.2%, so that the difference between input and reflected optical power can be used to develop a reflectance for the device.

Using an existing metric [5], equations 2.4 and 2.5 can be combined by multiplication, with the critical assumption that modulator and detector must operate at the same temperature. This assumption is reasonable given a standard configuration where modulators and detectors are coplanar in an optical

communication device on the same underlying electronics. The resulting equation is:

combined efficiency =

$$\eta_B(T) = (1 - R_{detector}(T)) \cdot \Delta R_{modulator}(T)$$

(2.1)

If both the modulators and detectors performance are maximized at each temperature by picking the optimum prebias and bias voltage, the resulting graph is shown in figure 2.6. The peak of the  $\eta_B$  defines the optimal operating temperature

Figure 2.6: Combined efficiency versus temperature (maximized)

of a system which uses these modulators and detectors, where a read beam is incident on a modulator, reflected, and the resulting modulated beam is incident on a detector. This graph indicates the temperature dependency of performance for

this optical data link. Additionally, the optimized values for the voltage for prebias for modulators and bias for detectors at any given temperature can be found on the scale on the right side of this graph.

## Optimization procedure

The steps used to produce the graph shown in figure 2.6 can be summarized as follows:

- 1. At the operating wavelength of the system, using the optical devices, measure the photocurrent produced by a quantum well diode (to be used as either a modulator or detector) across a range of voltages and temperatures. The range of voltages should include both the prebias value for the modulator, V<sub>prebias</sub>, and V<sub>prebias</sub>+ΔV, the maximum voltage that the system is expected to use. For separately fabricated modulators and detectors, two measurements must be taken

- From this data, it is possible to derive the graphs of: a) absorption versus voltage

and temperature and b) reflectivity difference versus voltage and temperature.

The reflectivity difference graph assumes a system logic swing, ΔV.

- Maximizing both absorption and reflectivity difference for a given temperature

and multiplying these results yields the graph of combined efficiency versus

temperature.

From this optimization procedure, it is possible to determine the optimal operating temperature of the device, and the resulting  $V_{bias}$  and  $V_{prebias}$  at this temperature for detectors and modulators, respectively. Using thermal management techniques

with a feedback loop for temperature control it is possible to set the device temperature accurately, as will be shown in the following chapters.

If it is desirable to operate the devices at a temperature other than this optimal temperature, then the resulting  $V_{bias}$  and  $V_{prebias}$  for another temperature can be determined from the optimization procedure. This is useful if, for example, thermal stabilization is possible using available packaging techniques but thermal control to an *optimal* temperature is not possible.

# 2.4.4 Thermal management

Once it has been established what the desired operating conditions of the device are, packaging must enforce these conditions. Accurate thermal modelling using finite element analysis (FEA) and computational fluid dynamics (CFD) software can help predict the thermal properties of a proposed package, and determine what elements this thermal management must incorporate.

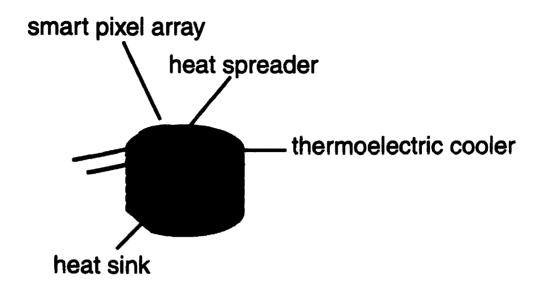

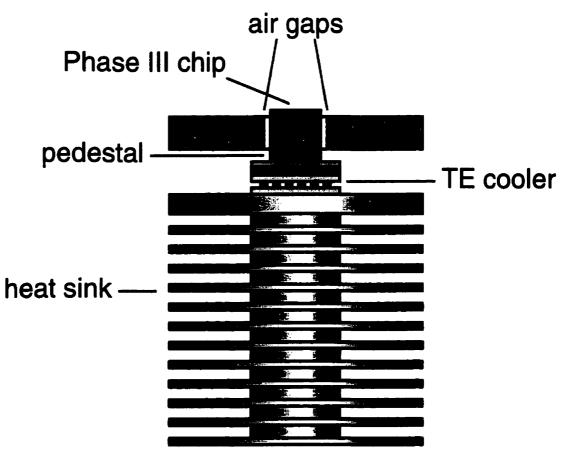

Thermoelectric coolers (figure 2.7) using the Peltier effect have been used in the

Figure 2.7: Thermoelectric cooler

optoelectronics industry to control both CCD and laser diode temperatures [for

example, 6], and more recently these temperature control elements have been used by researchers for two-dimensional arrays of surface-active devices [9]. A thermoelectric cooler uses thermocouples to set up a heat pump between its two surfaces [10], creating a hot and cold side. In general, this is used to cool a device in thermally conductive contact with the cold side that would, under natural convection, operate at a higher temperature. With current flowing in the reverse direction, the symmetric thermoelectric cooler pumps heat towards the device. With feedback from temperature sensors, this bidirectional nature can be used to accurately control the device temperature. Many commercial instruments are available to complete the control loop. These instruments use a single temperature sensor input with an internal control loop to set the output current magnitude and direction for a thermoelectric cooler [11]. The IDT 5910 temperature controller from ILX is a representative instrument that can accept temperature sensor input from a thermistor, a current output temperature sensor (the AD590) or a voltage output temperature sensor (the LM335).

For packaging systems that will be presented in subsequent chapters, this temperature controller (or a similar device) was used in a control loop with a thermoelectric cooler. In chapter 3, the CMOS-QCSE packaging used a sensor input from a thermistor chip mounted on a surface in immediate contact with the device side of the thermoelectric cooler. In chapter 4, BiCMOS-QCSE packaging used a simulated LM335 input that was generated by a computer scanning and then averaging an array of temperature sensors integrated into the electronics on the top side of the surface-active device array.

A serious concern in the design of such a temperature management system is the uniformity of device temperatures across a large array. It can be expected that convective and conductive heat transfer, dependent on package design, as well as nonuniform electrical heat dissipation will introduce nonuniformities in temperature on the device surface. It is not feasible to individually control the device temperatures in an array in the same active manner that a thermoelectric cooler can control the entire die temperature. Without control of the individual device temperatures, a nonoptimized package design will generate varying (nonoptimal) performance of devices across the surface, dependent on location.

Using thermal analysis software coupled with experimentation, it is possible to design the package structure so that these nonuniformities are made small and perhaps negligible. Such a method has been used in the past for electronic devices by James Sweet [12], where an array of temperature sensors was designed onto a test chip and incorporated into a mockup of the packaging system, so that thermal nonuniformities could be predicted and the thermal model in FEA software validated.

For optoelectronic devices, Nagesh Basavanhally has used FEA software to model a device array and to predict package design thermal performance with respect to temperature nonuniformities [9]. With software, the machining of the package design was optimized to minimize these nonuniformities.

For the system presented in chapter 3, no regard was paid to nonuniformities caused by package design. The package was simply athermalized, with a heat

spreader (pedestal) larger than the die assumed to produce temperature unformity over the 2 x 2 mm die. This design assumption was not verifiable using laboratory equipment that was available.

This assumption was removed in the system presented in chapter 4. This packaging system used a combination of CFD thermal analysis and an array of temperature sensors to verify the minimization of package temperature nonuniformities. In this system, an athermalized pedestal was machined in the mount, connected to the rest of the mount only by narrow, thermally resistive joints. This pedestal shared its dimensions with those of the die (8 x 8 mm). The success of this technique, using software to predict thermal performance, allowing this prediction to be corrected by thermal sensors, and then redesigning the package to compensate, compels the author to propose that it be continued in future systems, as an iterative technique to optimize package design.

# 2.5 Manufacturing and reliability

A packaging approach must satisfy additional constraints in order to make the transition between a realizable package and a reliable, manufacturable package. This thesis deals exclusively with the task and theory of realizing a packaging approach. The issues of reliability and manufacturability, although important, are not addressed here.

#### 2.6 Conclusions

The design issues inherent to a system using Quantum Confined Stark Effect modulators and detectors for communication in an optical backplane have been presented, indicating the specific design issues of thermal management, electrical connectivity and the particular optomechanical constraints of an interconnect architecture. Specific application of a temperature optimization technique has been developed, allowing the optimum temperature of a QCSE device to be determined. Subsequent chapters will demonstrate and address these design constraints for demonstrator systems.

#### 2.7 References

- [1] David V. Plant, Alain Z. Shang, Marcos R. Otazo, David R. Rolston, Brian Robertson, H. Scott Hinton, "Design, Modelling and Characterization of FET-SEED Smart Pixel Transceiver Arrays for Optical Backplanes," *IEEE Journal of Quantum Electronics*, August 1996, Vol. 32, No. 8, pp1391–1398.

- [2] David V. Plant, Brian Robertson, H.Scott Hinton, W.M. Robertson, M.H. Ayliffe, Guillaume C. Boisset, Wayne S. Hsiao, David Kabal, Nam-Hyong Kim, Yongsheng S. Liu, Marcos R. Otazo, and Alain Z. Shang, "A 4x4 VCSEL/MSM Optical Backplane Demonstrator System," *Applied Optics*, 1996

- [3] David R. Rolston, David V. Plant, Ted H. Szymanski, H. Scott Hinton, Wayne S. Hsiao, Michael H. Ayliffe, David Kabal, Michael B. Venditti, P. Desai, Ashok V. Krishnamoorthy, Keith W. Goossen, J.A. Walker, B. Tseng, S.P. Hui, J.E. Cun-

- ningham, and W.Y. Jan, "A Hybrid-SEED Smart Pixel Array for a Four-Stage Intelligent Optical Backplane Demonstrator," *IEEE Journal of Selected Topics in Quantum Electronics*, April 1996, Vol. 2, No. 1, pp97–105.

- [4] D. Kabal, G. Boisset, D.R. Rolston, D.V. Plant, "Packaging of two-dimensional smart pixel arrays," Presented at IEEE Summer Topical Meeting on Smart Pixels, Keystone, Colorado, Aug. 1996.

- [5] David T. Neilson, "Optimization and Tolerance Analysis of QCSE Modulators and Detectors," *IEEE Journal of Quantum Electronics*, July 1997, Vol. 33, No. 7, pp1094–1103

- [6] Ashok V. Krishnamoorthy, D.A.B. Miller, "Firehose Architectures for Free-Space Optically-Interconnected VLSI Circuits," *Journal of Parallel and Distributed* Computing, November 1996

- [7] Howard W. Johnson, Martin Graham, High-Speed Digital Design: A Handbook of Black Magic, Prentice-Hall, 1993

- [8] Alan R. Mickelson, Nagesh R. Basavanhally and Yung-Cheng Lee, editors, *Optoelectronic packaging*, John Wiley and Sons, Inc., 1997

- [9] Nagesh R. Basavanhally, Michael F. Brady, D. Bruce Buchholz, "Optoelectronic packaging of two-dimensional surface active devices," *IEEE Transaction on Components, Packaging and Manufacturing Technology Part B*, Feb. 1996, Vol. 19, No. 1, pp107–115.

- [10] Frigichip Thermoelectric Cooling Devices, Thermoelectric handbook, Melcor Thermoelectrics, 1995

- [11]LDT 5910B Instruction manual, Thermoelectric Temperature Controller, ILX Lightwave, June 20, 1997

- [12]James N. Sweet, David W. Peterson, Dahwey Chu, Bruce L. Bainbridge, Richard A. Gassman, Cathy A. Reber, "Analysis and measurement of Thermal Resistance in a 3-Dimensional Silicon Multichip Module Populated with Assembly Test Chips," *Proceedings of Ninth Annual IEEE SEMI-THERM Symposium*, November 1993.

# Chapter 3: CMOS-QCSE packaging

#### 3.1 Introduction

This chapter describes the design issues and constraints that formed the basis of a four board optical interconnect implemented by the Photonic Systems Group at McGill University. The packaging for this system had to take into account various constraints arising from the use of a two-dimensional array of surface-active devices: the QCSE modulators and detectors. The optoelectronic chip that was packaged in this system was a CMOS-QCSE device that required a GaAs substrate containing the QCSE devices, which was flip-chipped onto a CMOS die resulting in a hybridized chip of dimensions, 2 mm x 2 mm.

# 3.2 Chip-on-board packaging

When the use of an explicit chip-carrier becomes impossible due to system constraints, an alternate approach may be attempted. If a system has thermal

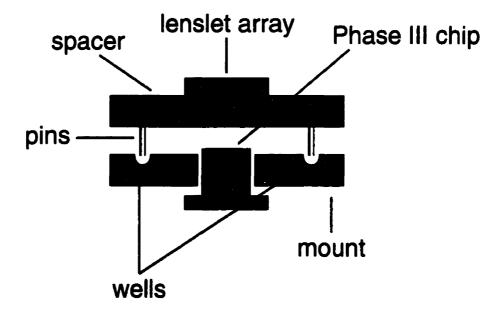

requirements, I/O counts and volume constraints that prohibit the use of standard packages, the optoelectronic device array may be mounted directly on the board, employing the alternative approach of chip-on-board (COB) or MCM-L mounting [1]. To accomplish this packaging task for a CMOS-QCSE optoelectronic device array, the following packaging hierarchy and constraints were proposed:

- 1. The 2-D optoelectronic device array should reside on a small printed circuit daughterboard (mount) that must satisfy optical design constraints. These constraints limits the maximum board area to be used by the packaging to 65.00 by 46.05 mm. The first optical surface needs to be 800 µm from the die surface. Via thermal management, the chip's surface should be maintained at a constant temperature to optimize the responsivity of the optoelectronics.

- 2. This daughterboard should be connected to the next level of hierarchy by a high-speed connection that provides at least 40 I/O pins at 100 Mb/s and can mechanically isolate the daughterboard from other electrical components.

- A motherboard should hold the processing electronics for the optoelectronic

device array, as well as connectivity to the outside world and any applicationspecific electronics.

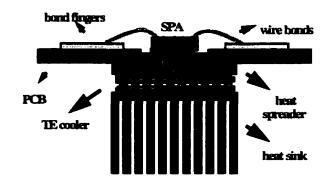

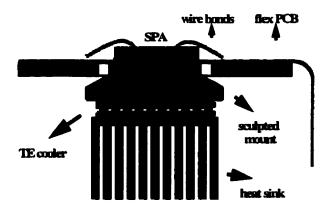

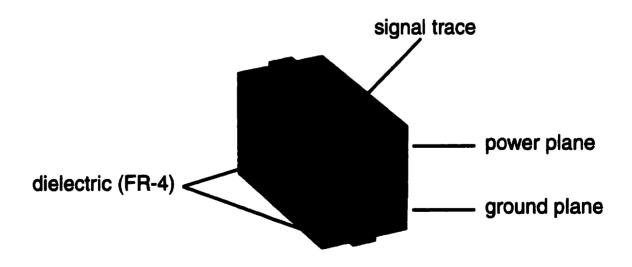

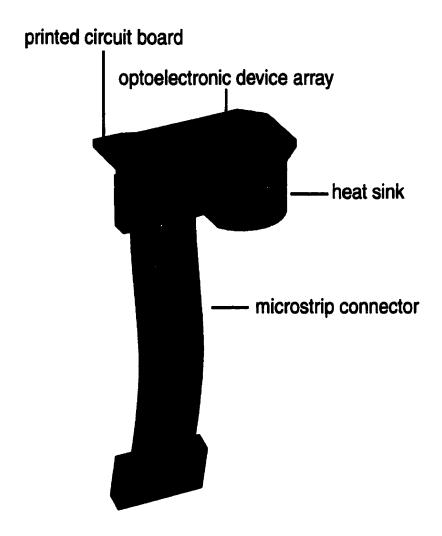

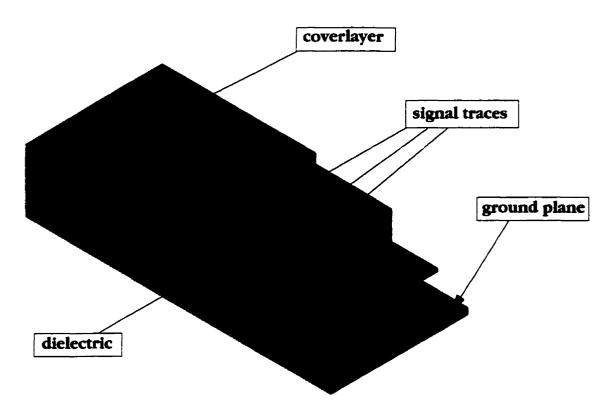

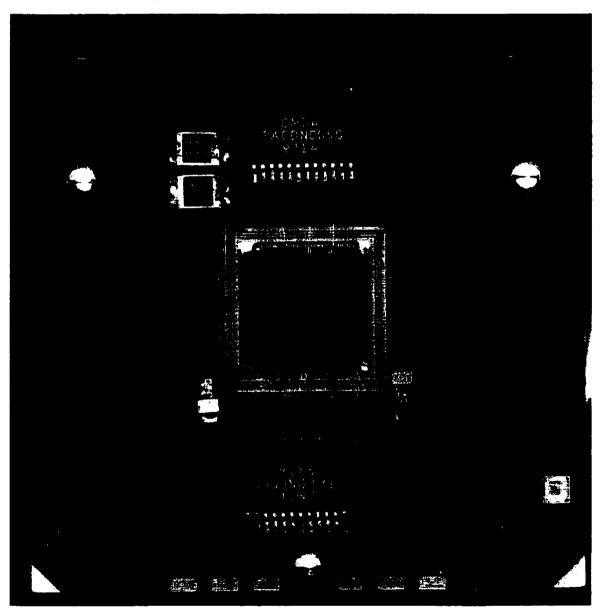

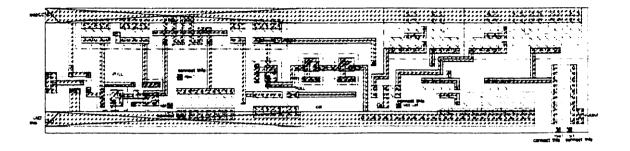

The fabricated daughterboard for COB II is shown in figure 3.2 An illustration of this packaging is shown in figure 3.3. The dimensions of the board are 63.88 mm x 41.80 mm. Including a thermoelectric cooler and heatsink, the thickness of the packaging is 40 mm. These dimensions satisfy the optical design constraints imposed by the system. This board follows an impedance controlled 4-layer FR-4

Figure 3.1: Packaging solutions

a) COB I

b) COB II

c) COB III

microstrip design with a characteristic impedance of 50  $\frac{34}{4}$  (figure 3.4). The impedance is set by fixing the dielectric thickness, b, (0.006"), trace width, w, (0.008") and trace thickness, t, (0.0015"):

$$Z_0 = \frac{87}{\sqrt{\varepsilon_R + 1.41}} \ln \left( \frac{5.98h}{0.8w + t} \right) \text{ (from [2])}$$

(3.1)

Figure 3.2: Completed daughterboard chip-on-board packaging

Figure 3.4: Microstrip stackup

Figure 3.3: Daughterboard packaging assembly

Inner layers in the daughterboard are power planes, while outer layers are reserved for signal lines.

The total board thickness is 0.092", allowing for a more rigid board than the standard 0.062", which was desirable for optical stability in alignment. The CMOS-QCSE optoelectronic device array was wirebonded to 44 bond fingers on the immersion-gold-plated daughterboard.

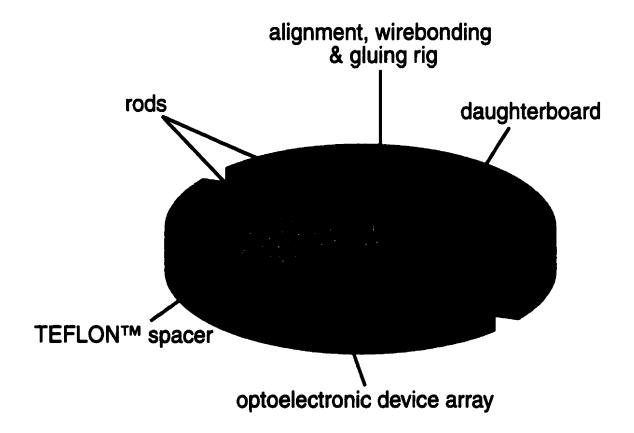

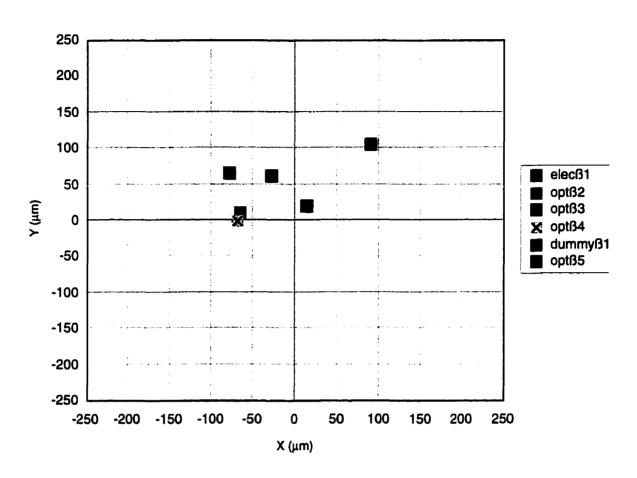

Positional tolerances were mandated by optical design, necessitating a custom assembly procedure using a custom alignment, wire-bonding and gluing rig. This rig is shown in figure 3.5. Application of this procedure to multiple daughterboards

Figure 3.5: Custom alignment, wire-bonding and gluing rig

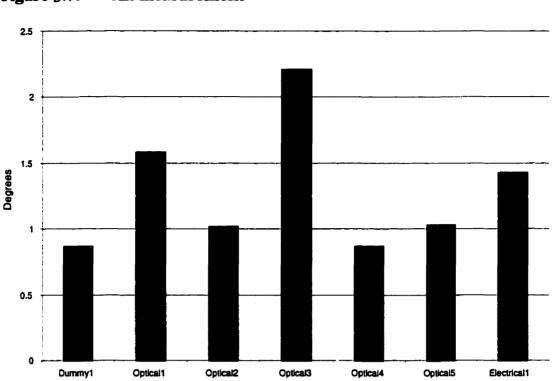

using the rig consistently acheived a lateral alignment tolerance of less than 150 µm (in chip's plane) to a 50 µm measurement resolution. The lateral alignment tolerance data are shown in figure 3.6 for the six fabricated circuit boards, where an HP ScanJet IIc scanner with a input resolution of 600 dots/per/inch was used to measure the alignment precision relative to the printed circuit board. Using microscope depth travel, with a repeatability of 10 µm on the chip corners, the

Figure 3.6: Lateral misalignment for six assembled daughterboards

packaging approach generated a die tilt of less than 2.5° (board plane to chip surface plane), these data are shown in figure 3.7.

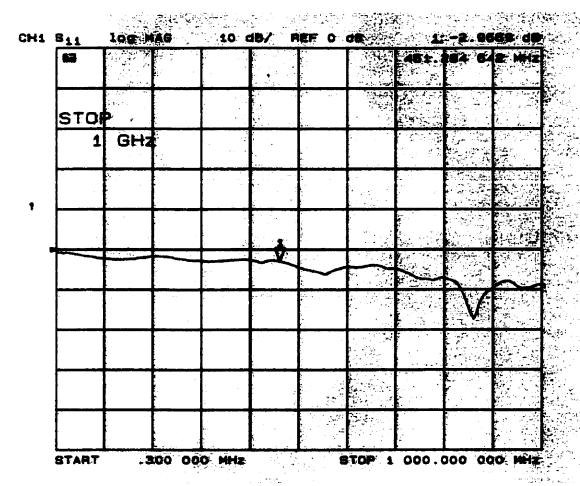

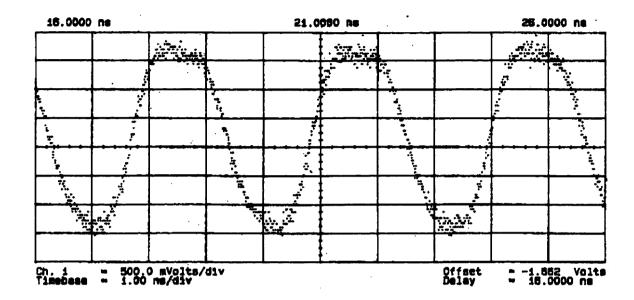

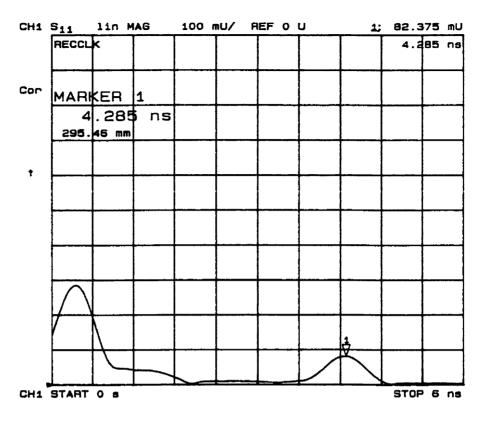

This daughterboard supports a single high-speed microstrip connector for connection to the motherboard via a flexible, impedance-controlled (50 ¾) ribbon. In this way, optical alignment of the photonic interconnect fabric is decoupled from the support electronics, while a reasonably high connectivity (40 pins) is maintained between motherboard and daughterboard at a bandwidth of 1 GHz per connection [3]. The measured -3dB frequency of the entire link between motherboard and daughterboard, including the ribbon cable, was 461 MHz (figure

Figure 3.7: Tilt measurement

3.8). This data was measured using a network analyser. This value indicates that our system was not package bandwidth limited.

In COB I (Fig. 3.1a), the chip was directly mounted on the daughterboard. To manage the higher heat dissipation of the CMOS-QCSE die in COB II, the optoelectronic device array is mounted on a gold-plated, ground-connected heat spreader that moves heat via conduction from the chip to a thermoelectric cooler mounted on the back of the board (figure 3.1b and figure 3.9). The designed peak responsivity of the CMOS-QCSE modulators occurs at 25°C with the available bias voltages (no temperature dependent optimization was performed), and the thermoelectric cooler was able to maintain the die's center at this temperature to within 0.25°C with the die dissipating up to 0.5W. This measurement does not take

Figure 3.8: Network analyser results for package bandwidth

into account die temperature nonuniformity as these data were not available for the CMOS-QCSE die.

Using a dedicated thermal characterization daughterboard, the thermal resistance of the packaging was accurately measured. The thermal resistance from junction to case,  $\theta_{jc}$ , is defined as:

$$\theta_{jc} = \frac{T_j - T_c}{P_{in}} \tag{3.1}$$

Where  $T_j$  and  $T_c$  are the temperatures of the junction (chip surface) and case (for this package, the back of the heat spreader), respectively, and  $P_{in}$  is the power

Figure 3.9: Thermal management

being dissipated on the chip surface. For the measurement of thermal resistance, a thermistor was mounted on the back of the heat spreader and on the top of an electrical-only version of the CMOS-QCSE die. The CMOS inputs were left to float thereby forcing a high power dissipation in the die. With this setup, the thermal resistance of the package was measured to be  $7 \pm 2$  °C/W.

The thermal model assumed a conduction-dominated thermal resistance, with the resistance of a conductive path being defined as:

$$R = \frac{l}{kA} \tag{3.2}$$

with A being the cross-sectional area ( $m^2$ ), l the length of the path (m), and k the thermal conductivity of the material ( $m \cdot {}^{\circ}C / W$ ). The predicted values using this first order model are tabulated below:

**Table 3.1: Modelled thermal resistances**

| Component     | Thermal resistance |  |

|---------------|--------------------|--|

| Silicon die   | 0.8 °C/W           |  |

| Ероху         | 2.0 ° C/W [4]      |  |

| Heat spreader | 0.2 °C/W           |  |

Using these values, the thermal resistance was 3°C / W, which agrees quite closely with the measured value.

It is clear, even in the coarse view offered by this simple model, that the thermal resistance of the epoxy used to glue the chip to the heat spreader dominates the thermal resistance of this packaging approach.

#### 3.3 Conclusions

The packaging approach presented here can be expanded and modified for future, increasingly demanding applications.

Results presented here indicate that the packaging techniques used for the CMOS-QCSE packaging (COB I & II) can be scaled to future systems employing larger and faster 2-D optoelectronic device arrays that will run hotter. Using hybridized QCSE on CMOS or BiCMOS technology, this future package could support a 1 cm x 1 cm

chip dissipating 5 W. This scaleability of approach will be demonstrated in the analysis of the Phase III packaging, which is in the following chapter.

# 3.4 References

- [1] R.R. Johnson, "Multichip modules: next-generation packages," *IEEE Spectrum*, March 1990, pp34–36, 46, 48.

- [2] MECL System Design Handbook, Fourth Edition, Motorola Semiconductor Products, 1983

- [3] AMP™, Inc., "AMP Micro-Strip Cable Assemblies," Cat. 65069, Dec. 1991.

- [4] Data sheet, Epo-Tek H20E, Electrically conductive, Silver Epoxy, Epoxy Technology Inc.

# Chapter 4: BiCMOS-QCSE packaging

#### 4.1 Introduction

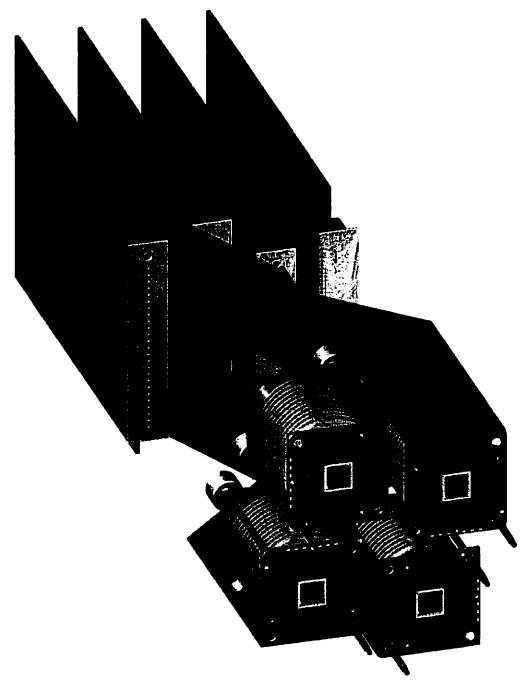

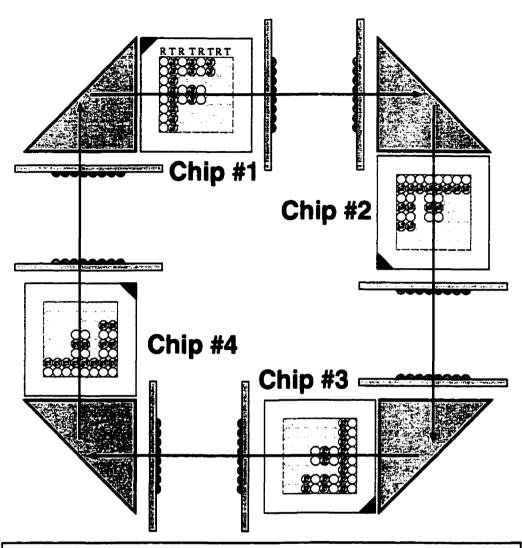

The Photonic Systems Group Phase III BiCMOS-QCSE chip is the core device for a future optical backplane, the Phase III demonstrator. It is a large, 8 x 8 mm chip with a 16 x 16 array of optoelectronic transceivers. On this surface-active chip there is 1024 QCSE devices, arranged into an 8x8 array of optical clusters. This chip must be integrated into a 4 stage free-space optical interconnect. The following section deals with the design, implementation and characterization of the packaging that was designed for this device, with the expectation that this packaging will be integrated into the completed system.

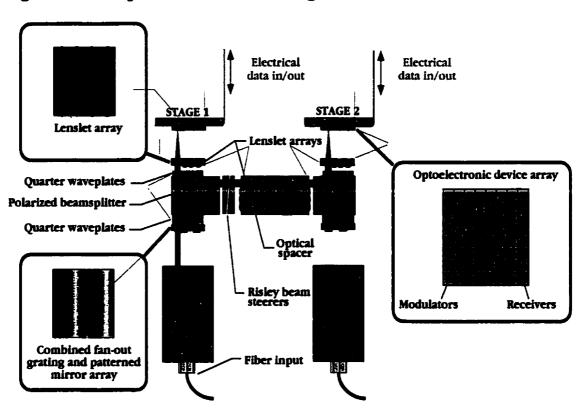

Figure 4.1: Optical interconnect design

# 4.2 Optical interconnect

The optical interconnect for the Phase III demonstrator was designed by Brian Robertson. A schematic of the interconnect is shown in figure 4.1. A detailed description of this interconnect and the design constraints and trade-offs that led to its development can be found in [1]. The optical system consists of mini-lenses that provide relay and interconnect functionalities. The optical data links (ODLs) that this design provides are arranged into clusters [2], because of the resulting increase in alignment tolerances and to increase the overall dimensions of the system.

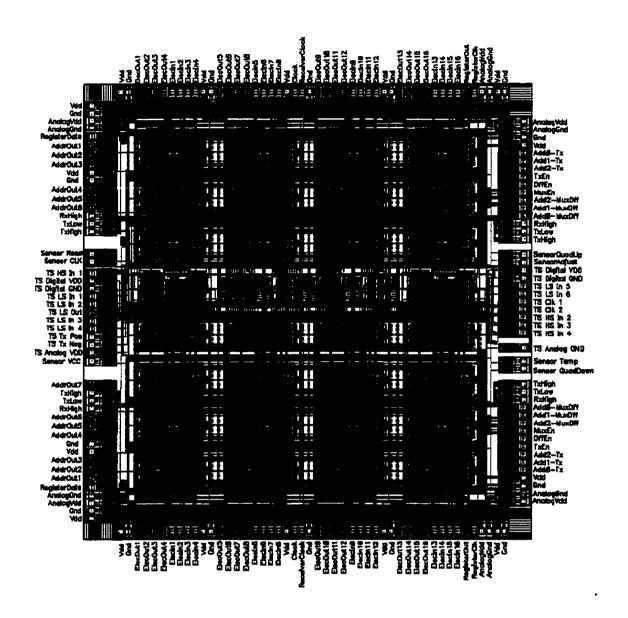

Figure 4.2: Phase III chip

# 4.3 Optoelectronic device description

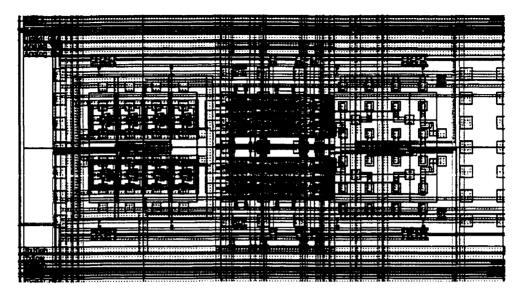

The Phase III chip (figure 4.2) is an 8x8 mm, 0.8  $\mu$ m BiCMOS device. It incorporates almost 0.5 million transistors. The optically active section of the chip is 6.4 mm x 6.4 mm (after it has been flip-chipped with the QCSE devices). The optically active section is divided into an 8x8 array of clusters, each containing 16 QCSE modulators

and 16 detectors. A single cluster is shown in figure 4.3. The Phase III chip has 189

Figure 4.3: Single cluster

bond pads, consisting of 32 inputs, 32 outputs, 2 clocks and control and power pads.

# 4.4 Physical design constraints

The optical interconnect for this system is extremely compact, and this compactness leads to a space constraint for the optoelectronic packaging. The total available footprint (area in chip's plane) was 4 cm x 4 cm. There was no inherent volumetric constraint.

Examining standard consumer electronic carriers and packaging techniques, it became apparent that none of these were adequate for this packaging task. The carrier and connectorization that allowed for mechanical decoupling of the support electronics would have to be housed within the 4 cm by 4 cm area. This area was not sufficient to support a standard 25 mil pitch (625 µm) high-density connector,

with the required 139 lines of off-chip connectivity. An alternate approach, moving the connector away from the packaging, proved to be very effective in side-stepping the problem of connector size.

#### 4.5 Electrical design constraints

To connect the Phase III chip to support and application electronics, it was apparent that the electronic packaging and connection technique would have to have the following specifications:

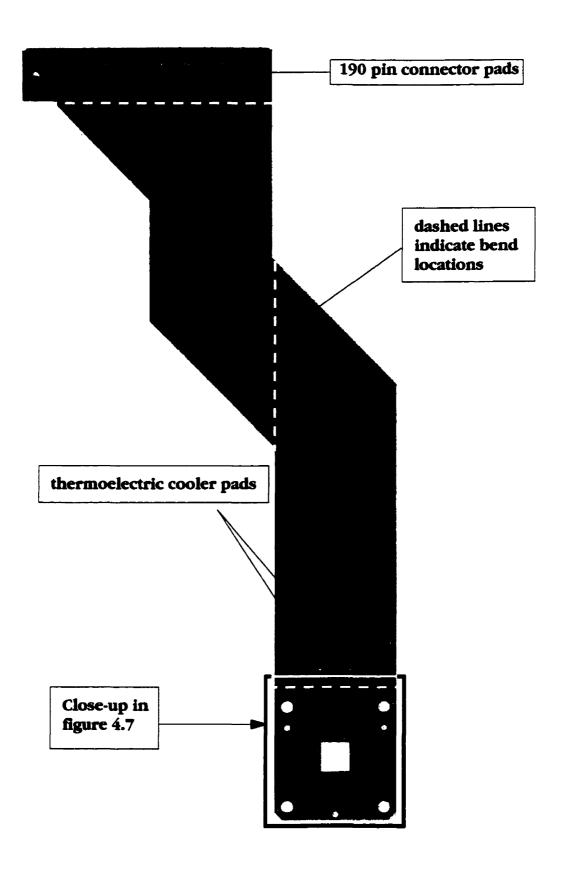

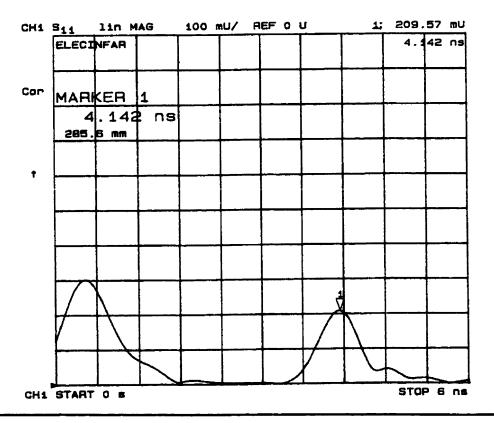

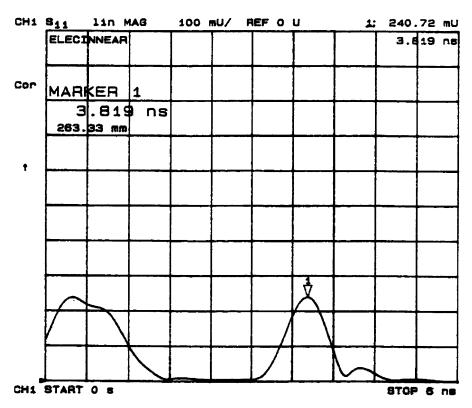

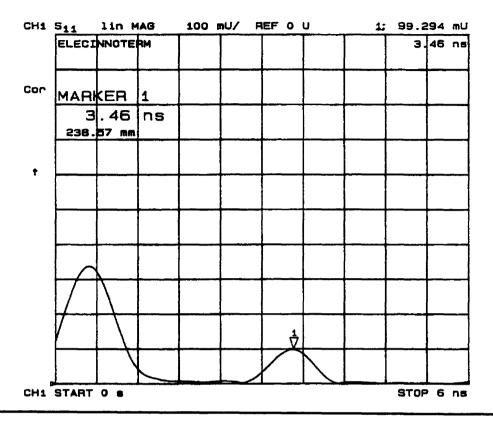

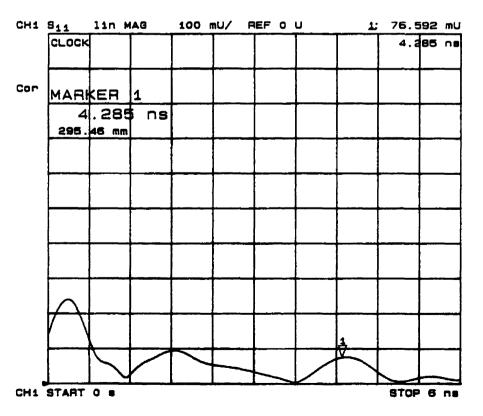

- 1. 139 signal connections to motherboard