# Growing Silicon Thin–Films Laterally Over Amorphous Substrates Using the Vapor–Liquid–Solid Technique

Jerome L. LeBoeuf

Doctor of Philosophy

Department of Mining and Materials Engineering

McGill University Montreal, Quebec 2014-08-15

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Doctor of Philosophy

© Jerome LeBoeuf, 2014

## **DEDICATION**

To everyone I have lost or left behind chasing these dreams.

#### ACKNOWLEDGEMENTS

I would foremost like to thank my family for never stopping me from pursuing my interests, as well as Prof. Nate Quitoriano for supporting this research. I would like to thank the Department of Mining and Materials, the McGill Nanotools Microfab, McGill University and NSERC for providing the resources and the funds which enabled this research. I would like to specifically thank the McGill Nanotools Microfab team members Don Berry, Jun Li, Dr. Lino Eugene and Dr. Matthieu Nannini, as without their aid, patience and encouragement, this research would not have progressed as far as it has. I would like to thank Nicolas Brodusch and Prof. Raynald Gauvin for their input and contributions to the scanning electron microscopy work presented in this research, as well as Dr. David Liu for his aid with transmission electron microscopy imaging, which contributed significantly to understanding of this research. I would like to thank Dr. Lihong Shang, Dr. Florence Paray and Helen Campbell for maintaining the departmental characterization equipment, and Dr. S. Kelly Sears and his team for their upkeep of the equipment at the Facility for Electron Microscopy Research. I would like to thank Barbara Hanley, Teresa Zatylny and the rest of the Mining and Materials administration staff for helping me with the paperwork I was too busy to manage myself. I would like to thank my group colleagues Alexandre Horth, Andrew O'Reilly and Jun Wang for their support and input on the research, as well as Dr. Sriraman Rajagopalan, Dr. Manas Paliwal, Dr. Hendrix Demers, Dr. Jason Milligan, Dr. David Heard, Prof. Marta Cerruti, Peter Gaskell, Matthew Gallaugher, Shirin Kaboli, and Paul Carriere for their insightful conversations on fundamental science, for their helpful instructions on operating characterization equipment, and for generously sharing their laboratory resources. I would like to thank Prof. George Demopoulos for his frank, periodic consultations. I would like to thank all of my fellow graduate students in the Mining and Materials Department for making the research environment familial, and lastly I would like to thank Emily McHugh for proofreading this thesis and Samantha Rudinsky for translating the abstract into French.

#### ABSTRACT

A new technique for growing two-dimensional, laterally grown silicon crystals has been developed. This research borrows from previously reported crystal growing techniques such as Bridgman-Stockbarger growth, epitaxial layer overgrowth, and the vapor-liquid-solid method. Reviews of these technologies are presented. To achieve laterally growth of silicon films, a variant of the vapor-liquid-solid method was utilized, along with equipment and materials traditionally used for microelectronics, to fabricate test structures know as micro-crucibles. These test structures are templates of amorphous materials which confine gold catalyst to a specified geometry. Upon the introduction of a reactive, silicon-containing gas, which diffuses into the micro-crucible and preferentially cracks at the confined gold catalyst, the vaporliquid-solid process takes place and two-dimensional silicon crystals are nucleated from supersaturated gold-silicon alloys within the confines of the micro-crucible. The experimental techniques used to fabricate the micro-crucibles and analyze the silicon growth are described, and new theories on the mechanics of vapor-liquidsolid growth within the micro-crucible test structures are discussed. Semiconducting films grown laterally from micro-crucibles are potential enablers of photovoltaic, optical interconnect, three-dimensional transistor and silicon/III-V on-chip integration technologies, and micro-crucibles are as useful research tools for fundamental studies on grain boundary and solidification theory.

### **ABRÉGÉ**

Une nouvelle technique pour faire croître des cristaux deux-dimensionnels de silicone, crûs latéralement, a été développée. Cette recherche prête des techniques rapportées antérieurement, tel que la croissance Bridgman-Stockbarger, la surcroissance épitaxiale par couches et la méthode vapeur-liquide-solide. Ces techniques sont révisées et discutées en détails. Pour obtenir des pellicules de silicone crues latéralement, une variation de la méthode vapeur-liquide-solide a été utilisée avec de l'équipement et des matériaux utilisés surtout dans des microélectroniques. Des structures tests, appelées des micro-creusets, ont donc été fabriquées. Ces structures tests sont des modèles de matériaux amorphes qui confinent un catalyseur d'or à une géométrie spécifique. Pendant l'introduction d'un gaz contenant de la silicone réactif, qui diffuse dans le micro-creuset et fend préférentiellement au catalyseur d'or confiné, le procédé vapeur-liquide-solide prend place et il y a une nucléation des cristaux de silicone deux-dimensionnels surgissant des alliages sursaturés d'or et de silicone dans les confines du micro-creuset. Les techniques expérimentales utilisées pour fabriquer les micro-creusets et pour analyser la croissance du silicone sont décrites, et de nouvelles théories sur les mécanismes de la croissance vapeur-liquidesolide dans les micro-creusets sont discutées. Les pellicules semi-conductrices crues latéralement sont des facilitatrices potentielles de photovoltaiques, d'interconnexions optiques, de transistors trois-dimensionnels et de technologies intégratrices de puces silicone/III-V. Les micro-creusets sont aussi des outils de recherche utiles pour des études fondamentales sur les fonds de grains et la théorie de solidification.

#### **PREFACE**

This thesis is presented in the manuscript-based form offered to PhD candidates at McGill University, with Sections 3.1, 3.2 and 3.3 being published, or in the process of being published though peer—reviewed journals. These sections are largely unaltered from their originally submitted manuscripts, and thus include abstracts and experimental sections with overlapping subject matter.

#### CONTRIBUTIONS OF AUTHORS

All manuscripts have been submitted with Prof. N. J. Quitoriano, as a co–author, with the manuscripts of Sections 3.2 and 3.3 also including N. Brodusch and Prof. R. Gauvin as co–authors. The papers that form these sections are as follows:

LeBoeuf, J.L., Quitoriano, N.J. (2014). "Nucleation and solidification of laterally grown silicon micro–films on amorphous substrates using the VLS mechanism", *Journal of Crystal Growth*, 391(0). (Section 3.1)

LeBoeuf, J.L., Brodusch, N., Gauvin, R., Quitoriano, N.J. (2014). "Preferred orientations of laterally grown silicon films over amorphous substrates using the VLS technique", *Journal of Applied Physics*, *Accepted*. (Section 3.2)

LeBoeuf, J.L., Brodusch, N., Gauvin, R., Quitoriano, N.J. (2014). "Lowtemperature, vapor–liquid–solid, laterally grown silicon films using alloyed catalysts", *Materials Research Express*, *Accepted*. (Section 3.3)

I hereby give copyright clearance for the inclusion of the above papers, of which I am a co–author, into the PhD dissertation of Jerome LeBoeuf.

| Prof. N.J. Quitoriano | N. Brodusch            |

|-----------------------|------------------------|

|                       | $\overline{Signature}$ |

|                       |                        |

| Date                  | $\overline{Date}$      |

| Prof. R. Gauvin       |                        |

|                       |                        |

|                       |                        |

|                       |                        |

Date

## TABLE OF CONTENTS

| DEI  | DICAT  | ON                                                        | ii |

|------|--------|-----------------------------------------------------------|----|

| ACF  | KNOW   | EDGEMENTS i                                               | ii |

| ABS  | STRAC  | Γ                                                         | v  |

| ABI  | RÉGÉ   |                                                           | ⁄i |

| PRE  | EFACE  |                                                           | ii |

| LIST | ГОГТ   | ABLES                                                     | ii |

| LIST | Г ОБ І | GURES                                                     | ii |

| 1    | Resea  | ch Motivations and Literature Review                      | 1  |

|      | 1.1    | Gold–Silicon Research and Technology                      |    |

|      | 1.2    | Vapor–Liquid–Solid Nanowires                              | 6  |

|      | 1.3    | Bridgman–Stockbarger Growth                               | 2  |

|      | 1.4    | Epitaxial Layer Overgrowth                                | 4  |

|      | 1.5    | Confined Lateral Growth                                   | 7  |

|      | 1.6    | Electron Beam Analysis                                    | 2  |

|      |        | 1.6.1 Electron Backscatter Diffraction                    | 8  |

|      |        | 1.6.2 Transmission Electron Forward Scatter Diffraction 3 | 9  |

| 2    | Expe   | mental Procedures                                         | 3  |

|      | 2.1    | List of Materials                                         | _  |

|      |        | 2.1.1 Substrates                                          | 3  |

|      |        | 2.1.2 Photoresists                                        | 5  |

|      |        | 2.1.3 Thin Metal Films                                    | 7  |

|      |        | 2.1.4 Wet Chemicals                                       | 9  |

|      |        | 2.1.5 Reactive Gases                                      | 3  |

|      |        | 2.1.6 Encapsulation and Adhesive Materials 5              | 5  |

|   | 2.2  | Fabrication Processes                               |                    | 57  |

|---|------|-----------------------------------------------------|--------------------|-----|

|   |      | 2.2.1 Micro-crucible Definition through Wet Etc     | ching              | 58  |

|   |      | 2.2.2 Micro-crucible Definition through Photore     | esist Lift-Off     | 61  |

|   |      | 2.2.3 PECVD Encapsulation Layers                    |                    | 62  |

|   |      | 2.2.4 Etching Gold Out of Micro-crucibles           |                    | 65  |

|   |      | 2.2.5 Sample Preparation Prior to Growth            |                    | 66  |

|   |      | 2.2.6 Chemical Vapor Deposition Process Paran       |                    | 66  |

|   |      | 2.2.7 Preparing Samples for Transmission Electronic |                    | 67  |

| 3 | Manı | nuscripts                                           |                    | 72  |

|   | 3.1  | Nucleation and solidification of laterally grown si | licon micro-films  |     |

|   |      | on amorphous substrates using the VLS mecha         |                    | 74  |

|   |      | 3.1.1 Abstract                                      |                    | 74  |

|   |      | 3.1.2 Introduction                                  |                    | 75  |

|   |      | 3.1.3 Experimental                                  |                    | 78  |

|   |      | 3.1.4 Results                                       |                    | 79  |

|   |      | 3.1.5 Discussion                                    |                    | 85  |

|   |      | 3.1.6 Conclusions                                   |                    | 94  |

|   |      | 3.1.7 Acknowledgments                               |                    | 95  |

|   | 3.2  | Observations on the preferred orientation of latera | ally grown silicon |     |

|   |      | films over amorphous substrates using the VLS       | S process          | 96  |

|   |      | 3.2.1 Abstract                                      |                    | 96  |

|   |      | 3.2.2 Introduction                                  |                    | 96  |

|   |      | 3.2.3 Experimental                                  |                    | 101 |

|   |      | 3.2.4 Results                                       |                    | 103 |

|   |      | 3.2.5 Discussion                                    |                    | 110 |

|   |      | 3.2.6 Conclusion                                    |                    | 117 |

|   |      | 3.2.7 Acknowledgments                               |                    | 118 |

|   | 3.3  | Alloyed catalysts and their effect on lateral, vap  |                    |     |

|   |      | grown thin–films                                    | _                  | 119 |

|   |      | 3.3.1 Abstract                                      |                    | 119 |

|   |      | 3.3.2 Introduction                                  |                    | 119 |

|   |      | 3.3.3 Experimental                                  |                    | 121 |

|   |      | 3.3.4 Results                                       |                    | 125 |

|   |      | 3.3.5 Discussion                                    |                    | 136 |

|   |      | 3.3.6 Conclusion                                    |                    | 150 |

|   |      | 3.3.7 Acknowledgments                               |                    | 151 |

|   | 3.4  | Summery of Manuscripts                              |                    | 152 |

| 4   | Concl | mons and Future Work |

|-----|-------|----------------------|

|     |       | Conclusions          |

| REF | FEREN | ES                   |

## LIST OF TABLES

| <u>Table</u> |                                                             |  | <u>p</u> | age |

|--------------|-------------------------------------------------------------|--|----------|-----|

| 2-1          | Process Parameters for PECVD Encapsulation Layer Deposition |  |          | 65  |

#### LIST OF FIGURES

| Figure | LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

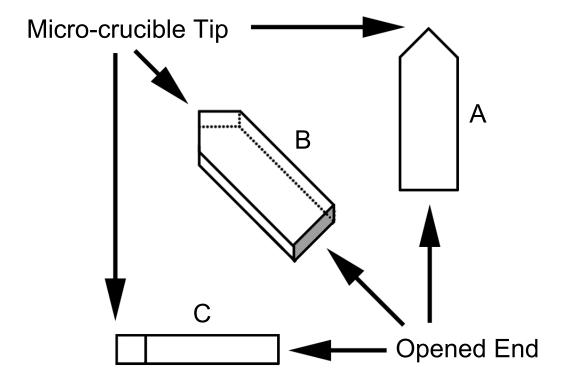

|        | Plan (A), isometric (B) and cross—sectional views (C) of the micro—crucible structure used to experimentally produce high—quality semiconducting crystals. A gold catalyst is located at the tip of the micro—crucible, and opening opposite the tip allows gaseous semi-conducting precursors to diffuse to the catalyst and preferentially crack at its surface, thus resulting in a VLS reaction and crystal growth within the crucible                                                                                                                                                                                                                                                                                             | . 4  |

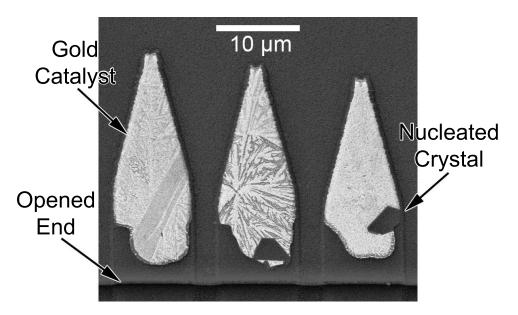

| 1–2    | A plan–view backscatter electron micrograph of three neighboring micro–crucibles, the middle and rightmost crucibles have nucleated semiconductor crystals during a CVD process using the VLS technique. The crystals are confined to morphology of the amorphous micro–crucible and grow laterally as they grow larger                                                                                                                                                                                                                                                                                                                                                                                                                | . 5  |

| 1–3    | A larger goal of this work is to provide a technology which lowers the cost of high efficiency photovoltaics. Here a large grained GaAs substrate is depicted as being produced by thermally oxidizing a silicon substrate, fabricating micro-crucibles (not pictured) on the substrate, and growing GaAs seeds in the micro-crucibles using the VLS process. The seeded substrate is placed into a VPE or MOVPE deposition process where the larger GaAs grain pictures in Figure 1–3A nucleate at sites where the previously grown micro-crucible seeds were located. After nucleating, the larger GaAs grains grew laterally over the amorphous silicon oxide substrate until covering the entire surface and impinging one another | . 8  |

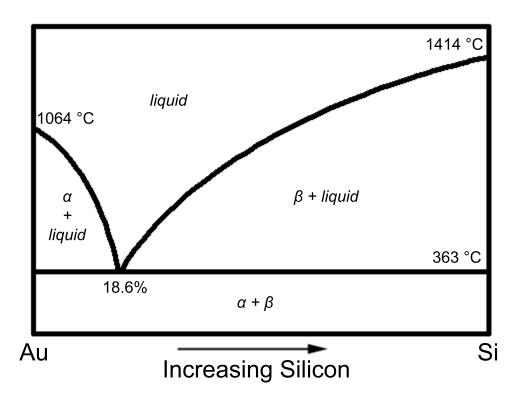

| 1–4    | Equlibrium Au–Si phase diagram in atomic percent with the relevant temperatures and compositions labeled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 11 |

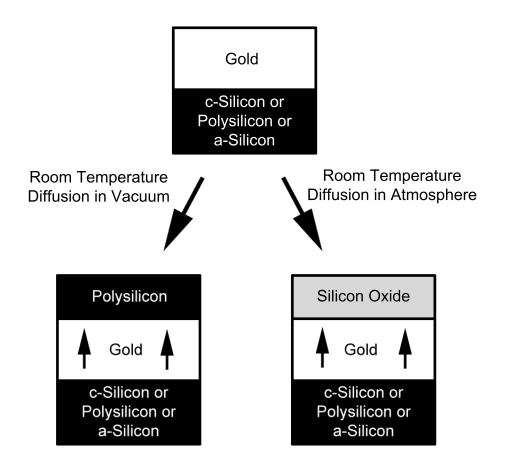

| 1–5  | Gold—silicon interface where a single crystal of silicon film (c-Silicon), a polycrystalline silicon film (Polysilicon) or a amorphous silicon film (a-Silicon) has diffused across a gold thin—film to the free surface at room temperature. In vacuum, the diffused silicon forms a polycrystalline silicon film at the free surface, on top of the gold film. In atmoshpere, the diffused silicon forms a silicon oxide film at the free surface, on top of the gold film.                                                                                                                                                                                                         | 14 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

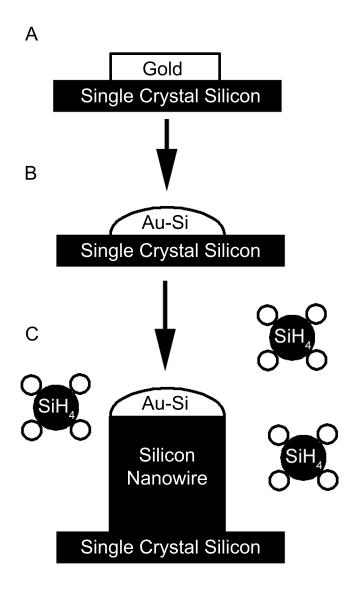

| 1-6  | (A) A Si {1 1 1} wafer which has had its native oxide layer removed and a thin Au film deposited on to its surface. (B) The Si wafer has been heated above the Au–Si eutectic temperature and the Au film has formed a liquid Au–Si alloy with Si dissolved from the substrate. (C) A gaseous Si precursor (SiH <sub>4</sub> ) has been introduced to the wafer, which preferentially cracks at the gold–vapor interface and deposits Si atoms into the Au–Si alloy. The alloy supersaturates and deposits the excess Si atoms on the silicon wafer on which it sits. A highly crystalline Si wire grows from underneath the Au–Si alloy as more Si is deposited into the Au–Si alloy | 17 |

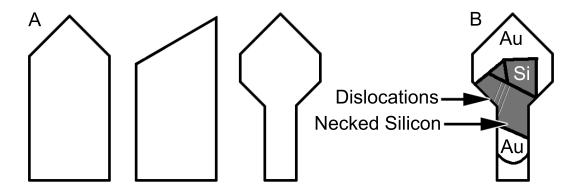

| 1–7  | Plan—view depictions of some of the micro—crucible designs for this work. Figure 1–7B depicts one of the designs which has necked out polycrysalline growth and dislocations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

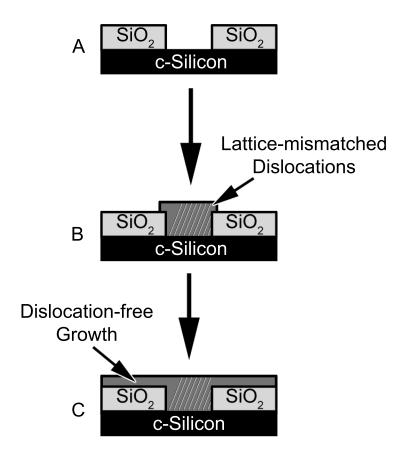

| 1-8  | (A) A silicon substrate which has been selectively masked with a thermal oxide. (B) The initial epitaxial growth nucleates where the silicon oxide mask has been selectively etch. The initial growth has dislocations which start at the interface of the silicon substrate and the dissimilar semiconducting film growing on top of it. (C) The dissimilar semiconducting grows laterally over the silicon oxide with the dislocations concentrated in the interfacial regions of the silicon substrate and the dissimilar semiconducting film                                                                                                                                      | 25 |

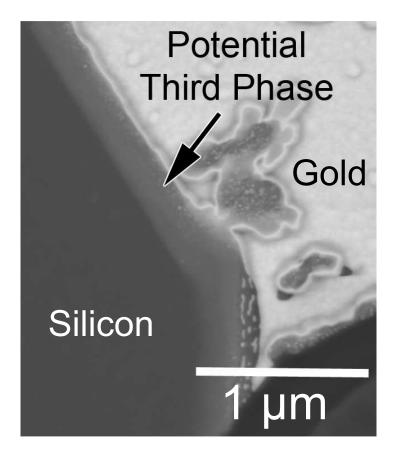

| 1–9  | Observed gray area and potential third phase in a micro–crucible at the interface of the facet crystal and lamellar gold–silicon phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

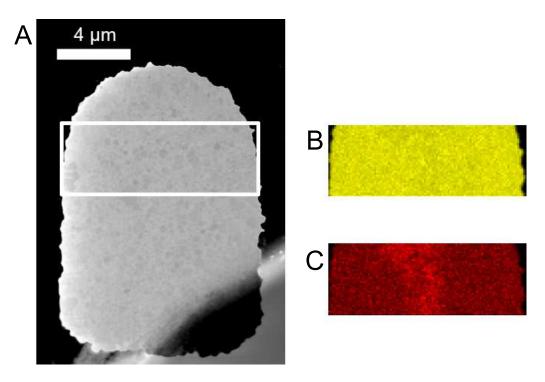

| 1–10 | (A) A HAADF image of a micro-crucible prior to the CVD step. (B) An EDS map of Au. (C) An EDS map of Cr showing that it is concentrated in the center of the crucible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35 |

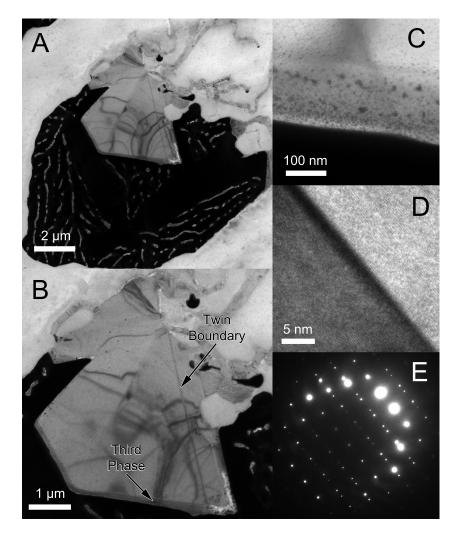

| 1–11 | A set of progressive TEM images analyzing a micro-crucible which has nucleated a twinned crystal. Figure 1–11A is a image of the whole micro-crucible. Figure 1–11B is magnified image of the faceted crystal. Figure 1–11C is a high magnification image of the interface between facet crystal and lamellar gold-silicon phases. This interface is believed to be the same imaged with a SEM in Figure 1–9. Figure 1–11D is a HRTEM image of the twin boundary between two neighboring grains and Figure 1–11E is the SAED pattern of the twin boundary                                             | 37 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

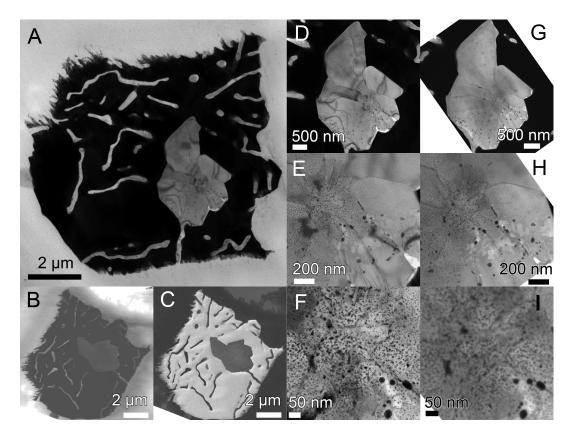

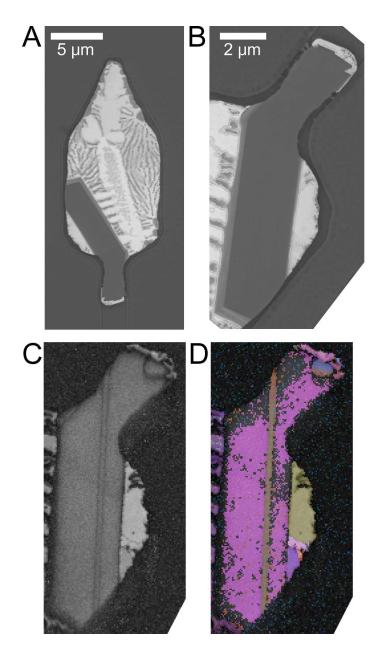

| 1–12 | Micrographs comparing bright–field imaging in a conventional TEM and transmission electron imaging in a SEM. Figure 1–12A is a TEM bright–field image of micro–crucible with a nucleated faceted crystal. Figures 1–12B and C image the same micro–crucible in 1–12A, but imaged using transmission SEM mode and secondary electron mode respectively. Figures 1–12D through F, and G through I image the same region of the nucleated crystal at progressively higher magnifications, using bright–field imaging TEM imaging and transmission SEM imaging respectively                               | 40 |

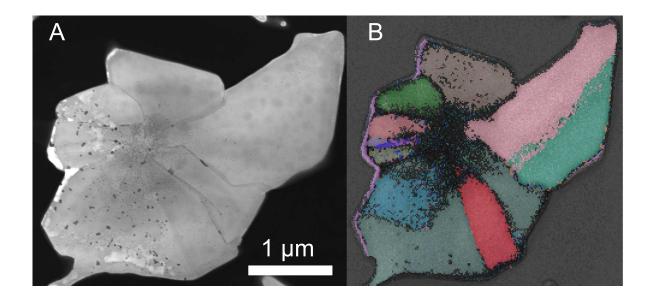

| 1–13 | The faceted crystal of Figure 1–12 which has been mapped using t-EFSD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41 |

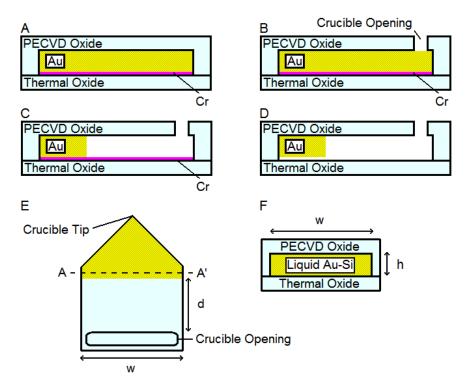

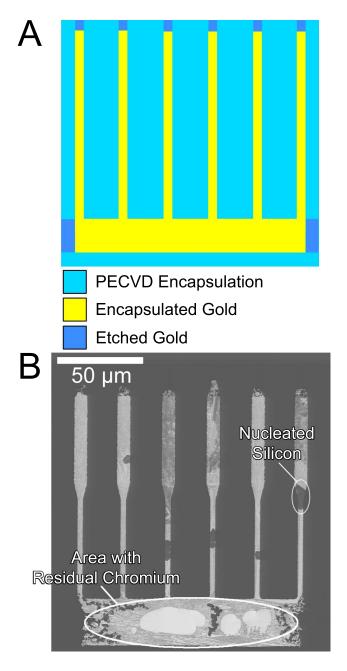

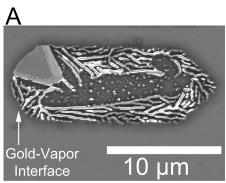

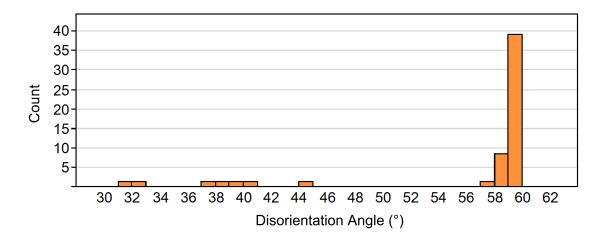

| 3-1  | Structure and fabrication process of micro-crucibles. (A) PECVD oxide encapsulated micro-crucible with film thickness of 150 nm Au and 5 nm Cr. (B) Opening of the micro-crucible using a dry etch. (C) Timed gold etch to control solid gold catalyst amount. (D) H <sub>2</sub> SO <sub>4</sub> etch to remove residual Cr and organics. (E) Planar diagram of finished micro-crucibles with d representing the silane diffuse distance. (F) A cross-section through the dotted line A-A' in Figure 3–1E of the assumed gold-vapor interface where the solid catalyst has transformed into a liquid | 76 |

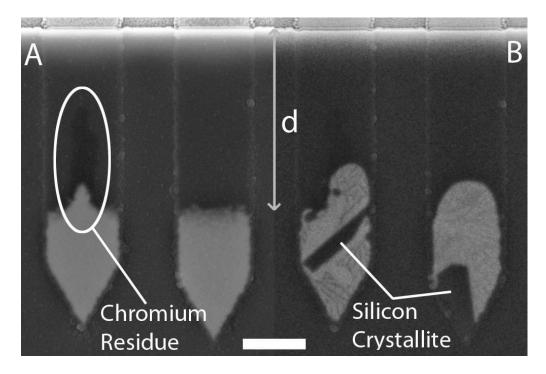

| 3-2  | Secondary electron images of neighboring micro-crucibles before (A) and after (B) the growth step. Dimension d represents the distance the silane diffused within the crucible to reach the gold-vapor                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | interface. The scale bar represents 6 μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80 |

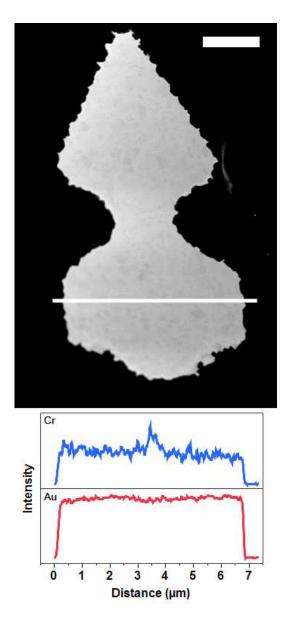

| 3–3 | High—angle annular dark—field (HAADF) image of a micro—crucible before deposition. The white line across the crucible represents the line scanned to determine the Au and Cr EDS profiles. The scale bar represents 2 µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

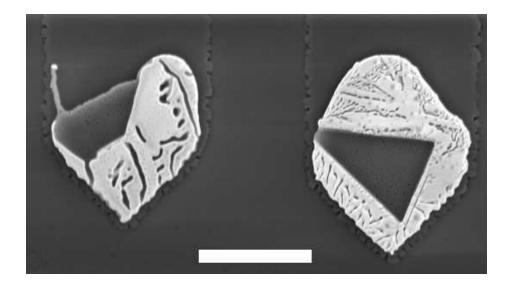

| 3-4 | Secondary electron image of neighboring micro—cubicles with the PECVD oxide encapsulation layer removed. The left and right crucibles display coarse irregular and fine irregular lamella, respectively. The scale bar represents 5 µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83 |

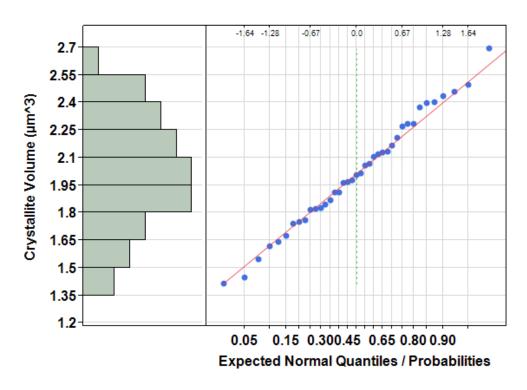

| 3-5 | Histogram and normal quantile (Q–Q) plot of crystallite volume for crystallites nucleated in micro–crucibles with fine eutectic microstructures. The counts from each bin in the histogram can be seen in the vertical divisions of the Q–Q plot. $N=39.\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84 |

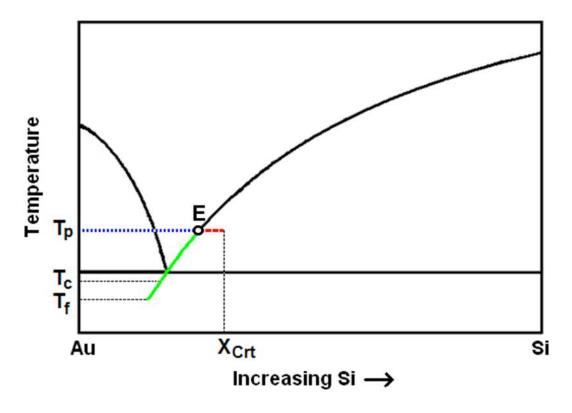

| 3-6 | A schematic of the Au–Si phase diagram which depicts the compositional variations in the micro–crucibles with fine and coarse lamellar structures as they are processed. The dotted blue line represents the gradual increase in Si concentration in the Au catalyst during deposition. The dashed red line represents the additional supersaturation required in the Au–Si liquid solution to nucleate a Si crystallite. The concentration at which a Si crystallite is nucleated is the critical supersaturation ( $X_{\rm crt}$ ). Point E represents the steady state composition after the faceted crystallite phase has nucleated. The solid green line represents the composition of the liquid Au–Si solution as it cools from the processing temperature ( $T_{\rm p}$ ) to its final undercooled temperature. The different temperatures at which the Au–Si liquid solutions solidify with fine and coarse lamella ( $T_{\rm f}$ and $T_{\rm c}$ respectively) and their respective silicon concentrations determine the $\Delta V$ between Si crystallites in micro–crucibles with coarse and fine lamellar morphologies | 87 |

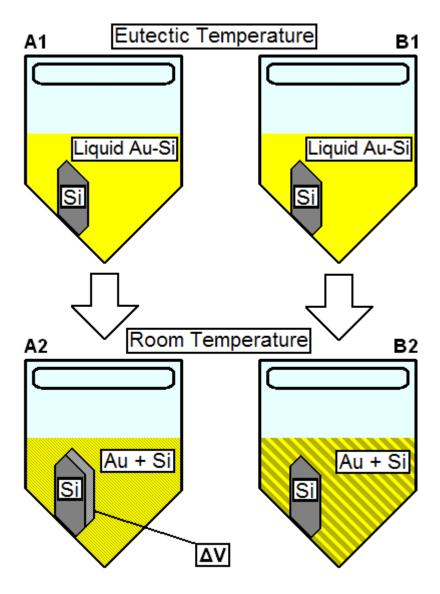

| 3-7 | Diagram of the effects of relative undercooling on silicon crystallite size. The averaged micro-crucible with fine (A) and coarse (B) lamella starts off with the same initial conditions (A1 and B1). Upon cooling, the additional rejected silicon atoms from the more undercooled liquid in the crucible with fine lamella deposit themselves onto the silicon crystallite and give it additional volume $(\Delta V)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90 |

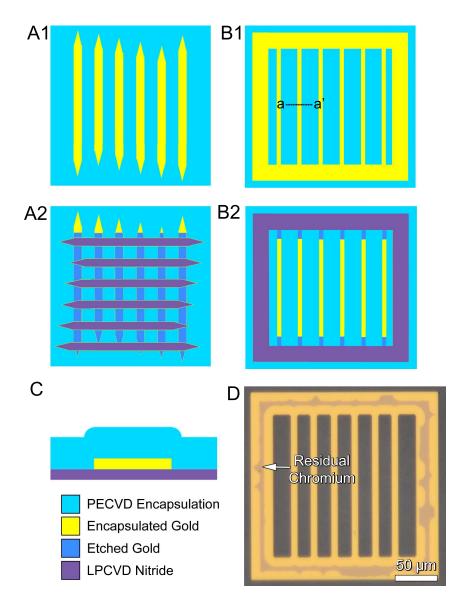

| 3-8    | A1 and A2 are diagrams of the single sided micro-crucible prestructure and of the micro-crucible geometry after the selective removal of gold respectively. B1 and B2 are diagrams of the doubled sided micro-crucible pre-structure and of the micro-crucible geometry after the selective removal of gold respectively. Figure 3–8C is a cross section of the micro-crucible structure at location a–a' as depicted in Figure 3–8B1. Figure 3–8D is an optical image showing the successful undercut etching of Cr from a micro-crucible pre-structure. The residual chromium ring around the central structure secures the gold structure to the amorphous substrate. Figure 3–8D was taken from the backside of a fused silica wafer |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-9 (  | (A) A plan view diagram of the double ended micro-crucible test structure with an altered geometry used for the 475° C, 180 minute growth and (B) a backscattered electron image the results of the growth showing nucleated crystals conforming to the micro-crucible. 104                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

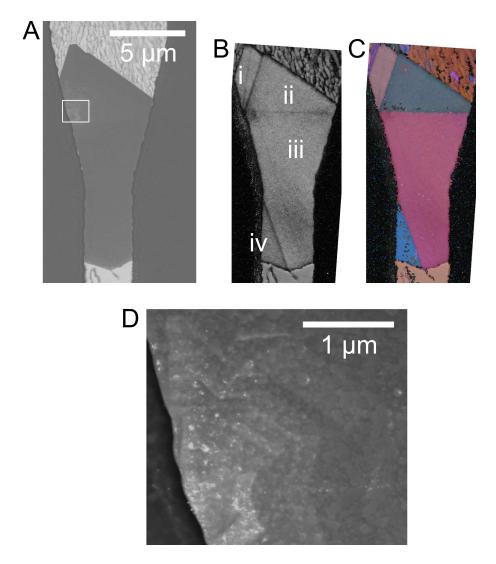

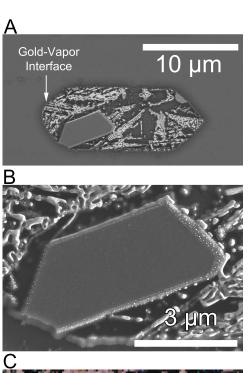

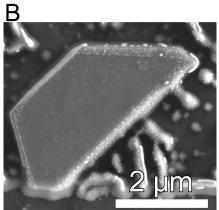

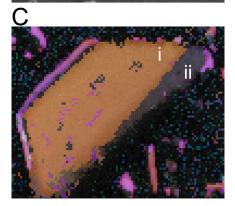

| 3-10 ( | Growth of a faceted silicon phase confined within the micro–crucible circled in Figure 3–9B. Figure 3–10A is backscatter electron micrograph of the region of interest. Figures 3–10B and 3–10C image the twinned silicon growth from 3–10A with an EBSD band contrast map and an EBSD band contrast map overlayed with the Euler angle map respectively. Figure 3–10D is a high magnification image of the area boxed in Figure 3–10A. The orientations of the grains labeled i, ii , iii and iv in Figure 3–10B are slightly off the {2 1 1}, slightly off the {2 1 1}, the {4 1 1} and slightly off the {1 1 0} planes respectively. All angle/axis pairs were found to be $60^{\circ}/\langle 1 1 1 \rangle.106^{\circ}$             |

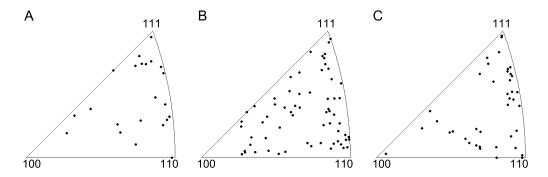

| 3–11 I | nverse pole figures of observed orientation of nucleated silicon crystals with respect to the normal of the substrates for (A) single, (B) potentially twinned and (C) polycrystals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3–12 Typical single crystal growth after 60 minutes of deposition. Figure 3–12A represents twinned growth which formed with a major grain which accounts for the majority of crystal, and a minor grain. Figure 3–12B is a high magnification backscatter image of the nucleated crystal. Figure 3–12C is a composite image of the EBSD band contrast map with the Euler angle map superimposed over it. The orientation of the imaged crystal facet is slightly off from the {3 2 2} plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 109 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3–13 Typical twinned crystal growth after 60 minutes of deposition where one grain is significantly larger than the other. Figure 3–13A is a backscatter electron micrograph depicting the condition of the micro–crucible in which the crystal nucleated. Figure 3–13B is a high magnification backscatter image of nucleated crystal. Figure 3–13C is a composite image of the EBSD band contrast map with the Euler angle map superimposed over it with areas of different colors/shades representing grains of different orientations. The orientations of the larger and smaller twinned grains are the {7 7 1} and sightly off the {10 3 1} planes respectively. Their angle/axis pair was measured to be 60°/(1 1 1)                                                                                                                                                                                                                                                       | 111 |

| 3–14 Typical twinned crystal growth after 60 minutes of deposition where no grain was significantly larger than the others. Figure 3–14A is a backscatter electron micrograph depicting the condition of the micro–crucible in which the crystal nucleated. Figure 3–14B is a high magnification backscatter image of nucleated crystal. Figure 3–14C is a composite image of the EBSD band contrast map with the Euler angle map superimposed over it with areas of different colors/shades representing grains of different orientations. The orientations of the grains labeled i, ii , iii and iv are slightly off the $\{5\ 5\ 1\}$ , the $\{7\ 7\ 1\}$ , slight off the $\{5\ 2\ 2\}$ and the $\{7\ 6\ 5\}$ planes respectively. All angle/axis pairs were found to be $60^\circ/\langle 1\ 1\ 1\rangle$ except between the grains labeled i and ii, which was one of the two $38.9^\circ/\langle 1\ 1\ 0\rangle$ $\Sigma 9$ grain boundaries observed in this experiment 1 | 112 |

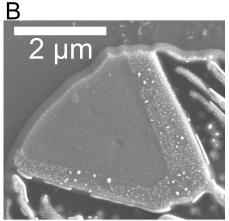

| 3–15 Distribution of disorientation angles between grain boundaries for all observed nucleation events. The $60^{\circ}$ $\Sigma 3$ coherent twin grain boundary was present in the overwhelming majority of observations. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 116 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

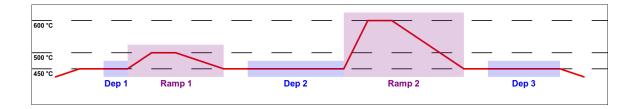

| 122 |

|-----|

| 124 |

| 126 |

| 127 |

| 129 |

| 1   |

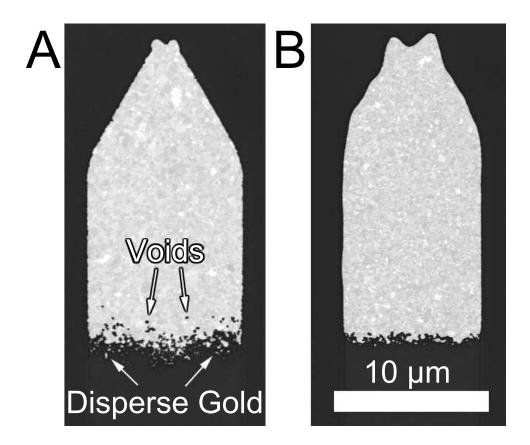

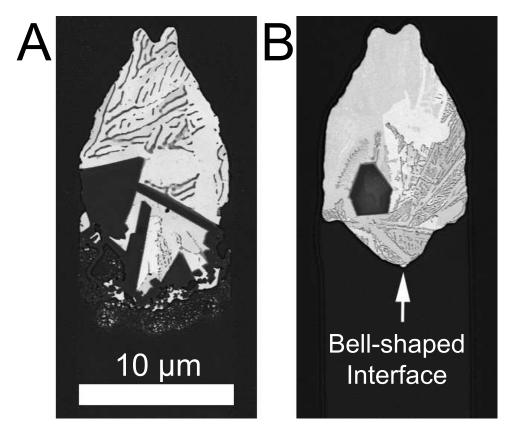

| 3–21 F | aceted silicon phase nucleation and growth in two micro-crucibles with a 150 nm film of Au using 1 nm of Ti as an adhesion layer. Figure 3–21A was not grown with a multi-step deposition process while Figure 3–21B was processed with the thermal treatment depicted in Figure 3–17. The bell-shaped gold-vapor interface was regularly observed in micro-crucibles with Ti adhesion                                                                                                                                                                                                                                                  | 131 |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

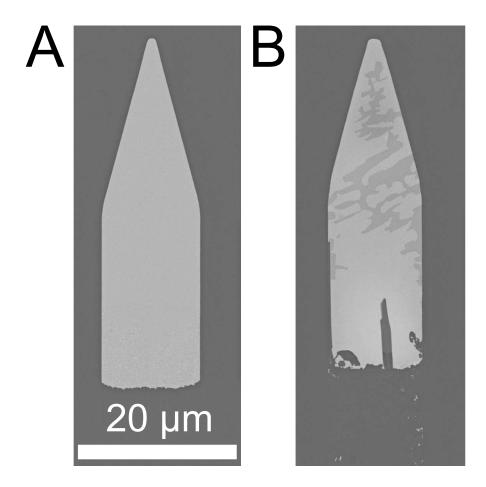

| 3–22 G | Growth in 50 nm Au micro-crucibles using 1 nm of Al as an adhesion layer at 475 °C for 60 minutes in Figure 3–22A and at 425 °C for 180 minutes in Figure 3–22B                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 132 |

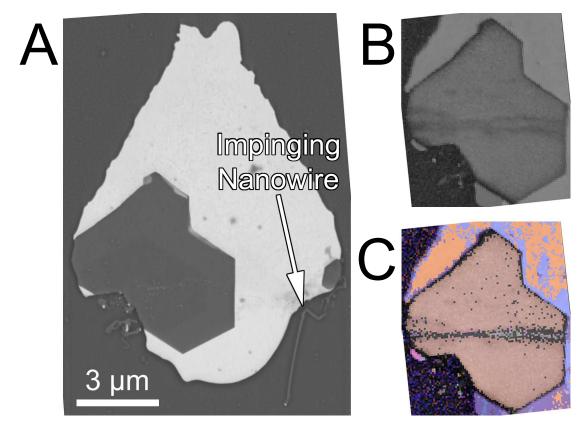

| 3-23 A | a micro-crucible with a 150 nm Au film using 1 nm of Al as an adhesion layer which has had a neck design implemented. Figure 3–23A depicts a faceted silicon crystal which had grown into the neck after 120 minutes of growth at 475 °C. Figure 3–23B is a higher magnification image of the necked growth. Figure 3–23C is an EBSD contrast map of the faceted silicon phase showing that a twinned grain was necked out and Figure 3–23D is a contrast map overlayed with a Euler angle map showing the crystallographic orientations on either sided of the necked out grain are the same orientation                               | 134 |

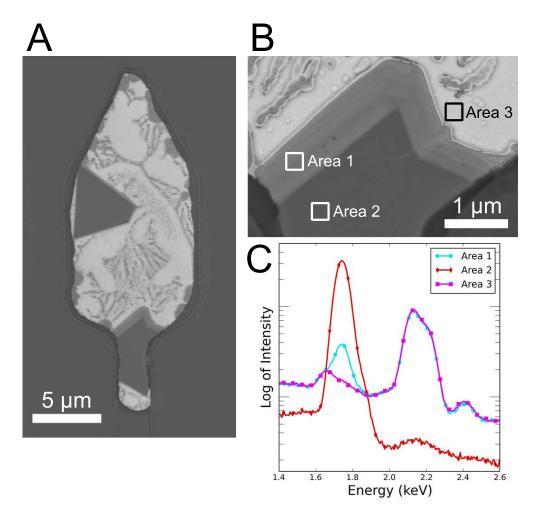

| 3-24 B | Backscatter micrographs and EDS scans of a 150 nm Au film in a crucible using 1 nm of Al as an adhesion layer which had nucleated a faceted silicon phase. Figure 3–24A depicts a faceted silicon crystal growth which occurred after 120 minutes at 475 °C. A potential third gray phase (labeled Area 1 in Figure 3–24B) was regularly observed in micro–crucibles which used Al as an adhesion layer. An EDS (Figure 3–24C) scan of the faceted silicon phase (Area 2), the gold–silicon alloy which had solidified (Area 3) and the gray area revealed that the gray area contains EDS peaks for both Si (1.74 kV) and Au (2.13 kV) | 135 |

|        | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

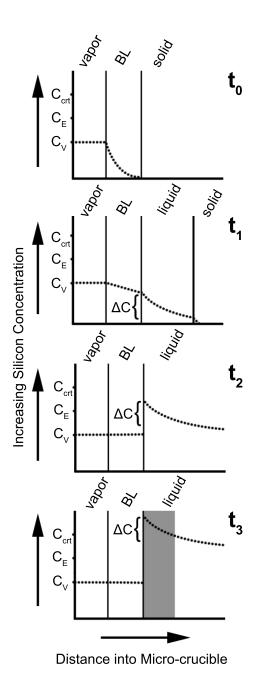

| 3–25 Diagrams of the evolution of the silicon concentration versus distance into the micro–crucible from the gold–vapor interface. At $t_0$ the vapor phase has a constant concentration ( $C_V$ ) and silane has yet to react with the catalyst. At $t_1$ the silane has diffused across the boundary layer (BL) and cracked at the surface of the catalyst. A solid–liquid interface has formed where the concentration of the silicon in the gold catalyst is greater than zero, and a silicon concentration gradient ( $\Delta C$ ) can be measured between the gold–vapor interface and the farthest distance the silicon has diffused into the liquid phase. At $t_2$ the entire gold catalyst has transformed into a gold–silicon alloy and the silicon concentration at the gold–vapor interface is greater than the silicon liquidus equilibrium concentration ( $C_E$ ), thus making it thermodynamically favorable to nucleate a faceted silicon phase there. At $t_3$ the area in the gray box has a concentration above one of the critical supersatruation |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| concentrations ( $C_{crt}$ ) required for a heterogeneous nucleation event. It is in the region defined by this gray box that a faceted silicon phase will first nucleate and grow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| phase will first flucteate and grow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 140 |

| 3–26 A micro–crucible with a 150 nm Au film utilizing 1 nm of Ti as an adhesion layer that was grown at 450 °C for 180 minutes. Figure 3–26A images faceted silicon growth which occurred at the gold–vapor interface due to a large silicon concentration gradient ( $\Delta$ C) present in the micro–crucible, and subsequent nanowire growth due to the gold–silicon interface becoming unstable and breaking up into discontinuous gold catalysts. Figure 3–26B depicts the silicon concentration profile needed to produce results similar to Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 3–26A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 147 |

## CHAPTER 1 Research Motivations and Literature Review

With the ever increasing demands for digitization, automation, telecommunication and energy production witnessed in the past half century, there is an impetus for the development of semiconducting materials and a mandate from modern societies to have scientists and engineers research new methodologies and establish new techniques to provide for these demands. Through the use of semiconductors, unimaginable progress in all fields of science and technology have been made, resulting in what is collectively known as the digital or information age. Developing processes which produce larger, higher quality semiconductor crystals at lower costs is the foundation on which this continuous technological progression sits, and in this work, a novel semiconductor growth process will be outlined with a potential to bring new applications to classes of semiconducting materials which have been traditionally been perceived as being too expensive for mass production.

The semiconducting material which has defined this digital age has been silicon grown using the Czochralski process [1]. Because of the low cost and the robustness of the process, boules of high–quality silicon are grown to diameters 450 millimeters commercially. These boules grown by the Czochralski process are diced into silicon wafer substrates for the current generation of complementary metal–oxide–semiconductor (CMOS) technologies, with which the majority of modern microelectronic devices are fabricated. Because the cost of silicon is essentially fixed due it

its abundance on Earth, Dr. Gordon Moore [2] made the economic prediction in 1965 that, for a given manufacturing cost, the only way to lower the price of a silicon microelectronic good is to fabricate more of it over a given substrate size. This prediction has been the business model of the integrated circuit industry since, and has resulted in the miniaturization of silicon microelectronics by orders of magnitude over the previous decades. Because there is a marginal cost difference, namely in the capital equipment investment, between fabricating one hundred integrated circuits on a 100 millimeter substrate and one thousand integrated circuits on a 450 millimeter substrate, reliable production of larger crystals and thus larger substrates has been as important as miniaturization with regards to the cost reduction of silicon microelectronic goods.

Unfortunately not all semiconducting materials of technological interest can be produced with the low cost Czochralski process, particularly the one which hold the most promise for photovoltaic, telecommunications, optics and laser applications. Typically, the III–V and II–IV semiconductors required for these applications are grown using more expensive processes like vapor–phase epitaxy (VPE) or metalorganic vapor–phase epitaxy (MOVPE) on latticed mismatched substrates like gallium arsenide or germanium, which themselves are grown using more expensive, less mass–producible processes [3]. The defects and impurities associated with VPE and MOVPE [4], as well as the dislocations associated with growth on lattice matched substrates [5] [6] [7] [8] makes commercial production of III–V and II–IV semiconductors significantly more difficult and expensive, and the current state–of–the–art for

these technologies limits the size of substrates which can be used. The difficulties associated with growing non–silicon high–quality crystals for semiconductor substrates and the limited producible substrate sizes for these materials drives up the costs of photovoltaic, telecommunications, optics and laser devices.

Currently, the majority of commercially produced, high-quality semiconducting substrates are grown using variations on the Czochralski or Bridgman-Stockbarger processes [9] [10], or with vapor phase epitaxy using either chemical vapor deposition (CVD) or molecular beam epitaxy (MBE). However, research on how to integrate high-quality growth onto preexisting, low cost substrates like Czochralski grown silicon or glass has been attempted since the beginning of microelectronics miniaturization, and relevant to this research is a technique known as epitaxial layer overgrowth (ELO) [11]. Using ELO, a high-quality, semiconducting thin-film is grown over a seeding substrate which is masked using an amorphous thin-film. Originally the semiconducting thin-films were seeded using homoepitaxy, that is from a substrate which is chemically and crystallographically the same as the thin-film growing over the amorphous layer, but once heteroepitaxy techniques were developed [12], ELO became a much more versatile and cost effective way to integrate high-quality growth on to inexpensive substrates. The vapor-liquid-solid (VLS) technique, first reported by Wagner and Ellis in 1964 [13], is another integrable growth technique which yields high-quality semiconductor crystals on inexpensive substrates and has received considerable amounts of attention with the realization that VLS growth is a key enabler of nanotechnologies [14]. The VLS technique is the primary inspiration for the research presented in this work and the understandings of the process will

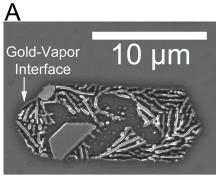

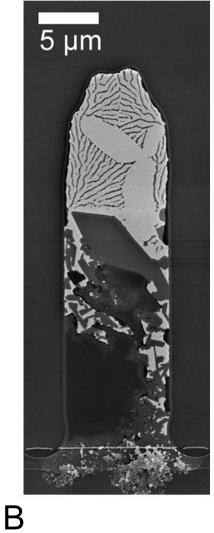

Figure 1–1: Plan (A), isometric (B) and cross–sectional views (C) of the micro–crucible structure used to experimentally produce high–quality semiconducting crystals. A gold catalyst is located at the tip of the micro–crucible, and opening opposite the tip allows gaseous semiconducting precursors to diffuse to the catalyst and preferentially crack at its surface, thus resulting in a VLS reaction and crystal growth within the crucible.

be discussed at length in Section 1.2. Most recently there has been a push in the research to develop spatially controlled, confined growth [15], and lateral growth [16], i.e. growth parallel to the substrate, of high–quality semiconducting materials using techniques which synthesize the lessons learned from the ELO, VLS and Bridgman–Stockbarger techniques, and it is here where this research attempts to contribute original knowledge to the field.

Figure 1–2: A plan–view backscatter electron micrograph of three neighboring micro–crucibles, the middle and rightmost crucibles have nucleated semiconductor crystals during a CVD process using the VLS technique. The crystals are confined to morphology of the amorphous micro–crucible and grow laterally as they grow larger.

To investigate the lateral growth of spatially controlled, semiconducting thinfilms, an amorphous template has been designed and fabricated using CMOS technologies on thermally oxidized silicon and glass substrates. The amorphous template used in this work has been termed a micro-crucible, as it functions much like the crucibles used for the Bridgman-Stockbarger technique, but its dimensions are on the order of microns. Figure 1–1 depicts a plan-view (A), isometric view (B), and crosssectional view (C) of the typical micro-crucible geometry. These micro-crucibles promote growth in spatially controlled, confined areas on the substrate by taking advantage of VLS research, and selectively depositing a gold catalyst at the microcrucible tip, marked in Figure 1–1. Allowing a gaseous semiconductor precursor to diffuse, using a CVD process, to the catalyst through the opening in the microcrucible causes the vapor-liquid-solid process to occur within the crucible and results in the nucleation of a high-quality semiconducting crystal. Unlike the vapor-liquidsolid growth associated with nanowire research, the semiconducting crystals grown within micro-crucibles, as imaged in Figure 1-2, nucleated from critically supersaturation solutions, where there is enough free energy in the solution to over come the energy barriers associated with forming the solid-liquid phase boundary of the new phase [17] [18] [19]. The newly nucleated crystals are grown laterally, within the micro-crucible, over the amorphous substrate as long as the CVD process continues and the crystals can be engineered into a number of morphologies defined by the confining structure. It is in this work that questions on micro-crucible fabrication, diffusion of semiconductor species within the micro-crucible, nucleation and growth of high–quality semiconductor crystals within micro–crucibles, and crystalline defections associated with VLS growth in micro–crucible will be addressed.

A larger goal of this work is to provide a technological platform, which lowers the cost of production of III–V and II–IV semiconductor substrates, particularly for photovoltaic applications. To enable third-generation photovoltaic technologies [20], high-quality thin-films of germanium, gallium arsenide and its allied III-IV compounds need to be produced cheaply to maximize solar energy conversion and minimize cost. This can be done using multi-junction solar cells, but in order to fabricate multi-junction, III-V solar cells, lattice matched substrates of germanium and gallium arsenide are used to mitigate the conversion-lowering effects of latticemismatched dislocations and grain boundaries. These substrates are expensive and the technology using them does not convert solar electricity at prices which are competitive with traditional energy sources used for large scale electric grids. Semiconductor growth using the VLS process and amorphous micro-crucibles is potentially enabling because high-quality semiconducting seeds are produced without the need of an expensive seeding substrate, and substrates such as glass, which is inexpensive and the substrate of choice for current thin-film photovoltaic manufacturers, are easily integrated into the micro-crucible fabrications process. Ideally, semiconducting silicon crystals grown in micro-crucibles will be used to seed larger crystals grown from VPE and MOVPE processes to produce substrates similar to the one depicted in Figure 1–3, where a large grained III–V substrate has been seeded by micro-crucible grown crystals over an amorphous silicon oxide thin-film. Outside of photovoltaics and in more traditional integrated circuit technologies, semiconducting films grown

Figure 1–3: A larger goal of this work is to provide a technology which lowers the cost of high efficiency photovoltaics. Here a large grained GaAs substrate is depicted as being produced by thermally oxidizing a silicon substrate, fabricating micro–crucibles (not pictured) on the substrate, and growing GaAs seeds in the micro–crucibles using the VLS process. The seeded substrate is placed into a VPE or MOVPE deposition process where the larger GaAs grain pictures in Figure 1–3A nucleate at sites where the previously grown micro–crucible seeds were located. After nucleating, the larger GaAs grains grew laterally over the amorphous silicon oxide substrate until covering the entire surface and impinging one another.

laterally from micro–crucibles can be used to enable optical interconnects, three–dimensional transistors and silicon/III–V on–chip integration.

#### 1.1 Gold-Silicon Research and Technology

The history of integrating gold into semiconducting materials is as old as the first point contact transistor [21]. Indeed the first metal contacts on that germanium transistor were gold, most likely due the widespread use of gold in the laboratory. Owing to its nobility, its ease of forming, its ease of purifying, its good conductivity and its heat conduction properties, gold is typically the first material used when an experiment calls for a "metal". Unfortunately for silicon microelectronics, gold acts as a deep–level electronic defect between the valence and the conduction bands of the silicon band gap, which reduces electron minority carrier lifetimes and inhibits electron mobility in the material and thus leaves gold unusable for commercial applications of silicon semiconducting technologies. This has not inhibited the use of gold and silicon with regards to fundamental research and growth studies, which is fortunate as gold and gold–silicon alloys offer some unique advantages to this field.

Figure 1–4 is an equilibrium gold–silicon phase diagram where the x–axis is taken to be the atomic percent of silicon in the gold–silicon alloy. The gold–silicon system is a simple binary with limited solid–state solubility of both gold in silicon and silicon in gold. Thermodynamic investigations of the gold–silicon system [22] [23] [24] [25] [26] [27] suggests insignificant solubility of gold in silicon, with exception to concentrations which effect the electrical properties of silicon. Silicon in gold is less studied and upwards of 2% silicon solubility [22] [27] could be possible, but has not been experimentally reported. In addition to the limited solid–state solubility of gold in silicon and silicon in gold, the gold–silicon systems lacks thermodynamically stable

Figure 1–4: Equlibrium Au–Si phase diagram in atomic percent with the relevant temperatures and compositions labeled.

gold silicide intermediate phases [22], which simplifies metallurgical analysis of solidified gold–silicon alloys further. Desirable to gold–silicon research and technology is the significant reduction of gold (1064 °C) and silicon (1414 °C) melting temperatures to the eutectic melting temperature (363 °C) when alloyed. This low eutectic temperature is one of the key advantages of VLS process and a motivation for its integration into microelectronic technologies. Other alloys like aluminum–silicon, silver–silicon, gold–germanium, aluminum–germanium and silver–germanium are analogous [28], but none posses the lack of solid–state solubility, lack of thermodynamically stable intermediate phases and the significant reduction in melting temperature that gold–silicon does. These properties coupled with nobility, malleability and purity of gold have made gold–silicon alloys a relevant and well studied material system.

Many properties of the gold–silicon system can be inferred from the analogous, more rigorously studied aluminum–silicon system, which aids and complements gold–silicon research. While studies on grain refinement, mechanical processing and thermal processing of aluminum–silicon alloys are less useful, as gold–silicon is not a structural material, work on microstructure characterization [29] [30], directional solidification [31] [32] [33], microstructure alteration via micro–alloying additions [34] [35] [36], and primary phase nucleation [37] [38] [39] have been useful when interpreting the gold–silicon microstructures analyzed in this work. Fundamental phenomenon such as rapid solidification/glass formation [40] [41] [42] [43], short–range order in liquids [44] [45] and thin–film surface energetics [46] [47] are often studied using the gold–silicon system because of its favorable qualities, and the ease of

using technologies adopted from semiconductor electronics industry to study these materials.

Gold-silicon interfaces are used as the prototypical interface to study the unique atomic interactions between metals and semiconductors. Metal-induced crystallization (MIC) [48] [49] [50] [51] is a commercially adopted technique to produce high-quality, large grain polycrystalline silicon thin-films which takes advantage of a unique semiconductor-metal interface phenomenon. The MIC process utilizes the ability of silicon to diffuse through gold and other metal layers, normally via grain boundary diffusion [52] [53] [54] [55], at room temperature to a free surface on the other side of the metal (Figure 1–5). When this diffusion occurs through the gold and other metal layers in vacuum, the silicon forms a polycrystalline silicon film which isolates the metal layer from the free surface. This polycrystalline film can be engineered to have a large grain structure and is useful for integrating silicon films fabricated in this method into CMOS processes. When this diffusion occurs through gold and other metal layers in atmosphere, the silicon at the surface will react with oxygen and form a silicon oxide film [56] [57] [58] [59], potentially microns thick, which isolates the metal layer from the atmosphere. The formation of silicon oxide at gold-atmosphere interfaces has been observed in this work for micro-crucible grown silicon which had been exposed to atmosphere after the growth step.

From a technological standpoint, gold is not used in commercial MIC processes due to the detrimental effect it has on electron mobility in silicon, and aluminum is normally used instead. Eutectic bonding is a commercial technology which takes advantage of the the gold—silicon system [60] [61] [62]. Because of the lower eutectic

Figure 1–5: Gold–silicon interface where a single crystal of silicon film (c-Silicon), a polycrystalline silicon film (Polysilicon) or a amorphous silicon film (a-Silicon) has diffused across a gold thin–film to the free surface at room temperature. In vacuum, the diffused silicon forms a polycrystalline silicon film at the free surface, on top of the gold film. In atmoshpere, the diffused silicon forms a silicon oxide film at the free surface, on top of the gold film.

temperature of gold—silicon, which is attractive for thermal budget management of integrated circuits, eutectic bonding of gold and silicon thin—films is used when two substrates need to be bonded together, typically for microelectromechanical systems (MEMS) and flip—chips. Also relevant to gold—silicon technology are the nanostructures grown by the vapor—liquid—solid method with gold—silicon catalyst. While not fully commercialized, precision control of nanowires remains a goal for the international technology roadmap for semiconductors, and gold—silicon the research is the foundation on which nanowires are understood.

## 1.2 Vapor-Liquid-Solid Nanowires

Fundamental to this work is the pioneering research on the vapor-liquid-solid growth done by Wagner and Ellis [13] at Bell Labs in 1964. Their work [63] [64] [65] is the most analogous and comprehensive study on VLS growth using gold-silicon systems which are not at the nano-scale. The most useful reference on understanding and controlling micro-scale VLS growth, which is what occurs when silicon is grown in micro-crucibles, is Wagner's chapter in A. P. Levitt's Whisker Technology [66] published in 1970. The contribution sums up the earlier published results of Wagner, as well as demonstrates common defects associated with the growth mechanism and their root causes. The majority of the work by Wagner and Ellis quantified and qualified silicon wires grown using a gold catalyst from silicon {1 1 1} substrates, although Ellis went on to do the some of the initial work on III-V VLS growth [67], which did not mature as a field to the level of the original silicon VLS work until the 1990s [68] [69].

Figure 1–6 describes the basic growth mechanics observed during the initial VLS experiments. Figure 1–6A is of a silicon {1 1 1} wafer which has been cleaned of all native silicon oxide, after which some gold has been patterned on top by any number of deposition techniques, including: electron beam induced deposition [70], effusion cell evaporation [71] [72] [73], thermal evaporation [74] [75] [76], gold nanoparticle colloid deposition [77] [78] [79] [80] [81] [82], ion implantation [83], plasma sputtering [84] [85], and electron beam evaporation [86]. The patterned gold on the oxide–free silicon {1 1 1} substrate is heated to gold–silicon eutectic temperature, at which the silicon substrate and pattered gold liquefy, forming a gold–silicon liquid alloy

Figure 1–6: (A) A Si {1 1 1} wafer which has had its native oxide layer removed and a thin Au film deposited on to its surface. (B) The Si wafer has been heated above the Au–Si eutectic temperature and the Au film has formed a liquid Au–Si alloy with Si dissolved from the substrate. (C) A gaseous Si precursor (SiH<sub>4</sub>) has been introduced to the wafer, which preferentially cracks at the gold–vapor interface and deposits Si atoms into the Au–Si alloy. The alloy supersaturates and deposits the excess Si atoms on the silicon wafer on which it sits. A highly crystalline Si wire grows from underneath the Au–Si alloy as more Si is deposited into the Au–Si alloy.

as depicted in Figure 1–6B. The liquid gold–silicon alloy takes the composition for which it is in thermodynamic equilibrium for a given temperature, and the substrate is etched back slightly to provide silicon for the liquid alloy. A gaseous silicon precursor, typically silane (SiH<sub>4</sub>) for modern studies but in the original work it was silicon tetrachloride (SiCl<sub>4</sub>), is introduced to the liquid gold-silicon alloy through a CVD process, as depicted in Figure 1–5C, and the silicon precursor preferentially cracks at the liquid alloy surface, dissolving the gaseous silicon into the liquid gold-silicon. The increase in concentration in the liquid gold-silicon is not in equilibrium with the processing conditions, and it is thermodynamically favorable for the supersaturated gold-silicon alloy to reject its excess silicon. This rejected silicon finds its lowest energy configuration at the crystalline silicon surface on which the gold-silicon alloy rests, and redeposits itself there in a manner which is highly ordered and free of dislocation defects. Because the deposited silicon starts in the vapor phase, transforms into a liquid intermediate and is incorporated into a highly crystalline solid, the vapor-liquid-solid method was given its appropriate name. Silicon is continuously deposited at the liquid-solid interface of the alloy and the crystal as long as the CVD process continues, and a wire-like crystal grows up from the substrate in a one-dimensional fashion with a hemispherical metal catalyst at its tip, because the surface tension between the alloy and the crystals does not allow the allow the metal catalyst to wet the surface. Interesting to note is the difference between the initial VLS studies and the more modern ones, where the choice in gaseous precursor not only effects the temperatures at which the VLS process takes place, but the residual products of the gas decomposition reactions, such as HCl and Cl<sub>2</sub> for SiCl<sub>4</sub>, appeared to have etched VLS catalysts [87] [88] during the CVD process.

The initial VLS research also noted that metal catalyst other than gold could be used [13], but much of the following VLS work continued to use gold as the predominate catalyst, as it has a very large processing temperature range at which controllable VLS growth will occur, in addition to the other desirable characteristics mentioned in Section 1.1. The other catalysts known to successfully grow silicon wires using the VLS technique have been reported as follows: platinum [89] [13] [90], palladium [91] [13] [90], silver [91] [89] [13], aluminum [88] [92] [93], nickel [94] [89] [90], iron [14] [63], copper [91] [89], gallium [87] [95] [88], indium [87] [96] [97], and tin [97]. Interesting for gallium, indium, and tin, which have low melting points and would appear to be ideal candidates for low temperature VLS growth, is that they are reported to be dependent on the experimental CVD conditions for successful growth [91] [71]. In the case of indium, silicon nanowires have been grown successfully at 900 °C - 1050 °C using SiCl<sub>4</sub> [87], and with plasma-enhanced chemical vapor deposition (PECVD) assisted growth at 300 °C - 500 °C using SiH<sub>4</sub> [97] [96] [98], but unsuccessful using SiCl<sub>4</sub> at 800 °C [91] and at 550 °C using physical vapor deposition of silicon [71]. Gallium, indium, and tin all share a particular phase diagram type with silicon [99] [100] [101], where the eutectic composition of the respective alloys is very close to pure gallium, indium and tin. With no reasonable concentration range where both silicon and the respective low melting temperature solvents are fully miscible in the liquid phase, it is entirely possible that the vaporliquid-solid transformations cannot occur at sufficiently low temperatures for these catalysts, and VLS growth needs to occur at temperatures where both species are miscible in the liquid phase for a sufficiently large concentration range, as observed with the indium used in gallium arsenide [102] and germanium [103] nanowire growth at  $500\,^{\circ}\text{C}$  -  $550\,^{\circ}\text{C}$ .