# Data Conversion in Residue Number System

Omar Abdelfattah

Department of Electrical & Computer Engineering McGill University Montreal, Canada

January 2011

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Master of Engineering.

#### Abstract

This thesis tackles the problem of data conversion in the Residue Number System (RNS). The RNS has been considered as an interesting theoretical topic for researchers in recent years. Its importance stems from the absence of carry propagation between its arithmetic units. This facilitates the realization of high-speed, low-power arithmetic. This advantage is of paramount importance in embedded processors, especially those found in portable devices, for which power consumption is the most critical aspect of the design. However, the overhead introduced by the data conversion circuits discourages the use of RNS at the applications. In this thesis, we aim at developing efficient schemes for the conversion from the conventional representation to the RNS representation and vice versa. The conventional representation can be in the form of an analog continuous-time signal or a digital signal represented in binary format. We present some of the currently available algorithms and schemes of conversion when the signal is in binary representation. As a contribution to this field of research, we propose three different schemes for direct conversion when interaction with the real analog world is required. We first develop two efficient schemes for direct analog-to-residue conversion. Another efficient scheme for direct residue-to-analog conversion is also proposed. The performance and the efficiency of theses converters are demonstrated and analyzed. The proposed schemes are aimed to encourage the utilization of RNS in various real-time and practical applications in the future.

#### Résumé

Cette thèse aborde le problème de la conversion de données dans le système numérique de résidus (Residue Number System - RNS). Le système RNS a été considéré comme un sujet intéressant par de nombreux chercheurs ces dernières années. Son importance découle de l'absence de la propagation de retenue entre ses unités de calcul. Ceci facilite la réalisation de circuits arithmétiques à grande vitesse et de faible puissance. Cet avantage est d'une importance primordiale dans les processeurs embarqués, en particulier ceux qu'on retrouve dans les appareils portables, pour lesquels la consummation d'énergie est l'aspect le plus critique de la conception. Cependant, le traitement supplémentaire introduit par les circuits de conversion de données décourage l'utilisation du RNS au niveau des applications. Dans cette thèse, nous cherchons des schémes efficaces pour la conversion de la représentation conventionnelle à la représentation RNS et vice-versa. La représentation conventionnelle peut être sous la forme d'un signal analogique en temps continu où d'un signal échantillonné numérique représenté en format binaire. Nous présentons quelques algorithmes actuellement disponibles et les systèmes de conversion associés lorsque le signal est sous une représentation binaire. Dans notre contribution à ce domaine de recherche, nous proposons trois astuces différentes pour la conversion lorsqu'une interaction avec le monde analogique réel est nécessaire. Nous dévelopons deux systèmes efficaces pour la conversion directe du domaine analogique à RNS. Un autre système efficace pour la conversion directe de RNS à analogique est également proposé. La performance et l'efficacité de ces convertisseurs sont mises en évidence et analysées. Les schémas proposés sont destinés à encourager l'utilisation du RNS dans diverses applications dans l'avenir.

#### Acknowledgements

I would like to express my gratitude to the following people who supported and encouraged me during this work. First, I am grateful to my supervisors, Zeljko Zilic and Andraws Swidan, for giving me full independence and trust till I reached to this research topic and then for their unlimited assistance throughout my research toward my Master degree. Second, I would like to thank all my talented friends in Integrated Microsystems Laboratory (IML) and Microelectronics And Computer Systems (MACS) Laboratory for their help and guidance and for providing the friendly atmosphere that encouraged me in my daily progress. I would like also to thank all the professors who taught me in my undergraduate study in Kuwait University and in my graduate career in McGill University. Special thanks go to my parents, the reason that I exist, and to my sister who offered me all help and support during writing this thesis. I cannot adequately express my gratitude to all those people who made this thesis possible.

# Contents

| 1 | Intro | oducti | on                                                                 | 13 |

|---|-------|--------|--------------------------------------------------------------------|----|

|   | 1.1   | Thes   | is Motivation                                                      | 14 |

|   | 1.2   | Mair   | n Contributions of This Work                                       | 15 |

|   | 1.3   | RNS    | Representation                                                     | 15 |

|   | 1.4   | Matl   | nematical Fundamentals                                             | 18 |

|   | 1.    | 4.1    | Basic Definitions and Congruences                                  | 18 |

|   | 1.    | 4.2    | Basic Algebraic Operations                                         | 19 |

|   | 1.5   | Conv   | version between Conventional Representation and RNS Representation | 23 |

|   | 1.6   | Adva   | antages of RNS Representation                                      | 24 |

|   | 1.7   | Drav   | vbacks of RNS Representation                                       | 25 |

|   | 1.8   | Appl   | lications                                                          | 26 |

| 2 | Con   | versio | on between Binary and RNS Representations                          | 27 |

|   | 2.1   | Forw   | vard Conversion from Binary to RNS Representation                  | 28 |

|   | 2.    | 1.1    | Arbitrary Moduli-Set Forward Converters                            | 28 |

|   | 2.    | 1.2    | Special Moduli-Set Forward Converters                              | 33 |

|   | 2.    | 1.3    | Modulo Addition                                                    | 37 |

|   | 2.2   | Reve   | erse Conversion from RNS to Binary Representation                  | 44 |

|   | 2.    | 2.1    | Chinese Remainder Theorem                                          | 44 |

|   | 2.    | 2.2    | Mixed-Radix Conversion                                             | 47 |

| 3 Convers | sion between Analog and Binary Representations     | 51  |

|-----------|----------------------------------------------------|-----|

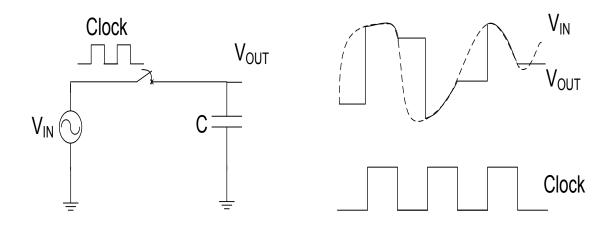

| 3.1 Sar   | mpling                                             | 52  |

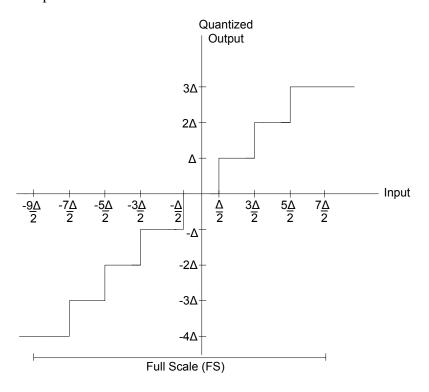

| 3.2 Qu    | antization                                         | 53  |

| 3.3 An    | alog-to-Digital Converter Architectures            | 60  |

| 3.3.1     | Flash (or parallel) ADC                            | 60  |

| 3.3.2     | Interpolating Flash ADC                            | 62  |

| 3.3.3     | Two-Stage Flash ADC                                | 63  |

| 3.3.4     | Multi-Stage Pipelined ADC                          | 64  |

| 3.3.5     | Time-Interleaved ADC                               | 64  |

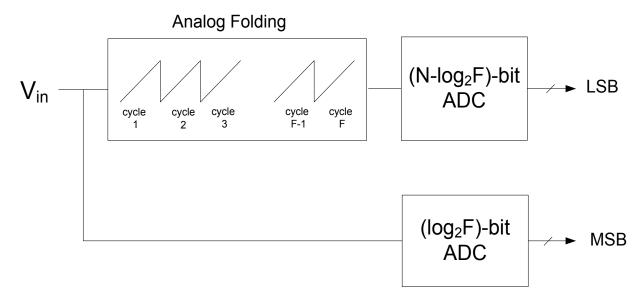

| 3.3.6     | Folding ADC                                        | 65  |

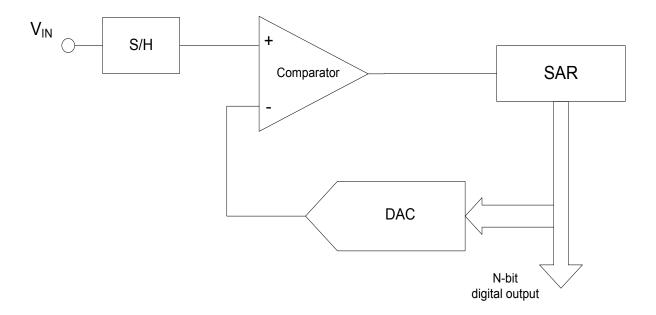

| 3.3.7     | Successive Approximation ADC                       | 66  |

| 3.3.8     | Summary Comparison                                 | 68  |

| 3.4 Dig   | gital-to-Analog Converter Architectures            | 69  |

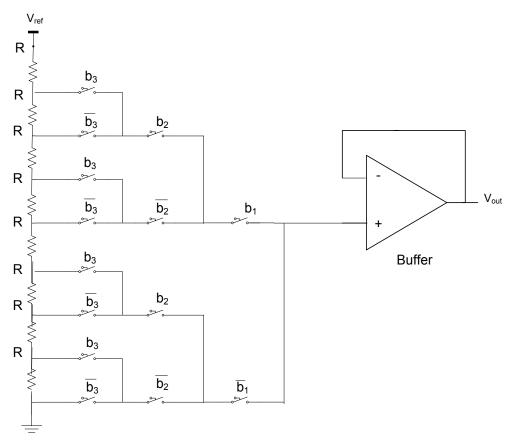

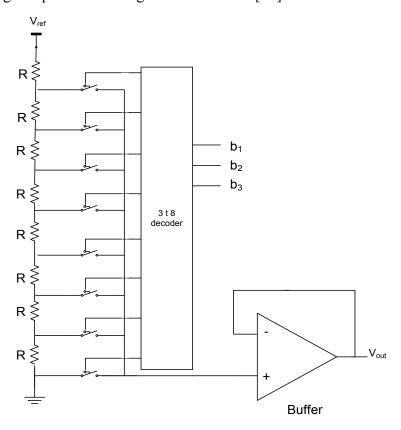

| 3.4.1     | Decoder-based DAC                                  | 69  |

| 3.4.2     | Binary-scaled DAC                                  | 70  |

| 3.4.3     | Thermometer-code DAC                               | 71  |

| 4 Convers | sion between Analog and RNS Representations        | 73  |

| 4.1 For   | rward Conversion from Analog to RNS Representation | 74  |

| 4.1.1     | Flash A/R Converter                                | 74  |

| 4.1.2     | Successive Approximation A/R Converter             | 89  |

| 4.1.3     | Folding A/R Converter                              | 94  |

| 4.2 Re    | verse Conversion from RNS to Analog Representation | 96  |

| 4.2.1     | MRC based R/A Converter                            | 96  |

| 4.2.2     | CRT based R/A Converter                            | 98  |

| 5 Conclus | ion and Future Work                                | 102 |

| References |     |

|------------|-----|

| Appendix I | 112 |

# List of Figures

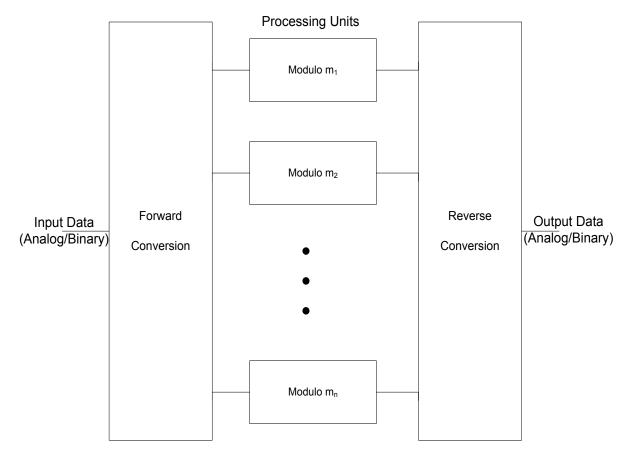

| 1.1  | General structure of an RNS processor                    | 14 |

|------|----------------------------------------------------------|----|

| 2.1  | Serial forward converter                                 | 30 |

| 2.2  | Modified structure for serial forward converter          | 30 |

| 2.3  | Parallel forward converter                               | 31 |

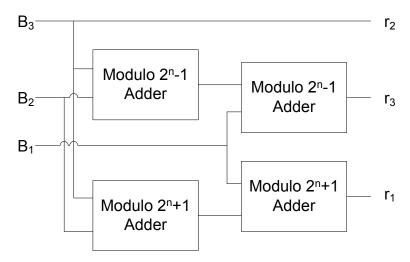

| 2.4  | $\{2^n - 1, 2^n, 2^n + 1\}$ forward converter            | 37 |

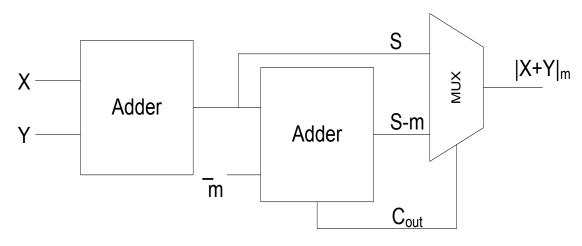

| 2.5  | Modulo- <i>m</i> adder                                   | 38 |

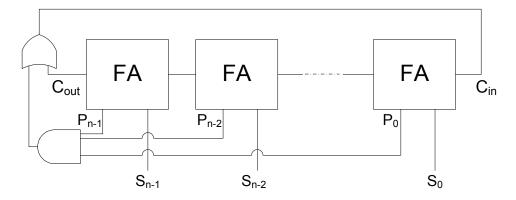

| 2.6  | Modulo $2^n - 1$ adder                                   | 41 |

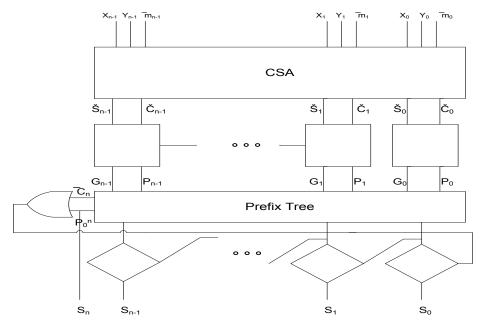

| 2.7  | Modulo $2^n + 1$ adder                                   | 43 |

| 2.8  | CRT based R/B converter                                  | 47 |

| 2.9  | MRC based R/B converter ( <i>n</i> =5)                   | 50 |

| 3.1  | Periodic sampling process                                | 52 |

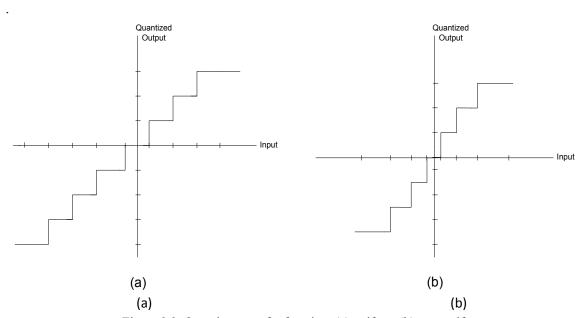

| 3.2  | Transfer function of a typical quantizer                 | 53 |

| 3.3  | Quantizer transfer function: (a) uniform (b) non-uniform | 54 |

| 3.4  | Quantizer transfer function: (a) midtread (b) midrise    | 55 |

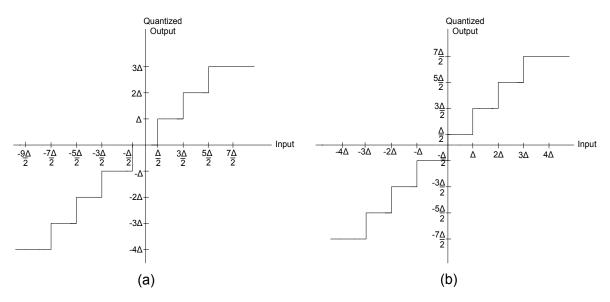

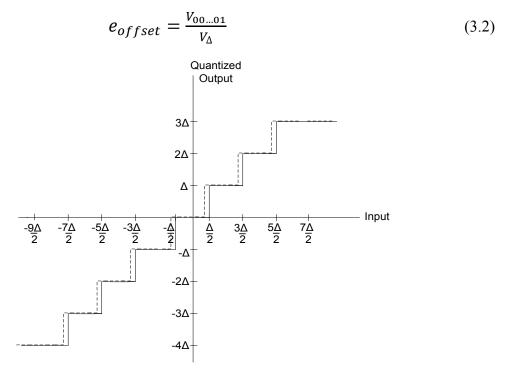

| 3.5  | Effect of offset error on quantizer transfer function    | 55 |

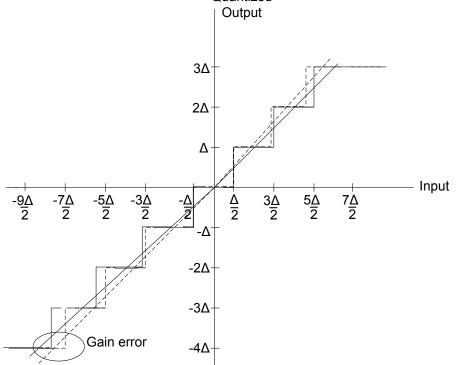

| 3.6  | Effect of gain error on quantizer transfer function      | 56 |

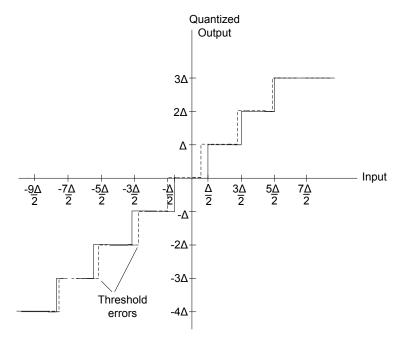

| 3.7  | Effect of linearity error on quantizer transfer function | 57 |

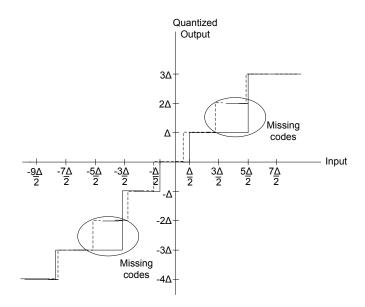

| 3.8  | Effect of missing codes on quantizer transfer function.  | 57 |

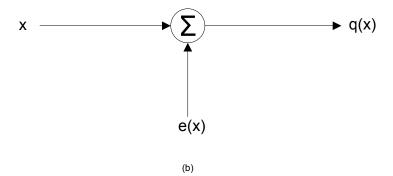

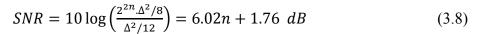

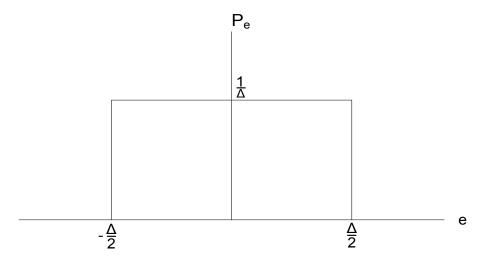

| 3.9  | Quantizer models: (a) non-linear (b) linear              | 58 |

| 3.10 | Quantizer PDF                                            | 59 |

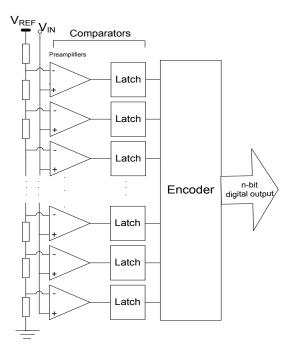

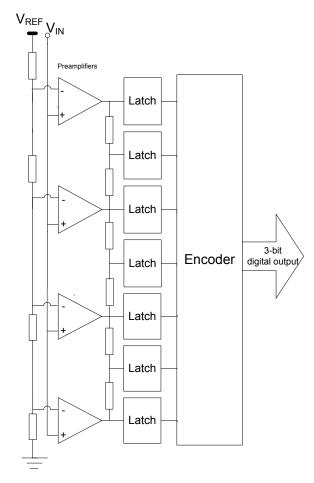

| 3.11 | Flash ADC                                                | 61 |

| 3.12 | A 3-bit interpolating flash ADC                          | 62 |

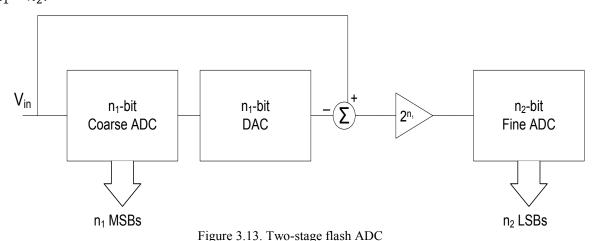

| 3.13 | Two-stage flash ADC                                               | . 63 |

|------|-------------------------------------------------------------------|------|

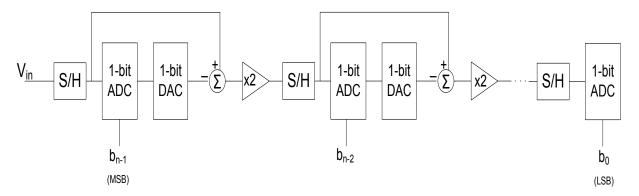

| 3.14 | Pipelined ADC architecture                                        | . 64 |

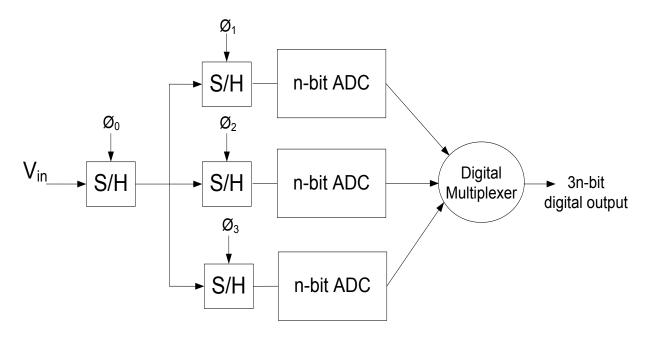

| 3.15 | A 3 <i>n</i> -bit three-channel time-interleaved ADC architecture | . 65 |

| 3.16 | Folding ADC architecture                                          | . 66 |

| 3.17 | Successive Approximation ADC architecture                         | . 67 |

| 3.18 | A 3-bit decoder-based DAC                                         | . 69 |

| 3.19 | An alternative implementation of decoder-based DAC                | . 70 |

| 3.20 | A 4-bit binary-weighted DAC                                       | . 71 |

| 3.21 | A 4-bit R-2R DAC                                                  | . 71 |

| 3.22 | A 3-bit thermometer-code DAC                                      | . 72 |

| 4.1  | Conversion from thermometer code to residue                       | . 75 |

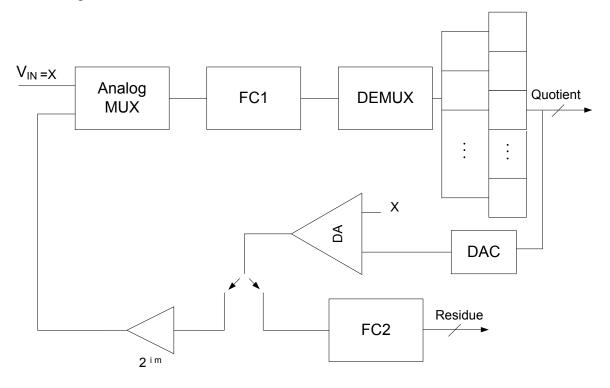

| 4.2  | Iterative flash A/R converter                                     | . 76 |

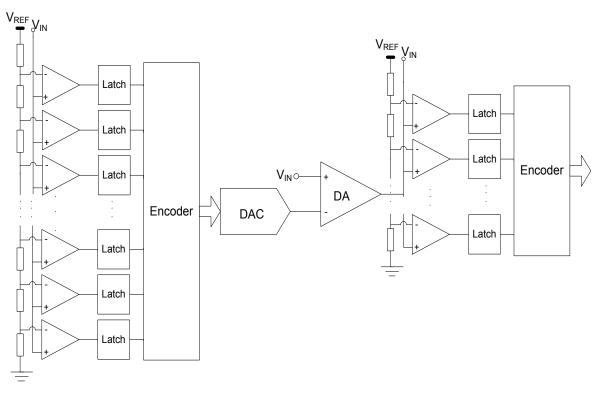

| 4.3  | Modified flash A/R converter                                      | . 77 |

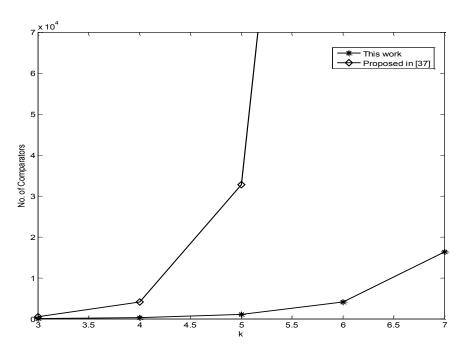

| 4.4  | Complexity vs. k of the proposed scheme compared to [37]          | . 79 |

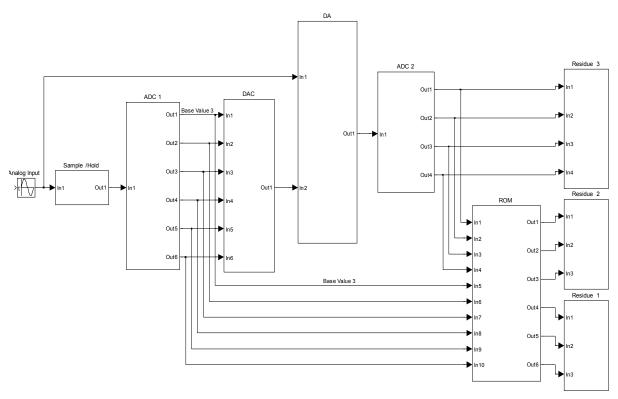

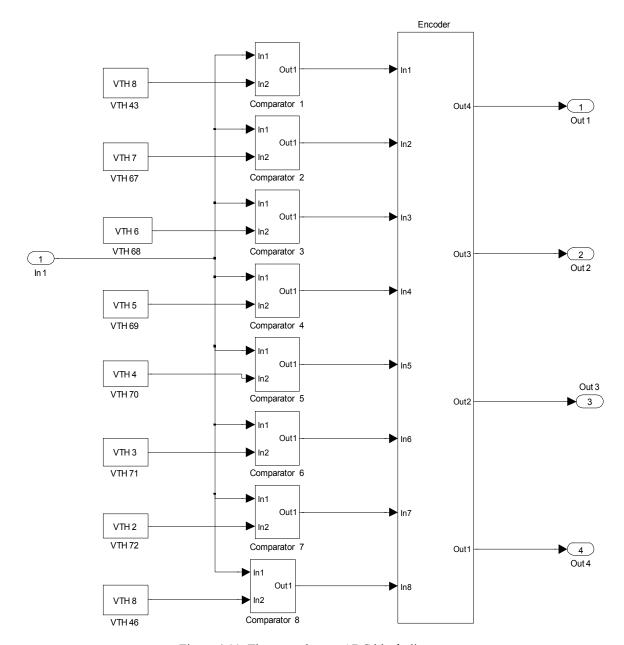

| 4.5  | Simulink model of the two-stage flash A/R converter               | . 80 |

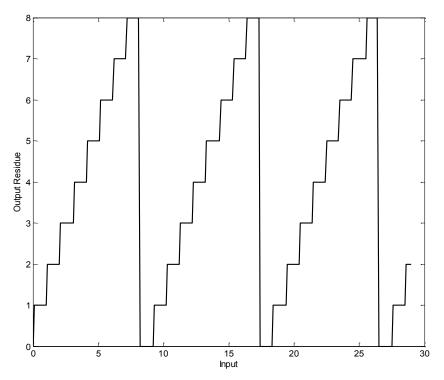

| 4.6  | Output response to a ramp input                                   | . 81 |

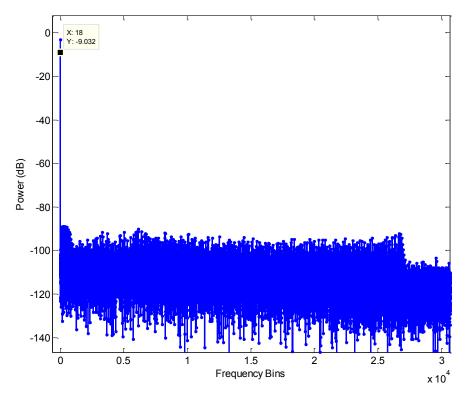

| 4.7  | The quantized output spectrum                                     | . 82 |

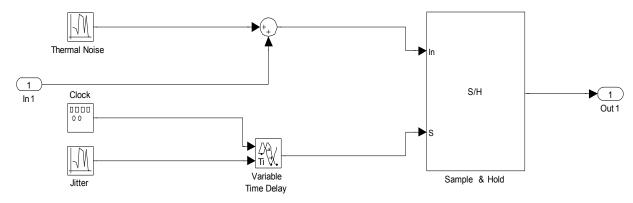

| 4.8  | The S/H circuit model                                             | . 82 |

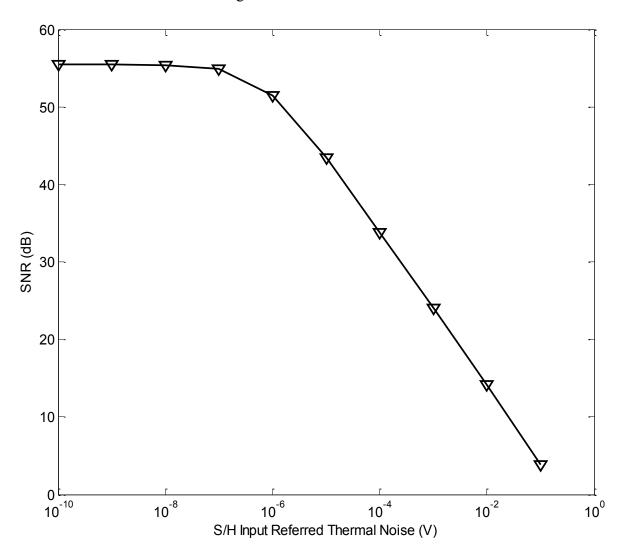

| 4.9  | SNR vs. S/H input referred thermal noise                          | . 83 |

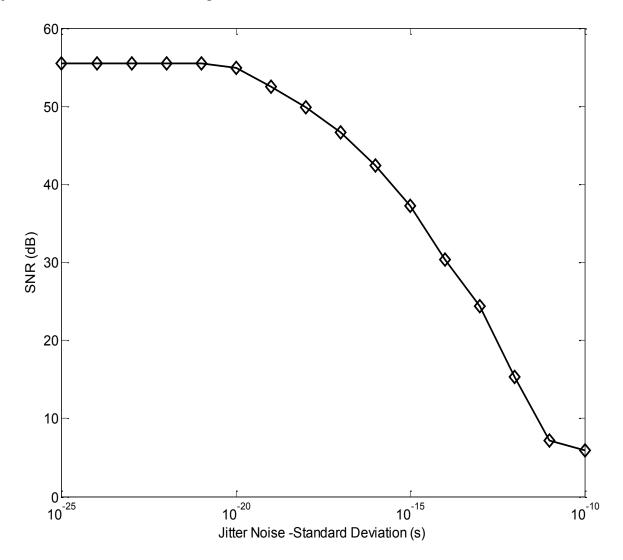

| 4.10 | SNR vs. clock jitter                                              | . 84 |

| 4.11 | The second stage ADC block diagram                                | . 85 |

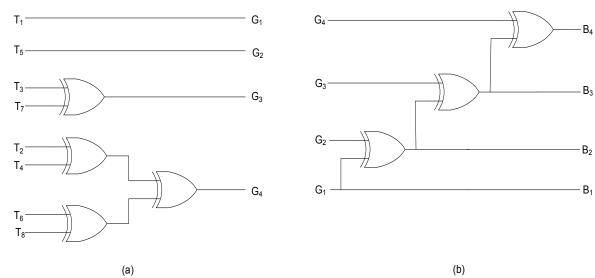

| 4.12 | A 4-bit encoder: (a) thermometer to gray (b) gray to binary       | . 86 |

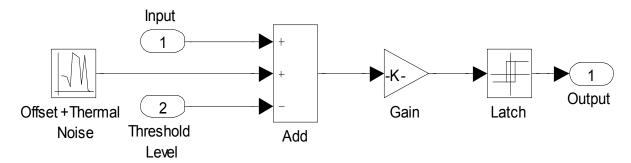

| 4.13 | The comparator model                                              | . 87 |

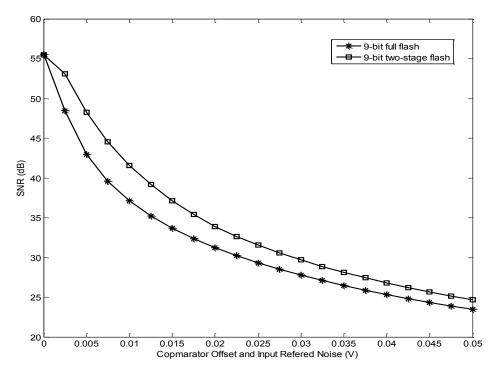

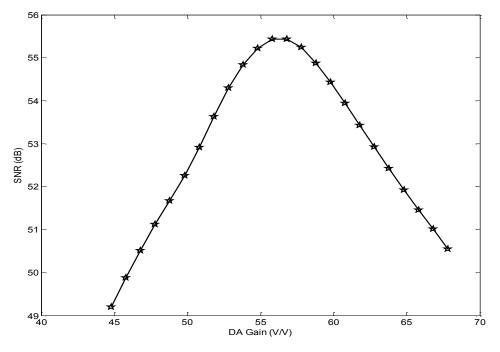

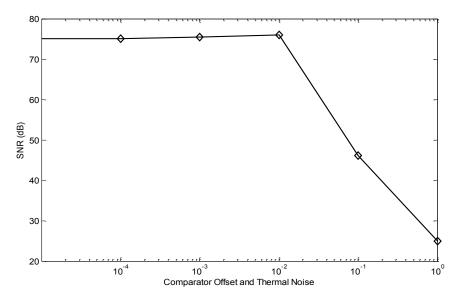

| 4.14 | SNR vs. comparator offset and thermal noise                       | . 88 |

| 4.15 | SNR vs. DA gain                                                   | . 88 |

| 4.16 | The successive Approximation A/R converter in [38] and [40]           | 89  |

|------|-----------------------------------------------------------------------|-----|

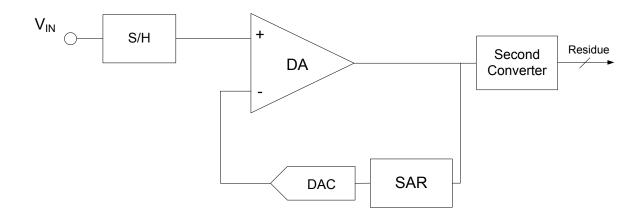

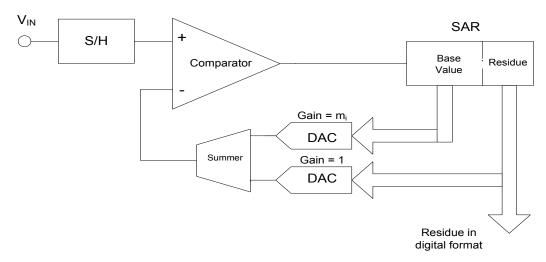

| 4.17 | The proposed successive approximation A/R converter                   | 89  |

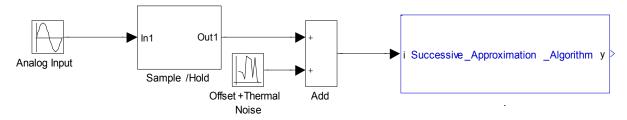

| 4.18 | Simulink model of the proposed successive approximation A/R converter | 91  |

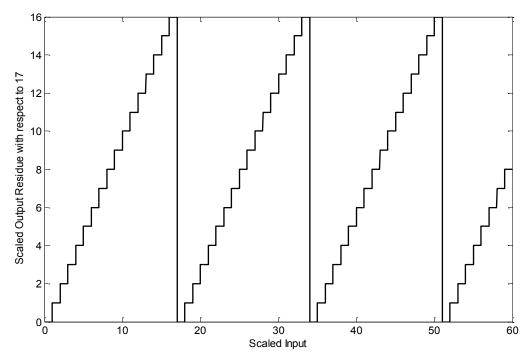

| 4.19 | Output response to a ramp input                                       | 91  |

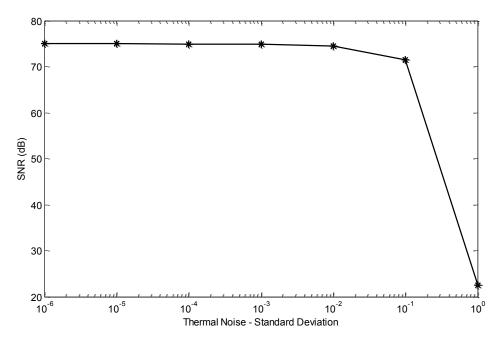

| 4.20 | SNR vs. S/H thermal noise                                             | 92  |

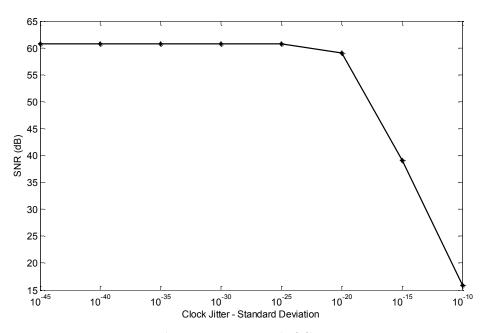

| 4.21 | SNR vs. clock jitter                                                  | 92  |

| 4.22 | SNR vs. comparator offset and thermal noise                           | 93  |

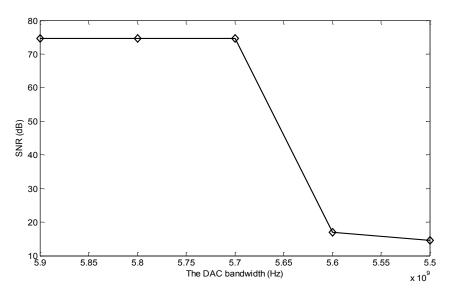

| 4.23 | SNR vs. the DAC bandwidth                                             | 93  |

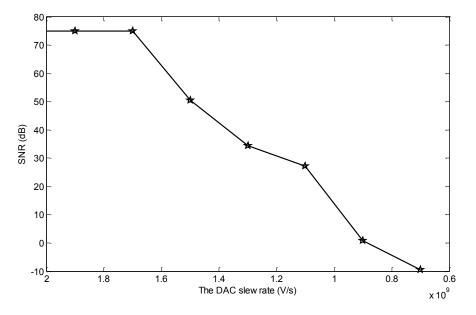

| 4.24 | SNR vs. the DAC slew rate                                             | 94  |

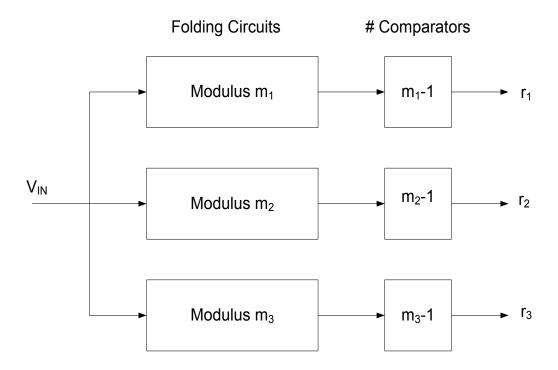

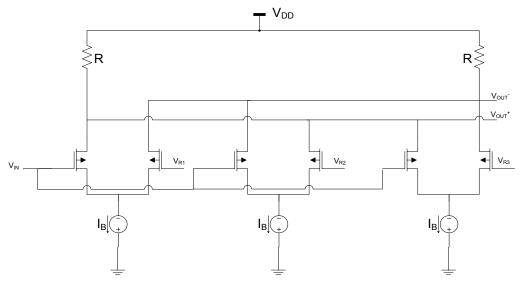

| 4.25 | A three-moduli folding A/R converter architecture                     | 94  |

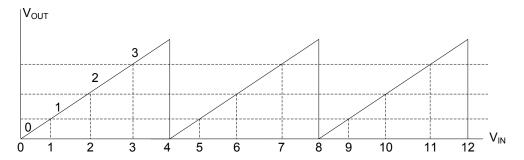

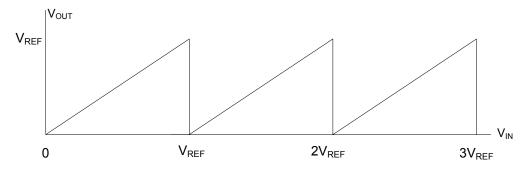

| 4.26 | Folding waveform with respect to modulus 4                            | 95  |

| 4.27 | Output waveform of the folding circuit                                | 95  |

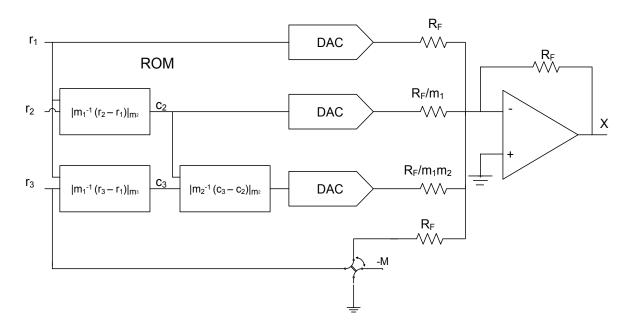

| 4.28 | MRC based R/A converter                                               | 97  |

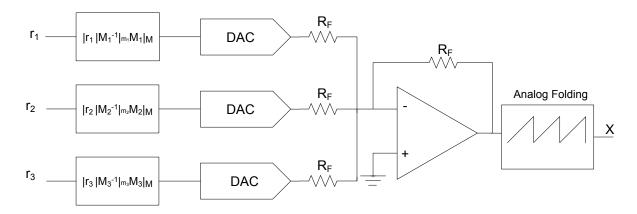

| 4.29 | CRT based R/A converter                                               | 98  |

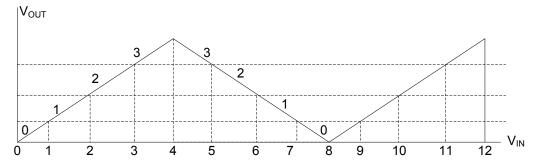

| 4.30 | Folded sawtooth waveform                                              | 99  |

| 4.31 | Folding circuit                                                       | 99  |

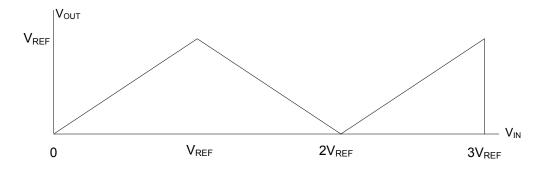

| 4.32 | Folded triangle waveform                                              | 100 |

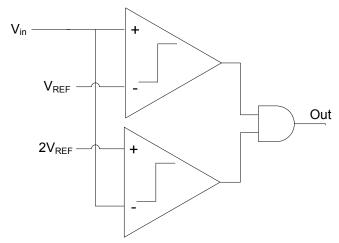

| 4.33 | Folding region detector                                               | 101 |

# List of Tables

| 1.1 | RNS representation for two different moduli-sets                                      | . 16 |

|-----|---------------------------------------------------------------------------------------|------|

| 1.2 | Multiplicative inverses with respect to two different moduli                          | . 22 |

| 2.1 | Periodicity of $ 2^n _m$ for different moduli                                         | . 32 |

| 3.1 | Comparison among the described ADC architectures                                      | . 68 |

| 4.1 | Number of comparators in [37] and in the proposed architecture                        | . 79 |

| 4.2 | Conversion from thermometer code to gray code                                         | . 86 |

| 4.3 | Hardware complexity and latency comparison among different reverse conversion schemes | S    |

|     |                                                                                       | 101  |

# List of Acronyms

RNS Residue Number System

CRT Chinese Remainder Theorem

MRC Mixed-Radix Conversion

ADC Analog-to-Digital Converter

DAC Digital-to-Analog Converter

B/R Binary-to-Residue

R/B Residue-to-Binary

A/R Analog-to-Residue

R/A Residue-to-Analog

ROM Read Only Memory

LUT Look-Up Table

## Chapter 1

## Introduction

A riddle posted in a book authored by a Chinese scholar called *Sun Tzu* in the first century was the first documented manifestation of *Residue Number System (RNS)* representation [1,2]. The riddle is described by the following statement:

We have things of which we do not know the number:

If we count them by threes, the remainder is 2.

If we count them by fives, the remainder is 3.

If we count them by sevens, the remainder is 2.

How many things are there?

The answer is 23.

The mathematical procedure of obtaining the answer 23 in this example from the set of integers 2, 3, and 2 is what was later called the *Chinese Remainder Theorem (CRT)*. The CRT provides an algorithmic solution of decoding the residue encoded number back into its conventional representation. This theorem is considered the cornerstone in realizing RNSs.

Encoding a large number into a group of small numbers results in significant speed up of the overall data processing. This fact encourages the implementation of RNS in some applications where intensive processing is inevitable.

In this chapter, we present the clear motivation of this thesis along with the main contributions. We also provide an introduction to RNS representation, properties, advantages, drawbacks, and applications.

#### 1.1 Thesis Motivation

A general structure of a typical RNS processor is shown in Figure 1.1. The RNS represented data is processed in parallel with no dependence or carry propagation between the processing units. The process of encoding the input data into RNS representation is called *Forward Conversion*, and the process of converting back the output data from RNS to conventional representation is called *Reverse Conversion*.

Figure 1.1. General structure of an RNS-based processor

The conversion stages are very critical in the evaluation of the performance of the overall RNS. Conversion circuitry can be very complex and may introduce latency that offsets the speed gained by the RNS processors. For a full RNS based system, the interaction with the analog world requires conversion from analog to residue and vice versa. Usually, this is done in two steps where conversion to binary is an intermediate stage. This makes the conversion stage inefficient due to their increased latency and complexity. To build an RNS

processor that can replace the digital processor in a certain application; we need to develop conversion circuits that perform as efficient as the analog-to-digital converter (ADC) and the digital-to-analog converter (DAC) in the digital binary-based systems. The reverse conversion process is based on the Chinese Remainder Theorem (CRT) or Mixed-Radix Conversion (MRC) techniques. Investigating new conversion schemes can lead to overcoming some obstacles in the RNS implementation of different applications. Thus, an analog-to-residue (A/R) converter and a residue-to-analog (R/A) converter are sought to eliminate the intermediate binary stage.

#### 1.2 Main Contributions of This Work

The main contributions of this work are summarized as follows:

- Two architectures for direct analog-to-residue conversion are proposed. The first proposed architecture is based on the two-stage flash conversion principle, while the second architecture is based on the successive approximation principle. The two architectures obviate the need of an intermediate binary stage and expedite the conversion process.

- 2. One architecture for direct residue-to-analog conversion is proposed. The proposed architecture is based on the CRT. The need for an intermediate binary stage is eliminated.

Overall, the proposed architectures facilitate the implementation of RNS based processors by reducing the latency and complexity introduced by the binary stage. This makes it more possible and more practical to build effective RNS based processors.

## 1.3 RNS Representation

An RNS is defined by a set of relatively prime integers called the *moduli*. The moduli-set is denoted as  $\{m_1, m_2, ..., m_n\}$  where  $m_i$  is the  $i^{th}$  modulus. Each integer X can be represented as a set of smaller integers called the *residues*. The residue-set is denoted as  $\{r_1, r_2, ..., r_n\}$  where  $r_i$  is the  $i^{th}$  residue. The residue  $r_i$  is defined as the least positive remainder when X is divided by the modulus  $m_i$ . This relation can be notationally written based on the congruence:

$$X \bmod m_i = r_i \tag{1.1}$$

The same congruence can be written in an alternative notation as:

$$|X|_{m_i} = r_i \tag{1.2}$$

The two notations will be used interchangeably throughout this thesis.

The RNS is capable of uniquely representing all integers X that lie in its *dynamic range*. The dynamic range is determined by the moduli-set  $\{m_1, m_2, ..., m_n\}$  and denoted as M where:

$$M = \prod_{i=1}^{n} m_i \tag{1.3}$$

The RNS provides unique representation for all integers in the range between 0 and M-1. If the integer X is greater than M-1, the RNS representation repeats itself. Therefore, more than one integer might have the same residue representation.

It is important to emphasize that the moduli have to be relatively prime to be able to exploit the full dynamic range M.

To illustrate the preceding principles, we present a numerical example.

#### Example 1.1.

Consider two different residue number systems defined by the two moduli-sets {2, 3, 5} and {2, 3, 4}. The representation of the numbers in residue format is shown in Table 1.1. for the two systems.

Table 1.1. RNS representation for two different moduli-sets

| v  | {2, 3, 5} |   | {2, 3, 4} |   |   |   |

|----|-----------|---|-----------|---|---|---|

| X  | 2         | 3 | 5         | 2 | 3 | 4 |

| 0  | 0         | 0 | 0         | 0 | 0 | 0 |

| 1  | 1         | 1 | 1         | 1 | 1 | 1 |

| 2  | 0         | 2 | 2         | 0 | 2 | 2 |

| 3  | 1         | 0 | 3         | 1 | 0 | 3 |

| 4  | 0         | 1 | 4         | 0 | 1 | 0 |

| 5  | 1         | 2 | 0         | 1 | 2 | 1 |

| 6  | 0         | 0 | 1         | 0 | 0 | 2 |

| 7  | 1         | 1 | 2         | 1 | 1 | 3 |

| 8  | 0         | 2 | 3         | 0 | 2 | 0 |

| 9  | 1         | 0 | 4         | 1 | 0 | 1 |

| 10 | 0         | 1 | 0         | 0 | 1 | 2 |

| 11 | 1         | 2 | 1         | 1 | 2 | 3 |

| 12 | 0         | 0 | 2         | 0 | 0 | 0 |

| 13 | 1         | 1 | 3         | 1 | 1 | 1 |

| 14 | 0 | 2 | 4 | 0 | 2 | 2 |

|----|---|---|---|---|---|---|

| 15 | 1 | 0 | 0 | 1 | 0 | 3 |

| 16 | 0 | 1 | 1 | 0 | 1 | 0 |

| 17 | 1 | 2 | 2 | 1 | 2 | 1 |

| 18 | 0 | 0 | 3 | 0 | 0 | 2 |

| 19 | 1 | 1 | 4 | 1 | 1 | 3 |

| 20 | 0 | 2 | 0 | 0 | 2 | 0 |

| 21 | 1 | 0 | 1 | 1 | 0 | 1 |

| 22 | 0 | 1 | 2 | 0 | 1 | 2 |

| 23 | 1 | 2 | 3 | 1 | 2 | 3 |

| 24 | 0 | 0 | 4 | 0 | 0 | 0 |

| 25 | 1 | 1 | 0 | 1 | 1 | 1 |

| 26 | 0 | 2 | 1 | 0 | 2 | 2 |

| 27 | 1 | 0 | 2 | 1 | 0 | 3 |

| 28 | 0 | 1 | 3 | 0 | 1 | 0 |

| 29 | 1 | 2 | 4 | 1 | 2 | 1 |

| 30 | 0 | 0 | 0 | 0 | 0 | 2 |

In the first RNS, the moduli in the moduli-set {2, 3, 5} are relatively prime. The RNS representation is unique for all numbers in the range from 0 to 29. Beyond that range, the RNS representation repeats itself. For example, the RNS representation of 30 is the same as that of 0. In the second RNS, the moduli in the moduli-set {2, 3, 4} are not relatively prime, since 2 and 4 have a common divisor of 2. We notice that the RNS representation repeats itself at 12 preventing the dynamic range from being fully exploited. Therefore, choosing relatively prime moduli for the RNS is necessary to ensure unique representation within the dynamic range.

In the preceding discussion on RNS, we assumed dealing with unsigned numbers. However, some applications require representing negative numbers. To achieve that, we can partition the full range [0: M-1] into two approximately equal halves: the upper half represents the positive numbers, and the lower half represents the negative numbers. The numbers X that can be represented using the new convention have to satisfy the following relations [4]:

$$-\frac{M-1}{2} \le X \le \frac{M-1}{2} \quad \text{if } M \text{ is odd}$$

(1.4)

$$-\frac{M}{2} \le X \le \frac{M}{2} - 1 \quad \text{if } M \text{ is even} \tag{1.5}$$

If  $X = \{r_1, r_2, ..., r_n\}$  represents a positive number in the appropriate range, then -X can be represented as  $\{\overline{r_1}, \overline{r_2}, ..., \overline{r_n}\}$  where  $\overline{r_i}$  is the  $m_i$ 's complement of  $r_i$ , i.e.  $\overline{r_i}$  satisfies the relation  $(r_i + \overline{r_i}) \mod m_i = 0$ . In our discussion, we will assume that the numbers are unsigned unless otherwise it is mentioned.

#### Example 1.2.

Consider an RNS with the moduli-set  $\{3, 4, 5\}$ . The number 18 is represented as  $\{0, 2, 3\}$  while the number -18 is represented as  $\{0, 2, 2\}$ .

The justification for that is as follows:

$$(0+0)$$

mod  $3=0$

$$(2+2) mod 4 = 0$$

$$(3+2) mod 5 = 0$$

Therefore, the positive numbers are represented in the upper half of the dynamic range and the conversion to residue representation is straightforward, while the negative numbers are represented in the lower half of the dynamic range and the conversion to residue representation is interpreted as the conversion of the compliments of the residues with respect to the corresponding moduli.

#### 1.4 Mathematical Fundamentals

In this section, we introduce the fundamentals of the RNS representation. The congruences are explained in details with their properties. These properties form a solid background to understand the process of conversion between the conventional system and the RNS. More advanced results and mathematical relations can be found in the subsequent chapters. Basic algebra related to RNS is introduced here. This includes finding the additive and the multiplicative inverses, and some properties of division and scaling which are not easy operations in RNS.

#### 1.4.1 Basic Definitions and Congruences

Residue of a number

The basic relationship between numbers in conventional representation and RNS representation is the following congruence:

$$X \bmod m_i = r_i \tag{1.6}$$

where  $m_i$  is the *modulus*, and  $r_i$  is the *residue*. The residue is defined as the least positive remainder when the number X is divided by the modulus  $m_i$ .

#### Example 1.3.

For X = 57,  $m_1 = 4$ , and  $m_2 = 5$ , we find the residues  $r_1$  and  $r_2$  with respect to the moduli  $m_1$  and  $m_2$ , respectively as follows:

$$57 \mod 4 = 1$$

since  $57 = 4 \times 14 + 1$

$$57 \mod 5 = 2 \quad since \quad 57 = 5 \times 11 + 2$$

#### Definition of the base values

With respect to modulus  $m_i$ , any number X can be represented as a combination of a base value  $B_i$  and a residue  $r_i$ :

$$X = B_i + r_i \tag{1.7}$$

and

$$B_i = k \times m_i$$

(1.8)

where k is an integer that satisfies Equations (1.7) and (1.8).

The definition of the base value will be exploited in Chapter 4 where these values will be generated to directly convert from analog to RNS representation.

#### 1.4.2 Basic Algebraic Operations

Addition (or subtraction)

We can add (or subtract) different numbers in the RNS representation by individually adding (or subtracting) the residues with respect to the corresponding moduli.

Consider the moduli-set  $S = \{m_1, m_2, ..., m_n\}$ , and the numbers X and Y are given in RNS representation:

$$X = \{x_1, x_2, ..., x_n\}$$

and  $Y = \{y_1, y_2, ..., y_n\}$

Then,

$$Z = X + Y = \{z_1, z_2, ..., z_n\}$$

where  $z_i = (x_i + y_i) \mod m_i$  (1.9)

This property can be applied to subtraction as well, where subtraction of Y from X is considered as the addition of  $\overline{Y}$ .

The modulo operation is distributive over addition (and subtraction):

$$|X \mp Y|_m = ||X|_m \mp |Y|_m|_m \tag{1.10}$$

#### Multiplication

In a similar way to addition, multiplication in RNS can be carried out by multiplying the individual residues with respect to the corresponding moduli. Consider the moduli-set  $S = \{m_1, m_2, ..., m_n\}$ , and the numbers X and Y are given in RNS representation:

$$X = \{x_1, x_2, ..., x_n\}$$

and  $Y = \{y_1, y_2, ..., y_n\}$

Then,

$$Z = X \times Y = \{z_1, z_2, ..., z_n\}$$

where  $z_i = (x_i \times y_i) \mod m_i$  (1.11)

The modulo operation is distributive over multiplication:

$$|X \times Y|_m = ||X|_m \times |Y|_m|_m \tag{1.12}$$

#### Additive Inverse

The relation between the residue  $r_i$  and its additive inverse  $\overline{r_i}$  is defined by the congruence:

$$(r_i + \overline{r_i}) \bmod m_i = 0 \tag{1.13}$$

The additive inverse  $\overline{r}_i$  can be obtained using the following operation:

$$\overline{r_i} = (m_i - r_i) \bmod m_i \tag{1.14}$$

Subtraction is one application of this property, where subtraction is regarded as the addition of the additive inverse.

#### Example 1.4.

Given the moduli-set  $\{2, 3, 5\}$ , the dynamic range is M = 30. The RNS can uniquely represent all numbers in the range [0:29]. Let  $X = 28 \triangleq \{0, 1, 3\}$  and  $Y = 24 \triangleq \{0, 0, 4\}$ . To find -Y, we need first to obtain  $\overline{Y}$ , and then find  $X + \overline{Y}$ . First,

$$\overline{Y} = \{(2-0) \mod 2, (3-0) \mod 3, (5-4) \mod 5\} = \{0,0,1\}$$

Then,  $X - Y = X + \overline{Y} = \begin{cases} (0+0) \mod 2, (1+0) \mod 3, \\ (3+1) \mod 5 \end{cases} = \{0,1,4\}$  which is the RNS representation of 4.

#### Multiplicative Inverse

The multiplicative inverse  $r_i^{-1}$  of the residue  $r_i$  is defined by the congruence:

$$(r_i \times r_i^{-1}) \mod m_i = 1$$

(1.15)

where  $r_i^{-1}$  exists only if  $r_i$  and  $m_i$  are relatively prime.

#### Example 1.5.

For the modulus m = 5, we find the multiplicative inverse  $r^{-1}$  of the residue r = 3 by applying Equation (1.15):

$$(3 \times r^{-1}) \mod 5 = 1$$

We notice that the modulo multiplication of 3 and 2 with respect to 5 results in 1.

Thus,

$$r^{-1} = 2$$

As illustrated in Example 1.5., there is no general method of obtaining the multiplicative inverse. The multiplicative inverse is usually obtained by brute-force search. Only when m is prime, we can utilize Fermat's Theorem which can be useful in determining the multiplicative inverse. This topic is out of the scope of this thesis. Reference [4] provides more details about the theorem and its application in RNS.

#### Example 1.6.

This example shows that the multiplicative inverse exists only if r and m are relatively prime. In Table 1.2., the multiplicative inverse  $r^{-1}$  is obtained, if exists, with respect to the modulus m. In the first column, m = 7 is always prime with respect to any integer. In the second column, m = 8 is not prime with respect to 2, 4, and 6. We notice that 2, 4, and 6 have no multiplicative inverse with respect to modulus 8.

| r | m = 7    | m = 8    |

|---|----------|----------|

| _ | $r^{-1}$ | $r^{-1}$ |

| 1 | 1        | 1        |

| 2 | 4        | -        |

| 3 | 5        | 3        |

| 4 | 2        | -        |

| 5 | 3        | 5        |

| 6 | 6        | -        |

| 7 |          | 7        |

Table 1.2. Multiplicative inverses with respect to two different moduli

#### Division

Division is one of the main obstacles that discourage the use of RNS. In RNS representation, division is not a simple operation. The analogy between division in conventional representation and RNS representation does not hold.

In conventional representation, we represent division as follows:

$$\frac{x}{y} = q \tag{1.16}$$

which can be rewritten as:

$$y \times q = x \tag{1.17}$$

where q is the quotient.

In RNS, the analogous congruence is:

$$y \times q = x \bmod m \tag{1.18}$$

Multiplying both sides by the multiplicative inverse of y, we can write:

$$q = x \times y^{-1} \bmod m \tag{1.19}$$

In Equation (1.19), q is equivalent to the quotient obtained from Equation (1.16) only if it has an integer value. Otherwise, multiplying by the multiplicative inverse in RNS representation will not be equivalent to division in conventional representation.

#### *Example 1.7.*

Consider an RNS with m = 7, we want to compute the following quotients:

a)

$$\frac{6}{2}$$

b)  $\frac{6}{4}$

a) In the first case:

$$\frac{6}{2} = q$$

$$2q = 6 \mod 7$$

$$q = 6 \times 2^{-1} \mod 7$$

$$q = 6 \times 4 \mod 7$$

$$q = 3$$

which is equivalent to division in conventional representation.

a) In the second case:

We know that the quotient in conventional representation is 1, and the result of the division is a non-integer value.

$$\frac{6}{4} = q$$

$$4q = 6 \mod 7$$

$$q = 6 \times 4^{-1} \mod 7$$

$$q = 6 \times 2 \mod 7$$

$$q = 5$$

We notice in part (b) of Example 1.7. that division in RNS is not equivalent to that in conventional representation when the quotient is a non-integer value. Due to this fact, division in RNS is usually done by converting the residues to conventional representation, performing the division, and then converting back to RNS representation. Tedious and complex conversion steps result in undesired overhead. This is one of the main drawbacks of RNS representation.

## 1.5 Conversion between Conventional Representation and RNS Representation

To utilize the properties of the RNS and carry out the processing in the residue domain, we need to be able to convert smoothly between the conventional (binary or analog) representation

and the RNS representation. The process of conversion from conventional representation to RNS representation is called *Forward Conversion*. Conceptually, this process can be done by dividing the given conventional number by all the moduli and finding the remainders of the divisions. This is the most direct way that can be applied to any general moduli-set. However, we show in Chapter 2 that for some special moduli-sets this process can be further simplified. The simplification arises from the fact that division by a number, that is a power of two, is equivalent to shifting the digits to the right. This property can be utilized to expedite and simplify the forward conversion. The process of conversion from RNS representation to conventional representation is called *Reverse Conversion*. The reverse conversion process is more difficult and introduces more overhead in terms of speed and complexity. The algorithms of reverse conversion are based on Chinese Remainder Theorem (CRT) or Mixed-Radix Conversion (MRC). The use of the CRT allows parallelism in the conversion process implementation. The MRC is an inherently sequential approach. In general, the realization of a VLSI implementation of a reverse converter is complex and costly. More details about CRT and MRC are given in Chapter 2.

## 1.6 Advantages of RNS Representation

Implementing an algorithm using parallel distributed arithmetic with no dependence between the arithmetic blocks simplifies the overall design and reduces the complexity of the individual building blocks. The advantages of RNS representation can be summarized as follows [4,5,6]: *High Speed:* The absence of carry propagation between the arithmetic blocks results in high speed processing. In conventional digital processors, the critical path is associated with the propagation of the carry signal to the last bit (MSB) of the arithmetic unit. Using RNS representation, large words are encoded into small words, which results in critical path minimization.

Reduced Power: Using small arithmetic units in realizing the RNS processor reduces the switching activities in each channel [7]. This results in reduction in the dynamic power, since the dynamic power is directly proportional to switching activities.

*Reduced Complexity:* Because the RNS representation encodes large numbers into small residues, the complexity of the arithmetic units in each modulo channel is reduced. This facilitates and simplifies the overall design.

Error Detection and Correction: The RNS is a non-positional system with no dependence between its channels. Thus, an error in one channel does not propagate to other channels. Therefore, isolation of the faulty residues allows fault tolerance and facilitates error detection and correction. In fact, the RNS has some embedded error detection and correction features described in [8].

### 1.7 Drawbacks of RNS Representation

We mentioned that RNS architectures result in great advantages, especially in terms of speed and power. This makes it very suitable to implement RNS in different applications. However, in spite of their great advantages, RNS processors did not find wide use but remained as an interesting theoretical topic. There are two main reasons behind the limited use of RNS in applications:

First, although the RNS representation simplifies and expedites addition and multiplication compared to the conventional binary system, other operations such as division, square-root, sign detection, and comparison are difficult and costly operations in the residue domain. Thus, building an RNS based ALU that is capable of performing the basic arithmetic is not an easy job.

Second, conversion circuitry can be complex and can introduce latency that offsets the speed gained by the RNS processor. Hence, the design of efficient conversion circuits is considered the bottleneck of a successful RNS.

Nevertheless, RNS architectures are considered an interesting theoretical topic for researchers. Some applications that are computationally intensive and require mainly recursive addition and multiplication operations, such as FFT, FIR filters, and public-key cryptography are appealing to be implemented using RNS. Therefore, investigating new conversion schemes can lead to overcoming some obstacles in the RNS implementation of different applications by reducing the overhead of the conversion stages.

## 1.8 Applications

As discussed in the last section, RNS is suitable for applications in which addition and multiplication are the predominant arithmetic operations. Due to its carry-free property, RNS has good potential in applications where speed and/or power consumption is very critical. In addition, the isolation between the modulo channels facilitates error detection and correction. Examples of these applications are digital signal processing (DSP) [9], digital image processing [10], RSA algorithms [11], communication receivers [12], and fault tolerance [8,13]. In most of these applications, intensive multiply-and-accumulate (MAC) operations are required.

One possible application of RNS in DSP is the design of digital filters. Digital filters have different uses such as interpolation, decimation, equalization, noise reduction, and band splitting [4]. There are two basic types of digital filers: Finite Impulse Response (FIR) filters and Infinite Impulse Response (IIR) filters. Carrying out the required multiplication and addition operations in the residue domain results in speeding up the system and reducing the power consumption [14,15]. Another possible application of RNS in DSP is the Discrete Fourier Transform (DFT) which is a very common transform in various engineering applications. Again, the main operations involved here are addition and multiplication. Using RNS in implementing DFT algorithms results in faster operations due to the parallelism in the processing. In addition, the carry-free property of the RNS makes it potentially very useful in fault tolerant applications. Nowadays, the integrated circuits are very dense, and full testing will no longer be possible. The RNS has no weight information. Therefore, any error in one of the residues does not affect the other modulo channels. Moreover, since ordering is not important in RNS representation, the faulty residues can be discarded and corrected separately. In summary, RNS seems to be good for many applications that are important in modern computing algorithms.

# Chapter 2

# Conversion between Binary and RNS Representations

In this chapter, we discuss the conversion between binary and RNS representations. To be able to process the data in RNS, the data has to be first converted to RNS representation. The process of converting the data from conventional representation (analog or binary) to RNS representation is called Forward Conversion. Meanwhile, we shall assume that the initial inputs are available in binary representation. We need to utilize efficient algorithms and schemes for the forward conversion process. The forward converter has to be efficient in terms of area, speed, and power. After the data is processed through the modulo processing units of the RNS, they have to be converted back into the conventional representation. The process of converting the data from RNS representation to conventional representation is called *Reverse Conversion*. We present the basic theoretical foundations for the methods of reverse residue-to-binary (R/B) conversion. In addition, we present some architectures for the implementation of these methods. The overhead of the reverse conversion circuitry is the main impediment to build an efficient RNS processor. Particularly, the design of the reverse converter is more important and constitutes the bottleneck of any successful RNS. Therefore, developing efficient algorithms and architectures for reverse conversion is a great challenge and it has received a considerable deal of interest among researchers in the past few decades. In this chapter, we focus on the methods of reverse conversion where the output is in binary representation. However, direct conversion from RNS to analog representation is also based on the same methods. More details about direct residue-to-analog conversion are provided in Chapter 4.

### 2.1 Forward Conversion from Binary to RNS Representation

The forward conversion stage is of paramount importance as it is considered as an overhead in the overall RNS. Choosing the most appropriate scheme depends heavily on the used moduliset. Forward converters are usually classified based on the used moduli into two categories. The first category includes forward converters based on arbitrary moduli-sets. These converters are usually built using look-up tables. The second category includes forward converters based on special moduli-sets. The use of special moduli-sets simplifies the forward conversion algorithms and architectures. The special moduli-set converters are usually realized using pure combinational logic.

We present here some of the available architectures for forward conversion from binary to RNS representation. First, we present forward converters based on arbitrary moduli-sets. Then, we present forward conversion based on the special moduli-set  $\{2^n - 1, 2^n, 2^n + 1\}$ . We show how the complexity of the overall design is minimized which reduces the overhead introduced by the forward converter. Finally, we provide some architectures for implementing the modulo addition that are used in the realization of all forward converters.

#### 2.1.1 Arbitrary Moduli-Set Forward Converters

We present here some architectures for forward conversion from binary to RNS representation using any arbitrary moduli-set. We mentioned earlier that using special modulisets, such as  $\{2^n - 1, 2^n, 2^n + 1\}$ , makes the forward conversion process fast and simple. In general, forward converters based on special moduli-sets are the most efficient available converters. However, some applications require a very large dynamic range which cannot be achieved efficiently using the special moduli-sets. For example, most of the employed modulisets consist of three or four moduli. When the required dynamic range is very large, these moduli have to be large, which results in lower performance of the arithmetic units in each modulo channel. In that case, the best solution is to use many small moduli (five or more) to represent the large dynamic range efficiently. The research on representing large dynamic ranges has two main approaches. The first approach is to develop efficient algorithms and schemes for arbitrary moduli-set forward converters. The second approach is to develop new special moduli-sets with a large number of moduli to represent the large dynamic range efficiently. In this approach, a special five-moduli-set  $\{2^n - 1, 2^n, 2^n + 1, 2^{n+1} - 1, 2^{n-1} - 1\}$

with its conversion circuits was proposed in [16]. The proposed moduli-set has a dynamic range that can represent (5n-1) bits while keeping the moduli small enough and the converters efficient. Nevertheless, it is important and useful to keep the research open for both approaches. Therefore, developing efficient schemes for forward conversion from binary to RNS representation using arbitrary moduli-sets is also of great importance.

The implementation of arbitrary moduli-set forward conversion algorithms is either based on look-up tables (typically ROMs), pure combinational logic, or a combination of both. Implementation of these converters using combinational logic is tedious and requires complex processing units. The all ROM implementation is preferred in this case. However, for a large dynamic range, the ROM size grows dramatically and makes the overall conversion process inefficient. A trade-off between the two implementations can be utilized using a combination of ROM and combinational logic [17].

In this section, we provide some basic architectures for arbitrary moduli-set forward converters. We aim at presenting the basic principle of each architecture. More advanced algorithms and architectures are available in [4]. As the look-up table implementation is preferred in the case of the arbitrary moduli-set, we shall focus on this implementation approach and show different techniques to realize it.

The main idea in the look-up table implementation of forward converters is to store all the residues and recall them based on the value of the binary input [18]. The binary input acts as an address decoder input that points at the appropriate value in the look-up table.

To find the residue of a binary number X with respect to a certain modulus m, we utilize the mathematical property of Equation (1.10) to obtain the residues of all required powers of two with respect to modulus m. To illustrate that, assume that X is a binary number:

$$X = x_{n-1}x_{n-2} \dots x_1x_0 = \sum_{j=0}^{n-1} x_j 2^j$$

(2.1)

The residue of *X* is represented as:

$$|X|_{m} = \left| \sum_{j=0}^{n-1} x_{j} 2^{j} \right|_{m} \tag{2.2}$$

Using Equation (1.10), we can write:

$$|X|_{m} = \left| \sum_{j=0}^{n-1} \left| x_{j} 2^{j} \right|_{m} \right|_{m} \tag{2.3}$$

where  $x_i$  is either 0 or 1.

#### Serial Conversion

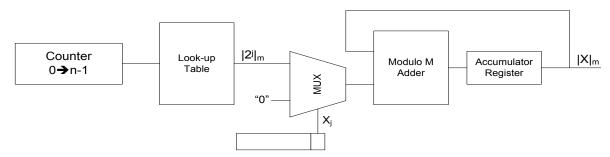

A direct implementation of Equation (2.3) is to store all the values  $|2^j|_m$  in a look-up table. The values are activated or deactivated (set to 0) based on whether  $x_j$  is 0 or 1, respectively. A modulo-m adder with an accumulator is required to obtain the modulo addition of all activated values in the table. A direct implementation of Equation (2.3) is shown in Figure 2.1.

Figure 2.1. Serial forward converter

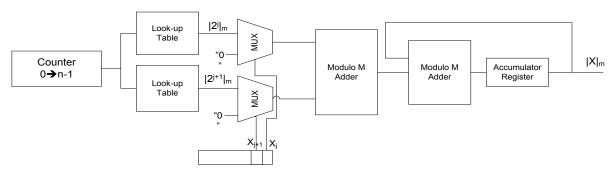

Initially the accumulator is set to zero. The conversion process requires n clock cycles, where n is the number of bits when X is represented in binary. The value of each bit  $x_j$  (either 0 or 1) instructs the multiplexer to accumulate the value  $\left|2^j\right|_m$  or a zero. The counter counts from 0 to n-1 to address the look-up table. The look-up table is typically implemented as a ROM of size  $(n \times \log_2 m)$  bits. The overall design is simple and only few components are required for the implementation. However, the algorithm is completely sequential. This makes it slow and inefficient for large dynamic range applications. Some modifications can be applied on the structure to improve its efficiency. As shown in [4], processing the two values  $\left|x_j 2^j\right|_m$  and  $\left|x_{j+1} 2^{j+1}\right|_m$  in each cycle doubles the conversion speed. The modified structure is shown in Figure 2.2. Pipelining is also possible in these architectures to increase the throughput.

Figure 2.2. Modified structure for serial forward converter

#### Parallel Conversion

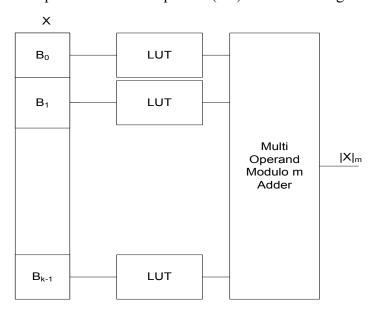

Another architecture for forward conversion from binary to RNS representation can be obtained by manipulating Equation (2.3). Suppose X is partitioned into k blocks, each of p-bits [19]. Let X be partitioned into the blocks  $B_{k-1}B_{k-2} \dots B_1B_0$ , then:

$$X = \sum_{i=0}^{k-1} 2^{jB} B_i \tag{2.4}$$

$$|X|_{m} = \left| \sum_{j=0}^{k-1} 2^{jB} B_{j} \right|_{m} = \left| \sum_{j=0}^{k-1} \left| 2^{jB} B_{j} \right|_{m} \right|_{m}$$

(2.5)

#### Example 2.1.

Consider X = 2456 and m = 19. We want to find  $|X|_m$  by partitioning X into four 3-bit blocks.

First, X is a 12-bit number that has the binary representation: 100110011000.

The four blocks are: 100, 110, 011, and 000. By applying Equation (2.5):

$$|2456|_{19} = ||2^{0} \times 0|_{19} + |2^{3} \times 3|_{19} + |2^{6} \times 6|_{19} + |2^{9} \times 4|_{19}|_{19}$$

$$= |0 + 5 + 4 + 15|_{19}$$

$$= 5$$

Equation (2.5) can be directly implemented by storing the values  $|2^{jB}B_j|_m$  in k look-up tables, where k is the number of partitioning blocks. The values of  $B_j$  are used to address the values  $|2^{jB}B_j|_m$  in the look-up table (LUT). These values are then added using a multi-operand modulo adder. A typical implementation of Equation (2.5) is shown in Figure 2.3.

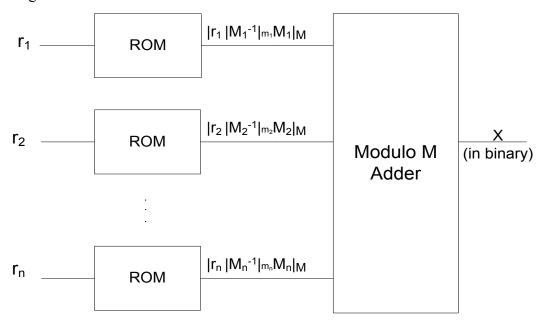

Figure 2.3. Parallel forward converter

Each look-up table (LUT) is a ROM cell that has a size of  $(p \times \log_2 m)$  bits, where p is the number of bits in each block, and m is the modulus. Compared to serial forward converters, the parallel forward converters are faster and more adequate for high speed applications. However, the parallel converters require k look-up tables and a modulo adder that adds k operands with respect to modulus m.

In order to reduce the size of each look-up table and therefore enhance the performance of the overall converter, a technique called *periodic partitioning* is utilized [20]. We know from Equation (2.3) that obtaining  $|X|_m$  requires storing all the residues  $|2^j|_m$ . Careful investigation of the residues of  $2^n$  with respect to modulus m shows that these residues repeat themselves in a period l less than m-1 for some moduli. We refer to m-1 as the *basic period*, and to l as the *short period* [4]. The periodicity of the residues  $|2^n|_m$  with respect to different moduli is shown in Table 2.1.

Table 2.1. Periodicity of  $|2^n|_m$  for different moduli

| m  | $ 2^n _m$                 | m-1 | l  | Saving (%) |

|----|---------------------------|-----|----|------------|

| 3  | 1,2,1,2,1,                | 2   | 2  | 0 %        |

| 5  | 1,2,4,3,1,2,              | 4   | 4  | 0 %        |

| 6  | 1,2,4,1,2,                | 5   | 3  | 40 %       |

| 7  | 1,2,4,1,2,                | 6   | 3  | 50 %       |

| 9  | 1,2,4,8,7,5,1,2,          | 8   | 6  | 25 %       |

| 10 | 1,2,4,8,6,2,4,8,          | 9   | 5  | 44.4 %     |

| 11 | 1,2,4,8,5,10,9,7,3,6,1,2, | 10  | 10 | 0 %        |

| 12 | 1,2,4,8,2,4,8,2,          | 11  | 4  | 63.3 %     |

| 13 | 1,2,4,8,3,6,12,11,        | 12  | 12 | 0 %        |

| 14 | 1,2,4,8,2,4,8,            | 13  | 4  | 69.2 %     |

| 15 | 1,2,4,8,1,2,4,            | 14  | 4  | 71.4 %     |

| 17 | 1,2,4,8,16,15,13,9,       | 16  | 8  | 50 %       |

| 18 | 1,2,4,8,16,14,10,2,4,8,   | 17  | 7  | 58.9 %     |

| 19 | 1,2,4,8,16,13,7,14,9,18,  | 18  | 18 | 0 %        |

| 21 | 1,2,4,8,16,11,1,2,4,      | 20  | 6  | 70 %       |

Table 2.1. shows the great saving when we design look-up tables for some values of m. For example, for m = 15, we need to store only 4 values. These values can be used for higher indices because of the periodicity of the residues. This results in saving of 71.4 % in the memory size.

#### 2.1.2 Special Moduli-Set Forward Converters

Choosing a special moduli-set is the preferred choice to facilitate and expedite the conversion stages. The special moduli-set forward converters are the most efficient available converters in terms of speed, area, and power. Usually, the special moduli-sets are referred to as *low-cost moduli-sets*. In this section, we will focus on the special moduli-set  $\{2^n - 1, 2^n, 2^n + 1\}$  as it is the most commonly used moduli-set.

In contrast to arbitrary moduli-set forward converters, the special moduli-set converters are usually implemented using pure combinational logic. To compute the residue of a number X (in binary representation) with respect to modulus m, we utilize the same principle of Equation (2.3), i.e. evaluate the values  $|2^j|_m$ . The only difference here is that m is restricted to  $2^n$ ,  $2^n - 1$ , and  $2^n + 1$ . We shall derive simple formulas that facilitate the algorithm used to obtain the residues. We show how the residues with respect to the special moduli can be obtained with reduced complexity algorithms and architectures.

#### Modulus 2<sup>n</sup>

Obtaining the residue of X with respect to modulus  $2^n$  is the easiest operation. To understand that, recall that the basic principle in residue computation is division. When the divisor is a power of two  $(2^n)$ , the division is further simplified to n-bit right shifting. Thus, the residue of X with respect to  $2^n$  is simply the first n least significant bits of the binary representation of X.

#### Example 2.2.

Let X = 2456 which has the 12-bit binary representation: 100110011000. We want to find the residue of X with respect to modulus  $m = 2^4 = 16$ .

The residue is simply the first four least significant bits of *X*:

$$|X|_{16} = (1000)_2 = 8$$

Modulus  $2^n - 1$

The computation of the residue with respect to modulus  $2^n - 1$  is also easy to implement. The only extra overhead is the need for adding an end-around carry in some cases. Many architectures are available to compute the residue with respect to  $2^n - 1$  [4,5].

In order to understand the operation of evaluating  $|X|_{2^{n}-1}$ , we notice that:

$$|2^{n}|_{2^{n}-1} = |(2^{n}-1)+1|_{2^{n}-1} = ||2^{n}-1|_{2^{n}-1}+|1|_{2^{n}-1}|_{2^{n}-1} = |0+1|_{2^{n}-1} = 1$$

(2.6) where  $n > 1$

The same concept can be applied to  $|2^{qn}|_{2^{n}-1}$  where q is an integer:

$$|2^{qn}|_{2^{n}-1} = \left| \prod_{n=1}^{q} |2^{n}|_{2^{n}-1} \right|_{2^{n}-1} = 1 \tag{2.7}$$

Thus, for  $m \neq n$ , the residue of  $2^m$  with respect to  $2^n - 1$  can be determined as follows:

$$|2^{m}|_{2^{n}-1} = |2^{qn+r}|_{2^{n}-1} = ||2^{qn}|_{2^{n}-1} + |2^{r}|_{2^{n}-1}|_{2^{n}-1} = |2^{r}|_{2^{n}-1}$$

(2.8)

where r is the remainder from the division of m by n.

#### Example 2.3.

Consider  $X = 2^9$ , and  $m = 2^4 - 1$ . We want to find the residue of X with respect to m.

Here: n = 4, m = 9, q = 2, and r = 1.

$$|2^{9}|_{2^{4}-1} = ||2^{2\times 4}|_{2^{4}-1} + |2^{1}|_{2^{4}-1}|_{2^{4}-1} = 2$$

$Modulus 2^n + 1$

In a similar procedure to modulus  $2^n - 1$ , we obtain the residue of X with respect to modulus  $2^n + 1$  as follows:

First, we notice that:

$$|2^{n}|_{2^{n}+1} = |(2^{n}+1)-1|_{2^{n}+1} = ||2^{n}+1|_{2^{n}+1} - |1|_{2^{n}-1}|_{2^{n}+1} = -1$$

(2.9)

Equation (2.9) can be extended for  $m \neq n$  and m = qn + r, where q is an integer, and r is the remainder from the division of m by n:

$$|2^{qn+r}|_{2^{n}+1} = ||2^{qn}|_{2^{n}+1} + |2^{r}|_{2^{n}+1}|_{2^{n}+1} = \begin{cases} 2^{r} & : q \text{ is even} \\ 2^{n}+1-2^{r} : q \text{ is odd} \end{cases}$$

(2.10)

The need for adding  $2^n + 1$  where q is odd comes from the fact that  $|2^{qn}|_{2^n + 1} = -1$  for odd values of q. Therefore, to make the residue positive, we need to add  $2^n + 1$ .

#### Example 2.4.

Consider  $X = 2^9$ , and  $m = 2^4 + 1$ . We want to find the residue of X with respect to m.

Here: n = 4, m = 9, q = 2 (even), and r = 1.

$$|2^{9}|_{2^{4}+1} = ||2^{2\times4}|_{2^{4}+1} + |2^{1}|_{2^{4}+1}|_{2^{4}-1} = 2$$

#### Example 2.5.

Let  $X = 2^{13}$ , and  $m = 2^4 + 1$ . We want to find the residue of X with respect to m.

Here: n = 4, m = 13, q = 3 (odd), and r = 1.

$$|2^{13}|_{2^4+1} = ||2^{3\times4}|_{2^4+1} + |2^1|_{2^4+1}|_{2^4+1} = 2^4 + 1 - 2 = 15$$

The Special Moduli-Set  $\{2^n - 1, 2^n, 2^n + 1\}$

By making use of the mathematical principles explained above, a general algorithm is presented to convert X (in binary representation) into RNS representation with respect to the special moduli-set  $\{2^n - 1, 2^n, 2^n + 1\}$  [4,21,22]. We first partition X into 3 blocks, each of n bits:  $B_1$ ,  $B_2$ , and  $B_3$ , where these blocks can be represented as follows:

$$B_1 = \sum_{j=2n}^{3n-1} x_j 2^{j-2n} \tag{2.11}$$

$$B_2 = \sum_{i=n}^{2n-1} x_i 2^{j-n} \tag{2.12}$$

$$B_3 = \sum_{j=0}^{n-1} x_j 2^j \tag{2.13}$$

Thus,

$$X = B_1 2^{2n} + B_2 2^n + B_3 (2.14)$$

The residue  $r_2$  is simply the first n least significant bits, and can be obtained by right shifting X by n-bits.

The residue  $r_3$  is obtained as follows:

$$r_3 = |X|_{2^{n+1}} = |B_1 2^{2n} + B_2 2^n + B_3|_{2^{n+1}}$$

$$= ||B_1 2^{2n}|_{2^{n+1}} + |B_2 2^n|_{2^{n+1}} + |B_3|_{2^{n+1}}|_{2^{n+1}}$$

(2.15)

We notice that:

$$|B_1 2^{2n}|_{2^{n+1}} = ||B_1|_{2^{n+1}} \times |2^{2n}|_{2^{n+1}}|_{2^{n+1}}$$

(2.16)

$$|B_2 2^n|_{2^{n+1}} = ||B_2|_{2^{n+1}} \times |2^n|_{2^{n+1}}|_{2^{n+1}}$$

(2.17)

$B_1$  and  $B_2$  are *n*-bit numbers. Therefore  $B_1$  and  $B_2$  are always less than  $2^n + 1$ . The values

$|X|_{2^{n}+1}$  are obtained as follows:

$$|2^{2n}|_{2^{n+1}} = ||2^{n} + 1 - 1|_{2^{n+1}} \times |2^{n} + 1 - 1|_{2^{n+1}}|_{2^{n+1}} = -1 \times -1 = 1$$

(2.18)

The value  $|2^{2n}|_{2^{n+1}}$  is obtained as follows:

$$|2^{n}|_{2^{n}+1} = |(2^{n}+1)-1|_{2^{n}+1} = ||2^{n}+1|_{2^{n}+1} - |1|_{2^{n}+1}|_{2^{n}+1} = |0-1|_{2^{n}+1} = -1$$

(2.19) Thus,

$$r_3 = |B_1 - B_2 + B_3|_{2^{n+1}} (2.20)$$

In a similar way, the residue  $r_1$  is obtained as follows:

$$r_1 = |X|_{2^{n-1}} = |B_1 2^{2n} + B_2 2^n + B_3|_{2^{n-1}}$$

$$= |B_1 2^{2n}|_{2^{n-1}} + |B_2 2^n|_{2^{n-1}} + |B_3|_{2^{n-1}}|_{2^{n-1}}$$

(2.21)

We notice that:

$$|B_1 2^{2n}|_{2^{n-1}} = ||B_1|_{2^{n-1}} \times |2^{2n}|_{2^{n-1}}|_{2^{n-1}}$$

(2.22)

$$|B_2 2^n|_{2^{n}-1} = ||B_2|_{2^{n}-1} \times |2^n|_{2^{n}-1}|_{2^{n}-1}$$

(2.23)

The values  $|X|_{2^{n}-1}$  are obtained as follows:

$$|2^{2n}|_{2^{n-1}} = ||2^{n} - 1 + 1|_{2^{n-1}} \times |2^{n} - 1 + 1|_{2^{n-1}}|_{2^{n-1}} = 1 \times 1 = 1$$

(2.24)

The value  $|2^{2n}|_{2^{n}-1}$  is obtained as follows:

$$|2^{n}|_{2^{n}-1} = |(2^{n}-1)+1|_{2^{n}-1} = ||2^{n}-1|_{2^{n}-1}+|1|_{2^{n}-1}|_{2^{n}-1} = |0+1|_{2^{n}-1} = 1 (2.25)$$

Thus,

$$r_1 = |B_1 + B_2 + B_3|_{2^n - 1} (2.26)$$

#### *Example 2.6.*

Consider the moduli-set {15, 16, 17}, and  $X = 2456 = (100110011000)_2$ . We want to find the residues  $r_1$ ,  $r_2$ , and  $r_3$ .

First, we need to obtain the blocks  $B_1$ ,  $B_2$ , and  $B_3$  as follows:

$$B_1 = (1001)_2 = 9$$

$B_2 = (1001)_2 = 9$

$B_3 = (1000)_2 = 8$

Then, we obtain the residues as follows:

$$r_2 = B_3 = (1000)_2 = 8$$

$r_1 = |9 + 9 + 8|_{15} = 11$

$r_3 = |9 - 9 + 8|_{17} = 8$

Therefore, the RNS representation of X = 2456 with respect to the moduli-set  $\{15, 16, 17\}$  is  $\{11, 8, 8\}$ .

A typical architecture for the implementation of a forward converter from binary to RNS representation for the special moduli-set  $\{2^n - 1, 2^n, 2^n + 1\}$  is shown in Figure 2.4. The design of modulo adders is briefly described in the next section.

Figure 2.4.  $\{2^n - 1, 2^n, 2^n + 1\}$  forward converter

#### 2.1.3 Modulo Addition

In Sections 2.1 and 2.2, we presented some available architectures for the implementation of forward converters from binary to RNS representation. All these architectures, whether they are based on arbitrary moduli or special moduli, require modulo addition in the conversion process. The modulo adder is one of the basic arithmetic units in RNS operations and converters. The performance of the modulo adder is very critical in the design of forward converters from binary to RNS representation. In this section, we provide a brief introduction to the modulo addition operation. We focus on the high-level design of modulo adders. However, the design of the underlying adder is very important in determining the overall performance of the modulo adder. The underlying adder is a conventional binary adder that can have different forms such as ripple-carry adder (RCA), carry-save adder (CSA), carry-lookahead adder (CLA), parallel prefix adder, and so on. Different modulo adders based on different conventional adder topologies are explained in [4] for more advanced details. Here, we restrict ourselves to the basic architectures.

#### Modulo Adder for an Arbitrary Modulus

For the same word length, a modulo adder is, in general, slower and less efficient than a conventional adder. The basic idea of modulo addition of any two numbers X and Y with respect to an arbitrary modulus m is based on the following relation:

$$|X + Y|_m = \begin{cases} X + Y &: X + Y < m \\ X + Y - m &: X + Y \ge m \end{cases}$$

(2.27)

where  $0 \le X, Y < m$ .

A typical straightforward implementation of Equation (2.27) is shown in Figure 2.5. The addition of X and Y is performed using a conventional adder. This results in an intermediate value S. Another intermediate value S-m is computed using another conventional adder. Subtracting m is performed easily by adding m's compliment ( $\overline{m}$ ). In binary representation,  $\overline{m}$  also represents the value  $2^n - m$ . If X + Y < m, then  $X + Y + \overline{m} < 2^n$ , and the carry-out ( $C_{\text{out}}$ ) is equal to 0. If  $X + Y \ge m$ , then  $X + Y + \overline{m} = (X + Y - m) + 2^n$ , and since  $X + Y - m \ge 0$ , a carry-out propagates in this case. The value of  $C_{\text{out}}$  instructs the multiplexer (MUX) to select the proper value between S and S - m.

Figure 2.5. Modulo-*m* adder

#### Modulo Adder for Special Moduli

The use of some special moduli instead of arbitrary moduli simplifies the design of the modulo adder and makes it more efficient. Here, we present the modulo addition operation for the special moduli:  $2^n$ ,  $2^n - 1$ , and  $2^{n+1}$ . We show some available architectures in the literature for the special moduli modulo adders.

#### Modulo 2<sup>n</sup> Adder

Modulo  $2^n$  addition is the easiest modulo addition operation in the residue domain because it does not require any extra overhead compared to the conventional addition. Modulo  $2^n$  addition of any two numbers X and Y, each of n bits, is done by adding the two numbers using a conventional adder. The result is an n + 1 bit output, where the most significant bit is the carry-out. The residue is the first n lowest significant bits, and the final carry-out is neglected. Therefore, modulo  $2^n$  addition is the most efficient modulo addition operation in the residue domain.

#### Example 2.7.

We want to compute the following modulo additions:

- a) (3+4) mod (8)

- b) (5+6) mod (8)

Since  $8 = 2^3$ , the result is simply the least three significant bits of the conventional addition, and the final carry-out is neglected.

a) (3+4)mod (8) is computed as follows:

b) (5+6) mod (8) is computed as follows:

#### $Modulo\ 2^n - 1\ Adder$

The modulo  $2^n - 1$  adder is an important arithmetic unit in RNS because  $2^n - 1$  is a commonly used modulus in most special moduli-sets, e.g.  $\{2^n - 1, 2^n, 2^n + 1\}$ . Some architectures to implement the  $2^n - 1$  modulo addition are available in the literature. Here, we shall present the basic idea behind these algorithms and architectures.

To understand the operation of modulo  $2^n - 1$  addition of any two numbers X and Y, where

$0 \le X, Y < m$ , we need to distinguish between three different cases:

- a)  $0 \le X + Y < 2^n 1$

- b)  $X + Y = 2^n 1$

- c)  $2^n 1 < X + Y < 2^{n+1} 2$

In the first case, the result of the conventional addition is less than the upper limit  $2^n - 1$  and no carry-out ( $C_{out}$ ) is generated at the most significant bit. In this case, the modulo addition of X and Y is equivalent to the conventional addition. In the second case, the result is equal to  $2^n - 1$  (i.e. all 1's in binary representation). However, from RNS definition, the result has to be less than  $2^n - 1$ . In this case, the result should be zero. This case can be detected when all bits of the resulting number are ones (i.e. all  $P_i = x_i \oplus y_i$  are ones). Correction is done simply in this case by adding a one and neglecting the carry-out. In the third case, the result of the conventional addition exceeds  $2^n - 1$  and a carry-out is generated at the most significant bit. This case is easily detected by the carry-out. Correction is done by ignoring the carry-out (equivalent to subtracting  $2^n$ ) and adding 1 to produce the correct result.

#### Example 2.8.

We want to find the following modulo  $2^n - 1$  addition operations. Let n = 5, and so the modulus is 31.

- a) (7 + 12) mod (31)

- b) (15+16) mod (31)

- c) (15+18) mod (31)

In part (a): 7 + 12 = 19 < 31, therefore no correction needed, and the residue is obtained as follows:

In part (b): 15 + 16 = 31, then:

Since  $P_i = x_i \oplus y_i = 1$  for all all *i*'s, we need to add 1 to the answer and ignore the final carry-out to obtain the desired value.

In part (c): 15 + 18 = 33 > 31, then:

A carry-out is generated which indicates that the result exceeds 31. To correct the result, we ignore the final carry-out and add 1 to the result.

A possible implementation of modulo  $2^n - 1$  adder using ripple-carry adder (RCA) principle is shown in Figure 2.6. Correction is done by feeding 1 into the carry-in ( $C_{in}$ ) of the first full-adder (FA) if one of the following two cases is detected:

- a)  $P_i = x_i \oplus y_i = 1$  for all all *i*'s

- b)  $C_{out}=1$

Figure 2.6. Modulo  $2^n - 1$  adder

In practice, the architecture in Figure 2.6. suffers from race condition because of the feedback. To avoid that, the operation can be done in two cycles where the intermediate output is latched in the first cycle.

#### $Modulo\ 2^n + 1\ Adder$

The modulo  $2^n + 1$  adder is the bottleneck of the design of a forward converter from binary to RNS representation for the special moduli-set  $\{2^n - 1, 2^n, 2^n + 1\}$ . Its importance arises from the fact that designing an efficient modulo  $2^n + 1$  adder is more difficult than that of the other two moduli. This is due to difficulties in detecting when the result is equal to  $2^n + 1$  and when it exceeds  $2^n + 1$ .

In a similar way to that used in modulo  $2^n - 1$  addition, three cases have to be distinguished [4]. First, we define Z as follows:

$$Z = X + Y - (2^n + 1) (2.28)$$

Then, we define the three cases as follows:

- a)  $X + Y \ge 2^n + 1$  (i. e.  $Z \ge 0$ )

- b)  $X + Y = 2^n (i.e.Z = -1)$

- c)  $X + Y < 2^n + 1$  and  $X + Y \neq 2^n$  (i. e. Z < 0 but  $Z \neq -1$ )

In the first case,  $(X + Y)mod(2^n + 1)$  is simply equal to Z. In the second case,  $(X + Y)mod(2^n + 1)$  is obtained from Z by setting the most significant bit of Z to 1 and adding 1 to the result. In the third case, Z is negative, and  $(X + Y)mod(2^n + 1)$  is obtained from Z by setting the most significant bit to 0 and adding 1 to the result. In summary:

$$|X+Y|_{2^{n}+1} = \begin{cases} Z & : Z \ge 0\\ 2^{n} + |Z+1|_{2^{n}} : Z = -1\\ |Z+1|_{2^{n}} & : otherwise \end{cases}$$

(2.29)

#### Example 2.9.

We want to compute the following modulo  $2^n + 1$  addition operations. Let n = 4 and so the modulus is  $2^n + 1 = 17$ .

- a) (7+14) mod(17)

- b) (10+6)mod(17)

- c) (7+4) mod(17)

In part (a):

$$Z = 7 + 14 - 17 = 4 \ge 0$$

, then  $(7 + 14) mod(17) = 4$

In part (b):  $Z = 10 + 6 - 17 = -1 = (11111)_2$

We set the most significant bit to 1, and add 1 to the result:

In part (c):

$$Z = 7 + 4 - 16 = -6 = (11010)_2$$

,  $Z < 0$  and  $Z \neq -1$

We set the most significant bit to 0: (01010)<sub>2</sub>, and add 1 to the result:

A possible architecture for implementing a modulo  $2^n + 1$  adder is proposed in [4]. The architecture is shown in Figure 2.7. A carry-save adder (CSA) reduces the three inputs X, Y, and  $-(2^n + 1)$  to two: partial sum ( $\check{S}$ ) and partial carry ( $\check{C}$ ). The two values  $\check{S}$  and  $\check{C}$  are then processed using a parallel-prefix adder. Case (b) is detected if  $P_0^n = P_0 P_1 \dots P_n = 1$ . Then, the correction is done by adding  $P_0^n$  as an end-around carry and setting  $S_n = P_0^n$ . Case (c) is detected if  $C_{n-1}$  and therefore  $C_n$  is 0. The correction is done in this case by adding the inverse of the end-around carry  $\overline{C_n}$  and setting  $S_n$  to zero.

Figure 2.7.  $Modulo 2^n + 1$  adder

# 2.2 Reverse Conversion from RNS to Binary Representation

Reverse conversion algorithms in the literature are all based on either Chinese Remainder Theorem (CRT) or Mixed-Radix Conversion (MRC). The MRC is an inherently sequential approach. On the other hand, the CRT can be implemented in parallel. The main drawback of the CRT based R/B reverse converter, is the need of a large modulo adder in the last stage. All the converters proposed in the literature have this problem. The reverse conversion is one of the most difficult RNS operations and has been a major, if not the major, limiting factor to a wider use of RNS [4]. In general, the realization of a VLSI implementation of R/B converters is still complex and costly. Here, we derive the mathematical foundations of the CRT and the MRC, and then we present possible implementations of these methods in reverse conversion.

#### 2.2.1 Chinese Remainder Theorem

The statement of the Chinese Remainder Theorem (CRT) is as follows [4]:

Given a set of pair-wise relatively prime moduli  $\{m_1, m_2, ..., m_n\}$  and a residue representation  $\{r_1, r_2, ..., r_n\}$  in that system of some number X, i.e.  $r_i = |X|_{m_i}$ , that number and its residues are related by the equation:

$$|X|_{M} = \left| \sum_{i=1}^{n} r_{i} |M_{i}^{-1}|_{m_{i}} M_{i} \right|_{M}$$

(2.30)

where M is the product of the  $m_i$ 's, and  $M_i = M/m_i$ . If the values involved are constrained so that the final value of X is within the dynamic range, then the modular reduction on the left-hand side can be omitted.

To understand the formulation of Equation (2.30), we rewrite X as:

$$\begin{split} X &\triangleq \{r_1, r_2, \dots, r_n\} \\ &\triangleq \{r_1, 0, \dots, 0\} + \{0, r_2, \dots, 0\} + \dots + \{0, 0, \dots, r_n\} \\ &\triangleq X_1 + X_2 + \dots + X_n \end{split}$$

Hence, the reverse conversion process requires finding  $X_i$ 's. The operation of obtaining each  $X_i$  is a reverse conversion process by itself. However, it is much easier than obtaining X.

Consider now that we want to obtain  $X_i$  from  $\{0,0,...,r_i,...,0,0\}$ . Since the residues of  $X_i$  are zeros except for  $r_i$ . This dictates that  $X_i$  is a multiple of  $m_j$  where  $j \neq i$ . Therefore,  $X_i$  can be expressed as:

$$X_i \triangleq r_i \times \{0,0,\ldots,1,\ldots,0,0\} \triangleq r_i \times \widetilde{X}_i$$

where  $\widetilde{X}_t$  is found such that  $\left|\widetilde{X}_t\right|_{m_i} = 1$ . We recall from Equation (1.15) that the relation between the number  $r_i$  and its inverse  $r_i^{-1}$  is as follows:

$$(r_i \times r_i^{-1}) \mod m_i = 1$$

We define  $M_i$  as  $M/m_i$ , where  $M = \prod_{i=1}^n m_i$ . Then:

$$\left| \left| M_i^{-1} \right|_{m_i} M_i \right|_{m_i} = 1$$

Since all  $m_i$ ,'s are relatively prime, the inverses exist:

$$\widetilde{X}_i = \left| M_i^{-1} \right|_{m_i} M_i$$

and

$$X_i = r_i \widetilde{X}_i = r_i \big| M_i^{-1} \big|_{m_i} M_i$$

$$X = \sum_{i=1}^{n} X_i = \sum_{i=1}^{n} r_i |M_i^{-1}|_{m_i} M_i$$

To ensure that the final value is within the dynamic range, modulo reduction has to be added to both sides of the equation. The result is Equation (2.30).

## Example 4.1.

Consider the moduli-set  $\{3,4,5\}$ . To find the conventional representation of the residue-set  $\{2,3,1\}$  with respect to the given moduli-set using the CRT, we first determine  $M_i$ 's:

$$M_{1} = \frac{M}{m_{1}}$$

$$= \frac{3 \times 4 \times 5}{3}$$

$$= 20$$

$$M_{2} = \frac{M}{m_{2}}$$

$$= \frac{3 \times 4 \times 5}{4}$$

$$= 15$$

$$M_{3} = \frac{M}{m_{3}}$$

$$= \frac{3 \times 4 \times 5}{5}$$

= 12

and their inverses:

$$|M_1 \times M_1^{-1}|_3 = 1$$

$|20 \times M_1^{-1}|_3 = 1$

$M_1^{-1} = 2$

Similarly:

$$|M_2 \times M_2^{-1}|_4 = 1$$

$|15 \times M_2^{-1}|_4 = 1$

$M_2^{-1} = 3$

and:

$$|M_3 \times M_3^{-1}|_5 = 1$$

$|12 \times M_3^{-1}|_5 = 1$

$M_3^{-1} = 3$

Using Equation (2.30):

$$X = \left| \sum_{i=1}^{3} r_i |M_i^{-1}|_{m_i} M_i \right|_{60}$$

$$= |2 \times 20 \times 2 + 3 \times 15 \times 3 + 1 \times 12 \times 3|_{60}$$

$$= 11$$

We notice from Equation (2.30) that implementing the CRT requires three main steps:

- Obtaining  $M_i$ 's and their inverses  $M_i^{-1}$ 's.

- Multiply-and-Accumulate operations

- Modular reduction

Since there is no general method to obtain  $M_i^{-1}$  using Equation (1.15), the best way to implement it is to save the constants  $X_i = \left| M_i^{-1} \right|_{m_i} M_i$  in a ROM. These constants are then multiplied with the residues  $(r_i)$  and added using a modulo M adder. This is a straightforward implementation of Equation (2.30). The resulting architecture has two main drawbacks when the dynamic range is large: one, large or many multipliers are required to multiply the constants  $X_i$  by the residues; two, a large modulo M adder is required at the final stage. One possible

remedy to obviate the delay and the cost of large or many multipliers is to replace them with ROMs (look-up tables). All possible values of  $r_iX_i$  are stored in the ROMs. This solves one of the drawbacks mentioned above. However, the need for a multi-operand modulo M adder at the final stage is inevitable.

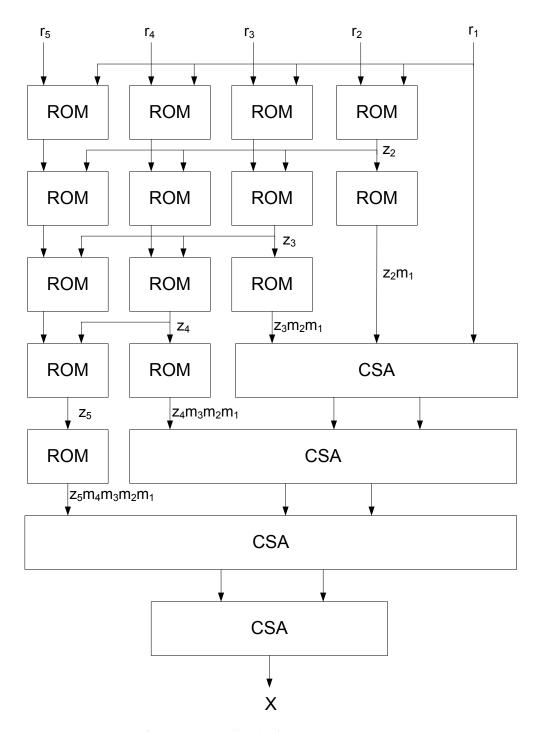

The modulo *M* adder can be realized using ROMs [23], pure combinational logic, or a combination of both. When the dynamic range is large, the speed and the complexity of the multi-operand modulo *M* adder becomes the bottleneck of the design of the R/B converter. Most of the available CRT based R/B converters have the general high-level block diagram shown in Figure 2.8.

Figure 2.8. CRT based R/B converter

#### 2.2.2 Mixed-Radix Conversion

Given a set of pair-wise relatively prime moduli  $\{m_1, m_2, ..., m_n\}$  and a residue representation  $\{r_1, r_2, ..., r_n\}$  in that system of some number X, i.e.  $r_i = |X|_{m_i}$ , that number X can be uniquely represented in mixed-radix form as [4,24]:

$$X = \{z_1, z_2, ..., z_n\}$$

where

$$X = z_1 + z_2 m_1 + z_3 m_2 m_1 + \ldots + z_n m_{n-1} m_{n-2} \dots m_1$$

and  $0 \le z_i < r_i$ . (2.31)

The Mixed-Radix Conversion (MRC) establishes an association between the unweighted, non-positional RNS and a weighted, positional mixed-radix system. All what is required to perform the reverse conversion is to obtain the values  $z_i$ .

The first value  $z_1$  is obtained by applying modulo  $m_1$  reduction on both sides of Equation (2.31):

$$|X|_{m_1} = z_1 = r_1$$

The value  $z_2$  is obtained by rewriting Equation (2.31) as follows:

$$X - z_1 = z_2 m_1 + \dots + z_n m_{n-1} m_{n-2} \dots m_1$$

and then applying modulo  $m_2$  reduction on both sides:

$$|X - z_1|_{m_2} = |z_2 m_1|_{m_2}$$

Multiplying both sides by  $|m_1^{-1}|_{m_2}$  yields:

$$\left| |m_1^{-1}|_{m_2} (X - z_1) \right|_{m_2} = |z_2|_{m_2} = z_2$$

but:

$$|X - z_1|_{m_2} = ||X|_{m_2} - |z_1|_{m_2}|_{m_2} = |r_2 - z_1|_{m_2}$$

Therefore,

$$z_2 = \left| |m_1^{-1}|_{m_2} (r_2 - z_1) \right|_{m_2}$$

The value  $z_3$  is obtained in a similar way:

$$z_3 = \left| \left| (m_2 m_1)^{-1} \right|_{m_3} (r_3 - (z_2 m_1 + z_1)) \right|_{m_2}$$

In general:

$$z_n = \left| \left| (m_n \dots m_2 m_1)^{-1} \right|_{m_n} (r_n - (r_{n-1} m_{n-2} \dots z_2 m_1 + z_1)) \right|_{m_n}$$

We notice from the above equations that the MRC is an inherently sequential approach, where obtaining  $z_i$  requires generating  $z_{i-1}$  first. This is the main drawback of the MRC approach. On the other hand, the CRT allows parallel computation of the partial sums  $X_i$ 's which results in faster conversion.

#### Example 4.2.

Consider the moduli-set {3,4,5}. To find the conventional representation of the residue-set {2,3,1} with respect to the given moduli-set using MRC, we determine the required inverses:

First, we determine  $|m_1^{-1}|_{m_2}$  as follows:

$$\begin{aligned} \left| |m_1^{-1}|_{m_2} m_1 \right|_{m_2} &= 1 \\ \left| |m_1^{-1}|_{m_2} \times 3 \right|_4 &= 1 \\ |m_1^{-1}|_{m_2} &= 3 \end{aligned}$$

Similarly, we determine  $|(m_2m_1)^{-1}|_{m_3}$ :

$$\begin{aligned} \left| |(m_2 m_1)^{-1}|_{m_3} (m_2 m_1) \right|_{m_3} &= 1 \\ \left| |(m_2 m_1)^{-1}|_{m_3} \times 12 \right|_5 &= 1 \\ \left| (m_2 m_1)^{-1}|_{m_3} &= 3 \end{aligned}$$

The values  $z_1$ ,  $z_2$ , and  $z_3$  are obtained as follows:

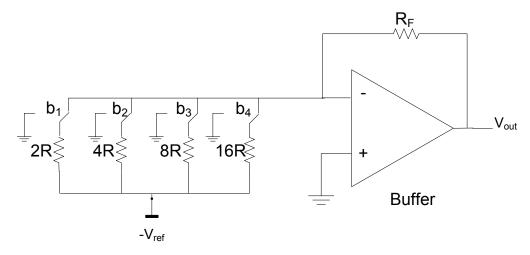

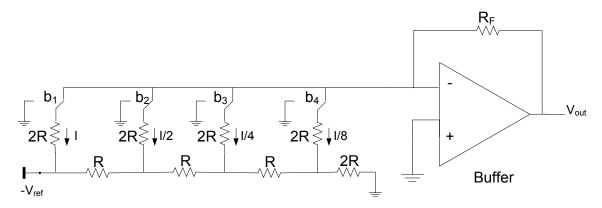

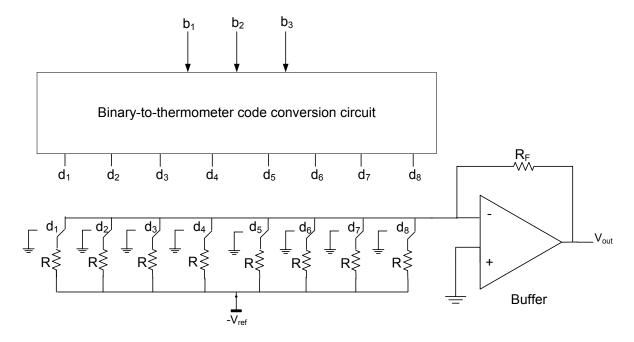

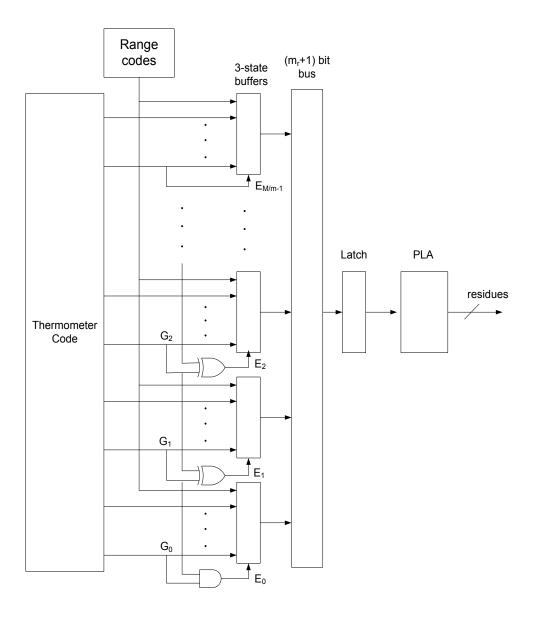

$$z_{1} = r_{1} = 2$$