# Low-Power High-Speed High-Resolution Delta-Sigma Modulators for Digital TV Receivers in nanometer CMOS

Mostafa A. N. Haroun

Department of Electrical and Computer Engineering

McGill University, Montreal

April 2014

A thesis submitted to McGill University in partial fulfilment of the requirements of the degree of Doctor of Philosophy

© Mostafa A.N. Haroun, 2014

# Abstract

The continuing advance in portable digital communication services is fuelling interest in analog-to-digital converters (ADCs) with high speed and high resolution. Moreover, the use of high-speed high-resolution ADCs allows part of the signal processing to be done in the digital domain allowing for higher system integration and cheaper fabrication. Becoming more in use, hand-held devices have low-power requirements to allow for longer battery life. Furthermore, designing ADCs in nanometer digital CMOS technologies make them more integrable with digital processing blocks and cheaper.

This thesis aims at designing a high-speed (16MS/s conversion rate) high-resolution ( $\approx$ 12bits)  $\Delta\Sigma$  modulator with low-power consumption in nanometer digital CMOS.  $\Delta\Sigma$  modulators can achieve a high resolution in low and medium speed applications. For higher speed applications, the oversampling ratio (OSR) will have to be kept low to avoid power-inefficient design. However, lowering the OSR requires special care in the design starting from the architecture until the full circuit implementation. In nanometer CMOS technologies, analog properties, such as intrinsic gain, degrade which might result in a higher power consumption. Moreover, the low nominal supply voltages associated with such technologies adds more challenges to the design of a low distortion power-efficient  $\Delta\Sigma$  modulator. Targeting a specific resolution, lowering the voltage supply usually results in a higher power consumption. This thesis suggests possible solutions to achieve low power consumption while targeting high-speed applications in nanometer low-voltage-supply environment.

This thesis presents a low-power Discrete-Time (DT)  $\Delta\Sigma$  modulator making use of a single-loop multibit DT digital input-feedforward  $\Delta\Sigma$  architecture. The main feature of this architecture is the reduced signal swings at the output of the integrators which allows the use of a low voltage supply. The low-power Switched-Capacitor (SC) implementation is ensured by using a novel opamp switching technique, optimizing simultaneous opamp's settling in cascaded nondelaying SC integrators, and using non-overlapping clock phases with unequal duty-cycles. The novel opamp switching technique is based on a current-mirror opamp with

switchable transconductances. The current-mirror opamp works with full current during the charge-transfer phase while the output current is partially switched during the sampling phase. Power saving can be achieved while ensuring that the opamp output is available during both phases. The simultaneous settling of series opamps in a two cascaded nondelaying SC integrators scheme is looked at as a two-pole system where power optimization is necessary to ensure minimum power consumption while meeting the settling requirements. The use of clock phases with unequal duty-cycles gives the designer an extra degree of freedom to further power optimize the design.

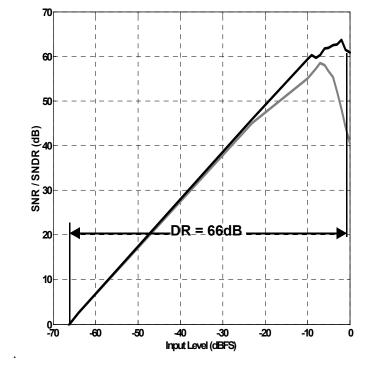

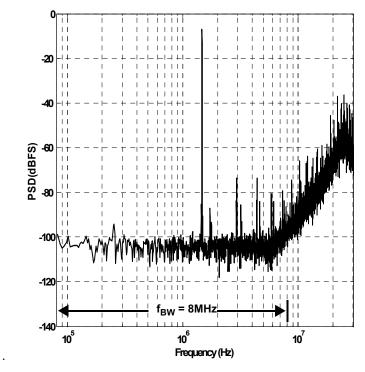

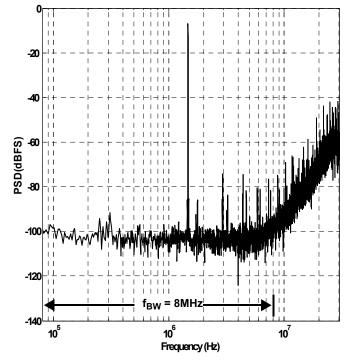

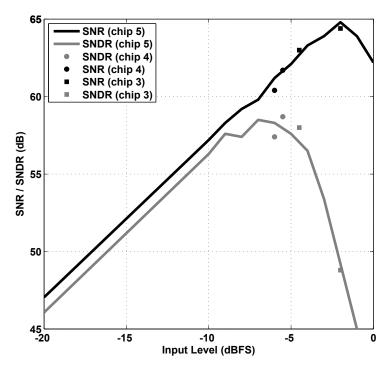

The experimental  $\Delta\Sigma$  ADC is a 4<sup>th</sup>-order 5.5bits single-loop  $\Delta\Sigma$  modulator with an OSR of 8. The design starts with the structural-level aspects in which system-level decisions are made and simulations are carried-out with behavioral models to find the suitable circuit parameters. Circuit-level design in then considered to design each block and simulate the full-system. Fabricated in 1V 65nm CMOS, the  $\Delta\Sigma$  modulator prototype occupies an active area of 1.2mm<sup>2</sup>. Although the targeted resolution is about 12bits, the experimental results shows a dynamic range (DR) of 66dB ( $\approx$ 11bits) over an 8MHz bandwidth while consuming 26mW and a peak SNR/SNDR of 64/58.5dB. The proposed opamp switching technique brings the total power consumption from 29mW to 26mW without affecting the performance (SNDR stays at 58.5dB). The deviation in experimental performance, from simulations, in thought to be due to higher parasitic capacitance requiring higher bias currents which results in drop of opamp dc gain. Compared to state of the art high-speed high-resolution  $\Delta\Sigma$  modulators operated from 1V supply and fabricated in CMOS, it achieves a reasonable Figure-of-Merit.

## Résumé

La progression des services de communication numériques portables augmente l'intérêt dans les convertisseurs analogique-numérique (CAN) à haute vitesse et à haute résolution. En outre, l'utilisation de CAN à haute vitesse et à haute résolution permet à une partie du traitement du signal d'être accompli dans le domaine numérique permettant une meilleure intégration du système et un cout de fabrication moins élevé. De plus en plus utilisés, les appareils portatifs ont des exigences de faible consommation pour permettre une plus longue durée de vie de batterie. En plus, la conception CAN en technologies CMOS numériques les rendent plus intégrable avec les blocs de traitement numérique et les rendent moins cher.

Cette thèse vise à concevoir un modulateur  $\Delta\Sigma$  à haute vitesse (taux de conversion de 16MS/s) et à haute résolution ( $\approx$ 12bits) et aussi à faible consommation d'énergie tout en étant fabriqué en technologie CMOS nanomètrique. Les modulateurs  $\Delta\Sigma$  peuvent atteindre une résolution élevée dans les applications de basse et de moyenne vitesse. Pour les applications plus rapides, le taux de suréchantillonnage devra être maintenu bas pour éviter une conception inefficace. Toutefois, la réduction du taux de suréchantillonnage nécessite un soin particulier à la conception depuis l'architecture jusqu'à la mise en œuvre complète du circuit. Dans les technologies CMOS nanométriques, les propriétés analogiques, telles que le gain intrinsèque, se dégradent ce qui pourrait se traduire à une consommation d'énergie plus élevée. En outre, les tensions d'alimentation nominales basses associées à ces technologies ajoutent de nouveaux défis à la conception d'un modulateur  $\Delta\Sigma$  à distorsion faible et consommation faible. Pour une résolution spécifique, l'abaissement de la tension d'alimentation se traduit généralement à une consommation plus élevée. Cette thèse suggère des solutions possibles pour atteindre une faible consommation tout en ciblant les applications à haute vitesse en milieu nanomètrique avec une alimentation à basse tension.

Cette thèse présente un modulateur  $\Delta\Sigma$  à faible consommation utilisant une architecture multi-bits à entrée "feedforward" numérique. La principale caractéristique de cette architecture est la réduction de la dynamique de signal à la sortie des intégrateurs, ce qui permet

l'utilisation d'une alimentation à basse tension. La mise en œuvre du circuit à condensateurs commutés (SC) à faible consommation est assurée par l'utilisation d'une nouvelle technique de commutation pour l'amplificateur opérationnel (opamp), l'optimisation de la stabilisation simultanée des intégrateurs SC sans délais en cascade, et l'utilisation des phases d'horloge à rapports cycliques inégaux. La technique nouvelle de commutation de l'opamp est basée sur un opamp à miroir de courant avec transconductances commutables. L'opamp à miroir de courant fonctionne en plein courant pendant la phase de transfert de charge tandis que le courant est partiellement commuté pendant la phase d'échantillonnage. Cette technique réduit la consommation et peut être réalisée tout en s'assurant que la sortie de l'opamp est disponible pendant les deux phases. La stabilisation simultanée des opamps en série dans le cas de deux intégrateurs SC sans délais en cascade est traitée comme un système à deuxième ordre où l'optimisation de puissance est nécessaire pour assurer une consommation minimale tout en répondant aux exigences de stabilisation. L'utilisation de phases d'horloge avec rapports cycliques inégaux donne au concepteur un degré de liberté supplémentaire pour optimiser la consommation de la conception.

Le modulateur expérimental de cette thèse est un modulateur  $\Delta\Sigma$  de 4° ordre avec 5.5bits et un taux de suréchantillonnage égal à 8. La conception commence avec les aspects structurels dans lequel des décisions au niveau du système sont prises et des simulations sont rapportées sur des modèles comportementaux pour trouver les paramètres de circuit appropriés. La conception au niveau circuit est examinée pour concevoir chaque bloc et simuler l'ensemble du système. Fabriquée en 65nm CMOS à 1V, ce prototype occupe une surface active de 1,2 mm². Bien que la résolution ciblée est de 12bits, les résultats expérimentaux montrent une gamme dynamique (DR) de 66dB ( $\approx$  11bits) sur une bande de 8MHz tandis que la consommation est de 26mW et le SNR/SNDR maximal est 64/58.5dB. L'écart de performance semble être dû à l'augmentation des condensateurs parasites nécessitant des courants plus élevés, ce qui entraîne la chute de gain de l'opamp. Par rapport aux modulateurs  $\Delta\Sigma$  à haute vitesse et à haute résolution des travaux de pointe opérés à partir d'1V et fabriqués en technologies CMOS, le prototype réalise une figure-de-mérite raisonnable.

# Acknowledgements

First and foremost, all my praise to ALLAH for enabling me to accomplish all that I have accomplished.

I am deeply grateful to my former Ph.D. supervisor Prof. Anas Hamoui (may he rest in peace) for giving me the chance to pursue a degree at McGill University. He guided me throughout most of my Ph.D. journey and taught me a lot, especially, in analog integrated-circuits. I am also very thankful to my current Ph.D. supervisor Prof. Fabrice Labeau for helping me through the last steps of my Ph.D. and for guiding me through my thesis presentation. In addition, I would like to thank my current and former professors who served in my Ph.D. supervisory committee, Prof. Peter Kabal, Prof. Mourad EL-Gamal, and Prof. Vamsy Chodavarapu for their support and advices.

I would like to thank my mother and father for all their tireless efforts and for always encouraging me to excel in all my studies. I would like to thank my wife, Yomna for her love, support, sacrifice and patience throughout my studies. I am also grateful to my parents-in-law for their tremendous support. I also credit our children, Sohaila, Raghad, and Khadija for amazing me and inspiring me. I would like to thank my brothers and sisters for their support and sincere love.

I had the chance to work with many colleagues at McGill University from whom I learnt a lot. In particular, I would like to thank Dr. Mohammad Taherzadeh-Sani, Dr. Philip Chopp, Dr. Mohammad Alghamdi, Mohamed Shaheen, Mohammad Sukhon, Furrookh Ali, Pavel Peev, and Aniroodh Mehta for their useful comments and advices.

Finally, I would like to thank all my friends and beloved ones in Montreal and back home for their continuous encouragements throughout my studies.

I would like to dedicate this work to the memory of Mohamed El Shanawany, victim of oppression, and to the memory of all victims of oppression all over the world.

# Table of Contents

|   | Abs  | tract                                                           | i    |

|---|------|-----------------------------------------------------------------|------|

|   | Rési | ımé                                                             | iii  |

|   | Ack  | nowledgements                                                   | v    |

|   | Tab  | le of Contents                                                  | iii  |

|   | List | of Figures                                                      | ciii |

|   | List | of Tables                                                       | xv   |

|   | List | of Acronyms and Abbreviations                                   | cvi  |

| 1 | Intr | roduction                                                       | 1    |

|   | 1.1  | Motivation                                                      | 1    |

|   | 1.2  | High-Speed High-resolution $\Delta\Sigma$ ADCs                  | 2    |

|   | 1.3  | Thesis Scope and Research Goals                                 | 4    |

|   | 1.4  | Thesis Outline                                                  | 6    |

| 2 | Low  | v-Power Discrete-Time Delta-Sigma Modulators                    | 9    |

|   | 2.1  | $\Delta\Sigma$ Modulation Fundamentals                          | 10   |

|   |      | 2.1.1 $\Delta\Sigma$ Modulation Operation Concepts              | 10   |

|   |      | 2.1.2 $\Delta\Sigma$ Modulators Performance Metrics             | 12   |

|   | 2.2  | Discrete-Time vs. Continuous-Time $\Delta\Sigma$ Modulators     | 14   |

|   | 2.3  | Low-Power Switched-Capacitor Circuit Techniques                 | 14   |

|   | 2.4  | Low-Power Discrete-Time $\Delta\Sigma$ Modulators Architectures | 17   |

|   |      | 2.4.1 Input-Feedforward (IFF) Topology                          | 18   |

|   |      | 2.4.2 Analog-Feedforward (AFF) Implementation                   | 19   |

|   |      | 2.4.3 Digital-Feedforward (DFF) Implementation                  | 20   |

|   | 2.5  | Feedback-Timing Relaxation Techniques                           | 22   |

|   | 2.6  | Conclusion                                                      | 24   |

| 3 | A S  | witchable -Opamp for Low-Power Switched-Capacitor Integrator   |            |

|---|------|----------------------------------------------------------------|------------|

|   | Des  | ign                                                            | <b>2</b> 5 |

|   | 3.1  | Overview and Previous Work                                     | 27         |

|   | 3.2  | A Current-Mirror Opamp with Switchable Transconductances       | 30         |

|   | 3.3  | Circuit Design                                                 | 31         |

|   | 3.4  | Power Savings Analysis                                         | 33         |

|   | 3.5  | Circuit Simulation Results                                     | 39         |

|   |      | 3.5.1 Gain Error of the SC integrator                          | 39         |

|   |      | 3.5.2 Linearity of the SC integrator                           | 41         |

|   |      | 3.5.3 Performance of a DT $\Delta\Sigma$ Modulator             | 42         |

|   | 3.6  | Conclusion                                                     | 44         |

| 4 | Set  | tling of Nondelaying Cascaded Switched-Capacitor Integrators   | 45         |

|   | 4.1  | Overview                                                       | 46         |

|   | 4.2  | Power Optimization of two cascaded nondelaying SC integrators  | 47         |

|   | 4.3  | Settling Glitch "Hesitation"                                   | 52         |

|   | 4.4  | Circuit Design Example                                         | 54         |

|   | 4.5  | Conclusion                                                     | 57         |

| 5 | Sys  | tem-Level Design of the Experimental $\Delta\Sigma$ Modulator  | 59         |

|   | 5.1  | System-Level Design                                            | 60         |

|   | 5.2  | Structural-Level Design                                        | 64         |

|   |      | 5.2.1 Low-Power SC Implementation                              | 64         |

|   |      | 5.2.2 Structural-Level Simulations:                            | 67         |

|   | 5.3  | Behavioral Simulations                                         | 67         |

|   |      | 5.3.1 Design Procedure                                         | 69         |

|   |      | 5.3.2 DAC Nonlinearity                                         | 73         |

|   | 5.4  | Conclusion                                                     | 76         |

| 6 | Circ | cuit-Level Design of the Experimental $\Delta\Sigma$ Modulator | 77         |

|   | 6.1  | Operational Amplifier Design                                   | 78         |

|   | 6.2 | Flash ADCs Design                                            | 85  |

|---|-----|--------------------------------------------------------------|-----|

|   | 6.3 | Sampling and DAC Switches Design                             | 88  |

|   | 6.4 | Digital Circuits Design                                      | 91  |

|   |     | 6.4.1 Digital Addition                                       | 91  |

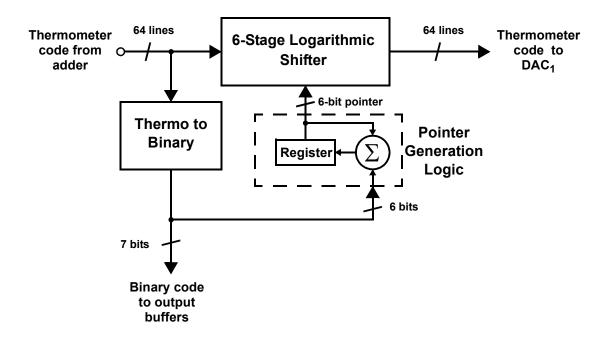

|   |     | 6.4.2 Data Weighted Averaging                                | 92  |

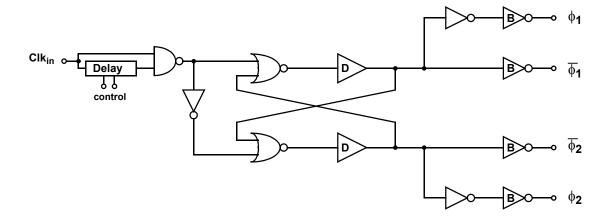

|   |     | 6.4.3 Clock Generation and Duty-Cycle Control                | 93  |

|   | 6.5 | Circuit Simulations Results                                  | 94  |

|   | 6.6 | Conclusion                                                   | 95  |

| 7 | Exp | perimental Results of the $\Delta\Sigma$ Modulator Prototype | 97  |

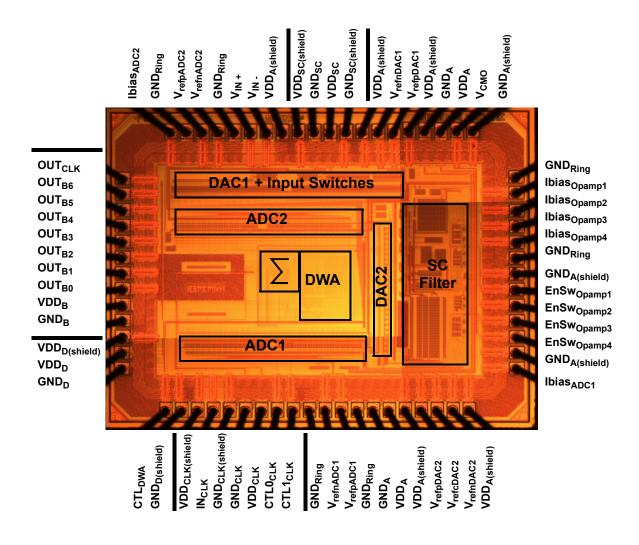

|   | 7.1 | Chip Layout                                                  | 98  |

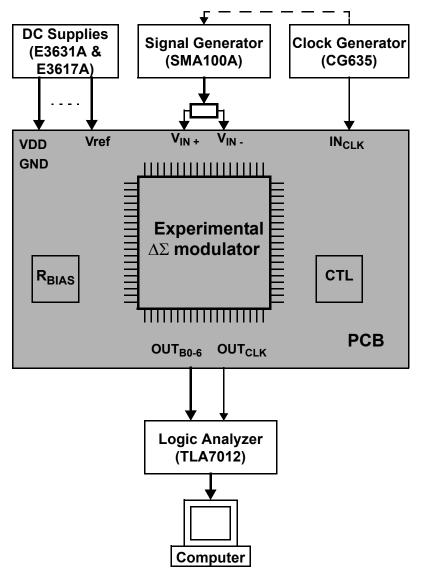

|   | 7.2 | Test Set-Up                                                  | 99  |

|   | 7.3 | Measured Performance                                         | 101 |

|   | 7.4 | Performance Comparison                                       | 106 |

|   | 7.5 | Conclusion                                                   | 107 |

| 8 | Cor | nclusion and Closing Remarks                                 | 109 |

|   | 8.1 | Thesis Summary                                               | 109 |

|   | 8.2 | Research Contributions                                       | 111 |

|   | 8.3 | Future Research Suggestions                                  | 112 |

# List of Figures

| 1.1  | Distribution of the $\Delta\Sigma$ modulators listed in Table 1.1 over $f_{BW}$ and $DR_{bits}$ |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | variations                                                                                      | 5  |

| 1.2  | Distribution of the $\Delta\Sigma$ modulators listed in Table 1.1 over $f_{BW}$ and FoM         |    |

|      | variations                                                                                      | 5  |

| 2.1  | Power spectral density of quantization error                                                    | 11 |

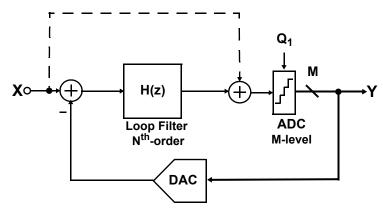

| 2.2  | Block diagram of a single-loop $\Delta\Sigma$ modulator                                         | 11 |

| 2.3  | Linear model of a single-loop $\Delta\Sigma$ modulator                                          | 12 |

| 2.4  | Power spectral density of quantization error in oversampling noise-shaping                      |    |

|      | ( $\Delta\Sigma$ ) ADC                                                                          | 12 |

| 2.5  | A switched-capacitor integrator with the loading effect of its next sampling                    |    |

|      | stage capacitor $C_{S,next}$                                                                    | 15 |

| 2.6  | Block diagram of a single-loop $\Delta\Sigma$ modulator with a single DAC feedback              |    |

|      | and an input feedforward (IFF) path (dashed line)                                               | 18 |

| 2.7  | Analag feedforward (AFF) implementation in an ${\rm N^{th}}\text{-}{\rm order}$ single DAC      |    |

|      | feedback architecture. [Sil01, Ham04b]                                                          | 19 |

| 2.8  | Analag feedforward (AFF) implementation in an ${\rm N^{th}}\text{-}{\rm order}$ multiple DAC    |    |

|      | feedback architecture. [Gag04, Ham04b]                                                          | 20 |

| 2.9  | Digital feedforward (DFF) implementation in an $2^{\mathrm{nd}}$ -order multiple DAC            |    |

|      | feedback architecture. [Kwo06]                                                                  | 21 |

| 2.10 | Digital feedforward (DFF) implementation in an $N^{th}$ -order single DAC                       |    |

|      | feedback architecture. [Ham08b]                                                                 | 22 |

| 2.11 | Timing diagram and available time for DEM in most AFF $\Delta\Sigma$ architecture               |    |

|      | with STF=1 [Kwo07]                                                                              | 23 |

| 2.12 | Timing diagram and available time for DEM in most DFF $\Delta\Sigma$ architecture               |    |

|      | [Kwo07]                                                                                         | 24 |

| 3.1  | A full-delay SC integrator with the loading effect of its next sampling stage        |    |

|------|--------------------------------------------------------------------------------------|----|

|      | capacitor $C_{S,next}$                                                               | 26 |

| 3.2  | A $half$ -delay SC integrator with the loading effect of its next sampling stage     |    |

|      | capacitor $C_{S,next}$                                                               | 26 |

| 3.3  | A full-delay SC integrator during its sampling phase $\phi_1$                        | 27 |

| 3.4  | A full-delay SC integrator during its charge-transfer phase $\phi_2, \ldots, \ldots$ | 27 |

| 3.5  | A half-delay SC integrator during its sampling phase $\phi_1$                        | 28 |

| 3.6  | A half-delay SC integrator during its charge-transfer phase $\phi_2$                 | 28 |

| 3.7  | The conceptual diagram of the switched-opamp method                                  | 29 |

| 3.8  | The conceptual diagram of the partially-switched-opamp method                        | 29 |

| 3.9  | The conceptual diagram of the proposed switchable-opamp                              | 30 |

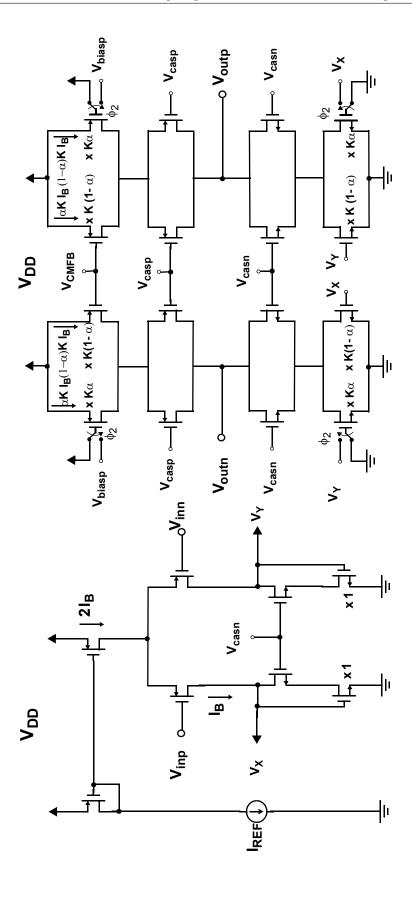

| 3.10 | The circuit diagram of the switchable-opamp                                          | 32 |

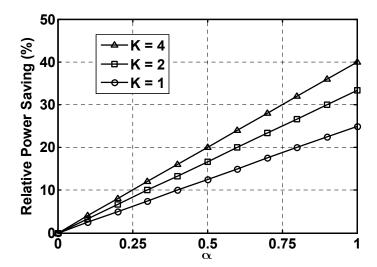

| 3.11 | Relative power-dissipation saving, achieved using the proposed                       |    |

|      | switchable-opamp (Figure 3.10) vs. switching ratio $\alpha$ , for various current    |    |

|      | gains $K$                                                                            | 34 |

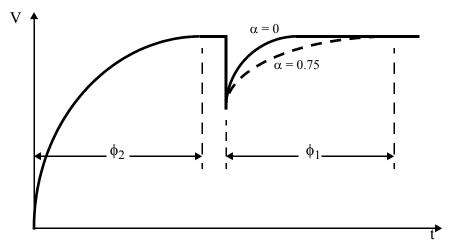

| 3.12 | Effect of switching on output sampling on $C_{S,next}$                               | 41 |

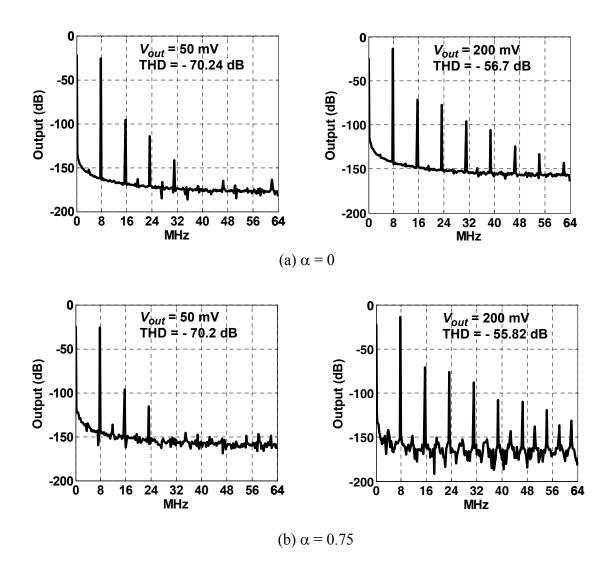

| 3.13 | The output spectrum of the SC integrator with a $20mV$ , and an $80mV$ input         |    |

|      | sinusoid, resulting in an output sinusoid having $V_{out} = 50mV$ and                |    |

|      | $V_{out} = 200mV$ . Two cases are considered for the switching ratio of the          |    |

|      | integrator's opamp: (a) $\alpha = 0$ (No switching), and (b) $\alpha = 0.75$         | 42 |

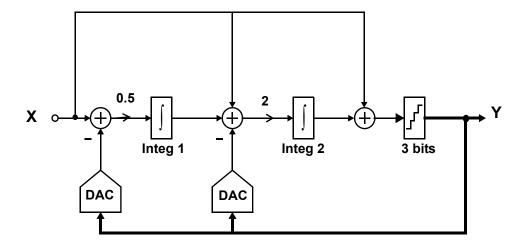

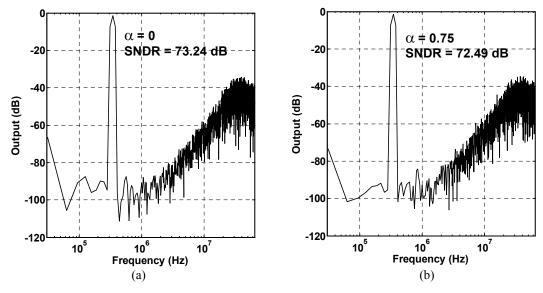

| 3.14 | The simulated second-order 3-bit $\Delta\Sigma$ modulator                            | 43 |

| 3.15 | The output spectrum of the $\Delta\Sigma$ modulator in Figure 3.14, when the opamps  |    |

|      | have a switching ratio of: (a) $\alpha = 0$ (no switching); and (b) $\alpha = 0.75$  | 43 |

| 4.1  | Two cascaded SC integrators with their non-overlapping clock phases $(\phi_1)$       |    |

|      | and $(\phi_2)$                                                                       | 46 |

| 4.2  | Two nondelaying cascaded SC integrators during the charge-transfer phase             |    |

|      | $(\phi_2)$ and the corresponding voltage waveforms for a step input                  | 47 |

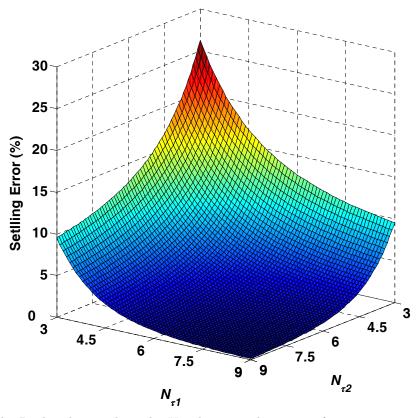

| 4.3  | A 3D plot showing how the $V_3$ relative settling error, for a unit step in          |    |

|      | cascaded SC integrators, changes with $N_{\tau 1}$ and $N_{\tau 2}$                  | 49 |

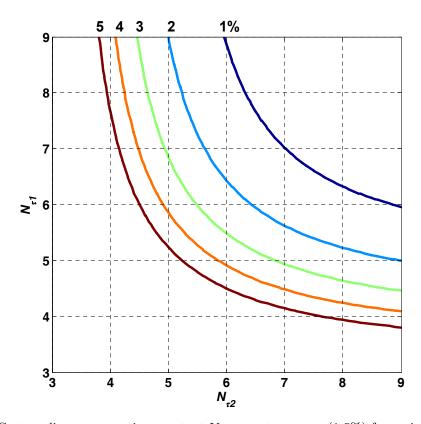

| 4.4 | Contour lines representing constant $V_3$ percentage error (1-5%) for various                        |    |

|-----|------------------------------------------------------------------------------------------------------|----|

|     | $(N_{\tau 1}, N_{\tau 2})$ combinations                                                              | 50 |

| 4.5 | Intersection of contour line for 5% error with constant total current $I_{DD,total}$                 |    |

|     | line at $N_{\tau 1} = 6$ and $N_{\tau 2} = 4.5$                                                      | 51 |

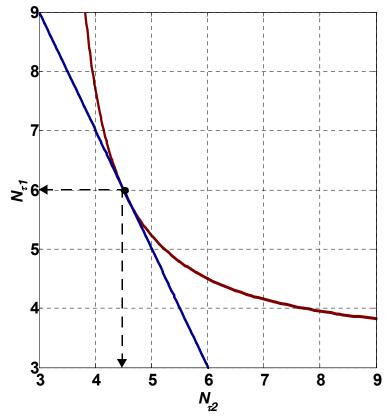

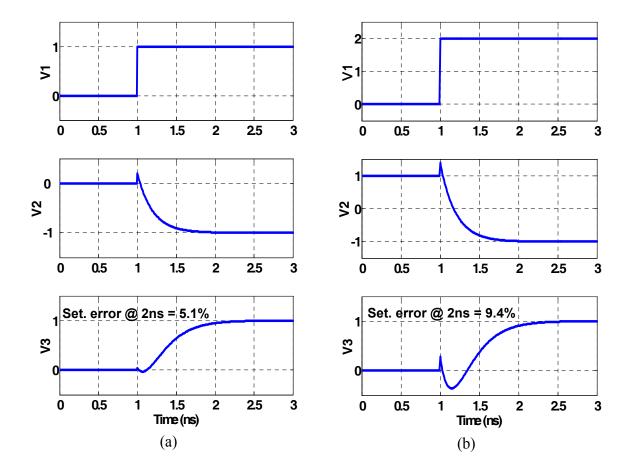

| 4.6 | The nondelaying cascaded SC integrators waveforms $V_1, V_2, \text{ and } V_3 \text{ with: (a)}$     |    |

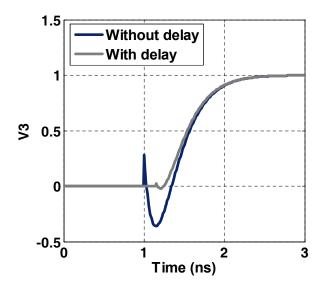

|     | standard input step; (b) excitation creating the "hesitation" at $V_3$                               | 53 |

| 4.7 | Effect of delay introduced between integrators on the settling of $V_3$ when                         |    |

|     | "hesitation" occurs (Matlab simulations)                                                             | 54 |

| 4.8 | Circuit simulation results (1-V 65-nm CMOS process) showing the effect of                            |    |

|     | adding $0.3-ns$ delay between integrators on settling "hesitation"                                   | 56 |

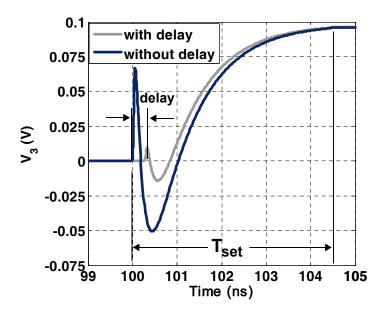

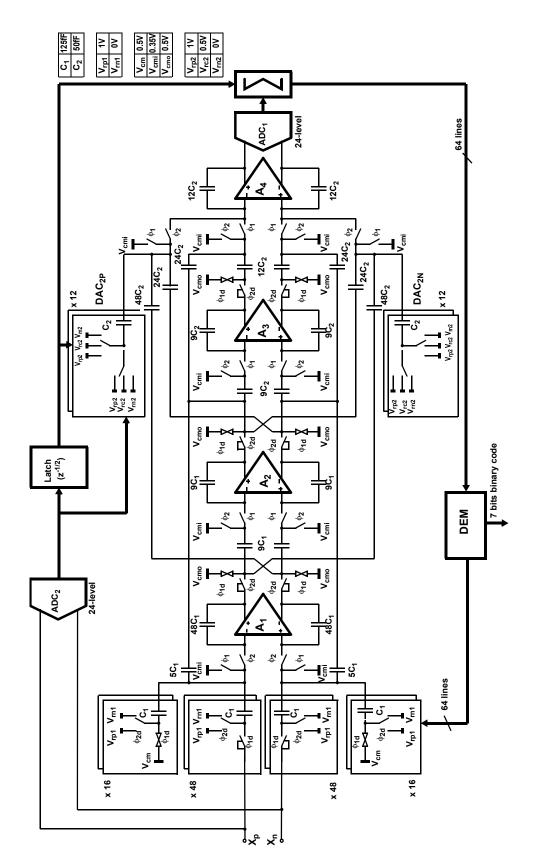

| 5.1 | The experimental 4 <sup>th</sup> -order multibit digitally-enhanced $\Delta\Sigma$ modulator and     |    |

|     | the corresponding coefficient values for an FIR NTF                                                  | 60 |

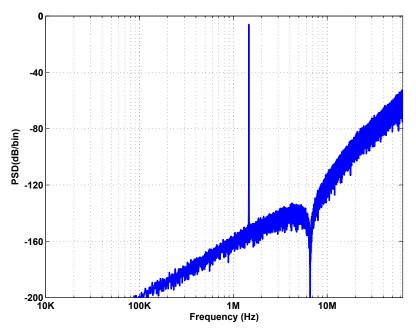

| 5.2 | The PSD of the ideal 4th-order 5.5 bits $\Delta\Sigma$ modulator for a 0dbFS 1.465MHz                |    |

|     | sinusoid simulated by SIMULINK                                                                       | 63 |

| 5.3 | The full-system SC implementation of the experimental 4 <sup>th</sup> -order 5.5 bits $\Delta\Sigma$ |    |

|     | modulator with DFF with the corresponding reference voltage and unit                                 |    |

|     | capacitor values.                                                                                    | 66 |

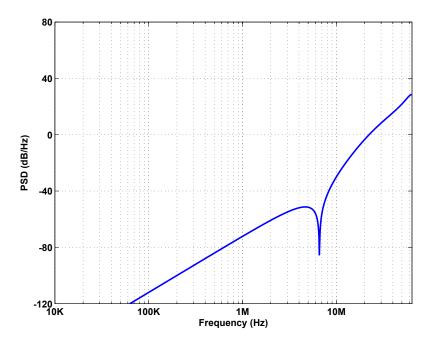

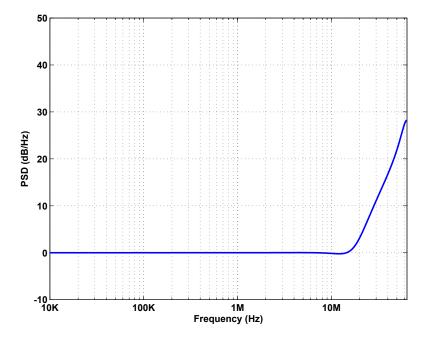

| 5.4 | The NTF simulated by SWITCAP                                                                         | 68 |

| 5.5 | The STF simulated by SWITCAP                                                                         | 68 |

| 5.6 | The output PSD of the $\Delta\Sigma$ modulator with thermal noise and finite BW/SR                   |    |

|     | models for an input with $0dBFS$ at 1.465MHz                                                         | 73 |

| 5.7 | The average PSD for a 50 run Monte-Carlo simulation with $0.5\%$ capacitor                           |    |

|     | mismatch in $DAC_1$ assuming nonlinear opamp models                                                  | 74 |

| 5.8 | The average PSD for a 50 run Monte-Carlo simulation with 0.5% capacitor                              |    |

|     | mismatch in $\mathrm{DAC}_1$ assuming nonlinear opamp models with DWA applied                        | 74 |

| 5.9 | The average PSD for a 50 run Monte-Carlo simulation with 0.5% capacitor                              |    |

|     | mismatch in $DAC_1$ and various nonidelaties and noise sources with DWA                              |    |

|     | applied                                                                                              | 75 |

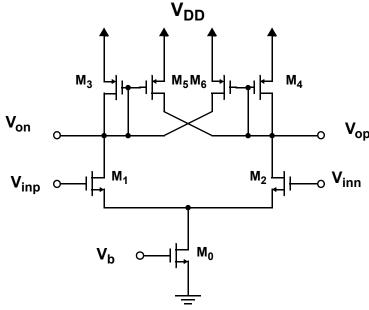

| 6.1  | The used current-mirror opamp and the used biasing circuit. The CMFB                 |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | circuit is not shown in this figure. $I_{REF}$ is implemented as an external         |     |

|      | biasing resistor and a current-mirror near the pad                                   | 80  |

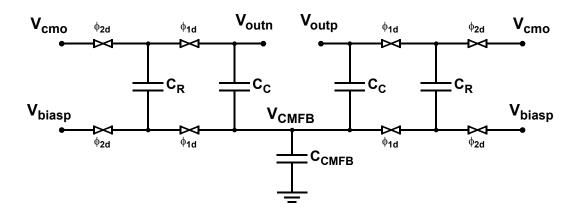

| 6.2  | The used SC common-mode feedback (CMFB) circuit                                      | 83  |

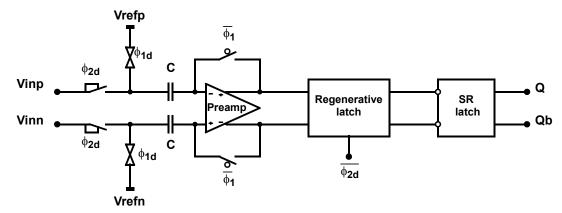

| 6.3  | The differential SC latched comparator used in both ADCs with the                    |     |

|      | corresponding clock phases for $ADC_1$                                               | 85  |

| 6.4  | The preamplifier                                                                     | 86  |

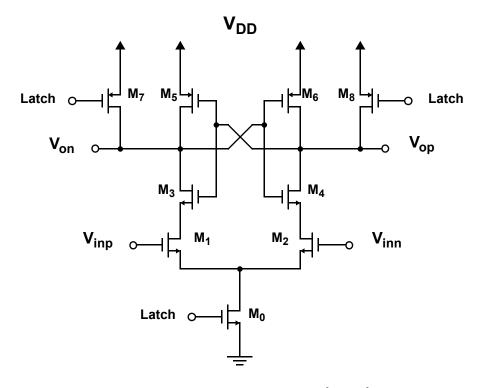

| 6.5  | The regenerative latch                                                               | 87  |

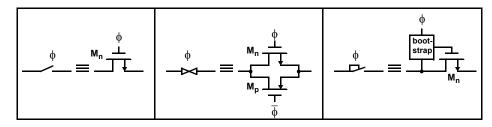

| 6.6  | The different types of switches used in the design                                   | 88  |

| 6.7  | Bootstrap switch [Abo99, Des01]                                                      | 89  |

| 6.8  | DAC switches.                                                                        | 90  |

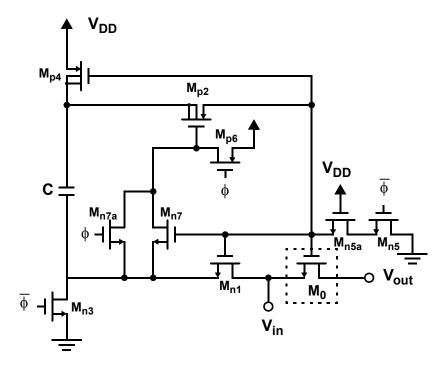

| 6.9  | Conceptual block diagram of the DWA                                                  | 93  |

| 6.10 | Non-overlapping clock generator with duty-cycle control (delayed clock               |     |

|      | phases are not shown for simplicity)                                                 | 94  |

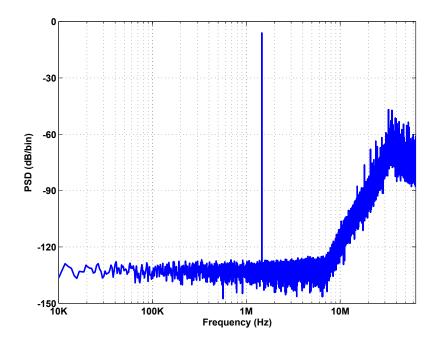

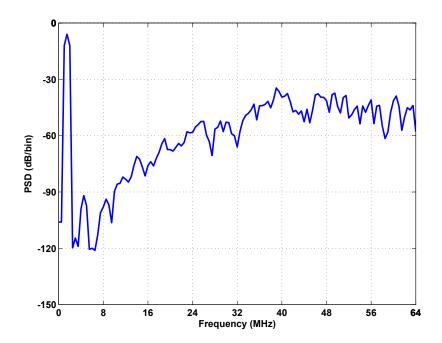

| 6.11 | The output PSD for the full-system circuit simulations for a $1.5\mathrm{MHz}$ input |     |

|      | sinusoid with 0dbFS amplitude                                                        | 95  |

| 7.1  | Chip micrograph of the experimental $\Delta\Sigma$ modulator                         | 98  |

| 7.2  | Experimental test set-up.                                                            | 100 |

| 7.3  | SNR and SNDR versus Input level (dBFS) (opamp switching enabled)                     | 101 |

| 7.4  | The measured output spectrum for -7dBFS 1.465MHz input sinusoid                      | 102 |

| 7.5  | The measured output spectrum for -7dBFS 1.465MHz input sinusoid                      | 102 |

| 7.6  | $\rm SNR$ and $\rm SNDR$ versus Input level (dBFS) for multiple chips at 128MHz      |     |

|      | sampling rate(opamp switching disabled)                                              | 103 |

# List of Tables

| 1.1 | High-speed ( $f_{BW} \ge 2 \text{MHz}$ ) high-resolution (DR or SNR $\ge 62 \text{dB}$ (10bits)) |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | state-of-the-art CMOS $\Delta\Sigma$ ADCs operated from power supplies $V_{DD} \leq 1.2V$        |    |

|     | (last updated in April 2013)                                                                     | 3  |

| 3.1 | The transconductance and current consumption in both $\phi_2$ and $\phi_1$ phase for             |    |

|     | the half-delay integrator employing the SO method                                                | 38 |

| 3.2 | The transconductance and current consumption in both $\phi_2$ and $\phi_1$ phase for             |    |

|     | the half-delay integrator employing the switchable-transconductances                             |    |

|     | technique for different values of $\alpha$                                                       | 38 |

| 3.3 | SC integrator's gain error $\epsilon$ and the achievable power savings using the                 |    |

|     | proposed switchable-opamp for various values of the opamp switching ratio                        |    |

|     | $\alpha$ , at a 50mV and 250mV input steps                                                       | 40 |

| 4.1 | Opamps' scale ratios, transconductances, and current consumptions                                | 55 |

| 4.2 | $V_3$ Settling error variation, from circuit simulations, for different current                  |    |

|     | scales with constant $I_{DD_{total}}$                                                            | 56 |

| 5.1 | Design parameters summary of the experimental $\Delta\Sigma$ modulator                           | 63 |

| 5.2 | Opamps' maximum output swing.                                                                    | 69 |

| 5.3 | Opamps' minimum required DC gain.                                                                | 69 |

| 5.4 | Integrators' sampling capacitor values and required opamp short-circuit                          |    |

|     | transconductance values                                                                          | 72 |

| 6.1 | Transistor sizes of the current-mirror opamps in Figure 6.1                                      | 82 |

| 6.2 | Transistor sizes of the opamp biasing circuits in Figure 6.1                                     | 82 |

| 6.3 | Opamps' loading conditions (capacitive load and feedback factor) and the                         |    |

|     | simulated specifications                                                                         | 83 |

| 6.4 | Capacitor sizes in the SC CMFB circuits                                                          | 83 |

| 6.5 | Transistor sizes of the CMOS switch used for the CMFB circuit.                                   | 84 |

| 6.6  | Power savings in opamps by implementing switching technique                                                                       | 84  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7  | Transistor sizes of the switches used to implement the switching technique                                                        | 84  |

| 6.8  | Transistor sizes of the preamplifier                                                                                              | 86  |

| 6.9  | Transistor sizes of the regenerative latch                                                                                        | 87  |

| 6.10 | Transistor sizes of the bootstrapped switches                                                                                     | 89  |

| 6.11 | Transistor sizes of the bootstrapped switches used in $DAC_1$ and $ADC_{1,2}$                                                     | 89  |

| 6.12 | Transistor sizes of the NMOS switches                                                                                             | 90  |

| 6.13 | Transistor sizes of the CMOS switches                                                                                             | 90  |

| 6.14 | Transistor sizes of the CMOS switches used in $DAC_1$ and $ADC_{1,2}$                                                             | 90  |

| 6.15 | Transistor sizes of the switches used in $DAC_1$ and $DAC_2$                                                                      | 91  |

| 7.1  | Measured Performance comparison between two tested chips for an input level of -5dBFS at 96MHz sampling rate (switching disabled) | 103 |

| 7.2  | Measured Performance summary of the experimental prototype (switching                                                             | 100 |

|      | enabled).                                                                                                                         | 104 |

| 7.3  | Measured Performance comparison between opamp switching enabled and                                                               |     |

|      | disabled                                                                                                                          | 104 |

| 7.4  | Measured Performance comparison between opamp switching enabled and                                                               |     |

|      | disabled                                                                                                                          | 105 |

| 7.5  | Comparison with state-of-the-art high-speed ( $f_{BW} \ge 2 \text{MHz}$ ) high-resolution                                         |     |

|      | (DR or SNR $\geq$ 62dB (10bits)) $\Delta\Sigma$ modulators fabricated in CMOS process                                             |     |

|      | and operated from 1V supply.                                                                                                      | 107 |

# List of Acronyms and Abbreviations

ADC analog-to-digital converter

AFF analog-feedforward

BW bandwidth

CMFB common-mode feedback

CMOS complementary metal-oxide-semiconductor

CT continuous-time

DAC digital-to-analog converter

DEM dynamic element matching

DFF digital-feedforward DS double sampling  $\Delta\Sigma$  delta-sigma

DT discrete-time

DR dynamic range

DWA data weighted averaging FIR finite impulse response

FoM figure of merit

IFF input-feedforward

LSB least significant bit

NTF noise transfer function

OSR oversampling ratio

PCB printed circuit board

PSD power spectral density

PSO partially switched-opamp

SO switched-opamp SC switched-capacitor

SNDR signal-to-noise-and-distortion ratio

SNR signal-to-noise- ratio

SQNR signal-to-quantization-noise ratio

SR slew rate

STF signal transfer function

## Chapter 1

# Introduction

| 1.1 | Motivation                                     | 1 |

|-----|------------------------------------------------|---|

| 1.2 | High-Speed High-resolution $\Delta\Sigma$ ADCs | 2 |

| 1.3 | Thesis Scope and Research Goals                | 4 |

| 1.4 | Thesis Outline                                 | 6 |

The Proliferation of broadband digital communications is stimulating the research towards high-speed (few to tens MS/s conversion rate) analog-to-digital converters (ADCs). Examples of broadband digital communication applications include digital TV such as DVB-T (4MHz), DMB-T (4MHz), ISDB-T (3-4MHz) and LTE standards (5-10-20MHz). The software-defined radio concept is encouraging the transfer of some analog processing to the digital domain for more programmability. This requires high-resolution (10 bits and more of dynamic range) ADCs. The ADCs provide the interface between the digital processing and the analog receiver front-end.

#### 1.1 Motivation

With the current advance in digital mobile applications many digital TV services have been adopted in mobile services such as DVB-H (4MHz), DMB-H (4MHz). The ADCs used in these digital TV receivers for hand-held devices have low-power requirements (few mW to tens of mW) to allow for longer battery lifetimes.

The design of ADCs in modern nanometer digital CMOS processes (such as 65nm CMOS) allows higher system-integration with digital circuitry and lower fabrication cost. This comes at the expense of poor analog properties, such as intrinsic gain, and low supply voltages in such processes.

Although the shrinkage of supply voltage has a desirable effect on power consumption in digital circuits, it is not the case in the analog domain. To explain the idea, let us consider a

2 Introduction

Discrete-Time (DT) Delta-Sigma ( $\Delta\Sigma$ ) modulator with switched-capacitor (SC) implementation with some targeted signal-to-noise-ratio (SNR). The direct effect of supply shrinkage is the lower signal swing which limits the maximum input signal allowed in the system. To meet the targeted SNR, and assuming kT/C thermal noise domination in the  $\Delta\Sigma$  modulator, the sampling capacitor (C) has to be increased to bring the thermal noise down. This, in turn, requires more opamp bandwidth, and hence, more opamp bias current. It can be shown, quantitatively, that lowering the supply voltage results, in this case, in the increase of power consumption to maintain the same SNR [Ham04a]. Another result of lowering the supply voltage in SC circuits is the limited overdrive voltage for the MOS switches since the NMOS and PMOS threshold voltage shrinkage is less than the supply voltage shrinkage. This requires additional circuitry (such as bootstrapping) to maximize signal swing and maintain a good linearity.

$\Delta\Sigma$  ADCs combine oversampling with noise shaping to achieve high resolution. They can achieve high resolution in low and medium speed applications. Recent research has shown interest in extending the  $\Delta\Sigma$  signal bandwidth for high-speed applications while maintaining low power consumption in low-voltage-supply nanometer CMOS processes.

## 1.2 High-Speed High-resolution $\Delta\Sigma$ ADCs

A wide range of high-speed high-resolution  $\Delta\Sigma$  ADCs can be found in the literature. Table 1.1 lists state-of-the-art  $\Delta\Sigma$  ADCs with signal bandwidth  $\geq$  2MHz and dynamic range (or SNR)  $\geq$  62dB (10bits). The survey focuses on  $\Delta\Sigma$  modulators fabricated in modern CMOS and operated from a power supply  $\leq$  1.2V. It was last updated in April 2013.

The table shows the signal bandwidth  $(f_{BW})$  and the sampling frequency  $(f_S)$ . The performance metrics used for comparison are the dynamic range (DR), the signal-to-noise ratio (SNR), and the signal-to-noise-and-distortion ratio (SNDR) (all defined in the next chapter). The power consumption is also listed as well as the supply voltage  $(V_{DD})$ . The table also lists the CMOS processes in which the  $\Delta\Sigma$  ADCs were fabricated and the area it occupies. The architecture used for the  $\Delta\Sigma$  modulator is shown and the implementation, Continuous-Time (CT) or Discrete-Time (DT), is also listed.

Table 1.1: High-speed ( $f_{BW} \geq 2 \mathrm{MHz}$ ) high-resolution (DR or SNR  $\geq 62 \mathrm{dB}$  (10bits)) state-of-the-art CMOS  $\Delta\Sigma$  ADCs operated from power supplies  $V_{DD} \leq 1.2 \mathrm{V}$  (last updated in April 2013).

| Reference | $f_{BW}$ | $f_S$ | DR   | SNR  | SNDR  |      |       | CMOS            | Area              | Input            | Architecture    |

|-----------|----------|-------|------|------|-------|------|-------|-----------------|-------------------|------------------|-----------------|

| reference | (MHz)    | (MHz) | (dB) | (dB) | (dB)  | (mW) | (V)   | Process         | $(\mathrm{mm}^2)$ | DT/CT            | order(bit)      |

| Potential | 8        | 128   | 80   | 78   | 74    | 20   | 1     | $65\mathrm{nm}$ |                   | DT               | 4(5.5b)         |

| [TZ-10]   | 2        | 128   | 75   |      | 72    | 3.6  | 1     | 00              | 0.4               | C/T              | 4/91-)          |

| [Ke10]    | 4        | 192   | 72   |      | 69    | 4.9  | 1     | 90nm            | 0.4               | СТ               | 4(2b)           |

| [Pre11]   | 20       | 640   | 63   | 63   | 61    | 7    | 1     | $65\mathrm{nm}$ | 0.08              | CT               | 3(1b)           |

| [Mat10b]  | 4        | 140   |      | 70.2 | 69.8  | 3.6  | 1     | $65\mathrm{nm}$ | 0.09              | CT               | 3(3b)           |

|           | 5        |       | 71   |      | 69    |      |       |                 |                   |                  |                 |

| [Car11]   | 10       | 400   | 68   |      | 65    | 28   | 1.05  | 32nm            | 0.13              | CT               | DI MASH         |

|           | 20       |       | 66   |      | 63    |      |       |                 |                   |                  |                 |

| [Mat10a]  | 10       | 300   | 70.2 | 68.2 | 62.5  | 5.32 | 1.1   | 110nm           | 0.32              | CT               | 5(3b)           |

| [Kwo09]   | 3.125    | 100   | 68   | 65   | 64    | 11   | A:1.1 | $65\mathrm{nm}$ | 0.6               | CT/DT            | 3(4b)           |

| [IXWOO9]  | 5        | 160   | 67   | 63   | 61    | 11   | D:1.2 | OSIIIII         | 0.0               | Hybrid           | 3(40)           |

| [Mor10]   | 2        | 120   | 66   |      | 63.3  | 8    | 1.2   | 90nm            | 0.66              | $_{ m DT}$       | 2(1.5b)-2(1.5b) |

|           | 4        |       | 62   |      | 59.1  |      |       |                 |                   |                  | ` ` ` `         |

| [Hua09]   | 2        | 128   | 80   | 79.1 | 79.07 | 4.52 | 1.2   | 65nm            | 0.084             | СТ               | 3(3b)           |

| [Yam12]   | 2.5      | 40    | 71.3 |      | 70.4  | 3.73 | 1.2   | 65nm            | 0.43              | DT               | 4 x 1(2b)       |

|           | 2.5      |       |      | 78   |       | 12.1 |       |                 |                   |                  | 2(4b)           |

|           | 5        |       |      | 77   |       | 15.7 |       |                 |                   |                  | 2(4b)-0(3b)     |

| [Mal08]   | 10       | 420   |      | 75   |       | 20.3 | 1.2   | $90\mathrm{nm}$ | 1                 | DT               | 2(4b)-1(3b)     |

|           | 20       |       |      | 67   | 64    | 20.3 |       |                 |                   |                  | 2(4b)-1(3b)     |

|           | 20       |       |      | 72   | 70    | 27.9 |       |                 |                   |                  | 2(4b)-2(3b)     |

| [Cro10]   | 4        | 512   | 72   |      | 70    | 5.5  | 1.2   | 90nm            | 0.4               | $_{\mathrm{CT}}$ | 3(1b)           |

|           | 10       | 640   | 67   |      | 65    | 6.8  |       | 9011111         |                   | 01               | ` ′             |

| [Oh12]    | 5        | 80    | 71.6 | 71   | 70.7  | 8.1  | 1.2   | 90nm            | 0.37              | DT               | 2(5b)           |

|           | 5        | 160   | 75.4 | 72.2 | 70.9  | 13.6 |       |                 |                   |                  | 3(1.5b)         |

| [Chr10]   | 10       | 240   | 71   | 68.7 | 66    | 20.2 | 1.2   | 130nm           | 0.27              | DT               | 3(3.5b)         |

|           | 20       | 400   | 70.4 | 66.9 | 64.4  | 34.7 |       |                 |                   |                  | 3(3.5b)         |

| [Ran11]   | 5        | 160   | 76   | 74.5 | 69.5  | 6    | 1.2   | 130nm           | 0.56              | CT               | 3(4b)           |

| [And12]   | 9        | 288   | 72   | 71   | 69    | 7.5  | 1.2   | 65nm            | 0.08              | CT               | 3(3b)           |

| [Kim09]   | 10       | 250   | 71   | 68   | 65    | 18   | 1.2   | 130nm           | 1.35              | CT               | 3(3.5b)         |

| [Str08]   | 10       | 950   |      | 86   | 72    | 40   | 1.2   | 130nm           | 1.7               | СТ               | 3(5b)           |

| [Jo10]    | 20       | 640   | 68   | 67.9 | 63.9  | 58   | 1.2   | 130nm           | 1.17              | CT               | 3(4b)           |

| [Mit06]   | 20       | 640   | 80   | 76   | 74    | 20   | 1.2   | 130nm           | 8.6               | CT               | 3(4b)           |

| [Bos10]   | 2        | 80    | 66   |      | 65    | 6.83 | 1.2   | 90nm            | 0.076             |                  | 2(1.5b)-1(1.5b) |

| [Kau11]   | 25       | 500   | 70   | 64.5 | 63.5  | 8    | 1.2   | 90nm            |                   | CT               | 3(4b)           |

| [Wit12]   | 25       | 500   | 72   | 69.1 | 67.5  | 8.5  | 1.2   | 90nm            | 1.7               | CT               | 2(4b)           |

| [Cho19]   | 25       | 2600  | 86   | 80.2 | 73.3  | 15   | 1.0   | 90nm            | 0.19              | CT               | 4(11-)          |

| [She12]   | 36       | 3600  | 83   | 76.4 | 70.9  | 15   | 1.2   | aoum            | 0.12              | СТ               | 4(1b)           |

| [Zan12]   | 5        | 130   | 78   | 75.8 | 75.7  | 16   | 1.2   | 130nm           | 1.6               | DT               | 2(4b)-2(4b)     |

4 Introduction

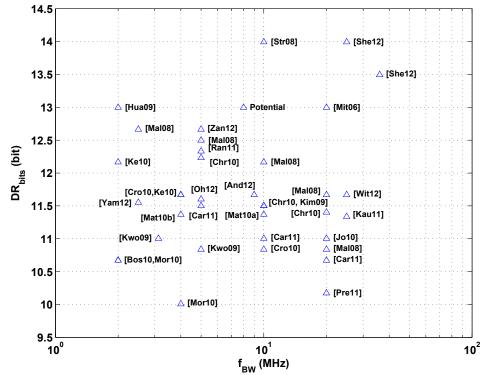

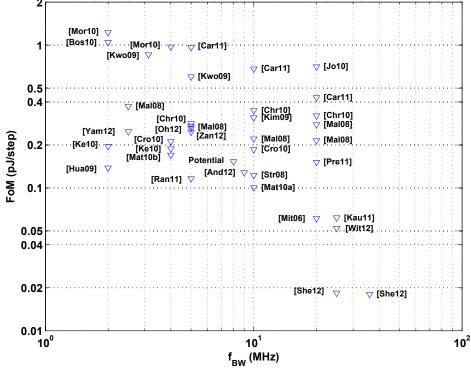

It is worth mentioning that two thirds of the  $\Delta\Sigma$  modulators listed in Table 1.1 are CT  $\Delta\Sigma$  modulators. Although the table does not put limits on power consumption, CT implementation is preferred over DT implementation for high-speed applications for their low-power advantage (explained in details in Section 2.2). Figure 1.1 shows the distribution of the  $\Delta\Sigma$  modulators listed in Table 1.1 over  $f_{BW}$  and  $DR_{bits}$  variations, where  $DR_{bits}$  is given by  $DR_{bits} = (DR - 1.76)/6.02$  in bits. Figure 1.2 depicts the distribution of the  $\Delta\Sigma$  modulators listed in Table 1.1 over  $f_{BW}$  and Figure-of-Merit (FoM) variations, where FoM is given by FoM =  $Power/(2f_{BW} \times 2^{DR_{bits}})$  in (pJ/step).

## 1.3 Thesis Scope and Research Goals

The goal of this thesis is the design of a high-speed (8MHz bandwidth, 16MS/s conversion rate)  $\Delta\Sigma$  ADC suitable for Digital TV receivers. A high resolution ( $\geq$  12bits) is targeted to allow part of the analog processing to be done in the digital domain. The implementation of this  $\Delta\Sigma$  ADC is meant to be in 65nm digital CMOS process for high system-integration and low cost. The design will assume a single low-voltage supply, 1V for this process, which will increase the power consumption as was explained earlier. The DT implementation, for the advantages listed in Section 2.2, is chosen for the scope of this thesis. Targeting 8MHz bandwidth, the DT implementation adds more challenge to the power consumption. The main challenge of this thesis will be the power consumption. The low power consumption will be achieved by means of:

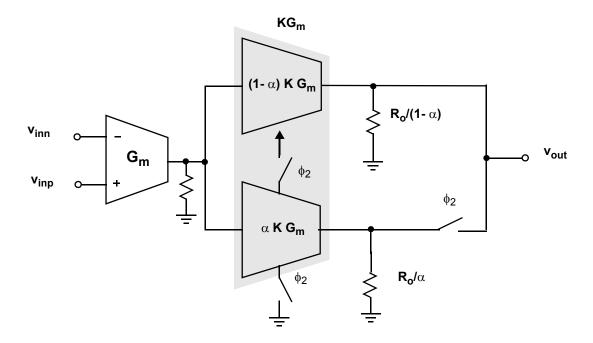

- 1. Exploring low-power SC integrator techniques and proposing a novel opamp switching technique based on a current-mirror opamp with switchable transconductances. The proposed current-mirror opamp works with full current during the charge-transfer phase while the output current is partially switched during the sampling phase. Power saving can be achieved while ensuring that the opamp output is available during both phases.

- 2. Investigating the simultaneous settling of series opamps in a two cascaded nondelaying SC integrators scheme, and developing a power optimization procedure to ensure minimum power consumption while meeting the settling requirements.

Figure 1.1: Distribution of the  $\Delta\Sigma$  modulators listed in Table 1.1 over  $f_{BW}$  and  $DR_{bits}$  variations.

Figure 1.2: Distribution of the  $\Delta\Sigma$  modulators listed in Table 1.1 over  $f_{BW}$  and FoM variations.

6 Introduction

3. Examining the possible use of non-overlapping clock phases with unequal duty-cycles (rather than both about 50 %) which would give the designer an extra degree of freedom to further power optimize the design.

The potential performance thought to be achievable by the experimental  $\Delta\Sigma$  modulator in this thesis is listed in the first row of Table 1.1. The power consumption is expected to be about 20mW from behavioral and circuit simulations. The potential performance is also depicted in both Figure 1.1 and Figure 1.2.

#### 1.4 Thesis Outline

This dissertation is organized in eight chapters including the introduction. The thesis outline is as follows:

Chapter 2 explores low-power techniques suitable for efficient discrete-time (DT)  $\Delta\Sigma$  modulators design on different levels. On the SC implementation level, some low-power SC integrator circuit techniques are explored, outlining the various advantages and disadvantages of each technique. On the system-level, various low-power DT  $\Delta\Sigma$  architectures are listed with the different aspects related to each architecture. Finally, the feedback timing issue is focused on, along with previously suggested solutions.

Chapter 3 introduces a novel switchable-opamp for the low-power design of SC integrators as part of the low-power DT  $\Delta\Sigma$  modulator design. It is based on a current-mirror opamp with output transconductances that can be switched off during the sampling phase. It can be used in the design of SC integrators with both half-delay and full-delay. Furthermore, since its input transconductance is on at all times, it doesn't suffer from operation-speed limitations found in previous designs. Simulation results are presented and confirm that power reductions of up to 30% can be achieved in SC integrators by using the proposed switchable-opamp, compared to having the current-mirror opamp fully active at all times.

Chapter 4 focuses on the design of two nondelaying cascaded SC integrators as part of the low-power design of DT  $\Delta\Sigma$  modulators. A design method is proposed which optimizes the power consumption for a given settling accuracy. Another issue is also addressed concerning a

1.4 Thesis Outline 7

possible excitation case that might lead to settling "hesitation" in two nondelaying cascaded SC integrators which affects settling accuracy. Finally, circuit simulations are presented to confirm the analytical methods and simulations.

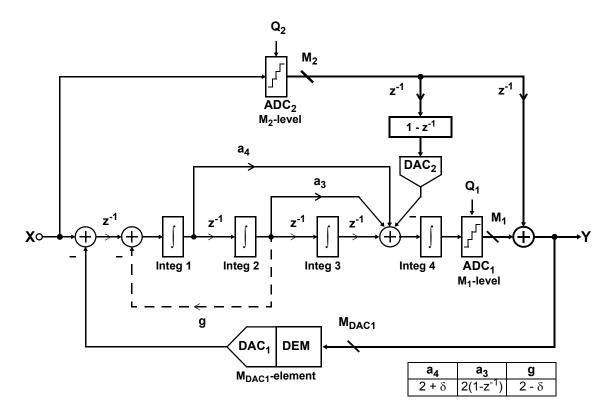

Chapter 5 presents a design procedure for the system-level design of the experimental  $\Delta\Sigma$  modulator, starting from choosing an architecture, until deciding on various circuit parameters for the circuit design. Structural-level (SC implementation) aspects are addressed and structural simulations (SC) are presented. Using behavioral simulations, a Figure of Merit based design procedure is developed to find circuit parameters for an efficient  $\Delta\Sigma$  modulator design.

Chapter 6 presents the design procedure of the various circuit building blocks of the experimental  $\Delta\Sigma$  modulator in 1V 65nm CMOS process. The chapter presents the design of the opamps, the SC comparator, the sampling switches, and the digital circuitry. The implementation of the switchable-opamp, presented in Chapter 3, is shown in this chapter. Circuit simulations of the main building blocks are performed to verify their functionality. Full-system circuit simulations are carried out as a final verification before preparing a prototype for fabrication.

Chapter 7 explores the experimental results of a prototype built for the experimental  $\Delta\Sigma$  modulator. Starting from silicon-level (in 65nm General Purpose GP Standard CMOS process) aspects, the chapter also sheds some light on the test set-up used for the experimental prototype. This chapter presents and summarizes the experimental results of the  $\Delta\Sigma$  prototype and compares it with state-of-the-art  $\Delta\Sigma$  modulators.

Chapter 8 summarizes the thesis, highlights the key research contributions, and suggests topics for future research.

Introduction S

## Chapter 2

# Low-Power Discrete-Time Delta-Sigma Modulators: from Integrator to Architecture

| 2.1 | $\Delta\Sigma$ Modulation Fundamentals                          | 10 |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Discrete-Time vs. Continuous-Time $\Delta\Sigma$ Modulators     | 14 |

| 2.3 | Low-Power Switched-Capacitor Circuit Techniques                 | 14 |

| 2.4 | Low-Power Discrete-Time $\Delta\Sigma$ Modulators Architectures | 17 |

| 2.5 | Feedback-Timing Relaxation Techniques                           | 22 |

| 2.6 | Conclusion                                                      | 24 |

VERSAMPLING  $\Delta\Sigma$  modulators offer a trade-off in ADC design by achieving a high resolution using low accuracy analog components but require higher sampling rates and more digital circuits [Ham04b]. This chapter explores low-power circuit techniques suitable for efficient Discrete-Time (DT)  $\Delta\Sigma$  modulators design as well as low-power DT  $\Delta\Sigma$  modulator architectures.

Section 2.1 starts with a brief introduction about the fundamentals of  $\Delta\Sigma$  modulators. Section 2.2 clarifies the reasons behind choosing the DT implementation over Continuous-Time (CT) implementation. Section 2.3 goes through various low-power switched-capacitor (SC) circuit techniques. Section 2.4 then explores different  $\Delta\Sigma$  architectures suitable for low-power design especially in a low-voltage-supply environment. Section 2.5 addresses the feedback timing issue in the  $\Delta\Sigma$  architectures of interest.

#### 2.1 $\Delta\Sigma$ Modulation Fundamentals

This section outlines the fundamentals of the  $\Delta\Sigma$  modulation. We start by the operation concepts in Section 2.1.1 then we summarize the main performance metrics in Section 2.1.2.

#### 2.1.1 $\Delta\Sigma$ Modulation Operation Concepts

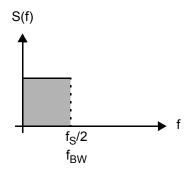

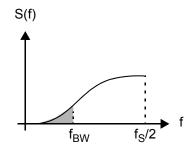

The operation of  $\Delta\Sigma$  modulation relies on quantization, oversampling, and noise-shaping. The quantization is the main process in any Analog-to-Digital Converter (ADC) in which a signal with infinite amplitude resolution is transformed into a signal with finite amplitude resolution. The quantizer usually operates on a uniform step size ( $\Delta$ ) and a uniform sampling rate ( $f_S$ ). A quantization error is introduced due the quantization process. Assuming uniform probability density function, the mean square of that error can be found to be  $\frac{\Delta^2}{12}$ . Under white noise assumption, this noise creates a uniform noise spectral density from 0 to  $f_S/2$  as depicted in Figure 2.1 (a). The signal-to-quantization-noise ratio (SQNR) is defined as the ratio of the input-signal power to the quantization noise power in the signal band.

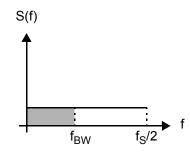

In Nyquist-rate ADCs, the sampling frequency  $(f_S)$  is set as twice the signal bandwidth  $(f_{BW})$ . In oversampling ADCs,  $f_S$  is set to a much larger value than  $2f_{BW}$ . We define the oversampling ratio as

$$OSR = \frac{f_S}{2f_{BW}} \tag{2.1}$$

Due to oversampling, the quatization noise is spread out and the SQNR increases because the in-band quantization noise is reduced as shown in Figure 2.1 (b).

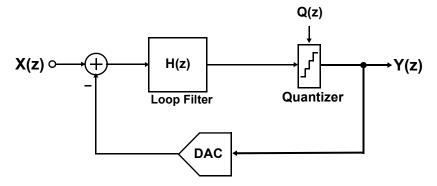

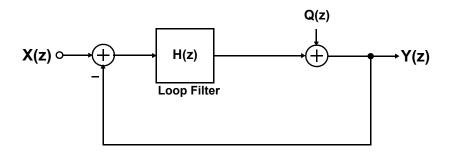

By making use of the negative feedback concept, the SQNR can be further improved. Combining oversampling and noise-shaping gives  $\Delta\Sigma$  modulation. Figure 2.2 depicts a single-loop  $\Delta\Sigma$  modulator. The linear model of the  $\Delta\Sigma$  modulator is shown in Figure 2.3, where the quantization error Q(z) is assumed to be additive white noise.

We can define the noise transfer function (NTF) and the signal transfer function (STF)

(a) Nyquist ADC.

(b) Oversampling ADC.

Figure 2.1: Power spectral density of quantization error.

Figure 2.2: Block diagram of a single-loop  $\Delta\Sigma$  modulator.

$$NTF(z) \equiv \frac{Y(z)}{Q(z)} \Big|_{X(z)=0} = \frac{1}{1 + H(z)}$$

(2.2)

$$STF(z) \equiv \frac{Y(z)}{X(z)} \Big|_{Q(z)=0} = \frac{H(z)}{1 + H(z)}$$

(2.3)

Figure 2.3: Linear model of a single-loop  $\Delta\Sigma$  modulator.

The NTF shapes the quantization error and pushes the quantization error from signal band to outside the band which further increases the SQNR. The loop filter (H(z)) order determines the noise shaping order.

Figure 2.4: Power spectral density of quantization error in oversampling noise shaping ( $\Delta\Sigma$ ) ADC.

#### 2.1.2 $\Delta\Sigma$ Modulators Performance Metrics

This section lists the main performance metrics used in this thesis to evaluate the performance of the  $\Delta\Sigma$  modulator.

#### Signal-to-Quantization-Noise Ratio

The signal-to-quantization-noise ratio (SQNR) is the ratio of the input-signal power  $(P_s)$  to the in-band quantization noise power  $(P_{q,BW})$  expressed as

$$SQNR \equiv 10\log_{10}\left(\frac{P_s}{P_{q,BW}}\right) \qquad (dB)$$

(2.4)

#### Signal-to-Noise Ratio

The signal-to-noise ratio (SNR) is the ratio of the input-signal power  $(P_s)$  to the total in-band noise power  $(P_{n,BW})$  expressed as

$$SNR \equiv 10\log_{10}\left(\frac{P_s}{P_{n,BW}}\right) \qquad (dB) \tag{2.5}$$

#### Signal-to-Noise-and-Distortion Ratio

The signal-to-noise-and-distortion ratio (SNDR) is the ratio of the input-signal power  $(P_s)$  to the sum of the in-band noise power  $(P_{n,BW})$  and the overall distortion (caused by the ADC nonlinearity)  $(P_d)$  expressed as

$$SNDR \equiv 10\log_{10}\left(\frac{P_s}{P_{n,BW} + P_d}\right) \qquad (dB)$$

(2.6)

#### **Dynamic Range**

The Dynamic Range (DR) is the ratio of the maximum input-signal power  $(P_{s,max})$  to the minimum input-signal power  $(P_{s,min})$  expressed as

$$DR \equiv 10\log_{10}\left(\frac{P_{s,max}}{P_{s,min}}\right) \qquad (dB)$$

(2.7)

where  $(P_{s,min})$  is the minimum input-signal corresponding to an SNR of 0dB while  $(P_{s,max})$  corresponds to the input-signal power causing the SNR to drop by 3dB from its peak value.

#### Figure-of-Merit

The Figure-of-Merit (FoM) expression used in this thesis reflects the energy efficiency of the ADC for the reason of comparison. It can be expressed as

$$FoM = \frac{P_{total}}{2f_{RW}.2^{\frac{DR-1.76}{6.02}}} \qquad (pJ/step)$$

(2.8)

where  $P_{total}$  is the total power consumption of the ADC and  $f_{BW}$  is its input-signal bandwidth.

#### 2.2 Discrete-Time vs. Continuous-Time $\Delta\Sigma$ Modulators

Although the first  $\Delta\Sigma$  ADCs implementation used Continuous-Time (CT) loop filter, Discrete-Time (DT)  $\Delta\Sigma$  modulators became more attractive, compared to their CT counterpart, for their coefficient accuracy and good linearity when implemented using SC circuits [Sch05b]. Switched-capacitor circuits are well known for their good accuracy since the coefficient accuracy depends on capacitor ratios rather than absolute time constant values in CT circuits. Consequently, CT circuits need calibration for their time-constants.

Moreover, the noise-transfer function (NTF) of a SC  $\Delta\Sigma$  modulator scales naturally with the sampling frequency and the modulator coefficients are independent of the sampling frequency while the CT  $\Delta\Sigma$  modulator is only designed for one unique sampling frequency and the modulator coefficients change with the sampling frequency. On the other hand, due to the settling requirements in SC circuits, the CT modulator can run at a clock frequency 2-4 times greater than its SC counterpart [Sch05b]. This makes CT designs more power-efficient for high-speed moderate-resolution applications while SC designs are more suited for moderate-speed high-resolution applications.

Targeting both high-speed and high-resolution applications we should either choose CT implementation and develop ways to improve the resolution or choose DT implementation and work on power reduction while increasing the speed. In this thesis, we will be focusing on DT  $\Delta\Sigma$  modulators with the challenge of achieving a power-efficient design while operating at a high speed. In the following sections, we will explore how the low-power implementation of DT  $\Delta\Sigma$  modulators can be achieved.

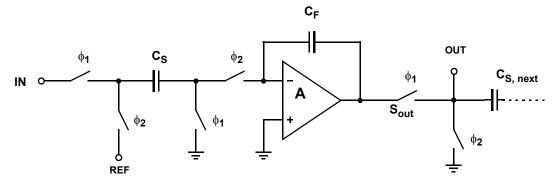

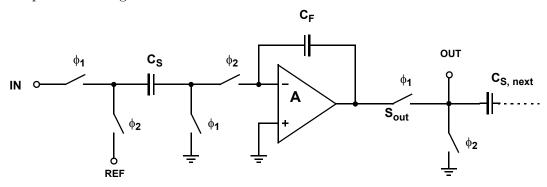

# 2.3 Low-Power Switched-Capacitor Circuit Techniques

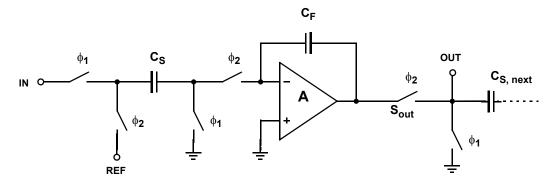

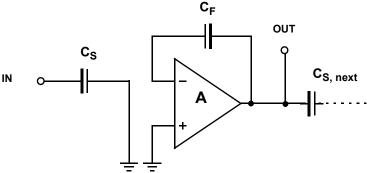

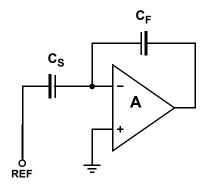

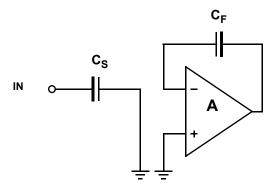

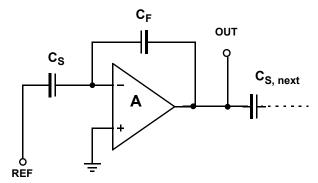

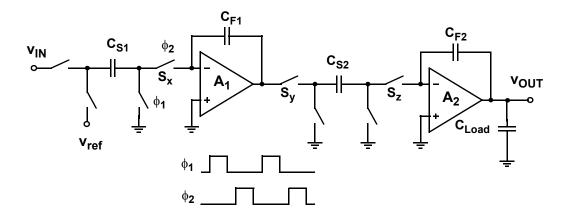

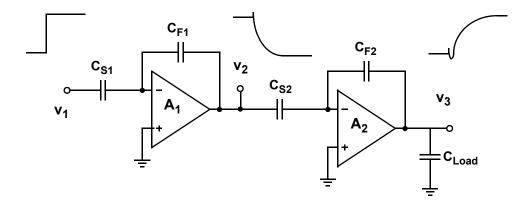

The coefficient accuracy and adequate linearity of SC circuits make it the best way, upto-date, for DT  $\Delta\Sigma$  implementation [Sch05b]. The power-efficient switched-capacitor circuit implementation plays an important role in achieving a good figure-of-merit (FoM) for any DT  $\Delta\Sigma$  modulator. SC circuits principles can be found in [Joh97]. The SC integrator (Figure 2.5) is the main building block of low-pass DT  $\Delta\Sigma$  modulators where the signal bandwidth is centred around DC. The basic operation of a SC integrator relies on sampling the input signal

during a sampling phase  $(\phi_1)$  on a sampling capacitor  $(C_S)$  then performing the integration, by accumulating the charge from the sampling capacitor onto another capacitor  $(C_F)$ , during another phase often called the charge-transfer phase  $(\phi_2)$ . The SC integrator operation is explained in more details in Chapter 3.  $\phi_1$  and  $\phi_2$  are non-overlapping clock phases.

Figure 2.5: A switched-capacitor integrator with the loading effect of its next sampling stage capacitor  $C_{S,next}$ .

The SC integrator has been subject to a lot of innovative low-power circuit techniques to save some of the consumed power in the power-hungry opamps used to build the SC integrators (80% of power consumption of the  $\Delta\Sigma$  modulator in [Nam05]). Most of these techniques look into saving or using the opamp power (current) wasted when not used during operation. Among these techniques we can mention:

#### 1. Double-Sampling (DS) technique [Hur90, Yan12]:

The Double-sampling technique in a SC integrator relies on sampling the input signal and processing it during both clock phases by means of two parallel sampling circuits (paths), to utilize the available resources (opamp) in a more efficient way [Hur90]. The effective sampling rate ends up being double the clock rate. The main disadvantage of the DS technique is the out-of-band noise folding near  $f_S/2$  into the signal band due to the mismatch between the two different DS paths. One of the suggested solutions to overcome this problem is adding an extra zero at  $f_S/2$  in the NTF [Rom03], but this will not necessarily maximize the SQNR that can be otherwise achieved by optimum zero placement [Sch05b]. It is important to note that none of the DT  $\Delta\Sigma$  modulators listed in Table 1.1 uses the DS technique.

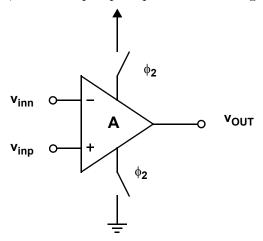

#### 2. Switched-Opamp (SO) technique [Cro94, Xu11]:

This technique was originally proposed as a low-voltage solution. Here, the integrator's opamp is fully switched off during the sampling phase and left on during the charge-transfer phase. The output floating switch ( $S_{out}$  in Figure 2.5) can be eliminated since the opamp output is in a high-impedance state during the sampling phase. This can improve the integrator's linearity, especially in low-voltage-supply designs.

In terms of the power savings, this scheme can save up to 50% of the power consumption, compared to conventional designs with opamps fully active at all times [Che03]. However, this can limit the operation speed, due to the time required to turn on the opamp. Moreover, the SO method can only be employed in SC integrators with half delay (half a clock-cycle delay), thereby restricting their use to specific DT  $\Delta\Sigma$  modulator or SC filter architectures [Pel98] (explained in details in Chapter 3). Furthermore, these opamps require special common-mode feedback (CMFB) circuits, since the opamp output is off during the sampling phase [Sin08]. None of the DT  $\Delta\Sigma$  modulators listed in Table 1.1 uses the SO technique.

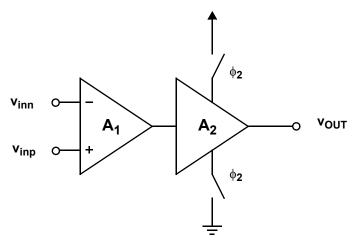

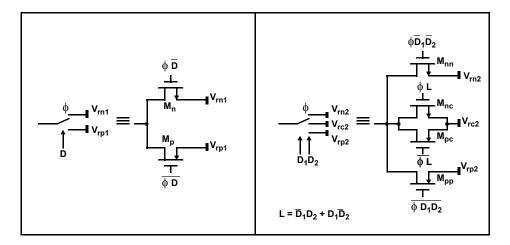

#### 3. Partially-Switched-Opamp (PSO) technique [Bas97, Che03, Kuo10]:

As a variant of the SO technique, a two-stage opamp is used here and only its output stage is switched off during the sampling phase. By keeping the opamp's input stage on at all times, a faster turn-on time and, hence, operation speed can be achieved, compared to a SC integrator with an SO design (explained in details in Chapter 3). Furthermore, since the input stage may burn 1/4 of the opamp's total power consumption, power reductions of 40% can be typically achieved with a PSO design [Che03]. Like the SO technique, the PSO has the same low-voltage advantage while suffering from the same disadvantages of being limited to SC integrators with half delay and requiring special CMFB circuitry [Pel98, Sin08]. We can notice that none of the DT  $\Delta\Sigma$  modulators listed in Table 1.1 uses the PSO technique.

#### 4. Dynamic biasing technique [Kas99, Wan08]:

The dynamic biasing scheme is based on a dynamically biased amplifier to adapt the biasing current according to the required slew-rate and settling accuracy. Some of these early proposed schemes have limited signal bandwidth and large distortion [Kas99]. In [Wan08], the implementation is based on sensing the differential input signal during the sampling phase and adjusting the bias current proportionally for the charge-transfer phase. By designing a fast current detection circuit, the opamp can run at high clock rates. Combining this technique with low-distortion architectures, a good linearity could be achieved. Nonetheless, this scheme does not allow capacitor sharing between the input path (IN in Figure 2.5) and the feedback path (REF in Figure 2.5). In a typical situation, the sampling capacitor can be shared between the input signal path and the feedback path to minimize kT/C thermal noise contribution and avoid possible capacitor mismatch. Moreover, not sharing the sampling capacitor adds time constraints on the feedback path since it has to be sampled simultaneously with the input during the sampling phase. It is important to note that none of the DT  $\Delta\Sigma$  modulators listed in Table 1.1 uses the dynamic biasing technique.

In the next chapter (Chapter 3) we will look into the proposed low-power SC circuit technique based on a current-mirror opamp with switchable transconductances. It avoids some of the drawbacks of the aforementioned techniques while saving considerable percentage of opamp power consumption. The proposed technique does not necessarily have all the previous advantages but does not have the same speed limitations found in some of the previously listed techniques.

## 2.4 Low-Power Discrete-Time $\Delta\Sigma$ Modulators Architectures

The  $\Delta\Sigma$  modulator architecture selection is a key factor in the design of a power efficient system. In the following, we will explore some  $\Delta\Sigma$  modulator architectures to give a justification on which architecture can be selected for the rest of the work in this thesis in a low-voltage-supply environment whilst targeting high-speed high-resolution applications.

#### 2.4.1 Input-Feedforward (IFF) Topology

In the input-feedforward (IFF) topology [Ben93], as shown in Figure 2.6, an input-feedforward path (dashed in Figure 2.6) is added by which the input signal is summed, at the input of the quantizer, to the output of the loop filter in order to cancel any signal flowing through the loop filter, which results in low-distortion [Sil01] design due to reduced swings. The reduced swings at the output of the opamps make this topology suitable for low-voltage-supply environment.

Figure 2.6: Block diagram of a single-loop  $\Delta\Sigma$  modulator with a single DAC feedback and an input feedforward (IFF) path (dashed line).

Moreover, allowing the input signal to flow through the IFF path instead of the loop filter maximizes the maximum input signal and hence allows decreasing the sampling capacitor value as more kT/C noise can be tolerated (assuming thermal-noise limited design) which leads to a lower power consumption. In  $\Delta\Sigma$  modulators without IFF, the quantizer reference  $(V_{ref})$  is chosen to be equal to the available analog swing at the output of the last integrator  $(V_{o,sat})$  and the maximum input signal ends up being limited by  $V_{o,sat}$  in the loop filter H(z). In a  $\Delta\Sigma$  modulator with IFF,  $V_{ref}$  is independent of  $V_{o,sat}$  which allows increasing the quantizer reference and making the maximum input signal independent of  $V_{o,sat}$ .

The IFF path can be implemented using either analog input-feedforward (AFF) implementation [Nam05, Fuj06], or digital input feedforward (DFF) implementation [Kwo06, Gha05, Ham08b, Gha09]. The implementation of both AFF and DFF architecture has practical challenges especially in multi-bit schemes where DAC linearization is necessary and has to be performed within the timing constraints of the architecture as will be explained in Section 2.5 in details.

#### 2.4.2 Analog-Feedforward (AFF) Implementation

In an AFF implementation, the IFF path addition occurs in the analog domain. This addition requires either an active adder [Lee09] or a passive SC adder [Nam05, Fuj06, Kan06]. The use of an active adder increases the power consumption and limits the signal swing. To overcome these problems, a passive SC adder can be used, but in turn, it introduces gain loss due to charge sharing depending on the number of paths in the addition, leading to the scaling down of the signal handed to the quantizer. This signal scaling down tightens the offset requirements of the comparator(s) [Ham04b]. In a multi-bit quantizer, the SC adder network should be replicated in front of each comparator which increases the complexity of the system.

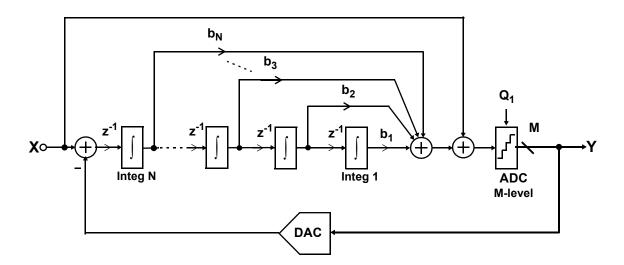

In most AFF structures, the signal-transfer function STF=1 which implies that no signal at all flows through the loop filter in a single DAC feedback architecture as depicted in Figure 2.7. In a multiple DAC feedback architecture (Figure 2.8), multiple IFF paths have to be added to cancel the signal throughout the loop filter. Another advantage of STF=1 is to further relax the anti-aliasing filtering requirements since the out-of-band interferers are not boosted compared to a typical STF with out-of-band gain. But, because of the delay-free IFF path, it puts some complications in the feedback timing as will be explained in Section 2.5.

Figure 2.7: Analag feedforward (AFF) implementation in an N<sup>th</sup>-order single DAC feedback architecture. [Sil01, Ham04b]. Here, the nondelaying integrator symbol  $\int \equiv 1/(1-z^{-1})$ .

Figure 2.8: Analag feedforward (AFF) implementation in an N<sup>th</sup>-order multiple DAC feedback architecture. [Gag04, Ham04b]. Here, the nondelaying integrator symbol  $\int \equiv 1/(1-z^{-1})$ .

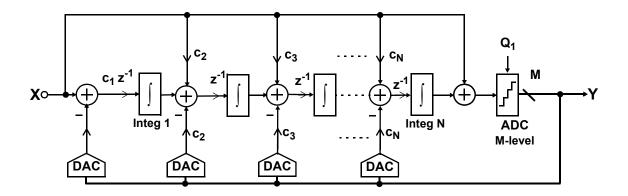

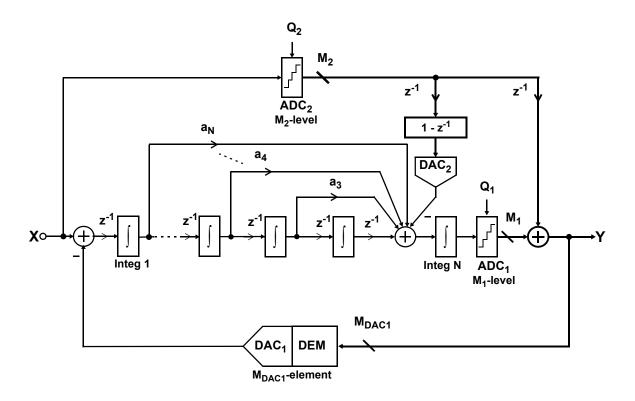

#### 2.4.3 Digital-Feedforward (DFF) Implementation

The DFF implementation [Kwo06, Gha05, Ham08b, Gha09] allows the implementation of the addition of the IFF path in the digital domain. Although an extra quantizer is required, the total number of comparators can be maintained the same given the extremely reduced swing at the input of the main quantizer. The quantization noise from the extra quantizer has to be cancelled to avoid performance degradation. Although the STF can't be unity in such designs, an |STF|=1 can still be achieved [Ham08a] to maintain the advantage of anti-aliasing filtering relaxation. Since most DFF architectures do not rely on a delay-free IFF path, the feedback timing is more relaxed than in AFF architectures.

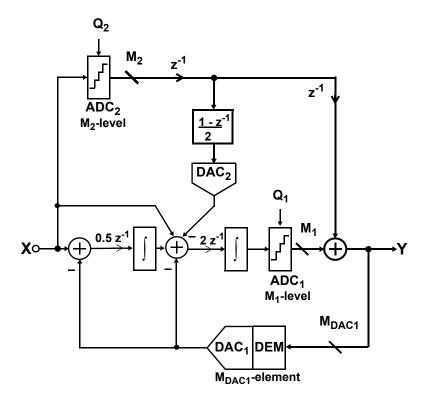

In [Kwo06], as shown in Figure 2.9, an additional AFF path is added to lower the signal swing at the output of the first integrator due to the multiple DAC feedback structure. In the architecture of [Ham08b], depicted in Figure 2.10, the signal component is highly suppressed at the output of the last integrator (input of the main quantizer) by the input DFF path. Although a signal component is still present at the output of the other integrators, the single DAC feedback architecture [Ham06] (versus multiple DAC feedback architecture) ensures that the signal components are highly suppressed at the output of the rest of the integrators. Having a single DAC feedback, the architecture in [Ham08b] looks more attractive for highorder  $\Delta\Sigma$  modulators.

Figure 2.9: Digital feedforward (DFF) implementation in an 2<sup>nd</sup>-order multiple DAC feedback architecture. [Kwo06]. Here,  $\int \equiv 1/(1-z^{-1})$ .

The maximum input signal swing in the DFF architectures is determined by the overload of the extra quantizer as long as the DAC can handle this signal swing. The proper design of the quantizers' references ensures more power savings. In some cases, overloading the extra quantizer can be tolerated as long as the quantization noise from the extra quantizer can still be cancelled and the feedback loop subtraction is properly performed [Gha09, Kwo09].

Many DT  $\Delta\Sigma$  modulators listed in Table 1.1 uses AFF architectures [Mor10, Oh12, Yam12, Zan12]. In [Kwo09], in Table 1.1, a DFF architecture is used along with some AFF paths like [Kwo06]. Due to the maximum signal swing advantage as well as the easier addition implementation, DFF architecture sounds preferable. In this thesis, we will focus on the DFF implementation of a single DAC feedback architecture (Figure 2.10 [Ham08b]) because of its reduced swings advantage.

Figure 2.10: Digital feedforward (DFF) implementation in an N<sup>th</sup>-order single DAC feedback architecture. [Ham08b]. Here,  $\int \equiv 1/(1-z^{-1})$ .

# 2.5 Feedback-Timing Relaxation Techniques

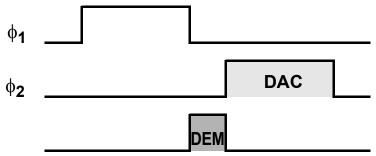

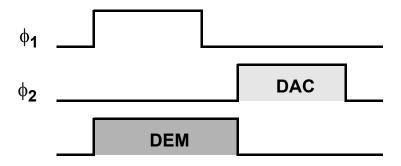

It is of critical importance to make sure that, while looking into various  $\Delta\Sigma$  architectures, the feedback timing requirements can be met on the implementation level. Looking into the feedback path, there is always a constraint on when the feedback signal should be ready for processing (DAC, subtract, and integrate). This is more important in multi-bit designs where most likely dynamic-element-matching (DEM) techniques must be used for DAC linearization. We are assuming here that the  $\Delta\Sigma$  modulator is operated from the standard two non-overlapping clock phases  $\phi_1$  and  $\phi_2$  necessary for proper SC circuits operation (Figure 2.11 and Figure 2.12).

In most AFF  $\Delta\Sigma$  architectures, where STF=1, the delay-free input feedforward path implies that the quantization and DEM processing (if applicable) has to be performed within the non-overlapping time, as explained in [Gha06], which might severely limit the operation speed (Figure 2.11). Several solutions have been suggested to solve this problem and relax the DEM timing. In [Fuj06] and [Gha06] a half delay is added in the signal path in front of the loop filter to give an extra half-delay for the DEM processing. The SC implementation is based on double sampling the input signal on two sampling capacitors. The obvious cost is the added kT/C switch noise and the noise folding due to path mismatch. The noise folding problem can be alleviated by not sharing the two sampling capacitors between the signal path and the feedback path and using a separate capacitor for the feedback path which adds more kT/C noise and consumes more power. This idea can be extended for more DEM timing relaxation by using triple sampling instead of double sampling to add a full delay (clock cycle) in the signal path and giving in turn a complete clock cycle for DEM processing [Kan06, Fuj09].

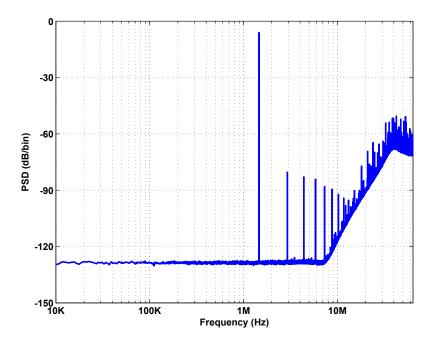

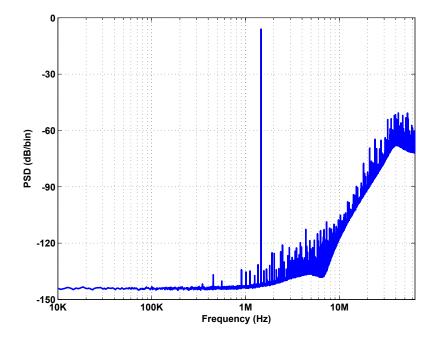

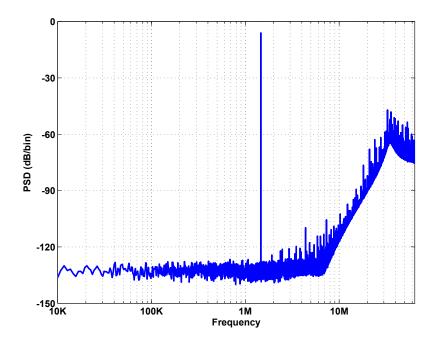

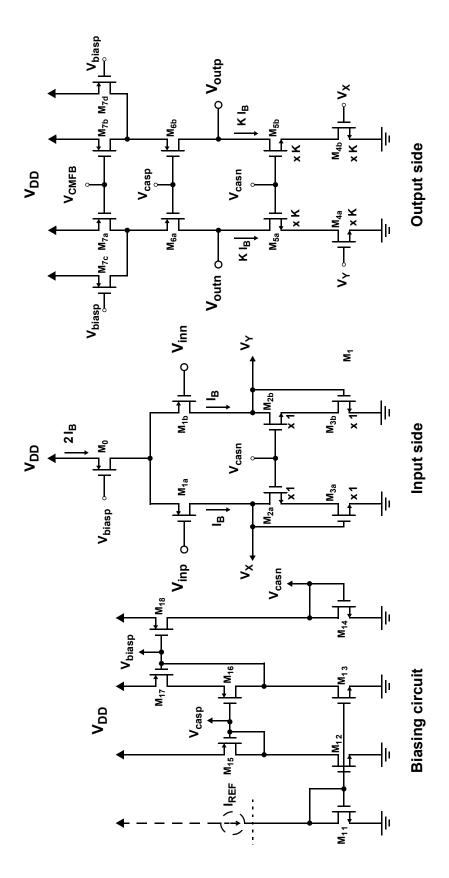

Figure 2.11: Timing diagram and available time for DEM in most AFF  $\Delta\Sigma$  architecture with STF=1 [Kwo07].