# A computing architecture for a multiple robot controller

Anthony Topper B. Eng.

Department of Electrical Engineering

McGill University, Montréal

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree

Master of Engineering

June 1991 © Anthony Topper

### **Abstract**

This thesis describes the architecture of the *Kali* multi-arm robot control system, including discussions on design trade-offs and performance, as well as a detailed implementation using off-the-shelf hardware and software. *Kali's* main objectives are flexibility, integration, and hardware and software modularity so as to facilitate programming, experimentation and portability. It is used primarily to prototype concepts in multi-arm coordination, teleoperation, force control, and sensor fusion etc. To implement *Kali* requires only a minimal real-time kernel, a sufficiently powerful computer and a robot interface. It is based on the principle that, today, computational hardware, real-time operating systems and robot interfaces no longer impede robot controller design. Rather it is control software and system integration which are now the main problems. To that end, this work also discusses in depth the fundamental problems in the design and engineering of robot controllers from an implementational point of view using *Kali* as a primary design example.

### Résumé

On décrit dans cette thèse l'architecture de *Kuli*, un système de commande de robots multi-bras. On discute aussi des différentes options de sa conception, de la performance, ainsi que de la mise en oeuvre à l'aide de composants matériels et logiciels disponibles dans le commerce Les objectifs du système *Kali* sont la flexibilité, l'intégration et la modularité matérielle et logicielle pour faciliter la programmation, l'expérimentation et la portabilité. On l'utilise principalement pour construire des systèmes prototypes de coordination multi-bras, de téléopération, de commande a retour d'efforts et de fusion multi-sensorielle. La mise en oeuvre de *Kali* se fait à l'aide d'un noyau temps-réel de fonctionalité minimale, d'un système informatique suffisament puissant et d'un interface manipulateur. Ce développement est basé sur le principe que de nos jours, le matériel de calcul, les systèmes temps-réels et les interfaces manipulateurs ne sont plus ce qui retarde la conception des systèmes de commande de manipulateurs. Le problème est maintenant celui du développement du logiciel et de l'intégration du système. Dans cette optique, ce travail examine en détail les problèmes fondamentaux de la conception des controleurs de manipulateurs du point de vue de la mise en oeuvre en utilisant *Kali* comme exemple principal.

### **Acknowledgements**

First and foremost I thank project leader Professor Vincent Hayward without whose vision and guidance *Kali* never would have become a reality. Secondly, I thank Professor Laeeque Daneshmend for his invaluable contributions, numerous suggestions and for the design of the *Kali* servo code. I also thank Ajit Nilakantan who along with Professor Hayward created the *Kali* trajectory generator software. I extend my gratitude to Dr. Samad Hayati of the Jet Propulsion Laboratory for pushing through red tape and funding the project. I also confer my appreciation to John Lloyd for his thoughts on robot software design, to Mike Parker for his help in UNIX networking intricacies and to Cem Eskenazi for honoring many special requests. Finally, I would like to thank my family for their encouragement and unfailing support.

# Contents

| 1. Introduction                            | l  |

|--------------------------------------------|----|

| 1.1 The Robot Controller Problem           | 1  |

| 1.2 Software is Paramount                  | 2  |

| 1.3 Thesis Overview                        | 3  |

| 1.4 Scope                                  | 5  |

| 2. The Elements of Robot Controller Design | 7  |

| 2.1 The Robot Control Hierarchy            | 7  |

| 2.2 Anatomy of a Robot Controller          | 9  |

| 2.2.1 Trajectory Generation                | 10 |

| 2.2.2 Intertask Interface                  | 11 |

| 2.2.3 Servo Control                        | 11 |

| 2.2.4 Computational Requirements           | 14 |

| 2.3 Computing Architecture                 | 16 |

| 2.3.1 Multiprocessing                      | 19 |

| 2.3.2 Systolic Arrays and Pipelines        | 22 |

| 2.3.3 Vector Machines                      | 24 |

| 2.3.4 Scalar Machines                      | 24 |

| 2.3.5 Super Chips                          | 27 |

| 2.5 Real-Time Kernels                      | 30 |

| 2.6 Robot Joints                           | 30 |

| 2.6.1 Sampling Issues                      | 31 |

| 2.6.2 Motors & Amplifiers                  | 33 |

| 2.7 System Implementation Approaches       | 35 |

| 2.7.1 Robot Controller Roundup             | 38 |

| 2.7.2 Commercial Competition               | 41 |

| 3. Kali Implementation                     | 43 |

| 3.1 Kali Overview                          | 43 |

| 3.2 Implementation                         | 45 |

| 3.2.1 Real-Time O/S                        | 45 |

| 3.2.2 Servo Control                        | 47 |

| 3.2.3 Other Considerations                 | 48 |

| 3.3 Process Model                       | 49 |  |

|-----------------------------------------|----|--|

| 3.3.1 Trajectory Generator Process (TG) | 49 |  |

| 3.3.2 User Process (UP)                 | 50 |  |

| 3.3.3 Servo I/O Process (SIO)           | 50 |  |

| 3.3.4 Servo Process (SV)                | 51 |  |

| 3.3.5 SIO/SV Dynamic Loading Algorithm  | 52 |  |

| 3.3.6 Feedforward Dynamic Compensation  | 52 |  |

| 3.3.7 Viewer Process                    | 53 |  |

| 3.4 Servo Programming Interface         | 55 |  |

| 3.5 Robot Drivers                       | 58 |  |

| 3.5.1 Calibration                       | 60 |  |

| 3.6 Real-Time Interface                 | 61 |  |

| 3.6.1 Shared Memory                     | 61 |  |

| 3.6.2 Wall Clock                        | 63 |  |

| 3.7 System Hardware                     | 65 |  |

| 3.7.1 McGill I/O Board                  | 66 |  |

| 3.7.2 Motor Drive                       | 67 |  |

| 4. Conclusion                           | 69 |  |

| 4.1 Summary                             | 69 |  |

| 4.2 Lessons Learned, The Hard Way       | 70 |  |

|                                         |    |  |

| Appendix A, Buses & CPUs                |    |  |

|                                         | 73 |  |

|                                         | 75 |  |

|                                         | 76 |  |

| A.2.1 Motorola                          |    |  |

|                                         |    |  |

| A.2.3 SPARC                             |    |  |

| A.2.4 Mips                              |    |  |

| A.2.5 Advanced Micro Devices (AMD)      |    |  |

| A.2.6 DSPs                              |    |  |

| A.2.7 Transputers                       |    |  |

| A.2.8 National Semiconductor            |    |  |

| A.2.9 IBM                               |    |  |

| Appendix B, Real-Time Kernels           |    |  |

| B.1 O/S Classification                  |    |  |

| B.2 Evaluation & Commentary             | 86 |  |

| B.2.1 pSOS+                             |    |  |

| B.2.2 VRTX Velocity 89             |

|------------------------------------|

| B.2.3 VxWorks 92                   |

| B.2.4 LynxOS 94                    |

| B.2.5 PDOS 95                      |

| B.3 Pertormance Comparison 96      |

| B.3 1 CPU Performance Impact       |

| B.4 Standards                      |

| Appendix C, McGill Robot I/O Board |

| C.1 Introduction                   |

| C.2 Specifications                 |

| C.2.1 Electrical Specifications    |

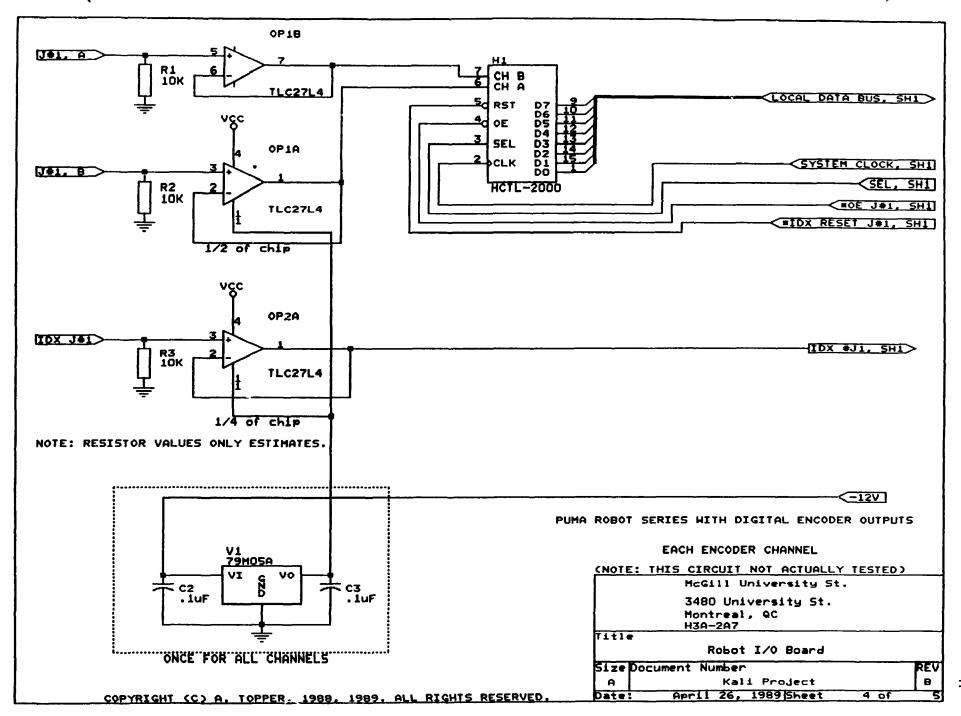

| C.3 Theory of Operation 103        |

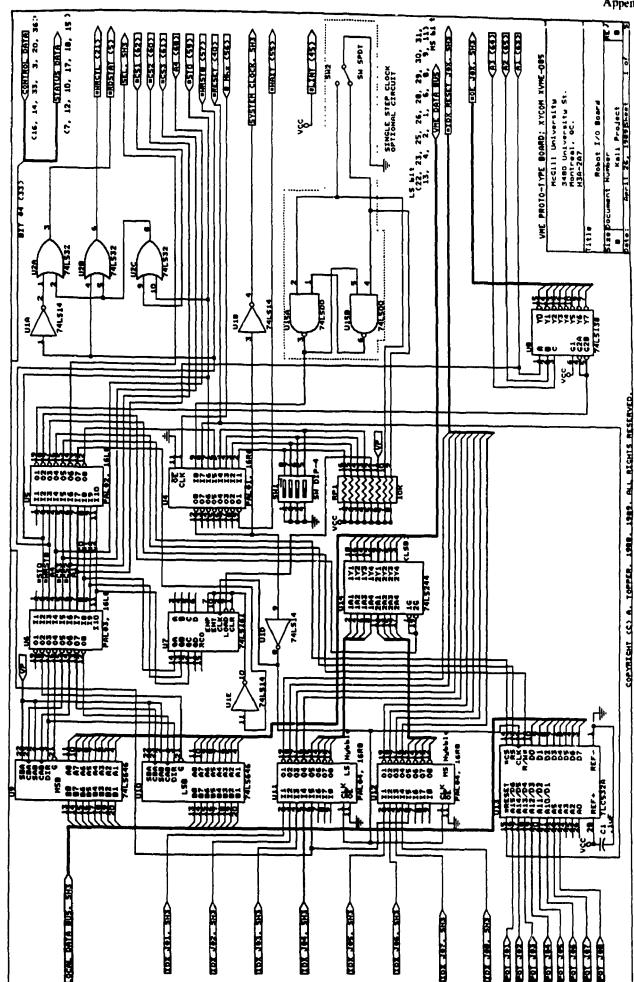

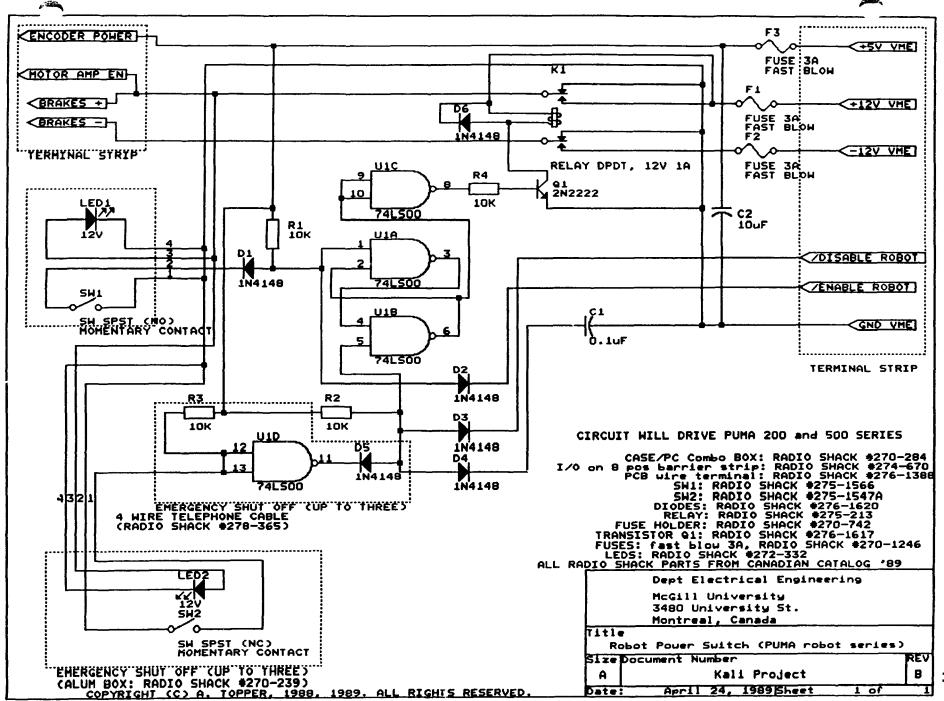

| C.4 Implementation 106             |

| C.4.1 PAL Programming              |

| C.4.2 Power Switch Circuit         |

| C.5 Programming 111                |

| C.5.1 Hardware Addresses           |

| C.5.2 Diagnostic Program           |

| C.6 Schematics                     |

| C.7 PAL Listings                   |

| C.8 IC Data Sheet References       |

| References                         |

# **List of Tables**

| Table                                           |                       |

|-------------------------------------------------|-----------------------|

| 2.1 Computational Requirements for Robot Contro | l15                   |

| 2.2 Summary of Reasearch Robot Controllers      | 38                    |

| 3.1 PUMA 560 Motor and Contraves Amplifier Pa   | arameters 68          |

| A.1 A Comparison of 32/64-bit Computer Buses    | 73                    |

| B.1 Classification of Selected Real-Time O/S's  | 73                    |

| B.2 Comparative Performance of Some Real-Time   | Kernels 84            |

| B.3 Comparison of a Typical Real-time Kernel on | Various Processors 98 |

# **List of Figures**

| F | Figure Pa                                                             | age |

|---|-----------------------------------------------------------------------|-----|

|   | 2.1 The Basic Robot Controller Model and System Trade-Ott             | 8   |

|   | 2.2 Anatomy of a Typical Robot Controller                             | 13  |

|   | 2.3 Parallel Computational Architectures in Robotics                  | -   |

|   | 2.4 Performance of Message Passing Used in Robotics                   | 20  |

|   | 2.5 Multiprocessor Bandwidth vs. Task Communication Overhead          | 20  |

|   | 2.6 Multiprocessor Communication Methods                              | 21  |

|   | 2.7 Relationship Between Robotics Code and Processor Architectures    | 25  |

|   | 2.8 Aggregate Performance of Current Microprocessors on Robotics Code | 26  |

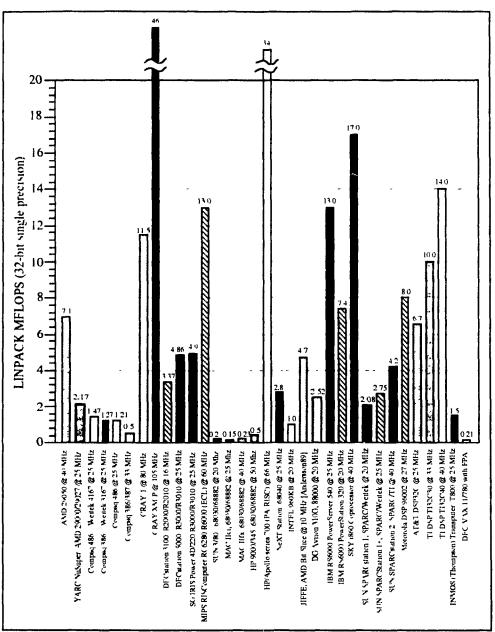

|   | 2.9 The LINPACK benchmark for Current Microprocessors                 |     |

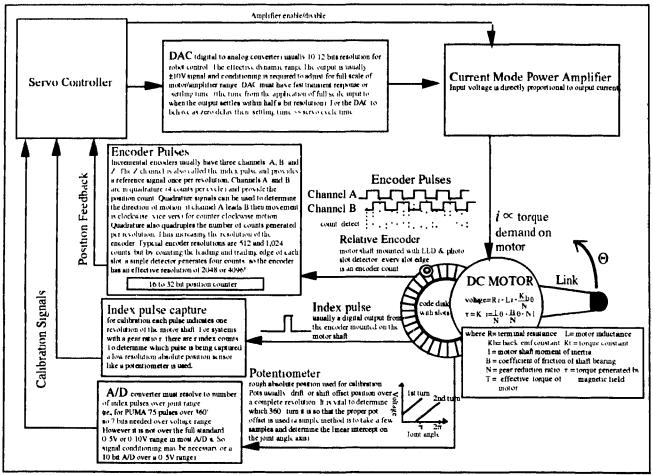

|   | 2.10 Typical Joint Control & Feedback                                 |     |

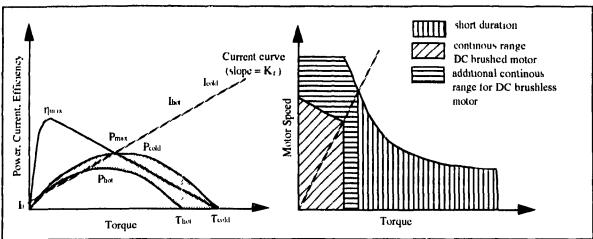

|   | 2.11 Motor Peformance Characteristics                                 |     |

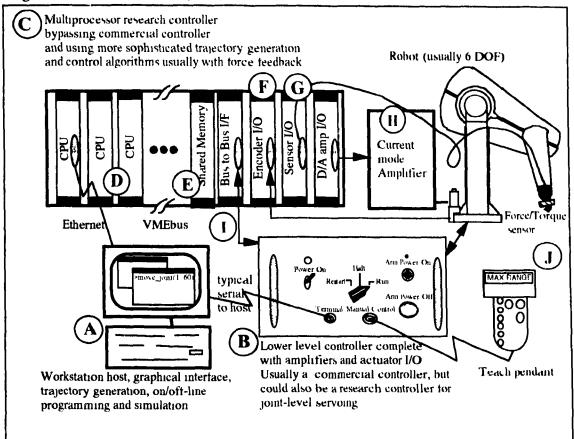

|   | 2.12 The Basic Robot Controller Architectures                         | 36  |

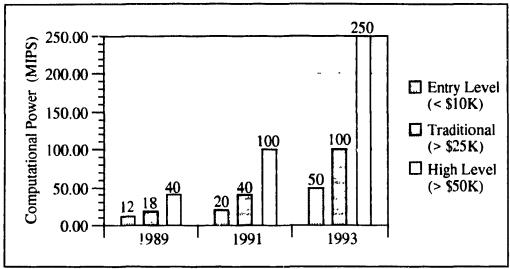

|   | 2.13 Current and Future Workstation Performance                       | 41  |

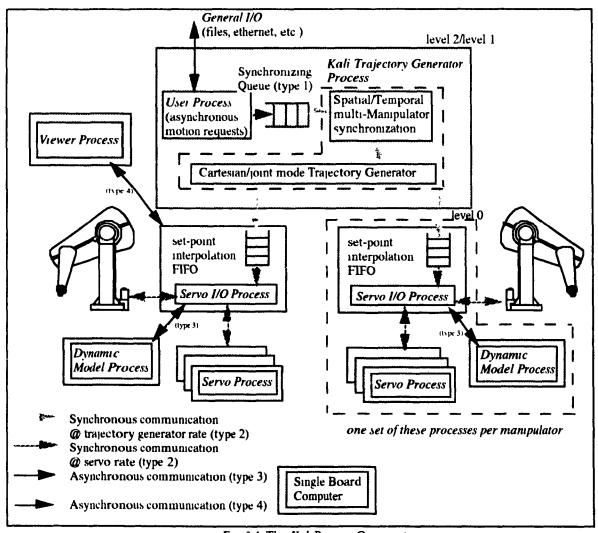

|   | 3.1 The Kalı Process Organization                                     | 53  |

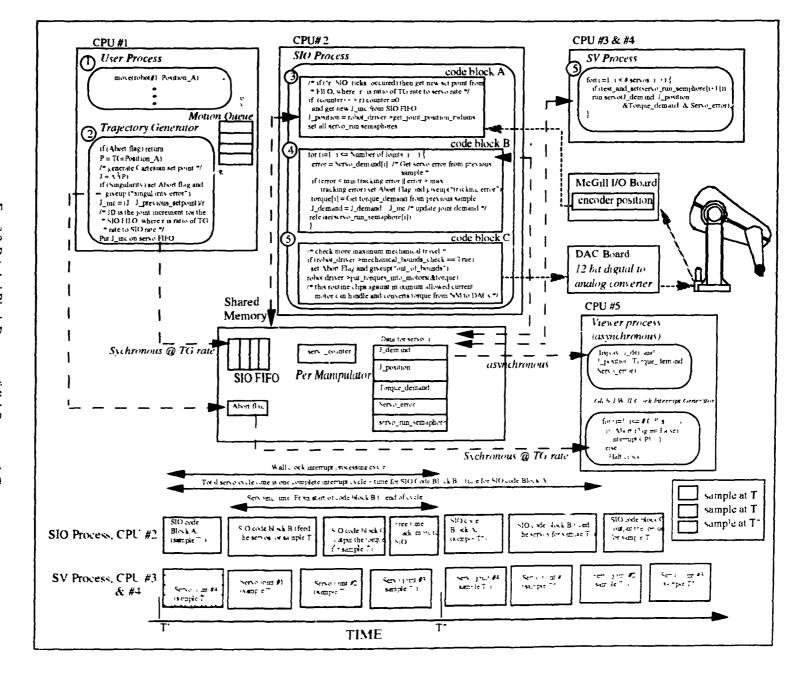

|   | 3.2 Detailed Block Diagram of Kalı Processes & Timing                 | 54  |

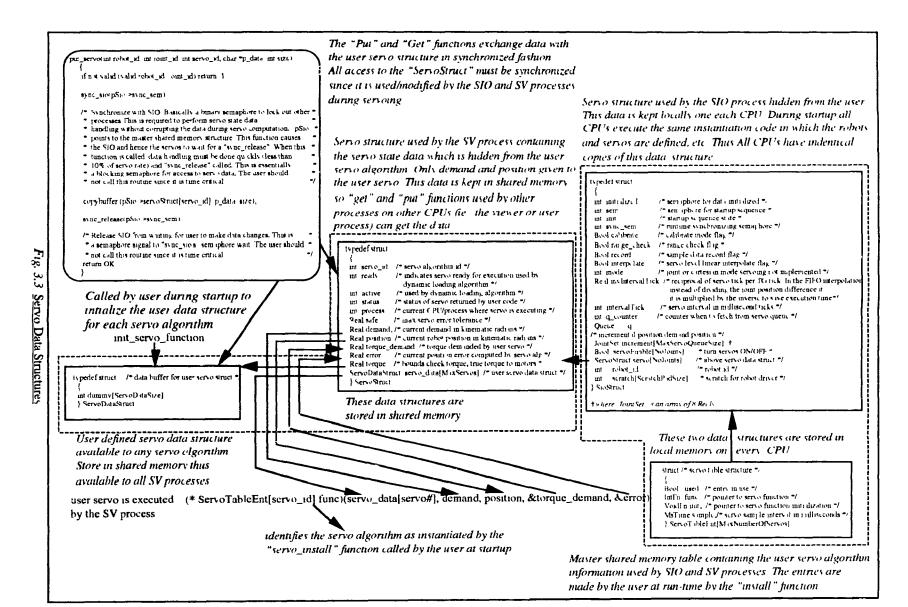

|   | 3.3 Servo Data Structures                                             | 57  |

|   | 3.4 Servo Algorithm Code Example                                      | 58  |

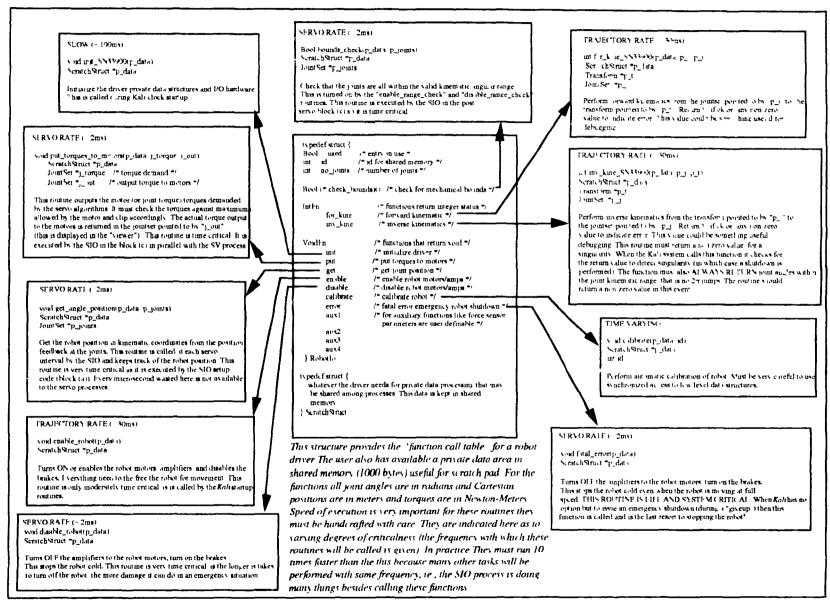

|   | 3.5. Kali Robot Driver Interface                                      | 59  |

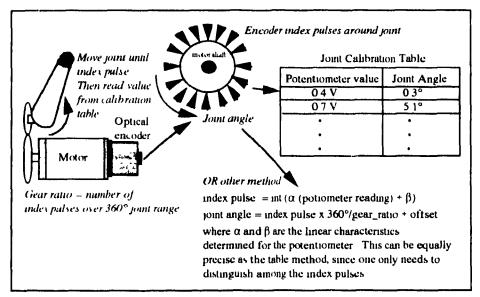

|   | 3.6 On-line Robot Calibration Methods                                 | 61  |

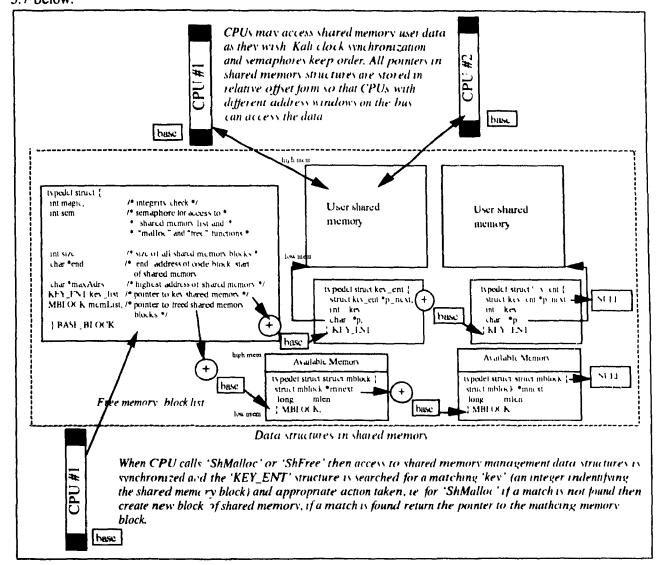

|   | 3.7 Kali Shared Memory Data Structures                                | 62  |

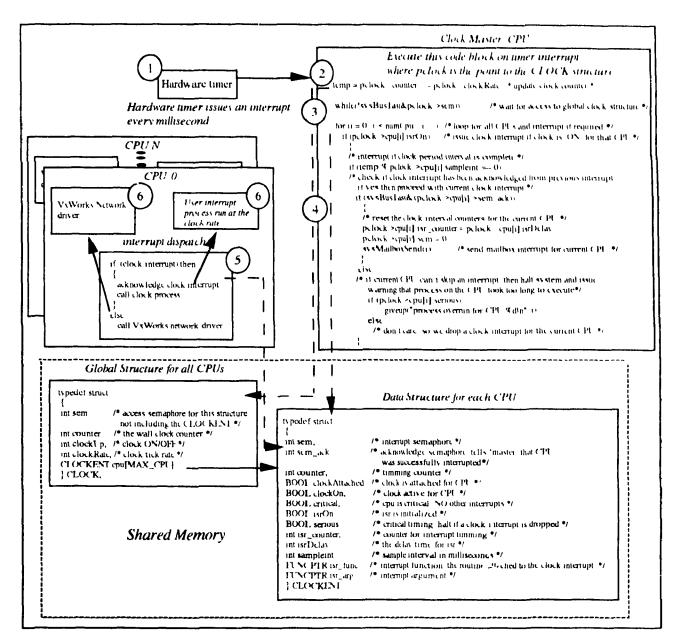

|   | 3.8 Kali Wall Clock Mechanism                                         | 64  |

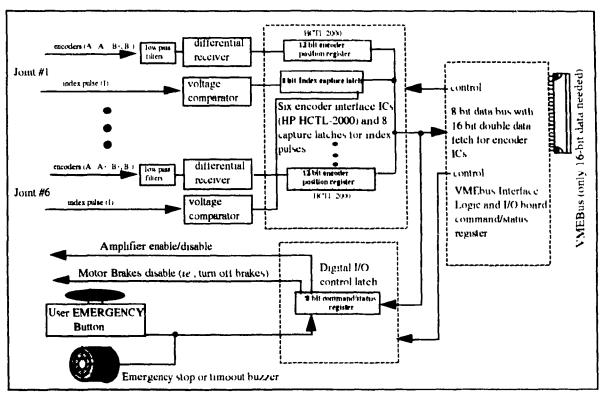

|   | 3.9 McGill Robot I/O board Overview                                   | 66  |

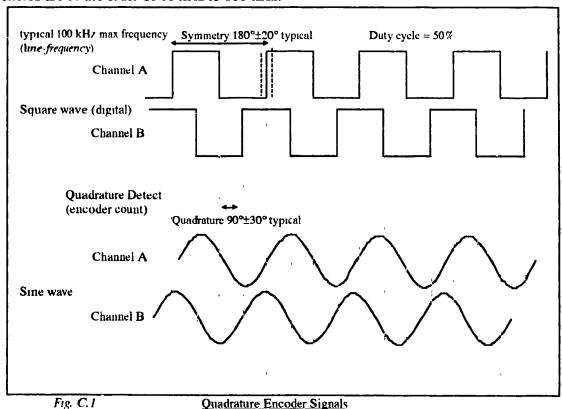

|   | C.1 Quadrature Encoder Signals                                        | 104 |

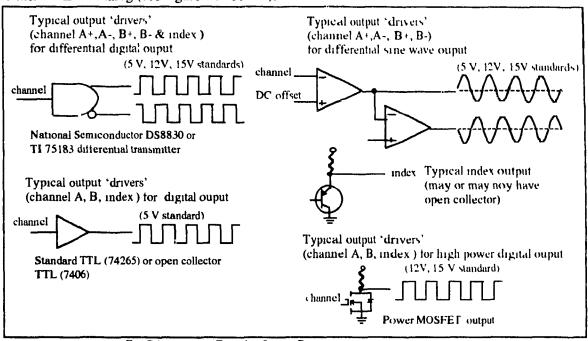

|   | C.2 Encoder Output Drivers                                            | 105 |

|   | C.3 Encoder Chip Interface Software                                   | 111 |

### 1.1 The Robot Controller Problem

4

Robotics is by its very nature an experimental science, yet rarely has the literature discussed one of the major practical difficulties in robotics, namely, the process of actually building a robot control system—the robot controller problem. It encompasses the process of engineering a solution to a particular application including all its practical and idiomatic aspects such as computing hardware, software, actuator interfaces, etc. It is not in itself any theory or rationale of the application at hand; nor is it about any particular design philosophy; it is, however, about communication mechanisms, servo rates, processor speed, kernel calls, and programming tools, etc. The former are prerequisites to the problem, the latter are the problem.

In the past, the major obstacles to building robot controllers were the poor floating point performance of commercial processors and the meager capabilities and often unbearable development environments of commercial real-time kernels. These limitations drove researchers to waste most of their effort just to build an adequate computing platform with sufficient software tools upon which to test their theories about robotics. In addition, interfacing a digital control system directly to a robot's motors and sensor feedback was a non-trivial task, and the lack of ready-to-use hardware interfaces made it a difficult undertaking for all but experienced robotics engineers. Thus, robot controllers often depended on unique hardware and software architectures and operated only with specific robots and host computers. Such systems were often too cumbersome to use and certainly too difficult. If not impossible, for others to adopt for their own research. Despite assertions of their powerful capabilities, most research controllers performed even simple tasks less well than the primitive commercial systems they were designed to surpass.

Today, however, thanks to vendor independent open architectures, and the advent of powerful yet inexpensive microprocessors with integrated real-time programming environments, it is now easy to engineer an impressive, yet easy-to-use, robot controller in a matter of weeks using off-the-shelf hardware and software. All that is required a sufficiently powerful computer, a minimal real-time kernel, a robot interface, and robot control software. The first three can be purchased simply from commercial sources, leaving the last to be obtained either from other researchers or created as needed. McGill University's *Kali*<sup>1</sup> robot control system is an example of this new trend. It is a software architecture for the control of multiple coordinated manipulators founded on the principle that the robot controller problem is no longer hindered by inadequate floating-point hardware, real-time operating systems, or robot interfaces. Rather it is control software and system integration which are now the main problems—precisely those areas of interest to researchers.

### 1.2 Software is Paramount

In seeking a plausible system architecture, the robot controller designer must, in effect, have a good knowledge of the empirical and idiomatic aspects and the various computational, programming, and I/O demands of a basic robot controller including computational hardware fast enough to perform trajectory generation and joint level servoing, user programming interface and development environment, and a real-time kernel to tie the system together. Once these are laid down, the problem becomes one of software architecture to meet all the specifications while 'mapping' the entire system onto an appropriate hardware implementation [Ostroff87]. In practice, this is far easier said than done, not only because of the myriad problems in designing a complex real-time system, but also because determining specifications 'a priori' during the design phase is a difficult task, since much information about the environment is not known until run-time [Ramamritham88]. Thus rapid prototyping, both in building a functional skeleton of the end-result and in simulating algorithms, plays an important role in the creation of any modern robot controller

<sup>&</sup>lt;sup>1</sup> In Hindu mythology, Kali the Divine Mother, is often represented as a creature with many arms

Without adequate ease in creating and altering code, or a fast enough edit-compile-test cycle, development bogs down and the flexibility necessary for research and experimentation quickly decays. In fact, it is the programming environment and the development tools which determine the usefulness of a robot control system, in the end.

### 1.3 Thesis Overview

1

It is to assist the reader in this endeavor—the building of functional, ease-to-use robot controllers—that this thesis is dedicated. It examines the problems in the design and implementation of such systems while providing *Kali* as the principal design example including all the critical nuts and bolts information, otherwise so often forgotten:

- Software structure. The blueprint for a robot controller are the processes

required to make it work, these include application code (task planning),

trajectory generation, and servoing. A detailed examination of their

organization, data structures, algorithms, and communication mechanisms is

made.

- Computational requirements. What performance features does each process need from the hardware? How much computational power is needed execute a given algorithm at the required sampling rate? How many MIPS<sup>1</sup> or MFLOPS<sup>2</sup> are needed?

- Computing architectures. What architecture best suits the robot controller problem: vectored, pipelined, dataflow, or connection machine? Since a robot controller is built on a foundation of computing hardware, a fundamental understanding of it is necessary in order to select/design computational components for a robot control system. Perhaps nothing has stirred so much confusion as the advantages/disadvantages among the different hardware architectures: CISC, RISC, DSP, VLIW, systolic arrays,

<sup>&</sup>lt;sup>1</sup> Million Floating Point Operations Per Second

<sup>&</sup>lt;sup>2</sup> Million Instructions Per Second usually based on the benchmark that a Digital Equipment Corp VAX 11/780 is 1 MIPS

- superscalar, superpipelining, etc. The costs/benefits of each as applied to robotics is explained.

- The communication bottle neck. Today, a robot controller is likely to be a tightly coupled multiprocessor system with complex interprocessor communication. The major architectural issue is whether to use either shared memory or message passing. What are the advantages/disadvantages of each? Which is most often used and Why? What mechanisms for interCPU messaging are necessary such as gang scheduled test-and-set, sleep-and-wake-up, or uncoordinated test-and-set? How are these implemented together with communication protocols and algorithms? In either case, synchronization of data exchange is always the crux of the problem. This, in turn, leads to the other major problem—bus traffic. As sampling rates and computation loads increase, it becomes the major bottleneck on performance. How does it increase and what can be done about it?

- Commercial hardware. No doubt this subject matter changes as fast as technology progresses, thus making any discussion of it quickly outdated, however, at some point decisions must be taken and real world hardware selected. For the reader's convenience an evaluation of current CPUs such as SPARC, MC68040, Mips¹ R3000, i860, etc., as well as computer buses such as VMEbus, EISAbus, FutureBus, etc. is also made. A discussion on other miscellaneous, though equally important, implementation issues like memory access time, power consumption, bus termination, and arbitration is also offered.

- Real-time Software requirements. A robot controller is very much a 'hard' real-time device for which scheduling deadlines such as servoing must be met unfailing. Thus what features are needed from a real-time kernel? How

<sup>1</sup> Corporate name for Mips Computer Inc., not to be confused with Million Instructions Per Second

long should it take to process an interrupt, a kernel call, or a interprocess message? Which con.mercial kernels provide these features and how well do they perform them?

- Control Issues. Fundamental to any robot control system are the trajectory generator rates and servo rates. How fast should these be generated to guarantee a smooth trajectory? Stable control of the manipulator? What are the upper and lower bounds? What are typical numbers? What about controller delay, quantization problems, and dynamic range of calculations?

- Robot Interfaces. What is the basic model for a robot joint? How are encoders used to determine position and velocity. How they are interfaced? How is a robot calibrated to absolute position? Some valuable tricks and techniques are explained as well as the complete design for a robot interface board is given. In addition, an examination of the advantages/disadvantages between brushed and brushless electric motors (the most common type of robot actuator), and between linear and switching amplifiers is made, although no comprehensive discussion of actuators is offered.

- Safety and robustness. Finally, how is safety and robustness (ability to withstand and recover from error or disaster) ensured in an experimental system? To prevent disaster it is essential to have a means of detecting faults, software failures and dangerous conditions.

## 1.4 Scope

i.

In short, this work examines all the empirical and idiomatic aspects of robot controller design and implementation. However, it does not discuss the theory of robot control, trajectory generation, robot language design, or programming. For such grounding, the reader is directed to these works: [Paul72] one of the original works in digital robot control; [Paul81] the inveterate and founding handbook of modern robot control and trajectory generation ([Luh83] also provides a useful synopsis on the subject); [Craig89] an updated and more comprehensive version of Paul's

classic; [Craig88] and [Asada86] provide useful explanations and examples about advanced manipulator control; lastly, [Brooks75] and [Allworth87] contribute many principles, techniques, and wise counsel in software and real-time systems design.

In this thesis, the *Kali* robot control system is used as the principal design example which deals with the issues of multi-processor, multi-robot performance and control that represent a significant step in complexity and requirements over that for a single robot Furthermore, this work deals with the diverse interrelated design issues concerning robot controllers and contains a wealth of information useful and necessary to the realization of any such systems.

Finally, it must also be pointed out that this thesis is not an attempt to proselytize the reader to some new, supposedly superior, scheme for a robot control system. Rather it is to demonstrate that the 'yet another robot controller' cliché is no longer relevant by showing the reader that any competent research team can quickly put together a controller tailored to the needs of a particular robotic system.

## 2 The Elements of Robot Controller Design

When we mean to build,

We first survey the plot, then draw the model;

And when we see the figure of the house,

Then we must rate the cost of the erection;

Which if we find outweighs ability,

What do we then but draw anew the model

—William Shakespeare (1564-1616)

## 2.1 The Robot Control Hierarchy

As with any engineering endeavor, the challenge is to decompose the problem into an as architecturally simple and economic solution as possible. Always it boils down to the design decisions and the engineering trade-offs. Of primary importance to robot controllers are the design choices imposed by that archetype of system design—the hierarchy of tasks. A scheme which takes maximum advantage of the natural data abstractions inherent in robotic control systems [Volz84]. Precise specifications for each layer or task in the hierarchy can be independently defined, thus simplifying development and removing, as much as possible, the burden of explicitly programming the details of the underlying mechanical system, *ie.*, manipulator kinematics, dynamics, motor parameters, etc. Changes in either hardware or software do not propagate throughout the system, but remain confined to the relevant levels in the hierarchy.

The fundamental system trade-off for robot controllers is between the computational complexity of their component tasks and the sampling rate of those tasks. That is, given the application: how complex are the strategies for planning, modeling, and control versus the sampling rate at which they are computed? The sampling frequency of control algorithms and, of course, the algorithms themselves define the performance of the system (aside from the inherent electromechanical limitations), but since the designer is always limited by the computational power available, he must trade-off between the two. For instance, a simple servo algorithm may provide fast position control at a high sampling rate, essential for pick-and-place applications, but a more

sophisticated algorithm using laser guiding sensors may provide better tracking control at slower sampling rate, necessary for seam welding. There is always the nagging possibility, though, that the poor performance of a sophisticated control scheme is due to a limitation in sampling frequency and not—as is sometimes the case with a well conceived algorithm, justified in simulation— tailing miserably because of some fundamental, ill perceived flaw.

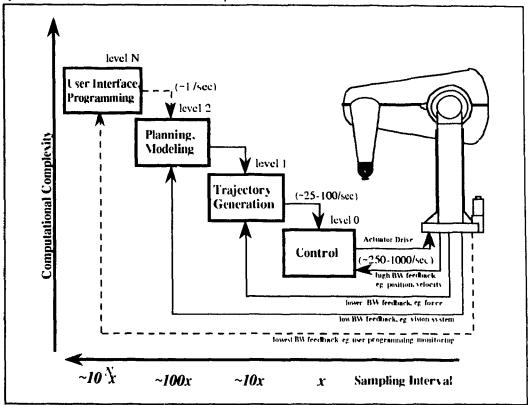

2.1 The Basic Robot Controller Model and System Trade-Oft

A hierarchy of control tasks with increasing complexity and sampling interval as one advances up the hierarchy level 0: actuator I/O and joint level control such as position or tracking control, force compliance, dynamics compensation, etc. Some sensor I/O such as torque feedback for gripping, grinding, better tracking level 1 temporal and geometric motion control. Some simple multi-sensor input is also common, ie., teleoperation with force feedback, peg-in-hole insertions, sensors to avoid collisions, etc. Depending on the system design, integration between levels 0 and 1 varies considerably level 2: world modeling, geometric reasoning, path planning, decisions based on symbolic sensor information, ie., pick up object recognized by vision system

level N user interface (graphic/iconic protocols), programming environment, operating system, and off-line programming

Figure 2.1 about illustrates this basic trade-off in terms of the generic architecture for robot controllers: the user's application process is at the highest level and issues task commands (about 1 per sec) to a trajectory planning process which creates motion requests (more commonly

the user code does the trajectory planning itself), these motions requests (Cartesian space motions, joint space motions, force profiles, almost anything) are then, in turn, processed by a trajectory generator which translates these into a continuous stream of joint set-points quickly enough to ensure smooth motion (~25-100 per sec) while satisfying all the specified spatial, temporal, and dynamic constraints (*ie.*, move in a straight line from A to B at a speed of 1 m/s while not exceeding 10 m/s<sup>2</sup> acceleration); in the final stage, these points are sent to servo loops (these could be individual joint-based PID servos or a Cartesian space control loop with force feedback) which stabilize the manipulator at these set-points (~250-1000 per sec). All motions are typically permitted by the trajectory generator provided that they are within the manipulator's kinematic and dynamic capability. When the trajectories are generated fast enough (usually ten times faster than the manipulator's natural structural resonant frequency [Paul81]), and the servos stabilize quickly enough (*ie.*, in one sample interval), so that tracking error dynamics are approximately linear over successive servo samples, then the generated set-points are perceived as continuous and smooth motions [Ahmad88]!

Despite the fact that manipulators are highly non-linear control plants, this scheme works because it exploits a successive small signal paradigm in which motions are seen as points along nominal trajectories in Cartesian velocity/force subspaces (level 1) and feed-forward dynamics are used to linearize the control (level 0). In this way each layer in the hierarchy locally linearizes its functionality, so as to provide to its higher, 'parent', layer a linear system, in effect. Thus, coupling is highly reduced and the problem is divided into smaller and better defined pieces—the basic principle behind robot controllers. The prevailing assumption, however, is that the nonlinearities are not sufficiently severe to prevent effective local linearizations in the neighborhood of the operating point.

## 2.2 Anatomy of a Robot Controller

In general, robot control requires an implementation of each level in the hierarchy including hardware interfaces. However, the trajectory generation and servoing tasks are the minimum required for the most basic, often sufficient, function of a robot controller, namely,

position and/or tracking control along some specified nominal trajectory. These two tasks, in essence, form the heart of every robot control system.

### 2.2.1 Trajectory Generation

The user application issues motion/position requests to the system in an asynchronous manner using either a blocking (wait for move to be completed) or non-blocking (motion is queued, user code continues) mode. The trajectory generator then interpolates between the last motion/position to the newly desired one. Initially, it is necessary to get smooth motion of the individual joints or joint space control—known as 'joint mode'—because 1) joint trajectory generation is the easiest type of motion to get up and running, and 2) it is often necessary to move the arm into a given position free from singularities, especially for the debugging of other system software. Next, the task is to get smooth motion along arbitrary curves in space, known as 'Cartesian mode,' which simplifies programming, ie., easy workspace geometry with jigs, etc

Generally, trajectory generation is split into three sections. 1) the generation of the set points along a straight line segment where constant linear velocity is variable of control (the user specifying the time for the movement). 2) the merging or blending of motions between line segments to maintain smooth motion (*ie.*, continuity of velocity and possibly acceleration) when rapid changes of direction lead to increased forces on the joints (a fourth or higher order polynomial is usually fitted as the transition path between the line segments [Paul81, Hayward88(2), Lloyd91]), and 3) inverse kinematics which converts the Cartesian space line geometry into the joint space used by the servos. The final, blended Cartesian trajectory can be sent either directly to a Cartesian-based controller, or, more commonly, through inverse kinematics to joint mode controllers. The rate of trajectory generation depends on the structural resonance of the arm [Paul81]—too slow a rate and the arm may begin to shake (resonate). Accurate set-point generation and effective segment transition algorithms in response to sensor feedback are still much of a research topic [Paul85, Hayward84], especially for multi-robot control systems [Ahmad88(2), Hayward88, Hsu89]

Checks for singularities and/or configuration changes are critical at the trajectory generation level, lest the servos are given discontinuous joint demands (eg., equally valid kinematic

solutions 180° apart). Avoiding the problem by picking the solution with the joints closest to the current position is not useful either, because near a singularity arithmetic round off error can cause unpredicted configuration 'flips'. It is standard practice, today, for robot controllers simply to leave it up to the programmer who decides on the configuration—the system simply 'advises' him, ie., checks and issues warning of singularities or imminent configuration changes before the navion or does nothing and crashes during the motion. Many higher level path planning systems, though, have attempted to automate the process

### 2.2.2 Intertask Interface

A queue is used to interface the asynchronous motion requests issued by the user code to the trajectory generator. A linearly interpolated FIFO (First-In First-Out buffer, similar to a queue, except each 'end' is tied to a synchronous task of a different frequency) is used to interface the trajectory generation with the much faster servo control level. In this way large motion displacements are 'smoothed' out into smaller ones that the servo controller can better handle. If a position vector,  $\mathbf{A}$ , represents the current position and,  $\mathbf{B}$ , the desired new position, and  $\mathbf{r}$  the ratio of the servo rate to the trajectory generator rate, then the incremental amount  $(\mathbf{B}-\mathbf{A})/\mathbf{r}$  can be added to  $\mathbf{A}$  for  $[\mathbf{r}]$  interpolated cycles (ie., at each cycle of the servo), so that  $(\mathbf{B}-\mathbf{A})/\mathbf{r}$  is the position at the final cycle. In the event  $[\mathbf{r}] < \mathbf{r}$ , the trajectory generator rate is not an integer multiple of the servo rate, the  $[\mathbf{r}]$ -1st cycle adds the remaining tail-end amount. It could also be spread-out among more cycles to avoid a 'jolt' at the  $[\mathbf{r}]$ -1st cycle.

#### 2.2.3 Servo Control

Because of the decomposition into what amounts to an approximately continuous linear time invariant system, the large body of theory developed for linear systems is usually applied to robot controllers. For tracking control, a dual rate computed torque control strategy is generally employed: pole-placement via state feedback in the main loop with a forward loop compensator

intended to invert the highly non-linear dynamics of the feedback compensated plant [Craig89]. Expressed as an equation:

$$\tau = H(q) u + h(q, q)$$

where  $\tau$  is the vector of torque demands on the joint actuators; H the manipulator inertia matrix, h, a vector function of joint position and velocity, representing all the dynamic forces acting on the manipulator, *ie.*, centrifugal, Coriolis, gravitational, joint friction, etc. (these parameters easily vary as much as three orders of magnitude over different configurations, speed, acceleration [Bejczy74]), finally, u represents the vector of decoupled linear joint controllers, *ie.* a PID controller where  $k_{D_1}$  and  $k_{P_1}$  are the proportional and derivative feedback respectively (for the  $j^{th}$  entry)

$$u_1 = q_{d_1} - k_{D_1} (q_{d_1} - q_1) - k_{P_1} (q_{d_1} - q_1)$$

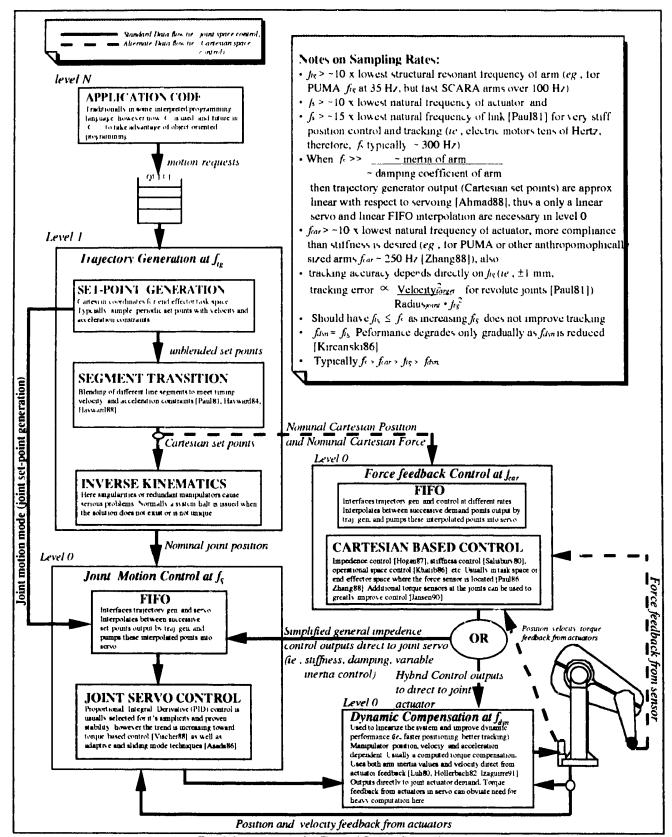

with  $q_j$  and its time derivative representing the joint position and velocity respectively, and  $q_{dj}$  with its time derivatives, the position demand, velocity demand, and acceleration demand respectively. The 'core' loop, *ie.*, the computation of u, must be calculated quickly enough to ensure stable control. A reasonable rule of thumb is that this should be sampled approximately 10 times higher than the joint's natural frequency [Paul81]. For most DC servo motors mechanically coupled to links of a representative mass, time constants are between 20 and 100 msec [Craig88]. Thus, from the point of view of linear theory it should suffice to sample at about 100—500 Hz. However, sampling rates as high as 5 kHz may be required for direct drive arms [Kanade84, Shalom88]. On the other hand, the parameters. If and h depend on the configuration q and change much more slowly than the sampling rate for u. Thus, if it is estimated that these functions vary with a significant amount, say for every 5° of joint displacement, and rate of change of the configuration of the robot is slow, say with a slew rate of less than 180° a sec (fast by todays' direct drive robot standards), then these 'inverse dynamics' need only be calculated at a mere 36 Hz (180°/sec – 5° = 36 Hz) [Kircanski86, Zhang88]! Figure 2.2 below shows the basic tasks of a robot controller and their how they interact, along with details on sampling rates.

Fig. 2.2 Anatomy of a Typical Robot Controller

As it turns out, though, both the gravity and joint friction actually help to dampen out the system and reduce the control bandwidth, so that moderate position/tracking control can be achieved using just plain individual joint PIDs without any dynamics compensation—initially a godsend tot slow computers in the past, now a curse, impeding higher performance and one of the compelling motivations behind 'cleaner' direct drive arms [Kanade84, Craig88, Kazerooni88] with simpler models.

In research robotics, however, the typical application involves not only position/tracking control, but also force control in Cartesian space, *te.*, insert peg in hole by 'feel', or more often a combination of the two. A force sensor at the wrist and/or in the joints provides the appropriate feedback. Other sensor modalities like tactile and vision are being employed in an integrated fashion, so as to achieve greater control than would be possible with any one sensor alone—known as multi-sensor fusion [Hackett90]. However, these algorithms are of a different nature than those used for traditional robotics motion/force control in that they lead themselves more easily to parallel decomposition (*ie.*, image processing algorithms) The discussion here, however, concentrates on the traditional modalities for robot control.

### 2.2.4 Computational Requirements

In general, the computational cost for position/tracking control—by far the most computationally intensive task in the robot control hierarchy—for a six degree of freedom arm is about 50 kFLOPS using ordinary PID servos at a 1 kHz sampling rate. More sophisticated algorithms, such as adaptive PID, require around 2000 kFLOPS @ 1 kHz sampling. Assuming a worst case scenario using, say a 6 DOF direct drive arm requiring a 5 kHz sampling frequency, and using a computed torque method with inverse kinematics in the core loop (about 1500 FLOPS per control cycle), then only 7.5 MFLOPS of computational power are needed—well within the reach of many current microprocessors (see section 2.3.5).

For generalized hybrid force/position control, on the other hand, the requirements are considerable greater. Typically about 750 kFLOPS @ 250 Hz sampling [Zhang88] or about 3 MFLOPS per kHz are needed (15 MFLOPS for the 5 kHz, direct drive manipulator example).

The traditional preoccupation among researchers, however, has been with the inverse dynamic computation—thought to be the critical component in achieving better tracking performance. From the theoretical perspective, the computational complexity has been reduced over the years from about  $O(n^2)$  (105 FLOPS for n= 6 DOF) using Lagrangian formulation, to about O(n) (103 FLOPS for n=6 DOF) [Luh80, Hollerbach82] using various Newton-Euler formulation. It has even be reduced further using a completely empirical approach employing sensitivity analysis techniques to estimate, within a given percentage accuracy, the inverse dynamics, as one would of any function, given enough experimental data points [Izaguirre91]. On other hand, parallel algorithms executed on specialized hardware can achieve O(log n) or better [Lathrop85, Fijani91, McMillan91] (discussed further in sections 2.3.2 and 2.3.3). Table 2.1 summarizes the computational requirements for a typical set of robotics algorithms.

Table 2.1 Computational Requirements for Robot Control

| Algo  | <u>rithm</u>                                 | <u>FLOPS</u>            |  |

|-------|----------------------------------------------|-------------------------|--|

|       |                                              | (per 6 DOF manipulator) |  |

|       | king/Position Control @ 1 kHz                |                         |  |

| (leve | •                                            | 50.1                    |  |

|       | control                                      | 50 k                    |  |

| Adap  | tive PID control                             | 2000 k                  |  |

| Forc  | e control @ 1 kHz (level 0):                 |                         |  |

|       | ness control [Salisbury 80]                  | 1600 k                  |  |

|       | dance control [Hogan87]                      | 2200 k                  |  |

|       | rid control [Raibert81]                      | 2200 k                  |  |

| •     | ational Space control [Khatib86]             | 3000 k                  |  |

| Feed  | -forward dynamic compensation                |                         |  |

|       | Hz (level 0):                                |                         |  |

| [Lut  | •                                            | 80 k                    |  |

| •     | Herbach82]                                   | 60 k                    |  |

| •     | guirre91]                                    | 40 k                    |  |

| (leve | 11):                                         |                         |  |

| Traje | ectory generation & rse kinematics (@ 50 Hz) | 25 k                    |  |

For each algorithm given (as applied to a six DOF robot), the approximate computation cost in floating point operations per second per Hertz of sampling frequency is shown. That is to control a robot, such as a PUMA 560, at 250 Hz sampling frequency using a PID requires 12.5 kFLOPS = 50 kFLOPS x (250 Hz/1 kHz). The force control computational requirements are examined in detail in [Zhang88]

## 2.3 Computing Architecture

Once the designer decides on basic strategies, he or she must precisely determine the functions every level in the hierarchy should perform, being careful to ensure each executes efficiently enough to meet the associated real-time constraints. Next, he or she establishes a computing architecture and then a suitable communication mechanism among the processes. Depending on the resource sharing required by the tasks and the design of applicable parallel algorithms, he or she may choose a loosely coupled architecture based on networks, a tightly coupled one based around a common bus or on some variation between the two

The cardinal rule of digital control systems is to minimize delay, since it most profoundly effects stability and performance [Korein78, Franklin86]. Great care must be taken to effectively reduce system bottlenecks without increasing latency. For instance, adding pipelining may improve system throughput, but it leads to larger delay times [Stone87]. There is nothing to be gained, for example, by using one processor to perform Cartesian trajectory generation while another processor, performing inverse kinematic transformations, waits for input from the first (a possible exception can be made, though, when an algorithm is implemented as an application specific integrated circuit, ASIC, where sheer speed of the pipeline results in a small overall delay [Lee86, Javaher187]). Similarly, the effective computation time in a control cycle (a level 0 control loop) is always diminished by the I/O latency, because the task must wait for input feedback before beginning computation, only the time elapsed from the input of operands to the time when the results are output is actually free for computation.

Since it is generally recognized that certain computations within a sample period can be performed independently of the others, and by allocating them in different ways on a number of concurrently running processors or processing elements (performing select operations), the realm of parallel computing has come to be inexorably tied to robot controller design. There are two major forms of parallel computing: coarse-grain and fine-grain. Coarse grained parallelism, popularly referred to as parallel processing, refers to multiple processes running in cooperative fashion to perform a single program, examples of which are dataflow machines, coarse pipelining, and not

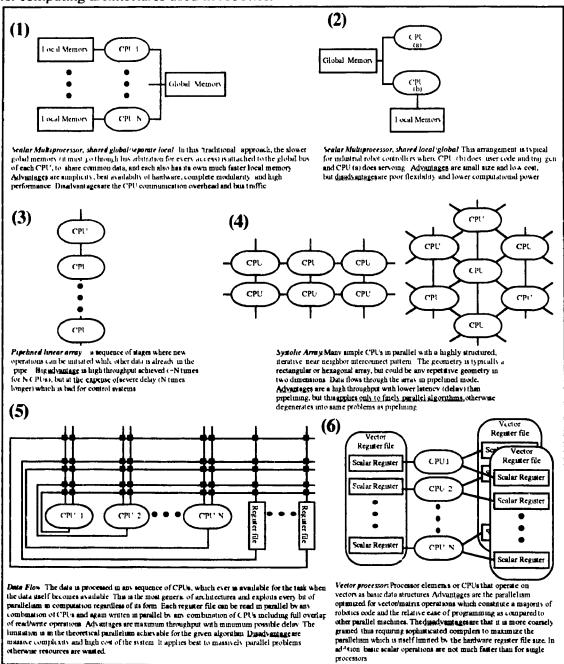

incidentally, multiprocessing systems defined by their communication paradigm like shared memory or message passing. In contrast fine-grain parallelism exists within a process at the the level of the individual operations (*ie.*, additions, subtractions, etc.), examples of which are vector machines, pipelines, systolic arrays, and host of CPU paradigms like CISC, RISC, VLIW, and DSP (terms explained later on). Fig 2.3 below shows basic advantages and disadvantages of typical parallel computing architectures used in robotics.

Fig. 2.3 Parallel Computational Architectures in Robotics

The two, coarse and fine grain parallelism, are, in fact, complementary and may be used concurrently. However, coarse grained parallelism is not user transparent, because it is still too difficult for compilers to translate generic sequential programs into multiple parallel processes. Although it has been observed that a great deal of fine-grain parallelism can be achieved at the cost of increased hardware complexity, the use of large grain parallelism tends to favor overall system simplicity [Stone87].

At first glance, it would seem that the most appropriate solution to the robot controller problem is some complex concoction that exists in the lore of massively parallel computing—a data flow approach (where computations are performed as soon as data becomes available, *ie.*, computation 'flows' with the data), or maybe a pipeline, or systolic array, or maybe something else?

To help in making this determination, a popular metric, first coined by Amdahl [Amdahl67], is used as a comparative measure for different parallel architectures: defined (as one might expect) as the ratio between execution time using a single processor versus that using multiple processors—the 'speedup factor'. Amdahl pointed out that this measure, far from being linear, is, in fact, inherently limited by the amount of parallelism in the algorithm. This parallelism can be characterized by a parameter f, the fraction of computation that must be done serially. Note that this is not the granularity of a parallel algorithm, but rather a more fundamental measurement. The granularity indicates the percentage communication overhead regardless of the parallelism in the algorithm. The two are often confused since highly parallel, small f, architectures are often finely grained and loosely parallel ones, big f, tend to be coarsely grained. The effective speedup, S, according to Amdahl becomes:

$$S = \frac{P}{fP + 1 - f}$$

when f=1 all computation must done serially, so hardware parallelism is wasted and no speedup is possible (S=1). The same or worse holds true for the granularity (it is quite conceivable that a multiprocessing system requires so much communication, that it actually runs slower than the single processor case). On the other hand, when f=0 then all computation is in parallel and performance increases more directly with the number of CPUs (S=P). Another important indicator is the efficiency, E, of a parallel architecture in matching an algorithm. It is defined as E = S/P ( $0 < E \le 1$ ,

when E=1 then 100 percent parallelism). E is essentially limited by the inherent parallelism of the algorithm. This measure of efficiency, interestingly, leads to a fundamental conclusion about the practical parallelism possible in level 0 robotics algorithms.

### 2.3.1 Multiprocessing

The general hope lying behind distributed processing systems is that if one conventional processor isn't fast enough then maybe more will be. However communication bottlenecks and the inherent limits in the parallelism of robotics code restrict performance gains. Because real-time control tasks are as much 1/O driven as computationally bound, communication schemes become a large part of the problem. Li and Malek [Li88] as well as Stone [Stone87] give detail analyses on various communication models. In the best case, assuming fully overlapping communications (rarely achieved), the system speedup is bounded by the communication overhead, for a uniform communications distribution,  $S_{max} = 1$ /(percent communication overhead or granularity). So a 10 percent overhead (a typical number) results in maximum speedup factor of less than ten, no matter how parallel the algorithm is (ie., f = 0) or how many CPUs are employed! (in general, there are an optimal number of CPUs resulting in maximum speedup for a given algorithm). Thus, as a rule, multiprocessor architectures should consist of inexpensive and simple processing elements with interprocess communication being as fast and efficient as possible, ideally easily reconfigurable and expandable with minimal deterioration of bandwidth. However, for practical purposes, a simple common bus architecture approach is often chosen (see appendix A).

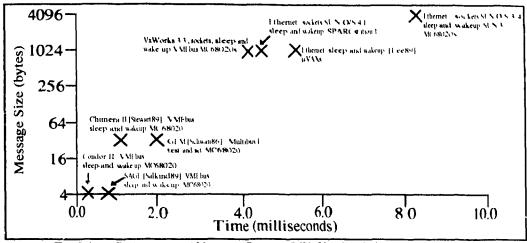

For communication design there are basically two techniques: message passing and shared memory. Message passing makes the software easier to design and debug (provides for better data hiding more like object oriented systems [Schwan85, Bihari89, Clark89, Gentleman89]), but at a severe cost due to the excess overhead required for the message protocol. The performance bottleneck comprises not only the effective bus data rate (especially where the system is loosely coupled and shared memory is not used to hold messages) and memory contention (in more tightly coupled systems). Typical latency times on the order of milliseconds (see figure 2.4 below).

Fig. 2.4 Performance of Message Passing O/S's Used in Robotics

Based on multiprocessor intercommunication across a common bus or network

Shared memory, on the other hand, offers an approach nearing the maximum speed of the bus. However, only when processors are designated fixed priority access to the bus and contention is kept to a minimum. Most researchers prefer a shared memory architecture, because the robot control hierarchy defines tasks with large granularities, *ie.* highly decoupled and serial in nature. So memory accesses are largely confined to the local processor, thus making bus contention infrequent and predictable—the case where shared memory works best. A major disadvantage, however, is that such algorithms result in poor hardware utilization for highly parallel architectures (*ie.*, many CPUs with communication overhead, figure 2.5 below). [Leung88].

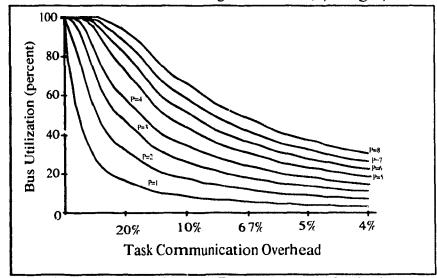

Fig. 2.5 Multiprocessor Bus Bandwidth vs Task Communication Overhead

Where P is the number of processors Based on a stochastic Petri Net

model with a Markovian queueing theory (ie., CPUs randomly accessing

the bus and waiting if it is busy)[Marsan83, Han89] Break point is 20%

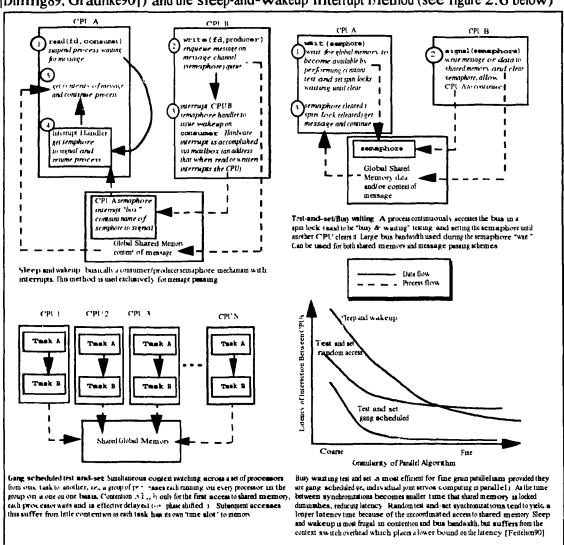

Bus contention depends on the two factors: a) bus hardware performance features such as arbitration and how fast memory is accessed (see Appendix A), and b) the amount of interaction between the tasks executing on the various processors which is basically synchronization problem: any shared data structure updated by more than one processor must be protected from conflicting concurrent updates by some sort of semaphore mechanism. The two common methods are the test-and-set spin-lock (on which many variations on exist such as delayed-retry, tournament scheduling, etc. [Dining89, Graunke90]) and the sleep-and-wakeup interrupt method (see figure 2.6 below)

Fig. 2.6 Multiprocessor Communication Methods

Nevertheless partitioning the robot control problem for a multiprocessor is straightforward along the traditional coarse-grain lines in the hierarchy (ie., trajectory generation in one processor and servo control in another) and a slew of systems have been designed strictly on

this paradigm (see section 2.7). Generally, the parallelism offered was the splitting of individual joint servo loops among different processors (S≈P, but S=1 for everything else including Cartesian based control). Another customarily adopted technique is to perform computations redundantly by all processors to achieve more partitioning for a given algorithm, sacrificing efficiency. On the other hand, for very coarsely grained cases, some researchers have even offered a network-based solution [Lee89]. More finely grained approaches targeted at specific algorithms (*te.*, inverse kinematics), however, require substantial engineering. Nigam and Lee [Nigam85] proposed the use of commercial microprocessors interconnected to suit the particular algorithm with S=2.5. On the other hand, Kasahara and Narita utilized a special depth first/initial heuristic search scheduling algorithm [Kasahara85] on a multiprocessor system connected by a common bus to perform inverse dynamics Levin [Levin87] employed a Transputer (general purpose CPU with serial links for communication, about 0.65 MFLOPS with floating point coprocessor) array for servo control with dynamics compensation. Other radical hardware approaches have been proposed all dealing with the intensive number crunching level 0 algorithms such as inverse dynamics, kinematics, Jacobians, and control.

### 2.3.2 Systolic Arrays and Pipelines

Most robotics algorithms can be conveniently represented as an array or vector, so it seems plausible that systolic array processing has the potential to offer great performance. However, these type of processors rely on a high degree of regularity, processing possibly hundreds of identical elements, to achieve high speed—a high degree of fine grain parallelism. The problem arises that as the number of sequential elements drops (ie., what is called a 'stall' when the data configurations or instructions change randomly which force a reloading of the array), the overhead in beginning or filling the array can far exceed the actual calculation time. Pipelines suffer from the exactly the same problem, being the one dimensional case of array processors.

Nash and Przytula [Nash85, Przytula88] were the first to successfully develop a systolic array (16x16 processing elements) to perform linear matrix operations useful for most robotics algorithms including kinematics and inverse dynamics. Orin et. al. [Orin85, Orin86, Ling88] designed a pipelined multiprocessor (32-bit floating point ASIC implementation) system for

Jacobian computations and inverse dynamics (S<1.5). Lee and Chang [Lee86. Chang88] employed the bit-serial CORDIC algorithm [Volder59, Harber88] in a 25 stage pipeline to solve the inverse Jacobian very quickly (40 μsec inverse kinematic solution), but with relative inefficiency (S=1.38, E=0.06), hence the large pipeline needed to 'squeeze-out' the last bit of computation. Javaheri [Javaheri87] designed a floating point ASIC with 4 communication ports intended as processing elements for more efficient systolic array (1<S<2.2, E<2.2/P). Kircanski *et al.* [Kircanski89] used array processor approach using a multi-stage pipeline which matches the number of hardware multipliers and adders in the system against the mix of additions and multiplications in the instruction stream. Coupled with a novel symbolic approach to robot kinematics and dynamics algorithms [Kircanski88], the control loop (for 6 DOF) was claimed to be computed in 100 μsec. Efficient use of processing elements, though, drops off rapidly as the number of multipliers and adders is increased (1<S<2.2, E<0.7).

The basic problem is that all such architectures is that provide only increased bandwidth or throughput and not smaller latency. The time required for computation is always the maximum array depth (*ie.*, the number of processing stages required to complete the algorithm) multiplied by the processing stage operation time.

Trying to avoid this, Wang and Butner [Wang87, Butner88] created a heterogeneous hierarchy of processors for level 0 control each specialized for a given operation: bit slice processor for inverse kinematics & dynamics, CORDICs for trigonometric functions, and Tl32020 DSPs for servoing. Results are impressive with 300 µsec for a complete control loop (computed torque servo with dynamics in the core loop). However interprocessor communication consumes over 16% of the processing time (S<2.3).

On the other hand, when the problem is confined only to inverse dynamics (no kinematics, trajectory generation, or code branching), remarkable speedups are possible. Fijani [Fijani91] showed that  $O(n^3)$  inverse dynamic algorithms are optimal for parallel computation and that systolic arrays can be built to achieve S>5 over the best serial algorithms [Fijani91(2)], including communication overhead! Similarly, early on, Lathrop [Lathrop85] presented results using a Newton-Euler formulation with a logarithmic recursion implementable as a systolic pipeline

1

having  $O(\log n)$  overall execution and S=4. A solution is available at each clock cycle; however, there is a 400+ pipeline stage latency (6 DOF) for the results.

### **2.3.3** Vector Machines

Alternatively, vector machines make use of the fact most robotics algorithms can be expressed as 3-element vector operations (*ie.*, optimally decomposed 4x4 homogeneous matrices). It seems straightforward that a three fold increase in speed is possible. Ling [Ling88] proposed a vector processor of this type with a 20 cycle vector-matrix multiple time (3x1 by 3x3) a 6 MFLOPS rating with 125 nsec cycle time (2.5 µsec for the vector-matrix operation). However even commercially available, non-vectored DSPs (Digital Signal Processors, optimized for vector and matrix operations) [Dyer88] such as the MC96000 (Motorola) can perform the same operation in 24 cycles [Sohie88], not mention the vastly superior implementation technology available to a major semiconductor houses like Motorola (the same vector-matrix operation using a 75 nsec cycle time executes in 0.89 µsec on the MC96000). Interestingly, this is accomplished using only a single overlapping multiplier/adder unit.

Again for the specialized inverse dynamics problem, new approaches have yielded remarkable results. McMillan [McMillan91] used a Parallel Block Predictor-Corrector numerical method to solve for inverse dynamics, treating it as a differential equation problem. Employing a CRAY Y-MP supercomputer (one of the traditional vector machines) speedups are as high as 5.2 were achieved (# CPUs = 8, E<0.67).

#### 2.3.4 Scalar Machines

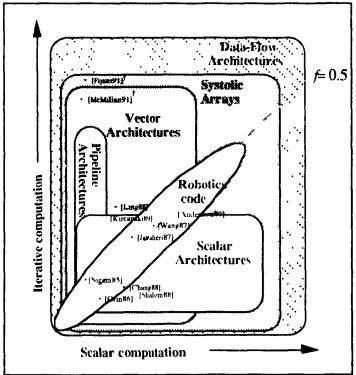

Quite clearly robotics algorithms are not very parallel in nature. In fact, it can be roughly concluded, by empirical evidence alone (ie., all the previous robotics architectures S<3, except for special sub-problems, eg., inverse dynamics) that only 2 CPUs really are needed for maximum speedup of level 0 robotics code, anything more seems to be wasted. So  $f \approx 0.5$  as figure 2.7 below illustrates.

Fig. 2.7 Relationship Between Robotics Code and Processor Architectures

As previous system architectures show, robotics code is actually more scalar in nature (hence the limited performance pipelines and systolic arrays). It seams that VLIW machines with only two floating point units is sufficiently optimal for robotics †Inverse dynamics only.

Realizing this Andersson [Andersson89] opted for the single 'big-iron' approach (a fast single scalar processor), where one general purpose CPU (in this case with two floating point units using parallel buses to memory called 'JIFFE') performs all level 0 tasks. Efficiency is over 99%, and the processor was capable of performing the complete inverse dynamics and PID servoing in less than 50 µsec (about 20 MFLOPS, 40 MFLOPS on matrix addition and multiplication operations.

It appears inescapable that scalar processors constantly absorb any advantage claimed by parallel processing for traditional robotics force/motion applications (the same cannot be said, however, for other areas like image processing). Thus, it can be argued that at level 0 in the robot control hierarchy, parallel processing (as applied to a single manipulator) doesn't work. Robotics must be thought of as a coarsely grain operation along the traditional lines in the robot control hierarchy: the user code and trajectory generation together, since the user code, basically Cartesian motion statements, is closely coupled to motion requests which may vary considerably in

computation at run-time (ie., error handling, collision avoidance, user code debugging, etc.), level () tasks, such as the servoing, can be placed in a separate CPU, since it is a critical process not to be burdened with unnecessary computation, or, worse, stopped because of a data error (eg., a singularity). In general, the problem is to deal with the physical limitations of the object being controlled.

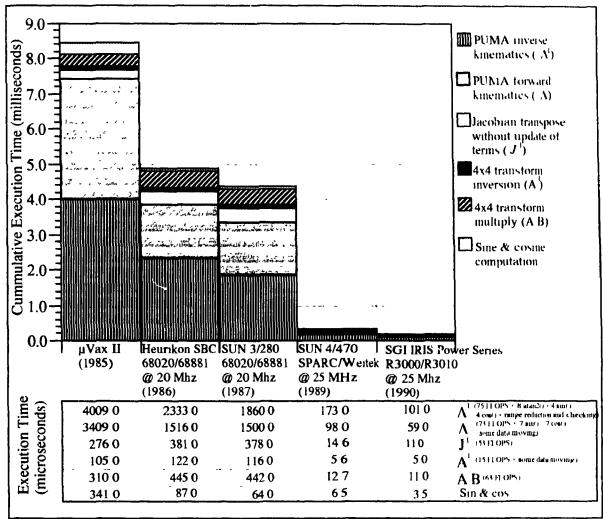

Fig. 2.8 Aggregate Performance of Current Microprocessors on Robotics Code

Using the RCCL speed test by John Lloyd All arithmetic is performed using single precision floating point and the standard C library for trigonometric functions A SPARCstation™ by SUN Microsystems is about 30 times faster than a μVAX and the Mips R3000 CPU with R3010 FPU (Floating Point Unit) in the Silicon Graphics IRIS workstation is up to 50 times faster than a μVAX in floating point performance on robotics code

Interestingly enough, commercial microprocessors are taking a similar track to the one used by Andersson—one instruction stream with 2 floating point units (usually one adder and one

multiplier) with overlapping operation. The progress of microprocessor technology has improved so much that the numerous algorithmic improvements and specialized hardware created by researchers in the past is rapidly becoming obsolete in comparison. In addition, on the hardware side, the highest performing research systems are rapidly losing their performance edge over commercial processors. Consider figure 2.8 above showing some of the improvements in recent microprocessors (already considered 'old', the newer CPUs are faster still, like Advanced Micro Devices 29050 performing vector-matrix (3x1 by 3x3) multiply operations in 0.3 µsec and 4x4 matrix multiplies in 0.9 µsec approaching 40 MFLOPS for these operations [AMD90]). It is getting increasingly difficult to out perform the major semiconductor houses with discrete home-brew solution like JIFFE, whether in silicon, ie., ASICs, or not.

### 2.3.5 Super Chips

The argument now is which commercial CPU is fastest? In order to make this decision, an understanding of minimizing the execution time is necessary: three factors contribute to this: N, the number of instructions that must be executed, C, the average number of processor cycles per instructions, and S, the number of seconds per processor cycle, so that execution time =  $N \times C \times S$ . Primarily these three depend on the compiler's optimization capability, the instruction set architecture, and the implementation technology. However the interrelationship between the factors is quite complicated, decreasing one factor may increase another by as much or more!

The traditional technique for general purpose processors is to decrease N at the expense of a smaller C. This approach, termed CISC (Complex Instruction Set Computing), attempts to better utilize the microparallelism present in horizontally microcoded machines by defining more complex instructions with more internal micro-parallelism in the hope that N would decrease more sharply than C. On the other hand, the RISC (Reduced Instruction Set Computing) approach employs the opposite philosophy: reduce C and S at the expense of N. In this case, hardwired instructions and heavy pipelining try to reduce C and S while powerful compiler optimization techniques keep N down [Gimarc87, Piepho89]. The result is a considerable overall reduction in the execution time. Current techniques to further improve performance involve increasing parallelism.

further decreasing C, by executing more than one instruction per cycle and using elaborate instruction sequencing techniques [Krick91]. Essentially, these are simplified dataflow designs made possible by 'look-ahead' techniques in the instruction stream, register scoreboarding (tagging those registers not being used by the current instruction as available for a concurrent instruction in another execution unit), and even more highly optimized compilers. One such new hardware technique is superpipelining where two or more pipelines are used in parallel an instruction is moved into each of execution pipelines every cycle. Essentially, it is a simple, fixed multiple dispatch architecture. Superscalar is another, where instructions are fed into more than one execution unit by a dispatch unit. It is more generalized than superpipelining, since dispatching is not on a fixed schedule, but depends more on the instruction stream (Johnson 911 provides an indepth discussion on superscalar design). Still another, though simpler variation, on these themes, is also possible by embedding more than one instruction (at compile time) in each machine word Known as VLIW (Very Long Instruction Word) processors, they seek to gain speed by increasing memory bandwidth to the CPU through shear word width, eg. 128 bits, so that many instructions can be fetched in one memory cycle (JIFFE, for example, uses a 200-bit instruction word length) Figure 2.9 below shows the comparison of single precision floating point capabilities of currently available microprocessors/computers (see Appendix A for detailed discussion on current and future commercial CPUs).

Fig. 2.9 The LINPACK Benchmark for Current Microprocessors

1

The LINPACK algorithms benchmark [Weicker90], developed at the Argon National Laboratory, measures aggregate floating point performance over a wide range or mathematical computations including matrix multiplication and trigonometric functions, etc. It is normally used to characterize efficiency in vector processing, but since robotics contains much matrix/vector and trig functions, a high LINPACK rating is a reasonable, though by far not definitive, indication of the relative ability of that processor to execute robotics code

### 2.5 Real-Time Kernels

Traditionally, real-time kernels have been a great preoccupation of robot controller designers, most of whom have dwelt on creating 'better' real-time kernels with more features and facilities. However, these kernels, varying from the simple [Chen86] to the complex [Stewart89], typically haven't achieved any better performance than other real-time kernels on the same hardware. This is because the real problem is that robot controller performance is not generally limited by the real-time kernel, but by the robot control software itself, or the lack of it, its integration with the real-time kernel and the application at hand [Gopinath89]

As a rule, in robotics applications the essential performance factors for real-time kernels are: a fast context switch time and low interrupt latency, to provide for the fastest possible response to critical events and a minimized overhead for periodic functions which comprise bulk of robot controller computational requirements; an interprocess (or in the case of multi-CPU systems) interprocessor communication and synchronization mechanism (eg., usually shared memory with semaphores), to provide for effective coordination among the required tasks, and debugging & development tools, though considered ancillary features, to provide the necessary ease in engineering a successful system. See Appendix B for an in-depth comparison of current commercial real-time kernels.

### 2.6 Robot Joints

A robot is essentially a collection of individually controlled joints each of which can be seen as a complete sub-system on its own (except in the case of Cartesian mode control in which all the joints are collectively controlled). Whereas many different types of actuation and feedback mechanisms exist and are being developed, the gear reduced DC electric motor with optical encoder position feedback is still the actuation/feedback most commonly employed today (though high torque output direct drive electric motors are being increasingly adopted [Kanade84, Kazerooni88, Shalom88]). Indeed, robot joints are becoming progressively more light weight, compact, easily integrated, efficient, and nearly maintenance free. [Dote90] provides a comprehensive examination

of both the practical and theoretical aspects in implementing a single joint or motor control systems. The typical joint control and feedback is shown in figure 2.10 below.

Fig. 2.10 Typical Joint Control & Feedback

### 2.6.1 Sampling Issues

There is no doubt that advances in technology will obviate—indeed, to a large degree, they already have obviated—the need for any consideration of the effects of discrete time controllers. The most obvious of which are:

• Sampling frequency. The approximation that the sampling rate of a discrete time algorithm is continuous which is usually acceptable if the controller sampling rate is sufficiently higher, ie., 10 times higher [Franklin86], than the natural frequency of the system being controlled. Otherwise explicit

consideration of the discrete time effects must be taken in consideration (eg., if a servo algorithm requiring one 'tick' is O(n), then for two 'ticks' it is  $O(n^2)$  instead).

- Controller delay. There is always a finite delay between sampling feedback variables and outputing resultant control signals. There is also a measurable delay in the power amplifier and in the current to the motor, and thus in torque at the joint. Such unmodeled delays should at be at least three times less than the control cycle time [Asada86].

- Quantization noise. Because the 'real world' is analog and feedback control signals are discretized through digital to analog and analog to digital converters, there is a quantization error in their measurement. This inherently limits the accuracy of any digital control system (ie., a joint position servo usually gets to within ±1 encoder counts of demanded position) and can lead to drastic results in adaptive systems that accumulate round off errors.

- Dynamic range and word size. Both Simulation and practical experience have shown that at least 16 bits of angular resolution are required for adequate motion control (typical high precision pick-and-place robots use 20 bits of accuracy [Seiko90]). In the past, attempts to minimize computational cost using integer arithmetic are now supplanted by the era of floating point calculations—no more bit rolling and twiddling to keep significant digits on integer only machines! The IEEE 32-bit floating point format [Coonan80] has a 20 bit mantissa giving one per million accuracy or 1.2 arc seconds (just enough for current high precision robots, double precision may be needed in the future otherwise a retreat to 32-bit integer arithmetic, yielding an accuracy of 3x10-4 arc seconds, may be necessary).

### 2.6.2 Motors & Amplifiers

In theory, most DC motors produce torque in direct proportion to their armature current, which means that one needs to servo the armature current to a command voltage using a power amplifier controlled through a D  $_4$ C (Digital to Analog Converter) in the digital domain. However, while accelerating the load, the motor is acting like a generator, and producing a 'back EMF' which is directly proportional to the motor (and load) speed. Therefore, in order to achieve a constant armature current, it is necessary to apply progressively more voltage to overcome the back EMF, which is often the limiting factor in the loop. One way to overcome the low-speed effect of back EMF is to put the armature in the feedback path of a DC power amplifier, or equivalently establish a 'current loop' servo (*ie.*, as a current mode voltage source). In fact, most sophisticated manipulator control schemes do adopt this technique, since generated motor torque is proportional to armature current,  $\tau = K_L I_{armature}$ , *ie.*, a computed torque servo control formulation).

A more efficient way to deal with the 'back EMF' is to use a switching amplifier such as a PWM (Pulse Width Modulation) amplifier which is designed to apply relatively high voltages to the motor for brief, variable time slices. In this case, it is required that the PWM amplifier is, at least roughly, matched to the motor's inductance so that power losses are minimized (ie., motor must meet a minimum inductance for smooth wave form). This is expressed as the form factor for the amplifier and defined as the ratio of the RMS current to the average current in the motor ( $k = \frac{1}{1}$  It is dependent on amplifier switching frequency, the electrical time constant of the motor (ie., L/R, see figure 2.10) and any other stray inductances ('ballast'). The power losses are proportional to the square of both the form factor and the torque generated (ie., Power loss  $\propto k^2\tau^2$ ). Thus once a motor has been selected and the torque requirements fixed through selection of gearing (if necessary), losses can be minimized by making k to as close to 1.0 as possible.

In general, power amplifiers are of two basic types: linear or switching. While linear amplifiers have excellent stability and control characteristics (*ie.*, no switching, so the form factor is 1.0), due to their linearity, they suffer from from heat generation in the output stage, because they operate in the high dissipation region of the transistor characteristic. Switching amplifiers overcome

this problem by controlling their output stage so that they are alternating between the fully on and off (ie., transistor saturation or off) value of the output voltage. By modulating the duty cycle of the output, switching amplifiers generate a given voltage or current, depending on the variable of control. Due to the high current square wave frequencies necessary a high electromagnetic radiation usually accompanies switching mode power amplifiers. However a few new designs, have used very high switching frequencies together with small output filters that largely eliminate the radiation, but leave a wide performance bandwidth [Copley88]. Furthermore, unbeknownst to most researchers. switching mode amplifiers have typical closed loop current-mode bandwidths (not sampling frequency) of about 1-3 kHz. This is not a problem for slower geared manipulators with low sampling needs (eg., less than 1 kHz), but for very high performance direct drive arms, which may need over 10 kHz sampling frequencies, this could become a problem as the control algorithm may respond to the current switching itself. Generally, the switching frequency must be high enough to ensure that the motor control system does not respond to the transistor switching itself (ie.,  $f_{switching} > 10 f_{bandwidth\ of\ control\ loop}$ ). However, hysteresis and eddy current losses in the motor increase with frequency, thus limiting the maximum switching frequency usable with a particular motor. On the other hand, the amplifier must be designed so that the  $1/f_{switching}$  is large enough relative to the transistor switching delay time to ensure linearity, yet small enough so that power losses in the transistors (which increase in proportion to  $f_{switching}$ ) are not excessive. Motor/amplifier selection is not as trivial as it first seems!

As far as motors are concerned, heat is the principal killer of performance; however, so long as it can be adequately removed, performance can be prevented from diminishing significantly (the same is true of power transistors and consequently power amplifiers). Electric motors can, in general, take peak currents many times higher than their continuous RMS values for short durations, ie., the time the motor can, in effect, 'sink' the excess heat generated. [Fleischer88] provides a useful summary on motor characteristics and selection. See figure 2.11 below.

Fig 2 11 Motor Performance Characteristics

Performance 'band' (ie., power, current, and efficiency) for electric motors is better when cold and diminishes considerably when hot (by as much as 50%) Brushless motors, because of superior heat dissipation and non-mechanical commutation, have a much larger operating envelope than their mechanically commutated, brushed counterparts

# 2.7 System Implementation Approaches

Since any system is a product of past experience and current influence, it is beneficial to examine the many possible overall system approaches to robot controller problem, each implementing to various degrees different levels in the hierarchy. Figure 2.12 below illustrates. A workstation host with graphical user interface is usually employed to perform application level programing and modeling/planning (A). This includes everything from basic robot motions, with on-line path modification in Cartesian end-effector space integrated with sensor I/O, to task level programming systems. The user is presented a C language library interface or increasingly a C++ [Stroustrup87] library interface to which user code is linked. Applications are built by creating, combining, and manipulating functions or objects defined from system primitives.

In high level motion planning (level 3) systems like 'Handey' [Lozano-Pérez88], the approach is to concentrate the code solely on higher level code and employ a commercial controller for all lower level control intricacies. It is convenience to do so, since point to point motions is all that is required. On the other hand, lower level, more control oriented systems like RCCL [Hayward86, Lloyd88] actually perform trajectory generation on the host workstation in real-time

(UNIX kernel modification needed) and use the commercial controller only to perform position servoing and other associated I/O (A, B).

Fig. 2.12 The Basic Robot Controller Architectures

Implementations of the robot controller model vary from complete ground-up systems (A, C, D, E, F, G, H) to high level only versions (A, B) using existing commercial controllers, and all the variations in between Such as (A) programming host, (C,D,E) traj gen, and (B) servoing with actuator drive Or incorporating the commercial controller for robot I/O, but not for sensors (A, B, C, D, E, G, I) It is also usually the case that some form of teach pendent (J) or handcontroller (whether

home-brew or commercial) is part of such systems