# Analog Test Bus Structure for Wide-Bandwidth High-Frequency Measurements

## William Dennis Ledingham

Department of Electrical and Computer Engineering McGill University Montréal, Québec, Canada

March 2025

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Masters of Science in Electrical Engineering

© 2025 William Dennis Ledingham

## Abstract

Analog test buses facilitate the testing of analog components in integrated circuits through dedicated test ports and switches. IEEE 1149.4 is the established analog test bus standard, but has had limited adoption due to the low maximum measurement frequency of existing implementations. A common approach to accurately measure high-frequency signals is to use high-speed test equipment, such as vector network analyzers (VNA), which employ a detailed calibration procedure. To extend the measurement bandwidth of an analog test bus, this thesis proposes a buffer-based structure that uniquely applies the VNA calibration methodology to de-embed the effects of the test bus components. Calibration reference resistors were integrated into the test bus constructed of voltage and current buffers that characterize the systematic errors present. The proposed test bus structure was tested and compared with the 1149.4 test bus using a discrete component PCB simulation and experiment aimed at measuring a transimpedance amplifier (TIA). The simulation showed the proposed test bus exactly measuring the TIA's performance, while the 1149.4 test bus deviated at higher frequencies. The experimentally measured results echoed the simulation, with the proposed test bus more closely tracking the ideal performance while the 1149.4 test bus became inaccurate. An additional simulation tested the performance of the proposed test bus in a high-speed on-chip implementation with a BiCMOS transistor-level design. The onchip simulation again showed that the proposed test bus successfully measured the TIA with little error, even with induced process and mismatch variations. These results verified the ability of the proposed test bus to characterize and extract high-frequency errors, extending the measurement bandwidth.

## Résumé

Les bus de test analogiques facilitent le test des composants analogiques dans les circuits intégrés grâce à des ports de test et des commutateurs dédiés. IEEE 1149.4 est la norme de bus de test analogique établie, mais son utilisation a été limité en raison de la faible fréquence de mesure maximale des implémentations existantes. Une approche courante pour mesurer avec précision les signaux à haute fréquence consiste à utiliser des équipements de test à haute vitesse, tels que les analyseurs de réseaux vectoriels (VNA), qui emploient une procédure d'étalonnage détaillée. Afin d'étendre la largeur de bande de mesure d'un bus de test analogique, cette thèse propose une structure basée sur un tampon qui applique de manière unique la méthodologie d'étalonnage des VNA afin de supprimer les effets des composants du bus de test. Des résistances de référence pour l'étalonnage ont été intégrées dans le bus de test constitué de tampons de tension et de courant qui caractérisent les erreurs systématiques présentes. La structure du bus d'essai proposé a été testée et comparée au bus d'essai 1149.4 à l'aide d'une simulation de circuit imprimé à composants discrets et d'une expérience visant à mesurer un amplificateur à transimpédance (TIA). La simulation a montré que le bus d'essai proposé mesurait exactement les performances de l'amplificateur de transimpédance, alors que le bus d'essai 1149.4 s'en écartait à des fréquences plus élevées. Les résultats des mesures expérimentales ont fait écho à la simulation, le bus d'essai proposé se rapprochant davantage des performances idéales, tandis que le bus d'essai 1149.4 devenait imprécis. Une simulation supplémentaire a testé les performances du bus de test proposé dans une implémentation sur puce à grande vitesse avec une conception au niveau des transistors BiCMOS. La simulation sur puce a de nouveau montré que le bus de test proposé mesurait avec succès le TIA avec peu d'erreur, malgré les variations induites de processus et de désadaptation. Ces résultats ont vérifié la capacité du bus de test proposé à caractériser et à extraire les erreurs à haute fréquence, en élargissant la bande passante de mesure.

# Acknowledgments

I extend my deepest gratitude to my supervisor, Professor Gordon Roberts, for his support and guidance throughout this project. His expertise in analog testing and scientific communication of engineering research pushed this project to be the best version of itself. Working under his supervision has been a valuable experience that I will take into the future and has guided my professional aspirations. My appreciation also goes to my colleagues and friends, Jean-Christophe Couture and Jasper Yun, for their help working with the various tools and circuit design programs used throughout this project. They were a great resource for discussing problems, understanding circuit design ideas, or complaining about a failed experiment. I would also like to thank Professor Roberts, McGill University, and the Natural Sciences and Engineering Research Council (NSERC) for their financial support towards this research project. I am grateful for the opportunity to study and conduct research full-time at a great institution. My appreciation also goes to my partner, Kira Feighan, for proofreading various parts of this project and providing excellent scientific writing advice. Finally, I want to thank my family for their endless support and encouragement throughout my academic journey.

# Table of Contents

| $\mathbf{A}$ | bstra                        | ct      |                                           | i   |

|--------------|------------------------------|---------|-------------------------------------------|-----|

| $\mathbf{R}$ | ésum                         | ıé      |                                           | ii  |

| $\mathbf{A}$ | ckno                         | wledgr  | nents                                     | iii |

| Ta           | able (                       | of Con  | tents                                     | iv  |

| Li           | st of                        | Figur   | es                                        | vii |

| Li           | $\mathbf{st}$ of             | Table   | ${f s}$                                   | xi  |

| Li           | st of                        | Abbro   | eviations                                 | xii |

| 1            | Intr                         | oduct   | ion                                       | 1   |

|              | 1.1                          | Motiv   | ation                                     | 1   |

|              | 1.2                          | Resea   | rch Goals                                 | 4   |

|              | 1.3                          | Struct  | cure of Thesis                            | 4   |

| 2            | $\operatorname{Lit}\epsilon$ | erature | e Review                                  | 6   |

|              | 2.1                          | Digita  | al Test Bus                               | 6   |

|              | 2.2                          | Analo   | g Test Bus                                | 7   |

|              |                              | 2.2.1   | High-Frequency Performance                | 8   |

|              |                              | 2.2.2   | Gain Calibration                          | 11  |

|              | 2.3                          | High-   | Frequency Measurements Using S-Parameters | 12  |

|              |                              | 2.3.1   | S-Parameter Background                    | 13  |

|              |                              | 2.3.2   | Directional Coupler and Schematic         | 15  |

|   | 2.4 | Vector Network Analyzer Calibration                          | 15 |

|---|-----|--------------------------------------------------------------|----|

|   |     | 2.4.1 Procedure Details                                      | 16 |

|   |     | 2.4.2 Calibration References                                 | 22 |

|   | 2.5 | Summary                                                      | 27 |

| 3 | Pro | posed Analog Test Bus Structure                              | 28 |

|   | 3.1 | 4-Port Test Bus                                              | 29 |

|   |     | 3.1.1 High-Frequency Errors                                  | 31 |

|   |     | 3.1.2 Structural Requirement to Enable Calibration           | 33 |

|   | 3.2 | 4-Port and 1149.4 Test Bus Structural Comparison             | 34 |

|   |     | 3.2.1 Highlighting the High-Frequency Limitations            | 35 |

|   | 3.3 | 2-Port Test Bus                                              | 37 |

|   | 3.4 | 2-Port, 4-Port, and 1149.4 Test Bus Structural Comparison    | 39 |

|   |     | 3.4.1 Highlighting the High-Frequency Limitations            | 40 |

|   | 3.5 | Summary                                                      | 41 |

| 4 | Enh | nancing High-Frequency Measurement Accuracy with Calibration | 42 |

|   | 4.1 | Converting S-Parameters to Voltage and Current               | 43 |

|   | 4.2 | 4-Port Test Bus to 2-Port Conversion                         | 45 |

|   | 4.3 | Calibration References                                       | 46 |

|   |     | 4.3.1 Reference Resistor Low-Frequency Measurement           | 48 |

|   |     | 4.3.2 Derivation of Resistor S-Parameters                    | 49 |

|   | 4.4 | Comparison of 4-Port and 1149.4 Test Bus                     | 50 |

|   |     | 4.4.1 1149.4 Test Bus Example                                | 51 |

|   |     | 4.4.2 4-Port Test Bus Example                                | 52 |

|   | 4.5 | 2-Port Test Bus Reverse Signal Requirement                   | 55 |

|   |     | 4.5.1 Comparison of 2-Port Test Bus                          | 56 |

|   | 4.6 | Practical Error Block Consideration                          | 58 |

|    | 4.7   | Summary                                        | 60 |

|----|-------|------------------------------------------------|----|

| 5  | PCI   | B Test Bus Experiment                          | 61 |

|    | 5.1   | Design of Experiment                           | 62 |

|    | 5.2   | Simulation Results                             | 66 |

|    | 5.3   | Measured Results                               | 68 |

|    |       | 5.3.1 Discussion                               | 69 |

|    | 5.4   | Summary                                        | 71 |

| 6  | Exte  | ending the Test Bus to the IC                  | 72 |

|    | 6.1   | Challenges of IC Integration                   | 72 |

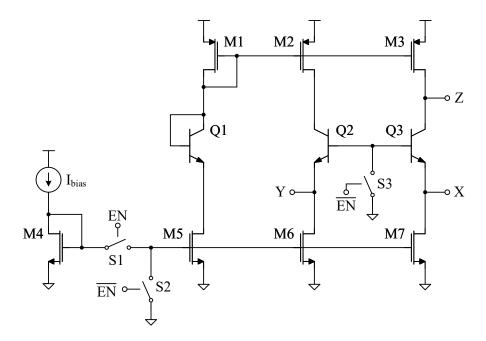

|    |       | 6.1.1 Buffers with Power On/Off Ability        | 73 |

|    |       | 6.1.2 Buffers with Reverse Signal Transmission | 76 |

|    |       | 6.1.3 On-Chip Calibration References           | 77 |

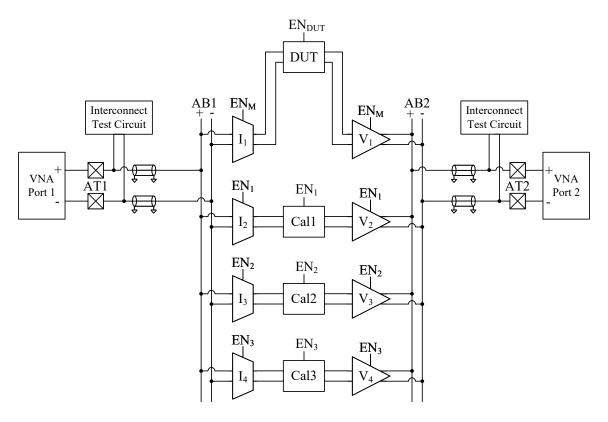

|    | 6.2   | BiCMOS Test Bus High-Level Schematic           | 80 |

|    | 6.3   | Simulation Results                             | 82 |

|    |       | 6.3.1 Discussion                               | 83 |

|    | 6.4   | Summary                                        | 86 |

| 7  | Con   | aclusion                                       | 87 |

|    | 7.1   | Summary                                        | 87 |

|    | 7.2   | Future Work                                    | 89 |

| Re | efere | nces                                           | 92 |

# List of Figures

| 2.1  | High-level diagram of IEEE 1149.1 with the mixed-signal extension IEEE             |    |

|------|------------------------------------------------------------------------------------|----|

|      | 1149.4 [2, 3]                                                                      | 8  |

| 2.2  | Schematic of the IEEE 1149.4 analog test bus structure constructed with            |    |

|      | voltage and current buffers for an internal DUT measurement [3]                    | 10 |

| 2.3  | Block diagram of IEEE 1149.4 calibration using transfer functions $Z_{DUT},A_{I},$ |    |

|      | and $A_V$                                                                          | 12 |

| 2.4  | S-parameter theory derived from traveling waves in transmission lines              | 14 |

| 2.5  | S-parameter theory simplification using zero length transmission lines to define   |    |

|      | S-parameter of a 2-port network                                                    | 14 |

| 2.6  | High-level internal structure of a VNA with the directional couplers used to       |    |

|      | measure the incident and reflected waves                                           | 15 |

| 2.7  | Typical VNA measurement setup showing separate measurements of the DUT             |    |

|      | and three calibration references (Cal1, Cal2, and Cal3)                            | 16 |

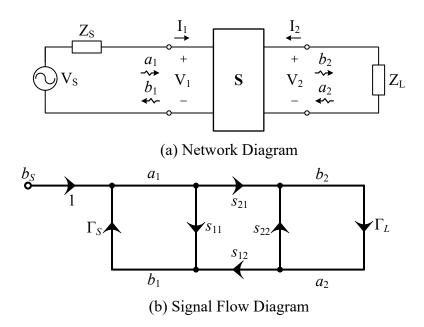

| 2.8  | 2-port network diagram of the 8-term VNA calibration model                         | 17 |

| 2.9  | Signal flow diagram of the 8-term VNA calibration model                            | 17 |

| 2.10 | 2-port network diagram of the three calibration references                         | 19 |

| 2.11 | Signal flow diagram showing of the three calibration references                    | 20 |

| 2.12 | Example through-reflect-line (TRL) and line-reflect-reflect-match (LRRM)           |    |

|      | calibration standards                                                              | 23 |

| 3.1  | Proposed 4-port analog test bus                                                    | 30 |

| 3.2  | Output signal path represented with (a) circuit schematic and (b) general          |    |

|      | 2-port networks                                                                    | 32 |

| 3.3  | 4-port test bus calibration model with 3-port input and output error blocks.       | 33 |

| 3.4  | 2-port network diagrams comparing the 1149.4 and 4-port test buses measur-            |    |

|------|---------------------------------------------------------------------------------------|----|

|      | ing transimpedance and input impedance                                                | 35 |

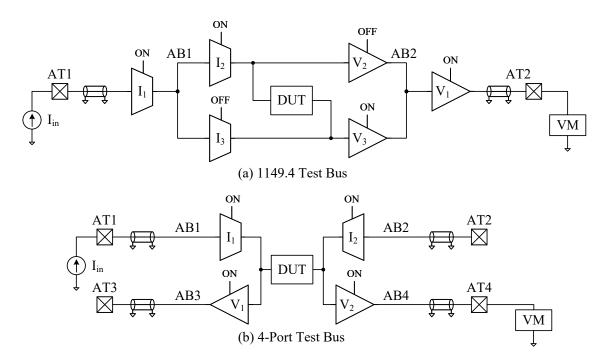

| 3.5  | (a) IEEE 1149.4 and (b) 4-port test bus setup for direct DUT measurement.             | 36 |

| 3.6  | Proposed 2-port analog test bus                                                       | 38 |

| 3.7  | 2-port test bus calibration model with 2-port input and output error blocks.          | 39 |

| 3.8  | 2-port test bus setup for direct DUT measurement                                      | 40 |

| 4.1  | General (a) 2-port network with load and source impedance represented with            |    |

|      | a (b) signal flow diagram.                                                            | 44 |

| 4.2  | Network diagram of the 4-port test bus created with 2-Port and 3-Port networks.       | 45 |

| 4.3  | Signal flow diagram of the complete 4-port test bus                                   | 46 |

| 4.4  | Signal flow diagram of the 4-port test bus simplified to eight error terms by         |    |

|      | setting $a_5 = a_6 = 0$                                                               | 46 |

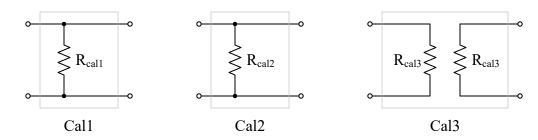

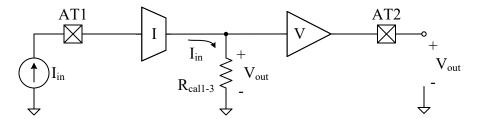

| 4.5  | Calibration references integrated within the proposed test bus                        | 48 |

| 4.6  | $R_{cal1-3}$ low frequency measurement setup equivalent circuit                       | 49 |

| 4.7  | 1149.4 test bus calibration measurement setup of both the (a) current buffers         |    |

|      | and (b) voltage buffers                                                               | 51 |

| 4.8  | General 4-port test bus measurement setup with the center block switching             |    |

|      | between the DUT, Cal1, Cal2, and Cal3                                                 | 54 |

| 4.9  | Signal flow diagram of the 2-port test bus with weak reverse error signals ( $e_{01}$ |    |

|      | and $e_{23}$ )                                                                        | 56 |

| 4.10 | General 2-port test bus measurement setup with the center block switching             |    |

|      | between the DUT, Cal1, Cal2, and Cal3                                                 | 57 |

| 4.11 | Network diagram of the proposed test bus calibration model with error block           |    |

|      | matching emphasized                                                                   | 59 |

| 5.1  | 4-port test bus PCB experiment schematic                                              | 63 |

| 5.2  | IEEE 1149.4 test bus PCB experiment schematic.                                        | 64 |

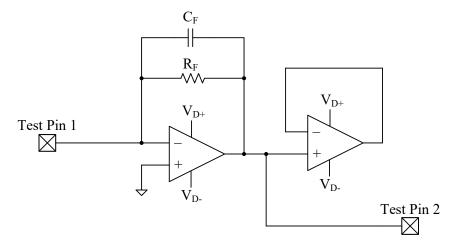

| 5.3  | Schematic of TIA DUT circuit used in the 4-port and 1149.4 test bus PCBs.      | 65 |

|------|--------------------------------------------------------------------------------|----|

| 5.4  | Photograph of the final 1149.4 (left) and 4-port (right) test bus PCBs         | 66 |

| 5.5  | Reference TIA DUT PCB schematic to compare performance of 4-port and           |    |

|      | 1149.4 test buses                                                              | 67 |

| 5.6  | Photograph of the final reference TIA DUT PCB                                  | 67 |

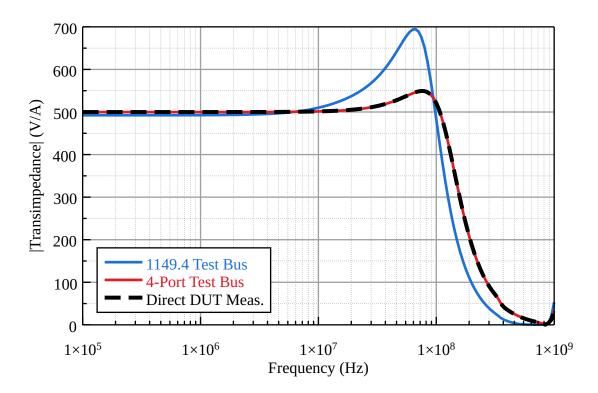

| 5.7  | Simulation results comparing the transimpedance measured from the proposed     |    |

|      | 4-port and 1149.4 test bus to a direct measurement of the DUT                  | 68 |

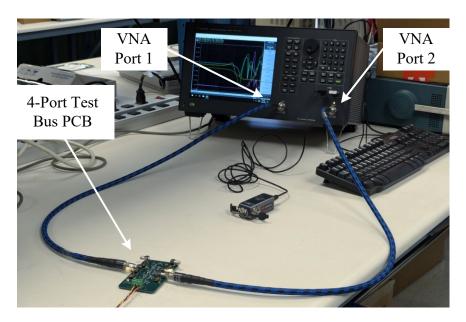

| 5.8  | Photo of VNA test setup measuring the proposed 4-port test bus                 | 69 |

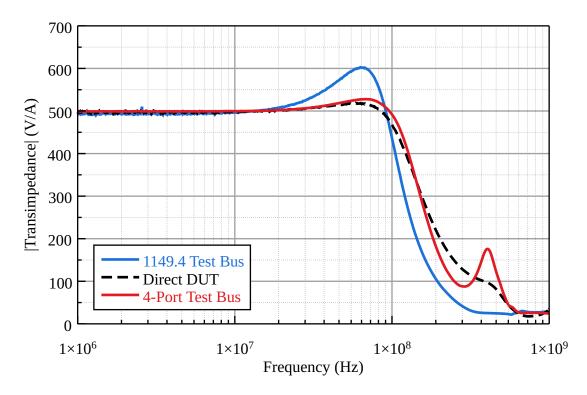

| 5.9  | Experimental results comparing the proposed 4-port and 1149.4 test bus to a    |    |

|      | direct measurement of the DUT                                                  | 70 |

| 6.1  | Current conveyor (CCII) [45] with power off switches S1-3                      | 74 |

| 6.2  | Current and voltage buffer arrangements of the current conveyor                | 74 |

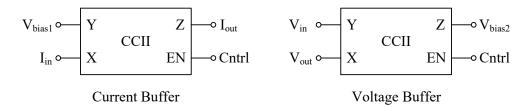

| 6.3  | Comparison of buffers turned off with and without the presence of S3 con-      |    |

| 0.0  | necting internal base to ground. Monte Carlo simulation with the average and   |    |

|      | standard deviation (Std) plotted                                               | 75 |

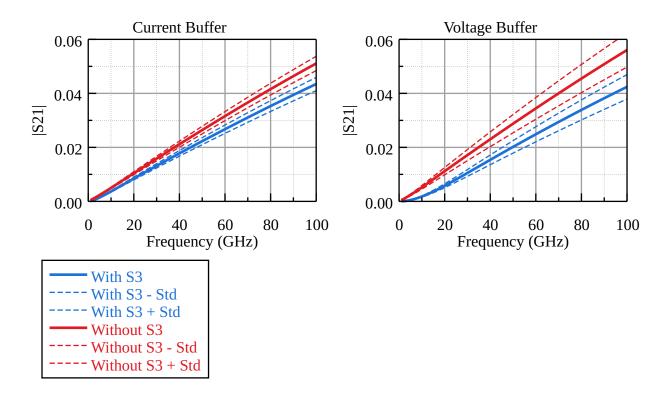

| 6.4  | Comparison of buffers turned off with the four combinations of S3 and power    |    |

|      | switches present or not. Monte Carlo simulation with only the average plotted. | 76 |

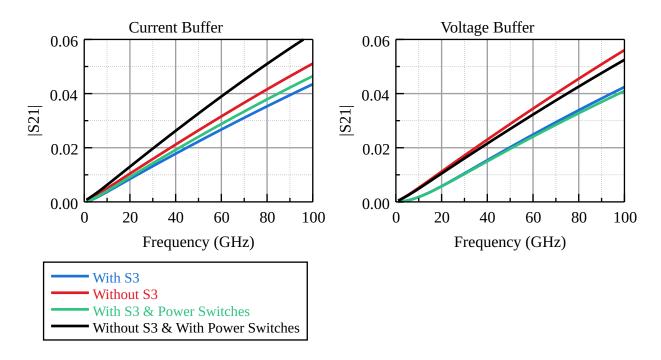

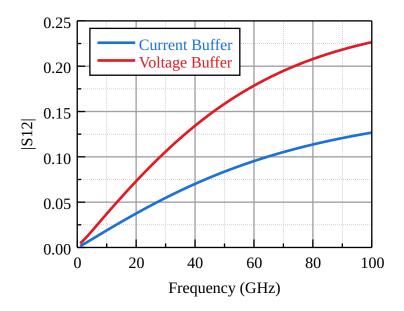

| 6.5  | Reverse signal transmission through switched on current and voltage buffer.    |    |

|      | Monte Carlo simulation with only the average plotted                           | 77 |

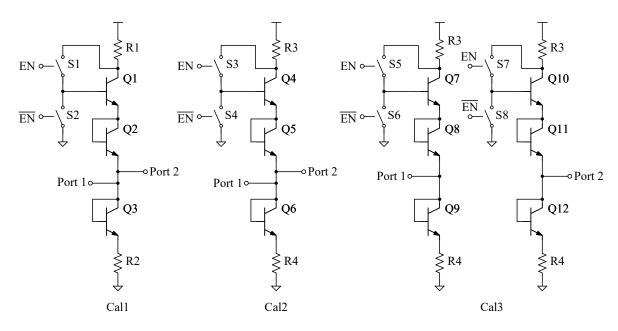

| 6.6  | 2-port and 4-port test bus calibration references                              | 78 |

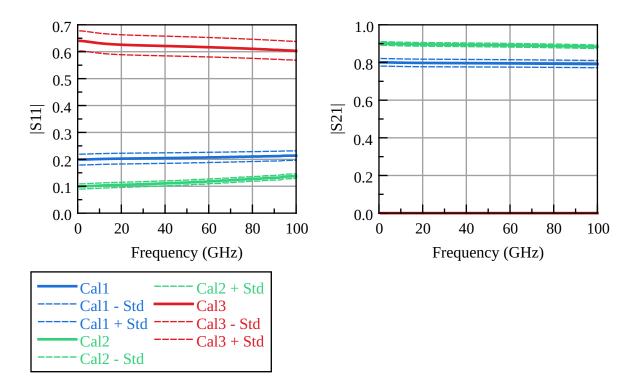

| 6.7  | Calibration reference (Cal1, Cal2, and Cal3) S-parameter performance. Monte    |    |

|      | Carlo simulation with the average and $\pm$ standard deviation (Std) plotted   | 79 |

| 6.8  | Differential 2-Port Proposed Test Bus                                          | 80 |

| 6.9  | Differential 4-Port Proposed Test Bus                                          | 81 |

| 6.10 |                                                                                |    |

|      | amplifier, buffer, and port connections                                        | 82 |

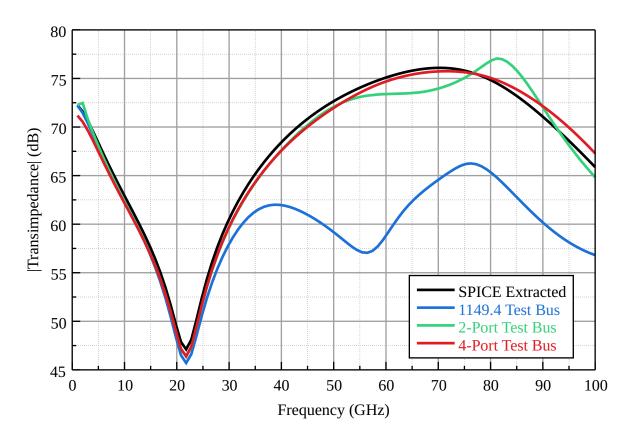

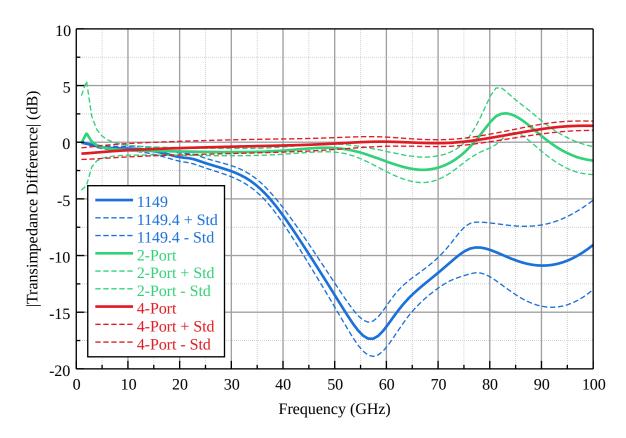

| 6.11 | Monte Carlo simulation showing the average transimpedance measured by the      |    |

|------|--------------------------------------------------------------------------------|----|

|      | 1149.4, 2-Port, and 4-Port test buses. Exact SPICE extracted transimpedance    |    |

|      | is included as a reference                                                     | 84 |

| 6.12 | Monte Carlo simulation results of the difference between the test bus measured |    |

|      | and ideal SPICE extracted transimpedance. Each result is plotted with the      |    |

|      | average value and $\pm$ the standard deviation (Std)                           | 85 |

# List of Tables

| 3.1 | Current and voltage buffer component values used for the example             | 37 |

|-----|------------------------------------------------------------------------------|----|

| 3.2 | Transmission line component values used for the example                      | 37 |

| 3.3 | Directly measured (no calibration) DUT transimpedance results through the    |    |

|     | 4-port and 1149.4 test bus                                                   | 37 |

| 3.4 | Directly measured (no calibration) DUT transimpedance results through the    |    |

|     | 2-port, 4-port, and 1149.4 test bus                                          | 40 |

| 4.1 | Calibration references (Cal1, Cal2, and Cal3) component parameters used in   |    |

|     | the example                                                                  | 53 |

| 4.2 | Calibration extracted DUT transimpedance obtained with the 4-port and        |    |

|     | 1149.4 test bus using either the ideal low-frequency or high-frequency test  |    |

|     | bus components.                                                              | 55 |

| 4.3 | New current buffer component parameters used in the 2-port test bus example. | 57 |

| 4.4 | Calibration extracted DUT transimpedance obtained with the 2-port test bus   |    |

|     | using either the ideal low-frequency, high-frequency, or zero reverse signal |    |

|     | high-frequency test bus components                                           | 58 |

| 6.1 | Calibration reference's component values                                     | 78 |

## List of Abbreviations

ATE . . . . . . . . . . . . . . . . . Automated Test Equipment BiCMOS . . . . . . . . . . . . . Bipolar Complementary Metal-Oxide-Semiconductor BIST . . . . . . . . . . . . . . . . Built-In Self-Test BJT . . . . . . . . . . . . . . . Bipolar Junction Transistor Cal1 . . . . . . . . . . . . . . . . Calibration Reference 1 Cal2 . . . . . . . . . . . . . . . . . . Calibration Reference 2 Cal3 . . . . . . . . . . . . . . . . Calibration Reference 3 CMOS . . . . . . . . . . . . . . . . Complementary Metal-Oxide-Semiconductor DfT . . . . . . . . . . . . Design for Test DIP . . . . . . . . . . . . . . . . Dual In-line Package DUT .... Device Under Test ECal . . . . . . . . . . . . Electronic Calibration LRM . . . . . . . . . . . . Line-Reflect-Match LRRM . . . . . . . . . . . . . Line-Reflect-Reflect-Match M-TRL . . . . . . . . . . . . . . . . Multiline Through-Reflect-Line

| mmWave Millimeter Wave             |

|------------------------------------|

| S-Parameters Scattering Parameters |

| SOLT Short-Open-Load-Through       |

| TIA                                |

| TRL Through-Reflect-Line           |

| VNA Vector Network Analyzer        |

# Chapter 1

## Introduction

### 1.1 Motivation

Testing is a critical step of the integrated circuit manufacturing process. Before a chip can be sent to a customer, it must be thoroughly tested to ensure that it behaves as expected and meets its specifications. An individual die is first tested while it is still part of the wafer and again after it is diced and packaged. Automated Test Equipment (ATE) is used to hold the chip/wafer, interface with the pins/pads, and conduct an extensive sequence of tests.

In the volumes and complexity associated with semiconductor manufacturing, testing can represent a significant proportion of manufacturing cost. The test systems are complicated and require a large engineering effort in their own right to effectively test a chip. ATE testers are an expensive and limited resource where it is best to maximize their throughput. The testing time of an individual chip is an important metric that directly influences its cost. Therefore, it is now standard practice to design the chip with knowledge of how it will be tested and to add circuitry to improve test time, accuracy, and coverage [1].

Digital IC test strategies are a mature field compared to their analog and mixed-signal counterparts. Analog and mixed-signal testing is orders of magnitude more complex and costly due to the difficulty in accessing, accurately measuring, and collecting all the rele-

vant performance parameters. This cost is again multiplied as the analog and mixed-signal systems increase in speed. Circuits that operate in the RF and millimeter wave (mmWave) frequency ranges require expensive and carefully configured equipment to test accurately.

Testing and validation are the key components of manufacturing high-frequency chips. Quite a lot of quality research is being conducted to create better analog circuits that will ultimately improve the speed, cost, and reliability of critical communication systems used in the world today. New technologies do not mean anything if they cannot be tested economically in a production environment.

The standard analog test strategy is to simply use the ATE tester and its connection to the chip's ports to measure the analog components. This limits the number of ports to only the final inputs and outputs of the chip. These ports can give a good view of the overall performance but lack insight into individual components. That is, unless an internal node is given a dedicated test port for the purpose of expanding the test abilities. The availability and number of ports are typically tightly controlled, so many dedicated test ports are not feasible.

Design-for-Test (DfT) and Built-In Self-Test (BIST) strategies include dedicated on-chip test circuitry to facilitate better analog testing. Many different types of DfT and BIST exist to best suit their application and goal. The advantages of these strategies include lowering the test cost, increased fault coverage, diagnostics and characterization, and system-level diagnostics [1]. Some of the general types of DfT include analog test buses with switches, loopback modes, on-chip sampling, and DC to RF performance correlation [1].

DfT and BIST tend to be very application specific, with every class of analog circuit having unique implementations of test circuits. There is also a trade-off between the test circuitry and the silicon area. Ideally, one wants to enable test functionality in the least amount of area possible. DfT and BIST are also less accurate compared to the equivalent measurement made with external equipment. Test equipment uses the fastest and most accurate version of the measurement hardware because it is not limited by space. They also

have traceability to established standards so that measurements are known to be accurate.

Analog test buses are a DfT strategy that is an extension of the popular digital test bus scan chain. Through a standardized test port, test equipment can interface with the IC and different test signals are sent to different parts of the IC through a series of analog switches (transmission gates). Analog test buses are a general structure that can be used in many different applications. IEEE 1149.4 [2] is the established analog test bus standard that defines the test bus interface and topology. The major limitation of analog test buses is the maximum measurement frequency, which has prevented its use in RF and mmWave applications. The poor high-frequency measurement is the result of significant parasitic capacitance on the test bus due to the amount and size of the analog switches.

RF and mmWave circuits are typically characterized using high-quality test equipment such as a Vector Network Analyzer (VNA). A major reason VNAs can accurately measure high-frequency signals is because of their calibration procedure. Systematic errors caused by defects and parasitic elements in the equipment's cables and probes corrupt the signal. By measuring calibration references, which are circuits with known behavior, the VNA can characterize the errors. Then after measurement of the device under test (DUT), the true DUT performance can be de-embedded from the errors, resulting in an accurate measurement.

Combining the high-frequency measurement capabilities of a VNA with an analog test bus would expand its maximum test frequency and make the test bus strategy viable in new applications. Continuing to use the high-quality external VNA would keep the measurements accurate and traceable. The calibration references could be integrated within the test bus on-chip to extract errors caused by the test bus itself. Therefore, allowing the effects of the test bus to be de-embedded from DUT measurements giving accurate results across the bandwidth of the DUT.

#### 1.2 Research Goals

This thesis proposes a high-frequency wide-bandwidth analog test bus structure that uses VNA-style calibration to improve the test and validation of an IC's high-frequency analog components. The components of the test bus are evaluated and optimized to increase their maximum operating frequency. VNA-style calibration references are integrated into the test bus to allow for extraction of the test bus systematic errors. Multiple test bus structures are considered to create strong signal paths.

The VNA calibration procedure is adapted and expanded to be compatible with the test bus. Unique calibration references are created that can be integrated on-chip with the test bus. The calibration algorithm is altered with a 4-port to 2-port conversion and unique calibration references. Common problems that affect VNA calibration are evaluated in the test bus context.

A discrete component PCB experiment of the test bus structure is constructed and measured to compare its performance with the prior art. Multiple simulations are presented to demonstrate ideal performance and challenges in integrating the test bus in an IC.

### 1.3 Structure of Thesis

The remainder of this thesis is organized as follows.

Chapter 2 contains a review of the literature on key topics related to the analog test bus and VNA calibration. The chapter begins by analyzing the established IEEE 1149.4 analog test bus, its published implementations, and its high-frequency measurement limitations. Then background on VNA measurements and scattering parameters (S-parameters) is given to provide context for the next section on VNA calibration. A step-by-step derivation of the calibration procedure used in this thesis is given. Next, an in-depth review of VNA calibration references is presented, including on-chip and electronic calibration references.

Chapter 3 presents the design of the proposed analog test bus topology and its important structural requirements. The proposed analog test bus design is described in detail while providing context for the decisions. A 4-port and 2-port version of the test bus are presented, and the structural differences between them and the IEEE 1149.4 test bus are compared. An example simulation is used to show the performance difference between ideal low-frequency measurements and high-frequency measurements with errors.

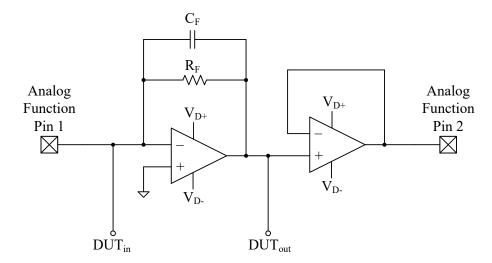

Chapter 4 documents the details of the calibration algorithm that are unique to the proposed test buses. First, how S-parameters are converted to circuit parameters, such as voltage or current gain, is recorded as background information. Then the 4-port to 2-port conversion required to use the 4-port test bus is derived using a signal flow diagram. The proposed calibration references are created using load resistors that can be characterized with a low-frequency measurement. The 2-port test bus needs a specific requirement with respect to the buffers in order to enable calibration. An example simulation is used to highlight the theoretical performance and difference compared to the IEEE 1149.4 test bus.

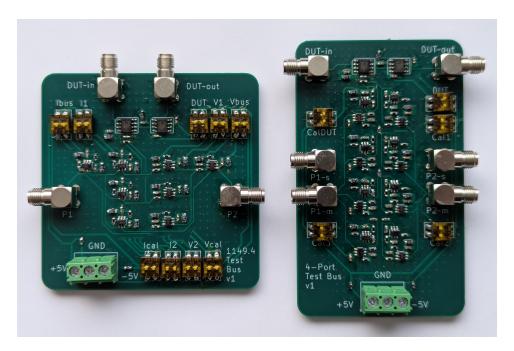

Chapter 5 presents the main experiment of the thesis in which the proposed 4-port test bus is built on a PCB using discrete components. An IEEE 1149.4 test bus PCB is also constructed out of the exact same components to provide a comparison of their structure and calibration ability. The DUT for both test buses is a transimpedance amplifier (TIA) circuit where the goal is to accurately measure the transimpedance at all frequencies.

Chapter 6 investigates the challenges in applying the proposed test bus to a high-frequency IC application. The proposed 4-port and 2-port test buses are implemented in a high-speed BiCMOS process. Special design decisions are required to create buffers with power on/off ability and calibration references that integrate into the test buses. The proposed test buses are simulated and compared against an 1149.4 implementation using a Monte Carlo simulation to induce mismatch variations.

Chapter 7 summarizes the key results of the thesis and ends with recommendations for future work.

# Chapter 2

## Literature Review

There are many works in the literature that report on the performance of existing analog test buses. VNA calibration is an even more extensive field with many different approaches catering to a multitude of applications. This chapter begins by analyzing the currently published work on the IEEE 1149.4 analog test buses. The gain calibration of the 1149.4 test bus is presented, and the high-frequency performance limitations are closely inspected. The general background on VNA measurements and S-parameters is then given before going into detail on the VNA calibration algorithm. An extensive review of VNA calibration references is documented, going into specific detail with on-chip and electronic calibration.

### 2.1 Digital Test Bus

Digital test buses and scan chains have become a common approach to testing digital components. The idea of a digital test bus is to provide a mechanism to apply arbitrary bit sequences to a digital block and read the resulting bits. The test bits are applied through a dedicated test port on the IC and moved around the chip through the use of a scan chain. This common testing infrastructure can test any digital block connected to the scan chain. The digital test bus eliminates the need to probe and connect individually to each input and output of a digital block to test it.

IEEE 1149.1 [2] defines the standard for creating a test access port and a boundary-scan architecture. The standard focuses on creating a boundary scan which places the scan chain at the perimeter of a chip between its pins and internal circuitry. This facilitates the testing of the interconnections between two ICs on the same PCB. The boundary scan can also be used to test the internals of the IC.

Other digital test bus implementations can create a more complete scan of the internal digital components and not just the boundary by routing the scan to smaller internal blocks. This more fine-grained approach gives greater insight into the chip.

### 2.2 Analog Test Bus

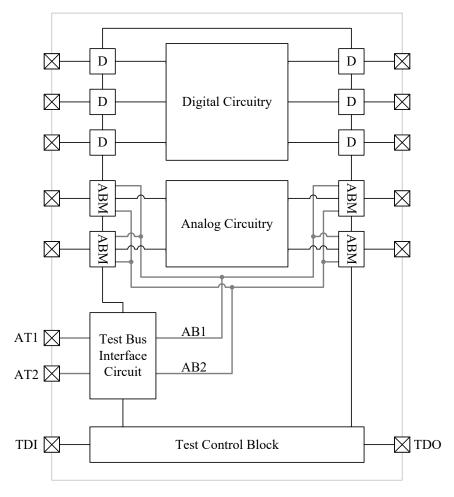

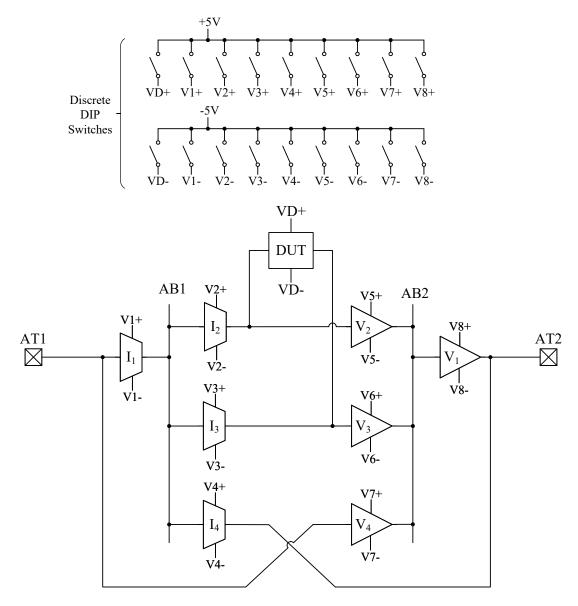

IEEE 1149.4 [3] is the mixed-signal extension to IEEE 1149.1 to add support for analog testing. The purpose of the standard is to provide a structure for analog interconnect, parametric, and internal tests. To accomplish this, 1149.4 uses switches to connect the DUT, test buses, and test ports along with the digital scan chain and interconnect test.

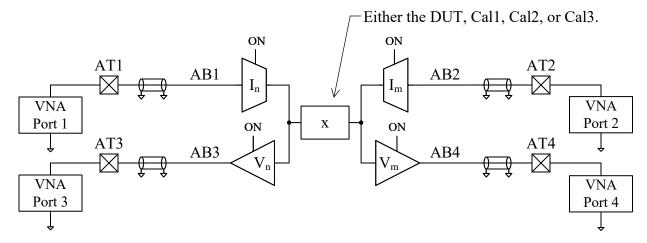

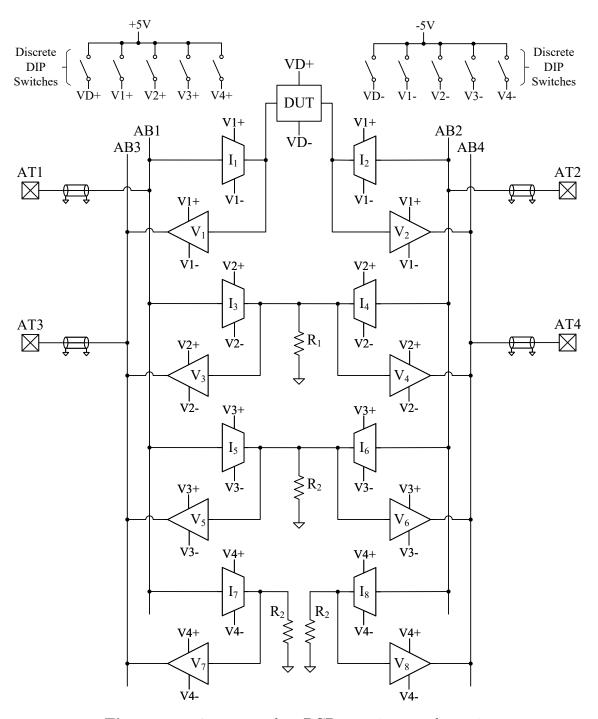

Fig. 2.1 shows the high-level 1149.4 extension, which includes new analog test infrastructure and a normal digital test bus. AT1 and AT2 are the analog test ports that interface the outside test equipment to the chip. The Test Bus Interface Circuit connects the test ports to the internal analog test buses (AB1 and AB2) with switches and supports basic calibration. Connected to the analog test buses are the Analog Boundary Modules (ABM) which connect the test buses to the DUT and contain interconnect test circuitry. The normal 1149.1 blocks include the Test Control Block with the digital test ports (TDI and TDO) and the boundary scan chain that traverses the Test Bus Interface Circuit, ABMs, and digital scan blocks.

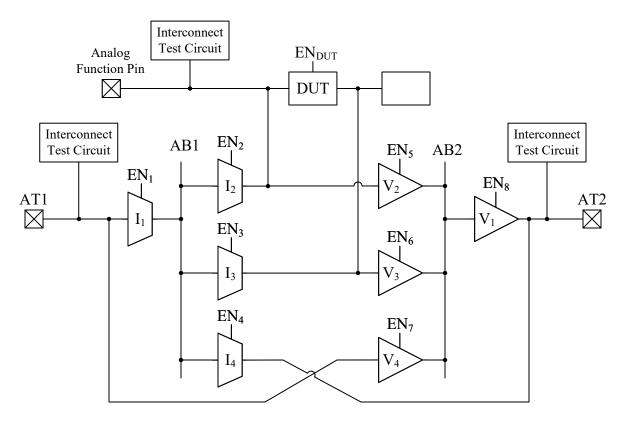

The focus of this thesis is on the internal DUT test performance of the test bus. Fig. 2.2 shows a simplified 1149.4 schematic of only the analog signal paths and components used to test an internal DUT. The two primary components of the test bus are the current and voltage buffers that act as switches to connect the ports and buses to the DUT. Important

**Figure 2.1:** High-level diagram of IEEE 1149.1 with the mixed-signal extension IEEE 1149.4 [2, 3].

to note is the fact that 1149.4 does not specify how the switches are implemented. In most cases using a CMOS process, transmission gates would be used. Alternatively, in a bipolar process, 1149.4 suggests using buffers because of the lack of transmission gates. In some cases, the switches are conceptual and can be implemented in more creative ways, such as cutting off power to circuit blocks.

### 2.2.1 High-Frequency Performance

A major limitation of 1149.4 is its maximum operating frequency. Technically, the standard does not specify a maximum operating frequency, but the reported bandwidths have

been limited. Hannu et al. [4] identified the lack of support for RF testing as one of the reasons why adoption of 1149.4 is slow. The 1149.4 test bus can simply only measure DC or low-frequency signals.

This low bandwidth is the result of large series resistance and shunt capacitance of the switches and bus [5, 6]. Test bus switches implemented using CMOS transmission gates can have significant series resistance depending on the size of transistors used. Parker [7] provides some basic specifications for the test bus, saying that the total series resistance from the test port to the DUT should be less than  $10 \text{ k}\Omega$ . Sunter et al. [6] gives an example resistance of  $1 \text{ k}\Omega$  and a total capacitance on and off the chip of 100 pF. This example says a voltage source could be monitored with a bandwidth of 1.6 MHz. The alternative 1149.4 implementation uses buffers instead of switches, which reduces the series resistance and generally allows for higher operating frequency. Sunter et al. [6] presents a 1149.4 design using buffers that improved the measurement frequency to 30 MHz.

Evidently from the above examples, using the 1149.4 test bus to conduct high-frequency signals in RF applications is not feasible. A different approach combining RF circuits and 1149.4 commonly found in the literature involves using 1149.4 to relay information at DC or low frequencies. Shrivastava and Banerjee [8] present an analog probe that interfaces with 1149.4 with the sole purpose of reading the DC voltages of the internal analog components. They position this work saying that improvements have been made in predicting RF performance with only DC voltages. Similarly, Zivkovic et al. [9] present an analog test bus design that measures DC voltages inside a CMOS transceiver. The design provides information on power and ground voltage, band-gap references and other biasing, and the DC component of signals.

Alternatively, the test bus can be used to send information about RF signals. Syri et al. [10] use RF power detectors to convert the RF signal strength to a DC voltage that is then read through an analog test bus. They also briefly present a frequency detector that produces a DC voltage proportional to the signal frequency. Hakkinen et al. [11] converts

Figure 2.2: Schematic of the IEEE 1149.4 analog test bus structure constructed with voltage and current buffers for an internal DUT measurement [3].

the RF signal to a sufficiently low frequency using frequency mixing and sub-sampling to send it out on the test bus.

These existing RF analog test bus approaches are incomplete and are only necessitated by the fact that a typical analog test bus cannot support high frequencies. Measurement of many DC voltages inside an analog component has the advantage of proving some information about the circuit's functionality. These low impact test points can also be placed in many locations. DC voltages do not prove the RF performance. It is an indirect measurement that can only predict performance. Adding additional circuitry to detect the RF power or convert the signal to low-frequency adds complexity and cost. Ideally, an analog test bus would be capable of performing accurate direct measurements through a simple and standardized structure.

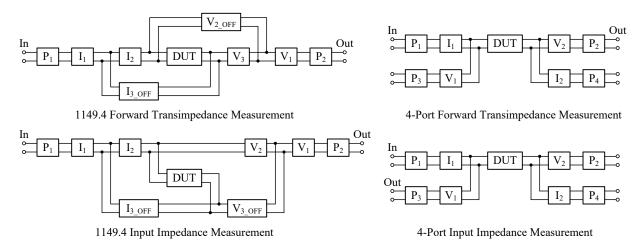

#### 2.2.2 Gain Calibration

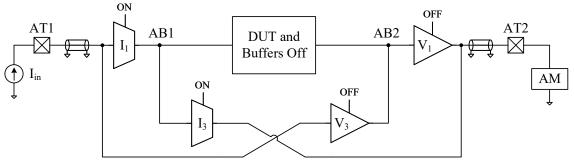

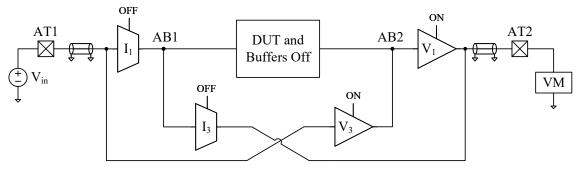

1149.4 provides a simple way to calibrate for non-ideal gain from the ports, bus, and switches/buffers. This is done by providing two additional calibration paths off the test bus to directly measure the calibration path gain. Referencing Fig. 2.2 again,  $I_4$  and  $V_4$  are the buffers that perform calibration by connecting directly to the opposite test port. To characterize the current buffers, only  $I_1$  and  $I_4$  are enabled, and the current gain is measured across the test ports. Similarly, to characterize the voltage buffers, only  $V_1$  and  $V_4$  are enabled, and the voltage gain is measured across the test ports. Using the measured buffer gains, their effects can be de-embedded from the DUT measurement.

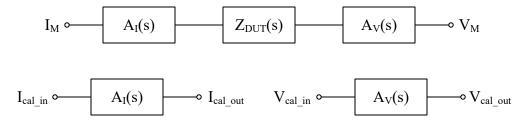

A block diagram representation of 1149.4 measuring a transimpedance DUT is shown in Fig. 2.3 and consists of three different transfer function blocks. The current and voltage buffer gain,  $A_I(s)$  and  $A_V(s)$ , are measured by the dedicated calibration paths

$$A_I(s) = \frac{I_{cal\_out}(s)}{I_{cal\_in}(s)} \qquad A_V(s) = \frac{V_{cal\_out}(s)}{V_{cal\_in}(s)}$$

(2.1)

where  $I_{cal\_in}(s)$  is the input current,  $I_{cal\_out}(s)$  is the output current,  $V_{cal\_in}(s)$  is the input voltage, and  $V_{cal\_out}(s)$  is the output voltage. Similarly, the test bus measured transimpedance,  $Z_M(s)$ , is measured by the test bus path

$$Z_M(s) = \frac{V_M(s)}{I_M(s)} \tag{2.2}$$

where  $V_M(s)$  is the output voltage,  $I_M(s)$  is the input current. The transfer function system can be written as

$$Z_M(s) = A_I(s) \cdot Z_{DUT}(s) \cdot A_V(s)$$

(2.3)

and rearranged to solve for the de-embedded DUT transimpedance

$$Z_{DUT}(s) = \frac{Z_M(s)}{A_I(s) \cdot A_V(s)}.$$

(2.4)

**Figure 2.3:** Block diagram of IEEE 1149.4 calibration using transfer functions  $Z_{DUT}$ ,  $A_I$ , and  $A_V$ .

The 1149.4 calibration approach assumes that the buffers measured as part of the calibration perform exactly the same as the buffers in the DUT measurement. The buffers are physically different and therefore rely on their behavior matching. Su and Chen [12] inspect the 1149.4 calibration procedure and its ability to remove the parasitic effects of the test bus. The authors find that using buffers instead of transmission gates improves the calibration performance because it lessons the loading differences between the DUT and the calibration measurements. One must ensure that the loading on the calibration path measurements is similar to the loading the switches/buffers will experience connected to the DUT.

1149.4 calibration is still limited to only account for the buffer gain. The load matching that was discussed aims to increase the time the buffer gain is the dominant factor. Loading can still impact the calibration performance, and this is especially true if the interfaces between the DUT and buffer have similar impedances. 1149.4 also fails to account for other high-frequency effects from the port and bus.

### 2.3 High-Frequency Measurements Using S-Parameters

The established way to measure high-frequency analog components is by using high-quality external test equipment, such as a Vector Network Analyzer (VNA) [13, 14]. Vector refers to the fact that both magnitude and phase of a signal is measured and network analyzer refers to the fact that it measures network parameters. The type of network parameters measured by a VNA are the scattering parameters (S-parameters) because the technology

was developed around directional couplers that can directly extract the S-parameters.

#### 2.3.1 S-Parameter Background

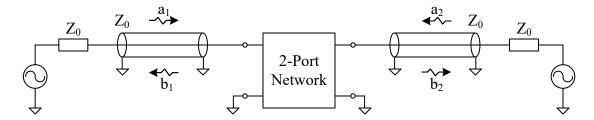

The fundamentals of S-parameters are summarized in this section to provide background for the next sections on calibration and test bus calibration. S-parameters are derived from transmission line theory and the concept of traveling waves. The theory in this section is adapted from Gonzalez [15].

The voltage at a position along a lossless transmission can be written as

$$V(x) = Ae^{-j\frac{2\pi}{\lambda}x} + Be^{j\frac{2\pi}{\lambda}x}$$

(2.5)

where A and B are complex constants, x is the distance from one edge, and  $\lambda$  is the wavelength. Inspecting (2.5) shows that the voltage is the sum of two different wave components. An important value of a transmission line is the characteristic impedance, which for a lossless transmission line is defined as

$$Z_0 = \sqrt{\frac{L}{C}} \tag{2.6}$$

where L and C are the inductance and capacitance per unit length, respectively. The notation for the two waves in a transmission line is then written as

$$a(x) = \frac{Ae^{-j\beta x}}{\sqrt{Z_0}} \tag{2.7}$$

and

$$b(x) = \frac{Be^{j\beta x}}{\sqrt{Z_0}}. (2.8)$$

Fig. 2.4 shows a 2-port network system with transmission lines and their traveling waves driven by a source and load signal. The S-parameters of the center 2-port network are defined by the traveling waves as the edges of the transmission line closest to the network block.

Figure 2.4: S-parameter theory derived from traveling waves in transmission lines.

**Figure 2.5:** S-parameter theory simplification using zero length transmission lines to define S-parameter of a 2-port network.

Transmission lines are not necessary to use S-parameters to describe circuit blocks. The S-parameters stop representing physical values of waves through transmission lines but work well as general network parameters. They can be derived by assuming transmission lines of zero length with characteristic impedance  $Z_0$ . Repeating (2.5), (2.7), and (2.8) with x = 0 gives

$$V = A + B \tag{2.9}$$

$$a = \frac{A}{\sqrt{Z_0}} \tag{2.10}$$

$$b = \frac{B}{\sqrt{Z_0}}. (2.11)$$

Fig. 2.5 shows a 2-port network system with no transmission lines and the wave notation at the nodes around the network block. The S-parameters are defined by ratios of reflected and transmitted waves when applying a signal to only one port such as

$$s_{11} = \frac{b_1}{a_1}\Big|_{a_2=0}$$

$s_{21} = \frac{b_2}{a_1}\Big|_{a_2=0}$   $s_{12} = \frac{b_1}{a_2}\Big|_{a_1=0}$   $s_{22} = \frac{b_2}{a_2}\Big|_{a_1=0}$ . (2.12)

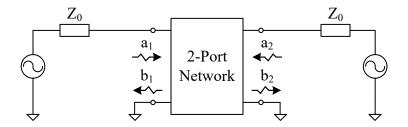

**Figure 2.6:** High-level internal structure of a VNA with the directional couplers used to measure the incident and reflected waves.

The S-parameters written in matrix form is then

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2.13)

and the S-parameter matrix is usually written as a single variable

$$\mathbf{S} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} . \tag{2.14}$$

### 2.3.2 Directional Coupler and Schematic

A VNA measures the S-parameter traveling waves using two directional coupler components. Fig. 2.6 shows a high-level internal VNA schematic with directional couplers and signal sources. S-parameter are measured in two stages. First,  $v_{p1}$  is turned on and  $v_{p2}$  is set to zero. This means that  $a_2$  is zero and  $s_{11}$  and  $s_{21}$  are extracted by the directional couplers. Next, during the second stage,  $v_{p2}$  is turned on and  $v_{p1}$  is set to zero, resulting in  $s_{22}$  and  $s_{12}$ .

### 2.4 Vector Network Analyzer Calibration

A VNA can accurately measure high-frequency signals due to its calibration procedure, which accounts for systematic errors in the probe cable, probe contact, and measurement

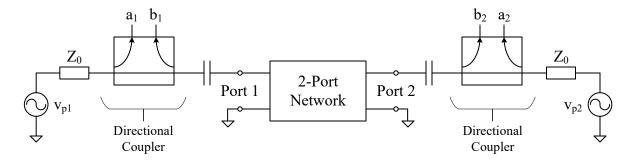

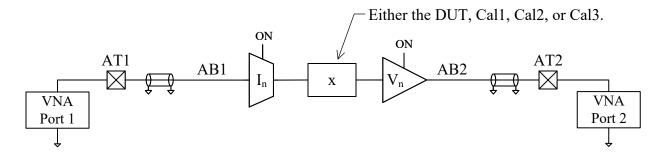

**Figure 2.7:** Typical VNA measurement setup showing separate measurements of the DUT and three calibration references (Cal1, Cal2, and Cal3).

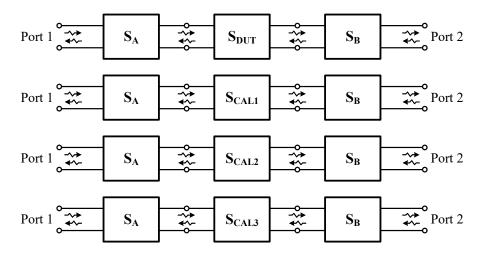

setup. Knowing these systematic errors, the true DUT can be de-embedded from the DUT measurement. Fig. 2.7 shows the typical VNA setup with the calibration measurements. A transmission line and port symbol are used to represent the parasitic circuit elements that exist between the VNA port, DUT, and calibration references.

The established VNA calibration procedure is presented in this section because it forms the basis for the new proposed analog test bus. The relevant error model is first chosen and the manipulation of the S-parameter matrices to extract the DUT is documented. Details on the importance of calibration references is also provided.

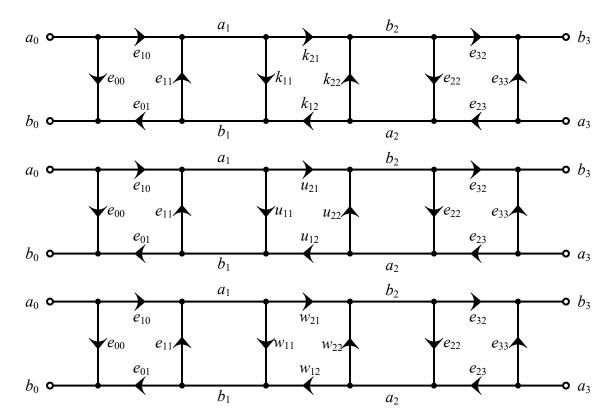

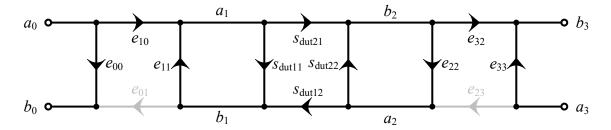

#### 2.4.1 Procedure Details

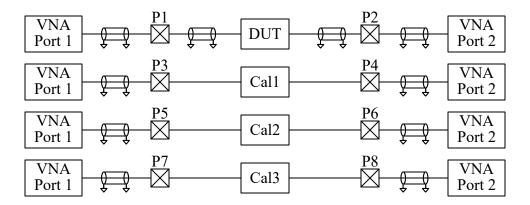

The first step in performing the VNA calibration is to choose an appropriate model for the system, including the errors. The most common error model, and the model chosen for the proposed test bus, is the 8-term error model shown in Fig. 2.8. The system is described by a cascade of three 2-port networks where the middle 2-port network is the DUT. Surrounding the DUT are the error parameter 2-port networks.

Alternate error models include the 12-term and 16-term models [13, 16]. The additional error terms are mainly used to describe signal paths that bypass across the DUT and to obtain a more accurate model. Additional error terms increase the complexity and cost of

Figure 2.8: 2-port network diagram of the 8-term VNA calibration model.

Figure 2.9: Signal flow diagram of the 8-term VNA calibration model.

the calibration due to the need for more measurements and quality references. The 8-term error model was chosen for simplicity and the assumption that signal paths across the DUT are insignificant and eclipsed by the other error parameters.

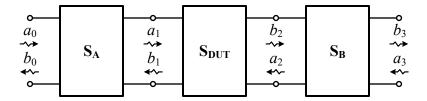

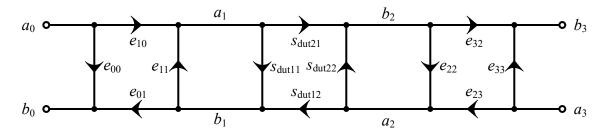

S-parameters are the 2-port network parameter of choice for VNA calibration because they are directly measured. Therefore, a convenient way to represent the calibration problem is through a signal flow diagram using S-parameters. The calibration model signal flow diagram is shown in Fig. 2.9. The S-parameter matrices in Fig. 2.8 expanded to the individual parameters in Fig. 2.9 are given the notation

$$\mathbf{S_A} = \begin{bmatrix} e_{00} & e_{01} \\ e_{10} & e_{11} \end{bmatrix} \qquad \mathbf{S_{DUT}} = \begin{bmatrix} s_{dut11} & s_{dut12} \\ s_{dut21} & s_{dut22} \end{bmatrix} \qquad \mathbf{S_A} = \begin{bmatrix} e_{22} & e_{23} \\ e_{32} & e_{33} \end{bmatrix}. \tag{2.15}$$

The three series 2-port networks make up a larger 2-port network with the input at port 0 ( $a_0$  and  $b_0$ ) and the output at port 3 ( $a_3$  and  $b_3$ ). This S-parameter matrix, which is measured, is denoted as

$$\mathbf{S_{M\_dut}} = \begin{bmatrix} s_{m11} & s_{m12} \\ s_{m21} & s_{m22} \end{bmatrix}. \tag{2.16}$$

The following calibration methodology was first described by Ferrero et al. [17] and the

more recent notation presented by Wollensack et al. [18] is used for its improved readability. This formulation is the fundamental calibration algorithm that is used and built off of in this thesis. It provides a relatively easy-to-understand view of the steps, and the final equations are exactly how they are implemented in the calibration program.

Ferrero et al. [17] showed that the signal flow diagram in Fig. 2.9 can be written as

$$S_{M.dut} = E_{00} + E_{01} (I - S_{DUT} E_{11})^{-1} S_{DUT} E_{10}$$

(2.17)

where

$$\mathbf{E_{00}} = \begin{bmatrix} e_{00} & 0 \\ 0 & e_{33} \end{bmatrix} \quad \mathbf{E_{10}} = \begin{bmatrix} e_{10} & 0 \\ 0 & e_{23} \end{bmatrix} \quad \mathbf{E_{01}} = \begin{bmatrix} e_{01} & 0 \\ 0 & e_{32} \end{bmatrix} \quad \mathbf{E_{11}} = \begin{bmatrix} e_{11} & 0 \\ 0 & e_{22} \end{bmatrix}. \tag{2.18}$$

This formulation of the signal flow diagram is convenient as it allows the equations to be easily rearranged to isolate the error parameters into a linear system of equations

$$\mathbf{S_{M.dut}E_{10}^{-1} - E_{00}E_{10}^{-1} - S_{M.dut}E_{10}^{-1}E_{11}S_{DUT} + \left(E_{00}E_{10}^{-1}E_{11} - E_{01}\right)S_{DUT} = 0.}$$

(2.19)

Fully multiplying (2.19) through and writing in matrix form results in the system

$$\begin{bmatrix} s_{m11} & 0 & 1 & 0 & s_{dut11}s_{m11} & s_{dut21}s_{m12} & s_{dut11} & 0 \\ s_{m21} & 0 & 0 & 0 & s_{dut11}s_{m21} & s_{dut21}s_{m22} & 0 & s_{dut21} \\ 0 & s_{m12} & 0 & 0 & s_{dut12}s_{m11} & s_{dut22}s_{m12} & s_{dut12} & 0 \\ 0 & s_{m22} & 0 & 1 & s_{dut12}s_{m21} & s_{dut22}s_{m22} & 0 & s_{dut22} \end{bmatrix} \begin{bmatrix} 1/e_{10} \\ 1/e_{23} \\ -e_{00}/e_{e10} \\ -e_{33}/e_{23} \\ -e_{11}/e_{10} \\ -e_{22}/e_{23} \\ (e_{01}e_{10} - e_{00}e_{11})/e_{10} \\ (e_{23}e_{32} - e_{22}e_{33})/e_{23} \end{bmatrix} = 0.$$

$$(2.20)$$

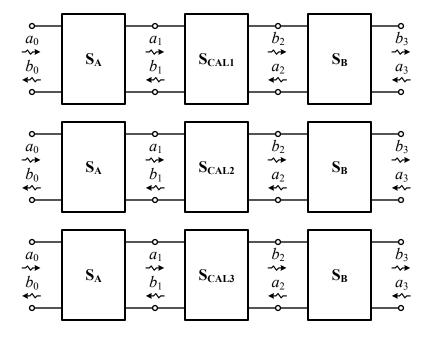

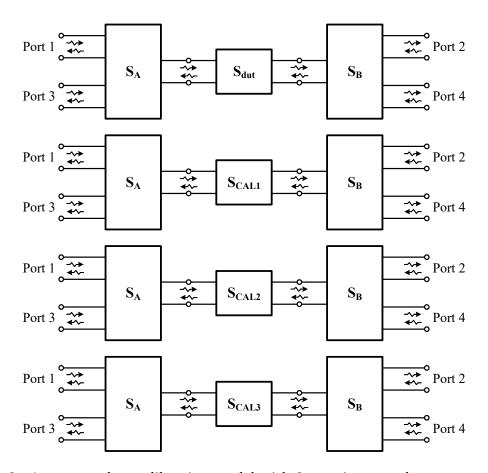

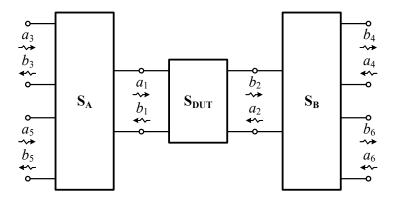

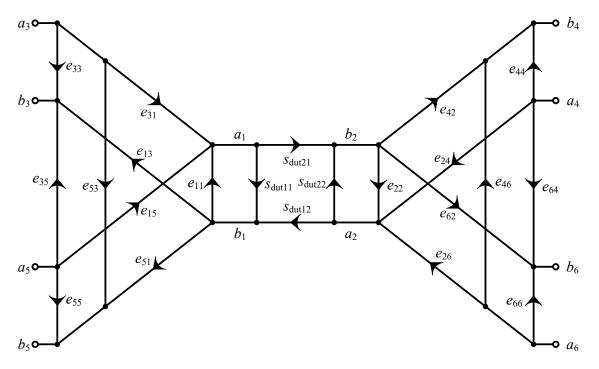

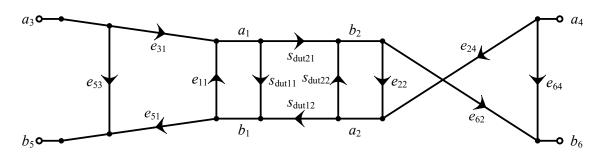

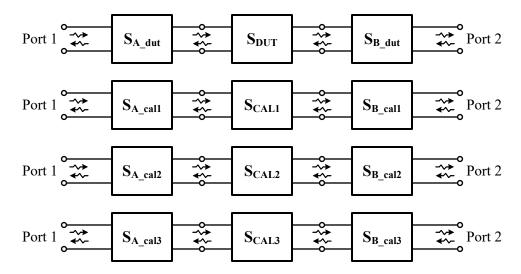

With knowledge of how to set up the system of equations, measurements of calibration references are used to fill in the left-hand matrix with known values. For the 8-term error model, three calibration references are needed to solve the system. The 2-port network

**Figure 2.10:** 2-port network diagram of the three calibration references.

diagram of the calibration reference system is shown in Fig. 2.10 and the equivalent signal flow diagram is shown in Fig. 2.11. The S-parameter matrices and individual parameters are given the notation

$$\mathbf{S_{CAL1}} = \mathbf{K} = \begin{bmatrix} k_{11} & k_{12} \\ k_{21} & k_{22} \end{bmatrix} \qquad \mathbf{S_{CAL2}} = \mathbf{U} = \begin{bmatrix} u_{11} & u_{12} \\ u_{21} & u_{22} \end{bmatrix}$$

$$\mathbf{S_{CAL3}} = \mathbf{W} = \begin{bmatrix} w_{11} & w_{12} \\ w_{21} & w_{22} \end{bmatrix}.$$

(2.21)

The overall S-parameters of the three networks measured from port 0 ( $a_0$  and  $b_0$ ) to port 3 ( $a_3$  and  $b_3$ ) are given the notation

$$\mathbf{S_{M.cal1}} = \mathbf{K_{M}} = \begin{bmatrix} k_{m11} & k_{m12} \\ k_{m21} & k_{m22} \end{bmatrix} \qquad \mathbf{S_{M.cal2}} = \mathbf{U_{M}} = \begin{bmatrix} u_{m11} & u_{m12} \\ u_{m21} & u_{m22} \end{bmatrix}$$

$$\mathbf{S_{M.cal3}} = \mathbf{W_{M}} = \begin{bmatrix} w_{m11} & w_{m12} \\ w_{m21} & w_{m22} \end{bmatrix}.$$

(2.22)

Figure 2.11: Signal flow diagram showing of the three calibration references.

Analyzing and rearranging the signal flow diagram results in

$$K_{M}E_{10}^{-1} - E_{00}E_{10}^{-1} - K_{M}E_{10}^{-1}E_{11}K + (E_{00}E_{10}^{-1}E_{11} - E_{01})K = 0$$

(2.23)

$$\mathbf{U_{M}E_{10}^{-1} - E_{00}E_{10}^{-1} - U_{M}E_{10}^{-1}E_{11}U + (E_{00}E_{10}^{-1}E_{11} - E_{01})U = 0}$$

(2.24)

$$\mathbf{W_M} \mathbf{E_{10}^{-1}} - \mathbf{E_{00}} \mathbf{E_{10}^{-1}} - \mathbf{W_M} \mathbf{E_{10}^{-1}} \mathbf{E_{11}} \mathbf{W} + \left( \mathbf{E_{00}} \mathbf{E_{10}^{-1}} \mathbf{E_{11}} - \mathbf{E_{01}} \right) \mathbf{W} = 0$$

(2.25)

which can be expanded and written in the matrix form

$$\begin{bmatrix} k_{m11} & 0 & 1 & 0 & k_{11}k_{m11} & k_{21}k_{m12} & k_{11} & 0 \\ k_{m21} & 0 & 0 & 0 & k_{11}k_{m21} & k_{21}k_{m22} & 0 & k_{21} \\ 0 & k_{m12} & 0 & 0 & k_{12}k_{m11} & k_{22}k_{m12} & k_{12} & 0 \\ 0 & k_{m22} & 0 & 1 & k_{12}k_{m21} & k_{22}k_{m22} & 0 & k_{22} \\ \hline u_{m11} & 0 & 1 & 0 & u_{11}u_{m11} & u_{21}c_{m12} & u_{11} & 0 \\ u_{m21} & 0 & 0 & 0 & u_{11}u_{m21} & u_{21}c_{m22} & 0 & u_{21} \\ 0 & u_{m12} & 0 & 0 & u_{12}u_{m11} & u_{22}u_{m12} & u_{12} & 0 \\ 0 & u_{m22} & 0 & 1 & u_{12}u_{m21} & w_{22}w_{m22} & 0 & u_{22} \\ \hline w_{m11} & 0 & 1 & 0 & w_{11}u_{m11} & w_{21}w_{m12} & w_{11} & 0 \\ w_{m21} & 0 & 0 & 0 & w_{11}u_{m21} & w_{21}w_{m22} & 0 & w_{21} \\ 0 & w_{m12} & 0 & 0 & w_{12}u_{m11} & w_{22}w_{m12} & w_{12} & 0 \\ 0 & w_{m22} & 0 & 1 & w_{12}u_{m11} & w_{22}w_{m12} & w_{12} & 0 \\ 0 & w_{m22} & 0 & 1 & w_{12}u_{m21} & w_{22}w_{m22} & 0 & w_{22} \end{bmatrix} = 0. \quad (2.26)$$

Note that (2.26) is a homogeneous system of equations, and to solve, one of the dependent variables must be defined in order to rearrange the equation. Typically, setting  $e_{10} = 1$  to rearrange the equation for solving

$$\begin{vmatrix} k_{m11} & 0 & 1 & 0 & k_{11}k_{m11} & k_{21}k_{m12} & k_{11} & 0 \\ k_{m21} & 0 & 0 & 0 & k_{11}k_{m21} & k_{21}k_{m22} & 0 & k_{21} \\ 0 & k_{m12} & 0 & 0 & k_{12}k_{m11} & k_{22}k_{m12} & k_{12} & 0 \\ 0 & k_{m22} & 0 & 1 & k_{12}k_{m21} & k_{22}k_{m22} & 0 & k_{22} \\ u_{m11} & 0 & 1 & 0 & u_{11}u_{m11} & u_{21}c_{m12} & u_{11} & 0 \\ u_{m21} & 0 & 0 & 0 & u_{11}u_{m21} & u_{21}c_{m22} & 0 & u_{21} \\ 0 & u_{m22} & 0 & 1 & u_{12}u_{m11} & u_{22}u_{m12} & u_{12} & 0 \\ 0 & u_{m22} & 0 & 1 & u_{12}u_{m21} & w_{22}w_{m22} & 0 & u_{22} \\ w_{m11} & 0 & 1 & 0 & w_{11}u_{m11} & w_{21}w_{m12} & w_{11} & 0 \\ w_{m21} & 0 & 0 & 0 & w_{11}u_{m21} & w_{21}w_{m22} & 0 & w_{21} \\ 0 & w_{m12} & 0 & 0 & w_{12}u_{m11} & w_{22}w_{m12} & w_{12} & 0 \\ 0 & w_{m22} & 0 & 1 & w_{12}u_{m21} & w_{22}w_{m22} & 0 & w_{22} \\ \end{vmatrix} \begin{bmatrix} 1/e_{23} \\ -e_{00}/e_{e10} \\ -e_{33}/e_{23} \\ -e_{11}/e_{10} \\ -e_{22}/e_{23} \\ (e_{01}e_{10} - e_{00}e_{11})/e_{10} \\ (e_{23}e_{32} - e_{22}e_{33})/e_{23} \end{bmatrix} = \begin{bmatrix} -k_{m11} \\ -k_{m21} \\ 0 \\ 0 \end{bmatrix}$$

Equation (2.27) is a general system of equations that can be easily solved to obtain the matrix of error parameters. Now knowing the error parameters and the test bus measured

DUT S-parameters, (2.17) can be rearranged to solve for the DUT S-parameters

$$S_{DUT} = \frac{S_{M_{-}dut}E_{10}^{-1} - E_{00}E_{10}^{-1}}{S_{M_{-}dut}E_{10}^{-1}E_{11} - (E_{00}E_{10}^{-1}E_{11} - E_{01})}.$$

(2.28)

#### 2.4.2 Calibration References

Many different kinds and arrangements of calibration references are used for VNA calibration. This is because there are many different applications for VNAs and each type of calibration references as its own trade-offs.

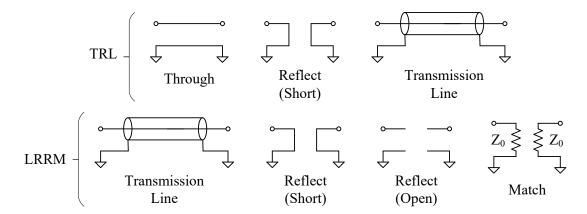

Calibration references have traditionally been integrated on standalone calibration substrates. Usually referred to as an impedance standard substrate (ISS). In this context, the VNA probes are physically moved between the references and measured one at a time. Then the VNA can measure the DUT and de-embed its S-parameters. The types of references used can include short, open, load, transmission line, and through. For example, two common standards are through-reflect-line (TRL) and line-reflect-reflect-match (LRRM). Fig. 2.12 shows a schematic representation of these two standards.

Generally, calibration references are built out of physical structures that, when ideal, have known S-parameters. These S-parameter are known because they are based on the definition of S-parameters with incident and reflected waves. In a reflect-type reference (short or open) all of the incident wave is reflected and the reflection coefficient is 1. In a through-type reference, there are no reflections and unity transmission. A match-type reference using the characteristic impedance of the system gives zero reflections and zero transmission. Therefore, the quality is a function of their physical construction and the S-parameter are inherently known and do not need to be measured.

Equation (2.27) is the critical system of equations that must be solved for calibration. Inspecting the system reveals seven variables and twelve equations, which means that the system is over-defined for the number of variables. This leaves space to strategically ignore equations or add variables to the system. What variables and equations are ignored or

**Figure 2.12:** Example through-reflect-line (TRL) and line-reflect-reflect-match (LRRM) calibration standards.

added is what really differentiates the many different types of standards available for VNA calibration. Some aspects of the calibration references may not be as accurate as others, so those can be ignored. Using a reflection-type standard with zero transmission automatically removes two equations because any through measurements will be zero.

Adding variables fundamentally changes the system of equations. One is essentially adding a variable to the coefficient matrix and the whole system needs to be rearranged to be solved. The algorithm presented in Section 2.4.1 is the most generic formulation with all the reference S-parameters known. Each calibration standard presented in the literature has a completely different solving algorithm geared to their set of variables. Sometimes using different notation and conventions.

TRL was first presented by Engen and Hoer [19] and does not require that all standards be fully known. The reflect reference and propagation constant of the line reference can be unknown and still allow error terms to be calculated [20]. An extension of TRL, multiline TRL (M-TRL), adds multiple line references to cover a greater bandwidth and increase accuracy [21]. LRRM allows the reflect type standards to be unknown [22].

An important concept in error calibration is the calibration/reference plane. Essentially what parts of the physical circuit are included in either the error blocks or DUT. Looking back at Fig. 2.8, the calibration plane is the boundary between the error blocks ( $S_A$  and

$\mathbf{S_B}$ ) and the DUT block. In a traditional VNA calibration with the dedicated calibration substrate, the calibration plane is located at the probe tips. This calibration approach does not account for any errors that may be located between the probe tips and the DUT. Differences in the pad parasitic elements and the on-chip interconnect to the DUT are errors not captured in the calibration.

#### On-Chip Calibration References

Moving the calibration references to the same chip as the target DUT helps move the calibration plane closer to the DUT. On-chip or on-wafer calibration are terms used describing references built in the same process as the DUT. With the on-chip references, the pad and interconnect better match those in the DUT measurements and ideally move more parasitic elements into the error blocks.

On-chip references have become an established technique to improve calibration performance at high frequencies with many books and guidelines written on the subject. Shang et al. [23] outline a guide to making planar S-parameter measurements at mmWave frequencies. It gives high-level pros and cons of references such as SOLT, TRL, LRM, LRRM, and multiline TRL and practical advice on setting up the VNA. Rumiantsev's [24] detailed book describes the design of calibration references for high-performance mmWave devices. Williams et al. [25] presents design guidelines for mmWave on-chip TRL.

TRL or multiline TRL is the generally recommended on-chip calibration reference. Rumiantsev et al. [26] present a comparison of on-wafer multiline TRL and LRM to typical off-wafer SOLT reference. The on-wafer references outperformed the off-chip references in the frequency range of 1 to 110 GHz. Williams et al. [27] perform a similar experiment comparing on-wafer TRL to off-wafer SOLT and LRRM. The experiment again finds a performance improvement for TRL in the mmWave frequencies. The advantages of moving the calibration plane closer to the DUT only become important at mmWave frequencies as this is when the parasitic element difference becomes large.

Other new on-wafer calibration standards have also been investigated. Huang et al. [28] present an extension to TRL with an additional transmission line. Huang et al. [29] present an on-chip reference for production test applications up to 110 GHz. Wei et al. [30] present a general 4-port CMOS calibration references for 1 to 110 GHz. Yau et al. [31] compare open-short, split-through, and TRL de-embedding techniques for on-wafer DUT measurement for frequencies DC up to 170 GHz.

On-chip references are essentially the same as off-chip references except they are optimized for different processes and form factors. They are still mostly passive circuits with their own pads that must be probed and measured individually. The only advantage they provide is to extend the calibration bandwidth into the mmWave frequency range.

#### **Electronic Calibration References**

An established alternative to using physical calibration substrates is using an electronic calibration (ECal) module. ECal uses active electronic components to switch between the calibration references of a standard. This means that a single connection is made to the ECal block instead of having to physically move the probes between the references like on a substrate standard. After using the ECal module, the DUT is measured separately as normal.

ECal modules are a popular offering due to their quality, capability, and convenience [13]. ECal modules usually communicate directly with the VNA, allowing the entire calibration procedure to be automated [32, 33]. A single button press measures all the calibration references and saves the data. In contrast to the multistep process to measure all the calibration references of a substrate standard. In all but the most demanding applications, ECal has been verified as an accurate way to calibrate a VNA [34, 35, 36].

Original ECals used a transmission line shunted by PIN diodes along its length. Forward biasing the diodes shorts the transmission line different lengths from the ports which creates the different references [13]. Abramowicz and Lewandowsk [37] present a different an ECal

created from micro-electromechanical system (MEMS) switches that works from DC to 8 GHz.

A logical extension for ECal is to integrate it on-chip alongside the DUT, like what was done with normal calibration substrate standards. This will move the calibration plane closer to the DUT while still having the ECal benefit of not having to reposition probes between the reference measurements. A variety of techniques exist to create electronic references on-chip.

Xie et al. [38] present an ECal that uses Schottky diodes as calibration references which are varied by changing the biasing voltages applied through the wafer probes. The paper aimed at significantly increasing the operating frequency to the submillimeter-wave band (325-500GHz). However, it first relies on a characterization step using TRL to obtain the reference S-parameters.

There are a series of papers from the same author that present multiple ECal standards that are created using CMOS transistors. Three CMOS transistors in a pi network arrangement are used to create the references [39, 40, 41]. The transistors are either turned on/off as switches or have their gate bias voltage varied to create different impedances. A low-frequency measurement is used to characterize the references. Chien and Niknejad [42] then use a single CMOS transistor that creates a LRRM-type standard by varying the gate bias voltage and disconnecting the wafer probes. Chien [43] uses a transmission line loaded with 20 distributed CMOS switches.

Integrated ECal modules show promise in providing the same convenience of standalone ECal modules while moving the calibration plane closer to the DUT. A difficult part of integrated ECal is accurately knowing the reference S-parameters and being able to ignore or account for parasitic elements that impact the references. Less of the references are based off physical structures with defined reflections. Additionally, most ECal implementations are not independent modules and rely on DC biasing sent in on the measurement probes.

## 2.5 Summary

The current implementations of the IEEE 1149.4 analog test bus standard are limited in the maximum measurement frequency they can obtain. Their gain calibration does a poor job of accounting for errors that can occur at higher frequencies. VNAs, in contrast, do an excellent job at measuring high-frequency signals by employing a detailed calibration procedure. The procedure measures multiple calibration references, which characterizes the systematic errors present in the measurement setup. Knowing the errors, the true DUT performance can be de-embedded. There are many types of calibration references, each geared for different applications. Of note are the on-chip and electronic calibration reference categories. On-chip calibration references move the calibration plane closer to the DUT and account for errors but are still based on the large physical structures used in normal VNA substrate standards. Electronic calibration references allow the VNA probes to remain stationary while measuring the references by changing them with active components. On-chip electronic calibration references combine these advantages but are more difficult to characterize and manipulate.

## Chapter 3

## Proposed Analog Test Bus Structure

Using the literature review background on analog test buses, VNA calibration, and calibration references, an analog test bus structure that can accurately de-embed high-frequency errors is proposed. The proposed structure is split into two variations: a 4-port and 2-port test bus. The 4-port test bus is the primary structure, and its design is described in detail first. Calibration references are added to the test bus and the structure is informed by the requirement to consistently fit an error block calibration model. A comparison with 1149.4 to highlight the high-frequency measurement performance is presented with a simulated example. The 2-port test bus requires a specific condition with the reverse signal in order to be accurate. The 2-port test bus structure is described and added to the simulated example to compare with the other designs.

As discussed in the literature review section, the 1149.4 test bus has poor high-frequency performance and limited calibration ability. These problems have prevented 1149.4 from being used in high-frequency applications. VNAs on the other hand, are an established high-frequency tool with comprehensive calibration ability. VNAs are not a replacement for an analog test bus applications because they require dedicated ports for each analog block to be tested.

Combining the benefits of an analog test bus with a VNA style calibration procedure

would extend the measurement bandwidth and open up new test bus applications. To accomplish this, VNA-style calibration references are integrated within the test bus, and the test bus structure is altered to facilitate this.

The backbone of the proposed test bus structure are voltage and current buffers capable of being turned on/off to act as switches and route signals to/from circuits connected to the test bus. Buffers are used instead of transmission gates because buffers offer a greater frequency bandwidth. This fact is the same for 1149.4, as was discussed in the literature review Section 2.2.

The switching buffers allow the system to move between three distinct operation modes: mission, test, and calibration. Mission mode is the default state when the DUT operates normally and the entire test bus is disabled. Test mode uses the VNA and first buffer group to measure the DUT. Calibration mode uses the three other buffer groups separately to measure the calibration references.

## 3.1 4-Port Test Bus

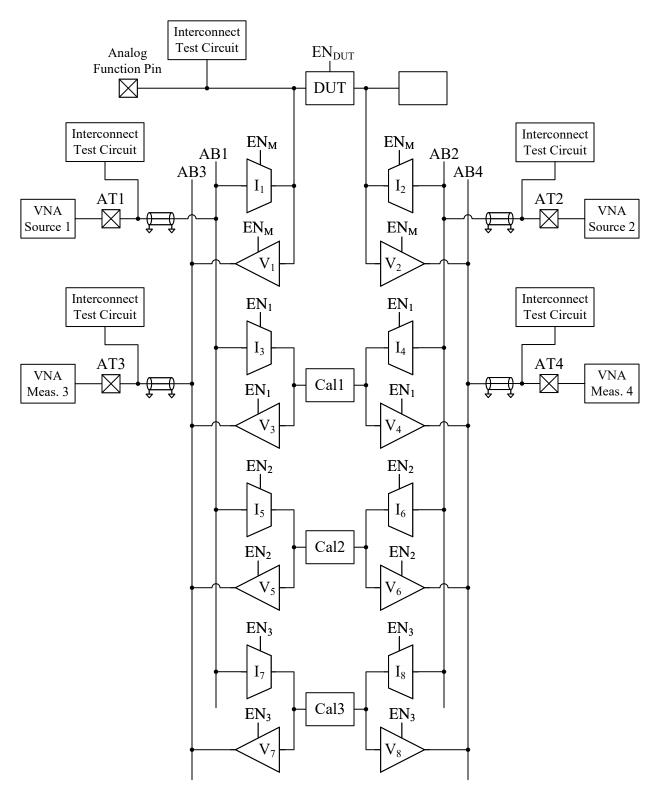

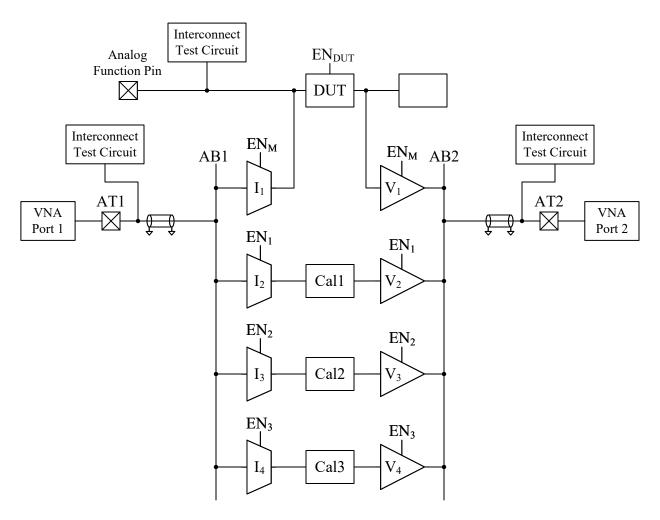

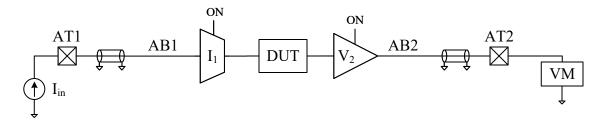

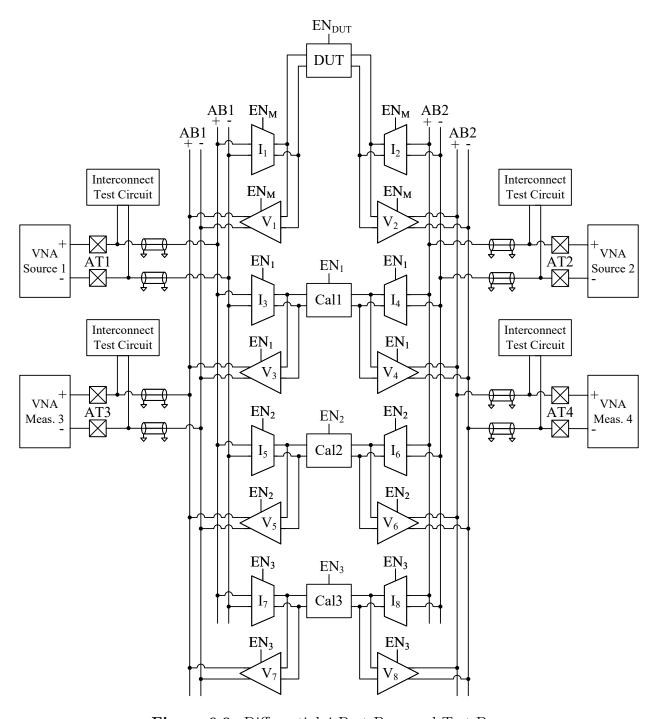

The high-level structure of the 4-port test bus is shown in Fig. 3.1 and will be referenced throughout this section. The 4-port test bus gets its name from the 4 external analog test ports it uses. At the top and center of the diagram is the DUT with its normal operation connections, in this case, its input connected to an external pin and its output connected to an arbitrary next circuit stage. Also connected below to the DUT input/output is the test bus.

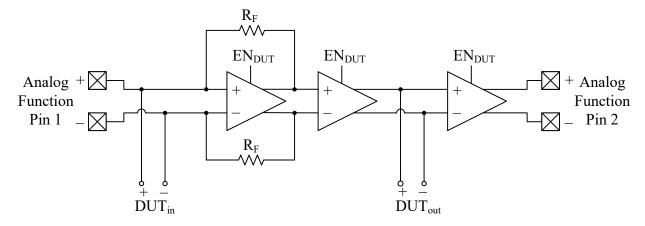

The four test ports (AT1 - 4) are each connected to an internal test bus (AB1 - 4) that is then connected to the buffers. The voltage and current buffers are labeled with  $V_n$  and  $I_n$  being the nth buffer, respectively. AT1 and AT2 are input ports that connect to the test signal source (VNA Source 1 and 2) and current buffers to drive the signal to the DUT or calibration references. AT3 and AT4 are output ports that connect to the voltage buffers to

Figure 3.1: Proposed 4-port analog test bus.

relay the test signal off-chip (VNA Meas. 3 and 4). Near the test ports are the Interconnect Test Circuit blocks which would perform basic port connection testing as in 1149.4, although they are not used during test bus measurements. Transmission lines between the test ports and buffers represent parasitic elements from long traces/interconnects that are accounted for during calibration.

The Cal1, Cal2, and Cal3 blocks represent three different calibration references much like those included in a typical VNA calibration. The exact internals of the calibration references will be discussed in Section 4.3. The ability of the voltage and current buffers to switch on or off is labeled with an enable pin at the top of the symbols. The three calibration references create three different zones controlled through  $EN_1$ ,  $EN_2$ , and  $EN_3$ .

$EN_M$  controls the test bus connection to the DUT. When switched off, the buffers should have little influence on the performance of the DUT. An optional enable pin,  $EN_{DUT}$ , is included to turn on and off the DUT when the test bus is in calibration mode. Large signals from an active DUT may leak through the buffers and contaminate the calibration.

## 3.1.1 High-Frequency Errors

Given ideal buffers and interconnects, both the 4-port and 1149.4 test buses can accurately measure an analog circuit's performance. As has been discussed repeatedly, the question becomes: What is the maximum frequency of the test bus and can calibration extend the bandwidth? Any test bus has a frequency limit at which it stops being accurate due to high-frequency effects such as parasitic capacitance, which starts to attenuate and shift the signal through the test bus.

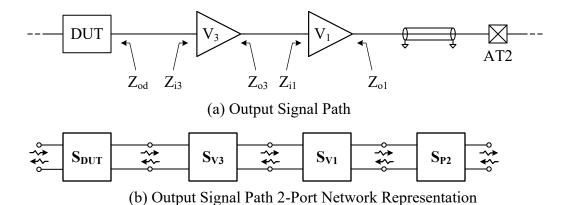

To more closely analyze the errors, Fig. 3.2 (a) shows a detail of the signal path from the DUT output to the test port. The gain transfer function has a low-pass characteristic, where the gain decreases at higher frequencies past the cutoff. In addition, the buffers have input and output impedances that start to change as frequencies increase. Focusing on the DUT and  $V_3$  connection, if  $Z_{od}$  and  $Z_{i3}$  have comparable magnitudes a voltage divider effect

Figure 3.2: Output signal path represented with (a) circuit schematic and (b) general 2-port networks.

will affect the gain.

Fig. 3.2 (a) also shows a transmission line and port symbol to represent the long interconnect and chip pad. The parasitic elements of these components become significant at high frequencies with the interconnect becoming an electrically long device. This could produce reflections causing phase shifts across the device.

This more detailed look at the errors that can affect test bus measurements begins to explain the complicated factors that impact measurements. It by no means includes every high-frequency error that could occur. One important effect to emphasize is the fact that not only does gain across the test bus signal path decrease, there is an interaction between the DUT and buffer input/output impedances. Given how complicated and intertwined high-frequency circuits are, it makes sense why S-parameters are a popular way to represent RF circuits. It is more convenient to represent circuit blocks with generic S-parameter 2-port networks. The 2-port model gives a generalized model of the system that does not assume anything about its performance. Continuing that logic, Fig. 3.2 (b) shows the test bus signal path replaced with S-parameter 2-port networks. Conceptualizing the test bus as a group of generic 2-port networks helps explain why the 4-port test bus is structured the way it is, as will be discussed.

Figure 3.3: 4-port test bus calibration model with 3-port input and output error blocks.

## 3.1.2 Structural Requirement to Enable Calibration

The structure of the 4-port test bus is informed by the requirement to fit the VNA calibration model. The S-parameter network model of the calibration system is shown in Fig. 3.3. As discussed in Section 2.4.1, a common VNA error model consists of two separate error blocks, one at the input of the DUT and a second at the output. The 4-port test bus conforms to the two error block system. The only difference is that the 4-port test bus error blocks contain an additional port making then 3-port networks. Exactly how the error terms of the error blocks are calculated will be discussed later in Section 4.2. For now, the high-level idea of VNA calibration remains. The 3 calibration references are used to calculated the contents of the error blocks to then be able to de-embed their effects from a DUT measurement.

The error block calibration model requires that the test bus components (buffers and ports) stay consistent between each measurement of the DUT and calibration references. Knowing the calibration model provides context for the structural differences between the 4-port and 1149.4 test buses, which are examined further in the following section.

## 3.2 4-Port and 1149.4 Test Bus Structural Comparison

Compared to the 1149.4 schematic as shown previously in Fig. 2.2, the 4-port test bus has one fewer buffer in the signal path and two additional test ports/buses. These differences are necessary to facilitate the VNA calibration approach and increase the frequency bandwidth.

In 1149.4, a buffer is placed between the test port and the test bus to give the option to disconnect the port from the bus. This buffer is part of the test bus interface circuit, which in a switch-based implementation allows both test ports and test buses to be connected interchangeably with each other. This is not included in a buffer-based implementation because the buffers are unidirectional. Making the signal cross 4 buffers increases the capacitance on the path and reduces its bandwidth. Additionally, the task of disconnecting the test bus and port is not strictly necessary, and a similar effect can be achieved by turning off all buffers connected to the bus. The proposed 4-port test bus removes this extra buffer for these reasons and directly connects the test port to the bus.