# THE DESIGN AND IMPLEMENTATION OF A STRUCTURED BACKEND FOR THE MCCAT C COMPILER

$by \\ Christopher \ M. \ Donawa$

School of Computer Science McGill University, Montréal

March 1994

A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

DESIGN AND IMPLEMENTATION OF A S

BACKEND FOR THE MCCAT C COMPILER

## Abstract

The McCAT system contains a highly optimizing, parallelizing C compiler that has been designed to support a high-level, structured intermediate representation, Simple. Although the high-level abstraction enables sophisticated analyses such as pointer analysis, it limits the effective detection and exploitation of opportunities for fine-grained parallelism through low-level transformations like register allocation and instruction scheduling.

This thesis presents Last, a low-level intermediate representation that exposes important architectural details, yet retains enough abstraction to simplify retargeting of the compiler.

LAST is structured, thus allowing easy access to information gathered by previous high-level analyses at SIMPLE, and also provides an elegant and simple framework for developing low-level analysis and transformation phases. To illustrate these features and their effectiveness, some example phases are presented, along with results from a small suite of benchmarks.

## Résumé

Le système McCAT comprend un compilateur C qui optimise et parallelise, il est conçu pour permettre l'utilisation de SIMPLE, une représentation intermédiaire structurée de haut niveau. Bien que le niveau élevé d'abstraction permette des analyses sophistiquées, telle que l'analyse des pointeurs, il restreint le dépistage efficace et l'exploitation des possibilités du parallelisme à travers des transformations de bas niveau, telle que l'allocation des registres et l'ordonnancement des instructions.

Cette thèse présente LAST, une représentation intermédiaire de bas niveau qui met en évidence les détails importants de l'architecture, tout en conservant l'abstraction nécessaire pour permettre l'utilisation du compilateur en vue de plusieurs processeurs cibles.

LAST est structuré, permettant l'accès facile à l'information récoltée précedemment par les analyses SIMPLE de haut niveau, et fournit également une structure simple et élégante pour le développement d'analyses de bas niveau et de transformations. Les caractéristiques et leur efficacité sont illustrées par des exemples (d'analyses et de transformations) ansi que les résultats d'une série des tests de performance.

# Genealogy of McCAT

This chapter presents the genealogy of the McCAT C compiler, from its origins in September 1990 to the present day. It is meant as a testament to all those who have worked on the project, an acknowledgment of their hard work to produce a system with which the author is proud to be involved.

The genealogy time line is broken down into individual semesters, as the components were roughly organized around the academic timetable.

- September, 1990. The origins of McCAT started with a compiler course project implemented by Erik Altman. Professor Gao taught the course. The project consisted of implementing a list scheduler in a version of GNU's GCC C compiler, using the RTL intermediate representation.

- January, 1991. In this winter term, two students joined Professor Laurie Hendren: Bhama Sridharan and Maryam Emami. Bhama started on deciphering the GCC front-end as part of her compiler course. It was during this course that the name McCAT(for the McGill Compiler/Architecture Testbed) was first coined.

- May, 1991. As part of a combined compiler and architecture project, Bhama implemented McCAT's first version of loop unrolling. Working with her was another student, Chandrika Mukerji, who extended Erik's work on scheduling to include the Shieh-Papachristou algorithm. It was this work on scheduling that the author cloned to implement McCAT's current list scheduler.

- A special note of appreciation is due to Ravi Shankar, who was always present to explain the many intricacies of C.

- September, 1991. After a long cross-country trip, Chris Donawa arrived in Montreal, and along with a few other students (including Justiani and Mizuho Iwaihara) took the compiler course taught by Laurie. For the first time, the modified GCC front-end being worked on by Bhama was used for the course, and the assignments and projects were used as a testing ground for several ideas about Simple. In particular, Mizuho's final project contributed heavily to some aspects of the simplify algorithm.

During this time, Maryam started her work on the call-graph and points-to analysis, while Bhama began development of the c-dump module.

January, 1992. After a very pleasant autumn, a frigid and severe winter gripped the city of Montréal. During this polar period, both Justiani and Chris began laying the foundations of their respective theses: the array dependence analyzer for Justiani, and the design and implementation of LAST for Chris. At the same time Ana Erosa, the next McCAT member, arrived to begin studies at McGill.

By March, Maryam had finished the call-graph framework, and the first version of the points-to analysis. Bhama finished implementing the SIMPLE intermediate representation.

May, 1992. After a late start, spring finally arrived in Montréal, and although the summer never really blossomed, the celebrations for the 350th anniversary of the city of Montréal made up for any lack of sun. During the festivities, Justiani started her implementation of the array dependence module, and Chris continued work on extending his course project to handle the entire SIMPLE C grammar, and generate code for the DLX architecture. Chris also started organizing the McCAT development environment.

The summer was also a flurry of activity for Bhama, as she wrote the McTAG module, implemented both reaching definitions and live variable analysis for SIMPLE, and graduated with a Masters degree.

September, 1992. After some construction delays, the ACAPS research group moved into their new lab (formerly two adjacent student offices). Into this new setup arrived the Rakesh Ghiya, who started work on extending Maryam's second version of points-to analysis to handle function pointers. Justiani finished an initial version of her array dependency analysis module.

For the second time, Laurie taught the compiler course with the McCAT compiler, and students projects developed into useful modules. Luis Lozano implemented Briggs' extension of Chaitin's graph-coloring register allocator. Matilda Leung wrote the initial version of the Last interpreter, Sandro Mazzucato developed a SPARC code generator and Claudia Pateras and Mary Iarocci extended Bhama's original loop unroller. Clark Verbrugge began work on generalized constant propagation, and Ana on the McCAT restructuring module.

January, 1993. This winter started later that the previous year, and was fortunately not as bitter. Shielded from the milder-but-still-cold weather, V.C. Sreedhar finished the unnest module, and cut the last chains to the old GCC framework that had up to

then been a heavy weight, by replacing the memory management routines. In addition, Sreedhar implemented an initial version of the ALPHA intermediate representation.

Some of the more ambitions projects lingered on into this semester, as Clark, Luis and Ana finished the work on their projects. Rakesh began his research into practical heap analysis methods.

May, 1993. Montréal was treated to a splendid summer, with near perfect weather. Besides the arrival of the sunshine, two talented undergraduate students on NSERC summer scholarships arrived to work over the summer: Christopher Lapkowski and Patrick Betremieux. Christopher wrote the McCAT XWindows interface and function inliner, and Patrick developed the source file linker and second version of the Last interpreter. Luis continued to fine-tune his register allocator, and Rakesh became a second McCAT administrator to help with module integration.

In July Maryam, after working night and day, submitted her massive Masters thesis on points-to analysis, which she had managed to cut down to 200 pages.

The end of the summer was marked by the beginning of a concerted effort to adopt 'serious' benchmarks for McCAT, made possible by the source linker.

September, 1993. The wonderful summer quickly gave way to a mediocre autumn, as clouds and chilly temperatures arrived in the city. Chris finished his work on integrating the list schedulers in McCAT, and handed over his duties as McCAT administrator to Rakesh and Patrick. In addition, a new position of benchmark administrator was taken by Ana, to coordinate the McCAT benchmark suite.

The third compiler course using McCAT was started, with a focus on code improving transformations.

The genealogy description ends here, but is not the end of the story, as many talented people continue to work on the compiler. The author looks forward to hearing the continuing unfolding saga of an interesting and exciting project.

# Acknowledgments

What were the lessons I learned from so many years of intensive work on the practical problem of setting type by computer? One of the most important lessons, perhaps, is the fact that software is hard. From now on I shall have significantly greater respect for every successful software tool that I encounter. During the past decade I was surprised to learn that the writing of programs for TeXand Metafont proved to be much more difficult than all the other things I had done (like proving theorems or writing books). The creation of good software demands a significantly higher standard of accuracy than those other things do, and it requires a longer attention span than other intellectual tasks.

-Donald Knuth, Keynote address to 11th World Computer Congress (IFIP Congress 1989).

My guideline in the morass of estimating complexity is that compilers are three times as bad as normal batch application programs....

-Frederick P. Brooks, Jr., "The Mythical Man Month: Essays on Software Engineering".

The McCAT compiler is, to say the least, a complex software project, and its success is a testament not only to the hard work of the students involved, but also to Laurie Hendren's management skills. Laurie has provided a sharp focus to the project, and nurtured its growth from a collection of course assignments to an exciting project with which I am proud to have been involved. I am also deeply appreciative of her keen insight into problems and her tremendously clarifying abstractions, which have made this thesis significantly less difficult than it could easily have been.

I would also like to thank one of the 'originals', Bhama Sridharan, for the countless times she has helped both me and everyone else in the lab with SIMPLE, and especially for enlightening us on the many mysteries of the GCC front-end. Luis Lozano and Sandro Muzzacato's excellent work on the register allocator and SPARC code generator was also invaluable in helping me produce working programs, and Patrick Betremieux's Last interpreter was a tool from the gods.

I'm also very appreciative of: Kristin Völundardóttir, Jill Ferrier and Siobhán Phelan for suffering me as a weekend roommate for several months; Helga Hermannsdóttir & Ian McAdam for their friendship and for keeping me from going insane; Rakesh Ghiya for many enlightening conversations; the incessant traveler, Ana Erosa, for enduring the constant teasing from Rakesh, Luis and myself; and Cécile Moura, for showing me my limits and what happens when they are exceeded.

I would also like to thank my co-workers Pierre Paulin, Francis Langlois, Cliff Liem, Trevor May and Shailesh Sutarwala at Bell-Northern Research for their patience and understanding while I was finishing this thesis, et merci à Isabelle Pot et Malte von Rüden pour la traduction.

# Contents

| Abstract |              |          |                                                |     |  |  |

|----------|--------------|----------|------------------------------------------------|-----|--|--|

| R        | Résumé       |          |                                                |     |  |  |

| G        | eneal        | ogy of   | McCAT                                          | iii |  |  |

| A        | cknov        | wledgn   | nents                                          | v   |  |  |

| 1        | Intr         | oducti   | on & Motivation                                | 1   |  |  |

|          | 1.1          | Thesis   | Contributions                                  | 2   |  |  |

|          | 1.2          | Organi   | ization of Thesis                              | 3   |  |  |

| 2        | Related Work |          |                                                |     |  |  |

|          | 2.1          | Motiva   | ation for Intermediate Representations         | 4   |  |  |

|          | 2.2          | Overvi   | iew of different IRs                           | 5   |  |  |

|          |              | 2.2.1    | Tuples                                         | 5   |  |  |

|          |              | 2.2.2    | Linear Forms                                   | 6   |  |  |

|          |              | 2.2.3    | Trees & DAGS                                   | 7   |  |  |

|          |              | 2.2.4    | Representing Flow of Control                   | 9   |  |  |

|          |              | 2.2.5    | Comparison                                     | g   |  |  |

|          | 2.3          | Specifi  | c Examples                                     | 10  |  |  |

|          |              | 2.3.1    | U-Code                                         | 10  |  |  |

|          |              | 2.3.2    | RTL                                            | 11  |  |  |

|          |              | 2.3.3    | SUIF                                           | 11  |  |  |

| 3        | Ove          | Overview |                                                |     |  |  |

|          | 3.1          | An Ov    | verview of the McCAT C Compiler                | 13  |  |  |

|          |              | 3.1.1    | Front-end Processing and Simplification Phases | 15  |  |  |

|          |              | 3.1.2    | The Blastify Phase                             | 16  |  |  |

|          |              | 3.1.3    | Code Generation Phase                          | 16  |  |  |

|          | 3.2          | Overvi   | iew of LAST                                    | 17  |  |  |

|          |              |          |                                                |     |  |  |

CONTENTS ix

|   |     | 3.2.1          | Design Mandate for LAST                          | 19              |

|---|-----|----------------|--------------------------------------------------|-----------------|

|   |     | 3.2.2          | Design Influences on LAST                        | 20              |

|   |     | 3.2.3          | Abstract Machine Model                           | 21              |

|   |     | 3.2.4          | Retargeting LAST: A Configurable IR              | 22              |

|   |     | 3.2.5          | Overview of Transformations and Analyses on LAST | 25              |

|   | 3.3 | Comp           | arison of LAST with SIMPLE                       | 25              |

|   |     | 3.3.1          | Three-address Code                               | 26              |

|   |     | 3.3.2          | Explicit Support of Load/Store Architectures     | 29              |

|   |     | 3.3.3          | Unique Variable Nodes                            | 32              |

|   |     | 3.3.4          | Parent/Child Relationship                        | 32              |

|   | 3.4 | Optim          | nizations Performed During Generation            | 33              |

|   |     | 3.4.1          | Pre-calculation and Folding of Offsets           | 34              |

|   |     | 3.4.2          | Loading of addresses outside of loops            | 34              |

|   |     | 3.4.3          | Multiplication by Integer Constants              | 35              |

|   |     | 3.4.4          | Reducing Stack Space                             | 35              |

|   | 3.5 | Impler         | mentation Restrictions                           | 36              |

|   | D-4 | -9-1 т         | Denovirualizat of T.A.C/D                        |                 |

| 4 |     |                | Description of LAST                              | <b>37</b> 37    |

|   | 4.1 |                | Common Nodes                                     | 37              |

|   |     | 4.1.1 $4.1.2$  | Common Nodes                                     |                 |

|   |     | 4.1.2          | Sequence Nodes                                   | 38              |

|   | 4.2 |                | Anchor Nodes                                     | 39              |

|   | 4.2 | 4.2.1          | Veriables Addresses Constants and Labels         | 39              |

|   |     | 4.2.1          | Variables, Addresses, Constants and Labels       | 41              |

|   |     |                | Load and Store Nodes                             | 42              |

|   |     | 4.2.3<br>4.2.4 | Function Declarations                            | 44              |

|   |     | 4.2.4 $4.2.5$  | Passing Parameters                               | 44              |

|   |     | 4.2.6          | Delay Slots                                      | 46              |

|   | 4.3 |                | Looping Nodes                                    | 46              |

|   | 4.0 | 4.3.1          | tor Nodes                                        | 46<br>47        |

|   |     | 4.3.2          | Logical Nodes                                    | 47              |

|   |     | 4.3.3          | Conversion Nodes                                 | 48              |

|   | 4.4 |                | of Control Nodes                                 | 49              |

|   | 1.1 | 4.4.1          | While and Do-While Statements                    | 49              |

|   |     | 4.4.2          | If Statements                                    | 49<br>51        |

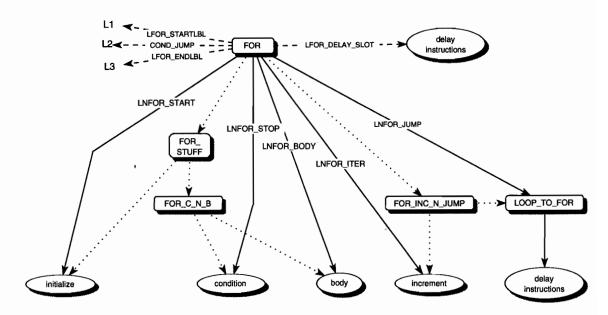

|   |     | 4.4.3          | For Statements                                   | $\frac{51}{52}$ |

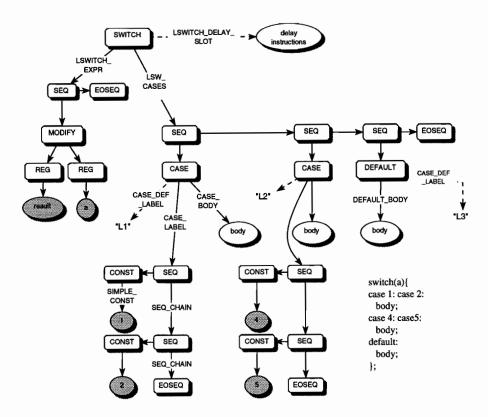

|   |     | 4.4.4          | Switch Statements                                |                 |

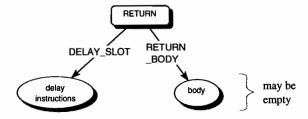

|   |     | 4.4.5          | Return, Continue and Break Statements            | 52<br>53        |

|   |     | T.T.U          | TOO WITH, CONTINUE AND DIEAN DIATEMENTS          | อฮ              |

*CONTENTS* x

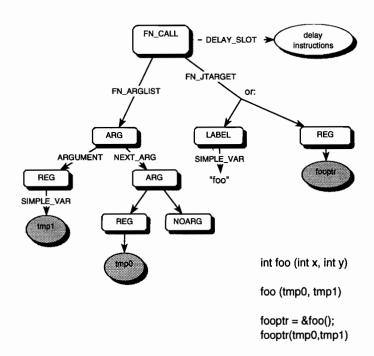

|              |                 | 4.4.6   | Function Calls                                   | . 53 |  |  |  |  |

|--------------|-----------------|---------|--------------------------------------------------|------|--|--|--|--|

| 5            | Tra             | nsform  | ning LAST                                        | 56   |  |  |  |  |

|              | 5.1             | Reduci  | ing the Number of Loads and Stores               | . 57 |  |  |  |  |

|              |                 | 5.1.1   | Handling the Register-Memory Consistency Problem | . 57 |  |  |  |  |

|              |                 | 5.1.2   | Algorithm for Reducing Loads and Stores          | . 59 |  |  |  |  |

|              | 5.2             | Instru  | ction Scheduling                                 | . 66 |  |  |  |  |

|              |                 | 5.2.1   | Overview of Instruction Scheduling               | . 66 |  |  |  |  |

|              |                 | 5.2.2   | List Schedulers in LAST                          | . 67 |  |  |  |  |

|              |                 | 5.2.3   | Implementation of Scheduling Framework           | . 69 |  |  |  |  |

| 6            | Analyzing LAST  |         |                                                  |      |  |  |  |  |

|              | 6.1             | Brief I | Review of Live Variable Analysis                 | . 71 |  |  |  |  |

|              | 6.2             | Live V  | Tariable Analysis in LAST                        | . 73 |  |  |  |  |

| 7            | Reta            | argetin | ng McCAT                                         | 79   |  |  |  |  |

|              | 7.1             | Archite | ectural Classes                                  | . 79 |  |  |  |  |

|              | 7.2             | Code-0  | Generator Generator                              | . 80 |  |  |  |  |

| 8            | Res             | ults    |                                                  | 85   |  |  |  |  |

|              | 8.1             | Descri  | ption of Benchmarks & Test Strategy              | . 85 |  |  |  |  |

|              | 8.2             | Benchi  | mark Results                                     | . 87 |  |  |  |  |

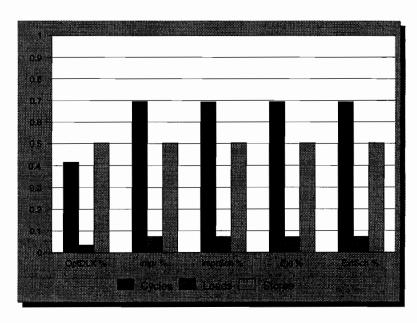

|              |                 | 8.2.1   | Dhrystone                                        | . 87 |  |  |  |  |

|              |                 | 8.2.2   | Hanoi                                            | . 87 |  |  |  |  |

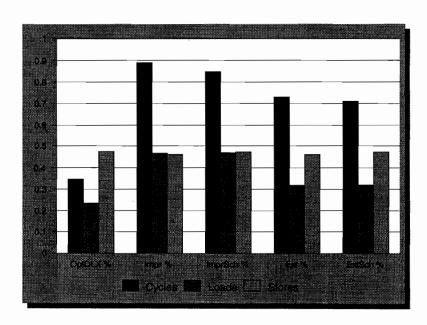

|              |                 | 8.2.3   | Intmm                                            | . 89 |  |  |  |  |

|              |                 | 8.2.4   | Knight                                           | . 89 |  |  |  |  |

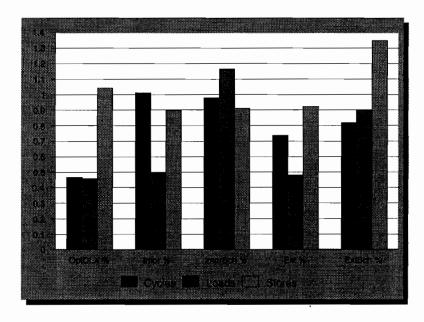

|              |                 | 8.2.5   | Mersenne                                         | . 89 |  |  |  |  |

|              |                 | 8.2.6   | Sorts                                            | . 90 |  |  |  |  |

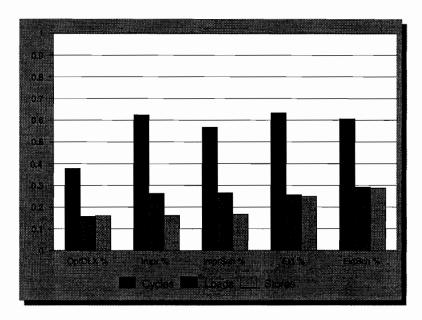

|              |                 | 8.2.7   | Tomcatv                                          | . 90 |  |  |  |  |

|              |                 | 8.2.8   | Whetstone                                        | . 92 |  |  |  |  |

|              | 8.3             | Observ  | vations & Impressions                            | . 92 |  |  |  |  |

| 9            | Con             | clusior | ns & Future Work                                 | 94   |  |  |  |  |

|              | 9.1 Conclusions |         |                                                  |      |  |  |  |  |

|              | 9.2             | Future  | e Work                                           | . 95 |  |  |  |  |

| A            | SIM             | PLE (   | Grammar                                          | 97   |  |  |  |  |

| В            | LAS             | ST Gra  | ammar                                            | 100  |  |  |  |  |

| $\mathbf{C}$ | Deta            | ailed R | Results                                          | 104  |  |  |  |  |

| CONTENTS     | xi  |

|--------------|-----|

|              |     |

| Glossary     | 106 |

| Bibliography | 107 |

# List of Tables

| 4.1 | Arithmetic nodes                                                    |

|-----|---------------------------------------------------------------------|

| 4.2 | Logical nodes                                                       |

| 4.3 | Conversion and register move nodes                                  |

| 8.1 | Description of benchmarks                                           |

| 8.2 | Latencies for DLX floating-point and load/store functional units 86 |

| 8.3 | Explanation of abbreviations for results                            |

| C.1 | Dhrystone results                                                   |

| C.2 | Hanoi results                                                       |

| C.3 | Intmm results                                                       |

| C.4 | Knight results                                                      |

| C.5 | Mersenne results                                                    |

| C.6 | Sorts results                                                       |

| C.7 | Tomcatv results                                                     |

| C.8 | Whetstone results                                                   |

# List of Figures

| 2.1  | Three-address code example                                            |

|------|-----------------------------------------------------------------------|

| 2.2  | $ Two-address\ code\ example\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\$ |

| 2.3  | Parse tree example                                                    |

| 2.4  | Hierarchy expressed in a parse tree                                   |

| 2.5  | Tree and DAG IR example                                               |

| 3.1  | Overview of McCAT                                                     |

| 3.2  | FIRST to SIMPLE conversion                                            |

| 3.3  | SIMPLE to LAST Transformation                                         |

| 3.4  | Code for SIMPLE to LAST Transformation                                |

| 3.5  | Code templates used by BURG to simplify retargeting                   |

| 3.6  | Example of Pseudo assembly code                                       |

| 3.7  | Analyses and transformations performed on LAST                        |

| 3.8  | LAST representation of an array reference                             |

| 3.9  | Example of a bit-field reference                                      |

| 3.10 | Example of a type conversion                                          |

| 3.11 | Example of register-use algorithm                                     |

| 3.12 | Optimization of array references                                      |

| 3.13 | Storage optimization                                                  |

| 3.14 | Replacing multiply with shifts for a = $97 * b \dots 36$              |

| 4.1  | The fields common to every LAST node                                  |

| 4.2  | SEQ node                                                              |

| 4.3  | How a SEQ accesses the flow information in an EXPR node               |

| 4.4  | REG node                                                              |

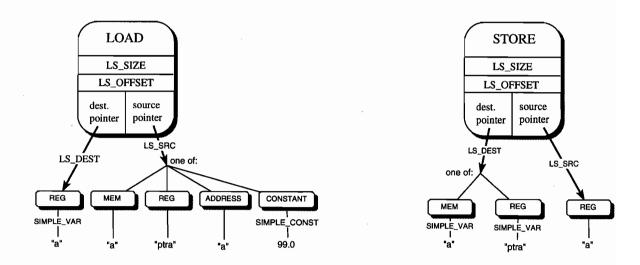

| 4.5  | Example of load and store in LAST 42                                  |

| 4.6  | Example of pointer dereference in LAST                                |

| 4.7  | LOAD and STORE nodes                                                  |

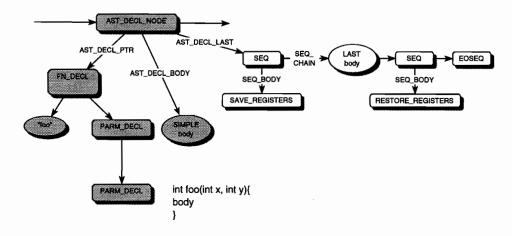

| 4.8  | LAST function declaration                                             |

| 4.9  | Passing parameters via the stack                                      |

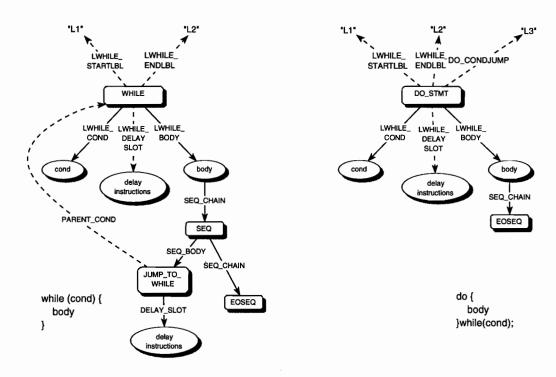

| 4.10 | while loop example                                                    |

|      | while and do while statements 50                                      |

| 4.12 | Pseudo and DLX assembly code illustrating labels in a while statement           | 50 |

|------|---------------------------------------------------------------------------------|----|

| 4.13 | do while loop example                                                           | 50 |

| 4.14 | Pseudo and DLX code illustrating labels in a do while statement                 | 51 |

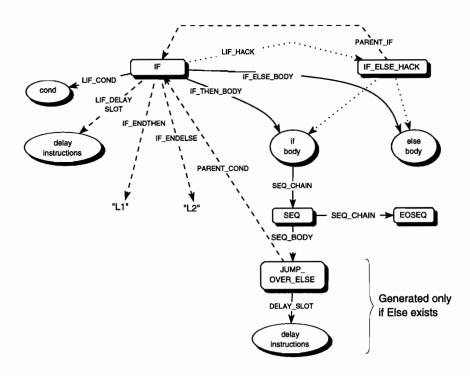

| 4.15 | If statement                                                                    | 52 |

| 4.16 | For loop statement                                                              | 53 |

| 4.17 | Switch statement                                                                | 54 |

| 4.18 | Return node                                                                     | 54 |

| 4.19 | LAST function call                                                              | 55 |

| 5.1  | Transformations performed on LAST                                               | 56 |

| 5.2  | Referencing a global variable across function boundaries                        | 58 |

| 5.3  | Pointer dereference example                                                     | 59 |

| 5.4  | Example C code showing the first definition of a variable in a conditional body | 59 |

| 5.5  | First reference of a variable in a conditional                                  | 60 |

| 5.6  | Reducing the number of loads and stores of local variables                      | 61 |

| 5.7  | Insertion of a dominating load for parameter variables                          | 63 |

| 5.8  | Sure and possibly points-to variables                                           | 64 |

| 5.9  | Sure alias substitution of pointer dereference                                  | 65 |

|      | Example of an invisible variable                                                | 65 |

|      | Three array references in a basic block                                         | 67 |

|      | Unscheduled and scheduled pseudo code                                           | 68 |

|      | Dependency Graph used for Scheduling Array References                           | 68 |

|      | Scheduling phases in the McCAT list scheduler                                   | 69 |

| 6.1  | Live Variable analysis on LAST                                                  | 71 |

| 6.2  | Example of live variable analysis                                               | 72 |

| 6.3  | Detail of live variable analysis algorithm at the statement level               | 73 |

| 6.4  | Detail of live variable analysis algorithm for an if statement                  | 74 |

| 6.5  | Pseudo code for live variable analysis example                                  | 74 |

| 6.6  | Three examples of live variable analysis algorithm for while statements         | 76 |

| 6.7  | Structure of while loop containing a conditional return statement               | 76 |

| 6.8  | High-level algorithm for performing live variable analysis on LAST              | 78 |

| 7.1  | Selection of Architectural Classes                                              | 80 |

| 7.2  | Code Generation Phase                                                           | 81 |

| 7.3  | Sample McBURG specification                                                     | 83 |

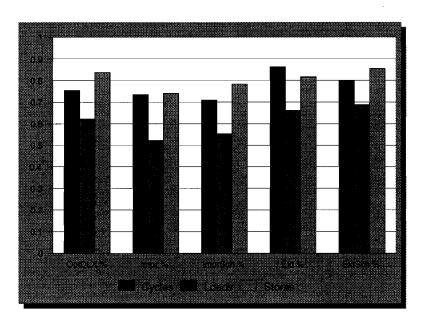

| 8.1  | Dhrystone results                                                               | 88 |

| 8.2  | Hanoi results                                                                   | 88 |

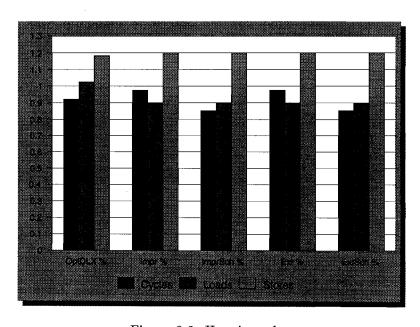

| 8.3  | Intmm results                                                                   |    |

| 8.4  |                                                                                 | 89 |

| 8.5  | Knight results                                                                  | 90 |

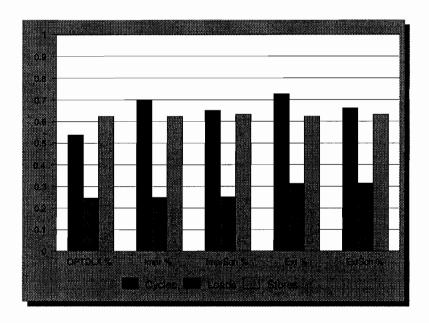

|      | Mersenne results                                                                | 91 |

| 8.6  | Sorts results                                                                   | 91 |

| LIST OF FIGURES |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 0.7             | The second secon | 00 |  |  |  |

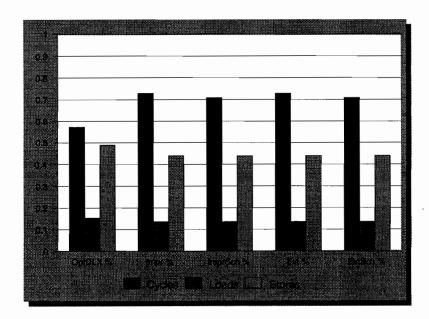

| 8.7             | Tomcatv results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92 |  |  |  |

| 8.8             | Whetstone results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93 |  |  |  |

# Chapter 1

## Introduction & Motivation

Because performance of a computer will be significantly affected by the compiler, understanding compiler technology today is critical to designing and efficiently implementing an instruction set.—Hennessy and Patterson [HP90].

Compiler technology is of vital importance to modern processors. High-performance processors are increasingly dependent on compilers to tweak, massage and contort input programs to take advantage of characteristics specific to their architectures. Non-blocking pipelined architectures, for example, such as the MIPS, SPARC, RS/6000, DEC Alpha [DS90, OHM+90, Dig92] and most other RISC (Reduced Instruction Set Computer [Pat85]) processors [HP90] expect the compiler to schedule instructions to maximize functional unit utilization; load/store architectures expect frequently-used values to be cached in registers [GH86]. These optimizations can be performed in hardware, but by shifting performance-improving manipulations from run-time to compile-time, scarce hardware resources can be devoted to other beneficial purposes, thus improving the overall performance of the architecture [SLH90]. For example, with instruction scheduling, the buffer for out-of-order execution architectures could be reduced and the saved hardware real-estate devoted to a larger register set, or a larger on-chip cache. Also, the overall complexity of the chip can be reduced, allowing for simpler, faster designs [DS90].

Needless to say, the increased responsibility of the compiler requires that architectural features, such as pipelined functional units and branch-delay slots, be exposed to the compiler. Representing these features is the domain of the compiler's intermediate representation (IR). The IR is a useful mechanism to abstractly represent the hardware, while representing some important characteristics (in terms of performance) of the underlying target processor. The user's program, written in some high-level language such as C, C++ or FORTRAN, is translated into the IR. The IR then becomes an interface between the

<sup>&</sup>lt;sup>1</sup>Sometimes referred to as an intermediate language (IL) or intermediate code (IC).

code-generation phase of the compiler (where actual assembly code instructions are generated), and the analysis and transformation phases. Depending on the compiler, the IR can be either very abstract (eg model a simple machine), very processor specific, or something in between. The more specific the IR, the greater the information available to expose fine-grain parallelism to the analysis and transformation phases. However, the compiler will be more difficult to retarget to a different architecture: the less abstract an IR is, the harder the compiler is to retarget as more of the analysis and transformation phases rely on processor-specific features.

This thesis presents an intermediate representation used in the McGill Compiler Architecture Testbed (McCAT) C compiler. This IR, called Last(Low-level Abstract Syntax Tree), forms part of the backend developed as the focus of this thesis. Last strives to reveal enough architectural details to the analysis and transformations phases, while retaining some abstraction to simplify retargeting of the compiler to a collection of RISC architectures.

In addition, Last is designed as part of a family of intermediate representations [HDE<sup>+</sup>92] (Section 3.1), of which Last forms the the lowest level. The other, higher IRs facilitate high-level analyses and transformations, such as points-to analysis, <sup>2</sup> array dependency analysis, loop transformations, and inlining. Last is specially designed to utilize the data-flow information generated from these previous analyses phases for low-level transformation *ie* support a paradigm of *pervasive flow-information*.

#### 1.1 Thesis Contributions

While several existing IRs can accomplish similar goals to Last, an experimental approach of making Last a hierarchical, structured IR, rather than unstructured, was taken. That is, instead of representing the flow-control of the program in terms of goto statements and labels, Last retains the notion of high-level control structures such as for and while loops, and supports nesting of these structures. The phrase 'structured IR' is used in this thesis to denote an intermediate representation which has the characteristic of representing nested control structures (ie hierarchical structures), without the use of goto statements.

A structured IR was chosen for LAST in order to support structured analyses and transformations, a central paradigm of the McCAT compiler. A structured IR is conceptually cleaner to use, since the program is always represented at a high-level. A structured IR was also chosen so as to simplify implementation of the pervasive flow-information paradigm. By supporting high-level constructs such as while and for loops, it is very simple to relate flow-analysis information generated at the other high-level IRs.

In addition to describing LAST, some example analyses and transformations are presented to illustrate the structured nature of the IR. And finally, the retargeting strategy of

<sup>&</sup>lt;sup>2</sup>Comparable to alias analysis [ASU88] in other compilers.

McCAT using Last is presented.

Specifically, the contributions of this thesis are itemized below.

- The design and implementation of LAST, a low-level tree-based retargetable intermediate representation that, while suitable for transformations such as register allocation and instruction scheduling, also retains the structured nature of programs, as well as supports the pervasive nature of data flow information in the compiler.

- The design and integration of a highly retargetable code generator (using the codegenerator generator Burg[FHP92b]) for RISC machines.

- The implementation of various structured analyses on Last, with a specific example of live variable analysis presented.

- The implementation of various code-improving transformations on Last, including instruction scheduling and reducing the number of load and store instructions.

- Experimental results from a suite of benchmarks illustrating the benefits of various analyses and transformations performed on LAST.

#### 1.2 Organization of Thesis

The rest of this thesis details the contributions listed above. The following chapter, Chapter 2, gives some background on intermediate representations, listing traditional, current and LAST-related IRs. Next, Chapter 3, is an overview of the McCAT compiler. The general framework of the compiler is presented, from the higher IRs to LAST to the code-generation phase. Following the overview is Chapter 4, which presents the individual nodes of LAST in detail, as well as the optimizations performed during the generation of LAST. Chapter 5 and Chapter 6 illustrate the structured nature of LAST by presenting some analyses and transformations, and highlight the simplicity and ease of using a structured IR such as LAST. Next is Chapter 7, which describes the code generation strategy used, and also how LAST simplifies retargeting of the compiler. Chapter 8 presents results of the transformations performed on LAST, with aid of both the LAST analyses and pervasive flow information gathered from previous analyses. Finally, Chapter 9 presents the conclusions of this thesis.

# Chapter 2

## Related Work

#### 2.1 Motivation for Intermediate Representations

As mentioned in the introduction, intermediate representations (IRs), are used to represent the target architecture in an abstract form. In optimizing compilers the analysis and transformation phases are run on the IR, after which the transformed IR is used to generate assembly code for the target machine. However, intermediate representations are not an essential part of compilers; compilers have the option of generating assembly code (and sometimes machine code) directly, without the overhead of generating and manipulating an IR [FL88].

Such 'one-pass' compilers are designed to quickly generate assembly/machine code, often at the cost of the quality of the generated code, *ie* little effort is spent performing code-improving transformations. However, the focus of high-performance compilers is obviously to improve the speed of compiled programs, and intermediate representations are used so the compiler has something to actually analyze and manipulate.

In addition to facilitating analyses and transformations, intermediate representations also simplify software maintenance problems for compiler developers, since the complexity of the analyses and transformation phases requires a large investment in design and development of the compiler. Due to the nature of evolving architectures, compilers can expect to be frequently re-targeted. Compiler developers naturally wish to minimize the loss of their usually substantial code investment, and designing the compiler to use an abstract IR, common to many back-ends, is one method of minimizing the work and effort required to retarget a compiler. As Tannenbaum et al. note [TvSS82]:

[I]t is desirable to do as much optimization as possible on the intermediate code, because that optimizer can be written once and for all and used without change as a filter for subsequent front ends and back ends.

An intermediate representation allows one to replace the code-generation part of the backend when retargeting the compiler, and in some compilers, also the front-end [Sta92, CHKW86], so that different languages can be compiled reusing most of the existing compiler.

Intermediate representations are designed to represent abstract machines, but there remains the problem of how abstract a machine to model. An IR that closely models a specific architecture will allow more efficient code to be generated, as intricate machine details can be exposed to the analysis and transformation phases. However, the compiler then becomes more difficult to retarget as these same phases might need to be rewritten should the compiler be retargeted to a new, different target architecture.

On the other hand, if the IR is very abstract, then the compiler is more flexible, but fewer machine details are revealed and the code-generation part of the back-end must be quite sophisticated and optimize the IR itself in order to produce efficient code [CHKW86]. Such optimizing back-ends, called peep-hole optimizers, already exist for CISC (Complex Instruction Set Computers) machines. Peep-hole optimizers combine adjacent instructions to produce more complex but cheaper (in terms of execution time or resource utilization) instructions. This is an important optimization for CISC machines, and several retargetable peep-hole optimizers have already been developed [DF84, Kes84, BD88], but they are of lesser help to compilers for RISC architectures.

RISC architectures require optimizations such as instruction scheduling and removal of redundant loads, transformations which require extensive analyses over potentially large blocks of code. Research into retargetable instruction schedulers is in progress [Con93, CCDM93], but requires that the target machine be accurately modeled *ie* too abstract a model defeats the purpose. A balance must therefore be struck between a very abstract model and a too detailed a model in order to obtain a highly optimizing but retargetable compiler.

#### 2.2 Overview of different IRs

There are a variety of intermediate representation forms that can be used in a compiler, but they fall into three main categories of tuples, linear forms, trees and directed acyclic graphs (DAGS).

#### 2.2.1 Tuples

Tuples are a simple, straight forward representation that can have a variety of forms [FL88]. A tuple will represent a destination variable, operator(s) and operand(s). The most common form is known as 'three-address code', which means that each statement contains three variables: one destination and two operands (plus a single operator). It is also known as a

quadruple (three variables plus an operator). A multi-operand, complex instruction, might be decomposed into the three-address statements as shown in Figure 2.1.

Figure 2.1: Three-address code example

As mentioned, there are different variations, some allowing several operators and some only two operands with no destination (a triple). A triple does not explicitly save intermediate values like quadruples, but instead refers to them by the number of the triple that created it as in Figure 2.2.

$$a = b + c * d - e$$

$$(1): c * d$$

$$(2): b + (1)$$

$$(3): (2) - e$$

$$(4): a = (3)$$

Figure 2.2: Two-address code example

Triples are more concise than quadruples, but are position dependent and so can create difficulties for transformations involving code motion.

Due to their potentially compact implementation, tuples were popular for compilers facing strict memory limitations, and allowed compilers to save the intermediate representations to files using this compact representation [Hor91]. Modern architectures allow more liberal use of their resources, so there are few compelling reasons for plain tuples. However, tuples, particularly three-address codes modified to hold flow-information, can be quite useful for modeling RISC machines, which are typically three-address architectures—a three-address IR can thus model a RISC architecture quite closely. However, three-address code IRs introduce complications through the addition of temporaries when modeling CISC architectures [BGM79], and so would be best suited for compilers that support RISC machines.

#### 2.2.2 Linear Forms

There are two types of linear forms—prefix and postfix. They are two forms common in mathematics, useful for expressing parenthesis-free arithmetic operations. In prefix form, the operator precedes the operands, and in postfix form it succeeds them. Intermediate

values are implicitly saved on a stack, and so linear representations are well suited for stack-based architectures. The expression a = b + c \* d -e is expressed in prefix as =a-+b\*cde and postfix as abcd\*+e-=.

Ganapathi and Fischer suggested an interesting variant of a linear form suitable for optimizing compilers—an attributed linear prefix form [GF84]. The prefix form allows analysis of variable-operand instructions, while minimizing the parsing of the IR itself. The 'attributed' part simply means associated flow information is stored with each linear prefix statement. The main advantage is that the IR can be mapped to an assembly instruction in one pass, whereas other IRs, such as trees, require multiple passes. However, this advantage is of less and less importance as other compiler phases, notably the analysis and transformation phases, become relatively more expensive, and the code-generation phase becomes relatively cheaper to run.

#### 2.2.3 Trees & DAGS

The most general intermediate representations are based on parse trees [FL88]. A parse tree represents arithmetic operations with operands as leaves, and operators as interior (parent) nodes. Intermediate results would also correspond to parent nodes. Figure 2.3 illustrates a parse tree for the expression a = b + c \* d - e.

Figure 2.3: Parse tree example

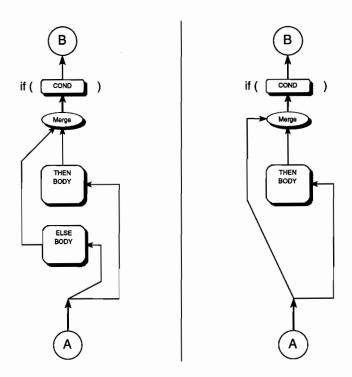

Parse trees can directly represent hierarchy (eg nested structures such as nested for loops), as well as complex, multi-operator statements; other representations 'flatten' out the hierarchy and the complex instructions. For example, Figure 2.4 illustrates a parse tree consisting of an if statement with a sub-tree of instructions representing the condition expression, as well as a sub-tree for the body of the if statement. This body can contain any series of valid statements, such as other if, while or for constructs. Preceding and following the if statement are two arbitrary statements, stmt1 and stmt2.

In a non-hierarchical representation (right side of Figure 2.4), the condition and body statements are just part of a long list of instructions that also include stmt1 and stmt2: all sense of nesting or hierarchy has disappeared. Most low-level intermediate representations take this approach. By transforming high-level constructs to assembly-level statements, analyses and transformations are simplified since they need deal with only a subset of instructions. For example, all conditional constructs (for, while, if, do while and switch) can be transformed to a series of test and branch instructions.

However, this simplification also has a disadvantage, in that high-level information is lost, and must be regenerated. For example, to perform loop transformations (software pipelining [HP90] is included in such a transformation), loops must first be identified, requiring the calculation of dominators [ASU88, p. 602]. In some cases, the transformation to a low-level IR loses too much information that cannot be recovered. A structured IR retains all this information, and saves the cost of recalculation. In addition, dealing with structured IRs is conceptionally clearer, as it is much closer to the original program.

Trees also have the option of being structured or not. A structured representation, as explained before, does not represent goto statements. Since many source languages (including C) support gotos, many IRs are unstructured, as automatic structuring programs are complex, difficult to write (although possible, [EH94]), and can degrade performance of the resulting program. Structured analysis is, however, an elegant approach, and is straight forward to implement [ASU88].

Figure 2.4: Hierarchy expressed in a parse tree

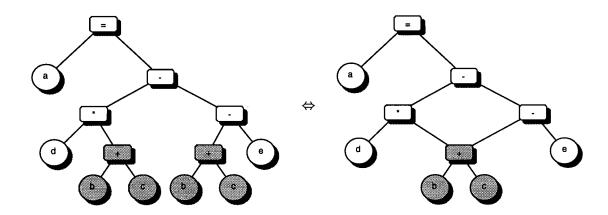

DAGS, or directed acyclic graphs, are variants of parse trees, where common parent and/or child nodes can be shared (Figure 2.5). DAGS can simplify some optimizations, such as common sub-expression elimination [ASU88], but some useful tools, such as the code-generator generator Burg[FHP92b], require trees and will not work with graphs.

The great power of parse-trees (and DAGS) is that all the information available at the source-level language is available in the representation. Parse trees, therefore, are an excellent IR when a compiler is performing source-to-source transformations. Parse trees are also good for generating code for CISC architectures, since complex instructions can (sometimes) map nicely onto subtrees in the parse tree [BGM79]. However, based on previous experience in building an optimizing compiler utilizing a parse-tree as an IR,

Figure 2.5: Tree and DAG IR example

the potential complexity of parse-trees, due to the hierarchy, can significantly complicate analyses and transformations. Trees and DAGS have the option of being structured, *ie* support flow-control without the use of **goto** statements and labels.

The McCAT compiler uses a simplified version of a parse-tree for one of its intermediate representations [Sri92, HDE<sup>+</sup>92], which provides the power of parse trees without the complexity (see Section 3.1).

#### 2.2.4 Representing Flow of Control

Once the program has been parsed and an IR generated, the program's flow of control must be determined. In an unstructured IR, a control-flow graph (CFG) [ASU88] is generated to capture the possibly arbitrary changes in control flow. The IR on the right in Figure 2.4 shows two control-flow arcs from the test associated with an if statement. One goes to the beginning of the body of the if statement, and the other to a label, indicating the end of the body.

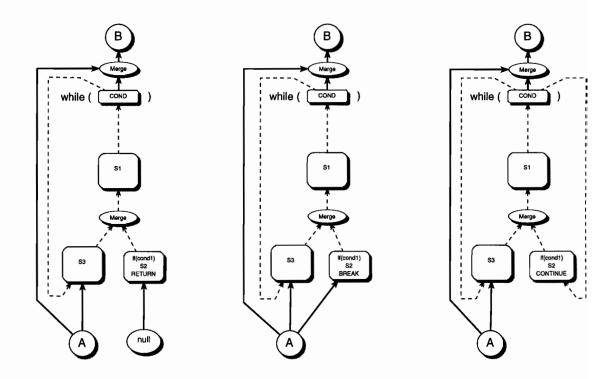

A structured IR, on the other hand, has flow-control represented explicitly, since each change in control is well defined (*ie* no goto statements). For example a continue will always transfer control to the inner-most enclosing loop.

The main advantage of a CFG is that it can handle goto statements. However, it must be generated, and the abstraction of high-level structures (like while loops) is lost, as all control structures are represented as low-level jumps to labels.

#### 2.2.5 Comparison

Enumeration of the different types of IRs is, in some sense, superfluous, because the methods of implementation overlap (eg many would be combinations of pointers to structures [GF84])

so that there is sometimes very little that distinguishes the representations from one another. In addition, there are, of course, modified versions of each category which only blur the distinctions even more. The tuples, linear forms and trees/DAGS can all be converted into one another, although it may take some work. For example, a pre-traversal over a parse tree will generate a prefix linear IR, and a quadruple can be used to regenerate a tree. It is often the resulting abstract machine being modeled which decides the IR; LAST takes a three-address approach to model abstract RISC machines, in combination with a tree to provide a structured IR.

#### 2.3 Specific Examples

The following subsections briefly describe some contemporary intermediate representations: U-code, RTL, and SUIF.

#### 2.3.1 U-Code

U-code, or Universal PASCAL Code, is an extension of the PASCAL Code (P-code) intermediate language developed by Wirth [Wir71, NAJ+81] for PASCAL. U-code was extended to simplify global (intra-procedural) optimizing transformations for both PASCAL and FORTRAN programs [PS79], and was used to develop a retargetable, machine-independent global optimizer UOPT [Cho83]. The central idea of UOPT is to perform as many analyses and transformations as possible on the machine-independent IR in order to reduce re-implementation when retargeting the compiler to different architectures, an idea prevalent in many modern compilers.

U-code (and P-code) is an unstructured, three-address code IR that models an abstract stack-based architecture called the P-machine. The machine is composed of three stacks: one for runtime (to model parameter passing and memory allocation), one for address and integer operations, and a third for set and real type operations [KKM80]. U-code is thus quite retargetable, due to its highly abstract nature. It is not an effective representation for CISC-based architectures (due to its three-address approach), as a large number of extraneous temporaries are generated that take considerable effort to collapse [BGM79], an operation needed for effective instruction set selection.

However, U-code can be quite effective for RISC architectures: it is currently used in the MIPS compiler [Cho88, CHKW86], although by itself the IR is too abstract to generate good assembly code. The code-generation modules are extremely sophisticated, and must perform many complicated transformations, including instruction scheduling and dead code elimination [CHKW86]. In addition, the MIPS U-code representation was modified to represent some architecture specific features (eg function calls) [CHKW86]. The MIPS version of U-code is used primarily to perform machine-independent optimizations such

as copy propagation, function inlining, common sub-expression elimination and strength reduction [ASU88].

#### 2.3.2 RTL

RTL, or Register Transfer Language, is the intermediate representation used in the popular GNU C compiler [Sta92, pp. 127-166], RTL is a variation of Jack Davidson's Register Transfer Lists [DF86]. There are many flavors of RTL, but the GNU version is perhaps the most widespread. The goal of RTL, like U-code, is to provide a machine-independent medium on which to perform analyses and transformations, and also be easily retargetable. However, RTL takes the opposite tack to U-code. Whereas U-code accomplishes portability by modeling a single, very abstract machine, RTL is configured to provide very machine-specific representations for different architectures. RTL provides actions that are at a lower level than corresponding assembly level operations. For example, RTL uses separate nodes to indicate register reads and register writes, whereas an assembly instruction will read the operands and write a result as an atomic operation eg the assembly instruction add r1,r2,r3 reads registers r2 and r3, and writes the result in r1. In addition, several RTL nodes are used to represent architecture-specific details, such as the size of character variables when performing a type-casting operation. Essentially, different sequences of RTL nodes are generated for different classes of architectures.

While some ideas from RTL were used in the design of Last(see Section 3), there are two fundamental differences. First, Last takes a higher-level approach, in that since its target architecture is limited to RISC, there are certain basic architectural assumptions that are made to simplify the design, whereas RTL must be flexible enough to handle a wider variety of architectures, which translates to a lower-level (and more verbose) approach than Last. For example, Last need not support CISC instruction sets, and so a simple, straight forward representation of operators suffices. GNU's RTL however, must support complex instructions, which leads to a plethora of nodes flexible enough to handle the many possible types of CISC instructions.

The second difference to LAST is the unstructured nature of RTL. For instance, the operands to branch instructions are located by convention: they are the nodes immediately preceding a conditional branch. This low-level, unstructured approach makes some low-level transformations, such as instruction scheduling, conceptually easy, but high-level analyses and transformations are more difficult.

#### 2.3.3 SUIF

SUIF, or the Stanford University Intermediate Format [TWL+91], is a hierarchical intermediate representation that was designed in order to marry high and low-level analyses and

<sup>&</sup>lt;sup>1</sup>And sometimes idiosyncratic!

transformations. Although SUIF is a hierarchical representation, it is unstructured, that is, SUIF supports arbitrary changes of flow control through goto statements. SUIF actually is polymorphic—there is a low-SUIF and a high-SUIF. The creation of two different forms was motivated by the two different types of parallelism available in programs: coarse- and fine-grain parallelism. Parallelizing (coarse-grain) transformations require a high-level view of the program, whereas scalar (fine-grain) optimizations prefer a low-level view. In many compilers this leads to two incompatible IRs, and thus duplicated analyses and transformation phases, since analysis information from the high-level IR is often unavailable to the low-level IR. This prompted the development of SUIF, which is a low-level IR with a superset of nodes that represent high-level structures and objects such as for loops and array references. The SUIF compiler first generates high-SUIF, performs coarse-grain transformations, and then transforms high-SUIF into low-SUIF, for scalar optimizations.

Low-SUIF represents the program in much the same way other unstructured IRs do: as a long linked list of assembly-level instructions (in three-address form with associated flow-information). However, for the parallelizing transformations, high-SUIF is used.

The main advantage of this multi-faceted approach is mainly in the software maintenance aspect of building the compiler. The common IR allows transformations to be implemented only once in the compiler (although they may be run several times after high-level transformations), saving time and effort.

## Chapter 3

# **Overview**

### 3.1 An Overview of the McCAT C Compiler

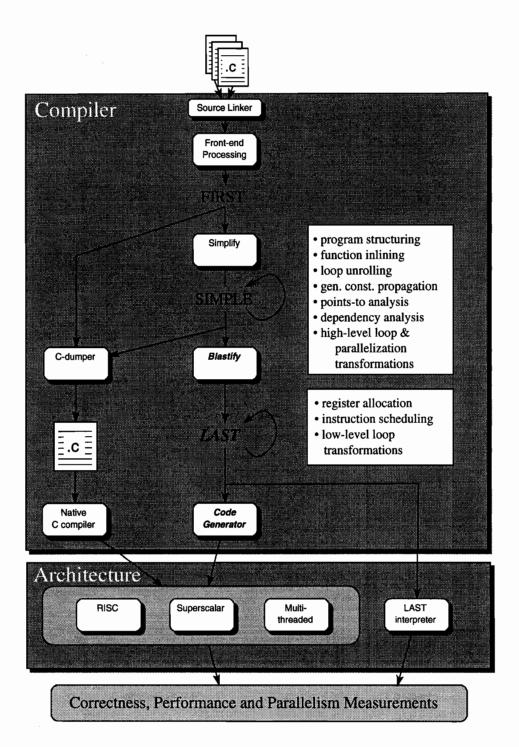

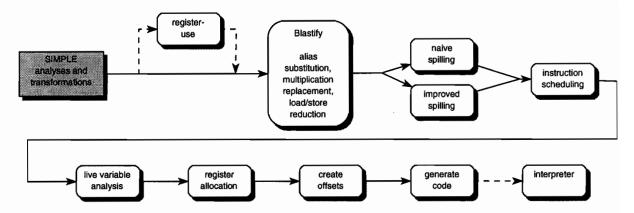

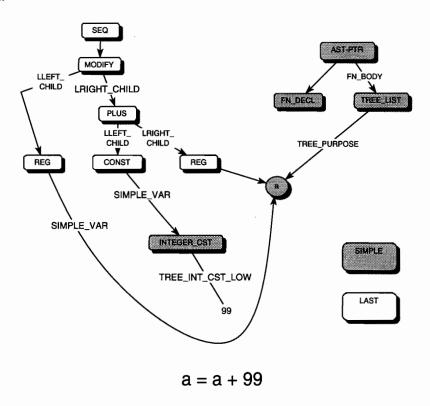

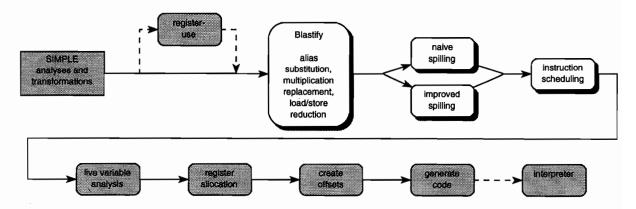

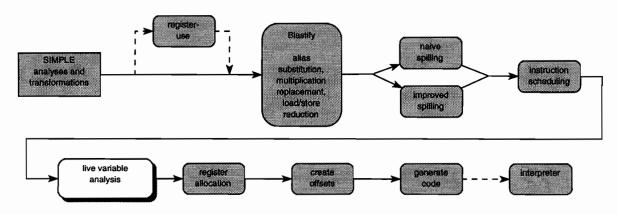

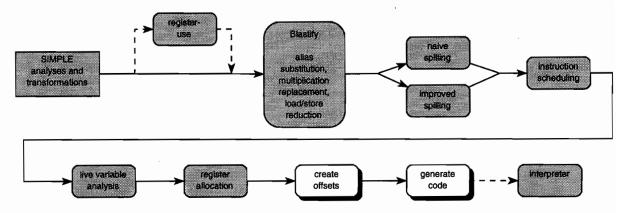

This section gives an overview of the McCAT C compiler, including the component intermediate representations, of which LAST forms the lowest level IR. McCAT is being developed by the Advanced Compilers, Architectures and Parallel Systems (ACAPS) research group at McGill as an optimizing and parallelizing C compiler, well suited to accurate points-to<sup>1</sup> [Ema93, EGH94] and dependency analysis [Wol82]. McCAT accomplishes this by utilizing a family of intermediate representations, which support pervasive flow information, ie flow information gathered from analysing one IR is available to lower-level intermediate representations for their transformations (see Figure 3.1).

The compiler uses a modified GCC<sup>2</sup> front-end for parsing the source files and generating a high-level abstract syntax tree (AST) [ASU88, p. 49], dubbed FIRST. This intermediate representation is then simplified into a similar AST called SIMPLE, upon which various high-level analyses and transformations are performed (for example, points-to analysis and loop unrolling).

SIMPLE is designed around the points-to analysis algorithm [HDE+92, EGH94], which requires a high-level view of the program, ie abstractions such as arrays, structures and pointer types are retained. This high-level information is required for alias analysis, but is inappropriate for low-level analyses and optimizing transformations such as register allocation or instruction scheduling: the architectural details required for these low-level optimizations are hidden in SIMPLE. LAST is designed to expose these details, yet at the same time retain some of the high-level features of SIMPLE such as abstract control flow structures (eg a for statement) so as to maintain a structured representation.

The McCAT compiler can be described as having four phases, with various analyses and transformations working on the two dominant IRs: SIMPLE and LAST. The first phase

<sup>&</sup>lt;sup>1</sup>Analogous to alias analysis in other compilers.

<sup>&</sup>lt;sup>2</sup>GNU's 1.37.1 version of GCC, to be specific.

Figure 3.1: Overview of McCAT

is the creation of FIRST and the second its transformation to SIMPLE. The third phase transforms SIMPLE to LAST, and the fourth, final phase generates assembly code from LAST. Figure 3.1 illustrates the overall process.

#### 3.1.1 Front-end Processing and Simplification Phases

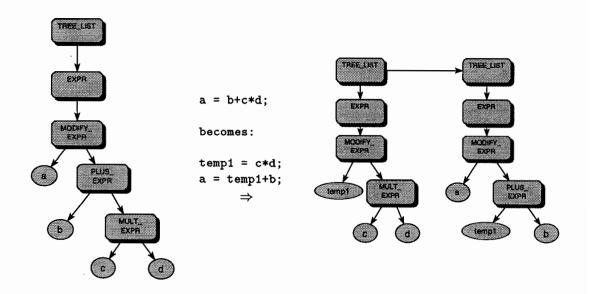

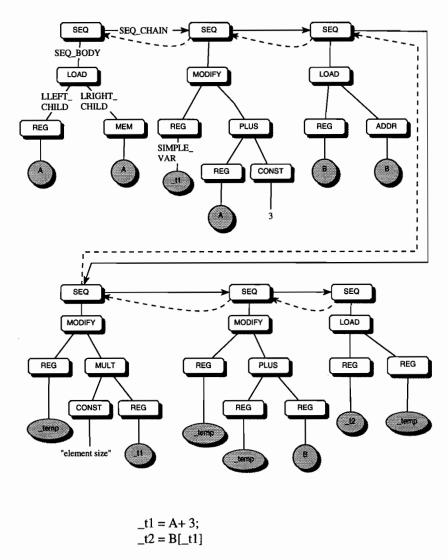

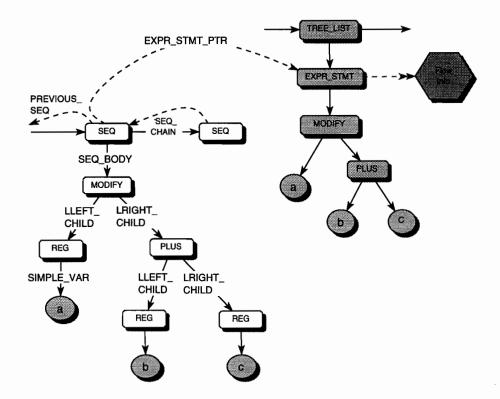

The McCAT compiler parses C source files and produces an AST.<sup>3</sup> In McCAT, this AST is called First, and is the first phase of compilation. This IR is immediately transformed, or simplified into Simple(the second phase), upon which the first set of analyses is performed. As the name would suggest, the simplify stage takes C, in all its gory glory, and simplifies it to a grammar corresponding to that in Appendix A. Typical simplifications include compiling complex statements into a series of basic statements, simplifying all conditional expressions in if and while statements to simple expressions with no side-effects, simplifying procedure arguments to either constants or variable names, and moving variable initializations from declarations to statements in the body of the appropriate procedure. Figure 3.2 captures the transformation of a complex arithmetic operation to a series of basic statements; the figure illustrates how a First tree is transformed into a sequence of two Simple trees. High-level abstractions such as array and structure references remain, but are simplified. Bhama Sridharan provides an excellent description of Simple in her masters thesis [Sri92].

Figure 3.2: FIRST to SIMPLE conversion

<sup>&</sup>lt;sup>3</sup>McCAT also has the ability to parse multi-file programs and produce a combined AST.

#### 3.1.2 The Blastify Phase

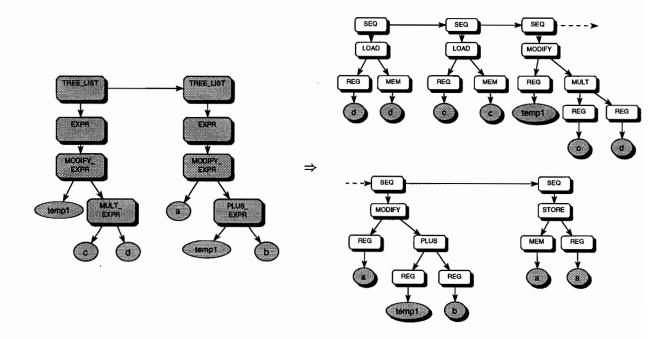

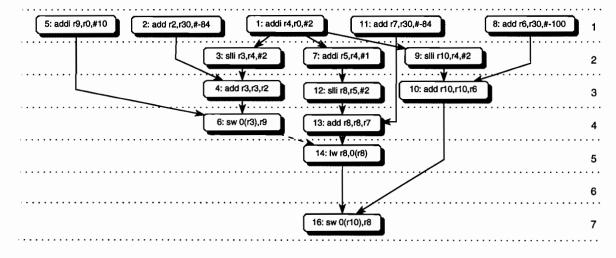

The blastify phase generates LAST from SIMPLE. Whereas SIMPLE hides the memory hierarchy, LAST exposes it by representing register loads and memory stores, as well as representing array and structure references as a series of arithmetic operations. In other words, the LAST IR is very close to assembly language: in most cases there is a one-to-one correspondence between LAST statements and assembly language instructions. At the same time, however, high-level constructs such as while loops are still represented, in order to maintain the structured representation and simplify access to flow-information stored in SIMPLE(explained in Section 3.2.1). Figure 3.3 illustrates the translation of the SIMPLE tree in Figure 3.2 to its LAST counterpart, and Figure 3.4 shows the C code (on the left hand side) for SIMPLE, and the corresponding LAST pseudo assembly code (on the right hand side). Essentially, variables c and d are loaded from memory into registers, multiplied, and the result placed in a register temp1. The variable b is then loaded, added to temp1, moved into a register and then stored in the memory location reserved for a.

Figure 3.3: SIMPLE to LAST Transformation

#### 3.1.3 Code Generation Phase

The final and simplest of phases in McCAT is code generation. Since the focus of research for McCAT is on IR transformations, rather than generating object code, the compiler

```

REG(d)(0) \leftarrow LOAD(Int) - MEM(d)

REG(c)(0) \leftarrow LOAD(Int) - MEM(c)

REG(c)(0) \leftarrow LOAD(Int) - MEM(c)

REG(temp1) := REG(c) * REG(d)

REG(b)(0) \leftarrow LOAD(Int) - MEM(b)

REG(a) := REG(temp1) + REG(b)

MEM(a)(0) \leftarrow STORE(Int) - C REG(a)

```

Figure 3.4: Code for SIMPLE to LAST Transformation

produces assembly code, and uses existing simulators/assemblers for running the input programs.

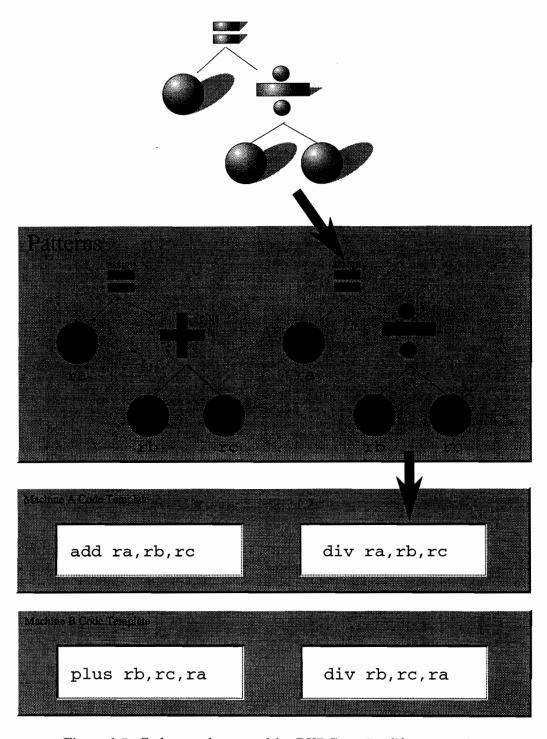

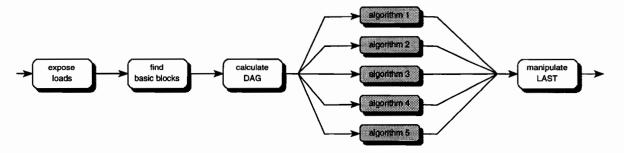

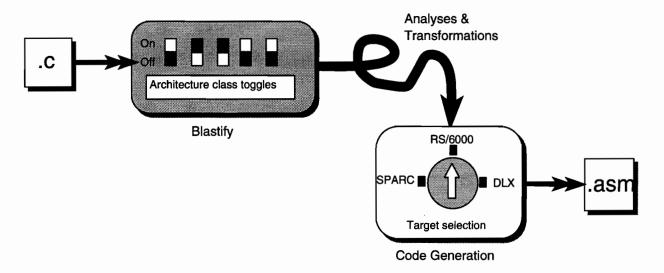

The design philosophy of LAST is to push as much complexity into the IR, to use transformations on LAST to perform optimizations such as instruction scheduling and to make the code generation (the actual printing of assembly instruction to a file) as trivial as possible. This is accomplished by a code-generator generator called Burg[FHP92b], which allows simple templates of assembly code to be written for various LAST constructs. Burg constructs a tree traversal routine that traverses LAST, and when it finds a group of LAST nodes that match a particular pattern, the corresponding code template is printed. No complicated analyses or transformations are performed within the code generator, and so retargeting is greatly simplified as most the work consists of only rewriting simple templates for each new machine targeted. Figure 3.5 gives an example of the overall strategy. Blastify generates a LAST subtree corresponding to a division statement x = y / z, which the Burg-generated code generator matches with one of its patterns. In the example there are only two patterns to match: addition and division. Once the match is made, the appropriate code template is used to generate assembly code. Templates for two machines (machine A and machine B) are shown, with machine A's template being used (so div ra,rb,rc is generated).

#### 3.2 Overview of LAST

McCAT was constructed utilizing the GNU C compiler. The parsing phase was kept, but its entire back-end, including the analysis, transformation and code generation phases, was removed. The GCC back-end utilizes RTL [Sta92], but the code was judged too complicated to modify. One major contributor to the GNU C and GNU C++ compilers considers the "common back-end of these compilers very difficult to comprehend and/or modify" [Gui94]. As a result, Simple was developed and serves its function well as a structured IR for high-level analysis.

However, Simple is too abstract a representation for low-level transformations such as instruction scheduling and register allocation—high-level constructs such as arrays and

Figure 3.5: Code templates used by BURG to simplify retargeting

structures still exist. As a result, another low-level IR was required, and so the mandate for LAST was born.

#### 3.2.1 Design Mandate for LAST

Based on the desire to utilize high-level flow information (gathered at the Simple level) to aggressively exploit fine-grain parallelism in target machine architectures, the following six criteria were developed to guide the design and implementation of Last.

Support for structured analysis: A structured, compositional representation, where control flow is regular and explicit (ie no goto statements) simplifies analysis tremendously, as control structures can be analyzed compositionally. For instance, if analyzing a while loop, only the conditional expression and body of the loop under analysis are inspected; surrounding control constructs are disregarded.

A compositional representation enables program analysis to be abstracted to a simple model, and thus implemented in a straight forward fashion, and allows for the use of automated tools. Also, by maintaining the program structure, it becomes easy to find and transform groups of loop nests. Our register allocation algorithm, based on hierarchical cyclic interval graphs [HGAM92], uses this compositional property.

The critic might point out that goto statements can and do appear in popular programs, particularly in interpreters and automatically-generated code. An unstructured program must therefore be converted into an equivalent structured program, an achievable target [WO75, Bak77, Amm92]. Currently, the McCAT compiler has a restructuring module that converts all programs with goto statements into equivalent structured programs [EH94].<sup>4</sup>

Support for pervasive analysis: Last is only one in a family of intermediate representations. Each IR has its own advantages. For example, Simple, the high-level representation, is suitable for points-to analysis. Such high-level information is crucial to determining available fine-grain parallelism, and is needed at the lower-level representation Last. Therefore, propagation of information from the higher IRs to Last was an essential design criterion.

Support for load/store machines: Reduced instruction set computer (RISC) architectures are perceived as having a significant performance advantage over complex instruction set computer (CISC) architectures [DS90, HP90]. One of the distinctive features of a RISC architecture is that it is a load/store architecture, that is, all memory references are through explicit stores(loads) to(from) memory, and arithmetic operations take only register operands.

<sup>&</sup>lt;sup>4</sup>With the exception of setjmp and longjmp, which are currently unsupported.

Considering the gravitation of high-performance computer systems towards RISC architectures, LAST was required to support them, and thus load/store architectures.

Expose opportunities for transformations: Obviously, since McCAT is an optimizing compiler, it should aggressively seek to improve the efficiency of generated code. As a corollary, LAST should expose all opportunities for code and performance-improving transformations, such as exposing the use of all registers to the register allocator, filling branch delay slots, removing induction variables (plus strength reduction), and exposing a function's prologue and epilogue to the instruction scheduler. This means that LAST must be able to represent individual assembly level instructions.

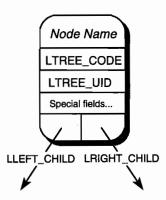

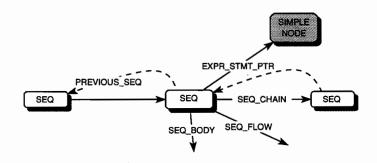

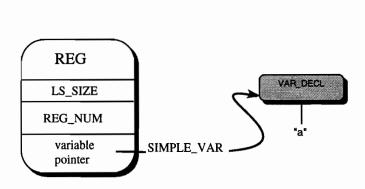

Support simplistic code generators: Since McCAT is a research and pedagogical tool, it has a mandate to investigate a wide variety of real and experimental architectures. McCAT therefore needs to be highly retargetable, and so should require minimal intelligence of its code generation module. That is, as much complexity as possible should be embedded in the non-machine specific intermediate representation, and the IR should be generic enough for load/store architectures so that the compiler is easily retargeted between such machines.