# System-Level Test Interface Considerations for High Speed Interconnect

Man Wah Chiang

Department of Electrical and Computer Engineering

McGill University, Montreal

February 2004

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering

© Man Wah Chiang 2004

Library and Archives Canada

hives Canada Archives Canada

Published Heritage Branch Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Your file Votre référence ISBN: 0-612-98519-9 Our file Notre référence ISBN: 0-612-98519-9

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **Abstract**

Although modern system operating speed and performance largely benefit by the advanced technology, designing the system level test circuitry is still a great challenge. Traditional ad-hoc or informal design practice is not adequate, and an early well planned testing scheme is required to meet the concerns raised by the increasing size and complexity of the system. Moreover, many high speed communication issues including BER testing, jitter measurement and jitter injection also need to be considered due to the increasing need for newly developed high speed interconnect architectures such as PCI Express, Fibre Channel and InfiniBand. In this thesis, a disciplined test interface design methodology based on the layered model is presented in order to ease the test circuitry design by maximizing the flexibility and reusability. Instead of setting up a completely new test access channel, test circuitry is integrated into each functional layer of the system to reuse the existing communication mechanisms. InfiniBand and Sensor Networks are used to demonstrate the proposed design methodology and a new BER testing scheme is also discussed.

## Résumé

Bien que la vitesse opérative et le fonctionnement du système moderne sont en grande mesure améliore par la technologie, concevoir un niveau système d'examen de circuit est tout de même un grand défi. La conception traditionnelle et familière n'est pas satisfaisante. Ainsi, un meilleur plan doit ètre élaboré pour rencontrer l'augmentation de grandeur et de complexité du système. De plus, il faut considérer les questions de haute vitesse comme l'examen BER, la mesure frousse et l'injection frousse à cause de leur architecture interconnective, par exemple PCI Express, Fibre Channel et InfiniBand. Dans cette thèse, une méthodologie pour tester, interface basé sur le modèle, est presenté pour faciliter le dessein de la conception de circuits visant à améliorer leur flexibilitéet et réutilisabilité. Au lieu d'installer un canal complètement nouveau, l'examen de circuit est integer à la couche fonctionnelle du système, ce qui permet de réutiliser les mécanismes existants de communication. InfiniBand et les réseaux de sonde sont employés pour démontrer la méthodologie de conception proposée. Finalement, un plan pour tester le nouveau BER est aussi discuté.

## **Acknowledgements**

Lots of people have helped me throughout my thesis work and I would like to acknowledge them for their support and assistance.

Firstly, I would like to thank my supervisor, Professor Zeljko Zilic for his great support and guidance throughout my thesis work. His great academic knowledge and industrial experiences provide a good vision in the research topics. Without his patience and suggestions, it is impossible to complete this work. He also provided an excellent research environment including financial aid, up-to-date software which allowed me to focus on my research and under his great supervising, I really learn a lot of things that will definitely benefit in my future career development.

Secondly, I would like to thank to my family who supported me throughout my studies and had patience to endure my second scholastic stay. I really thanks for their support and understanding of my decision of quitting the job and continuing my master studies.

Lastly, I would like to thank my colleagues Yongquan Fan for his assistance in the BER testing area and all my friends in the Macs Lab who bring me the enjoyment

and happiness during my master studies in McGill.

# **Table of Contents**

| Abstra  | ct                                                             |

|---------|----------------------------------------------------------------|

| Résum   | éi                                                             |

| Acknov  | vledgementsii                                                  |

| Table o | f Contentsv                                                    |

| List of | Figuresix                                                      |

| List of | Tablesxi                                                       |

| Chapte  | r 1 - Introduction 1                                           |

| 1.1     | Overview                                                       |

| 1.2     | Motivations                                                    |

| 1.3     | Thesis Outline                                                 |

| Chapte  | er 2 - Background                                              |

| 2.1     | Overview                                                       |

| 2.2     | Peripheral Component Interconnect (PCI)                        |

| 2.3     | AMBA                                                           |

| 2.4     | InfiniBand                                                     |

| Chapte  | er 3 - Layered Approach to Designing System Test Interfaces 15 |

| 3.1     | Overview                                                       |

| 3.2     | Previous Test Architecture                                     |

| 3.2     | 2.1 IEEE 1149.5                                                |

| 3.2.2       | PCI                                                  | 17        |

|-------------|------------------------------------------------------|-----------|

| 3.2.3       | MTM-Bus                                              | 18        |

| 3.2.4       | P1500                                                | 20        |

| 3.2.5       | AMBA Test Interface                                  | 24        |

| 3.3 Lay     | yered Methodology                                    | 27        |

| 3.3.1       | Case Study: InfiniBand                               | 28        |

| 3.3.1.      | 1 IBA Test Architecture Considerations               | 29        |

| 3.3.1.      | 2 The TCN Design                                     | 33        |

| 3.3         | .1.2.1 Channel Adapter                               | 34        |

| 3.3         | .1.2.2 Test Controller                               | 34        |

| 3.3         | .1.2.3 Memory                                        | 35        |

| 3.3         | .1.2.4 Single Node Testing Sequences                 | 36        |

| 3.3         | .1.2.5 Multiple Node Testing                         | 37        |

| 3.4 Ex      | perimental Results                                   | 38        |

| 3.4.1       | IBA Test Interface Based on MTM-Bus Architecture     | 39        |

| 3.4.2       | Comparison                                           | 41        |

| 3.5 Cor     | nclusions                                            | 42        |

| Chapter 4 - | Extended Usage of the Test Interface Based on Layere | ed Design |

| Approach    |                                                      | 43        |

| 4.1 Ove     | erview                                               | 43        |

| 4.2 Ext     | ended Usage of the Test Interface                    | 44        |

| 4.2.1       | IEEE 1532                                            | 44        |

| 4.2.2       | Modifications of the IBA Test Interface              | 45        |

| 4.2.3       | Experimental Results                                 | 47        |

| 4.3 App       | lication to the Distributed Measurement System          | 48 |

|---------------|---------------------------------------------------------|----|

| 4.3.1         | The Distributed System                                  | 48 |

| 4.3.2         | Sensor Networks                                         | 50 |

| 4.3.3         | System-Level Testing Considerations for Sensor Networks | 52 |

| 4.3.4         | Case Studies: Sensor Node based on MSP430 Architecture  | 56 |

| 4.3.4.1       | Test Interface Module                                   | 58 |

| 4.3.          | 4.1.1 JTAG Control by CPLD                              | 58 |

| 4.3.          | 4.1.2 JTAG Control by Microcontroller                   | 59 |

| 4.4 Con       | clusions                                                | 62 |

| Chapter 5 - S | ystems Performance and Measurements                     | 63 |

| 5.1 Ove       | rview                                                   | 63 |

| 5.2 Con       | nmunication System Performance Indicators               | 64 |

| 5.2.1         | Signal-to-Noise Ratio (SNR)                             | 64 |

| 5.2.2         | Bite Error Rate (BER)                                   | 64 |

| 5.2.3         | Jitter                                                  | 65 |

| 5.2.4         | Eye Diagram                                             | 68 |

| 5.3 Jitte     | er Tolerance Test Methodologies                         | 70 |

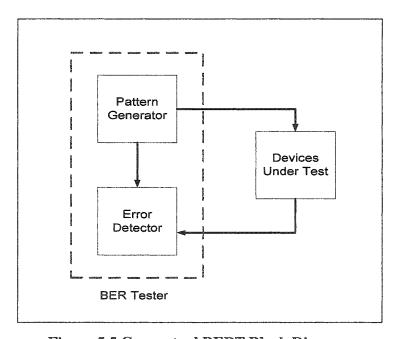

| 5.3.1         | Bit Error Rate Tester (BERT)                            | 70 |

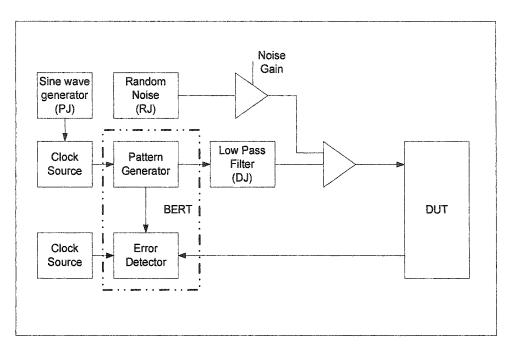

| 5.3.2         | Jitter Source Injection                                 | 71 |

| 5.3.3         | Jitter Test Methodologies                               | 73 |

| 5.3.3.1       | Direct TJ Measurement                                   | 73 |

| 5.3.3.2       | 2 Oscilloscope Measurement                              | 73 |

| 5.3.3.3       | BERT Scan                                               | 74 |

| 5.4 Nev       | v Proposal for BER Testing                              | 75 |

|      | 5.4.1      | Existing Industrial Solutions     | . 75 |

|------|------------|-----------------------------------|------|

|      | 5.4.2      | New FPGA-based BER Testing Scheme | . 76 |

|      | 5.4.3      | Performance                       | . 77 |

|      | 5.4.3.1    | FPGA-based BERT Design            | . 78 |

|      | 5.4.3.2    | Baseband Transmission Testing     | . 82 |

|      | 5.4.3.3    | Comparison                        | . 84 |

| 5.:  | 5 Nev      | Proposal for Jitter Measurement   | . 86 |

| 5.   | 6 Con      | clusions                          | . 88 |

| Cha  | pter 6 - C | Conclusions                       | . 89 |

| 6.   | 1 Con      | clusions                          | . 89 |

| 6.   | 2 Futu     | are Work                          | . 90 |

| Refe | rences     |                                   | . 91 |

# **List of Figures**

| Figure 1.1 Silicon Manufacturing and Test Cost Trends Predicted in      |

|-------------------------------------------------------------------------|

| 2001 by ITRS [1]                                                        |

| Figure 1.2 A Typical Measurement System                                 |

| Figure 2.1 Block Diagram of a Typical Computer System                   |

| Figure 2.2 PCI System Block Diagram                                     |

| Figure 2.3 Basic SoC System Based on AMBA Bus 10                        |

| Figure 2.4 Block Diagram of the AHB11                                   |

| Figure 2.5 Block Diagram of the InfiniBand Network 12                   |

| Figure 2.6 Consumer Queuing Model 13                                    |

| Figure 2.7 IBA Communication Stack 14                                   |

| Figure 3.1 Block Diagram of a Typical Boundary Scan Test Circuitry . 16 |

| Figure 3.2 Block Diagram of the MTM-Bus Architecture 19                 |

| Figure 3.3 Block Diagram of the MTM-Bus Connections                     |

| Figure 3.4 Block Diagram of P1500 21                                    |

| Figure 3.5 P1500 Serial Interface Layer (SIL) Architecture 22           |

| Figure 3.6 Core Test Wrapper23                                          |

| Figure 3.7 Block Diagram of the Typical AMBA-Based SoC 25               |

| Figure 3.8 Sequence of Events of the Write Operation26                  |

| Figure 3.9 Typical IBA Network                                        |

|-----------------------------------------------------------------------|

| Figure 3.10 IBA Layer Model 30                                        |

| Figure 3.11 IBA Network with Proposed Test Circuitry Design 32        |

| Figure 3.12 Block Diagram of the Test Control Node (TCN)              |

| Figure 3.13 Block Diagram of the Standard IBA Channel Adapter 34      |

| Figure 3.14 State-Machine of Test Controller 36                       |

| Figure 3.15 Timing Diagram of the Write and Read Test Operation 37    |

| Figure 3.16 Block Diagram of Our TCN Design with Single Target Node   |

|                                                                       |

| Figure 3.17 Block Diagram of the IBA test Interface Based on the MTM- |

| Bus Protocol 40                                                       |

| Figure 3.18 Logic Cells Utilizations of the TCN and MTM-Bus Interface |

|                                                                       |

| with Different System Size 42                                         |

|                                                                       |

| with Different System Size 42                                         |

| with Different System Size                                            |

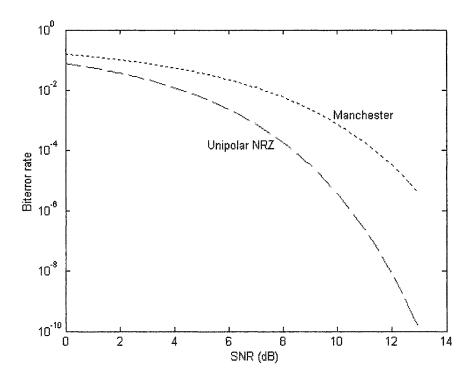

| Figure 5.1 BER vs SNR for Baseband Transmis            | sion of D                                            | ifferent |

|--------------------------------------------------------|------------------------------------------------------|----------|

| Encoding Schemes                                       | <b>૧૯૦૦ ૦૦ ૦૦ ૦૦ ૦૦ ૦૦ ૦૦</b> ૦ ૦૦ ૦૦ ૦૦             | 65       |

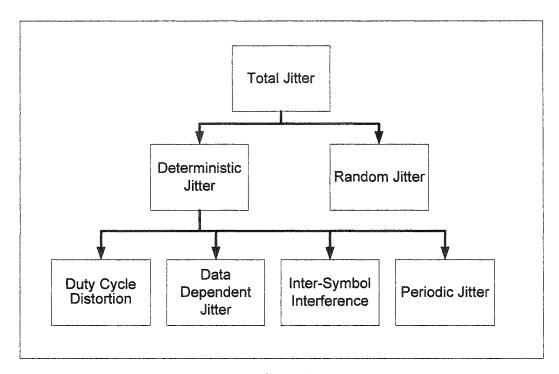

| Figure 5.2 Jitter Classification Diagram               | 0 2 6 5 8 8 8 8 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0        | 66       |

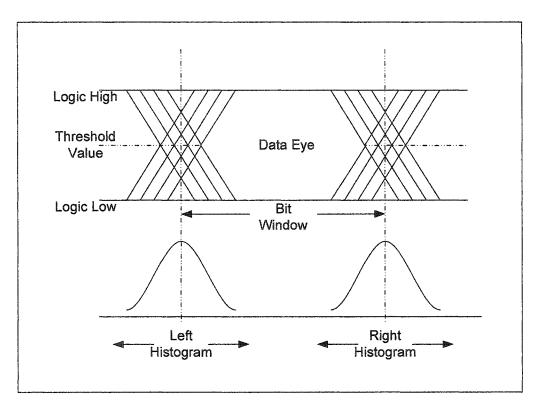

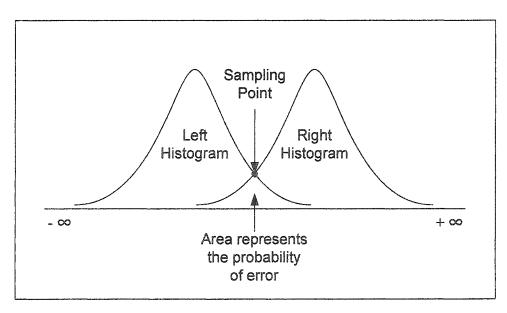

| Figure 5.3 Eye Diagram                                 | 000000000000000000000000000000000000000              | 69       |

| Figure 5.4 PDF of Jitter Error                         | 2 4 3 4 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2              | 69       |

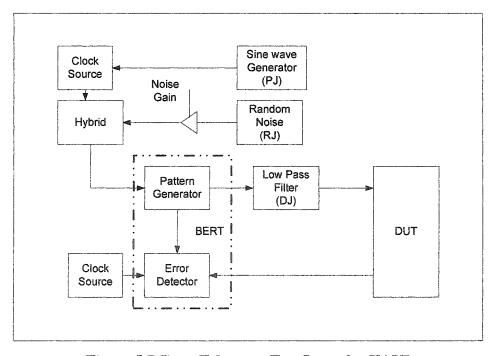

| Figure 5.5 Conceptual BERT Block Diagram               | @ 8 © 8 <b>0 0 0 0 0</b> 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 70       |

| Figure 5.6 Jitter Tolerance Test Setup for Fibre Chann | el                                                   | 72       |

| Figure 5.7 Jitter Tolerance Test Setup for XAUI        | 9 6 8 8 3 6 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8            | 72       |

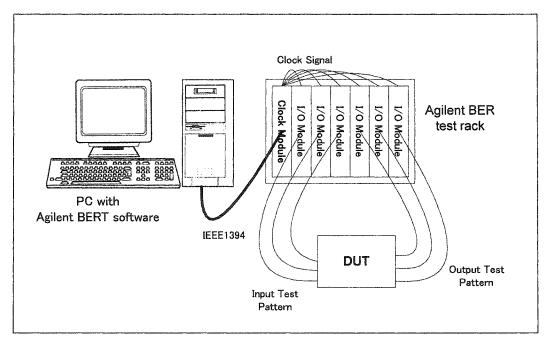

| Figure 5.8 Agilent BERT                                | ********                                             | 76       |

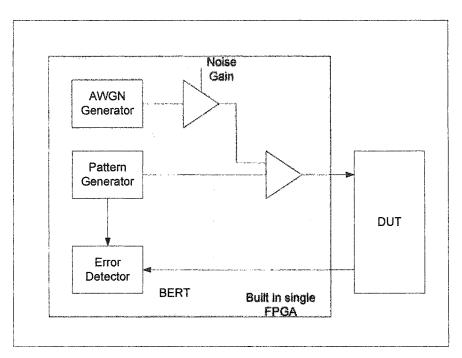

| Figure 5.9 Yongquan Fan's proposed BERT testing sch    | eme                                                  | 77       |

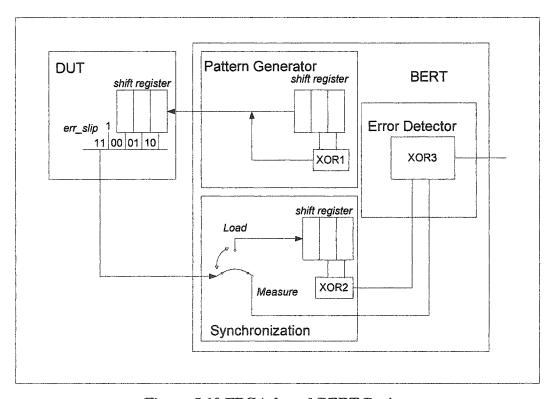

| Figure 5.10 FPGA-based BERT Design                     | ************                                         | 78       |

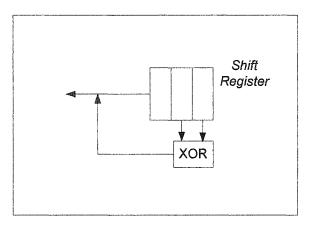

| Figure 5.11 Pattern Generator                          | ****                                                 | 79       |

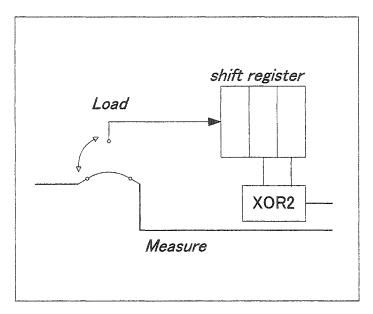

| Figure 5.12 Test Synchronization Circuit               | 88988888888888888                                    | 80       |

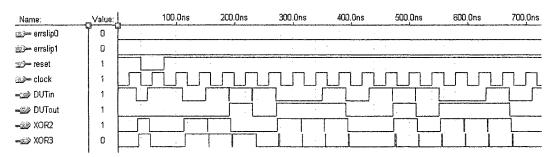

| Figure 5.13 Simulation Waveform of the BERT Design     | 000000000000000000000000000000000000000              | 82       |

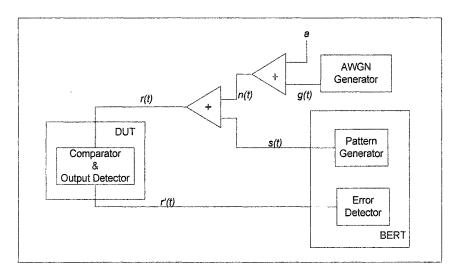

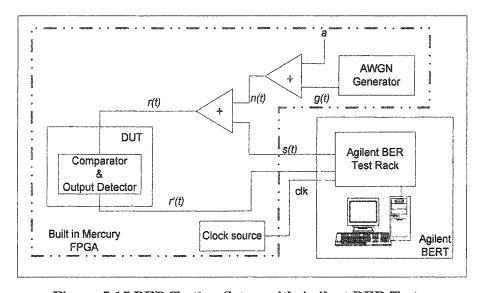

| Figure 5.14 BER Testing Setup                          | 000000000000000000000000000000000000000              | 82       |

| Figure 5.15 BER Testing Setup with Agilent BER Teste   | I                                                    | 84       |

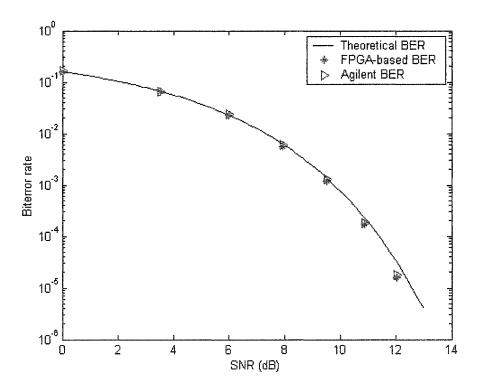

| Figure 5.16 Plot of Measured BER and Theoretical E     | SER for Ba                                           | ıseband  |

| Transmission                                           | && & & & & & & & & & & & & & & & & & &               | 85       |

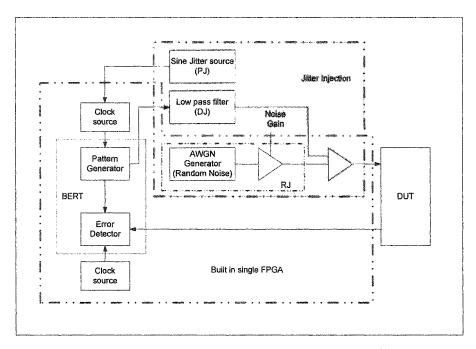

| Figure 5.17 Proposed Jitter Test Setup for Fibre Chann | le1                                                  | 87       |

# **List of Tables**

| Table 3.1 Test Control Signals during Test Mode 26                    |

|-----------------------------------------------------------------------|

| Table 3.2 TCN Control Signals during Test Mode 35                     |

| Table 3.3 Performance Results of TCN with Different Programmable      |

| Logic Architectures 39                                                |

| Table 3.4 Performance Results of IBA Test interface Based on MTM-Bus  |

| with a Single End Node40                                              |

| Table 4.1 Control Signals during Test Mode and Program Mode 46        |

| Table 4.2 Performance Results of modified TCN with Different          |

| Programmable Logic Architectures 47                                   |

| Table 5.1 Jitter Specifications of Different Communication Systems 68 |

| Table 5.2 Control Signals for DUT 81                                  |

| Table 5.3 BER measurement result of FPGA-based BERT 84                |

| Table 5.4 BER measurement result of Agilent BERT 85                   |

## Chapter 1 - Introduction

### 1.1 Overview

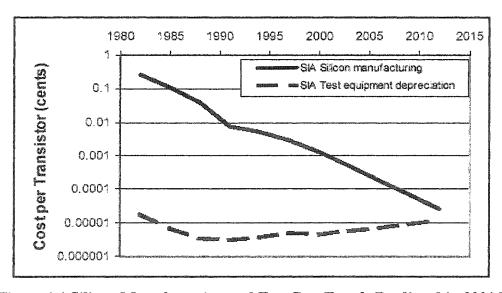

With the increasing complexity of modern systems, testing becomes a fairly difficult task. According to the International Technology Roadmap For Semiconductors (ITRS) [1] produced in 1997, the manufacturing cost is projected to be gradually decreasing due to the improved manufacturing processes and technologies. However, the testing cost does not benefit from the advanced technology and is projected to remain constant as shown in Figure 1.1. With this trend, testing cost will be eventually equal to the manufacturing cost in 2010 and will become a major factor in the overall production cost. As a result, a well-planned and highly efficient system testing scheme is needed to lower the testing cost.

Figure 1.1 Silicon Manufacturing and Test Cost Trends Predicted in 2001 by ITRS [1]

Testing cost is always proportional to the complexity and size of the system. With the help of the rapidly advancing manufacturing processes, the transistor density of the chip is gradually increased. Designers can now put the whole System on a Chip (SoC). In addition, IP cores are usually used in the SoC design which makes the system-level testing more difficult. In order to ease the integrations of the system, designers usually include the Design For Test (DFT) features in their board-level and chip-level designs. Since most of these testing features are non-functional during normal operation, a system-level access channel is needed for test control. Test data also needs to be imported and exported to the target modules.

Notice that by decreasing the size of the transistors, we lower the power dissipation and increase the system operating speed. This trend influences the interconnect architecture development and many new high bandwidth, low latency interconnect architectures have been proposed. Traditional interconnect schemes use a tri-state buffer which shares a common bus among different modules. Typical such example is Peripheral Component Interconnect (PCI), which is one of the most popular interconnect architectures used in the computer systems. Due to its slow transmission speed, PCI becomes the bottleneck of the modern computer systems. Several upgraded versions of PCI, such as PCIX or PCI Express are developed to provide the higher transmission speed by adapting the serial packet based communication mechanisms. The main advantage of these schemes is their backward compatibility with the existing PCI components. It maximizes the reuse and decreases the development cost. On the other hand, many new interconnect architecture standards are also developed (such as InfiniBand and Fiber Channel) to overcome the speed problem. Among all these standards, InfiniBand seems to be the most promising architecture. It is largely supported and developed by the major computer industrial vendors such as Sun, IBM etc. Moreover, its high transmission speed and flexibility are achieved by its networked nature. Existing testing standards such as JTAG and MTM-Bus become inadequate since they are mainly targeting the board level designs and are unsuitable for the coming complex networked systems.

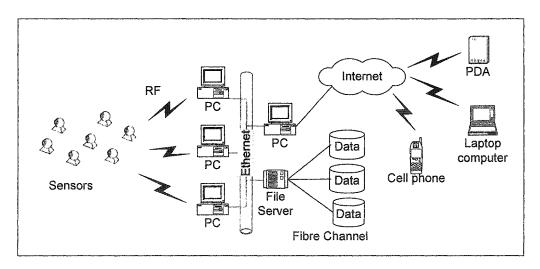

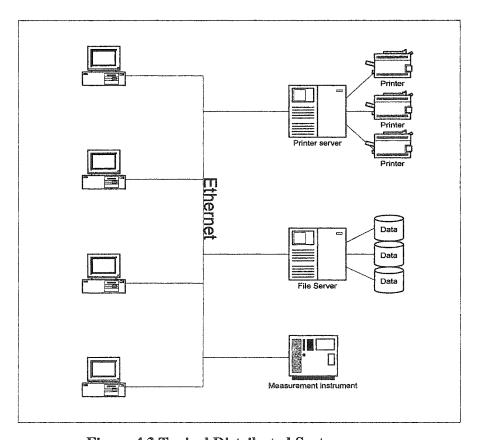

Figure 1.2 shows a typical distributed measurement system. Depending on the applications domain, various interconnect architectures are used. Sensors are placed in the remote area to capture the environmental data. Low power RF transmissions are used to communicate with the control center to preserve energy. Control center is formed by several personal computers (PC) for data analysis and measurement control. Each of them interconnects through the Ethernet in order to form a Local Area Network (LAN). Ethernet is used because of its great flexibility and low setup cost. In order to provide a fast and reliable data storage, a file server is included in the system. File server is made up by interconnecting several storage devices including tapes and harddisks through Fibre Channel. The LAN is also connected to the Internet to allow user obtaining the measurement data through the wireless mobile devices such as PDA handheld or cellular phone.

Figure 1.2 A Typical Measurement System

System-level testing is extremely difficult in such a system due to the existence of various interconnect architectures. Let us assume that a user is using the PDA handheld device and would like to test the sensors once the abnormal measured data is received. It is almost impossible to achieve this based on the existing

testing architectures. A new system-level testing scheme that can reuse the existing connection for test control is needed.

### 1.2 Motivations

As discussed above, the traditional interconnect architectures are starting to be replaced by the high speed point-to-point switching interconnect architectures. New system-level testing schemes need to be developed. As described in the 2001 ITRS, several major concerns are raised in the testing area as follows:

- 1. High frequency As the new interconnect standards provide both the high bandwidth and high transmission speed, test equipment with low skewing and low latency is needed.

- 2. Port count As the low-power gigabit IO becomes reality by the lower threshold voltage of CMOS, it enables massive integration into ASICs and SoCs. ASICs with more than 100 pairs of multi-gigabit transmitters and receivers are produced in 2002. Traditional rack model-based testing standards are not applicable due to the extensive wirings. New testing schemes should develop to address this issue.

- Testing Cost Both the high clock speed and large port count of the modern systems increase the testing cost due to the expensive test equipment and complicate test setup. An efficient and low cost testing scheme is needed.

- 4. Transparency As the complexity of the system increases, various interconnect architectures may be used within the same system. System-level testing is only possible if the existing communication channels are reused for the testing purposes. All the testing circuitries should be transparent to the system during the normal operations.

- 5. DFT consideration Currently, most of the high speed communication devices such as Serializers and Deserializers (SerDes) modules are equipped with the basic DFT features. They are based on the internal serial

- and parallel data loopback mechanism. Additional DFT components such as build-in pseudo random bit sequence generator and error detector are needed to increase defect coverage.

- 6. Jitter As the point-to-point switching mechanism is adapted in the new interconnect standards, some of the high speed communication concerns such as jitter measurement and jitter injection also need to be considered.

- a. Jitter Measurement Existing jitter measurement instruments still fail to meet the noise floor, analog bandwidth and the test speed requirements of the high performance systems. On-chip DFT needs to be developed to address these issues and lower the testing cost.

- b. Jitter Injection In order to accomplish the jitter measurement, well controlled jitter should be deliberately added to the data streams. Currently, there is no integrated ATE solution in this area due to the high speed requirements.

In this thesis, we addressed some of the above issues by introducing layered design methodology for the system level test interfaces. By doing so, a low cost, high flexibility and low latency test interfaces can be achieved. Moreover, a new FPGA-based BER testing scheme is introduced and used for jitter measurement.

## 1.3 Thesis Outline

In Chapter 2, the background of the system testing is described. Both new and old system interconnect architectures such as PCI, PCI-X, PCI Express, AMBA and InfiniBand will be introduced.

Chapter 3 is focused on applying the layered design methodology for designing the system-level test interface. Existing test architectures such as JTAG, MTM-Bus and P1500 are introduced. Their main advantages and disadvantages are also discussed. The basic concept of layered approach is presented and demonstrated by applying it to the InfiniBand architecture.

In Chapter 4, the proposed test interface is studied and its usage is expanded in other areas such as programming and instrumentations. In order to show the generalization of the new design approach, a distributed system such as sensor network is discussed. The possibility of applying the layered approach to design the system-level test interface to the sensor networks is also examined.

In Chapter 5, the communication issues that are raised by the new interconnect architecture are described. General BER measurement, jitter measurement and jitter injection are discussed. A new FPGA-based BER testing scheme is introduced and we validate its performance by performing a baseband transmission test. Based on this new BER testing scheme, a low cost and efficient jitter measurement test setup is proposed. The necessary modifications of the FPGA-based BERT [57] to facilitate the jitter measurement are discussed.

Finally, the conclusions and the future work are presented in Chapter 6.

## Chapter 2 - Background

## 2.1 Overview

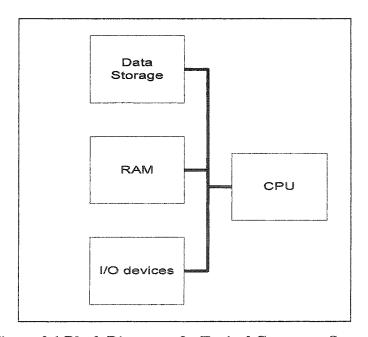

Before introducing layered approach for the system test interfaces, it is necessary to have an overview of the various system interconnect architectures. Figure 2.1 shows the conceptual block diagram of a computer system. It is made up of different functional modules that are interconnected by a common bus. In general, functional modules can be the Central Processor Units (CPU), Random Access memory (RAM) or I/O devices.

Figure 2.1 Block Diagram of a Typical Computer System

In the past, all these functional modules were the major limiting factor for the system performance. As now the CPUs have entered the gigaHertz era, the

bottleneck of the system performance has shifted to the interconnect. Industrial vendors have started optimizing the performance of the system by researching new interconnect architectures. Recently, many new interconnect architectures have been developed. Some are based on the existing widely accepted PCI architecture such as PCI-X and PCI-Express. On the other hand, some interconnects are based on the network architecture and use the point-to-point switching connection. By doing so, a direct and private communication channel can be established between the two connected devices and data can be transmitted at the maximum speed.

In this chapter, several popular system interconnect standards such as PCI, PCI-X, PCI Express, AMBA and InfiniBand will be introduced in Section 2.2, 2.3, 2.4 and 2.5 accordingly.

## 2.2 Peripheral Component Interconnect (PCI)

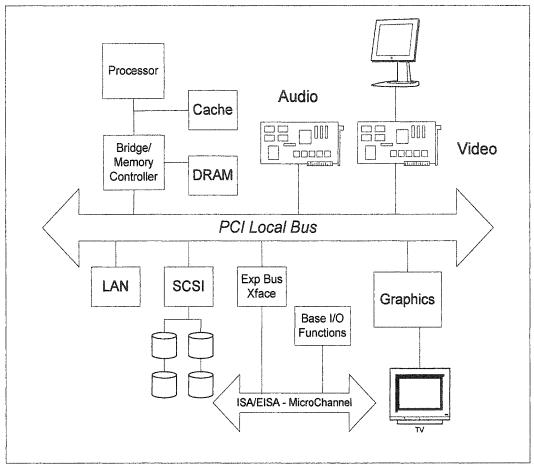

Since it was first time released by Intel in 1991, PCI [2] has evolved rapidly to replace the Industrial Standard Architecture (ISA) bus and become the most commonly used interconnect in the personal computer systems. Unlike the slow ISA bus, PCI is a synchronized parallel bus architecture which provides a maximum 33MHz transfer rate over a multiplexed 32-bit or 64-bit width data path. Figure 2.2 shows the block diagram of the PCI system. PCI bus provides a direct memory access to the connected devices and a bridge is used to connect the processor.

Figure 2.2 PCI System Block Diagram

Although PCI was first introduced in 1991, it did not gain the popularity until the arrival of the Windows 95 in 1995. This is mainly due to the fact that the new operating system supports the Plug and Play (PnP) feature that was standardized by Intel and implemented in PCI. With this feature, new hardware can be recognized and configured to work once it is inserted into the computer. In order to ensure that every PCI card is compatible with all PCI-enabled systems, PCI Special Interest Group (PCI-SIG) was formed to set, manage and develop the standard of the PCI bus.

In order to facilitate high computing power, several high speed versions of PCI standards were proposed. One of them is called PCI-X [3] and provides a maximum speed up to 4.3 gigabytes per second. Another new standard is PCI-Express [4] which uses the serial interconnect technology to offer a 250 megabyte

per second per lane in each direction. It provides a total bandwidth of 16 gigabytes per second for a 32-lane configuration.

## **2.3 AMBA**

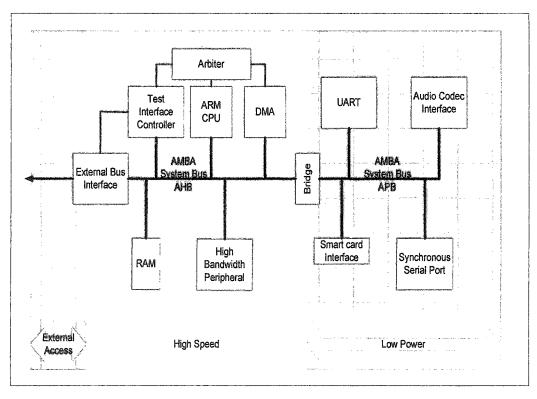

Advanced Microcontroller Bus Architecture (AMBA) [5] is an open standard, onchip bus specification that details the modular interconnect in a System-on-Chip (SoC). As shown in Figure 2.3l, an AMBA based SoC system includes the high performance system bus – AHB and the low power peripheral bus – APB. AHB is responsible for connecting the processor, memory modules or any other devices that require high bandwidth usage. On the other hand, APB is responsible for all other devices which are less bandwidth demanding. APB's protocol is a simplified version of AHB and both can be communicated through a bridge.

Figure 2.3 Basic SoC System Based on AMBA Bus

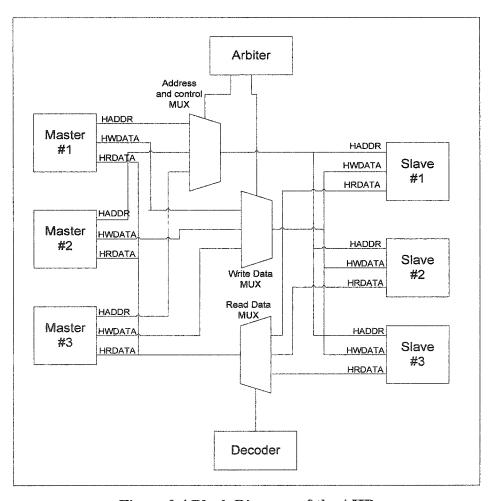

Unlike the traditional tri-state buffer bus architecture, AMBA uses the multiplexer

to gain the control of the bus. The multiplexers eliminate the timing issues and perform a one-to-one transaction as shown in Figure 2.4. During each transaction, one master module requests the access to the bus by sending a request command to the Arbiter. Arbiter controls the access of the bus based on the priority of the bus master module. Once the bus access is granted, an isolated transmission path is formed between the master and target modules and data can be transferred to the target module. Split transactions and burst transfers are also supported in the AHB to provide high transfer rate. The main difference between AHB and APB is that multiple bus masters are supported in AHB. Bridge is the only master module presented in APB and no arbiter is needed. Moreover, some advanced features like pipelined operations are supported in AHB, but are not included in APB.

Figure 2.4 Block Diagram of the AHB

## 2.4 InfiniBand

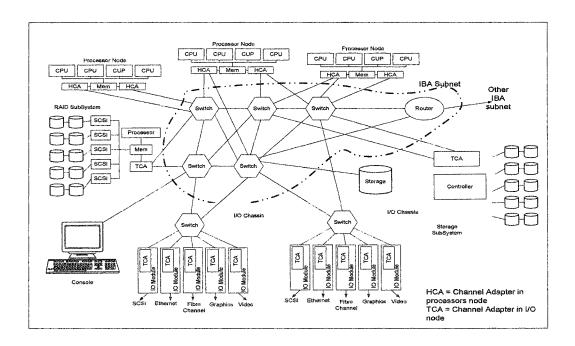

InfiniBand Architecture (IBA) [6] is a new interconnect architecture. It is jointly developed by major computer industrial vendors aiming to replace the PCI bus architecture. IBA defines a System Area Network (SAN) that connects the nodes. These nodes can be independent processors, I/O units or routers to another network through switches, as shown in Figure 2.5. Each node contains one or multiple Channel Adapters (CAs) that connect to the fabric.

Figure 2.5 Block Diagram of the InfiniBand Network

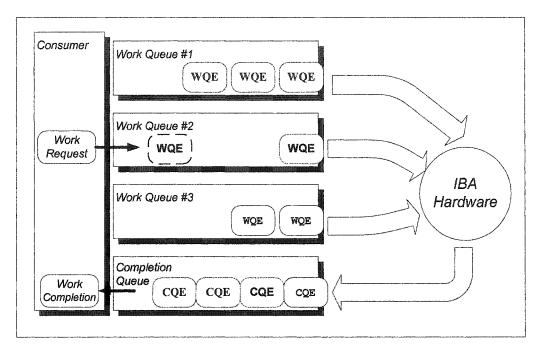

Queuing mechanism is used in IBA to initialize the communication between nodes. Consumers can queue up a set of hardware-executed instructions by creating a Work Queue Pair (QP), one for each send and receive operation, as shown in Figure 2.6. During normal operation, consumers submit a Work Request that causes the creation of an instruction called a Work Queue Element (WQE) to be placed on the work queue. Once the channel adapter executes and completes a WQE, a Completion Queue Element (CQE) is placed on the completion queue.

Figure 2.6 Consumer Queuing Model

Consumer posts the WQE to the QP and channel adapter interprets each WQE to perform the operation. InfiniBand supports three kinds of send queue operations, SEND, Remote Memory Access (RDMA) and Memory Binding.

- For a SEND operation, WQE specifies a block of memory in the consumer's memory space to send to the destination. In the destination, an already queued WQE will decide where to place the received data.

- For a RDMA operation, WQE also specifies the target memory address of the destination and the destination WQE is not involved. Three kinds of RDMA operations, RDMA-WRITE, RDMA-READ and ATOMIC are supported by IBA:

- o In the RDMA-WRITE operation, data is transferred from the consumer's memory to the destination consumer's memory address.

- o In the RDMA-READ operation, data is transferred from the target consumer's memory address to the local consumer memory.

- o ATOMIC operation allows performing a read operation to a remote 64-bit memory location. The target node returns the read value and updates the remote memory contents.

• For a Memory Binding operation, consumer defines the portion of the registered memory that is shared with the target nodes and allows the remote nodes to perform the RDMA operations. This information will pass through the network as the form of memory key which is called R\_KEYS.

There is only one receive queue operation in IBA, called RECEIVE WQE. It is used to specify the memory location that the received data should be placed in.

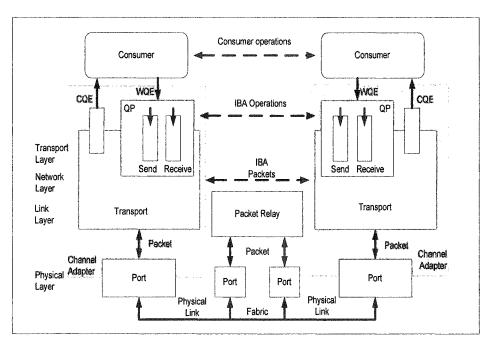

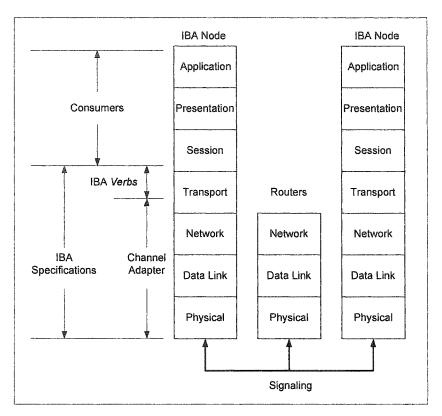

Figure 2.7 IBA Communication Stack

Figure 2.7 shows the IBA communication protocol stack. IBA *Verbs* are specified to describe the service interface between the channel adapter and the operating system. Instead of specifying an API, IBA *Verbs* describe the parameters necessary to configure, manage and operate the channel adapter. It permits the OS vendors to define appropriate APIs that take advantage of the architecture. This network system approach provides a high bandwidth interconnect that can be easily upgraded or expanded by adding the nodes to the network, rather than rebuilding the whole system.

# Chapter 3 - Layered Approach to Designing System Test Interfaces

## 3.1 Overview

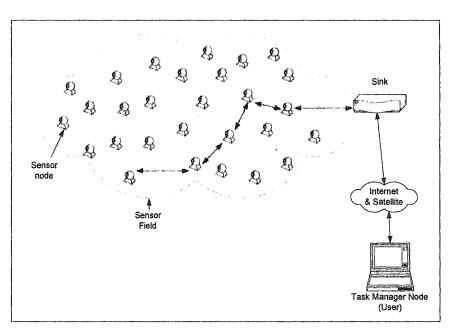

The difficulty of designing the system level test circuitry continues to rise with the increasing size and complexity of the system. An early well-planned test interface becomes essential to the needs of future complex systems on a chip (SoCs) and even distributed systems such as sensor networks [7], and home automation, including HomePNA [8]. In such systems, incorporating testing subsystems involves considerable design complexity.

In this chapter we propose a layered approach to the test interface design. Due to its flexibility and reusability, a wide class of systems can benefit from this approach. In Section 3.2, the evolution to layered test interfaces is presented by studying both advantages and disadvantages of several existing test architectures, including Boundary Scan Test techniques (JTAG), MTM-Bus, P1500, PCI test architecture and AMBA test architecture. The layered test methodology is introduced in Section 3.3. In Section 3.4, we illustrate the proposed method in detail by constructing the system test circuits for InfiniBand Architecture. We validate the proposed method by comparing it with the JTAG in Section 3.5 and conclude this chapter in Section 3.6.

## 3.2 Previous Test Architecture

Several standards for system test architecture have been developed. The most widely known is the IEEE 1149.5. In this section, some of the existing test architectures are presented and their advantages and disadvantages are examined.

### 3.2.1 IEEE 1149.5

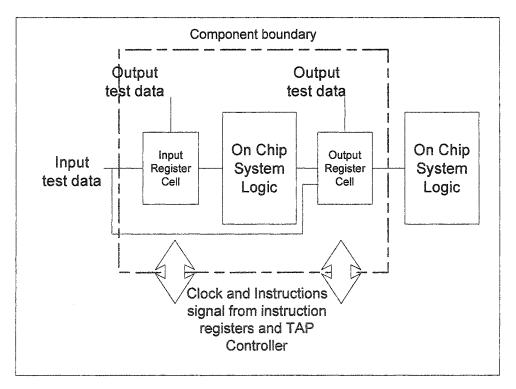

IEEE Boundary Scan Test (JTAG) standard [9] is one of the early, well-defined system testing standards. It is defined primarily for testing interconnect between integrated circuits once they have been placed onto a printed circuit board. In this technique, all the modules under test are serially connected to form a daisy chain through the register cells, as shown in Figure 3.1.

Figure 3.1 Block Diagram of a Typical Boundary Scan Test Circuitry

The register cells, which are controlled by Test Access Port (TAP) controller,

isolate the target module from the rest of the system and provide the external interface to input the test vectors and receive the test results. By controlling the following four pins: Test Clock (TCK), Test Mode Select (TMS), Test Data In (TDI), and Test Data Out (TDO), data is allowed to propagate through the device when the registered cells are inactive. During test mode, test data is shifted in or out of each module serially through the TDI and TDO of the register cell. Finally, Instruction Registers (IR) is working in conjunction with the TAP controller to perform the requested type of test.

The main advantages of JTAG are wide industry support and a good test and diagnostics at board level. It has also been used for many applications beyond the intended test application such as in-circuit programming and instrumentation. However, there are several major pitfalls while applying JTAG to the large-scale system level testing [10].

First, the test speed decreases significantly as the system size increases because of its serial data bus architecture. Second, the flexibility of the system is limited by the daisy chain configuration. Any system changes will affect the test circuitry configuration and create the hardware and software changes. Third, to avoid limitations of a single scan chain, the test setup cost becomes high due to large amount of interconnect. As demonstrated in [10], a specially designed cabinet is needed to overcome the daisy chain configuration of a highly integrated switching system. The cost of the test setup is proportional to the size and the complexity of the system. Finally, the speed of the testing is two orders of magnitude smaller than its normal operation [10].

#### 3.2.2 PCI

In the PCI bus standard, the test circuitry was not included in the original specification. In a fairly ad-hoc manner, the JTAG interface presence on the bus has been instead added in the later specification. By employing this widely

accepted standard technique, the system test circuitry development becomes easy and increases the product compatibility. As we have discussed before, the main bottlenecks are the test speed and flexibility, which limit the capacity of the PCI system. At the moment, these disadvantages did not appear to be critical as PCI standard defined a single bus system with a limited number of components.

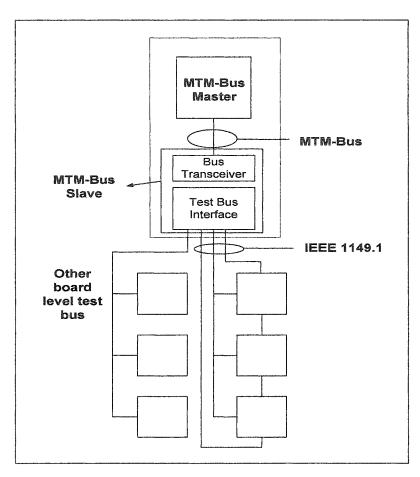

#### 3.2.3 MTM-Bus

In order to overcome the system level constrains of the IEEE 1149.1, IEEE standard 1149.5: Test and Maintenance Bus (MTM-Bus) Protocol [11] was developed. MTM-Bus is a solution to the integration of logic boards with different board-level test buses into a testable and maintainable subsystem. Due to the fact that design-for-test (DFT) features are included in the modern component design, a system-level access channel is necessary to enable users to initialize and control these features in the final product.

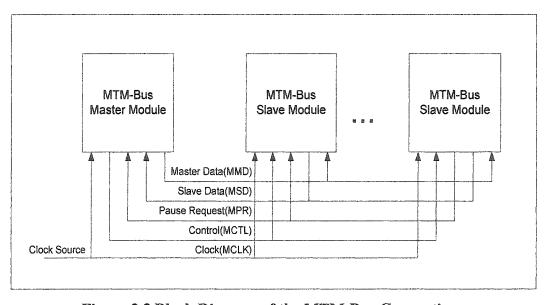

As shown in Figure 3.2, MTM-Bus consists of two main components: MTM-Bus Master Module and MTM-Bus Slave Module. MTM-Bus Master Module is responsible for controlling and initializing the testing process through communicating with the MTM-Bus Slave modules by the MTM-Bus. Each MTM-Bus Master can control up to 255 slave modules. MTM-Bus Slave module acts as a transceiver and coordinates various board-level testing architectures, as shown in Figure 3.2. A standard MTM- Bus is used to communicate the Master module with the Slave module. It consists of five signals which are Master Data (MMD), Slave Data (MSD), Pause Request (MPR), Control (MCTL) and Clock (MCLK) as shown in Figure 3.3.

Figure 3.2 Block Diagram of the MTM-Bus Architecture

Figure 3.3 Block Diagram of the MTM-Bus Connections

By applying the MTM-Bus to different systems such as "centralized design" system or "distributed design" system, it simplifies the system integration of different board-level test architectures. In the centralized system, users can reduce the development cost by pushing all the local board-level test control functions into the MTM-Bus Slave module. This also reduces the cost of the test interface in each module. While applying it to a distributed system, the MTM-Bus interface allows each module to be fully interchangeable as long as the self-test routines and test patterns are self-contained within the module.

However this standard is not widely adapted by the industry and no commercial products are available yet. As demonstrated in [12], authors intended to use this protocol in testing VMA-based large backplane bus-based systems, with many parallel data lines on each bus. Due to the lack of commercial MTM-Bus supported product, authors are forced to use other commercial Boundary Scan Interface Devices to provide the connection link between one or several scan chains and the common test bus.

### 3.2.4 P1500

P1500 [13] is a new standard which targets the core testing. A typical SoC system may include several IP cores such as CPU, DSP, Memory and ADC/DAC, provided by different industrial vendors. Two major design problems are as follows. First, to decrease both the system development time and production cost, designers need to optimize the usage of IP cores and eliminate any probable compatibility issues. Secondly, system-level testing becomes more difficult due to the increased system complexity. Test Standard for Embedded Core (P1500) is developed by IEEE in order to eliminate these testing issues in the SoC systems. As described in Section 3.2.1, Boundary Scan method achieved success in the board-level testing and the scan-in mechanism is borrowed to the embedded core testing by P1500.

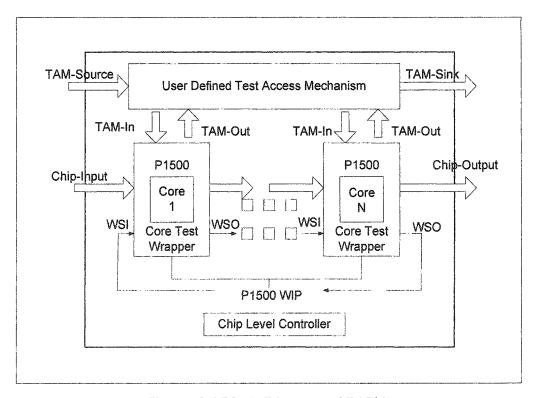

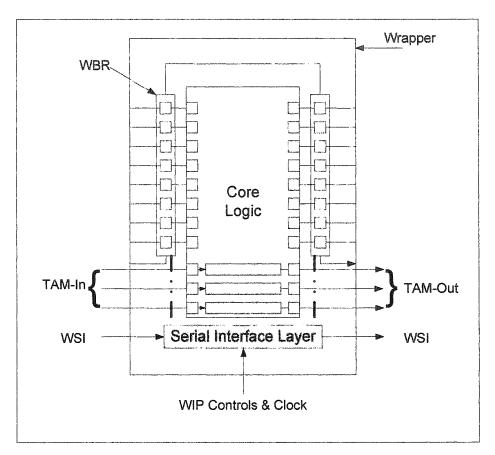

Figure 3.4 shows the block diagram of a SoC system equipped with P1500. P1500 provides a pseudo path that allows test data to scan in or out to different cores within the system. It defines the testing interface between the embedded core and the system chip, setup of the access and isolation mechanisms. As a result, it facilitates the test reuse and allows the P1500 compatible core to be tested in any SoC that supports P1500 without any hardware modifications.

In P1500, each core is wrapped by the standard P1500 Core test Wrapper. Test data can be imported from TAM-Source and transferred to the embedded cores through TAM-In in either serial or parallel manner. Once the test is completed, test result can be exported from TAM-Out and sent to TAM-Sink for analysis. P1500 can be divided into three parts, Core Test Wrapper, Chip Level Controller and User-Defined Access Mechanism.

Figure 3.4 Block Diagram of P1500

- Core Test Wrapper By applying the standard Core Test Wrapper to wrap all the input and output pins of the core, necessary test data and control signals can be easily transmitted to the cores.

- Chip Level Controller Instead of specifying the standard Chip Level Controller, P1500 provides freedom to specify it based on the designers' system requirements. It generates the control signals for the TAM and Wrapper Instruction Register inside the standard P1500 Core Test Wrapper in order to complete the testing process.

- User-Defined Test Access Mechanism (TAM) TAM is a user defined mechanism which transfers the test data to the target core through the TAM-In and exports the test result through TAM-Out.

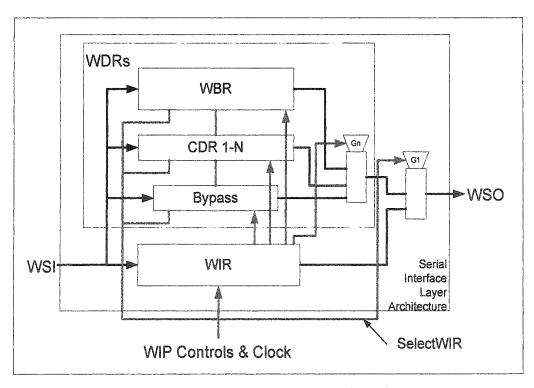

P1500 specifies the scan-in mechanism. Test data are scanned into the target core through the Wrapper Serial Input (WSI) port and scanned out to the next core through the Wrapper Serial Output (WSO) port as shown in Figure 3.5.

Figure 3.5 P1500 Serial Interface Layer (SIL) Architecture

Figure 3.6 Core Test Wrapper

During the testing process, Wrapper Interface Port (WIP) Control signals are sent to the Wrapper Instruction Register (WIR). It controls and updates the content of the Wrapper Boundary Register (WBR), Core Data Register (CDR) and Bypass Register. WBR is made up of the Wrapper Boundary Cell (WBC) which is applied to each I/O pin of the core. WBC provides the same function as the register cell in the IEEE 1149.1 Boundary Scan. It allows the test data to scan into or scan out of the target core. Bypass Register is a 1-bit register that allows the test data to bypass the core through the WSO.

Since the serial test data transmission provided by the SIL architecture may not meet the system requirements, P1500 also supports the parallel data transmission as shown in Figure 3.6. On top of the original SIL architecture (WSI, WSO), parallel Test Access Mechanism (TAM-In, TAM-Out) is added to the Core Test

Wrapper. This parallel interface allows multiple I/O pins can get access to the test data at the same time to decrease the testing time. Unfortunately, the implementation of this parallel TAM is not specified in P1500 and users need to define it based on their own systems. Recently, many studies were done in this area. Several parallel TAMs have already been proposed, including CSA-BUS [39] and TestRail [40].

Although P1500 provides an easy way for chip designers to test the target cores in the SoCs by scan of the test data, topological limitation is the main disadvantage due to its daisy chain configuration. Moreover, a system-level access path that allows users to initialize and control the P1500 is needed once the SoC is integrated into the system.

### 3.2.5 AMBA Test Interface

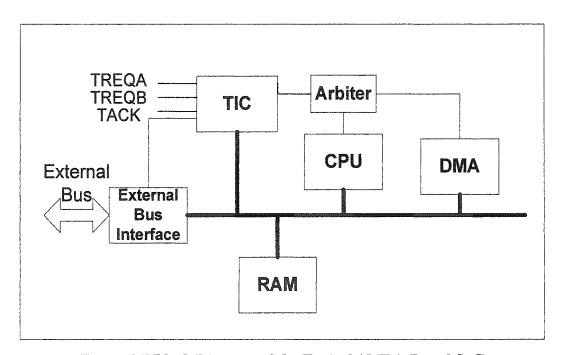

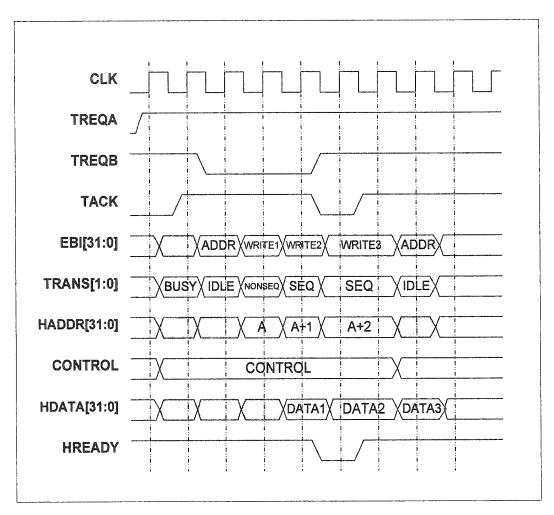

The challenges of designing the SoC test interface were addressed when ARM proposed a test methodology for its AMBA, instead of adapting the standard boundary scan (IEEE standard) technique. In AMBA bus architecture, testing is performed by a centralized scheme. As shown in Figure 3.7, a specialized Test Interface Controller (TIC) module is used for the modular testing and the external interface for test control and data inputs. TIC uses a minimal three wire handshake mechanism, consisting of Test Bus Request Input (TREQA), Test Control Input (TREQB) and Test Acknowledge (TACK) to control the test operation and the External Bus Interface (EBI) that is used to provide a 32-bit, high speed, parallel vector interface.

As shown in Figure 3.8, the TREQA and TREQB signals are pipelined in testing mode. They are used to encode the mode of operation (as shown in Table 3.1.) and indicate the type of vectors that will be applied in the next cycle. The bus access is granted by the arbiter to ensure that only a single module initializes one data transfer at a time. When TREQA is inserted during the normal system operation,

TIC requests the arbiter to grant the bus access to the External Bus Interface (EBI) and the system enters into the test mode. By inserting the TACK, the TIC gives the external indication of the test bus has been granted. The TIC initializes the special burst data transfer by broadcasting the start address and indicating the bus slave for a sequential transaction through the TRANS data line. The write data is sampled and driven on the AMBA bus (HDATA) in the next cycle. If the transfer is not completed, the TACK signal is driven to low, and the external test vectors must be applied for another cycle. AMBA's test methodology demonstrates an early well-planned test approach that is essential for an efficient and flexible test circuitry.

Figure 3.7 Block Diagram of the Typical AMBA-Based SoC

Figure 3.8 Sequence of Events of the Write Operation

| TREQA | TREQB | TACK | Description       |

|-------|-------|------|-------------------|

|       |       | 0    | Current access    |

| ••    | 72    | 0    | incomplete        |

|       |       | 1    | Address vector,   |

| 1     | 1     |      | Control vector or |

|       |       |      | Turnaround vector |

| 1     | 0     | 1    | Write vector      |

| 0     | 1     | 1    | Read vector       |

| 0     | 0     | 1    | Exit test mode    |

|       |       |      |                   |

Table 3.1 Test Control Signals during Test Mode

The speed of AMBA bus system test is improved relative to the JTAG standard by providing a high-speed parallel test interface. Further, topology limitations that are given by the fixed order of JTAG interconnections are avoided in AMBA. The centralized TAC controller can access any unit under test directly, through the common shared bus. For these reasons, system self-test of complex systems-on-chip is better addressed by AMBA standard than by employing the JTAG standard.

# 3.3 Layered Methodology

Both JTAG and AMBA approaches are based on one-to-one direct bus connection which leads to a high development cost as the size and the complexity of the system increase. Because of that, authors in [16] proposed a Test Access Mechanism (TAM) architecture for SoCs based on a packet switching communication network. Other studies conducted in applying the layered approach to SoC designs include [17].

We believe that applying the layered approach to design the test circuitry will be more efficient for large and complex systems. Instead of directly producing the detailed specifications of the test circuitry for a given system, which is inflexible, one is focused on specifying the requirements of each layer that maximizes the reuse and minimizes the development cost. The increased flexibility also allows this approach to be applied to a wide class of systems such as sensor network, HomePNA or SoC designs.

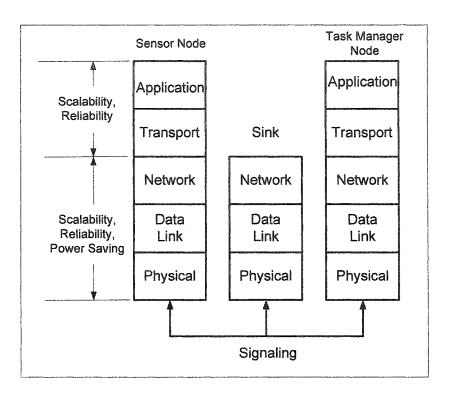

Each system can be partitioned into Open System Interconnect (OSI) layers, which are the physical layer, data link layer, network layer, transport layer, session layer, application layer and service layer, according to their functionality. The number of layers used is determined by the size and the complexity of the system. For example, a system may be partitioned into seven layers in HomePNA system while only three layers are needed in a simple SoC design.

The layered structure gives the framework for our test circuitry design and designers should specify the requirements of the test circuitry based on its system functionality. Once we have decided the basic structure of the test interface, each system layer is examined in detail for necessary hardware and software changes.

In this chapter, we describe the layered approach to test circuitry design within an example of InfiniBand Architecture (IBA) test architecture proposal. The suggested methodologies will target developing a test interface to control and initialize all the tests of the system. It also cooperates with the standards or with vendor developed local board level testing circuitry for in-circuit testing. Notice that it is not limited to IBA but can also be applied to any general system.

# 3.3.1 Case Study: InfiniBand

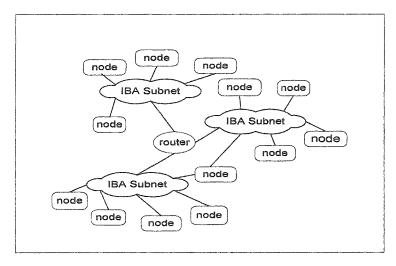

As described in Chapter 2, InfiniBand Architecture (IBA) is a new interconnect architecture aiming to replace the PCI bus architecture. It defines a System Area Network (SAN) that connects the nodes that can be independent processors nodes, I/O units or routers to another network through switches as shown in Figure 3.9. Each node contains one or multiple Channel Adapters that connect to the network and forms the IBA Subnet. Each IBA subnet can interconnect together through router.

Figure 3.9 Typical IBA Network

### 3.3.1.1 IBA Test Architecture Considerations

It is clear that boundary scan test circuitry is not applicable for this complex network system because of its low speed and inflexibility. Traditional ad-hoc and informal design approaches are also unable to provide an efficient test circuitry and only layered approach design methodology can fit this system.

Due to the networked nature of IBA systems, it can be defined to the layered test structure as shown in Figure 3.10.

- Physical Physical layer is the lowest level. It specifies the transmit medium. IBA architecture defines it in terms of voltage, data encoding and packet framing. They provide the service for:

- Establishing the physical link

- Informing link layer of the status of the physical link

- Monitoring the status of the physical link

- Transmitting and receiving the control and data bytes from the link layer to the physical link when available

- 2. Data Link This layer ensures the error-free transmission of the data. In IBA architecture, it is defined as the state machine and provides the error detection service by checking the packet by the length, operation code, Variant CRC (VCRC), Invariant CRC (ICRC) and virtual lane. It is also responsible for addressing, buffering and the flow control.

- 3. Network The network layer provides a topology-independent view of end-to-end communication to the upper level protocol. In IBA architecture, the network layer is responsible for routing the packets to the sub-net. IBA supports a two-layer topological division. The lower layer refers to a

Figure 3.10 IBA Layer Model

sub-net in which packets are forwarded by the switches. The higher layer refers to the interconnection of the sub-nets where packets are forward by the routers.

- 4. Transport The transport layer establishes and maintains the end-to-end connection. It is responsible to deliver the packets to the proper Queue Pair (QP) and provide the operation instructions. If the message data is larger than the maximum payload size of the packet, the transport layer partitions it into multiple packets for transmission and reassembles it in the receiver's memory. Five different transport service types are supported in IBA:

- Reliable Connection

- Reliable Datagram

- Unreliable Datagram

- Unreliable Connection

### • Raw IPv6 Datagram & Raw Ethertype datagram

IBA uses the software interface that is called software transport verbs to provide the abstract definition of the IBA hardware.

- 5. Session Session layer synchronizes messages between peers and ties all different data streams into a single application.

- 6. Presentation Presentation Layer handles the format of the data exchange between peers.

- 7. Application Application layer hides the details of the lower layers and focuses on the abstraction of the overall system.

The top three layers are beyond the scope of the IBA specification and are omitted since they depend on the software applications which eventually are based on the software transport verbs of the IBA.

Once the system is partitioned into several layers, designer should specify the requirements of its design. In IBA, test circuitry should obey the following requirements:

- Flexibility The high upgradeability of the IBA architecture should be

preserved and no modification of the test circuitry system should be needed as

the system is expanded or collapsed by adding or removing the function nodes.

- Reusability The reuse of the existing design can dramatically cut the development cost in the complex network system.

- Test Speed With the provided high bandwidth interconnect system, it is preferable to have a high speed testing circuitry.

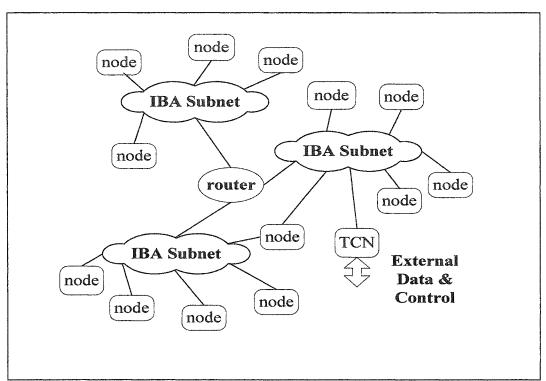

Figure 3.11 IBA Network with Proposed Test Circuitry Design

We decided to use a specialized functional node, Test Control Node (TCN) to initialize tests and to provide the external interface for data input and test control. As Figure 3.11 shows, the TCN is connected to the IBA network through the standard IBA switches and routers. One can initialize and control the testing of the target node through the external interface provided by the TCN. In testing mode, TCN and target nodes should be isolated and become transparent to the rest of the system. If a failure node is detected, based on the failure nature, user can isolate the end node through the provided standard IBA subnet management or replace the failure node.

Due to this transparency requirement, there should be no changes in the physical layer, the data link layer and the network layer. By doing this, TCN can reuse the standard design of these three layers and no modification is needed for both switches and routers since the standard IBA communication protocol will be reused. For the transport layer, specific operation code should be added to handle starting the test operation, sending test vectors and receiving test result. Within

the five different transport service types, reliable connection should be used to minimize the data loss through the network.

At this stage, the framework of the IBA system test circuitry is formed and designers can detail each layer of the TCN based on the given topology of IBA. Consider the difference between two IBA systems is the transmission media, where one uses cables while the other uses fiber optics for interconnect. Instead of designing two TCNs for each system, the layered design approach allows reusing the TCN design for both systems as long as the physical layer is modified appropriately. This provides a high flexibility and decreases the designing cost through the reuse.

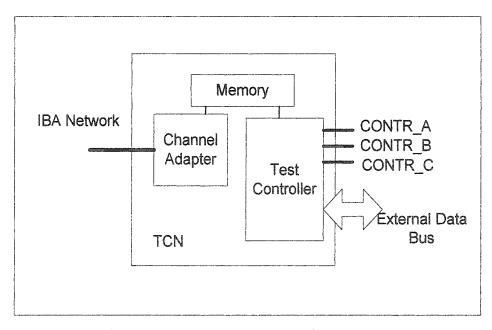

# 3.3.1.2 The TCN Design

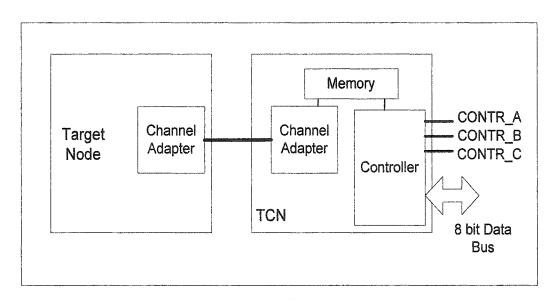

As shown in Figure 3.12, TCN is divided into three main components, Channel adapter, Memory and Test Controller.

Figure 3.12 Block Diagram of the Test Control Node (TCN)

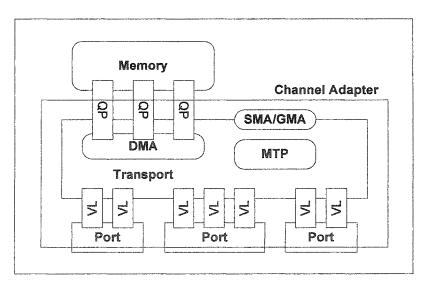

### 3.3.1.2.1 Channel Adapter

Channel Adapter is a standard IBA component that provides the communication channel between the TCN and IBA network. It provides the service of the physical layer, data link layer and network layer, such as performs the error checking to the incoming packets, by introducing the appropriate connection interface to the IBA.

As shown in Figure 3.13, the standard IBA channel adapter works as the Direct Memory Administrator (DMA) that receives the data and commands from the local memory and interfaces with the IBA network through the ports. Each port has its own set of transmit and receive buffers that are channeled through the Virtual Lane (VL). Memory Translation & Protection (MTP) mechanism is used to translate virtual addresses to physical addresses and validate access rights. When communication is established, both ports from the master and slave nodes are connected and isolated from the rest of the network.

Figure 3.13 Block Diagram of the Standard IBA Channel Adapter

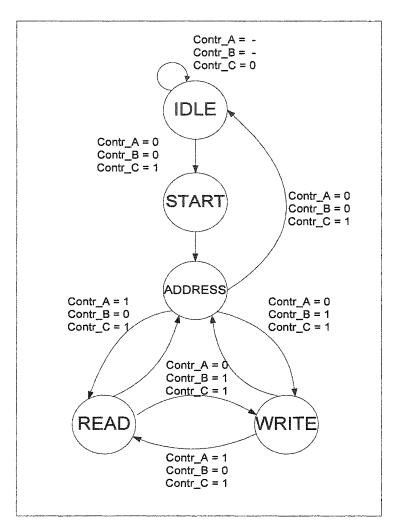

#### 3.3.1.2.2 Test Controller

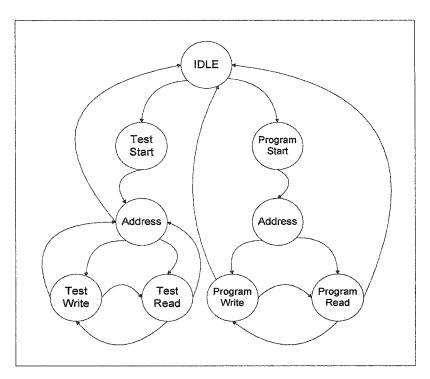

Test controller is a finite state machine as shown in Figure 3.14. It controls and

monitors testing based on the control signals and test vectors that are received from the external interface. On one hand, it analyzes the input packets and exports the test result to the external data bus. On the other hand, it receives all the input commands from the user interface and controls the test processes. Table 3.2 shows the control signals of the TCN during test mode.

### 3.3.1.2.3 Memory

Based on the IBA specification, memory buffers all the data and instructions that are sent between Test Controller and Channel Adapter. In IBA architecture, all the instructions are sent as send/receive queue pairs which are stored in the memory. The size of the memory will be determined by the number of the target nodes and the number of ports in the channel adapter.

| Control<br>Pin |   |    | STATE | Description                                                                     |

|----------------|---|----|-------|---------------------------------------------------------------------------------|

| A              | В | C  |       |                                                                                 |

| 0              | o | 0  | IDLE  | TCN is in the IDLE state and no test operation is performed                     |

| 0              | 0 | 11 | START | Test operation starts and transits to the ADDRESS state in the next clock cycle |

| 0              | 1 | 1  | WRITE | Write test data                                                                 |

| 1              | 0 | 1  | READ  | Read test result                                                                |

Table 3.2 TCN Control Signals during Test Mode

Figure 3.14 State-Machine of Test Controller

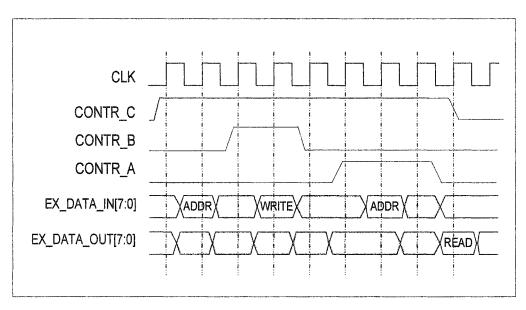

## 3.3.1.2.4 Single Node Testing Sequences

Three input signal pins, Control Pin A (CONTR\_A), Control Pin B (CONTR\_B) and Control Pin C (CONTR\_C) which are driven by the external tester are used to encode the mode of operation. As shown in Figure 3.15, by inserting the CONTR\_C, Controller places a Test Start Work Queue Entry on the work queue. In the next cycle, target address is imported to the Controller through the External Data Bus and buffered in the memory. Channel Adapter detects the test start request, validates the target address, formats the test request instruction packet and sends it the target node. Once the target node received the packet, the built-inself test activates and the functional test starts. By controlling the CONTR\_A and

CONTR\_B signal pins, data can be written to or read from the target node following the same transaction flow. Since IBA architecture specifies various management infrastructures within the standard channel adapters, a reliable communication service is guaranteed.

Figure 3.15 Timing Diagram of the Write and Read Test Operation

### 3.3.1.2.5 Multiple Node Testing

Although a single TCN is sufficient to handle the single node testing operation within the system, multiple concurrent node testing may require in some system. Fortunately, designers can add multiple TCNs to form the TCN network while no hardware modification is necessary. Each TCN has the ability to test every single end node within the system concurrently. During testing, each target node is isolated from the rest of the system. All the tests run locally, depending only on the externally provided test data. The Subnet Management Agent (SMA) and General Management Agent (GMA), located on the Channel Adapter of the TCN, handle the test scheduling and isolate the target nodes within the system. The testing sequences of each TCN and target node pair will be the same as a single node testing while multiple pairs can be performed in parallel. Notice that ideally if all the test processes are controlled locally and no external test vectors are

needed, the test time of multiple node testing is the same as the single node testing case. However, test time will increase dramatically in multiple node testing scenarios as external control and test vectors are needed.

# 3.4 Experimental Results

To validate the proposed approach based on the layered system design methodology, we designed and simulated the proposed IBA test circuits in VHDL and ported it to the FPGAs.

Figure 3.16 Block Diagram of Our TCN Design with Single Target Node

Figure 3.16 shows the block diagram of our TCN design with the target node. To simplify the design, we used an eight bit external data bus with 2K memory in our TCN design. Both the channel adapters of the TCN and the target node are designed to handle the packet formation. As discussed above, the controller is a state machine that controls the testing process, inputs the test vectors and exports the test result. The design is ported to two different Altera Corp. programmable logic device architectures, Flex 10KE device (EPF10K30ETC144-1) with 1728 logic elements and MAX 9000 (EPM9320LC84-15) device with 320 macrocells. The area and speed results are shown in the Table 3.3.

|                              | Flex 10KE | MAX9000 |

|------------------------------|-----------|---------|

| % of Logic<br>Cells Utilized | 30        | 78      |

| Max Speed                    | 90MHz     | 90.9MHZ |

Table 3.3 Performance Results of TCN with Different Programmable Logic

Architectures

The size of our TCN design is mainly dictated by the Channel Adapters and the choice of the Memory core. In our design, the gate count of the TCN is around 10K and the size of the Controller is only 20% of the whole design. The size of the TCN may increase by expanding the memory size and the functionality of the channel adapter; however, it will keep constant for various system sizes. Notice that the maximum test speed is only 90MHz. This is due to the choice of FPGA devices used. The speed can substantially increase by using FPGA with better speed grade or using in ASICs.

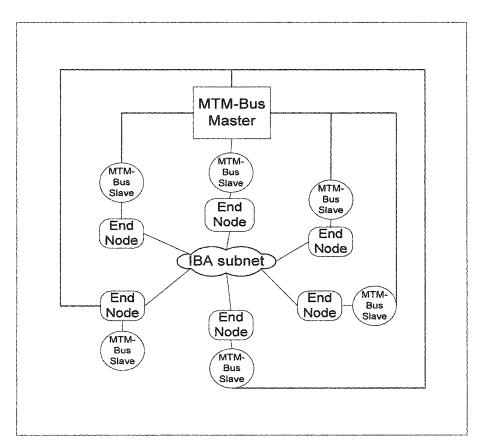

# 3.4.1 IBA Test Interface Based on MTM-Bus Architecture

For comparison, the IBA test interface model of a single end node based on MTM-Bus is simulated and ported to Altera's Flex 10KE (EPF10K30ETC144-1) and MAX9000 (EPM9320LC84-15) devices and the results are shown in Table 2.

Figure 3.17 shows the details of applying the MTM bus protocol to the IBA. MTM-bus Master module controls and monitors the entire test system through the dedicated MTM-Bus by communicating with the MTM-Bus Slave interfaces of each end node. Notice that by using eight bit address size, a maximum of 255 modules (end nodes) can be controlled by one MTM-Bus Master Module.

|                              | Flex 10KE | MAX9000 |

|------------------------------|-----------|---------|

| % of Logic<br>Cells Utilized | 9         | 13      |

| Max Speed                    | 81MHz     | 29MHZ   |

Table 3.4 Performance Results of IBA Test interface Based on MTM-Bus with a Single End Node

Figure 3.17 Block Diagram of the IBA test Interface Based on the MTM-Bus Protocol

## 3.4.2 Comparison

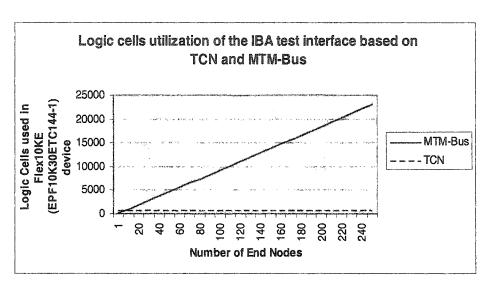

Reusability is the main disadvantages of MTM-Bus when compared with our layered approach methodology. As shown in Figure 3.17, the size of the test interface based on MTM-Bus will grow proportionally to the number of end nodes.

In order to visualize this problem, the logic cells utilizations of both test interfaces are estimated and plotted against the IBA network with different number of end nodes. As shown in Figure 3.18, TCN enables a low gate count design that is not affected by the system size, while additional hardware (MTM-Bus Slave Interface) and wires will be needed to serially connect each node if MTM-Bus is applied. This degrades the expandability and flexibility of the system. As a result, the cost of our test scheme only depends on the physical layer of the system. Although in some systems, they may consist costly components such as wireless transceivers or optical front-ends, our approach will still cost less when compared to the MTM-Bus since the test cost is kept constant and not related to the system size.

Due to the fact that the physical layer, data link layer and network layer are unchanged in our test circuitry, this approach maximizes the reuse of the existing hardware. Moreover, multiple nodes can also be tested concurrently by adding TCNs to form the TCN network, which is not achievable in the MTM-Bus architecture.

Figure 3.18 Logic Cells Utilizations of the TCN and MTM-Bus Interface with Different System Size

# 3.5 Conclusions

The existing boundary-scan test circuitry fails to meet the challenges posed by the complex networked systems. By comparing the PCI bus architecture and AMBA, one can conclude that ad-hoc or informal design approach ends up with inefficient and slow testing circuitry. In this Chapter, we have presented a disciplined layered design methodology for the complex system test circuitry and demonstrated its benefits on the InfiniBand architecture. This approach is not limited to the IBA network system, but is equally applicable to the wider class of systems including Systems on Chip (SoC). The proposed designed methodology is also presented in the VLSI Test Symposium 2002 [36].

# Chapter 4 - Extended Usage of the Test Interface Based on Layered Design Approach

## 4.1 Overview

As mentioned in Chapter 3, the main concept of layered approach is to partition the system into different layers based on their functionality. Instead of building the test interface directly from scratch, each functional layer is modified so as to provide the testing access. By doing so, the developed test interface is embedded in the system, which can maximize the reuse and flexibility. Because of this reuse, the developed test interface can also be viewed as the access channel to the various components within the system. This provides the possibility of using the developed test interface for other operations such as online programming, debugging and software upgrade. In terms of flexibility, the highly reused system-level test interface also ensures the compatibility to the distributed systems such as sensor networks and eases the product development.

In this chapter, we explore the benefits of our approach in several systems. In Section 4.2, the extended usage such as online programming, debugging and software upgrade, of our proposed test interface in the general system is discussed. Our IBA TCN is revisited in Section 4.3 and examined the necessary modifications in order to provide the system access features. In Section 4.4, we apply our design methodology to the distributed systems and demonstrate it in the sensor networks. Finally, this chapter is concluded in Section 4.5.

# 4.2 Extended Usage of the Test Interface

Rapidly developed technology not only forces industry to push their products to the market sooner but also shortens the product life. As a result, industry vendors are always concerned about decreasing the length of the development phase and adding the upgradeability features to their designs in order to lengthen the product life. In order to support this upgradeability feature, the system must provide the access interface for the designer to communicate with the target devices. As our proposed test interface is based on the layered design approach, only small modifications are needed to provide the access channel for the various components within the system. In order to show the simplicity of adding the system access features in the test interface based on layered design methodologies, our proposed IBA test interface is used for demonstration.

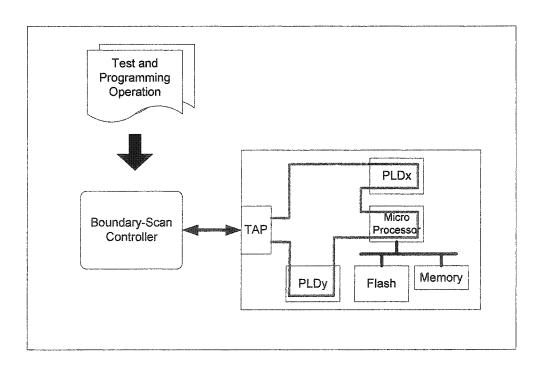

### 4.2.1 IEEE 1532

Figure 4.1 Block Diagram of IEEE 1532

In JTAG, the programming features are accomplished by establishing a new set of programming instruction and associated data registers. IEEE standard 1532 [52] defines the additional instructions, the data file format and Boundary-Scan Description Language (BSDL) extensions that are used for the programming algorithms. As shown in Chapter 3, section 3.2, device that is compliant with IEEE standard 1149.1 has a 'test' mode and a 'system' mode. During test mode, the device is isolated from the system and test data is scanned into or out of the device through the register cells. IEEE standard 1532 (as shown in Figure 4.1) extends the JTAG functions by introducing four additional system modal states, programmed, Operational, In-System Configurations (ISC) Accessed and ISC Completed, that handles the in-system configurations. Three control signals, ISC\_Done, ISC\_Completed and ISC\_Disable\_Completing are used to control the mode transition. Unprogrammed devices can be isolated from the system by setting it into the Unprogrammed mode. By activating the ISC\_Enable signal, the target device enters the ISC Accessed mode and performs the programming operation. Once the programming operation is done, it transits to the ISC\_Completed mode by deactivating the ISC\_Enable and activating the ISC\_Disable\_Completing signals. Target device can resume its normal system operations by entering the Operational mode once the ISC\_Done signal is set.

### 4.2.2 Modifications of the IBA Test Interface

The main tasks in the programming mechanisms include writing the programming data to the target devices and reading the programming results. Based on the IBA layer model that we defined in Chapter 3, the lowest three layers, the physical, data link and the network layers are only responsible for the IBA communication mechanisms. They do not need any modification and can be reused. The only part that needs to be modified in order to handle the software upgrading and programming mechanisms is the transport layer.

| Control Pin |   | l | STATE | Description       |                                         |

|-------------|---|---|-------|-------------------|-----------------------------------------|

| A           | В | C | D     |                   | D O O O O O O O O O O O O O O O O O O O |

| 0           | 0 | 0 | 0     | IDLE              | TCN is idle                             |

|             |   |   |       |                   | Test operation starts and wait for      |

| 0           | 0 | 1 | 0     | Test START        | the target address in the next clock    |

|             |   |   |       |                   | cycle                                   |

| 0           | 1 | 1 | 0     | Test WRITE        | Write test data to the target device    |

|             |   | * |       | 100t WIGHE        | in the next clock cycle                 |

| 1           | 0 | 1 | 0     | Test READ         | Read test result to the target device   |

| *           |   |   |       | 1000 1027 112     | in the next clock cycle                 |

|             |   |   |       | !                 | Programming operation starts and        |

| 0           | 0 | 1 | 1     | Program START     | wait for the target address in the      |

|             |   |   |       |                   | next clock cycle                        |

|             |   |   |       |                   | Write programming data to the           |

| 0           | 1 | 1 | 1     | Program WRITE     | target device in the next clock         |

|             |   |   |       |                   | cycle                                   |

|             |   |   |       |                   | Read programming result to the          |

| 1           | 0 | 1 | 1     | Program READ      | target device in the next clock         |

|             |   |   |       |                   | cycle                                   |

| -           |   | 0 | 0     | Exit Program Mode | Exit the program mode and TCN is        |

|             |   |   |       | ū                 | idle in the next clock cycle            |

Table 4.1 Control Signals during Test Mode and Program Mode

For our proposed TCN, Channel Adapter (CA) and memory should not be changed while Controller needs to be slightly adjusted to fulfill this requirement. Four additional states, Program START, Program ADDRESS, Program WRITE and Program READ are added in the Controller to handle the programming functions as shown in Figure 4.2.

In order to enter and control these programming states, a special control signal pin, CONTR\_D, is added for the programming function. The control signals for both

the test mode and program mode are shown in Table 4.1.

Figure 4.2 State Machine of the Modified TCN's Controller

# 4.2.3 Experimental Results

The design is ported to two different Altera Corp. programmable logic device architectures, Flex 10KE device (EPF10K30ETC144-1) with 1728 logic elements, -1 speed grade and MAX 9000 (EPM9320LC84-15) device with 320 macrocells, -15 speed grade. The area and speed results are shown in the Table 4.2.

|                | Flex 10KE | MAX9000 |

|----------------|-----------|---------|

| % of Logic     | 40        | 86      |

| Cells Utilized | 70        | GO .    |

| Max Speed      | 90MHz     | 90.9MHZ |

Table 4.2 Performance Results of modified TCN with Different Programmable Logic Architectures

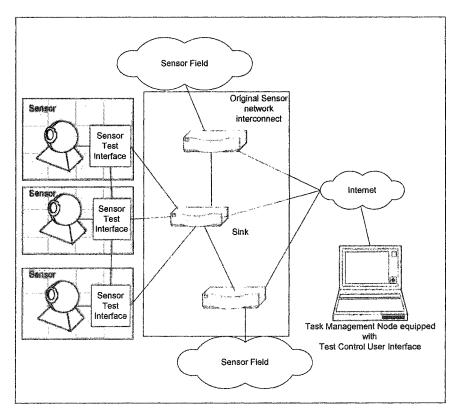

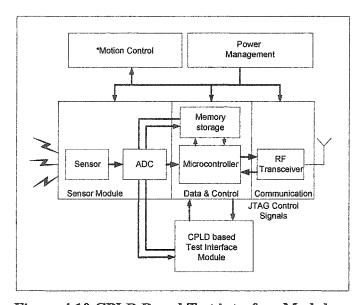

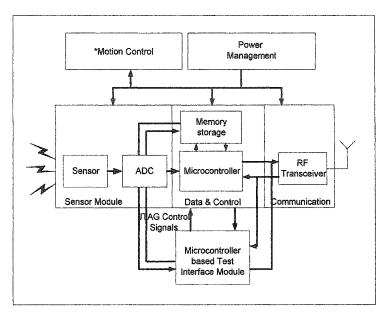

By using the Flex10KE device, the gate count of our modified TCN is around 12K. Notice that there is a 20% increased in size when comparing with the original TCN (which the size is 10K) as shown in Table 3.3. This overhead is caused by the additional programming function in the TCN's controller. Since the state machine of the program mode is similar to the one in the test mode, the maximum operating speed is remained the same.