National Library of Canada

Bibliothèque nationale du Canada

Direction des acquisitions et

des services bibliographiques

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontano K1A 0N4 395, rue Wellington Ottawa (Ontano) K1A 0N4

Our life - Nation informace

#### AVIS

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

NOTICE

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Rapid Current Analysis for CMOS Digital Circuits

Na-Han CHAN

McGill University, Montreal

July 1994

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering.

© Na-Han CHAN, 1994

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your Ne Votre reference

Our Me Notre référence

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS. L'AUTEUR A ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION. L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

ISBN 0-315-99960-8

### Abstract

A versatile and efficient computer-aided analysis tool, CUREST, has been developed for the analysis of supply currents in CMOS digital circuits. It is based on Nabavi-Lishi's semi-analytical model for computing the current and delay in a CMOS logic gate which, when compared to HSPICE running the level-3 MOSFET model, is more than three orders of magnitude faster, and accurate to within 10%. CUREST is built on top of the timing analyser TAMIA and, in particular, uses its circuit parser and its data structure to store the circuit topology and primary input pattern.

Extensive tests on benchmark circuits containing up to 555 gates, which were analysed with CUREST using thousands of primary input patterns, demonstrate that the current analysis time is in the range of 1ms per gate per input pattern, using a SUN4/490 workstation with 32 Mb of main memory, running the SUN OS 4.103 operating system. The peak value of the total supply current, the current rise-time, and the time at which the peak occurs are usually computed to within 10% of HSPICE. However, appreciable errors often occur in the average current. This is because at the moment we do not have a good model for dealing with incomplete transitions associated with glitches in a CMOS gate.

i

### Résumé

CUREST est un outil versatile et efficace d'analyse assistée par ordinateur qui a été conçu pour l'analyse des courants d'alimentation dans les circuits digitaux CMOS. L'outil est basé sur les modèles semi-analytiques de Nabavi-Lishi pour le calcul des délais et courants des portes logiques CMOS. En comparaison à HSPICE (au *3ième* niveau de complexité des modèles MOSFET), ces nouveaux modèles permettent des calculs de l'ordre de milliers de fois plus rapides que HSPICE. De plus, les calculs sont précis à 10% de la valeur exacte. CUREST a été implanté à partir du système d'analyse temporelle TAMIA. En particulier CUREST se sert du programme d'analyse lexicographique et des structures de données de TAMIA pour la mise en mémoire des circuits et de leur topologie ainsi que les signaux d'entrée.

Plusieurs tests, ayant des milliers de signaux d'entrée chacun, ont été effectués sur des circuits étalons comportant jusqu'à 555 portes logiques. Les résultats indiquent une performance moyenne d'une milliseconde multiplier par le nombre de portes logiques et par le nombre de signaux d'entrée. Cette formule s'applique à un système d'exploitation SUN OS 4.103 en opération sur un SUN4/490 possédant 32 MegaOctets. Les résultats pour le courant maximal, la durée de transit du courant, et le temps lorsque le courant atteint son maximum sont tous à l'intérieur de 10% des valeurs obtenues par HSPICE. Cependant le calcul du courant moyen est souvent inexact. Ceci est dû à une carence de nos modèles pour l'analyse des transitions incomplètes causées par les soubresauts des portes logiques CMOS.

### Acknowledgements

I would like to thank my thesis supervisor, Prof. Nicholas Rumin, for his support and guidance throughout my Master's research studies. His encouragement and patience were greatly appreciated. In addition, I am thankful to A. Nabavi-Lishi, S. Gaiotti, Prof. M. Dagenais and Prof. J. Rajski for their valuable help in my research work.

I would also like to take this opportunity to acknowledge the help of the staff of the Microelectronic and Computer System(MACS) laboratory. In particular, thanks to Jacek Slaboszewicz, and Christine Marquis for all their help. I have also enjoyed many fruitful discussions with my fellow graduate students in the MACS laboratory and I cherish the friendships that have been built between us.

This work was supported by research grants from the Natural Sciences and Engineering Research Council(NSERC) of Canada as well as by FCAR Scholarship.

# Contents

| AÌ | bstra | ct                                                       | i        |

|----|-------|----------------------------------------------------------|----------|

| R  | ésum  | é                                                        | ii       |

| A  | cknov | wledgements                                              | iii      |

| 1  | Intr  | oduction                                                 | 1        |

|    | 1.1   | Pattern-independent current estimation techniques        | <b>2</b> |

|    | 1.2   | Pattern-dependent current estimation techniques          | 6        |

|    | 1.3   | Motivation and overview of thesis                        | 12       |

| 2  | Del   | ay and current models                                    | 14       |

|    | 2.1   | Inverter Model                                           | 14       |

|    | 2.2   | Inverter with falling input transition: CP and CW Models | 16       |

|    |       | 2.2.1 CP model                                           | 16       |

|    |       | 2.2.2 CW model                                           | 18       |

|    | 2.3   | Inverter with rising input: DP model                     | 20       |

|    | 2.4   | Computing parasitic capacitances in an inverter          | 22       |

|   | 2.5  | Current calculation in an inverter chain                         | 24 |

|---|------|------------------------------------------------------------------|----|

|   | 2.6  | Collapsing of a general CMOS gate into an inverter               | 25 |

|   | 2.7  | Collapsing a series-connected group of transistors               | 25 |

|   |      | 2.7.1 Width collapsing                                           | 26 |

|   |      | 2.7.2 Capacitances collapsing                                    | 28 |

|   | 2.8  | Collapsing a parallel-connected group of transistors             | 31 |

|   |      | 2.8.1 Width collapsing                                           | 32 |

|   |      | 2.8.2 Capacitances collapsing                                    | 34 |

| 3 | CUI  | Rrent ESTimation Algorithm: CUREST                               | 36 |

|   | 3.1  | The timing analyser TAMIA                                        | 37 |

|   |      | 3.1.1 Circuit Decomposition                                      | 38 |

|   | 3.2  | The overview of CUREST                                           | 38 |

|   | 3.3  | Technology dependent parameters for current and delay estimation | 40 |

|   | 3.4  | Order of processing of logic gates in the circuit                | 41 |

|   | 3.5  | Random input generation                                          | 42 |

|   | 3.6  | Output logic evaluation of a CMOS logic gate                     | 44 |

|   | 3.7  | The total circuit current waveform evaluation                    | 45 |

|   | 3.8  | Glitch current estimation of a logic gate                        | 46 |

|   | 3.9  | Obtaining the total current waveform                             | 49 |

|   | 3.10 | The output of CUREST                                             | 50 |

| 4 | Res  | ults                                                             | 57 |

|   | 4.1  | Speed comparisons between CUREST and HSPICE                      | 58 |

|   |      |                                                                  |    |

v

•

|   | 4.2 Accuracy of CUREST with respect to HSPICE | 59 |

|---|-----------------------------------------------|----|

| 5 | Discussion and conclusions                    | 65 |

| в | ibliography                                   | 67 |

| A | The cell-types in the test circuits           | 71 |

| в | The input format for CUREST                   | 76 |

.

.

.

# List of Figures

-

| <ul> <li>2.2 A general case for the input signals in a series chain when q = 3. Here i, j, and k ∈{1, 2,, q}. The signal T<sub>xj</sub> is used as the effective input for the equivalent transistor which replaces the group[29]</li> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          | 2.1 | (a) Transistor-level model of a CMOS inverter. The effect of the loading            |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------|----|

| <ul> <li><i>i<sub>GP</sub></i>(0), and <i>i<sub>CP</sub></i>() [29].</li> <li>2.2 A general case for the input signals in a series chain when q = 3. Here <i>i</i>, <i>j</i>, and k ∈ {1, 2,, q}. The signal T<sub>xj</sub> is used as the effective input for the equivalent transistor which replaces the group[29].</li> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29].</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors [29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (), and</li> </ul> |     | gate(s) is included in $C_N$ and $C_P$ . (b) Charging and discharging currents      |    |

| <ul> <li>2.2 A general case for the input signals in a series chain when q = 3. Here i, j, and k ∈ {1, 2,, q}. The signal T<sub>xj</sub> is used as the effective input for the equivalent transistor which replaces the group[29]</li> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     |     | of the inverter shown in (a) when driven by another inverter. $i_{PS}(-)$ ,         |    |

| <ul> <li>i, j, and k ∈{1, 2,, q}. The signal T<sub>xj</sub> is used as the effective input for the equivalent transistor which replaces the group[29]</li> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | $i_{GP}(0)$ , and $i_{CP}(-)$ [29]                                                  | 15 |

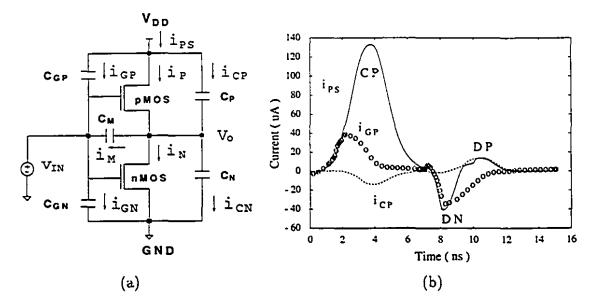

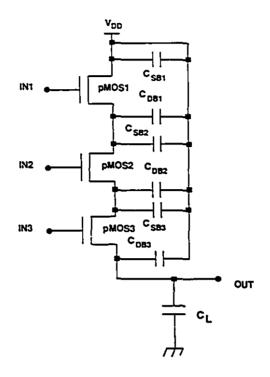

| <ul> <li>for the equivalent transistor which replaces the group[29]</li> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29]</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (), and</li> </ul>                                                                                                                                                                                                                                                      | 2.2 | A general case for the input signals in a series chain when $q = 3$ . Here          |    |

| <ul> <li>2.3 Parasitic capacitances reduction in three series transistors. (a) Parasitic capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29].</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (-), and</li> </ul>                                                                                                                                                                                                                                                                                                                        |     | i, j, and $k \in \{1, 2,, q\}$ . The signal $T_{xj}$ is used as the effective input |    |

| <ul> <li>capacitances in three series pMOS transistors. Drain(source)-to-bulk capacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29].</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (-), and</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        |     | for the equivalent transistor which replaces the group $[29]$                       | 26 |

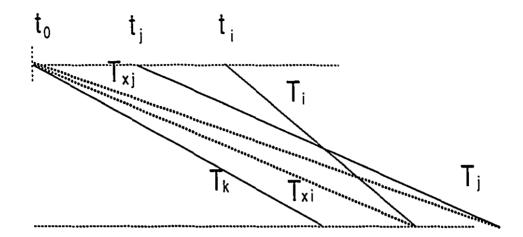

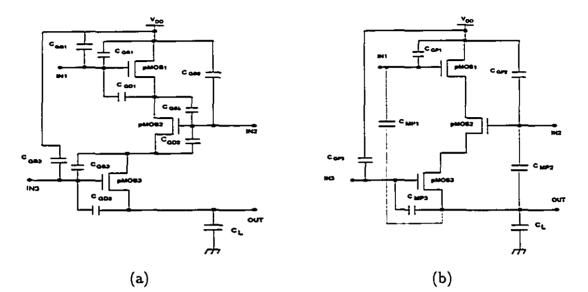

| <ul> <li>pacitances are not shown. (b) Equivalent capacitances after capacitance reduction in (a)[29].</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (-), and</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3 | Parasitic capacitances reduction in three series transistors. (a) Parasitic         |    |

| <ul> <li>reduction in (a)[29].</li> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (-), and</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | capacitances in three series pMOS transistors. Drain(source)-to-bulk ca-            | •  |

| <ul> <li>2.4 Drain and source-to-bulk capacitances in three series pMOS transistors[29].</li> <li>2.5 Effective width for parallel transistors in a 2-input NAND gate (W<sub>p1</sub> = W<sub>p2</sub> = 9.0µm, L<sub>p</sub> = L<sub>n</sub> = 3.0µm). T<sub>1</sub> = 10ns, HSPICE (-), and</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | pacitances are not shown. (b) Equivalent capacitances after capacitance             |    |

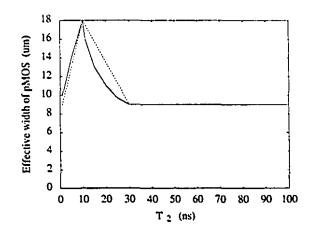

| 2.5 Effective width for parallel transistors in a 2-input NAND gate ( $W_{p1} = W_{p2} = 9.0 \mu m$ , $L_p = L_n = 3.0 \mu m$ ). $T_1 = 10 ns$ , HSPICE (), and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | reduction in (a)[29]                                                                | 29 |

| $W_{p2} = 9.0 \mu m$ , $L_p = L_n = 3.0 \mu m$ ). $T_1 = 10 ns$ , HSPICE (-), and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.4 | Drain and source-to-bulk capacitances in three series pMOS transistors[29].         | 30 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.5 | Effective width for parallel transistors in a 2-input NAND gate ( $W_{p1} =$        |    |

| approximation (). Both signals starts at $t=0[29]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | $W_{p2} = 9.0 \mu m$ , $L_p = L_n = 3.0 \mu m$ ). $T_1 = 10 ns$ , HSPICE (), and    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | approximation (). Both signals starts at $t=0[29]$                                  | 32 |

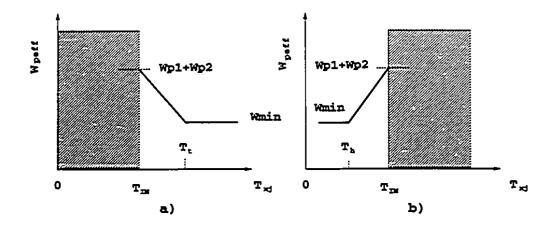

| 2.6 | The effective width for the two parallel transistors in a 2-input NAND<br>gate, versus $T_{xj}$ for: (a) rising output, (b) falling output. In each case<br>one transistor is driven by $T_{IN}$ , while the other one is driven by $T_{xj}$<br>which never crosses into the shaded area. Moreover, $W_{voin}$ is the width<br>of the transistor driven by $T_{vol}[20]$ |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7 | of the transistor driven by $T_{IN}[29]$                                                                                                                                                                                                                                                                                                                                 | 33 |

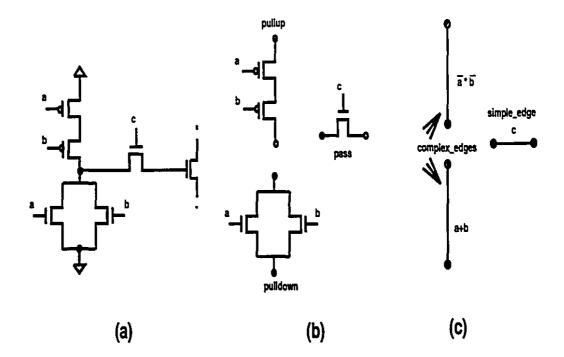

| 3.1 | The circuit decomposition:(a) a transistor group, (b) transistor sub-<br>groups (c) virtual edges                                                                                                                                                                                                                                                                        | 37 |

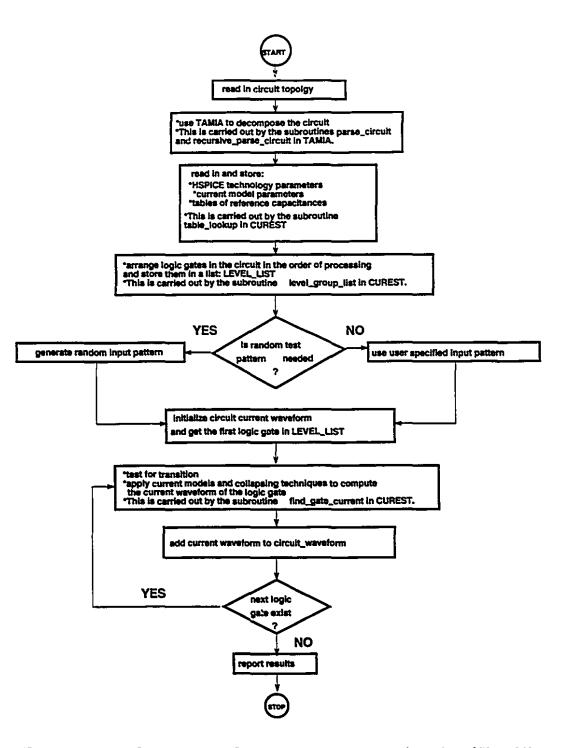

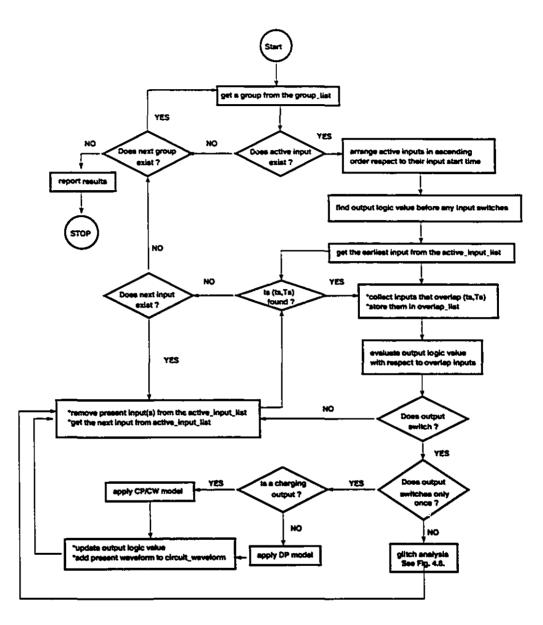

| 3.2 | The flow diagram of the current estimation algorithm CUREST                                                                                                                                                                                                                                                                                                              | 39 |

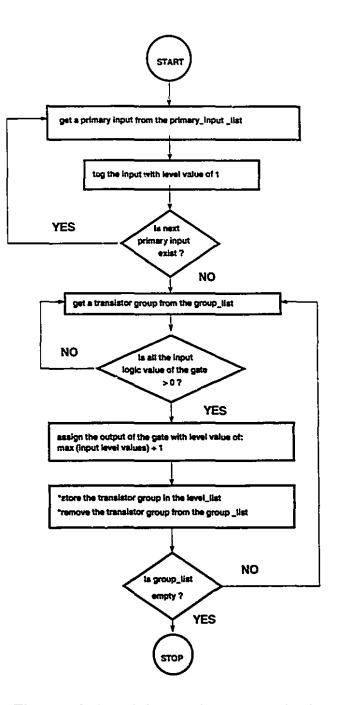

| 3.3 | The re-ordering of the transistor groups in the group_list                                                                                                                                                                                                                                                                                                               | 42 |

| 3.4 | The logic_evaluation                                                                                                                                                                                                                                                                                                                                                     | 51 |

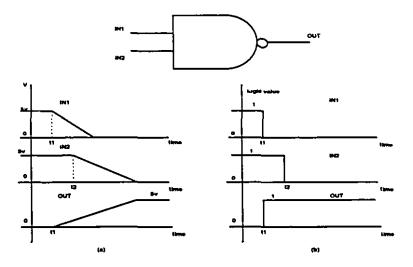

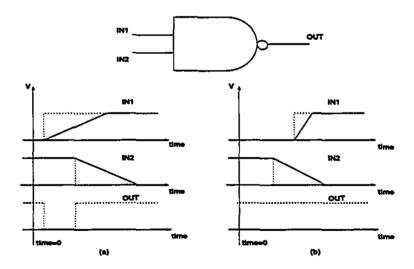

| 3.5 | Logic evaluation of 2-input NAND gate with respect to its inputs. (a)<br>The input and output transition changes. (b) The input and output                                                                                                                                                                                                                               |    |

|     | logic changes.                                                                                                                                                                                                                                                                                                                                                           | 52 |

| 3.6 | The flow diagram of circuit waveform evaluation                                                                                                                                                                                                                                                                                                                          | 53 |

| 3.7 | Logic evaluation of 2-input NAND gate with overlapping inputs. The dotted lines indicate the logic values of the inputs and outputs. (a) The output emitted as twices high law high. (b) The output does not emitted                                                                                                                                                     | 54 |

|     | output switches twice: high-low-high. (b) The output does not switch.                                                                                                                                                                                                                                                                                                    | 54 |

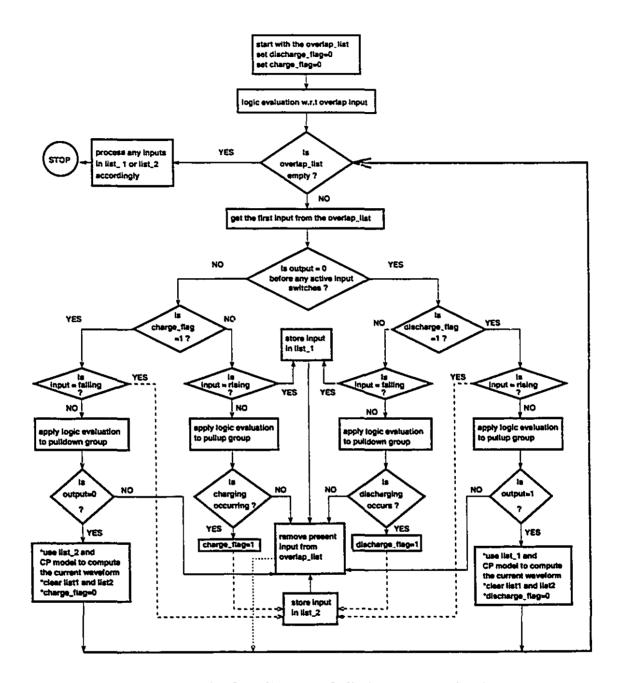

| 3.8 | The flow diagram of glitch current evaluation                                                                                                                                                                                                                                                                                                                            | 55 |

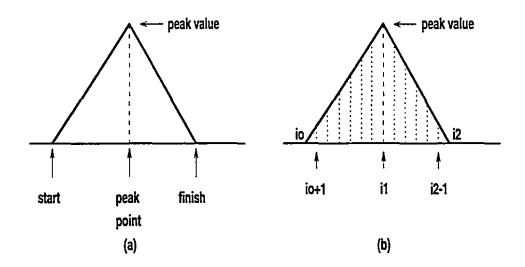

| 3.9 | Current triangle obtained from CP or DP model. (a)The four points<br>required to uniquely define a current triangle. (b) The array indices of                                                                                                                                                                                                                            |    |

|     | the current triangle                                                                                                                                                                                                                                                                                                                                                     | 56 |

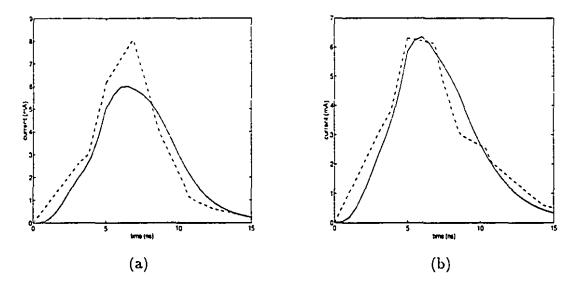

| 4.1 | The current waveform of 139 Decoder(dash) with respect to HSPICE(solid). |     |

|-----|--------------------------------------------------------------------------|-----|

|     | (a)Worst case out of 10. (b)Best case out of 10                          | 60  |

| 4.2 | The current waveform of 4-bit adder(dash) with respect to HSPICE(solid). |     |

|     | (a)Worst case out of 10. (b)Best case out of 10                          | 60  |

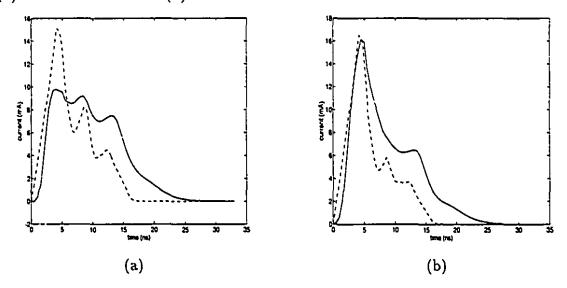

| 4.3 | The current waveform of ALU 181(dash) with respect to HSPICE(solid).     | •   |

|     | (a)Worst case out of 10. (b)Best case out of 10                          | 61  |

| 4.4 | The current waveform of ISCAS85 benchmark circuit c880(dash) with        |     |

|     | respect to HSPICE(solid). (a)Worst case out of 10. (b)Best case out of   | ~ 1 |

|     | 10                                                                       | 61  |

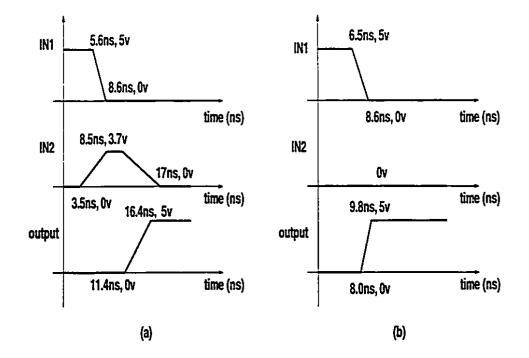

| 4.5 | The input and output transitions of an internal 2-input NCR gate in the  |     |

|     | 4-bit adder. IN2 is a glitch. (a) The transition information associated  |     |

|     | with the inputs and output computed by HSPICE. (b) The transition        |     |

|     | information associated with the inputs and output computed by CUREST.    | 62  |

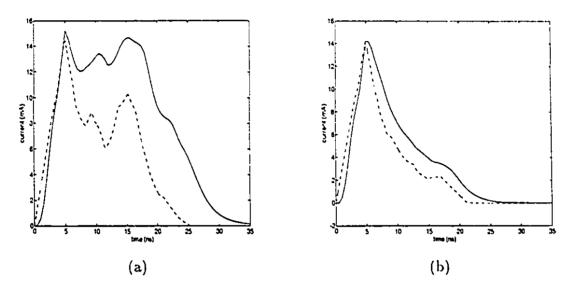

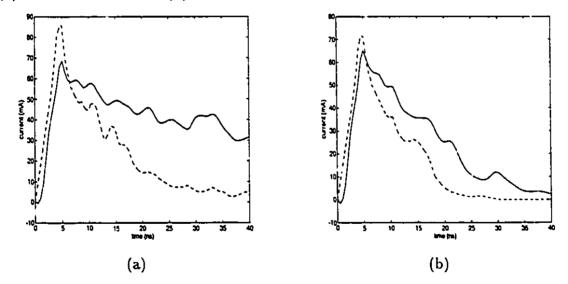

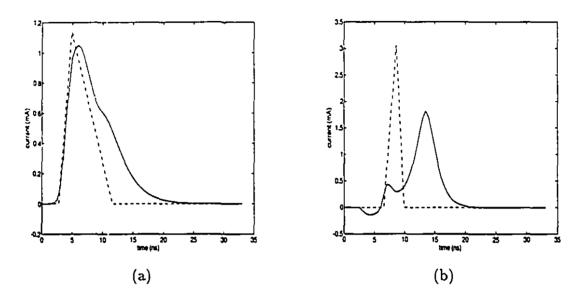

| 4.6 | The current waveforms of individual gates in the 4-bit adder. The trian- |     |

|     | gular waveform computed by CP or DP model is represented by $()$         |     |

|     | line and the smooth current waveform obtained from HSPICE is drawn       |     |

|     | in solid line. (a) The current waveforms of gate 12. (b) The current     |     |

|     | waveforms of gate 46                                                     | 64  |

# List of Tables

| Appropriate values of $a$ and $b$ obtained for a 1.2 micron technology [29].                                                                                                 | 19                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Coefficients to obtain $W_{sc}$ from $W_{pug}(W_{pdg})$ for a 1.2 micron technology.<br>The input node number increases from the one nearest $V_{DD}$ (GND)[29].             | 28                                                                                                                                                                                                                                                                                       |

| HSPICE: Maximum glitch current drawn by 2-input NAND and NOR gates. IN1 falls with 5ns and IN2 rises with 5ns                                                                | 47                                                                                                                                                                                                                                                                                       |

| Test circuits used for speed and accuracy analysis of CUREST                                                                                                                 | 57                                                                                                                                                                                                                                                                                       |

| The amount of CPU time required for CUREST to analyse the four test circuits on SUN4/490 with 32 Mb main memory and running with SUN OS 4.103 operating system.              | 58                                                                                                                                                                                                                                                                                       |

| CPU time required for HSPICE to simulate the four test circuits on<br>SUN4/490 running with SUN OS 4.103 operating system. The maxi-<br>mum integration step equals to 0.5ns | 59                                                                                                                                                                                                                                                                                       |

| Individual and total gate current drawn at 13ns. A gate is identified by                                                                                                     | 63                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                              | Coefficients to obtain $W_{sc}$ from $W_{pug}$ ( $W_{pdg}$ ) for a 1.2 micron technology.<br>The input node number increases from the one nearest $V_{DD}$ (GND)[29].<br>HSPICE:Maximum glitch current drawn by 2-input NAND and NOR<br>gates. IN1 falls with 5ns and IN2 rises with 5ns |

....

### Chapter 1

### Introduction

As VLSI circuit densities continue to increase, accurate information on the current distribution in the chip power and ground buses is needed by the designer. The reasons include the need to minimize the sizes of the power rails without, at the same time, producing current densities high enough to cause premature failure due to electromigration, or performance degradation due to excessive voltage drops. The current information is also needed to determine the power requirements of the chip. In this chapter, a number of existing current and power estimation techniques are reviewed and, in Section 1.3 our own approach is introduced.

The existing current and power estimation techniques can be grouped into two major categories: pattern-dependent and pattern-independent. The pattern-dependent method evaluates the current waveform of a circuit according to one particular primary input pattern. On the other hand, the pattern-independent approach produces the average current waveform corresponding to a large number of input patterns. In order to tackle the excessive heat dissipation, electromigration, and excessive voltage drop problems, it is the true pattern-dependent current waveforms that are required to determine the worst case conditions. However, these are impractical for circuits with more than approximately 20 inputs. Hence, pattern-independent methods, which are more efficient, are often used. In the following section, the pattern-independent methods are discussed which is followed by the pattern-dependent methods. Finally, the objective and outline of this dissertation are presented.

## 1.1 Pattern-independent current estimation techniques

In general, pattern-independent methods adopt a statistical approach to estimate the current and power dissipation in a circuit. This method does not provide the information on the instantaneous current waveform associated with a particular input pattern, but it is fast in computing the average current and power over a large number of input test patterns.

Najm et al. computed the expected current waveform of a circuit by carrying out an event-driven probabilistic simulation of the circuit [1][2][3]. First, they replaced logic values and transitions of primary inputs of a circuit by signal probabilities [4] and transition probabilities respectively. Then, they derived the corresponding probability waveforms at internal circuit nodes and propagated these waveforms towards the primary outputs. The expected current pulses of each individual gates are summed to create the expected current waveform of the circuit. In particular, the expected current waveform at each subcircuit is approximated by a right-angled triangular pulse that starts with a peak of E[i(t)] at time t and decays linearly to zero at time  $(t + \tau)$ . The expected current value E[i(t)] is computed by assuming the transistor behaves as a resistor and operates in its saturation region, and  $\tau$  is evaluated as a function of E[i(t)]. In [5], the authors extended the probabilistic simulation approach to include the computation of the variance waveform of the circuit which is useful in obtaining a better estimation of the median time-to-failure(MTF) of a circuit.

The current model used in the above approach ignores the short circuit current

and assumes the input transitions are step functions. In addition, the authors in [5] assume that there is no signal correlation between internal circuit nodes which results in overestimating the total current drawn by the circuit. Although Kriplani *et al.* [6] develop an algorithm that resolves the signal correlation problem as mention above, their approach complicates the algorithm and hence, slows down the analysis.

In [7], Kriplani *et al* proposed a method to predict an upper bound for the current waveform that a circuit can draw. For each of the excitations, low, high, high $\rightarrow$ low, and low $\rightarrow$ high, the authors stored a list of intervals during which a node might carry that excitation. The internal node transition information is derived by merging these intervals. It is assumed that there are only two possible current waveforms associated with every gate; one due to low $\rightarrow$ high transitions and the other due to high $\rightarrow$ low transitions. The maximum of the two current waveforms at every time point is considered to be the worst case supply current. A right-angled triangular current pulse is used to approximate the current waveform of a switching gate, where the peak of the current is user specified, and the duration is computed by charge conservation. Once all the gates' currents have been computed, the total current waveform is determined by adding together the individual gate contributions.

In this approach, the authors assumed in each combinational block the inputs switch simultaneously. Moreover, they assumed the delay of each gate is fixed and specified ahead of time.

Burch et al. [S] proposed to combine the simulation-based approaches with the probabilistic approaches to estimate the power of a circuit. The basic idea of their method is to apply randomly generated input vectors to the circuit and monitor, with a simulator, the resulting power value. Since this approach uses a finite number of patterns to estimate the average power, which really depends on the complete set of possible input patterns, this method belongs to the general class of so-called *Monte Carlo* methods. The total power is computed as the sum of the average power dissipated

at every internal node in the circuit. The average power dissipated at node i during the time interval T is evaluated as:

$$\frac{1}{2}V_{dd}^2C_i\frac{n_i(T)}{T}$$

where  $n_i(T)$  is the number of transitions at node *i* and  $C_i$  is the total capacitance at *i*. To make sure that the measured power is typical, the circuit has to be in its steady state. This is achieved by simulating the circuit for a period of time, which is called the *setup time*, before evaluating the power. A number of randomly generated input patterns are applied to the circuit until the power value obtained reaches a desired accuracy which is specified by the user. The authors are able to achieve excellent speed performance with this method; however, the computational cost increases as higher accuracy is desired. There is a specific problem in handling sequential circuits, where it is not clear how to obtain the *setup time*.

The CAD tool PowerPlay [9] developed by Krodel is designed to compute the instantaneous power waveform of a VLSI circuit design based on standard cells. First, analog simulation is employed to accurately compute the energy and the power waveform associated with each cell-type by taking into account the input transition and loading capacitances. Then, the power waveform is derived by approximating the original analog power waveform with a rectangle, where the area equals the corresponding energy and the height meets the peak power value. These power waveforms are stored in a data-base which is used together with the timing and transition information provided by a logic simulator to obtain the instantaneous power waveform of a circuit. The speed-up of PowerPlay is more than four orders of magnitude faster than SPICE and good accuracy is claimed for average power computation.

In [10], Dresig et al developed a method to compute the average dynamic power of a CMOS circuit based on the following equation derived in [11].

$$P_D = \frac{1}{2} V_{DD}^2 \cdot \sum_i f_i C_i$$

where  $f_i$  is the frequency of signal transitions at the output of gate *i*, and  $C_i$  is its load capacitance. It is assumed that the wiring capacitance is negligible, and hence  $C_i$  is the sum of the output capacitance  $C_o$  of the driving gate and the input capacitances  $C_{in_i}$ of the driven gates. The authors also assumed that the average output capacitance and input capacitance of all gates are constants. Therefore,

$$C_i = C_{out} + fanout_i \cdot C_{in}$$

where  $fanout_i$  is the gate fanout and  $C_{out}$ ,  $C_{in}$  are constants determined from technology parameters.

To relate  $f_i$  and the switching frequency, f, of the circuit, the authors defined  $a_i$  as follow:

$$a_i = \frac{f_i}{2f}$$

where  $a_i$  can be interpreted as the mean switching probability at node *i* during a clock cycle. As a result, the total power can be expressed as:

$$P_D = V_{DD}^2 \cdot f \cdot C_{in} \sum_i a_i \left(\frac{C_{out}}{C_{in}} + fanout_i\right)$$

(1.1)

The switching activity  $a_i$  is derived as the total number of switching  $A_i$  at node i divided by the number of cycles n, where  $A_i$  and n can be obtained through gate level simulations. Since the fanout of each internal node is known, the total average power is readily computed by Equation(1.1). The limitation of this approach is that short circuit current is not taken into account and heuristic is needed to tackle the signal correlation problem.

In [12], Vanoostende et al proposed to compute the maximal currents and maximal current derivatives of CMOS circuits using activity waveforms. The activity waveform consists of a set of parameter pairs describing the periods of time that a node can switch. To capture the switching activities associated with a node, the authors assumed that only one input of a gate switches at a certain time. Then, the input patterns that correspond to the fastest or slowest switching output is determined. Using the derived input patterns, the gate is simulated using the traditional circuit simulation method. The peak current observed during the simulation is used as the amplitude of the maximal current waveform of the gate. A trapezoid is used to approximate the maximal current waveform with a duration determined by the output activity intervals which are also computed from the simulation. The maximal current derivative waveform is approximated using a square shape, with a shorter duration than for the maximal current waveform. The total current waveform is obtained by adding the contributions of all logic gates in the circuit.

Landman et al proposed a power estimation technique for high level system architectures in [13]. The power consumption is determined by the system input statistics, where the input signal patterns are described by using three statistical parameters: mean, variance and correlation coefficient. From the input statistics, the statistics of its outputs are computed. By propagating statistics in this fashion, the statistical parameters for each internal bus are derived. Once the internal bus statistics are known, the bit transition probabilities( i.e. gate input transition probabilities) can be derived based on a stochastic model developed by the authors. Finally, the energy required to drive data with the given statistics onto a bus is computed from these bit probabilities. At present, the proposed method is limited to compute power for datapath components.

#### **1.2** Pattern-dependent current estimation techniques

In general, this approach involves using event driven simulation. The results of the timing analysis of the circuit are combined with the supply current waveform of each CMOS gate to obtain the total supply current. In principle, SPICE[14] is the most accurate approach. However, in order to find the worst case conditions, we have to

examine all possible combinations of the input signals. This is extremely expensive if it takes a considerable amount of CPU time, like SPICE, to compute each current waveform. Numerous methods have been developed to trade accuracy for speed. These are summarized in the following paragraphs.

In [15], the power dissipation of a single logic gate is computed by reducing the CMOS gate to an inverter circuit containing resistances and capacitances. The nonswitching transistors are replaced with resistors and capacitors whose values are determined by a set of parameters. These parameters are obtained by circuit simulations or by direct measurements. For more than one input switching, the switching transistors are combined and the equivalent input start time, and transition time, and transistor size are computed. The resulting nonlinear equations are solved by a method analogous to that used in SPICE but optimized for the inverter. The speed of this approach is claimed to be two orders of magnitude faster than conventional circuit simulators with an average error of 10% per logic cell.

In [16] and [17] methods are developed to find the worst case voltage drop in the power bus network. The program Hercules designed by Tyagi [16] used a table-lookup method to estimate the current. The authors used SPICE simulation to find the current information of a logic gate based on its input transition time,  $\beta$  ratio, and its loading capacitances. These factors are later combined into one variable called *risetime-ratio* which is used to index the look-up tables. To compute the current drawn by a circuit, the author decomposed it into *stages* which consist of a chain of transistors leading from a strong voltage source to an output node or a gate. The current drawn from a *stage* is computed using the tables and the worst case current drawn from a *stage* is obtained by assuming all transistors are fully on except the trigger transistor.

In [17], Stark and Horowitz proposed using the simulation tool Ariel to find the worst case voltage drop and current density in the power bus network of CMOS circuits. First, a resistor network is extracted from the circuit description using a Magicbased[17] resistance extractor. Then, a transistor level simulator RSIM[17] is used to generate node transition information. This procedure identifies the transistors that inject charge to the supply network and computes the inject current as

$$\frac{C_{load} \cdot V_{DD}}{T_{in}}$$

where  $T_{in}$  is the node transition time and  $C_{load}$  is the total capacitance at that node. From the analysis of RSIM, the current distribution of the resistive network is obtained. Finally a linear-tree-based algorithm is used to solve the branch currents and node voltages in the resistive network. In this approach, the short-circuit current is ignored which accounts for as high as 20% of the total supply current [18].

Similar to Hercules, SPIDER [19] is a CAD tool used to adjust the line width of a power bus. The transient current waveform at each identified node in the power bus is obtained through analysis of the individual subcircuits where SPICE is used to determine the subcircuit current waveforms. As a result, this process becomes very expensive as the number of inputs increase. Besides, it is hard to find the timing to cascade subcircuit outputs as inputs to its loading subcircuits.

Chowdhury and Barkatullah [20] used Shockley's transistor models to estimate the maximum current in CMOS logic circuits. For a general CMOS logic gate, the authors reduced it to an equivalent inverter depending on the sizes of the transistors in the pull-up and pull-down transistor sub-groups. Then, the current drawn by the inverter is obtained by solving the Kirchoff's current equations at the output node using the Forward-Euler method. The linear portion of the output transition is taken as input(s) to the loading gate(s) and the current associated with the loading gate is obtained similarly as the driving gate.

The above approach is implemented in the procedure CEST [20] to compute the current in a CMOS circuit in response to a particular input pattern. First, the logic gates in a given CMOS circuit are divided into stages. Then, stage numbers are assigned such that no gate in stage i is driven by a gate whose stage number is greater than or

¢

equal to *i*. This ensure that the inputs of a gate are known as functions of time before the gate is processed. The order of processing gates within the same stage does not matter. Therefore, the current and output voltage of each gate in the CMOS circuit can be computed in the order of its stage number, starting with the lowest stage number. The total current drawn from the circuit is obtained by adding the individual current associated with each gate which are switching.

To find the input pattern corresponding to the maximum current drawn in a CMOS circuit, the authors use a branch-and-bound algorithm. In order to reduce the computational cost of this algorithm, a heuristic method is developed. However, the solution obtained from the heuristic is only a local optimal. Besides, the above current model tends to increase delay in series networks and tends to decrease delay in a parallel networks because the authors assumed that all inputs of a gate are identical in arrival time and rise time. Finally, the computational cost of this method is high, because numerical integration is used to obtain the maximum current.

In [21], [22], [23], [24] and [25], methods are proposed to compute the current waveform of a circuit. In SIMCURRENT [21], a database of analog current waveforms is used to estimate the final current waveform of a circuit. This database keep records of both inverting and non-inverting current waveforms of a reference gate. Furthermore, simulated current waveforms of the reference gate with zero load up to maximum load is also kept in the database. The current waveform of a gate is determined from the database according to the total loading capacitance and the switching capacitance of the gate, where the switching capacitance  $C_{sw}$  of the processed gate is defined as the mean of the current consumption of the rising and falling edges of the output. The speed of this method is claimed to be three orders of the magnitude faster than SPICE. Its database is huge.

CURRANT [22] is a switch-level simulator that can generate current waveforms for VLSI circuits. The authors use a simple RC model to compute the peak drain source current of a transistor and model the decaying waveform as an exponential function.

$$I = I_o(e^{\frac{-\epsilon}{RC}})$$

where R and C are the resistance and capacitance of the transistor and  $l_0$  is its saturation current. The gate current is accounted for as the summation of the drain source current that flows to and from the node that a gate is connected to. CURRANT comprises three major components which work together to generate drain source current waveforms for each transistor in a circuit. First, the authors use RTL[22], a switch-level simulator, to simulate digital MOS circuits and obtain the timing and logic information. Then, they use ENTRACT[22], an interface module, to interface the RTL simulator with the waveform generating module GENERATE[22] which produces the drain source current waveforms for each transistor in the circuit, based upon the information that is extracted from RTL. The accuracy of this method is claimed to be within 10% of SPICE for a single logic gate.

Deng et al. [23] used a symmetric triangular current pulse to approximate the current waveform of a logic gate. This triangular pulse is uniquely specified by a triplet( $t_{peak}, I_{peak}, \Delta T$ ) where  $t_{peak}$  is the time that  $I_{peak}$  occurs, and  $\Delta T$  is the time duration of the triangular pulse.  $\Delta T$  is calculated from the precharacterized switch-level delay library based on the input rise/fall time and the RC delay parameter.  $t_{peak}$  is computed as:

$$t_{peak} = e.time + \frac{\Delta T}{2}$$

where *e.time* is the start time of the input transition. The current peak  $I_{peak}$  is computed as:

$$I_{peak} = 2 \times \frac{charge}{\Delta T}$$

where *charge* is the product of output node voltage swing and load capacitances at the output node. When the output load is large, the triangular pulse becomes asymmetric and better estimation can be achieved by using an asymmetric triangular pulse characterized by  $(t_{peak}, I_{prak}, \Delta T_1, \Delta T_2)$  where  $\Delta T_1$  and  $\Delta T_2$  are respectively the rising and falling times of the pulse. The speed of this method is claimed to be three orders of magnitude faster than SPICE with 20% accuracy.

Wang *et al.* [24] adopted a more complex model to approximate the current waveform of a CMOS gate. They divided the gate current waveform into three regions and the characteristic in each region is approximated by an exponential function. These three exponential functions are specified by four parameters which are functions of load capacitances, aspect ratios of MOS transistors, and the slopes of input signals. The authors stored these parameters in a database from which the corresponding current waveform of a gate can be constructed. More accurate results are obtained with this method as compare to [23] at the expense of a more complex database.

Rouatbi et al. [25] combined the timing analysis results of a CMOS circuit with the estimation of supply current waveforms for each logic gate to obtain the total supply current waveform of the circuit. The supply current waveform of a gate is found as a combination of the capacitive and short-circuit current waveforms which are restricted to certain basic forms. The basic capacitive and short-circuit current waveforms of a particular CMOS gate are characterized by a set of parameters. To compute these parameters, the authors collapsed the logic gate, and derived an analytical model from the collapsed gate. Then, they used a symbolic software package(Maple [26]) to solve the involved model equation for the waveform parameters.

In this approach, the individual capacitance contribution from the switched nodes are assumed independent of their position in the topology. The authors claimed that they have achieved 3-4 orders of magnitude speed-up with respect to SPICE with maximum 10% deviation in the obtained current waveforms.

In [27], Benini et al estimated the power dissipation in CMOS circuit using an approach derived from the *current-limited switch-level timing simulation* technique presented in [28]. It is assumed that the current drawn by a CMOS gate can have two possible values which are controlled by the gate-to-source voltage. Furthermore, the reactive effects are modeled as capacitors connected between circuit nodes and ground. Because the choice of the model, no integration is needed during the computation of the time domain responses. Modifications have been made to the approach described in [28] in order to allow the simulation of non-fully-complementary CMOS circuits with increased accuracy and robustness. The event-driven simulator built by the authors is capable of handling different types of CMOS digital circuits including pass-transistors and sequential logic with positive feedback loops. The authors claimed that the speed of their method is 2 orders of magnitude faster than SPICE with an error lower than 10%.

#### **1.3** Motivation and overview of thesis

In [29], an inverter-base model was presented to compute the maximum current and delay of a CMOS gate without integration. The speed of this model is three orders of magnitude faster than SPICE, and it is more accurate than other models that have been reported. The model takes into account the sizes of the devices, output load, input transition time, input transition positions, and short-circuit current in computing the current waveforms. A relatively small database is needed. From the test results presented in [29], this model has an excellent performance in predicting the maximum current and its time of occurrence. It is also capable of producing an accurate current waveform of a gate. Therefore, its application to large VLSI circuits is promising.

In order to test the speed and accuracy of this model on large circuits with a large number of test vectors, an analysis program was needed. In this thesis, the approach presented in [29] is implemented in an event-driven simulation program CUREST which is based on the timing analysis tool TAMIA [31]. The information on the circuit topology as well as the input patterns are provided by TAMIA while the current waveforms of the circuit are computed by CUREST.

The outline of this thesis is presented as follows. In Chapter 2, the current model proposed in [29] is reviewed, which is followed by the current estimation algorithm in Chapter 3. The accuracy and speed of CUREST are analysed in Chapter 4. Finally, conclusions are made and future work is discussed in Chapter 5.

### Chapter 2

### Delay and current models

In this chapter, we review the models that were developed by Nabavi-Lishi [29] to evaluate the supply current and the delay in a CMOS gate, and which we used in the design of CUREST. It is important to understand how these models work in order to appreciate how CUREST is constructed.

#### 2.1 Inverter Model

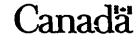

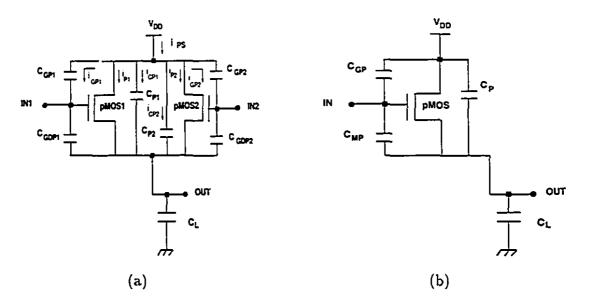

A transistor-level model of an inverter is shown in Figure 2.1, where the parasitic capacitunces are shown explicitly.  $C_{GP}(C_{GN})$  represented the gate-to-source and the gate-to-bulk capacitances of the pMOS(nMOS) transistor while  $C_P(C_N)$  represented the sum of drain-to-bulk capacitance of the pMOS(nMOS) transistor and the  $C_{GP}(C_{GN})$  of the loading pMOS(nMOS) transistors.  $C_M$  includes the gate-to-drain capacitances of both the pMOS and the nMOS transistors. These parasitic capacitances are replaced by equivalent constant values which will be discussed in Section 2.4.

The supply current  $i_{PS}$  is computed from the three branch currents  $i_{GP}$ ,  $i_{CP}$  and  $i_{P}$ . From HSPICE simulation and experiment, it is observed that there is only one current

Figure 2.1: (a) Transistor-level model of a CMOS inverter. The effect of the loading gate(s) is included in  $C_N$  and  $C_P$ . (b) Charging and discharging currents of the inverter shown in (a) when driven by another inverter.  $i_{PS}(-)$ ,  $i_{GP}(0)$ , and  $i_{CP}(-)$  [29].

peak associated with a charging output node. The current model used to evaluate this peak is called the CP model. In order to compute the charging current of an inverter accurately, a CW model is developed. When the output is discharging, as illustrated in Figure 2.1(b), the supply current shows both a current maximum, DP, and a current minimum, DN. The models used to compute these two peaks are called the DP model and DN model respectively. As will be explained in section 2.5, the DN peak is rarely computed explicitly and hence, the DN model will not be presented. All these models are based on the assumption of a ramp voltage input.

## 2.2 Inverter with falling input transition: CP and CW Models

In this section, the models that are used to compute the maximum current and delay of a charging inverter i.e. an inverter with a falling input transition are presented. To compute the charging current either CP or CW model can be used. The CP model is presented first.

#### 2.2.1 CP model

When the input falls from  $V_{DD}$  to  $V_{DD} - |V_{tp}|$ , where  $V_{tp}$  is the threshold voltage of the pMOS transistor, the pMOS transistor enters the saturation region. At this moment, the supply current  $i_{PS}$  is dominated by  $i_P$  which carries both the short-circuit and load currents. For a charging output,  $i_P$  is much greater than  $i_N$  and hence  $i_{CP}$  tracks  $i_P$ . Now  $i_P$  will reach its maximum before the pMOS transistor enters the triode region, but not later than when the input transition is complete. For this reason, and also because  $i_{GP}$  becomes zero when the input transition is completed, it follows that the maximum in  $i_{PS}$  must occur at:

$$t_m = \min(t_{st}, T_i) \tag{2.1}$$

where  $t_{st}$  is the time when pMOS leaves the saturation region and  $T_i$  is the input transition time. In order to obtain an explicit expression for  $t_{st}$ , the output voltage  $v_o(t_{st})$  at time  $t_{st}$  is required. To find  $v_o(t_{st})$ , a simple ramp approximation of the output voltage is used for which the transition time  $T_o$  is given by:

$$T_{o} = aT_{i} + b \frac{V_{DD}(C_{N} + C_{P})}{I_{P}}$$

(2.2)

where  $I_P$  is the pMOS drain current corresponding to  $v_{SG} = v_{SD} = V_{DD}$ , and a, b are empirical parameters obtained by fitting the delay and maximum current of a minsized symmetric inverter computed by the CP model to that obtained from HSPICE simulation. The output voltage can be approximated in any manner of our choice as long as it produces an accurate value of the output voltage at the time  $t_{st}$ . A ramp is used because of its simplicity.

At time  $t_{st}$ , the source-to-drain voltage of the pMOS transistor is equal to  $V_{DSATP}$ , the pMOS transistor's drain saturation voltage. In order to obtain a closed-form solution for the time  $t_{st}$ , the long-channel approximation has to be used for  $V_{DSATP}$ . This would possibly lead to the resulting HSPICE MOS-3 model overestimating the drain current. However, it has been shown in [29] that, by setting the static feedback parameter ETA to zero, good agreement is obtained with respect to the HSPICE MOS-3 model for operation near pinch-off. Therefore, by combining Eq.( 2.2) with the long-channel approximation for  $V_{DSATP}$ ,  $t_{st}$  is given by:

$$t_{st} = \frac{T_i(1 + FB_p + \frac{V_{tp0}}{V_{DD}})}{1 + \frac{T_i}{T_0}(1 + FB_p)}$$

(2.3)

where  $FB_p$  is a SPICE technology constant for the pMOS transistor, and  $V_{tp0}$  represents its threshold voltage. Once  $t_{st}$  is known,  $t_m$  can be easily determined from Eq.( 2.1).

Hence,  $v_o(t_m)$  and  $v_{in}(t_m)$  are obtained from:

$$v_o(t_m) = V_{DD} \cdot \frac{t_m}{T_o}$$

$$v_{in}(t_m) = V_{DD}(1 - \frac{t_m}{T_{IN}})$$

This permits the determination of  $i_P(t_m)$  and  $i_N(t_m)$ . Moreover, the first derivative of the output voltage at  $t_m$ , which is also taken as the effective slope of the input to the loading gate, can be computed from:

$$\alpha_m \equiv \frac{dv_O}{dt}|_{t=t_m} = \frac{i_P(t_m) - i_N(t_m) - C_M \frac{V_{DD}}{T_i}}{C_N + C_P + C_M}$$

(2.4)

Now, the maximum supply current  $i_{PS}(t_m)$  can be obtained as the sum of three branch currents  $i_P$ ,  $i_{CP}$  and  $i_{GP}$ . Since  $i_P(t_m)$  is already known, only two branch currents have to be computed:

$$i_{CP}(t_m) = C_P \cdot \alpha_m$$

$$i_{GP}(t_m) = C_{GP} \cdot \frac{V_{DD}}{T_i}$$

To find the delay, which is defined as the difference between the time when the input and output voltages reach  $V_{DD}/2$ , the fact that  $v_O(t_m)$  lies within the approximately linear region of the output voltage is utilized. This means that a straight line with slope  $\alpha_m$  can be used to extrapolate from  $v_O(t_m)$  to  $v_o = V_{DD}/2$  and the delay can be computed as:

$$\tau = t_m + \frac{\frac{V_{DD}}{2} - v_O(t_m)}{\alpha_m} - \frac{T_i}{2}$$

In general, the accuracy of the models presented above depends on both the range of  $T_i$  and the  $\beta$ -ratio in the inverter. For a symmetric inverter ( $\beta_p = \beta_n$ ), with a = 0.86and b = 3.18,  $i_{PS}(t_m)$  is determined with a 10% error for a range of  $T_i$  from 1 to 100ns, for the 0.8, 1.2 and 3.0 microns technologies. For asymmetric inverters, a look-up table or empirical equations are used to adjust the coefficients a and b to meet the requirements on the range of  $T_i$  and the  $\beta$ -ratio as illustrated in Table 2.1.

#### 2.2.2 CW model

The CW model can be used to compute the charging current of an inverter. This is obtained in two steps. First the supply current is computed for the time interval  $[0,t_m]$ , where  $t_m$  is the time when the supply current is maximum, and then the remaining part of the supply current is evaluated for  $t > t_m$ .

For  $t \in [0, t_m]$ , the pMOS transistor operates mostly in the saturation region and its drain saturation current is relatively independent of the output voltage. Therefore,  $i_P$ can be computed without having to estimate accurately the output voltage. It follows

| range of $W_p/W_n$ | а    | ь    |

|--------------------|------|------|

| 12.5-15.5          | 0.50 | 7.00 |

| 9.5-12.5           | 0.58 | 4.00 |

| 7.5-9.5            | 0.62 | 4.00 |

| 6.5-7.5            | 0.65 | 4.00 |

| 5.5-6.5            | 0.67 | 4.00 |

| 4.0-5.5            | 0.72 | 3.80 |

| 3.2-4.0            | 0.79 | 3.20 |

| 2.9-3.2            | 0.81 | 3.30 |

| 2.5-2.9            | 0.86 | 3.18 |

| 1.3-2.5            | 0.99 | 2.90 |

| 0.7-1.3            | 1.10 | 3.00 |

| 0.3-0.7            | 1.30 | 2.80 |

Table 2.1: Appropriate values of a and b obtained for a 1.2 micron technology [29].

that the supply current  $i_{PS}$  is obtained by evaluating  $i_P$  using the preceding method, and then by adding  $i_P$  to  $i_{GP}$  and  $i_{CP}$ , obtained as follows:

$$i_{GP} = C_{GP} \times \frac{V_{DD}}{T_i}$$

$$i_{CP} \approx -C_P \times \frac{V_{DD}}{T_0},$$

where  $T_i$  is the input transition time and  $T_0$  is defined by Eq.(2.2).

For  $t > t_m$ , the supply current is calculated using an integration method because accurate output voltage is needed to evaluate  $i_P$  in the triode region.  $v_o(t_m)$ ,  $i_P(t_m)$  and  $i_N(t_m)$  obtained with the CP model are used as initial conditions to compute the supply current  $i_{PS}$  using the first order Euler integration method. The derivative of the output voltage at each time point is given as:

$$\frac{dv_o}{dt} = \frac{i_P(t) - i_N(t) - C_M \frac{V_{DP}}{T_*}}{C_N + C_P + C_M}$$

In order to avoid instability during the integration process, it is required that the following conditions should be satisfied.

$$\frac{dv_o}{dt} \ge 0,$$

$$v_o(t + \delta t) \ge v_o(t),$$

$$v_o \le V_{DD}$$

The integration stops when  $v_o$  reaches  $V_{DD}$ . It is shown by experimental results that accuracy considerations in computing  $i_{PS}$  always limit the step size to a value where instability cannot occur. A typical integration time step is found to be:

$$\delta t = 0.02 \times T_i$$

#### 2.3 Inverter with rising input: DP model

The supply current associated with a falling output voltage is characterized by a negative "peak" followed by a positive one. The DP model is used to compute the latter, while the DN model is design for the former.

For a discharging inverter, the supply current  $i_{PS}$  is dominated by the short circuit current  $i_P$ , which reaches it maximum at the pinch-off point of the pMOS transistor. To determine the time  $t_{mp}$  at which maximum  $i_P$  occurs, a similar approach is used to that for the CP model. Thus  $t_{mp}$  is computed from Eq.(2.3) where the coefficients a and b, used to determine  $T_o$  from Eq.(2.2), are replaced by a different set, c and d, respectively. The maximum current calculations proceeds as in the CP model.

Since the output voltage at time  $t_{mp}$  has not yet reached the linear region, we cannot use  $v_o(t_{mp})$  and  $t_{mp}$  to compute the delay. However, at time  $t_{stn}$  when the nMOS leaves the saturation region, the output voltage can be taken as linear and hence it can be used to calculate the delay. In this case, another ramp approximation is needed to predict  $v_o(t_{stn})$  at  $t_{stn}$  accurately. Thus,

$$t_{sin} = \frac{T_i(1 + FB_n + \frac{V_{inO}}{V_{DD}})}{1 + \frac{T_i}{T_{O2}}(1 + FB_n)}$$

where

$$T_{O2} = eT_i + f \frac{V_{DD}(C_N + C_P)}{I_N}$$

(2.5)

$V_{tnO}$  is the threshold voltage for nMOS transistor corresponding to modified HSPICE model,  $FB_n$  is a HSPICE level-3 technology constant for the nMOS transistor, e and f are empirical constants, and  $I_N$  is the drain current for the nMOS transistor at  $v_{GS}=v_{DS}=V_{DD}$ .

Now, the delay can be computed as:

$$\tau = t_{stn} + \frac{\frac{V_{DD}}{2} - v_{On}}{\alpha_{stn}} - \frac{T_i}{2}$$

where

$$v_{On} = V_{DD} (1 - \frac{t_{stn}}{T_{O2}})$$

and

$$\alpha_{stn} \equiv \frac{dv_O}{dt} \mid_{t=t_{stn}} = -\frac{i_P(t_{stn}) - i_N(t_{stn}) + C_M \frac{V_{DD}}{T_i}}{C_N + C_P + C_M}$$

Since the charging current contributes the major part of the total supply current, the accuracy in computing the total current in a combinational circuit depends mainly on accurate calculation of the charging supply current. Therefore, we do not have to develop a "DW" model to approximate the discharging current waveform accurately. The DP model is used in all discharging cases, and the waveform is approximated by a triangle(Section 2.5).

#### 2.4 Computing parasitic capacitances in an inverter

In this section, we review how the parasitic capacitances associated with an inverter are evaluated and replaced with constant values. A pMOS transistor is chosen as an example to demonstrate the evaluation processes which are equally valid for nMOS transistor.

#### Computing $C_{GP}$ :

The capacitance  $C_{GP}$  of a pMOS transistor comprises the effects of gate-to-bulk, gateto-source and gate-over-channel capacitances. Since a pMOS transistor with falling input is in saturation for most of the transition time,  $C_{GP}$  is computed as:

$$C_{GP} = CF5 \cdot Cap_p + CGSOp \cdot W_p + CGBOp \cdot L_p \quad for \ falling \ inputs \qquad (2.6)$$

By the same token,  $C_{GN}$  is given as:

$$C_{GN} = CF5 \cdot Cap_n + CGSOn \cdot W_n + CGBOn \cdot L_n \quad for \ rising \ inputs \qquad (2.7)$$

where

$$Cap_{p} = \frac{\epsilon_{OX}}{t_{OX}} \cdot W_{p} \cdot L_{p},$$

$$Cap_{n} = \frac{\epsilon_{OX}}{t_{OX}} \cdot W_{n} \cdot L_{n},$$

$L_p(L_n)$  and  $W_p(W_n)$  are respectively, the channel length and device width of the pMOS(nMOS) transistor,  $t_{OX}$  is the gate oxide thickness,  $c_{OX}$  is the oxide dielectric constant, CF5 is a user-definable constant in HSPICE with a default value of 2/3, CGSOp(CGSOn) and CGBOp(CGBOn) are the gate-to-source and gate-to-bulk overlap capacitances per meter of channel width for the p-type(n-type) transistor. When transistors operate in triode region,  $C_{GP}$  and  $C_{GN}$  are computed as:

$$C_{GP} = Cap_{p} \cdot CF5 \cdot K_{vp} + CGDOp \cdot W_{p} + CGBOp \cdot L_{p} \quad for \ rising \ inputs$$

$$C_{GN} = Cap_{n} \cdot CF5 \cdot K_{vn} + CGDOn \cdot W_{n} + CGBOn \cdot L_{n} \quad for \ falling \ inputs$$

where  $K_{vp}$  and  $K_{vn}$  are voltage-dependent coefficients used in HSPICE capacitance equations. From HSPICE simulations,  $K_{vp}$  equals to  $K_{vn}$  which has a average value 3/4 provided CF5 = 2/3.

#### Computing $C_P$ :

The equivalent capacitance  $C_P(C_N \text{ for nMOS})$  includes the drain-to-bulk capacitance  $C_{DB}$  and the input capacitances of the loading gate(s). The drain-to-bulk capacitance of a transistor can be evaluated as follow:

$$C_{DB} = K_{\epsilon}(C_j \cdot AD + C_{jsw} \cdot PD) \tag{2.8}$$

where  $C_j$ ,  $C_{jsw}$ , AD, PD are HSPICE parameters, and  $K_e$  is a constant determined by using HSPICE simulation. For 1.2 micron technology,  $K_e = 0.615$  for pMOS transistor and  $K_e = 0.127$  for nMOS transistor. The total input capacitance  $C_{IN}$  is equal to:

$$C_{IN} = C_{GP} + C_{GN} + \overline{C_M}$$

where  $C_{GP}$ ,  $C_{GN}$  and  $C_M$  are equivalent capacitances of the loading gates, and  $\overline{C_M} \approx 1.5 \cdot C_M$  for 1.2 micron technology. To account for the overlap currents between the driving and loading gates which will be discussed in Section 2.5, the capacitances  $C_{GP}$  and  $C_{GN} + \overline{C_M}$  of the loading gate are added, respectively, to  $C_P$  and  $C_N$  of the driving gate.

#### Computing $C_{MP}$ :

When a pMOS transistor is in triode region, the gate-to-drain capacitance is given by:

$$C_{GDP} = Cap_{p} \cdot CF5 \cdot K_{vp} + CGDO_{p} \cdot W_{p}$$

In saturation, the drain side of the channel is pinched off, and hence only the second term which corresponds to overlap capacitance contributes. From simulation, the average value of  $K_{vp}$  and  $K_{vn}$  for 1.2 micron technology are respectively,

$$\overline{K_{vp}} = 0.43/CF5$$

, and  $\overline{K_{vn}} = 0$  for a rising input

$$\overline{K_{vn}} = 0.43/CF5$$

, and  $\overline{K_{vp}} = 0$  for a falling input.

Therefore,

$$C_{MP} = \begin{cases} 0.43 \cdot Cap_p + CGDOp \cdot W_p & \text{for a rising input;} \\ CGDOp \cdot W_p & \text{for a falling input} \end{cases}$$

and

$$C_{MN} = \begin{cases} CGDOn \cdot W_n & \text{for a rising input;} \\ 0.43 \cdot Cap_n + CGDOn \cdot W_n & \text{for a falling input} \end{cases}$$

#### 2.5 Current calculation in an inverter chain