# Analog-to-Digital Conversion via Time-Mode Signal Processing

Christopher Taillefer, (B.Eng. 2000, M.Eng. 2003)

Department of Electrical and Computer Engineering

McGill University, Montréal

August 2007

### **Abstract**

Conventional voltage-mode analog-to-digital converters use voltage amplifiers, voltage comparators, and switch capacitor networks to perform their signal processing. When compared to digital circuitry, these analog circuit blocks consume significant power, occupy large silicon areas, and operate at relatively slow data processing speeds. A signal processing methodology is proposed that performs analog-to-digital conversion on voltage signals while implementing all the circuits in a digital CMOS logic style. This methodology, called *time-mode signal processing*, uses time-difference variables as an intermediate signal between the input voltage and digital output. The resulting silicon devices offer very compact, low power, high-speed, and robust analog-to-digital converter alternatives.

There are five main analog-to-digital converter topologies: flash, successive-approximation, pipeline, delta-sigma, and integrating converters. Each converter topology is presented in the context of the time-mode signal processing methodology. The circuits that implement each time-mode data converter are described and when appropriate system-level, transistor-level, and experimental results are revealed.

Three integrated circuits (IC) were fabricated in a 0.18-µm CMOS technology to demonstrate the feasibility of the time-mode ADC methodology. The first IC

implemented the time-mode comparator and a time-mode flash ADC. The time-mode delta-sigma ADC design was demonstrated in the second IC. Two circuits were implemented in the third IC: a differential-input time-mode delta-sigma ADC and a cyclic (or algorithmic) ADC.

### Résumé

Les convertisseurs conventionnels pour changer la tension analogique à une tension numérique emploient les amplificateurs de tension, les comparateurs de tension, et les résaux de condensateur sélectionable pour acquir leur traitement de signal. En comparaison le circuit des modules analogues vis-à-vis le circuit numérique nous constatons une augmentation de puissance, une superficie de silicium moins compacte, et un traitement de données beaucoup plus lent. Une méthodologie est proposée pour le traitement du signal qui établi la conversion analogue à numérique sur les signaux de tension et tout en mettant en oeuvre tous les circuits dans un format numérique de type circuit à semiconducteur oxyde-métal à symétrie complémentaire (CMOS). Cette méthodologie reconnue sur le nom de technique-temporelle donne un traitement de signal par domaine temporel en employant la variance de cadence entre les temps comme un signal intermédiare entre la tension d'entrée et la tension de sortie numérique. Les formats numériques de type circuit semiconducteur nous offrent une alternative en temps convertisseur d'analogue à numérique avec l'avantage d'une unité compact, robuste, un coût de puissance réduit, et une haute-vitesse efficace.

Il existe cinq topologies principales dans les convertisseurs analogiques à numérique: flash, approximations successives, pipeline, delta-sigma, convertisseurs intégrés. Dans chacune des topologies mentionnées ci-dessus, le traitement de signal par technique-temporelle est une méthode réconnue.

Les circuits employés par chaque convertisseur de donnée par techniquetemporelle sont décrits lorsque le niveau du système est approprié, le niveau du transitor, et les données expérimentales sont identifiés.

Trois circuits intégrés (CI) ont été conçus et fabriqués, avec une technologie de 0,18-µm CMOS pour démontrer la possibilité de la méthodologie du technique-temporelle convertisseur analogique-numérique (CAN). Le premier CI emploie le technique-temporelle comparateur et Flash CAN. La conception de technique-temporelle delta-sigma CAN a été démontrée avec le deuxième CI. Deux circuits ont été conçus et fabriqués dans le troisième CI. Une entrée différentielle technique-temporelle delta-sigma CAN et un CAN à cyclique (ou algorithmique).

## **Acknowledgements**

I would like to express my deepest gratitude towards my supervisor, Dr. Gordon W. Roberts. His enthusiasm, dedication, and understanding have made my Ph.D. degree enjoyable, intellectually stimulating, and very rewarding. Dr. Roberts' leadership and mentorship is truly one-of-a-kind; offering technical guidance, friendship, and professional advice always at the perfect time. I would also like to thank my Ph.D. committee members, Dr. Zeljko Zilic and Dr. Roni Khazaka for their invaluable support and advice.

To all the members of the MACS lab I would like to offer my appreciation for their friendship and support. Collectively, they are a tremendous pool of knowledge for which I could not have succeeded without. Specifically, I would like to thank Mona Safi-Harb for all her advice and technical support throughout the years.

Being a student is stressful, and at times emotionally challenging. I would like to thank my wife and best friend, Michelle, for being so patient and understanding while I struggled to complete this thesis. She is my greatest source of encouragement and support. I am also incredibly grateful to all my family and friends who brought social balance into my life.

Finally, I must acknowledge the Natural Science and Engineering Council of Canada, le Fonds de Recherche sur la Nature et les Technologies du Québec, and the Walter C. Sumner Foundation for their outstanding financial contributions. Moreover, the work presented in this thesis could not have been completed without the integrated circuit fabrication facilities and computer-aided design software infrastructure offered by CMC Microsystems.

## **Claim of Originality**

The contributions of this dissertation are described as follows:

- The concept of time-mode signal processing (TMSP) is utilized in Chapter 3 whereby time-difference variables are used as an intermediate processing variable in the conversion of analog voltages into digital signals. The merits and limitations of analog-to-digital conversion via TMSP are investigated. Specifically, TMSP offers the advantages of compact, low power, and high-speed operation through a digital implementation of the analog-to-digital processing. However, resolution and linearity are sacrificed due to limited linear input voltage range.

- The circuit building blocks to convert voltage-to-time, process time, and convert time-difference variables into digital data are presented in Chapter 3. A critical building block, known as the voltage-to-time converter (VTC), is developed. The VTC is composed of two voltage-controlled delay circuits and two CMOS implementations are revealed. Other TMSP blocks are described such as voltage-to-time adders, voltage-to-time integrators, time-amplifiers, time comparators, and time-to-digital converters. The implementations of these circuits and their limitations are described in detail. Signal-processing blocks which are not easily realizable are also described.

- A comparator constructed from TMSP blocks is presented in Chapter 4. Using a VTC and a time comparator a very simple and compact voltage comparator is realized, called a *time-mode comparator*. Using only digital circuitry, a calibration mechanism is introduced to remove the mismatch effects that would otherwise result in input-referred voltage offsets. Furthermore, the calibration circuitry is incorporated in the regular operation of the comparator and thus compensates for its own error contribution. An integrated circuit was fabricated implementing a time-mode comparator with calibration and the experimental results are presented in Section 4.4.

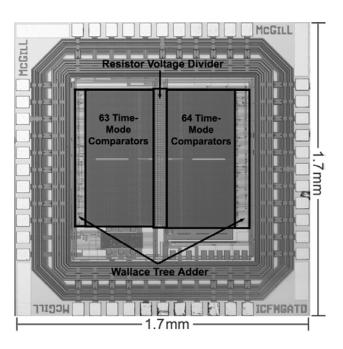

- Two flash ADC architectures are presented in Chapter 5 which take advantage of TMSP. The first flash ADC topology using a VTC followed by a time-to-digital converter. The advantages and limitations of this circuit are investigated. The second flash ADC design is built conventionally using 2<sup>N</sup>-1 time-mode comparators and a resistor voltage divider circuit. A 7-bit flash ADC was fabricated in an integrated circuit and its experimental results are presented in Section 5.4.

- The design of first-order delta-sigma ADCs is explained in Chapter 6. It is constructed from two VTCs and a time comparator which offers an incredibly compact, low power, and high-speed design. Both single-ended-input and differential-input time-mode delta-sigma ADC designs are described in detail and they were fabricated in two separate integrated circuits. Their experimental results are presented in Section 5.4. Higher-order modulation and multi-bit quantization are discussed along with there implementations and limitations.

- The design of pipeline and cyclic ADCs using TMSP are presented in Chapter

7. They are constructed from VTCs, time-amplifiers, time-comparators, and digital logic. The time amplifier was modified from the circuit reported in [29] to provide the appropriate gain. An integrated circuit incorporating a cyclic

ADC was fabricated and the experimental results are presented in Section 7.3.

• The design of integrating and successive approximation register (SAR) ADCs using the TMSP methodology are discussed in Chapter 8. The time-mode SAR ADC is implemented with a time-mode comparator, a DAC, a sample-and-hold, digital control logic, and a register. The time-mode integrating ADC is composed of a time-mode integrator and digital logic. Although they were not fabricated, these designs are discussed along with MATLAB simulations to illustrate their operation.

Some of the work described in this thesis was presented at international conferences. Specifically, the time-mode comparator along with its calibration mechanism was presented at the 2006 International Symposium on Circuits and Systems. The single-ended input time-mode delta-sigma ADC was presented at the 2007 International Symposium on Circuits and Systems. This paper was awarded the second prize in the Best Student Paper competition which resulted in two invitations to journal publications in the Transactions on Circuits and Systems I.

# **Table of Contents**

| Abstract                                 | i        |

|------------------------------------------|----------|

| Résumé                                   | iii      |

| Acknowledgements                         | <b>v</b> |

| Claim of Originality                     | vii      |

| Table of Contents                        | x        |

| List of Figures                          | xv       |

| List of Tables                           | xxi      |

| List of Acronyms                         | xxiii    |

| Chapter 1: Introduction                  | 1        |

| 1.1 - Motivation                         | 1        |

| 1.2 - Thesis Scope                       | 4        |

| 1.3 - Thesis Overview                    | 4        |

| Chapter 2: Analog-to-Digital Conversion  | 7        |

| 2.1 - ADC Design Specifications          | 9        |

| 2.1.1. Signal Bandwidth or Sampling Rate | 10       |

| 2.1.2. Resolution                        | 11       |

| 2.1.3. Distortion                        | 11       |

| 2.1.4. Dynamic Range                                                  | 11 |

|-----------------------------------------------------------------------|----|

| 2.1.5. Power                                                          | 12 |

| 2.1.6. Area                                                           | 12 |

| 2.1.7. Noise Immunity                                                 | 12 |

| 2.1.8. Latency                                                        | 13 |

| 2.2 - ADC Performance Metrics and Figures of Merit                    | 13 |

| 2.2.1. Gain and Offset Error                                          | 13 |

| 2.2.2. Integral Nonlinearity                                          | 14 |

| 2.2.3. Differential Nonlinearity                                      | 15 |

| 2.2.4. Signal-to-Noise Ratio                                          | 15 |

| 2.2.5. Signal-to-Noise-and-Distortion Ratio                           | 15 |

| 2.2.6. Effective Number of Bits                                       | 16 |

| 2.2.7. Total Harmonic Distortion                                      | 16 |

| 2.2.8. Spurious-Free Dynamic Range                                    | 16 |

| 2.2.9. Figures of Merit                                               | 17 |

| 2.3 - Conventional Analog-to-Digital Converters                       | 17 |

| 2.3.1. Flash Analog-to-Digital Conversion                             | 18 |

| 2.3.2. Pipeline and Cyclic Analog-to-Digital Conversion               | 20 |

| 2.3.3. Successive Approximation Register Analog-to-Digital Conversion | 22 |

| 2.3.4. Delta-Sigma Analog-to-Digital Conversion                       | 23 |

| 2.3.5. Integrating Analog-to-Digital Conversion                       | 26 |

| 2.4 - Summary                                                         | 28 |

| Chapter 3: Time-Mode Signal Processing Circuits                       | 29 |

| 3.1 - Voltage-to-Time Conversion                                      | 30 |

| 3.1.1. Voltage-Controlled Delay Unit                                  | 30 |

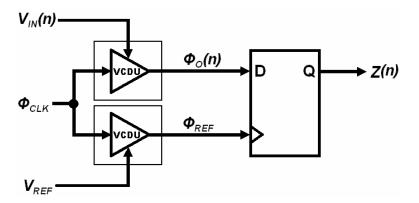

| 3.1.2. Voltage-to-Time Converter                                      | 41 |

| 3.2 - Time-Mode and Mixed-Mode Signal Processing                      | 42 |

| 3.2.1. Voltage-to-Time Adder                                          | 43 |

| 3.2.2. Voltage-to-Time Integrator                                     | 44 |

| 3.2.3. Time Amplifier                                                 |    |

| 3.2.4. Delay Elements                                                 | 49 |

| 3.3 - Time-to-Digital Conversion                                      | 49 |

| 3.3.1. Time Comparator                                                | 49 |

| 3.3.2. Time-to-Digital Converter                                | 50 |

|-----------------------------------------------------------------|----|

| 3.4 - Time-Mode Signal Processing Advantages and Disadvantages  | 51 |

| 3.5 - Summary                                                   | 52 |

| Chapter 4: Time-Mode Voltage Comparator                         | 54 |

| 4.1 - Time-Mode Voltage Comparator                              | 54 |

| 4.2 - Time-Mode Comparator with Calibration                     | 57 |

| 4.3 - Integrated Circuit Implementation                         | 60 |

| 4.4 - Experimental Results                                      | 62 |

| 4.5 - Conclusion                                                | 63 |

| Chapter 5: Time-Mode Flash ADC                                  | 66 |

| 5.1 - Time-Mode Flash ADC using Time-Mode Voltage Comparators   | 66 |

| 5.2 - Time-Mode Flash ADC using Voltage-to-Time Converter & TDC | 68 |

| 5.3 - Integrated Circuit Implementation                         | 69 |

| 5.4 - Experimental Results                                      | 70 |

| 5.5 - Summary                                                   | 73 |

| Chapter 6: Time-Mode Delta-Sigma ADC                            | 75 |

| 6.1 - Design Methodology                                        | 75 |

| 6.2 - Implementation Issues                                     | 79 |

| 6.2.1. Non-Uniform Sampling                                     | 79 |

| 6.2.2. Synchronization                                          | 80 |

| 6.2.3. Mismatch                                                 | 80 |

| 6.2.4. Jitter Noise                                             | 81 |

| 6.2.5. Flip-Flop Metastability                                  | 81 |

| 6.2.6. VCDU Non-Linearity                                       | 82 |

| 6.3 - Single-Ending Input Implementation                        | 82 |

| 6.3.1. Mathematical Modeling with MATLAB and Simulink           | 82 |

| 6.3.2. Low-Speed TMΔΣADC Transistor Design and Simulation       | 84 |

| 6.3.3. High-Speed TMΔΣADC Transistor Design and Simulation      | 86 |

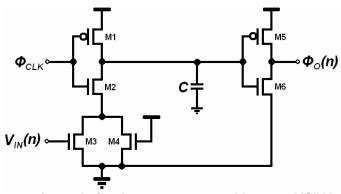

| 6.4 - Differential-Input Implementation                         | 88 |

| 6.4.1. Mathematical Modeling with MATLAB and Simulink           | 89 |

| 6.4.2. Transistor Schematic and Simulation                      | 80 |

| 6.5 - Higher-Order TMΔΣADCs                                             | 92         |

|-------------------------------------------------------------------------|------------|

| 6.6 - Multi-Bit TMΔΣADCs                                                | 92         |

| 6.7 - Single-Ended Input IC Prototype and Experimental Results          | 95         |

| 6.7.1. Integrated Circuit Implementation and Experimental Setup         | 95         |

| 6.7.2. High-Speed TMΔΣADC Experimental Results                          | 96         |

| 6.7.3. Low-Speed TMΔΣADC Experimental Results                           | 98         |

| 6.8 - Differential-Input IC Prototype and Experimental Results          | 100        |

| 6.8.1. Integrated Circuit Implementation                                | 100        |

| 6.8.2. Experimental Results                                             | 102        |

| 6.9 - Comparisons and Discussion                                        | 105        |

| 6.9.1. Single-Ended Input Design: High-Speed versus Low Speed Compariso | n105       |

| 6.9.2. Single-Ended Input Design: MATLAB Model versus HSPICE Transistor | r          |

| Simulations                                                             | 106        |

| 6.9.3. Single-Ended Input Design: HSPICE Transistor Simulations versus  |            |

| Experimental Results                                                    | 106        |

| 6.9.4. Single-Ended versus Differential-Input Design                    | 107        |

| 6.9.5. TMΔΣADCs versus other Designs                                    | 108        |

| 6.10 - Conclusion                                                       | 110        |

| Chapter 7: Time-Mode Pipeline and Cyclic ADC                            | .111       |

| 7.1 - Pipeline Stages and Cyclic ADC                                    | 111        |

| 7.1.1. Pipeline ADC                                                     |            |

| 7.1.2. Cyclic or Algorithmic ADC                                        |            |

| 7.2 - Integrated Circuit Prototype and Implementation                   |            |

| 7.2.1. Voltage-to-time Converters                                       |            |

| 7.2.2. Time Amplifier                                                   |            |

| 7.2.3. Digital-to-Analog Converter                                      |            |

| 7.2.4. Time Comparator                                                  |            |

| 7.2.5. Digital Output Circuitry                                         | 118        |

| 7.3 - Experimental Results                                              |            |

| 7.4 - Conclusion                                                        |            |

| Chapter 8: Successive Approximation and Integratin                      |            |

| Chapter of Successive Approximation and integration                     | <b>'</b> 9 |

| ADCs                                                                    | 125        |

| 8.1                            | Successive Approximation Register ADCs                                                                                                                                              | 125                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 8.                             | 1.1 Time-Mode SAR ADC MATLAB Modeling and Simulation                                                                                                                                | 126                                    |

| 8.                             | 1.2 Implementation Details and Practical Limitations                                                                                                                                | 128                                    |

| 8.2                            | Integrating ADCs                                                                                                                                                                    | 128                                    |

| 8.                             | 2.1 Time-Mode Integrating ADC MATLAB Modeling and Simulation                                                                                                                        | 130 m                                  |

| 8.                             | 2.2 Implementation Details and Practical Limitations                                                                                                                                | 132                                    |

| 8.3                            | Summary                                                                                                                                                                             | 132                                    |

| Chap                           | oter 9: Conclusion                                                                                                                                                                  | 134                                    |

| 9.1                            | Thesis Summary                                                                                                                                                                      | 134                                    |

| 9.2                            | Future Works                                                                                                                                                                        | 136                                    |

| Refe                           | rences                                                                                                                                                                              | 139                                    |

| Valu                           | es for all Circuits                                                                                                                                                                 | 151                                    |

| A.1                            |                                                                                                                                                                                     |                                        |

|                                | - Direct Voltage-Controlled VCDU                                                                                                                                                    | 151                                    |

| A.Z                            | - Direct Voltage-Controlled VCDU Current-Starved Inverter VCDU                                                                                                                      |                                        |

|                                |                                                                                                                                                                                     | 152                                    |

| A.3                            | - Current-Starved Inverter VCDU                                                                                                                                                     | 152<br>153                             |

| A.3<br>A.4                     | - Current-Starved Inverter VCDU Time-Mode Comparator                                                                                                                                | 152<br>153<br>154                      |

| A.3<br>A.4<br>A.5              | - Current-Starved Inverter VCDU<br>- Time-Mode Comparator<br>- Single-Ended Input TMΔΣADC                                                                                           | 152<br>153<br>154<br>155               |

| A.3<br>A.4<br>A.5<br>A.6       | - Current-Starved Inverter VCDU  - Time-Mode Comparator  - Single-Ended Input TMΔΣADC  - Differential- Input TMΔΣADC  - Time-Mode Cyclic ADC  6.1. VCDU Design                      | 152<br>153<br>154<br>155<br>157        |

| A.3<br>A.4<br>A.5<br>A.6<br>A. | - Current-Starved Inverter VCDU  - Time-Mode Comparator  - Single-Ended Input TMΔΣADC  - Differential- Input TMΔΣADC  - Time-Mode Cyclic ADC  6.1. VCDU Design  6.2. Time-Amplifier | 152<br>153<br>154<br>155<br>157<br>158 |

| A.3<br>A.4<br>A.5<br>A.6<br>A. | - Current-Starved Inverter VCDU  - Time-Mode Comparator  - Single-Ended Input TMΔΣADC  - Differential- Input TMΔΣADC  - Time-Mode Cyclic ADC  6.1. VCDU Design                      | 152<br>153<br>154<br>155<br>157<br>158 |

# **List of Figures**

| Figure 1.1: Conventional analog data processing system with DSP, s       | torage        |

|--------------------------------------------------------------------------|---------------|

| memory, and DAC for analog re-transmission                               | 1             |

| Figure 1.2: Analog-to-digital conversion process via time-mode signal    |               |

| processing                                                               | 3             |

| Figure 2.1: Analog-to-digital conversion process example                 | 7             |

| Figure 2.2: Analog-to-digital converter (ADC) (a) block diagram; (b) tr  | ansfer        |

| characteristic.                                                          | 8             |

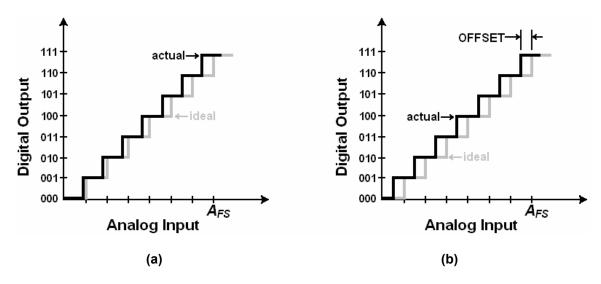

| Figure 2.3: 3-bit examples of ADC (a) gain error and (b) offset error    | 13            |

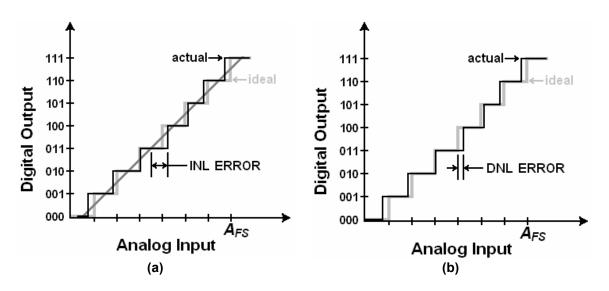

| Figure 2.4: 3-bit ADC linearity error examples of (a) integral nonlinear | rity (INL);   |

| (b) differential Nonlinearity (DNL)                                      | 14            |

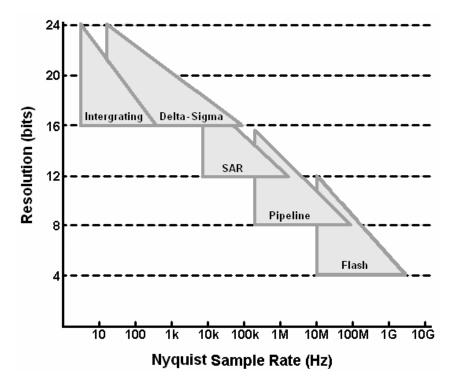

| Figure 2.5: Comparison between five ADC topologies demonstrating         | their         |

| intended Nyquist sampling rates and their typical resolutions            | 18            |

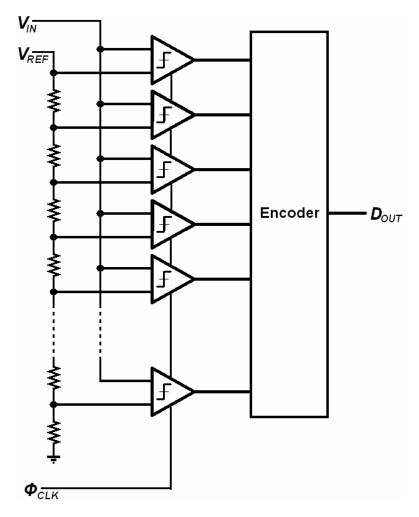

| Figure 2.6: Flash ADC                                                    | 19            |

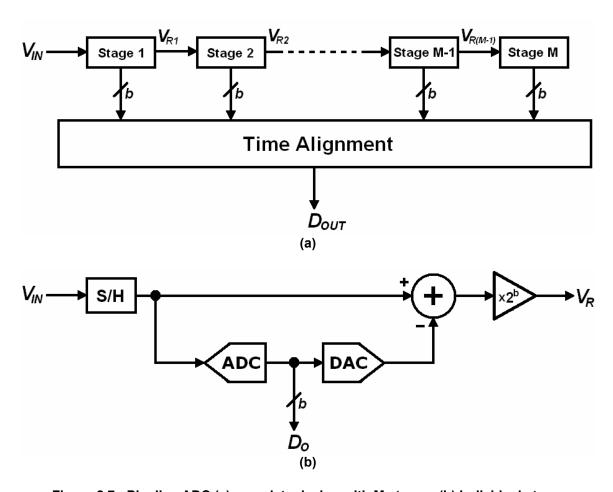

| Figure 2.7: Pipeline ADC (a) complete design with M stages; (b) indiv    | ridual stage. |

|                                                                          | 20            |

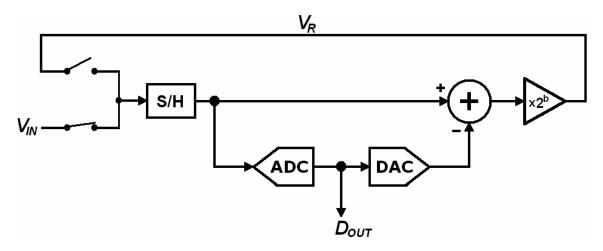

| Figure 2.8: Cyclic or algorithmic ADC                                    | 21            |

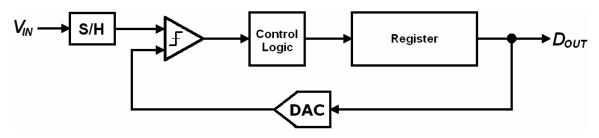

| Figure 2.9: Successive approximation register (SAR) ADC                  | 22            |

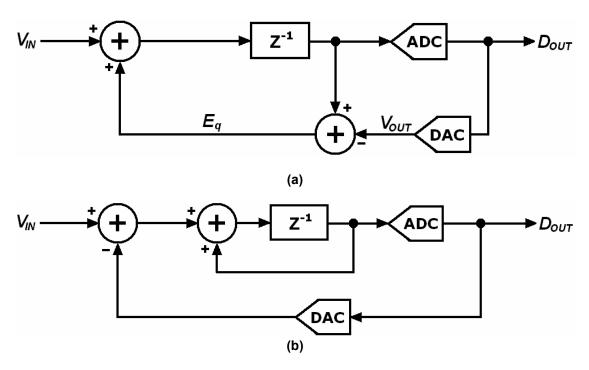

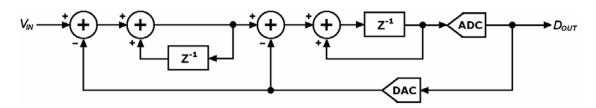

| Figure 2.10: First-order delta-sigma ADC: (a) error-feedback model, (    | b) output-    |

| feedback model                                                           | 24            |

| Figure 2.11: Second-order delta-sigma ADC                                | 25            |

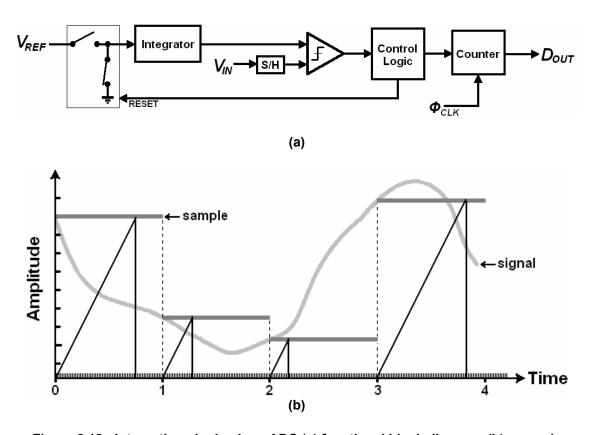

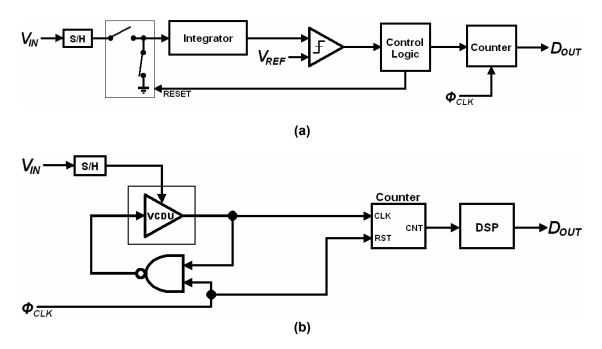

| Figure 2.12: Integrating single-slope ADC (a) functional block diagram; (b)            |

|----------------------------------------------------------------------------------------|

| example operation26                                                                    |

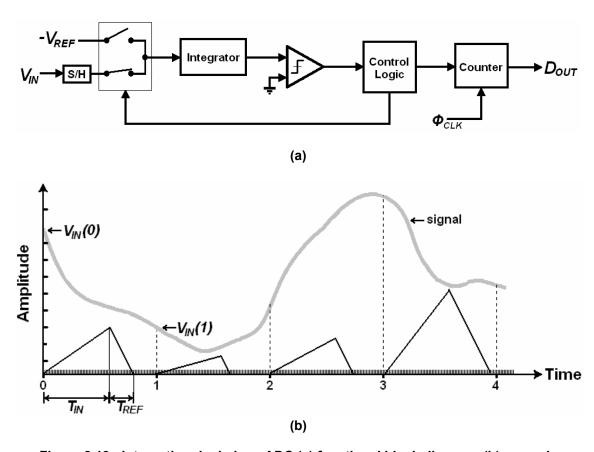

| Figure 2.13: Integrating dual-slope ADC (a) functional block diagram; (b)              |

| example operation27                                                                    |

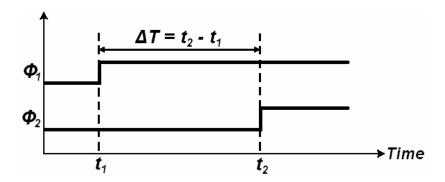

| Figure 3.1: Timing diagram example demonstrating a time-difference variable $\Delta 7$ |

| as the difference between two digital clock rising edge transition times 29            |

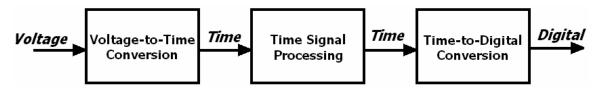

| Figure 3.2: Block diagram of the analog-to-digital conversion process via time-        |

| mode signal processing30                                                               |

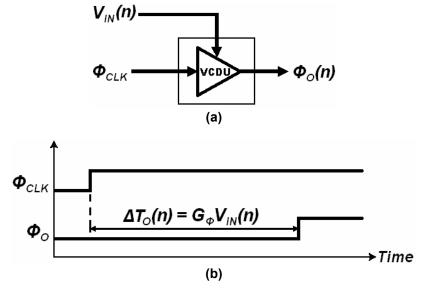

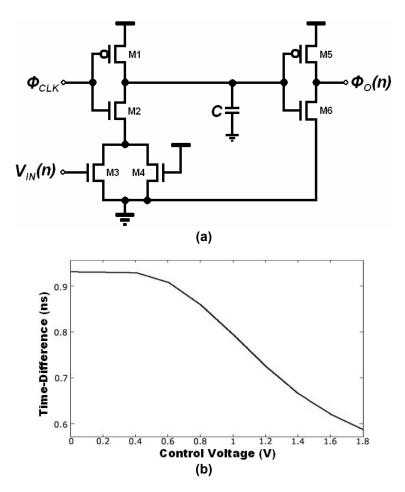

| Figure 3.3: Voltage-controlled delay unit (VCDU): (a) block diagram; (b) example       |

| timing diagram31                                                                       |

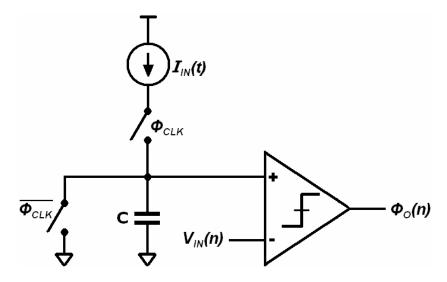

| Figure 3.4: Voltage-controlled delay unit (VCDU) functional diagram 32                 |

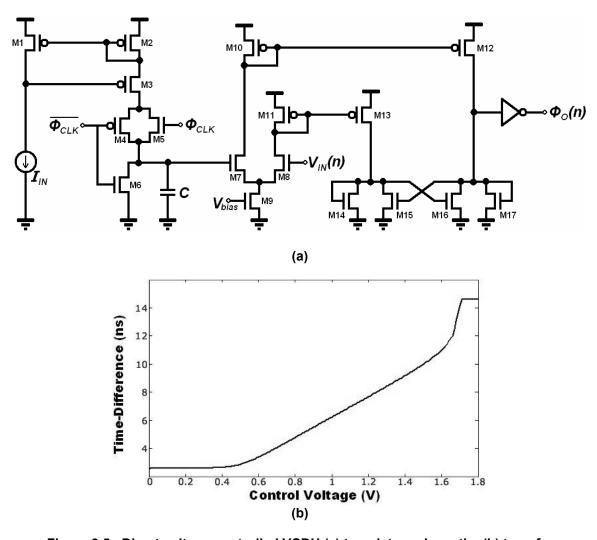

| Figure 3.5: Direct voltage-controlled VCDU (a) transistor schematic; (b) transfer      |

| characteristic obtained through an HSPICE simulation33                                 |

| Figure 3.6: Current-starved inverter VCDU (a) transistor schematic; (b) transfer       |

| characteristic obtained through an HSPICE simulation35                                 |

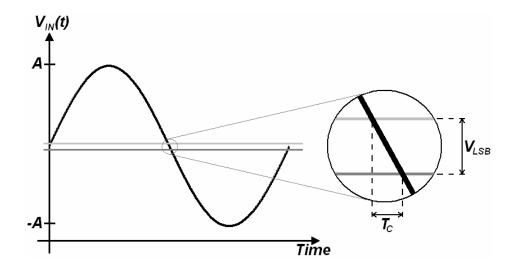

| Figure 3.7: Analysis of sinusoidal input voltage to determine when a sample-and-       |

| hold is required37                                                                     |

| Figure 3.8: Voltage-to-time converter (VTC) (a) block diagram; (b) timing              |

| diagram illustrating the VTC operation41                                               |

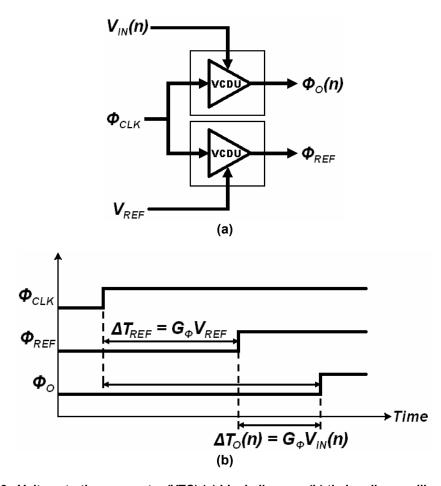

| Figure 3.9: Voltage-to-time adder (a) block diagram; (b) timing diagram43              |

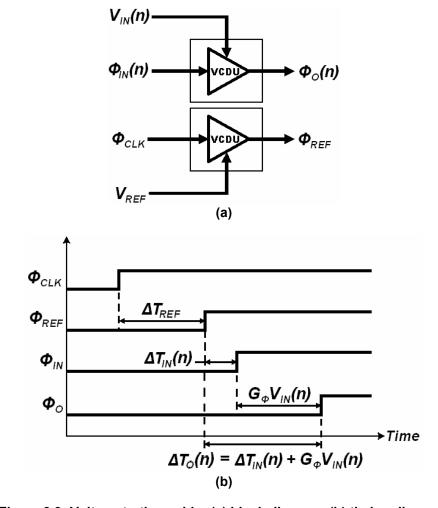

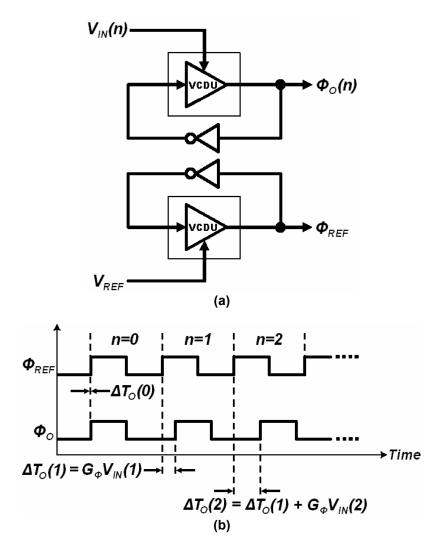

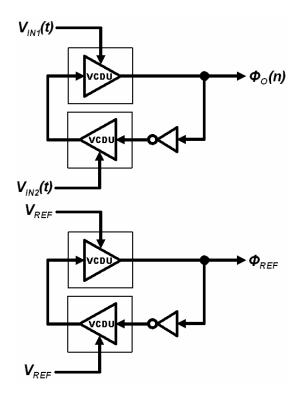

| Figure 3.10: Voltage-to-time integrator (a) block diagram; (b) timing diagram 44       |

| Figure 3.11: Block diagram of a dual-input voltage-to-time integrator 45               |

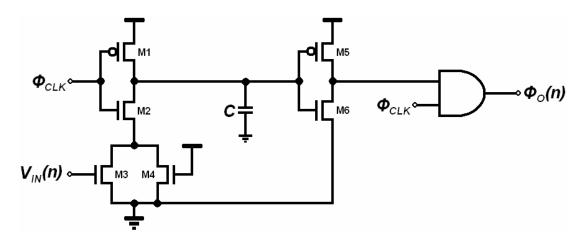

| Figure 3.12: Current-starved inverter VCDU with an output AND gate to bypass           |

| the clock's falling edge46                                                             |

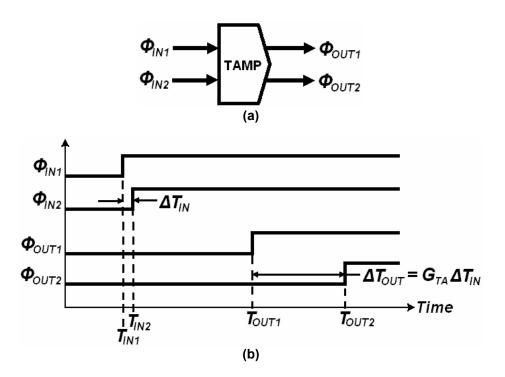

| Figure 3.13: Time amplifier (TAMP (a) block diagram; (b) example timing                |

| diagram47                                                                              |

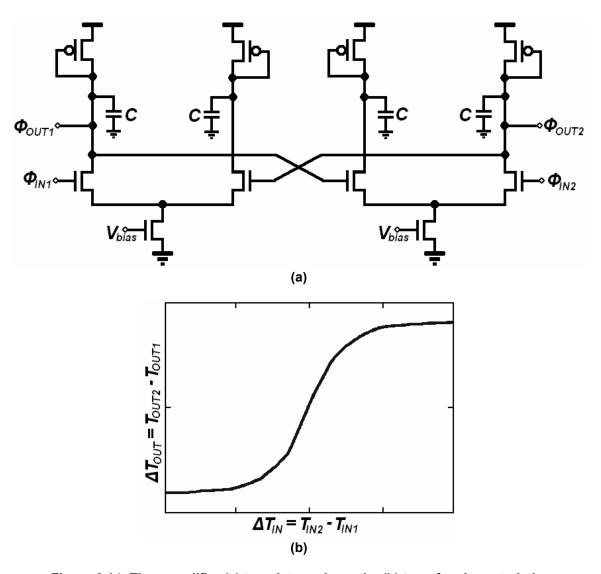

| Figure 3.14: Time amplifier (a) transistor schematic; (b) transfer characteristic. 48  |

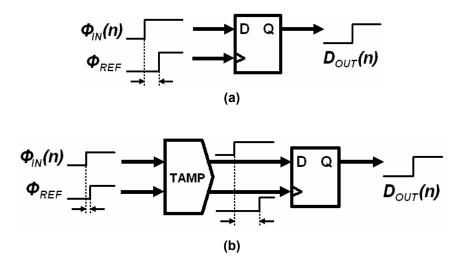

| Figure 3.15: Time comparator implemented using a (a) edge-triggered D-type             |

| flip-flop (b) edge-triggered D-type flip-flop with a time amplifier (TAMP) used        |

| as a pre-amplifier50                                                                   |

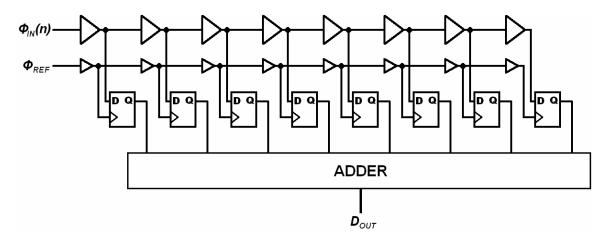

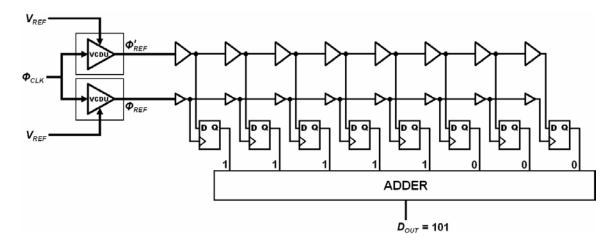

| Figure 3.16: 3-bit time-to-digital converter using a Vernier delay line51              |

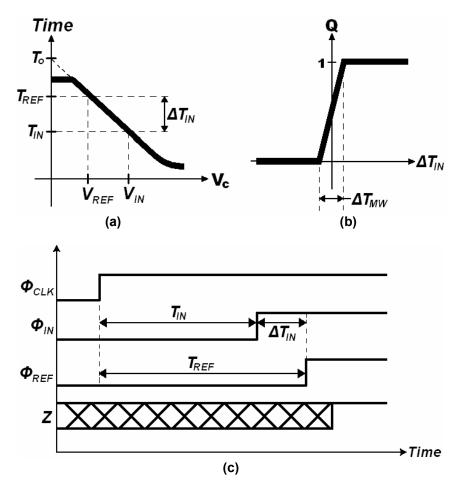

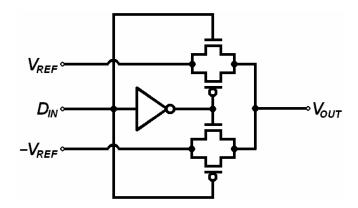

| Figure 4.1: Time-mode voltage comparator (TMVC)                                          | 55 |

|------------------------------------------------------------------------------------------|----|

| Figure 4.2: Time-mode voltage comparator (TMVC) (a) VCDU transfer                        |    |

| characteristic; (b) D flip-flip transfer characteristic; (c) timing diagram 5            | 56 |

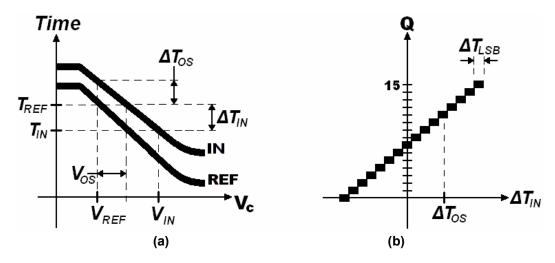

| Figure 4.3: Transfer characteristics for the time-mode voltage comparator                |    |

| (TMVC) with calibration: (a) two mismatched VCDUs; (b) time-to-digital                   |    |

| converter5                                                                               | 58 |

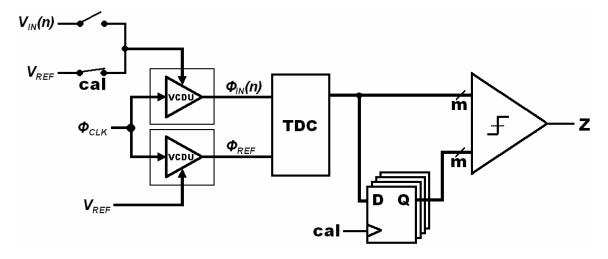

| Figure 4.4: Time-mode voltage comparator (TMVC) with calibration                         | 59 |

| Figure 4.5: Illustration of the calibration mechanism for the time-mode voltage          |    |

| comparator (TMVC) incorporating the voltage-to-time converter (VTC) and                  |    |

| the time-to-digital converter (TDC).                                                     | 31 |

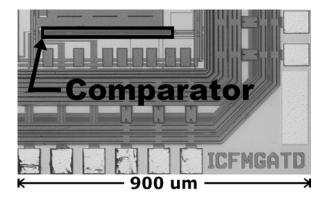

| Figure 4.6: Microphotograph section of the integrated circuit test chip                  |    |

| implementing a time-mode voltage comparator (TMVC)6                                      | 31 |

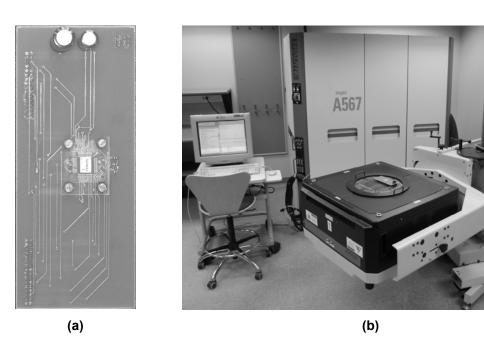

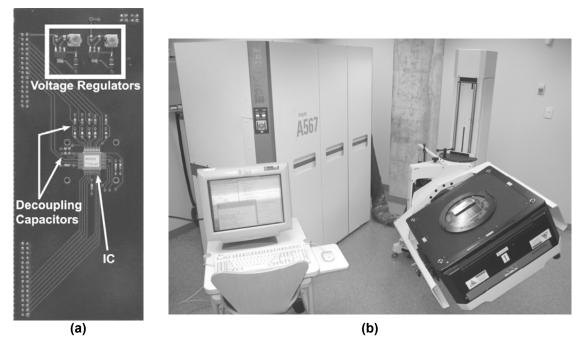

| Figure 4.7: Experimental test setup (a) PCB designed to test the integrated              |    |

| circuit; (b) A567 ATE used to test the IC.                                               | 32 |

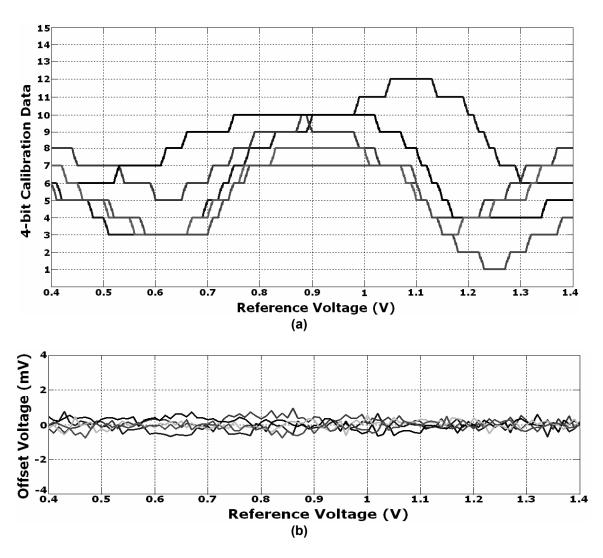

| Figure 4.8: Experimental results for the time-mode comparator with calibration.          |    |

| (a) Calibration data of 5 chips collected over a 1-V input reference range. (b)          | )  |

| Compensated input-referred offset voltage.                                               | 34 |

| Figure 5.1: Time-mode flash ADC implemented with TMVCs6                                  | 37 |

| Figure 5.2: Time-mode flash ADC implemented with a VTC followed by a TDC.6               | 38 |

| Figure 5.3: Integrated circuit microphotograph of a test chip implementing a 7-bi        | t  |

| time-mode flash ADC using TMVCs7                                                         | 70 |

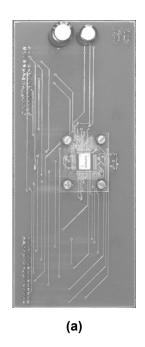

| Figure 5.4: Experimental test setup: (a) PCB designed to test the time-mode              |    |

| flash ADC integrated circuit; (b) Teradyne A567 ATE used to test the IC 7                | 71 |

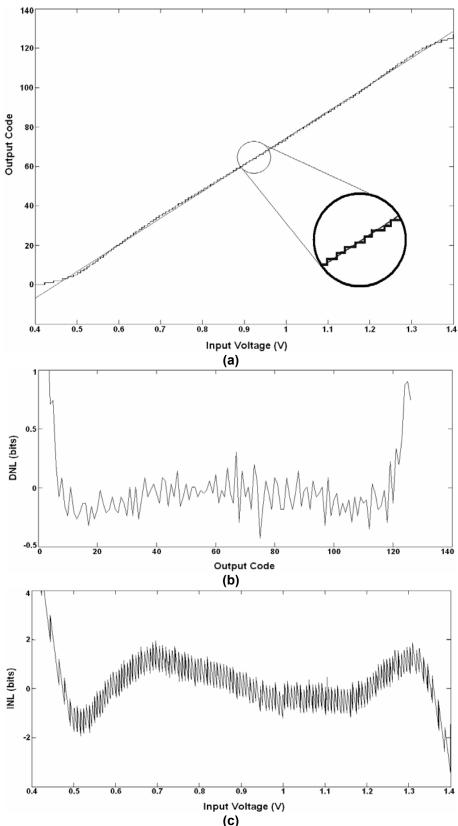

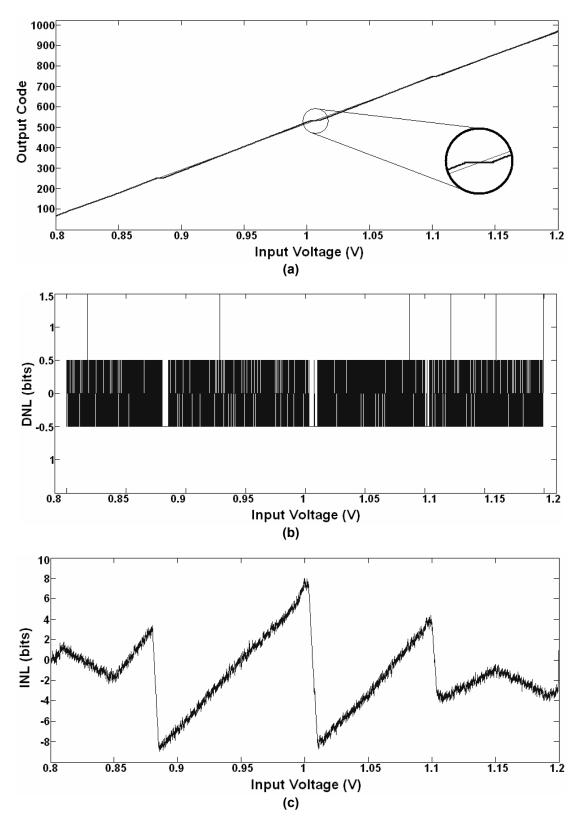

| Figure 5.5: Experimental results for the time-mode flash ADC. (a) Output digital         |    |

| code and line-of-best fit. (b) Differential Nonlinearity (DNL), (c) Integral             |    |

| Nonlinearity (INL)                                                                       | 72 |

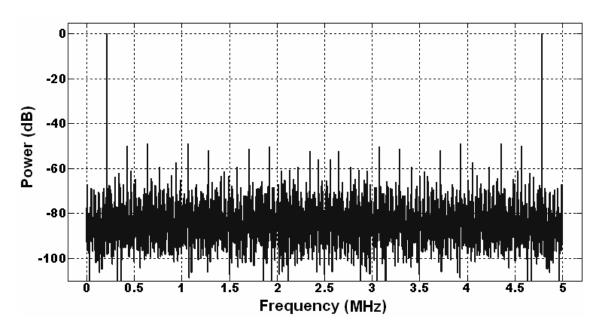

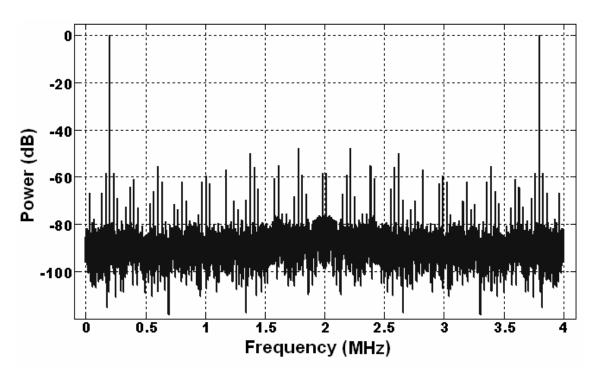

| Figure 5.6: PSD for the time-mode flash ADC operating with a sampling                    |    |

| frequency of 5 MHz and 215-kHz input test signal with a 1-V $_{\text{p-p}}$ amplitude. 7 | 73 |

| Figure 6.1: First-order single-bit delta-sigma analog-to-digital converter error-        |    |

| feedback model                                                                           | 76 |

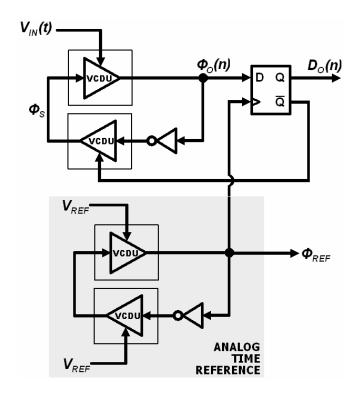

| Figure 6.2: First-order single-bit delta-sigma time-mode delta-sigma analog-to-              | -    |

|----------------------------------------------------------------------------------------------|------|

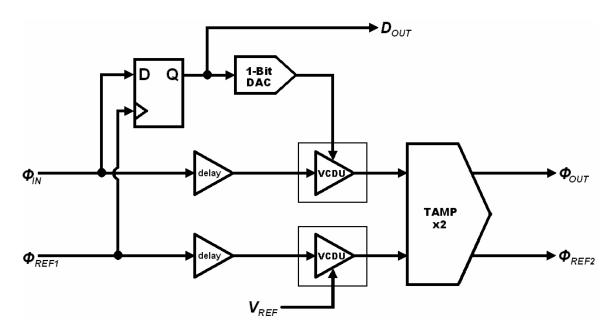

| digital converter (ΤΜΔΣΑDC).                                                                 | . 77 |

| Figure 6.3: Example timing diagram for the first-order single-bit TM $\!\Delta\Sigma ADC$    | . 78 |

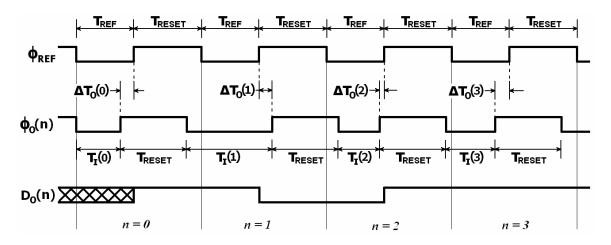

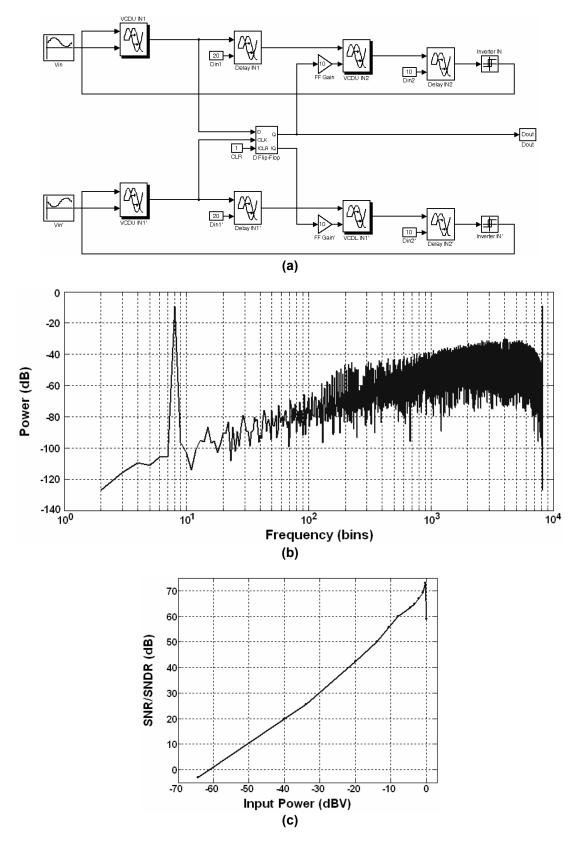

| Figure 6.4: Mathematical modeling of the TMΔΣADC: (a) MATLAB Simulink                        |      |

| model diagram, (b) MATLAB simulation power spectral density (PSD)                            |      |

| results, (c) dynamic range                                                                   | . 83 |

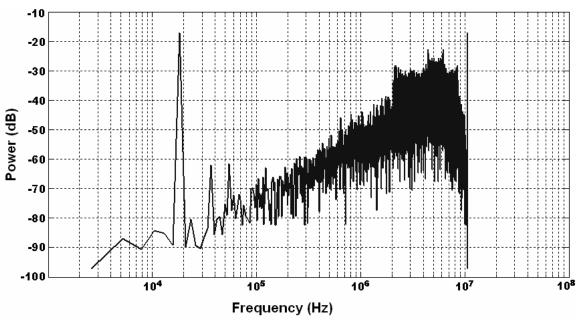

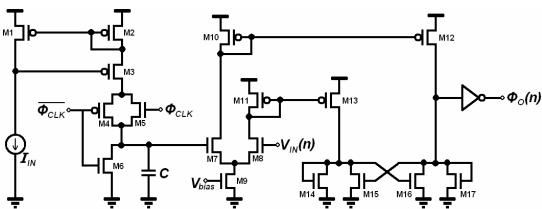

| Figure 6.5: Transistor schematic for the low-speed first-order single-bit                    |      |

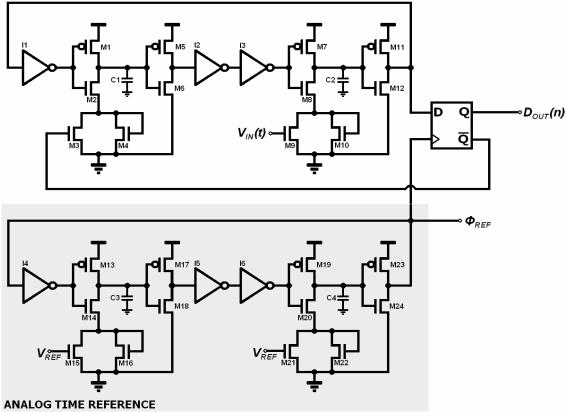

| ΤΜΔΣΑDC                                                                                      | . 84 |

| Figure 6.6: HSPICE simulation PSD results of the single-ended input first-order              | ∍r   |

| single-bit TMΔΣADC sampling at 10.7 MHz                                                      | . 85 |

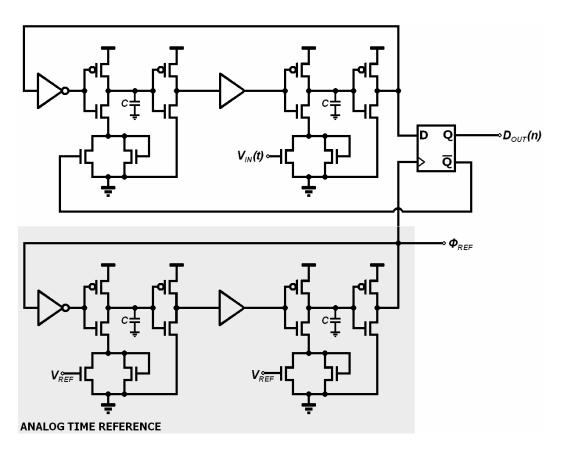

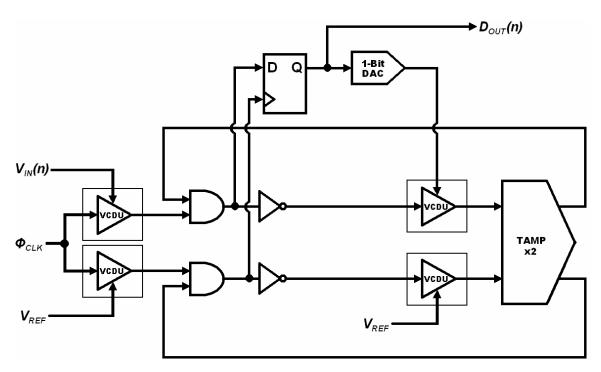

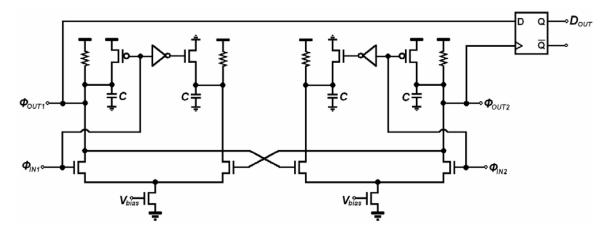

| Figure 6.7: First-order single-bit high-speed TM $\Delta\Sigma$ ADC (a) transistor schematic | tic; |

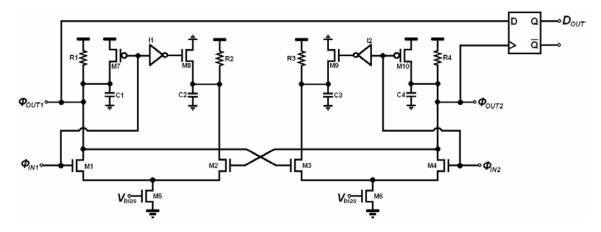

| (b) HSPICE simulation PSD result.                                                            | . 87 |

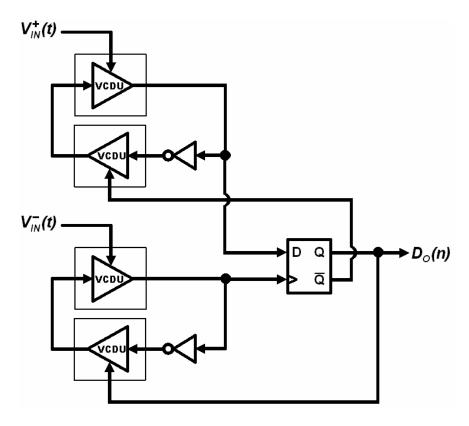

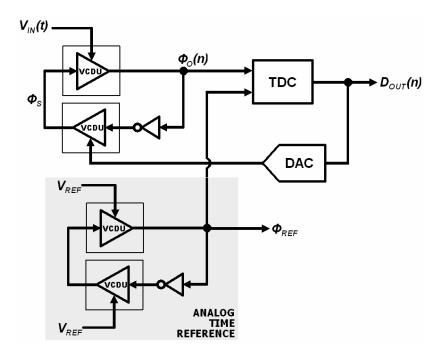

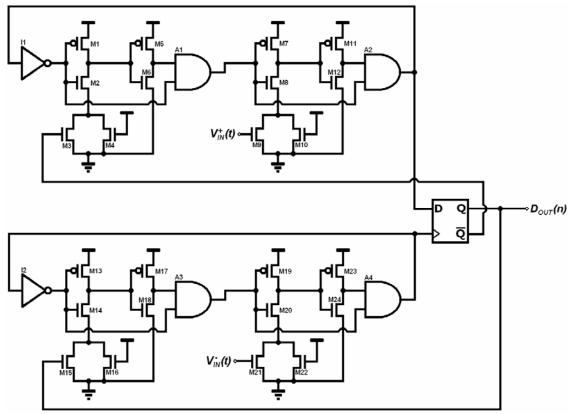

| Figure 6.8: Differential-input first-order single-bit TM $\Delta\Sigma$ ADC                  | . 88 |

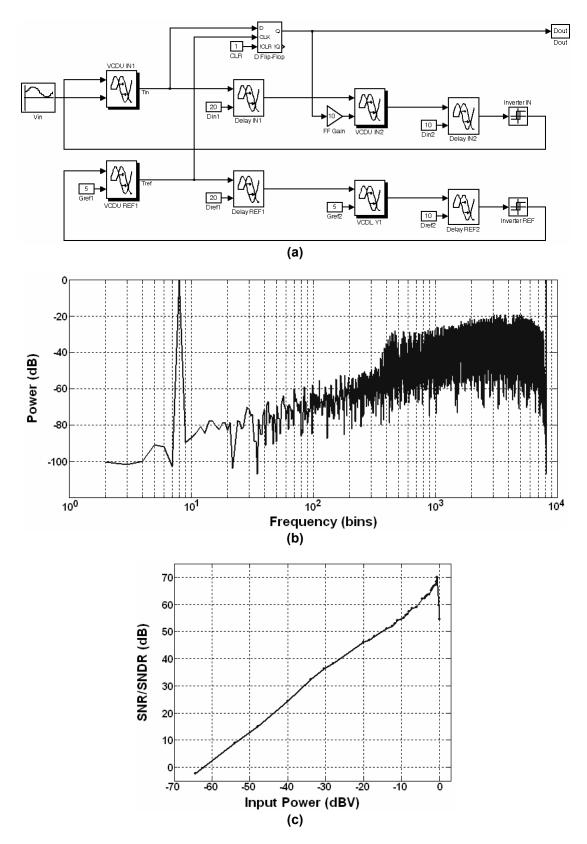

| Figure 6.9: Mathematical modeling of the differential-input TMΔΣADC: (a)                     |      |

| MATLAB Simulink model diagram; (b) MATLAB simulation PSD results, (                          | c)   |

| dynamic range                                                                                | . 90 |

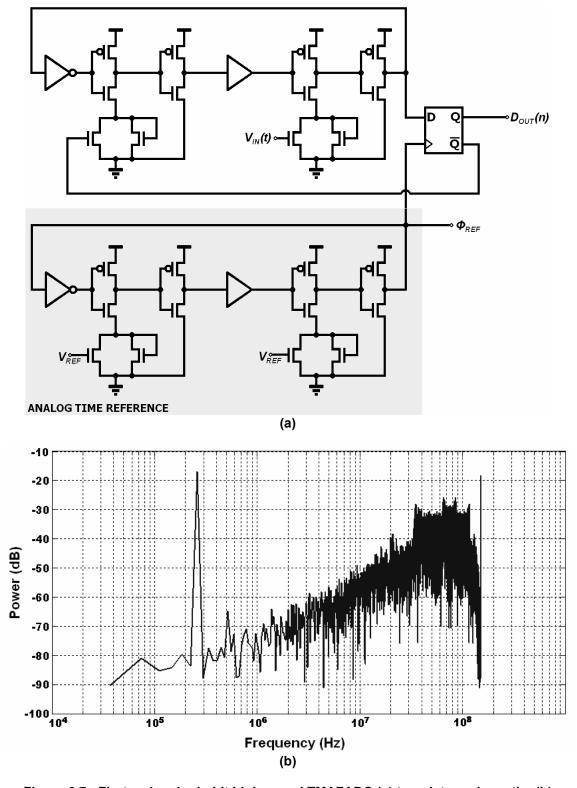

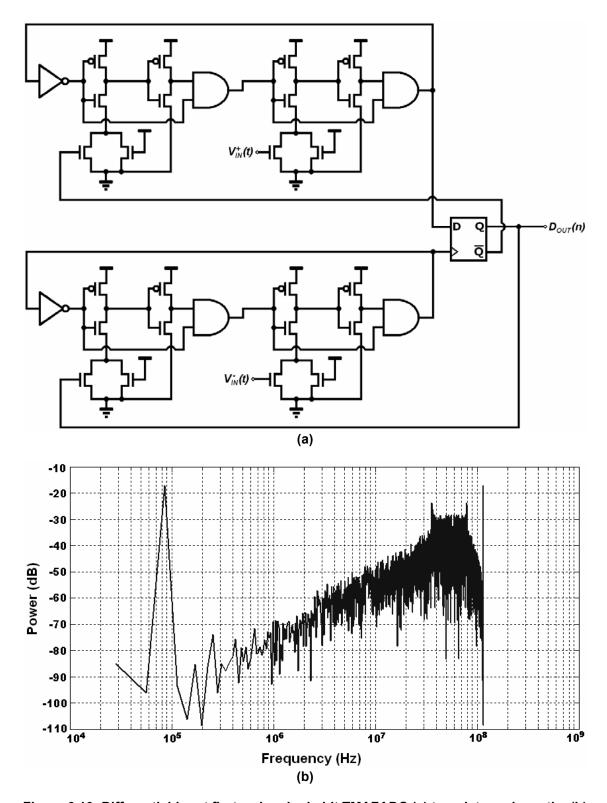

| Figure 6.10: Differential-input first-order single-bit TM $\Delta\Sigma$ ADC (a) transistor  |      |

| schematic; (b) PSD HSPICE simulation result.                                                 | . 91 |

| Figure 6.11: First-order multi-bit TMΔΣADC.                                                  | . 93 |

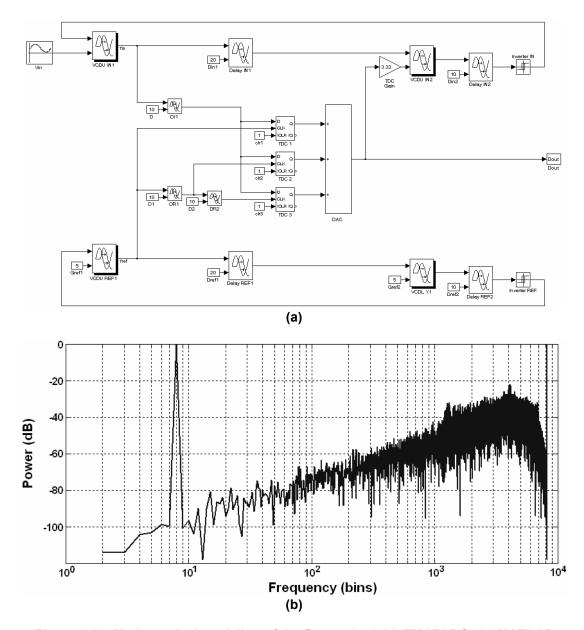

| Figure 6.12: Mathematical modeling of the first-order 2-bit TMΔΣADC: (a)                     |      |

| MATLAB Simulink model diagram; (b) MATLAB simulation PSD result                              | . 94 |

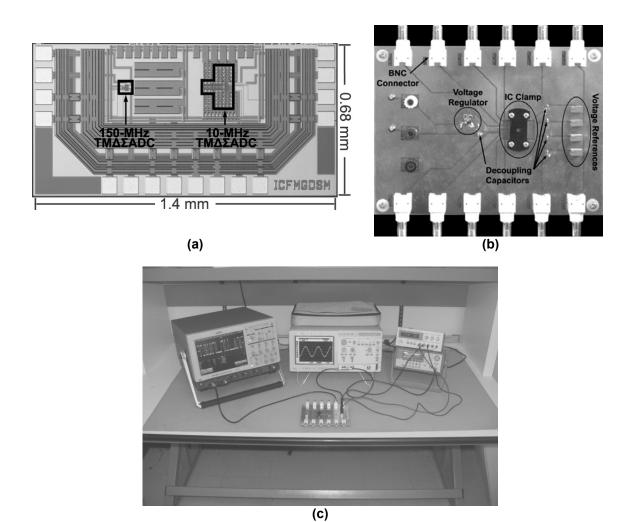

| Figure 6.13: (a) Integrated circuit microphotograph of a test chip implementing              | J    |

| two single-ended input time-mode delta-sigma ADCs. (b) PCB to interface                      | Э    |

| the test chip to the test equipment. (c) Experimental setup                                  | . 96 |

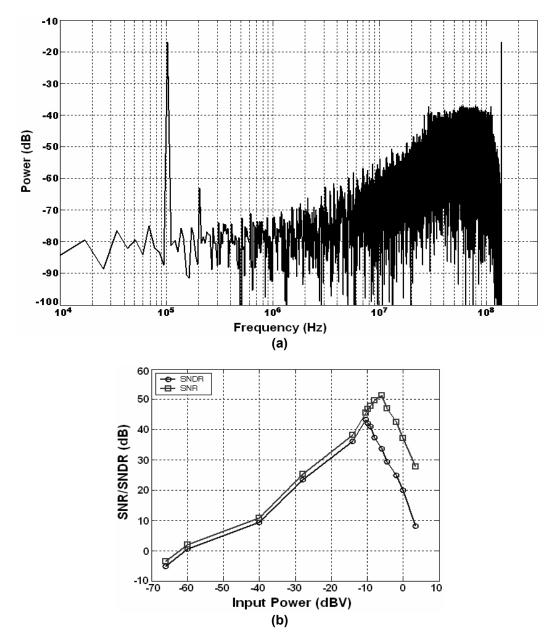

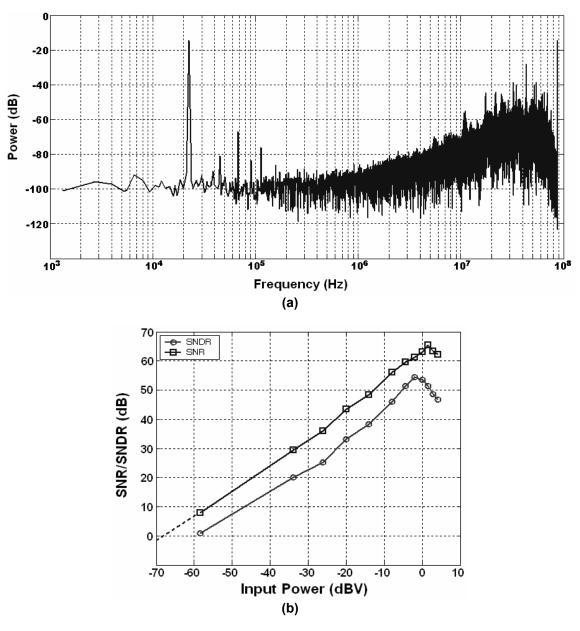

| Figure 6.14: Experimental results for the single-ended input high-speed time-                |      |

| mode delta-sigma analog-to-digital converter: (a) power spectral density;                    | (b)  |

| dynamic range                                                                                | . 97 |

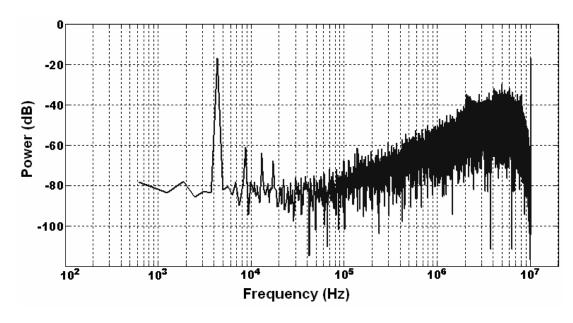

| Figure 6.15: PSD experimental results for the single-ended input low-speed                   |      |

| time-mode delta-sigma analog-to-digital converter                                            | . 99 |

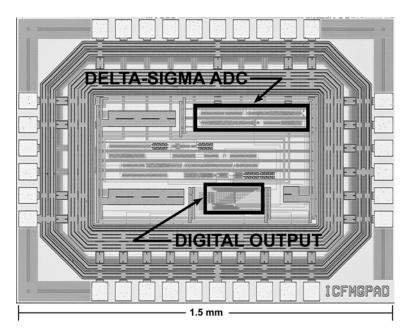

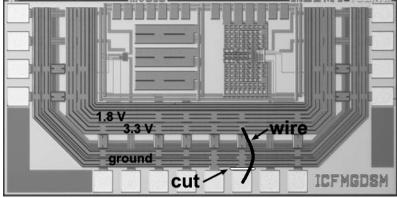

| Figure 6.16: Microphotograph of the test chip implementing the differential-inp              | ut   |

| ΤΜΔΣΑDC                                                                                      | 100  |

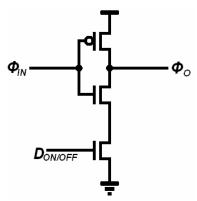

| Figure 6.17: Inverter used to turn the TM $\Delta\Sigma$ ADC oscillators on or off       | )1         |

|------------------------------------------------------------------------------------------|------------|

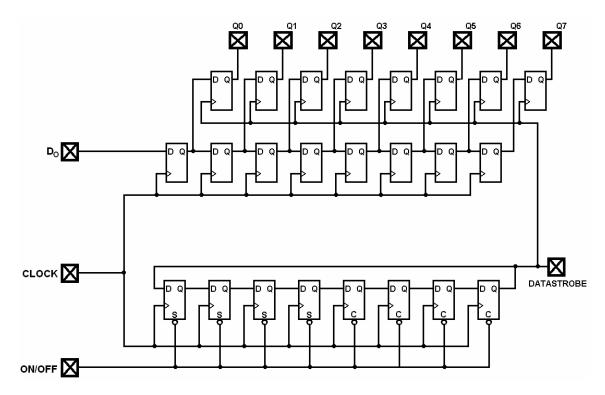

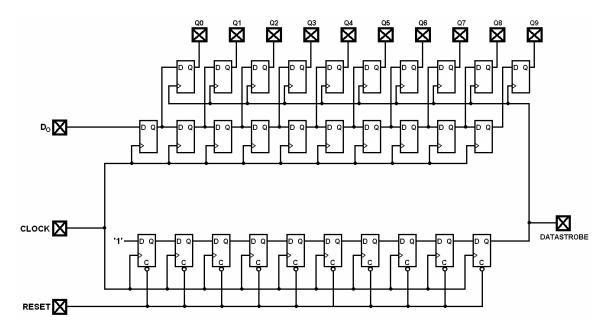

| Figure 6.18: Serial-to-parallel digital output circuitry for the differential-input time | <b>;</b> – |

| mode delta-sigma ADC10                                                                   | )2         |

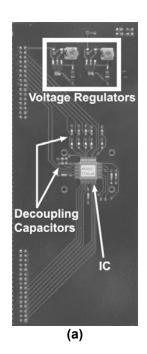

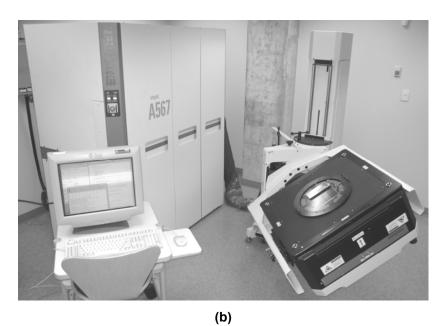

| Figure 6.19: Experimental setup: (a) PCB used to interface the test chip to the          |            |

| Teradyne A567 tester. (b) Test environment with the IC, PCB, and A567                    |            |

| tester10                                                                                 | )3         |

| Figure 6.20: Experimental results for the differential-input first-order single-bit      |            |

| TMΔΣADC: (a) PSD of the ADC output. (b) Dynamic range10                                  | )4         |

| Figure 6.21: Focused ion beam (FIB) microsurgery                                         | )6         |

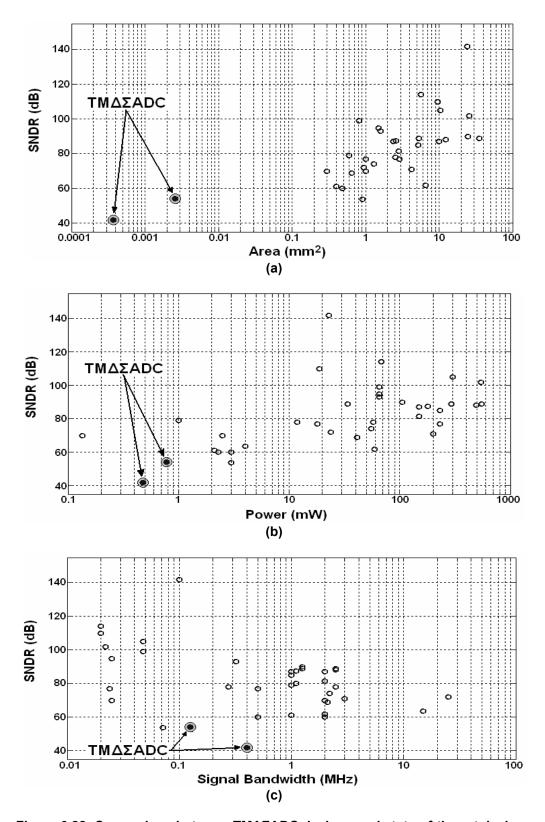

| Figure 6.22: Comparison between TMΔΣADC designs and state-of-the-art                     |            |

| designs recorded in the literature: (a) SNDR versus area, (b) SNDR versus                |            |

| power, (c) SNDR versus signal bandwidth10                                                | )9         |

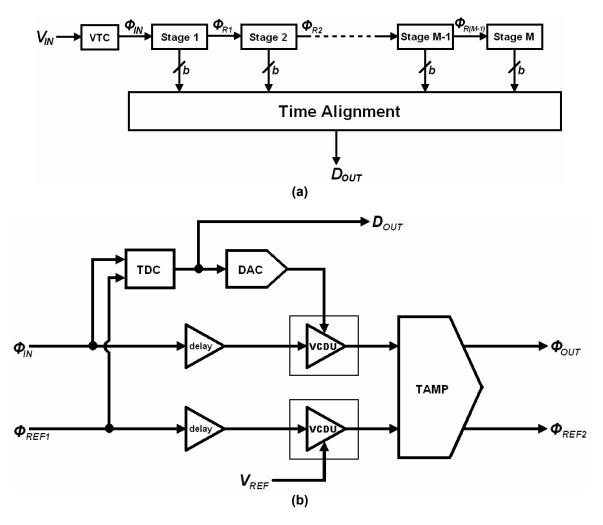

| Figure 7.1: Time-mode pipeline ADC: (a) high-level block diagram of the                  |            |

| complete ADC system, (b) single pipeline stage11                                         | 12         |

| Figure 7.2: Single-bit stage for a radix-2 time-mode pipeline ADC11                      | 13         |

| Figure 7.3: Time-mode cyclic ADC11                                                       | 14         |

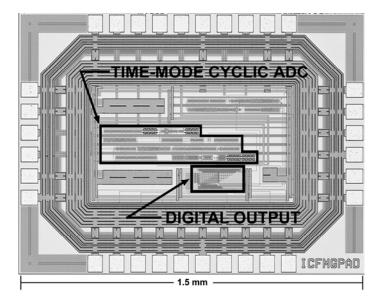

| Figure 7.4: Microphotograph of the test chip implementing the time-mode cyclic           |            |

| ADC11                                                                                    | 15         |

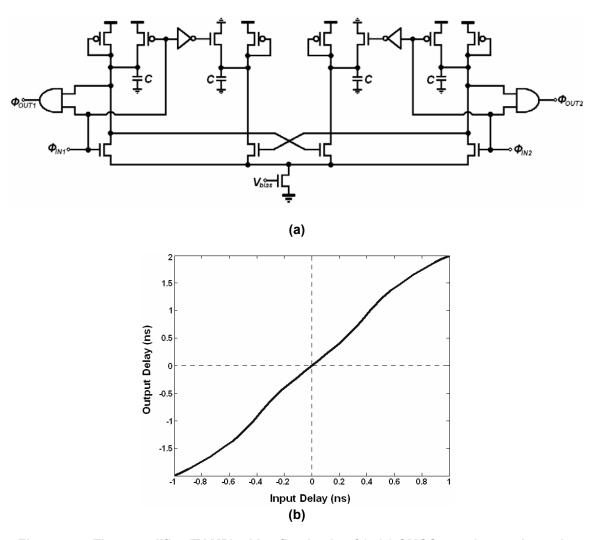

| Figure 7.5: Time-amplifier (TAMP) with a fixed gain of 2: (a) CMOS transistor            |            |

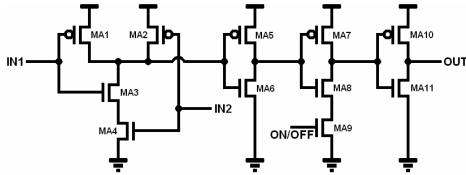

| schematic; (b) transfer characteristic11                                                 | 16         |

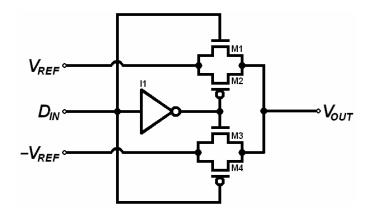

| Figure 7.6: CMOS transistor schematic of a one-bit DAC                                   | 17         |

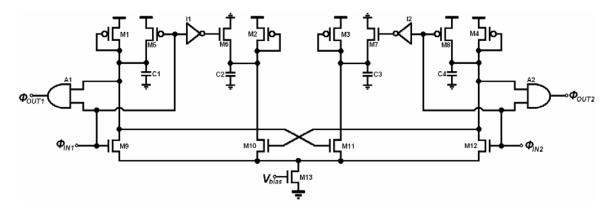

| Figure 7.7: Time comparator with preamplifier                                            | 18         |

| Figure 7.8: Digital output circuitry for the time-mode cyclic ADC11                      | 19         |

| Figure 7.9: (a) PCB used to interface the test chip to the Teradyne A567 tester.         |            |

| (b) Test setup with the IC, PCB, and A567 tester12                                       | 20         |

| Figure 7.10: PSD experimental results for the time-mode cyclic ADC12                     | 20         |

| Figure 7.11: Experimental results for the time-mode cyclic ADC. (a) Output digital       | al         |

| code and line-of-best fit. (b) Differential Nonlinearity (DNL), (c) Integral             |            |

| Nonlinearity (INL)                                                                       | 22         |

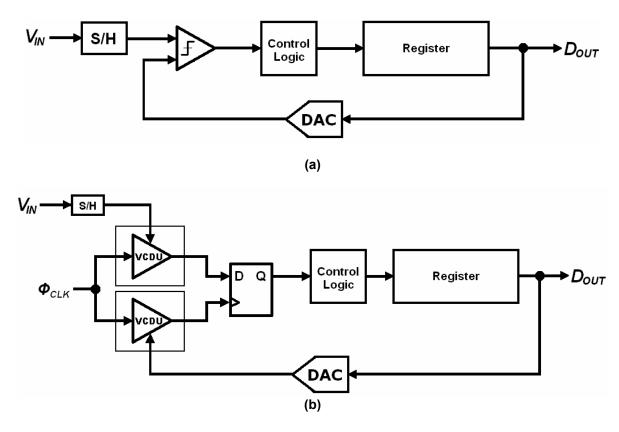

| Figure 8.1: (a) Successive approximation register (SAR) ADC. (b) Time-mode               |            |

| SAR ADC                                                                                  | 26         |

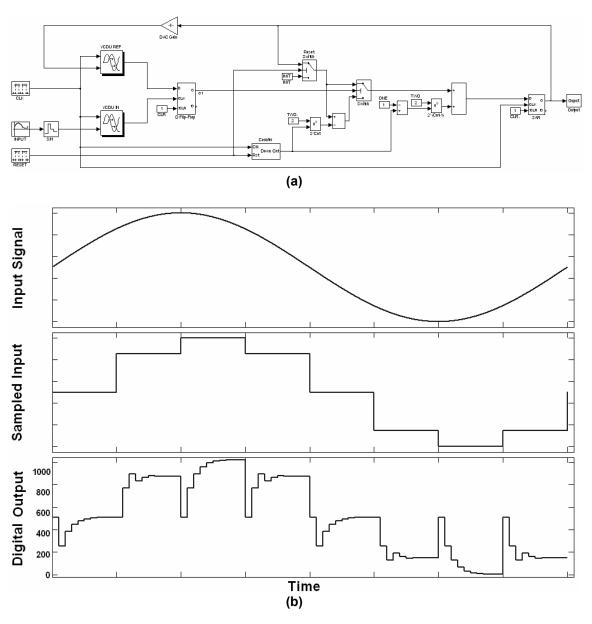

| Figure 8.2: Time-mode SAR ADC: (a) MATLAB Simulink model; (b) MATLAB               |      |

|------------------------------------------------------------------------------------|------|

| simulation results                                                                 | 127  |

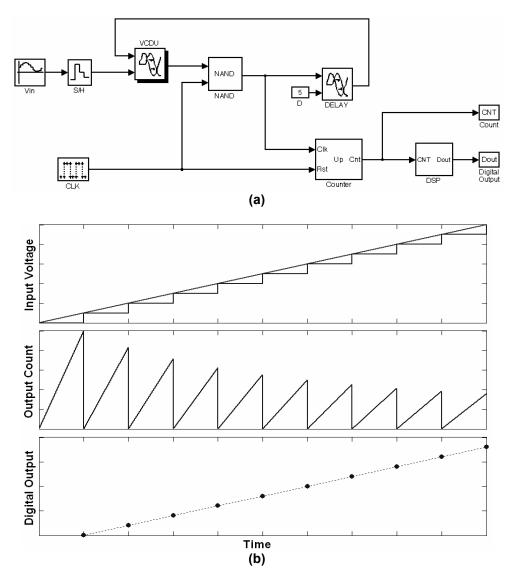

| Figure 8.3: Integrating single-slope ADC (a) conventional block diagram; (b)       |      |

| time-mode Integrating ADC                                                          | 129  |

| Figure 8.4: Time-mode integrating single-slope ADC (a) MATLAB Simulink             |      |

| model; (b) MATLAB simulation results                                               | 131  |

| Figure A.1: Transistor schematic for the direct voltage-controlled VCDU            |      |

| presented in Figure 3.5(a).                                                        | 151  |

| Figure A.2: Transistor schematic for the current-starved inverter VCDU preser      | nted |

| in Figure 3.6(a).                                                                  | 152  |

| Figure A.3: Transistor schematic for the single-ended input first-order single-b   | it   |

| TMΔΣADC presented in Figure 6.5 and Figure 6.7(a)                                  | 154  |

| Figure A.4: Transistor schematic for the differential-input first-order single-bit |      |

| TMΔΣADC presented in Figure 6.10(a)                                                | 156  |

| Figure A.5: Transistor schematic for the AND gates A1, A2, A3, and A4 shown        | ı in |

| Figure A.4.                                                                        | 157  |

| Figure A.6: Transistor schematic for the time amplifier used in the time-mode      |      |

| cyclic ADC                                                                         | 159  |

| Figure A.7: Transistor schematic for the time comparator with pre-amplification    | า.   |

|                                                                                    | 160  |

| Figure A.8: Transistor schematic for the time comparator with pre-amplification    | ٦.   |

|                                                                                    | 160  |

# **List of Tables**

| Table 2.1: ADC applications and their intended bandwidths and required                      |      |

|---------------------------------------------------------------------------------------------|------|

| resolutions                                                                                 | . 10 |

| Table 3.1: Performance comparisons between the direct-voltage control and                   |      |

| current-starved inverter VCDUs.                                                             | . 36 |

| Table 4.1: Time-mode voltage comparator performance summary                                 | . 63 |

| Table 5.1: Time-mode flash ADC performance summary                                          | . 74 |

| Table 6.1: Design and experimental result summary for the high-speed single-                |      |

| ending input 1 <sup>st</sup> -order single-bit time-mode delta-sigma ADC                    | . 98 |

| Table 6.2: Design and experimental result summary for the low-speed single-                 |      |

| ending input 1 <sup>st</sup> -order single-bit time-mode delta-sigma ADC                    | . 99 |

| Table 6.3: Design and experimental result summary for the differential-input 1 <sup>s</sup> | ;t_  |

| order single-bit time-mode delta-sigma ADC                                                  | 103  |

| Table 7.1: Design and experimental result summary for the time-mode cyclic                  |      |

| ADC                                                                                         | 121  |

| Table A.1: Component values and bias conditions for the direct voltage-                     |      |

| controlled VCDU presented in Figure A.1                                                     | 152  |

| Table A.2: Component values and bias conditions for the current-starved inver               | ter  |

| VCDU presented in Figure A.2.                                                               | 153  |

| Table A.3: Component values for the VCDUs (i.e. Figure A.2) used in the time-               | -    |

| mode comparator                                                                             | 153  |

| Table A.4: Component values for the single-ended input first-order single-bit      |      |

|------------------------------------------------------------------------------------|------|

| TMΔΣADC presented in Figure A.3                                                    | 155  |

| Table A.5: Component values for the differential-input first-order single-bit      |      |

| TMΔΣADC presented in Figure A.4                                                    | 156  |

| Table A.6: Transistor dimensions for the AND gate presented in Figure A.5. $\dots$ | 157  |

| Table A.7: Component values used to implement the VCDUs incorporated in t          | he   |

| time-mode cyclic ADC                                                               | 158  |

| Table A.8: Component values used to implement the time-amplifier given in          |      |

| Figure A.6                                                                         | 158  |

| Table A.9: Component values used to implement the time comparator shown            | in   |

| Figure A.7                                                                         | 159  |

| Table A.10: Component values used to implement the time comparator shown           | ı in |

| Figure A.8                                                                         | 160  |

# **List of Acronyms**

A/D Analog-to-Digital

ADC Analog-to-Digital Converter

ATE Automated Test Equipment

**CMOS** Complimentary Metal Oxide Semiconductor

DAC Digital-to-Analog ConverterDEM Dynamic Element Matching

**DLL** Delay-Locked Loop

**DNL** Differential Nonlinearity

**DR** Dynamic Range

**DSP** Digital Signal Processing

**EMI** Electromagnetic Interference

**ENOB** Effective Number of Bits

FIB Focused Ion Beam

**FM** Frequency Modulation

**FoM** Figure of Merit

**HDL** Hardware Description Language

IC Integrated Circuit

**IF** Intermediate Frequency

INL Integral NonlinearityLSB Least Significant Bit

MiM Metal-insulator-Metal

MSB Most Significant Bit

**OSR** Oversampling Ratio

PCB Printed Circuit Board

**PDM** Pulse Density Modulation

PLL Phase-Locked Loop

**PSD** Power Spectral Density

**RF** Radio Frequency

**RMS** Root-Mean-Square

S/H Sample and Hold

**SAR** Successive Approximation Register

**SDA** Serial Data Analyzer

**SFDR** Spurious-Free Dynamic Range

**SNR** Signal-to-Noise Ratio

**SNDR** Signal-to-Noise and Distortion Ratio

**SoC** System-on-Chip

SR Slew Rate

**THD** Total Harmonic Distortion

**TMΔΣADC** Time-Mode Delta-Sigma Analog-to-Digital Converter

**TAMP** Time Amplifier

**TMSP** Time-Mode Signal Processing

**TMVC** Time-Mode Voltage Comparator

VCDU Voltage-Controlled Delay Unit

VCO Voltage-Controlled Oscillator

**VDL** Vernier Delay Line

**VLSI** Very Large Scale Integration

VTC Voltage-to-Time Converter

# **Chapter 1: Introduction**

#### 1.1 - Motivation

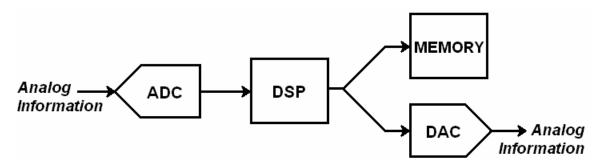

An analog-to-digital converter (ADC) is a very popular circuit that transforms real world continuous-time analog information into a digital representation to be processed and stored in the digital domain. Digital signal processing (DSP) is dominating the processing, transport, and storage of analog information as it has been proven to be fast, accurate, reliable, and relatively inexpensive. A conventional analog data processing system, as illustrated in Figure 1.1, consist of an ADC, followed by a DSP, followed by a storage memory or a digital-to-analog converter (DAC) to supply the processed data to a real-world user interface or transmission medium.

Figure 1.1: Conventional analog data processing system with DSP, storage memory, and DAC for analog re-transmission.

ADC circuits can be found in a wide range of applications such as communication systems, sensor networks, imaging and video applications, test and measurement apparatus, data acquisition systems, and consumer electronics such as cellular telephones, DVDs, digital cameras, and MP3 players. Each application requires ADCs with different performance specifications resulting in a wide range of commercially available ADC circuits. Selection of an ADC design is based on two main criteria: resolution and speed. The resolution of an ADC dictates how accurately the analog input will be represented by its digital output data. The speed of an ADC refers to the input signal bandwidth for which the analog-to-digital (A/D) conversion will maintain its quoted resolution. Two other important ADC criteria are power and area. ADC power consumption may be critical in battery operated devices or embedded systems such as system-on-chip (SoC) [1]. Silicon area usage may also be a serious concern in SoC designs.

Digital design is the driving force for the rapidly emerging deep submicron CMOS technologies. As such, CMOS processes are typically optimized for the needs of digital circuitry. In other words, CMOS technologies are being developed to improve digital switching speeds, lower the supply voltages, and reduce transistor geometries to increase the packing density of digital circuits. These pursuits have pushed the processing of digital information into the gigahertz frequency range. The need for digital, analog, and mixed-signal circuits to be integrated on a single die (i.e. SoC) is escalating as companies struggle to drive down cost, boost productivity, and create lower power and smaller devices.

There are many challenges in integrating analog and mixed-signal circuits in state-of-the-art digital CMOS technologies. As emerging CMOS technologies reduce feature size dimensions, transistor gate oxide thickness reduces forcing the system voltage to decrease. This negatively impacts analog and mixed-signal circuit performance by exercising transistors at non-optimal operating points and permitting currents to leak through transistor gates [2]. This dilemma results in

reduced input voltage swings and linearity problems for the processing of analog voltage signals. To upset the design challenge even further, area and power budgets are at best being preserved if not reducing. Additional implementation challenges are imposed when analog and mixed signal processing functions must coexist with digital circuits. The switching noise [3] from the digital circuitry may couple into the analog blocks thus corrupting analog information.

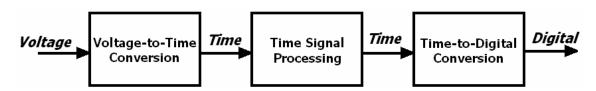

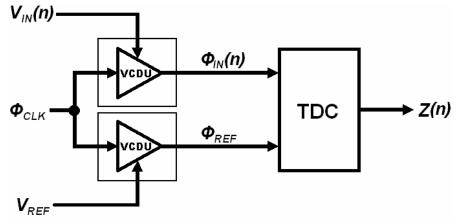

In order to offset some of the ADC design challenges imposed by digitally-driven deep submicron CMOS processes, a potential candidate to replace conventional voltage signal processing is being investigated, referred to as *time-mode signal processing* or TMSP. Although the concept of TMSP is fairly new, several works have begun to investigate its potential in many applications including A/D conversion [4] – [11]. The A/D conversion process using the TMSP methodology is depicted in Figure 1.2. Since most information begins in the form of a voltage, a voltage-to-time converter (VTC) is employed to convert the input signal into a time signal. The time signal is then processed by various circuits resulting in an output time signal. Finally, the processed time signal is transformed into a digital representation using a time-to-digital converter (TDC).

The circuits involved in the time-mode ADC processing are comprised of a digital CMOS construction. Therefore, this system offers all the benefits of the digital CMOS technology. Specifically, TMSP circuits will operates at high speeds, consume low power, and occupy small silicon area. Moreover, these performances specifications will improve with newer and smaller digitally-driven CMOS technologies.

Figure 1.2: Analog-to-digital conversion process via time-mode signal processing.

### 1.2 - Thesis Scope

The research described in this thesis aims to address the growing need for innovative circuit design techniques that will permit and continue the integration of high-performance analog-to-digital converters in emerging state-of-the-art digital CMOS technologies. This broad objective is narrowed down to a classification of circuits and signal processing techniques referred to as time-mode signal processing or TMSP.

The primary discovery goal is achieved by first defining the TMSP methodology and then describing its signal processing circuits in the context of analog-to-digital conversion. Several experimental circuits were designed and fabricated to demonstrate the feasibility of the proposed TMSP circuit design technique. Specifically, this thesis reveals that the TMSP methodology, when used in analog-to-digital conversion, can achieve high sampling speed and low power circuit designs while occupying very little silicon area. It should be noted, however, that the experimental ADCs designed herein demonstrate only mediocre effective resolutions due to the non-linearity of some of the CMOS circuits involved. Nevertheless, the proposed methodology offers an interesting alternative to conventional ADC design techniques with great potential.

#### 1.3 - Thesis Overview

This thesis is organized into eight chapters excluding this introduction. Each chapter is described as follows.

Chapter 2 presents the concept of analog-to-digital (A/D) conversion. The theoretical and mathematical basis of A/D conversion is explained. ADC design specifications are presented along with performance metrics used to characterize

ADCs. The five main ADC architectures are introduced while offering insight into their application space.

The concept of time-mode signal processing as it applies to A/D conversion is explored in Chapter 3. Various system blocks and transistor circuits to implement the TMSP functions, which will be used throughout this work, are described.

A time-mode voltage comparator design is presented in Chapter 4. The design was incrementally modified to compensate for process variation using an all-digital calibration scheme. The time-mode comparator with calibration was fabricated in 0.18-µm CMOS technology and its experimental results are presented.

Chapter 5 outlines the use of TMSP to construct flash ADCs. Two flash architectures are described. An integrated circuit was manufactured incorporating a 7-bit time-mode flash ADC. Its design and experimental results are also presented.

Chapter 6 describes a delta-sigma ( $\Delta\Sigma$ ) A/D conversion technique using the TMSP blocks presented in Chapter 3. First-order single-bit  $\Delta\Sigma$  designs were explored in depth for both single-ended and differential inputs. Multi-bit and higher-order designs are investigated. Each of these  $\Delta\Sigma$  circuit variants were modeled and simulated in MATLAB and HSPICE. The first-order single-bit single-ended and differential input  $\Delta\Sigma$  ADCs were fabricated in a standard 0.18- $\mu$ m CMOS technology and the experimental results are revealed in Chapter 6.

Pipeline and cyclic A/D conversion is described in Chapter 7, again in the context of TMSP. The TMSP circuit blocks that comprise the time-mode cyclic ADC are described in detail. The design was fabricated in a 0.18-µm CMOS technology, and the experimental results are presented.

For completeness, the time-mode implementation of successive approximation register and integrated ADCs are described in Chapter 8. MATLAB system level simulations were performed to aid in the discussion and understanding of these time-mode ADC topologies.

Finally, this dissertation is concluded in Chapter 9 where the work is summarized, strengths and weaknesses are highlighted, and future advancements of this work are offered.

## **Chapter 2: Analog-to-Digital Conversion**

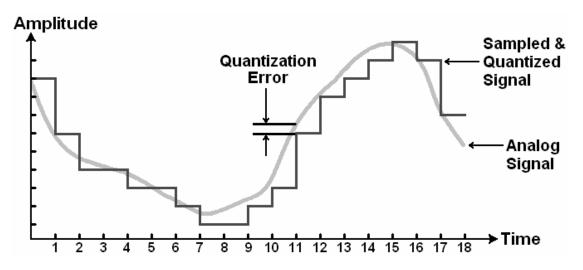

An analog-to-digital converter (ADC) is a circuit that samples continuous-time analog information and converters it into a discrete digital representation. Analog-to-digital (A/D) conversion may be viewed as a two-step process. Figure 2.1 demonstrates the ADC process where in the first step a continuous-time analog input signal is sampled at discrete instances of time. In the second step the sampled analog amplitude is quantized. The error between the true input analog value and the quantized digital output value is known as the quantization error  $\varepsilon_q$ .

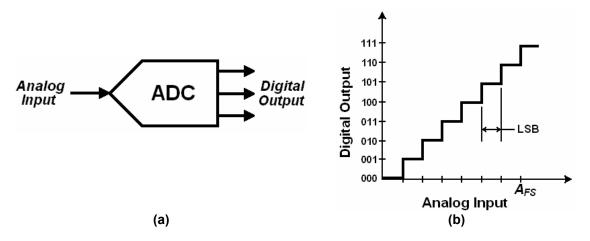

Figure 2.2(a) displays a block diagram of an ADC. The continuous-time analog input, typically a voltage signal, can be any value between zero and the full-scale

Figure 2.1: Analog-to-digital conversion process example.

amplitude  $A_{FS}$ . The digital output is a binary number where the number of digits (i.e. bits) dictates the converter's resolution. The ADC resolution is defined by the smallest analog input change that will result in a least significant bit (LSB) digital output code change. If there are N output bits, then the ADC may resolve  $2^{N}$  analog levels. The digital output is represented as

$$D_{OUT} = d_{N-1}d_{N-2}d_{N-3}...d_2d_1d_0, (2.1)$$

where  $d_{N-1}$  is the most significant bit (MSB) and  $d_0$  is the LSB. The input analog value  $A_{IN}$ , digital output bits  $D_{OUT}$ , and quantization error  $\varepsilon_q$  are related by the expression

$$A_{IN} = A_{FS} \left( \frac{d_{N-1}}{2^N} + \frac{d_{N-2}}{2^{N-1}} + \dots + \frac{d_1}{2^2} + \frac{d_0}{2^1} \right) + \varepsilon_q.$$

(2.2)

An example transfer characteristic of an ADC is offered in Figure 2.2(b). In this case the ADC has a 3-bit resolution (i.e. N=3) and the LSB is given by

$$LSB = \frac{A_{FS}}{2^{N} - 1}.$$

(2.3)

In a perfect ADC the quantization error is bounded between ±LSB/2. If it is assumed that the quantization error signal is uncorrelated with the input signal and that it is uniformly distributed within ±LSB/2 then we may approximate the

Figure 2.2: Analog-to-digital converter (ADC) (a) block diagram; (b) transfer characteristic.

power of the quantization noise as

$$P_{\varepsilon} = \frac{LSB^{2}}{12} = \frac{\left(\frac{A_{FS}}{2^{N} - 1}\right)^{2}}{12}.$$

(2.4)

There are two classifications of ADC based on their conversion rate: Nyquist rate and oversampled. Nyquist-rate data converters sample the input at a frequency which is greater than two times that of the input signal bandwidth (i.e. at the Nyquist frequency). Flash, pipeline, SAR, and integrating ADCs all participate in this category. Oversampled ADCs process the input signal at a much higher conversion rate. Delta-sigma ADCs fulfill this classification.

There are many applications for ADCs with varying performance criteria. For example, measurement systems require high-resolution converters, video processing applications need high-speed ADCs, and battery operated devices use lower power designs. Therefore Section 2.1 is dedicated to the design specifications used to measure and compare ADCs. Section 2.2 presents the performance metrics and figure of merits of ADCs. There are five fundamental ADC processing algorithms and circuit topologies: flash ADCs, pipeline ADCs, successive approximation register ADCs, delta-sigma ADCs and integrating ADCs. Each of these conversion strategies are described in Section 2.3.

### 2.1 - ADC Design Specifications

There are many design requirements when selecting an ADC topology and implementing its circuitry. They are: signal bandwidth or sampling rate, resolution, distortion, power, area, noise immunity, dynamic range, and latency. Each of these specifications will be described separately in the following subsections.

### 2.1.1. Signal Bandwidth or Sampling Rate

The signal bandwidth of an ADC is typically defined as the frequency range over which the ADC will maintain its quoted resolution. Signal bandwidth and clock sampling rate of an ADC are related by the Nyquist criterion. In other words, the sampling rate is at least twice the signal bandwidth. There are many applications requiring A/D conversion some of which are presented in Table 2.1 along with their required sampling rates. The information in Table 2.1 was compiled from the data sheets found in [12], [13], and [14]. It may be seen that applications span and overlap almost the entire frequency spectrum up to 4 GHz.

Table 2.1: ADC applications and their intended bandwidths and required resolutions.

| Application                        | Sampling Rate   |         |

|------------------------------------|-----------------|---------|

| Sensors                            |                 |         |

| Energy monitoring                  | 1 – 100 Hz      | 16 – 24 |

| Motor-control                      |                 |         |

| Audio market (computer audio,      |                 |         |

| CD, FM stereo, digital audio tape, | 48 – 192 kHz    | 12 – 16 |

| DVD audio)                         |                 |         |

| Data acquisition systems           |                 |         |

| Instrumentation applications       | 500 kHz – 5 MHz | 12 – 18 |

| ATE                                |                 |         |

| Medical Imaging                    | 5 – 200 MHz     | 10 – 16 |

| Communication (IF sampling,        | 30 – 100 MHz    | 10 – 14 |

| base stations)                     |                 |         |

| Instrumentation (digital           |                 |         |

| oscilloscopes, spectrum            | 5 – 100 MHz     | 10 – 14 |

| analyzers)                         |                 |         |

| Consumer electronics (digital      |                 |         |

| cameras, display electronics,      | 5 – 75 MHz      | 10 – 12 |

| DVD, HDTV)                         |                 |         |

| Digital Video                      | 29 – 100 MHz    | 12 – 14 |

| Software Defined Radio             | 125 – 500 MHz   | 12 – 14 |

| Test & Measurement                 |                 |         |

| Direct RF Down conversion          | 0.5 – 4 GHz     | 6 – 8   |

| High-Speed Data Acquisition        |                 |         |

#### 2.1.2. Resolution

Resolution of an ADC is a measure of how accurately the digital output will represent the analog input. It may be defined as the smallest analog input change that will results in an LSB change in the digital output code. Resolution is often expressed in number of bits N in the digital output. Hence, there are  $2^N$  digital output possibilities. Table 2.1 presents several applications and their required resolutions. Note that resolution and sampling rate are generally inversely related.

Quantization error is related to the resolution of an ADC and generates a noise floor in the power spectral density of an ADC's output. The power of this noise floor may be approximated by Equation (2.4).

#### 2.1.3. Distortion

The nonlinearity of semiconductor devices and the mismatch between identical circuit components may produce distortion in the output of an ADC. Layout techniques [15] such as common centroid configurations may be implemented to reduce mismatch. Many calibration mechanisms have been reported to compensate for mismatch, such as laser-trimming, offset cancellation [16], dynamic element matching (DEM) [17], and calibration look-up tables [18]. Regardless of these efforts distortion is a rapidly growing problem in the integration of analog and mixed-signal CMOS circuits designed in state-of-the-art digital CMOS processes.

### 2.1.4. Dynamic Range

As emerging CMOS technology scales down, the transistor gate oxide thickness reduces which forces the supply voltage to decrease. Consequently, the linear operating region of a transistor circuit decreases thus reducing the usable input voltage signal swing of an ADC. The dynamic range of an ADC is loosely

defined as the range of input amplitudes which are larger than the noise and distortion from the system. Therefore, the dynamic range of an ADC will suffer if the signal swing is reduced, or if the noise or distortion is increased.

#### 2.1.5. Power

An important goal in any circuit design is to minimize its power consumption. In large VLSI systems where digital, analog, and mixed-signal components are integrated together, the maximum power dissipation is often stipulated and governed by circuit reliability issues and power supply restrictions (e.g. battery-powered devices). As such, a power budget is allocated to an ADC. The control of power dissipation is achieved with architectural selection and circuit design techniques.

#### 2.1.6. Area

When a design is laid out in a silicon-based technology it inevitably occupies an area. Cost of silicon grows proportionally with area. Moreover, CMOS processes are subject to defects within the technology. Statistically the density of these defects will affect larger circuits. Therefore, minimizing area will reduce cost and decrease the probability that a circuit fails due to defects.

# 2.1.7. Noise Immunity

All electronics circuits are subjected to random environmental and external noise sources such as thermal noise, flicker noise, cross talk, power supply noise, clock jitter, and electromagnetic interference (EMI). Thermal noise may be reduced significantly by circuit design techniques while cross talk may be eliminated with layout techniques. Power supply noise and clock jitter are external influences to an ADC and will seriously affect its performance if the supply and clock source are not designed with care.

#### **2.1.8. Latency**

Latency in ADCs refers to the number of clock cycles between the sampling of the analog input signal and the instance when the digital data is presented to the ADC output. Latency is an important design consideration for real-time data conversion systems.

#### 2.2 - ADC Performance Metrics and Figures of Merit

Metrics and figures of merit are used to evaluate the performance, characterize, and compare ADCs. The most widely used measurements are described in the following subsections.

#### 2.2.1. Gain and Offset Error

ADCs are typically designed with a unity gain such that the full scale input voltage range maps uniformly to the  $2^N$  different digital output codes. In some cases, exemplified in Figure 2.3(a), the gain differs from unity. The input voltage range is decreased when the gain is greater than unity, however all digital codes

Figure 2.3: 3-bit examples of ADC (a) gain error and (b) offset error.

exist as shown in Figure 2.3(a). If the gain is reduced from unity then the most significant digital codes may never be exercised. Another result of ADC gain error is that the length of an LSB is modified such that

$$LSB = G \frac{A_{FS}}{2^{N} - 1},$$

(2.5)

where *G* is the gain factor which deviated from unity.

Offset error is a common problem in some ADC designs resulting in the digital code transitions occurring at input voltages which are offset from the ideal ADC design, as illustrated in Figure 2.3(b). Offset is easily calibrated in many ADC designs.

#### 2.2.2. Integral Nonlinearity

Integral nonlinearity (INL) is a measure of the deviation of an ADCs output transfer characteristic from a straight line. Figure 2.4(a) shows a 3-bit ADC example. The straight line may be drawn as a best fit line, as shown in the figure, or it may be drawn between the end points. INL is typically measured in the number or fraction of LSBs that the actual transitions occur from the straight line. A linear ADC must have its INL error bounded between ±0.5 LSBs.

Figure 2.4: 3-bit ADC linearity error examples of (a) integral nonlinearity (INL); (b) differential Nonlinearity (DNL).

#### 2.2.3. Differential Nonlinearity

The differential nonlinearity (DNL) error of an ADC is defined as the difference between the ideal step width and the width of an ideal LSB. Figure 2.4(b) shows an example of a 3-bit ADC with its DNL error. If the DNL error exceeds 1 LSB then there is a possibility that missing codes or non-monotonic behaviour will result.

#### 2.2.4. Signal-to-Noise Ratio

The signal-to-noise ratio (SNR) is the ratio of the RMS value of the input signal  $V_{INRMS}$  to the RMS value of the sum of all other spectral components (i.e. noise)  $V_{NOISERMS}$  over a defined bandwidth excluding the harmonics and DC component. SNR is usually expressed in decibels using the formula

$$SNR = 20\log\left(\frac{V_{IN_{RMS}}}{V_{NOISE_{RMS}}}\right). \tag{2.6}$$

The noise information may be comprised of quantization, thermal, flicker, jitter-induced, power supply, or EMI noise. In the case where the noise is only due to quantization error, then the signal-to-quantization noise ratio (SQNR) is expressed as

$$SQNR = 20\log\left(\frac{V_{IN_{RMS}}}{V_{QN_{RMS}}}\right), \tag{2.7}$$

where  $V_{QNRMS}$  is the RMS quantization noise. An ADC's resolution, expressed in number of bits, may be deduced from the SQNR using

$$resolution = \frac{SQNR - 1.76}{6.02}.$$

(2.8)

# 2.2.5. Signal-to-Noise-and-Distortion Ratio

The signal-to-noise-and-distortion ratio (SNDR) is the ratio of the RMS value of the input signal  $V_{INRMS}$  to the RMS value of the sum of all other spectral

components over a defined bandwidth including noise  $V_{NOISERMS}$  and distortion  $V_{DISTORTIONRMS}$ , but excluding the DC component. SNDR is usually expressed in decibels using the formula

$$SNDR = 20\log\left(\frac{V_{IN_{RMS}}}{V_{NOISE_{RMS}} + V_{DISTORTION_{RMS}}}\right).$$

(2.9)

#### 2.2.6. Effective Number of Bits

An alternate expression for SNDR is to represent it in bit resolution, called the effective number of bits (ENOB). ENOB may be computed from SNDR using the expression

$$ENOB = \frac{SNDR - 1.76}{6.02} \,. \tag{2.10}$$

#### 2.2.7. Total Harmonic Distortion

A measure of the ratio between the input signal RMS value and just the harmonically-related distortion components  $V_{DISTORTIONRMS}$  is called total harmonic distortion (THD) and is expressed in decibels with the equation

$$THD = 20\log\left(\frac{V_{IN_{RMS}}}{V_{DISTORTION_{RMS}}}\right). \tag{2.11}$$

# 2.2.8. Spurious-Free Dynamic Range

Spurious-free dynamic range (SFDR) is defined as the ratio between the RMS values of the input signal  $V_{INRMS}$  to the RMS value of the greatest spurious tone in the output signal spectrum  $V_{SPURRMS}$ . It is conventionally expressed in decibels using the formula

$$SFDR = 20\log\left(\frac{V_{IN_{RMS}}}{V_{SPUR_{RMS}}}\right). \tag{2.12}$$

#### 2.2.9. Figures of Merit

There are thousands of ADC designs which vary in circuit topology, technology, operating frequency, resolution, power consumption, and circuit area. In order to compare them fairly many authors use a figure of merit (*FoM*). For example, a very popular *FoM* [19] is using a measure of conversion step per unit energy

$$FoM_1 = \frac{2^{ENOB} \cdot 2 \cdot BW}{P}, \tag{2.13}$$

where P is the power dissipation and BW is the signal bandwidth of the ADC. Another variation of this FoM incorporates area per conversion step described by

$$FoM_2 = \frac{2^{ENOB} \cdot 2 \cdot BW}{P \cdot \left(A/2^n\right)}, \tag{2.14}$$

where *A* is the circuit area and *n* is the converter's desired bit resolution.

# 2.3 - Conventional Analog-to-Digital Converters

There are five main ADC topologies: flash, pipeline, successive approximation register (SAR), delta-sigma, and integrating. Each of these architectures is best suited for particular applications based on sampling frequency, resolution, power, and area requirements. Figure 2.5 shows the intended operating region for each ADC topology in the context of Nyquist conversion speed versus resolution. Each of the five ADC designs is introduced in the following subsections.

Figure 2.5: Comparison between five ADC topologies demonstrating their intended Nyquist sampling rates and their typical resolutions.

## 2.3.1. Flash Analog-to-Digital Conversion

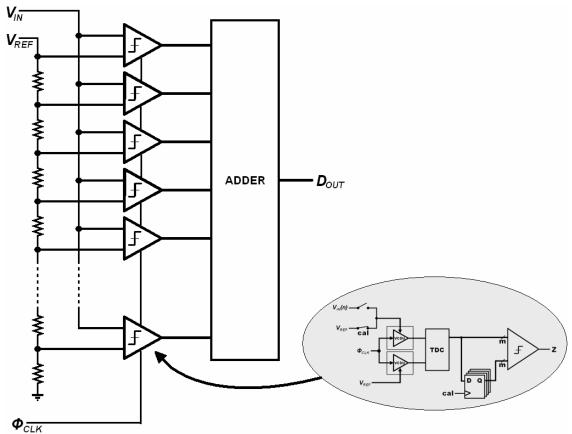

The flash ADC uses comparators in parallel whereby each compares the analog input signal to a different analog reference value. A typical flash ADC architecture is depicted in Figure 2.6. An N-bit flash ADC would require  $2^N$ -1 comparators. In this example, the reference voltages are generated by a resistor string voltage divider. The comparator outputs form a thermometer code which is encoded to generate a binary number.

Due to the parallelism the greatest benefit of a flash ADC is its extremely fast operating speed. Consequently, all other design specifications suffer. The resolution of the flash ADC is restricted by the power and area that the  $2^{N}$ -1 comparators occupy. Typically, flash converters are limited to a resolution below 8-bits. Mismatch within each comparator, between all comparators, and between

resistors will result in non-linear distortion mechanisms that will severely cripple the flash ADC performance.

The comparator output is a thermometer code. This implies that there should be only one transition between logic 0 and logic 1 when traversing from the LSB to the MSB. However, it may happen that a logic 1 may appear between two logic 0 outputs. This is known as a bubble error. If the thermometer code is convertered directly with a priority encoder, then the wrong binary data may result. Therefore, it is also the responsibility of the encoder to remove bubble errors.

Figure 2.6: Flash ADC.

# 2.3.2. Pipeline and Cyclic Analog-to-Digital Conversion

A pipeline ADC is presented in Figure 2.7(a) and consists of M conversion stages and circuitry to digitally align the output. Each individual stage, shown in Figure 2.7(b), samples the analog input voltage  $V_{IN}$  using a sample-and-hold circuit, converts  $V_{IN}$  into a b-bit digital word using a flash ADC, and produces a residual voltage  $V_R$ . The residual voltage is the difference between the stage input voltage and the digital output converted into voltage via a DAC multiplied by a gain factor of  $2^b$ . For example, if b = 2 then

$$V_R = 2^2 \left( V_{IN} - V_{FS} \left( \frac{d_1}{2^2} + \frac{d_0}{2^1} \right) \right), \tag{2.15}$$

where  $V_{FS}$  is the full scale voltage of the input signal and consequently is used

Figure 2.7: Pipeline ADC (a) complete design with M stages; (b) individual stage.

as the DAC reference voltage. Typically, the number of bits *b* is between one and four to relax the requirements of the ADC.

Once the first pipeline stage has completed its processing of an input sample, it is passed to the next stage. At the same time, the first stage begins to process the next input sample. This action is know as *pipelining* and accounts for the high data throughput since the entire converter may operated on *M* input samples simultaneously. The digital data corresponding to a single input sample is propagated through the pipeline resulting in misalignment of the data and data latency. Shift registers are used to perform time alignment on the data. However, the latency of the pipeline architecture is inevitable.

The flash ADC, DAC, and amplifier in each pipeline stage will be influenced by process variation thus limiting their accuracy. Error correction mechanisms are extensively implemented to reduce the ADC requirements. A popular correction scheme is to produce an extra bit from each pipeline stage while maintaining the amplifier gain. This overlapping bit provides sufficient redundancy such that comparator offsets in the flash ADCs will be compensated. However, the gain and linearity error in the DACs and amplifiers cannot be fixed by this error

Figure 2.8: Cyclic or algorithmic ADC.

correction strategy. Hence, a calibration scheme would also need to be applied.

In order to minimize power and area consumption, the pipeline ADC may be converted into a cyclic or algorithmic architecture, as illustrated in Figure 2.8. This design uses only one pipeline stage and feeds back the residue voltage  $V_R$  through a switch to be processed by the same stage. The cyclic ADC no longer benefits from the speed of the pipelining, however it consumes significantly less power and occupies a much smaller silicon area. Furthermore, only one ADC, DAC and amplifier need to be calibrated. The data latency problem no longer exists for the cyclic design as it may only process one sample per clock period.

Pipeline ADCs are perhaps the most popular ADC conversion strategy as the offer the best compromise between speed and resolution.

# 2.3.3. Successive Approximation Register Analog-to-Digital Conversion