# Stochastic Decoding of Low-Density Parity-Check Codes

Saeed Sharifi Tehrani

Doctor of Philosophy

Department of Electrical and Computer Engineering

McGill University

Montreal, Quebec, Canada

January 2011

A thesis submitted to McGill University in partial fulfilment of the requirements of the degree of Doctor of Philosophy

© Saeed Sharifi Tehrani, 2011

# **DEDICATION**

I dedicate this dissertation to my parents for their unconditional love and support that made it possible.

#### ACKNOWLEDGEMENTS

I consider myself fortunate to have been able to work in this doctoral research with professors and talented scholars from universities in Canada, the United States, and France. First and foremost, I would like to express my sincere gratitude to my advisors, Prof. Warren J. Gross and Prof. Shie Mannor, for their guidance as well as their continuous encouragement and support throughout this five-year journey.

I wish to thank Prof. Paul H. Siegel, my host advisor during a six-month visit to the Center for Magnetic Recording Research (CMRR), University of California, San Diego (UCSD). I benefited extensively from his vast knowledge and experience, and was impressed by his open and warm personality. The joint stochastic decoding of low-density parity-check codes and partial-response channels, presented in Chapter 6 of this dissertation, was developed during my visit to the CMRR, UCSD, in 2010.

I am thankful to Prof. Fabrice Labeau and Prof. Zeljko Zilic for taking precious time to serve on my advisory committee. I am also thankful to Prof. Vincent Gaudet at the University of Waterloo for helpful discussions and for encouraging me to start my Ph.D. at McGill University. His interesting paper with Anthony Rapley on stochastic decoding was the first inspiration for this doctoral research. I would like to thank Prof. Chris Winstead at Utah State University, and Prof. Sheryl L. Howard at Northern Arizona University, for helpful discussions and their support during this doctoral research. I am also indebted to my M.Sc. advisors at the University of Alberta, Prof. Bruce F. Cockburn and Prof. Stephen Bates, for their kind support.

I would like to thank the coauthors of my publications for their collaborations. I am thankful to Prof. Christophe Jego at the ENSEIRB-MATMECA Bordeaux, France, for his help in applying the stochastic decoding approach to the turbo-oriented adaptive belief propagation. I would like to thank Ali Naderi and Guy-Armand Kamendje for their help in the Verilog development and place-and-routing of ASIC stochastic decoders. I also would like to thank Bo Zhu for providing and discussing the initial results for stochastic Reed-Solomon decoding, and Saied Hemati for his helpful suggestions on making hard-decisions in stochastic decoders using majority criterion and on performing the tracking forecast memory operation using one adder/subtractor unit.

I am thankful to my officemates and my wonderful friends at McGill University and UCSD. They have filled the past five years of my life with so many joyful moments.

I am sincerely grateful to my parents and my brother for always being supportive and encouraging in my pursuit of academic excellence. I would like to express my profound appreciation and deepest gratitude to my parents for their constant care and love. Without them, I would not ever have completed this dissertation.

I acknowledge the Natural Science and Engineering Research Council of Canada (NSERC) for awarding the Alexander Graham Bell Canada Graduate Scholarship (CGS Doctoral) and the Michael Smith Foreign Study Scholarship. I also acknowledge the Fonds Québécois de la Recherche sur la Nature et les Technologies (FQRNT) for awarding the Quebec International Internship Scholarship. This doctoral research was financially supported by the NSERC, the FQRNT, and the Canada Research Chair (CRC) funds. Also, research work presented in Chapter 6 of this dissertation was supported in part by the United States National Science Foundation (NSF) grant number CCF-0829865. Results reported in Chapter 5 of this dissertation were obtained in part thanks to the use of WestGrid and CLUMEQ computing resources.

#### ABSTRACT

Low-Density Parity-Check (LDPC) codes are one of the most powerful classes of error-control codes known to date. These codes have been considered for many recent digital communication applications. In this dissertation, we propose stochastic decoding of state-of-the-art LDPC codes and demonstrate it as a competitive approach to practical LDPC decoding algorithms.

In stochastic decoding, probabilities are represented as streams of random bits using Bernoulli sequences in which the information is contained in the statistics of the bit stream. This representation results in low hardwarecomplexity processing nodes that perform computationally-intensive operations. However, stochastic decoding is prone to the acute problem of latching. This problem is caused by correlated bit streams within cycles in the code's factor graph, and significantly deteriorates the performance of stochastic LDPC decoders.

We propose edge memories, tracking forecast memories, and majority-based tracking forecast memories to address the latching problem. These units efficiently extract the evolving statistics of stochastic bit streams and rerandomize them to disrupt latching. To the best of our knowledge, these methods are the first successful methods for stochastic decoding of state-of-the-art LDPC codes.

We present novel decoder architectures and report on several hardware implementations. The most advanced reported implementation is a stochastic decoder that decodes the (2048,1723) LDPC code from the IEEE 802.3an standard. To the best of our knowledge, this decoder is the most silicon areaefficient and, with a maximum core throughput of 61.3 Gb/s, is one of the fastest fully parallel soft-decision LDPC decoders reported in the literature.

We demonstrate the performance of this decoder in low bit-error-rate regimes.

In addition to stochastic LDPC decoding, we propose the novel application of the stochastic approach for joint decoding of LDPC codes and partialresponse channels that are considered in practical magnetic recording applications. Finally, we investigate the application of the stochastic approach for decoding linear block codes with high-density parity-check matrices on factor graphs. We consider Reed-Solomon, Bose-Chaudhuri-Hocquenghem, and block turbo codes.

### **ABRÉGÉ**

À ce jour, les codes Low-Density Parity-Check (LDPC) font partie des codes correcteurs d'erreurs les plus performants. Ces codes sont inclus dans différents standards de communications numériques. Dans ce manuscrit, nous proposons d'utiliser le décodage stochastique pour les codes LDPC. D'autre part, nous démontrons que pour les codes LDPC, le décodage stochastique représente une alternative réaliste aux algorithmes de décodage existants.

Dans le processus de décodage stochastique, les probabilités sont représentées sous forme de séquences de Bernoulli. L'information est contenue dans la statistique de ces flux binaires aléatoires. Cette représentation particulière permet d'exécuter des calculs intensifs avec une faible complexité matérielle. Cependant le décodage stochastique est enclin au problème du verrouillage ("latching"). La corrélation entre les bits des différents flux au sein des cycles du graphe biparti dégrade les performances du décodage stochastique des codes LDPC.

Pour résoudre le problème du verrouillage, nous proposons trois solutions: les mémoires de branche, les mémoires de suivi, et les mémoires de suivi à majorité. Ces différents composants permettent de suivre l'évolution de la statistique des flux binaires et de réintroduire des éléments aléatoires au sein des séquences observées, minimisant ainsi le phénomène de verrouillage. À notre connaissance, il s'agit là des premiers résultats probants permettant un décodage stochastique efficace des codes LDPC.

Nous proposons de nouvelles architectures de décodeurs associées à leurs implantations matérielles respectives. La plus perfectionnée des architectures présentée ici est celle d'un décodeur stochastique pour le code LDPC (2048,1723) associé au standard IEEE 802.3an. À notre connaissance, en comparaison avec

l'état de l'art actuel, ce décodeur dispose du meilleur rapport vitesse/complexité. Le débit maximum (au niveau du coeur), est de 61.3 Gb/s, il s'agit là du plus rapide des décodeurs de codes LDPC à décisions souples connu à ce jour. Nous présentons par ailleurs les performances de ce décodeur à très faible taux d'erreurs binaire.

De plus, nous proposons d'appliquer le calcul stochastique au décodage conjoint des codes LDPC et des canaux à réponse partielle qui est utilisé dans les applications d'enregistrement magnétique. Enfin, nous étudions l'extension du décodage stochastique au décodage des codes en blocs ayant une matrice de parité à forte densité. Nous appliquons le décodage stochastique sur des graphes biparti aux codes Reed-Solomon, Bose-Chaudhuri-Hocquenghem, et aux turbocodes en blocs.

# TABLE OF CONTENTS

| DED      | OICATI     | ON                                                                        |

|----------|------------|---------------------------------------------------------------------------|

| ACK      | NOWI       | EDGEMENTS                                                                 |

| ABS      | TRAC       | Γ                                                                         |

| ABR      | ÆÉGÉ       |                                                                           |

| LIST     | OF T       | ABLES xiii                                                                |

| LIST     | OF F       | GURES                                                                     |

| 1        | Introd     | action                                                                    |

|          | 1.1        | Motivations                                                               |

|          | 1.2<br>1.3 | Objectives                                                                |

|          | 1.4        | 1.3.1 List of Publications and Patent Applications 8 Dissertation Outline |

| 2        |            | ound                                                                      |

| <i>L</i> | O          |                                                                           |

|          | 2.1        | LDPC Codes and Iterative Decoding                                         |

|          | 2.2        | Strategies and Challenges of Hardware Implementations of                  |

|          | 2.3        | LDPC Decoders                                                             |

|          |            | 2.3.1 Stochastic Representation                                           |

|          |            | 2.3.2 Main Stochastic Operations                                          |

|          |            | 2.3.2.2 Multiplication                                                    |

|          |            | 2.3.2.3 Division                                                          |

|          |            | 2.3.2.4 Addition                                                          |

|          | 2.4        | Early Stochastic Decoding Methods                                         |

|          |            | 2.4.1 Basic Stochastic Variable Node                                      |

|          |            | 2.4.2 Stochastic Parity-Check Node 26                                     |

|          |            | 2.4.3 The Latching Problem                                                |

|          |            | 2.4.4 Supernodes                                                          |

|          |            | 2.4.5 Scaling Channel Reliabilities                                       |

| 3 | Edge | -Based Rerandomization Using Edge Memories                 | 32 |

|---|------|------------------------------------------------------------|----|

|   | 3.1  | Edge Memories and Regenerative Bits                        | 32 |

|   | 3.2  |                                                            | 34 |

|   | 3.3  |                                                            | 36 |

|   | 3.4  | Effects on the Decoding Performance                        | 38 |

|   | 3.5  | A (1056,528) Fully Parallel EM-based LDPC Decoder 4        | 41 |

|   |      |                                                            | 41 |

|   |      | 3.5.1.1 Scaling                                            | 42 |

|   |      |                                                            | 42 |

|   |      | 3.5.1.3 Architecture of Variable Nodes                     | 43 |

|   |      | 3.5.1.4 Hard-Decision using Saturating Up/Down             |    |

|   |      |                                                            | 45 |

|   |      | 3.5.1.5 Architecture of Parity-Check Nodes                 | 45 |

|   |      | 3.5.1.6 Asynchronous Pipelining and Interleaver Design     | 47 |

|   |      |                                                            | 49 |

|   |      | 3.5.1.8 Termination Criteria                               | 50 |

|   |      | 3.5.1.9 Input/Output Unit                                  | 50 |

|   |      |                                                            | 51 |

|   |      | 3.5.2.1 Decoding Performance                               | 51 |

|   |      | 3.5.2.2 Area and Clock Frequency                           | 52 |

|   |      |                                                            | 53 |

|   |      | 3.5.2.4 Latency                                            | 55 |

|   | 3.6  | A (1024,512) Fully Parallel EM-based LDPC Decoder          | 56 |

|   | 3.7  | Comparison                                                 | 57 |

|   |      | 3.7.1 Comparison with FPGA Fully Parallel Decoders         | 58 |

|   |      | 3.7.2 Comparison with FPGA Partially Parallel Decoders . 3 | 59 |

|   | 3.8  | Conclusion                                                 | 60 |

| 4 | T2 1 |                                                            | co |

| 4 | Eage | -Based Rerandomization Using Tracking Forecast Memories    | 63 |

|   | 4.1  | Tracking Forecast Memories                                 | 64 |

|   | 4.2  |                                                            | 67 |

|   |      |                                                            | 67 |

|   |      |                                                            | 68 |

|   |      |                                                            | 69 |

|   |      |                                                            | 71 |

|   | 4.3  |                                                            | 72 |

|   | 4.4  | •                                                          | 74 |

|   |      | - •                                                        | 74 |

|   |      |                                                            | 77 |

|   | 4.5  | - v -                                                      | 77 |

| 5 |       | e-Based Rerandomization Using Majority-Based Tracking recast Memories |

|---|-------|-----------------------------------------------------------------------|

|   | 5.1   | Majority-Based Tracking Forecast Memories 80                          |

|   | 5.2   | Hardware Realization of MTFMs                                         |

|   |       | 5.2.1 General Architecture                                            |

|   |       | 5.2.2 Reduced-Complexity Architecture 84                              |

|   | 5.3   | Comparison of the Hardware-Complexity and Decoding                    |

|   |       | Performance of MTFMs with EMs and TFMs 85                             |

|   | 5.4   | A (2048,1723) Fully Parallel MTFM-based Stochastic LDPC               |

|   |       | Decoder                                                               |

|   |       | 5.4.1 Decoder Architecture and Specifications                         |

|   |       | 5.4.1.1 Random Number Generation                                      |

|   |       | 5.4.1.2 Early Decoding Termination Criterion 91                       |

|   | F F   | 5.4.1.3 Redecoding and Postprocessing 93                              |

|   | 5.5   | Performance and Tradeoffs                                             |

|   |       | 5.5.1 Decoding Performance                                            |

|   |       | Complexity                                                            |

|   |       | 5.5.3 Throughput                                                      |

|   |       | 5.5.4 Latency                                                         |

|   |       | 5.5.5 Input and Output Buffer Requirements                            |

|   | 5.6   | Comparison with State-of-the-Art ASIC LDPC Decoders 101               |

|   | 5.7   | Conclusion                                                            |

| 6 |       | Stochastic Decoding of LDPC Codes and Partial-Response nannels        |

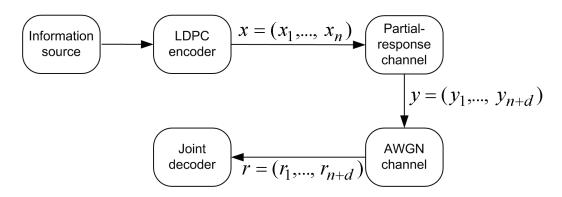

|   | 6.1   | System Model                                                          |

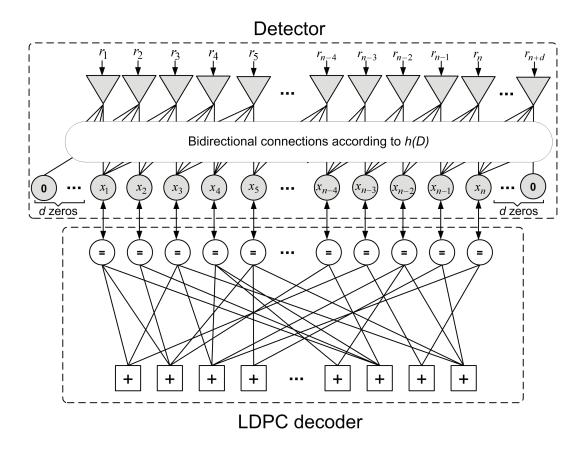

|   | 6.2   | Overview of Joint Message-Passing Decoding 105                        |

|   | 0.2   | 6.2.1 Operation of Triangle Nodes                                     |

|   |       | 6.2.2 Operation of Bit Nodes                                          |

|   | 6.3   | The Proposed Method                                                   |

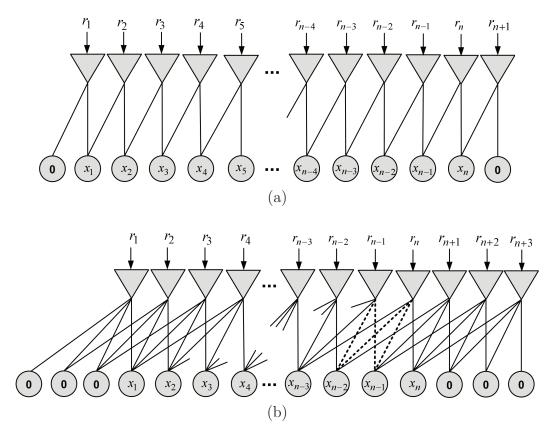

|   | 0.0   | 6.3.1 Stochastic Triangle Nodes for the Dicode Channel                |

|   |       | Detector                                                              |

|   |       | 6.3.2 Stochastic Triangle Nodes for the EPR4 Channel                  |

|   |       | Detector                                                              |

|   | 6.4   | Decoding Performance Results                                          |

|   | 6.5   | Estimation of Decoding Latency and Throughput 117                     |

|   | 6.6   | Stochastic Channel Detection and Log-Based LDPC Decoding 120          |

|   | 6.7   | Conclusion                                                            |

| 7 | Stock | nastic Decoding of Linear Block Codes with High-Density               |

| ' |       | rity-Check Matrices                                                   |

|   |       |                                                                       |

|   | 7.1   | Overview                                                              |

|     |        | 7.1.1 Adaptive Belief Propagation                   | 23 |

|-----|--------|-----------------------------------------------------|----|

|     |        | 7.1.2 Turbo-Oriented Adaptive Belief Propagation 12 |    |

|     | 7.2    | The Stochastic Decoding Method                      | 26 |

|     |        | 7.2.1 High-Degree Stochastic Nodes                  | 27 |

|     |        | 7.2.2 Representing Soft-Output Information          | 27 |

|     |        | 7.2.3 Summary of the Stochastic Decoding Method 12  | 29 |

|     | 7.3    | Decoding Performance Results                        | 29 |

|     | 7.4    | Complexity Comparison and Trade-Offs                | 33 |

|     | 7.5    | Conclusion                                          | 38 |

| 8   | Concl  | usion and Future Work                               | 39 |

|     | 8.1    | Advances                                            | 39 |

|     | 8.2    | Future Work                                         |    |

|     |        | 8.2.1 Power-Efficient Stochastic LDPC Decoders 14   |    |

|     |        | 8.2.2 Reduced-Latency Stochastic LDPC Decoders 14   |    |

|     |        | 8.2.3 Reconfigurable Stochastic LDPC Decoders 14    |    |

|     |        | 8.2.4 Different Channel Models                      | 14 |

|     |        | 8.2.5 Asynchronous Stochastic Decoding              | 14 |

|     |        | 8.2.6 Quantum Stochastic Decoding                   |    |

| A   | Decod  | ling Performance Results for Various LDPC Codes 14  | 16 |

|     | A.1    | Results for EM-Based Decoding                       | 16 |

|     | A.2    | Results for TFM-Based Decoding                      |    |

|     | A.3    | Results for MTFM-Based Decoding                     |    |

| REF | FEREN  | CES                                                 | 52 |

| KEN | / TO / | ADDDTVI ATIONS 16                                   | รถ |

# LIST OF TABLES

| <u>Table</u> |                                                                                                                                                                    | p | age |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

| 3-1          | Irregular LDPC codes chosen from the IEEE 802.16e standard.                                                                                                        |   | 42  |

| 3-2          | Decoding parameters used                                                                                                                                           |   | 51  |

| 3–3          | Xilinx Virtex-4 XC4VLX200-11FF1513 device utilization (LUT: 4-input look-up-table, FF: flip-flop)                                                                  |   | 52  |

| 3-4          | Comparison of FPGA-based fully parallel LDPC decoders (LUT: 4-input look-up-table, FF: flip-flop, LE: Logic Element)                                               |   | 62  |

| 4–1          | Hardware-complexity of TFM-based and EM-based degree-6 VNs in CMOS 90nm technology                                                                                 |   | 74  |

| 4–2          | Synthesis results for EM-based and TFM-based (1056,528) stochastic LDPC decoders in CMOS 90nm technology. All decoders are synthesized for 500 MHz clock frequency |   | 78  |

| 5–1          | Hardware-complexity of degree-6 VNs and degree-32 PN in CMOS 90nm technology                                                                                       |   | 88  |

| 5–2          | Summary of the ASIC implementation results for the (2048,1723) MTFM-based stochastic LDPC decoder                                                                  |   | 96  |

| 5–3          | Comparison with some state-of-the-art high throughput soft-decision ASIC LDPC decoders                                                                             | • | 103 |

| 7–1          | Basic 2-input resources in the fixed-point Offset MSA and stochastic nodes (FX: Fixed-point, ADD: adder, SUB: subtractor, CMP: comparator, CNT: u/d counter)       | • | 136 |

| 7–2          | Implementation comparison on a Xilinx Virtex-4 XC4VLX200-10FF1513 FPGA device (LUT: look-up-table, FF: flip-flop).                                                 | • | 137 |

|              |                                                                                                                                                                    |   |     |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                         | pa | age |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1–1    | The schematic diagram of a communication system                                                                                                                                                                                         |    | 2   |

| 2-1    | A typical factor graph and the interleaver for a full-rank $(n,k)$ LDPC code. A length-4 cycle is dashed. In a conventional implementation with $W$ -bit representation of messages, each edge requires $2W$ wires (for two directions) | •  | 14  |

| 2-2    | Message-passing in the SPA                                                                                                                                                                                                              |    | 16  |

| 2-3    | Some possible streams for a probability of 0.8125                                                                                                                                                                                       |    | 21  |

| 2-4    | Probability to stochastic stream conversion                                                                                                                                                                                             |    | 22  |

| 2-5    | Stochastic multiplication [32]                                                                                                                                                                                                          |    | 23  |

| 2-6    | Stochastic division [32]                                                                                                                                                                                                                |    | 23  |

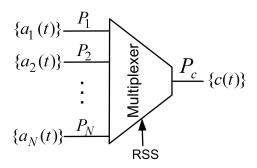

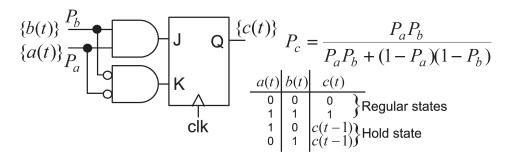

| 2-7    | Approximate stochastic addition [32]                                                                                                                                                                                                    |    | 24  |

| 2-8    | Scaled stochastic addition [16]                                                                                                                                                                                                         |    | 25  |

| 2-9    | The structure of a basic stochastic variable node [36]                                                                                                                                                                                  |    | 26  |

| 2-10   | The structure of a stochastic parity-check node [36]                                                                                                                                                                                    |    | 27  |

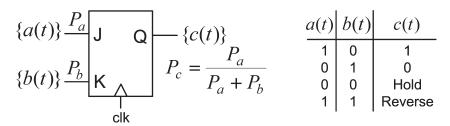

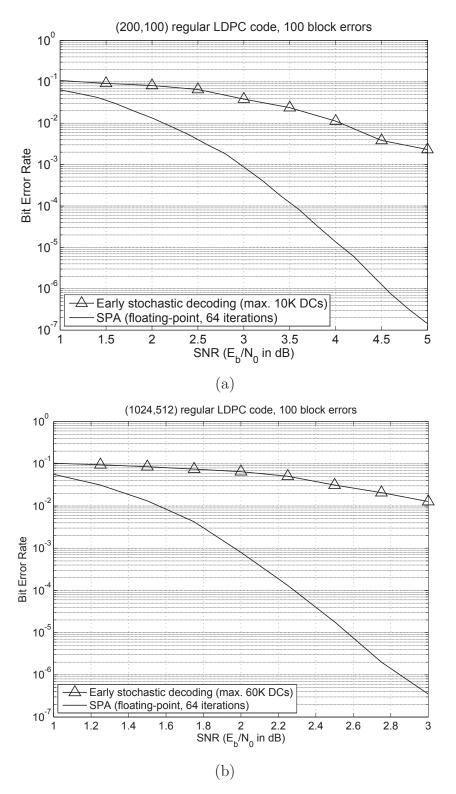

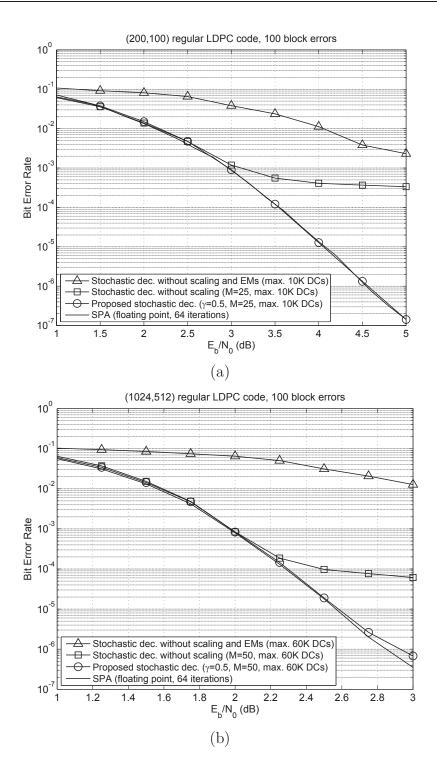

| 2–11   | Decoding performance of the early scholastic decoding method for decoding (a) a (200,100) LDPC code and (b) a (1024,512) LDPC code                                                                                                      |    | 28  |

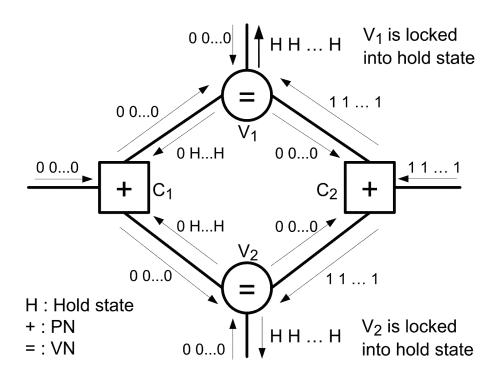

| 2-12   | An example of latching within a length-4 cycle in a factor graph                                                                                                                                                                        | 1. | 29  |

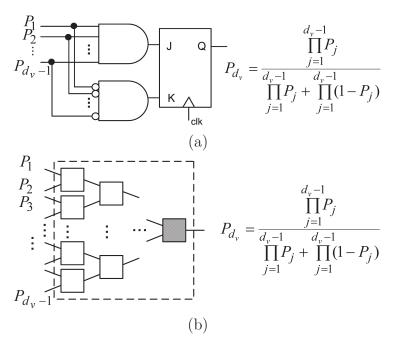

| 2-13   | Structure of supernodes used (a) in [97] and (b) in [37]                                                                                                                                                                                |    | 31  |

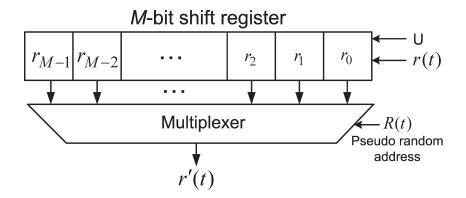

| 3–1    | An EM is implemented as an $M$ -bit shift register with a single selectable bit                                                                                                                                                         |    | 34  |

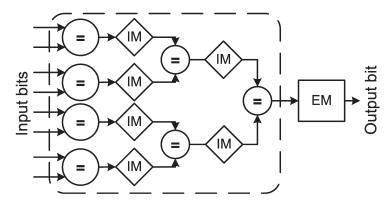

| 3–2    | <ul><li>(a) A structure which is not suitable for high-degree VNs.</li><li>(b) An example of constructing a high-degree VN based on low-degree subnodes</li></ul>                                                                       | •  | 36  |

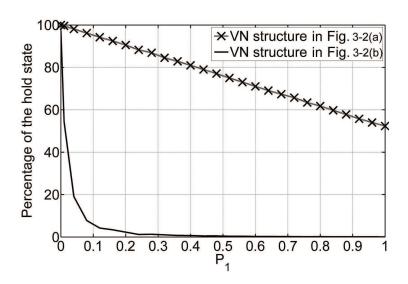

| 3–3    | (a) Percentage of holds on the output of two $d_v = 9$ VNs based on structures in Figure 3–2(a) and Figure 3–2(b), $P_1$ is varying and $P_2 = = P_8 = 0.9.$                                                                            |    | 37  |

| 3–4  | The construction of a VN based on IMs for low-degree sub-VNs. An EM is only used for the exit edge                                                                                                                                                                                                        | 37 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3–5  | The proposed low complexity structure for the implementation of a degree-16 stochastic VN                                                                                                                                                                                                                 | 38 |

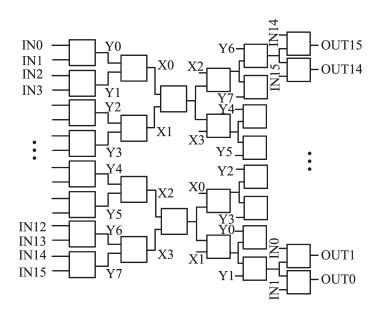

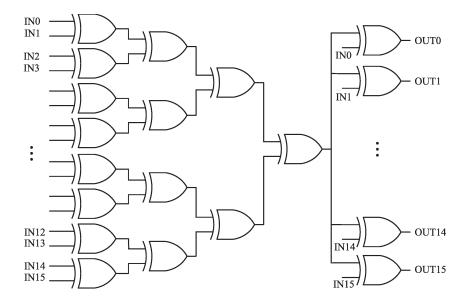

| 3–6  | The structure of a degree-16 stochastic PN based on 2-input binary XORs                                                                                                                                                                                                                                   | 39 |

| 3-7  | Performance of the EM-based approach for decoding (a) a (200,100) code and (b) a (1024,512) code. A high maximum number of decoding cycles is used to show that the significant performance loss (for the case in which EMs and scaling are not used) is not improved by increasing the decoding latency. | 40 |

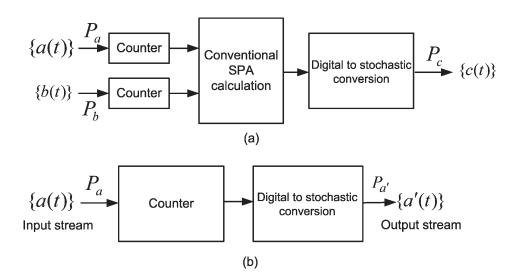

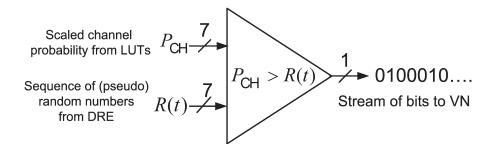

| 3-8  | Conversion of channel probabilities to stochastic streams                                                                                                                                                                                                                                                 | 43 |

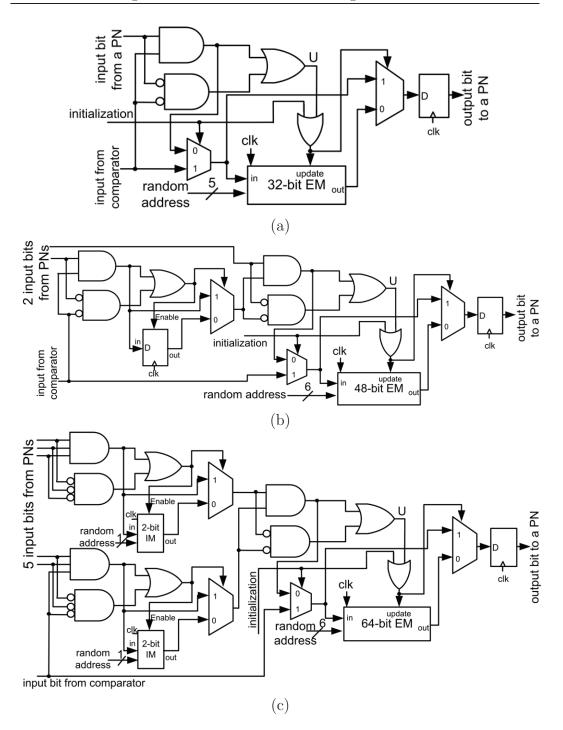

| 3-9  | Architectures of (a) a degree-2 VN, (b) a degree-3 VN, and (c) a degree-6 VN based on IMs and an EM (in each figure, only one output and its corresponding inputs are shown)                                                                                                                              | 46 |

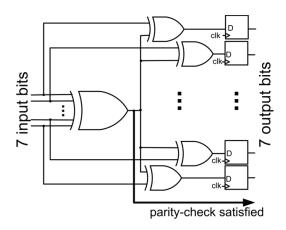

| 3-10 | Architecture of a degree-7 stochastic PN. The "parity-check satisfied" signal is used for termination criteria                                                                                                                                                                                            | 47 |

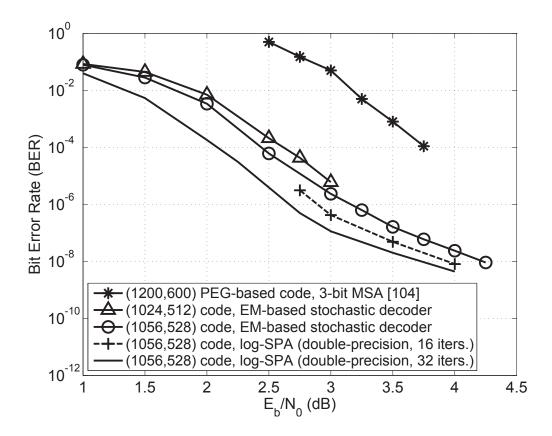

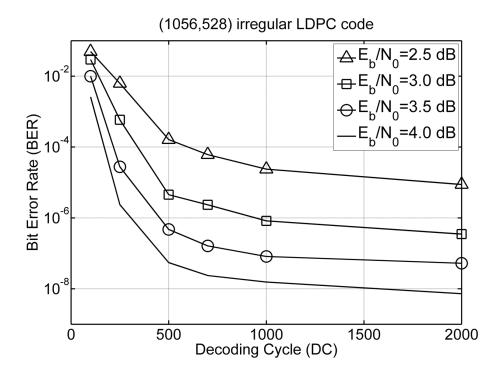

| 3–11 | Decoding performance of the implemented (1056,528) irregular stochastic decoder                                                                                                                                                                                                                           | 52 |

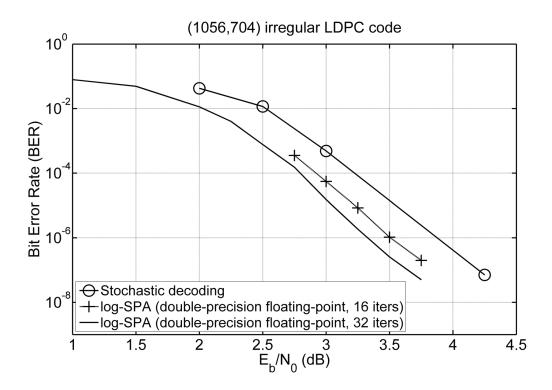

| 3-12 | Decoding performance of the (1056,704) irregular stochastic decoder                                                                                                                                                                                                                                       | 53 |

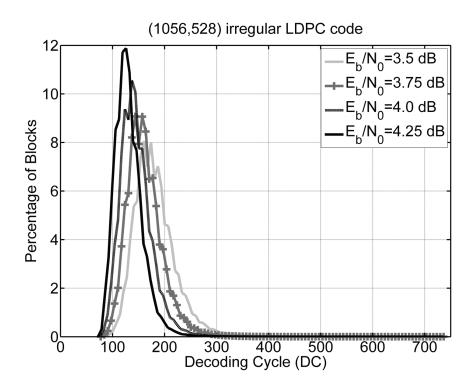

| 3–13 | 8 Histograms of $T_{\text{AVG}}$ at different SNRs (based on 1 million blocks). Each decoding cycle takes one clock cycle                                                                                                                                                                                 | 54 |

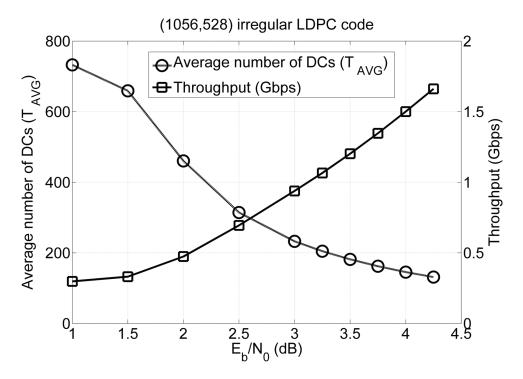

| 3-14 | $T_{ m AVG}$ and throughput of the decoder at different SNRs (based on 1 million blocks). Each decoding cycle takes one clock cycle.                                                                                                                                                                      | 55 |

| 3–15 | Decoding performance of the (1056,528) stochastic decoder over decoding cycles. Each decoding cycle takes one clock cycle                                                                                                                                                                                 | 56 |

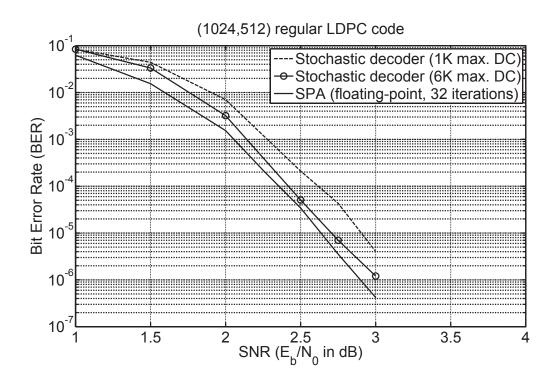

| 3-16 | Decoding performance of the (1024,512) stochastic decoder                                                                                                                                                                                                                                                 | 57 |

| 4–1  | EMs or TFMs are used for rerandomization/decorrelation of stochastic streams and are assigned to each outgoing edge of stochastic VNs                                                                                                                                                                     | 64 |

| 4–2  | Structure of a degree-2 stochastic VN (only one output and its corresponding inputs are shown). An EM or a TFM can be used as a rerandomization unit                                                                                                                                                      | 65 |

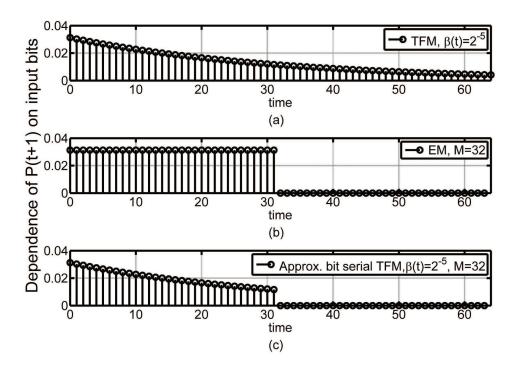

| 4–3  | The dependence of output probability on previous input bits in (a) TFM with $\beta = 2^{-5}$ , (b) EM with $M = 32$ bit length and, (c) approximate bit-serial TFM with $M = 32$ bit length and $\beta = 2^{-5}$       | 67 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

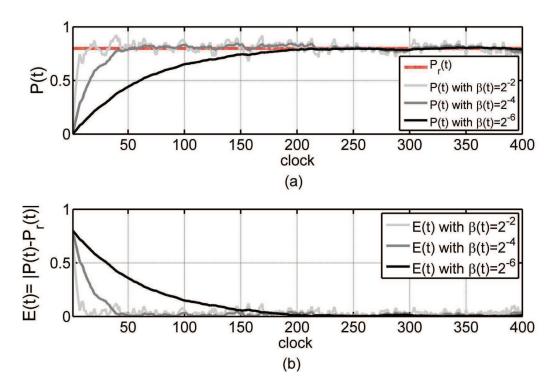

| 4–4  | (a) The convergence speed and (b) the corresponding estimation error of a TFM for different values of $\beta(t)$                                                                                                       | 68 |

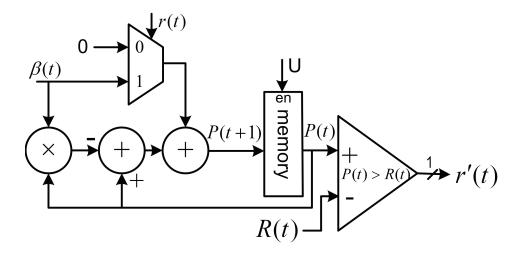

| 4–5  | General architecture of a TFM. $\beta(t)$ can change and take any value in the [0,1] interval                                                                                                                          | 69 |

| 4–6  | Architecture of a reduced-complexity TFM. $\beta(t)$ is a negative power of 2                                                                                                                                          | 70 |

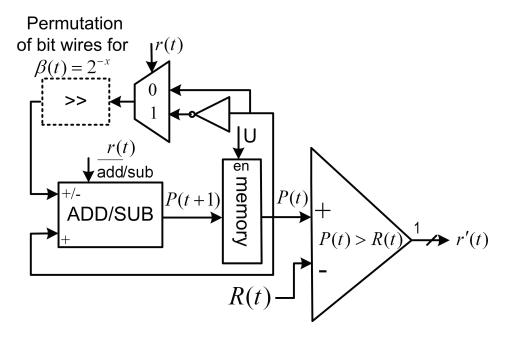

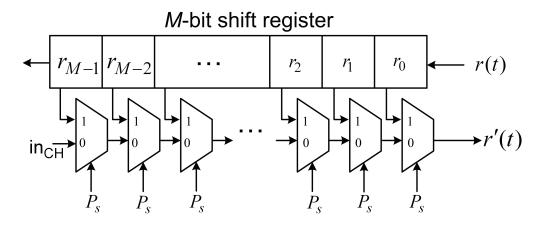

| 4–7  | Architecture of an approximate bit-serial TFM. in <sub>CH</sub> is the input stochastic bit from the channel and $P_s = \beta$                                                                                         | 71 |

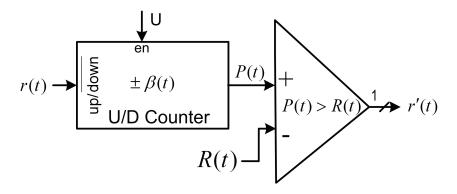

| 4-8  | Architecture of an approximate counter-based TFM                                                                                                                                                                       | 72 |

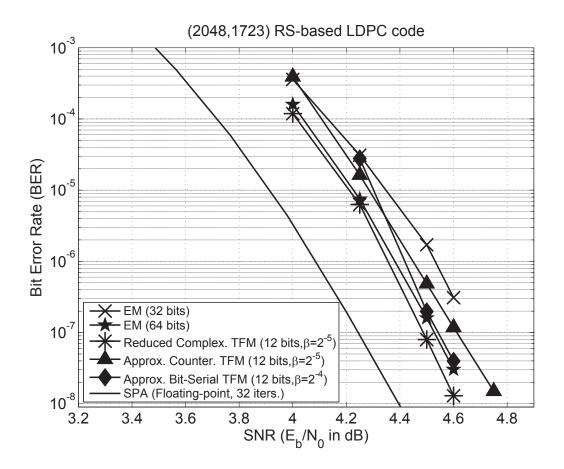

| 4-9  | Comparison of decoding performance of EMs and TFMs                                                                                                                                                                     | 73 |

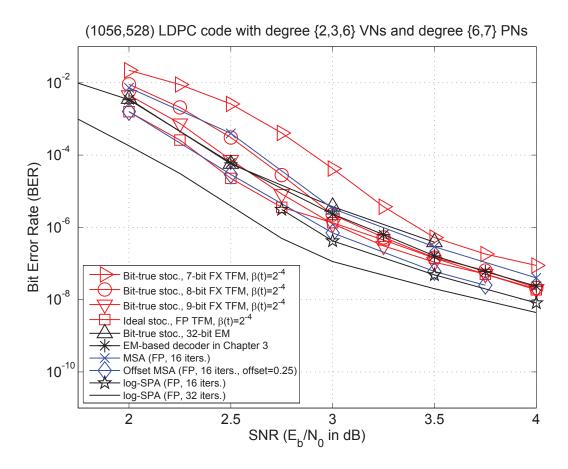

| 4–10 | Decoding performance results for a (1056,528) LDPC code (FP:floating-point, FX:fixed-point)                                                                                                                            | 76 |

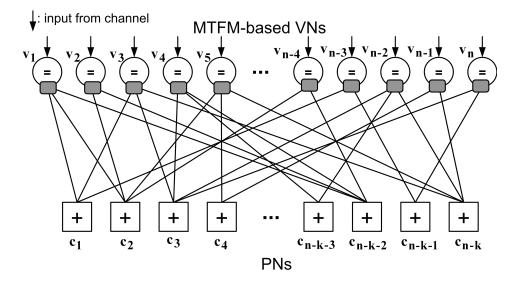

| 5–1  | An MTFM-based stochastic decoder uses one MTFM per VN                                                                                                                                                                  | 80 |

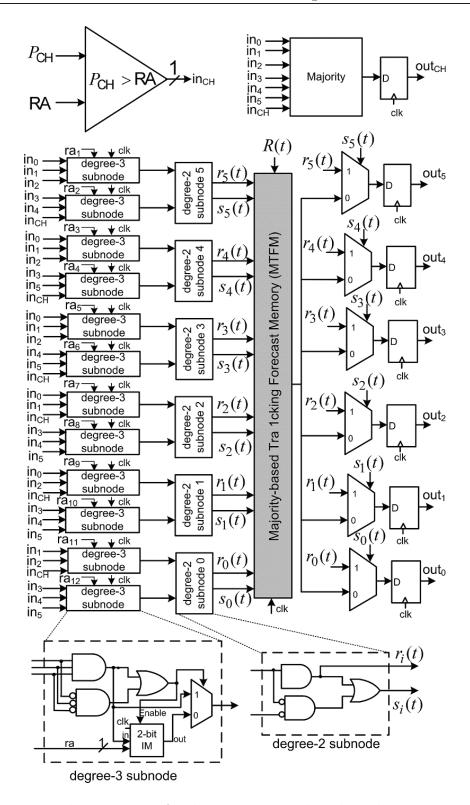

| 5–2  | The structure of a degree-6 MTFM-based stochastic VN. $P_{\text{CH}}$ is the channel probability, $R(t)$ and $RA$ are (pseudo) uniform random numbers, $\text{ra}_i$ is a random bit, and IM refers to internal memory | 82 |

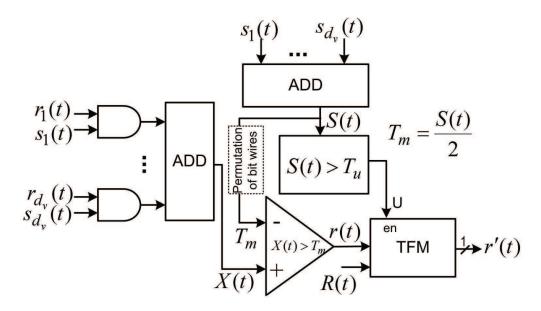

| 5–3  | General architecture of an MTFM. $T_u$ is a fixed threshold for updating the TFM and $T_m$ is the majority threshold                                                                                                   | 84 |

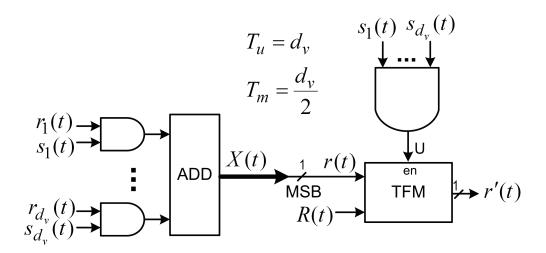

| 5–4  | Architecture of a reduced-complexity MTFM. $r(t)$ is the most significant bit (MSB) of $X(t)$                                                                                                                          | 85 |

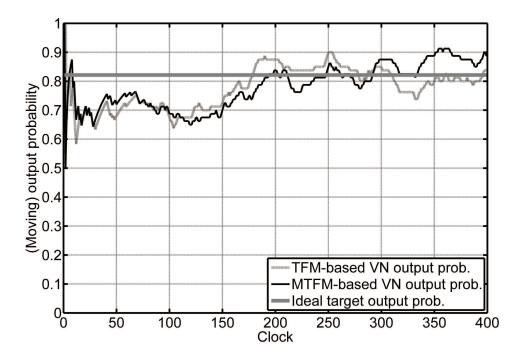

| 5–5  | Extracted output probability of an edge in degree-6 TFM-based and MTFM-based VNs. Both VNs receive the same input stream                                                                                               | 86 |

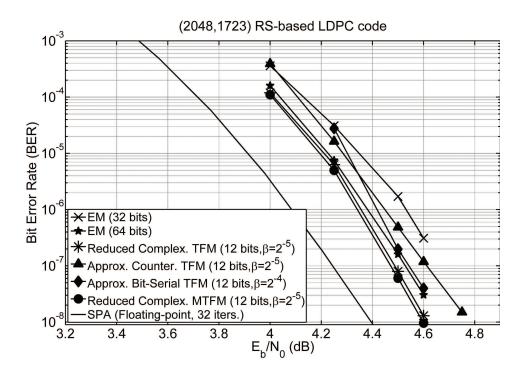

| 5–6  | Comparison of decoding performance of EM-based, TFM-based, and MTFM-based stochastic decoding approaches                                                                                                               | 87 |

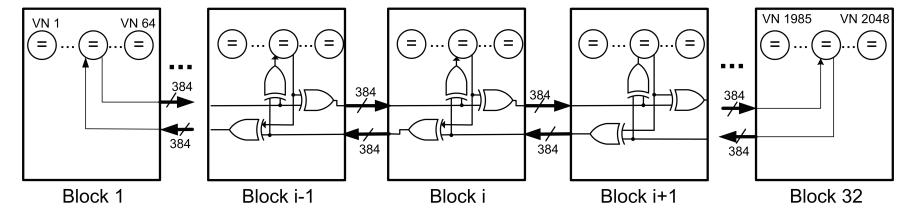

| 5-7  | blocks in which each block contains 64 degree-6 VNs. Each block receives 384 input bits from each one of its neighbor blocks and outputs 384 bits to each of them. To form the parity-check equation, each VN inside a block XORs its output bit with the input receives from the neighboring block and passes it to the next neighboring block. The VN also XORs the inputs received from neighbor blocks to from its input bit. One level of flip-flops is used after every 8 VN blocks to break long wires |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

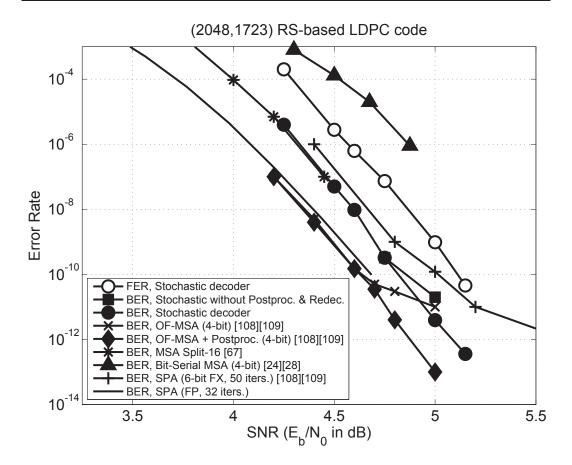

| 5–8  | Decoding performance of the MTFM-based stochastic decoder.  The stochastic decoder uses early termination until a maximum of 400 decoding cycles has been exhausted 95                                                                                                                                                                                                                                                                                                                                        |

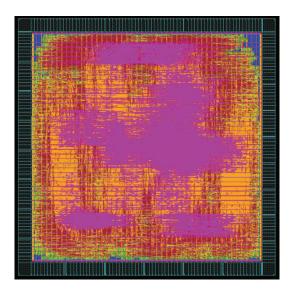

| 5-9  | The stochastic decoder chip layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

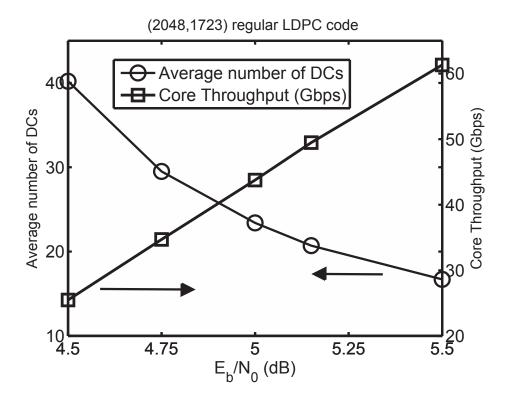

| 5–10 | Average number of decoding cycles used (left y-axis) for decoding at different SNRs and the corresponding core throughput (right y-axis) for the achieved clock frequency of 500 MHz. Each decoding cycle takes one clock cycle                                                                                                                                                                                                                                                                               |

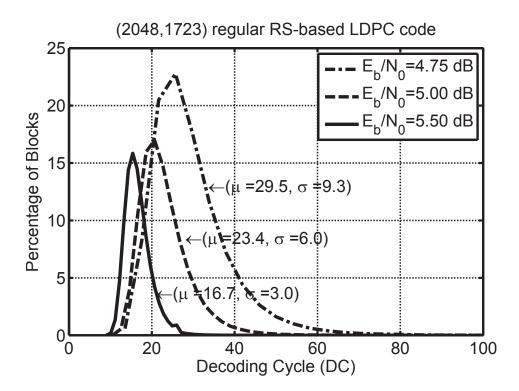

| 5–11 | Histograms of decoding cycles used for decoding codewords at different SNRs. One million codewords used for each histogram. $\mu$ is the average number of decoding cycles and $\sigma$ is the standard deviation. Each decoding cycle takes one clock cycle                                                                                                                                                                                                                                                  |

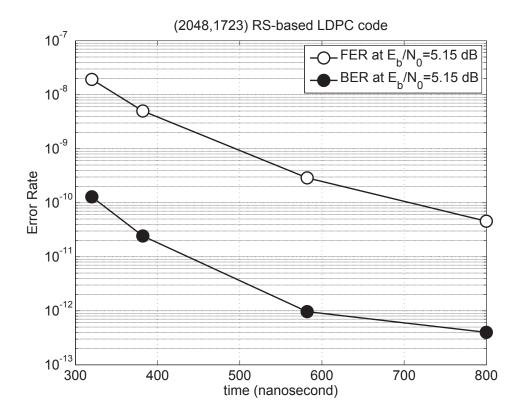

| 5–12 | Decoding performance versus latency (in nanoseconds) at $E_b/N_0=5.15$ dB. A BER of about $10^{-12}$ is achieved with about 580 ns maximum decoding latency (i.e., maximum 290 decoding cycles). The shown 800 ns latency corresponds to the maximum 400 decoding cycles with the achieved 500 MHz clock frequency. Each decoding cycle takes one clock cycle                                                                                                                                                 |

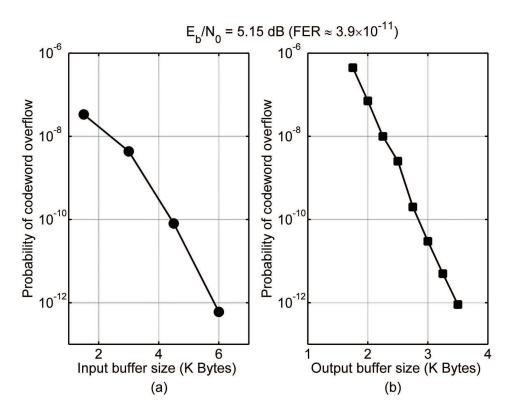

| 5–13 | Probability of codeword overflow for different sizes of (a) input buffer and (b) output buffer at $E_b/N_0=5.15$ dB 101                                                                                                                                                                                                                                                                                                                                                                                       |

| 6–1  | System model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6–2  | Joint message-passing diagram for decoding LDPC codes and partial-response channels. $d$ is the degree of the partial-response channel                                                                                                                                                                                                                                                                                                                                                                        |

| 6–3 | (a) The message-passing diagram for the dicode channel with $h(D) = 1 - D$ . The p-th triangle node is connected to bit nodes numbered p and $p - 1$ . (b) The message-passing diagram for the EPR4 channel with $h(D) = 1 + D - D^2 - D^3$ . The p-th triangle node is connected to bit nodes numbered $p, p - 1, p - 2$ , and $p - 3$ . A length-4 cycle is highlighted in the graph | . 107 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

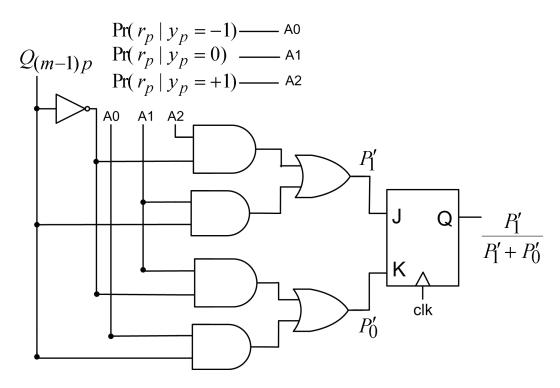

| 6–4 | The hardware architecture of a stochastic triangle node for the dicode channel (only one output and its corresponding inputs are shown)                                                                                                                                                                                                                                                | . 112 |

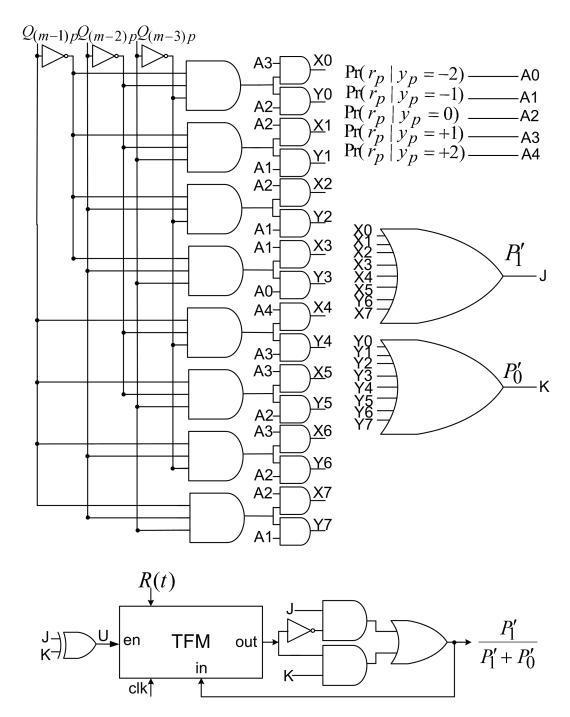

| 6–5 | The hardware architecture of stochastic triangle node for the EPR4 channel (only one output and its corresponding inputs are shown). $R(t)$ is a (pseudo) random number varying in every decoding cycle                                                                                                                                                                                | . 115 |

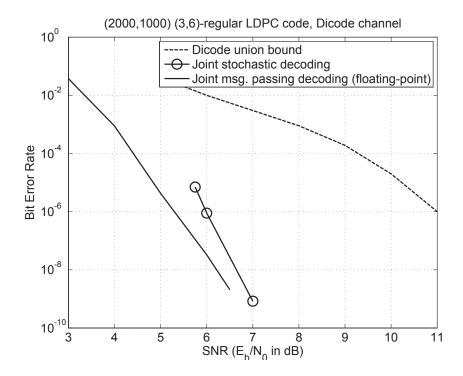

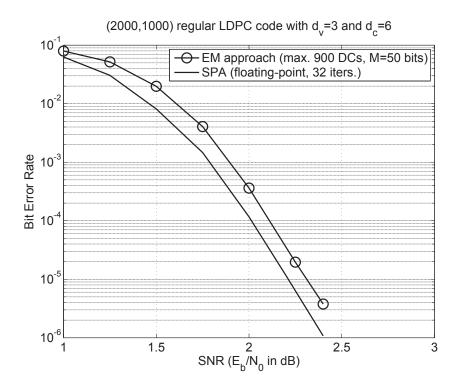

| 6–6 | Decoding performance of the stochastic approach for joint decoding of a (2000,1000) LDPC code and the dicode partial-response channel                                                                                                                                                                                                                                                  | . 117 |

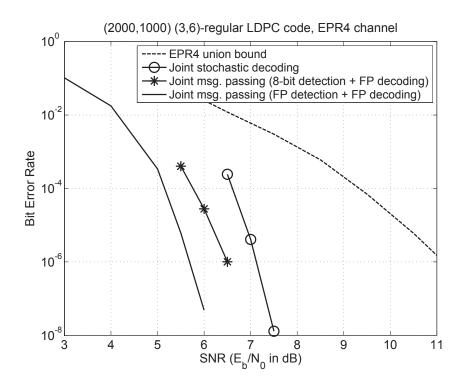

| 6–7 | Decoding performance of the stochastic approach for joint decoding of a (2000,1000) LDPC code and the EPR4 partial-response channel (FP: floating-point)                                                                                                                                                                                                                               | . 118 |

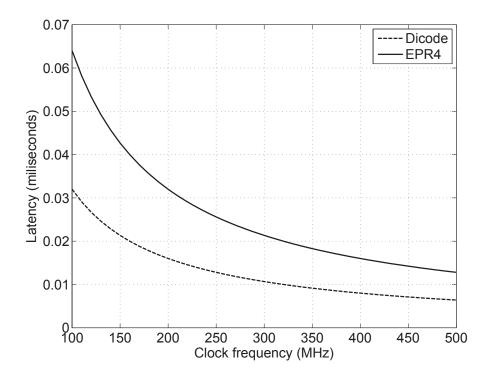

| 6–8 | Estimated latency of joint stochastic decoding for different clock frequencies                                                                                                                                                                                                                                                                                                         | . 119 |

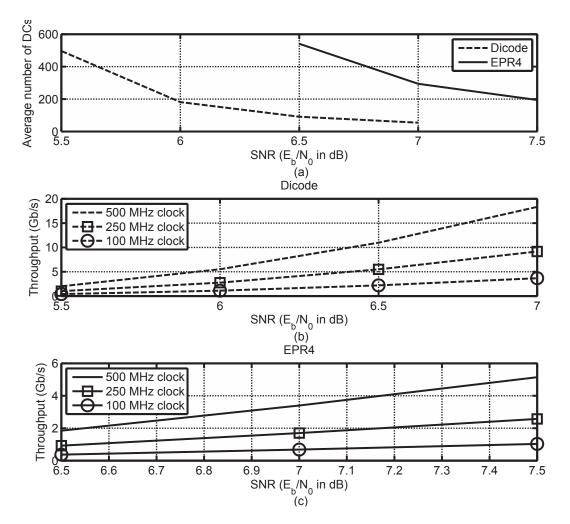

| 6-9 | (a) Average number of decoding cycles used for joint stochastic decoding at different SNRs. (b) Estimated (core) throughput for joint stochastic decoding of the (2000,1000) LDPC code and the dicode channel. (c) Estimated (core) throughput for joint stochastic decoding of the (2000,1000) LDPC code and the EPR4 channel                                                         | . 120 |

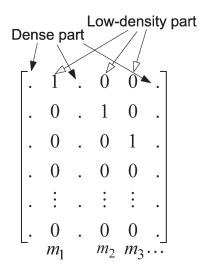

| 7–1 | Form of an adapted parity-check matrix in the ABP [47]                                                                                                                                                                                                                                                                                                                                 | . 125 |

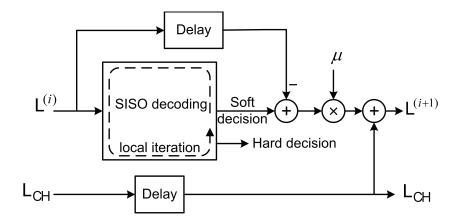

| 7–2 | Block turbo decoding.                                                                                                                                                                                                                                                                                                                                                                  | . 127 |

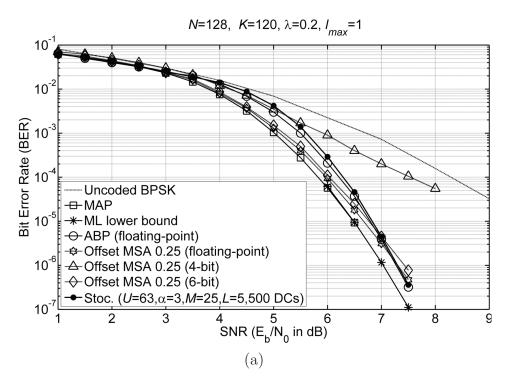

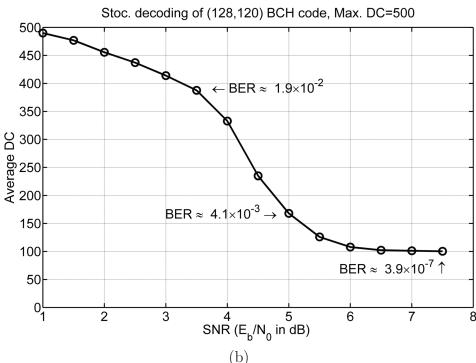

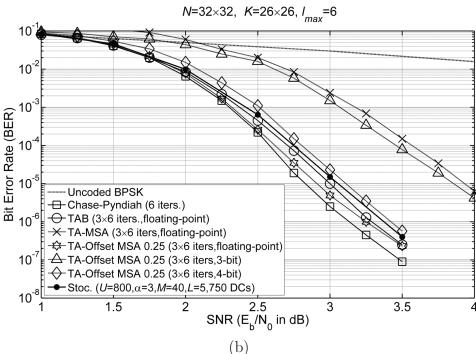

| 7–3 | (a) Simulation results for a (128,120) BCH code. (b) Average number of decoding cycles for stochastic decoding of (128,120) BCH code                                                                                                                                                                                                                                                   | . 131 |

| 7–4 | Simulation results for (a) a (31,25) RS code over $GF(2^5)$ and (b) a (63,55) RS code over $GF(2^6)$                                                                                                                                                                                                                                                                                   | . 132 |

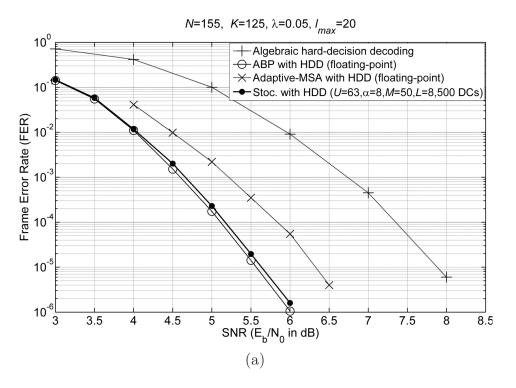

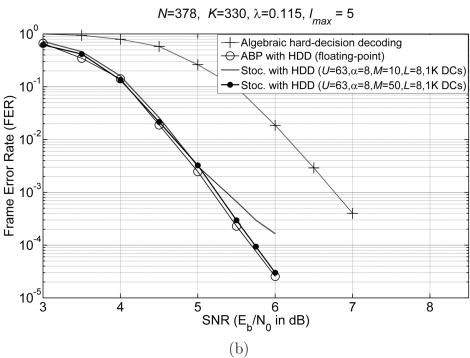

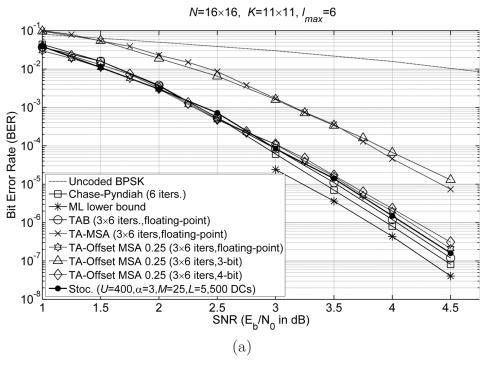

| 7–5 | Simulation results for (a) a (256,121) BCH block turbo code and (b) a (1024,676) BCH block turbo code                                                                                                                                                                                                                                                                                  | . 134 |

| A-1 | Performance of the EM approach for decoding a (2000,1000) LDPC code                                                                                 | . 147 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

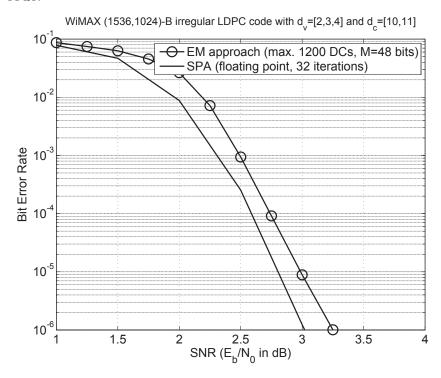

| A-2 | Performance of the EM approach for decoding a (1536,1024) LDPC code                                                                                 | . 147 |

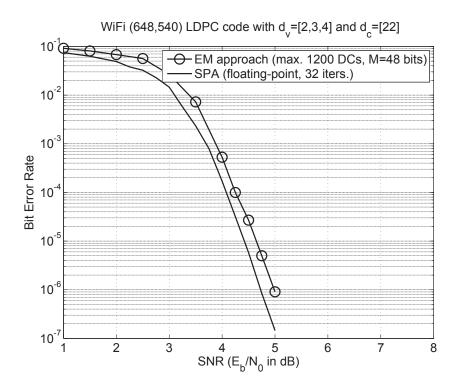

| A-3 | Performance of the EM approach for decoding a (648,540) LDPC code                                                                                   | . 148 |

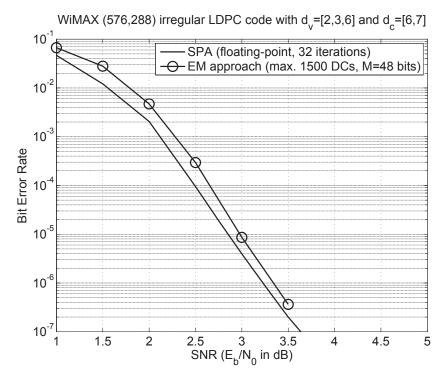

| A-4 | Performance of the EM approach for decoding a (576,288) LDPC code                                                                                   | . 148 |

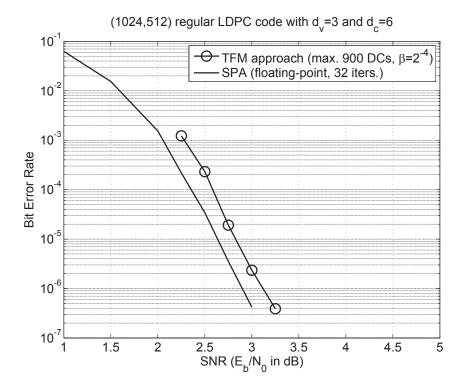

| A-5 | Performance of the TFM approach for decoding a (1024,512) LDPC code                                                                                 | . 149 |

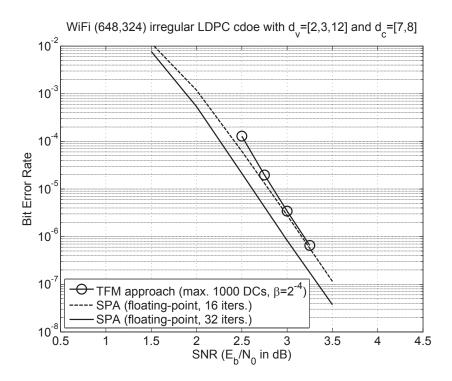

| A-6 | Performance of the TFM approach for decoding a (648,324) LDPC code                                                                                  | . 150 |

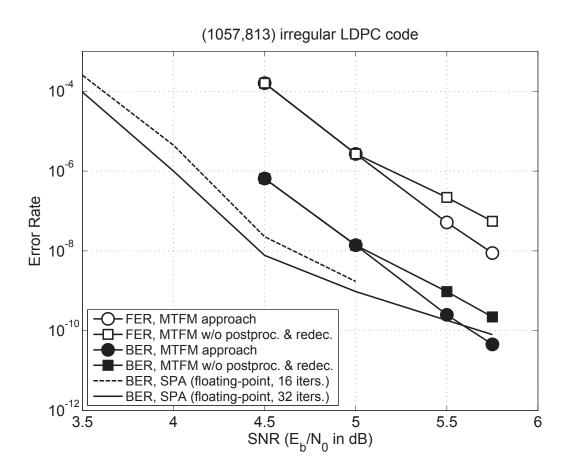

| A-7 | Performance of the MTFM approach for decoding a (1057,813) LDPC code. An early termination criterion until a maximum of 400 decoding cycles is used | . 151 |

## CHAPTER 1

# Introduction

#### 1.1 Motivations

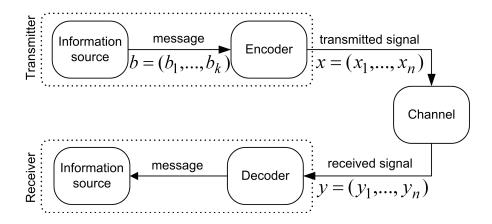

Error-control coding (channel coding) is a powerful technique in digital communications used to ensure reliable communication over an unreliable channel. In this technique, error-control codes are used to efficiently add redundant structure to the transmitted data to allow the receiver to detect and correct errors introduced during passage through a noisy and distorting communication channel (see Figure 1–1). Error-control coding has evolved since the advent of information theory by Shannon in 1948 [81] and it has become essential in a wide variety of modern applications [22]. In particular, error-control coding has received a lot of attention in recent years because of the significant progress in designing powerful error-control codes as well as the progress in Very-Large-Scale Integration (VLSI) technology, which has facilitated the hardware implementation of computationally-complex decoding algorithms.

Among different classes of error-control codes, Low-Density Parity-Check (LDPC) codes [33, 34] are one of the most powerful classes known to date. LDPC codes have been considered as forward error correction in several recent communication applications and standards including digital video broadcasting (DVB-S2) [1], 10 Gb/s Ethernet (IEEE 802.3an or 10GBASE-T) standard [2], broadband wireless access (IEEE 802.16e or WiMAX) standard [3],

Figure 1–1: The schematic diagram of a communication system.

wireless local area network (IEEE 802.11n or WiFi) standard [4], and deepspace communications [9]. LDPC codes were invented by R. G. Gallager in 1962 [34]. Gallager discovered and applied an iterative decoding algorithm to a new class of error-control codes. He named these codes low-density paritycheck codes, because their parity-check matrices had to be sparse in order to have good performance. However, LDPC codes had been ignored for almost three decades mainly because of the requirement for high complexity computation, particularly for LDPC codes with long code length. The advent of turbo codes in 1993 [12] and the observation of their remarkable "capacityapproaching" performance raised many questions and triggered many research efforts toward iterative decoding. Turbo codes made it possible to get within a few tenths of a decibel (dB) away from the Shannon capacity limit at a Bit-Error-Rate (BER) of  $10^{-5}$ . This in fact started a new paradigm in the design of error correcting codes, which led to the rediscovery of LDPC codes in 1995 [57,58], and graph-based codes. Like Turbo codes, LDPC codes were demonstrated to perform very close to the Shannon limit when decoded iteratively on graphs using a message-passing algorithm such as the Sum-Product Algorithm (SPA) [20, 56, 58, 75]. It was also shown that iterative LDPC decoding and turbo decoding of turbo codes are instances of the Pearl's belief propagation algorithm [72], collecting LDPC codes and Turbo codes under the same model [57,58,62]. In addition, the graph-based code-description became a common way of representing error correcting codes [50].

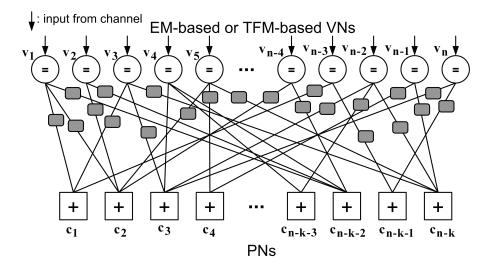

An LDPC code and its iterative decoding can be graphically represented by a factor graph [50]. A factor graph is a bipartite graph which consists of two different groups of processing nodes: Variable Nodes (VNs) and Paritycheck Nodes (PNs). The VN and PN groups in a factor graph are connected to each other by bidirectional edges. The connection between VNs and PNs are defined by the parity-check matrix of the code. Iterative decoding of LDPC codes usually involves message-passing between VNs and PNs over the edges of the factor graph for some number of decoding iterations. These messages represent the VNs' and PNs' beliefs (in the form of probabilities) about the correctness of the received information from the channel. In general, LDPC decoders can be categorized into fully parallel and partially parallel decoders. In a fully parallel decoder the entire factor graph is implemented in hardware, while in a partially parallel decoder a portion of the graph is implemented and, hence, hardware resource sharing and memory blocks are employed to compute, save and pass probability messages between different portions of the factor graph.

Despite the excellent error-correcting performance of LDPC codes, the hardware implementation of LDPC decoders is complex and challenging [13, 24–26, 28, 90, 107], hence, an LDPC decoder is often implemented optionally, as an additional premium, in communication systems (e.g., in [3, 4]). Powerful LDPC codes usually have long code lengths. Also, their parity-check matrix usually imposes random-like/irregular connections between VNs and PNs. In this respect, a fully parallel hardware implementation of a capacity-approaching LDPC decoder usually requires the implementation of thousands

of processing nodes in a silicon chip. In addition, thousands of physical wires are needed in the silicon chip to accommodate message-passing between VNs and PNs. For instance, a decoder for the LDPC code that is considered for the 10Gb/s Ethernet standard [2], has 2048 VNs and 384 PNs. Each VN communicates with six PNs in each decoding iteration. Therefore, by using W-bit quantization to represent probability messages passed between nodes in a fully parallel implementation, a total of  $2048 \times 6 \times 2 \times W = 24576 \times W$ physical wires are needed between PNs and VNs (in both the input and output directions). Using 4-bit and 6-bit quantization, the number of physical wires between VNs and PNs in the decoder chip is 98304 and 147456, respectively. The high number of processing nodes and the abundant number of physical wires make the chip consume a large silicon area. In addition, the random-like connections between VNs and PNs result in long and random physical wires and interconnections across the chip, which causes routing congestion. These long wires also limit the clock frequency and the throughput of the decoder and increase its power consumption [13, 25, 26, 28]. In partially parallel decoders, the large and irregular communication network between VNs and PNs results in large memory blocks and address generation units with high power consumption. Another challenge in the design of LDPC decoders is that simplifying the decoder hardware by using a low number of quantization levels can degrade the error-correcting behavior of an LDPC decoder, particularly, in low BER regimes where LDPC codes are usually supposed to operate [111]. Conversely, most modern communication applications require high throughput decoding while demanding low silicon area and power consumption, as well as good decoding performance in low BER regimes. These challenges have made efficient LDPC decoding a focal point of research at both the theoretical/algorithm level and the hardware implementation level (see Section 2.2).

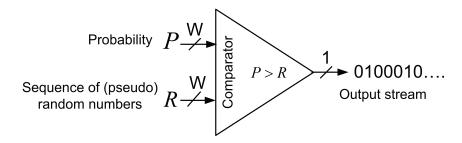

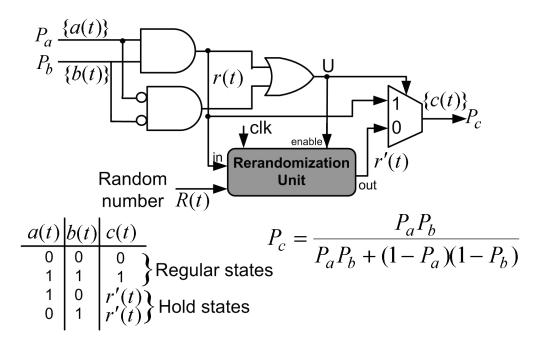

To address the above-mentioned problems, this work proposes the stochastic decoding of practical capacity-approaching LDPC codes on factor graphs. Stochastic decoding is a new approach for iterative decoding on graphs. This approach is inspired by the method of stochastic computation developed in the 1960's [32]. In stochastic decoding, instead of propagating probabilistic beliefs by exchanging distinct probability messages, as in the conventional message-passing algorithms, beliefs are conveyed in streams of stochastic bits in a sense that the probability of observing a "1" in a stream is equal to the original (encoded) probability. Therefore, VNs and PNs exchange beliefs in a bit-serial manner along the edges of the graph. Stochastic decoding reduces the hardware-complexity of processing nodes in an LDPC decoder and, more importantly, it significantly reduces the number of physical wires between processing nodes. The first stochastic decoding method was proposed in [36,74]. However, stochastic decoding methods prior to this work (i.e., [36,37,74,95,97]) resulted in significant decoding performance loss compared to the conventional iterative LDPC decoding methods and thus were not practical solutions for decoding LDPC codes (see Section 2.4).

#### 1.2 Objectives

The objectives in this work are to develop stochastic decoding approaches that (a) can decode practical capacity-approaching LDPC codes on factor graphs, (b) have area-efficient hardware implementations, (c) achieve high throughput, and (d) provide good decoding performance, especially in low BER regimes.

#### 1.3 Contributions

This dissertation proposes stochastic decoding as a new competitive approach for decoding state-of-the-art LDPC codes on factor graphs.

We propose edge-based rerandomization using Edge Memories (EMs) [82, 85,86 as the first successful stochastic approach in the literature for decoding practical capacity-approaching LDPC codes on factor graphs. We also propose a fully parallel decoder hardware architecture for the EM-based stochastic LDPC decoding and discuss its novel architectural features. We apply this architecture to decode an irregular state-of-the-art (1056,528) LDPC code (chosen from the WiMAX standard [3]) on a field-programmable gate-array (FPGA) device. This decoder is the first stochastic LDPC decoder architecture in the literature that decodes a practical LDPC code. The implemented decoder achieves a clock frequency of 222 MHz and a maximum throughput of about 1.66 Gb/s on FPGA. The EM-based stochastic decoder provides good decoding performance behavior at low BERs. We demonstrate the performance of this decoder down to a BER of about  $10^{-8}$  and compare it with other decoding approaches. We show that the proposed decoder provides a performance within 0.5 dB and 0.25 dB of the floating-point SPA with 32 and 16 iterations, respectively. We compare this decoder with other high throughput FPGA-based fully parallel LDPC decoders in detail and demonstrate that this decoder is one of the fastest and most resource-efficient FPGA-based fully parallel LDPC decoders.

We consider the ASIC implementations of stochastic LDPC decoders. We discuss ASIC implementation challenges of EM-based stochastic decoding and propose edge-based rerandomization using Tracking Forecast Memories (TFMs) [87, 88] to significantly reduce the silicon area consumption of

ASIC stochastic decoders. By comparing EM-based decoders with the TFM-based LDPC decoders, we show that TFM-based decoders provide similar or better decoding performance compared to EM-based decoders while having about 40% to 65% less silicon area consumption. The ASIC TFM-based decoder proposed in this dissertation is the first ASIC stochastic LDPC decoder reported in the literature.

We propose node-based rerandomization using Majority-based Tracking Forecast Memories (MTFMs) [89] for area-efficient high throughput ASIC implementation of stochastic LDPC decoders. We apply the MTFM approach for ASIC implementation of a fully parallel stochastic decoder that decodes the (2048,1723) LDPC code from the IEEE 802.3an (10GBASE-T) standard [2]. This stochastic decoder occupies a silicon core area of 6.38 mm² in CMOS 90 nm technology, achieves a maximum clock frequency of 500 MHz, and provides a maximum core throughput of 61.3 Gb/s. The decoder also has good decoding performance and error-floor behavior. We investigate and demonstrate its decoding performance down to a low BER of about  $4 \times 10^{-13}$ . We compare this decoder with several recent ASIC LDPC decoders in detail. To the best of our knowledge, the proposed MTFM-based stochastic LDPC decoder and it is one of the fastest fully parallel LDPC decoders reported in the literature.

In addition to stochastic LDPC decoding, we consider other applications of the stochastic approach. We propose the novel application of stochastic decoding for joint message-passing decoding of LDPC codes and partial-response channels that are considered in practical magnetic recording applications. We propose low hardware-complexity stochastic processing nodes to perform computationally-intensive operations required in partial-response channel detectors. We present decoding performance results for the dicode

partial-response channel and the Extended Class-4 Partial-Response (EPR4) channel, and discuss the throughput and latency of the proposed method.

Finally, we investigate stochastic decoding of linear block codes with high-density parity-check matrices on factor graphs [83]. Stochastic decoding was previously applied to Reed-Solomon (RS) codes in [112]. In this dissertation, we further investigate stochastic RS decoding and extend the application of stochastic decoding to Bose-Chaudhuri-Hocquenghem (BCH) codes and BCH-based turbo block codes. We also propose efficient hardware implementations of high-degree nodes used in the decoding of linear block codes with high-density parity-check matrices on factor graphs. Results demonstrate decoding performance close to floating-point iterative soft-input soft-output (SISO) decoding while offering nodes with considerably lower complexity compared to fixed-point SISO decoding. These results are the first results reported in the literature for stochastic decoding of Bose-Chaudhuri-Hocquenghem (BCH) codes and BCH-based turbo block codes.

### 1.3.1 List of Publications and Patent Applications

This doctoral research has resulted in the following publications and patent applications:

- Published or Accepted Journal Articles:

- i S. Sharifi Tehrani, C. Winstead, W. J. Gross, S. Mannor, S. Howard, and V. C. Gaudet, "Relaxation Dynamics in Stochastic Iterative Decoders," IEEE Transactions on Signal Processing, vol. 58, no. 11, November 2010, pp. 5955-5961.

- ii S. Sharifi Tehrani, A. Naderi, G.-A. Kamendje, S. Hemati, S. Mannor, and W. J. Gross, "Majority-Based Tracking Forecast Memories for Stochastic LDPC Decoding," IEEE Transactions on Signal Processing, vol. 58, no. 9, September 2010, pp. 4883-4896.

- iii S. Sharifi Tehrani, A. Naderi, G.-A. Kamendje, S. Mannor, and W. J. Gross, "Tracking Forecast Memories for Stochastic Decoding," Invited paper by Journal of Signal Processing Systems, Special Issue on the DISPS Track of IEEE ICASSP 2009, Springer Publishing, To Appear (online publication: January 2010), DOI: 10.1007/s11265-009-0441-5.

- iv S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "Fully Parallel Stochastic LDPC Decoders," IEEE Transactions on Signal Processing, vol. 56, no. 11, November 2008, pp. 5692-5703.

- v S. Sharifi Tehrani, C. Jego, B. Zhu, and W. J. Gross, "Stochastic Decoding of Linear Block Codes with High-Density Parity-Check Matrices," IEEE Transactions on Signal Processing, vol. 56, no. 11, November 2008, pp. 5733-5739.

- vi S. Sharifi Tehrani, W. J. Gross, and S. Mannor, "Stochastic Decoding of LDPC Codes," IEEE Communications Letters, vol. 10, no. 10, October 2006, pp. 716-718.

#### • Peer-Reviewed Conference Papers:

- i S. Sharifi Tehrani, A. Naderi, G.-A. Kamendje, S. Mannor, and W. J. Gross, "Tracking Forecast Memories in Stochastic Decoders," Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASSP), April 2009, Taipei, Taiwan, pp. 561-564.

- ii S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "An Area-efficient FPGA based Architecture for Fully-Parallel Stochastic LDPC Decoding," Proceedings of the IEEE International Workshop on Signal Processing Systems (SiPS), October 17-19, 2007, Shanghai, China, pp. 255-260.

iii S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "Survey of Stochastic Computation on Factor Graphs," Proceedings of the 37th IEEE International Symposium on Multiple-Valued Logic (ISMVL), May 14-16, 2007, Oslo, Norway, pp. 54-59.

### • Workshop Papers:

- i S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "A Novel Architecture for Fully-Parallel Stochastic LDPC Decoders," presented at the 7th annual Analog Decoding Workshop (ADW 2008), July 12th, 2008, Logan, USA.

- ii S. Sharifi Tehrani, W. J. Gross, and S. Mannor, "Stochastic Decoding of LDPC Codes," presented at the 6th annual Analog Decoding Workshop (ADW 2007), May 24-25, 2007, Montreal, Canada.

### • Submitted Patent Applications:

The following patent applications have been filed by the office of technology transfer at McGill University:

- i S. Sharifi Tehrani, P. H. Siegel, S. Mannor, and W. J. Gross, "Method for Joint Decoding of LDPC Codes and Partial-Response Channels and Apparatuses Thereof," United States Patent Application 61/433,997, Filed in January 2011.

- ii S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "Method and Systems for Improving Iterative Signal Processing," United States Patent Application 12/566,829, Filed in September 2009.

- iii S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "Methods and Apparatuses of Mathematical Processing," United States Patent Application 12/250,830, Filed in October 2008.

- iv S. Sharifi Tehrani, S. Mannor, and W. J. Gross, "Method for Implementing Stochastic Equality Nodes," United States Patent Application 12/153,749. Filed in May 2008.

#### 1.4 Dissertation Outline

Chapter 2 provides background materials. It reviews LDPC codes, the SPA, the strategies and challenges of hardware implementation of LDPC decoders, stochastic computation and its benefits, and early stochastic decoding methods. Chapter 2 is in part based on the material in our papers [82,84].

Chapter 3 proposes the EM approach as the first successful stochastic method for decoding state-of-the-art LDPC codes. It also proposes the first hardware architecture for stochastic decoding of practical Low-Density Parity-Check (LDPC) codes on factor graphs. Chapter 3 is in part based on the material in our papers [82, 85, 86].

Chapter 4 focuses on ASIC implementations of stochastic LDPC decoders. It discusses the silicon area complexity of stochastic decoders and proposes the TFM approach to significantly reduce the hardware-complexity of stochastic decoders for ASIC implementation. It proposes the first ASIC architecture for stochastic decoding of LDPC codes on factor graphs. Chapter 4 is in part based on the material in our papers [87–89]

Chapter 5 continues the theme of Chapter 4 on ASIC implementation of stochastic decoders. It proposes MTFMs for area-efficient high throughput ASIC implementation of stochastic LDPC decoders. The proposed method is applied for the ASIC implementation of a fully parallel stochastic decoder that decodes the (2048,1723) LDPC code from the IEEE 802.3an (10GBASE-T) standard. To the best of our knowledge, this implemented decoder is the most area-efficient and one of the fastest fully parallel soft-decision LDPC decoders reported in the literature. The decoding performance of this decoder has been investigated down to a BER of about  $4 \times 10^{-13}$ . Chapter 5 is in part based on the material in our paper [89].

Chapter 6 proposes the novel application of stochastic decoding for joint decoding of LDPC codes and partial-response channels that are considered in practical magnetic recording applications. This chapter presents hardware architectures for stochastic processing nodes to perform the complex operations required in the partial-response channel detectors. Performance, latency, and throughput of the proposed joint stochastic decoding method are discussed.

Chapter 7 investigates the application of the stochastic decoding approach to decode linear block codes with high-density parity-check matrices on factor graphs. It demonstrates results for decoding the important and popular classes of RS codes, BCH codes, and BCH block turbo codes. Chapter 7 is in part based on the material in our paper [83].

Finally, Chapter 8 concludes the dissertation and provides potential venues for future work.

# CHAPTER 2

# Background

### 2.1 LDPC Codes and Iterative Decoding

A binary (n, k) LDPC code is defined as the null space of a sparse  $(n - k) \times n$  binary parity-check matrix  $\mathbf{H}$ . This LDPC code consists of codewords  $\mathbf{x} = (x_1, x_2, ..., x_n)$  such that

$$xH^T = 0, (2.1)$$

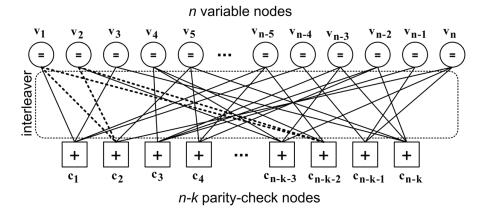

where  $\boldsymbol{x}$  contains k information bits and n-k parity bits, and  $\boldsymbol{x}\boldsymbol{H}^T$  is computed in the Galois field GF(2) [33]. LDPC codes and their iterative decoding process can be graphically represented using bipartite factor graphs [50]. Factor graphs consist of two distinctive groups of processing nodes, VNs and PNs, and edges that connect VNs to PNs. A factor graph for an (n,k) full-rank LDPC code has n VNs and n-k PNs. The i-th VN,  $v_i$ , is connected to j-th PN,  $c_j$ , if and only if  $h_{ji}$ , the entry in  $\boldsymbol{H}$  at row j and column i, is 1. The connecting/communication network between VNs and PNs is called interleaver (see Figure 2–1). The number of edges connected to a node (in the interleaver) is referred to as the degree of the node and represented as  $d_v$  for the VNs and  $d_c$  for the PNs. In regular codes,  $d_v$  and  $d_c$  are fixed for all VNs and PNs, respectively. In irregular LDPC codes,  $d_v$  and  $d_c$  vary for different nodes. Figure 2–1 also highlights a length-4 cycle in the depicted factor graph. A cycle is a closed path in the graph and its length is defined as the

Figure 2–1: A typical factor graph and the interleaver for a full-rank (n, k) LDPC code. A length-4 cycle is dashed. In a conventional implementation with W-bit representation of messages, each edge requires 2W wires (for two directions).

corresponding number of path edges. The length of the smallest cycle is the girth of the factor graph. While the factor graph of a practical LDPC code can have thousands of cycles, its girth should be more than four to provide a good decoding performance.

LDPC codes are encoded using a  $k \times n$  generator matrix, G, where

$$\mathbf{G}\mathbf{H}^T = 0. \tag{2.2}$$

During the encoding process, n - k parity bits are added to  $\mathbf{b} = (b_1, ..., b_k)$ , the information vector, to form the codeword  $\mathbf{x} = (x_1, ..., x_n)$ , where

$$x = bG. (2.3)$$

In a typical LDPC-coded communication system, after encoding the information vector at the transmitter, the codeword  $\boldsymbol{x}$  is transmitted through a communication channel. At the receiver, the received vector,  $\boldsymbol{y} = (y_1, ..., y_n)$ , is passed to the LDPC decoder (see Figure 1–1).

### 2.1.1 Sum-Product Algorithm

LDPC codes are usually iteratively decoded by means of belief propagation [72] using message-passing algorithms such as the SPA (see [50]) or its less-complex approximation, the Min-Sum Algorithm (MSA) [94]. The SPA is an iterative algorithm for decoding LDPC codes. The SPA uses soft information (probabilities) received from the channel and iteratively processes them using VNs and PNs. The SPA makes decisions by comparing final probabilities to a threshold value (hard-decision) at the end of the decoding process.

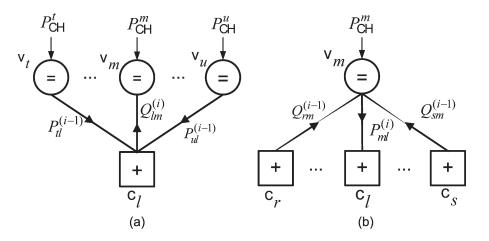

Suppose that  $x_m$  and  $y_m$ , respectively, denote the m-th sample  $(1 \le m \le n)$  in the transmitted vector,  $\mathbf{x}$ , and in the received vector,  $\mathbf{y}$ , in a Binary Phase-Shift Keying (BPSK) transmission over an Additive White Gaussian Noise (AWGN) channel with zero mean and a single-sided noise power spectral density of  $N_0$ . Let  $P_{ml}^{(i)}$  be the probability message from the VN  $\mathbf{v}_m$  to the PN  $\mathbf{c}_l$  and  $Q_{lm}^{(i)}$  be the probability message from  $\mathbf{c}_l$  to  $\mathbf{v}_m$  in the i-th iteration (see Figures 2–2 (a) and (b)). Also, let N(m) be the set of PNs connected to  $\mathbf{v}_m$  and M(l) be the set of VNs connected to the  $\mathbf{c}_l$ . The SPA steps in the probability domain can be described as follows (see [50,79] for details):

I Set the iteration counter to zero (i = 0).

II For all VNs, i.e., for  $1 \le m \le n$ ,  $l \in N(m)$ , initialize  $P_{ml}^{(0)}$  to  $P_{CH}^m$ , the a posteriori probability (channel probability), computed as:

$$P_{\text{CH}}^m = \Pr(x_m = 1|y_m) = \frac{\exp(L_{\text{CH}}^m)}{\exp(L_{\text{CH}}^m) + 1},$$

(2.4)

where  $L_{\text{CH}}^m$  is the log-likelihood ratio (LLR) of  $y_m$  and it is computed as:

$$L_{\text{CH}}^{m} = \log \left( \frac{\Pr(x_{m} = 1 | y_{m})}{\Pr(x_{m} = 0 | y_{m})} \right) = \frac{4y_{m}}{N_{0}}.$$

(2.5)

Figure 2–2: Message-passing in the SPA.

III Update all the PNs, i.e., for  $1 \le l \le n - k$ ,  $m \in M(l)$  compute:

$$Q_{lm}^{(i)} = 0.5 - \left(0.5 \prod_{m' \in M(l) \backslash m} (1 - 2P_{m'l}^{(i-1)})\right), \tag{2.6}$$

where  $M(l)\backslash m$  denotes the set of VNs connected to  $c_l$  excluding  $v_m$ .

IV Update all the VNs, i.e., for  $1 \le m \le n, l \in N(m)$  compute:

$$P_{ml}^{(i)} = \frac{P_{\text{CH}}^{m} \prod_{l' \in N(m) \setminus l} Q_{l'm}^{(i)}}{\left(P_{\text{CH}}^{m} \prod_{l' \in N(m) \setminus l} Q_{l'm}^{(i)}\right) + \left((1 - P_{\text{CH}}^{m}) \prod_{l' \in N(m) \setminus l} (1 - Q_{l'm}^{(i)})\right)}. \quad (2.7)$$

V For all VNs, i.e.,  $1 \le m \le n, l \in N(m)$ , compute  $P_{\text{ext}}^m$  as:

$$P_{\text{ext}}^{m} = \frac{P_{\text{CH}}^{m} \prod_{l' \in N(m)} Q_{l'm}^{(i)}}{\left(P_{\text{CH}}^{m} \prod_{l' \in N(m)} Q_{l'm}^{(i)}\right) + \left((1 - P_{\text{CH}}^{m}) \prod_{l' \in N(m)} (1 - Q_{l'm}^{(i)})\right)}.$$

(2.8)

Make the hard-decision to obtain the estimated vector,  $\hat{\boldsymbol{x}} = (\hat{x}_1, ..., \hat{x}_n)$ , where  $\hat{x}_m = 1$  if  $P_{\text{ext}}^m > 0.5$ , and  $\hat{x}_m = 0$ , otherwise.

VI Terminate decoding if  $\hat{x}H^T = 0$  or if i has reached the maximum number of iterations. Otherwise, set i = i + 1 and return to step III.

Because of the high hardware-complexity of VNs' and PNs' operations in the probability domain, the SPA is usually implemented in the log-domain where channel probabilities are considered as LLRs. Using the log-domain conversion, VNs calculate the summation of LLR messages and PNs employ  $tanh(\cdot)$  processing to compute their outgoing messages [79]. In the MSA, the  $tanh(\cdot)$  processing in PNs is approximated to reduce the complexity, usually at the expense of some decoding performance loss, compared to the SPA [8, 38]. To compensate for some of the loss, different improved methods are suggested in the literature (e.g., see [17, 18, 38, 42, 44]).

### 2.2 Strategies and Challenges of Hardware Implementations of LDPC Decoders

In general, fully parallel and partially parallel architectures are two main strategies for the implementation of LDPC decoders. In the fully parallel strategy, the entire factor graph is implemented in hardware and all VNs and PNs in the graph are updated concurrently. Fully parallel decoders are usually implemented to achieve high-throughput decoding of a certain LDPC code, usually at the cost of high area consumption. This approach is particularly considered for applications with high-speed requirements such as the IEEE 802.3an (10GBASE-T) standard [2]. The partially parallel approach instantiates a portion of the factor graph. Partially parallel decoders employ memory and hardware resource sharing to manage message-passing between different portions of the factor graph. The main benefits of this approach are to minimize the area and/or to offer the flexibility to support different code lengths and code rates in applications such as IEEE 802.16e (WiMAX) [3] and IEEE 802.11n (WiFi) [4]. However, the partially parallel approach usually has a lower throughput compared to the fully parallel approach. The partially parallel approach is also used for the implementation of LDPC decoders with very long code lengths where the fully parallel approach is not feasible today, such as the LDPC code for the DVB-S2 standard with a code length of 64800 bits [90].

A major challenge in the implementation of LDPC decoders is the complexity of the interconnections between VNs and PNs. The complexity of the interleaver is due to the random-like locations of ones in the code's parity-check matrix. This problem is acute for practical fully parallel decoders (where the code block length is usually long) and results in routing congestion and interconnection problems [13, 24, 25, 28]. The routing congestion causes high area consumption and low logic utilization in the decoder. For instance, with 4-bit precision of probability messages, the 52.5 mm<sup>2</sup> die size of the (1024,512) decoder in [13] has a logic utilization of 50% in its core; the rest of the core area is occupied by wires. In addition to high area consumption, the presence of long physical wires in the interleaver increases the power consumption and limits the maximum achievable clock frequency and thus the throughput of a fully parallel LDPC decoder (see [13, 25, 26, 28]).

To alleviate these problems, different approaches are investigated in the literature at both the code design and the hardware implementation levels. One approach is to design "implementation-aware" codes. In this approach, instead of randomly choosing the locations of ones in the parity-check matrix (at the code design stage), the parity-check matrix of an LDPC code is designed with constraints allowing for a suitable structure for a decoder implementation and providing acceptable decoding performance [14, 17, 60, 61, 102, 106].

Another approach used to alleviate the routing congestion problem is to use bit-serial or digit-serial architectures to implement LDPC decoders. Examples of this approach are the FPGA implementation of a bit-serial (480,355) LDPC decoder in [27] and the ASIC implementation of a (660,480) LDPC decoder in [28] based on the bit-serial approximate MSA, and also the MSA-based

bit-serial (256,128) LDPC decoder in [15]. Additionally, a message broadcasting technique was suggested in [25] to alleviate the routing congestion by reducing node-to-node communication complexity in LDPC decoders.