# Genetic Algorithms and Cache Replacement Policy

Erik R. Altman

McGill University, Montreal

October 1991

A Thesis submitted to the Faculty of Graduate Studies and Resaearch in partial fulfillment of the requirements for the degree of Master of Engineering.

# Acknowledgements

Thanks start with Jonathan C. Rand, who introduced me to genetic algorithms and kindly lent, then gave me Goldberg's book on the subject. Anne Brindle's unsolicited donation of her Thesis further sparked my interest in genetic algorithms.

Professor Guang R. Gao's inspired teaching has stimulated my interest in many areas of computer architecture, particularly caches. Professor Vinod K. Agarwal has offered numerous insightf' suggestions along the way, and has been extremely patient in waiting for the final result. Professor P.C.P. Bhatt's review of an early, and none too polished, draft has improved this one considerably. As well, the many conversations with my fellow students helped crystalize several ideas for me.

This work also depended on the considerable computing facilities made available to me in the Computer Systems and Circuits Laboratory. Jacek Slaboszewicz insured that system downtime was minimized, and was always willing to increase my disk quota when needed.

Thanks also to Russell A. Olsen and Yoshiko Fueki, who provided me with a delicious dinner and merriment more times than I can count. Visits and conversation with my family were always fun and helped me keep things in perspective.

Finally and especially thanks to my wonderful wife, Sheila Sundaram, who never complained about my odd hours, who gave me encouragement when I needed it the most, who proofread this thesis on a moment's notice, who translated the abstract, and who helped me with the proofs in the Appendix.

# **Contents**

| A | ckno                 | wledgements                                          | i  |  |  |  |  |  |

|---|----------------------|------------------------------------------------------|----|--|--|--|--|--|

| 1 | Introduction         |                                                      |    |  |  |  |  |  |

| 2 | Cache Basics         |                                                      |    |  |  |  |  |  |

| 3 | S Genetic Algorithms |                                                      |    |  |  |  |  |  |

| 4 | Ger                  | etic Algorithms Applied to Cache Replacement         | 17 |  |  |  |  |  |

|   | 4.1                  | Basics                                               | 17 |  |  |  |  |  |

|   | 4.2                  | Example                                              | 19 |  |  |  |  |  |

|   | 4.3                  | Combination Approaches                               | 21 |  |  |  |  |  |

|   | 4.4                  | Hardware Implementation                              | 23 |  |  |  |  |  |

| 5 | Sim                  | ulations                                             | 29 |  |  |  |  |  |

|   | 5.1                  | Methodology and Details                              | 29 |  |  |  |  |  |

|   | 5.2                  | Line Hit Rate                                        | 35 |  |  |  |  |  |

|   |                      | 5.2.1 Parameters                                     | 35 |  |  |  |  |  |

|   |                      | 5.2.2 Results for Individual Benchmarks              | 42 |  |  |  |  |  |

|   |                      | 5.2.3 Results for a Multitasking Suite of Benchmarks | 58 |  |  |  |  |  |

|    |             | 5.2.4 Random Performance                             | . <b>.</b> |   |   |   | 66  |

|----|-------------|------------------------------------------------------|------------|---|---|---|-----|

|    | 5.3         | OPT Match Rate                                       | , .        | • |   |   | 76  |

|    | 5.4         | History                                              |            | • |   |   | 88  |

|    |             | 5.4.1 Canonical Form                                 |            |   | • |   | 89  |

|    |             | 5.4.2 Genetic Algorithms versus Least Recent History |            |   |   | • | 93  |

|    |             | 5.4.3 Two History Variants                           |            |   | • |   | 97  |

|    | 5.5         | Shadow Cache                                         |            |   |   |   | 99  |

|    | 5.6         | Optimization by Set                                  |            |   | • |   | 100 |

| 6  | Con         | nclusion                                             |            |   |   |   | 103 |

| A  | Pro         | oofs                                                 |            |   |   |   | 106 |

|    | <b>A</b> .1 | Derivation of Number of Orbits                       |            |   |   |   | 106 |

|    | <b>A.2</b>  | Proof of Compression Ratio                           |            |   |   |   | 108 |

|    | <b>A.3</b>  | Proof of Increase in Canonical Forms                 |            |   |   |   | 108 |

| Bi | bliog       | graphy                                               |            |   |   |   | 110 |

# List of Tables

| 5.1  | Number of Total Addresses and Number of Unique Addresses in Each Benchmark                                                                                        | 31 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | Overall Hit Rates for 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines                                                                | 32 |

| 5.3  | Line Hit Rates for 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines.                                                                  | 32 |

| 5.4  | LRU-OPT Gains for 512 byte I-cache, 4-way associativity, 16 byte lines                                                                                            | 54 |

| 5.5  | LRU-OPT Gains for 512 byte D-cache, 4-way associativity, 16 byte lines                                                                                            | 54 |

| 5 6  | LRU-OPT Gains for 512 byte I-cache, 4-way associativity, 32 byte lines                                                                                            | 55 |

| 5.7  | LRU-OPT Gains for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                                            | 55 |

| 5.8  | Individual-Suite Ratios for LRU-History                                                                                                                           | 64 |

| 5.9  | Mean Generation at which Best String Occurred                                                                                                                     | 70 |

| 5.10 | Mean Percentage Differences in Line Hit Rates between Best Strings Generated by Genetic Algorithm Approach and by Random Approach                                 | 73 |

| 5.11 | Mean Percentage Differences in Line Hit Rates between Best Strings Generated by Population of 100 for 9 Generations and by a Population of 800 for 2 Generations. | 76 |

| 5.12 | OPT Match Rates: Percentage of Misses in which Different Algorithms Replaced the Line OPT Would Have.                                                             | 83 |

| 5.13         | Mean Overall Hit Rates When Genetic Algorithm Policies Maximize OPT  Match Rate                                                                                                            | 88  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.14         | Number of Canonical Forms for History Replacement                                                                                                                                          | 90  |

| 5.15         | Line Hit Rates using Canonical and Non-canonical Representation. 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines                                              | 92  |

| 5 16         | Line Hit Rates for Least Recent History and other Replacement Policies. 512 byte I-cache with 4-way associativity, 32 byte lines                                                           | 94  |

| 5.17         | Line Hit Rates for Least Recent History and other Replacement Policies. 512 byte D-cache with 4-way associativity, 32 byte lines                                                           | 95  |

| 5.18         | Percentage Distribution of Distinct Lines Accessed in Set When Miss Occurs using LRH replacement. 512 byte I-Cache with 4-way associativity, 32 byte lines                                 | 96  |

| 5.19         | Percentage Distribution of Distinct Lines Accessed in Set When Miss Occurs using LRH replacement. 512 byte D-Cache with 4-way associativity, 32 byte lines                                 | 96  |

| <b>5.2</b> 0 | Line Hit Rates for History of Line References and for History of Line References and Hits/Misses. 512 byte Instruction and Data Caches with 4-way associativity, 32 byte lines             | 98  |

| 5.21         | Line Hit Rates for LRU, LRU-History, and Shadow Caches. 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines                                                       | 100 |

| 5.22         | Performance of LRU-History with Common Cache Replacement Policy and with Individual Set Replacement Policies. 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines | 101 |

# List of Figures

| 2.1 | Typical Cache Layout                                                                                                                                                                                         | 5  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Block Diagram of Cache Miss Hardware                                                                                                                                                                         | 24 |

| 4.2 | Hardware for LRU-FIFO Method                                                                                                                                                                                 | 25 |

| 4.3 | Hardware for LRU-Count Method on Misses                                                                                                                                                                      | 26 |

| 4.4 | Hardware for History Method                                                                                                                                                                                  | 28 |

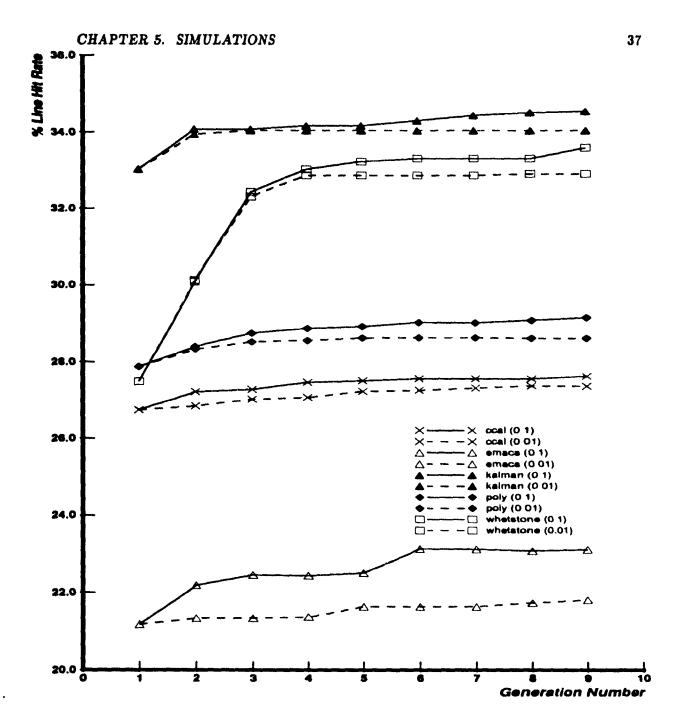

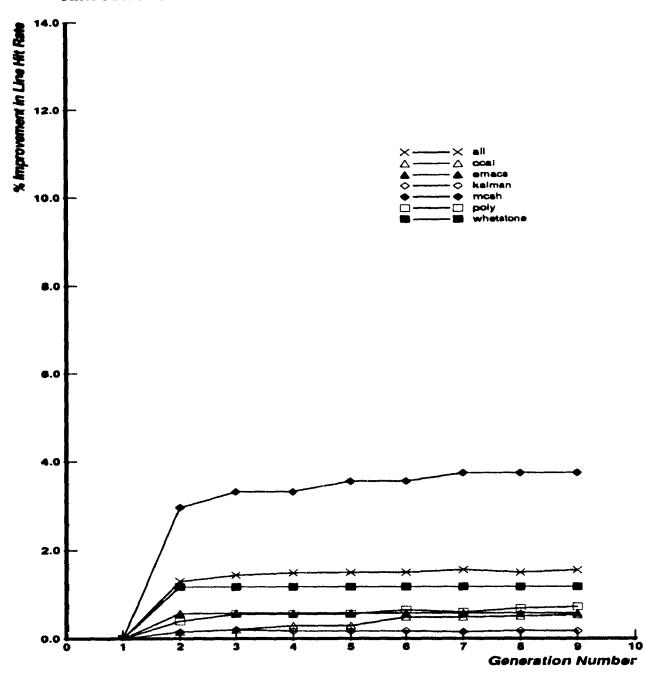

| 5.1 | Comparison of Performance of Best String by Generation for a Mutation Rate of 0 1 (solid lines) and 0.01 (dashed lines) for a 512 byte I-cache, 4-way associativity, 16 byte lines                           | 37 |

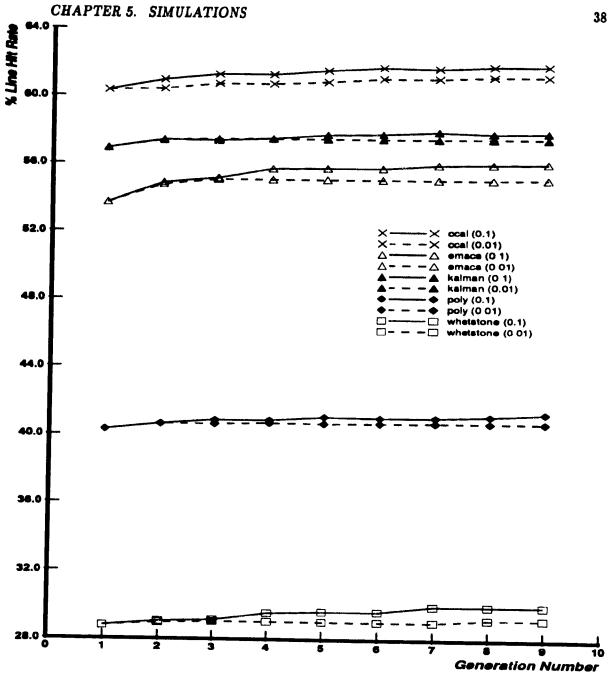

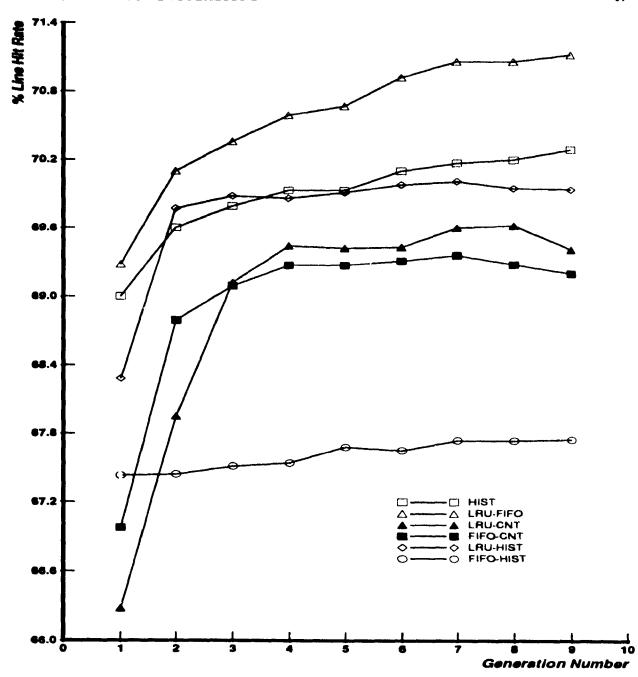

| 5.2 | Comparison of Performance of Best String by Generation for a Mutation Rate of 0.1 (solid lines) and 0.01 (dashed lines) for a 512 byte D-cache, 4-way associativity, 16 byte lines                           | 38 |

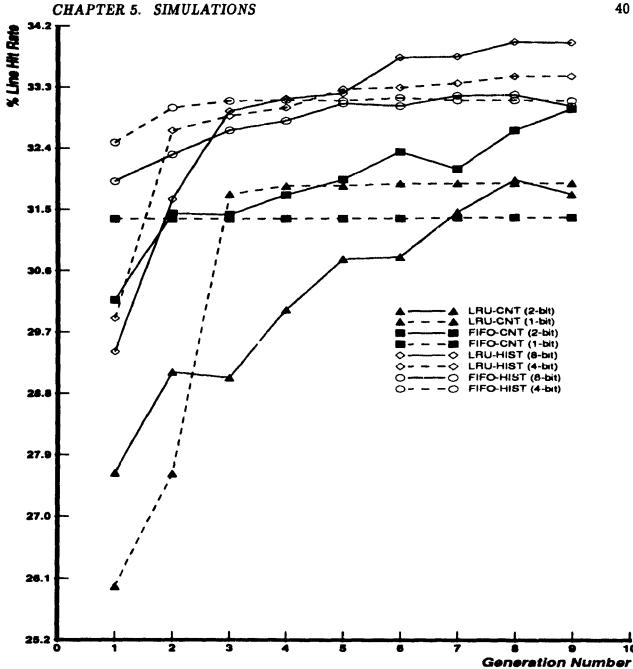

| 5.3 | Improvement in Best Strategy for kalman by Generation Solid lines represent longer history or count record, dashed lines represent shorter. Results for 512 byte I-cache, 4-way associativity, 32 byte lines | 40 |

| 5.4 | Improvement in Best Strategy for poly by Generation. Solid lines represent longer history or count record, dashed lines represent shorter. Results for 512 byte I-cache, 4-way associativity, 32 byte lines  | 41 |

| 5.5 | Improvement in Best Strategy for ccal by Generation for 512 byte I-cache, 4-way associativity, 32 byte lines                                                                                                 | 43 |

| 5.6  | Improvement in Best Strategy for emacs by Generation for 512 byte I-cache,  4-way associativity, 32 byte lines                                                                                | <b>4</b> 4 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.7  | Improvement in Best Strategy for whetstone by Generation for 512 byte Icache, 4-way associativity, 32 byte lines                                                                              | 45         |

| 5.8  | Improvement in Best Strategy for <i>ccal</i> by Generation for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                           | 46         |

| 5.9  | Improvement in Best Strategy for <i>emacs</i> by Generation for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                          | 47         |

| 5.10 | Improvement in Best Strategy for whetstone by Generation for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                             | 48         |

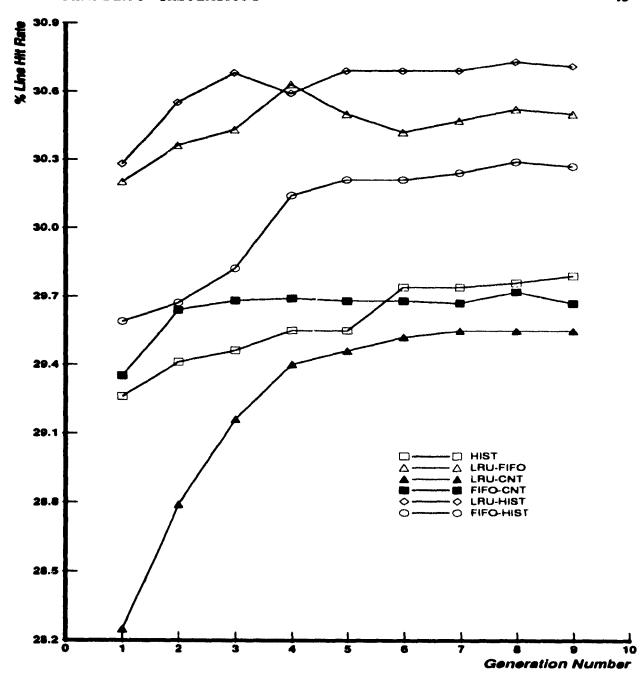

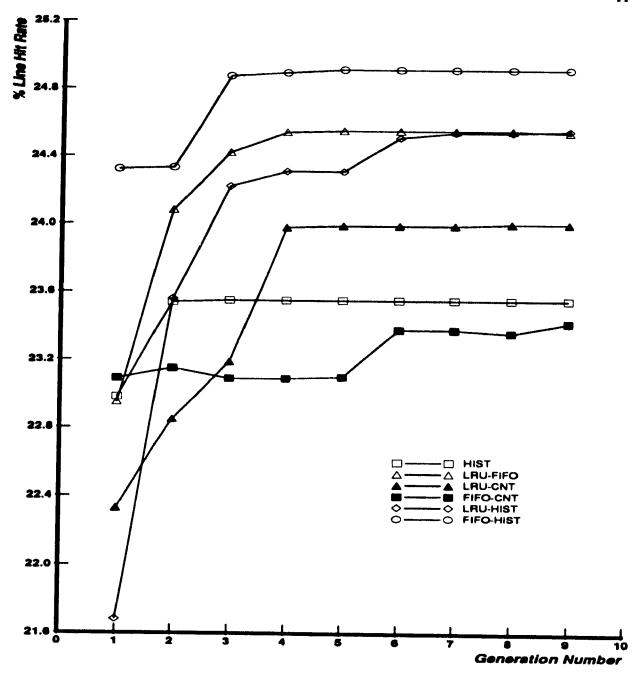

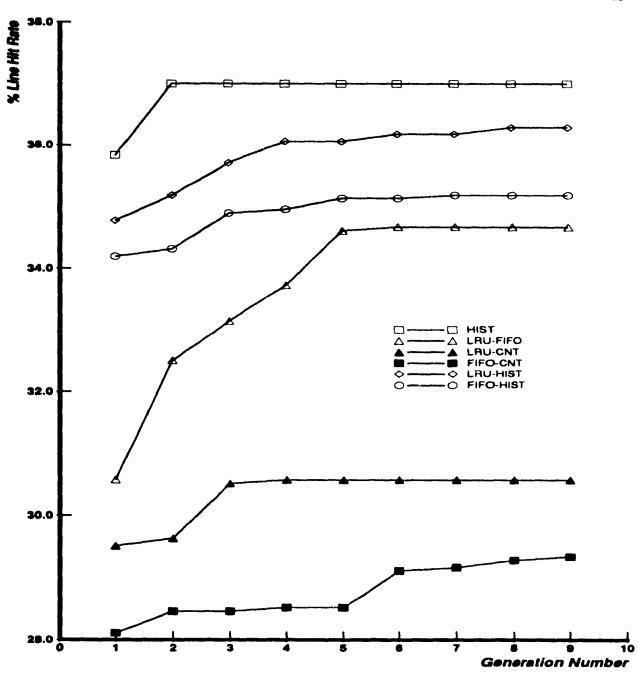

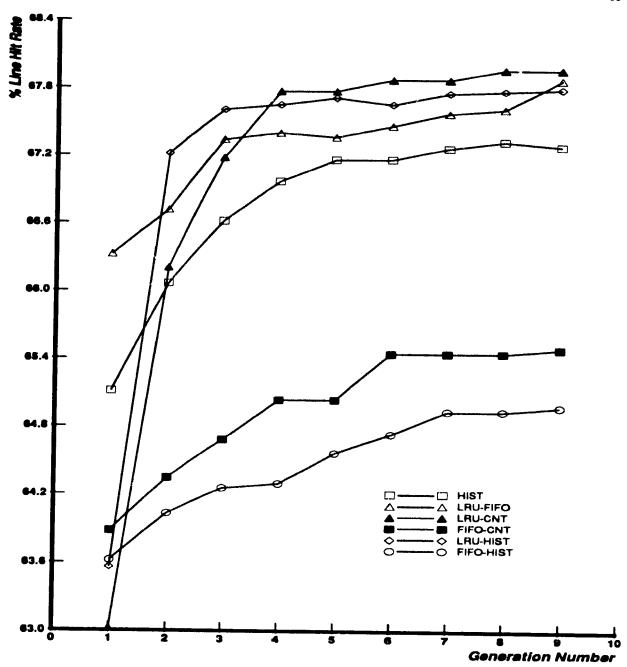

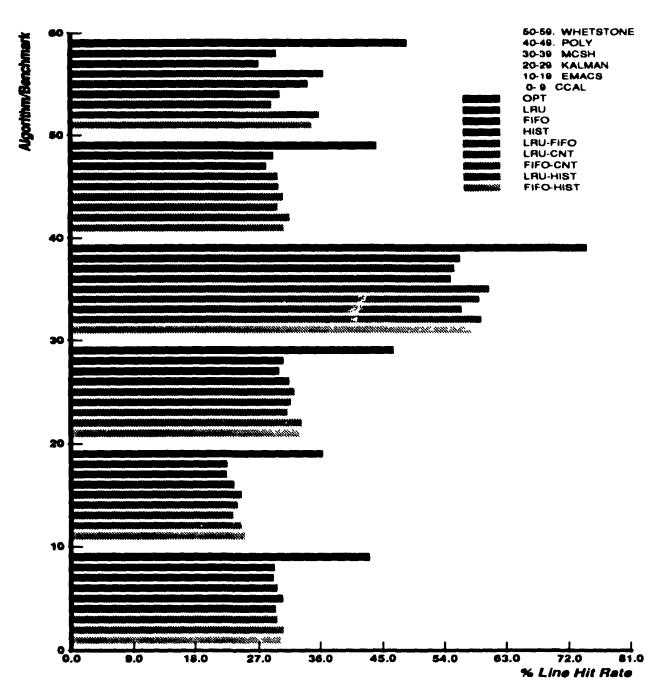

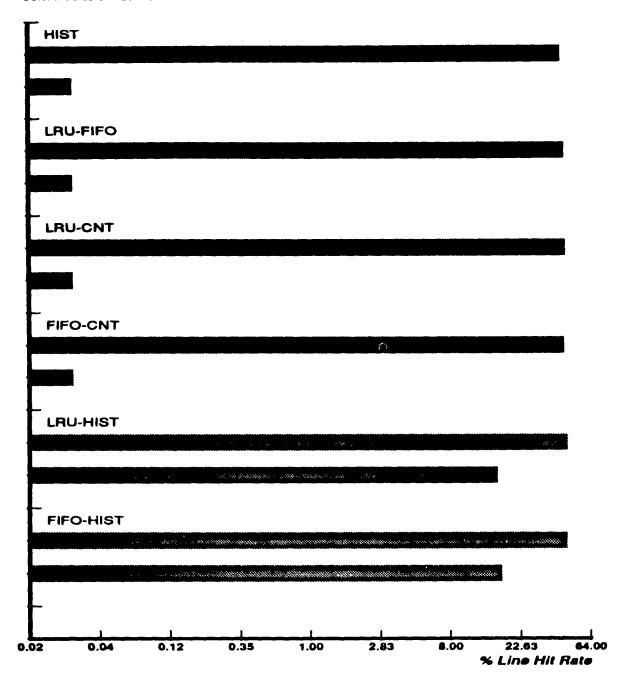

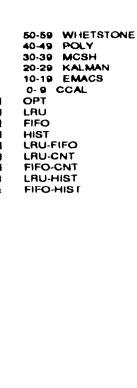

| 5.11 | Line Hit Rates for 512 byte I-cache, 4-way associativity, 16 byte lines                                                                                                                       | 49         |

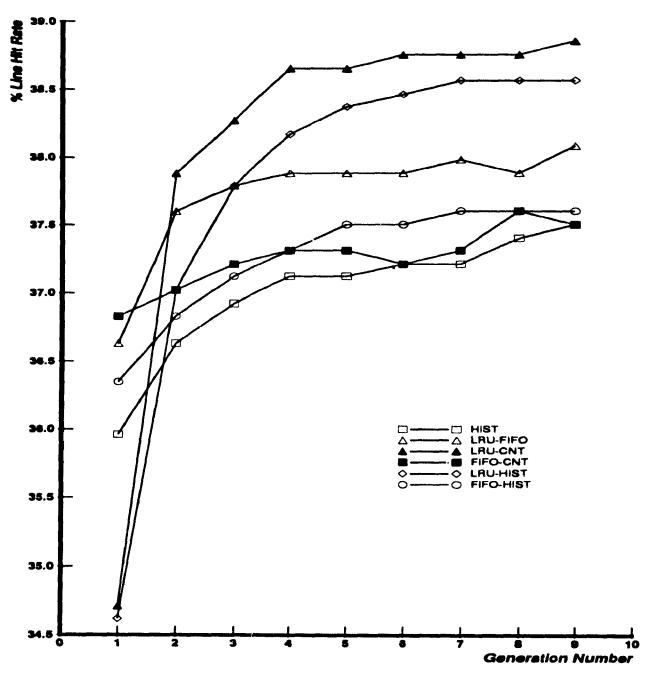

| 5.12 | Line Hit Rates for 512 byte D-cache, 4-way associativity, 16 byte lines                                                                                                                       | 50         |

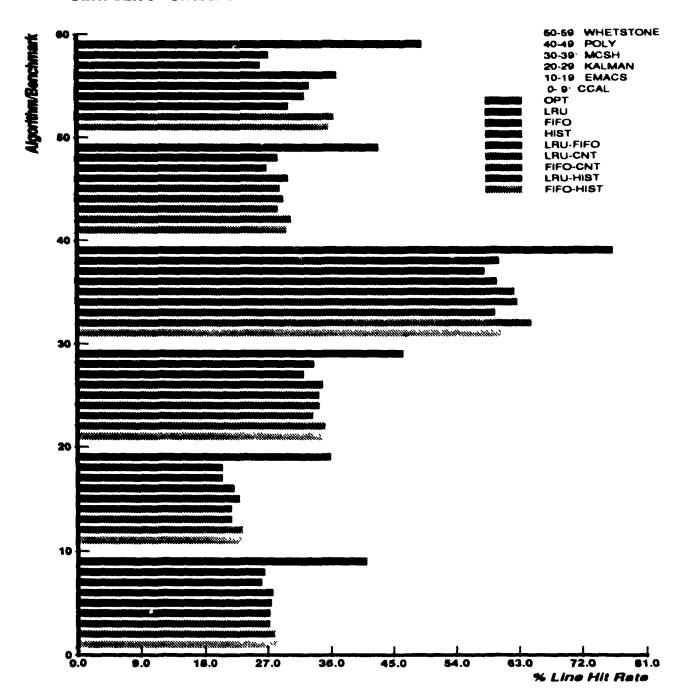

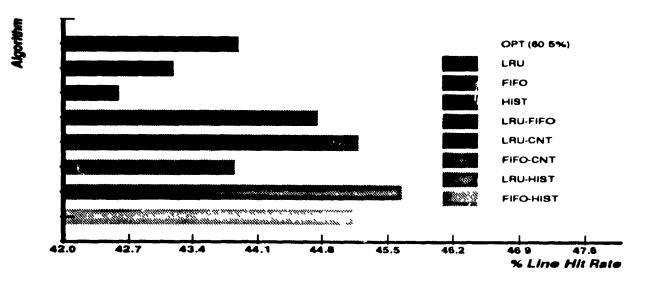

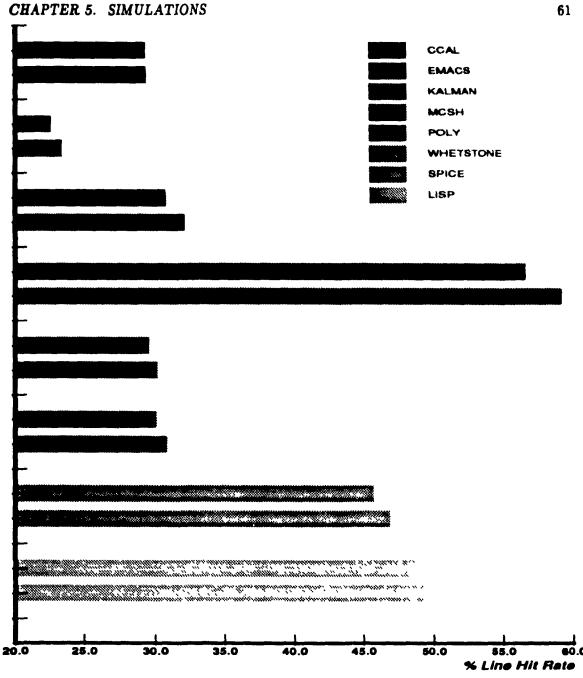

| 5.13 | Line Hit Rates for 512 byte I-cache, 4-way associativity, 32 byte lines                                                                                                                       | 51         |

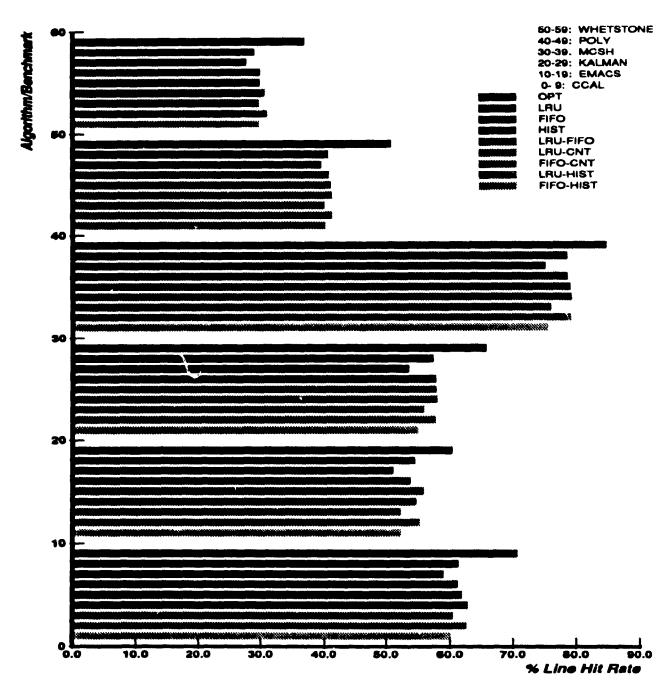

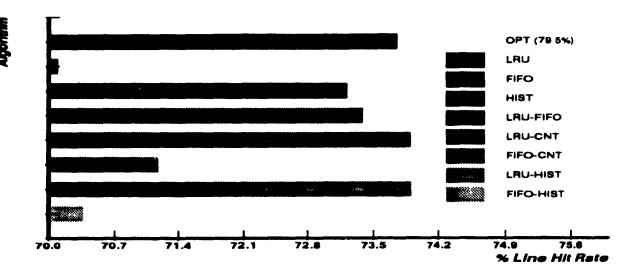

| 5.14 | Line Hit Rates for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                                                                       | 52         |

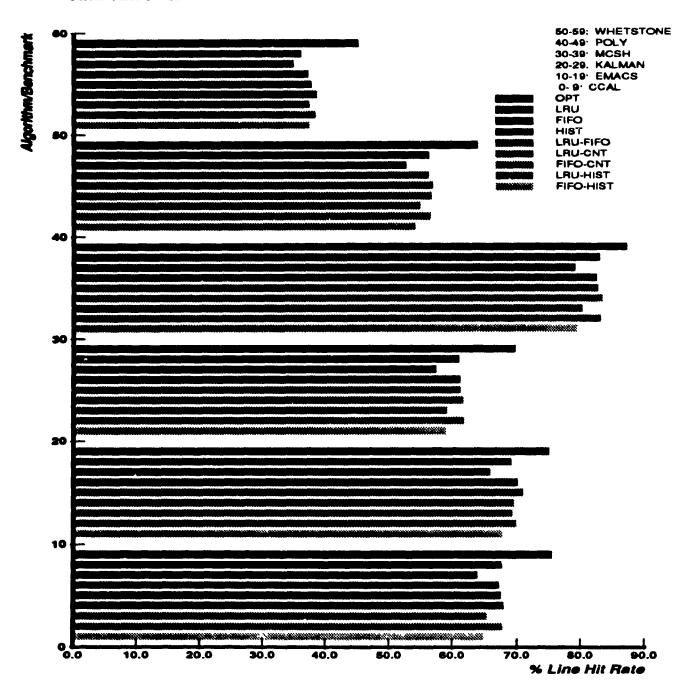

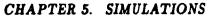

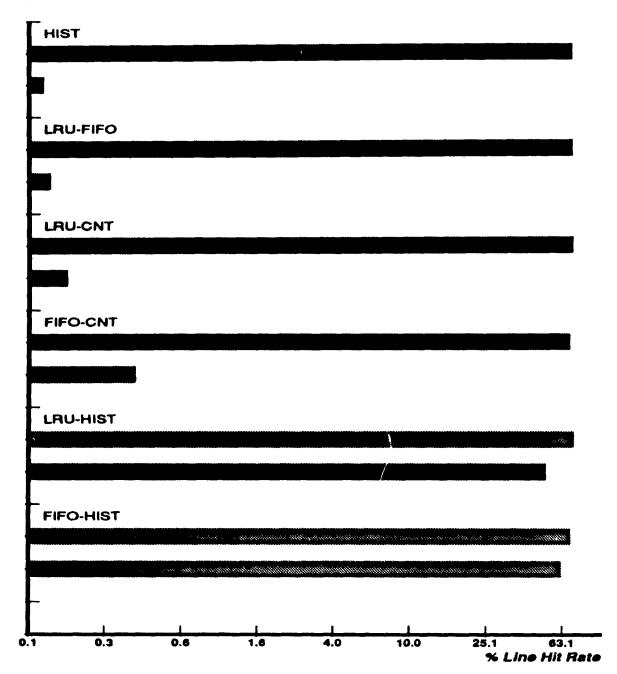

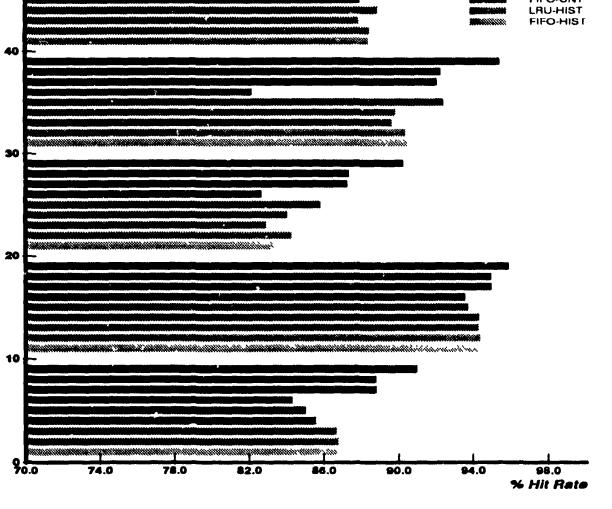

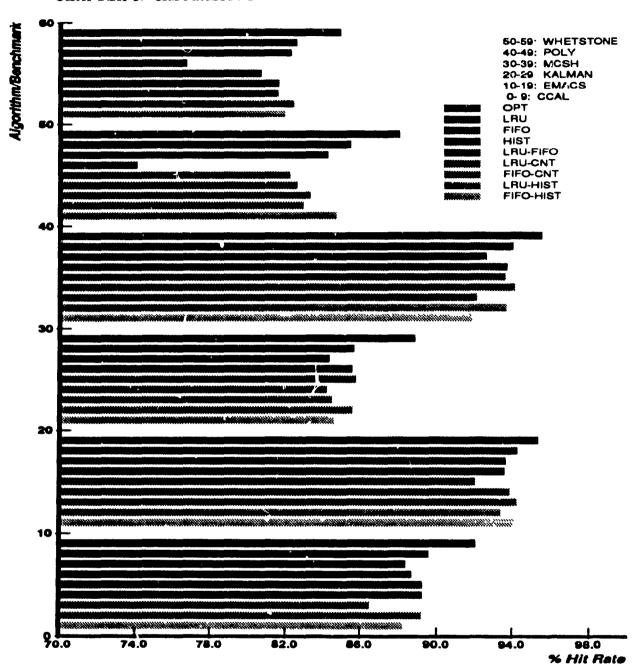

| 5.15 | Results by Algorithm for a Multitasking Suite of All Benchmarks for 512 byte I-cache, 4-way associativity, 32 byte lines                                                                      | 59         |

| 5.16 | Results by Algorithm for a Multitasking Suite of All Benchmarks for 512 byte D-cache, 4-way associativity, 32 byte lines                                                                      | 60         |

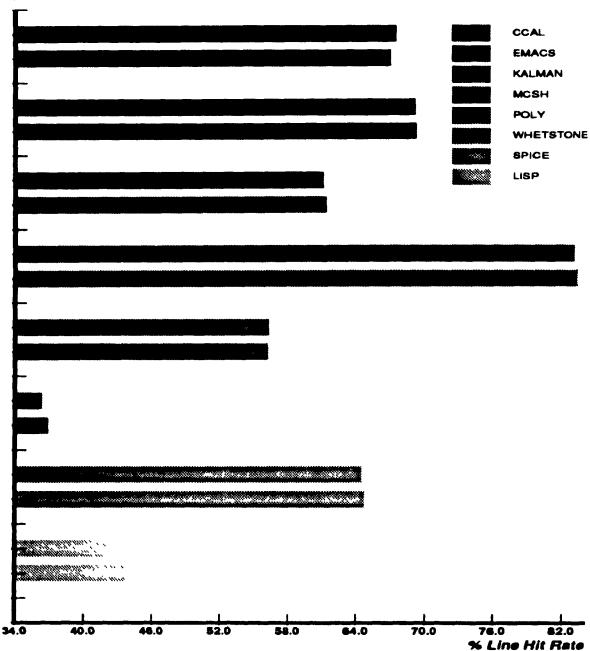

| 5.17 | Results of using the overall best <i>LRU-History</i> algorithm on individual benchmarks. Upper Bar is LRU, Lower is <i>LRU-History</i> . 512 byte I-cache, 4-way associativity, 32 byte lines | 61         |

| 5.18 | Results of using the overall best <i>LRU-History</i> algorithm on individual benchmarks. Upper Bar is LRU, Lower is <i>LRU-History</i> . 512 byte D-cache, 4-way associativity, 32 byte lines | 62         |

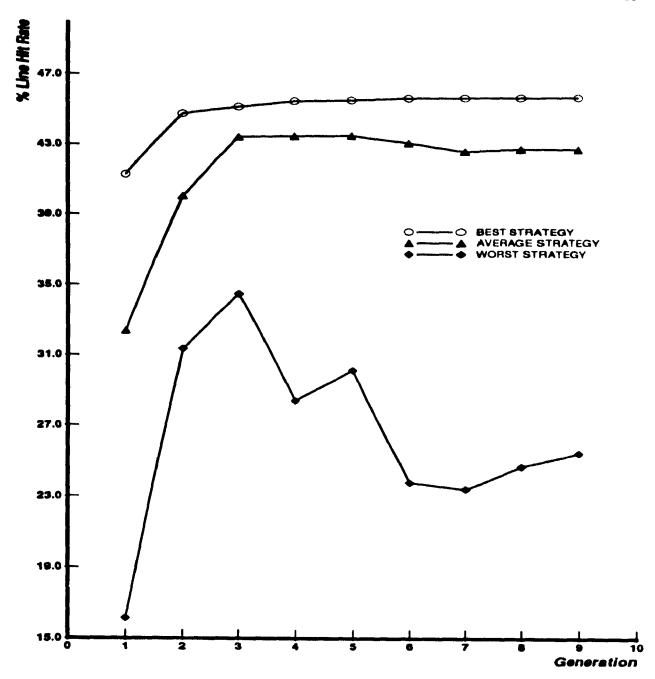

| 5.19 | Best, Worst, and Mean Performance of LRU-History Strings on Suite of Benchmarks for 512 byte I-cache, 4-way associativity, 32 byte lines                                                      | 65         |

| 5.20 | Performance of Best and Worst Strings for Suite of Benchmarks for 512 byte  I-cache, 4-way associativity, 32 byte lines.                                                                      | 67         |

| 5.21 | Performance of Best and Worst Strings for Suite of Benchmarks for 512 byte I-cache, 4-way associativity, 32 byte lines.                                                                                        | 68 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

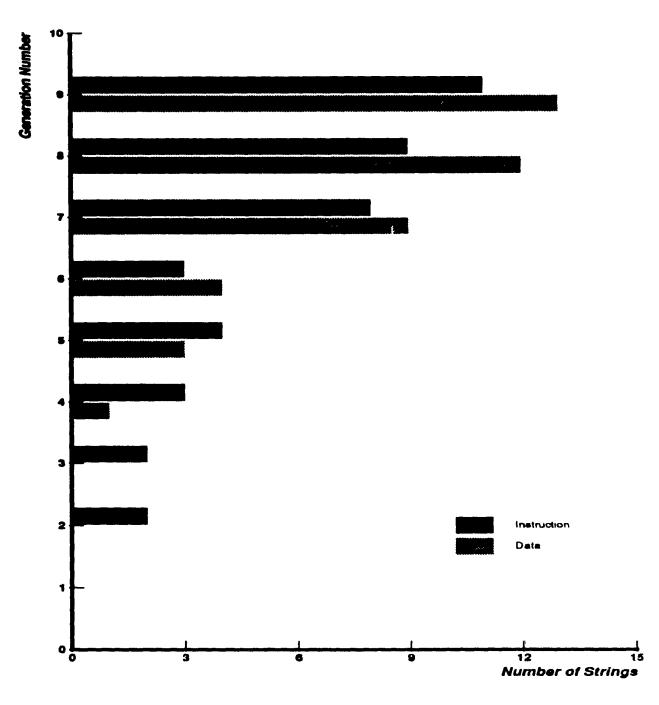

| 5.22 | Distribution of Generations at which Best Strings Occurred                                                                                                                                                     | 69 |

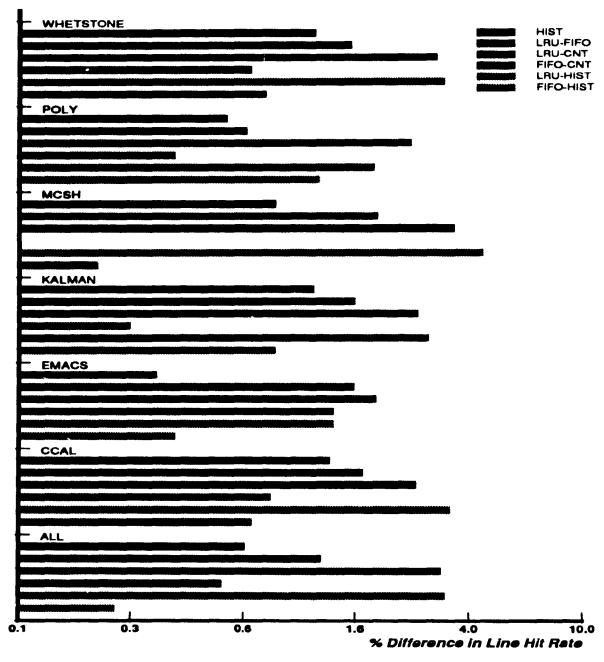

| 5.23 | Percentage Differences in Line Hit Rates between Best Strings Generated by Genetic Algorithm Approach and Best Strings Generated by Random Approach for a 512 byte I-cache, 4-way associativity, 32 byte lines | 71 |

| 5.24 | Percentage Differences in Line Hit Rates between Best Strings Generated by Genetic Algorithm Approach and Best Strings Generated by Random Approach for a 512 byte D-cache, 4-way associativity, 32 byte lines | 72 |

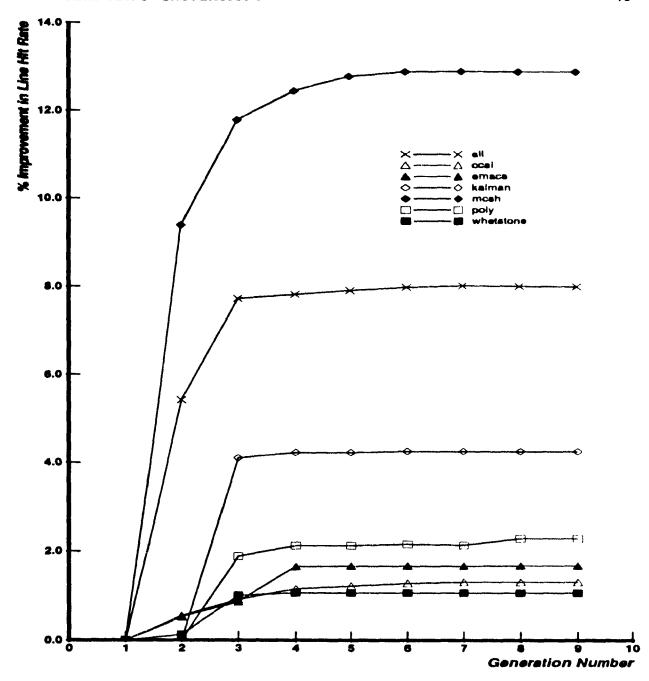

| 5.25 | Improvement in Line Hit Rate by Generation using the History Method for a 512 byte I-cache, 4-way associativity, 32 byte lines.                                                                                | 74 |

| 5.26 | Improvement in Line Hit Rate by Generation using the LRU-Count Method for a 512 byte I-cache, 4-way associativity, 32 byte lines                                                                               | 75 |

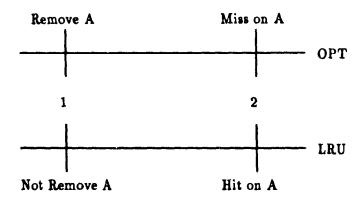

| 5.27 | Misses under LRU and OPT                                                                                                                                                                                       | 77 |

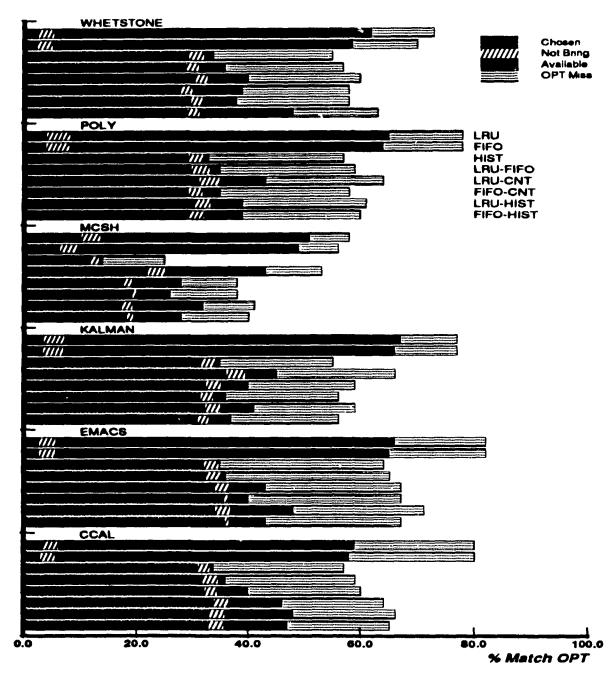

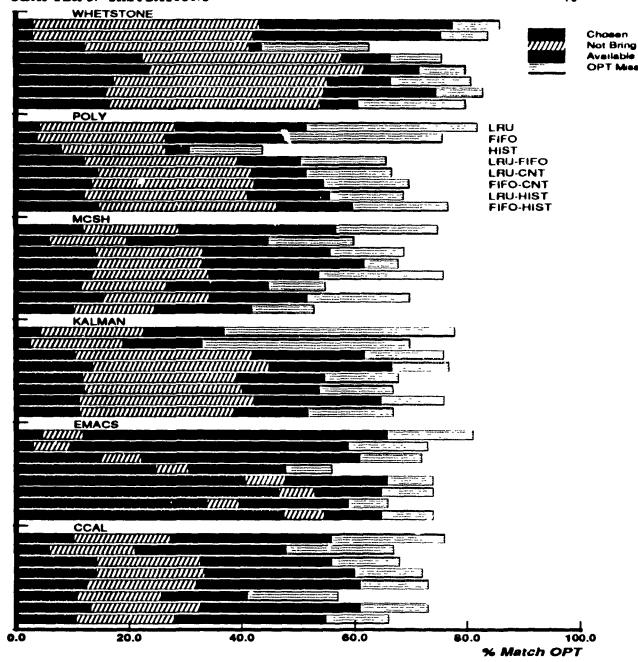

| 5.28 | Behavior of Replacement Policies Compared to OPT. Genetic Algorithm Policies have OPT Match Rate Maximized. 512 byte I-cache, 4-way associativity, 32 byte lines.                                              | 78 |

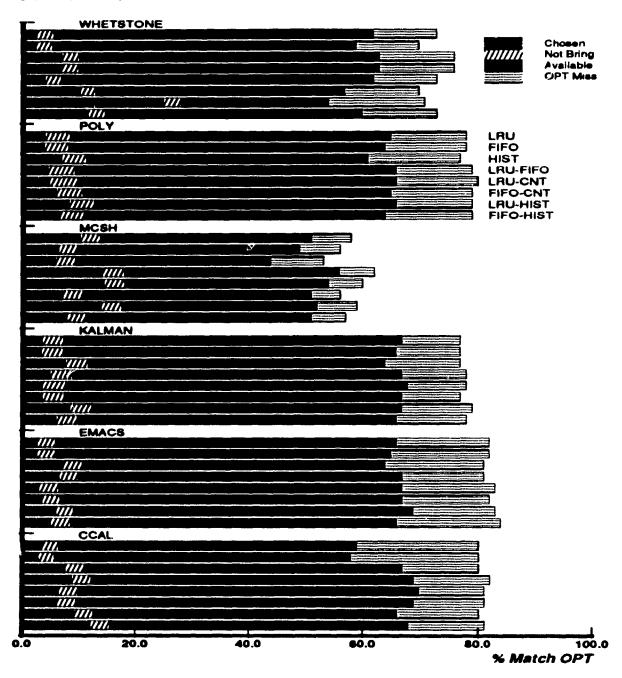

| 5.29 | Behavior of Replacement Policies Compared to OPT. Genetic Algorithm  Policies have OPT Match Rate Maximized. 512 byte D-cache, 4-way associativity, 32 byte lines                                              | 79 |

| 5.30 | Behavior of Replacement Policies Compared to OPT. Genetic Algorithm Policies have Line Hit Rate Maximized 512 byte I-cache, 4-way associativity, 32 byte lines                                                 | 80 |

| 5.31 | Behavior of Replacement Policies Compared to CPT. Genetic Algorithm Policies have Line Hit Rate Maximized. 512 byte D-cache, 4-way associativity, 32 byte lines                                                | 81 |

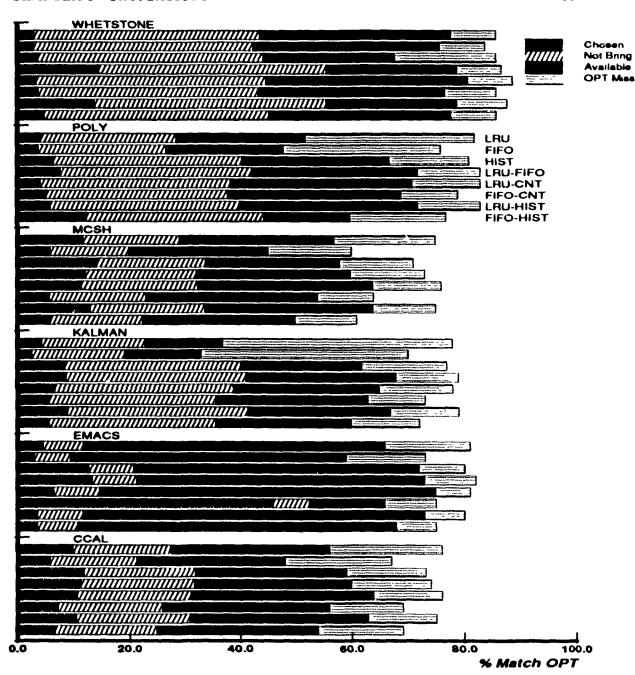

| 5.32 | Overall Hit Rates When Genetic Algorithm Policies Maximize OPT Match Rate. 512 byte I-cache, 4-way associativity, 32 byte lines                                                                                | 86 |

| 5.33 | Overall Hit Rates  | When Genetic    | Algorithm Policies   | Maximize ( | OPT Match |    |

|------|--------------------|-----------------|----------------------|------------|-----------|----|

|      | Rate. 512 byte D-c | ache, 4-way ass | sociativity, 32 byte | lines      |           | 87 |

#### Abstract

The most common and generally best performing replacement algorithm in modern caches is LRU. Despite LRU's superiority, it is still possible that other feasible and implementable replacement policies could yield still better performance [34] found that an optimal replacement policy (OPT) would often have a miss rate 70% that of LRU.

If better replacement policies exist, they may not be obvious. One way to find better policies is to study a large number of address traces for common patterns. Such an undertaking involves such a large amount of data, that some automated method of generating and evaluating policies is required. Genetic Algorithms provide such a method, and have been used successfully on a wide variety of tasks [21].

The best replacement policy found using this approach had a mean improvement in overall hit rate of 0.6% over LRU for the benchmarks used. This corresponds to 27% of the 2.2% mean difference between LRU and OPT. Performance of the best of these replacement policies was found to be generally superior to shadow cache [33], an enhanced replacement policy similar to some of those used here.

#### Résumé

Le plus performant et le plus utilisé des algorithmes de remplacement dans les systèmes de cache modernes est l'algorithme LRU. Malgré cette supériorité, il est possible d'implanter d'autres algorithmes de remplacement avec une meilleure performance. Dans [34], on a trouvé un algorithme optimal qui le plus souvent fait preuve d'un "miss rate" valant 70% de celui du LRU.

Même si des algorithmes plus performants existent, la question d'en trouver est autrement difficile. Une technique pour trouver un meilleur algorithme est d'étudier un grand nombre de traces d'adresses pour le même motif. Cette tâche exige le traitement d'une quantité énorme de données, et par conséquent n'est pas praticable sans un outil automatique pour engendrer et évaluer les différents algorithmes. La méthode des Algorithmes Génétiques fournit un tel outil; les chercheurs s'en sont servis avec succès pour une large gamme de tâches [21].

Le meilleur algorithme de remplacement trouvé dans cette thèse, en utilisant cette méthode, jouit d'une amélioration moyenne de 0,6% dans le "hit rate" global, relativement à celui de l'algorithme LRU, par rapport aux "benchmarks" utilisés. Cette amélioration correspond à 27% de la différence moyenne de 2,2% entre les algorithmes LRU et OPT.

La performance du meilleur des algorithmes de remplacement ici présentés s'est révélée généralement supérieure à celle du "shadow cache" [33], une règle de remplacement qui ressemble à certains des algorithmes dans cette thèse.

## Chapter 1

### Introduction

This introduction assumes a basic familiarity with caches and genetic algorithms. If this is not the case, Chapter 2 reviews fundamentals of cache operation, and Chapter 3 provides basic motivation and theory of genetic algorithms.

An important aspect in determining cache performance is the replacement policy used. In a typical system, main memory may be 10 times slower than cache [36] [41] [23]. In this case improving cache hit rate from 90% to 95% reduces the effective memory access time by more than 30%. Furthermore the gap between cache speed and main memory speed is growing [27].

The problem of increasing hit rate has been handled by:

- 1. Increasing the cache size

- 2. Increasing the line size

- 3. Maintaining separate instruction and data caches

- 4. Increasing the associativity

- 5. Prefetching

- 6. Software "hints" to the cache

Ì

#### 7. Investigating alternative replacement policies

The order of this list gives some indication of the relative emphasis that has been placed on different solutions. However, the ranking is not rigid and some may prefer a slightly different order. Nevertheless, the most common replacement policies now in use, such as LRU and FIFO, have been employed at least since the 1960's [36].

There are several reasons for this. Both LRU and FIFO are relatively simple to implement and offer good performance, with LRU generally having the higher hit rate. Other replacement methods have been tried, for example Random, Least Frequently Used (LFU), and Partition LRU—a slightly simplified version of LRU [29] [36]. However LRU has generally been found to have the highest hit rate of all these replacement policies [36]. Upon reflection, the reader will likely find that few additional policies come to mind.

Different cache parameters are most often tested using software simulators. A typical way to do this is to collect "representative" benchmark programs and execute them on an architectural simulator. As part of the simulation, the stream of addresses generated by the benchmark are stored to a file. This address trace file is then used as input to the cache simulator.

Variations are possible, such as integrating the cache simulator with the architectural simulator, thereby eliminating the need for the intermediate address trace file. This is important, as address trace files are often many megabytes or even gigabytes. Unfortunately, address trace files are needed here for reasons given in Chapter 4.

One of the advantages of using trace driven cache simulation is that it is possible to determine the optimal performance achievable by any replacement algorithm [6]. This optimal replacement policy is sometimes called MIN, but here it will be referred to as OPT following the convention of [29]. It has been found that OPT often has a miss rate only 70% that of LRU [34]. Thus there is significant room for improvement in replacement policies.

However, if improved replacement policies exist, they may not be obvious. One way to find better policies is to study a large number of address traces for common patterns. Such an undertaking involves such a large amount of data, that some automated method of generating and evaluating policies is required. Genetic Algorithms (GA's) provide such a method, and have been used successfully on a wide variety of tasks [21].

Some examples of these include VLSI circuit layout [13], adaptive filter design [17], the travelling salesman problem [8] [22] [42], prisoner's dilemma [5], and job shop scheduling [12]. Other areas of application range from cellular biology to demographics.

In essence, genetic algorithms attempt to mimic evolution: different replacement policies compete, with the fittest surviving and evolving to even fitter policies. Different replacement policies are represented as different bit strings, in a manner analogous to DNA sequences.

As described here, genetic algorithms would be employed during the design of an architecture or possibly at compile time. They would not be used on the fly by the cache, as the time and space overhead is far too prohibitive.

The basic notion is as follows. Start with a population of random strings (replacement policies). For each string, run a cache simulation on a benchmark address trace. Record the hit rate or some other performance measure for the string. After all strings have been simulated, reproduce the better strings in a new generation of strings. Finally apply additional genetic operators such as mutation and crossover between strings to find new and better replacement policies.

The goal of this work is to use this genetic algorithm approach to find replacement policies which improve upon traditional policies, in particular, LRU.

### Chapter 2

### Cache Basics

CPU's have historically been able to operate at faster clock rate than main memory and this imbalance is likely to continue for the foreseeable future. [27]. One means of alleviating this bottleneck has been to employ fast cache memory between the CPU and main memory. However, in order to achieve this speed, the size of caches has been far smaller than that of main memory. (Because they are small, caches can employ more expensive, higher power memory chips than main memory. They can also be placed on the die of modern CPU's, thereby avoiding the speed penalty caused by the large capacitances on the chip's output pins.)

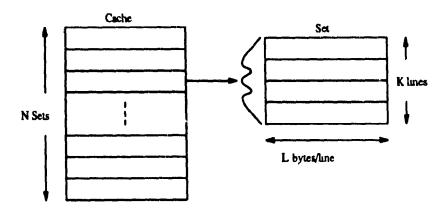

Since caches are smaller than main memory, some means is required to map main memory addresses to cache. There are a multitude of ways to do this, but the basics of almost all caches are the same. Caches function as an associative memory. As is illustrated in Figure 2.1, internally they are almost all divided into 3 parts which determine the overall size of the cache:

- N Sets

- K Lines per Set (K is the Associativity)

- L Bytes Per Line

- Cache Size =  $N \times K \times L$

Figure 2.1: Typical Cache Layout.

In the literature, the synonym block is often used for line [36].

This structure facilitates quickly finding whether a particular main memory address is present in the cache. To see this, consider the steps a sample cache follows in finding whether an address is present:

- 1. 16-bit Address, ABCDEFGHIJKLMNOP

- 2. 1024 byte Cache

- 3. K = 4-way associativity

- 4. L = 8 bytes per line

- 5.  $N = \frac{Cache\ Size}{K \times L} = \frac{1024\ bytes}{4 way \times 8\ bytes} = 32\ sets$

- 6. Address Bits NOP specify which of the 8 bytes in the line

- 7. Address Bits IJKLM specify which of the 32 sets

- 8. Address Bits ABCDEFGH form a tag

- 9. Use K=4 comparators to determine if the tag is present in the set

Note than every memory address maps to a specific cache set, and hence one of K lines. The cache must determine whether a value requested by the CPU is present and return it as quickly as possible. Hence the number of tag comparisons (K) performed to check if a value is present must be minimized. Even if all the comparisons are performed in parallel, there are problems: a large amount of space is required for the comparators and the larger space implies a reduced maximum clock frequency. Peak power consumption is increased. On the other hand, too small an associativity, K, can cause problems when many memory addresses to map to the same set. The result is thrushing while the different addresses compete for space in the set. Typically K is 2 or 4, but values from 1 to 16 have been used [36]. K is typically a power of two, but as can be seen in the example above, it need not be. [31] for example uses a K = 3-way associative cache. N and L must be powers of 2.

As can also be seen in the example, the lower order bits are used to map addresses to sets. As one might expect this acts as a quasi-random function to evenly distribute addresses among all sets. A random mapping generally minimizes the number of multiple addresses competing for space in the same set, i.e. it minimizes thrashing. However, since caches are smaller than main memory, conflicts sometimes occur. If each of the K lines in a set contains an address, then one of the K addresses must be replaced, when a new line also maps to that set.

There are several common algorithms which are used to decide which line to replace. The algorithms must be simple as usually they must operate in one or two CPU cycles.

- LRU, the Least Recently Used line is replaced.

- Partition LRU, a simplified approximation to LRU. Here the K lines in a set are partitioned into subsets. For example, an 8-way associative cache may have 4 subsets of 2 lines each. The order of use of each subset is maintained, as is the order within each subset. On a miss the least recently used line in the least recently used subset is replaced. Partition LRU is used mainly in "highly" associative  $(K \ge 4)$  caches.

- LFU, the Least Frequently Used line is replaced.

- FIFO, the First In line is the First Out.

- Random, a pseudo-randomly chosen line is replaced.

• OPT, the optimal strategy where the line which is used furthest in the future is replaced [6].

Since future information is unknown to the cache, OPT cannot be used in real caches. However software cache models are commonly used to test a specific cache configuration [36] [37] [1] [16]. These models take as input, a trace of memory addresses generated by a particular benchmark or benchmarks. (Methods of generating such a trace are described below.) A prepass can be done on this trace to determine how long until each line is referenced again. OPT can then use this information on a second pass to expel the line referenced furthest in the future. The performance achieved using OPT provides a good basis against which other strategies can be compared. It is actually possible to write a single pass OPT [7]. LRU is the most common and generally the best performing of the (implementable) algorithms above [36]

In order to determine which replacement and which cache parameters are best, some measure of cache performance is required. There are several:

- Hit Rate, the percentage of time that the location desired by the CPU is present in the cache. This metric is a good measure of overall cache performance.

- Line Hit Rate [39], similar to hit rate, but for a given set, the only accesses considered are those which are to a different line than the previous time the set was accessed. Any series of accesses within a single line produces hits no matter what replacement algorithm is used. As a consequence maximizing the line hit rate also maximizes the overall hit rate. However, the line hit rate more closely reflects the difference between two replacement policies.

The behavior of line hit rate can be surprising. If the metric used is overall hit rate and one of the cache size parameters—line size (L), associativity (K), or number of sets (N)—is increased while the others are held constant, then the overall hit rate is increased (or possibly held constant). However if the metric user is line hit rate, this is not true.

This is because the *line hit rate* considers only those references which access a different line than the previous time a given set was accessed. When the cache size is increased, the number of references in which a new line is referenced is generally decreased. The

line hit rate of this decreased number of new line references may be lower than for a smaller cache with more new line references.

- OPT Match Rate, the percentage of time that the line replaced is the same line that OPT would have replaced.

- Average Access Time, the average number of cycles the cache takes to return a value to the CPU. This is directly related to the hit rate.

- Memory Traffic, the number of transfers between cache and main memory. This is especially important for a multiprocessor system with global memory and where each processor has a local cache.

- Utilization, the number of times each location in the cache is accessed. This is a measure of the value of a cache compared to alternative uses of the chip or board space. If utilization is low, it may be a better use of space to have two simple processors with small caches, than one complex processor with a single larger cache.

Here we are most interested in the effectiveness of replacement algorithms. Hence hit rate, line hit rate, and OPT match rate are used. Trying to find a replacement policy which matches OPT is one way of having the cache recognize certain access patterns and respond to them, hopefully in an optimal way.

Although most caches are organized as has been described, a single CPU need not have only one unified or combined cache. The CPU may have multiple caches, each containing distinct information. Two types of divisions are most often suggested [36]:

- Instruction Cache and Data Cache

- Supervisor Cache and User Cache

Separate supervisor and user caches are designed to increase hit rate and utilization by keeping user code in cache during interrupts. These goals are not always accomplished. This is because two, half-size caches can be too small to accommodate the working set of references, whereas one larger cache would be sufficient. The larger cache also dynamically shifts what fraction of it is used for one purpose and what fraction is used for the other. For this reason, separate supervisor/user caches are rarely used [36].

Separate instruction and data caches have two other advantages. Bandwidth from cache to processor is increased—barring cache misses the processor can be continuously fed with instructions and data. An instruction cache can also be simpler (and hence larger and faster) since it need never be concerned with memory writes. (Most modern architectures assume that self-modifying code is not used.)

A CPU may also have multiple levels of cache. In a multi-level system, instead of placing a single cache in between the CPU and main memory, an additional, generally slower cache is placed between the first cache and main memory. This hierarchy may be extended arbitrarily deep, but there is generally not enough difference in speed between main memory and the CPU to warrant more than two levels of cache [41].

Finally as already noted, most cache study is done using software cache simulators and address traces. Some methods of trace collection are

- Special instrumentation and recording hardware for existing systems.

- Software architectural simulators.

- ATUM or Address Tracing Using Microcode [2]. Patches are made to microcode to record all address references made by the machine including operating system calls and interrupts.

Architectural simulators are simplest, but have the drawback that they usually generate traces from only a single (user) program. Obtaining and properly mixing addresses from system code and interrupts is virtually impossible. Microcode patches become less viable as RISC (no microcode) and VLSI (microcode not patchable) grow ever stronger. Instrumentation hardware is too expensive and too complicated to be of general use. It is especially difficult to synchronize trace collection with the execution of specific programs.

Trace simulation allows complete flexibility as to cache parameters, and even allows the OPT replacement policy to be used. However, trace simulation is also orders of magnitude slower than an actual cache and deals with traces that almost always represent very little computing time. 20 million addresses might represent only one second of computing in a modern RISC processor, but take up 80 megabytes of disk space.

į

This large disk space requirement has spurred some researchers to integrate their cache simulator more fully with an architectural simulator [26]. Desired benchmarks are executed on the simulator and as address references are generated, they are immediately passed to the cache simulator, which maintains the desired statistics. Unfortunately this approach is not practical here. As will be seen, the same trace must be reused hundreds and thousands of times. The additional overhead of simulating an entire architecture running the desired benchmark is prohibitive.

An alternative to trace simulation or architecture/cache simulation is to have the cache maintain CPU addressable counters for the number of hits and the number of misses [4]. The CPU could clear these counters and later record the number of hits and misses at any desired point. Incrementing of the counters can be done in parallel with other cache activity and hence need not slow it down. This method could provide the hit rate for the system including all interrupts and system code. With a small additional bit of hardware, the line hit rate could also be maintained in this manner. Memory traffic could also be accurately measured via onboard counters.

Clearly, this counter scheme could not be used directly in developing new architectures. However if it were generally implemented, cache performance statistics would be available for a much wider variety of machines and workloads than is presently the case.

## Chapter 3

# Genetic Algorithms

The goal of genetic algorithms is to mimic evolution to find optimal or near optimal solutions for a given problem<sup>1</sup>. The problem must be well defined, and a function must exist to evaluate proposed strategies. A number of approaches for genetic algorithms have been proposed. Almost all modern approaches use a population of binary strings (or strategies) [21], all of the same length, *l*-bits Each string represents a possible solution.

Any moderately complex problem has more solutions than can reasonably be enumerated and searched for an optimum. If l=32, exhaustive search requires that  $2^{32}\approx 4$  billion strategies be evaluated to find the optimum of the function. Genetic algorithms attempt to reduce the search space to a manageable size at the risk of finding only an approximately optimal solution.

A simple genetic algorithm, typical of many modern approaches, is outlined below:

- 1. Generate a random population of l-bit binary strings.

- 2. Evaluate fitness of all strings.

- 3. Use fitness to determine which strings to reproduce in the next generation.

<sup>&</sup>lt;sup>1</sup>The exposition in this Chapter borrows heavily from descriptions given in Goldberg's comprehensive 1989 book [21]

- 4. Original generation "dies".

- 5. Pair off strings in new generation.

- 6. For each pair, randomly choose a bit position, p in the string.

- 7. Swap the bits to the right of p between the two strings in the pair. (Crossover)

- 8. Randomly mutate (with small probability) bits in resulting population.

- 9. Goto Step 2.

This algorithm uses three operations to systematically seek improvements in the population, or in other words to search for an optimum solution.

- Reproduction rewards the fittest strategies.

- Crossover generates new strategies and rewards good substrings.

- Mutation adds diversity and insures that all strings may be generated at all times.

To make matters more concrete, consider the following example which goes through one iteration of the basic algorithm above.

- 1. Initial Population: A = 0111000, B = 0101010, C = 1001001, and D = 1010110

- 2. Assume A, C, and D are best by some criteria and two A's, one C, and one D are reproduced in the next generation.

- 3. Assume the pairing is A/C and A/D.

- 4. Randomly choose 3 as the crossover position for A/C, and 5 as the crossover position for A/D.

- 5. This yields: A' = 0111001, B' = 1001000, C' = 0111010, and D' = 1010100.

- 6. Randomly choose the 2nd bit of C' and the 7th bit of D' to mutate.

- 7. The new generation is: A' = 0111001, B' = 1001000, C' = 0011010, and D' = 1010101.

A simple and innovative use of genetic algorithms was proposed by Axelrod and Forest [5] [18] for the game, Prisoner's Dilemma. In this game, two accomplices are held in separate rooms by police as suspects in some crime. In truth both prisoners are guilty However, the suspects will receive longer or shorter sentences depending on whether both, neither or one of them confess. To make the game more interesting, this sequence is repeated for a large number (150) of moves, thereby allowing each of the two prisoner's to learn about the other's behavior.

At a 1985 computer tournament, a tit-for-tat strategy was victorious over many more complicated strategies. (In tit-for-tat, one does what the opponent did in the previous move.) Using a genetic algorithm approach, Axelrod and Forest found a strategy that consistently beat tit-for-tat as well as the other strategies in the tournament Their approach can be summarized (and slightly simplified) as follows:

- 1. At each move each prisoner can confess or not. Hence each move can be recorded with 2 bits.

- 2. Record the 6-bit history of past 3 moves.

- 3. Choose the next move based on this 6-bit history.

- 4. 6 bits  $\Rightarrow$   $2^6 = 64$  possible histories.

- 5. For each of the 64 histories, the strategy must indicate whether to confess or not.

- 6. Goal: Find the optimal 64-bit strategy.

- 7. Method: Generate a random population of 64-bit strings and use genetic algorithm as described above. At each generation, play each string against every other. A string's fitness is a (nonlinear) function of the total amount of prison time incurred by that string.

Although genetic algorithms have some appeal merely by analogy to nature, it can be shown in a more mathematically rigorous manner, that the operations of reproduction, crossover, and mutation will tend to produce successively more optimal populations [24]. To begin a pair of definitions are needed.

1

- A schema is a binary string, but not all bit positions need be defined. Don't Cares,

\*, are allowed. For example, H = 011 \* 1 \* \*. (The plural of schema is schemata).

- The defining length,  $\delta(H)$  of a schema, H, is the number of bits between the first and last defined bit position. For example,  $\delta(H=011*1**)=4$ .

These definitions can now be used to show that over time, reproduction creates exponential growth in the number of above average schemata in the population.

- Let there be a population, P containing n strings of length l at time t.

- Let the fitness of string, j be  $f_j$ .

- Let the average fitness of strings representing schema, H in this population be f(H).

- Let m(H, t) be the number of strings containing schema, H at time t.

- Then the expected number of strings containing H after reproduction at time t+1 is proportional to  $\frac{f(H)}{\sum_{i=1}^{n} f_i}$ :

$$m(H,t+1) = m(H,t) \frac{nf(H)}{\sum_{1}^{n} f_{j}}$$

$$= m(H,t) \frac{f(H)}{\overline{f}}$$

• If strings containing H are a factor c better than average at each generation, then

$$m(H,t+1) = m(H,t)\frac{(\overline{f}+c\overline{f})}{\overline{f}}$$

$$= (1+c)m(H,t)$$

This produces exponential growth in number of above average schemata and exponential decay for below average schemata.

$$m(H,t) = (1+c)^t m(H,0)$$

Reproduction never produces new strings. Alone it can never improve on the performance of the original population. Crossover does introduce new strings, and does so in such a way as to reward highly fit, short schemata. In other words good, small building blocks are favored. To see this, consider an example.

- Let  $H_1 = *1 * * * * *0$  and  $H_2 = * * *10 * *$ . Then  $\delta(H_1) = 5$  and  $\delta(H_2) = 1$ .

- There are 6 possible crossover locations for both  $H_1$  and  $H_2$ .  $H_1$  is destroyed by  $\delta(H_1) = 5$  of the 6 choices.  $H_2$  is destroyed by only  $\delta(H_2) = 1$  of the 6 crossover choices.

More generally, this idea can be summarized as follows.

• If crossover occurs with probability,  $p_c$ , the probability,  $p_s$ , of schema, H surviving is

$$p_s(H) = 1 - p_c \frac{\delta(H)}{l-1}$$

• In pure reproduction,  $p_c = 0$  and  $p_{\bullet} = 1$ . Allowing crossover changes the number of occurrences of schema, H expected in the next generation:

$$m(H, t+1) = m(H, t) \frac{f(H)}{\overline{f}} p_s(H)$$

$$= m(H, t) \frac{f(H)}{\overline{f}} \left[ 1 - p_c \frac{\delta(H)}{l-1} \right]$$

• Now the number of schemata, with short defining lengths,  $\delta(H)$  grows exponentially: the system rewards good, small building blocks.

Note that in this derivation, we ignore the small chance that crossover of two schemata not containing H will create an instance of H in the new generation. Including this effect does not change the main result [21].

Here mutation is assumed to occur as inversion of single bits. Multiple bits in a string may mutate, but each occurrence is assumed to be independent. Mutation has two roles. It can add diversity to a population, as well as guarantee that it is always possible to generate

any string. Always being able to generate any string is necessary to avoid getting stuck at a suboptimal solution when all strings in the population are identical at certain bit positions. Mutation also has a danger. If the mutation rate is too high, then the progress made through reproduction and crossover can be destroyed. Formally, the effect of mutation is as follows.

- Let pm be the probability of a bit mutating.

- Define the order of a schema, o(H) to be the number of fixed positions in H. For example, if H = 0.11 \* 1 \* \*, then o(H) = 4.

- The probability of H surviving mutation is

$$p_{m,sur} = (1 - p_m)^{o(H)} \approx 1 - o(H)p_m \text{ for } p_m \ll 1$$

• The probability of H not surviving mutation is

$$p_{mdie} \approx 1 - [1 - o(H)p_m] = o(H)p_m$$

Subtracting the destruction rate of schemata due to mutation from the previous recurrence for number of schemata in a generation yields *The Fundamental Theorem of Genetic Algorithms*:

$$m(H,t+1)=m(H,t)\frac{f(H)}{\overline{f}}\left[1-p_c\frac{\delta(H)}{l-1}-o(H)p_m\right]$$

## Chapter 4

# Genetic Algorithms Applied to Cache Replacement

### 4.1 Basics

As noted in Chapter 2, LRU is currently the most common replacement strategy used in caches. To improve upon it, either more or different information must be kept about the lines residing in cache. One way of using more information is to use both LRU and FIFO information in deciding which line to replace. Keeping a history of cache accesses is a way of using different information. A history could be kept and used with a genetic algorithm as follows:

- For the previous m accesses to a cache set, record whether the access is a hit or miss.

- If the access is a hit, record to which line it is a hit.

- If the access is a miss, record which line was replaced.

- If K is the cache associativity, then a genetic algorithm would require a population of strategy strings, each of B bits, where B is

### $B = log_2(K) \times 2^{m[1 + log_2(K)]}$

The derivation of this is quite simple. For each of the previous m accesses  $1 + log_2(K)$  bits are used to record what happened on that access. Thus there are  $2^{m[1+log_2(K)]}$  possibilities for the previous m accesses. For each of these possibilities, the line to be replaced must be specified. This takes  $log_2(K)$  bits, which yields the formula for B given above.

• For K=4-way associativity and a history of the last 4 accesses, each string is 8192 bits! For comparison [10] used some of the longest strings in genetic algorithm applications. They were the equivalent of less than 4000 bits. There are ways to reduce the complexity here as is discussed briefly below in Section 4.4 and more fully in Section 5.4.1.

Regardless of what approach is used—a combination of LRU and FIFO, history, or something else—some means is needed to find good solutions in the myriad of possible solutions. As noted, if even a relatively short history is kept, a brute force method would entail a search of 2<sup>8192</sup> possibilities. Genetic algorithms offer an attractive alternative to such a method.

Note that only one approach—an *LRU-FIFO* combination, *history*, etc—is tried at a time. A genetic algorithm tries to find a near optimal strategy within that one approach. However, for each approach, the same basic method is used to find a good replacement strategy:

- 1. Generate a random population of strategies (strings) for the approach (LRU-FIFO, history, etc).

- 2. For each string in the population, perform a cache trace simulation using a particular benchmark or set of benchmarks.

- 3. During each simulation, use the string to determine which line to replace when a cache miss occurs.

- 4. After each simulation, record the line hit rate or some other performance measure for the string.

- 5. Calculate the fitness of the string as a nonlinear function of the performance measure.

- 6. After a simulation has been performed for each string, use reproduction, crossover, and mutation to generate a new generation of strategies based on these fitnesses.

- 7. Goto step 2.

### 4.2 Example

To make this more concrete, consider an example using the history method. Let the cache have K = 4-way associativity and keep a history of m = 1 previous accesses. This requires

$$B = 2 \times 2^{1 \times [1 + \log_2(4)]} = 16 \text{ bits}$$

for each strategy string. More intuitively

- The history of the previous access is recorded in 3 bits,  $Hist = B_2B_1B_0$ . The 3 bits refer to the line referenced (2 bits) and whether the access was a hit or a miss (1 bit).

- The strategy must indicate which line to replace on a miss for each of the  $2^3 = 8$  possible histories.

- 4-way associativity  $\Rightarrow$  2 bits to specify the line to be replaced.

- Since 8 lines must be specified,  $8 \times 2 = 16$  bits are required for each strategy string.

Several additional assumptions are required:

- Let  $B_2 = 1$  for a hit, 0 for a miss.

- Let  $B_1B_0$  specify the line to be replaced.

- Let the Strategy string S under consideration be

S can be viewed as an array of 8, 2-bit elements, one for each possible history. Each element specifies which line to replace for a given history.

### CHAPTER 4. GENETIC ALGORITHMS APPLIED TO CACHE REPLACEMENT 20

• Assume Hist = 101 and there is a miss.

The history method then works as follows

- The line replaced is that specified by the  $B_2B_1B_0 = 101_2 = 5th$  pair in the strategy,  $10_2 = 2$ .

- Thus the new Hist = 010: a miss occurred and line 2 was replaced.

- Next assume there is a hit to line 0 of the set.

- Therefore the new Hist = 100.

The string S is used in this manner for the entire address trace, i.e. based on the past history of accesses to a set, S indicates which line should be replaced when a miss to that set occurs. When the simulation finishes with the address trace, the performance of S is noted. Then the same procedure is repeated for the rest of the strings in the population. Finally after the performance of all strings has been measured, the reproduction, crossover, and mutation operators are applied in an attempt to produce a new and hopefully improved generation. This process continues, generation after generation until each generation performs approximately as well as its predecessor. (There is no hard and fast rule for determining when this convergence has occurred [21].)

Clearly the choice of address trace is critical to this process. (The address trace corresponds to some benchmark program or programs.) Some strings perform well with some programs, others with different programs. One goal is find a single string which performs well, although perhaps never optimally for a wide variety of traces. Well might be defined as better than LRU.

Alternatively the replacement string could be dynamically specified to the cache. This would allow different applications to use different replacement policies. Such an approach raises the question: how does the application know what is a good replacement policy? One way is to generate an address trace from the application and use the complete genetic algorithm procedure described above. Another possibility is for the compiler to use heuristics to specify the strategy. For example a large number of deeply nested loops might suggest

one replacement strategy, and recursion another. Using this approach it might even be possible for each subroutine or procedure to specify its own replacement strategy.

A third alternative would be for the cache itself to recognize certain access patterns. Upon recognizing a pattern, the cache would use a corresponding replacement strategy. Patterns would probably have to be relatively simple in order that the cache could recognize them in real time. (For example, the full blown genetic algorithm approach described above is clearly too complex for a cache to perform in real time.)

### 4.3 Combination Approaches

In addition to LRU-FIFO, several "combination" approaches are possible. Those combination approaches implemented here are listed below along with number of bits they require in each strategy string. The computation of the number of bits is similar to that described above for history. Note that in all cases the number of bits B is a multiple of  $log_2(K)$ , since  $log_2(K)$  bits are needed to specify which line is to be replaced.

1. Combination of LRU and FIFO information (LRU-FIFO). In this case the replacement algorithm must know the FIFO rank of each LRU line. (In this document the term, "LRU line" is sometimes used to mean a line's rank from most recently used to least recently used. In such cases it does not mean literally the least recently used line. Context should make clear whether this or the literal meaning is intended.)

However most LRU to FIFO mappings are impossible. LRU lines 1 and 2 cannot both correspond to FIFO line 4. For example the following mapping is legal:

1 -> 4

2 -> 2

3 -> 3

4 -> 1

While this is not:

1 -> 4

2 -> 4

3 -> 3

4 -> 1

Formally the LRU to FIFO mapping must be 1:1, i.e. each LRU line must correspond to a single FIFO line and no other LRU line may correspond to that same FIFO line.

There are K! ways the LRU ordering can map to the FIFO order. Hence  $B = K! \log_2(K)$ . This produces relatively short strings. For example, if K = 4, then B = 48 bits.

A more brute force method could be used in which an explicit LRU to FIFO table is maintained. This table would have K entries each of  $log_2K$  bits or  $Klog_2K$  bits total. In this method  $B = 2^{Klog_2K}log_2(K) = K^Klog_2(K)$ . Using the same example with K = 4 yields a far larger B = 512 bits.

- 2. Combination of LRU and a c-bit count of hits to each line (LRU-Count). Note that the count must stop incrementing when it reaches  $2^c 1$ . Here cK bits are required to record the number of hits for all the lines, and hence there are  $2^{cK}$  possible combinations of hits and lines. Thus  $B = 2^{cK} \log_2(K)$ . This produces strings of intermediate length. For example, if K = 4 and C = 2, then C = 512 bits.

- 3. Combination of LRU and an h-bit history (hit/miss) of accesses to each set (LRU-History). With an h-bit history, there are  $2^h$  possible histories, so  $B = 2^h log_2(K)$ . This produces short strings. If K = 4 and h = 4, then B = 32 bits.

- 4. Combination of FIFO and a c-bit count of hits to each line (FIFO-Count). The analysis is the same as with LRU and a c-bit count, hence  $B = 2^{cK} log_2(K)$ . If K = 4 and c = 2, then B = 512 bits.

- 5. Combination of FIFO and an h-bit history (hit/miss) of accesses to each set (FIFO-History). The analysis is the same as with LRU and an h-bit history, hence  $B = 2^h log_2(K)$ . If K = 4 and h = 4, then B = 32 bits.

### 4.4 Hardware Implementation

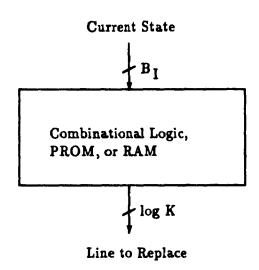

The amount of space and time required for the approaches described is generally small. Each method requires combinational logic, PROM, or RAM to encode the string corresponding to the replacement policy. When a cache miss occurs, the function must produce the  $log_2K$  bit value of the line to replace, where as usual K is the cache associativity, and is typically less than or equal to 4 [36]. Different replacement functions require different input: history requires a record of hits, misses, and lines accessed while LRU-FIFO requires the mapping from LRU to FIFO. Let the replacement strategy be a function of  $B_I$  bits. Note  $B_I$  is different than B, the number of bits in a strategy string. However, the two are related:

$$B_I = \left\lceil log_2\left(\frac{B}{log_2(K)}\right)\right\rceil$$

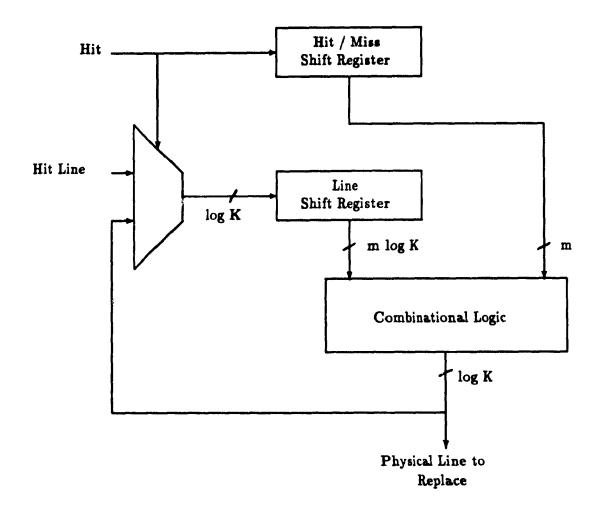

A block diagram of the cache replacement hardware is in Figure 4.1.

A more detailed hardware description for each method is given below. Note that standard cache hardware is not covered, instead only what is unusual or extra for these methods is discussed.

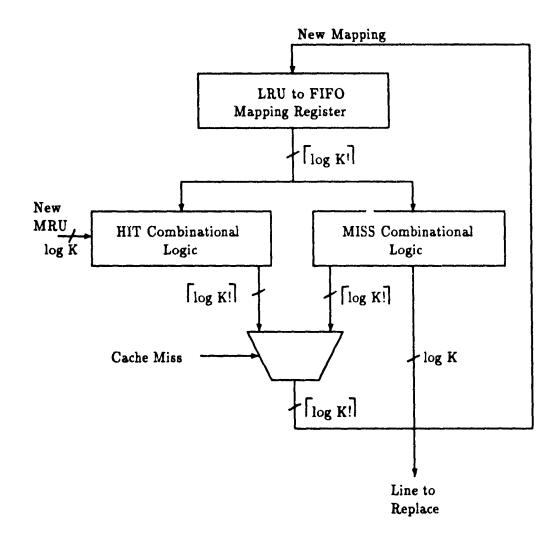

#### 1. LRU-FIFO.

$B_I = \lceil log_2 K! \rceil$ . If K = 4, then  $B_I = 5$  bits. Note that the brute force approach would require  $B_I = K log_2 K$  bits.

To implement this, the LRU to FIFO mapping must be updated whenever a set is referenced. A block diagram of this is shown in Figure 4.2. The mapping must be updated differently depending on whether the reference results in a hit or a miss. This hit logic must also know which line is the new MRU. For the miss logic, the new MRU is just the replaced line. The replacement line specified on a miss is not a physical line in the set, but instead the LRU ranking of the line to be replaced—for example, replace the 2nd least recently used line. Hence a second translation would be necessary to obtain the physical cache line.

Figure 4.1: Block Diagram of Cache Miss Hardware.

The combinational logic in Figure 4.2 could equally well be PROM or RAM as previously noted. All sets could share a single copy of the combinational logic portion of the mapping hardware. Each set must however, maintain the register which maps LRU lines to FIFO lines.

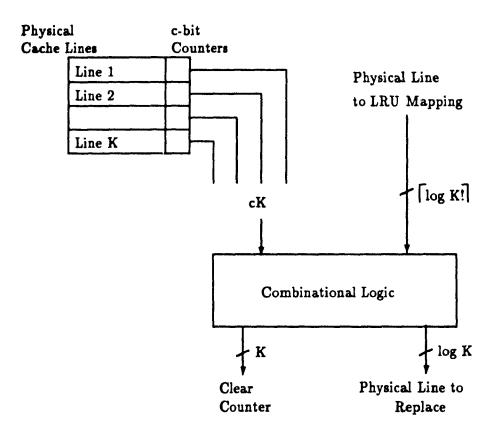

#### 2. LRU-Count or FIFO-Count.

$B_I = cK$ . If K = 4 and c = 2,  $B_I = 8$  bits. The c-bit counter must be updated whenever there is a hit to the line. The counter must also stop when the count reaches its maximum and be resettable to 0 when the line corresponding to it, is replaced. Unlike LRU-FIFO, the actual physical line to be replaced is output from the combinational logic. This is because the combinational logic requires the LRU to physical line mapping in order to determine which LRU line to associate with each c-bit counter. Since the logic already has the physical mapping it makes use of it by providing the physical line as output. A block diagram of the circuitry required on a miss is shown in Figure 4.3. On a hit, all that is required is a demultiplexer to map the line with the hit to an increment signal for that line's counter.

#### 3. LRU-History or FIFO-History.

Figure 4.2: Hardware for LRU-FIFO Method.

Figure 4.3: Hardware for LRU-Count Method on Misses.

$B_I = h$ . If h = 4, then  $B_I = 4$  bits. This method is particularly simple on both hits and misses: on a miss, a 0 is shifted into an h-bit shift register, while on a hit a 1 is shifted in. A simple function of h bits specifies which line to replace on a miss. In this case the LRU ranking of the line is specified and must be mapped to the physical line.

#### 4. History.

$B_I = m(1 + log_2K)$ . If K = 4 and m = 4,  $B_I = 12$  bits. Recall that at the start of this chapter, it was stated that the complexity of the history method can be significantly reduced. Unfortunately the simplification applies only to genetic algorithms searching for a good replacement strategy, not to the hardware implementation.

The simplification uses the fact that many histories are actually equivalent. To make use of that here would require a three step process. 1) Reduce to the equivalent form, 2) Determine line to replace, and 3) Tranlate the equivalent replacement line to the actual replacement line. This is almost certainly more complicated than implementing the function directly. For more details see Section 5.4.1.

The implementation is simple and similar to LRU-History. Each time a hit occurs to a line, this information is shifted into a  $1 + log_2K$  bit wide shift register—the extra "1" is for the hit/miss information. Likewise when a line is replaced on a miss, the line number and miss bit are shifted into the shift register. This is depicted in Figure 4.4. Since this method manipulates lines directly without the need of correlating LRU or FIFO information, the line specified for replacement is the physical line.

As can be seen the time required for these methods is also generally small. Actually there are two separate times, the time for a cache hit and the time for a cache miss. The cache hit time is most important because most accesses are hits. Most cache studies find hit rates well over 80% and often greater than 90% [36] [1] [3] [11]. As was seen the methods proposed here require little time on a hit: generally a counter must be incremented or a shift register updated. LRU-FIFO is the most complicated. Miss time is generally small too, consisting of the combinational logic or PROM delay to find which line should be replaced plus time to clear a counter or update a shift register.

Figure 4.4: Hardware for History Method.

# Chapter 5

# **Simulations**

## 5.1 Methodology and Details

The cache simulator used in this work was developed by R.A. Olsen, a student in the McGill Advanced Computer Architecture and Program Structures (ACAPS) Group [32]. The simulator has been extensively modified and supplemented by the author. The genetic algorithm portion of the simulator follows the outline presented in [21].

All code was written in the C language. The source contains over 9000 lines of code, while the optimized executable SPARC version has a text size of 81920 bytes.

Traces from six benchmark programs have been used throughout <sup>1</sup>. The benchmarks are drawn from a variety of applications, some numerically intensive, others not. The six benchmarks are:

1. ccal† (PASCAL): Simulates a simple pocket calculator.

<sup>&</sup>lt;sup>1</sup>All simulations were run on Sun-4 SPARC (tm) architectures. The time to complete an individual simulation (one benchmark and one genetic algorithm approach) was typically 30 minutes to 6 hours depending on the parameters used.

- 2. emacs (): The common text editor program.

- 3. kalman (FORTRAN): A kalman filter routine.

- 4. mcsh (): The "Mouse" shell, an enhanced emacs-like UNIX c-shell.

- 5. polyt (FORTRAN): Symbolic polynomial manipulation.

- 6. whetstone† (FORTRAN): The standard floating point benchmark program.

Items with a † are benchmarks distributed by Stanford University with their Architect's Workbench program.

The traces correspond to execution of the benchmarks on a SPARC architecture. Benchmarks were first compiled using standard UNIX C, FORTRAN, and PASCAL compilers. Traces were then collected by simulating program execution on a SPARC architectural simulator developed by Sun Microsystems.

The ccal, kalman, poly, and whetstone traces correspond to complete program execution. The other two, emacs and mcsh correspond to start of program execution. All traces are relatively small by modern standards, ranging up to a few hundred thousand addresses at most. However, the number and duration of the simulations required that the length of traces be kept relatively low. The exact number of addresses and number of unique addresses are given in Table 5.1. Note that in the Table the sum of instruction addresses and data addresses is slightly less than the number of combined addresses. This is because the traces also contain a small number of system traps which are not considered to be in either category.

All results given here refer to separate instruction and data caches of 512 byte caches each, and both with 4-way associativity. The use of separate instruction and data caches is in keeping with most modern architectures, for example the 68040 [15], the R6000 [28], the NS32532 [30], the Clipper [25], and the i860 [23].

The choice of 4-way associativity reflects the maximum value used in most modern caches [36]. Use of an associativity less than 4 minimizes the effect of the replacement policy. With an associativity of 1 (direct-mapped), there is no choice for the replacement policy, and for an associativity of 2 or 3, the choice of lines to replace is limited.

|           | INSTRU | CTION         | DAT    | ГА    | COMBINED     |        |

|-----------|--------|---------------|--------|-------|--------------|--------|

|           | Unique | Total         | Unique | Total | Unique       | Total  |

| CCAL      | 4721   | 53570         | 880    | 15128 | 5602         | 68803  |

| EMACS     | 8525   | 205936        | 7195   | 50982 | 15721        | 256973 |

| KALMAN    | 6258   | <b>7399</b> 0 | 2085   | 17076 | 8344         | 91261  |

| MCSH      | 2050   | 309929        | 2618   | 78024 | 4669         | 388012 |

| POLY      | 4913   | 42679         | 2266   | 11975 | 7180         | 54835  |

| WHETSTONE | 2154   | 14046         | 1530   | 3811  | <b>3</b> 685 | 17914  |

Table 5.1: Number of Total Addresses and Number of Unique Addresses in Each Benchmark.

A 512 byte cache is quite small for modern processors, even for an onchip cache. This small size was chosen in order to emphasize the effect of the replacement policy. Using a larger (but still relatively small) 4K cache, results in little difference in hit rates between different replacement policies. Using a 512 byte cache results in overall hit rates of between 85% and 95% for most benchmarks and replacement policies. Table 5.2 gives overall hit rates for caches with 32 byte lines. Table 5.3 gives the corresponding line hit rates.

The results from two types of approaches are presented. First are results where a genetic algorithm approach was used to find a good strategy for each benchmark individually. This is useful for a cache with a small RAM containing the replacement strategy. The operating system could load this RAM with the appropriate strategy whenever the program is run. This approach is also useful in providing a rough upper bound on how well the second approach can do.

The second approach provides results from using a genetic algorithm to find a good strategy for a group of benchmarks. If these benchmarks represent a "typical" workload, then the best strategy can be hardcoded into combinational logic or a PROM in the cache.

The replacement policies simulated, LRU-FIFO, LRU-Count, LRU-History, FIFO-Count, FIFO-History, and History are as described in Chapter 4, with the exception of History.

As described in Chapter 4, the History method maintained for each set a record of lines

|           | L    | nstructio | n    | Data |      |      |  |

|-----------|------|-----------|------|------|------|------|--|

|           | LRU  | FIFO      | OPT  | LRU  | FIFO | OPT  |  |

| CCAL      | 88.8 | 88.8      | 91.0 | 89.6 | 88.4 | 92.1 |  |

| EMACS     | 95.0 | 95.0      | 95.9 | 94.3 | 93.7 | 95.4 |  |

| KALMAN    | 87.4 | 87.3      | 90.3 | 85.7 | 84.4 | 88.9 |  |

| MCSH      | 92.3 | 92.1      | 95.5 | 94.1 | 92.7 | 95.6 |  |

| POLY      | 90.7 | 90.6      | 92.7 | 85.5 | 84.3 | 88.1 |  |

| WHETSTONE | 91.5 | 91.2      | 93.8 | 82.6 | 82.3 | 85.0 |  |

| Mean      | 91.0 | 90.8      | 93.2 | 88.6 | 87.6 | 90.9 |  |

| SUITE     | 92.2 | 92.1      | 94.5 | 92.1 | 91.0 | 93.8 |  |

Table 5.2: Overall Hit Rates for 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines.

|           | Iı   | nstructio | n    | Data |              |      |  |

|-----------|------|-----------|------|------|--------------|------|--|

|           | LRU  | FIFO      | OPT  | LRU  | FIFO         | OPT  |  |

| CCAL      | 29.4 | 29.2      | 43.2 | 67.7 | 64.0         | 75.6 |  |

| EMACS     | 22.6 | 22.5      | 36.5 | 69.3 | 66.0         | 75.2 |  |

| KALMAN    | 30.8 | 30.2      | 46.7 | 61.3 | 57.6         | 69.9 |  |

| MCSH      | 56.6 | 55.7      | 74.8 | 83.3 | 79.4         | 87.5 |  |

| POLY      | 29.6 | 28.5      | 44.5 | 56.4 | 52.8         | 64.1 |  |

| WHETSTONE | 30.1 | 27.5      | 49.0 | 36.3 | <b>3</b> 5.0 | 45.2 |  |

| Mean      | 33.2 | 32.3      | 49.1 | 62.4 | 59.1         | 69.6 |  |

| SUITE     | 43.9 | 43.2      | 60.5 | 73.7 | 70.1         | 79.5 |  |

Table 5.3: Line Hit Rates for 512 byte Instruction and Data caches with 4-way associativity, 32 byte lines.

accessed and hits/misses. Except in Section 5.4.3, the History simulations in this Chapter maintain no hit/miss information.

There are several reasons for this. Common replacement methods such as LRU and FIFO maintain information about lines, i.e. recency of line use and order of line entry into the set respectively. No information is maintained about hits/misses. Thus keeping no hit/miss information makes *History* in some sense more comparable to LRU and FIFO. Excluding hit/miss information also makes the length of *History* strings 30 bits instead of 480 bits. 30 bits is more comparable to the other methods which generally have string lengths from 32 to 48 bits.

Additional justification for excluding hit/miss information is given in Sections 5.4.2 and 5.4.3. Section 5.4.3 also investigates the effect of excluding the hit/miss information.

The genetic algorithm techniques employed here are quite simple, employing only the basic techniques outlined in Chapter 3. Other techniques are widely used. Population size can be allowed to vary between generations, overlap between generations can be allowed, crossover can be done between deterministically chosen pairs instead of randomly chosen pairs—the best performing pairs would generally be crossed in this case. Techniques can also be used to promote diversity, particularly early in the simulation when the danger of finding a poor local optima is highest. Simulation of dominant and recessive genes can also be used. More sophisticated forms of crossover such as PMX (Partially Matched Crossover) could also be employed. These additional techniques were not employed primarily for four reasons:

- The duration of the simulations is already quite lengthy and the memory requirements

quite large. This additional overhead would make the simulations prohibitively long

and large.

- 2. The time required to write software and simulate all of these additional techniques was judged to be excessive for the scope of this work.

- 3. The fundamental operators provide a sufficient basis on which to test the concept of applying genetic algorithms to cache replacement policy.

- 4. Many of the enhancements seem unlikely to produce significantly better results. For example, consider PMX. In all discussion thus far, it has been assumed that the

position of a group of bits in a string determines the function of those bits. However, this need not be the case, and is not in nature. If a gene is moved to a different location on a chromosome it will continue to perform the same function. PMX and related techniques allow this capability to be added to genetic algorithms.

Bit location is important. Bits which are highly correlated in function may be widely separated in the string. In order to obtain the full benefit of crossover and its effect of finding good, small schemata, the string must use a representation in which related bits are grouped closely together.

PMX is essentially a more complicated form of crossover [12], that makes a bit's function independent of its position. It attempts to find natural groupings of bits in addition to finding good values for the bits. In this work, some effort was made to manually find representations in which correlated bits are grouped together. In most cases, natural representations appear to group bits reasonably well. For example, in the LRU-Count method, bits representing what to do when the least recently used line has been accessed 1 or 2 times are grouped adjacently. Given this natural grouping (and the added time and space requirements for adding position independence), it was decided not to implement position independence. However this might be an interesting area for further study.

Nonetheless some of the advanced techniques described above could prove useful in extending this work. For example, dominant and recessive genes are useful when the environment changes over time. Some criteria may be important at some time, then cease to be so, and later become important again. Recessive genes provide a natural way of storing useful information, even in generations where it is not needed [21].

For cache replacement algorithms, recession and dominance could be useful in the following procedure.

- 1. Simulate the first benchmark program for a "few" generations.

- 2. Take the population of strategies from the last generation of the previous benchmark and use them as the initial population in simulating the next benchmark for a "few" generations.

- 3. Repeat Step 2. until the last benchmark is reached, then go to Step 1.

Although this procedure is reasonable without employing recession and dominance, using them could improve performance. This is because certain criteria might be very important in some benchmarks, but not important in others. These criteria would have a good chance of being preserved in recessive genes, but might be lost otherwise. This might make an interesting area for further study.

### 5.2 Line Hit Rate

Much of the discussion here also applies to Section 5.3, Opt Match Rate. Here the goal is to maximize the line hit rate. (Recall from Chapter 2 that maximizing the line hit rate also maximizes the overall hit rate.) In Section 5.3, the goal is to maximize the fraction of misses in which the replacement algorithm replaces the same line OPT would have. In particular, much of the Parameters Section below applies equally to the Section on OPT Match Rate.

### 5.2.1 Parameters

As discussed in Chapter 3, there are four major genetic algorithm parameters in addition to the many cache parameters. To try all possible reasonable combinations of these would result in simulations taking billions of years, even for these six small benchmarks. Hence only a few variations are presented here, along with discussion on the effect of altering the values selected for the parameters.

The four basic genetic algorithm parameters are

- The probability of crossover

- The probability of mutation (or mutation rate)

- The population size

- The number of generations

In addition to these four parameters, there is an additional important "parameter" which is hard-coded into the simulator. This is the objective function. The objective function takes the metric used to measure the performance of a string, such as the line hit rate, and returns some (usually nonlinear) function of it. The value of the objective function probabilistically determines the relative number of the string that will be reproduced in the next generation.

Here the objective function used was  $2^{lane\ hit\ rate}$ . Hence if string, A has a 1% better line hit rate than string B, then approximately twice as many of A will usually be produced in the next generation as are produced of B. Since the simulation uses a fixed finite population, strings with low line hit rates will likely not be reproduced at all in the next generation.

Less steep objective functions, such as line hit rate<sup>10</sup>, were tried, but reproduced too many poor strings, resulting in slow improvement from generation to generation. Steeper objective functions have the opposite problem and tend to lose needed population diversity. The result is that they often converge at relatively poor local optima.

Returning to the four "major" parameters, the probability of crossover was always 0.6 in these simulations. This value has been found to be suitable for a wide range of applications by other researchers [14].

A very important parameter in obtaining good results in this study is the mutation rate. Recall from Chapter 3 that the mutation rate is the probability that a single bit will change its value. Two values of mutation rate were used in this study, 1% and 10%. Figures 5.1 and 5.2 compare the performance of *LRU-FIFO* using a 1% mutation rate and a 10% mutation rate. As can be seen, a mutation rate of 10% generally provides superior results to a mutation rate of 1%.