# Rapid System Prototyping for Error-Control Coding in Optical CDMA Networks

Martin Irman

Department of Electrical and Computer Engineering

McGill University

Montreal, Canada

August 2005

Library and Archives Canada

Branch

Published Heritage Di

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-24969-7 Our file Notre référence ISBN: 978-0-494-24969-7

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### Abstract

With increasing bandwidth requirements of individual users, fibre-to-the-home systems are promising candidates for last mile communication. In case of local area networks, optical CDMA with nonorthogonal spreading sequences has emerged as an attractive technology that can manage quickly varying user requirements, while enabling total bandwidth utilization, avoiding network congestion and preventing denial of service. However, powerful error-control codes have to be utilized within optical CDMA systems to prevent errors caused by multiuser interference. Due to data rates common in optical communication, dedicated hardware is required to run such error-control codes at very high speeds, e.g., 155 Mbps or 652 Mbps.

This work presents a rapid system prototyping platform for error-control codes which are to be incorporated into the above mentioned optical CDMA systems. The platform consists of a design methodology, an extensive library of modules and an environment for testing designed specifically for optical CDMA systems but applicable to other communication systems as well. It is built on System Generator from Xilinx, a Matlab/Simulink based visual design tool, and enables a "push of a button" transition from code specification to real-time implementation on an FPGA chip.

Initially, both the hardware specifics of this platform and the details of the developed modular design methodology are presented. Consequently, implementation of a custom design construct (a *Generate* block) and a library of communication system modules are described together with blocks and methodology for testing the developed algorithms. Finally, design and evaluation of three different communication systems are presented. These designs show that the platform can be used for prototyping and evaluation of error-control algorithms running at the required processing speeds mentioned above.

### Sommaire

En réponse à une demande croissante de vitesse de chargement pour les individus, les systèmes « fibre optique jusqu'au domicile » sont de candidats intéressants pour les communications de dernier kilomètre. Dans le cas de réseaux locaux, l'accès multiple par répartition en code (AMRC) optique avec séquences de codes non orthogonales s'est démontré être une solution intéressante, qui entre outre s'adapte au va et viens des utilisateurs tout en maintenant l'utilisation totale de la bande passante et en évitant la congestion du réseau et le refus de service.

Cependant, des codes de correction d'erreur puissants doivent faire partie du système d'AMRC optique afin d'en éliminer les erreurs dues à l'interférence entre les utilisateurs. Comme ces codes présentent de très hauts débits, le matériel qui leur est dédié devra fonctionner à très grande vitesse, par exemple 155 Mbps ou 652 Mbps.

Cette dissertation présente une plateforme de développement de prototype rapide pour les codes de correction d'erreurs incorporés dans les systèmes AMRC décrits ci-haut. Cette plateforme consiste d'une méthodologie de conception, une librairie de modules extensive et un environnement permettant la validation des prototypes conçu spécifiquement pour les systèmes d'AMRC optiques mais applicable à d'autres systèmes de communication aussi bien. Cette plateforme est créée à l'aide de System Generator de Xilinx, un outil basé sur Matlab/Simulink, permet la transformation automatique de spécifications codées implémentation temps réel sur un réseau prédiffusé programmable par l'utilisateur. En premier lieu, nous présentons les détails du matériel spécifique à cette plateforme et la méthodologie de conception que nous lui associons. Ensuite, l'implémentation d'un bloc de génération automatique et une librairie de modules de communication sont décrites, ainsi que les blocs et la méthodologie utilisés pour la validation des algorithmes.

Finalement, la conception et l'évaluation de trois systèmes de communication sont présentées. Nous démontrons que cette plateforme peut être utilisée pour créer des prototypes et évaluer des algorithmes de correction d'erreurs aux vitesses mentionnées ci-haut.

# Acknowledgements

I would like to express my gratitude to my advisor, Professor Jan Bajcsy, for his patience, valuable insights and extensive feedback. His support and guidance made my stay here at McGill University pleasant and enriching. Working on hardware design and coding has been a truly great experience and I am thankful to Professor Jan Bajcsy that he exposed me to this magnificent field.

My special thanks go to my colleagues and friends who helped me in forming the ideas presented in this thesis. Naveen Mysore, Aminata Amadou Garba, Phillip Sawbridge, Isabel Deslauriers, Xu Bo, Samer Lutfi and Mehmet Akçakaya helped create and intellectual environment that always pushed me forward.

Additionally, I would like to acknowledge McGill University, Natural Sciences and Engineering Research Council of Canada, Le Fonds Québécois de la Recherche sur la Nature at les Technologies, Canada Foundation for Innovation and Xilinx Corp. for support during various stages of preparation of this thesis.

Above all, I would like to thank my girlfriend Eva Wang, my father František, my mother Eva and my brother Vladimír for continuous support and encouragement. Without the gentle pressure and encouragement of my girlfriend, this work would be much harder to write. It is to her and my family that I dedicate this thesis.

| 1 | τ |

|---|---|

It is a mistake to think you can solve any major problems just with potatoes.

– Douglas Adams

# Contents

| Chapter | 1     | Introduction                                         | 1  |

|---------|-------|------------------------------------------------------|----|

| 1.1     | Mot   | vation                                               | 1  |

| 1.2     | Impl  | ementing a Flexible Design Platform                  | 3  |

| 1.3     | Proj  | ect Description                                      | 5  |

| 1.4     | Orga  | anization of this Thesis                             | 6  |

| Chapter | 2     | Initial Project Setup                                | 8  |

| 2.1     | Desi  | gn Path Options in Software and Hardware Development | 8  |

| 2.1.1   | l     | Performance of Instruction Based Processors          | 9  |

| 2.1.2   | 2     | Performance of Hardware Solutions                    | 10 |

| 2.2     | Hard  | lware Design Using Programmable Logic                | 11 |

| 2.2.1   | l     | Field Programmable Gate Arrays (FPGA)                | 11 |

| 2.2.2   | 2     | Hardware Design for an FPGA                          | 13 |

| 2.2.3   | 3     | Hardware Design Using a Hardware Description         |    |

|         |       | Language (HDL)                                       | 14 |

| 2.2.4   | 1     | From Hardware Description to Hardware Programming    | 16 |

| 2.2.5   | 5     | Using System Generator in Hardware Design            | 16 |

| 2.3     | Com   | mercially Available Solutions                        | 21 |

| 2.4     | Initi | al Platform Setup                                    | 22 |

| 2.5     | Cha   | pter Summary                                         | 24 |

| Chapter | 3     | Proposed Modular Design Architecture                 | 25 |

| 3.1     | Mod   | ule Data Exchange: Packets                           | 26 |

| 3.1.1   | l     | Packet Structure                                     | 28 |

| 3.1.2   | 2     | Module Structure                                     | 29 |

| 319     | ₹ .   | Module Parameters                                    | 30 |

| 3.2     | Mod  | dule Implementation Methodology                               | 31         |

|---------|------|---------------------------------------------------------------|------------|

| 3.2.    | 1    | Module Internal Structure                                     | 32         |

| 3.2.5   | 2    | Masking a Module                                              | 38         |

| 3.3     | Exa  | mples                                                         | 39         |

| 3.4     | Cha  | pter Summary                                                  | 40         |

| Chapter | 4    | Developed Generate Block                                      | 41         |

| 4.1     | Gen  | erate Block Introduction                                      | 41         |

| 4.2     | Gen  | erate Block Implementation                                    | 42         |

| 4.2.    | 1    | Automatic Cell Replication                                    | <b>42</b>  |

| 4.2.2   | 2    | Interconnection of Generated Cells                            | <b>43</b>  |

| 4.2.3   | 3    | Contextual Behaviour of Several Generate Blocks               | 14         |

| 4.2.4   | 4    | Implementation of the Generate Block                          | <b>46</b>  |

| 4.3     | Desi | ign with the Implemented Generate Block                       | <b>4</b> 8 |

| 4.3.    | 1    | Multiple Generate Blocks                                      | <b>1</b> 8 |

| 4.3.2   | 2    | Nesting of Generate Blocks                                    | <b>1</b> 8 |

| 4.3.3   | 3    | Structured Interconnect                                       | 19         |

| 4.4     | An   | Example Using the Generate Block                              | 51         |

| 4.5     | Cha  | pter Summary                                                  | 53         |

| Chapter | 5    | Implemented Prototyping Platform                              | 54         |

| 5.1     | Imp  | lemented Functional Modules Library                           | 55         |

| 5.1.1   | l    | Data Conversion and Simple Operations Modules                 | 56         |

| 5.1.2   | 2    | Vector Operations and Manipulation Modules                    | 56         |

| 5.1.3   | 3    | Packet Form Editing Modules                                   | 57         |

| 5.1.4   | 1    | Packet Routing and Other Utility Modules                      | 57         |

| 5.1.5   | 5    | Communication Systems Algorithms                              | 58         |

| 5.1.6   | 3    | Building Error Control Modules Using the Functional           |            |

|         |      | Module Library                                                | 59         |

| 5.2     | Imp  | lemented Library of Debugging Blocks                          | 60         |

| 5.2.1   | ĺ    | Communication System Simulation Modules                       | 31         |

| 5.2.2   | 2    | Data Display and Analysis Blocks                              | 32         |

| 5.3     |      | omated Testbed: Blocks and Schemes for Hardware Co-Simulation |            |

| 5.4     | Fun  | ctional Sub-blocks                                            | 64         |

| 5.5     | Chapter Summary                                      | . 66 |

|---------|------------------------------------------------------|------|

| Chapter | 6 Real-time Error Control Schemes                    | 67   |

| 6.1     | Linear Block Code Encoder and Decoder                | .68  |

| 6.1.    | 1 Linear Block Code Encoder                          | 69   |

| 6.1.    | 2 Linear Block Code Decoder                          | 70   |

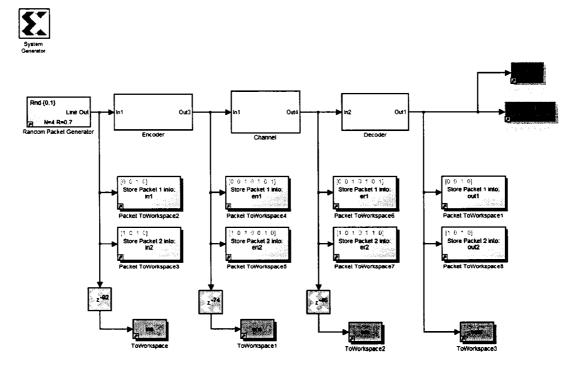

| 6.1.    | Communication System Setup and Testing               | 72   |

| 6.1.    | Performance of Implemented Block Encoder and Decoder | 73   |

| 6.2     | Convolutional Codes Encoder and Decoder              | .74  |

| 6.2.    | Encoding and Decoding of an FSM Encoded Messages     | 75   |

| 6.2.    | Finite State Machine Encoder Implementation          | 79   |

| 6.2.    | 3 Viterbi Decoder                                    | 80   |

| 6.2.    | 4 Communication System Setup and Testing             | 83   |

| 6.2.    | 5 Performance of our Implementation of               |      |

|         | Convolutional Coding                                 | 83   |

| 6.3     | (4,3) <sup>4</sup> Turbo Product Code                | 84   |

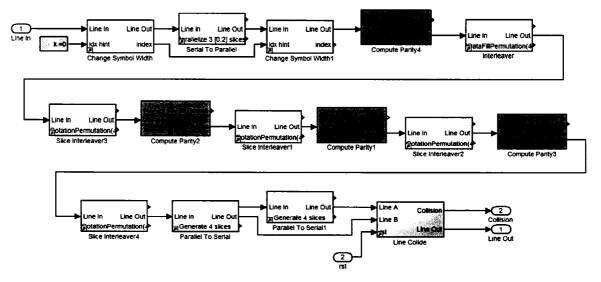

| 6.3.    | Encoder of the Turbo Product Code                    | 85   |

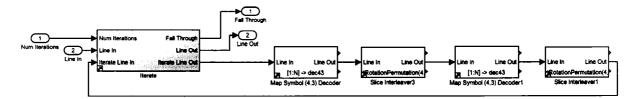

| 6.3.    | 2 Decoder of the Turbo Product Code                  | 85   |

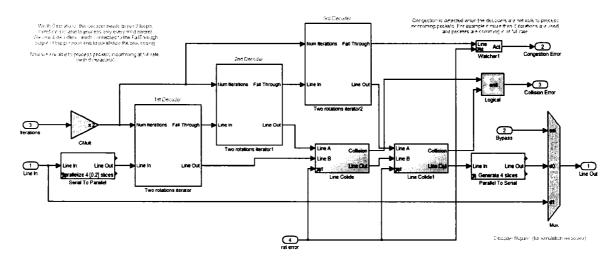

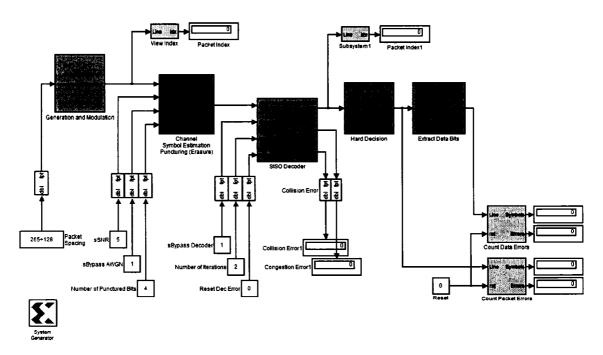

| 6.3.    | 3 Communication System Setup and Testing             | 87   |

| 6.3.    | 4 Performance of our Implementation of a Turbo       |      |

|         | Coded System                                         | 87   |

| 6.4     | Performance of Implemented Codes in OCDMA Network    | 91   |

| 6.5     | Chapter Summary                                      | 92   |

| Chapter | 7 Conclusion                                         | 93   |

| 7.1     | Summary of Research Achievements                     | 93   |

| 7.2     | Future Work                                          | 94   |

| Appendi | x A Workstation Setup                                | 96   |

| A.1     | Introduction                                         | 96   |

| A.2     | Preparing for Hardware Development with Xilinx       | 96   |

| A.3     | Workstation Installation                             | . 97 |

| Appendi | x B Library Reference Manual                         | 99   |

| B.1 U      | Jsing the Library Front-end      | 99  |

|------------|----------------------------------|-----|

|            | Block Reference                  |     |

| B.2.1      | Analyzer Folder                  | 102 |

| B.2.2      | Blocks Folder                    | 105 |

| B.2.3      | CDMA Modules Folder              | 105 |

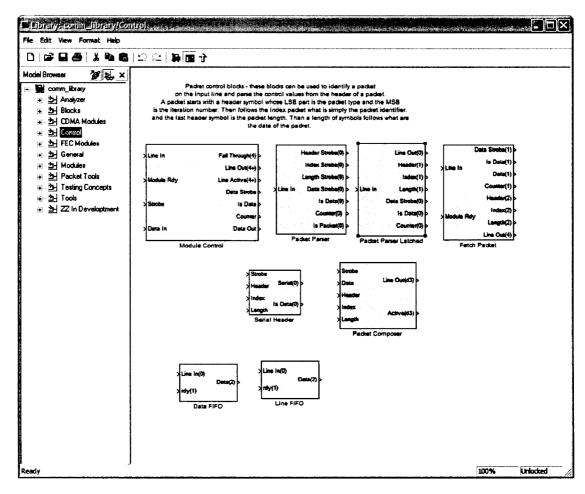

| B.2.4      | Control Folder                   | 106 |

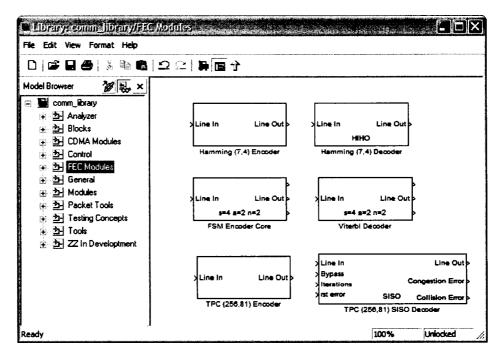

| B.2.5      | FEC Modules Folder               | 110 |

| B.2.6      | General Folder                   | 112 |

| B.2.7      | Modules Folder                   | 114 |

| B.2.8      | Packet Tools Folder              | 120 |

| B.2.9      | Testing Concepts Folder          | 121 |

| B.2.10     | Tools Folder                     | 121 |

| B.2.11     | ZZ in Development Folder         | 123 |

| B.3 N      | Module and Packet Specifications | 123 |

| B.3.1      | Mask Customization               | 127 |

| B.4 L      | ist of Support Matlab functions  | 129 |

| Appendix   | C Designs and Source Code        | 130 |

| References | 3                                | 131 |

# List of Figures

| Figure 1.1: Scheme of an optical CDMA network                                      | 1          |

|------------------------------------------------------------------------------------|------------|

| Figure 1.2: Optical CDMA prototype as a point to point communication system        | ı 2        |

| Figure 2.1: Virtex-II chip configuration                                           | 12         |

| Figure 2.2: VHDL source code example                                               | 15         |

| Figure 2.3: Transforming a Simulink model into System Generator design             | 17         |

| Figure 2.4: Illustration of the concept of signal translation from the floating po | int        |

| domain to fixed point domain using Gateway In and Gateway Out                      | 19         |

| Figure 2.5: The Xtreme DSP Kit development board                                   | 23         |

| Figure 3.1: Schematic block diagram of a digital communication system              | 26         |

| Figure 3.2: Data interface with handshaking                                        | 26         |

| Figure 3.3: Digital communication system as specified                              |            |

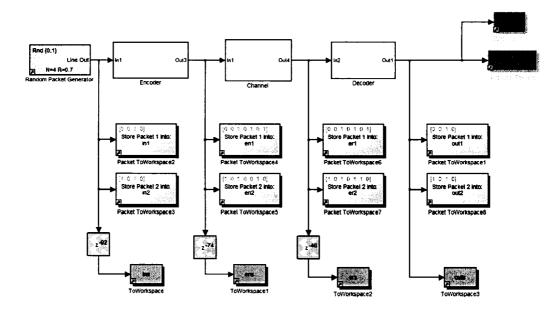

| using our library modules                                                          | 27         |

| Figure 3.4: Data-packet structure                                                  | 27         |

| Figure 3.5: An example of a module                                                 | 28         |

| Figure 3.6: Linking modules                                                        | 29         |

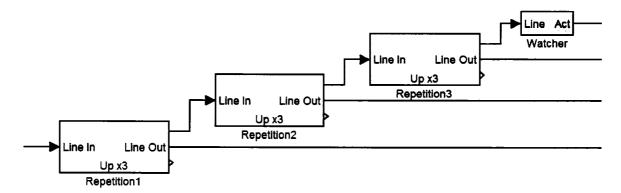

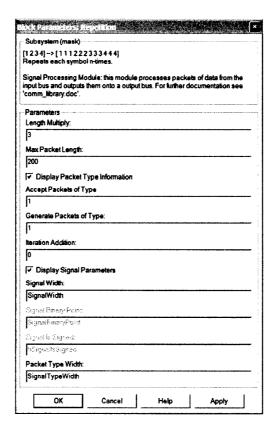

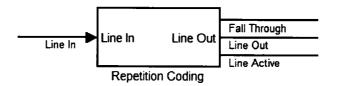

| Figure 3.7: Mask of a Repetition Module                                            | <b>3</b> 0 |

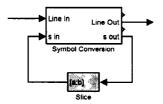

| Figure 3.8: Symbol Conversion module                                               | 32         |

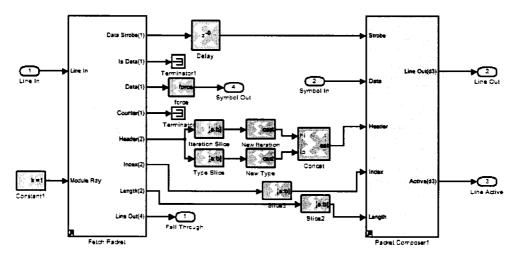

| Figure 3.9: Schematics of the Symbol Conversion module                             | 33         |

| Figure 3.10: Setting the $mask$ of $Fetch\ Packet\ and\ Packet\ Composer\ modules$ | 33         |

| Figure 3.11: Schematics of the FIR Filter module                                   | 35         |

| Figure 3.12: Map Symbol module                                                     | 35         |

| Figure 3.13: Passing parameters to an inner module                                 | 36         |

| Figure 3.14: The mask of the Symbol Conversion module                              | 37         |

| Figure 3.15: Implementing a BSC channel using AWGN channel                         | 38         |

| Figure 3.16: Iteration loop                                                        | 39         |

| Figure 3.17: Parallelizing designs using the FallThrough output                    | <b>4</b> ∩ |

| Figure 4.1: The Generate Block                                                  | 42     |

|---------------------------------------------------------------------------------|--------|

| Figure 4.2: Generic design illustrating the use of the developed Generate block | : . 43 |

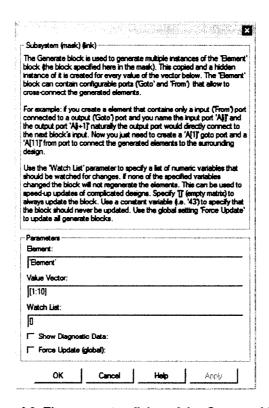

| Figure 4.3: The parameter dialog of the Generate block                          | 45     |

| Figure 4.4: The parameter dialog of a From block                                | 47     |

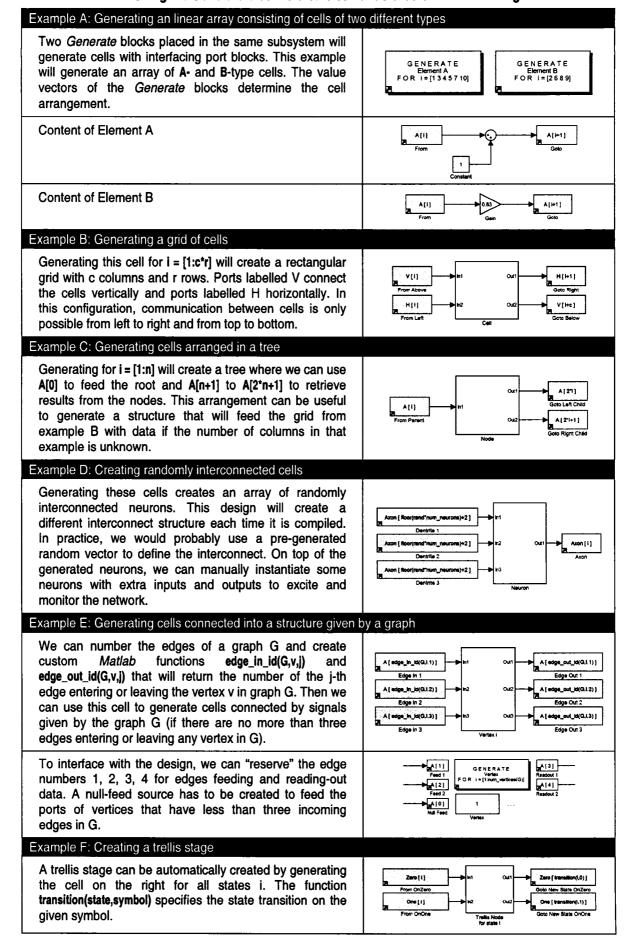

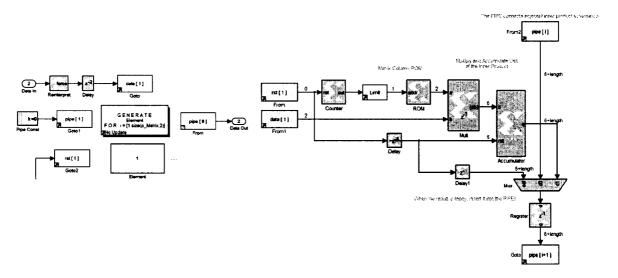

| Figure 4.5: Matrix multiplication module                                        | 52     |

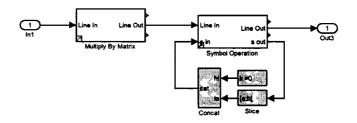

| Figure 5.1: A functional communication system module                            | 55     |

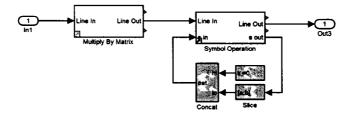

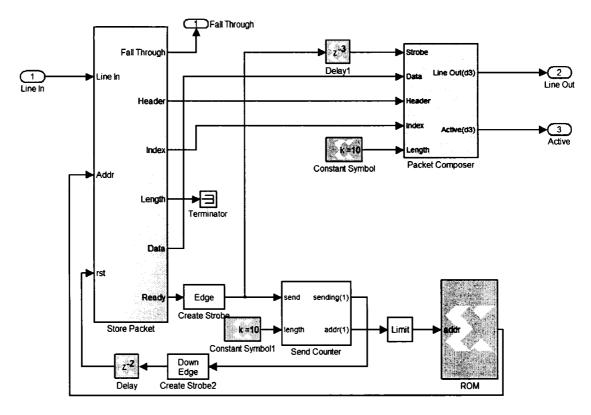

| Figure 5.2: Implementation of the encoder for the Hamming (7,4) code            | 59     |

| Figure 5.3: Implementation of the syndrome decoder for the                      |        |

| Hamming (7,4) code                                                              | 59     |

| Figure 5.4: Testing a system in Simulink simulation                             | 61     |

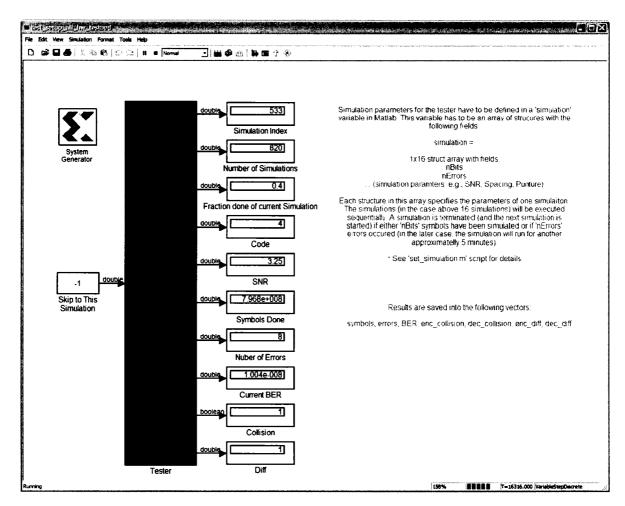

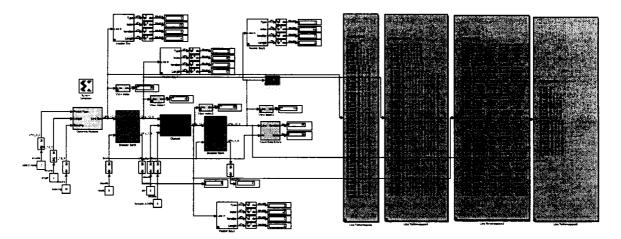

| 5.4 Figure 5.5: Performance testbed front-end Functional Sub-blocks             | 64     |

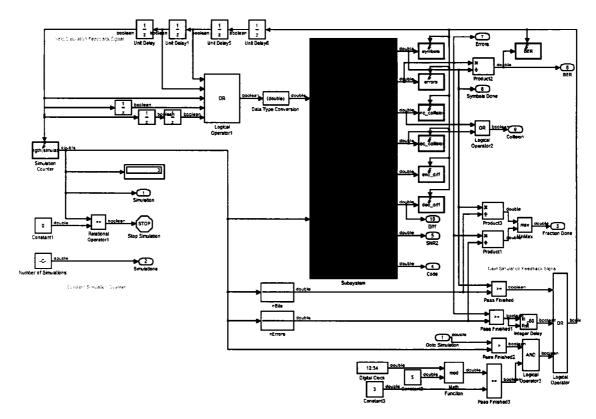

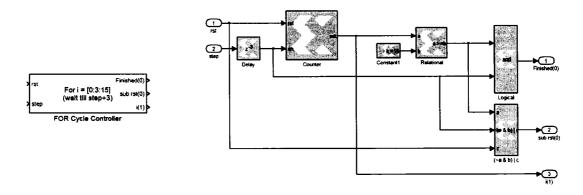

| Figure 5.6: Performance testbed implementation I: Simulation control            | 65     |

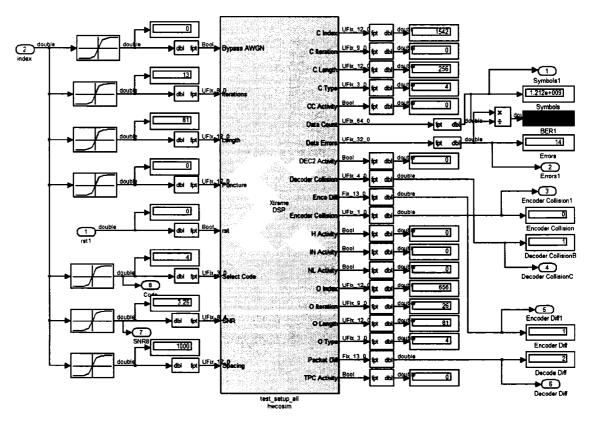

| Figure 5.7: Performance testbed implementation II: Driving the FPGA             | 65     |

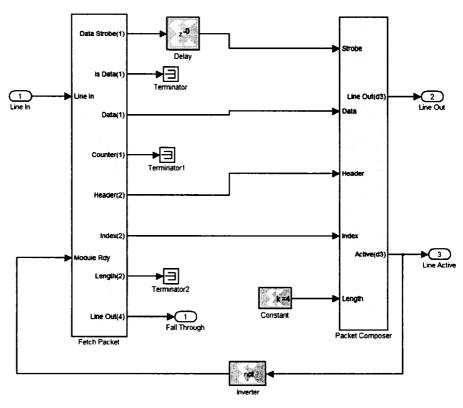

| Figure 5.8: An example of a simple functional sub-block                         | 66     |

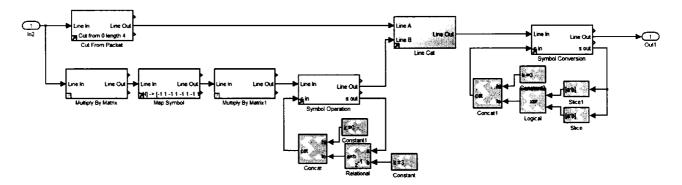

| Figure 6.1: Schematics of the linear block code encoder                         | 69     |

| Figure 6.2: Schematics of the Hamming (7,4) code decoder                        | 70     |

| Figure 6.3: Modulation and channel estimation used for                          |        |

| the Hamming(7,4) scheme                                                         | 72     |

| Figure 6.4: Testing of the Hamming (7,4) scheme in System Generator             | 72     |

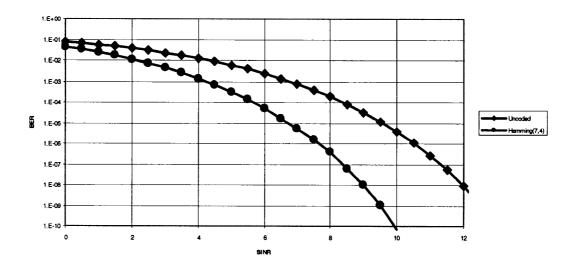

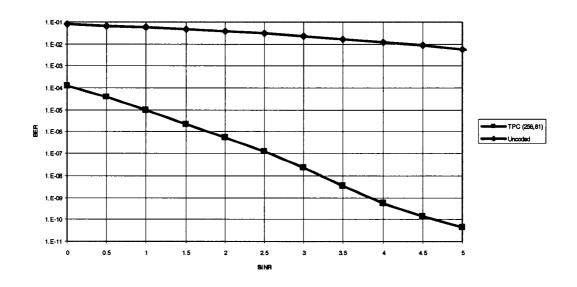

| Figure 6.5: Bit error rate performance of the Hamming (7,4) block code          | 73     |

| Figure 6.6: An example of a simple finite state machine                         | 75     |

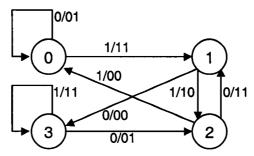

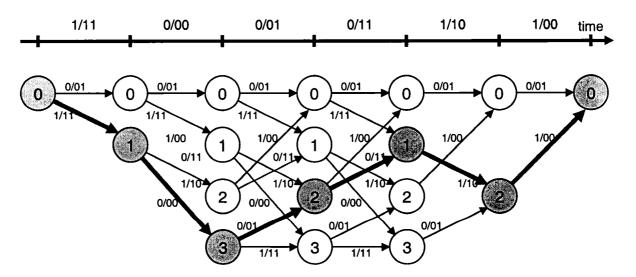

| Figure 6.7: Trellis representation of FSM encoding                              | 76     |

| Figure 6.8: Matlab specification of a finite state machine                      | 77     |

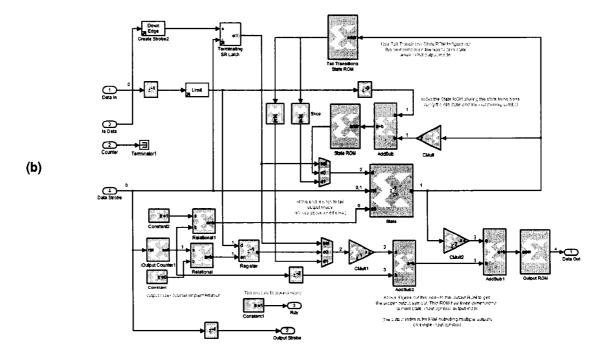

| Figure 6.9: Implementation of the FSM encoder                                   | 78     |

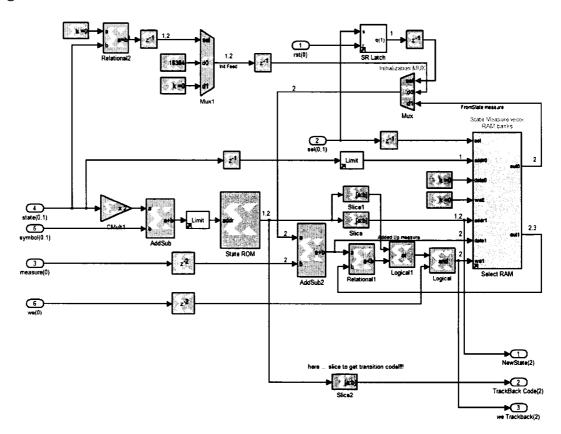

| Figure 6.10: Core of the forward pass of the Viterbi algorithm                  | 81     |

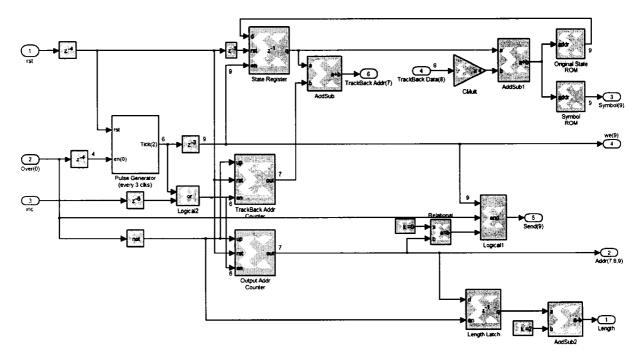

| Figure 6.11: Backwards (track-back) pass of the Viterbi algorithm               | 82     |

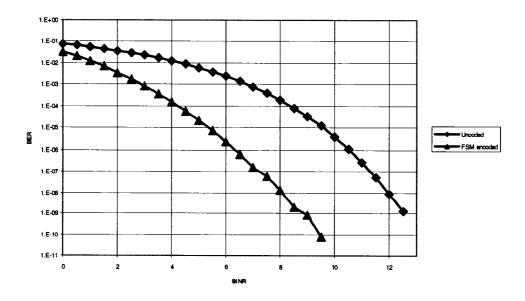

| Figure 6.12: Bit error rate performance of a simple 2 state FSM code            | 83     |

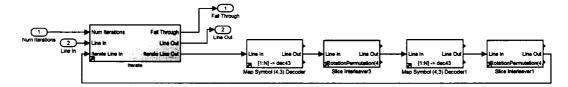

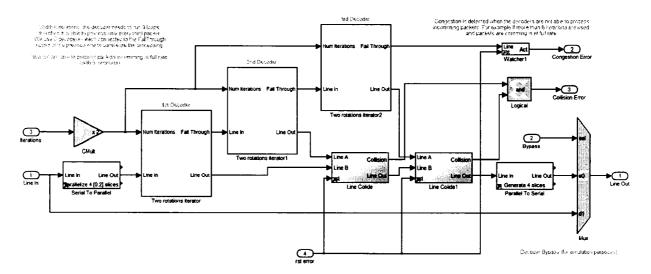

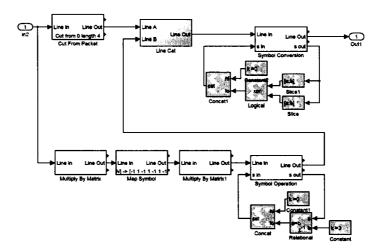

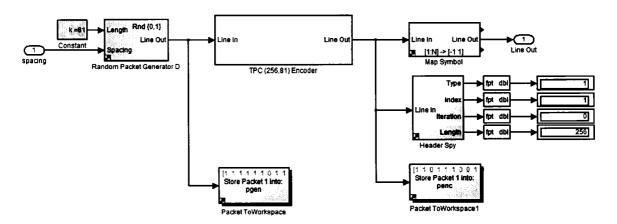

| Figure 6.13: Turbo Product Code encoder implementation                          | 84     |

| Figure 6.14: Iteration loop                                                     | 85     |

| Figure 6.15: The Turbo Product Code decoder                                     | 86     |

| Figure 6.16: Testing setup of the TPC decoder                                   | 87     |

| Figure 6.17: BER performance of our Turbo Product Code implementation           |        |

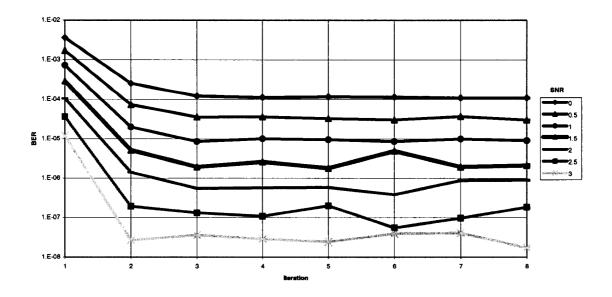

| Figure 6.18: Convergence of the Turbo Product Code                              | 89     |

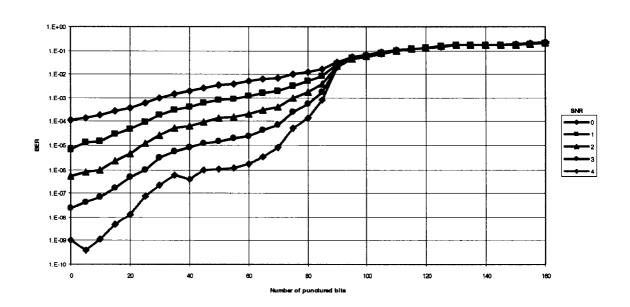

| Figure 6.19: Performance of the Turbo Product Code with puncturing              | 90     |

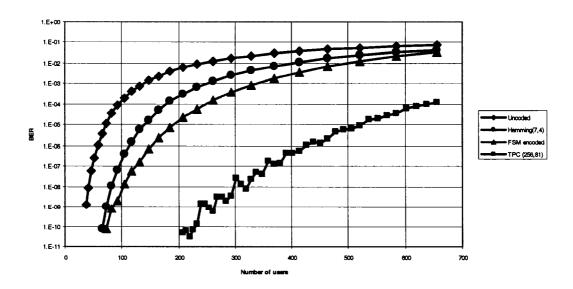

| Figure 6.20: Improvement in the number of active users for OCMA network |

|-------------------------------------------------------------------------|

| transmission based on different error-control codes and the BCDD (41,32 |

| 0.0991) optical spreading code[44], [45]91                              |

| Figure 7.1: Setup of an optical CDMA prototype94                        |

| Figure 7.2: Back-to-back encoder and decoder setup95                    |

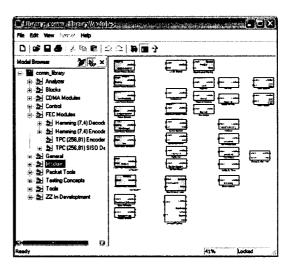

| Figure B.1: A Simulink design window                                    |

| Figure B.2: An open communication library window                        |

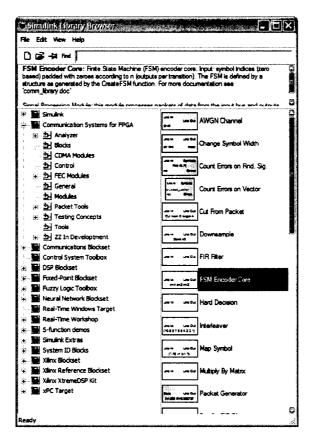

| Figure B.3: The Simulink Library Browser                                |

| Figure B.4: An example of a module                                      |

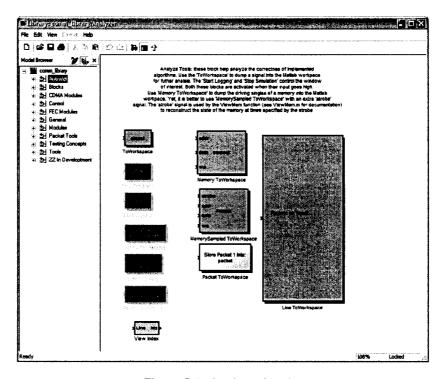

| Figure B.5: Analyzer blocks                                             |

| Figure B.6: Usage of Packet ToWorkspace and Header Spy blocks           |

| Figure B.7: Usage of Analyzer blocks for debugging                      |

| Figure B.8: Control blocks                                              |

| Figure B.9: Schematics of the Cut From Packet module                    |

| Figure B.10: Schematics of the <i>Interleaver</i> module                |

| Figure B.11: Forward error correction modules                           |

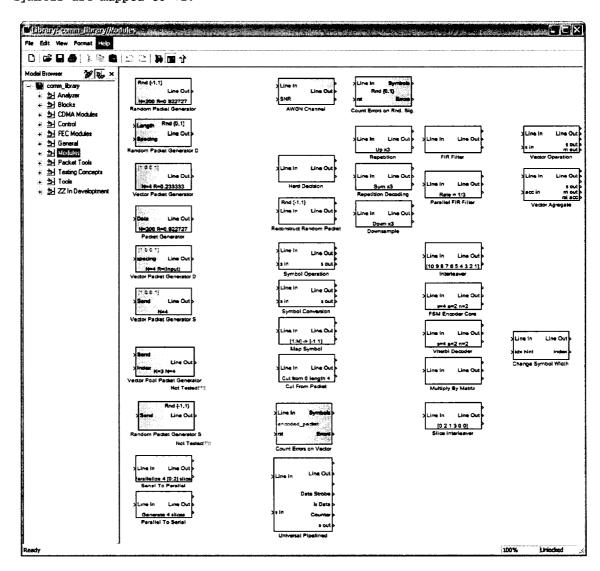

| Figure B.12: An open communication library window                       |

| Figure B.13: An open communication library window                       |

| Figure B.14: Module's mask (parameter dialog) 125                       |

# List of Tables

| Table 2.1: Performance and processing requirements comparison         | 9   |

|-----------------------------------------------------------------------|-----|

| Table 2.2: Approximate speed comparison of different FPGA speed grade | s11 |

| Table 2.3: Parameters of error-control solutions available            |     |

| commercially from Xilinx                                              | 22  |

| Table 2.4: Various FPGA devices resource comparison                   | 24  |

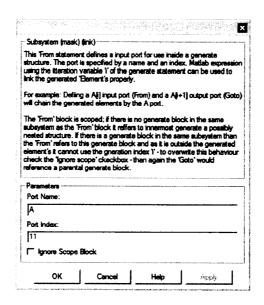

| Table 4.1: Using the Generate block to create cell                    |     |

| structures of various arrangements                                    | 50  |

| Table 5.1: Data conversion and simple operations modules              | 56  |

| Table 5.2: Vector operations and manipulation modules                 | 56  |

| Table 5.3: Packet-form editing modules                                | 57  |

| Table 5.4: Packet routing and other utility modules                   | 58  |

| Table 5.5: Communication system algorithms                            | 58  |

| Table 5.6: Communication system simulation modules                    | 61  |

| Table 5.7: Debug control and output modules                           | 62  |

| Table 6.1: Comparing the performance of commercially                  |     |

| available and our decoders                                            | 90  |

| Table B.1: Packet Structure                                           | 124 |

| Table B.2 Module parameters                                           | 126 |

| Table B 3: Support Matlah functions                                   | 120 |

# List of Acronyms

ASIC Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BSC Binary Symmetric Channel

CDMA Code Domain Multiple Access

CLB Configurable Logic Block

DSP Digital Signal Processing

FEC Forward Error Correction

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

IOB Input/Output Block

LUT Look-Up Table

LVDS Low-Voltage Differential Signalling

OCDMA Optical Code Domain Multiple Access

SINR Signal to Interference and Noise Ratio

SNR Signal to Noise Ratio

# List of Applied Terms

symbol An entity represented by the state of a binary bus with a

specific number of bits.

packet A sequence of symbols transmitted over a signal bus

consisting of a packet header followed by the packet data.

packet header First three symbols of a packet specifying packet parameters.

packet type Numeric user defined value included in the packet header.

packet data A sequence of symbols of length given by the packet header.

block Simulink subsystem implementing specific functionality.

module A block processing data organized in packets.

line

Simulink signal interconnect used to transmit packets

schematic

Simulink diagram consisting of interconnected blocks

port An input port or an output port.

input port A block making a signal, with a specific label in a specific

context, available.

output port

A block assigning a label to a signal in a specific context.

nesting

Use of a concept in a design based on an identical concept.

signal width

The number of bits of a binary representation of a block's

input/output.

signal binary point The position of a binary point in the representation of a

signal enabling interpreting the signal as a real number.

subsystem Block representing a Simulink schematics and defining

inputs and outputs of this schematics.

the user to enter *block* specific parameters.

mask parameter A parameter within the mask dialog of a block.

# Chapter 1

# Introduction

### 1.1 Motivation

Optical systems are established in long haul data transmission where these offer the required transmission capacity [1]. With increasing bandwidth requirements of individual end-users, fibre based systems are a promising candidate for the *last mile* communication. In the case of local or regional networks, optical CDMA with nonorthogonal users' signatures, as described in [27] [29] and [30], is emerging as a network protocol that can manage the quickly varying user requirements while enabling *total bandwidth utilization*, avoiding *congestion* and preventing *denial of service*.

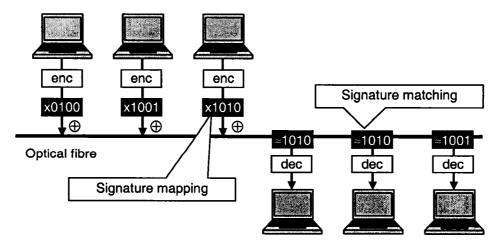

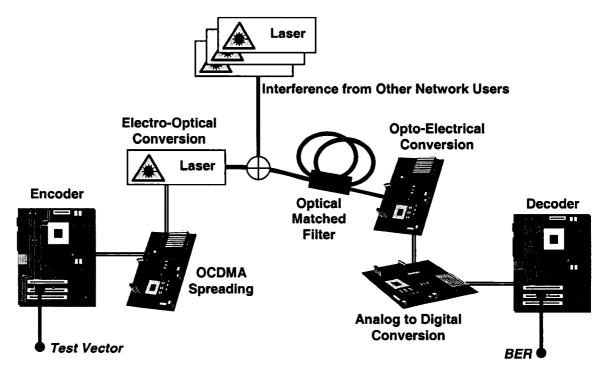

Figure 1.1: Scheme of an optical CDMA network

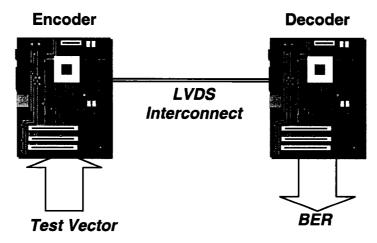

Figure 1.2: Optical CDMA prototype as a point to point communication system

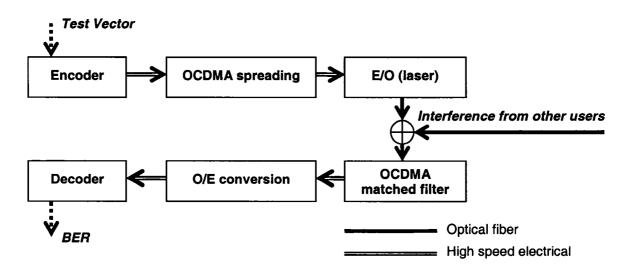

In an optical CDMA network, the data from multiple users is merged onto an optical fibre as depicted in Figure 1.1. Therefore, every transmission on the network will suffer from the interference caused by other users and powerful error-control codes have to be utilized to correct these errors [9] [11]. Only with recent advances in electronics, it is possible to employ powerful computationally intensive codes (e.g., *Turbo Codes* [4]) at the data rates seen in optical systems while utilizing inexpensive hardware.

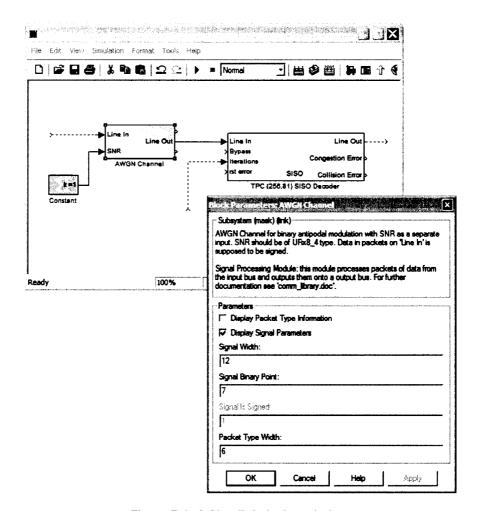

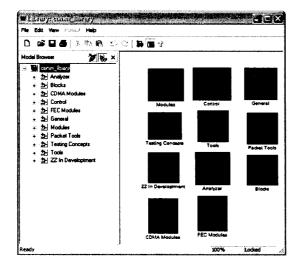

This work presents a rapid system prototyping platform for error-control codes which are to be used in an optical CDMA network prototype. The prototype will be used to test the performance of the system while implementing the functionality of a single user and emulating the interference caused by other users. This prototype will be modular and its components are depicted in Figure 1.2. In this work, we are concerned only with the *encoder* and the *decoder* modules which will be later integrated into the prototype. We present a platform based on *System Generator* from *Xilinx* that enables fast design, verification and performance testing of error-control codes for these modules.

The platform was implemented specifically for prototyping optical CDMA systems but many components of the platform are generic and can be used for development of other communication systems (e.g., wireless or wireline). The developed *Generate* block can be a utilized to simplify any structured hardware design and the modular design methodology, many of the implemented modules

and the performance testing tools can be applied to communication systems in general.

The goal of this thesis is to use the platform to implement error-control at speeds above 155 Mbps. The results in this thesis were in part presented in [17], [18] and the platform was demonstrated at [11]. The specifics of the interconnection between the user, the encoder/decoder hardware and the optical hardware as well as the specifics of the optical CDMA transmission and the optical matched filter are beyond the scope of this thesis and are briefly addressed in the conclusion. In our setup, the encoder and the decoder have been connected directly and the noise was added using a pseudo-random noise generator run in hardware.

### 1.2 Implementing a Flexible Design Platform

The high speed of optical communication is pushing real-time implementations of signal processing algorithms for these systems from software to hardware platforms. The latter technology allows key soft-decision decoding algorithms (e.g., Viterbi [36] [10], SOVA [15], BCJR [3] [14]) to posses a throughput rate of hundreds of megabits per second. Therefore, to achieve the required speed, our platform will be based on programmable hardware technology. We present an implementation of a rapid system prototyping platform that enables the development of fully customizable communication systems for use in optical CDMA transmission. Full customizability is important for research purposes as well as for quick deployment of re-configurable systems.

While there is a fairly standard suite of software development tools allowing a "push of a button" transition from customizable specification (source-code) to an implementation (running application), the world of hardware development tools is much more complex. Various design paths are used in practical hardware development to proceed from the specification to a hardware (FPGA or ASIC) prototype. In many instances, this process consists of a number of steps, where the output of one software tool is the input to another tool.

In case of software development, the design process usually consists of numerous steps hidden from the user with intermediate results in an internal format that is not human-readable, i.e., suitable only for processing by the appropriate tool. On the other hand, in hardware development, depending on the design path, the intermediate results are in a well-defined human-readable language (e.g., VHDL [2]) and are expected to be modified by the developer. This breaks the chain of a "push of a button" transition from specification to a functional prototype, because modifications of intermediate results cannot be incorporated into the original specifications. Moreover, it is hard to track what modifications have been made and, once the necessity arises to regenerate the intermediate results, it might be hard to apply these modifications. Therefore, it is highly desirable to design a hardware development environment that would allow the design of customizable algorithms with a "push of a button" transition from specifications to implementation.

Hardware prototyping is usually done using a programmable logic chip (e.g., an FPGA). The advantage of developing a design on an FPGA is easy reprogrammability which enables direct verification of the prototype under development. Another advantage of an FPGA is that using this chip in production units shortens the time-to-market and lowers the fixed production cost as there is no necessity of manufacturing of an Application-Specific Integrated Circuit (ASIC). The low fixed cost makes an FPGA suitable for use in units manufactured in small quantities, such as telecommunications systems switches and base-stations. For high quantity consumer electronics, such as cell phones, designing an ASIC might be more cost effective. Nonetheless, prototyping of such devices is done using an FPGA, where an ASIC can be designed and manufactured as a direct copy of the logic implemented on the programmable logic chip.

The platform developed in this work facilitates seamless transition from an error correcting code specification to the bit stream that can be uploaded directly onto an FPGA chip. We describe the design methodology employed in the prototyping platform, tools for testing design, the testbed used in verifying the design and custom enhancements of the design environment. We have developed an environment that effectively allows the user to modify most of the parameters

of an encoding system from a top-level module view and the system automatically propagates these changes to the low level building components. This ease of customizability and the high throughput of the systems implemented in hardware will allow us to execute reliability tests in scenarios where the error rate is below  $10^{-9}$  within several hours. In contrast, conventional simulation in C/C++ or Matlab could require weeks to finish. This will allow us to compare scenarios by considering different factors, such as: the error correcting capabilities of the decoder, size of the design and speed in real time operation.

### 1.3 Project Description

In the setup phase of our project, to achieve the above stipulated goal of easy implementation and testing of highly customizable algorithms, we have:

- Selected the platform for hardware co-simulation (Nallatech Xtreme DSP Kit development board with a Virtex II FPGA chip) and set-up the software environment necessary to communicate with and compile for this platform.

- Chosen System Generator from Xilinx [43] to implement our design. This tool allows us to program an FPGA by defining our implementation using basic hardware elements in a visual environment based on Matlab/Simulink [20]. The tool enables us to clearly define modules and their interfaces. Furthermore, it uses Matlab as a powerful scripting language which allows us to dynamically create custom algorithmic constructs.

In the following stage, we have developed a design platform that consists of software environment, methodologies and architectures to facilitate fast and easy design, testing and verification of digital communication algorithms. Specifically, in this process of developing a hardware design platform, we have:

• Created a library of modules that perform signal processing tasks. These blocks can be used as building blocks of different algorithms in communications.

- Defined a system for dispatch and scheduling of packets that allows identifying the processing bottlenecks and parallelizing the necessary components to achieve higher data throughput.

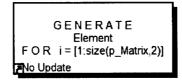

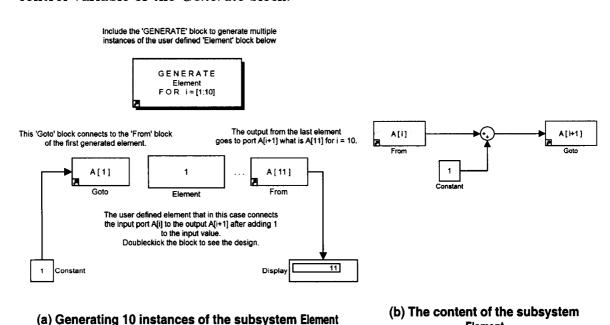

- Developed a special "Generate" block that allows defining customizable regular structures within the *System Generator* environment. The *Generate* block is used inside many modules in the library mentioned in the first bullet to achieve customization where parallel processing is necessary for effective implementation.

- Established an environment that allows automated execution of bit error rate simulations (i.e., an automated testbed) with different channel characteristics on an FPGA. This is a system that uses System Generator capabilities to control simulations on an FPGA from the host PC and stores the simulation results in Matlab.

Finally, we have used the developed hardware design platform in the design of several communication algorithms. In particular, we have:

- Implemented a Convolutional Codes Encoder with a Viterbi Decoder, Block Codes Encoder with a hard decision Syndrome Decoder to test and demonstrate the functionality of our development platform at high speeds.

- Designed a soft decision Turbo Product Codes (TPC) Decoder, which allows the implementation of communication system using an average sized FPGA with throughputs over 200 Mbps over additive white Gaussian noise channel (AWGN).

- Verified the bit-error-rate performance of these coding schemes using the design platform's automated testbed.

## 1.4 Organization of this Thesis

In this thesis, we present a development platform for rapid prototyping and hardware co-simulation of coded communication systems. Following this introductory chapter, Chapters 2 through 6 present the work on this platform and the implementation of an error control scheme for optical CDMA. Specifically:

- Chapter 2 introduces the initial hardware and software setup and elaborates on design options for hardware development.

- Chapter 3 describes the modular design methodology employed in this project. The chapter outlines the rules for data exchange between modules in the form of packets, proposes standards for the module customization user interface and describes the implementation of modules that conform to this specification. This methodology was in part presented in [18].

- Chapter 4 focuses on the software implementation of an enhancement on System Generator that enables automatic generation of arrays of regular structures in this specification language. This tool, which we call "the Generate block", enables the design of generic modules with parameters specifiable in the front end. The implementation of this tool was in part presented in [17].

- Chapter 5 explains the usage of the platform for rapid prototyping. It describes a library of communication system building blocks (based on previous chapters), tools for debugging and a testbed for automated performance evaluation.

- Chapter 6 focuses on implemented solutions. It presents the implementation of several error-control schemes and evaluates their performance by simulations. The chapter further discusses the advantages of the implemented *Turbo Product Code* over other *Turbo Coded* schemes and, finally, compares the implemented code to similar commercially available solutions.

- Chapter 7 concludes with a summary of our work and an outline for future development of the platform into a standalone prototype.

Appended to this work are three technical sections:

- Appendix A presents a step-by-step workstation installation guide.

- Appendix B provides the developer with documentation of the modular library.

- Appendix C includes the platform implementation on an attached compact disk.

# Chapter 2

# **Initial Project Setup**

In this chapter, we outline the options considered and decisions made that formed our initial software and hardware system setup. First, we give an introduction into the various design options for high performance communication systems, specifically hardware design using System Generator from Xilinx. Next, we list error-control system implementations available commercially for comparison with our system. Finally, we introduce our design platform based on System Generator and a development board from Nallatech.

The reader may want to skip the introduction into programmable logic hardware, HDL or *System Generator* design if he/she is familiar with these subjects. Nevertheless, Section 2.4 contains details on the setup of our specific development platform.

# 2.1 Design Path Options in Software and Hardware Development

When considering the implementation of forward error correction with high throughput we have several options of what hardware to use. We can:

- Use a common high performance processor (such as an Intel Pentium 4),

- Use a processor optimized for Digital Signal Processing (DSP processor),

- Use a programmable hardware chip (such as an FPGA),

- Create an Application-Specific Integrated Circuit (ASIC).

Table 2.1: Performance and processing requirements comparison

| Unit / Algorithm                         | Performance / Requirement                 |

|------------------------------------------|-------------------------------------------|

| Intel Pentium 4, 3.6Ghz                  | 9000 MIPS                                 |

| DSP Processor                            | 1200 – 8000 MIPS                          |

| FPGA (XC2V2000)                          | 60 000 MIPS, roughly compares to          |

| ASIC                                     | approx. 20% better than a comparable FPGA |

| Syndrome (7,4) Block Decoder at 155 Mbps | ≈190 MIPS                                 |

| Turbo Decoding at 1 Mbps (TCC)           | ≈1000 MIPS                                |

| Turbo Decoding at 155 Mbps (TCC)         | ≈150 000 MIPS                             |

The design process substantially differs for the first two and the second two options. In the first two cases, where an instruction based processor is used, a sequential language such as C/C++ or Matlab can be used to implement our design. The simple data model and the powerful data manipulation and computational techniques of these languages enable us to implement algorithms (software design) that are easily customizable both at design time as well as run time. On the other hand, describing the behaviour of a hardware implementation (hardware design) on an FPGA or an ASIC is much more complicated.

#### 2.1.1 Performance of Instruction Based Processors

Solutions based on processor architectures are not able to achieve performance sufficient to decode complex codes (e.g., Turbo Codes) at high speeds. Processor performance can be measured in Million Instructions Per Second (MIPS). In reference [13], a low-complexity Turbo Decoder is presented which enables decoding at an average throughput of 70kbit/s on a 40 MIPS DSP processor. More recently, a high-speed implementation of Turbo Codes is available in reference [8]. This implementation achieves the throughput of approximately 3 Mbit/s on a 4500 MIPS desktop processor. These results justify a rough estimate of 1000 instructions to be the complexity of decoding a single Turbo Coded bit.

The latest desktop processors have a performance just below 10000 MIPS. Specifically, the Intel Pentium 4 running at 3.6 GHz is rated at 9000 MIPS [16].

The performance of DSP processors is similar. State of the art processors in the Texas Instruments TMS320C6400 family range up to 8000 MIPS [33]. The advantage of a DSP processor is mainly in a low power consumption, unit cost and increased memory bandwidth. Using the above estimate, we see that Turbo decoding on a processor will be limited to about 10 Mbit/s. The processor performance and decoding requirements are summed up in Table 2.1 (together with FPGA and ASIC solutions performance).

#### 2.1.2 Performance of Hardware Solutions

The second two options mentioned above (i.e., FPGA and VLSI solutions) allow us to specify a custom structure consisting of logical elements and registers that will be implemented in hardware. Compared with software design it is considerably more difficult to construct a hardware structure (hardware design) to perform a specific task (e.g., complex decoder). Hardware description languages such as VHDL [2] Verilog [7], or SystemC [5] can be used. An alternative is the use of System Generator, what is a tool that allows us to draw up the system schematics in Simulink/Matlab environment.

The performance of systems designed in hardware can be substantially better that the performance of software systems even though the processing speed (i.e., the clock speed) of an FPGA or an ASIC might be substantially lower than the processing speed of an instruction based processor. Hardware design allows high parallelization (pipelining) which will dramatically increase the performance of the system. A decoder of a Turbo Code based on the concatenation of two convolutional codes implemented on an FPGA can process data at a rate as high as 12 Mbps [39], while utilizing only part of the logic available on the FPGA. The processing speed of a decoder of a Turbo Code based on the concatenation of block codes can perform at a rate as high as 150 Mbps.

Design intended for an FPGA can be easily ported to an ASIC, where an ASIC will generally perform better, as it does not have the disadvantage of additional delay introduced when a signal is routed through switches on the FPGA's interconnect network. Due to these advantages, an ASIC might be able to work at a higher clock frequency as well as consume approximately 20% less power.

FPGA

Speed Grade:

-4

-5

-6

-7

Virtex II

100%

114%

126%

Virtex II Pro

128%

143%

161%

Table 2.2: Approximate speed comparison of different FPGA speed grades

Table 2.2 lists the approximate differences in performance of the two most common FPGA families from Xilinx. Each of these FPGAs is manufactured in 3 different speed grades between -4 (the slowest) and -7 (the fastest). The performance is normalized to the speed of the Virtex II -4 speed grade chip. The table was compiled using the Virtex II and Virtex II Pro handbooks [41] [42] and comparing the claimed performance of solutions listed in [39] on different platforms. We use this table to normalize the performance of algorithms with speeds listed for one of these chips.

## 2.2 Hardware Design Using Programmable Logic

Due to the high throughput requirements on the algorithms in this thesis we will design these in hardware; for an implementation on an FPGA. Modern FPGAs include sufficient logic to address the complexity of these algorithms as well as built-in high speed serial interfaces that enable the FPGA to communicate with the host system at the required data rates. The following subsections describe the programmable logic technology as well as the hardware and software setup that is necessary for FPGA development.

## 2.2.1 Field Programmable Gate Arrays (FPGA)

An FPGA is the latest generation of programmable logic. In contrast to ASICs, the gate array structure of an FPGA is programmable after manufacture. This is achieved with an array of configurable cells that perform custom logical operation and a configurable interconnect network that is used to route signals between the cells.

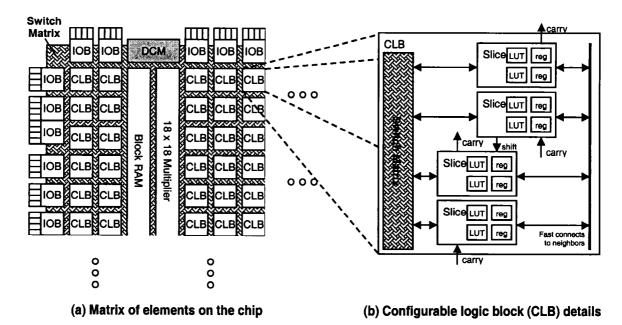

Figure 2.1: Virtex-II chip configuration

In this work, we will be using a system with a *Virtex-II* FPGA from *Xilinx*. Therefore, in this section, we will describe this particular chip. Nevertheless, other FPGA implementations have a similar structure. The core element, enabling configurability of the executed logic, is a 16 bit Look-Up Table (LUT). This LUT can be configured to:

- Implement a custom logic operation on 4 input bits, with the LUT storing the truth table of this operation.

- Function as a RAM block, storing a 16 bit word.

- Work as a 16 bit shift register.

In Virtex-II, the LUTs are grouped by two to form a Slice and four slices are grouped again to form a Configurable Logic Block (CLB). The details of a Slice are outlined in Figure 2.1(b). This grouping, with the introduction of additional signals (carry and shift), enables effective implementation of moderately complex elements (e.g., long shift registers, operations using a carry-over flag) within one CLB. The CLB is connected to a Switch Matrix, which enables to route signals on the FPGA chip. Additional lines connect the CLB to its neighbours in the matrix depicted in Figure 2.1(a). With elements performing elementary logic

operations and a configurable network connecting these elements, we are able to emulate the behaviour of any logic circuitry.

Input/Output Blocks (IOBs) placed on perimeter of the chip connect the FPGA to external signals via an actual physical pin of the chip. Using the Switch Matrix, these external signals can be routed from the IOB to any other location on the FPGA. Other resources, such as 18 by 18 bit multipliers and RAM blocks, are available to the designer and accessible using the Switch Matrix. The programming of an FPGA consists of:

- Configuring the CLBs to perform synchronous (employing the register reg in Figure 2.1(b)) or combinatorial operations.

- Setting-up the Switch Matrix to properly route signals between the CLBs and other resources on the FPGA.

The additional logic in these elements that is necessary to allow the programming of the chip causes an FPGA to be slower and less power efficient than an equivalent ASIC. The advantage of an FPGA is the shorter time-to-marked and the lower development cost which makes ASIC design feasible only for large quantities (above ten thousand units). Nevertheless, if desired an ASIC can be made that is a hard-copy of an FPGA.

#### 2.2.2 Hardware Design for an FPGA

To design an algorithm on an FPGA, we have to define the behaviour of the chip. We have three possible entry points for hardware design:

- Using a Hardware Description Language (HDL), e.g., VHDL, Verilog, SystemC,

- Describing the design using schematics,

- Implementing the behaviour in a high-level sequential language, such as Java.

Specifications, in any of these formats, must be compiled into a *net list*. A *net list* specifies how to implement the design using elementary logic by enumerating the logic elements and listing the connections between these elements. This specification is then mapped to the resources of an actual FPGA. A binary file, called *bitstream*, is created and this file can be used to program the FPGA.

Creating a net list from a schematic specification or a specification in VHDL or Verilog is a straightforward, even though not simple, process. On the other hand, creating a description suitable for hardware from a high-level sequential language, which was not designed for hardware development, is tricky. Several utilities, which enable a translation from a sequential language to VHDL or Verilog, are available on the market. An example is Forge [38] developed by Xilinx, which facilitates the translation from Java to VHDL. Nonetheless, these utilities do not produce optimal results and are scarcely used by hardware designers.

The way programming is uploaded onto a chip and the way an FPGA chip can communicate with the surrounding environment are dependent on the development board that contains the chip. Generally constraints specifications have to be created to define which pin of a FPGA chip will be driven by which internal signal in the design. These signals can than drive other logic present on the board alongside the FPGA (e.g., RAM, digital to analog converters, PCI/USB controllers). Often there is a communication controller present on the board such as the previously mentioned PCI or USB controller that allows us to transfer data between the FPGA board and a host PC. After transferring the design to the FPGA board, we can verify its functionality by stimulating it appropriately and monitoring the response.

### 2.2.3 Hardware Design Using a Hardware Description Language (HDL)

A Hardware Description Language such as VHDL, Verilog or SystemC describes the behaviour of a hardware circuit. This description can be used for:

- Simulation, where we try to verify the functionality of the circuit and

- Synthesis, the process of mapping the description onto the hardware.

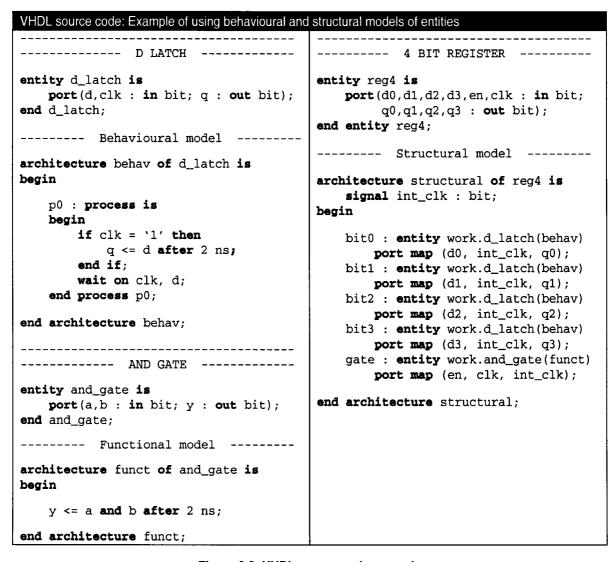

In this work, VHDL is used internally by the tools involved in our design process. This language is also used to integrate third party intellectual property (IP cores), such as a Reed-Solomon encoder/decoder, into our designs. Thus, let us introduce the language in brief. In the following source code we present the VHDL implementation of these three various elements: an and gate, a d-latch and a 4-bit register.

A d-latch is a simple circuit that samples the value of its q input when the clk input is high and otherwise holds the value of its q output. Each of these implementations demonstrated a different construct in VHDL. The d-latch is implemented using a behavioural model that describes the behaviour of the element in sequential statements similar to a high-level language. The and gate is described using a functional model that consists of concurrent assignment operations. The 4-bit register is then constructed using four d-latches and a and gate and connecting the inputs and outputs of these elements. This description is called a structural model. Please refer to referenced literature for further information on VHDL.

Figure 2.2: VHDL source code example

The VHDL description can be simulated using a HDL simulator such as ModelSim [21], which can be supplied with input test vectors and compare the outputs against expected output sequences.

### 2.2.4 From Hardware Description to Hardware Programming

To translate the design onto an FPGA, another tool such as XST (which is part of the Xilinx integrated development environment ISE [40]) has to be employed. This elaborates the description and creates a net consisting of the interconnection of elementary logical elements. This net fully specifies the logic that is necessary to implement the functionality, as described by the VHDL source code.

With the *net* already elaborated, the logic elements have to be mapped onto the resources available on the FPGA. This process is called *place and route*. Each logic elements in the *net* is assigned to a specific resource on the *FPGA* and the configuration of the *Switch Matrix* (internal signal routing of the FPGA) is determined to properly route all the signals.

The place and route process might fail if there are not enough resources on the target FPGA to either implement the specified logic or to route the signals. After the design has been placed onto the FPGA, the maximum clock speed can be determined by computing the maximum register-to-register delay. Typically only about half of this delay would be due to the design logic. The other half would be due to the delay introduced by the switches on the FPGA's Switch Matrix. If we are not satisfied with the achieved clock speed, the tools can try to alter the placement and routing to cut down the biggest delay.

The *synthesis* as well as *place and route* processes are executed by different tools that are all integrated into the development environment from Xilinx.

#### 2.2.5 Using System Generator in Hardware Design

System Generator from Xilinx [43] is a graphic tool that allows us to draw up the schematics of the desired system and is based on the Matlab/Simulink [20] environment, a model-based environment for simulation of dynamic systems. The model consisting of interconnected blocks can be translated directly onto an

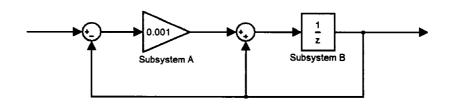

FPGA. System Generator uses a graphic interface where blocks (subsystems) are represented by icons and signals by lines connecting these icons. The diagram in Figure 2.3(a) is an example of a simple Simulink system.

System Generator provides us with blocks representing basic hardware elements (e.g., registers, logic gates, math operations, RAM) in Simulink. If we build a circuit from these blocks, we can simulate it inside Simulink to determine its behaviour. We can use this simulation to verify the functionality of the design without having to compile it into a hardware programming file. Simulink provides us with multitude of tools to analyze data generated by this simulation. If the behaviour conforms to what we request of the system then we can use System Generator to translate the schematics into hardware. The diagram in Figure 2.3(b) shows the implementation of the system from part (a) using System Generator blocks.

Moreover, all its blocks have an equivalent FPGA implementation. A circuit designed using *System Generator* can be easily translated into FPGA programming and the translation is done automatically in three steps:

(a) Simulink model of a system with feedback

(b) The system in (a) implemented using built-in System Generator blocks

Figure 2.3: Transforming a Simulink model into System Generator design

- 1. VHDL source code and Xilinx development environment configuration files are created to instantiate all the logic elements in the schematics and to connect the elements properly.

- 2. The generated source and project files are compiled into an FPGA programming file (i.e., a "bitstream").

- 3. A hardware co-simulation block is created in *Simulink*. This block represents the compiled design. If the block is included in schematics, *System Generator* will automatically upload the design to an FPGA, where it will be executed in parallel with the *Simulink* simulation.

In the last step, the design running on hardware was integrated back into Simulink environment. This is useful for hardware co-simulation, but the design can also be uploaded into the FPGA independently for standalone solutions.

#### Integration of System Generator and Simulink design

The signal interconnects in Figure 2.3(b) represent hardware busses which have to be fixed point binary numbers in simulation. General Simulink blocks cannot be translated into hardware (there is not an equivalent hardware implementation for every possible Simulink block) and, furthermore, the System Generator blocks only accept fixed point numbers as inputs, whereas a general Simulink signal is a floating point double precision number (double). Therefore, any Simulink design using other block libraries than the ones provided by System Generator has to be isolated using translation blocs. This design will not be translated into hardware.

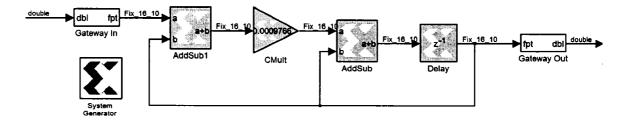

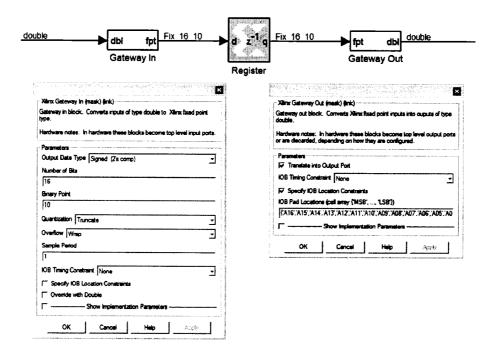

The translation is done using the Gateway In and Gateway Out blocks shown in Figure 2.3(b). The Gateway In block must specify the format of the input. In Figure 2.4, the output of a Gateway In is specified (in the parameters dialog box) to be a signed 16 bit number with 10 decimal bits. Usually the format of the output signal of a block can be inferred from the format of the input. For example, in the same figure the output of the "Register" block will be of the same format as its input signal. The output of a Gateway Out will be double, independent on the format of the input, as the Gateway Out marks the transition back to the Simulink environment. The gateway blocks also allow specifying to which actual pins of the FPGA chip these signals will be routed (IOB Location Constraints), when translated into hardware programming.

Figure 2.4: Illustration of the concept of signal translation from the floating point domain to fixed point domain using *Gateway In* and *Gateway Out*

#### Hardware co-simulation

When finishing the compilation process, System Generator creates a block that represents the programming of the FPGA and is associated with the new bitstream. If we include this block in a Simulink design, the bitstream will be uploaded onto the FPGA and it will run in hardware. The inputs and outputs of the design will be connected to Simulink signals as specified. Data can be transferred between the Simulink simulation and the design running on the FPGA via an appropriate interface (e.g., JTAG, USB, PCI).

Nevertheless, we have to be aware that *Simulink* runs at a much slower "clock" speed than the *FPGA*. Thus these two designs (one being simulated in *Simulink* and the other running on the *FPGA*) run on independent clocks and thus the communication between them has to be handled as communication between two asynchronous circuits. A setup like this is very useful if we use the *FPGA* to accelerate simulations under different conditions. We call this concept hardware co-simulation.

While we want the simulation to run at full hardware speed of the *FPGA*, we want to be able to easily influence the configuration of the simulation parameters. Therefore, it is better to generate the configuration parameters inside *Simulink*, where we have more flexibility and it is not necessary to recompile the whole design to introduce changes.

Internally, System Generator creates a register for each Gateway In and Gateway Out block. This register is used during hardware co-simulation to realize the communication between the design running in the FPGA and the Simulink environment. System Generator integrates custom logic into the FPGA that enables it reading and writing such registers using a register transfer protocol. This protocol enables the host PC connected to the FPGA board to retrieve and set the values of the inputs and outputs of the designed logic. In the host PC, the Gateway In and Gateway Out blocks use customized System Generator code to access the register transfer protocol and integrate the hardware registers into the software simulation in Simulink.

The hardware link used for the register transfer protocol is dependent on the development board configuration, where theoretically any data interface connecting the board to the host PC can be used. System Generator generally supports only the JTAG interface while other interfaces would require custom logic in the FPGA and customization of the System Generator gateway blocks. Nevertheless, virtually all development boards have the JTAG interface and this makes System Generator compatible with virtually any Xilinx based FPGA development board. Only a small configuration file is required by System Generator to set-up the communication via the JTAG interface for hardware cosimulation. The disadvantage of using the JTAG is that it is fairly slow and therefore the data transferred into Simulink from the FPGA board will be updated at a fairly slow rate.

System Generator supports other interfaces (USB or PCI) on a few specific boards. One of the boards supported by System Generator is the Xtreme DSP Kit development board from Nallatech. This development board has both: a USB and a PCI interface. The vendor provides hardware design and software API that implements a register transfer protocol between the board and the host PC via one of these interfaces. System Generator uses this design and API to enable

hardware co-simulation on this specific board using the USB or PCI interface. Thus enabling faster communication with the board and improving the performance of the hardware co-simulation scheme.

### Customizable design using Simulink

In our design paradigm, we want to develop a front-end customizable communication library, where all parameters must be configurable in the front-end interface. In a hierarchical design, this requires that the parameters are propagated downwards through the design hierarchy up to the point where the parameter invokes the necessary customization. In some cases, this customization might involve only setting a specific parameter of a *System Generator* block. In other cases, this customization might require custom processing, where different design has to be instantiated depending on the value of the parameter. This custom processing has to be defined within a module and encapsulated into the module's front-end interface. The complexity of the custom processing might require the employment of a programming language. The *masking* methodology in *Simulink* enables both: to propagate parameters down a design hierarchy and to apply customization using a powerful programming language – Matlab.

The masking concept assigns a parameter dialog box to a Simulink block and hides the internal design of the block from user view. The masks of the Gateway In and Gateway Out blocks in Figure 2.4 are good examples of the mask dialogs. Parameters set within the mask can be used in the block's design to either initialize the block using Matlab scripts or to set values within the masks of subblocks contained within the block. This way, parameters can propagate through a hierarchy of masked blocks. An initialization script that is executed whenever the design is updated can be defined for each masked block. The design is updated before a simulation is run and before it is translated into hardware.

## 2.3 Commercially Available Solutions

Numerous commercially available hardware designs can be included in your system on an FPGA or an ASIC. These are usually precompiled designs with a documented outward interface and are called IP-cores (Intellectual Property Cores). Implementations of FEC are also available. Whereas these cores are usually optimized and it would be hard to compete with their performance, the cores are implemented according to an industrial standard and implement a very specific code with no or little possibility of customization (e.g., in terms of rate, code parameters, soft-decision decoding abilities). Table 2.3 lists some FEC solutions available from Xilinx. The speeds are derived from the datasheets of these cores and normalized to the performance of a -4 speed grade *Virtex II* FPGA chip according to Table 2.2.

## 2.4 Initial Platform Setup

Our initial platform setup consists of a design environment as well as the FPGA hardware and is the starting point for a prototyping platform described in the Chapters 3, 4 and 5. The prototyping platform augments this initial setup to enable rapid prototyping of error control codes and to allow emulation of a coded optical CDMA network.

Table 2.3: Parameters of error-control solutions available commercially from Xilinx

| Algorithm                                              | Speed    | SLICES | Block RAM |

|--------------------------------------------------------|----------|--------|-----------|

| Reed Solomon                                           |          |        |           |

| (207,187) 8-bit                                        | 722 Mbps | 764    | 2         |

| (255,239) 8-bit                                        | 727 Mbps | 877    | 4         |

| Viterbi Decoder <sup>1</sup>                           |          |        |           |

| Parallel, cl=5, tb=30, sb=3                            | 150 Mbps | 805    | 2         |

| Parallel, cl=7, tb=42, sb=4                            | 132 Mbps | 3299   | 4         |

| Parallel, cl=9, tb=54, sb=4                            | 91 Mbps  | 12821  | 16        |

| Serial, cl=5, tb=30, sb=3                              | 18 Mbps  | 261    | 2         |

| Serial, cl=7, tb=42, sb=3                              | 15 Mbps  | 638    | 2         |

| Serial, cl=9, tb=54, sb=3                              | 10 Mbps  | 2107   | 4         |

| Turbo Product Code (64,57) <sup>2</sup> , 5 iterations | 123 Mbps | 3313   | 17        |

| Turbo Convolutional Code <sup>2</sup> , 5 iterations   | 6.2 Mbps | 1618   | 47        |

<sup>1</sup> cl: constraint length, tb: trace-back length, sb: soft value bit width

Reference: Xilinx, http://www.xilinx.com/ipcenter/fec\_index.htm [39]

<sup>&</sup>lt;sup>2</sup>3G compliant, sliding window size: 32, block size: 378 – 20730

Figure 2.5: The Xtreme DSP Kit development board

We have chosen System Generator from Xilinx as the front end design interface of our platform because of the following reasons:

- It is visually attractive, easy to learn and allows us to build modules with clear interface.

- It enables us to use Matlab as a powerful scripting and specification language in applying customization into the hardware design.

- It facilitates a "push of a button" transition to a hardware programming file.

- It enables easy and intuitive communication with the running design seamlessly integrated into *Simulink*.

- It supports most Xilinx based FPGA platforms.

System Generator offers a hardware design environment that is compatible with almost all Xilinx based development boards with data exchange between System Generator and the board (necessary to conduct hardware co-simulation) via the JTAG interface. Nevertheless when using JTAG, data can only be transferred at a fairly low rate and this configuration could influence the performance of our simulation testbed.

For use in our platform, we have chosen the Xtreme DSP Kit development board from Nallatech in Figure 2.5. The board hosts either an XC2V2000 or an XC2V3000 Virtex II FPGA chip. The resources available on these devices are outlined in Table 2.4. Moreover, this board allows us to use the communication

| FPGA Device                                    | SLICES <sup>1</sup> | Block RAM <sup>2</sup> | Multipliers |

|------------------------------------------------|---------------------|------------------------|-------------|

| XC2V2000                                       | 10,752              | 56                     | 14          |

| XC2V3000                                       | 14,336              | 96                     | 16          |

| XC2V8000                                       | 46,592              | 168                    | 28          |

|                                                |                     |                        |             |

| <sup>1</sup> 1 SLICE = 2 LUT, 4 SLICES = 1 CLB |                     |                        |             |

| <sup>2</sup> Each Block RAM has 18kbits        |                     |                        |             |

**Table 2.4: Various FPGA devices resource comparison**

via the USB supported in System Generator. This setup is to be used for hardware co-simulation while testing the performance of the designed error control algorithms or when emulating the optical network within the FPGA and it does not provide sufficient host-to-FPGA bandwidth for the required speeds. Other hardware options (e.g., Avnet's Virtex-II Development Kit, Xilinx ML310 Embedded system development board) are considered for our prototype deployment, where constraints on connectivity with an optical link require a board with a high-speed digital interface. Nevertheless, these development boards do not have a high speed interface that could be utilized by System Generator to perform hardware co-simulation and therefore are not suitable in the initial phase of our project.

Several other software packages have to be installed on a workstation to facilitate design in *System Generator* and communication with the *Nallatech Xtreme DSP Kit*. These packages include *Matlab*, *Xilinx ISE* and *Nallatech* software suite. The detailed instructions, on how to set-up a workstation, are included in Appendix A.

# 2.5 Chapter Summary

In this chapter, we have introduced the software and hardware setups of our development platform. We have also outlined other design options to give support to our decisions and for reference purposes.

# Chapter 3

# Proposed Modular Design Architecture

This chapter and the following Chapter 4 introduce design methodologies and concepts that are employed in the development of our rapid prototyping platform described later in Chapter 5. These design methodologies were drawn up to:

- Allow the construction of front-end customizable communication modules,

- Enable easy data routing and scheduling for data processing,

- Facilitate clear, fast and error-free design.

The prototyping platform incorporates several concepts that had to be designed to allow for easy usage, high customizability, convenient design verification and runtime control. These concepts are:

- Self-descriptive packets to enable easy routing and scheduling of data processing,

- A unified module interface and internal naming conventions,

- A Generate block that allows to generate arrays of regular hardware structure enabling high level customization,

- A system of "debugging" modules to verify the design operation,

- A Hardware-Simulink-Matlab interface to retrieve data from a system running on the hardware, control it and run batch-tests.

The following sections in this chapter describe the first two bullets of the above concepts while the remaining concepts are explained in detail in Chapter 5. First, we will discuss the concepts and advantages of our modular design. Next, we will describe how to implement a specific module based on these concepts. Finally, we present a simple example of an iterative loop employing modules based on our concepts that demonstrates its advantages in data routing and parallelization.

The implementation of our platform is done in *System Generator* from *Xilinx* due to its advantages outlined in Section 2.4.

## 3.1 Module Data Exchange: Packets

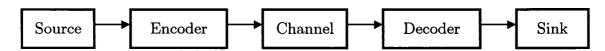

Communication is a problem of reliably delivering information from the *source* to the *sink* through a *channel*. In digital communication, an *encoder* and a *decoder* allow increased reliability of information transmission by introducing redundancy into the transmission and formatting the message for channel impairments. We commonly draw a diagram of such a communication system that looks like the diagram in Figure 3.1.

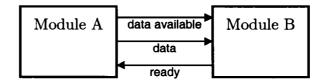

Such a diagram clearly states the components involved in a communication systems or the flow of information and dependencies between these components. In our hardware design paradigm, we would like to work with the same level of abstraction and simple interface as used in the above diagram. Commonly, more complicated interfaces are used between modules that include several control signals going in both directions.

This is not only aesthetically displeasing, but also creates opportunities to introduce errors into the design. With a feedback loop via the signals in both directions neither of the modules A and B can be tested properly without the other one and more care has to be taken to properly anticipate all situations that can arise on the interface of these two modules.

Figure 3.1: Schematic block diagram of a digital communication system

Figure 3.2: Data interface with handshaking

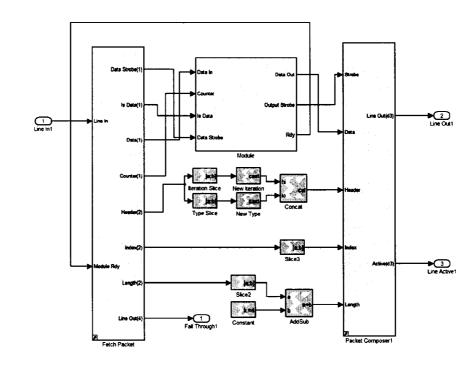

Figure 3.3: Digital communication system as specified using our library modules

In the library we implement a scheme where data is transmitted on a single line (even though this bus is a multi-bit bus it is not being considered to consist of multiple control signals) in packets that are self-descriptive. That is:

- The meaning of the data (packet type) can be automatically identified.

- Data boundaries and null transmission times can be identified.

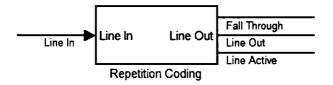

Furthermore, all modules in the library are required to be always ready to accept a packet on the input but they may route this packet to a special "Fall Through" output if the module is:

- Not ready to process the packet,

- Not able to process the specified packet data type.

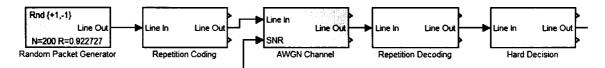

These two concepts eliminate the necessity for additional signalling (and notably they eliminate the need for feedback) between two modules, thus keeping the interface as simple as in the previous abstract block diagram of a communication system. Figure 3.3 shows a setup of a generic communication system that can be used for performance testing using modules from our library. Note that the "Fall Through" outputs of the modules are left unconnected.

Figure 3.4: Data-packet structure

Figure 3.5: An example of a module

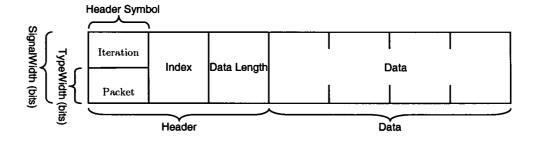

#### 3.1.1 Packet Structure

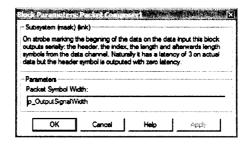

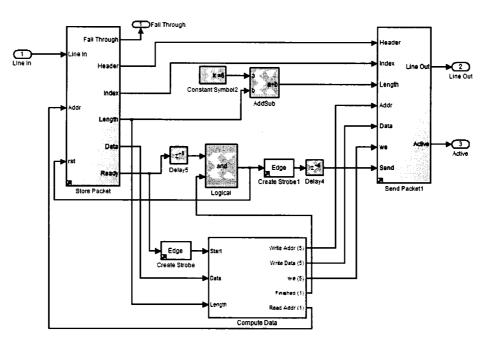

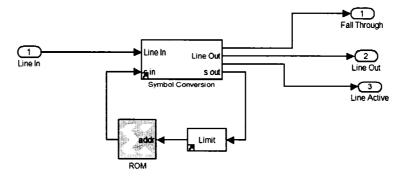

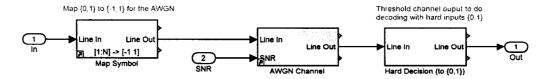

A data line is a k-bit bus that connects two modules. Packets can be transmitted on this data line and if no packet is being transmitted, all the bits of the data line have to be set to 0. Thus, the beginning of a packet is recognized as the first nonzero symbol on the line. The packet starts with a header that is 3 symbols long and specifies the packet type, some user information and the packet length L. The next L symbols are the payload data of the packet (thus also zero symbols will be identified as packet data). After the payload data has been transmitted, the line returns to all-zero state or a nonzero symbol that would be identified as the beginning of a new packet. Figure 3.4 details the structure of a typical packet.