# A Hierarchical Method of Fault Diagnosis with Built-In Self-Test Applications

Robert Campbell Aitken

B.Sc. (Hon), University of Victoria, 1985M.Sc., University of Victoria, 1986

Department of Electrical Engineering McGill University

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy

**April 1990**

### Abstract

The problem of fault diagnosis in digital circuits is composed of two sub-problems: Fault detection (identifying that a fault is present) and fault location (identifying the failure responsible for faulty behaviour). Tests using randomly or pseudo-randomly selected input stimuli have been suggested both as a means of reducing the costs associated with generating deterministic tests and as a means by which circuits could test themselves (built-in self-test). The majority of research into random testing has dealt only with its fault detection properties. Fault location has typically been treated as a dictionary search problem, or ignored altogether.

This dissertation proposes a new approach to fault location in randomly or pseudorandomly tested digital circuits. Faults will be isolated by a hierarchical sequence of steps, each of which identifies a particular property of the fault which has occurred. The method uses available circuit information to aid in location. The advantages of this method include greatly reduced dictionary generation costs, the ability to locate a fault without searching an entire dictionary, and the ability to partially characterize unmodelled faults. In addition, a hierarchical approach allows dictionaries to be constructed in a demand-driven fashion, avoiding unnecessary work for faults which do not occur in practice, and reducing the costs of changes in the test set.

Sample applications of the proposed location technique are given, for use in both random compact testing and built-in self-test Experimental results are presented to demonstrate the performance of the method.

### Résumé

Le diagnostique de défauts dans les circuits digitaux se divise en deux sous problèmes la détection des défauts et leur identification. Des méthodes qui utilisent les entrées aléatoires ont été proposés comme façon de réduire les coûts associés à la genération des patrons de test et pour faciliter le test intégré. La plupart des recherches reliées aux tests aléatoires ont seulement considéré la détection des défauts. L'identification des défauts a été considérée comme un problème de recherche en dictionnaire ou tout simplement ignorée.

Ce document propose une nouvelle approche à la question de l'identification des défauts dans les circuits digitaux vérifiés à l'aide de patrons de test aléatoires. Les défauts sont isolés par une séquence hiérarchique d'étapes où chacune identifie un attribut particulier du défaut qui est présent dans le circuit. La méthode utilise les caractéristiques connues du circuit pour faciliter l'identification des défauts. Les avantages de cette méthode sont entre autre une grande réduction des coûts de génération de dictionnaire, la possibilité d'isoler un défaut sans la recherche complète du dictionnaire et l'abilité de caractériser partiellement les défauts qui n'ont pas été modelé De plus, une approche hiérarchique permet aux dictionnaires d'être construits sur demande évitant ainsi des efforts inutiles et réduisant les coûts associés aux modifications du test

Ce mémoire contient quelques exemples des applications envisagées ainsi qu'une évaluation expérimentale de la méthode proposée.

### Acknowledgements

I would like to acknowledge my supervisor, Vinod K. Agarwal, for his assistance and guidance throughout my doctoral studies. His enthusiasm and vision have been greatly appreciated, as has his insistence on and support for publication of results. The latter has enriched this work and broadened my experience as a researcher considerably

I would also like to acknowledge Prof. Janusz Rajski for his suggestions relating to the organization of this dissertation. In addition, as members of my approximate, both he and Prof. Hossam ElGindy contributed worthwhile suggestions during the earlier stages of my research work.

I am indebted to my friends in the VLSI Design Lab, present and past members, for their assistance — notably to Fidel Muradali, for proofreading the various drafts of this dissertation, and also to Henry Cox, André Ivanov, Fadi Maamari, Ashish Pancholy, Dhirendran Xavier, Yervant Zorian, and to Francis Larochelle for his assistance in writing the French version of the abstract.

In addition, I would like to express my thanks to Jon Muzio and Micaela Serra, of the University of Victoria, for introducing me to the testing field.

For financial support, I would like to acknowledge the Natural Sciences and Engineering Research Council of Canada, and the Centre de recherche informatique de Montréal.

Finally, on a more personal level, I am grateful to my wife Denise Aitken for her support throughout the course of my studies, including delaying some of her own goals in order to help me realize mine

# Table of Contents

| Chapt | er 1 Introduction                                | 1  |

|-------|--------------------------------------------------|----|

| 1.1   | Definitions                                      | 1  |

| 1.2   | Overview of Problem                              | 3  |

| 1.3   | Outline of Dissertation                          | 4  |

| Chapt | er 2 A Brief History of Fault Diagnosis          | 6  |

| 2.1   | Early History                                    | 6  |

| 2.2   | Test Sets                                        | 7  |

|       | 2.2.1 Hierarchical Levels of Circuit Description | 7  |

|       | 2.2.2 Hierarchical Levels of Fault Description   | 8  |

|       | 2.2.3 Quality Measurements                       | 9  |

| 2.3   | Aspects of Automated Test Pattern Generation     | 11 |

|       | 2.3.1 Deterministic Test Pattern Generation      | 11 |

|       | 2.3.2 Random Test Pattern Generation             | 12 |

|       | 2.3.3 Deterministic Fault Location Techniques    | 13 |

|       | 2.3.4 Testing Equipment                          | 16 |

| 2.4   | Use of Exhaustive Testing in Fault Diagnosis     | 16 |

| 2.5   | Use of Random Vectors in Fault Diagnosis         | 17 |

|       | 2.5.1 Random Pattern Test                        | 17 |

|       | 2.5.2 Random Compact Testing                     | 18 |

|       | 2.5.3 Fault Detection Probability                | 19 |

|       | 2.5.4 Random Pattern Resistant Faults            | 21 |

|       | 2.5.5 Weighted Random Patterns                   | 21 |

|       | 2.5 6 Fault Location with Random Vectors         | 21 |

| 2.6   | Design for Testability                           | 23 |

|       | 2.6.1 Board-Level Approaches                     | 25 |

| Chapt | er 3 Built-In Self-Test and Data Compaction      | 26 |

| 3.1   | Programmed BIST                                  | 27 |

| 3.2   | Structured BIST                                  | 27 |

| 3.3   | Performance Measures of BIST                     | 27 |

| 3.4   | Error Models                                     | 28 |

|       | 3.4.1 Uniform Error Model                        | 29 |

|       | 3.4.2     | Burst Error Model                                   | 29       |

|-------|-----------|-----------------------------------------------------|----------|

|       | 3 4.3     | Independent Error Model                             | 29       |

|       | 3.4.4     | Asymmetric Error Model                              | 30       |

|       | 3.4.5     | Generalized Error Model                             | 31       |

| 3.5   | Data      | Compaction Techniques                               | 31       |

|       | 3 5 1     | Signature Analysis                                  | 31       |

|       | 3.5.2     | Transition Counting                                 | 33       |

|       | 3.5.3     | Weight Counting                                     | 33       |

|       | 3.5.4     | Parity Testing                                      | 33       |

|       | 3.5.5     | Spectral Testing                                    | 34       |

|       | 3.5.6     | Output Data Modification                            | 34       |

|       | 3.5.7     | Other Techniques                                    | 34       |

| Chapt | ter 4     | Fault Location in Random Compact Testing            |          |

|       |           | and Built-In Self-Test                              | 36       |

| 4.1   | Signa     | ture by Simulation                                  | 37       |

| 4.2   | Inter     | mediate Signature Collection                        | 38       |

| 4.3   | Algeb     | oraic Analysis.                                     | 41       |

| 4.4   | Requ      | irements for Fault Location in the RCT Environment  | 42       |

| Chapt | ter 5     | Hierarchical Fault Diagnosis: Theory and            |          |

| Ondp. |           | Background                                          | 44       |

| 5.1   | Outli     | ne of Proposed Technique                            | 45       |

| 5.2   |           | retical Analysis                                    | 48       |

| 0.2   | 5.2.1     | Preliminary Definitions                             | 48       |

|       | 5.2.2     | Classes of Hierarchical Observations                | 50       |

|       | 5.2.3     | Diagnostic Performance of Hierarchical Observations | 52       |

| 5.3   | Cons      | traints on Parameter Observation                    |          |

| 5 4   |           | plexity of Predicting Observations                  |          |

| 04    | 5 4 1     | Failing Pattern Measurements                        | - 60     |

|       | 5.4 2     | Failing Output Measurements                         | 64       |

|       | 5.4.3     | Fixed Length Signatures                             | 64       |

|       | 5 4.4     | Cost Effect of Fault Simulation                     |          |

| Char  |           |                                                     |          |

| Chapt | ret. O    | Structures for Observing Circuit Parameters         | 66       |

| 6.1   | Dona!     |                                                     |          |

| 0.1   |           | Ilel to Serial Conversion       Serial Streaming    | 67<br>67 |

|       | V2. 1 . I | DELIGN DREGIUME                                     | n/       |

|       | 6.1.2 | Parallel to Serial Compaction                      | 69  |

|-------|-------|----------------------------------------------------|-----|

| 6.2   | Creat | ing the Error Stream                               | 72  |

|       | 6.2.1 | Partial Matching.                                  | 74  |

|       | 6.2.2 | Constructing a Modifier Block for Partial Matching | 75  |

| 6.3   | Signa | ture Hardware                                      | 78  |

|       | 6.3.1 | Error Weight Count                                 | 80  |

|       | 6.3.2 | Failing Pattern Signatures                         | 80  |

|       | 6.3.3 | Failing Output Set                                 | 80  |

| Chapt | er 7  | Applications of Hierarchical Fault Diagnosis       | 82  |

| 7.1   | Stand | lard DAPPER                                        | 83  |

|       | 7 1.1 | Resolution With Detection Probability              | 84  |

|       | 7.1.2 | Modifications with Partial Matching                | 88  |

|       | 7.1.3 | Diagnosing Faults Within the DAPPER Hardware       | 91  |

| 7.2   |       | DAPPER                                             | 91  |

| 1.2   | 7.2.1 | Overhead Considerations                            | 92  |

|       | 7.2.2 | Modifications with Partial Matching                |     |

| 7.3   | k-Ma  | x DAPPER                                           |     |

| 1.0   | 7.3.1 | Estimating Test Lengths                            |     |

|       | 7.3.2 | Modifications with Partial Matching                | 97  |

|       | 7.3.3 | Pros and Cons                                      | 98  |

| 7.4   | Alias | ing Probability                                    | 99  |

|       | 7.4.1 | Cancellation Error                                 |     |

|       | 7.4.2 | Signature Aliasing                                 | 100 |

|       | 7.4.3 | Non-Unique Diagnosis                               | 101 |

| 7.5   | Fault | s and Fault Models                                 | 103 |

|       | 7.5.1 | DAPPER with Multiple Faults                        | 104 |

|       | 7.5.2 | Locating Unmodelled Faults                         | 105 |

| Chapt | ter 8 | Performance of Hierarchical Fault Diagnosis        | 107 |

| 8.1   | Com   | pleteness of Methods                               | 108 |

| 8.2   |       | ing of Methods                                     | 110 |

| 8.3   |       | onary Constructed in Advance                       | 110 |

| 0.0   | 8.3.1 | Dictionary Development Costs                       | 111 |

|       |       | Dictionary Storage Costs                           | 114 |

|       |       |                                                    |     |

|      | 8.3.3  | Dictionary Look-Up Costs                   | 115 |

|------|--------|--------------------------------------------|-----|

|      | 8.3.4  | Test Application Costs                     | 115 |

|      | 8.3.5  | Information Content                        | 117 |

|      | 8.3.6  | Effect of Partial Matching                 | 117 |

| 8.4  | Dem    | and-Driven Diagnosis, No Dictionary        | 118 |

|      | 8.4.1  | Start-up Costs                             | 118 |

|      | 8.4.2  | Run-time Costs                             | 120 |

|      | 8.4.3  | Information Content                        | 123 |

|      | 8.4.4  | Extensibility of Methods                   | 124 |

| 8.8  | Dem    | and-Driven Dictionary Construction         | 125 |

|      | 8.5.1  | Run-Time and Long Term Costs               | 125 |

| Chap | ter 9  | Experimental Results                       | 126 |

| 9.1  | Diag   | nosability with Detection Probability      | 127 |

|      | 9 1.1  | Set-Up and Procedure                       | 127 |

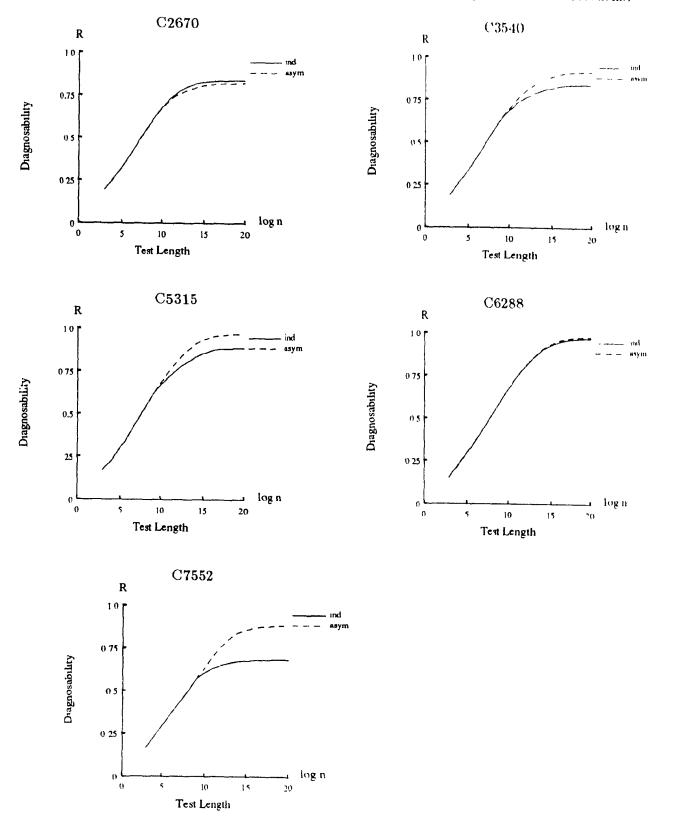

|      | 9.1.2  | Results                                    | 13  |

|      | 9.1.3  | Conclusions                                | 132 |

| 9.2  | Accu   | racy of Weight Prediction                  | 132 |

|      | 9.2.1  | Set-Up                                     | 133 |

|      | 9 2.2  | Procedure                                  | 133 |

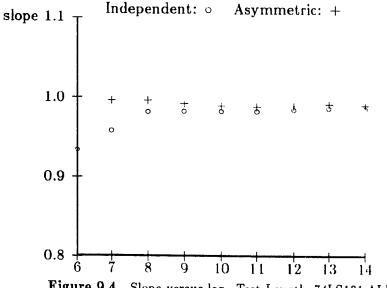

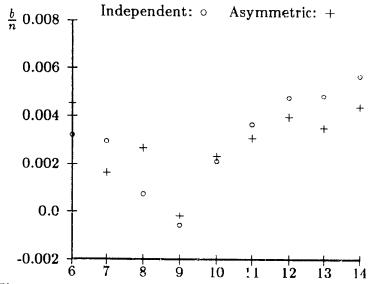

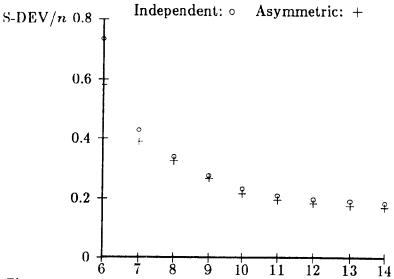

|      | 9.2.3  | Fixed Test Length                          | 133 |

|      | 9.2.4  | Variable Test Length                       | 139 |

|      | 9.2.5  | Effect of Detection Probability Estimation | 143 |

|      | 9.2.6  | Results                                    | 14  |

| 9.3  | Effor  | t Required for Fault Resolution            | 144 |

|      | 9.3.1  | Set-Up                                     | 14  |

|      | 9.3.2  | Procedure                                  | 14  |

|      | 9.3.3  | Fixed Test Length                          | 14  |

|      | 9.3.4  | Variable Test Length                       | 152 |

|      | 9.3.5  | k-Max DAPPER                               | 153 |

|      | 9.3.6  | Effect of Detection Probability Estimation | 15  |

|      | 9.3.7  | Results                                    | 150 |

| 9.4  | Inter  | mediate Signature Collection               | 15' |

| Chap | ter 10 | Conclusions                                | 160 |

| 10.  | .1 Ope | en Problems                                | 16  |

| Appen  | dix A  | A Aliasing Probability of Weight Counting | 162 |

|--------|--------|-------------------------------------------|-----|

| A 1    | II : C | -                                         |     |

| A.1    | Uniic  | orm Error Model                           | 163 |

| A.2    | Indep  | endent Error Model                        | 164 |

|        | A.2.1  | Exact Expression                          | 164 |

|        | A.2.2  | Asymptotic Behaviour                      | 165 |

|        | A.2.3  | Summary of Aliasing Behaviour             | 170 |

| A.3    | Asyn   | nmetric Error Model                       | 171 |

|        | A.3.1  | Exact Expression                          | 171 |

|        | A.3.2  | Asymptotic Behaviour                      | 172 |

|        | A.3.3  | Summary of Aliasing Behavior              | 173 |

| A.4    | Gene   | ralized Error Model                       | 174 |

|        | A.4.1  | Exact Expression                          | 174 |

|        | A.4.2  | Asymptotic Behaviour                      | 175 |

| Refere | nces . |                                           | 176 |

# List of Figures

| 2.1        | Hierarchy of Structural and Functional Circuit Models                 | 8           |

|------------|-----------------------------------------------------------------------|-------------|

| 2.2        | The RCT Environment                                                   | 18          |

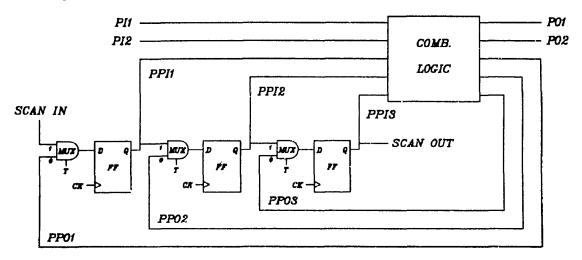

| 23         | Typical Scan Design                                                   | 24          |

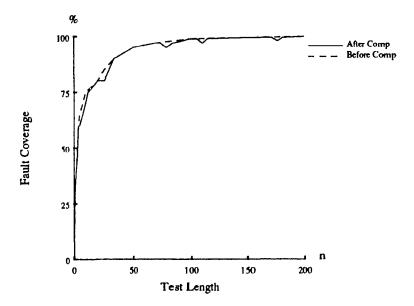

| 3.1        | Fault Coverage Before and After Data Compaction                       | <b>2</b> &  |

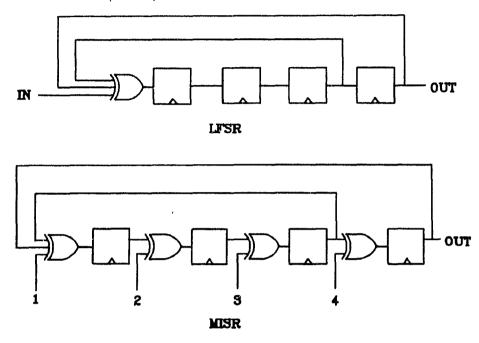

| 3.2        | Signature Analyzers, Feedback polynomial: $x^4 + x + 1 \dots$         | 32          |

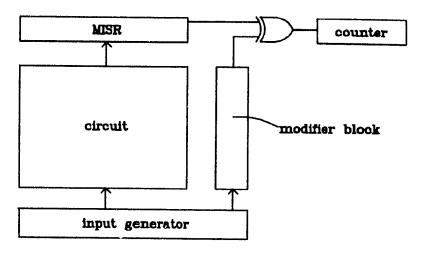

| 3.3        | Output Data Modification Setup                                        | 35          |

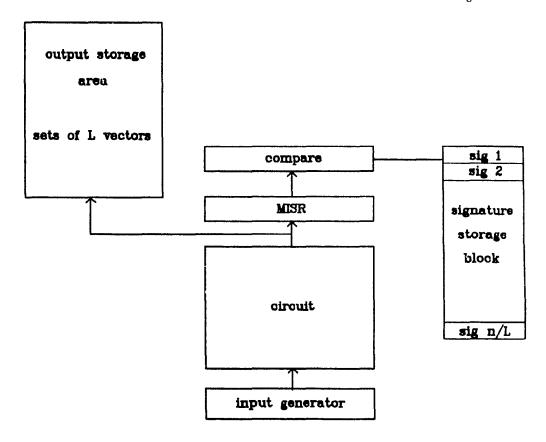

| 4 1        | Intermediate Signature Collection                                     | 39          |

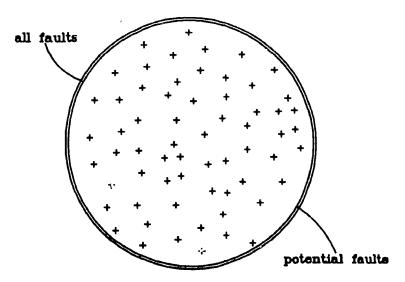

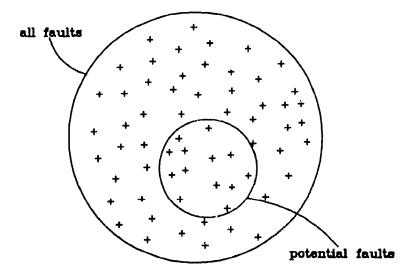

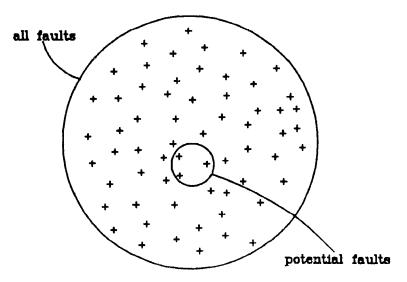

| 5.1        | Potential Faults, Pass/Fail Signature                                 | 45          |

| <b>5.2</b> | Potential Faults, After Coarse Resolution                             | 4ô          |

| 5.3        | Potential Faults, After Further Reduction                             | 46          |

| 5.4        | Potential Faults, Final Diagnosis                                     | 47          |

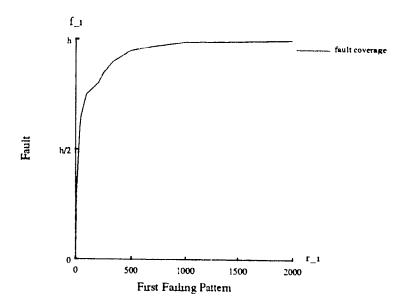

| 5.5        | First Failing Pattern or Fault Coverage Curve                         | 61          |

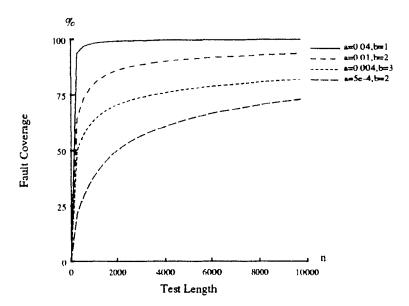

| 5.6        | Arctangent Model of Fault Coverage                                    | 62          |

| 5.7        | Fitting an arctangent curve to fault coverage                         | 63          |

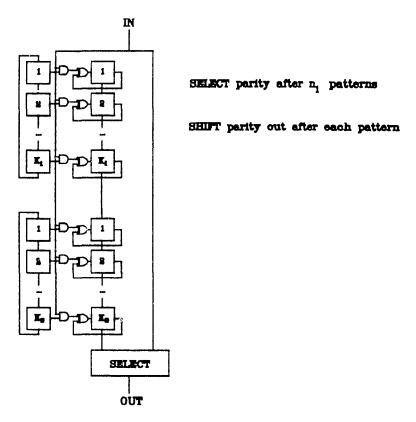

| 6.1        | Parity Block for Serial Streaming                                     | 68          |

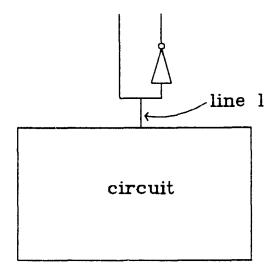

| 6.2        | Example Fault                                                         | 70          |

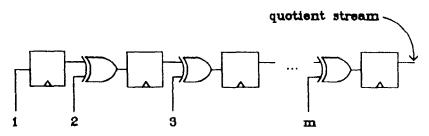

| 6.3        | MINSR Structure for P/S Compaction                                    | 71          |

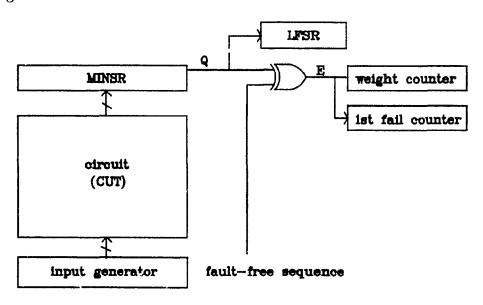

| 7 1        | The DAPPER Method                                                     | 83          |

| 7.2        | Ideal Scan DAPPER, $n_1 = n$                                          | 92          |

| 7.3        | Scan DAPPER, $n_1 \ll n \dots$                                        | 93          |

| 7.4        | Scan DAPPER with Hardware Constraints, $n_1 = 0$                      | 94          |

| 7.5        | k-Max DAPPER                                                          | 94          |

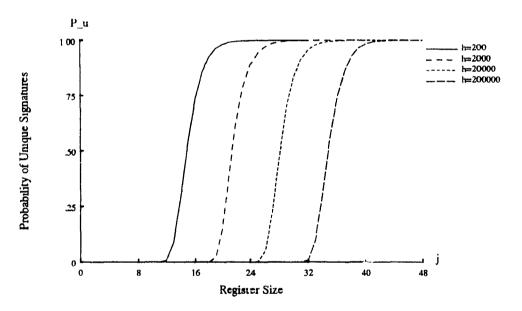

| 8.1        | Probability of matching signatures versus register size               | 109         |

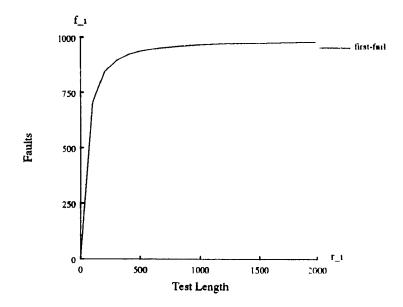

| 8.2        | Relative simulation effort with first-fail                            | 112         |

| 8.3        | Relative simulation effort with first-fail                            | 112         |

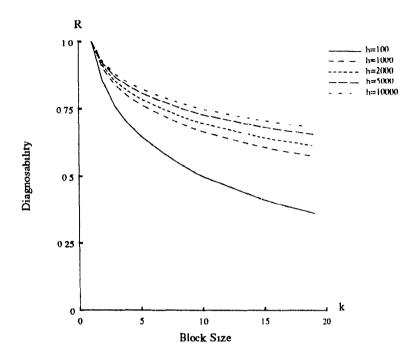

| 9.1        | Diagnosability versus Size of Groupings                               | 128         |

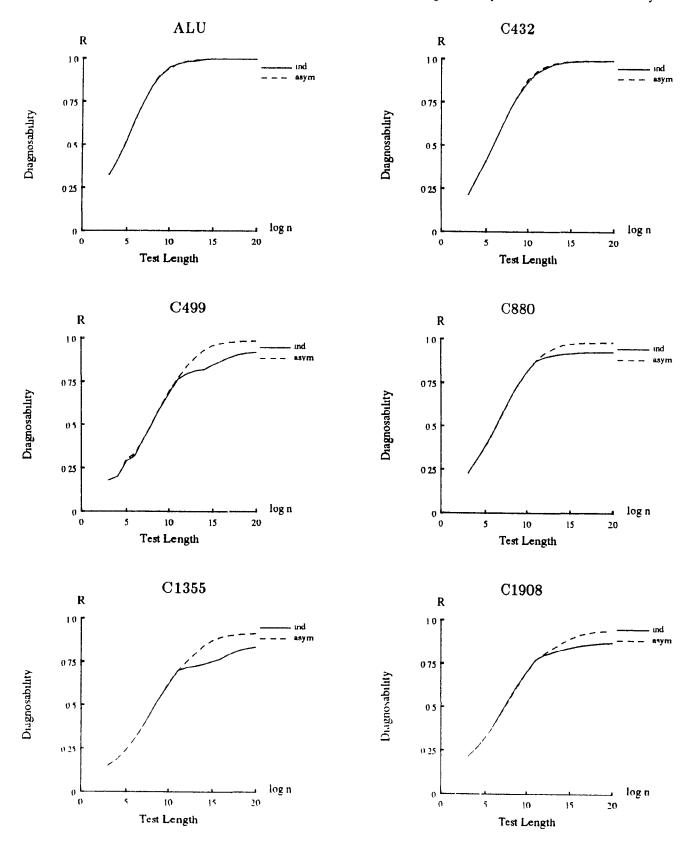

| 9.2        | Diagnosability Functions, part 1                                      | <b>12</b> 9 |

| 9.3        | Diagnosability Functions, part 2                                      | 130         |

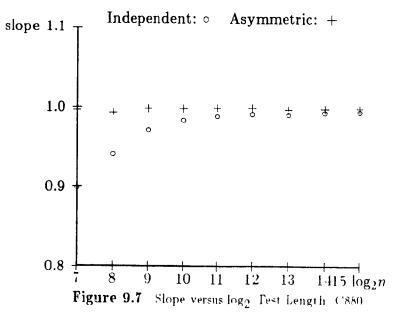

| 9.4        | Slope versus log <sub>2</sub> Test Length, 74LS181 ALU                | 140         |

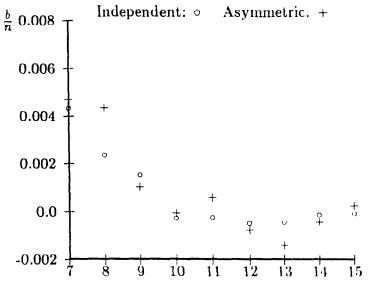

| 9.5        | Normalized Intercept versus log <sub>2</sub> Test Length, 74LS181 ALU | 140         |

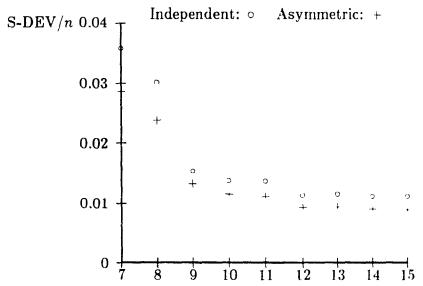

| 9.6         | Normalized Standard Deviation versus log <sub>2</sub> Test Length. 74LS181        |     |

|-------------|-----------------------------------------------------------------------------------|-----|

|             | ALU                                                                               | 141 |

| 9.7         | Slope versus log <sub>2</sub> Test Length, C880                                   | 141 |

| 9.8         | Normalized Intercept versus log <sub>2</sub> Test Length, C880                    | 142 |

| 9.9         | Normalized Standard Deviation versus log <sub>2</sub> Test Length, C880           | 142 |

| A.1         | Output regions in weight test                                                     | 163 |

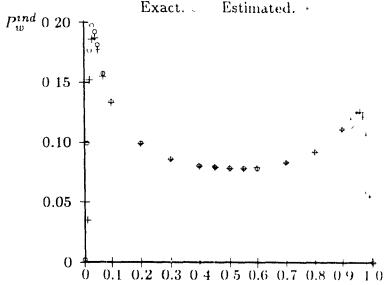

| A.2         | Weight Aliasing Probability $P_w^{ind}$ vs $p: n = 100, w = 49 \text{ or } 51$    |     |

|             |                                                                                   | 168 |

| A.3         | Weight Aliasing Probability $P_w^{ind}$ vs. $p: n = 100, w = 50$                  | 168 |

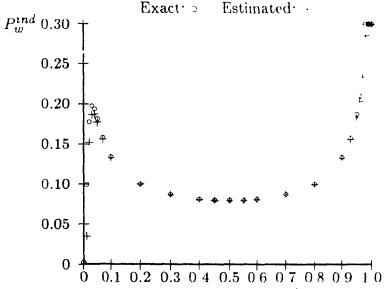

| A.4         | Weight Aliasing Probability $P_w^{ind}$ vs. $p: n = 100, w = 40$ or               |     |

|             | 60                                                                                | 169 |

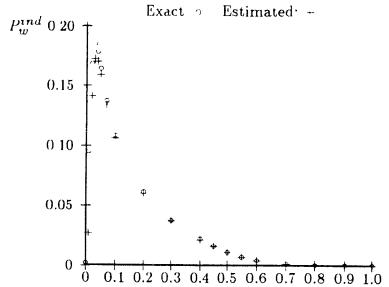

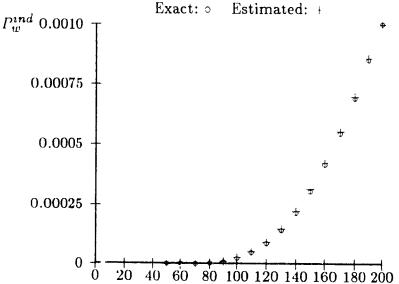

| <b>A.5</b>  | Weight Aliasing Probability $P_w^{ind}$ vs. $n$ :                                 |     |

|             | $ n-2w  = 40, \ p = 0.5 \ldots \ldots$                                            | 169 |

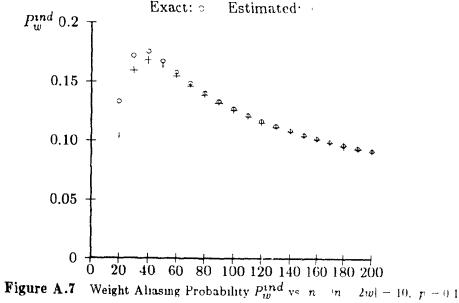

| <b>A.</b> 6 | Weight Aliasing Probability $P_w^{ind}$ vs. $n$ :                                 |     |

|             | $ n-2w =10, \ p=0.5$                                                              | 170 |

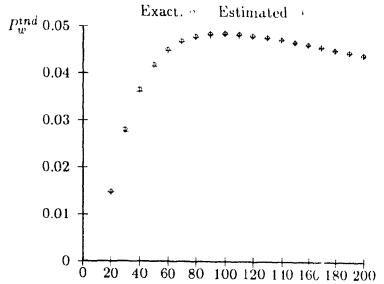

| <b>A.7</b>  | Weight Aliasing Probability $P_w^{ind}$ vs. $n$ :                                 |     |

|             | $ n-2w =10, \ p=0.1$                                                              | 170 |

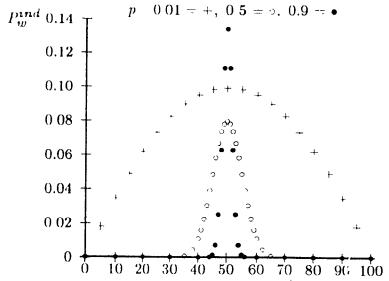

| A.8         | Weight Aliasing Probability $P_w^{ind}$ vs $w: n = 100$ , various $p \dots \dots$ | 171 |

# List of Tables

| 2.1  | Gate Behaviour in the Presence of Stuck-At Faults                    | . 9 |

|------|----------------------------------------------------------------------|-----|

| 5.1  | Determining coefficients for arctan model, knee at $(x, y)$          | 62  |

| 6.1  | Example functions for partial matching                               | 74  |

| 6.2  | Average Numbers of Cubes for Various Test Lengths                    | 77  |

| 6.3  | Size of Modifier Circuit for Various Test Lengths                    | 78  |

| 7.1  | Aliasing Behaviour, $P_w^{ind}$ , $n = 2048$ , $w = 95$              | 101 |

| 8.1  | Relative simulation effort, $n = 2048 \dots$                         | 113 |

| 8.2  | Sizes of various signatures                                          | 115 |

| 9.1  | Circuits Used in Experiments                                         | 126 |

| 9.2  | Undetected Faults After 2048 Vectors                                 | 134 |

| 9.3  | Accuracy of DAPPER Weight Predictions, 100% Matching                 | 135 |

| 9.4  | Accuracy of DAPPER Weight Predictions, Partial Matching              | 137 |

| 9.5  | Accuracy of DAPPER Weight Predictions, Serial Streaming              | 138 |

| 9.6  | Accuracy of DAPPER Weight Predictions, Various Probability Estimates | 143 |

| 9.7  | Fault Resolution, Standard DAPPER                                    | 146 |

| 9.8  | Total Equivalencies Found During Fault Location                      | 148 |

| 9.9  | Normalized Equivalencies Found During Fault Location                 | 148 |

| 9.10 | Fault Resolution, Standard DAPPER, Partial Matching                  | 150 |

| 9.11 | Fault Resolution, Scan DAPPER, $n_1 = n \dots \dots$                 | 151 |

| 9.12 | Fault Resolution versus Test Length, 74LS181 ALU                     | 153 |

| 9 13 | Fault Resolution versus Test Length, C880                            | 154 |

| 9.14 | k-max simulation, 2048 maximum length                                | 155 |

| 9.15 | k-max simulation, longer test lengths                                | 156 |

| 9.16 | Fault Resolution with Various Probability Estimates                  | 157 |

| 9 17 | Performance of ISC, $n = 2048$                                       | 158 |

| 9.18 | Maximum and Observed values for $r_{av}$                             | 159 |

### Claim of Originality

The author claims originality for the following contributions of the dissertation:

- Chapters 1 through 4 are largely review, although they are original in the sense

of providing a unified background to the field of fault diagnosis in randomly-tested

circuits employing data compaction (signature-tested circuits).

- Chapter 3 includes a description of the asymmetric error model which was proposed for built-in self-test by the author.

- Chapter 4 includes a novel set of criteria to be used when evaluating fault location methods for signature-tested circuits.

- Chapter 5 develops a new model for fault coverage curves, which permits the estimation of the relative effort required in fault simulation when faults are dropped after detection or simulated over an entire test set

- Chapter 5 proposes a hierarchical methodology for fault location in signature-tested circuits. The methodology involves a succession of reduction steps on an initial fault set and represents a marked departure from previous efforts in this area.

- Chapter 5 also suggests new signatures for random testing which contain useful fault location information, and develops a new technique for evaluating the location capability of these in the context of demand-driven fault diagnosis.

- Chapter 6 suggests circuit structures to implement these signatures. These adaptations are novel, with the exception of the partial sequence matching method suggested for reducing hardware overhead, which has been applied previously to the output data modification technique of built-in self-test. However, a new algorithm for producing a partial matching is developed

- Chapter 7 gives a detailed description of application techniques for hierarchical fault diagnosis, including expressions for expected values, variance, and aliasing

- probability of signatures. Together, these new methods are suitable for a widvariety of signature-tested circuits.

- Chapter 8 contains a detailed cost comparison between the proposed hierarchical

fault location method and two other methods previously proposed for fault location

in signature-tested circuits. To the author's knowledge, such cost evaluations have

never been reported for either of the previously-developed methods.

- Chapter 9 provides extensive experimental verification of the performance of the hierarchical fault location technique. Since the techniques are new, the evaluation is also novel.

- Appendix A gives exact and asymptotic expressions for the aliasing probability

of the weight counting BIST technique for both the independent and asymmetric

error models. Standard combinatorial techniques were used to derive these, but the

expressions themselves are new.

Chapter 1 Introduction

This dissertation develops a new method for performing fault diagnosis in combinational digital circuits tested with random or pseudo-random input vectors. Fault detection is accomplished using signatures from output data compaction, and fault location is performed hierarchically using each signature to reduce the fault set. The major contributions of this method include the development of signatures which contain useful circuit information, the ability to use this information for diagnosis, and the potential to implement the diagnosis hardware on the chip or module being tested. These properties allow the proposed method to overcome what has has previously been a major drawback to the use of data compaction techniques in fault diagnosis — the difficulty of performing fault location. The vocabulary of fault diagnosis as well as a brief introduction to the field are given in the following section.

### 1.1 Definitions

A typical digital circuit contains inputs, internal logic, and outputs. Digital signals, represented by a set of binary 1s and 0s called an input vector or input pattern, are applied at the inputs, and the internal logic's response, correspondingly referred to as an output vector or output pattern, is read at the outputs. If the output function of the circuit is determined solely by its present input vector, the circuit is called combinational If, on the other hand, the output function is determined by the sequence of input vectors applied, then the circuit contains memory and is termed sequential

Manufacturing digital circuits is a complex process, and, as a result, some of the circuits produced are faulty. A fault is defined as the cause of incorrect circuit behaviour Fault diagnosis for digital circuits can be defined as answering the question "Which, if any, faults are present in this circuit?" Fault diagnosis encompasses the testing of digital circuits, and is in fact composed of two subproblems: fault detection, "Is there any fault

present in this circuit?" and fault location, "Which of the many possible faults is (are responsible for the incorrect behaviour of this circuit?"

Fault diagnosis is needed during the manufacturing of digital circuits — whether the systems (computers and other machines) themselves, or the boards, cards and modules of which they are comprised, or the integrated circuits (ICs) or "chips" which in turn make up the boards. This distinguishes fault diagnosis from the problem of design verification, which answers the question "Does this design perform the function it is intended to perform?" Testing assumes that design verification has already been performed, so that if the circuit contains no faults it will implement the correct function.

The goal of fault diagnosis, naturally, is to find faulty circuits as early as possible in the manufacturing process. The cost of a fault increases by approximately an order of magnitude at each step of the process from silicon wafer to chip to package to board to system to shipped product [Wil83] The complexity of modern circuits has increased the difficulty of fault diagnosis to such an extent that testing now accounts for about a third of the cost of an IC [Bha89].

The faults to be diagnosed may be logical, which cause changes in a faulty circuit output function known as errors, or parametric, which cause some parameter of circuit operation, such as voltage level, timing, or capacitance, to degrade beyond the specified minimum level for the design. Faults may be permanent, transient (occurring only once), or intermittent (recurring). Faults may be either combinational or sequential in nature, independent of the circuit under test. Faults can result from either physical defects or electrical failures within the manufactured circuits. A circuit without any such failures is said to be fault-free.

The failures, or defects, are caused by a variety of physical phenomena: Many of today's chips contain elements which are smaller than  $1 \mu m$  — one millionth of a meter — across. These can have their properties altered by minor imperfections in the silicon, be destroyed by microscopic dust fragments, or be obliterated by tiny misalignments in the "masks" used to create them. Additional defects, such as extra or missing connections, can occur when the chips are packaged, and still more are possible when the chips are installed on circuit boards.\* Not all defects result in faults, only those which cause some sort of erroneous circuit behaviour. Fault diagnosis attempts to discover such behaviour and pinpoint its cause

<sup>\*</sup> For more information on IC defects, see [Rav81] [McC87]

<sup>†</sup> Certain faults, called redundant faults cause no observable change in circuit output on their own, but may cause errors if they occur together with other faults [Fri67].

This dissertation is primarily concerned with the diagnosis of permanent logical faults in combinational circuits. Where the results obtained may be applied to other forms of diagnosis, the fact is noted, but the primary focus remains.

### 1.2 Overview of Problem

As integrated circuits have increased in complexity, testing has become a significant production expense, and now represents on the order of one third of the total cost of an IC. The expense arises from both the hardware required to perform the tests, and the effort needed to develop them. The primary focus for fault diagnosis strategies has been deterministic test pattern generation (DTPG) techniques, where test stimuli are designed explicitly to detect (and possibly locate) modelled faults

In an effort to avoid the costs of DTPG, random test patterns have been proposed as an alternate testing method. A random or pseudo-random source generates input stimuli for the circuit under test, and faults are detected implicitly. A sufficiently long random test will contain test patterns which detect all faults detected by its deterministically generated equivalent. Random test sets are often considerably longer than deterministic test sets.

Data compaction techniques are often used in random testing in order to reduce the amount of data resulting from the large number of input patterns. Data compaction and random test stimuli can greatly simplify test generation and hence reduce test development costs. In addition, the hardware required by the methods is simpler than that needed for deterministic testing, so test application costs may be reduced, and test hardware may be included as part of the circuit under test. This last approach is known as built-in self-test (BIST). When the hardware is external, the technique is referred to as random compact testing (RCT).

One failing of both BIST and RCT has been that while fault detection is straightforward, fault location in the presence of data compaction has been difficult and expensive Fault location is required for repairable or fault tolerant systems, and also to evaluate and improve the manufacturing process for conventional circuits. Several techniques have been suggested previously, but none of these is able to satisfy all the requirements of such methods. This dissertation proposes data compaction techniques and a fault location method which meets these criteria, and in addition can reduce location effort significantly over the previous approaches

The essential feature of the proposed method is its hierarchical nature: the set of possible faults is reduced over a sequence of steps to include only those faults consistent

with the various observed circuit behaviours. The data compaction process ensure that useful information about faults present in the circuit is readily available — a result which has not been possible with conventional approaches.

### 1.3 Outline of Dissertation

The remainder of this dissertation describes the hierarchical fault diagnosis method in detail, and is organized as follows:

Chapter 2 provides a brief history of fault diagnosis, reviewing the literature on the subject as it has evolved and giving a general background to the field.

Chapter 3 reviews built-in self-test of circuits, and includes sections on error modelling and data compaction techniques, which apply to both self-testing and randomlytested circuits. These techniques provide a basis for the signatures proposed in this dissertation.

Chapter 4 reviews the methods which have been proposed previously for locating faults in a signature testing environment, which includes random input vectors and output data compaction. The chapter examines their relative advantages as well as their shortcomings, and concludes with set of criteria which must be met by any fault location method employing data compaction.

Chapter 5 introduces the hierarchical fault location method which is the focus of the dissertation. It also provides a formal methodology for analyzing and comparing fault location techniques. This is used to show the benefits of the hierarchical approach with a variety of possible signatures. In addition, a model for calculating the fault and compactor simulation effort required by dictionary construction is developed.

Chapter 6 discusses the physical structures necessary to observe the circuit parameters mentioned in chapter 5 as potential signatures. Tradeoffs between potential diagnostic resolution and the amount of hardware overhead are investigated.

Chapter 7 uses the signatures examined in chapter 5 and the structures of chapter 6 to develop sample applications of the hierarchical fault location method. The techniques apply to both random compact testing and built-in self-test and are examined in detail. Means of calculating expected values for each signature given an error model and fault detection probabilities are shown, and the uses of each of the sample applications are discussed

Chapter 8 compares the costs (including start-up and run-time costs in terms of time, space and hardware complexity) of the hierarchical fault location method with those of

the techniques reviewed in chapter 4. The superiority of the hierarchical approach a demonstrated for a variety of cost criteria and potential applications

Chapter 9 outlines some experiments conducted to validate the performance projections of earlier chapters. The circuits used belong to a standard set of combinational benchmarks.

Finally, chapter 10 concludes the dissertation and outlines open problems in the area.

# Chapter 2

Most literature on fault diagnosis is concerned with permanent logical faults. Parametric testing is important and has not been entirely ignored (see, for example, [Zas85] [Mal88] [Nig90]). Similarly, intermittent faults have been considered (e.g. [Bal69] [Yen69] [Kam75] [Sav80b]), but nonetheless the trend remains. This chapter reviews the progress of fault diagnosis in digital circuits throughout the last thirty years, showing the changes in methods and in the perception of the issues involved as circuit complexity has increased from logic gates constructed from vacuum tubes to today's ultra-large scale integration and beyond.

# 2.1 Early History

Initially, fault detection and fault location were essentially the same process. A circuit was given a test, which consisted of applying an input vector (for combinational circuits) or sequence of input vectors (for sequential circuits), then comparing the output vector(s) with some expected results. Each test would check for a particular possible physical failure [Tsi62] [Cha65]. However, many input vectors are able to test for several faults, even in simple circuits. So, lists were created, showing for every possible input vector the corresponding effect that each fault would have on the circuit output. These lists are called fault dictionaries. (The earliest reference appears to be [Tsi62], which refers to them as "maintenance dictionaries") These dictionaries were originally issued as books, and the individuals performing the tests would scan through them to diagnose any faults in the system they were observing. Even the earliest dictionaries were large — [Dow64] describes that of [Tsi62] as being 1200 pages long

As circuits became more complex, such dictionaries became impractical. A record of all possible faulty output values for all possible inputs is almost always an excessive and unnecessary amount of information for the diagnosis process. Throughout the 1960s,

work continued on reducing, or better, minimizing, the required dictionary size ([Ses62] [Ses65] [Cha65] [Arm66] [Kau68]). Fault diagnosis was frequently treated as an extension of the well-known boolean function minimization problem [McC56]. Such treatment required that the full dictionary be known, even if it was not physically produced. Its construction was assumed to be straightforward, as evidenced by this offhand remark in [Kau68]: "One has no difficulty in imagining that an analysis of [the circuit] has been conducted in order to determine the effect that each of various hypothetical faults has on its output." Today this is beyond imagination, even for combinational circuits Circuits with 75 inputs are not uncommon. Such a circuit has a total of 2<sup>75</sup> possible input combinations. If one billion of these combinations could be analyzed every second, it would take more than a million years to complete the dictionary. Each additional input would double both the generation time and the storage required

### 2.2 Test Sets

The excessive cost of calculating a complete dictionary led to a search for approaches other than minimization to the problem of generating smaller dictionaries. The smaller dictionary would list faulty responses only for a subset of possible input combinations called the *test set*. The vectors in a test set should both detect each potential fault and permit fault location. When developing a test set, both a circuit and its potential faults may be considered at various hierarchical levels of abstraction.

#### 2.2.1 Hierarchical Levels of Circuit Description

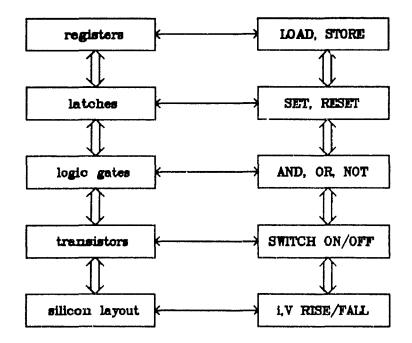

There are two main classes of circuit descriptions: functional and structural. A functional description of a computer register, for example, could contain a list of the various operations possible on it (load, store, add, etc.), while a structural model could list the transistors which made up the register and the interconnections and signals between them. Various of levels of description are possible for both functional and structural models. Registers may be combined into modules such as memories or decomposed into their constituent elements, called latches or flip-flops. Transistors may be grouped together to form gates performing logic functions such as AND. OR and NOT, or decomposed into the silicon and metal layers which form them. The hierarchical nature of these models is shown in figure 2.1. More information on digital circuit design may be found in [Man79] [Mea80] and [Wes85].

Figure 2.1 Hierarchy of Structural and Functional Circuit Models

### 2.2.2 Hierarchical Levels of Fault Description

The fault description depends on the circuit description. The idea of reading an incorrect address within memory has no direct meaning at the transistor level, and an electrical short between a transistor input and ground is similarly without direct meaning at the register transfer level, although both may describe the same physical failure. Test sets are designed to detect particular sets of faults which are determined by a fault model.

Most test sets are developed at the structural level rather than the functional level [Bha89], since structural tests are believed to be much more thorough than functional tests. The fault model most frequently used is the gate-level stuck-at model.

In the gate-level stuck-at fault model, inputs or outputs of logic gates within a circuit may be "stuck-at", i.e. permanently set to, either 0 or 1, which is analogous to being shorted to either ground or power respectively. Table 2.1 shows the behaviour of some common logic gates in the presence of stuck-at faults. The stuck-at model was introduced by Eldred in [Eld59] as a suggested fault model for testing logic gates comprised of vacuum tubes and diodes. While such gates have long since passed into history, the model remains. Various authors have since questioned its applicability, e.g. [Cle71] [Sus73] [Mei74] [Wad78a] [Gal80] [Wil83] [She85] [McC87], and additional models have been proposed, among them bridging faults [Mei74], where lines are shorted to one

| f   | AB | $oldsymbol{\mathbf{C}}$ | <b>A/0</b> | <b>A</b> /1 | B/0 | B/1 | C/0 | C/1 |

|-----|----|-------------------------|------------|-------------|-----|-----|-----|-----|

| AND | 00 | 0                       | 0          | 0           | 0   | 0   | 0   | 1   |

|     | 01 | 0                       | 0          | 0           | 0   | 1   | 0   | 1   |

|     | 10 | 0                       | 0          | 1           | 0   | 0   | 0   | 1   |

|     | 11 | 1                       | 0          | 1           | 0   | 1   | 0   | 1   |

| OR  | 00 | 0                       | 0          | 1           | 0   | 1   | 0   | 1   |

|     | 01 | 1                       | 1          | 1           | 0   | 1   | 0   | 1   |

| 1   | 10 | 1                       | 0          | 1           | 1   | 1   | 0   | 1   |

|     | 11 | 1                       | 1          | 1           | 1   | 1   | 0   | 1   |

| XOR | 00 | 0                       | 0          | 1           | 0   | 1   | 0   | 1   |

|     | 01 | 1                       | 1          | 0           | 0   | 1   | 0   | 1   |

|     | 10 | 1                       | 0          | 1           | 1   | 0   | 0   | 1   |

|     | 11 | 0                       | 1          | 0           | 1   | 0   | 0   | 1   |

Table 2.1 Gate Behaviour in the Presence of Stuck-At Faults

another, CMOS stuck-open [Wad78a] and transition faults [She85], based on extra or missing connections at the transistor level, and crosspoint faults [Smi79], which result from connectivity errors in PLAs. Nonetheless, the stuck-at model, and in particular the single stuck-at model, where at most one fault is assumed to occur within a circuit, remain the most popular [Bha89]. The most common justification for the continued use of the model is that complete tests for single stuck-at faults tend to be excellent tests for other types of faults as well [Wil83] [Raj85] [Jac86].

### 2.2.3 Quality Measurements

With the preponderance of methods available for generating test sets, it is necessary to have some means of comparing them. Besides the obvious criteria of test length and test generation time, the quality of the methods can be compared

#### 2.2.3.1 Fault Coverage

The fault detection capability, or fault coverage of a test set is usually defined as

Confusion over the number of modelled faults (including or not including equivalent faults, redundant faults, dominated faults, etc.) can affect the fault coverage value

[Aga80] [Cox88], but the measure remains useful.\* A test set is considered to be *complete* with respect to a fault model if all irredundant faults within the model are detected.

### 2.2.3.2 Diagnosability

The fault location capability of different test generation methods can also be compared. The size of the fault dictionary, complexity of creating it, and the resolution of the method are all important comparison criteria. Mandelbaum [Man64] has suggested using the entropy function of communication theory [Sha48] for resolution comparisons. This is the function used in this dissertation. For a diagnosis method which potentially divides the faults into N classes, the diagnosability function is given as:

$$R = -\frac{1}{\log h} \sum_{i=1}^{N} g(i) \log(g(i))$$

where

h = total number of modelled faults

$$g(i) = \frac{1}{h} \times \text{number of faults in class } i$$

and the indeterminate 0 log 0 is defined to be 0.

This function has minimum value 0 when all faults are in the same class, and maximum value 1 when each forms its own class.

#### 2.2.3.3 Relationships with Circuit Yield

The number of faulty circuits released for sale is exponentially affected by test quality, according to Williams and Brown [Wil81], who give the defect level, DL, of a group of manufactured circuits as:

$$DL = 1 - Y^{1-T}$$

where Y is the yield of the manufacturing process and T is the fault coverage of the testing process. High fault coverage is clearly an important property of any test set, particularly when process yield is low. For the formula to be accurate, it is important that the figure T be the coverage of actual failures, not necessarily the coverage figure from a particular fault model

<sup>\*</sup> Other fault cove. age measures based primarily upon circuit topology and likely failure points have been proposed, e.g. [Wad78b], but their technology-dependent nature has kept them from common use

### 2.3 Aspects of Automated Test Pattern Generation

In order to make the testing process more scientific, methods have been proposed to produce a test set automatically for a given circuit. Two classical techniques for this automated test pattern generation (ATPG) were characterized as test pattern generation and fault insertion by Susskind in [Sus73]. In current terminology, these are deterministic test pattern generation and random test pattern generation respectively. Despite the fact that most manufactured circuits contain sequential elements, much research has gone into investigating ATPG methods for combinational circuits. There are two reasons for this: First, test generation for combinational circuits is an easier problem, and second, scan techniques (see section 2.6) can convert a sequential circuit to a combinational one for the purpose of testing.

#### 2.3.1 Deterministic Test Pattern Generation

Deterministic test pattern generation (DTPG) does not require a physical implementation of the circuit. Instead, a test set is derived algorithmically based on a circuit description and a fault model. The fault coverage of this test set may be verified analytically or by simulation. The DTPG techniques investigated apply primarily to combinational circuits.

#### 2.3.1.1 DTPG Methods

Deterministic test pattern generation using the gate-level stuck-at model has existed since the early 1960s. The idea of path sensitization was reportedly in existence in 1961 [Arm66]. The D-Algorithm [Rot66] (and its extension to sequential circuits in [Bou71]), boolean difference [Sel68], PODE11 [Goe81], FAN [Fuj83], critical path tracing [Abr84], Socrates [Sch88], and CAMP [Raj90] are just some of the test pattern generation strategies developed over the years.

### 2.3.1.2 Complexity of Test Pattern Generation

The development of new test pattern generation schemes is largely devoted to developing heuristic methods. Test pattern generation for a single fault has been shown [Iba75] [Fuj82] to belong to a class of problems known as "NP-Complete" [Gar78], which are believed to inherently require an exponential number of steps to solve in the worst case, written  $O(2^n)$ ,\* where n refers to the size of the program input, in this case the

<sup>\*</sup> A function f(n) is said to be O(g(n)) iff  $f(n) \leq kg(n)$  for all  $n \geq n_0$ , where k and  $n_0$  are constants

number of circuit inputs. Thus, adding a single input to a circuit can potentially double the amount of time required to generate test patterns for it. The source of the complexity is reconvergent fanout. Lines called fanout stems branch and then later reconverge, causing correlation between gate input values

#### 2.3.2 Random Test Pattern Generation

Selecting test vectors at random has been proposed as a means of reducing the costs of deterministic test pattern generation. The original use of random test stimuli in automated test pattern generation was in fault insertion. Fault insertion [Sus73] involves physically inserting failures in a replica of the circuit to be tested, then running various inputs and noting when responses change. This of course requires physical access to the potential fault sites. There is typically no such access inside an IC \* Fault insertion for ICs requires the circuit to be modelled by a collection of simpler packages, usually TTL chips, each containing only a few transistors and implementing a small part of the circuit. A circuit such as Intel's i860 RISC processor [Per89] contains over 1 million transistors. The logistics of producing a fault-free TTL version, let alone inserting faults into it, are difficult to comprehend. Furthermore, important factors such as circuit timing often cannot be duplicated in a large-scale TTL model. For this reason, physical fault insertion is no longer a practical method of developing test sets. The concept remains, however, in random test pattern generation (RTPG) [Bre71] [Agr72] [Agr75]

RTPG mimics fault insertion by using fault injection coupled with fault simulation. A list of faults is generated using some fault model. These are injected into a circuit description whose behaviour is then simulated over a set of randomly selected input vectors. This simulation is used to see which, if any, faults are detected by each successive pattern, and only those patterns which detect a previously undetected fault are retained. The operation can terminate when a desired level of fault coverage has been achieved, or once a limit on the amount of effort to be expended has been exceeded. Despite a recent claim that RTPG has no value [Abr89], there remains a class of faults for which deterministic tests are difficult to generate, yet can be detected easily

Thus  $f(n) = 3n^2 + 2n + 4$  is O(g(n)) where  $g(n) = n^2$  since  $f(n) \le 10g(n)$  for all  $n \ge 1$

<sup>\*</sup> Election beam testers (see for example [Yan87] [Lee89]) offer physical observation of surface sites on a silicon chip, but do not offer the potential to temporarily insert failures into a working circuit. One manufacturer now offers individual site access as part of its gate array design [Swa89], but such efforts are rare and probably excessive.

by randomly-selected patterns. ATPG is often accomplished by using RTPG initially, followed by DTPG on the remaining undetected faults.

#### 2.3.2.1 Fault Simulation in RTPG

4

In simulation, circuit behaviour is determined algorithmically from a circuit description. Simulation of a fault-free circuit is known as circuit simulation, while simulation where a fault has been injected into a circuit description is called fault simulation. Simulators have progressed from rudimentary parallel fault simulation [See65], where all faults are simulated in parallel for a given input pattern, through deductive simulators [Arm72] and the related concurrent simulators [Ulr74], where divergences between faulty and fault-free values are deduced logically, to parallel pattern single fault simulators [Wai85], where the word length of the simulating processor is used to obtain a reduction in the simulation time, to those employing stem regions [Maa88] [Maa90], which take advantage of circuit structure in order to speed execution.

### 2.3.2.2 Complexity of Fault Simulation

Simulating one fault for one input pattern is believed to require  $O(G^2)$  steps in the worst case [Goe80] [Har87],<sup>†</sup> where G here refers to the number of gates within a circuit. As in section 2.3.1.2, the source of the complexity is reconvergent fanout—while doubling the number of circuit gates can quadruple simulation time.

While this worst case complexity is retained by all simulators, actual simulation time can vary immensely between methods. The use of heuristics, parallelism, and circuit information all aid in reducing execution time. The fastest simulators are those which are designed exclusively for combinational circuits and stuck-at faults [Wai85] [Maa88]. An expanded fault model or simulation over sequential circuits requires other algorithms, such as those listed above, which tend to be slower in combinational simulation.

Fault simulation has become so expensive that special purpose computers, called hardware accelerators, have been developed for the express purpose of performing simulations. Overviews of these are given in [Bla84] and [MuE90]

### 2.3.3 Deterministic Fault Location Techniques

The ATPG techniques discussed so far have tended to emphasize fault detection as

It is shown in [Har87] that if fault simulation could be performed in linear time (O(G)), then the product of two  $m \times m$  matrices could be obtained in  $O(m^2)$  time. All common algorithms for this operation [Aho74] are  $O(m^3)$  complexity. No known algorithm is  $O(m^2)$

a primary goal over fault location. This shift in perspective results from manufacturing considerations. In terms of producing a fault-free product, manufacturers are typically interested in locating failures down only to the smallest replaceable component, usually an IC [Sus73] [Bat76], while remaining able to detect any failure which may occur. Individual failure location within an IC is less important for immediate production and shipping of circuits than it is for improving circuit design and the manufacturing process itself by providing some feedback about weak points. Once these have been identified, corrective action may be taken and process yields can improve. Such feedback between the design and production divisions of a circuit manufacturer characterizes a "living process" according to Parker [Par87], who states that such processes are more profitable than conventional static processes.

Although much research effort is devoted to fault detection, fault location nonetheless remains an important topic. An important example of the need for reliable fault location is the Thermal Conduction Packaging technique, where large numbers of die are mounted on a single wafer [Blo82]. The entire Thermal Conduction Module (TCM) behaves as a large combinational circuit during test mode [Cur83]. Fault location is required for both module repair (by replacing faulty silicon die) and for tracking repetitive failure mechanisms. Both problems can be solved simultaneously by locating faults to individual circuit elements [Cur83]. While TCM circuits have the complexity of boards, conventional board diagnosis methods cannot be applied to them. Fault diagnosis in such systems is a major motivation of this dissertation

Fault dictionaries have been proposed by many authors as reasonable tools for fault location. However, dictionary methods can fail when a multiple fault model is used. Consider, for example, a circuit with L lines. Neglecting fault equivalence, there are 2L possible single stuck-at faults within the circuit. In a multiple stuck-at fault model, every line can be in one of three states: fault-free, stuck-at 1, or stuck-at 0. The total number of multiple stuck-at faults is thus  $3^L - 1$ . This number is completely beyond comprehension for circuits with thousands of lines. Hayes [Hay71] showed that fault equivalence reduces this number to less than  $2^s$ , where s is the total number of inputs to all the fanout-free subsections of the circuit, but even this number is usually far beyond enumeration ability.

Thus, no fault dictionary can be constructed to include all multiple faults. Since multiple faults can mask the behaviour of single faults, a single fault dictionary, even if lists every failing pattern for every fault, may not always be useful. When multiple faults can occur in circuits, a fault location technique should provide some means of

dealing with them. A variety of such methods have been proposed.

Some authors have attempted to determine multiple fault coverage through enumeration, for example by solving boolean equations resulting from test data [Bos71] Eventually, however, the sheer number of faults will render such techniques unusable It is possible to reduce the complexity by ignoring faults with greater than a certain multiplicity. This approach has intuitive appeal, since circuits containing more than a few faults have failed catastrophically — knowing which lines are responsible may not be overly beneficial. Of course, the definition of "few" will depend on the size of the circuit, its fault-tolerance, and the frequency with which such catastrophic failures occur. A problem with any such explicit enumeration is that the number of faults in the dictionary is likely to be far greater than the number actually observed in practice during the circuit's lifetime. In a sense, the effort expended to create the unused entries has been "wasted" [Abr80]

Another approach is that advocated by Abramovici and Breuer [Abr80] and more recently by Rajski and Cox [Raj87], of implicit multiple fault diagnosis by identifying lines which can be shown to be fault-free. The faults are then isolated to the remaining lines. The basic premise of the methods is that any line which can be shown to have had a transition is known to be neither stuck-at 0 nor stuck-at 1. The CERBERUS system of [Raj87] extends the idea to include multiple stuck-open and delay faults, by noting, for example, that if a 0 \rightarrow 1 transition can be shown to have occurred, then the line cannot have a slow-to-rise fault. While the methods of both [Abr80] and [Raj87] are pessimistic, in that they may not locate all fault-free lines, they are able to give a set of lines which is known to contain any modelled faults which have occurred.

All the methods in this section are fault model dependent. Most employ only the multiple stuck-at fault model. CERBERUS [Raj87] adds stuck-open and delay faults to its basic fault set. None of the models includes bridging faults (since any line could be bridged to any other, the number of multiple bridging faults could be, depending on symmetry and transitivity constraints, as great as  $O(2^{(L-1)^2})$  ) or intermittent faults, whose presence could invalidate conclusions as to presence or absence of faults on given lines.

The use of layout-dependent fault models may permit a single fault model to be retained. This is the approach of Inductive Fault Analysis [She85], proposed by Shen et al. as an alternative to the layout-independent fault models noted previously. In this technique, silicon point defects are simulated to determine their effect on the electrical characteristics of their surroundings. Those which cause faulty behaviour are retained

in a fault list. This list is collapsed to eliminate as many duplicates as possible. The number of defects which collapse into a particular faulty behaviour is used as an indicator of the relative probability of that failure occurring. Since single point defects can manifest themselves as multiple stuck-at or stuck-open failures, Shen et al. claim that their single defect analysis is sufficient for most failures. A fault dictionary could be developed using this method, providing a circuit-based and thus potentially more accurate diagnosis tool.

Expanding the fault model permits diagnosis of more potential faults, but at an increased cost. Tradeoffs between the costs of fault location and the benefits of increased potential resolution must be evaluated. In some cases, a simpler fault model with fast, inexpensive diagnosis may be preferable to a more costly, but complete, model, while in other cases the reverse may be true.

### 2.3.4 Testing Equipment

As circuit complexity has increased, so has the complexity of circuit testing equipment. Testers have become more and more expensive as they have progressed from ad hoc devices assembled for a given circuit design, to internally developed general testing devices, to a wide variety of commercially available models which now form their own industry. A good history and general description of these is available in [Par87]. Circuit testers suffer from two major problems: expense and performance. Testers can cost millions of dollars, yet can never match the state of the art in component speed, since the tester is an "old" design by the time it reaches the market. The performance factor is usually offset by differences in device technologies. For example, CMOS, a common device technology, tends to be much slower than ECL, so CMOS testers are often implemented in ECL.

# 2.4 Use of Exhaustive Testing in Fault Diagnosis

An exhaustive test is guaranteed to detect all combinational faults in a circuit (not necessarily sequential faults, such as stuck-open or delay faults). For this reason, some authors, e.g. [Sed79] [McC81], have suggested the use of these test sets in fault diagnosis.

Since exhaustive tests are not feasible for circuits with more than about 20 inputs, patitioning techniques to allow exhaustive excitation of subcircuits have been developed. Some examples of these pseudo-exhaustive techniques may be found in [Boz80] [McC81] [Ude88]. The bibliography in [Ude88] provides a good overview of research efforts in exhaustive and pseudo-exhaustive testing.

An exhaustive or pseudo-exhaustive (also known as a verification test [McC87]) can require extremely long test lengths, on the order of millions of test vectors. As a result, some form of output compaction is required. Methods of performing this compaction are investigated in section 3.5. Exhaustive testing avoids the costs involved in determining the quality of test sets and allows for simpler testing equipment than ATPG, but at the expense of additional test time.

### 2.5 Use of Random Vectors in Fault Diagnosis

Selecting patterns at random has been proposed as a way to avoid both the expense of generating deterministic test patterns and the exponential test lengths of exhaustive testing [Bre71] [Agr72] [Bas73] [Sus73] [Agr75] [Dav76]. In most cases patterns are selected in some pseudo-random fashion,\* both for ease of generation and in order to avoid repeats. Two common pseudo-random generating techniques are linear feedback shift register (LFSR) sequences [Pet72] [Gol67] and cellular automaton (CA) sequences [Wol83] [Hor89], each of which can generate, in a deterministic but apparently random order, a maximal sequence of input patterns [Pet72] [Ser88]. Two options are available when random or pseudo-random input patterns are employed: One, RTPG, retains only those patterns which detect a previously undetected fault and has already been examined (see section 2.3.2); while the other applies all patterns and provides the basis for random pattern test.

#### 2.5.1 Random Pattern Test

In random pattern test (RPT), the test is made sufficiently long to detect a high percentage of faults with high probability. (Savir et al [Sav84] suggest detection of 98% of the faults with 99.9% probability. The confidence level comes from the use of testability measures, which are discussed in section 2.5.3) Fault coverage of individual patterns is not determined, resulting in a reduction in fault simulation cost at the expense of added test application time. When an LFSR or CA is used to generate the input patterns, some of the complexity of standard testers may be avoided. Without simulation, however, the fault coverage of the test set can only be estimated, no fault

<sup>\*</sup> Pseudo-random vectors are able to pass some tests for randomness, but are characterized by the repeatability of the sequence, and often by a lack of repetition in the patterns themselves

<sup>†</sup> A maximal sequence of n-bit vectors is of length  $2^n - 1$ , since the all 0 pattern forms its own sequence. Adding the all 0 pattern to a maximal sequence produces an exhaustive sequence. Some methods of adapting LFSRs to produce exhaustive sequences are given in [McC86] and [Wan86].

dictionary can be constructed, and fault location cannot be performed. (Simulation over a fraction of the fault set has been proposed as a means of estimating coverage with reduced effort [Jai84]). These random pattern test sets tend to be longer by several orders of magnitude than their deterministic equivalents [Sus73] [Chi87], although this additional length may allow them to detect some unmodelled faults that would be missed by a shorter deterministic test set. Recent experiments by Maxwell [Max89] have documented the existence of such faults in actual manufactured circuits.

When RPT is used, several choices are available for analysis of the circuit output. The results may simply be compared against the fault-free response (from simulation), a reference or gold unit may be used [Dav76] [She77],\* or finally the output may be compacted into a more manageable size [Los78]. This last alternative is known as random compact testing.

### 2.5.2 Random Compact Testing

Random compact testing (RCT) employs data compaction, a process which records some attribute (or set of attributes) of an output sequence. This attribute is known as the sequence's signature, and is typically orders of magnitude smaller than the original sequence, e.g., a 32 bit signature for a sequence several million bits in size.

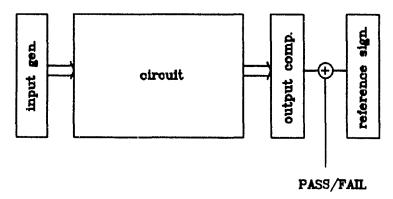

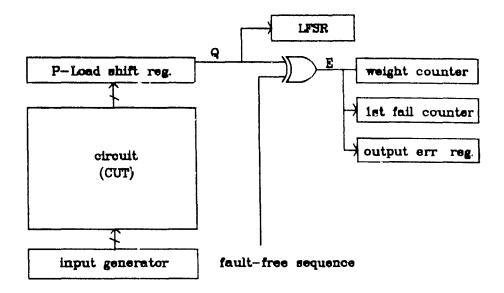

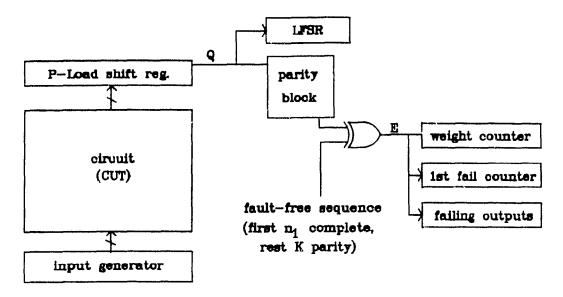

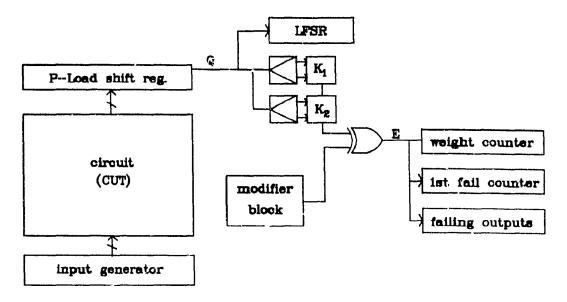

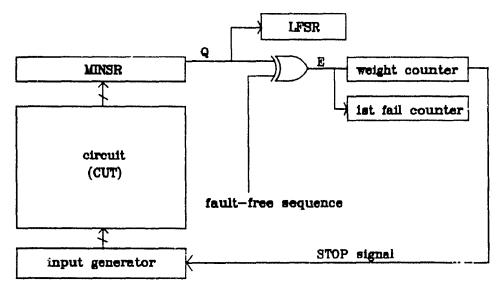

The RCT environment consists of a psuedo-random input generator, the circuit under test, a response compactor, and a comparator to match the observed signature with its expected (fault-free) value. This set-up is shown in figure 2.2.

Figure 2.2 The RCT Environment

The input generator is typically an LFSR, but potentially a cellular automaton (CA) or similar structure, or may be a pseudo-exhaustive structure, such as a counter or

<sup>\*</sup> Of course, the use of a reference unit begs the question of how such a device is known to be fault-free

maximal length LFSR or CA. The RCT environment is also used in another technique, referred to as built-in self-test. More information on data compaction techniques is given in section 3.5.

### 2.5.3 Fault Detection Probability

When testing is performed with randomly or pseudo-randomly selected test patterns, test length is determined by the *detection probability* of the faults in question. This probability can be defined for a given fault f as:

$$p_f = P(\text{Randomly selected pattern detects } f)$$

If each pattern has equal probability of being selected, the fault's detection probability is thus:

$$p_f = \frac{N_f}{2^l}$$

where  $N_f$  patterns detect the fault and l is the number of circuit inputs.

The test length required for a random test can be determined from a fixed non-detection probability threshold  $P_{nd}$  for the "hardest" fault — the one with the smallest detection probability. David [Dav76] suggests choosing test length, n, so that the "detection uncertainty",  $P_{nd}$  or the probability that the hardest fault within the circuit will escape detection, of the circuit is reduced to some desired value. Thus, given

$$p_{min} = \min_{\text{all } f}(p_f)$$

and a fixed threshold  $P_{nd}$ , test length can be determined from

$$(1-p_{min})^n \leq P_{nd}$$

so

1

$$n \geq \frac{\log(P_{nd})}{\log(1-p_f)}$$

The use of pseudo-random, rather than random, vectors complicates the problem somewhat [Chi87] [Wag87], although the overall test length is often reduced

Detection probability is important in RTPG as well, since the test length in RPT is roughly equivalent to the number of patterns likely to be simulated before a complete test set is found. Detection probability is one of numerous testability measures which have been proposed, e.g. [Gol79] [Brg84] [Set85] [Kri86] [Set86]. Testability measures are intended to give some idea of the amount of effort which will be required for test

generation, without actually generating any test. Circuits which are labelled difficult to test may then be redesigned in order to make them more easily testable. As has been pointed out in [Agr82] and [Sav83], testability measures may be of limited use in deterministic test pattern generation, but they remain important in all facets of random testing (one testability measure, test counting [Ake89], is claimed by its authors to be more useful in deterministic test generation than in random testing). Most of these measures can be converted to detection probability in a straightforward manner, so no further distinction will be made between them.

Calculation of exact detection probabilities for each fault is a time consuming operation. It has in fact been shown to be a #P-complete problem [Kri86].\* The method described in [Par75a] [Par75b] gives exact results, but a fault may require exponential time in the worst case.

The difficulties involved in exact calculation of these probabilities have led to a variety of approximate methods. Reconvergent fanout again is the source of the complexity, (without it, computing detection probabilities is a linear algorithm in the number of circuit lines, L), and is handled in different ways by different algorithms. The simplest, COP [Brg84], ignores it entirely, and has O(L) complexity as a result. The algorithm in [Kri86] uses repeated applications of a slightly modified COP strategy to eliminate the first-order effects of input reconvergence. Other algorithms attempt to eliminate the reconvergence through the use of "supergates" [Set85] [Set86], which treat fanout regions as individual gates, perform exhaustive analysis on them, and use the linear algorithm everywhere else. Such algorithms give exact results but retain the worst-case exponential time complexity. The "cutting algorithm" in [Sav84] provides bounds on detection probability, although these can be very weak [Gae86]. Statistical methods have also been developed, whether with fault simulation [Wai85] [Bri86], or without [Jai84]. More comprehensive reviews of these methods may be found in [Hui88] and [Pat90].

Throughout this dissertation it is assumed that random-pattern detection probability, whether exact or estimated, is available for each fault. No attempt is made to add to the wealth of information already available on its calculation

<sup>\*</sup> Similar to NP-complete problems, only the number of solutions, rather than the existence of a solution, is sought [Gar78] Since the number of solutions may be exponential, guessing these in one step would still not help, as the time required to verify them would remain at least  $O(2^n)$  using known algorithms

### 2.5.4 Random Pattern Resistant Faults

There are certain types of faults which have very small detection probabilities, and hence require long random test lengths. These are known as random pattern resistant faults. Totton and Shaw [Tot88] give four main causes of random pattern resistance

- Redundancy: These faults cannot be detected by any test pattern, and hence have detection probability 0.

- Reconvergent famout: Fault effects on reconvergent paths can cancel one another out.

- High fan-in: It may be difficult to set values which will permit propagation

- Test vector quality. Correlation between successive patterns, especially from an LFSR, may make detection more difficult.

Since random pattern test length is usually determined by the lowest detection probability in the circuit, random pattern resistant faults are a serious problem. One potential solution is biasing the random selection algorithm.

### 2.5.5 Weighted Random Patterns

Detection probability of random pattern resistant faults, and consequently the length of a pseudo-random test sequence, can be altered through the use of biased or weighted random patterns [Sch75] [Sav84] [Wun87] [Wai88] [MuF90]. These change the selection probability of each input vector in an effort to make the hardest faults more easily testable. The weighting algorithms typically focus on individual inputs, giving a fraction of the time for which each input will be 1 (this fraction will be  $\frac{1}{2}$  for an unbiased input). These biases can be used by the methods of section 2.5.3 to obtain estimates of detection probability.

Weighted random patterns offer other advantages in addition to shorter test lengths, notably the potential to detect faults more frequently than they would be detected by an unweighted set. Varying degrees of success have been reported recently [Wun87] [Wai88], and although to date no provably optimal strategy for selecting the biasing method has been reported, the use of biased vectors can reduce random test lengths by several orders of magnitude [MuF90]

#### 2.5.6 Fault Location with Random Vectors

Fault location when pseudo-random test vectors are employed has long been considered a difficult problem [McA87]. This dissertation proposes a solution, which is

discussed in later chapters. A brief overview of the problem is given here — a detailed review of previously proposed techniques for fault location in the random compact testing environment is given in chapter 4.

When simulation is not performed to validate the performance of a test set, no dictionary is generated. Creating one is an expensive process, again with effectiveness and cost factors in the choice of fault models. Faults can be diagnosed by performing circuit analysis or simulation after the fact in an effort to construct the dictionary entries for the fault(s) observed [Arz81]. Without excellent search techniques, there will be little saving in simulation time over the initial generation of a fault dictionary for the entire fault set and all input patterns, especially if data compaction is used. Whether the fault dictionary is constructed in advance, or in a demand-driven fashion, fault simulation is the largest cost component in fault location in the RCT environment.

### 2.5.6.1 Complexity of Fault Simulation

The major expense in generating complete fault dictic raries for use with random testing is fault simulation. These dictionaries, especially in RCT, require the generation of every output bit for every fault. As mentioned in section 2.3.2.2, fault simulation is believed to inherently require  $O(G^2)$  steps, where G is the number of gates in the circuit, for one input vector and for one fault. For an n vector test on an m output circuit, the complexity for h distinct faults and n input vectors is certainly not less than O(hmn). This requirement of full fault simulation to produce complete output functions eliminates many of the "tricks" used by fault simulators in an effort to reduce simulation time.