In compliance with the Canadian Privacy Legislation some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

## Low-Voltage Integrated RF CMOS Modules and Frontends for 5GHz RF Applications

by

Koon Hung Lee, B.Eng. 2000

Department of Electrical and Computer Engineering McGill University, Montreal, Canada.

March, 2003

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment for the requirements for the degree of Master of Engineering.

© Koon Hung Lee, 2003

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-88371-X Our file Notre référence ISBN: 0-612-88371-X

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

### Abstract

As the demand for wireless communications increases, high speed and low cost electronics are desired. Traditionally, RF circuits are implemented using high performance technologies such as GaAs or SiGe in order to minimize noise and achieve high gain. However, those high performance processes are incompatible with mainstream digital circuitry, which are usually implemented in CMOS technologies.

In this thesis, an RF receiver frontend which consists of a differential low noise amplifier, active mixers, passive mixers, and a quadrature voltage-controlled oscillator, for 5 GHz applications are designed and manufactured in a digital CMOS process, in order to demonstrate the RF potential of CMOS processes. We explore the use of simple circuit topologies and common packaging to build CMOS receivers that can operate from 1V supplies and lower, while providing reasonable image rejection without the use of any special image rejection filters. In addition, a high image rejection receiver is explored after designing it based on good and simple frequency planning.

Apart from inductors and capacitors, transformers are very useful passive components in RF applications. For example, transformers can act as on-chip single-ended to differential converters. In this thesis, a comprehensive study of transformer modeling is presented and discussed. A modeling program has been developed, and its accuracy verified through measurements of several transformer prototypes fabricated in a variety of state-of-the-art CMOS technologies. The program allows the generation of compact lumped transformer models to be used in circuit simulation.

### Résumé

A cause de l'augumentation de la demande pour la communication sans fil, électronique de vitesse haute et de coût bas sont désirés. Traditionnellement, RF circuits sont réalisés en utilisant des technologies de haut performance telle que GaAs ou SiGe dans le but de reduire le bruit et obtenir le gain haut. Cependant, ces procédés de haut performance sont incompatibles avec le circuitry courant dominant numérique, qui sont habituellementdans réalisés dans technologies CMOS.

Dans cette thèse, un récepteur RF frontend, qui consiste en un amplificateur différentiel de bruit bas, des mixeurs actifs, des mixeurs passifs, et un quadrature voltage -contrôlé oscillateur, pour 5GHz applications sont conçus et sont fabriqués dans un procédé CMOS numériques. Nous explorons l'emploi de circuit simple topologies de circuit simple et emballage commun à bâtir récepteurs CMOS qui peuvent opérer 1V de ravitaillements ou moins, en même temps en fournissant le rejet raisonnable d'image sans l'emploi aucuns filtres spéciaux de rejet d'image. En outre, un récepteur de rejet d'image haut est exploré basé sur une planfication de fréquence qui est bien et simple.

A part des inducteurs et des capaciteurs, les transformateurs sont des composants passifs très utiles dans les applications RF. Par exemple, transformateurs peuvent agir comme sur-puce seul-terminait aux convertisseurs différentiels. Dans cette thèse, une étude compréhensive du modéle de transformateur est présentée et discutée. Un modéle de programme a été développé et son exactitude est vérifié par des mesures de plusieurs

prototypes de transformateur fabriqués dans une variété d'état technologies CMOS. Le programme permet la génération de modèles de transformateur compacte à être employés dans la simulation de circuit.

### Acknowledgments

This thesis is dedicated to my grandmother who taught me multiplication table when I was three years old, and also to my grandfather who always reminds me that I should always strive to excel. Without them, the door to my scientific mind would have not be opened and I shall treasure everything that they gave me for the rest of my life.

I need to thank my supervisor, Prof. El-Gamal, for giving me the opportunity to study RF at McGill, and his guidance during this research. I also need to thank Ahmed and Ramez for their help. Without them, my life in McGill would have been a lot harder.

I wish to acknowledge the Canadian Microelectronics Corporation (CMC) for technology and equipment access, and Quebec's Government FCAR award for financial support.

I also need to thank my girlfriend, Sandy, for helping me to rediscover the lovely world outside the lab. Last but not least, my deepest appreciation to my parents and my sister, Kit Yue. No matter what happens to me, they are always my perfect fans.

# **Table of Contents**

| Abstra     | ct                                                |                                                                                      |                       |

|------------|---------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|

| Résum      | ć                                                 |                                                                                      |                       |

| Acknow     | wledg                                             | ments                                                                                | V                     |

|            |                                                   | ntents                                                                               |                       |

|            |                                                   |                                                                                      |                       |

| LIST OF    | rigui                                             | res                                                                                  | IX                    |

| List of    | Table                                             | es                                                                                   | Xİİ                   |

| Chapte     | er 1:                                             | Introduction                                                                         | 1                     |

| 1.1        |                                                   | luction                                                                              |                       |

| 1.2        | Motiv                                             | vation                                                                               | 2                     |

|            | 1.2.1                                             | State-of-the-art RF receiver frontends                                               | 2                     |

|            | 1.2.2                                             | Integrated transformers                                                              | 5                     |

| 1.3        | Thesi                                             | s Contributions                                                                      |                       |

| Chapte     | er 2:                                             | Wireless Receivers Architectures                                                     | 9                     |

| 2.1        |                                                   | ver performance metrics                                                              |                       |

|            | 2.1.1                                             | Noise figure                                                                         |                       |

|            | 2.1.2                                             | Distortion                                                                           |                       |

|            | 2.1.3                                             | Image-rejection ratio                                                                | 13                    |

| 2.2        | High:                                             | integration receivers architectures                                                  |                       |

|            | . خەرخى خىد ش                                     | micgianon toolvers are mootures                                                      |                       |

|            | 2.2.1                                             | Direct conversion (Homodyne)                                                         | 14                    |

|            | ~                                                 |                                                                                      |                       |

| 2.3        | 2.2.1<br>2.2.2                                    | Direct conversion (Homodyne)                                                         | 16                    |

|            | 2.2.1<br>2.2.2<br>Concl                           | Direct conversion (Homodyne)                                                         | 16<br>19              |

|            | 2.2.1<br>2.2.2<br>Concler 3:5                     | Direct conversion (Homodyne)  The two-IF receiver topology usion                     | 16<br>19<br><b>21</b> |

| Chapte     | 2.2.1<br>2.2.2<br>Concler 3:5                     | Direct conversion (Homodyne)  The two-IF receiver topology usion  GHz CMOS Receivers | 16<br>19<br><b>21</b> |

| Chapte 3.1 | 2.2.1<br>2.2.2<br>Concler 3:5                     | Direct conversion (Homodyne)  The two-IF receiver topology usion  GHz CMOS Receivers |                       |

| Chapte 3.1 | 2.2.1<br>2.2.2<br>Concler 3:5<br>Introd<br>A very | Direct conversion (Homodyne)  The two-IF receiver topology usion  GHz CMOS Receivers | 16 21 21 21 22        |

|      | 2. <i>4</i> | .3 Simulation and Model Extraction      | 31   |

|------|-------------|-----------------------------------------|------|

|      | 2.4         | .4 Compact Model Generation             | 33   |

|      | 2.4         | .5 Inductor Synthesis                   | 37   |

| 2    | 2.5 Co      | mparison of Results                     | 38   |

|      | 2.5         | .1 Introduction                         | 38   |

|      | 2.5         | .2 Measurement Procedure                | 39   |

|      | 2.5         | .3 Importance of Deembedding            | 40   |

|      | 2.5         | .4 Comparing MIND to Measurements       | 41   |

| 2    | 2.6 Co      | nclusion                                | 46   |

| Chaj | pter 3      | : Integrated CMOS Low Noise Amplifiers. | . 48 |

| 3    | .1 Int      | roduction                               | 48   |

| 3    | .2 No       | ise Fundamentals                        | 49   |

|      | 3.2         | .1 Thermal Noise                        | 49   |

|      | 3.2         | 2 MOS Transistor Noise Sources          | 50   |

|      | 3.2         | 3 Noise Figure                          | 51   |

|      | 3.2.        | 4 Cascaded Noise Figure                 | 53   |

| 3    | .3 Dis      | stortion                                | 55   |

|      | 3.3         | 1 Nonlinearity                          | 55   |

|      | 3.3.        | 2 Gain Compression                      | 56   |

|      | 3.3.        | 3 Intermodulation Distortion            | 57   |

|      | 3.3.        | 4 Cascade of Nonlinear Amplifiers       | 59   |

| 3    | .4 LN       | A Performance Metrics                   | 61   |

| 3    | .5 CM       | IOS LNA Fundamentals                    | 62   |

|      | 3.5.        | 1 Input Matching                        | 63   |

|      | 3.5.        | 2 Gain                                  | 65   |

|      | 3.5.        | Noise Figure                            | 67   |

| 3    | .6 Co       | nclusion                                | 73   |

| Char | oter 4:     | 2.4 - 5.8 GHz CMOS LNA's: Simulations   |      |

|      |             | and Measurements                        | 74   |

| 4    | .1 Inti     | oduction                                | 74   |

| 4    | .2 A F      | Fully-Integrated 2.5 GHz CMOS LNA       | 75   |

|      | 4.2.        | 1 Circuit Description                   | 75   |

|      | 4.2.        | 2 Layout Implementation                 | 77   |

|      | 4.2.        | 3 Simulation Results                    | 78   |

|      | 4.2.        | 4 Experimental Measurements             | 81   |

|      | 4.2.        | 5 Discussion of Measurements            | 82   |

|      | 4.2.        | 6 Conclusion About First Prototype      | 84   |

| 4.   | .3 An       | Improved 2 GHz-Range LNA                | 84   |

:

|     |      | 4.3.1  | Introduction                                | 84 |

|-----|------|--------|---------------------------------------------|----|

|     |      | 4.3.2  | Improved Layout Implementation              | 85 |

|     |      |        | Measurements                                |    |

|     |      | 4.3.4  | Conclusion                                  | 88 |

|     | 4.4  | 3 GHz  | CMOS LNA                                    | 88 |

|     |      | 4.4.1  | Introduction                                | 88 |

|     |      | 4.4.2  | Results                                     | 89 |

|     | 4.5  |        | usion                                       |    |

| Ch  | apte | er 5:  | Conclusion                                  | 93 |

| Ap  | pen  | dices. | 003066200000000000000000000000000000000     | 96 |

|     |      |        | : Sample Inductor Netlist                   |    |

|     |      |        | : S-Parameters for the Narrowband RLC Model |    |

|     |      |        | : Open-Circuit Deembedding                  |    |

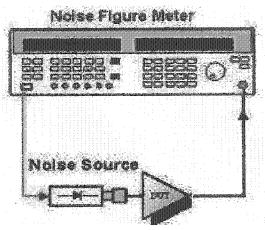

|     |      |        | : Manual Noise Figure Measurement           |    |

|     |      |        | : MIND Graphical User Interface             |    |

| Ref |      |        | 000000000000000000000000000000000000000     |    |

# **List of Figures**

| 1.1  | Simplified conventional superheterodyne receiver frontend             |

|------|-----------------------------------------------------------------------|

| 1.2  | Simplified direct conversion receiver frontend                        |

| 1.3  | Simplified two-IF architecture receiver frontend                      |

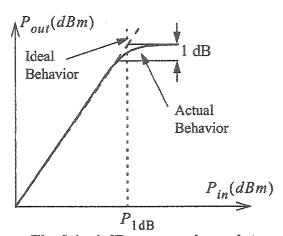

| 2.1  | 1 dB compression point                                                |

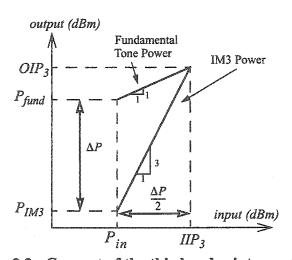

| 2.2  | Concept of the third-order intercept                                  |

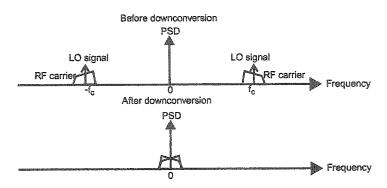

| 2.3  | Power density spectrum for a simple direct conversion architecture 14 |

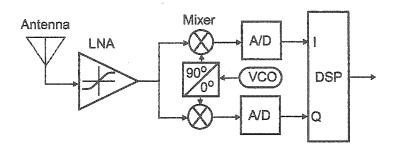

| 2.4  | Direct conversion receiver frontend with I/Q paths                    |

| 2.5  | Low-IF image-rejection architecture                                   |

| 2.6  | Frequency domain representation for the image-rejection architecture  |

|      | in Fig. 2.5                                                           |

| 2.7  | Half-RF image-rejection architecture                                  |

| 3.1  | Receiver architecture                                                 |

| 3.2  | Off-chip microstrip balun. 24                                         |

| 3.3  | Example of a p-model for an on-chip inductor [11][14]                 |

| 3.4  | Schematic of the LNA                                                  |

| 3.5  | Schematic of the I/Q mixer                                            |

| 3.6  | Grounded-source differential pair                                     |

| 3.7  | Schematic of the quadrature VCO                                       |

| 3.8  | Input resistance of the VCO core pair                                 |

| 3.9  | (a) Simulated LNA noise figure, and (b) mixer noise figure            |

| 3.10 | Simulated 1-dB compression point for (a) LNA (b) mixer                |

| 3.11 | Simulated VCO phase noise                                             |

| 3.12 | ADS schematic                                                         |

| 3.13 | Receiver chip micrograph                                              |

| 3.14 | Test fixture for the receiver. 35                                     |

| 3.15 | Loss of the test fixture with package replaced by a short             |

| 3.16 | Loss of the test fixture with an empty package shorted internally 36  |

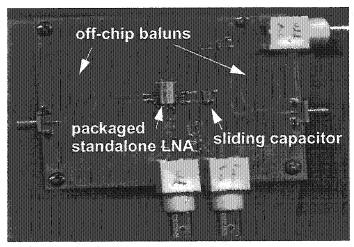

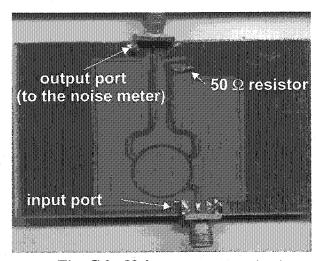

| 3.17 | Testing PCB setup                                                               |

|------|---------------------------------------------------------------------------------|

| 3.18 | Loss of the RF part of test fixture                                             |

| 3.19 | PCB for testing the standalone LNA                                              |

| 3.20 | Measured S11 of the standalone LNA                                              |

| 3.21 | Measured S21 of the standalone LNA                                              |

| 3.22 | Micrograph of the standalone VCO                                                |

| 3.23 | LO leakage in the receiver. 41                                                  |

| 3.24 | Input reflection S11 of the receiver. 41                                        |

| 3.25 | (a) frequency response of the two-tone test (b) Measured third-order intercept  |

|      | plot                                                                            |

| 3.26 | Frequency response of the image signal                                          |

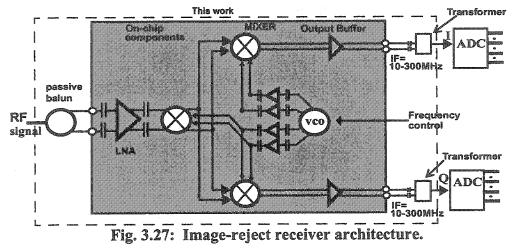

| 3.27 | Image-reject receiver architecture                                              |

| 3.28 | Simplified schematic of the LNA                                                 |

| 3.29 | Schematic of the passive mixer                                                  |

| 3.30 | Schematic of the core LC oscillator                                             |

| 3.31 | Simulated LNA (a) noise figure (b) 1-dB compression point                       |

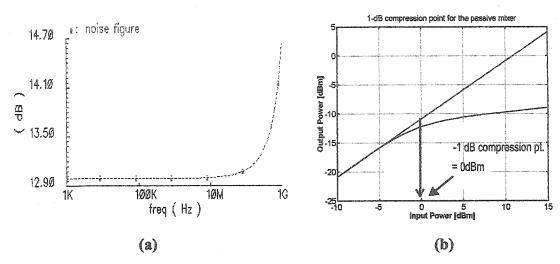

| 3.32 | Simulated passive mixer (a) noise figure (b) 1-dB compression point 50          |

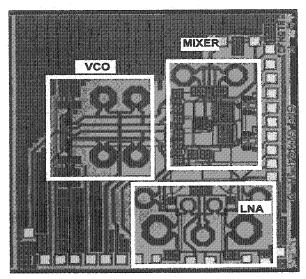

| 3.33 | Image-reject receiver chip                                                      |

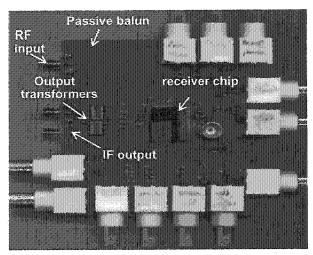

| 3.34 | Text fixture for the image-reject receiver                                      |

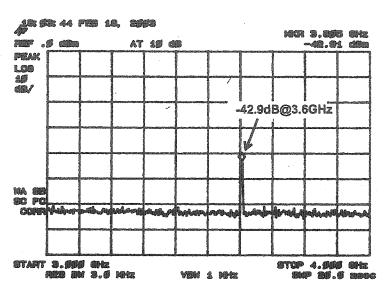

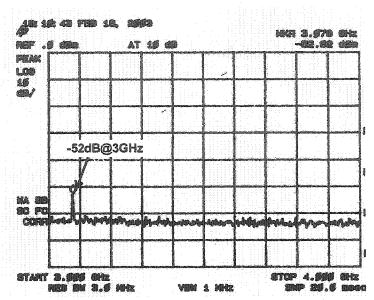

| 3.35 | Measured LO leakage for the receiver at 3.6GHz, with all switching capacitor    |

|      | turned off                                                                      |

| 3.36 | Measured LO leakage for the receiver at 3GHz, with all the switching capacitors |

|      | turned on, and the varactors at maximum setting53                               |

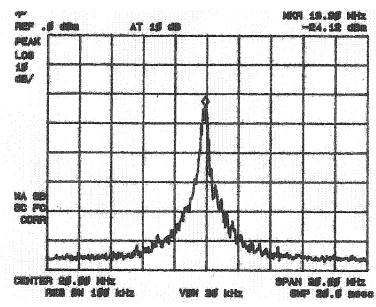

| 3.37 | Measured second IF output for a 6.8GHz input RF signal53                        |

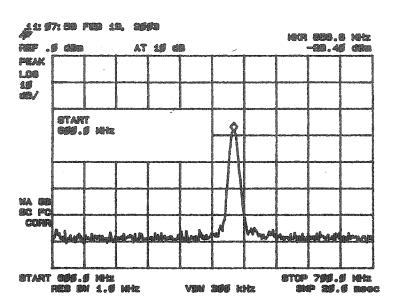

| 3.38 | Measured second IF output for a 6.2GHz input RF signal                          |

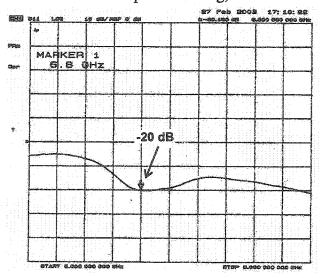

| 3.39 | Measured input reflection of the receiver                                       |

| 3.40 | Measured third-order intercept plot for the image-reject receiver 55            |

| 3.41 | Measured frequency response for an image signal                                 |

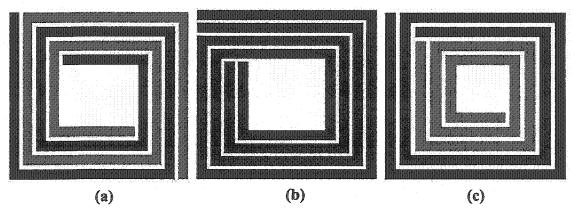

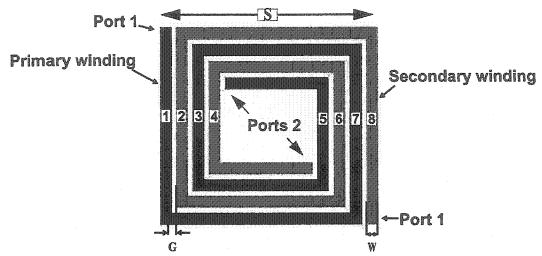

| 4.1  | Common transformer configurations (a) interleaved (b) parallel winding          |

|      | (c) concentric 59                                                               |

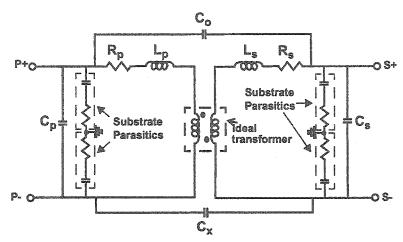

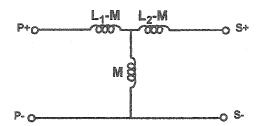

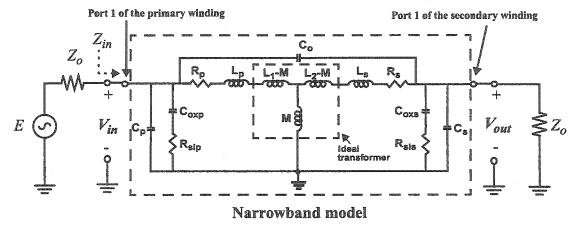

| 4.2  | Transformer model                                                               |

| 4.3  | Transformer parameters                                                          |

| 4.4  | T-section model for an ideal transformer                                        |

|      |                                                                                 |

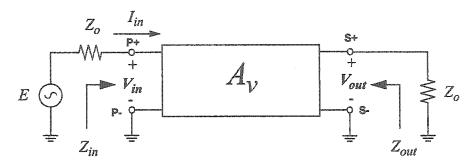

| 4.5  | Equivalent circuit for S-parameter evaluation                               |

|------|-----------------------------------------------------------------------------|

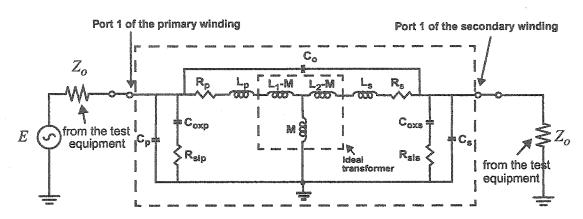

| 4.6  | The complete lumped-element model for a transformer                         |

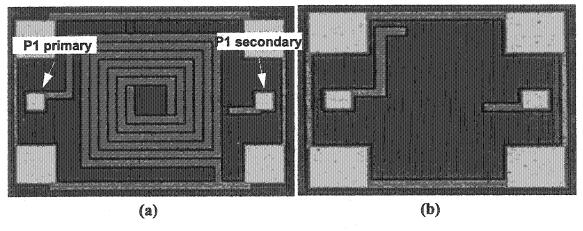

| 4.7  | Micrograph of a transformer prototype (a) sample transformer test structure |

|      | (b) calibration structure                                                   |

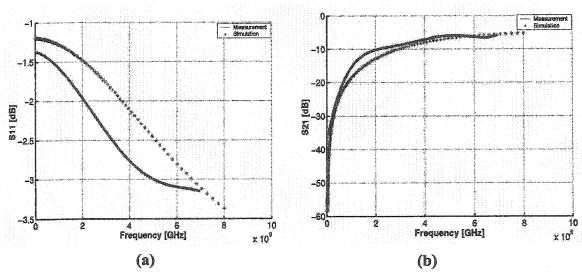

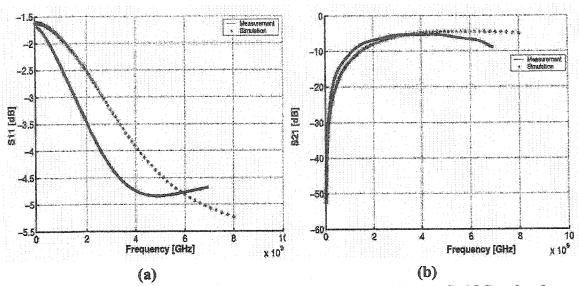

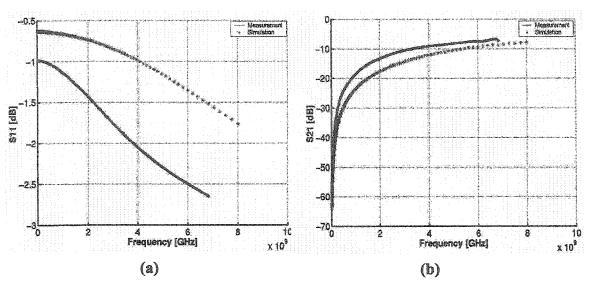

| 4.8  | Transformer response in a 0.25mm CMOS technology, N=2, W=15mm,              |

|      | G=0.8mm, S=210mm (a) S11 (b) S21                                            |

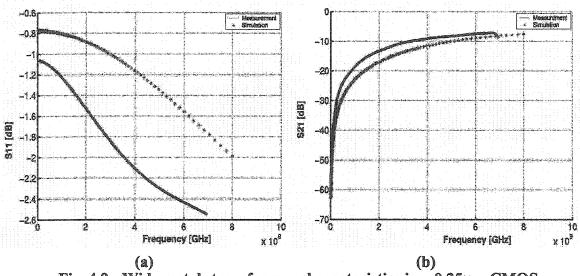

| 4.9  | Wide metals transformer characteristics in a 0.25mm CMOS technology,        |

|      | N=2, W=20mm, G=0.8mm, S=210mm (a) S11 (b) S21                               |

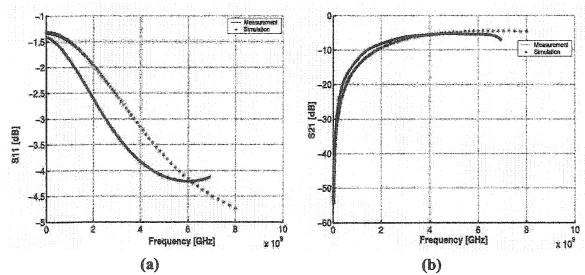

| 4.10 | Large transformer characteristic in a 0.25mm CMOS technology,               |

|      | N=2, W=20mm, G=0.8mm, S=300mm (a) S11 (b) S2169                             |

| 4.11 | Many turns transformer characteristic in a 0.25mm CMOS technology,          |

|      | N=3, W=20mm, G=0.8mm, S=300mm (a) S11 (b) S21                               |

| 4.12 | Transformer characteristic in a 0.18mm CMOS technology, N=2,                |

|      | W=20mm, G=0.8mm, S=210mm (a) S11 (b) S2171                                  |

| A.1  | Narrowband model S-parameters extraction setup                              |

| B.1  | SOLT calibration fixture                                                    |

| C.1  | Noise measurement setup                                                     |

| C.2  | Noise measurement setup                                                     |

# **List of Tables**

| 1.1 | Comparison of recent RF transceiver frontends            | 3  |

|-----|----------------------------------------------------------|----|

| 1.2 | Comparison of transformer modeling programs.             | 6  |

| 2.1 | Receiver components parameters used in HP ADS simulation | 18 |

| 2.2 | IRR with respect to LO mismatch.                         | 18 |

| 3.1 | Comparison of different methods for balun implementation | 23 |

| 3.2 | First receiver components simulation results.            | 33 |

| 3.3 | Losses due to the test fixture.                          | 37 |

| 3.4 | Measured receiver performance.                           | 43 |

| 3.5 | Receiver components simulation results.                  | 50 |

| 3.6 | Losses due to the test fixture for the second receiver   | 52 |

| 3.7 | Summary of measured receiver performance                 | 56 |

| 4.1 | Components values for the transformer in Fig. 4.8        | 70 |

| 4.2 | Different transformers k-factors.                        | 70 |

|     |                                                          |    |

# **Chapter 1: Introduction**

#### 1.1 Introduction

With the explosion of the demand for wireless communications such as cellular phones, wireless local area networks etc., new frequency bands are needed in order to accommodate an increasing number of users and transmission speeds. In Europe, the standards for the HIPERLAN (High Performance Radio LAN) system, which operates in the 5.15-5.35/5.47-5.725 GHz frequency range, have been defined. Similar standards have also been defined in the United Staes.

Traditionally, radio-frequency (RF) transceiver frontends were implemented using Gallium Arsenide or bipolar technologies, since they had higher unity-gain frequencies and better transconductances than other technologies such as CMOS. On the other hand, CMOS processes are the choice for implementing the baseband sections of transceivers, since they offer low cost and low power consumption. As a result, it is highly desirable to be able to integrate both the frontend circuitry and the baseband sections onto a single chip.

As the feature sizes of CMOS technologies shrink, the unity-gain frequencies of CMOS transistors is improving. For example, in a  $0.1\,\mu m$  technology, the unity-gain

frequency of a MOS device can reach up to 100GHz under a 1V supply [1]. However, CMOS processes still suffer from the limitation of low transconductance values when compared to other processes. The primary objective of this work is to demonstrate the feasibility of using a CMOS process in realizing modern RF receiver frontends.

#### 1.2 Motivation

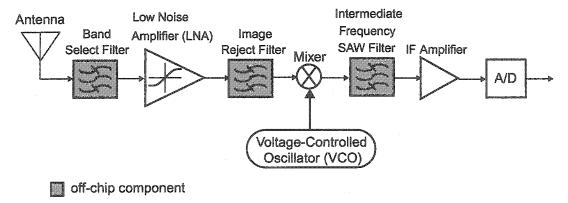

A typical integrated RF receiver frontend consists of three main building blocks (Fig. 1.1 - 1.3), independent of the architecture:

- 1. A low-noise amplifier (LNA): It amplifies the incoming RF signal.

- 2. Mixers: Downconvert the high frequency RF signal to a lower frequency band.

- A voltage-controlled oscillator (VCO): It provides a reference signal for the downconversion process. The output of the VCO needs to be tunable by an external voltage source.

Depending on the architecture chosen, surface acoustic wave (SAW) filters may be needed as off-chip components.

#### 1.2.1 State-of-the-art RF receiver frontends

Table 1.1 summarizes the specifications of recently reported RF transceiver frontends operating in the 5-GHz range [2]-[9]. The table shows a trend in shifting from traditional technologies, such as SiGe and BiCMOS, to CMOS technologies for higher integration. Besides, all the transceivers operate from supply voltages at or above 1.8V. In order to have a single voltage supply for the entire transceiver chip, it is highly desirable for the

|                                  | [2]<br>ISSCC'02                      | [3]<br>JSSC '01                      | [4]<br>ISSCC '01                     | [5]<br>JSSC '00     | JSSC '00<br>[6]                | [7]<br>TMT '00   | [8]<br>JSSC '99  | [9]<br>CICC '99  |

|----------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------|--------------------------------|------------------|------------------|------------------|

| Technology                       | CMOS<br>0.25 μm                      | CMOS<br>0.25 µm                      | CMOS<br>0.24 µm                      | CMOS<br>0.25 µm     | Bipolar                        | SiGe<br>HBT      | BiCMOS           | SiGe             |

| Center Frequency                 | 5.2 GHz                              | 5.2 GHz                              | 5 GHz                                | 5.25 GHz            | 5-6 GHz                        | 5 GHz            | 5 GHz            | 5.2 GHz          |

| Noise Figure                     | 8 dB                                 | 6.4 dB                               | 7.2 dB                               | 3 dB                | 5.1 dB                         | 5.9 dB           | 7 dB             | 7.5 dB           |

| Forward Gain                     | 36 dB<br>(with<br>baseband<br>ampl.) | 43 dB<br>(with<br>baseband<br>ampl.) | 26 dB<br>(with<br>baseband<br>ampl.) | 8.7 dB              | 17 dB                          | 19 dB            | 18 dB            | 11.7 dB          |

| Output Third-<br>Order Intercept | -                                    | -15 dBm                              | -7 dBm                               | -11.3 dB<br>m       | -4.5 dBm                       | -                | -17dBm           | -11 dBm          |

| Voltage Supply                   | 2.5 V                                | 2.5 V                                | 1.8 V                                | 3 V                 | 2.34 V                         | 3.5 V            | 3 V              | 3.3 V            |

| Power Dissipa-<br>tion           | 250 mW                               | 29 mW                                | 58.8 mW                              | 114 mW              | 55 mW                          | 45 mW            | 55.5 mW          | 122 mW           |

| Packaging                        | 64-pin<br>LPCC                       | -                                    | 32-pin<br>ceramic<br>flat pack       | On-wafer<br>probing | 32-pin<br>ceramic<br>flat pack | On-wafer probing | On-wafer probing | On-wafer probing |

Table 1.1: Comparison of recent RF transceiver frontends.

RF section to operate from the same voltage supply as the baseband circuitry. The latter has its voltage supply constantly dropping. For example, most recent digital circuits implemented in CMOS  $0.1~\mu m$  technologies operate from 1V supplies.

There exists three main RF receiver architectures:

#### 1. The superheterodyne receiver (Fig. 1.1): Many of the RF transceivers manufactured

Fig. 1.1: Simplified conventional superheterodyne receiver frontend.

Fig. 1.2: Simplified direct conversion receiver frontend.

to date employ the superheterodyne architecture. This approach offers high selectivity and better image rejection. However, it requires off-chip high quality SAW filters for filtering the image of the RF signal. As a result, this architecture is not suitable for high levels of integration.

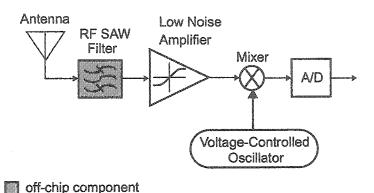

- 2. The direct conversion receiver (Fig. 1.2): It is a well-known architecture that does not require off-chip high quality filters, since the output is directly converted to base-band using a single mixer stage. As a result, this approach has the potential for higher levels of integration. However, this architecture suffers from DC offsets. The LO signal is at the same frequency as the RF carrier, and any LO leakage to the mixer's RF inputs or to the antenna will result in self-mixing, producing a time-varying DC offset at the mixer output, which is difficult to separate from the baseband signal.

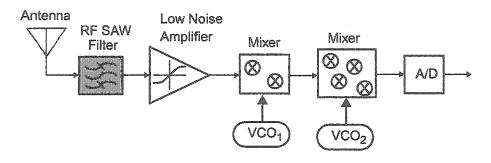

- 3. The two-IF receiver (Fig. 1.3): It is a relatively new topology, which is similar to the superheterodyne architecture. It consists of downconverting the RF signal to an intermediate frequency (IF). The IF signal is then translated directly to baseband via a second mixer stage. Because of the non-zero IF after the first mixer stage, the image

off-chip component

Fig. 1.3: Simplified two-IF architecture receiver frontend.

problem is introduced. Instead of using an off-chip filter as in the case of a superheterodyne architecture, the image problem is mitigated by using a second mixer stage to implement image-rejection through a special structure such as the Weaver structure [18], in order to allow high integration. However, the amount of image rejection is very sensitive to any mismatches in the signal paths.

One of the objectives of this thesis is to demonstrate the feasibility of using a CMOS process to implement a fully packaged integrated very low voltage RF receiver frontend at 5 GHz, and to explore alternate receiver architectures, such as the two-IF approach. A detailed analysis of the two architectures will be covered in Chapter 2. Simulation and measurement results of two receiver prototypes will be presented in chapter 3.

#### 1.2.2 Integrated transformers

Passive devices, such as inductors and capacitors, are widely used in RF circuits. On the other hand, transformers, which can be used for differential to single-ended signal conversion [27], etc., are not as widely used. Unlike inductors, for which serveral robust modeling tools such as ASITIC from Berkeley [11], and the McGill Inductor Modeler

| Program      | Speed        | Comments                                                                                        |

|--------------|--------------|-------------------------------------------------------------------------------------------------|

| Maxwell [10] | Very<br>Slow | EM simulation     Any topology                                                                  |

| ASITIC [11]  | Fast         | <ul><li>Pseudo-EM simulation</li><li>Many topologies</li></ul>                                  |

| Gemcap [12]  | Fast         | <ul> <li>Transmission-line modeling</li> <li>Basic interface</li> <li>Few topologies</li> </ul> |

| SISP[13]     | Fast         | <ul><li>Transmission-line modeling</li><li>Many topologies</li></ul>                            |

| MIND [14]    | Fast         | Transmission-line modeling     Basic structures only                                            |

Table 1.2: Comparison of transformer modeling programs.

(MIND) [14] exist, there are not many non-computational intensive and affordable tools available for transformers modeling. Before we can take advantage of using transformers in RF circuits, we need to fully understand their characteristics and be able to accurately model them when integrated on-chip.

Many of the available commercial transformer modeling programs (Table 1.2) employ electro-magnetic (EM) modeling techniques, based on Maxwell's equations. Although this method can provide very accurate results, it requires lenghty simulations. Since the structures of common transformers are pre-defined to a large extent, the generality of the EM technique is not needed. Transmission-line modeling, where each microstrip is modeled by an equivalent RLC circuit, trades-off generality for speed. The second objective of this thesis was to augment the in-house transmission-lines based inductor modeling tool, MIND, to be able to model transformers from measurements and to synthesize transformers from a given set of design specifications. This is discussed in

details in chapter 4.

#### 1.3 Thesis contributions

Following is a summary of the contributions of this thesis:

- Demonstrated that using folded cascode topologies, CMOS technologies can be used to implement 5GHz RF frontends which can operate from a very low-voltage supplies.

This work was reported in:

- A. Koon Hung Lee and Mourad N. El-Gamal, "A Very Low-Voltage (0.8V) CMOS Receiver Frontend for 5 GHz RF Applications," Proc. IEEE International Symposium on Circuits and Systems (ISCAS'02), pp. 125-128, May 2002.

- B. Mourad N. El-Gamal, Koon Hung Lee, and Tommy Tsang, "CMOS Receiver Frontend for 5GHz RF Applications," IEE Proceedings on Circuits, Devices and Systems, pp. 355-362, October 2002.

- 2. Designed and tested a 5-6GHz two-IF downconversion architecture receiver, with high image rejection and wide frequency tuning capacility:

- A. Koon Hung Lee and Mourad N. El-Gamal, "A 6-7GHz CMOS Receiver Frontend with wide tunning range," submitted for publication, 4 pages, 2003.

- 3. Designed and characterized on-chip inductors and transformers for RF applications, and augumented the in-house modelling tool to include transformers modelling. The work on inductor modelling was reported in:

- A. Ahmed H. Mostafa, Koon Hung Lee, and Mourad N. El-Gamal, "Character-

ization of CMOSP18 Inductors," Technical Report, Canadian Microelectronics Corporation, January 2001.

### Chapter 2: Wireless Receivers Architectures

Over the past decades, thanks to the advances in digital signal processors (DSP) used for signal demodulation, the focus for RF receivers has shifted from high sensitivity to high integration. Complex demodulation schemes can now be implemented in DSP, resulting in an increase in the overall signal quality and bit error rate. As a result, architectures that favor high levels of integration, such as the direct conversion and two-IF architectures, are gaining popularity over the traditional superheterodyne approach which requires off-chip components, namely filters.

This chapter presents the most common receiver performance metrics, and a qualitative study of the direct conversion and the two-IF receiver architectures.

#### 2.1 Receiver performance metrics

#### 2.1.1 Noise figure

The noise figure (NF) is one of the most important parameters in measuring a receiver performance. It represents the amount of signal-to-noise ratio (SNR) degradation as the signal passes through a system. In a typical RF receiver, the main source of noise is the thermal noise, which is a white noise generated by resistors, the channel resistances of MOS transistors, etc. As a result, the use of resistors in the RF paths is always avoided in

order to minimize thermal noise. The noise factor is defined by:

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{S_{in}/N_{in}}{S_{out}/N_{out}}, \qquad (2.1)$$

and the noise figure is given by:

$$NF = 10\log_{10} F , \qquad (2.2)$$

where S and N are the signal power and the noise power respectively, and F is known as the noise factor.

In order to evaluate the NF for a receiver, it is important to accurately evaluate the noise contribution from each stage. The overall noise factor from a cascaded system is given by:

$$F = F_1 + \frac{F_2 - 1}{A_1^2} + \frac{F_3 - 1}{A_1^2 A_2^2} + \dots , \qquad (2.3)$$

where  $A_i$  and  $F_i$  are the gain and noise factor for stage i. From Eq. (2.3), it can be seen that it is very important for the first stage in a receiver chain, usually an LNA, to have a high gain and low noise figure, in order to minimize the overall noise figure of the system. The noise figures of the subsequent stages will have secondary effects on the total noise figure, as long as the first stage has a high gain.

#### 2.1.2 Distortion

Ideally, an RF receiver is modelled as a linear system. However, due to the practical nonlinearity effects resulting from characteristics such as the square-law i-v relationship

in MOS transistors, nonlinear models are needed to predict a more realistic circuit response. Let us assume that the system has the following transfer function:

$$y_{out}(t) = \alpha_1 x_{in}(t) + \alpha_2 x_{in}^2(t) + \alpha_3 x_{in}^3(t)$$

, (2.4)

and if  $x_{in}(t) = A_1 \cdot cos(\omega_1 t) + A_2 \cdot cos(\omega_2 t)$ , then the fundamental output components are:

$$\left[\alpha_{1}A_{1} + \frac{3}{4}\alpha_{3}A_{1}^{3} + \frac{3}{2}\alpha_{3}A_{1}A_{2}^{2}\right]cos(\omega_{1}t) + \left[\alpha_{1}A_{2} + \frac{3}{4}\alpha_{3}A_{2}^{3} + \frac{3}{2}\alpha_{3}A_{2}A_{1}^{2}\right]cos(\omega_{2}t) , \quad (2.5)$$

while the third-order intermodulation (IM) products for  $(2\omega_1 \pm \omega_2)$  are:

$$\frac{3\alpha_3 A_1^2 A_2}{4} cos(2\omega_1 + \omega_2)t + \frac{3\alpha_3 A_1^2 A_2}{4} cos(2\omega_1 - \omega_2)t, \qquad (2.6)$$

and for  $(2\omega_2 \pm \omega_1)$  the IM products are:

$$\frac{3\alpha_3 A_2^2 A_1}{4} cos(2\omega_2 + \omega_1)t + \frac{3\alpha_3 A_2^2 A_1}{4} cos(2\omega_2 - \omega_1)t . \tag{2.7}$$

It is clear from the above expressions that, when a signal passes through a nonlinear system, the fundamental term, that is  $\cos(\omega t)$ , generates many other higher-order harmonic terms. In the following sub-sections, we briefly discuss the two most important distortion metrics used to describe the nonlinear effects in systems.

#### A. 1-dB gain compression point

In a linear system, as the input signal increases, the output will increase proportionally. However, in reality, the output will increase up to a certain point within the transfer function. As shown from Eq. (2.5), when the input is relatively small,  $\alpha_1 A_1$

Fig. 2.1: 1 dB compression point.

will be the dominant term for the fundamental output signal. As the signal increases, the contribution from  $\frac{3}{4}\alpha_3A_1^3$  will increase. If  $\alpha_3$ < 0, then the gain will start decreasing as the input signal,  $A_1$ , increases. As shown in Fig. 2.1, the 1-dB compression point describes the point where the actual and ideal response differ by 1 dB.

#### B. Third-order intercept point

If two adjacent tones,  $\omega_1$  and  $\omega_2$ , are applied at the input of a non-linear system, the output described by Eq. (2.6) and Eq. (2.7) will be corrupted by nearby third-order

Fig. 2.2: Concept of the third-order intercept.

intermodulation products, i.e. at  $(2\omega_1\pm\omega_2)$  and  $(2\omega_2\pm\omega_1)$ . The third-order intercept point (IP3) is used to characterize this behavior. To measure the IP3, a two-tone test is performed with sufficiently small inputs in order to avoid gain compression. As the input signals increase, the output fundamental signals increase proportionally, while the third-order intermodulation products increase at three times the rate of the fundamentals (on a logarithmic scale). The third-order intercept point is defined as the intersection between these two lines, as shown in Fig. 2.2. The x and y-coordinates for the IP3 are called the input and output intercept points (IIP3/OIP3) respectively.

Similar to the noise analysis, the overall IIP3 of cascaded systems can be expressed in terms of the IIP3 of each stage:

$$\frac{1}{IIP3} \approx \frac{1}{IIP3_1} + \frac{G_1}{IIP3_2} + \frac{G_1G_2}{IIP3_3} + \dots , \qquad (2.8)$$

where IIP3<sub>i</sub> and G<sub>i</sub> are the IIP3 and power gain for stage *i*. As proposed by the above expression, as long as the later stages in the chain have good IIP3 figures, a reasonable overall IIP3 can be achieved, even though the first stage, usually an LNA, may have a low IIP3 figure. This agrees with intuition since the LNA usually receives small signals, while the subsequent stages normally operate on amplified signals from the LNA and the following stages.

#### 2.1.3 Image-rejection ratio

The image-rejection ratio (IRR) measures the amount of image suppression with respect to the wanted signal. For example, if the input signal is at 5 GHz and it is

Fig. 2.3: Power density spectrum for a simple direct conversion architecture.

downconverted to 1 GHz, any signal at the image band, that is at 3 GHz, will also be downconverted to 1 GHz and will appear at the output. The IRR can be expressed as:

$$IRR = 10\log_{10}\left(\frac{P_{out-image}}{P_{out-signal}}\right) - 10\log_{10}\left(\frac{P_{in-image}}{P_{in-signal}}\right), \tag{2.9}$$

where  $P_{i-i}$  is the power for the wanted signal and the image for both input and output.

### 2.2 High integration receivers architectures

#### 2.2.1 Direct conversion (Homodyne)

Figure 1.2 shows the basic structure of a direct conversion receiver. Although this approach eliminates the use of off-chip components, it suffers from the following limitations:

1. Although direct conversion does not suffer from the same kind of image problem that the superheterodyne architecture suffers from [23], it has its own image limitations. Figure 2.3 shows the power density spectrum (PSD) of an intended signal and its counterpart from the mirror frequency, with the lower and upper sidebands overlap-

Fig. 2.4: Direct conversion receiver frontend with I/Q paths.

ping at baseband. As a result, the two signals can not be separated. The problem can be easily solved by performing the downconversion with two different local oscillator (LO) signals which are at 90° phase shift with respect to each other, as shown in Fig. 2.4 [16]. However, with the introduction of the I/Q quadrature structure, the image suppression for direct conversion architectures becomes very sensitive to phase and amplitude mismatches in the I and Q signal paths.

- 2. Since the RF carrier is downconverted to baseband, a direct conversion receiver requires the frequency for the LO signal to be the same as that of the RF input. As a result, a high frequency and low phase noise VCO is needed.

- 3. Since the isolation between the LO port to the RF port of the mixer is finite, any signal leakage between the two ports will contribute to DC offsets, resulting from self-mixing. This problem is amplified if the amount of DC offset is time varying as discussed in Chapter 1. The subsequent baseband sections may be saturated by this DC offset.

#### 2.2.2 The two-IF receiver topology

Although the direct conversion architecture eliminates the use of off-chip filters, other drawbacks, such as DC offsets, greatly reduce the practical performance of those receivers. As a result, a non-zero intermediate IF stage is often used before downconverting the signal to baseband. Although the mixer in the second stage would have a finite LO feedthrough as well, the resulting DC offset is not as problematic as in direct conversion. This is because the frequency is lower and the potential for the LO signal of the second stage to rebound back from surrounding objects, after being transmitted through the antenna, is low. As a result, the main DC offset in this case is not time-varying, and can be removed using the methods proposed in [16]. Besides, with two downconversion stages, no LO signal needs to operate at the same frequency as the RF input, thus the VCO requirement is relaxed.

However, with the use of a non-zero IF, the image problem that superheterodyne architectures suffer from is reintroduced. Since there are two frequency downconversions that take part in cascade, on-chip image rejection schemes can be used, instead of off-chip filters. In the following, two image-rejection approaches will be explored.

#### A. Low-IF image-rejection architecture

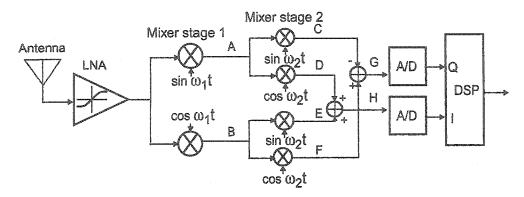

This architecture is similar to the Weaver structure (Fig. 2.5) [18]. The RF carrier is first downconverted to IF by a pair of quadrature LO signals. With a special arrangement, the IF signals are translated to baseband by another set of quadrature LO signals. By exploiting the phase relationships, both the I and Q channels can be obtained. Figure 2.6

Fig. 2.5: Low-IF image-rejection architecture.

Fig. 2.6: Frequency domain representation for the image-rejection architecture in Fig. 2.5.

shows the frequency domain representation for the signals of the architecture in Fig. 2.5 at various nodes as indicated.

Although this architecture allows high level of integration, the amount of image rejection again depends heavily on the phase matching between the I/Q paths. In order to illustrate this, HP's Advance Design Systems (ADS) is used to perform a high level receiver simulation. Figure 2.5 is implemented in ADS except for the digital section. The outputs from the combiners are taken to calculate the IRR using Eq. (2.9). Table 2.1

|                     | LNA    | Mixer<br>(stage 1) | Mixer<br>(stage 2) |

|---------------------|--------|--------------------|--------------------|

| Forward Gain        | 10 dB  | 10 dB              | -5 dB              |

| Noise Figure        | 4 dB   | 15 dB              | 10 dB              |

| IIP3                | -10 dB | -1 dB              | 5 dB               |

| S <sub>11</sub>     | -10 dB | -                  | *                  |

| LO-IF<br>Feedthough | -      | -40 dBm            | -40 dBm            |

Table 2.1: Receiver components parameters used in HP ADS simulation.

| LO Phase Mis-<br>match | IRR   |

|------------------------|-------|

| 00                     | 95 dB |

| 10                     | 40 dB |

| 2°                     | 35 dB |

| 3°                     | 32 dB |

Table 2.2: IRR with respect to LO mismatch.

shows the performance parameters of the receiver components that were used in the simulation. Note that active mixers were used for the first stage, and passive mixers for the second stage. Table 2.2 shows the resulting IRR with different degrees of phase mismatch. As shown, the IRR is very sensitive to the phase mismatch in this type of architecture: It decreases from 95 dB to 32 dB as a result of a few degrees of mismatch!

#### B. Half-RF image rejection architecture

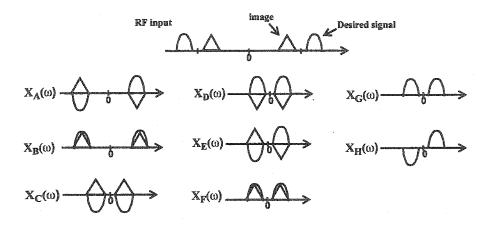

The second image-rejection architecture considered performs downconversion twice, using the same LO signal for the two stages (Fig. 2.7) [3]. In order to translate the RF signal to baseband, the frequency of the LO signal is set to be half that of the RF carrier. Unlike the previous image-rejection architecture that had additional circuitry for image rejection, this approach performs image rejection by selecting a specific LO signal. For

Fig. 2.7: Half-RF image-rejection architecture.

the first stage, since the LO signal is half that of the RF carrier, the image lies at DC. By using a DC blocking capacitor at the input, or using an on-chip high pass filter, which is feasible since the wanted signal and the image are widely separated, the image is eliminated. As a result, this architecture is considerably less sensitive to the mismatches in the signal paths compared to the previous topology.

Nevertheless, this architecture has its own limitations. First, the flicker noise of the LNA, which lies around the zero frequency, may upconvert to the IF signal and then subsequently downconvert to baseband. By using relatively large transistors for the LNA, the flicker noise corner frequency can be reduced. Second, if the LO-IF feedthrough for the first mixer stage is large, it may corrupt the IF signal, since both the IF and the LO signals are at the same frequency.

#### 2.3 Conclusion

From the above discussion we conclude that the half-RF image rejection architecture is more immune to phase mismatch between the I and Q paths, and requires less components than the low-IF architecture. In order to demonstrate that a CMOS

technology can be used to implement such an architecture for 5 GHz applications, and to investigate the effect of the MOS transistor flicker noise on the system, detailed simulation and measurement results for a half-RF architecture implementation are presented and discussed in the following chapter.

## **Chapter 3: 5 GHz CMOS Receivers**

#### 3.1 Introduction

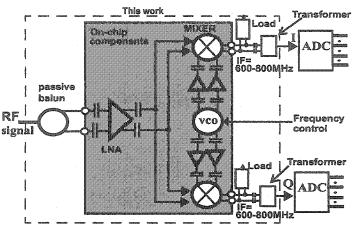

Two RF CMOS receiver frontends were designed and fabricated using TSMC's digital 0.18 µm CMOS technology available to the author. The objectives of each one of the two receivers are:

- To demonstrate the feasibility of using a CMOS process to implement very low-voltage (0.8-1V) RF circuitry.

- To explore the performance of the half IF image-reject receiver architecture discussed in the previous chapter.

#### 3.2 A very low-voltage receiver frontend

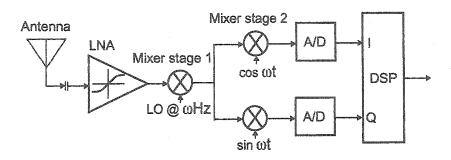

Figure 3.1 shows the complete architecture of the first receiver prototype. An external microstrip balun is used to convert a single-ended signal to differential. The chip consists of a differential low noise amplifier (LNA) connected to a set of I/Q mixers, which are driven by a voltage-controlled oscillator (VCO) with quadrature outputs. The outputs of the I/Q mixers can subsequently be connected to another downconversion stage to translate the IF signal to baseband, and thus implementing a Weaver image reject

Fig. 3.1: Receiver architecture.

architecture (e.g. [18]). Another alternative is to directly process the IF signal, after being converted to single-ended by a transformer, using a high-speed ADC [7] followed by a digital signal processor, as suggested in Fig. 3.1. DC blocking capacitors are used between stages in order to be able to bias each sub-circuit independently. Buffers are used between the mixers and the VCO to increase isolation. Off-chip transformers are used to convert the differential outputs to single-ended for measurement purposes. All of these components are assembled together on a custom built PCB for testing.

# 3.2.1 Circuit description

## A. Signal generation

Since the receiver requires a differential input, a balun (unbalanced-to-balanced transmission converter) is used to convert the single-ended signal from the signal generator to a differential signal. There are generally three methods to perform this conversion:

1. An on-chip transformer can be used, since it is hard to find a discrete off-chip trans-

|             | On-chip transformer                                                                                                                            | Active balun                                                                                                                                  | Off-chip balun                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Advantages  | easy to use     no power consumption     fully integrated solution                                                                             | can provide signal gain     consumes less space than     an on-chip transformer                                                               | <ul> <li>phase and amplitude are<br/>well matched for the dif-<br/>ferential outputs</li> <li>no power consumption</li> </ul> |

| Limitations | no accurate models available for the designer     depending on the structure and process, signal loss after conversion can be as high as 10 dB | <ul> <li>phase and amplitude outputs are very sensitive to parasitic effects at high frequency (&gt;3 GHz)</li> <li>consumes power</li> </ul> | <ul> <li>needs a relatively large<br/>off-chip space to imple-<br/>ment</li> <li>about 3 dB signal loss</li> </ul>            |

Table 3.1: Comparison of different methods for balun implementation.

former which can operate at 5 GHz.

- 2. An on-chip active balun, which is basically a differential amplifier with one of its input terminals grounded.

- 3. An off-chip microstrip balun on the PCB.

Table 3.1 shows the advantages and limitations for the different possible balun implementations. Ideally, the on-chip balun would be the best choice, since both the amplitude and the phases of the outputs can be better controlled and predicted, compared to the active balun. Also, it would provide a fully integrated solution. However, since there were no accurate transformer models available to the designer during the early design phases, it was decided that, from a research point of view, the off chip balun provides the most reliable solution. It's performance can be easily tested in a stand-alone setup. As a result, an off-chip balun is used to generate the differential signals, and transformer modeling was investigated at a later stage (Chapter 4) so that accurate modelling is made available for future use.

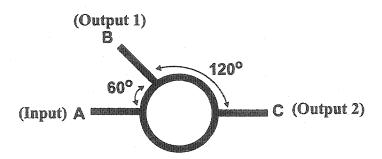

Figure 3.2 shows the structure of the off-chip balun, also known as a ring hybrid. Port 'A' is the input while the outputs at port 'B' and 'C' are 180° out of phase with respect to

Fig. 3.2: Off-chip microstrip balun.

each other. The circumference of the balun is  $3*\lambda_g/2$ , where  $\lambda_g = \frac{\lambda_o}{\sqrt{\epsilon_{eff}}}$ , and  $\lambda_o$  is the wavelength of the signal in free space, that is 1/5.2GHz in our case, and  $\epsilon_{eff}$  is the effective permittivity of the microstrip material. An additional advantage of using the ring hybrid balun is the fact that if port A sees an impedance  $Z_o$ , then the same impedance appears at both output ports.

As for the outputs of the receiver, since they are at frequencies lower than 1 GHz, transformers from MiniCircuits are used to combine the differential signals to single-ended for measurement.

#### **B.** Inductors modelling

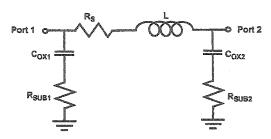

The performance of the receiver depends heavily on the quality factors of the on-chip inductors. In order to obtain accurate inductor models for simulation, ASITIC - an inductor modeling tool from Berkeley [11], and MIND (MIND: McGill INDuctor modeler), an in-house modeling tool [14], were used to produce and cross-check the  $\pi$ -models generated (Fig. 3.3).

## C. Low noise amplifier

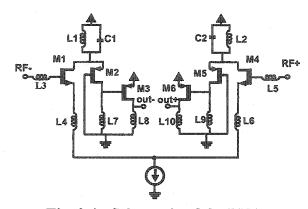

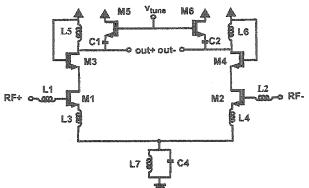

Figure 3.4 shows the simplified schematic of the LNA, including all on-chip

Fig. 3.3: Example of a  $\pi$ -model for an on-chip inductor [11][14].

components. In order to be able to operate from a very low voltage supply, a folded cascode structure is used, since it eliminates one level of transistor stacking [19]. In this configuration, transistors M1 and M4 act as common-source amplifiers, and transistors M2 and M5 are used as common-gate current buffers, with load inductors L7 and L9. As a result of this circuit topology, more voltage headroom can be used in biasing the transistors in saturation, leading to an improved linearity. An important added advantage of this topology is its improved reverse isolation.

The LC tanks, which resonate at the RF frequency, formed by inductors L1 and L2 and capacitors C1 and C2, behave as DC current sources. The advantage of using such an approach is to provide the necessary DC bias current without requiring extra voltage headroom, while presenting a high impedance to the RF signals at 5.2GHz. Besides, current sources implemented using transistors provide a wideband high impedance

Fig. 3.4: Schematic of the LNA.

response, while an LC tank provides a low impedance to other frequency bands, including the image signal, resulting in better image rejection. The other advantage of using an LC tank as such is to nullify the effect of the parasitic capacitances of the transistors, resulting in an improvement of the noise figure (NF) [20].

In order to achieve minimum noise, the widths of transistors M1 and M4 need to be set to their optimum values, W<sub>opt</sub>. According to [21]

$$W_{opt} = \frac{1}{3\omega L R_s C_{ox}} \quad , \tag{3.1}$$

where  $\omega$  is the operating frequency of the circuit in radian, L is the minimum feature size of the fabrication process (0.18  $\mu$ m in this work),  $C_{ox}$  is the gate capacitance per unit area, and  $R_S$  is the input resistance (50 $\Omega$  in this case).

Inductors L3 and L4 are used for matching the input resistance,  $Z_{in}$ , to  $50\Omega$ , and to simultaneously resonate at the operating frequency of 5.2GHz. It can be shown that

$$Z_{in} = s(L3 + L4) + \frac{1}{sC_{gs}} + \left(\frac{g_m}{C_{gs} + C_{gd}}\right)L3.$$

(3.2)

At the operating frequency, the first two terms in Eq. (3.2) should cancel each other by adjusting the value of L4. This leaves  $\left(\frac{g_m}{C_{gs}+C_{gd}}\right)L_3$  to set the value of the real part of the input impedance, by selecting an appropriate value for L3. Buffers formed by transistors M3 and M6 are used to provide extra gain, and to increase isolation between the LNA and the mixer.

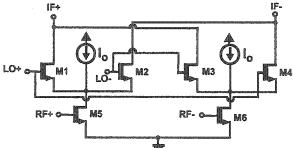

#### D. Mixer

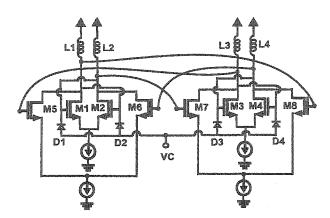

The mixer (Fig. 3.5), which is based on a double-balanced Gilbert active structure in order to reject any LO-to-RF feedthrough, downconverts the differential RF signal from 5.2 GHz to a 600 - 800 MHz IF. It consists of a pair of transconductors (M5 - M6) and four transistors (M1-M4) which act as switches.

Although passive mixers generate less noise than active mixers, they require a larger LO signal and have no conversion gain, resulting in a severe noise figure deterioration. On the other hand, while active mixers can provide signal gain, they suffer from the noise generated by the transconductor and the switching transistors. To minimize the noise from the latter, which appears directly in the output signal path, extra current sources  $I_0$  are used as shown in Fig. 3.5. This decreases the DC biasing currents of M1 - M4, thus reducing their shot noise, while maintaining the high bias of transistors M5-M6 necessary to ensure a high RF gain [23]. Apart from lowering the shot noise, the use of sources  $I_0$  also enables higher conversion gain by allowing the use of larger resistive loads, since the drain currents through the switching transistors are lowered. Besides the shot noise, the switching transistors M1 to M4 also contribute thermal noise to the output. At the zero-crossing of the LO signal, all the switching transistors will be on injecting thermal noise to the output. Therefore, a large LO is desired to minimize the transition time.

Fig. 3.5: Schematic of the I/Q mixer.

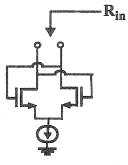

To improve the mixer linearity, the transconductor pair is realized as a grounded-source differential pair, rather than a differential pair with constant current source biasing. A current source biasing would introduce third-order intermodulation products and lower the overall linearity of the mixer [24], since the output drain current depends on the square of the input voltage. On the other hand, with the grounded-source pair (Fig. 3.6), the differential output current, I<sub>out</sub>, can be expressed as:

$$I_{out} = \frac{1}{2} \mu_o C_{ox} \frac{W}{L} [(V_{gs1} - V_{th})^2 - (V_{gs2} - V_{th})^2] = \frac{1}{2} \mu_o C_{ox} \frac{W}{L} (V_{gs1} - V_{gs2}) (V_{gs1} + V_{gs2} - 2V_{th})$$

$$I_{out} = \mu_o C_{ox} \frac{W}{I} V_{in} (V_{gs} - V_{th}) . \tag{3.3}$$

As a result, the output current,  $I_{out}$ , only depends linearly on the input voltage,  $V_{in}$ . This topology also helps reducing the voltage headroom requirements, as it eliminates any additional transistor stacking, such that needed for a tail biasing current source.

Since the mixer is to operate from a 0.8-V supply, transistors with relatively large widths are used, in order to lower the threshold voltage required to bias the transistors in the saturation region. In addition, the gates of transistors M1-M4 are biased near threshold, in order to minimize their switching times, thus reducing the output noise. The RF signals from the LNA are AC coupled to the inputs of the mixers, in order to allow the latter to be set to different DC biasing points. As for the loads at the IF outputs, they can

Fig. 3.6: Grounded-source differential pair.

Fig. 3.7: Schematic of the quadrature VCO.

be either resistive or reactive (e.g. an LC tank).

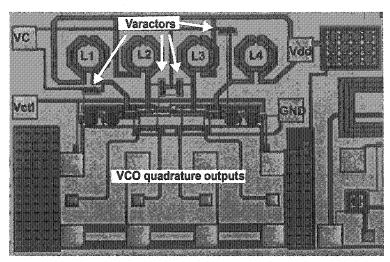

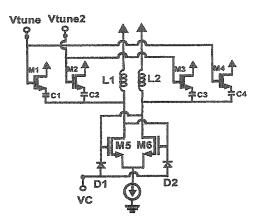

#### E. Voltage-controlled oscillator

The core structure of the VCO (Fig. 3.7) is a differential topology, which consists of two pairs of cross-coupled LC oscillators formed by transistors M1-M2 and M3-M4, using on-chip load inductors L1-L4. The two transistor pairs are coupled through transistors M5-M8 in order to provide quadrature outputs for both the I and Q paths [25]. The two cross-coupled transistor pairs can only co-exist in quadrature phase. If the two pairs are in-phase or in anti-phase, then the negative resistance will be absorbed by one of the pairs, turning off the other pair and pulling up both of its drain nodes to V<sub>DD</sub>. As a result, it will also shut off the remaining pair through the cross-coupled transistors, since both of the gates of the transistor pair cannot be connected to V<sub>DD</sub> at the same time in order for oscillation to occur. In summary, oscillation cannot be maintained if the two pairs are in-phase or in anti-phase. Inductors L1-L4 resonate with the parasitic capacitors of the transistors to set the oscillation frequency, while the transistors provide the negative resistances necessary to overcome the inductors losses.

In order to ensure oscillation, the oscillator must provide sufficient transconductance

to overcome the losses in the LC tanks. Figure 3.8 shows the input resistance,  $R_{\rm in}$ , seen by the LC tanks; it equals  $2/g_{\rm m}$ , where  $g_{\rm m}$  is the transconductance of one transistor. Assuming a biasing current of 3mA for each one of transistors M1 to M4, and the Q factor and series resistance of the inductor being 5 and  $5\Omega$  respectively, and  $\mu_{\rm o}C_{\rm ox}$  is  $429\mu{\rm A/V}^2$  for the CMOS technology used, the minimum width of the transistor core is found using the following equation,

$$R_{in} = \frac{2}{g_m} = Q^2 \times R_s \tag{3.4}$$

where

$$g_m = \sqrt{2I_D \mu_o C_{ox} \frac{W}{L}} . ag{3.5}$$

From Eq. (3.4) and Eq. (3.5),  $g_m$  is 0.016S, and thus W/L needs to equal 100.

However, in order to guarantee that the VCO starts up, a safety factor of 3 was used. As a result, the transconductance value was tripled, and from Eq. (3.5):

$$g_m = \sqrt{2I_D\mu_o C_{ox} \frac{W}{L}} = 0.016 \times 3 \quad ,$$

and the corresponding W/L is 900. To minimize the parasitics due to the drain capacitances of the transistors, minimum channel lengths were used, i.e.,  $L=0.18 \mu m$ ,

Fig. 3.8: Input resistance of the VCO core pair.

resulting in the widths of transistors M1 to M4 to be 150µm.

The output phase noise at an offset  $\Delta f$  from  $f_0$  can be approximated by the following relationship [26]

$$L\{\Delta f\} = kT(1+A) Z_o \frac{1}{Q_{tank}} \left(\frac{f_o}{\Delta f}\right)^2 \frac{1}{V_{rms}^2},$$

(3.6)

where kT is the product of the Boltzman constant by the absolute temperature, A is the noise factor safety margin necessary to ensure oscillation start-up,  $V_{rms}$  is the root mean square voltage at the oscillation nodes, and  $Z_0 = \sqrt{(L/C_{tank})}$  and  $Q_{tank}$  are the tank characteristic impedance and quality factor, respectively.

In order to provide tuning capabilities, accumulation mode varactors D1 - D4, which are implemented as NMOS transistors over N-wells [26], are used and are controlled with an external DC voltage source, V<sub>c</sub>, in order to provide the desired capacitance. As a result, the tuning range of the VCO is from 4.4GHz to 4.6GHz. Common-source buffers with inductive loads are used to increase isolation to the mixer, and to provide a much desirable amplification for the VCO signals driving the mixers.

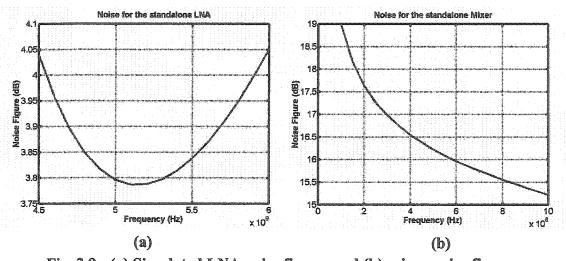

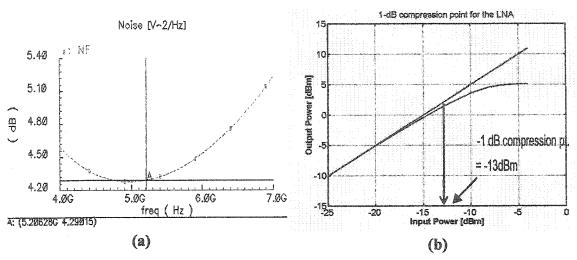

Fig. 3.9: (a) Simulated LNA noise figure, and (b) mixer noise figure.

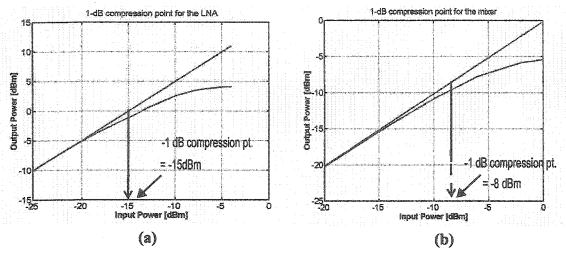

Fig. 3.10: Simulated 1-dB compression point for (a) LNA (b) mixer.

## 3.2.2 Simulation results

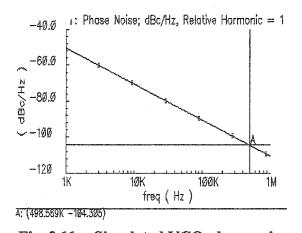

HSPICE and SpectreRF were used to simulate the different receiver components, as well as the overall performance of the receiver from the extracted layout with parasitics. Figure 3.9 shows that the expected noise figure of the LNA is 3.8 dB at 5.2GHz, while the mixer has an expected noise figure of about 16.5dB. Figure 3.10 shows the 1-dB compression point of the LNA and of the mixer to be -15dBm and -8dBm respectively. The simulated phase noise of the VCO is about -104dBc/Hz at a 500kHz offset as shown

Fig. 3.11: Simulated VCO phase noise.

| LNA               |        |

|-------------------|--------|

| Operating freq.   | 5.2GHz |

| Power consumption | 24mW   |

| Noise figure      | 3.8dB  |

| $S_{11}$          | -15 dB |

| 1dB compression   | -15dB  |

| Voltage gain      | 15 dB  |

| Mixer                                            | vanadeka e ndari e dikita en e Pada e dea e de Ville da dizion e Addizional |

|--------------------------------------------------|-----------------------------------------------------------------------------|

| Power consumption                                | 16mW                                                                        |

| SSB noise figure                                 | 16.5dB                                                                      |

| 1dB compression                                  | -8dB                                                                        |

| Conversion gain with (inductive/ resistive) load | 10dB/0dB                                                                    |

| VCO                            |                 |

|--------------------------------|-----------------|

| Operating Freq.                | 4.5GHz          |

| Power consumption              | 30mW            |

| Phase noise @<br>500kHz offset | -104 dBc/<br>Hz |

Table 3.2: First receiver components simulation results.

in Fig. 3.11. Table 3.2 summarizes the simulation results for each individual component of the first prototype, with a 0.8V supply. The overall gain for the receiver is 15dB and the image rejection ratio is 20.5dB with an image signal at 3.8GHz.

#### A. Receiver overall performance

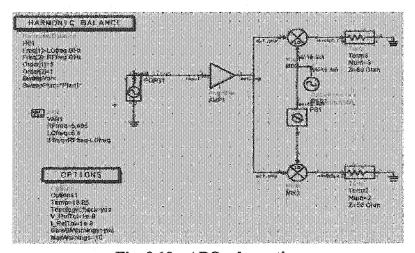

In order to verify the overall performance of the receiver, HP ADS was used to evaluate the system noise figure and 1-dB compression point. Figure 3.12 shows the ADS schematic that was used to perform the simulation. All the receiver components are taken from the ADS standard libraries, and the parameters for each component were set based

Fig. 3.12: ADS schematic.

on the simulated performances shown in Table 3.2. In order to generate the quadrature VCO signal in ADS, a 90° phase shifter was added, since a quadrature VCO component was not available in ADS. The simulated noise figure and 1-dB compression point for the receiver were found to be NF = 6.5 dB and -15 dBm respectively.

## 3.2.3 Measurement results

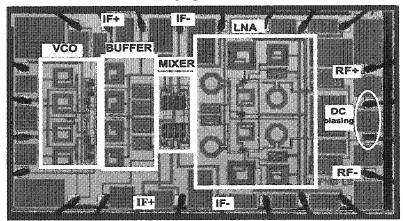

The low-voltage receiver frontend was fabricated in a standard  $0.18\,\mu m$  CMOS technology from TSMC. Figure 3.13 shows the micrograph of the chip with an area of  $3.2mm \times 1.7mm$ . As shown in the micrograph, the LNA and the VCO are placed as far as

Fig. 3.13: Receiver chip

possible from each other to minimize interference. The differential RF inputs are separated by DC biasing pins in order to minimize the cross-coupling effects between them. A standalone LNA, which was designed to operate at 5.8GHz and was packaged in the same package (CFP24) as the receiver, and a standalone VCO, were also built in order to verify their performance. The only difference between the integrated components and the standalone versions is that the standalone versions had additional buffers with resistive loads in order to drive the  $50\Omega$  impedances of the measurement equipment,

Fig. 3.14: Test fixture for the receiver.

instead of inductive loads.

### A. Calibrating for the package and the test fixture losses

Since the CFP24 package (the best option that was available to the designer at the time) is optimized for operation up to 2GHz frequency, extra losses at 5GHz were expected, but could not be predicted during design/simulation.

To account for the package losses, the exact same test fixture (Fig. 3.14) that was used

Fig. 3.15: Loss of the test fixture with package replaced by a short.

Fig. 3.16: Loss of the test fixture with an empty package shorted internally.

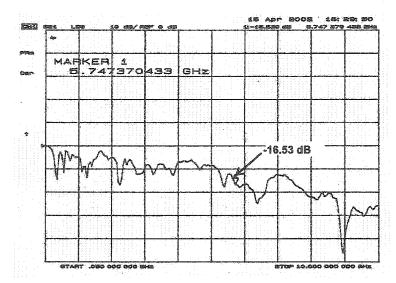

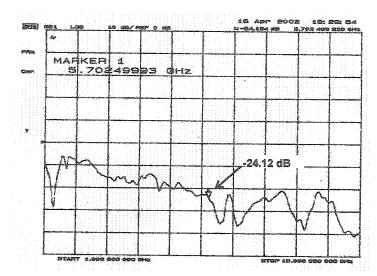

in measuring the performance of the receiver, was used with an empty CFP24 package having the two input and output pins of the receiver connected by a metal wire internally. This was done in order to measure the losses due to the package. The losses due to the test setup were measured separately: A metal wire was used to short two pins of the package on the PCB while the package was removed. Fig. 3.15 shows a -16dB loss for the test setup alone at 5.7GHz. With the empty package, as shown in Fig. 3.16, the loss at 5.7GHz is -24dB. As a result, it is estimated that each pin of the package has (24-16)/2 = 4dB loss at 5.7GHz.

Apart from accounting for the losses in the package, the losses due to the PCB and to the connection wires will also decrease the measured overall gain of the receiver.

| Each pin of the CFP24 package @ 5GHz   | -4dB    |

|----------------------------------------|---------|

| RF part of the PCB in the 5GHz range   | -6.5dB  |

| IF transformer @300MHz                 | -3dB    |

| Connection cables and connectors @5GHz | -3dB    |

| Total                                  | -16.5dB |

Table 3.3: Losses due to the test fixture.

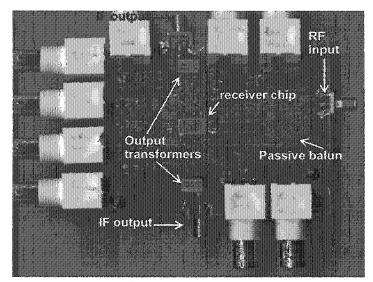

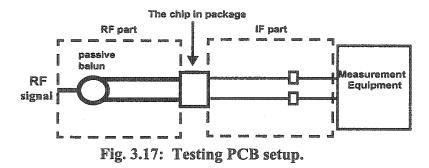

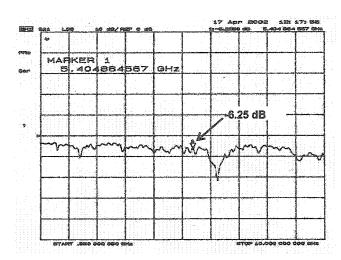

Depicted in Fig. 3.17 is the testing PCB setup: The circuit consists of two sections, an RF part and an IF part. The RF part includes the passive balun and all the PCB traces that carry the input 5GHz signals, while the IF part includes the IF transformers. All the signals after the chip are in the few mega-hertz frequency range. The PCB in Fig. C.2 in Appendix C was used to measure the losses due to the RF part at 5GHz. Figure 3.18 shows a -6.2dB loss at 5.7GHz. Finally, it was found through measurements that the cables and connectors between the measurement equipment and the PCB contribute about 3dB of loss in the 5GHz range. Since the IF portion of the setup operates at a lower frequency, it does not contribute with significant losses, apart from the 3dB loss associated with the IF transformer. Table 3.3 summarizes all the estimated losses due to

Fig. 3.18: Loss of the RF part of test fixture.

the test setup, with a total of -16.5dB.

#### B. Standalone LNA

A custom PCB was built to test the standalone LNA (Fig. 3.19). As described in section 3.2.1, a ring hyrid is used to generate the differential input signal. The same structure is used to combine the differential output signal to single-ended for measurement. To calibrate out the losses due to the baluns and to the PCB, a special test structure was built and used. The calibration procedure is detailed in Appendix B.

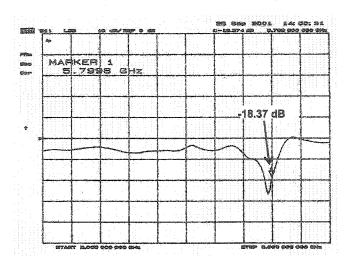

Although the LNA was designed to match a  $50\Omega$  input resistance, the parasitics from the PCB traces, connectors, cables, and the package do affect the input resistance. As a result, a simple off-chip matching network was used (Fig. 3.19). It consists of a pair of transmission lines that connect the balun to the LNA input, and a sliding capacitor. Together they form a differential  $\pi$ -matching network. By sliding the capacitor along the transmission lines, an input reflection coefficient  $S_{11} = -18.4$  dB is obtained for the LNA, as shown in Fig. 3.20.

Fig. 3.19: PCB for testing the standalone LNA.

Fig. 3.20: Measured  $S_{11}$  of the standalone LNA.

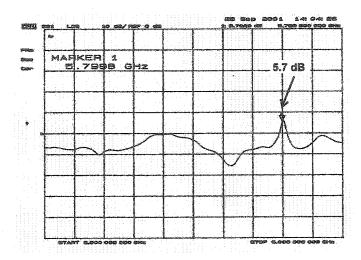

As for the gain of the LNA, Fig. 3.21 shows a 5.7dB gain at 5.8 GHz. Taking into account the losses due to the package (section 3.2.3A), the gain of the standalone LNA is estimated to actually be (5.7 + 4 + 4) = 13.7dB, which is fairly close to the gain predicted by simulation (15 dB). The lower measured value is attributed to the fact that, at resonance, slightly lower than expected quality factors of the on-chip inductors and capacitors were achieved. As a result, a portion of the RF signal could be lost to the LC tank [5].

Fig. 3.21: Measured  $S_{21}$  of the standalone LNA.

Fig. 3.22: Micrograph of the standalone VCO.

#### C. Standalone VCO

On-chip probing was used to test the performance of the standalone VCO (Fig. 3.22). The VCO generates quadrature signals at 4.5GHz. It has a tuning range from 4.4GHz to 4.6GHz, which agrees well with simulation (Table 3.2).

#### D. Overall

Since the performance of both the standalone versions of the LNA and of the VCO used in the receiver were verified, the next step is to test the receiver as a whole. Similar to the testing procedure for the standalone LNA, a custom test fixture which employs the hybrid balun to generate the differential RF input signals for the receiver is used. As was mentioned earlier, off-chip transformers from MiniCircuits were used to combine the output 700MHz IF signals. Figure 3.14 shows the PCB used in performing all the receiver measurements.

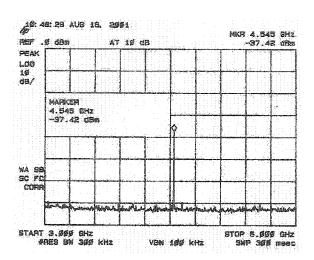

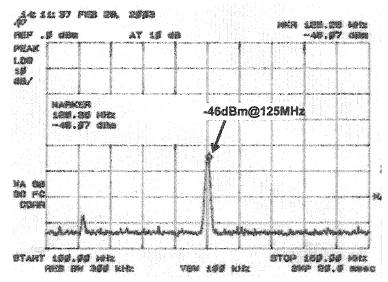

To verify that the on-chip VCO is functional and find its frequency, LO leakage was measured while turning off the supply voltage of the LNA. As shown in Fig. 3.23, an LO

Fig. 3.23: LO leakage in the receiver.

leakage signal of -37.4 dBm is observed at 4.5GHz, which shows that the VCO is functional.

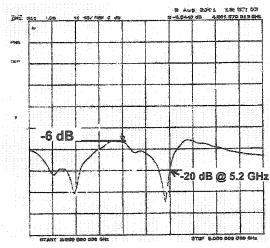

The next step in testing the receiver is to power up the entire chip from a 0.8V power supply. A sweep of the RF input frequency reveals that the LNA operates at 5.2 GHz, which was the desired operating frequency. With the VCO centered at 4.5 GHz, the IF signal is at 700 MHz. Resistive loads ( $50\Omega$ ) are used at the mixer outputs. Figure 3.24 shows a plot of the input reflection coefficient  $S_{11}$  (-20dB @ 5.2GHz) of the receiver, obtained with the help of a sliding capacitor as discussed earlier.

Fig. 3.24: Input reflection  $S_{11}$  of the receiver.

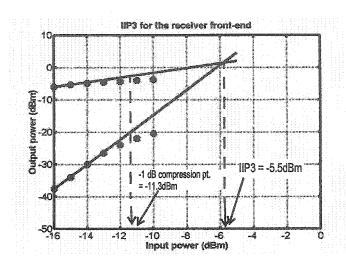

Fig. 3.25: (a) frequency response of the two-tone test (b) Measured third-order intercept plot.

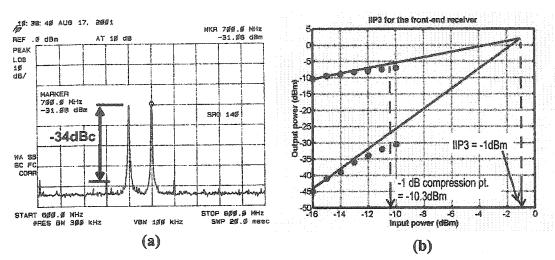

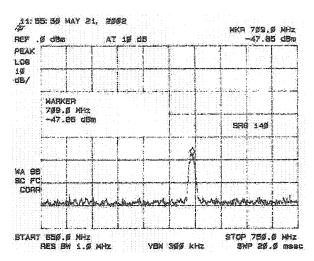

Figure 3.25a shows the measured output spectrum for a two-tone test input at 5.2GHz and 5.22GHz, with -20dBm of power. The fundamental signals appear at 680MHz and 700MHz, while the third-order intermodulation outputs, which are located at 660MHz and 720MHz, are -34dBc below the fundamentals. The same setup was used to obtain the overall 1-dB compression point and the IIP3 of the receiver, by sweeping the power of the two-tone input. Figure 3.25b depicts the third-order intercept plot, with the 1-dB compression point clearly denoted at -10.3dBm.

As can be deduced from Fig. 3.25a, the gain of the receiver without any calibration is about -11 dBm. As discussed in section 3.2.3A, the losses in the package and in the test fixture should be accounted for (Table 3.3). Doing so, the actual gain of the receiver is estimated to be about 6dB. However, the receiver overall gain was expected to be 13.5dB, knowing that the standalone LNA has a 13.5dB gain and that resistive loads are used at the mixer outputs, resulting in an expected mixer conversion gain of 0dB. A newly developed in-house tool was used to estimate and model the parasitic inductances of the

Fig. 3.26: Frequency response of the image signal.