# The Design of Low-Voltage High Frequency CMOS Low Noise Amplifiers for Future Wireless Applications

by Tommy Tsang, B.Eng. 2000

Department of Electrical & Computer Engineering McGill University, Montreal, Canada.

March, 2002

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your Me Yother Martines

Our Be Note retirence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-79101-7

Canadä

### **Abstract**

Increasing demand for bandwidth, for both voice and data communications, has motivated the need for high speed electronics. Particularly, in the wireless domain, new standards are constantly evolving towards higher operating frequencies and higher level of integration, with strong emphasis on low voltage, low power, and low cost.

RFIC's are traditionally implemented in III - V compounded semiconductors or in bipolar technologies, due to their superior RF performances (e.g. low noise) when compared to CMOS technologies. As technology advances, modern sub-micron CMOS technologies, which used to be delicated for digital circuits operating at lower frequencies, are now becoming more performant and more suitable for radio frequency circuit designs. The challenges are not only to design RF transceivers in standard CMOS processes, but also to establish design methodologies and optimization techniques for their building blocks.

This thesis is concerned with one of the key building blocks, namely the Low Noise Amplifier (*LNA*). Several low-voltage LNA's were successfully implemented in a standard 0.18 µm CMOS technology, operating in the 5-9 GHz frequency band, targeted for future wireless applications. A new and very simple gain control mechanism is suggested for the first time, which does not affect the optimum noise and impedance matching. The 8-9 GHz prototypes are the highest LNA frequencies reported to-date in

CMOS. All prototypes exhibit gain tuning ranges of over 10 dB, and can operate from a supply voltage as low as 0.7 V.

Designing circuits at RF imposes many uncertainties and challenges, owing to the poor modeling of integrated passives and/or active devices. A design strategy for optimizing RF passive components (e.g. inductors, capacitors, and varactors) beyond 5 GHz is presented. Trade-offs between different design issues are discussed. The effectiveness of these techniques has been demonstrated through measurement results of several LNA's.

An attempt is made to explore the possibility of using Micro-Electro Mechanical Systems (*MEMS*) in the RF arena. Several successful tunable capacitor implementations, targeted to RF applications, are demonstrated through measurement results, and a detailed discussion of design equations is presented. Challenges and limitations of MEMS for future RF applications are addressed.

### Résumé

Dû à une demande accrue pour la bande passante des systèmes de la voix et des données, des circuits électroniques opérant à de grandes vitesses sont maintenant rendu nécessaire. Cet énoncé s'applique particulièrement au domaine du sans fil, les nouveaux standards ne cessent d'évoluer vers des fréquences de plus en plus élevées. Ces même circuits doivent dorénavant opérer à des fréquences élevées et être très intégrés, tout en consommant moins de puissance et ayant de faible coûts de production.

La technologie bipolaire ou composée III - V, dû à leurs performances supérieures pour les applications RF (ex. bruit, linéarité et gain) lorsque comparée à la technologie CMOS, est normalement utilisée dans la construction des circuits intégrés RF. Avec les récentes avancées technologiques, la technologie CMOS, principalement utilisée dans des circuits digitaux de fréquences plus basses, est maintenant convenable pour la conception des circuits de fréquence radio. En plus de concevoir de circuits RF robustes utilisant la technologie CMOS conventionnelle, les défis se portent aussi vers la méthodologie ainsi que les techniques d'optimization de ces même circuits.

Ce mémoire se penche sur une des composantes importantes de tel circuit: les amplificateurs à faible bruit (*AFB*). Différents AFB opérants à de bas potentiels ont été réalisés avec succès dans une technologie CMOS de 0.18 µm. Ces AFB opèrent dans une bande pour les futures applications sans fil: 5-9 GHz. Pour la première fois, un circuit

simple controllant le gain en affectant ni le bruit optimal ni l'impédance d'entrée du circuit est présenté. Les prototypes opérants dans la bande de 8-9 GHz sont les AFB les plus rapides à avoir été rapportés à ce jour. Opérant jusqu'à une tension de 0.7 V, tous les prototypes montrent un ajustement de gain de plus de 10 dB.

La conception de circuit RF est difficile dûe aux incertitudes liées à la modélisation incomplète des composantes actives et passives. Une stratégie de conception pour l'optimisation des composantes passives (ex. inductances, condensateurs et varators), opérant à plus de 5 GHz, est ici présentée. L'efficacité de ces techniques est démontrée à l'aide de mesures concluantes prises sur plusieurs AFB.

Une tentative a été faite pour explorer la possibilité d'utiliser des Micro-Electro Mechanical Systems (*MEMS*) dans le domaine du RF. Plusieurs condensateurs variables convenables aux applications RF sont présentés ainsi qu'une discussion détaillée des équations utilisées pour la conception. De plus, une discussion sur les défis et les limitations des MEMS pour de future application RF est faite.

# **Acknowledgments**

I would like to acknowledge many people, who have helped and supported me throughout the course of the research and writing of this thesis. In Him, I am grateful that I have grown up and learned so much. 'My heart trusts in Him, and I am helped.' - Psalm 28:7.

First and foremost, I would like to thank my supervisor, Prof. Mourad El-Gamal, for giving me the opportunity to pursue a master degree at the Microelectronics and Computer Systems (MACS) laboratory. His valuable guidance and insightful advises have been the key success of this work.

I would like to thank all the members of the MACS lab. for such a friendly and pleasant working environment. Special thanks goes to Ramez, Ahmed, Clarence, Nazmy, Geoffrey, Francis, Rola, Koon, Antonio and Tang, for actively participating in countless 'mind-stimulating' Q&A's. I am very thankful to my friends outside the lab. for their constant encouragement and enlightenment. Sincere thanks to Yan Yan, Lam Lam, Hoi Ying, Miranda, Ting, Pui Sang, Angie, and members of the Enoch fellowship. I would like to give my deepest thanks to Vanessa Lai who had sacrificed her time to take care of me during the period of my knee surgery.

I also wish to acknowledge the Canadian Microelectronics Corporation (CMC) for technology and equipment accesses, and MICRONET for partial funding of this work.

This thesis is delicated to my wonderful parents, Pak On and Lai Lin, for their never ending support and love. To them, I will always be grateful and proud.

# **Table of Contents**

| Abstract                                                                                                                                                                                                                                                         |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Résumé                                                                                                                                                                                                                                                           | iii                  |

| Acknowledgments                                                                                                                                                                                                                                                  | V                    |

| Γable of Contents                                                                                                                                                                                                                                                | <b>v</b> i           |

| List of Figures                                                                                                                                                                                                                                                  | vii                  |

| List of Tables                                                                                                                                                                                                                                                   | <b>X</b> i           |

| Chapter 1 - Introduction                                                                                                                                                                                                                                         | 1                    |

| 1.1 - Technology Choices in RF Designs 1.2 - Motivation 1.3 - State-of-the-Art in LNA Designs 1.4 - Thesis Outline 1.5 - Thesis Contributions                                                                                                                    | 2<br>5<br>7<br>11    |

| Chapter 2 - CMOS LNA Basics and Circuit Topolog                                                                                                                                                                                                                  | ies15                |

| 2.1 - Noise         2.1.1 - Thermal Noise         2.1.2 - Shot Noise         2.1.3 - Flicker Noise (1/f Noise)         2.1.4 - Noise Sources in MOSFET's         2.1.5 - Noise Figure         2.1.6 - Noise Temperature         2.1.7 - Cascade of Noise Figures | 15<br>17<br>18<br>19 |

| 2.2 - Distortion                                          | 22     |

|-----------------------------------------------------------|--------|

| 2.2.1 - Non-linearity                                     | 22     |

| 2.2.2 - Gain Compression                                  | 23     |

| 2.2.3 - Intermodulation Distortion                        | 24     |

| 2.2.4 - Cascaded Non-Linearities                          | 26     |

| 2.3 - CMOS LNA Fundamentals                               | 27     |

| 2.3.1 - Input Impedance Matching                          | 28     |

| 2.3.2 - LNA Gain                                          | 31     |

| 2.4 - Low Voltage LNA Topologies                          |        |

| 2.4.1 - Single Transistor LNA Topology                    |        |

| 2.4.2 - Conventional Cascode LNA Topology                 | 36     |

| 2.4.3 - LC-Coupled LNA Topology                           |        |

| 2.4.4 - Folded Cascode LNA Topology                       | 41     |

| Chapter 3 - Design of RF Passive Components               | 15     |

|                                                           |        |

| 3.1 - Passive Devices in Si CMOS Technologies             |        |

| 3.1.1 - The Quality of Passive Devices                    |        |

| 3.1.2 - Loss Mechanisms                                   |        |

| 3.2 - Integrated Inductor Design Guidelines               |        |

| 3.2.1 - Existing Work on Integrated Inductor Design       | 49     |

| 3.2.2 - Integrated Inductors Design Strategy Beyond 5 GHz |        |

| 3.2.3 - Integrated Capacitors Design                      | 57     |

| 3.2.4 - Integrated Varactors Design                       | 59     |

| 3.3 - MEMS for RF Applications                            | 61     |

| 3.3.1 - The Multi-User MEMS Processes (MUMPs)             | 61     |

| 3.3.2 - MEMS-Based Variable Capacitors                    |        |

| 3.3.3 - Limitations of the RF MEMS Varactors Presented    | 74     |

| Chapter 4 - Sub-1 V, > 5.8 GHz, Tunable LNA Measur        | rement |

| Results                                                   |        |

|                                                           |        |

| 4.1 - RF Layout Techniques                                |        |

| 4.2 - Tunable Sub-1 V 5.8 GHz CMOS LNA                    |        |

| 4.3 - Integrated 8 and 9 GHz CMOS LNA's                   | 87     |

| Chapter 5 - Conclusion                                    | 94     |

| 5.1 - Summary                                             | 94     |

| 5.2 - Topics for Future Research                          |        |

| •                                                         |        |

| References                                                | 97     |

# **List of Figures**

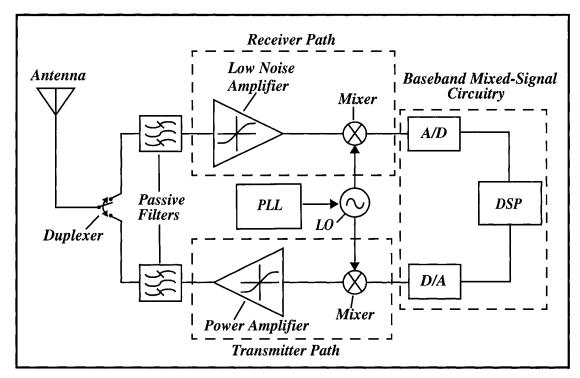

| Figure 1.1  | The conceptual block diagram of a typical RF transceiver                 | 2  |

|-------------|--------------------------------------------------------------------------|----|

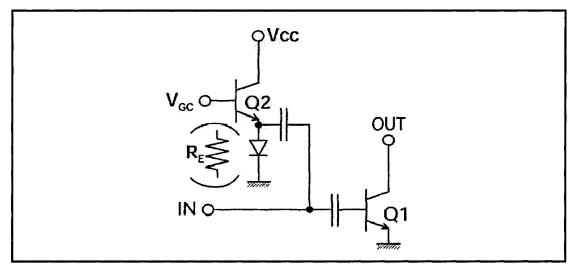

| Figure 1.2  | Simplified schematic of the proposed gain controlled LNA [30]            | 8  |

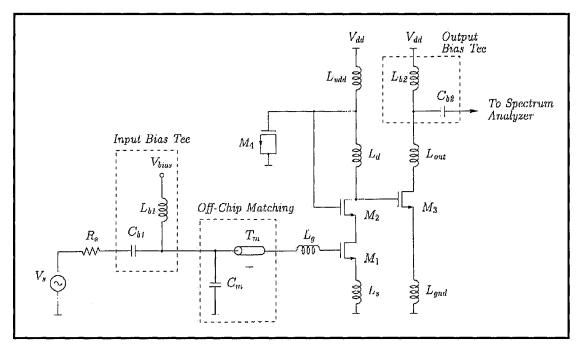

| Figure 1.3  | Complete schematic of the LNA in [31], including off-chip elements       | 10 |

| Figure 2.1  | (a) Noise voltage model and (b) noise current model for computing the    | •  |

|             | thermal noise of a resistor                                              | 16 |

| Figure 2.2  | Noise equivalent block diagram of a system                               | 20 |

| Figure 2.3  | Cascaded noisy stages.                                                   | 21 |

| Figure 2.4  | Graphical explanation of 1 dB compression point                          | 23 |

| Figure 2.5  | (a) Intermodulation in a non-linear system. (b) Third-order intercept    | 24 |

| Figure 2.6  | Cascade of two non-linear stages.                                        | 26 |

| Figure 2.7  | LNA input matching topologies: (a) resistive terminations, (b) 1/gm      |    |

|             | terminations, and (c) inductive degeneration.                            | 28 |

| Figure 2.8  | Small signal equivalent circuit at the input of the LNA                  | 29 |

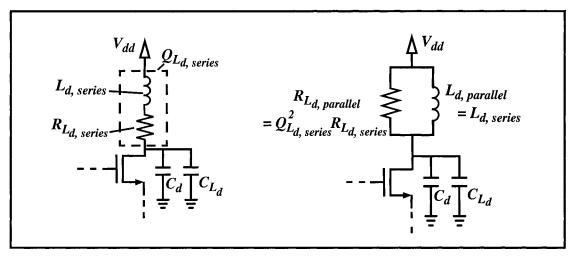

| Figure 2.9  | Series-shunt transformation of the resonant tank                         | 32 |

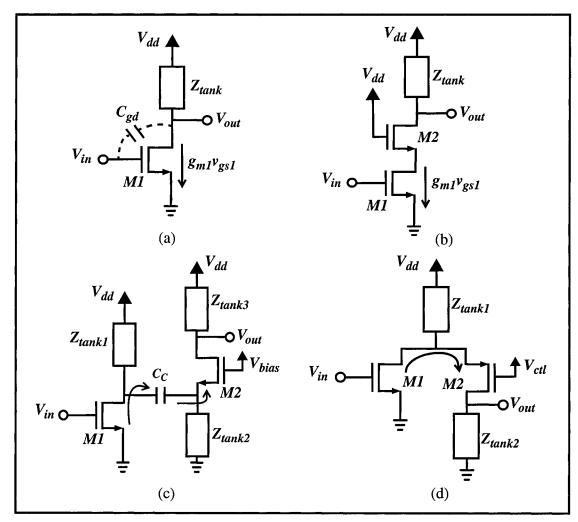

| Figure 2.10 | LNA topologies: (a) Single transistor. (b) Conventional cascode.         |    |

|             | (c) LC-coupled. (d) Modified folded cascode [44]                         | 34 |

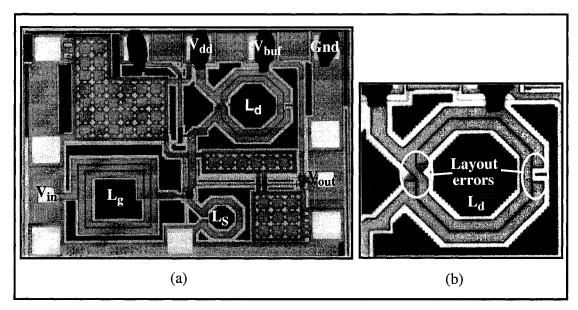

| Figure 2.11 | (a) Microphotograph of the 1 V 5.8 GHz cascode CMOS LNA.                 |    |

|             | (b) A zoom-in view of the tank inductor [47]                             | 36 |

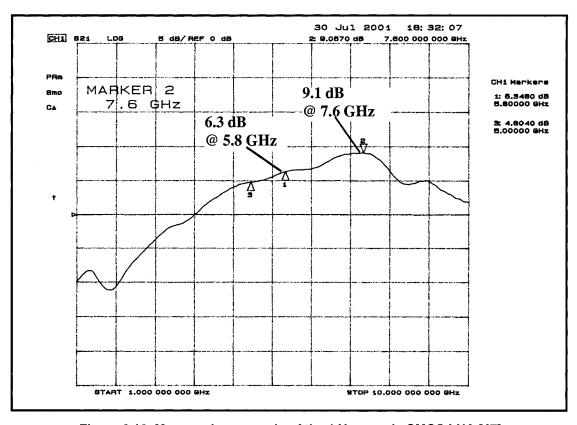

| Figure 2.12 | Measured power gain of the 1 V cascode CMOS LNA [47]                     | 37 |

| Figure 2.13 | Folded cascode topologies: (a) Wideband conventional.                    |    |

| _           | (b) Narrowband modified.                                                 | 41 |

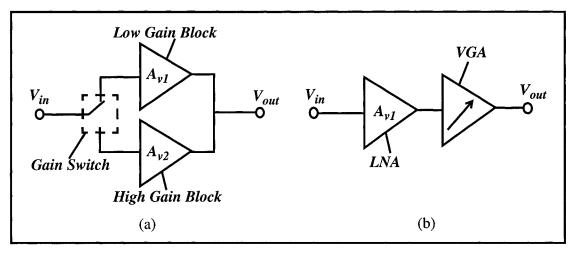

| Figure 2.14 | Conceptual view of the variable gain amplifiers: (a) Switch-control type | e. |

| _           | (b) Two-stage LNA-VGA type.                                              |    |

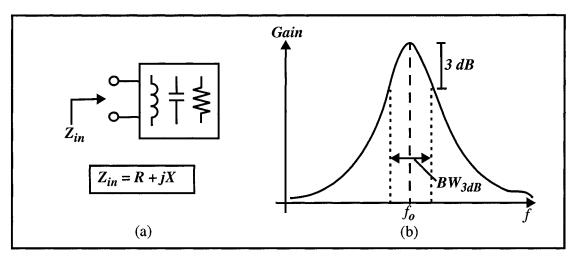

| Figure 3.1  | (a) Input impedance of a practical passive device. (b) Quality factor    |    |

|             | of an LC resonant tank.                                                  | 46 |

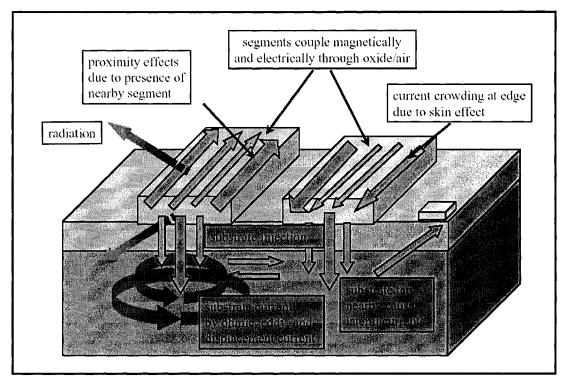

| Figure 3.2  | Various loss mechanisms in an IC process [50]                            | 47 |

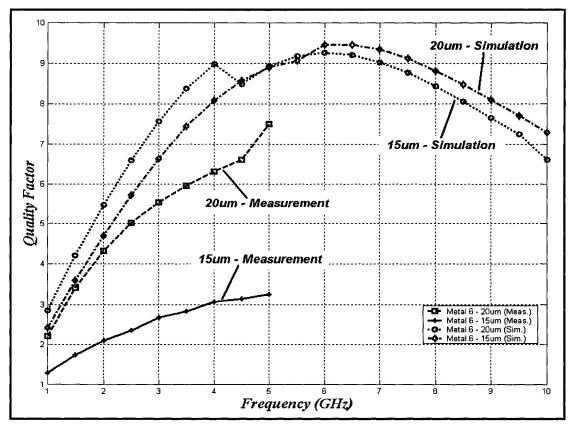

| Figure 3.3  | A comparison of the quality factor of the two inductor structures with   |    |

| -           | different conductor widths                                               | 53 |

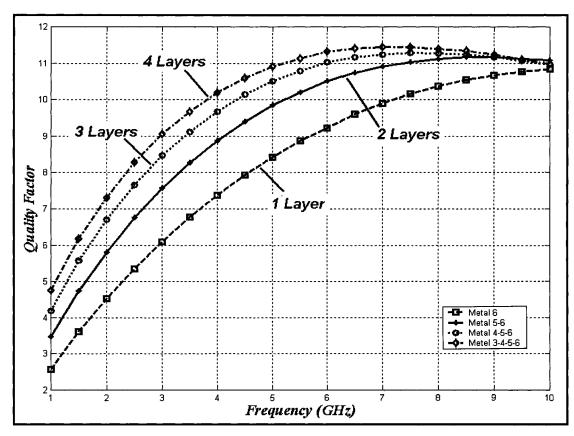

| Figure 3.4   | Simulation plot of the quality factor of the multi-layer stacking inductor structures.                               | .54      |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------|

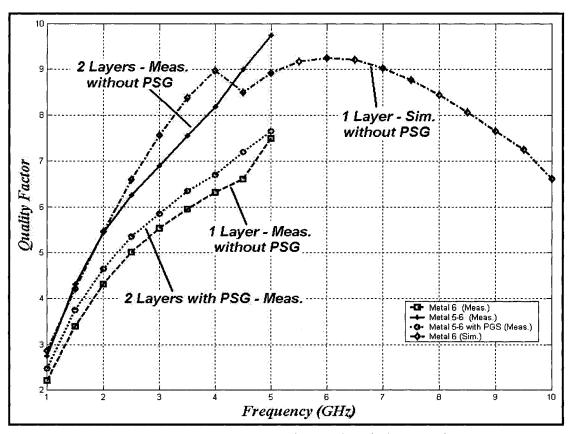

| Figure 3.5   | A comparison on the quality factor of the inductors with or without patterned ground shield.                         | .55      |

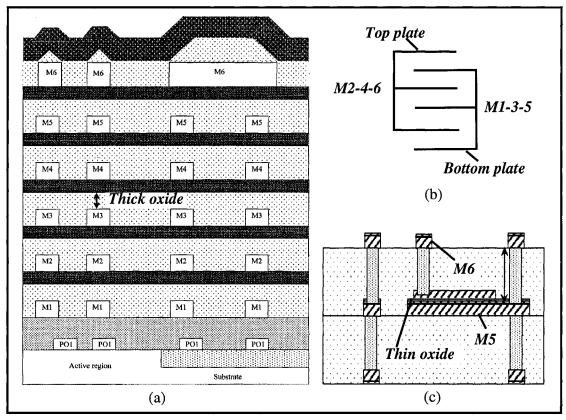

| Figure 3.6   | (a) The cross section of a typical CMOS process. (b) Multi-layer                                                     |          |

| C            | capacitor structure. (c) The cross section of a special MIM structure                                                | 57       |

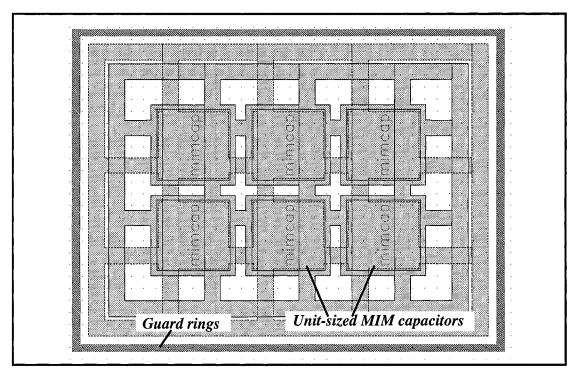

| Figure 3.7   | Example layout of a MIM capacitor                                                                                    |          |

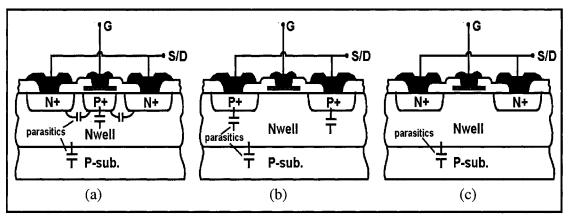

| Figure 3.8   | The cross-sectional views of (a) PN-junction, (b) PMOS, and                                                          |          |

|              | (c) NMOS over Nwell varactors.                                                                                       | 59       |

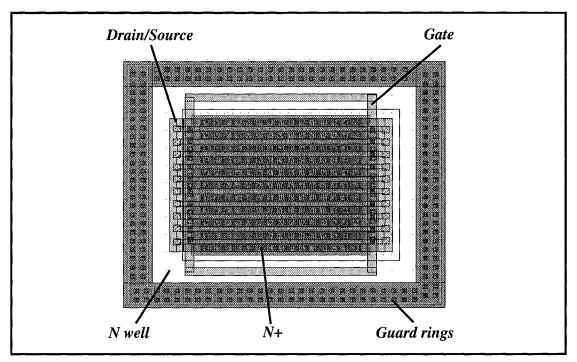

| Figure 3.9   | The layout of the accumulation-mode varactor                                                                         | 60       |

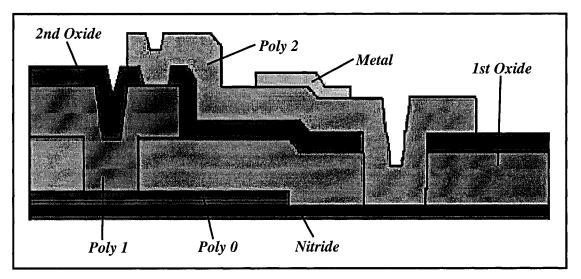

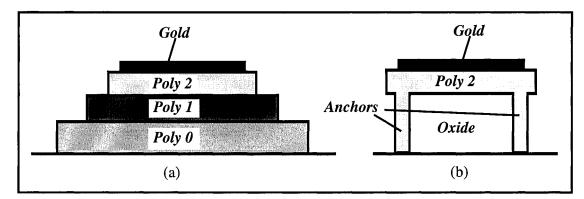

| Figure 3.10  | The cross-sectional view of the 7-layers MUMPs process [68]                                                          |          |

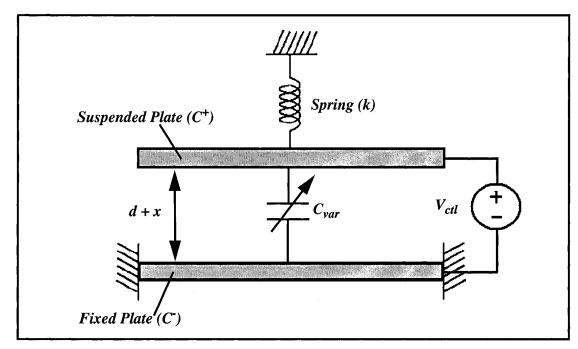

| Figure 3.11  | The conceptual model of a MEMS-based tunable parallel plate                                                          |          |

|              | capacitor.                                                                                                           | 63       |

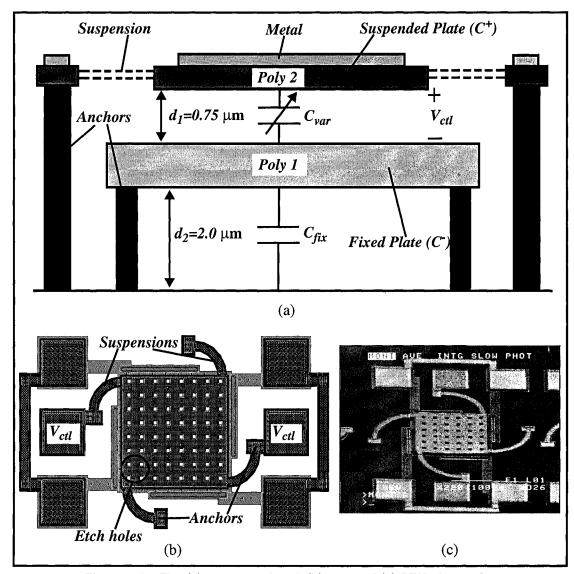

| Figure 3.12  | The (a) cross-sectional, (b) top, and (c) SEM views of a tunable                                                     |          |

|              | capacitor (Type 1)                                                                                                   | 66       |

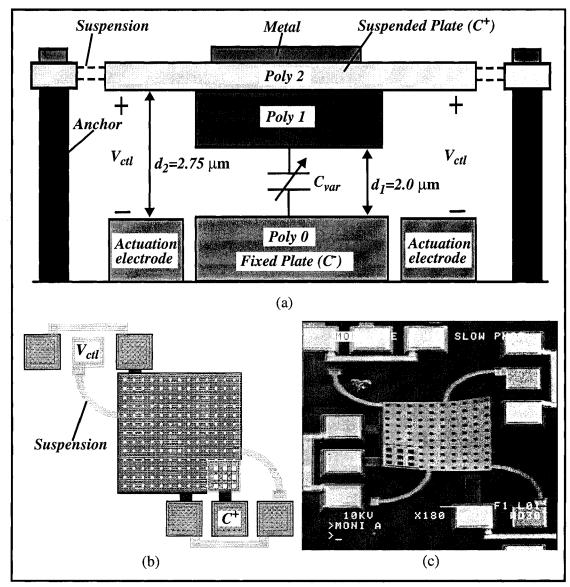

| Figure 3.13  | The (a) cross-sectional, (b) top, and (c) SEM views of a tunable                                                     |          |

|              | capacitor (Type 2)                                                                                                   | 67       |

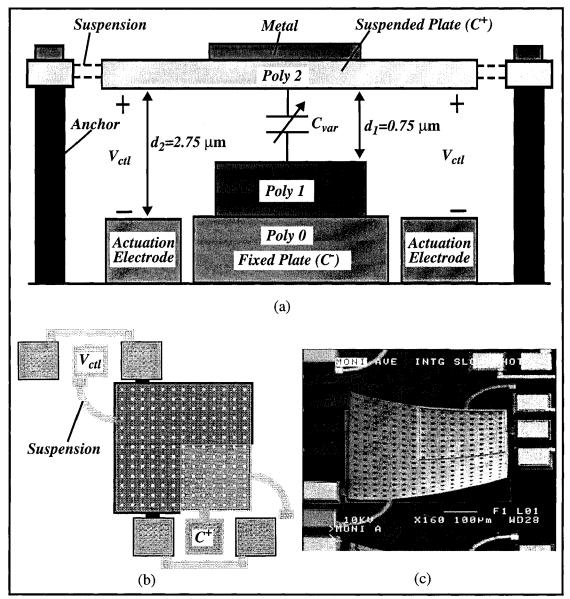

| Figure 3.14  | The (a) cross-sectional, (b) top, and (c) SEM views of a tunable                                                     |          |

|              | capacitor (Type 3)                                                                                                   | 68       |

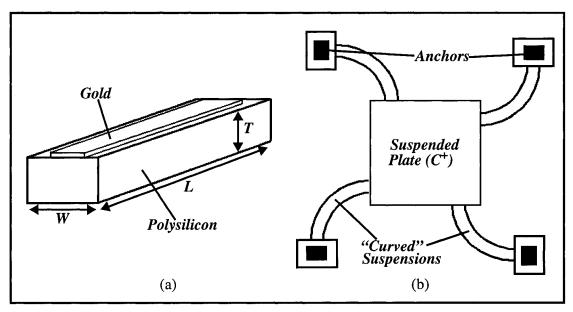

| Figure 3.15  | (a) The schematic of the suspension. (b) The top view of the tunable                                                 |          |

|              | capacitor.                                                                                                           | 69       |

| Figure 3.16  | The cross-sectional views of the (a) conventional and (b) low parasitic                                              |          |

|              | pad structures                                                                                                       |          |

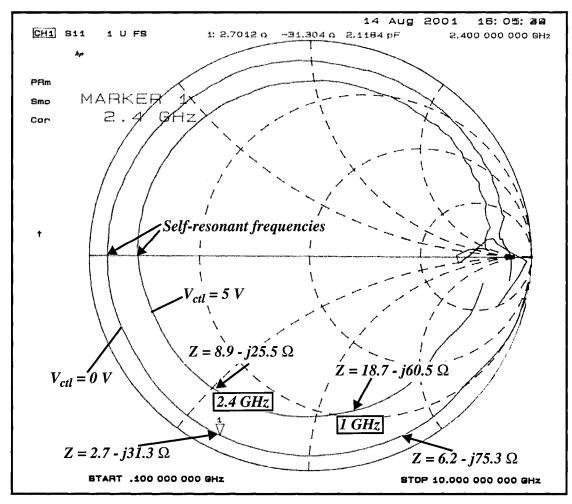

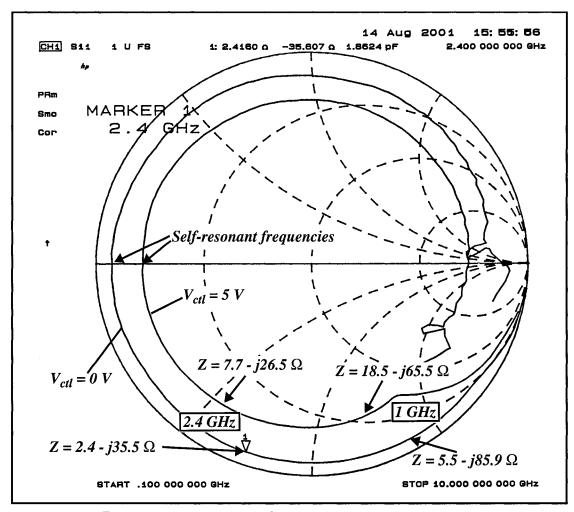

| Figure 3.17  | The measured S11 of the type-1 tunable capacitor                                                                     |          |

| Figure 3.18  | The measured S11 of the type-3 tunable capacitor                                                                     | .72      |

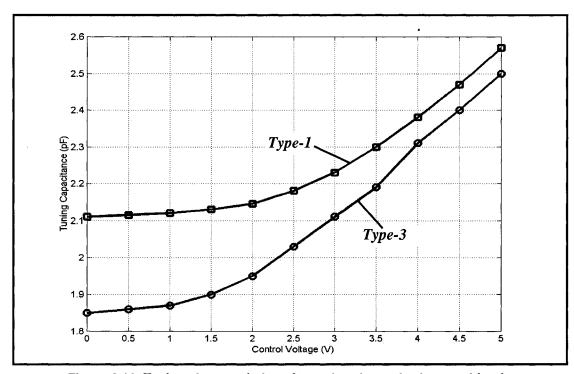

| Figure 3.19  | Tuning characteristics of type-1 and type-3 micromachined tunable                                                    | <b>-</b> |

| E: 2 20      | capacitors.                                                                                                          | 13       |

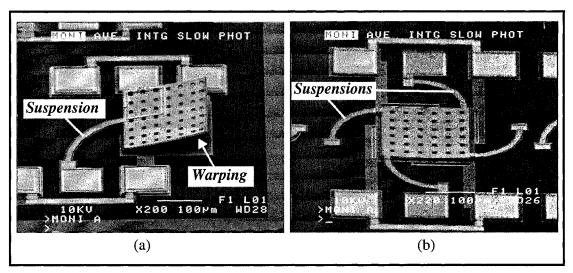

| Figure 3.20  | The effects of warping due to residual stresses in MEMS-based tunable capacitors - a) high stress and b) low stress. | 74       |

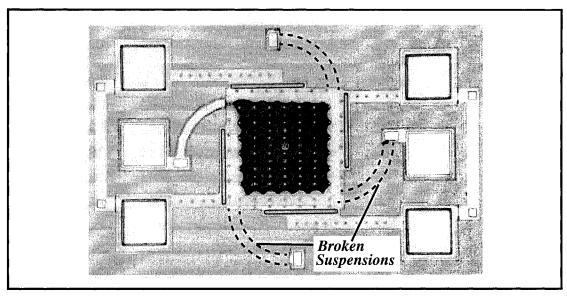

| Figure 3.21  | A MEMS-based tunable capacitor with damaged suspensions                                                              |          |

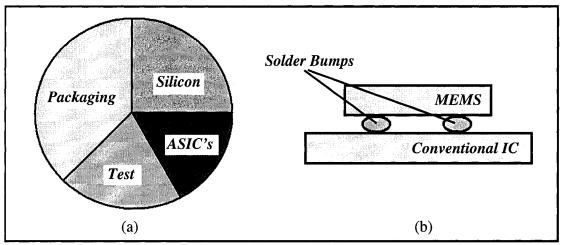

| Figure 3.22  |                                                                                                                      | 15       |

| 1 15410 3.22 | (b) Flip-chip bonding technology.                                                                                    | 76       |

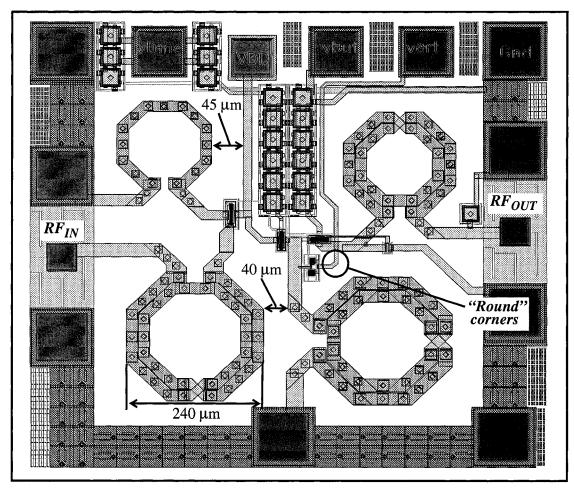

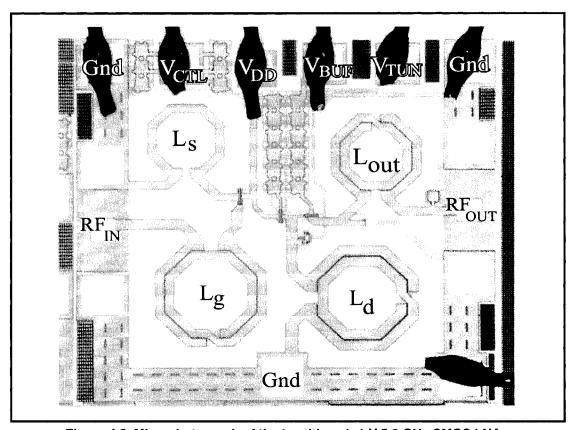

| Figure 4.1   | Layout of a 5.8 GHz CMOS LNA.                                                                                        |          |

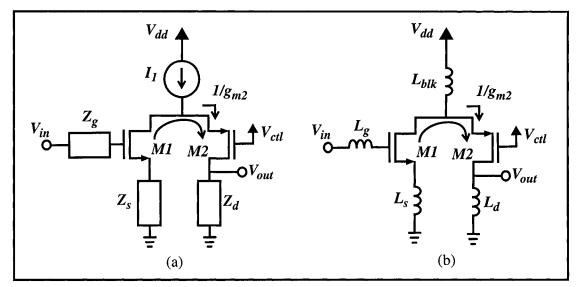

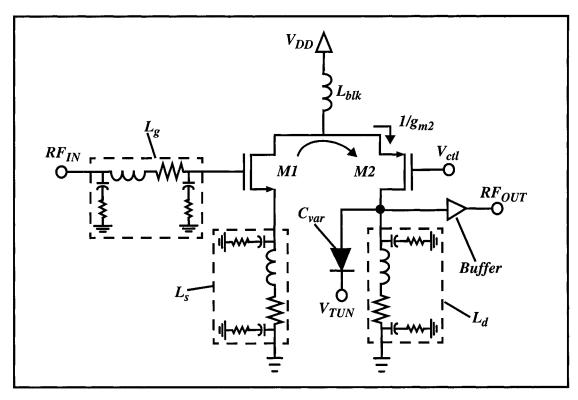

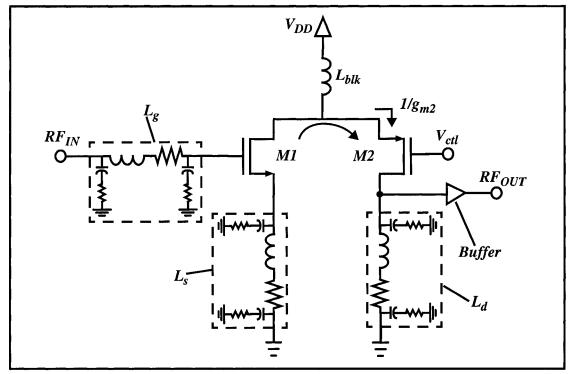

| Figure 4.2   | Schematic of the gain and frequency tunable sub-1 V CMOS LNA                                                         |          |

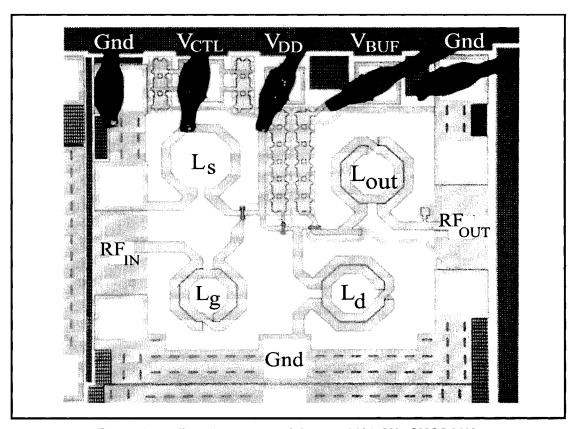

| Figure 4.3   | Microphotograph of the tunable sub-1 V 5.8 GHz CMOS LNA                                                              |          |

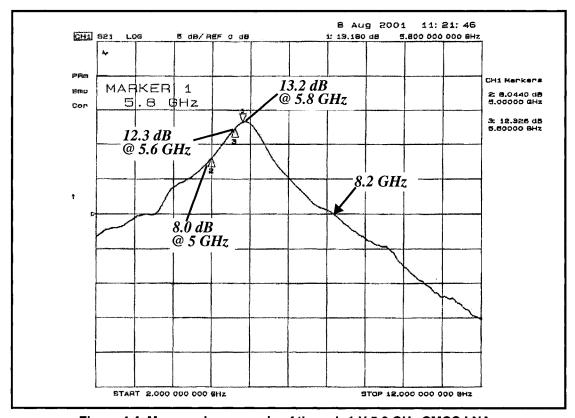

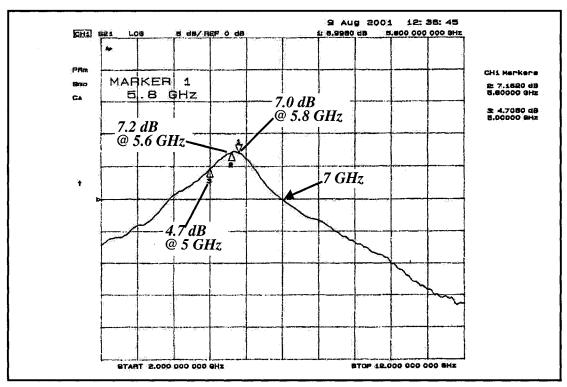

| Figure 4.4   | Measured power gain of the sub-1 V 5.8 GHz CMOS LNA                                                                  |          |

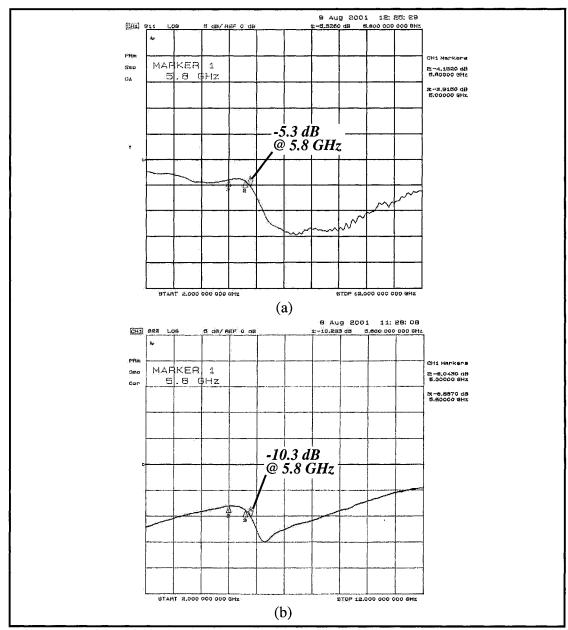

| Figure 4.5   | Measured (a) input and (b) output reflection coefficients of the tunable                                             |          |

| -            | sub-1 V 5.8 GHz CMOS LNA.                                                                                            | 82       |

| Figure 4.6   | Measured power gain with a supply voltage of 0.7 V.                                                                  |          |

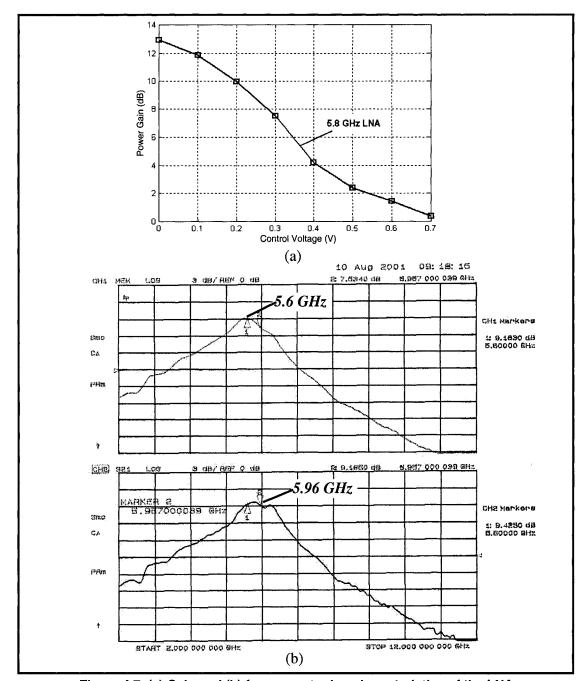

| Figure 4.7   | (a) Gain and (b) frequency tuning characteristics of the LNA                                                         |          |

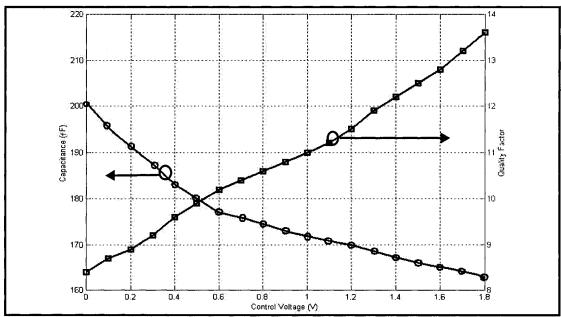

| Figure 4.8  | Capacitance tuning characteristics and quality factor of the varactor                        | 85 |

|-------------|----------------------------------------------------------------------------------------------|----|

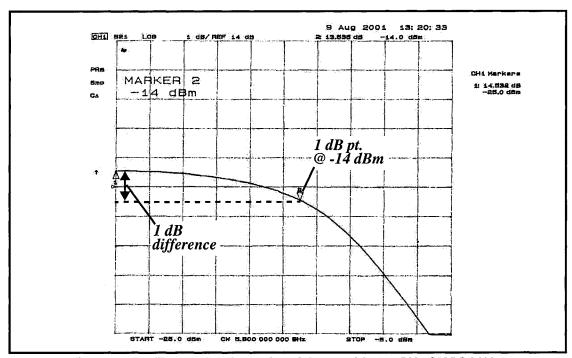

| Figure 4.9  | 1-dB compression point of the tunable 5.8 GHz CMOS LNA                                       | 86 |

| Figure 4.10 | Schematic of the gain controllable sub-1 V CMOS LNA                                          | 87 |

| Figure 4.11 | Microphotograph of the sub-1 V 9 GHz CMOS LNA                                                | 88 |

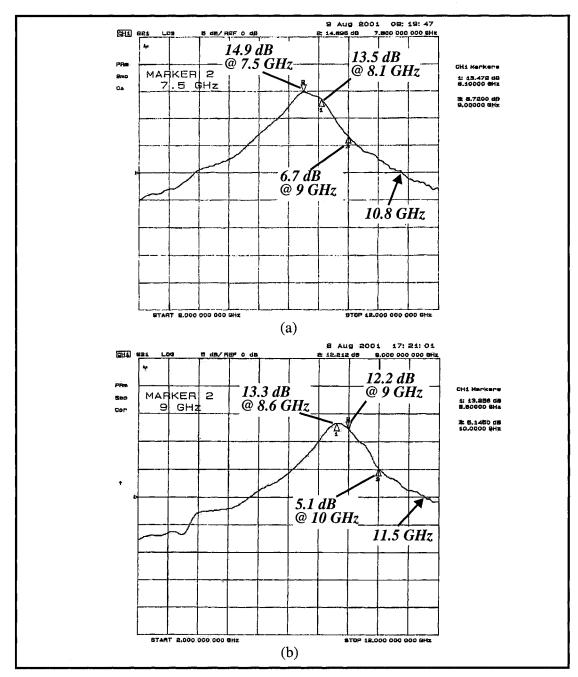

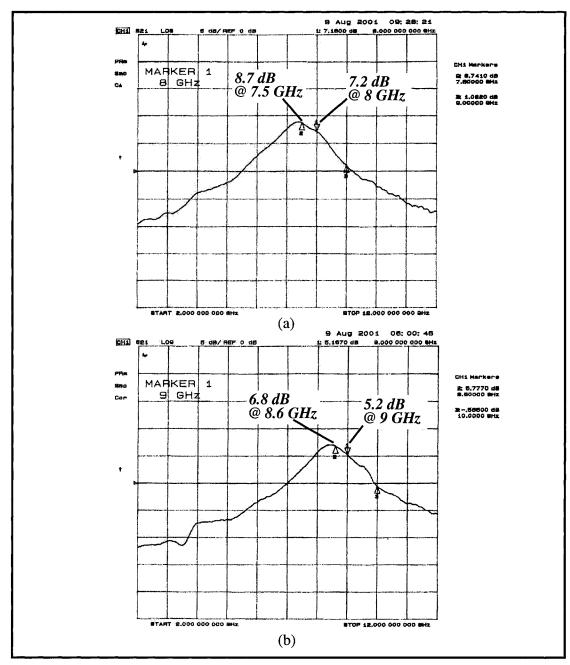

| Figure 4.12 | Measured power gain of the (a) 8 GHz and (b) 9 GHz CMOS LNA's                                | 89 |

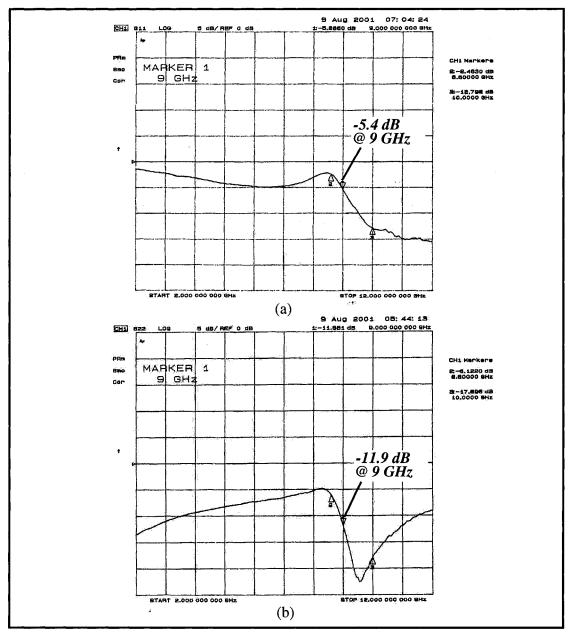

| Figure 4.13 | Measured (a) input and (b) output reflection coefficients of the sub-1 V 9 GHz CMOS LNA      |    |

| Figure 4.14 | Measured power gain of the (a) 8 GHz and (b) 9 GHz CMOS LNA's with a supply voltage of 0.7 V | 91 |

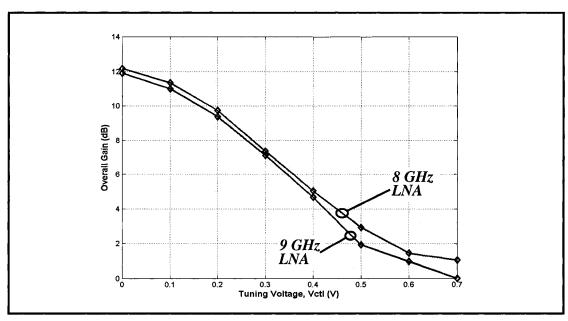

| Figure 4.15 | Gain tuning characteristics of the 8 GHz and 9 GHz LNA's.                                    | 92 |

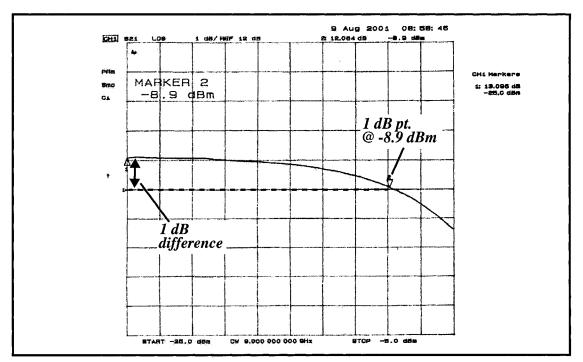

| Figure 4.16 | 1-dB compression point of the 9 GHz CMOS LNA                                                 | 93 |

|             |                                                                                              |    |

# **List of Tables**

| Table 1.1 | RF performances and process issues of various technologies    | 3  |

|-----------|---------------------------------------------------------------|----|

| Table 1.2 | Examples of high performance LNA's                            | 8  |

| Table 1.3 | State-of-the-Art CMOS LNA's in the literature                 | 9  |

| Table 2.1 | Performance summary of the 1 V cascode CMOS LNA [47]          | 38 |

| Table 2.2 | Performance summary of the 1 V LC-coupled bipolar LNA [35]    | 40 |

| Table 3.1 | Integrated inductor performance trends.                       | 56 |

| Table 3.2 | Summary of the MUMPs process parameters                       | 62 |

| Table 4.1 | Performance summary and comparison to other low-voltage LNA's |    |

|           | operating above 5 GHz                                         | 86 |

| Table 4.2 | Performance summary of the two CMOS LNA's, and comparison to  |    |

|           | [34]                                                          | 93 |

| Table 5.1 | LNA performance summary in this work.                         | 95 |

|           |                                                               |    |

## **Chapter 1 - Introduction**

Wireless technology came to existence when Guglielmo Marconi successfully demonstrated a radio signal transmission across the Atlantic Ocean in 1901. In later years, the invention of the transistor, the development of Shannon's information theory, and the concept of cellular systems - all developed by the bright minds at Bell Laboratories, had a big impact towards the evolution of modern mobile communications in the field of radio engineering.

Historically, radio frequency (RF) designs were thought to be incompatible with integrated circuit (IC) technology, because they rely heavily on tuned circuits and discrete filters, which are costly and bulky in nature. As a result, not much immediate development effort had been conducted in industry. As mobile telephony became popular in the 1990's, it was evident that there was a need to develop complex wireless transceivers to cope with the explosive growth in the number of mobile subscriber and base station infrastructure. Furthermore, the hardware had to be small in physical dimensions and to consume as little power as possible at minimal cost in order to remain competitive. These constraints revolutionized the research focus in radio architectures and analog circuit designs (e.g. [1] - [6]).

Nowadays, driven by an insatiable commercial demand for lower cost and higher bandwidth with enhanced digital functionality in RF transceivers, RF designs are moving towards high integration, low power, and low cost, while operating at higher frequencies (i.e. in the GHz range). A technology which can maintain a balance among all of these

Figure 1.1 The conceptual block diagram of a typical RF transceiver.

factors will become the dominant technology choice for future wireless applications.

### 1.1 - Technology Choices in RF Designs

Portable RF communications devices are a fast growing market segment. Currently, the majority of RF transceivers are implemented as multi-chip modules (*MCM*), based on multiple technologies. A conceptual block diagram of a typical RF transceiver is shown in Fig. 1.1. Baseband and mixed-signal components (e.g. *D/A*, *A/D* and *DSP*) are predominantly implemented in Complementary Metal-Oxide Semiconductor (*CMOS*) technologies. The Low Noise Amplifier (*LNA*), mixer, and Power Amplifier (*PA*) are typically implemented in III - V compounded semiconductors, such as Gallium Arsenide (*GaAs*) and Indium Phosphide (*InP*). The Phase-Locked Loop (*PLL*) and Voltage-Controlled Oscillator (*VCO*) are usually implemented in Silicon (*Si*) and Silicon Germanium (*SiGe*) bipolar technologies. Passive filters and resonant tanks are realized as discrete passive components.

There are several limitations to this classical implementation, which include large size,

high weight and integration cost. Besides, interconnections between sub-systems introduce parasitics, which can deteriorate the overall RF performance of a transceiver. Due to the lack of a single technology which can support a commercially viable single-chip RF transceiver with adequate performance, the MCM approach remains the optimum one. As technology advances and matures, the level of integration of RF transceiver blocks is steadily rising, especially in the 1-6 GHz frequency range, where consumer-class wireless electronics dominate.

Substantial research efforts have been invested to explore the advantages and disadvantages of different competing technologies, mainly in terms of their noise, power efficiency, and linearity performances (e.g. [7], [8]). The RF performances and process issues in various existing technologies are summarized in Table 1.1.

It is evident that III - V compounds (e.g. GaAs and InP) dominate in all areas for wireless applications except for cost and integrability. Their intrinsic superior noise performance and higher speed over other technologies (e.g. Si BJT and CMOS) are mainly due to their improved electron mobilities (i.e. use of majority carriers) and saturated drift velocities. The use of low resistive metal gate structures, as opposed to polysilicon gates in CMOS, enhances their noise performance. Furthermore, the high resistivity nature of the substrate enables the realization of high quality monolithic

| Technology             | GaAs PHEMT<br>[9]   | SiGe HBT<br>[10]    | Si BJT<br>[10] | Si CMOS<br>[11] | SOI CMOS<br>[12] |

|------------------------|---------------------|---------------------|----------------|-----------------|------------------|

| f <sub>T</sub> (GHz)   | 225                 | 76                  | 100            | 70              | > 100            |

| f <sub>max</sub> (GHz) | > 200               | 180                 | 101            | 150             | 135              |

| NF                     | Good<br>(100 GHz)   | Fair<br>(20 GHz)    | Good           | Fair (1 GHz)    | Fair             |

| Integration            | Fair                | Fair                | Fair           | Excellent       | Good             |

| Passives               | Good                | Fair                | Fair           | Poor            | Excellent        |

| Reliability            | Good                | Fair                | Very good      | Excellent       | Good             |

| Availability           | Fair<br>(expensive) | Fair<br>(expensive) | Very good      | Excellent       | Very good        |

Table 1.1 - RF performances and process issues of various technologies.

passive devices.

Among the III - V compounds, the High Electron Mobility Transistors (*HEMT's*) have the best overall performance. However, they are more useful in the microwave and millimeter wave frequency ranges, rather than in the 1-6 GHz which is targeted for low cost commercial telecommunication applications. The main reason is that in microwave and millimeter wave applications, device performance is the dominant factor rather than the production cost of each unit. The use of HEMT in these applications, mainly where high performance is required, such as for satellite transceivers, are not directly intended for the consumer market, but rather to niche market segments. In many cases, even a few tenths of a decibel improvement in noise figure is significant for specific wireless applications, especially in a base station or satellite receiver, because it translates directly into reductions in the transmit power requirements.

Despite the excellent RF performances of III-V compounds (e.g. GaAs), the incapability of integrating multiple functionalities on a single substrate (e.g. RF and digital) is one of the biggest drawbacks, especially when compared to other technologies with higher level of integration capability and with improved RF performances, such as Silicon-on-Insulator (SOI) CMOS and SiGe Heterojunction Bipolar Transistors (HBT's). Furthermore, higher processing costs, smaller wafer sizes, and moderate process reliability are additional shortcomings of III-V compounds, which prevent them from spreading to logic and mixed-signal circuitries.

Silicon BJT's are mainly used for implementing signal generation blocks (e.g VCO's) and mixing stages in a transceiver, due to their superior 1/f noise performance. Performances of BJT's have been improved by the advent of SiGe HBT's, which emerge as a competitive candidate for wireless applications. Its performance is very comparable to III - V compounds, with inherent advantages in terms of low production cost, good manufacturing volumes, and good reliability of bulk silicon. Successful implementations of integrated RF building blocks, operating at the 5 GHz frequency band, in SiGe HBT's have been demonstrated [13], [14]. Despite its great promises in the RF arena, the lack of complementary devices in SiGe HBT's is one of its biggest limitations, making it difficult to integrate digital circuitries onto the same substrate.

Driven by increasing demand on digital functionalities at a reduced cost for wireless transceivers, CMOS and Bipolar-CMOS (*BiCMOS*) are becoming the popular choices of technologies for consumer electronics. BiCMOS technology has been viewed for a long time as a suitable compromise between RF and digital baseband circuitries, operating at 1-3 GHz [15], [16]. However, this comes at a higher technology cost, as well with a loss of performance in the digital components, since the minimum feature size of MOS transistors in a BiCMOS process is always larger than that of a delicated state-of-the-art CMOS process.

As the minimum feature size of CMOS devices decreases, the RF performances (e.g.  $f_T$ ) continue to improve to the point where they become comparable to those of GaAs and SiGe processes. Deep sub-micron CMOS devices with  $f_T$ 's exceeding 100 GHz and minimum noise figures less that 0.5 dB at 2 GHz have been realized in [17]. Rapid technology advances, coupled with the overwhelming dominance of CMOS in the digital arena, is making Si CMOS the best candidate for a single-chip solution for modern RF transceivers. Although the RF performances of CMOS will probably never match those of GaAs or SiGe, its integration potential, combined with cost advantages and good process maturity, provide a strong driving force for its adoption over other technologies.

### 1.2 - Motivation

While the low cost and low power advantages of the CMOS technology are the dominant driving forces in the digital sector, the analog front-ends become the bottle necks in today's RF transceiver designs. Mainstream CMOS technologies are optimized for digital applications. The use of these CMOS technologies to implement high performance analog front-ends is highly desirable and beneficial, since higher integration with digital components results in significant space, cost, and power reductions. As a result, serious attention and research efforts, both from industry and from university research groups, have investigated the possibilities of single-chip CMOS RF transceiver solutions for future wireless applications [18] - [21].

Apart from the increasing acceptance of CMOS RFIC's in the wireless domain, there is always a need for efficient networks at high data rates. Motivated by the insatiable

demand for larger bandwidth, wireless standards are constantly evolving towards higher carrier frequencies, and at the same time driving the research focus of CMOS RFIC's into the GHz range [22], [24]. Over the last few years, wireless applications were developed for the 900 MHz and 1.8 GHz bands, followed by the current 2.4 GHz Bluetooth applications, then the 5-6 GHz bands for wireless LAN systems (e.g. IEEE 802.11a and HIPERLAN). Future technological advances and demand anticipate the use of CMOS technologies, operating at higher frequency bands (e.g. 5-10 GHz), for next-generation wireless communications applications.

The intense deployment of CMOS technologies for consumer wireless products has lead to the reduction in supply voltage standards for integrated circuits, mainly attributed to the continuous device scaling. This trend has motivated the evolution of low-voltage (e.g. < 1 V) RFIC design topologies [25], [26].

The Low Noise Amplifier (*LNA*) is a critical building block in communications systems. It is usually the first active circuitry in the signal path in a receiver, which is supposed to amplify the weak RF signals received, while introducing as little noise as possible. The performance of the LNA affects the overall performance of a receiver, such as its sensitivity.

The increased demand for single-chip CMOS RFIC's solutions, as well as technological advances in CMOS processes, have recently attracted substantial research focuses of CMOS LNA's. Although the CMOS technology is a promising cost effective choice, it represents several limitations and challenges in implementing monolithic CMOS LNA's. One dominant shortcoming is the inherently low quality factors of passive components, mainly the integrated inductors. The qualities of integrated inductors play an important role in the performance of an LNA. There are many factors that contribute to losses in integrated inductors and degradation in quality, which make them very hard to model, especially at GHz frequencies. Furthermore, the lack of general and systematic design guidelines for integrated inductors, and RF layout techniques in general, has increased the level of difficulties and uncertainties in designing CMOS LNA's. As a result, a typical successful CMOS LNA implementation usually requires a minimum of two design runs. The results from the first design cycle are used to fine tune

the design (e.g. center frequency) for the second run. This is highly inefficient and costly, especially in nowadays' competitive market with short turn-around time.

In this thesis, several successful implementations of high frequency low-voltage integrated CMOS LNA's are presented, demonstrating their performance and proving the feasibility of using standard CMOS technologies for the current, as well as for the future, low cost wireless telecommunication applications. Systematic design guidelines for optimizing integrated passive devices and RF layout techniques are also presented, in order to minimize design uncertainties in CMOS LNA's. The effectiveness of this design methodology has been supported by good measurement results of three successful LNA implementations.

### 1.3 - State-of-the-Art in LNA Designs

The Low Noise Amplifier (*LNA*) is an essential building block in a transceiver, which dictates the overall performance of the system. CMOS LNA design has become an interesting research topic, both in industry and in academia. In this section, some examples of LNA's, both commercially available and in academic research, are presented. Recently reported state-of-the-art CMOS LNA's in the literature are summarized and compared. The frequency range of the presented examples is limited to 1-12 GHz, since this is the frequency of interest for current and future portable and consumer products.

High performance LNA's are often implemented in various technologies other than CMOS, typically in III - V compounds. The main reason is their superior noise performance and high frequency behaviour when compared to CMOS technologies. As a result, almost all available commercial LNA's are implemented in technologies such as HEMT, MESFET, and HBT. Table 1.2 summarizes some existing high performance LNA's, both in industry [27], [28] and in academia [29], [30]. Note that all of the LNA designs exhibit excellent noise figures of less than 1.5 dB at a wide frequency range, especially when considering the commercial LNA's (e.g. [27], [28]), where all the package parasitics are taken into account. Typical reported noise figures are 1-2 dB lower

Figure 1.2 Simplified schematic of the proposed gain controlled LNA [30].

than the CMOS implementations, at similar frequencies.

One special feature of the proposed design in [30] is its gain controlability. Typical LNA's are designed for a fixed gain at a specific frequency with as low noise figure as possible. In this design, a wide gain control range (i.e -25 dB to 15 dB) was achieved without degrading the overall noise performance. This gain controlability is a desirable

|                                                      | [27]                                    | [28]                                    | [29]                    | [30]                                                    |

|------------------------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------|---------------------------------------------------------|

| Technology                                           | PHEMT                                   | MESFET                                  | PHEMT                   | НВТ                                                     |

| Center Frequency, f <sub>o</sub>                     | 9-12 GHz                                | 5.4-5.9 GHz                             | 5.4 GHz                 | 2 GHz                                                   |

| Power Gain, S <sub>21</sub>                          | 22 dB                                   | 12 dB                                   | 16 dB                   | 15 dB                                                   |

| Noise Figure, NF                                     | 1.3 dB                                  | 1.0 dB                                  | 0.76 dB                 | 1.4 dB                                                  |

| 1-dB Compression<br>Point (input), P <sub>1-dB</sub> | -12 dBm                                 | -17 dBm                                 | •                       | -6.6 dBm                                                |

| Voltage Supply, V <sub>dd</sub>                      | 3 V                                     | 15 V                                    | 3 V                     | 3 V                                                     |

| Power Consumption                                    | 105 mW                                  | 900 mW                                  | -                       | 36 mW                                                   |

| Others                                               | i) Fully<br>integrated and<br>packaged. | i) Fully<br>integrated and<br>packaged. | i) On-chip<br>matching. | i) -40 dB gain<br>control.<br>ii) Off-chip<br>matching. |

Table 1.2 - Examples of high performance LNA's.

function in today's wireless applications since it can help enhancing the linearity of the system, especially the input third order intercept point  $(IIP_3)$ , by decreasing the gain at a high input power level. The simplified schematic of the variable gain LNA is shown in Fig. 1.2. The basic idea behind this design is as follows: When the gain control voltage  $(V_{GC})$  of transistor Q2 increases, the output impedance of the diode-loaded emitter follower decreases. The input RF signal is thus shorted to ground through this impedance, hence the overall gain of the LNA decreases.

One common drawback of all presented examples above is the need for a relatively high supply voltage (i.e. a minimum of 3 V) with high power consumption (36-900 mW), which goes against the current low-voltage and low-power trends. Furthermore, high production cost is another limiting factor. The unit cost of a typical high performance LNA (e.g. [27], [28]) is around \$USD 1000 - 1500, whereas a CMOS implementation costs less than \$USD 10. Such big cost difference has driven the industry to move towards CMOS RF implementations for consumer wireless products, while expensive high performance LNA's are only used for satellite applications at microwave

|                                                      | [31]                     | [32]                                               | [33]                                               | [34]                                                         |

|------------------------------------------------------|--------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------|

| Technology                                           | CMOS<br>0.6 μm           | CMOS<br>0.25 μm                                    | CMOS<br>0.25 μm                                    | CMOS<br>0.25 μm                                              |

| Center Frequency, fo                                 | 1.5 GHz                  | 5.2 GHz                                            | 1.2 GHz                                            | 7 GHz                                                        |

| Power Gain, S <sub>21</sub>                          | 22 dB                    | 16 dB                                              | 20 dB                                              | 6.2 dB                                                       |

| Noise Figure, NF                                     | 3.5 dB                   | 2.5 dB                                             | 0.8 dB                                             | 3.3 dB                                                       |

| 1-dB Compression<br>Point (input), P <sub>1-dB</sub> | -19.3 dBm                | -11.7 dBm                                          | -24 dBm                                            | -1.6 dBm                                                     |

| Voltage Supply, V <sub>dd</sub>                      | 1.5 V                    | 3 V                                                | 1.5 V                                              | 2 V                                                          |

| Power Consumption                                    | 30 mW                    | 48 mW                                              | 9 mW                                               | 13.8 mW                                                      |

| Others                                               | i) Off-chip<br>matching. | i) On-chip<br>matching.<br>ii) Thick top<br>metal. | i) Bondwire<br>matching.<br>ii) ESD<br>protection. | i) On-chip<br>matching.<br>ii) Special layout<br>techniques. |

Table 1.3 - State-of-the-Art CMOS LNA's in the literature.

Figure 1.3 Complete schematic of the LNA in [31], including off-chip elements.

frequencies, where a stringent noise performance is required.

As the main focus of this thesis is on CMOS Low Noise Amplifiers, a summary of state-of-the-art CMOS LNA's in the literature is provided in Table 1.3. The work presented in [31] is considered to be a classic. It was the first successful implementation with detailed analysis of CMOS LNA's operating at GHz range. The proposed design was based on a conventional cascode topology with source inductive degeneration, as shown in Fig. 1.3. Off-chip high quality passive components were used for impedance matching. It was also shown that this architecture offers the possibility of achieving the best noise performance over any other architecture. The contribution of that work was significant, as most of the later CMOS LNA implementations (e.g. [22], [32] - [34], [47]) were based on this structure. In [32], the design targeted the 5 GHz band utilizing a conventional cascode structure with on-chip impedance matching. A thick top metal layer was available for high quality on-chip inductors, hence an overall low noise figure was achieved. A relatively large power consumption with the use of high supply voltage was the main drawback of that work. In [33], an excellent noise figure of less than 1 dB was achieved at low GHz frequency (i.e. 1.2 GHz), with the additive feature of ESD protection. Bonding wires were used for impedance matching. Finally, in an attempt to

push the frequency limit, a CMOS LNA operating at 7 GHz has recently been demonstrated [34]. Special layout techniques of transistors were employed in the design to enhance the RF performance. Unfortunately, the low power gain of 6.9 dB has put the effectiveness of these layout techniques in question.

The main focus of this thesis is to use a standard commercial CMOS technology to implement low-voltage fully integrated LNA's, operating in the 5-10 GHz frequency range, for next-generation wireless applications. Systematic performance enhancement techniques are also presented.

### 1.4 - Thesis Outline

The thesis began with an overview on the current technology choices in RF applications, with a focus on LNA designs. Application examples and performance summaries of state-of-the-art LNA designs were presented. The challenges and the need for integrated CMOS LNA's operating in the 5-10 GHz frequency band, with a strong emphasis on low-voltage design topologies, were motivated.

In Chapter 2, basic theory and important parameters such as noise and distortion in RF designs are reviewed. Design equations and constraints on CMOS LNA's are then discussed in details. Different LNA topologies, which are suitable for low-voltage sub-1 V applications, are presented. Trade-offs, in terms of gain, linearity, and noise performances, in each architecture are addressed. Finally, a modified architecture, based on a well-known folded cascode topology, is proposed to be the choice in today's low-voltage designs with good performances in all aspects, when compared to other architectures. Gain tunability is suggested for the first time for this architecture.

In Chapter 3, a systematic design strategy for optimizing RF passive elements (e.g. inductors and capacitors) beyond 5 GHz is presented. Trade-offs between different design issues are addressed. In inductor designs, the conductor width (W), the number of turns (N), the conductor spacing (S), and the number of conductor layers (L), are the key design parameters. An approach to optimize the quality factors of the inductors at 5-10 GHz, while extending their self-resonant frequencies  $(f_{RES})$ , is addressed. For capacitor and varactor designs, the tuning ranges and the methods to reduce parasitic resistances are the

key design issues which needed to be optimized.

Apart from a discussion of the mainstream RF passive devices, an attempt is made to explore the possibility of using Micro-Electro Mechanical Systems (*MEMS*) in the RF arena. Several successful tunable capacitor implementations, which are suitable for current RF applications, are demonstrated by measurement results, along with a detailed discussion of design equations. Challenges and limitations of MEMS for future RF applications are addressed.

In Chapter 4, three successful CMOS LNA implementations are demonstrated and verified by measurement results. Guidelines for RF layout techniques towards successful LNA implementations are presented. The first LNA is operating at the 5-6 GHz frequency range with gain and frequency tunability, targeted for applications of wireless LAN in the US (IEEE 802.11a standard for the FCC unlicensed national information infrastructure, the U-NII band), and the European High Performance Radio LAN (HIPERLAN). In an attempt to push the frequency limit in CMOS RF technologies, the second and third LNA's are designed to operate at a much higher carrier frequency of 8 GHz and 9 GHz. Different inductor structures are used in these two designs. Both LNA's have the advantage of tunability in gain over any other popular LNA implementation (e.g. conventional cascode amplifier structures). All three LNA implementations are designed with a low supply voltage of 1 V and are still functional at a much lower supply voltage of 0.7 V. Finally, a summary of all three implementations, together with a comparison to other designs from the literature, is presented.

In Chapter 5, the thesis concludes with a summary of the work done and with the results obtained, ending up with suggestions for future work.

### 1.5 - Thesis Contributions

The following is a summary of the contributions of this thesis:

- 1. Provided a summary of some existing topologies which are suitable for low-voltage sub-1 V LNA applications. Demonstrated the validility of these topologies to operate beyond 5 GHz, by implementing several chips both in modern bipolar and CMOS technologies. More specifically, the following work was the result of this thesis:

- a) A successful chip implementation of a fully integrated 5.8 GHz bipolar LNA using the LC-coupled topology. It was the *first to demonstrate* a 5.8 GHz LNA running from a 1 V supply with a low power consumption of 6.6 mW in a 0.5 μm bipolar technology. This was published as [35]:

- 1- T. K. K. Tsang and M. N. El-Gamal, "A Fully Integrated 1 V 5.8 GHz Bipolar LNA", 2001 IEEE International Symposium on Circuits and Systems (ISCAS 01), vol. 2, pp. 843-845, May 2001.

- b) A chip implementation of an integrated 1 V conventional cascode LNA in a 0.18 μm CMOS technology. Due to some fatal layout errors, a resonant frequency of 7.6 GHz was measured, which was different from the designed value of 5.8 GHz. Nonetheless, the measurements have shown the usability of the cascode topology with a 1 V power supply, operating beyond the 5 GHz band.

- c) Based on the well-known folded cascode topology with some modifications, three successful chip designs were fabricated in a 0.18 µm CMOS technology. Gain tunability of this modified structure was suggested for the first time. The first prototype was targeted at the 5.8 GHz band, while the other two prototypes were the first successful demonstrations for sub-micron CMOS LNA's operating at 8-9 GHz to be reported in the literature. The results were published in [36], [37]:

- 2- T. K. K. Tsang and M. N. El-Gamal, "Gain and Frequency Controllable Sub-1 V 5.8 GHz CMOS LNA", 2002 IEEE International Symposium on Circuits and Systems (ISCAS 02), accepted May 2002.

- 3- T. K. K. Tsang and M. N. El-Gamal, "Gain Controllable Very Low Voltage (<1 V) 8-9 GHz Integrated CMOS LNA", 2002 Radio Frequency Integrated Circuits (RFIC) Symposium, accepted June 2002.

- 2. Provided a design methodology, which is strongly supported by excellent measurement results, on designing CMOS LNA's beyond 5 GHz. Detailed design guidelines for optimizing RF passive devices, and essential layout techniques to enhance the LNA performance are presented. This provides a valuable input for CMOS RF designers to avoid the "trials-and-errors" design approach.

- 3. An attempt to implement RF passive devices in MEMS, particularly in a low cost and commercially available Multi-User MEMS Process (MUMPs). Several variable capacitor structures were implemented, with one newly proposed structure which has an infinite tuning range in theory. Preliminary measurement results have shown that the devices are suitable for up to 4 GHz RF applications.

# Chapter 2 - CMOS LNA Basics and Circuit Topologies

The first active circuitry of a receiver is usually a Low Noise Amplifier (*LNA*), whose main function is to provide adequate gain to suppress the additive noise of subsequent stages (e.g. mixer and image rejection filter). The noise characteristics of the LNA limits the sensitivity of the entire receiver. Apart from providing enough gain while adding as little noise as possible, an LNA with low distortion is highly desirable.

In this chapter, some basic parameters such as noise and distortion in RF circuits are addressed. This is then followed by a detailed derivation of design equations and constraints on CMOS LNA's. Different LNA topologies, which are suitable for low-voltage (i.e. < 1 V) applications, are presented and their advantages and limitations are discussed. Finally, this chapter concludes with the presentation of a detailed design methodology for the chosen low-voltage LNA topology.

### 2.1 - Noise

#### 2.1.1 - Thermal Noise

Thermal noise is caused by the thermal agitation of charge carriers in a conductor, which results in a random fluctuation in current and gives rise to a random voltage in a load. The available noise power  $(P_{NA})$  is given by:

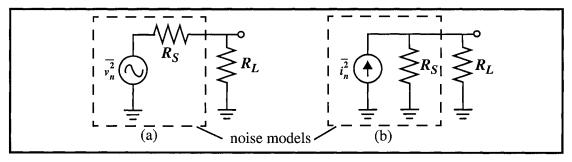

Figure 2.1 (a) Noise voltage model and (b) noise current model for computing the thermal noise of a resistor.

$$P_{NA} = kT\Delta f, (2.1)$$

where  $k = 1.38 \times 10^{-23}$  J/K is the Boltzman's constant, T is the absolute temperature, and  $\Delta f$  is the noise bandwidth. For a noise bandwidth of 1 Hz at room temperature (i.e. 298 °K), the available noise power is about -174 dBm, which is often referred to the 'noise floor' of the system.

The available thermal noise power of a resistor is defined as the power delivered by a noisy source resistor ( $R_S$ ) to a noiseless and matched load resistor ( $R_L$ ). The noisy resistor can be modeled in two ways [38]: i) A noisy voltage source in series with a noiseless resistor, or ii) a noisy current source in parallel with a noiseless resistor. Both resistor thermal noise models, which are used to compute the thermal noise power, are shown in Fig. 2.1.

From the noise voltage model shown in Fig. 2.1(a), the power delivered by the source resistor to a load resistor of equal value (i.e.  $R_S = R_L = R$ ) is by definition the available noise power:

$$P_{NA} = kT\Delta f = \overline{v_n^2} \cdot \frac{R_L}{(R_S + R_L)^2} = \frac{\overline{v_n^2}}{4R},$$

(2.2)

and

$$\overline{v_n^2} = 4kTR\Delta f, \tag{2.3}$$

where  $\overline{v_n^2}$  is the root-mean-square (rms) noise voltage generated by the resistor R over a

bandwidth of  $\Delta f$  at a given temperature.

Similarly, the rms noise current can be derived from the noise current model shown in Fig. 2.1(b), and is equal to:

$$\overline{i_n^2} = \frac{4kT\Delta f}{R} = 4kTG\Delta f. \tag{2.4}$$

From the above equations, it can be seen that an approach to reduce the thermal noise of a given resistance is either to keep the temperature as low as possible or to limit the noise bandwidth to the minimum useful value.

### **2.1.2** - Shot Noise

Shot noise occurs due to the direct flow of current in diodes and transistors. It is due to the random drifting of charge carriers across the PN-junction, which results in current fluctuation (i.e. shot noise) around the average current value. The shot noise current is expressed as:

$$i_{sn}^{2} = 2qI_{D}\Delta f, \tag{2.5}$$

where  $\overline{i_{sn}^2}$  is the rms noise current,  $q = 1.602 \times 10^{-19} \, \text{C}$  is the electron charge,  $I_D$  is the average DC current, and  $\Delta f$  is the noise bandwidth.

From equation 2.5, the additive shot noise can be reduced by minimizing the bias current of an active device.

### 2.1.3 - Flicker Noise (1/f Noise)

Flicker noise is due to random trapping of charge carriers associated with contaminations and defects in crystal lattices, which gives rise to a noise power dominated at low frequencies.

Similar to shot noise, flicker noise  $\overline{i_{fn}^2}$  occurs in the presence of direct current flow, and is given by:

$$\overline{i_{fn}^2} = K \frac{I^a}{f^b} \Delta f, \tag{2.6}$$

where K is a device-specific empirical parameter, I is the average DC current,  $\Delta f$  is again the noise bandwidth, a is a constant ranging from 0.5 to 2, and b is another constant of about unity.

In LNA applications, RF signals are amplified in a narrowband fashion with a typical bandwidth of few hundreds of MHz around the center frequency. Hence, flicker noise does not play an important role in LNA applications, because it only dominates at low frequencies. However, it becomes an important noise source when considering a complete transceiver where frequency translation is performed. On the receiver side, excessive flicker noise will corrupt the downconverted RF signals at baseband. On the transmitter side, flicker noise can be upconverted to the RF band where it interferes with the desired RF signals. Nonetheless, flicker noise is a bigger concern in oscillator designs, for example, compared to the main focus of this work.

### 2.1.4 - Noise Sources in MOSFET's

There are two dominant noise sources in MOS transistors at RF: Namely, the intrinsic channel thermal noise, and the geometry related gate resistance noise.

(a) Channel thermal noise - The inversion layer joining the source and drain regions is modulated by the gate-source voltage and is resistive in nature, hence it exhibits thermal noise. It can be shown that this noise source can be modeled by an rms noise current source:

$$\overline{i_{ch}^2} = 4kT\gamma g_{d0}\Delta f, \qquad (2.7)$$

where  $g_{d0}$  is the zero-bias drain conductance of the transistor, and  $\gamma$  is a bias and layout dependent parameter, found to be in the range of  $\frac{2}{3} < \gamma < 1$  for long channel devices. For short channel devices, measurements have shown that  $\gamma$  can be as high as two to three, depending on the bias conditions [39]. This excess noise may be attributed to the presence of hot electrons in the channel, where the high electric fields in sub-micron

MOS devices cause the electron temperature to exceed the lattice temperature.

(b) Gate resistance noise - The additive thermal noise to the gate due to the distributed gate resistance. It can be modeled by an rms noise voltage source in series with a resistance at the gate. The amount of additive gate resistance noise is layout-dependent. By interdigitating the device, the contribution of this noise source can be significantly reduced. The distributed gate resistance is given by [40]:

$$R_g = \frac{R_{sh}W}{3n^2L},\tag{2.8}$$

where  $R_{sh}$  is the sheet resistance of the polysilicon, W is the total gate width of the device, L is the gate length, and n is the number of gate fingers used. The factor 1/3 arises from the distributed analysis of the gate resistance and is assumed that only one side of each gate finger is connected together. By connecting both ends, this factor reduces to 1/12. Nonetheless, by doing a careful layout with multiple fingers,  $R_g$  can be minimized and rendered insignificant.

### 2.1.5 - Noise Figure

A useful measure of the noise performance of a system is the noise factor (F), which is defined as the degradation of the signal-to-noise ratio (SNR) due to the device under test (DUT) and is given by:

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{S_{in}/N_{in}}{S_{out}/N_{out}},$$

(2.9)

where  $S_{in}$  and  $N_{in}$  are the signal and noise power at the input of the *DUT*, respectively, while  $S_{out}$  and  $N_{out}$  are the output signal and noise power, respectively.

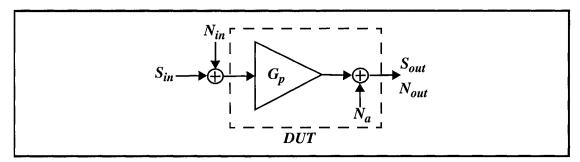

Consider a DUT having a power gain  $G_p$ , the input-output relationship can be expressed as (Fig. 2.2):

$$S_{out} = G_p \cdot S_{in}, \tag{2.10}$$

and

Figure 2.2 Noise equivalent block diagram of a system.

$$N_{out} = G_p \cdot N_{in} + N_a, \tag{2.11}$$

where  $N_a$  is the induced available noise power of the *DUT* to the subsequent stage. Equation 2.9 can then be rewritten as:

$$F = \frac{S_{in}/N_{in}}{(G_p \cdot S_{in})/(G_p \cdot N_{in} + N_a)} = \frac{G_p N_{in} + N_a}{G_p N_{in}} = 1 + \frac{N_a}{G_p N_{in}}. \quad (2.12)$$

Thus, the noise factor can be viewed as the ratio of the total output noise to the part of the output noise which is due to the input source:

$$F = \frac{total\ output\ noise}{output\ noise\ due\ to\ input\ source},\tag{2.13}$$

or alternatively,

$$F = 1 + \frac{output \ noise \ due \ to \ injected \ noise}{output \ noise \ due \ to \ input \ source}.$$

(2.14)

In RF designs, it is common to express the noise performance in terms of the noise figure (NF), which is merely the noise factor F expressed in dB:

$$NF = 10\log_{10}F = SNR_{in}(dB) - SNR_{out}(dB)$$

. (2.15)

In an ideal case, where the system is noiseless, this results in F = 1 and NF = 0 dB, which never occurs in real life.

Figure 2.3 Cascaded noisy stages.

### 2.1.6 - Noise Temperature

In addition to the noise figure, another figure of merit used to determine the noise performance of a system is the noise temperature. The noise temperature  $(T_N)$  is defined as the increase in the required temperature of the source resistance for it to account for all of the output noise at the reference temperature  $T_{ref}$  (i.e. 290 K). It is related to the noise factor as follows:

$$F = 1 + \frac{T_N}{T_{ref}} \Rightarrow T_N = T_{ref} \cdot (F - 1). \tag{2.16}$$

The noise temperature is particularly useful for systems with a noise factor quite close to unity, since it offers a higher resolution on noise performance compared to the noise figure metric.

### 2.1.7 - Cascade of Noise Figures

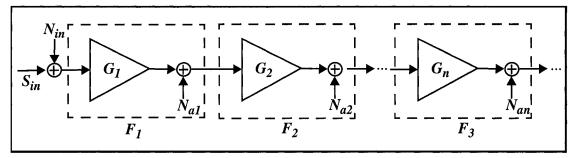

Considering a cascade of n matched noisy stages with power gains  $G_k$  and noise factors  $F_k$  as shown in Fig. 2.3, the equivalent total injected noise contribution of k stages relative to the input of the system can be expressed as:

$$F = \frac{N_{in} + \sum_{k=1}^{n} N_{ai, k}}{N_{in}} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_n}.$$

(2.17)

The above equation is called the Friis equation [41]. It expresses the overall noise

figure in terms of the noise figure of each stage. It also indicates that the noise contributed by each stage decreases as the gain of the preceding stage increases, implying that the first stage in a cascade system is critical. In fact, the first stage, usually a low noise amplifier, has the most pronounced effect on the noise performance. Hence, it is highly desirable to have a low noise figure and a high gain in an LNA in order to minimize the overall noise figure of the system.

### 2.2 - Distortion

### 2.2.1 - Non-linearity

The behaviour of many analog and RF circuits can be approximated by a linear model represented in the form of a small signal response. As the input signal power increases to a level beyond the small signal approximation, non-linear effects become prominent. In circuits, these non-linearities are mainly due to the characteristics of the transistors.

To account for the non-linear effects, consider a practical system with a transfer function:

$$y(t) \approx \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \dots,$$

(2.18)

where  $\alpha_l$  is the linear gain factor of the system and  $\alpha_n > l$ , for n > l, are the non-linear gain factors.

By applying a sinusoid at input  $x(t) = G\cos\omega t$  to a non-linear system, the output generally exhibits frequency components that are integer multiples of the input frequency and is given by [42]:

$$y(t) = \alpha_1 G \cos \omega t + \alpha_2 G^2 \cos^2 \omega t + \alpha_3 G^3 \cos^3 \omega t + \dots$$

(2.19)

$$= \alpha_1 G \cos \omega t + \frac{\alpha_2 G^2}{2} (1 + \cos 2\omega t) + \frac{\alpha_3 G^3}{4} (3\cos \omega t + \cos 3\omega t) + \dots$$

(2.20)

Figure 2.4 Graphical explanation of 1 dB compression point.

$$= \frac{\alpha_2 G^2}{2} + \left(\alpha_1 G + \frac{3\alpha_3 G^3}{4}\right) \cos \omega t + \frac{\alpha_2 G^2}{2} \cos 2\omega t + \frac{\alpha_3 G^3}{4} \cos 3\omega t + \dots (2.21)$$

It can be easily seen from equation 2.21 that the n th harmonic is approximately proportional to  $G^n$ , and that the even-order harmonics resulting from  $\alpha_j$ , for even j, will vanish for systems with symmetry (i.e. fully differential). In reality, finite accuracy in matching will corrupt the symmetry, hence yielding weak even order harmonics.

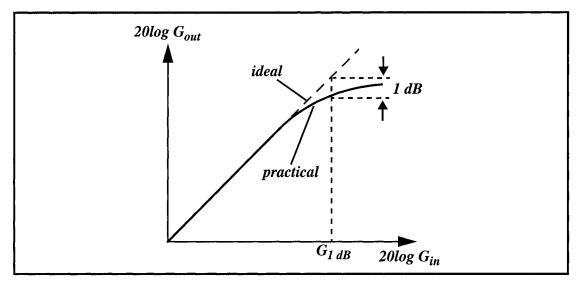

### 2.2.2 - Gain Compression

The small signal gain of a circuit is usually obtained with the assumption that the harmonics are negligible. In other words, from equation 2.21, it is assumed that  $\alpha_I G$  is much larger than all other terms. However, as the input signal amplitude increases beyond the linear range, the output begins to saturate. This effect is often quantified by the 1 dB compression point, which is defined as the input signal power that causes the small signal gain to drop by 1 dB from its nominal value, as shown in Fig. 2.4.

The 1 dB compression point is calculated as the difference between the practical gain,  $G_{practical} = \left(\alpha_1 G + \frac{3}{4}\alpha_3 G^3\right)$ , and the ideal gain,  $G_{ideal} = \alpha_1$ , being 1 dB and is expressed as:

Figure 2.5 (a) Intermodulation in a non-linear system. (b) Third-order intercept.

$$20\log_{10}\left|\alpha_{1}G + \frac{3}{4}\alpha_{3}G^{3}\right| = 20\log_{10}\left|\alpha_{1}\right| - 1dB, \tag{2.22}$$

resulting in:

$$G_{1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|} \quad (dB) \quad , \tag{2.23}$$

alternatively in dBm:

$$G_{1dB} = 0.36 + 10\log\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right| \quad (dBm) \quad .$$

(2.24)

### 2.2.3 - Intermodulation Distortion

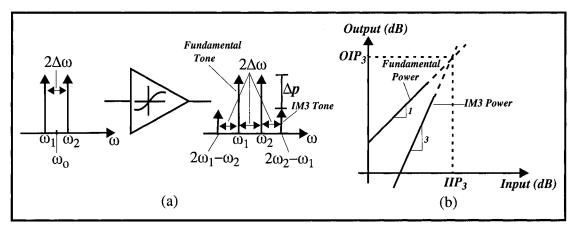

Another performance metric used to evaluate the distortion of a system is to measure how "multiplicative" the distortion is, by applying an input with multiple-tones and measuring the system response. A common measure used is the intermodulation distortion in a "two-tone" test, and is quantified by the input and output third-order intercepts,  $IIP_3$  and  $OIP_3$ , respectively.

When two adjacent tones, separated by a frequency of  $2\Delta\omega$ , are applied to the input of a non-linear system, the output generally exhibits some frequency components that are not direct harmonics of the input frequencies, called intermodulation (*IM*) products,

which are due to the mixing of the two input tones as shown in Fig. 2.5(a).

Consider the input signal  $x(t) = G\cos\omega_1 t + G\cos\omega_2 t$ , where  $\omega_1 = \omega_o - \Delta\omega$ , and  $\omega_2 = \omega_o + \Delta\omega$ , and  $\omega_o$  is the center frequency. The output spectrum, as given by equation 2.18, becomes:

$$y(t) = \alpha_1 (G\cos\omega_1 t + G\cos\omega_2 t) + \alpha_2 (G\cos\omega_1 t + G\cos\omega_2 t)^2 + \alpha_3 (G\cos\omega_1 t + G\cos\omega_2 t)^3 + \dots$$

(2.25)

By expanding equation 2.25, the third order *IM* products (*IM3*) can be obtained as:

$$\omega = 2\omega_{1} - \omega_{2}; \ \ y_{IM3} = \frac{3\alpha_{3}G^{3}}{4}\cos(2\omega_{1} - \omega_{2})t = \frac{3\alpha_{3}G^{3}}{4}\cos(\omega_{o} - 3\Delta\omega)t, (2.26)$$

$$\omega = 2\omega_2 - \omega_1; \ \ y_{IM3} = \frac{3\alpha_3 G^3}{4} \cos(2\omega_2 - \omega_1)t = \frac{3\alpha_3 G^3}{4} \cos(\omega_o + 3\Delta\omega)t. (2.27)$$

From equations 2.26 and 2.27, it can be easily seen that the third order IM products increase in proportion to  $G^3$ , whereas the fundamental tone increases linearly with G. On a logarithmic scale, the magnitude of the IM products grows at three times the rate at which the main tone increases. The  $IIP_3$  and  $OIP_3$  are defined as the point where the powers of the fundamental tones (i.e.  $\alpha_1 G$ ) equal the powers of the third order intermodulation products (i.e.  $\frac{3\alpha_3 G^3}{4}$ ), as shown in Fig. 2.5(b). Mathematically, it can be expressed as:

$$\alpha_1 II P_3 = \frac{3\alpha_3 (II P_3)^3}{4} {2.28}$$

Hence,

$$IIP_3 = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \quad (dB) \quad , \tag{2.29}$$

and alternatively, the  $IIP_3$  can be expressed in dBm and is given by:

Figure 2.6 Cascade of two non-linear stages.

$$IIP_3\Big|_{dBm} = \frac{\Delta P\Big|_{dB}}{2} + P_{in}\Big|_{dBm},\tag{2.30}$$

where  $P_{in}$  is the input power level in dBm, and  $\Delta P$  is the difference in the power level in dB between the fundamental and the *IM3* tones, as shown in Fig. 2.5(a).

### 2.2.4 - Cascaded Non-Linearities

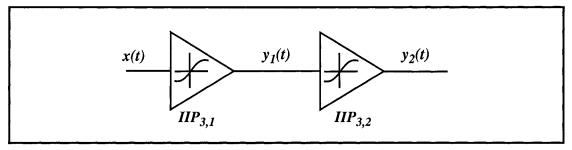

Consider two non-linear stages in cascade as shown in Fig. 2.6, with input-output characteristics expressed as:

$$y_1(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t),$$

(2.31)

$$y_2(t) = \beta_1 y_1(t) + \beta_2 y_1^2(t) + \beta_3 y_1^3(t).$$

(2.32)

Then, by only considering the first and third order terms, it can be easily shown that the overall transfer function of a cascade system is given by:

$$y_2(t) = \alpha_1 \beta_1 x(t) + (\alpha_3 \beta_1 + 2\alpha_1 \alpha_2 \beta_2 + \alpha_1^3 \beta_3) x^3(t) + \dots$$

(2.33)

Thus, similar to equation 2.29, the overall  $IIP_3$  of two non-linear stages in cascade is:

$$IIP_{3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_{1}\beta_{1}}{\alpha_{3}\beta_{1} + 2\alpha_{1}\alpha_{2}\beta_{2} + \alpha_{1}^{3}\beta_{3}} \right|} (dB) . \tag{2.34}$$

Alternatively, by manipulating equation 2.34, we can write:

$$\frac{1}{IIP_3^2} = \frac{3}{4} \cdot \frac{|\alpha_3\beta_1| + |2\alpha_1\alpha_2\beta_2| + |\alpha_1^3\beta_3|}{|\alpha_1\beta_1|}$$

(2.35)

$$= \frac{1}{IIP_{3,1}^2} + \frac{3\alpha_2\beta_2}{2\beta_1} + \frac{\alpha_1^2}{IIP_{3,2}^2},$$

(2.36)

where  $IIP_{3,1}$  and  $IIP_{3,2}$  are the input  $IP_3$  of the first and second stages, respectively.

For n cascaded non-linear stages, the overall  $IIP_3$  of the system can be derived by generalizing equation 2.36 and is expressed as:

$$\frac{1}{IIP_3^2} \approx \frac{1}{IIP_{3,1}^2} + \frac{\alpha_1^2}{IIP_{3,2}^2} + \frac{\alpha_1^2 \beta_1^2}{IIP_{3,3}^2} + \dots + constant.$$

(2.37)

As can be seen from equation 2.36, the non-linearity of the latter stages have a bigger impact on the overall non-linearity of the system, since the  $IP_3$  of each stage is effectively degraded by the total gain preceding that stage.

## 2.3 - CMOS LNA Fundamentals

Apart from the low noise characteristics targeted in LNA designs, input matching and power gain are also two important performance metrics. Input impedance matching is essential in an LNA design because the device has to provide a 50  $\Omega$  termination for the transmission line delivering the RF signal from off-chip. It should be noted that often the performance of the preceding filter (e.g. band selection filter) depends heavily on the quality of the terminating impedance. The power gain of an LNA is also critical, since higher gain translates into an improvement in the overall receiver noise figure, at the expense of higher non-linearity for the subsequent stages, as evident from equations 2.17 and 2.37.

In this section, a detailed derivation of design equations and constraints on the input matching and the gain of CMOS LNA's are presented.

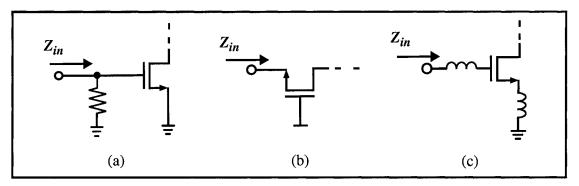

Figure 2.7 LNA input matching topologies: (a) resistive terminations, (b) 1/g<sub>m</sub> terminations, and (c) inductive degeneration.

### 2.3.1 - Input Impedance Matching

There exists several input impedance matching approaches in LNA designs, as shown in Fig. 2.7. Each of these matching techniques can be applied in either a single-ended (as shown) or in a differential form. Note that a balun is required to transform a single-ended RF signal from the antenna to the differential form. Practical baluns introduce losses to the signal path, which directly add to the overall noise figure of the system.

The first topology, shown is Fig. 2.7(a), uses resistive termination at the input port in order to provide a  $50 \Omega$  impedance matching. There are several disadvantages in using this technique: The extra resistor contributes its own thermal noise to the output, which equals the noise contribution of the source resistance. This means that there would be an immediate 3 dB increase in the noise figure. Furthermore, the input signal is attenuated by the resistor termination before reaching the active device, which translates into a reduction in gain and a further degradation in the overall noise performance. The large noise penalty due to the use of a resistive termination makes this architecture undesirable.

The second topology, shown in Fig. 2.7(b), uses the source of a common gate stage as the input termination. Appropriate transistor sizing and biasing is chosen such that the impedance looking into the source of the transistor (i.e.  $1/g_m$ ) equals the characteristic impedance of 50  $\Omega$ . It can be shown that the lower bounds on the noise factor of this topology in a CMOS technology is given by:

Figure 2.8 Small signal equivalent circuit at the input of the LNA.

$$F = 1 + \frac{\gamma}{\alpha} \ge \frac{5}{3} \Rightarrow NF = 2.2 \, dB, \qquad (2.38)$$

and

$$\alpha = \frac{g_m}{g_{d0}},\tag{2.39}$$

where  $\gamma$  is a bias-dependent factor of the channel thermal noise,  $g_m$  is the device transconductance, and  $g_{d0}$  is the zero-bias drain conductance. The computed minimum noise figure of 2.2 dB in equation 2.38 is based on the assumption of long channel devices with parameters  $\gamma = 2/3$  and  $\alpha = 1$ . In today's deep sub-micron CMOS devices,  $\gamma$  can be as high as two-to-three, which is due to the hot electrons effect, and  $\alpha$  can be less than one. The theoretical minimum achievable noise figure for short channel devices in this topology is around 3 dB, which doesn't satisfy today's low noise requirements.

The third topology is popular due to its inherent good noise performance: It employs inductive source degeneration, as shown in Fig. 2.7(c), to present a real impedance at the input terminal. This architecture has been adopted in our designs and is discussed in details.

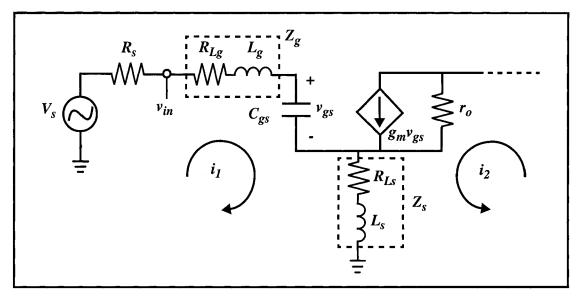

Consider the small signal equivalent circuit at the input of the LNA, as shown in

Fig. 2.8. We can write down the following KVL equation:

$$v_{in} = i_1 Z_g + v_{gs} + (i_1 + i_2) Z_s, (2.40)$$

where

$$v_{gs} = \frac{i_1}{j\omega C_{gs}}. (2.41)$$

By ignoring the effect of channel length modulation, modeled by  $r_o$ , the loop current  $i_2$  becomes  $g_m v_{gs}$ . This assumption is valid in the case of the cascode configuration, since the impedance looking into the following stage equals to  $1/g_{m2}$ , which is much smaller than  $r_o$ .

By manipulating equation 2.40, the input impedance  $(Z_{in})$  can be expressed as:

$$Z_{in} \equiv \frac{v_{in}}{i_1} = Z_g + Z_s + \frac{1}{j\omega C_{gs}} + \frac{g_m}{j\omega C_{gs}} Z_s$$

(2.42)