## Digital Architectures For Analog Signal Generation

by Evan M. Hawrysh, P. Eng.

Department of Electrical Engineering

McGill University, Montreal

July 1996

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your tile - Vatre référence

Our time. Notice reference

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque Canada nationale dи reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-19868-5

#### **Abstract**

Analog and mixed-signal testing is far more complex than its digital equivalent. This thesis will identify the analog test requirements through an extensive analysis of integrated circuit testing, possible error sources, and the different levels of test hierarchy. The results will show that analog testing requires spectrally pure, high-quality predictable test signals. These signals are most robust when reproduced through digital techniques such as direct digital frequency synthesis. Delta-sigma ( $\Delta\Sigma$ ) modulation is perhaps the most versatile technique, as it can precisely encode arbitrary analog waveforms into an pulse-density modulated (PDM), infinite-length, single bit-wide pattern. The noise-shaping characteristics of the  $\Delta\Sigma$  modulator also allow for simple reconstruction of the embedded signal. Unfortunately, on-chip signal generation using this method is currently hindered by the high area overhead and limited programmability of  $\Delta\Sigma$  modulation oscillators. We will introduce the concept of forcing the PDM pattern to be finite in length and thus periodic. Although other periodic encoding algorithms exist, forced-periodic PDM patterns will be shown to be far superior for their precise control over signal amplitude, frequency, phase, and also for their ability to encode an arbitrary waveform. Its effectiveness will be demonstrated with several experiments of single- and multi-tone waveforms of varying degrees of complexity. By creating a fixed-length pattern, we can take advantage of many common digital built-in self-test (BIST) concepts such as scan and RAMBIST, found on most digital and mixed-signal integrated circuits, to supply the necessary hardware. We will show how analog signal generation can be integrated into digital ICs using any or all of the IEEE 1149.1-1990 standard, embedded RAMs, and scan chains. These applications will indeed prove that with very little additional hardware, on-chip, high-quality analog signal generation is possible and that mixed analog-digital built-in-self-test is feasible in today's IC technologies.

#### Résumé

La vérification de circuits analogiques et hybrides analogiques/numériques est beaucoup plus difficile que la vérification de circuits exclusivement numériques. Ce mémoire identifie les ressources nécessaires pour la vérification des circuits analogiques par une analyse détaillée de la vérification des circuits intégrés en général et des sources d'erreurs potentielles, en tenant compte des différents niveaux de vérification. Les résultats démontrent que la vérification de circuits analogiques requiert des signaux de qualité supérieure. Or, ces signaux sont plus stables lorsque produits à l'aide de techniques numériques. La modulation delta-sigma est probablement la technique la plus versatile puisqu'elle permet de coder un signal arbitraire en une séquence infinie de bits. De plus, puisque le bruit généré par la quantization est localisé hors de la bande passante, le signal peut être récupéré facilement. Malheureusement, la production de signaux de cette façon directement sur le substrat du circuit à vérifier entraîne un coût exagéré et souffre d'une versatilité limitée. Nous présentons une méthode pour contraindre les séquences de bits à une longueur limitée et ainsi les rendre périodiques. Bien que d'autres algorithmes permettant de coder un signal sur une séquence périodique existent, notre méthode est supérieure de par son contrôle précis de l'amplitude, de la fréquence et de la phase de même que pour la possibilité de coder une grande variété de signaux. Son efficacité est démontrée par plusieurs expériences reproduisant des signaux de complexité variable. En créant une séquence de longueur définie, il devient possible de réutiliser plusieurs outils de vérification numérique. Nous démontrons comment notre méthode de génération de signaux analogiques peut être intégrée sur un circuit numérique par le standard IEEE 1149.1-1990, par un bloc de mémoire vive ou à l'aide d'une chaîne de vérification. Ces applications prouvent qu'avec peu de matériel additionnel, la génération de signaux analogique de haute-qualité et l'auto-vérification de circuits hybrides analogiques/ numériques sont possibles à l'aide de la technologie actuellement disponible.

### **Acknowledgments**

The single name on this thesis does not do justice to the several people who have contributed their knowledge, experience, and support over the past two years to assist in my pursuit of original and purposeful ideas.

First and foremost, my dynamic advisor, Dr. Gordon Roberts, was the epitome of patience and enthusiasm in my desire to accomplish my goals. His knowledge proved to be an invaluable wealth of information, and his motivation carried me over the course of my research.

I also wish to acknowledge my colleagues who have contributed in several ways with their collective knowledge and friendship, most notably Mourad El-Gamal, Nicolas Gagnon, Ara Hajjar, Xavier Haurie, Arman Hematy, Vincent Leung, and Benoit Veillette. Combined with the efforts of the system administrator, Jacek Slaboszewicz, these people provided an environment conducive to success.

Finally, I would like to thank my family for their unconditional love and support. I am forever indebted to my wife, Linda MacKinnon, who stood by my side for this entire episode and never yielded from her continual support and encouragement.

Funding and equipment for this undertaking has been supplied by Micronet, the National Sciences and Engineering Research Council (NSERC), and the Canadian Microelectronics Corporation.

## **Table Of Contents**

| Abstract                                         |

|--------------------------------------------------|

| Résuméi                                          |

| Acknowledgments i                                |

| List of Figures vi                               |

| List of Tables                                   |

| Chapter 1 - Introduction                         |

| 1.1 - Motivation                                 |

| 1.2 - Integrated Circuit Testing                 |

| 1.3 - Sources of Error                           |

| 1.3.1 - Functional Errors                        |

| 1.3.2 - Manufacturing Defects                    |

| 1.4 - Impact of Defects on Digital Circuits      |

| 1.5 - Impact of Defects on Analog Circuits       |

| 1.6 - The System Hierarchy 1                     |

| 1.7 - Thesis Overview                            |

| 1.8 - Test and Data Collection Environment       |

| Chapter 2 - MADBIST and Analog Signal Encoding 1 |

| 2.1 - The MADBIST Method of IC Self-Test         |

| 2.2 - Digital Encoding of Analog Signals         |

| 2.2.1 - Pulse Generation                         |

| 2.2.2 - MBS Generation                           |

| 2.2.3 - PDM Signal Generation                          | 23   |

|--------------------------------------------------------|------|

| 2.3 - Delta-Sigma Oscillator                           | 29   |

|                                                        |      |

| Chapter 3 - Applications of the Delta-Sigma Oscillator |      |

| 3.1 - The Dedicated Test System                        |      |

| 3.2 - Voltage and Current Signal Generation            |      |

| 3.3 - Delta-Sigma Oscillator ASICs                     | 39   |

| 3.3.1 - Delta-Sigma Oscillator Structure               | 39   |

| 3.3.2 - Deficiencies of the Delta-Sigma Oscillator     | 41   |

| 3.3.3 - Delta-Sigma Oscillator ASIC                    | 43   |

| 3.3.4 - Analog Signal Generator ASIC                   | 44   |

| 3.3.5 - Simulation/Experimental Results                | 47   |

|                                                        |      |

| Chapter 4 - Forced-Periodic PDM Patterns               |      |

| 4.1 - Periodic PDM Pattern                             |      |

| 4.2 - Determining Minimum Bit Pattern Length           |      |

| 4.3 - Finite Length Effects                            |      |

| 4.3.1 - Periodic Noise                                 | 60   |

| 4.3.2 - Error Detection and Correction                 | 62   |

| 4.4 - Arbitrary Waveform Generation                    | 64   |

| 4.4.1 - Multi-tone Encoding                            | 64   |

| 4.4.2 - Two-tone Sinusoid                              | 65   |

| 4.4.3 - Sawtooth Waveform                              | . 65 |

| 4.5 - High Frequency Tone Generation                   | . છ6 |

| Object Stranger December 1                             | ec   |

| Chapter 5 - Memory-Based Storage                       |      |

| 5.1 - Advantages of Memory-Based Storage               |      |

| 5.2 - RAM-Based Signal Generation                      |      |

| 5.2.1 - Processor-Accessible RAM                       |      |

| 5.2.2 - Hardware-Accessible RAM                        | . 73 |

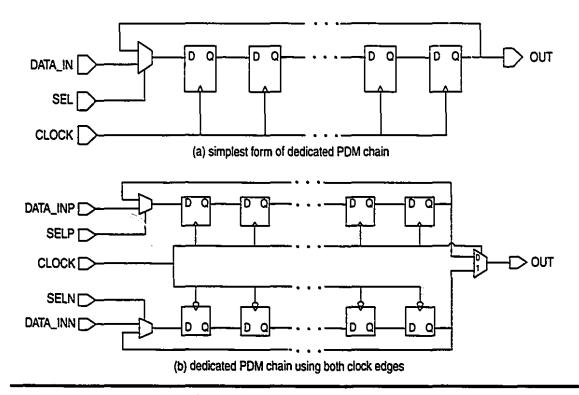

| 5.3 - Flop-Based Signal Generation                     | . 76 |

| 5.3.1 - Scan Chain Sequencing              | 77 |

|--------------------------------------------|----|

| 5.3.2 - Dedicated Chain Sequencing         | 80 |

| 5.4 - Design Considerations                | 81 |

| 5.4.1 - Area Overhead                      | 81 |

| 5.4.2 - Power Consumption                  | 82 |

| 5.4.3 - Maximum Data Throughput Rate       | 82 |

|                                            |    |

| Chapter 6 - Conc'usions                    | 85 |

| 6.1 - Summary                              | 85 |

| 6.2 - Recommendations For Further Research | 87 |

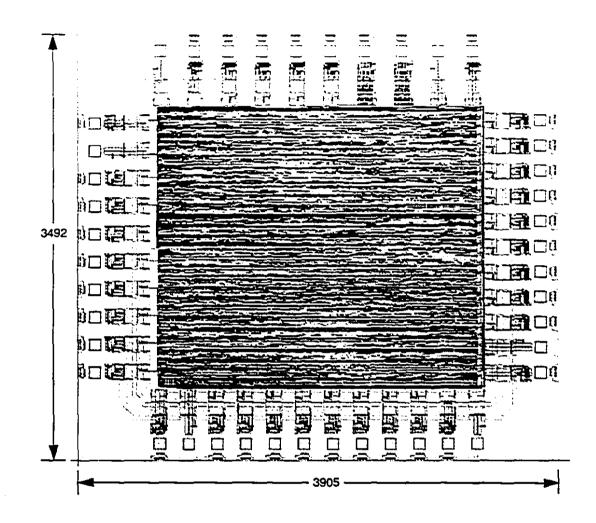

| Appendix A - ASIC Layouts                  | 88 |

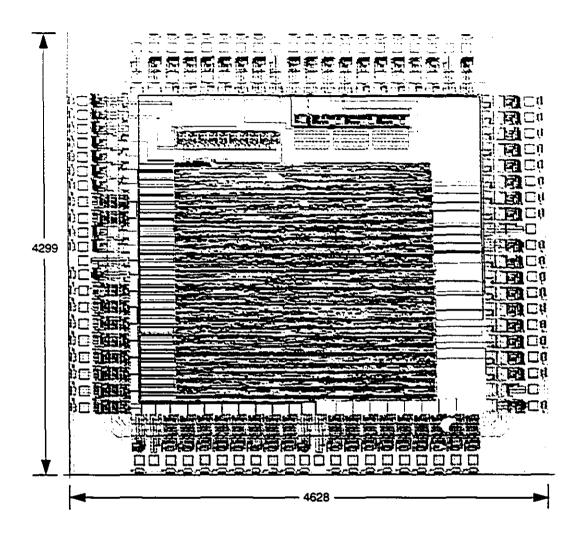

| A.1 - IBAMGOSC ASIC                        | 89 |

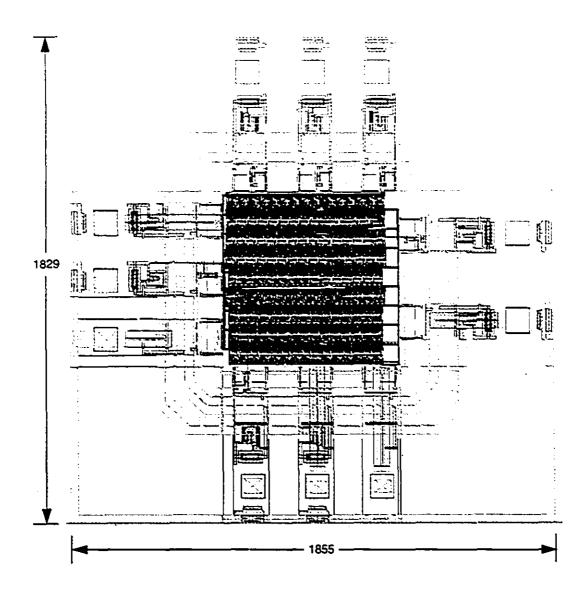

| A.2 - IBAMGODF ASIC                        | 90 |

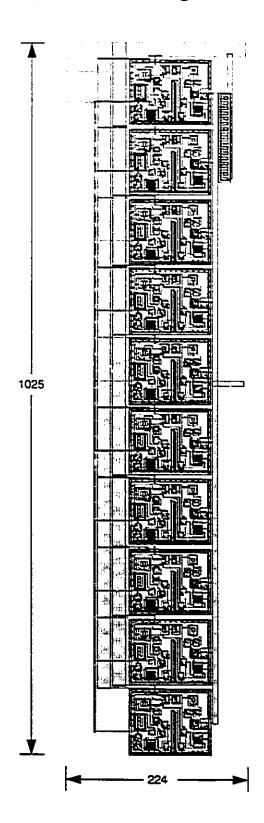

| A.3 - One-Bit Digital-to-Analog Converter  | 91 |

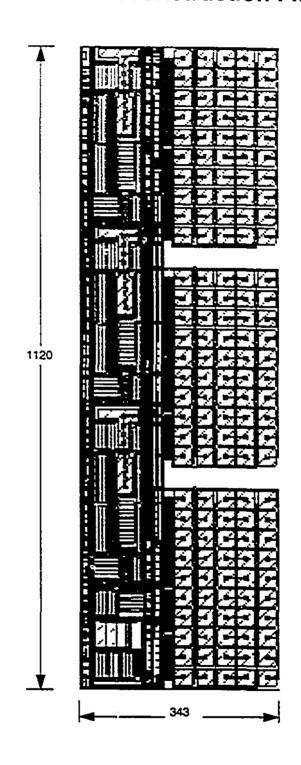

| A.4 - Sixth-Order Reconstruction Filter    | 92 |

| A.5 - Dedicated Flip-Flop Chain            | 93 |

| Appendix B - References                    | 94 |

## **List of Figures**

| Fig. 1.1 - Typical Analog Test Station                                   | 2  |

|--------------------------------------------------------------------------|----|

| Fig. 1.2 - Digital Test Station Retrofitted for Analog Testing           | 3  |

| Fig. 1.3 - Black Box Functional Test Configuration                       | 4  |

| Fig. 1.4 - The Two Failure Modes Due To Manufacturing Defects            | 6  |

| Fig. 1.5 - Effect of Oxide Thickness Due To Process Variation            | 7  |

| Fig. 1.6 - Effect of Device Mismatch on a Digital MOS Inverter           | 8  |

| Fig. 1.7 - Effect of Device Mismatch on an Analog Inverter               | 8  |

| Fig. 1.8 - The Hierarchical Levels of an Electronic System               | 0  |

| Fig. 1.9 - Component Variation Effects on Sub-System Design Tolerances 1 | 1  |

| Fig. 1.10 - Test Station for Conducting Experiments                      | 4  |

| Fig. 2.1 - Signal Flow for a Generic Mixed-Signal Integrated Circuit 1   | 5  |

| Fig. 2.2 - Mixed-Signal IC in a Self-Test Loopback Configuration 1       | 6  |

| Fig. 2.3 - MADBIST IC Test and Component Structure                       | 7  |

| Fig. 2.4 - Example of a Pulse Waveform and Its Frequency Spectrum 1      | 9  |

| Fig. 2.5 - Bit Pattern Storage and Retrieval                             | 20 |

| Fig. 2.6 - Spectrum of an MBS-Encoded 6-Tone Signal                      | 22 |

| Fig. 2.7 - Spectrum of an MBS-Encoded Sine Wave                          | 23 |

| Fig. 2.8 - Typical and Linear Modulator Structures                       | 24 |

| Fig. 2.9 - First- and Second-Order Modulator Structures                  | 25 |

| Fig. 2.10 - Modulator-Based Encoding of a Sinusoid                       | 26 |

| Fig. 2.11 - Analog Signal Recovery                                           | 7         |

|------------------------------------------------------------------------------|-----------|

| Fig. 2.12 - Second- and Fourth-Order Modulator Inband Power Spectra 28       | 8         |

| Fig. 2.13 - Amplitude and Frequency Variability Over a Fixed Bandwidth 28    | 8:        |

| Fig. 2.14 - Encoding Other Types of Analog Signals                           | 9         |

| Fig. 2.15 - Design of a Multiplierless Delta-Sigma Oscillator                | 0         |

| Fig. 3.1 - Block Diagram of a Test System                                    | 4         |

| Fig. 3.2 - Bipolar Non-Return-to-Zero and Return-to-Zero Coding Schemes . 35 | 5         |

| Fig. 3.3 - Use of an RC Filter To Reduce Input Signal Amplitude 3            | 7         |

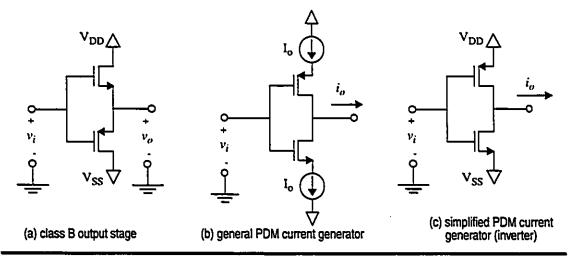

| Fig. 3.4 - PDM Current Signal Circuits                                       | 8         |

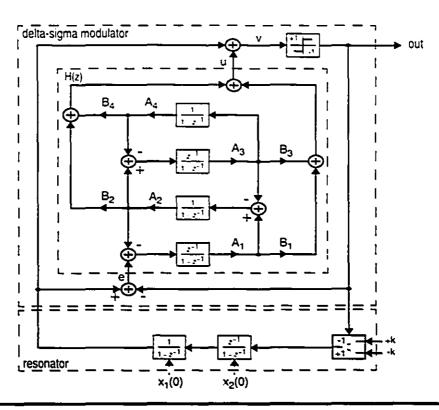

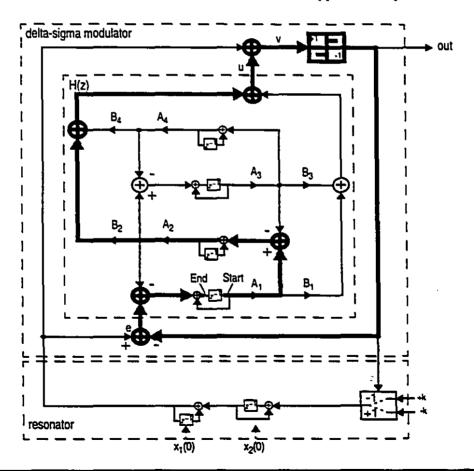

| Fig. 3.5 - Signal Flow Graph for a Fourth-Order Delta-Sigma Oscillator 4     | ŀO        |

| Fig. 3.6 - Forward and Backward Euler Integrators 4                          | 0         |

| Fig. 3.7 - Critical Path for a Fourth-Order Delta-Sigma Oscillator 4         | 1         |

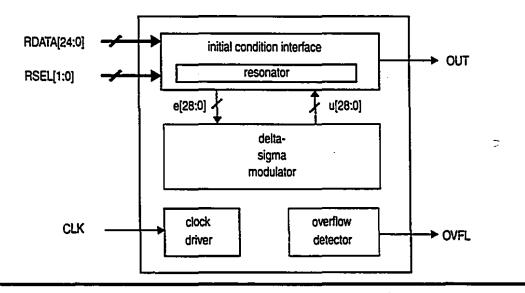

| Fig. 3.8 - IBAMGOSC ASIC Functional Block Diagram 4                          | I3        |

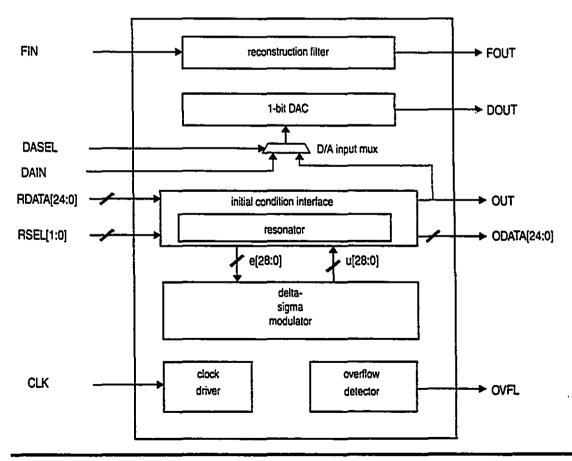

| Fig. 3.9 - IBAMGODF ASIC Functional Block Diagram 4                          | 15        |

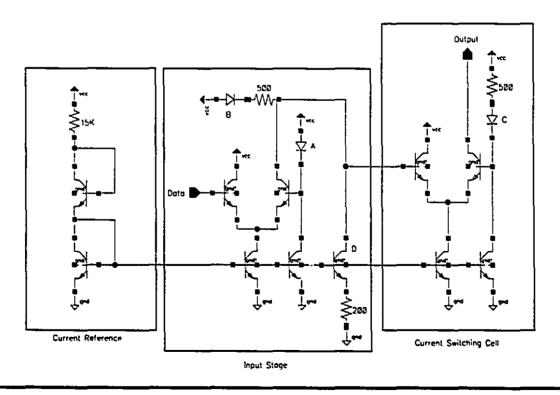

| Fig. 3.10 - Schematic of BiCMOS One-bit DAC                                  | 16        |

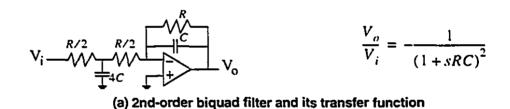

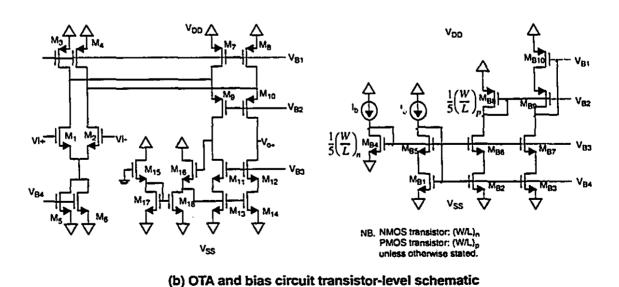

| Fig. 3.11 - Second-Order Biquad Filter Schematic 4                           | <b>17</b> |

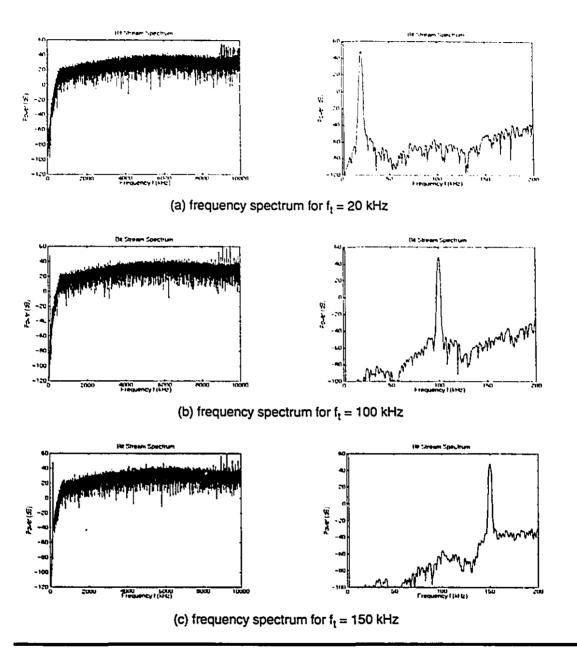

| Fig. 3.12 - Fourth-Order Oscillator Simulation Results 4                     | 19        |

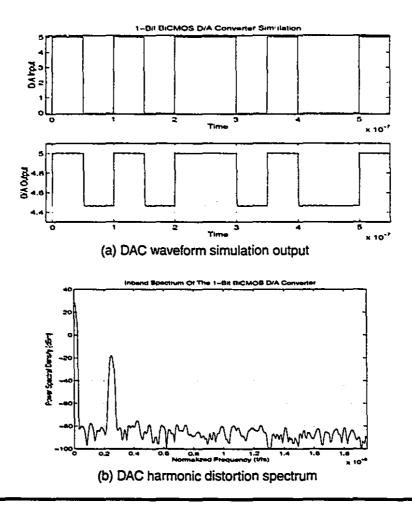

| Fig. 3.13 - DAC Simulation Results 5                                         | 50        |

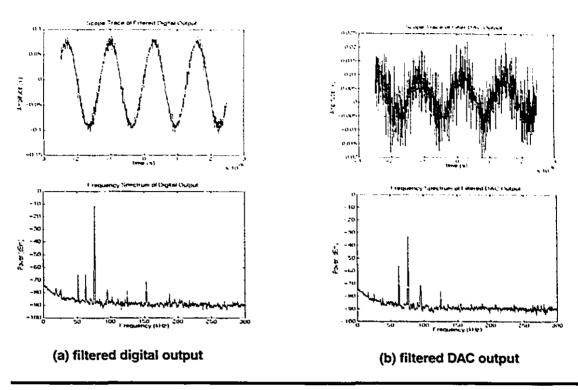

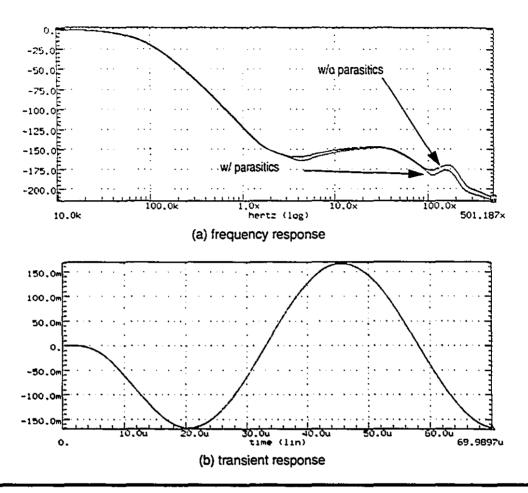

| Fig. 3.14 - Comparison of Filtered DAC Output vs. Digital Output 5           | 51        |

| Fig. 3.15 - Frequency and Transient Response of the Reconstruction Filter 5  | 52        |

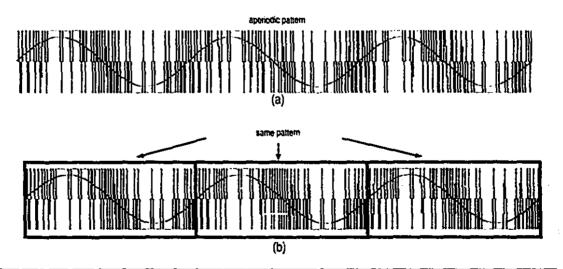

| Fig. 4.1 - An Aperiodic Sine Wave and Its Periodic Approximation 5           | 53        |

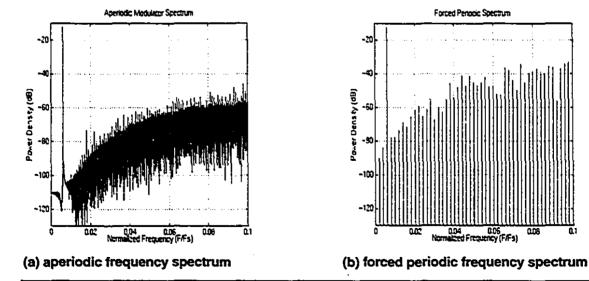

| Fig. 4.2 - Spectra of Aperiodic and Forced Periodic PDM Pattern              | 54        |

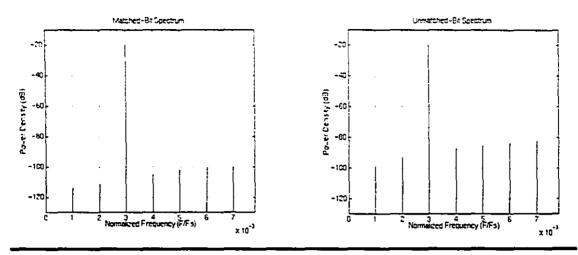

| Fig. 4.3 - Comparison of Matched-Bit and Unmatched-Bit Pattern Spectra 5     | 56        |

| Fig. 4.4 - 392-Bit Sinusoidal Waveform 5                                     | 58        |

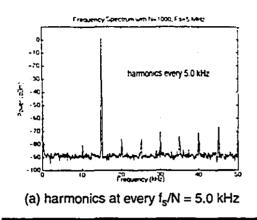

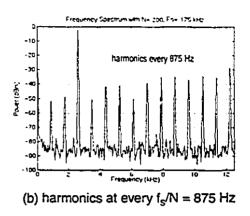

| Fig. 4.5 - Frequency Spectra Illustrating Harmonic Placement 6               | 32        |

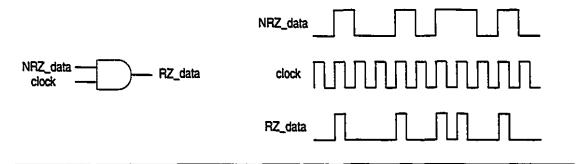

| Fig. 4.6 - A Simple NRZ-to-RZ Coding Circuit                                  | 63 |

|-------------------------------------------------------------------------------|----|

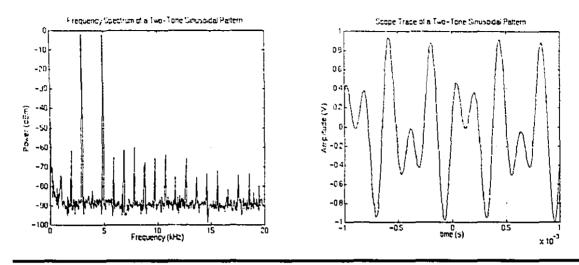

| Fig. 4.7 - Two-Tone Sinusoidal Waveform Extracted From 1024 Bits              | 66 |

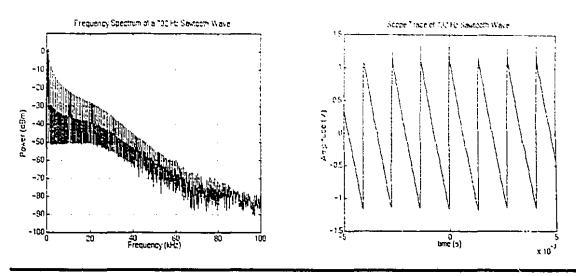

| Fig. 4.8 - 732 Hz Sawtooth Waveform                                           | 67 |

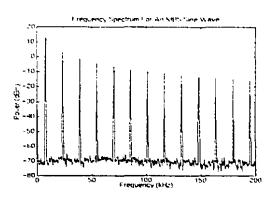

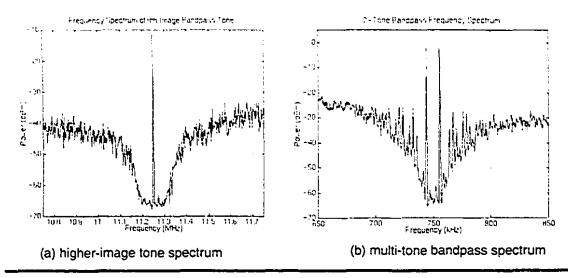

| Fig. 4.9 - Frequency Spectrum of a 8th Image Bandpass Tone                    | 68 |

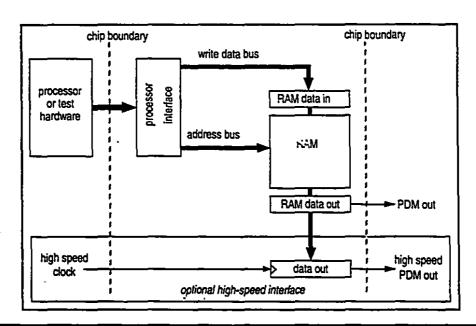

| Fig. 5.1 - Finite-Length PDM Controller Utilizing a Processor Interface       | 72 |

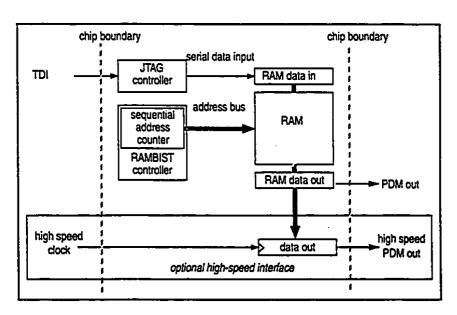

| Fig. 5.2 - Finite-Length PDM Controller Utilizing Existing On-Chip Test Logic | 73 |

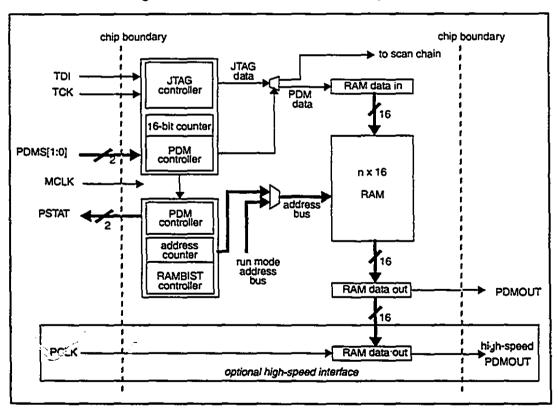

| Fig. 5.3 - PDM Controller Utilizing JTAG and RAMBIST Controllers              | 74 |

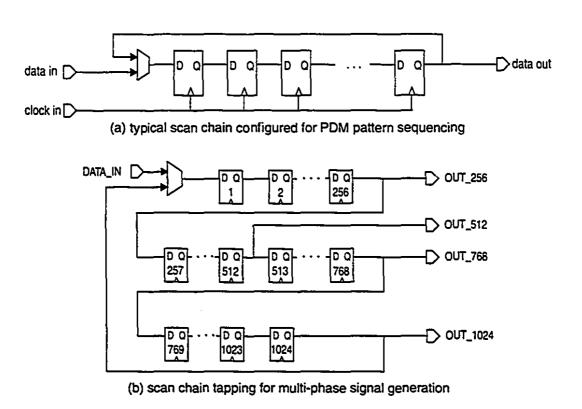

| Fig. 5.4 - Scan Chain Configurations                                          | 76 |

| Fig. 5.5 - Phase-Shifted Signals Created By Tapping The PDM Chain             | 77 |

| Fig. 5.6 - PDM Chain Configured Over Existing Scan Chains                     | 78 |

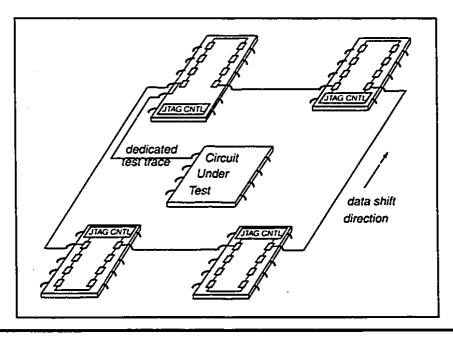

| Fig. 5.7 - PDM Chain Configured Over Multiple ICs                             | 79 |

| Fig. 5.8 - Dedicated Chain Circuits                                           | 80 |

## **List of Tables**

| Table 1.1 - Typical Parameter Tolerances For Various Monolithic Devices | 12 |

|-------------------------------------------------------------------------|----|

| Table 3.1 - Fourth-Order Modulator Coefficients                         | 39 |

| Table 3.2 - Functional Simulation Results                               | 48 |

| Table 4.1 - Periodic vs. Aperiodic Dynamic Range Comparison             | 55 |

| Table 5.1 - PDMS and PSTAT Pin Mapping                                  | 75 |

| Table 5.2 - Performance Summary                                         | 83 |

## **Chapter 1 - Introduction**

The purpose of this thesis is to focus on the generation of digital signals for use in analog testing and their integration into the testing environment. Research in the area by Lu et al [1] provided the basis for area-efficient analog signal generation using digital encoding. The concept of mixed analog-digital built-in-self-test (MADBIST) introduced by Toner and Roberts [2] combined the signal generator with data collection methods to demonstrate the feasibility of BIST for mixed-signal ICs. We plan to build on this previous work to introduce two major advancements in the area. The first demonstrates the creation of finite-length digital patterns which eliminate the need for an on-chip analog signal generator. The second focusses on the applications of digital-encoded signals. The first describes a system designed as a stand-alone test circuit or as a sub-system that can retrofit a digital tester for analog or mixed-signal IC testing. The second application focusses on the mixed analog-digital built-in self test (MADBIST) application with the introduction of two on-chip signal sequencers that integrate into current digital DFT techniques. These configurations allow for the generation of on-chip stimuli with very little and in some cases, no additional area overhead.

#### 1.1 - Motivation

Digital integrated circuit (IC) manufacturers have incorporated built-in-self-test (BIST) schemes into the design process in an attempt to minimize production costs and improve quality. BIST creates a methodical approach to the detection and isolation of manufacturing defects. Today, the most accepted forms of digital BIST are based on the interface set out in the IEEE 1149.1-1990 Standard, specifically boundary scan. Other types of IC BIST include internal scan and memory tests that verify RAM functionality (RAMBIST).

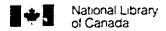

Analog or mixed-signal ICs, on the other hand, rely mostly on ad hoc, unstructured test methodologies. Analog test stimuli are most often generated off-chip in a traditional test setup as shown in Fig. 1.1. In a production environment, the test station includes a test module consisting of a digital signal generator, high-precision digital-to-analog and analog-to-digital converters (DACs and ADCs), and a test head fixture. The remote location of the test station with respect to the circuit under test exposes the circuit to parasitics present in the test apparatus and the in interconnect between the circuit and the test module. This is true even if the test module is located on the test head. The interconnect is potentially quite long (with respect to the wavelength of the test signals) and, as a result, the signals carried through them are susceptible to signal degradation. As circuit speed increases, greater attention is placed on board layout in order to minimize energy reflection, noise, and other effects not directly related to the circuit itself. These effects must be accounted for when performing tests. Thus, the manufacturing and test processes for these ICs often require extensive setup time for proper device characterization and very expensive test equipment to guarantee high noise immunity and to minimize the change on the circuit behaviour it is testing. Addressing these complexities makes the mixed-signal test field a very promising and active area of research.

One way to minimize the complexity and expense of the traditional analog test method is to place the test apparatus directly on-chip as a built-in-self-test, or BIST. Alternatively, one could avoid signal degradation over the interconnect by digitally encoding the analog test stimuli, provided little complexity is required at the test fixture to decode it. Toner and

Fig. 1.1 - Typical Analog Test Station

Roberts [2] have proposed MADBIST, and have shown that the above two concepts are feasible. Research in this area is based on the digital encoding of analog signals using delta-sigma ( $\Delta\Sigma$ ) modulation techniques and serves as the basis for the work set out in this thesis.

$\Delta\Sigma$  modulation allows us to transform a multi-bit digital pattern into a single-bit pattern through the principles of oversampling with a pulse-density modulation (PDM) coding scheme. PDM serves as a practical method to encode an analog signal in a digital one [3], with simple reconstruction of the original signal [4]. This pattern is, unfortunately, of infinite length and requires the use of an area-intensive  $\Delta\Sigma$  oscillator for on-chip signal generation. Our previous research indicates, however, that we can create an approximate finite-length digital bit pattern that contains the desired analog test signal [5]. Having obtained a pattern of reasonable length, we can now integrate analog signal generation into existing digital BIST hardware. In particular, we can utilize the scan chain configuration and controller logic set out in IEEE Standard 1149.1 or even use existing RAMBIST logic to minimize hardware overhead. This now makes MADBIST a practical method of performing analog BIST.

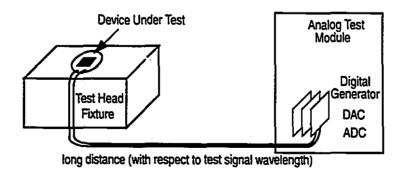

We can make further progress into minimizing test complexity and cost by simplifying the traditional analog setup described earlier. Now that signal generation can be achieved reliably with little hardware in the digital domain, relatively cheap digital testers can be retrofitted to perform the tasks once dedicated to analog testers. This is possible since a modified test head can hold the minimal additional logic, and only digital signals need be exchanged between the test head and the digital test module as shown in Fig. 1.2.

Fig. 1.2 - Digital Test Station Retrofitted for Analog Testing

#### 1.2 - Integrated Circuit Testing

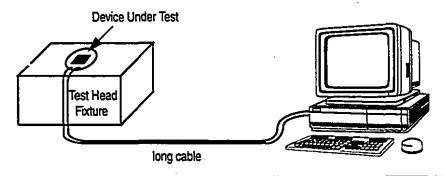

Testing in its simplest form is the stimulation and observation of the pins of an electronic device. This is termed the "black box" method of testing (as depicted in Fig. 1.3) in which there is no knowledge of the inner workings of the circuit (nor is there a need to know), just the knowledge of the overall function of the circuit and its input and output signals. The circuit performs a known function, and it is the job of the test engineer to determine whether or not the circuit performs its function within an acceptable tolerance level. For digital devices, the circuit output response is either a logic-0 or logic-1. Hence there is a zero tolerance level. Analog or mixed-signal circuits, on the other hand, may have a range of output values within which the measured output is acceptable. This type of stimulation and response analysis is known as functional testing. In all cases however, as design complexity grows, functional testing becomes increasingly costly to perform. Sophisticated digital circuits, for example, require several lengthy test patterns or long circuit preparation time to mimic a particular circuit function. Analog circuits require very accurate and precise test equipment to not only generate realistic input signals but also to capture and process output data to verify circuit behaviour. These situations require extensive preparation and test execution time to maximize circuit fault coverage. The culmination of test preparation, lengthy test times, and complex output analyses make the functional testing approach an expensive task. Thus one must consider possible alternatives.

Fig. 1.3 - Black Box Functional Test Configuration

#### 1.3 - Sources of Error

In determining alternatives, we must first examine likely sources of error. We can categorize errors into two different types: functional errors and manufacturing defects.

#### 1.3.1 - Functional Errors

Simply put, functional defects are errors in the operation of the circuit caused by an error made during the design phase. In the digital domain, the cause is easily identifiable: the designer either misinterpreted the functional specification or made a careless mistake, causing an outcome different from the desired result (e.g. a logic-1 was observed when a logic-0 was expected). While the analogy holds true for the analog circuits, the designer assumes a greater responsibility in the functional performance of the circuit by practising analog design techniques such as symmetrical layout, component isolation to avoid coupling effects, and ensuring current operation within IC manufacturing tolerances. Assuming the designer is competent at his or her job, we turn our attention to the other error source, that is, defects caused by the manufacturing process.

#### 1.3.2 - Manufacturing Defects

We define manufacturing defects as being those created during the fabrication process, and are beyond control of the designer. There are generally two types of manufacturing defects: those caused by environmental impurities and those caused by process variation.

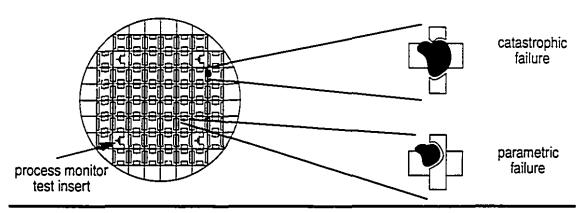

One example of an environmental defect is a piece of dust or debris originating, for example, from the gears driving the conveyer belt and landing on a die. This can cause two types of component failures (as shown in Fig. 1.4): catastrophic and parametric. A catastrophic failure is one in which a component simply does not change state. Using a transistor as an example, it is either stuck on (shorted) or off (open-circuited). A parametric failure, on the other hand, is one in which the component appears to function, but may not be within tolerances. Such would be the case for a transistor that may turn on and off but carries less current than is typical.

Fig. 1.4 - The Two Failure Modes Due To Manufacturing Defects

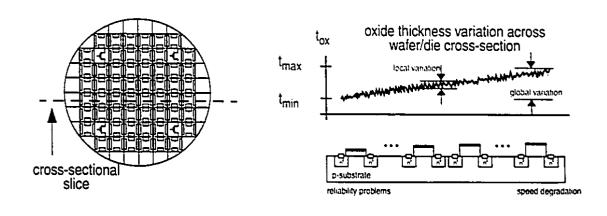

Process variation is the change of layer depositions due to fluctuation of equipment alignment or performance. One example would be the variation of oxide thickness over a die or wafer, as illustrated in Fig. 1.5. Caused by a machine drift or alignment skew, differing oxide thicknesses occur at various points on the wafer. Where the thickness is minimal, there is increased risk of a non-functional transistor and reduced reliability (i.e., pin holes through the oxide). At the other extreme, where the oxide is thicker than the nominal value, the speed of the device is degraded due to reduced drain-to-source current.

Process variation can be categorized into two types: global and local variation. Global variation (in the gate oxide example) focusses on the oxide thickness across the entire wafer, with the assertion that so long as the geographical extrema of the wafer fall within specifications, adjacent dies have a strong likelihood of also being within specifications. Consequently, all ICs, be they digital, analog, or mixed-signal, must be monitored for global variation to provide a confidence level for a properly manufactured wafer or die. This can be done through strategically-placed test monitor inserts (see Fig. 1.4). Local variation (again using the gate oxide example) is the difference in oxide thickness among adjacent dies on the wafer or among components on the same die. Local variation measurements give no indication as to the overall wafer yield; rather they quantify the variability between adjacent components. This is useful information for circuits based on component-matching, i.e., designed by ratios.

Now that we have covered the different types and causes of manufacturing defects, we will study the significance of each on both digital and analog integrated circuits.

Fig. 1.5 - Effect of Oxide Thickness Due To Process Variation

#### 1.4 - Impact of Defects on Digital Circuits

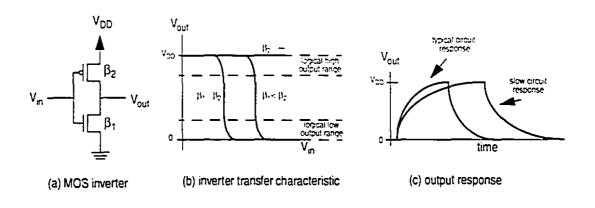

To observe the effects of the different manufacturing defects, consider the typical MOS inverter, given in Fig. 1.6(a), with transistor gain factors  $\beta_1$  and  $\beta_2$ . Due to local process variation,  $\beta_1$  will differ slightly from  $\beta_2$ , and result in the skewed transfer characteristic as shown in Fig. 1.6(b). However, as long as the output logic levels fall within an acceptable range, the circuit will function properly. Thus the logic function is insensitive to device mismatches caused by local process variation.

Since parametric deficiencies due to environmental contamination directly affect the gain factor of the transistor, digital circuits are somewhat immune to parametric failures. This depends, of course, on the transistor  $\beta$  still yielding sufficient drive capability and the circuit response, typified in Fig. 1.6(c), falling within the required timing specifications. Fortunately, these failures can still be identified by an incorrect logic level in a given time interval (i.e., the failure is considered catastrophic).

When there are significant differences between the transistor gain factors, for example,  $\beta_2$  approaching  $\infty$ , the affected transistor is now short-circuited, and the device logic function fails to operate correctly. Thus, the logic function is sensitive to catastrophic failures.

Since digital devices are sensitive to catastrophic failures, digital test methods concentrate on incorrect logic function, rather than on device mismatch effects. Note that as digital

Fig. 1.6 - Effect of Device Mismatch on a Digital MOS Inverter

designs approach the sub-micron technology, analog design techniques such as interconnect matching are practised, and thus the characteristics of analog behaviour on digital circuits are of importance. The impact of defects on analog circuits are discussed in the following section.

#### 1.5 - Impact of Defects on Analog Circuits

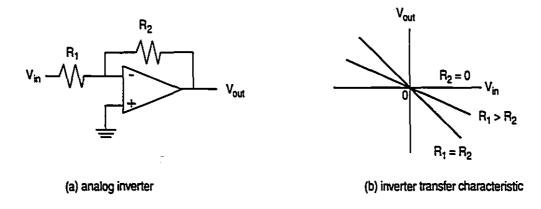

Unlike digital circuits, the function of analog circuits are sensitive to device mismatches. Consider the analog inverter shown in Fig. 1.7(a). Ideally,  $R_1$  and  $R_2$  are equal. Due to local process variation, however, it is not likely that an IC containing this circuit will have equal resistors. The end result is a deviation from the expected transfer characteristic illustrated in Fig. 1.7(b).

Fig. 1.7 - Effect of Device Mismatch on an Analog Inverter

Analog designers have acknowledged that the output response may vary from ideal. Therefore, in an attempt to minimize signal variability, great importance is placed on design layout. Techniques such as designing circuits so that their characteristics depend on a ratio of components (design by ratios), symmetrical component layout, matched interconnect lengths, and impedance matching are employed as good design practice for this reason. In addition, the tolerances and variability of the manufacturing process must be minimized in order to maximize yield. The above practices serve to minimize the effect of local process variation on an analog circuit. Parametric failures in which the device still functions can be treated as a local variation.

Like the digital circuit, analog circuits are also sensitive to catastrophic errors. Revisiting the inverter example, it is obvious that a large change in one of the resistors (like say,  $R_2$  approaching  $\infty$ ) will prevent correct circuit function. In general, however, components such as resistors and capacitors are large in comparison to minimum device sizes and, as a result, catastrophic failures are less likely to occur.

A third exposure in analog design is component limitation, such as non-linearities and noise. Higher-order effects may yield a different function for a given component that was designed as a linear element, introducing a degree of uncertainty to the expected results. Analog components are susceptible to noise, may generate noise themselves, and/or couple with neighbouring components to create spurious noise — all which may degrade IC performance.

Because of the dependency on component mismatches and component limitations, analog test methods focus on these effects. Of course, catastrophic failures are equally as important; yet the discovery of catastrophic errors is an artifact of mismatch/limitation testing and does not normally require an extra suite of tests. Unfortunately, no simple method exists to provide fault coverage for mismatch/limitation testing. It is the position of the author that functional testing must be performed to ensure correct device functionality and to identify parametric and catastrophic errors.

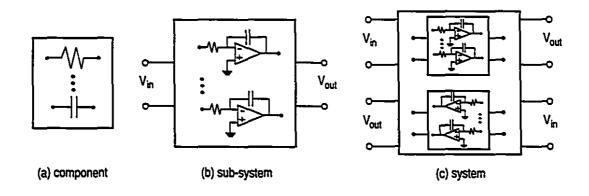

#### 1.6 - The System Hierarchy

Another aspect to consider is the practicality and complexity of testing at different levels of the design hierarchy, from the component level (within a single IC) to an entire multifunction chip or multi-chip system. Consider an electronic system consisting of three levels of hierarchy, shown in Fig. 1.8. The lowest level is the component level, indicated in Fig. 1.8(a). These are building blocks, and their individual behaviours may interact to form the desired function of a larger block. For example, the behaviour of two resistors in series is based on the sum of the two -- not on their individual absolute values. The next level of hierarchy is the sub-system level in Fig. 1.8(b). A sub-system is a building-block whose behaviour is not designed to interact with other sub-systems in order to achieve a desired behaviour. An example of a sub-system would be the receive and transmit circuits of a telephony coder-decoder (CODEC); it is undesirable to have the function of one affect the function of the other. The third and highest level is the system level as in Fig. 1.8(c). It is comprised of multiple sub-systems to perform a desired function or number of functions. Again, it is undesirable to have any interaction between blocks here. We now have to ascertain what information is contained in the tests performed at the different hierarchical levels.

At the component level, we can obtain the absolute values and hence the variation of each individual element. However, because of the behavioural interaction of components at the next hierarchical level (sub-system), individual component variation is not sufficient to

Fig. 1.8 - The Hierarchical Levels of an Electronic System

deduce individual sub-system acceptability. That is, rejection of individual components may unnecessarily lower the yield by rejecting components which, while individually falling out of tolerance specifications, collectively combine to form an acceptable device at the sub-system level. This is evident if we examine the resistors of an analog inverter in Fig. 1.9. Here we have specified typical design tolerances on the individual resistors of ±20%, and an inverter transfer function tolerance of ±3%. Consider Case 1: due to manufacturing error, the resistors individually fall outside their specified tolerance level; yet the inverter falls within specifications. Using component tests as a guide, a properly functioning inverter would have been rejected. Conversely, consider Case 2: the individual components fall well within specification but in opposite tolerance directions; in this case, the inverter falls outside of its acceptable tolerance range. Component testing would have passed a non-functional circuit. Thus, testing at the component level does not ensure a properly functioning circuit.

The sub-system level, as described earlier, has no intended interaction between sub-systems to produce the desired circuit behaviour. As a result, tests performed at this level verify sub-system function and also guarantee correct sub-system function at the system level. As illustrated in Fig. 1.9, the sub-system is tolerant to individual component variation, provided the components are affected in the same manner. Immunity to component variation can, however, be maximized during the layout phase of the design.

Specifications: individual component tolerances: ± 20% inverter (sub-system) design tolerance: ± 3%

Ideal transfer function:

$$TF_{ideal} = \frac{V_{out}}{V_{in}} = -\frac{R_{2ideal}}{R_{1ideal}}$$

Case 1:

$$R_{1} = R_{1ideal} + 25\%$$

$$R_{2} = R_{2ideal} + 22\%$$

$$R_{2} = R_{2ideal} + 22\%$$

$$R_{2} = R_{2ideal}$$

$$R_{3} = R_{2ideal}$$

$$R_{4} = R_{2ideal}$$

$$R_{2} = R_{2ideal}$$

$$R_{3} = R_{2ideal}$$

$$R_{4} = R_{2ideal}$$

$$R_{2} = R_{2ideal}$$

$$R_{3} = R_{2ideal}$$

$$R_{4} = R_{4ideal}$$

$$R_$$

Case 2:

$$R_{1} = R_{1ideal} + 3\%$$

$$R_{2} = R_{2ideal} - 2\%$$

$$R_{3} = R_{2ideal} - 2\%$$

$$R_{4} = R_{2ideal} - 2\%$$

$$R_{5} = R_{2ideal} - 2\%$$

$$R_{1ideal} - 2\%$$

$$R_{1ideal} - 2\%$$

$$R_{2} = R_{2ideal} - 2\%$$

$$R_{3} = R_{2ideal} - 2\%$$

$$R_{4} = R_{2ideal} - 2\%$$

$$R_{5} = R_{5} = R_{2ideal} - 2\%$$

$$R_{5} = R_{5} = R_{5}$$

$$R_{5} = R_$$

Fig. 1.9 - Component Variation Effects on Sub-System Design Tolerances

Component Parameter/Ma **Absolute** Matching Type terial Value Tolerance Tolerance NPN Transistor ±20% ±5% β ±20mV V<sub>BE</sub> ±1mV **NMOS** ٧<sub>T</sub> ±100mV ±10mV Transistor ±20% ±5% K<sub>p</sub> Resistor p-type diffused ±20% ±1% ±30% ±5% epitaxial thin film ±5% - ±10% ±1% - ±2% Capacitor MOS ±20% ±0.1% - ±1% ±20% ±0.1% - ±1% poly-poly

Table 1.1 - Typical Parameter Tolerances For Various Monolithic Devices

Table 1.1 exemplifies the advantages of designing by ratios to utilize the componentmatching attributes of the fabrication process. Note the obvious reduction in matching tolerances versus absolute value tolerances.

Sub-systems are often partitioned by their intended behaviour. That is, functional partitioning is analogous with sub-system partitioning. This suggests that functional testing is best performed at the sub-system level. Several advantages to functional testing exist at the sub-system level. First, there is inherent fault isolation since sub-systems are partitioned by function. Second, functional testing serves to characterize the circuit by its functional black-box behaviour, thereby eliminating the need to manually probe (and potentially disturb) internal nodes to characterize circuit performance. Finally, since functional testing and device characterization are performed simultaneously, there is a reduction in test time and complexity.

System level testing encompasses the entire multi-function chip or multi-chip circuit. Tests at this level appear similar to actual field usage of the device, except that they may push the limits of system characteristics, such as data throughput, signal quality, noise immunity, and temperature stresses. This technique is known as "soaking" the circuit. Often this is done to ensure compliance with governing standards. While system testing is the only manner in which to guarantee an end-to-end functional product, it is not intended to characterize its sub-systems or attempt to detect its faults. The complexity of a circuit

consisting of multiple sub-systems and countless components makes complete fault detection cost- and time-prohibitive at this level. In larger circuits consisting of thousands or millions of individual elements, the interaction of all components makes this task virtually impossible. Thus, in order to minimize test complexity and effort, testing should be done at the sub-system level.

#### 1.7 - Thesis Overview

We have just brought forth the importance of performing functional tests on analog circuits at the sub-system level. This necessitates the requirement for high-quality analog signals as test stimuli. It will be our mandate to create a signal generator using digital circuitry in order to achieve spectrally pure signals and have precise control over amplitude and frequency. Moreover, we will arrive at a technique which minimizes the area a signal generator requires so that it can be placed on-chip for BIST and other test or signal generation applications. We will also integrate the method into today's digital test architectures to facilitate its introduction to industry and simplify its implementation.

This thesis will continue by introducing the concept of MADBIST. The idea of performing on-chip BIST for mixed-signal ICs in a simple and area-efficient manner is ground-breaking research which this thesis uses as the basis for development. We will describe three main types of analog signal encoding, all of which endeavour to embed an analog signal into a bit-wide digital pattern, and justify our decision to favour pulse-density modulation (PDM) as the most powerful and versatile encoding scheme available today. We will also demonstrate the use of PDM in an analog signal generator known as the  $\Delta\Sigma$  oscillator.

Chapter 3 will highlight several applications of the  $\Delta\Sigma$  oscillator, including the dedicated test system which creates a simple yet effective analog IC tester. We will also describe two fabricated oscillator ASICs and provide simulation and experimental results.

Chapter 4 will introduce our first original concept: the forced-periodic PDM bit pattern. We will describe how to establish the minimum bit pattern required to encode an analog

signal using PDM techniques, examine the effects of truncating an infinitely-long bit pattern, and demonstrate its versatility in encoding both simple and complex analog waveforms.

Chapter 5 will focus on the application of finite-length PDM patterns. Here we provide two unique and original techniques for integrating analog signal generation into the current digital test architectures. Using such test logic as the 1149.1-1990 IEEE JTAG interface and RAMBIST, we introduce various hardware configurations that make MADBIST a feasible concept in today's mixed-signal ICs, and put analog signal generation on an IC with virtually no additional logic.

This thesis will conclude with a summary of the work that has been introduced thus far. We feel the originality of truncating PDM patterns and integrating analog test generation into digital test architectures creates several new opportunities for further research and will propose a few ideas that can make use of the powerful techniques described herein.

#### 1.8 - Test and Data Collection Environment

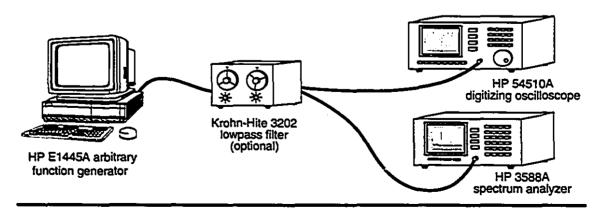

Unless otherwise indicated, all experimental results given in this thesis were collected with a test station as indicated in Fig. 1.10. Data patterns were generated on an HP E1445A arbitrary function generator. When required, a Krohn-Hite 3202 maximally-flat lowpass filter was included in the signal path. Graphs and other data collection were obtained from an HP 54510A digitizing oscilloscope and an HP 3588A spectrum analyzer.

Fig. 1.10 - Test Station for Conducting Experiments

# Chapter 2 - MADBIST and Analog Signal Encoding

One of the primary applications for advancements in the area of digitally-encoded analog signals is mixed analog-digital built-in self-test, or MADBIST. This chapter will explain the concept of MADBIST and the variety of methods to digitally-encode an analog signal.

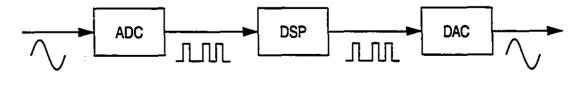

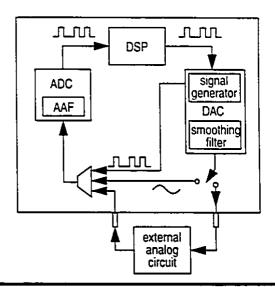

#### 2.1 - The MADBIST Method of IC Self-Test

The MADBIST scheme, as set out in [1], is directed towards the self-testing of a mixed-signal IC consisting of an analog-to-digital converter (ADC), a digital signal processing (DSP) unit, and a digital-to-analog converter (DAC), each of which is classified as a subsystem. Generally, a generic mixed-signal IC has an analog signal that passes through the ADC, is processed in the digital domain using a DSP unit, and is converted back to an analog signal using a DAC as shown in Fig. 2.1.

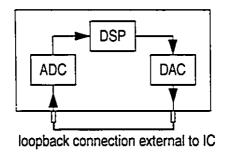

One method to test all sub-systems of the IC is to place the device in a loop-back mode, as shown in Fig. 2.2. Here, the DSP unit generates a signal which is passed through the DAC and is looped back to the ADC input. The digital signal of the ADC is then passed on to the DSP unit for comparison with the original digital pattern. This test mode is not conclusive, however, since errors in the DAC may be masked by errors in the ADC. Consequently, it is not an acceptable test method, according to the CCITT standards body.

Fig. 2.1 - Signal Flow for a Generic Mixed-Signal Integrated Circuit

Fig. 2.2 - Mixed-Signal IC in a Self-Test Loopback Configuration

MADBIST proposes a test method which verifies the functionality of the IC by testing each sub-system individually. The key element is the PDM signal generator in which, if the ADC utilizes a  $\Delta\Sigma$  modulator, there is little additional area overhead associated with the setup. Figure 2.3 shows the required modifications. The test sequence is described below.

First, the DSP unit and any other digital circuitry on the IC is tested using normal digital BIST techniques. Next, the digital components are configured to generate a PDM bit pattern, within which is encoded an analog signal, and is multiplexed into the ADC. The anti-aliasing filter of the ADC extracts the analog signal from the digital bit pattern. In cases where the ADC input cannot handle a rail-rail input digital input, a simple filter (such as a passive RC) with a cut-off frequency at the bandedge can reduce the signal levels considerably. The filter may exist on- or off-chip (for the purposes of a pure BIST it would of course, reside on-chip and preferably part of the input stage of the anti-aliasing filter). The digitized signal output from the ADC is then fed back into the DSP unit for comparison with the original signal. Through a variety of tests, the ADC may be completely exercised in this manner.

With the functionality of the ADC verified, PDM stream generation is disabled, and the DAC is placed in normal operating mode. A loopback configuration is then established through the switch and multiplexer internal to the chip. Since the DSP unit and the ADC have passed their tests, the DAC can now be fully tested without the risk of any errors being masked. The performance of each component has now been individually

Fig. 2.3 - MADBIST IC Test and Component Structure

characterized. Assuming all tests were satisfactorily completed, the chip as a whole has passed its BIST and can now be used for testing analog circuits external to the IC.

The MADBIST configuration relies on a relatively powerful digital processing unit to perform the certain analyses necessary for performance measurements. For example, industrial tests such as frequency response, gain tracking, and signal-to-noise ratio measurements require post-processing of the digital bit stream for parameter extraction. Such measuring techniques include the Fast Fourier Transform (FFT) or a narrowband digital filter. Currently, the hardware overhead associated with such techniques can be significant and must be considered at the design stage. However, it is anticipated that further research in the area can produce smaller, more efficient data extraction methods. For the purposes of the MADBIST discussion, we will assume a narrowband digital filter is used [2].

The key element in MADBIST is the use of a one-bit digital signal stream to represent an analog signal. The signal generator is also the most area-intensive component of the system. If the ADC uses oversampling logic (i.e., it consists of a  $\Delta\Sigma$  modulator), then that same modulator can be shared with a  $\Delta\Sigma$  oscillator to convert a multi-bit digital signal to a one bit-wide, over-sampled data stream. This may not always be the case however; more generally, we should examine the various techniques of digitally encoding an analog

signal to determine which may be the most useful or practical while minimizing costs due to additional hardware overhead and complexity. A variety of signal generation methods will be discussed in the following section.

#### 2.2 - Digital Encoding of Analog Signals

There are various techniques to encode an analog signal into a digital bit pattern. For instance, a multi-bit representation that quantizes the infinitely-variable analog signal into a digital word is often used in digital signal processing but requires sophisticated A/D and D/A converters for encoding and decoding. We must not forget that we are focussed on testing these converters and thus cannot use them for test signal generation. Moreover, it would be much more convenient if the encoded signal were embedded in a single-bit rather than multi-bit representation. Intuitively, we would expect the extraction of the encoded signal to be an easier procedure.

Three common methods of generating a single-bit pattern to represent an arbitrary analog waveform exist: pulse generation, multi-frequency binary sequence (MBS) generation, and pulse-density modulated (PDM) signal generation. These will now be examined in greater detail.

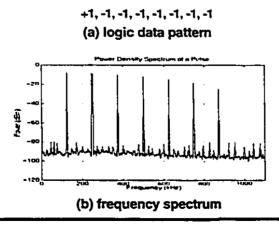

#### 2.2.1 - Pulse Generation

The simplest form of analog signal generation is the creation of an analog signal by simply applying and repeating periodic bit pattern composed of a single pulse. The fundamental frequency is given by

$$f_t = \frac{f_s}{N},\tag{2.1}$$

where N is the pattern length in bits and  $f_s$  is the sampling frequency. A total of N-I tones exist over the frequency range  $f_s$ , occurring at

$$f_{tones} = f_s - k f_t, 1 \le k \le N - 1$$

(2.2)

Figure 2.4 shows an example of a pulse pattern (a) and its spectrum (b) over the bandwidth,  $f_s$ . Here we have a periodic 8-bit pattern containing a single +1 and seven -1s clocked at a rate of 1 MHz. Thus,

$$f_t = \frac{1MHz}{8} = 125kHz.$$

As expected, the frequency spectrum consists *N-1*, or seven tones: a fundamental at 125 kHz followed by six harmonics every 125 kHz thereafter over the frequency range of 1 MHz.

This approach has applications in frequency-domain system identification, where a system under test is subjected to multiple frequencies simultaneously. We, on the other hand, are interested in a technique that will generate high-quality signals that are easy to reconstruct from the pattern in which they are embedded. Unfortunately, signal generation by pulses suffers from a few deficiencies in our desired application that we must consider. First, for single-tone generation, a selectable high-order filter is required to isolate the desired tone. It must be especially acute at low frequencies. Second, if the environment is such that the binary signal generator cannot vary the amplitude of the pulse train (such as in a fixed 5 V digital system), one has no control over the amplitude of the extracted signal. Third, each tone has a different amplitude — for multitone signal generation, the variance may be intolerable. However, for simple test schemes where the user can manage with some or all of these parameters fixed, this method of analog signal generation may be the most compact.

Fig. 2.4 - Example of a Pulse Waveform and Its Frequency Spectrum

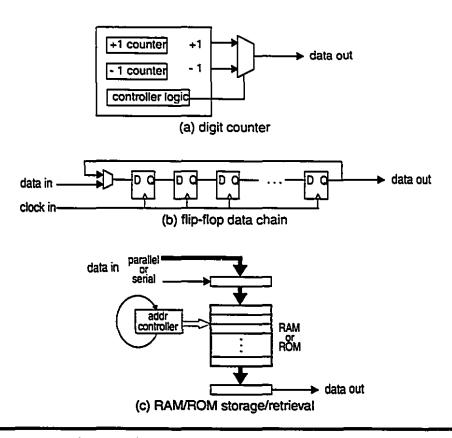

Implementation of the pulse generator can take several forms. One application requires the use of a counter to keep track of the number of ±1s or -1s, as in Fig. 2.5(a). By programming the counter to vary the number of ±1s, the user obtains frequency selectivity, albeit a limited range. The alternative is a pattern storage approach. The first is a simple chain of memory elements such as flip-flops as in Fig. 2.5(b). The pattern is loaded into the chain which is then configured into a loop so that the sequence can repeat itself. Next, the pattern is serially shifted out to generate the pulse train for a filter to select the appropriate tone or collection of tones with which the device under test will be stimulated. Alternatively, one can store and play back the pattern in a RAM as in Fig. 2.5(c). Read and write addresses are generated by a sequential address controller. We will refer to the approach of filling a scan chain or memory with a digital data pattern for analog signal generation as a memory-based generation technique, which could conceivably be used wherever analog signal generation is required. This will be examined more closely in Chapter 4 - Forced-Periodic PDM Patterns.

Fig. 2.5 - Bit Pattern Storage and Retrieval

Note that one could manipulate the bit pattern and add more +1s or -1s in different locations to generate different spectra and vary the power distribution. This is the basis behind multifrequency binary sequence signals and is discussed in the following section.

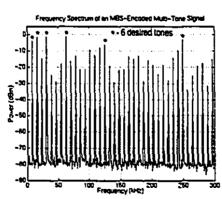

#### 2.2.2 - MBS Generation

An extension of pulse generation is the binary representation of analog signals by multi-frequency binary sequence (MBS) generation, commonly used for multi-frequency test signals. MBS signals are periodic with an even number of bits per period and have a mean value of zero with their energy concentrated in a limited number of harmonics [6].

As an example, consider the case where one desires a signal containing six selected frequencies, one octave apart [7]. Assuming we let the function be even, and that we choose the Fourier series coefficients to all be equal, we arrive at the pattern u(t), where

$$u(t) = \cos\frac{2\pi t}{T} + \cos\frac{2\pi 2t}{T} - \cos\frac{2\pi 4t}{T} + \cos\frac{2\pi 8t}{T} - \cos\frac{2\pi 16t}{T} + \cos\frac{2\pi 32t}{T}.$$

and T is subdivided into N intervals. The binary signal is determined to be  $\pm 1$  depending of the polarity of u(t), or equivalently,  $sgn[u(t)]^1$  evaluated for each interval. For a total of 128 intervals, we find the first half of the even pattern to be:

where the integer preceding the sign is the number of bits of that polarity. For example, 3<sup>+</sup> indicates three consecutive +1 bits. The resulting signal spectrum is given in Fig. 2.6.

For the simplest case (i.e. a single-tone frequency spectrum), consider the signal s(t), where

$$s(t) = \sin\left(\frac{2\pi t}{T}\right).$$

$$sgn(x) = \begin{cases} 1, x > 0 \\ 0, x = 0 \\ -1, x < 0 \end{cases}$$

<sup>1.</sup> Recall that the sgn function has the following definition:

Let N be the number of points over the interval of interest (i.e., one period of the waveform). The sign of the function evaluated at each interval t = k/N, k = 0, 1, 2, ..., N, determines the binary representation via the sgn function. Since the signal is a sine wave, exactly N/2 bits are +1 and N/2 bits are -1. This generates the fundamental tone at I/(NT) Hz, but unfortunately places harmonics at every integer multiple of twice the fundamental. This is illustrated in Fig. 2.7. Here, we encode the sine wave according to the MBS strategy and get the even function coding pattern of  $32^+$   $32^-$ . This creates a 128-bit pattern, which places the fundamental at  $f_t = \frac{1}{128}f_s$ . In Fig. 2.7,  $f_s = 1$  MHz, placing the fundamental at  $f_t = 7.8125$  kHz, and the harmonics at integer multiples of  $2f_t$ , or every 15.625kHz thereafter.

MBS is most often used for the generation of multi-frequency signals. While the opportunity exists for distributing the power over the harmonics of interest [7], optimization techniques must be used to achieve this. Again, unwanted harmonics that fall within the band of interest are generated. One advantage that MBS has over the pulse technique is that since MBS signals are even functions in time, only half of the full pulse train need be stored.

Those deficiencies that exist in the pulse method, however, also exist in MBS. For arbitrary analog signal generation, the amplitude is fixed unless the pulse train amplitude can be varied. Also, there lies difficulty in signal extraction from the bit pattern. Consider the previous example in which a sine wave was generated. From the frequency spectrum, we can see that a filter could extract the fundamental tone to yield a high-quality sine

Fig. 2.6 - Spectrum of an MBS-Encoded 6-Tone Signal

Fig. 2.7 - Spectrum of an MBS-Encoded Sine Wave

wave. Unfortunately, this requires a precise, tunable, high-order lowpass filter in order to remove the harmonics from the passband.

Implementation of the pulse generator and the MBS signal generator would typically be done using memory elements on an IC, such as a chain of flip-flops that would be loaded with the bit pattern and then configured in a loop to repeat itself. Alternatively, a RAM or counter logic (as described in *Section 2.2.1 - Pulse Generation*) could be used.

Ideally, we would like a bit pattern in which we can vary the amplitude of the encoded signal while maintaining a constant pulse train amplitude (e.g., 5 V for a digital IC application). We would also like to have frequency selectivity and be able to remove the harmonic noise from the band of interest so that the analog signal can be easily extracted. We may also want to create sophisticated multi-tone signals. All of this can be accomplished with pulse-density-modulation encoding, the subject of the next section.

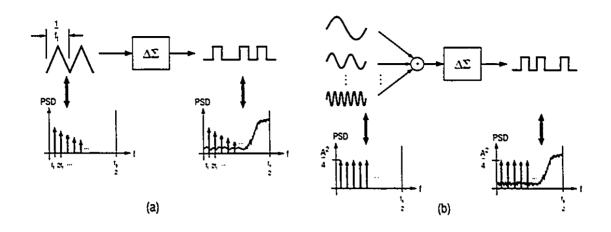

#### 2.2.3 - PDM Signal Generation

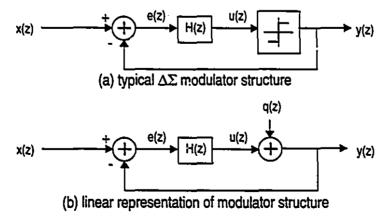

Pulse density modulation is the pattern generator of choice for oversampling D/A and A/D converters using single-bit  $\Delta\Sigma$  modulation [3]. A typical modulator has the structure shown in Fig. 2.8(a), consisting of a summer, a linear filter, and a one-bit quantizer. By modelling the quantizer as an additive white noise source, we can obtain the linear model as in Fig. 2.8(b), and describe the modulator in terms of its signal transfer function (STF) and noise transfer function (NTF) in the z-domain:

$$Y(z) = STF(z)X(z) + NTF(z)Q(z)$$

$$NTF(z) = \frac{1}{1 + H(z)}$$

$$STF(z) = 1 - NTF(z).$$

(2.3)

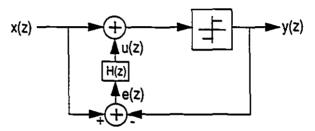

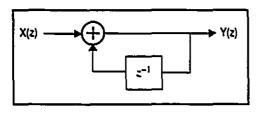

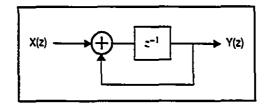

For the modulator to be stable, the NTF must be bounded at all physical frequencies. Stability has been shown to exist for NTF < 2.0 [8]. A modulator can realize any NTF whose numerator and denominator have identical orders and leading coefficients, i.e., for  $NTF(z)|_{z=\infty} = 1$  [9]. It is desirable to have an STF equal to one so that the signal is not attenuated or amplified in any way. Such a modulator has the structure as shown in Fig. 2.9(a).

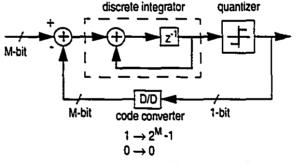

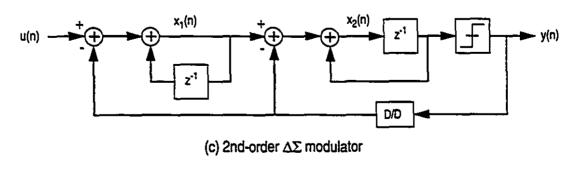

An example of a first-order, single-bit, digital  $\Delta\Sigma$  modulator is given in Fig. 2.9(b). It is made up of a multi-bit summer and integrator, a multi-to-single-bit quantizer block, and a single-to-multi-bit digital-to-digital converter. The integrator consists of a multi-bit summer and a delay element, denoted by its z-domain representation,  $z^{-1}$ . The delay element is simply a data register or bank of flip-flops. The function of the quantizer is to set the output to a logic-1 if its input is greater than a set threshold, and a logic-0 otherwise. The digital-to-digital (D/D) converter performs a code conversion by converting the output signal to a multi-bit signal (either the largest or smallest number in the number system being used), and feeding it back to the modulator input. This introduces an error signal -- the difference between the single-bit output signal and the multi-bit input signal. The output of the modulator is now a single-bit representation of the multi-bit input signal, with the encoded signal embedded in a PDM representation. That

Fig. 2.8 - Typical and Linear Modulator Structures

is, the greater the amplitude of the signal, the more logic-1s used to represent it. Conversely, the smaller the amplitude, the more logic-0s used. Higher order modulators can also be created, such as the second-order design shown in Fig. 2.9(c). These better approximate the error signal fed back to the modulator input and, as a result, decrease the amount of inband error noise.

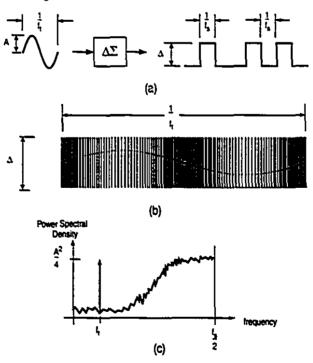

Figure 2.10(a) illustrates the conversion of a sinusoidal input signal into a PDM bit pattern. The input sinusoid has an amplitude of A and a frequency  $f_t$  that has been greatly oversampled (i.e.,  $f_s >> f_t$ ). The output signal of amplitude  $\Delta$ , provided in Fig. 2.10(b),

(a) unity STF  $\Delta\Sigma$  modulator structure

(b) quantized 1st-order  $\Delta\Sigma$  modulator

Fig. 2.9 - First- and Second-Order Modulator Structures

shows the digital pattern that represents the input sinusoid by the density of logic-1s and 0s. It is important to note that the  $\Delta\Sigma$  modulator is based on an infinite-impulse response system which maps the input signal to an infinitely-long series of bits. Thus, the pattern does not repeat itself [3]. Another characteristic of the  $\Delta\Sigma$  modulator is fact that the quantization noise is orthogonal to the input signal and thereby occupies a different frequency region. In the case of a lowpass modulator, the majority of the noise occurs at higher frequencies. This characteristic is known as "noise shaping". A typical power spectral density (PSD) plot of the output is given in Fig. 2.10(c).

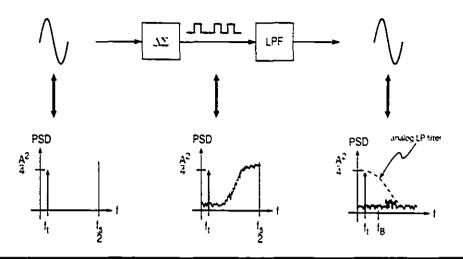

Since quantization noise is orthogonal to the inband tones, signal extraction from the digital pattern is very easy. For a lowpass modulator, such as in the previous example, one simply passes the data pattern through a lowpass filter with a cutoff frequency  $f_B$ , as shown in Fig. 2.11. Note that the order of the modulator dictates the noise shape, i.e. the rate at which the noise increases out-of-band. This places the requirement that the filter be of at least the same order (preferably greater) to completely filter the out-of-band noise. However, it cannot remove the in-band noise as this noise cannot be removed from the signal by simple filtering.

Fig. 2.10 - Modulator-Based Encoding of a Sinusoid

Fig. 2.11 - Analog Signal Recovery

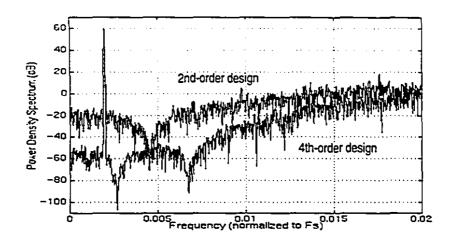

The in-band noise can be reduced by using a higher-order modulator which better approximates the quantization error and thus results in a lower in-band noise floor. This is exemplified in Fig. 2.12. Note how the power density spectrum of the second-order lowpass modulator has a higher noise floor in the passband versus the fourth-order modulator. The simulation of a fourth-order design yielded a 30 dB increase in dynamic range to 110 dB. Another alternative for reducing the noise component is to increase the oversampling ratio (OSR), defined as  $\frac{f_s/2}{f_B}$ , where  $f_s$  is the sampling frequency and  $f_B$  is the modulator bandwidth. For a second-order design, the signal-to-noise ratio in decibels as a function of the OSR can be expressed as:

$$SNR = 15\log_2 OSR + 6\log_2 \left(\frac{A}{\Delta}\right) - 8. \tag{2.4}$$

The above equation suggests that the higher the OSR, the closer the conversion is to ideal.

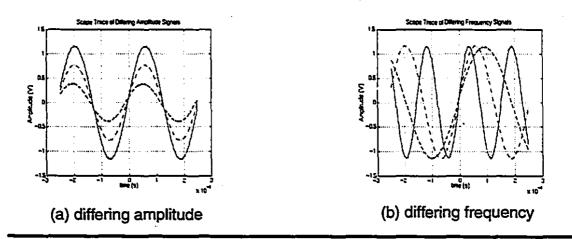

Perhaps the most powerful property of PDM encoding is that signal amplitude and frequency are completely programmable and can be recovered with a fixed-bandwidth filter. That is, we can place a signal (or group of signals) anywhere within the passband and recover it with a fixed filter tuned to the bandedge; it is not necessary for the filter to track the signal. This is demonstrated experimentally in Fig. 2.13. Here we show reconstructed signals of differing amplitude (a) and differing frequency (b), all generated within a 10 kHz passband region.

Fig. 2.12 - Second- and Fourth-Order Modulator Inband Power Spectra

PDM has the advantage of being able to encode other types of waveforms, such as multitone and triangular signals via  $\Delta\Sigma$  modulation as illustrated in Figs. 2.14(a) and (b). It is important to ensure that the modulator bandwidth is sufficiently wide to include all of their harmonics, since these signals have significant power at higher-frequencies. However, since the quantization noise power increases with frequency, a fundamental trade-off exists between signal purity and noise [10].

The versatility of  $\Delta\Sigma$  modulators makes them the preferred analog signal encoding scheme of the author for many reasons. First, the user has amplitude and frequency selectivity of the signal to be encoded. Second, the noise-shaping characteristic ensures that only the

Fig. 2.13 - Amplitude and Frequency Variability Over a Fixed Bandwidth

Fig. 2.14 - Encoding Other Types of Analog Signals

signal tone(s) exists in the passband region (plus, of course, a minimal amount of quantization noise). Third,  $\Delta\Sigma$  modulators permit the encoding of virtually any waveform into a single-bit pattern. And finally, signal reconstruction is achieved simply by using a filter of a fixed bandwidth, unlike that required by the pulse and MBS signal generation methods. In the following section, we will focus on a primary use of the  $\Delta\Sigma$  modulator—the  $\Delta\Sigma$  oscillator.

# 2.3 - Delta-Sigma Oscillator

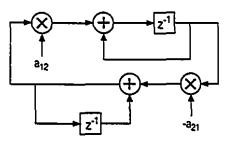

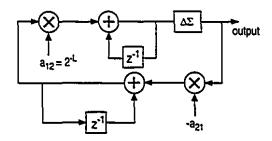

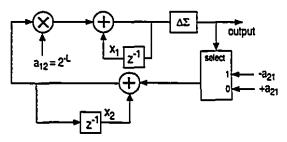

Previous work on analog oscillators introduced the concept of using  $\Delta\Sigma$  modulators in digital resonator circuits [1] and can be summarized with the following example. Figure 2.15(a) shows a second-order digital resonator circuit made up of two integrators in a loop, with a characteristic equation given by:

$$z^{2} + (a_{12}a_{21} - 2)z + 1 = 0. (2.5)$$

With some flow graph manipulation and the introduction of a  $\Delta\Sigma$  modulator, we arrive at the circuit shown in Fig. 2.15(b). Keeping in mind that we wish to fabricate this design on a monolithic IC, it is desirable to keep the hardware complexity to a minimum (and also minimize logic area). Logic subject to minimization is the multipliers. By forcing the coefficient  $a_{12}$  to be a power of two, we can remove the first multiplier, as a power-of-two

multiplication is simply a wire-mapping in hardware. Next, realizing that the output of the modulator is either a logic-1 or 0, the second multiplier can be simplified to a two-input multiplexer which chooses between either  $-a_{21}$  or  $+a_{21}$ . The end result is the minimized circuit shown in Fig. 2.15(c).

The memory elements in each integrator set the initial conditions of the resonator (denoted  $x_1$  and  $x_2$  in Fig. 2.15(c)). These, combined with coefficient  $a_{21}$  (which we will subsequently refer to as the loop coefficient k), create the variables that allow for very accurate frequency and amplitude tuning. The frequency of oscillation f, and the amplitude A, of the encoded signal are related to the loop coefficient and the initial register conditions by the following set of expressions:

$$k = 2(1 - \cos 2\pi f)$$

$$x_2(0) = A$$

$$x_1(0) = \frac{k}{2}x_2(0)$$

(2.6)

The  $\Delta\Sigma$  oscillator has several advantages with the main ones discussed next.

(a) 2nd-order digital resonator circuit

(b) resonator with  $\Delta\Sigma$  modulator and power of 2 multiplier

(c) multiplierless  $\Delta\Sigma$  modulation oscillator

Fig. 2.15 - Design of a Multiplierless Delta-Sigma Oscillator

Signal generation logic is self-contained.

That is, all logic and frequency selectability can be built into a single resonator- $\Delta\Sigma$  modulator structure. This lends itself to IC fabrication, most likely on a single die. With programmable registers, arbitrary signal frequencies (within the predetermined passband) and amplitudes can be generated. Thus the need for external, off-chip signal generation equipment is eliminated.

The PDM stream is repeatable.

Since the start-up states of each integrator in the oscillator design are known, the bit pattern is completely deterministic. With the same initial conditions, the output stream can therefore be reproduced.

However, the oscillator, having many predetermined attributes such as order, bandwidth, and the number of simultaneous tones, suffers from the following disadvantages:

Signal quality and bandwidth are fixed.

The bandwidth of the passband and the dynamic range of the generated signal are functions of the order of the modulator and its coefficients, and thus are determined beforehand. As a result, one must carefully select the desired order and modulator characteristics for a desired SNR during the design phase of the oscillator.

Higher-order structures require large increases in area.

Generally, a desired increase in bandwidth or SNR requires an increase in the order of the oscillator. Frequency selectivity also necessitates an increase in register length (data bus width) to minimize the effect truncation noise has in increasing the signal noise floor. In addition, the generation of multiple tones or complex waveforms require and bandwidth extension at the expense of SNR and more logic. As order (and hence area) increases, the feasibility of oscillators for MADBIST applications decrease i.e., the MADBIST overhead is no longer a negligible amount.

It is difficult to ensure stability for a given modulator design.

As one attempts to maximize the SNR for a given order or modulator structure, the potential for instability (i.e. an overflow condition) increases. One limiting factor is the amplitude of the encoded signal. In general, the amplitude is kept low to ensure stability. Presently, there is no easy way to guarantee stability other than through very long simulations or bench-testing.

The coefficients (initial conditions and loop coefficient) must be kept small for a high OSR.

The fact that the coefficients must be small in our number system requires the use of larger bus widths to minimize the effect of truncation noise, since we are using fixed-point arithmetic.

Despite these deficiencies, the  $\Delta\Sigma$  oscillator has some very practical applications. Research in the area of  $\Delta\Sigma$  modulators by Haurie and Roberts has revealed an area-efficient, multiplier-free structure for arbitrary-order modulators [9]. This design algorithm has been conveniently packaged in a software application written in Matlab, called DSMOD [10]. One advantage of the software is the ability to generate  $\Delta\Sigma$  oscillators using an area-efficient structure, as introduced in [11]. This software has proved to be a very useful  $\Delta\Sigma$  modulator and oscillator design tool. Two applications using the  $\Delta\Sigma$  oscillator will be discussed in detail in the following chapter.

# Chapter 3 - Applications of the Delta-Sigma Oscillator

This section highlights applications utilizing the  $\Delta\Sigma$  oscillator. The MADBIST proposal introduced in Section 2.1 - The MADBIST Method of IC Self-Test covers one such application in detail and will not be covered here. Instead we will focus on applications in which logic area is not a constraint -- that is, where a single IC or significant portion of an IC is dedicated to the oscillator.

This chapter will introduce the dedicated test system, which is directed at the analog tester market. High precision analog testers have a purchase price in the vicinity of \$1 million. In contrast, digital testers cost approximately \$100,000. With the proposed dedicated test system (that could be mass-produced for say, \$20), the test engineer can equip the digital tester to perform functions normally reserved for the analog test unit. We will examine a dedicated test system for use either as an on-board unit or as a retrofit for a digital tester.

The following sections will also introduce two oscillator ASICs, fabricated in the Nortel 0.8 $\mu$  BiCMOS fabrication process. The first is an all digital, fourth-order lowpass  $\Delta\Sigma$  oscillator. The second consists of the same oscillator, a one-bit DAC, and a sixth-order lowpass reconstruction filter to form a complete analog signal generation unit.

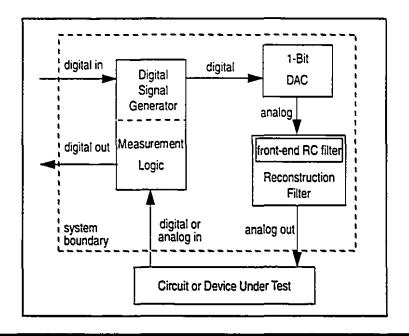

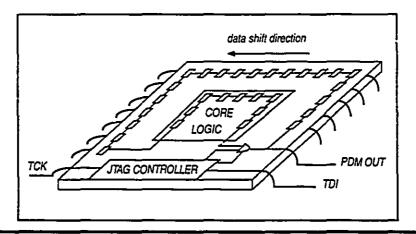

### 3.1 - The Dedicated Test System

One application for the  $\Delta\Sigma$  oscillator in the context of analog signal testing is in a test system consisting of one or more dedicated ICs to perform the signal generation and data collection functions. An example of such a system is shown in Fig. 3.1. Although represented in the context of a board system, the entire system can be fabricated on a

Fig. 3.1 - Block Diagram of a Test System

single die, yielding a single test-chip retrofitting solution. The operation of the test system is described below.

The test system can be designed with either a memory- or oscillator-based signal generation approach or conceivably both. First, a digital controller, typically a processor or a digital test head, communicates with the signal generator to either load a serial bit pattern (in the memory-based configuration) or the initial conditions necessary for an oscillator to generate a test signal. That resulting serial output is then fed into a one-bit DAC.

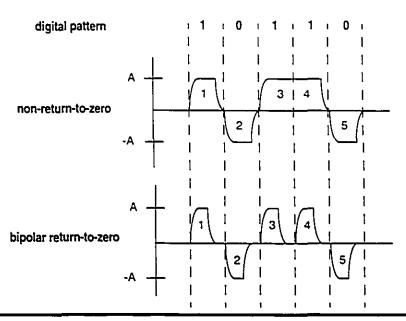

The purpose of the DAC is twofold. First, the DAC can clean up the edges of the digital input signal, providing a signal with sharper level transitions. Second, the DAC can change the coding of the digital signal from its typical 0 to 5V non-return-to-zero scheme to one that has better characteristics. Using a bipolar, return-to-zero bit coding pattern reduces distortion by equalizing rise and fall times. For example, to reconstruct a high-quality analog signal, it is critical that the rise and fall shape of the digital signal be as similar as possible i.e., the area under each pulse is identical. Figure 3.2 illutrates this in detail. Note that pulse 1 does not have the same area as pulse 3, since pulse 3 is followed

Fig. 3.2 - Bipolar Non-Return-to-Zero and Return-to-Zero Coding Schemes

by another pulse of the same polarity. As a result, pulse 3 does not need to discharge towards zero. This gives the appearance that pulse 4 has a zero-time rising edge. A bipolar return-to-zero coding pattern forces each pulse, regardless of polarity, to return to zero halfway through the period of the pulse. This ensures each pulse has one rising and one falling edge, minimizing the area differences. A bipolar coding scheme also removes the DC bias associated with 0-5 V coding, as the average will be zero (assuming an equal number of logic-1 and 0s<sup>1</sup>). The DAC can also provide a high output impedance for the reconstruction filter. This minimizes the loading placed on the filter by the output stage of the previous circuit.

The next stage is the reconstruction filter. This filter is generally a lowpass<sup>2</sup> structure that has its cutoff frequency at the bandedge of the frequency spectrum of interest. It is this filtering action that extracts the analog signal from the digital bit stream. The output of the filter is the reconstructed analog signal that is then sent to the analog device under test (DUT). As the out-of-band noise from a  $\Delta\Sigma$  modulator will increase at a rate that is

<sup>1.</sup> Recall that in a  $\pm 1$  bipolar coding scheme, a logic-0 is coded as -1.

<sup>2.</sup> Note that with just a change of filter, the system could make use of  $\Delta\Sigma$  bandpass signals. This would prove effective in high-frequency testing such as in wireless applications. See [12] for further details.

proportional to the order of the modulator, it is advisable to make the filter at least one order above the maximum order of the modulator used. This will minimize the amount of noise that accompanies the signal.

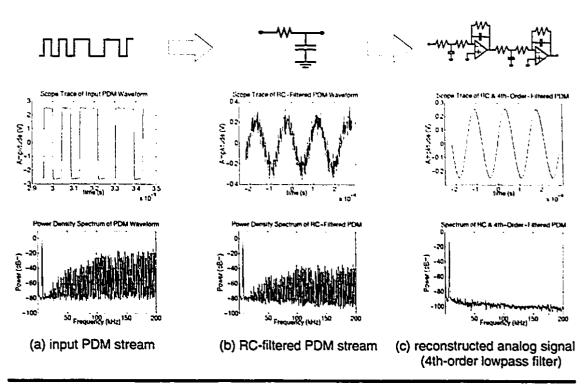

If the reconstruction filter cannot handle the rail-to-rail swing from the DAC, then a simple fixed-bandwidth filter structure can be used to reduce the signal input amplitude (as introduced in Section 2.1 - The MADBIST Method of IC Self-Test). Note that this filtering circuit should be part of the design constraints for the front end of the reconstruction filter and used regardless of the mode of operation (normal or test mode). Alternatively, a simple passive RC structure could be used if BIST were added to an existing design. This significantly reduces the output amplitude and relaxes the steep slope of the digital signal to an input level which the filter could easily handle. An experimental demonstration of signal reduction possible with use of an RC filter is provided in Fig. 3.3.

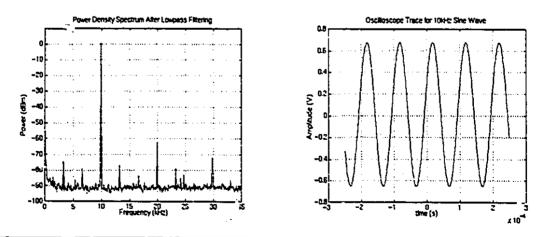

Using a 7 kHz PDM bit pattern from a third-order modulator with a bandedge of 18 kHz, a ±2.5 V signal PDM bit pattern (and its frequency spectrum) is generated as shown in Fig. 3.3(a). The input is then fed into a first-order RC circuit with a cutoff frequency of 18.8 kHz. The waveform in the time and frequency domains is given in Fig. 3.3(b). Note the substantially-reduced signal waveform from a 5 V swing to approximately a 0.7 V swing as well as a noticeable attenuation of higher-order frequencies in the spectrum plot. To complete the signal reconstruction, the output of the RC filter is fed into a fourth-order lowpass filter with a cutoff frequency of 18 kHz. Figure 3.3(c) shows the end result: a reconstructed sine wave with a 0.25 V amplitude and a dynamic range of approximately 75 dB.

The final component of the dedicated test system is the measurement logic. It is designed to receive either a digital or analog input and characterize the performance of the DUT through a quantitative measurement. Such functions may include a Fast Fourier transform (FFT) or narrow-band filter [2]. It is anticipated that further research in the area will lead to simple and compact data measurement schemes.

Fig. 3.3 - Use of an RC Filter To Reduce Input Signal Amplitude

Up until now, we have only considered the type of signal being generated. However, we need to understand the requirements of the input device we are stimulating. That is, we must decide whether we require a voltage or current signal source. We will show in the following section how a PDM output can be configured for either mode of operation.

# 3.2 - Voltage and Current Signal Generation