# **Accelerating Jitter and BER Qualifications of High Speed Serial Communication Interfaces**

Yongquan Fan

## Department of Electrical and Computer Engineering McGill University, Montreal

February 2010

A Thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

© Yongquan Fan, 2010

#### **Abstract**

High-Speed Serial Interface (HSSI) devices have witnessed an increased use in communications. As a measure of how often bit errors happen, Bit Error Rate (BER) performance is of paramount importance in any communication interface. The bit errors in HSSIs are in large part due to jitter. This thesis investigates the topic of accelerating the jitter and BER testing and characterization [1].

The thesis first proposes a new algorithm, suitable for extrapolating the receiver jitter tolerance performance from higher BER regions down to the  $10^{-12}$  level or lower [2]. This algorithm enables us to perform the jitter tolerance characterization and production test more than 1000 times faster [3]. Then an under-sampling based transmitter test scheme is presented. The scheme can accurately extract the transmitter jitter and finish the whole transmitter test within 100ms [4] while the test usually takes seconds. All the receiver and transmitter testing schemes have been successfully used on Automatic Test Equipment (ATE) to qualify millions of HSSIs with speed up to 6 Gigabits per second (Gbps).

The thesis also presents an external loopback-based testing scheme, where a novel jitter injection technique is proposed using the state-of-the-art phase delay lines. The scheme can be applied to test HSSIs with data rate up to 12.5 Gbps. It is also suitable for multilane HSSI testing with a lower cost than pure ATE solutions. By using high-speed relays, we combine the proposed ATE based approaches and the loopback approach along with an FPGA-based BER tester to provide a more versatile scheme for HSSI post-silicon validation, testing and debugging [5]. In addition, we further explore the unparallel advantages of our digital Gaussian noise generator in low BER evaluation [6].

#### Résumé

Les interfaces sérielles à haute vitesse (interfaces HSSI) ont connu une utilisation accrue dans les télécommunications. Le taux d'erreur sur les bits (BER), mesure de la fréquence des erreurs, est d'une importance cruciale dans les interfaces modernes de télécommunication. Cette thèse traite de l'accélération de la caractérisation du vacillement et des tests BER.

Cette thèse propose tout d'abord un nouvel algorithme, approprié pour l'extrapolation de la performance de la tolérance au vacillement d'un récepteur pour un taux d'erreur sur les bits (BER) à un niveau de 10<sup>-12</sup> ou moins. Cet algorithme permet de caractériser la tolérance au vacillement dans les tests de production plus de 1000 fois plus rapidement. Ensuite, une conception de transmetteur à sous-échantillonnage est présenté. Cette conception permet d'extraire précisément le vacillement du transmetteur et de compléter les tests de ce dernier en moins de 100 ms alors que ces tests durent normalement plusieurs secondes. Toutes les méthodes de test de récepteurs et de transmetteurs ont été utilisées avec succès sur un équipement d'éssai automatique (ATE) pour qualifier des millions d'interfaces HSSI à des vitesses allant jusqu'à 6 gigabits par seconde (6 Gbps).

Cette thèse présente aussi une conception de test en bouclage où une nouvelle méthode d'injection de vacillement est proposée en utilisant des lignes de délai de phase. Cette méthode peut être appliquée pour tester des interfaces HSSI avec un taux de transfer allant jusqu'à 12.5 Gbps. Elle permet aussi de tester des interface HSSI multi-lignes à un coût moindre qu'une solution utilisant un ATE. En utilisant des relais à haute vitesse, les approches sur ATE et par test en bouclage peuvent être combinées en incorporant un testeur de BER sur circuit intégré prédiffusé programmable (FPGA), ce qui permet une méthode de tests HSSI polyvalente pour la validation post-fabrication, les tests et le

débogage. Finalement, nous explorons les avantages de notre générateur de bruit Gaussien dans l'évaluation de BER à bas niveau.

### Acknowledgments

First and foremost, I would like to thank my supervisor, Professor Zeljko Zilic. His guidance, encouragement and support throughout the research are greatly appreciated. He is highly insightful in directing the academic research to solve current challenges in the industry. His guidance and help in preparing my thesis, papers and presentations are especially appreciated. I am truly fortunate to have such an excellent supervisor.

I also would like to thank my former co-supervisor, Dr. Yi Cai, for his support in the research. As a renowned expert in high-speed testing, he provided me with invaluable guidance and support in establishing research topics and publishing two papers. My thanks also go to Liming Fang, Anant Verma, Bill Burcanowski, and Sandeep Kumar for co-authoring one paper. I also appreciate the technical support and help from the whole PHY and Storage team at Agere/LSI, especially from Angshu Bhattacharyya, Joe Martone, John Janney, Suri Basharapandiyan, Bernhard Lanchiski, Tom Gibson, Kahn Neguen, Bob Hein and Ken Paist.

In addition, I thank the many people who have given me valuable advice and feedback at conferences and various occasions. Special thanks are extended to Gordon Roberts and Warren Gross at McGill University, Mohamed Hafed at DFT Microsystems, Yang Liang at Maxim, Steve Sunter at Logic Vision, Mike Li at Wavecrest and Xu Fang at Teradyne. Also, I would like to thank students in the MACS lab who have helped me with the research. In particular, I thank Jean-Samuel Chenard for translating the thesis abstract into French.

Last but not least, I would like to thank my whole family, especially my wife Ji Lei, for their love and support over the years.

### **Table of Contents**

| Abstract                              | i    |

|---------------------------------------|------|

| Résumé                                | ii   |

| Acknowledgments                       | iv   |

| Table of Contents                     | V    |

| List of Figures                       | ix   |

| List of Tables                        | xiii |

| List of Acronyms                      | xiv  |

| Chapter 1 - Introduction              |      |

| 1.1 Motivation                        |      |

| 1.1.1 HSSI Technology Trends          | 3    |

| 1.1.2 Qualification Challenges        |      |

| 1.1.3 ATE Perspectives                | 7    |

| 1.2 Contributions                     | 9    |

| 1.3 Overview of the Thesis            | 11   |

| Chapter 2 - Background                | 12   |

| 2.1. High-Speed Serial Communication  | 12   |

| 2.1.1 HSSI Structure                  | 16   |

| 2.1.2 CDR Characteristics             | 17   |

| 2.1.3 BER Mechanisms                  | 23   |

| 2.1.4 Jitter and Noise Impacts to BER | 27   |

| 2.2 Timing Jitter                     | 29   |

| 2.2.1 Jitter Overview                 | 29   |

| 2.2.2 Litter and RER                  | 31   |

| 2.2.3 Jitter Testing and Jitter Injection                     | 34      |

|---------------------------------------------------------------|---------|

| 2.3 Amplitude Noise                                           | 37      |

| 2.3.1 BER and SNR                                             | 38      |

| 2.3.2 Simulation and Emulation                                | 43      |

| 2.3.3 AWGN Emulation                                          | 45      |

| Chapter 3 – Accelerating Receiver Jitter Tolerance Testing of | n ATE49 |

| 3.1 Introduction.                                             | 49      |

| 3.1.1 Jitter Tolerance Testing                                | 49      |

| 3.1.2 Proposed New Method                                     | 51      |

| 3.2 Jitter Test Signal Generation                             | 56      |

| 3.2.1 Choosing Test Signal Parameters                         | 57      |

| 3.2.2 Periodic Jitter Injection                               | 60      |

| 3.2.2.1 Creating Jitter-Free Data Signal.                     | 60      |

| 3.2.2.2 Creating a Digitized Jitter Signal                    | 61      |

| 3.2.2.3 Modulating the Data Signal                            | 62      |

| 3.2.2.4 Generating Bandwidth Limited Signals                  | 63      |

| 3.2.2.5 Downsampling to Get AWG Samples                       | 65      |

| 3.2.3 Fractional Sampling                                     | 66      |

| 3.2.4 Jitter Calibration                                      | 67      |

| 3.2.5 Random Jitter Control                                   | 71      |

| 3.3 Receiver Bit Error Monitoring                             | 72      |

| 3.3.1 ATE-based Error Detection                               | 72      |

| 3.3.2 DFT-based Error Detection                               | 74      |

| 3.4 Jitter Tolerance Extrapolation.                           | 76      |

| 3.4.1 Jitter Tolerance Extrapolation Algorithm                | 76      |

| 3.4.2 Accelerating Jitter Tolerance Characterization          | 80      |

| 3.4.3 Accelerating Jitter Tolerance Compliance Testing        | 86      |

| 3.4.4 Discussions                                             | 88      |

| Chapter 4 – Transmitter Jitter Extraction on ATE              | 90      |

| 4.1 Introduction                                              |         |

| 4.1.1 Transmitter Jitter Testing Overview                 | 90  |

|-----------------------------------------------------------|-----|

| 4.1.2 Proposed Solution                                   | 92  |

| 4.2. Test Setup for Data Acquisition                      | 93  |

| 4.2.1 Overview of the Test Setup                          | 93  |

| 4.2.2 Principles of Clock Settings                        | 94  |

| 4.2.3 Test Setting Parameter Calculations                 | 97  |

| 4.3. Jitter Extraction                                    | 101 |

| 4.3.1 Generating Edge Displacement                        | 101 |

| 4.3.2 Time Domain Approach                                | 104 |

| 4.3.2.1 RJ Extraction                                     | 105 |

| 4.3.2.2 DJ Extraction                                     | 106 |

| 4.3.2.4 TJ Calculation                                    | 107 |

| 4.3.3 Frequency Domain Approach                           | 110 |

| 4.3.3.1 RJ Extraction                                     | 110 |

| 4.3.3.2 DJ Extraction                                     | 112 |

| 4.3.4 Hybrid Approach                                     | 113 |

| 4.3.5 Limitations of Each Approach                        | 115 |

| 4.4 Experimental Results                                  | 116 |

| 4.4.1 Bench Correlation                                   | 116 |

| 4.4.2 Correlating Two RJ Approaches                       | 117 |

| 4.4.3 Impact of Test Patterns                             | 119 |

| 4.4.4 Impact of the Reference Clock                       | 120 |

| 4.4.5 Extending to 6 Gbps Applications                    | 122 |

| 4.5 Summary                                               | 123 |

| Chapter 5 – Testing HSSIs with or without ATE Instruments | 125 |

| 5.1 FPGA-based Bit Error Detection                        | 126 |

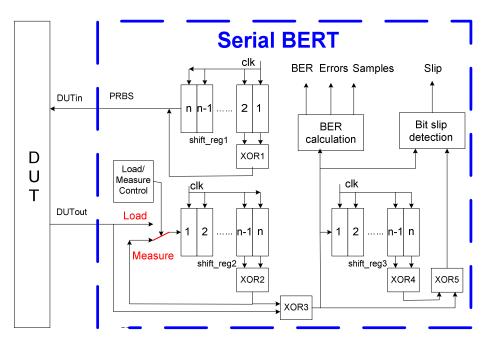

| 5.1.1 Implementing a Serial BERT                          | 127 |

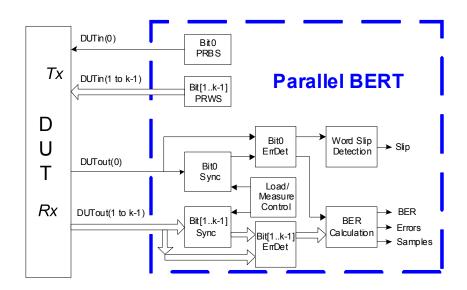

| 5.1.2 Implementing a Parallel BERT                        |     |

| 5.1.3. HSSI Testing Demonstration                         |     |

| 5.2 Loopback Testing with Jitter Injection                | 131 |

| 5.2.1 Testing Setup                                   | 131 |

|-------------------------------------------------------|-----|

| 5.2.2 Phase Delay Based jitter Injection              | 133 |

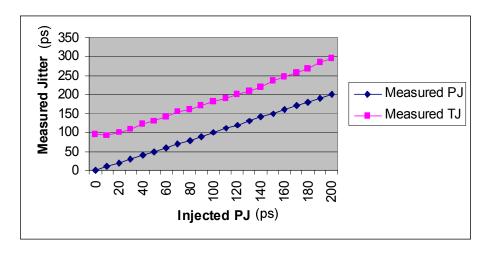

| 5.2.3 Experimental Results                            | 136 |

| 5.3 A Versatile HSSI Testing Scheme                   | 139 |

| 5.3.1 Major Functions of our Setup                    | 140 |

| 5.3.2 High Speed Relays                               | 143 |

| 5.3.3 Limitations and Further Considerations          | 148 |

| 5.4 BER Testing Under Noise                           | 149 |

| 5.4.1 Our AWGN Generator                              | 150 |

| 5.4.1.1 Hardware Implementation                       | 150 |

| 5.4.1.2 Statistical Properties                        | 152 |

| 5.4.2 BER Testing Demonstration                       | 154 |

| 5.4.3 Advantages of Our AWGN Generator                | 158 |

| Chapter 6 – Conclusions and Future Work               | 161 |

| 6.1 Conclusions                                       | 161 |

| 6.2 Future Investigations                             | 163 |

| 6.2.1 PLL and CDR Characteristics Analysis            | 163 |

| 6.2.2 Further Phase Delay Line Performance Evaluation | 166 |

| 6.2.3 AWGN Generator Implementation                   | 167 |

| References                                            | 168 |

### **List of Figures**

| Figure 1-1: HSSIs in communication infrastructure                              | 3  |

|--------------------------------------------------------------------------------|----|

| Figure 1-2: High speed serial interface technology trend                       | 8  |

| Figure 2-1: CDR transmission mechanism                                         | 12 |

| Figure 2-2: Applications of multiple HSSIs                                     | 13 |

| Figure 2-3: Current-mode LVDS driver                                           | 14 |

| Figure 2-4: Block diagram of an HSSI                                           | 16 |

| Figure 2-5: Block diagram of the CDR with a typical linear PLL                 | 18 |

| Figure 2-6: Phase transfer characteristics of the PLL                          | 19 |

| Figure 2-7: Jitter transfer function of the receiver                           | 19 |

| Figure 2-8: BBPD PLL sampling                                                  | 20 |

| Figure 2-9: First order model of a BBPD PLL                                    | 21 |

| Figure 2-10: Graph of the binomial distribution ( $n = 10^8$ , $p = 10^{-7}$ ) | 25 |

| Figure 2-11: Test time vs. BER confidence level                                | 27 |

| Figure 2-12: Ideal digital signal                                              | 28 |

| Figure 2-13: Timing and amplitude deviations in an actual data signal          | 28 |

| Figure 2-14: Jitter components                                                 | 30 |

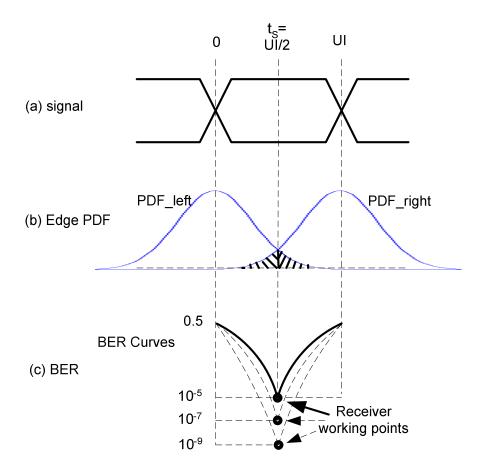

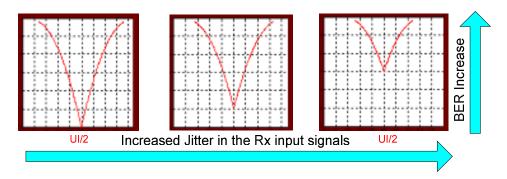

| Figure 2-15: Jitter and BER in the receiver                                    | 32 |

| Figure 2-16: AWGN channel model                                                | 38 |

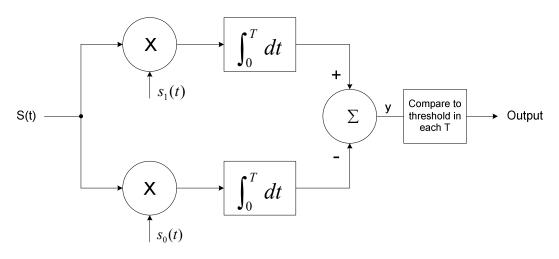

| Figure 2-17: Binary matched filter receiver                                    | 39 |

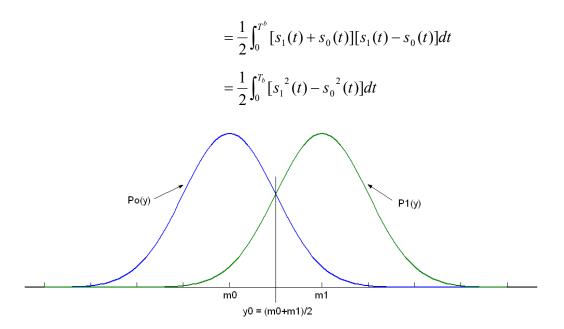

| Figure 2-18: Probability densities of <i>y</i>                                 | 41 |

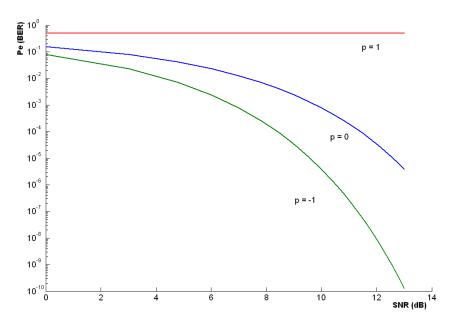

| Figure 2-19: BER vs. SNR for baseband transmission                             | 43 |

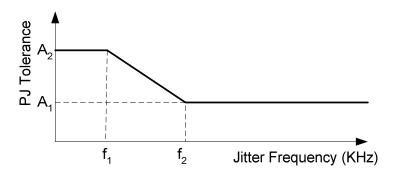

| Figure 3-1: Jitter tolerance specifications                                    | 50 |

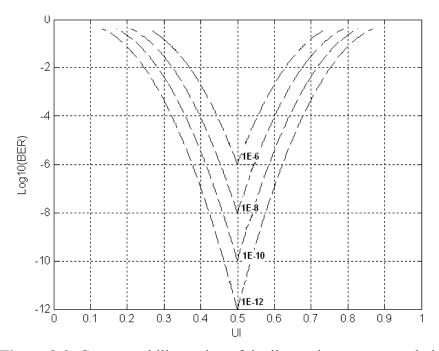

| Figure 3-2: Conceptual illustration of the jitter tolerance extrapolation      | 51 |

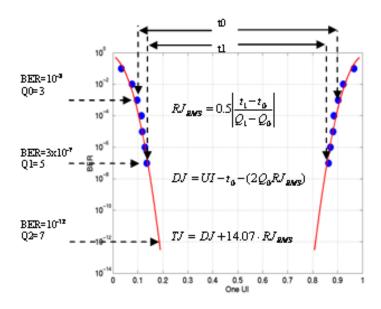

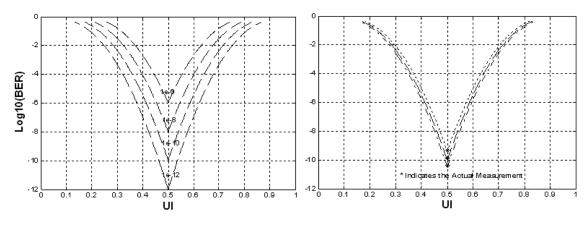

| Figure 3-3: Transmitter BER scan                                               | 52 |

| Figure 3-4: Receiver BER scan                                                  | 54 |

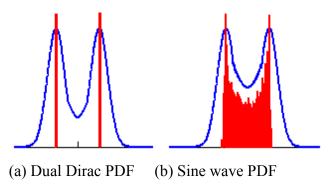

| Figure 3-5: Jitter PDFs for curve fitting                                    | 55  |

|------------------------------------------------------------------------------|-----|

| Figure 3-6: Test setup for jitter tolerance testing                          | 55  |

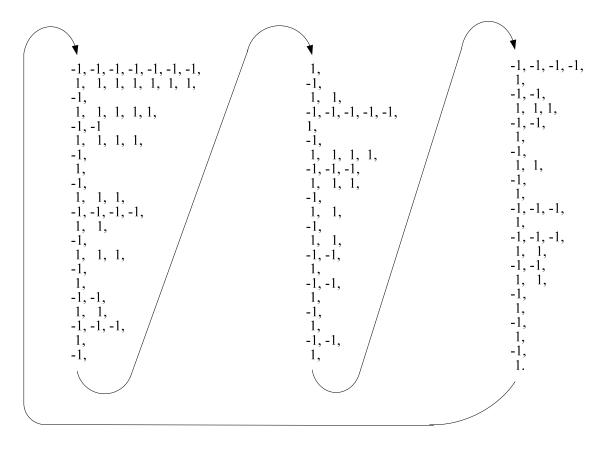

| Figure 3-7: The 128-PRBS sequence                                            | 58  |

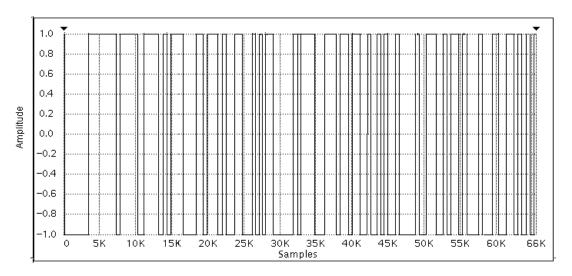

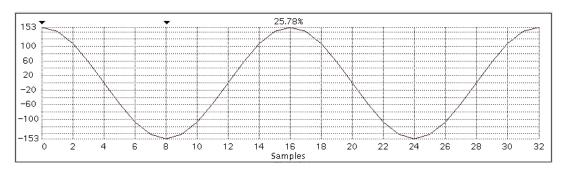

| Figure 3-8: Oversampled jitter-free data signal                              | 61  |

| Figure 3-9: Jitter signal and modulated data signal                          | 63  |

| Figure 3-10: Adding edge transition time                                     | 64  |

| Figure 3-11: Frequency spectrum of the oversampled data signal               | 64  |

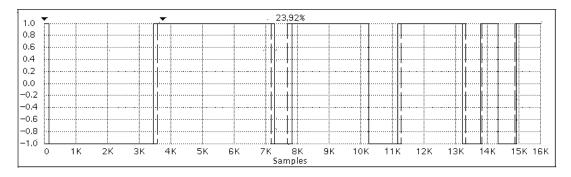

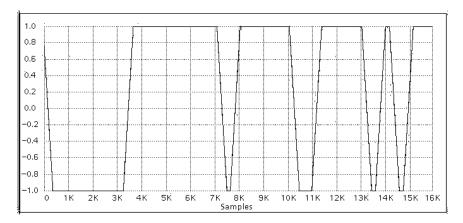

| Figure 3-12: Time domain data after the inverse FFT                          | 65  |

| Figure 3-13: AWG waveform – data after under-sampling                        | 65  |

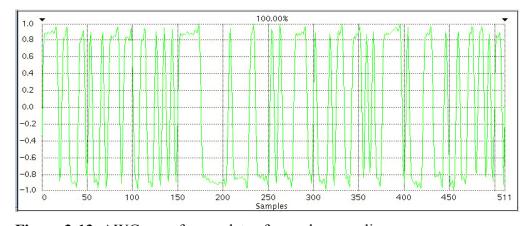

| Figure 3-14: The eye diagram of the AWG samples with 300ps PJ injected       | 68  |

| Figure 3-15: Test setup for jitter calibration on ATE                        | 69  |

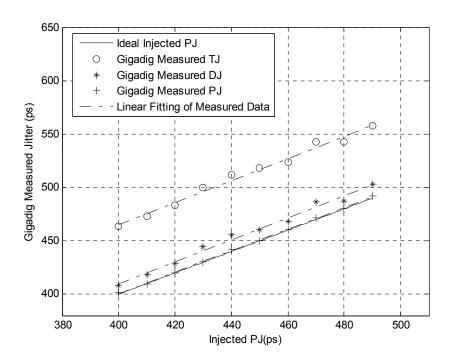

| Figure 3-16: Jitter injection calibration curves with the digitizer          | 70  |

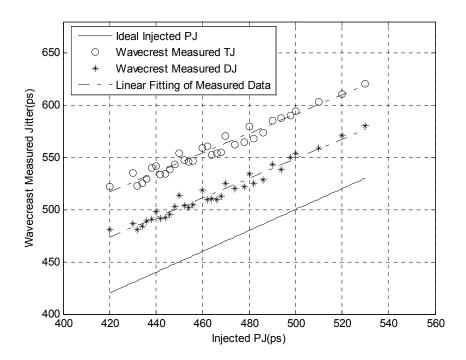

| Figure 3-17: Jitter injection calibration curves with Wavecrest SIA-3000     | 70  |

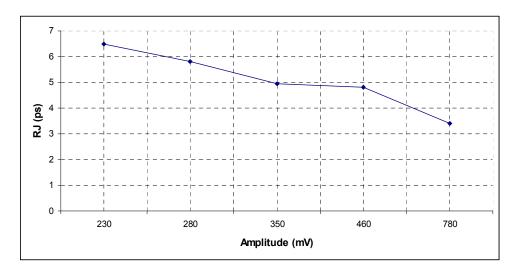

| Figure 3-18: RJ vs. AWG output amplitude                                     | 71  |

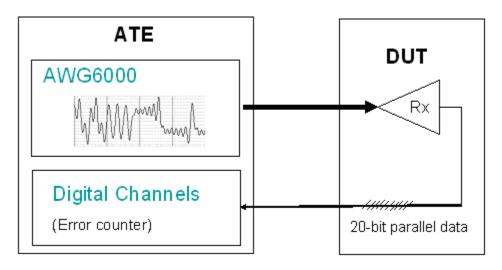

| Figure 3-19: ATE-based BERT                                                  | 73  |

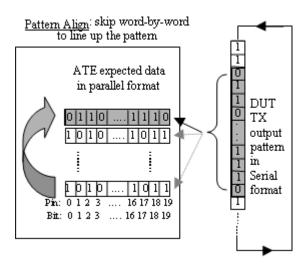

| Figure 3-20: Pattern alignment between the serial data and the parallel data | 74  |

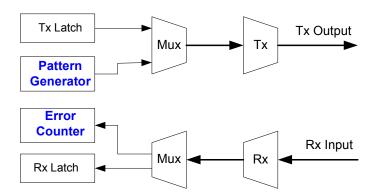

| Figure 3-21: Conceptual illustration of the DFT-based BERT                   | 75  |

| Figure 3-22: Overview of the jitter tolerance extrapolation                  | 76  |

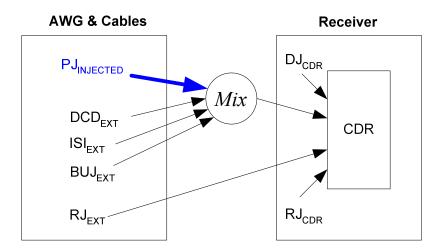

| Figure 3-23: Jitter sources to the CDR                                       | 77  |

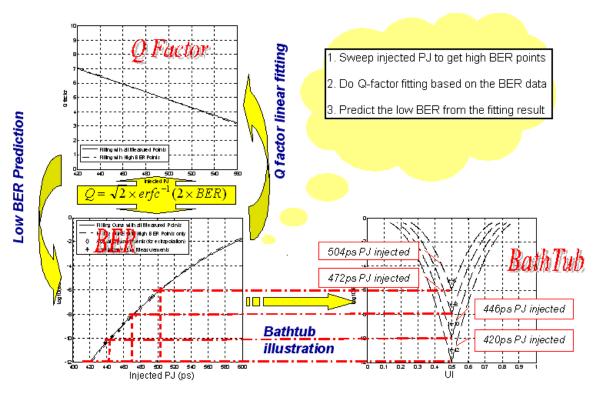

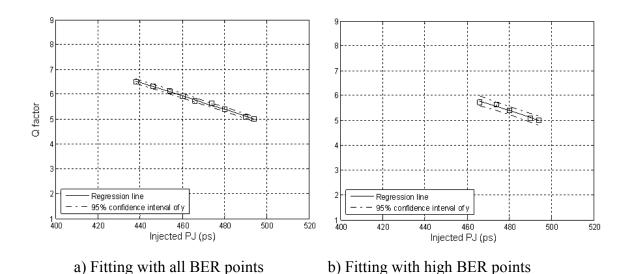

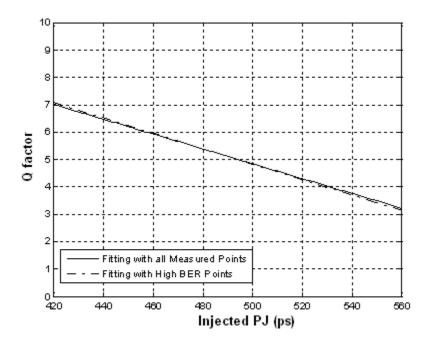

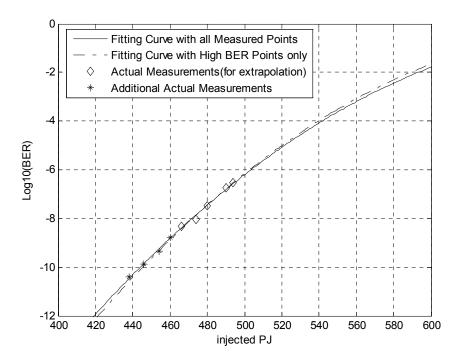

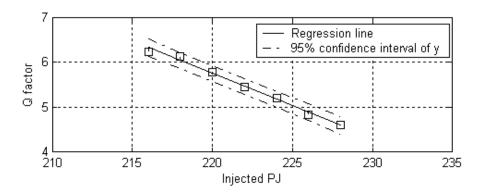

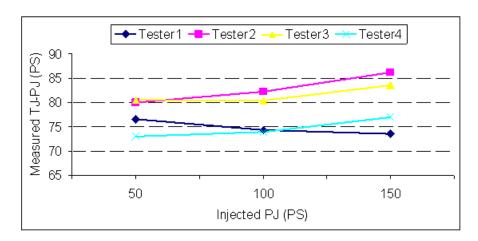

| Figure 3-24: Linear regression of Q factor as a function of the injected PJ  | 81  |

| Figure 3-25: A comparison between the two fitting results                    | 81  |

| Figure 3-26: A comparison of BER curve fitting results                       | 82  |

| Figure 3-27: Bathtub curve prediction                                        | 83  |

| Figure 3-28: 3Gbps test signal calibration results                           | 84  |

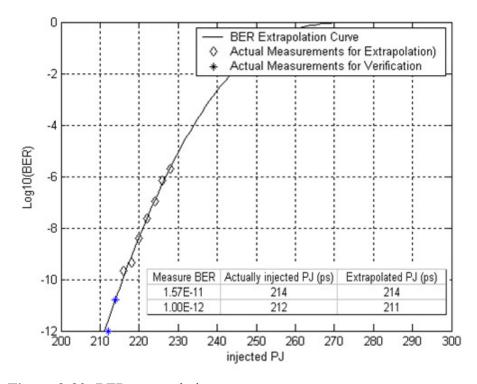

| Figure 3-29: Q factor vs. PJ                                                 | 85  |

| Figure 3-30: BER extrapolation.                                              | 85  |

| Figure 3-31: The offset between PJ and TJ at different testers               | 87  |

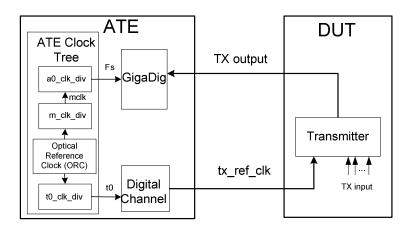

| Figure 4-1: Transmitter test setup for data acquisition                      | 93  |

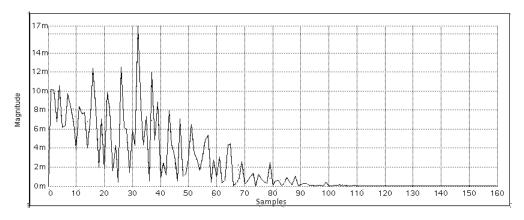

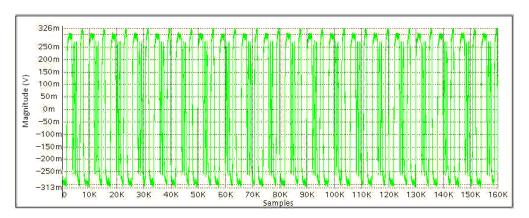

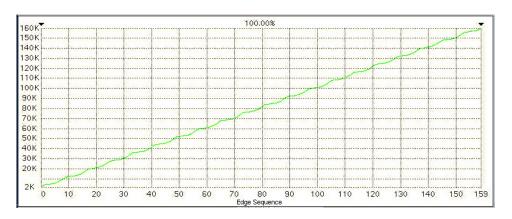

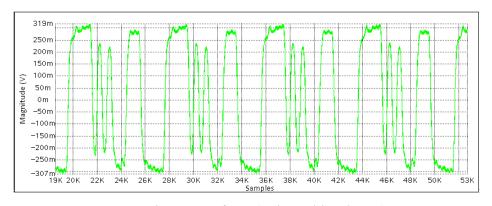

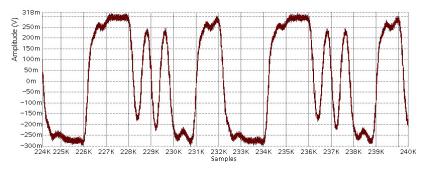

| Figure 4-2: Captured transmitter output signal                               | 101 |

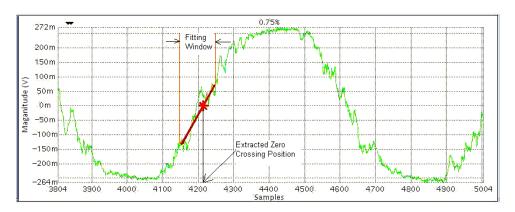

| Figure 4-3: Actual edge transitions and curve fitting                        | 102 |

| Figure 4-4: Derived edge positions from curve fitting                        | 102 |

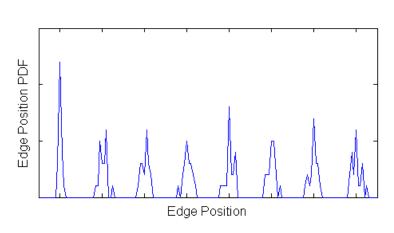

| Figure 4-5: Edge displacement data after interpolation                        | 103 |

|-------------------------------------------------------------------------------|-----|

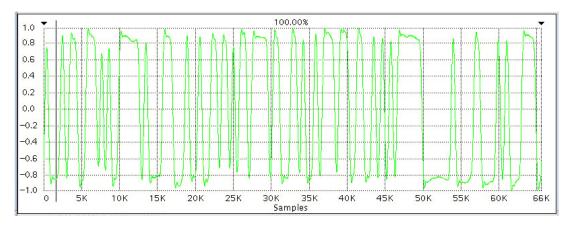

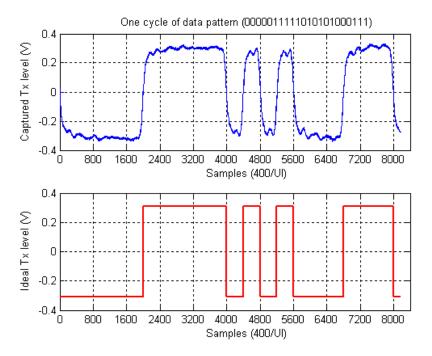

| Figure 4-6: One cycle of the test pattern                                     | 104 |

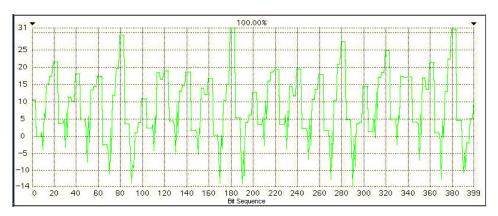

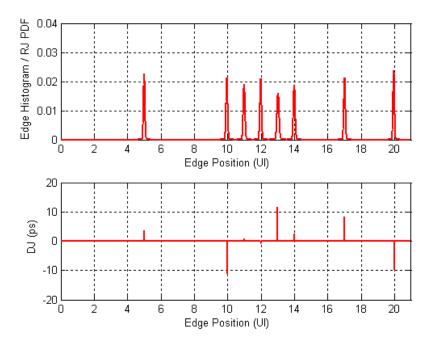

| Figure 4-7: Histograms and DJ of all eight edges                              | 105 |

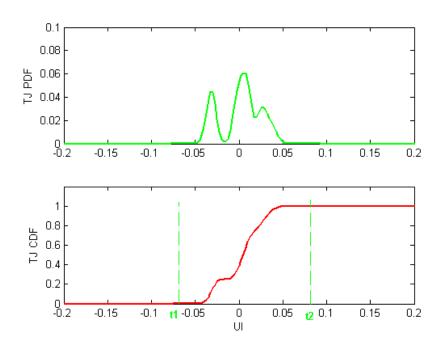

| Figure 4-8: The PDF and CDF of the device TJ                                  | 109 |

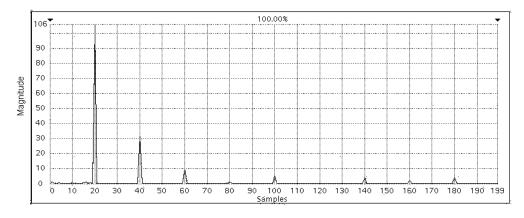

| Figure 4-9: TJ spectrum                                                       | 110 |

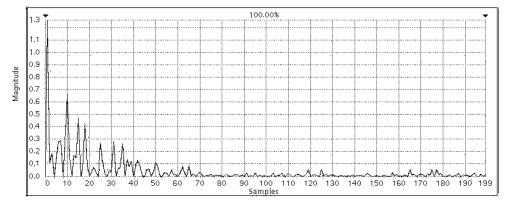

| Figure 4-10: RJ spectrum                                                      | 11  |

| Figure 4-11: Histograms with low frequency DJ: SD = 4.08Ps                    | 114 |

| Figure 4-12: Histograms after removing low frequency DJ: RJ = SD = 1.70Ps     | 114 |

| Figure 4-13: DJ leakage                                                       | 115 |

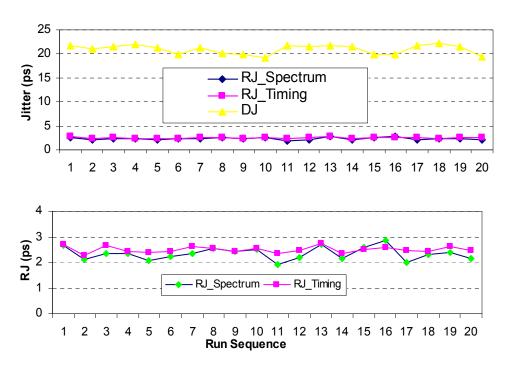

| Figure 4-14: RJ repeatability and correlation                                 | 118 |

| Figure 4-15: Jitter distribution across PVT corners                           | 119 |

| Figure 4-16: Captured 6G waveform (only 45 bits shown)                        | 122 |

| Figure 4-17: RJ and DJ at 6G data rate                                        | 123 |

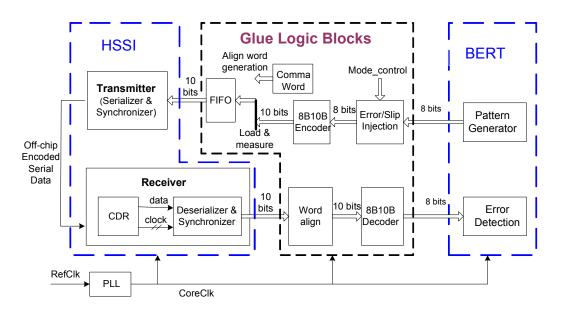

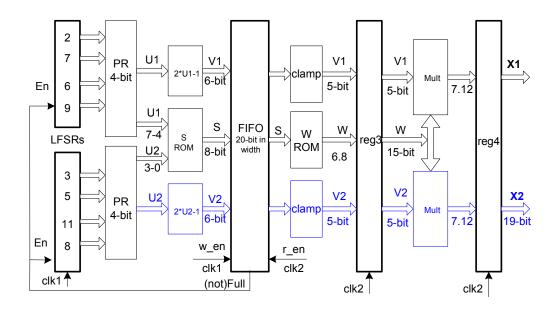

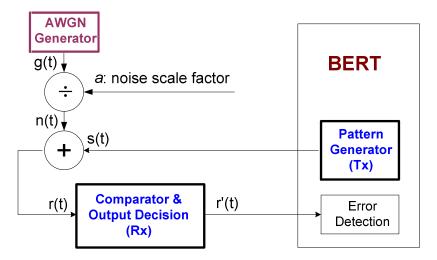

| Figure 5-1: Block diagram of a serial BERT                                    | 127 |

| Figure 5-2: Block diagram of the parallel BERT                                | 129 |

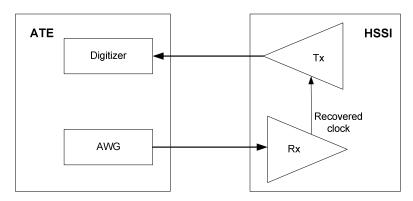

| Figure 5-3: HSSI testing setup to verify BERT functionality                   | 130 |

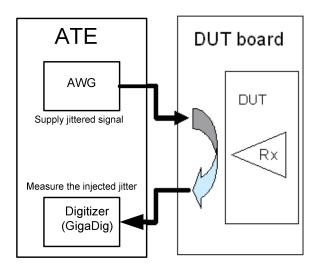

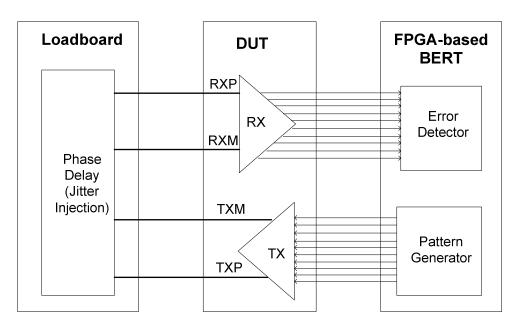

| Figure 5-4: Loopback-based jitter testing                                     | 132 |

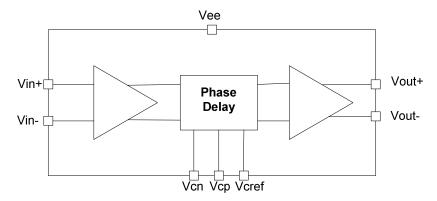

| Figure 5-5: Block diagram of iT4036                                           | 134 |

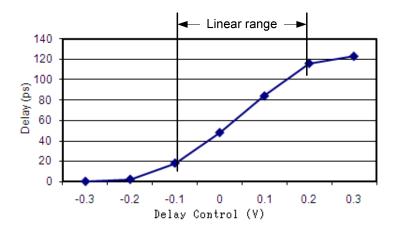

| Figure 5-6: Delay vs. delay control                                           | 135 |

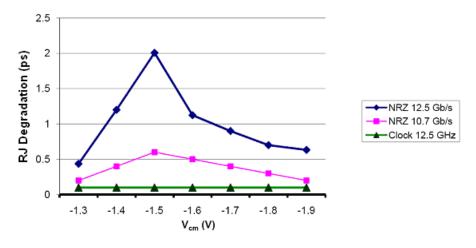

| Figure 5-7: RJ degradation vs. Vcm (courtesy of GigOptix)                     | 135 |

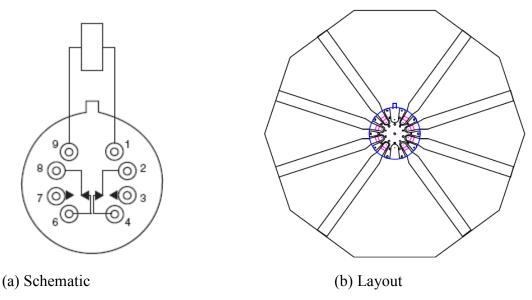

| Figure 5-8: Phase delay line iT4036 evaluation board (courtesy of GigOptix)   | 136 |

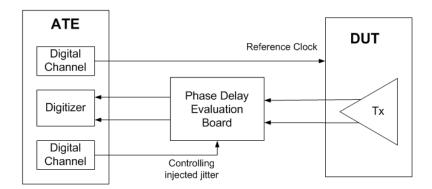

| Figure 5-9: Phase delay evaluation setup                                      | 136 |

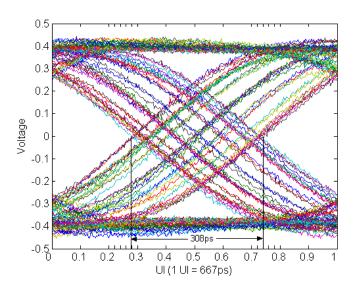

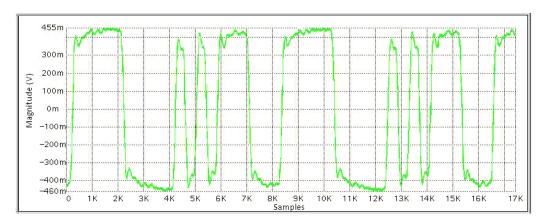

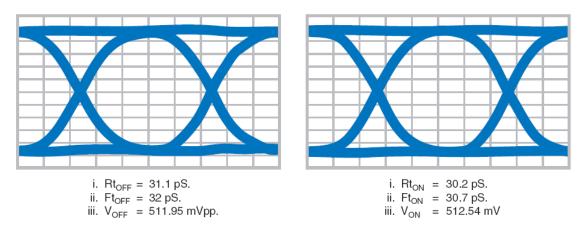

| Figure 5-10: The transmitter output waveform after the delay line             | 137 |

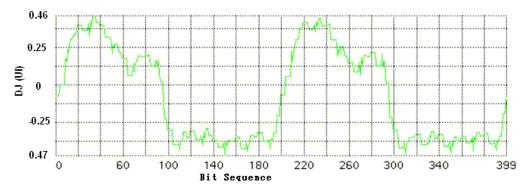

| Figure 5-11: Extracted DJ profile from captured data signal.                  | 137 |

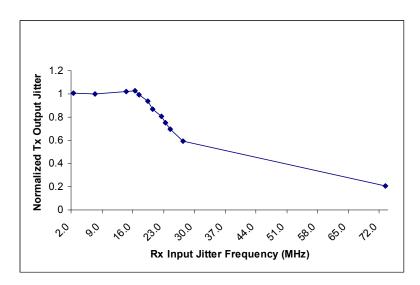

| Figure 5-12: Extracted DJ from the phase delay output                         | 138 |

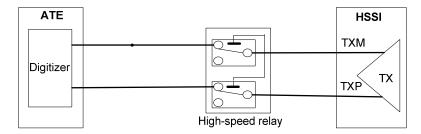

| Figure 5-13: A versatile scheme for HSSI validation and test                  | 139 |

| Figure 5-14: Testing HSSIs on ATE                                             | 140 |

| Figure 5-15: Characterizing the relay and the phase delay using the digitizer | 141 |

| Figure 5-16: Characterizing the relay using the digitizer                     | 142 |

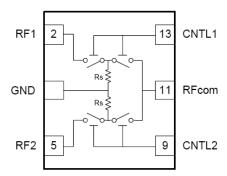

| Figure 5-17: TT1244 functional block diagram                                  | 143 |

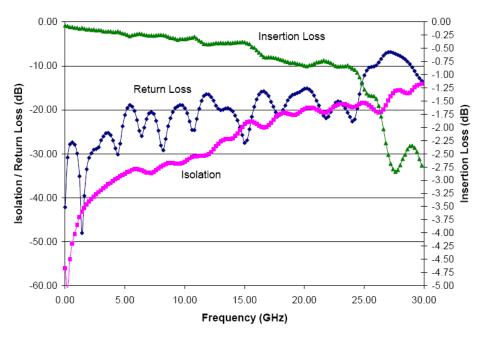

| Figure 5-18: TT1244 measured performance by TeraVicta                         | 144 |

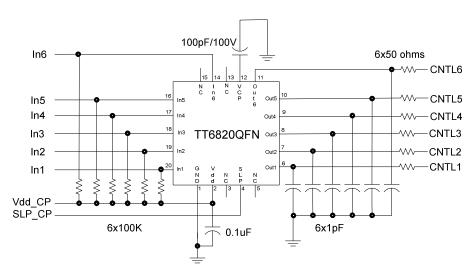

| Figure 5-19: Charge-pump circuit for the MEMS                                       | 145 |

|-------------------------------------------------------------------------------------|-----|

| Figure 5-20: GRF300 relay (Courtesy of Teledyne)                                    | 146 |

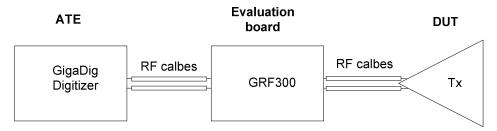

| Figure 5-21: Typical signal integrity performance at 10Gbps (courtesy of Teledyne). | 146 |

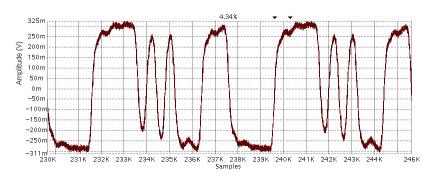

| Figure 5-22: GRF300 relay evaluation setup.                                         | 147 |

| Figure 5-23: Captured waveforms on ATE                                              | 147 |

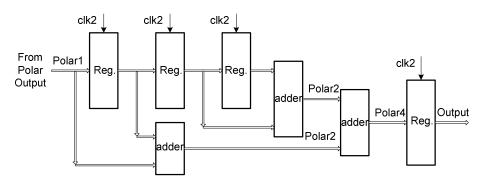

| Figure 5-24: Block diagram of the Polar method                                      | 151 |

| Figure 5-25: Our CLT method ( <i>N</i> =4)                                          | 151 |

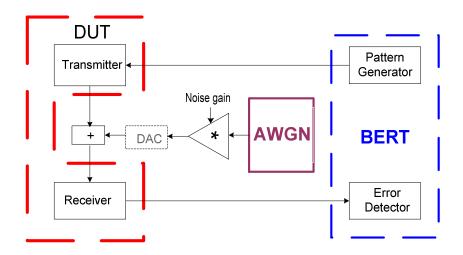

| Figure 5-26: Setup of testing BER under noise                                       | 155 |

| Figure 5-27: BER testing setup for digital baseband transmission                    | 155 |

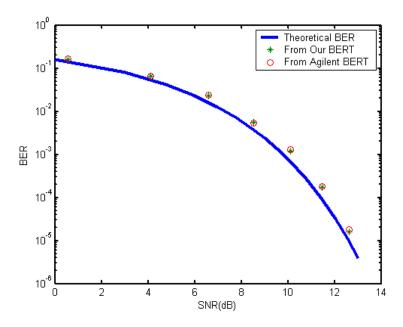

| Figure 5-28: Measured BER vs. theoretical BER                                       | 157 |

| Figure 6-1: Test setup for the PLL jitter transfer characterization                 | 164 |

| Figure 6-2: Measured PLL jitter transfer characteristics                            | 164 |

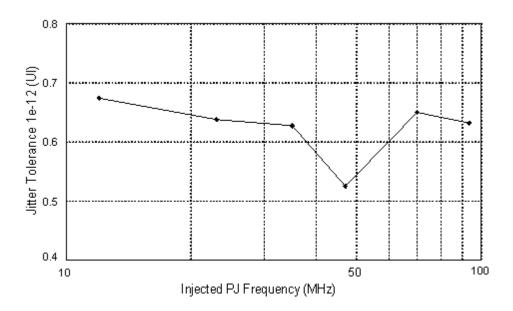

| Figure 6-3: Jitter tolerance frequency response                                     | 165 |

### **List of Tables**

| Table 2-1: SATA Physical Layer General Specifications [22]                       | 15  |

|----------------------------------------------------------------------------------|-----|

| Table 2-2: VCO Judgments in BBPD PLL                                             | 20  |

| Table 2-3: An Example of BER Estimation ( $CL$ =99% and $p$ =10 <sup>-10</sup> ) | 26  |

| Table 2-4: Transmitter Jitter Specifications for SATA                            | 31  |

| Table 2-5: Receiver Jitter Tolerance Specifications for SATA                     | 31  |

| Table 3-1: High BER Data for Jitter Tolerance Extrapolation                      | 84  |

| Table 4-1: Transmitter Jitter Specifications for SATA Gen2                       | 91  |

| Table 4-2: Parameter Settings for 20-bit Pattern 3Gpbs Data Capture              | 98  |

| Table 4-3: Actual Clock Frequencies for the 3Gbps Data Application               | 99  |

| Table 4-4: Parameter Settings for 6Gpbs Data Capture                             | 99  |

| Table 4-5: Parameter Settings for 5.5Gpbs Data Capture                           | 100 |

| Table 4-6: RJ and DJ Values in Figure 4-7.                                       | 107 |

| Table 4-7: Jitter Measurement Results between ATE and Bench                      | 117 |

| Table 4-8: Jitter Measurement Results Using Different Test Patterns              | 120 |

| Table 4-9: Reference Clock Impacts to Transmitter Jitter Measurement             | 121 |

| Table 5-1: 6Gbps Signal Parameters in Different Signal Paths.                    | 148 |

| Table 5-2: $Q(x)$ Relative Error of Our Generators                               | 153 |

| Table 5-3: BER Measurements for Digital Baseband.                                | 156 |

### **List of Acronyms**

AC: Alternating Current

A-D: Anderson-Darling

ADC: Analog to Digital Converter

ATE: Automatic Test Equipment

AWG: Arbitrary Waveform Generator

AWGN: Additive White Gaussian Noise

BBPD: Bang Bang Phase Detector

BER: Bit Error Rate

BERT: Bit Error Rate Tester

BIST: Built-in-Self-Test

BUJ: Bounded Uncorrelated Jitter

CDF: Cumulative Distribution Function

CDR: Clock Data Recovery

CL: Confidence Level

CMOS: Complementary Metal-Oxide Semiconductor

CTL: Central Limit Theorem

DAC: Digital Analogy Converter

DCD: Duty Cycle Distortion

DDJ: Data Dependant Jitter

DFT: Design-For-Test

DJ: Deterministic Jitter

DSP: Digital Signal Processing

**DUT**: Device Under Test

ECL: Emitter Coupled Logic

FC: Fiber Channel

FFT: Fast Fourier Transform

FIFO: First-In-First-Out

FM: Frequency Modulation

FPGA: Field Programmable Gate Array

Gbps: Gigabits per second

HBT: Heterostructure Bipolar Transistor

HSD: High Speed Digital

HSSI: High Speed Serial Interface

I/O: Input/Output

ISI: Inter-Symbol Interference

K-S: Kolmogorov-Smirnov

LF: Loop Filter

LFSR: Linear Feedback Shift Register

LSB: Least Significant Bit

LVDS: Low Voltage Differential Signaling

MEMS: Micro-Electro-Mechanical System

MSB: Most Significant Bit

NRZ: Non Return Zero

NRZI: Non Return Zero Inverted

OE: Output Enabled

OOB: Out of Band

ORC: Optical Reference Clock

PCB: Printed Circuit Board

PDF: Probability Distribution Function

PFD: Phase Frequency Detector

PJ: Periodic Jitter

PLL: Phase Lock Loop

PRBS: Pseudo Random Bit Sequence

PRWS: Pseudo Random Word Sequence

PVT: Process, Voltage and Temperature

RAM: Random Access Memory

RJ: Random Jitter

**RO**: Ring Oscillator

ROM: Read Only Memory

Rx: Receiver

RZ: Return Zero

SAS: Serial Attached SCSI

SATA: Serial Advanced Technology Attachment

SCSI: Small Computer System Interface

SD: Standard Deviation

SerDes: Serializer Deserializer

SMA: Sub-Miniature type-A

SNR: Signal-to-Noise Ratio

SoC: System-on-Chip

TIA: Time Interval Analysis

TJ: Total Jitter

Tx: Transmitter

UI: Unit Interval

VCDL: Voltage-Controlled Delay Line

VCO: Voltage-Controlled Oscillator

VHDL: VHSIC Hardware Description Language

VHSIC: Very High Speed Integrated Circuit

XAUI: 10 Gigabit Attached Unit Interface

### **Chapter 1 - Introduction**

#### 1.1 Motivation

The High-Speed Serial Interface (HSSI), which is interchangeably referred to as Serializer/Deserializer (SerDes) or transceiver, is a cornerstone of modern communication. As the HSSI data rate reaches a few Gbps and continues increasing, the room for its timing deviation, i.e., jitter, is getting tighter and tighter. To achieve high data rates, sophisticated techniques such as equalization and pre-compensation have now become common in HSSIs. With the concurrent increase in design complexity and decrease in the timing budget, the traditional "Guaranteed by Design" paradigm is not valid anymore. It is becoming imperative to qualify the tight timing specifications in silicon in order to guarantee the design quality.

The post-silicon qualification usually consists of three processes: validation of the first set of fabricated devices, characterization of the devices under all settings across Process, Voltage and Temperature (PVT) corners, and production testing. *Validation* emphasizes on verifying complete device functionality, including parameter values and electrical characteristics. Because of the increasing design complexity, close to 25% of all design resources at Intel are now spent on post-silicon validation [20]. Validation is usually performed in a lab environment, where standard instruments, such as oscilloscopes, signal generators and logic analyzers are used. The standard equipment is also referred to as *bench* equipment, and the standard equipment based validation and testing approaches are also referred to as bench solutions. *Characterization* is more concentrating on verifying that the device can work under all settings and can accommodate process variations allowed in manufacturing. Characterization can be done either in the lab or on Automatic Test Equipment (ATE). *Production* testing determines the pass/fail of each device in a

mass production environment. Throughput is paramount in production testing because it directly affects the device cost. ATE is widely used in production because of its high throughput.

Among all the HSSI parameters that we need to qualify, BER and Jitter are critical specifications. BER is the bit error probability of the system, which shows how well the system works. *Jitter* is the deviation of a signal from its ideal timing. It usually is expressed relative to the clock signal, where such deviations can cause bits to be incorrectly latched. In data communications, we usually talk about bit errors caused by jitter. Jitter specifications are normally defined at  $10^{-12}$  BER or lower. It is very challenging and costly to qualify the timing specification mainly for three reasons:

- (1) ATE has been widely used in production testing because of its high throughput. However, the increasing demand for more bandwidth is continuously pushing the data communication rate higher, at a pace faster than the test equipment evolves; systematic HSSI testing solutions on ATE for data rates above 6 Gbps are not commercially mature yet [8].

- (2) Cost goals set by the marketplace demand competitive test solutions testing needs to be done as fast as possible using as inexpensive equipment as possible; it is infeasible to use traditional lab instruments in a production environment because it takes hours or even days to qualify the jitter and BER performance.

- (3) Validating the jitter performance across PVT corners is becoming necessary with the continuing scale of the process technology, but the validation is very time-consuming; shortening the validation time (including debugging when necessary) would directly reduce the time-to-market, which provides great competitive advantages in gaining profit and market share.

Motivated by the great economic significance in qualifying HSSIs, this research concentrates on developing HSSI test and characterization methodologies to address the above challenges. We aim to qualify HSSIs accurately and cost-effectively, yet overcoming ATE limitations.

#### 1.1.1 HSSI Technology Trends

With the evolution of information technology during the past few decades, commodities such as cell phones and computers have become commonplace. They have made it a reality for people all over the world to share information or communicate directly in one way or another. This evolution has caused a drastic increase in the amount of information generated and the number of end users that need to access the information. As a platform to communicate information, Internet has become the main driver for technology innovation and bandwidth growth. The key to meeting the increasing demand for bandwidth is the HSSI.

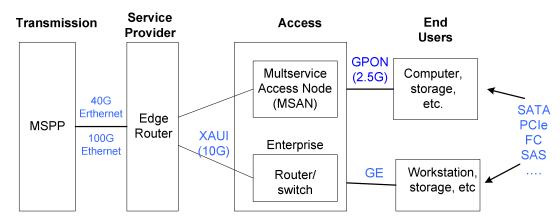

Figure 1-1 illustrates the structure of an Ethernet-based communication infrastructure. In this network, HSSIs are widely adopted into backplane applications, short and long-haul communications, mass storage access networking, and computer peripherals. The bandwidth requirement of the HSSIs depends on the proximity to the end-user and the location in the network. Different serial communication protocols have arisen to address different applications, such as Ethernet, XAUI, GPON and SATA.

Figure 1-1: HSSIs in communication infrastructure

The HSSI protocols are continuously evolving to higher speeds to meet the demand for higher bandwidth. One example is the Serial ATA (SATA): when the SATA 1.0 Working

Group was formed in February 2000 to design SATA for desktops, the target speed was only 1.5Gps; in 2004 it evolved to 3Gps and now SATA 3.0 provides 6Gbps data rate [22]. Another example is the Ethernet: 10Gbps Ethernet (10GbE) was first published by IEEE in 2002 [9]. Currently it is the fastest matured standard, but IEEE is already in development of 40GbE and 100GbE.

The increasing bandwidth requirements are driving silicon vendors to provide HSSIs with higher speeds. In 2002, the highest data rate in Altera Field Programmable Gate Arrays (FPGAs) was only 1.25 Gbps per channel, available in its Mercury devices [10]; now in Altera Stratix IV GT FPGAs, the rate has increased to 11.3 Gbps per channel, with up to 48 transceivers each device [11]. Another major FPGA provider, Xilinx, provides up to thirty-six 11.2 Gbps transceivers in its Virtex-6 and Spartan-6 FPGAs, capable of supporting 40G/100G applications [12].

The increase in data rate and integration in FPGAs is just a snapshot of the trend in the whole semiconductor industry. Moore's law is still driving the industry to double the number of transistors in an integrated device every two years, making it possible to integrate more functions and provide higher performance. The aggressive scaling in deep submicron technologies has enabled the System-on-Chip (SoC) integration of a microcontroller/DSP, ADC/DAC, memory blocks, power management, PLL and external interfaces. Many Giga-Hertz serial interfaces are built in SoC type devices with CMOS process. The data rate of the interfaces also scales accordingly. Besides the FPGA providers, some other semiconductor companies have developed HSSIs with data rates up to 10Gbps per channel, and with up to 100 channels per device [13], [14]. It has been a trend to put more and faster HSSIs in a single device to meet the increasing bandwidth demand.

When we keep pushing the speed envelope and increase the integration, many signal integrity related issues arise, such as timing jitter, noise and frequency loss. A few key technologies have been developed recently to address the issues [15]. Pre-emphasis and equalization techniques are used to compensate frequency-related losses, especially those

related to Printed Circuit Board (PCB) design due to the skin effect and dielectric loss [16]. Pre-emphasis is used in the transmitter to boost the high-frequency components of a data signal before it is launched to the transmission medium. Equalization in the receiver acts as a high-pass filter to the data signal when it enters the receiver and re-shapes the signal in order to interpret the received signal correctly.

With the integration increase, there is a trend to implement multiple data rates in a single HSSI to accommodate multiple protocols. This requires the HSSI capable of providing multiple rate clock signals. The Phase Locked Loop (PLL) is widely used for clock generation, where a Voltage-Controlled Oscillator (VCO) is a key component. There are two types of oscillators: Ring Oscillator (RO) and LC tank oscillator (LC tank). RO has the advantages of small chip area and wide tunable frequency range, but LC tanks provide lower noise and better jitter performance [17], [18]. Multiple data rates can be implemented by changing divider ratios inside the PLL or by providing additional VCOs. In Altera Stratix IV GT FPGAs, the RO can support data rates from 600Mbps to 10.3 Gbps; two LC tanks are also implemented in this device, one with 4.9~6.375 Gbps optimized for PCIe/CEI-6 compliance and the other with 9.9~11.3 Gbps optimized for XLAUI/CAUI/CEI-11G compliance [19].

A side effect of implementing multiple data rates is that the jitter performance of the HSSI can vary across its data range. If the same PLL is used at two speeds, such as 6Gbps and 8.5Gbps, one speed can be susceptible to higher jitter because the two speeds are derived from the same VCO that can only be optimized at one speed. If different PLLs are used to support different data rates, the performance at one data rate does not correlate to another data rate. In either case, good performance at a higher data rate does not guarantee better margin at lower data rates because PLL characteristics may be different.

#### 1.1.2 Qualification Challenges

With the increasing data rate and higher degree of integration, the staggering complexity makes it challenging to design fault-free devices. Post-silicon qualifications are critical in guaranteeing the design quality and the device quality. It is challenging and expensive to qualify the HSSI devices, especially the jitter performance – transmitter jitter and receiver jitter tolerance. Numerous HSSI standards define jitter performance at the  $10^{-12}$  BER level, which requires running at least  $10^{13}$  bits. This requirement fundamentally limits the test speed: for instance, at 3Gbps data rate, it takes around one hour to run so many bits. With some emerging applications demanding  $10^{-14}$  BER, direct measurements are even further from being practical.

In addition, many settings in the HSSI may affect its jitter performance. A few examples include the boost control settings in the equalizer, the bandwidth setting in the PLL and the driver strength settings in the transmitter. These settings are quite common in today's HSSIs. Choosing the optimal setting for the whole HSSI from hundreds or even thousands of available settings is challenging. It requires a tremendous amount of resources in validation and test in order to guarantee the device quality.

Because of the long test time, traditionally the jitter performance of multi-gigabit HSSI devices is only evaluated on bench in limited combinations of PVT. Besides the long test time, another reason that jitter is not qualified in production is the limited availability of ATE instruments, especially for very high-speed applications. For example, to evaluate 8.5GHz FC devices, we prefer the signal generator for the receiver and the digitizer for the transmitter with a bandwidth much higher than 8.5G (such as 15GHz), but they are not commercially mature yet on ATE [8]. Furthermore, there are currently no systematic ATE solutions that can perform complete HSSI testing accurately and cost-efficiently. Most companies only do loopback tests in production to check the functionality. Some HSSI parameters, such as transmitter jitter and receiver jitter tolerance, are assumed to be guaranteed by design.

Unfortunately, the "Guaranteed by Design" quality paradigm is no longer valid while we keep advancing the semiconductor technology and increasing the data rate, which results in tightening the jitter specifications. The devices can increasingly fail just because they do not comply with the specifications. According to the data by Collett International, the

timing, mixed-signal interfaces, clocking and crosstalk are among the prime failure reasons, each contributing 18% or more to the failure of the first silicon. HSSIs personify all such issues, and are hence critical to achieving the overall system quality. It therefore is becoming imperative to develop systematic HSSI compliance testing solutions on ATE to distinguish bad devices from good ones in production. This is the only way to ensure the device quality and to eliminate or reduce customer returns.

Besides the production testing, ATE is also becoming more and more popular in characterization and validation due to its high throughput. A thorough validation and characterization of a design requires performing measurements on different process materials at different temperature and voltage combinations. All these combinations may lead to measure the same parameter more than 100 times on one device in order to get its characteristics under different conditions. The traditional bench validation approach can no longer meet the requirement of measuring a large amount of parameters in a short time. ATE-based characterization and validation solutions have to be employed to meet the requirement. Our aim is to develop systematic HSSI testing solutions on ATE that can measure the HSSI standard parameters and design specifications for validation and characterization purposes. To achieve the best test economy, we use a simplified test flow in production to qualify key parameters only.

#### 1.1.3 ATE Perspectives

In general, ATE can provide high throughput and has been widely used in production test. It is also more and more widely use for validation and characterization to shorten the time-to-market. To validate, characterize and test HSSIs on ATE, there are several considerations that need to be addressed.

The first concern is the test cost. In early days, HSSI devices were designed as high-performance and high-margin devices. With the introduction of the low cost CMOS processes, most of the Gigahertz HSSIs are now built in high-volume and low-priced SoCs. The large scale integration makes it challenging to design a high performance HSSI

block in a very noisy SoC environment. It is more challenging to provide competitive production test solution because of the test time budget. For an average high-volume SoC, the normal acceptable test time ranges from a few seconds to ten seconds. The HSSI testing is tied with the testing of all other analog and digital blocks in the SoC. As one of many blocks in an SoC, it is expected that the HSSI block testing can be done within 1~2 seconds. For transmitter jitter testing and the receiver jitter tolerance testing, the test time budget is usually limited to a few tens or hundreds milliseconds because there are hundreds of other parameters to test. Test cost control is one of the biggest challenges in a mass-production environment. It is urgent to develop jitter testing techniques that can meet the cost requirement.

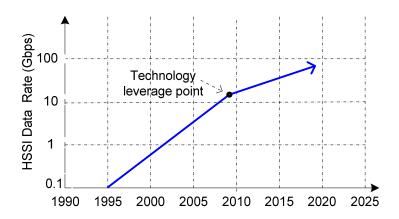

Figure 1-2: High speed serial interface technology trend

The second concern is the availability of high-speed instruments on ATE. The increasing bandwidth demand has been pushing the HSSI data rate higher and higher. Figure 1-2 illustrates the historic technology points and future trends [8]. During the past ten years, the data rate has increased from around 1Gbps to the 10 Gbps range. The HSSI I/O frequency is growing faster than the packaging and test fixture technology. Because of the physical limits due to the packaging and test socket, the data rate may slow down somewhat beyond 13 Gbps, shown as the technology leverage point in Figure 1-2 [8]. During the past few years, the ATE industry has made significant progress in providing HSSI test solutions. Several ATE suppliers have provided production pin-card solutions up to 6Gbps. For higher speed, such as 8.5Gbps and 10Gbps applications, systematic

ATE production solutions with jitter testing are not commercially mature yet. Normally only loopback testing is implemented in production to provide limited coverage. It is therefore imperative to address the ATE limitations in order to provide systematic production test solutions for applications above 6Gbps. Another ATE limitation is in multi-lane HSSI testing; most ATE platforms do not have enough high-speed instruments to accommodate the testing of multi-lane HSSI devices.

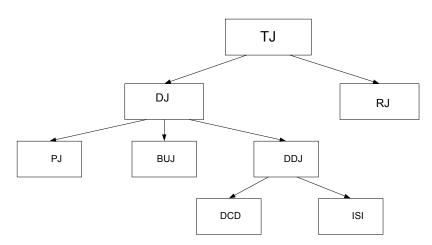

The third challenge is jitter decomposition and jitter injection. Many HSSI standards specify the jitter specifications in term of Deterministic Jitter (DJ) and Random Jitter (RJ). The traditional concept of histogram based peak-to-peak jitter has been replaced the by the concept of Total Jitter (TJ), which is related to a certain BER level. Jitter test solutions need to be capable of decomposing TJ to DJ and RJ. In addition, uncorrelated jitter detection is also needed because it can fail the device in real applications but some jitter measurement techniques cannot detect it. To conduct a jitter tolerance test for the receiver, we need to have instruments that can deliberately inject controllable amounts of jitter. Depending on applications, we may need to inject PJ, RJ or DJ. Integrated ATE instruments that can inject all these kinds of jitter do not exist currently. It is expected that these issues can be addressed in the test community.

#### 1.2 Contributions

The thesis addresses the urgent need in the semiconductor industry for cost efficient solutions to qualify HSSI jitter and BER performance [1]. We develop accelerated jitter testing solutions based on existing ATE instrument. We also develop novel low cost, non-ATE solutions that overcome the ATE instrument limitation. The contributions include:

1) Develop a jitter tolerance extrapolation algorithm that can accelerate jitter tolerance testing by >1000 times [2]. Based on the algorithm, the thesis proposes a solution for jitter tolerance production testing and a solution for characterization. Using existing ATE instruments, the production testing only takes a few tens milliseconds and the characterization only takes around 1 second, the fastest

solution to the best of our knowledge. Direct measurements down to  $10^{-12}$  BER in 3Gpbs applications demonstrate the excellent extrapolation accuracy: the discrepancy between the measured results and extrapolation results is within 2 ps [3].

- 2) Present solutions for transmitter jitter testing using the time domain, frequency domain and hybrid approaches based on existing ATE instruments [4]. We manage to achieve sub-picosecond RJ measurement accuracy: the discrepancy between the ATE and bench measurement results is within 0.5ps and the run-to-run variation on ATE is also within 0.5ps. The DJ discrepancy is only a few pico-seconds. The transmitter jitter testing along with other transmitter testing can be done in less than 100 milliseconds while existing solutions usually take a few seconds. In addition, our innovative hybrid approach eliminates some limitations posed by the time domain and the frequency domain approaches, making test results more reliable.

- 3) Propose low cost HSSI testing solutions without the need for high-speed ATE instruments: a) Develop a novel jitter injection technique using the state-of-the-art phase delay lines that can handle data rates up to 12.5Gpbs [5]. b) Investigate the applications of high-speed relays and propose a versatile loopback-based jitter compliance testing solution [5]. c) Modify the FPGA-based BER Tester (BERT) proposed in the M. Eng thesis titled "A Versatile FPGA-based High Speed Bit Error Rate Testing Scheme" to fit into the HSSI bit error detection [5].

- 4) Besides exploring the jitter impact to BER, the thesis also addresses the amplitude noise impact on BER. We further investigate the digital Gaussian noise generation and BER testing scheme proposed in my M. Eng thesis by further exploring the superiority of our approach, adding more accuracy evaluation approaches, improving the BER vs. SNR testing results and reviewing the most recent Gaussian noise generation techniques [6].

#### 1.3 Overview of the Thesis

In the remainder of the thesis, Chapter 2 presents the background of the research. We first discuss the HSSI technologies and the BER mechanism. BER is a measure of the HSSI overall performance. We then introduce how the timing jitter and the amplitude noise can affect the BER performance.

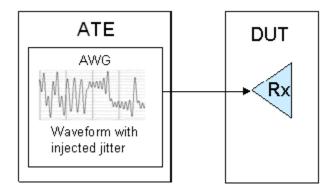

In Capture 3, the details of an ATE-based receiver testing solution are presented. We use a high-speed Arbitrary Waveform Generator (AWG) to generate test signals with controllable amounts of injected jitter. Based on the calibrated test signals and the test setup, we develop a jitter tolerance extrapolation algorithm. This algorithm enables us to accelerate the jitter tolerance characterization and production testing by more than 1000 times. Experimental results demonstrate the excellent accuracy of the approach.

In Chapter 4, we present the details of an ATE-based transmitter testing solution. A high bandwidth digitizer is used to capture the transmitter output. We will introduce how the test settings are developed for data acquisition and how the jitter components are extracted. The proposed solution can complete the transmitter testing and characterization in 100 milliseconds, and the test accuracy reaches sub-picosecond.

Capture 5 discusses the HSSI testing techniques that do not rely on high-speed ATE instruments. We propose a phase-delay line based jitter injection scheme. Based on the novel scheme, an external loopback testing solution is developed to reduce the test cost and also overcome some ATE limitations. By putting the ATE-based approach and the loopback approach together using high-speed relays, we propose a more versatile scheme for HSSI validation, debugging, characterization and production testing. In this chapter, we also further address the BER testing under noise and further investigate the Gaussian noise generation techniques.

Conclusions and future investigation directions are provided in Chapter 6.

### **Chapter 2 - Background**

#### 2.1. High-Speed Serial Communication

The high-speed serial communication interface has been widely used in modern communication to deliver fast and robust data transmission. It delivers data at rates from a few Gigabits per seconds to more than 10 Gbps. Typically, single-ended I/O standards, such as in PCI and VME, are noise limited and load limited to about 200 Mbps. They reach noise limitations at frequencies of about 250 MHz due to the signal integrity deterioration. Differential I/O standards break the frequency barrier of single-ended I/O standards with common mode rejection. They allow data transmission at higher speed, though the clock skew issue arises for differential I/O standards when the frequency approaches 1 Gbps.

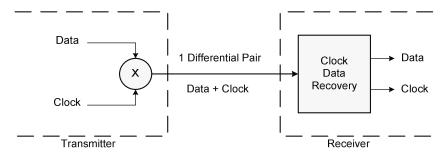

The technology that enables multiple Gbps high-speed serial communication is Clock Data Recovery (CDR). Removing clock skew concerns by encoding the clock into every data stream, CDR circuitry provides a mechanism for the clock to track the data. Hence, it eliminates frequency barriers faced by clock synchronous systems. Figure 2-1 shows the CDR mechanism: a transmitter embedding the clock in the data stream and a receiver recovering the clock from the data.

Figure 2-1: CDR transmission mechanism

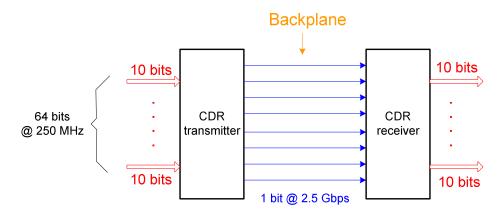

The CDR circuitry is the key structure of an HSSI. At present, the HSSI, which employs the CDR technology and differential signaling, can support applications with data rates above 10 Gbps. The roadmaps of many companies point to higher data rates on each pair of wires. In addition, a wider pipe or datapath can be built by gluing multiple transceivers. Figure 2-2 shows such an example, where 64 bits of data at 250 MHz are transmitted through 8 transceivers. Each transceiver works at 2.5Gpbs (8B10 encode/decode is used to guarantee data transitions for clock recovery). The aggregated data rate is 16 Gbps.

Figure 2-2: Applications of multiple HSSIs

Besides the high-speed capability, the serial communication also simplifies routing. In parallel communication, data are usually transmitted one bit at a time down one wire. In multi-gigabit HSSIs, differential I/Os are used and two wires are needed for each connection, but the wires are still much reduced from the parallel approach. Furthermore, in serial communication, the clock signal is embedded in the data and no clock skew exists. All these factors greatly simplify the routing of serial communication. Routing for parallel communication is always challenging. For example, in an 8-bit parallel communication system, 8 wires or 16 wires (differential IOs) are needed for data signals and another one or two wires are needed for the clock signal. Routing 9 or 18 wires across a board and keeping them all synchronized are very difficult and costly, especially for long distance connections. Because much less wires are used in a serial communication system compared to a traditional parallel one, it is possible to put more circuitry on one

die or in one package. Serial communication greatly relieves the package pin count "bottleneck" problem for SoCs.

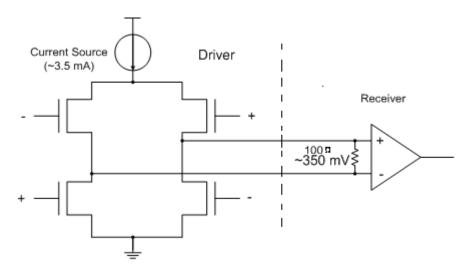

Finally, a significant advantage of serial communication is the lower energy consumption. Low energy consumption is mainly achieved by using low voltage differential signaling technologies, such as LVDS. The LVDS technology uses a constant-current line driver rather than a voltage-mode driver, so the supply current remains constant as the operating frequency increases, whereas the supply current for CMOS technology increases as the frequency increases. As shown in Figure 2-3, the constant current is typically 3.5 mA [21]. The current passes to a resistor of about 100 Ohms (matched to the cable impedance) at the receiver end, generating a signal with amplitude around 350mV. The low power consumption of serial communication interfaces eliminates the need for either heat sinks or special packaging. Hence, serial communication reduces the system cost.

Figure 2-3: Current-mode LVDS driver

Due to these advantages, multi-gigabit HSSIs are more and more widely used in high speed communications between devices, boards and systems. To address different applications, several HSSI standards have been developed, such as SATA [22], Fiber Channel (FC) [23] and 10 Gigabit Attachment Unit Interface (XAUI) [24]. Each standard specifies the detailed requirements of its functionalities and signal/device parameters, such as the data rate, amplitude level, slew rate and jitter. As an example, Table 2-1 lists

the physical layer general specifications for SATA. Each device or system designed for the standard has to comply with these specifications.

**Table 2-1:** SATA Physical Layer General Specifications [22]

| Parameter                   | Units | Limit | Gen1                           | Gen2                           | Gen3                           |

|-----------------------------|-------|-------|--------------------------------|--------------------------------|--------------------------------|

| Channel<br>Speed            | Gbps  | Nom   | 1.5                            | 3.0                            | 6.0                            |

| FER, Frame<br>Error Rate    |       | Max   | 8.2e-8 at 95% confidence level | 8.2e-8 at 95% confidence level | 8.2e-8 at 95% confidence level |

| T <sub>UI</sub> ,           |       | Min   | 666.4333                       | 333.2167                       | 166.6083                       |

| Unit                        | ps    | Nom   | 666.6667                       | 333.3333                       | 166.6667                       |

| Interval                    |       | Max   | 670.2333                       | 335.1167                       | 167.5583                       |

| F <sub>tol</sub> , Tx freq. | ppm   | Min   | -350                           | -350                           | -350                           |

| accuracy                    |       | Max   | 350                            | 350                            | 350                            |

SATA is one of the most popular HSSI standards. It is the primary storage interconnect for PCs to connect the host system to peripherals, such as hard drives, solid state drives, optical drives and removable magnetic media devices [25]. SATA is an evolutionary replacement for the Parallel ATA interface. It can drastically increase the communication bandwidth and reduce the design cost compared to Parallel-ATA. Even compared to other HSSI standards used in storage systems, SATA costs significantly less than SCSI or FC hard drivers. SATA market share has increased tremendously during the past few years: from 43% in 2006 to 97.7% in 2008 in the mobile PC market, and from 58.1% in 2006 to 99% in 2008 in the desktop PC market [26]. More than 1.1 billion SATA hard drivers have been shipped from 2001 to 2008 [27]. Therefore, it is especially beneficial in developing cost-efficient test methodologies for SATA. The experiments in this thesis concentrate on SATA devices, but the methodologies are applicable to other HSSI standards.

#### 2.1.1 HSSI Structure

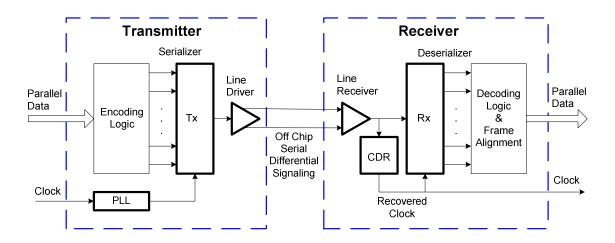

An HSSI consists of two parts: a transmitter (Tx) and a receiver (Rx), connected by transmission medium, such as cables or PCB traces. Figure 2-4 shows the block diagram of an HSSI. The transmitter and the receiver can function independently for half-duplex operation. They can also be combined for full-duplex operation.

Figure 2-4: Block diagram of an HSSI

The transmitter takes parallel data and converts it into a serial format. The PLL in the transmitter generates an internal high-speed clock for the serializer to time the serial data. The differential line driver drives the serialized data into the transmission media. The receiver accepts the high speed serial data from the transmitter. The CDR in the receiver recovers a clock from the received serial data, and re-times the data using the recovered clock. Then the deserializer restores the re-timed serial data to the parallel format.

In the above transmission mechanism, the clock is embedded in the data signal, so only one differential data signal needs to be transmitted. The clock is recovered by the CDR in the receiver side. The CDR circuit extracts the clock information by monitoring the edge transitions of the received data. To ensure that the CDR circuit can function correctly, special encoding logic is needed in the transmitter to make sure that the transmitted data has enough transitions all the time. One solution to guarantee the transitions is to encode

the original parallel data using an 8B10B encoder. An 8B10B encoder converts 8-bit words into 10-bit words, so it can always make sure there are bit transitions, regardless of what pattern is transmitted. For example, in the 8B10B encoding scheme, there are four different symbols for the zero character; all the four symbols have transitions, but get interpreted as zero. In the receiver, the frame alignment block recognizes the word boundary and correctly restores the transmitted parallel sequences. Then the 8B10B decoding logic converts the 10-bit format to the original 8-bit format. The converted sequences are presented on the output ports of the receiver.

In the HSSI structure shown in Figure 2-4, the *Encoding Logic* block and *Decoding logic & Frame Alignment* block can be built with digital circuits; all other blocks can only be built with analog circuits. For HSSIs embedded in FPGAs, the analog blocks are usually hard cores; users can instantiate them and set some parameters, such as PLL frequencies and differential signaling formats. For the digital blocks, the users have the option to use Intellectual Property (IP) cores or develop their own designs. We will demonstrate how these blocks can be instantiated or built in Chapter 5.1.3.

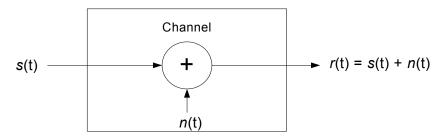

In any communication system, including an HSSI system, we need physical medium to transmit the signal from the transmitter to the receiver. The medium may be PCB traces, cables, or optical fiber in serial communication. One essential feature of the communication medium is that the transmitted signal is corrupted by a variety of possible mechanisms, such as medium loss and additive thermal noise.

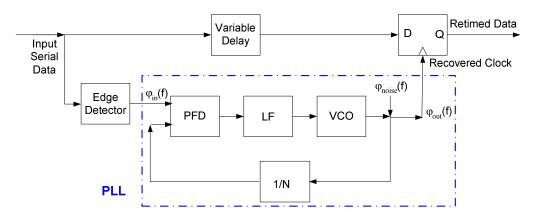

#### 2.1.2 CDR Characteristics

As shown in Figure 2-4, the CDR circuitry in the receiver recovers a clock from the received serial data, and then re-times the data using the recovered clock. CDR is the most critical block of the receiver. Figure 2-5 shows a more detailed block diagram of the CDR. The Edge Detector generates all the data edge transitions (both low to high and high to low transitions). Therefore, the output of the edge detector has the frequency component of the data rate. The edge detector output is then fed into a PLL to recover a

clock that is locked to the input serial data rate. The serial data are then re-timed by the recovered clock.

The CDR characteristics are mainly determined by the PLL inside the CDR. The structure of a linear PLL is included in Figure 2-5. The input signal to the PLL comes from the Edge Detector. The Phase Frequency Detector (PFD) compares the frequency and phase difference between the edge detector output and the recovered clock signal, and produces narrow pulses with widths proportional to the phase error. The narrow pulses are sent to the Loop Filter (LF) to generate a voltage, and the voltage adjusts the frequency and phase of the VCO output.

Figure 2-5: Block diagram of the CDR with a typical linear PLL

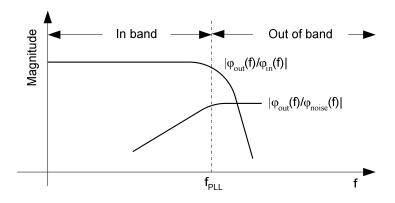

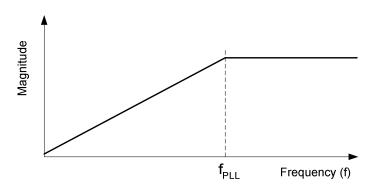

To illustrate the characteristics of the PLL, we use  $\varphi_{in}(f)$  to denote the PLL input phase of the signal and  $\varphi_{out}(f)$  to denote the PLL output phase in Figure 2-5. In the PLL model,  $\varphi_{noise}(f)$  represents the random VCO phase noise, such as the thermal noise and the simultaneous switching noise [68]. Figure 2-6 shows the frequency behavior of the PLL [69]. The function  $\varphi_{out}(f)/\varphi_{in}(f)$  is the input jitter transfer function, showing a low-pass characteristic. Therefore, the PLL tracks the jitter in the input signal with jitter frequencies below the PLL bandwidth  $f_{PLL}$  (in band jitter). The function  $\varphi_{out}(f)/\varphi_{noise}(f)$  is the VCO jitter transfer function, showing a high-pass characteristic. The PLL will pass through the spectral content of the phase noise that is above the PLL bandwidth (out of band jitter).

Figure 2-6: Phase transfer characteristics of the PLL

From the application point of view, the jitter that the receiver sees is relative to its recovered clock. Therefore, the output jitter is the timing difference between the recovered clock and the data. Because the PLL has a low pass transfer function, the jitter seen by the receiver will have a high-pass transfer characteristic as shown in Figure 2-7. A "golden" PLL for Fiber Channel has a low-pass loop filter with a -3dB frequency at  $F_d/1666$  [70], where  $F_d$  is the data rate. The jitter transfer function implies that a receiver can tolerate more low frequency jitter than high frequency jitter. The jitter tolerance function is the mirror function of the jitter transfer function [71]. Therefore, transmitter jitter and receiver jitter tolerance specifications are defined by jitter frequency bands.

Figure 2-7: Jitter transfer function of the receiver

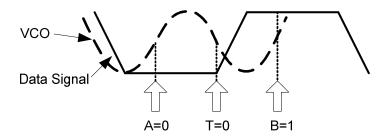

The above discussion concentrates on the linear PLL. In Recent years, the Bang-bang Phase Detector (BBPD) PLL is gaining popularity in HSSI designs. The BBPD PLL samples the incoming data with both the rising edge and falling edge of the VCO clock.

Based on three consecutive samples, the phase detector can determine whether the VCO runs faster or slower. Figure 2-8 illustrates the sampling mechanism: after the PLL is locked, the rising edge of the VCO samples the centre of the data bit and produces a retimed data bit (A), and the next VCO rising edge produces a retimed data bit (B). The VCO falling edge between the two rising edges samples the transition (T) between the data bits A and B. Table 2-2 shows the early/late/hold judgments from the three consecutive samples [73]. The VCO frequency is adjusted according to the early/late judgment.

Figure 2-8: BBPD PLL sampling

Table 2-2: VCO Judgments in BBPD PLL

| State | A | Т | В | Judgment |

|-------|---|---|---|----------|

| 0     | 0 | 0 | 0 | Hold     |

| 1     | 0 | 0 | 1 | Early    |

| 2     | 0 | 1 | 0 | Hold     |

| 3     | 0 | 1 | 1 | Late     |

| 4     | 1 | 0 | 0 | Late     |

| 5     | 1 | 0 | 1 | Hold     |

| 6     | 1 | 1 | 0 | Early    |

| 7     | 1 | 1 | 1 | Hold     |

Compared to the linear PLL, the BBPD PLL has a few unique advantages. First, it does not need to generate narrow pulses and hence can operate at the highest speed at which a process can make a working flip-flop [73]. In addition, the VCO is undisturbed in the absence of data transitions; therefore it suppresses pattern dependent jitter. However, the

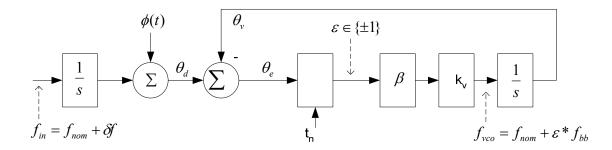

nonlinear nature of BBPDs makes the analysis and design of a BBPD PLL difficult. Figure 2-9 shows the first order model of a BBPD PLL presented in [73].

Figure 2-9: First order model of a BBPD PLL

In this model,  $\theta_e(t_n)$  is defined as the difference between the data phase  $\theta_d(t_n)$  and the VCO phase  $\theta_v(t_n)$  at the *n*th sampling time  $t_n$ . The data phase  $\theta_d(t_n)$  can be represented by

$$\theta_d(t_n) = \theta_d(0) + 2\pi \delta f t_n + \phi(t_n)$$

where  $\delta f$  is the frequency difference between the incoming data signal and the VCO centre frequency, and  $\Phi(t)$  is the phase jitter with a zero mean.

The phase detector quantizes the loop phase error to a ternary value at each sampling time. The error can be denoted by

$$\varepsilon_n = sign[\theta_e(t_n)]$$

The error signal  $\varepsilon_n$  is -1 when the phase is early, 1 when the phase is late or 0 when it is not possible to determine the phase error due to no data transitions. The error signal drives the VCO to produce a change in the frequency of

$$f_{bb} = \beta * k_V$$

where  $\beta$  is an attenuator.

Therefore, from time  $t_n$  to  $t_n+1$ , the VCO runs at one of the two frequencies determined by  $f_{nom} + \varepsilon_n f_{bb}$  ("hold state discussed later), where  $f_{nom}$  is the ideal clock frequency. In a typical CDR,  $f_{bb}$  is on the order of 0.1% of  $f_{nom}$ . The VCO frequency changes in each cycle. We can approximate the update period by

$$t_{update} = 1/f_{nom}$$

and the up-or-down phase change (also called bang-bang phase step) by

$$\theta_{bb} = 2\pi (f_{bb} / f_{nom})$$

The loop will remain phase locked as long as the input data signal frequency is in the range of VCO frequency. Assuming the phase jitter  $\Phi(t)$  is small, the input signal frequency error  $\delta f$  needs to be smaller than the  $f_{bb}$  frequency, which gives the lock range:

$$-f_{hh} < \delta f < f_{hh}$$

Based on the  $f_{bb}$  frequency, we can also calculate the maximum allowed phase jitter. For phase jitter  $\phi(t) = A\sin(2\pi f_{\rm mod}t)$ , where  $f_{mod}$  is the phase modulation frequency, the instant jitter-induced frequency error is the derivative of the data phase derivation:

$$f_{jitter} = \frac{d[\phi(t)]}{dt} = 2\pi f_{\text{mod}} A \cos(2\pi f_{\text{mod}} t)$$

Assuming  $\delta f = 0$ , in order to keep the loop locked, the phase modulation amplitude A at frequency  $f_{mod}$  should satisfy

$$A < \frac{|f_{bb}|}{2\pi f_{\text{mod}}}$$

Otherwise, the loop goes into a jitter-induced slew rate limiting. Even though the average input frequency is in the loop lock range, the added jitter causes the instantaneous input frequency deviation to exceed  $\pm f_{bb}$ , resulting in a transient phase error.

For the first order bang-bang loop, all parameters, such as jitter generation, lock range and jitter tolerance, are controlled by one parameter,  $f_{bb}$ , which gives us little design freedom. This limitation can be solved by adding another loop to dynamically adjust the VCO center frequency  $f_{nom}$  to be equal to the incoming data rate. The second loop can be implemented by an integrator.

We can consider the PLL being composed of two non-interacting branches – an integral branch and a bang-bang branch (or proportional branch). To keep the quality of the first order loop, it is needed to keep the phase change due to the proportional branch

dominating over the phase change from the integral branch. The stability factor  $\xi$  of the PLL is defined as the ratio of two phase changes [73]:

$$\xi = \frac{\Delta \theta_{\textit{proportina } l}}{\Delta \theta_{\textit{int egral}}} = \frac{2\beta \tau}{t_{\textit{update}}}$$

The dual branch BBPD structure provides two degrees of freedom: the loop frequency step  $f_{bb}$  and the stability factor  $\xi$ . In this way, it is possible to make the lock range independent of jitter tolerance and jitter generation. However, more loops also make the PLL design more complicated. There are many factors to consider when implementing a CDR and sometimes we have to make tradeoffs [74]. There is a great pressure to characterize and test well the CDR whether it is implemented with a linear PLL or a BBPD PLL.

### 2.1.3 BER Mechanisms

In the serial communication system, the transmitter, the receiver or the transmission media can introduce distortion or cause bit errors. The correctness and performance of communication interfaces depend on many design choices, such as the CDR mechanism, the PLL bandwidth, the method of encoding/decoding and the transmitter power. As a measure of how well the overall communication system performs, BER is the probability of a bit error at the output of the receiver, compared to the input of the transmitter [28].

By definition, BER is derived by calculating the ratio of the number of erroneous bits to the number of transmitted bits. The concept is very simple, but there are a few issues we need to consider when performing the BER measurement, such as how many bits need to be transmitted and how many bit errors need to be captured in order to get a reliable BER test result. If we transmit 10<sup>12</sup> bits and get one erroneous bit, can we claim that the BER performance of the system is 10<sup>-12</sup>? If we transmit another 10<sup>12</sup> bits, will we also get one and just one erroneous bit? I would say most likely no. The BER confidence level is used to solve these problems and define how reliable the test result is.

For a given digital communication system or component, there usually is a minimum specification for the BER - p(e). In practice, p(e) is often estimated by calculating the ratio of detected bit errors (l) to total bits transmitted (n) in a fixed length test sequence. If we denote the ratio by p'(e), p'(e) is only an estimation of p(e). The estimation accuracy improves with the increase of the number of transmitted bits. As shown in the following equation, p'(e) only equals to p(e) if an infinite number of bits are transmitted.

$$p'(e) = \frac{l}{n} \xrightarrow{n \to \infty} p(e)$$

However, it is impossible to transmit an infinite number of bits to get p(e) in real BER testing because the test time would be infinite. The actual number of transmitted bits depends on the desired BER confidence level. The BER confidence level is defined as the probability that the actual p(e) is better than a specified BER level y (such as  $10^{-12}$ ). The Confidence Level (CL) is mathematically expressed as

$$CL = p[p(e) < y \mid l, n]$$

where p[] indicates probability, y is a specified BER level, and |l,n| denotes a system where n bits are transmitted and l bits of errors are detected.

The confidence level is based on a set of BER measurements. One interpretation of the confidence level is that, if the BER test is repeated many times and the value p'(e) = l/n is recomputed each time, we expect p'(e) to be better than the BER level p'(e) for p'(e) in percent) of the measurements. To measure BER with a constant confidence level, we need to use a variable-length test sequence [29], [30]. The BER confidence level can be calculated based on the binomial distribution function [31], [32]. The binomial distribution function models events that have only two possible outcomes and is generally written as

$$p_n(k) = {n \choose k} p^k q^{n-k}$$

, where  ${n \choose k} = \frac{n!}{k!(n-k)!}$

where  $p_n(k)$  is the probability that k events (i.e., bit errors) occurs in n trials (i.e., bits transmitted), p represents the probability that an event occurs in a single trial (i.e. a bit

error), and q represents the probability that the event does not occur in a single trial (i.e., no bit error). According to these denotations, we have p + q = 1.

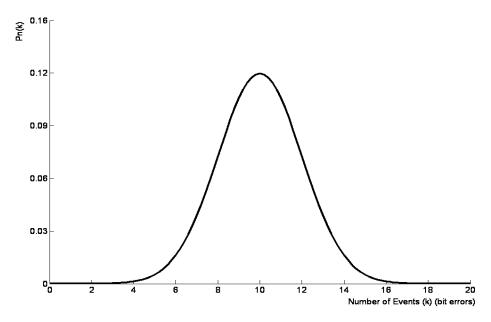

**Figure 2-10:** Graph of the binomial distribution ( $n = 10^8$ ,  $p = 10^{-7}$ )

Figure 2-10 plots the graph of the binomial distribution with  $n = 10^8$  and  $p = 10^{-7}$ . If we treat the n as the total number of bits transmitted, p as the BER, and  $p_n(k)$  as the probability that k bit errors will occur, we can use the distribution to calculate the BER confidence level. We are interested in the probability that N or fewer bit errors occur in n transmitted bits. The probability is the Cumulative Distribution Function (CDF) of the binomial distribution and is expressed as

$$p(e \le N) = \sum_{k=0}^{N} p_n(k) = \sum_{k=0}^{N} \frac{n!}{k!(n-k)!} p^k q^{n-k}$$

Then the confidence level can be written as:

$$CL = 1 - \sum_{k=0}^{N} \left[ \frac{n!}{k!(n-k)!} \right] p^{k} (1-p)^{n-k}$$

To qualify a BER p, we need to determine how many bits n must be transmitted with N or few errors. We can first choose a hypothetical value of p and a desired CL, then solve the above CL equation to determine n and N to prove the hypothesis. It is difficult to directly

solve n and N. One solution is to use Poisson theorem [31] to simplify solving n and N. Poisson theorem provides a conservative estimate of the binomial distribution function and is written as

$$p_n(k) = (\frac{n!}{k!(n-k)!})p^k q^{n-k} \xrightarrow{n\to\infty} \frac{(np)^k}{k!}e^{-np}$$

An example of the solutions for N and n is listed in Table 2-3 [33]. In this system, p is specified to  $10^{-10}$  and the confidence level CL is set to 99%. For various bit errors of N, the corresponding required transmitted bits of n are solved. According to the table, we have a 99% confidence level to claim  $p(e) < 10^{-10}$  in a 2.5Gbps system if no erroneous bit is detected in 18.5s of testing, one erroneous bit occurs in 26.7s, or two erroneous bits occur in 33.7s.

**Table 2-3:** An Example of BER Estimation (CL=99% and  $p = 10^{-10}$ )

| Bit Errors N            | 0                     | 1                     | 2                     | 3                     | 4                     |

|-------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Required bits <i>n</i>  | 4.61*10 <sup>10</sup> | 6.64*10 <sup>10</sup> | 8.40*10 <sup>10</sup> | 1.00*10 <sup>11</sup> | 1.16*10 <sup>11</sup> |

| Test time @ 2.5Gbps (s) | 18.5                  | 26.7                  | 33.7                  | 40.2                  | 46.6                  |

The test time *t* can be calculated using Gaussian error distribution:

$$t = \frac{\ln(1 - CL)}{p * r}$$

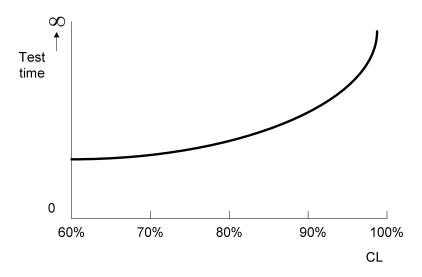

where CL is degree of confidence level, p is the upper bound of BER and r is the data rate. Figure 2-11 shows the relationship between the test time and the confidence level. If we want to achieve higher confidence level, the test time must increase. We can not achieve 100% confidence level in BER testing because it requires infinite test time. The BER measured by BERT equipment is only an estimate of the true BER. In practice, we are hence forced to make tradeoffs between the confidence level and the test time.

Figure 2-11: Test time vs. BER confidence level

Table 2-3 also shows that we need to give some margin for a measured BER if we use only a few bit errors to qualify BER performance. For example, if we measure 3 bit errors out of  $10^{11}$  transmitted bits, we should not think that the BER performance is  $3.33*10^{-11}$ . It is only reasonable to say that we have 99% confidence level that the BER performance is better than  $10^{-10}$ . We normally need at least 10\*(1/p) transmitted bits in order to qualify p BER performance. As shown in Table 2-3, to qualify  $10^{-10}$  BER performance, we can tolerate up to 3 bit errors if we transmit  $10^{11}$  bits. This provides us guidelines on how to efficiently and confidently test the BER for jitter tolerance qualifications discussed in Chapter 3.

# 2.1.4 Jitter and Noise Impacts to BER

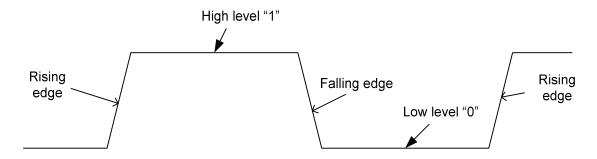

In serial communication systems, there are various signal formats in time domain. The most commonly used format is Non Return Zero (NRZ). Non Return Zero Inverted (NRZI) and Return Zero (RZ) are also used in some systems. In NRZ format, the binary information digit 1 is encoded as a high signal represented by "1", and the binary information digit 0 is encoded as a low signal represented by "0". The ideal NRZ signal can be represented by a trapezoidal waveform as shown in Figure 2-12. The waveform

consists of four components: high level "1", low level "0", rising edge (0 to 1 transition) and falling edge (1 to 0 transition).

Figure 2-12: Ideal digital signal

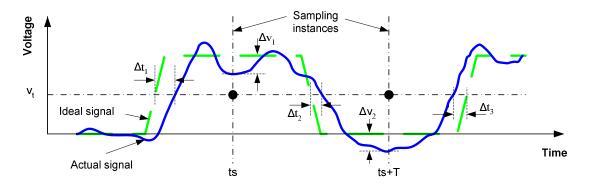

When the ideal signal is transmitted, it gets contaminated by a physical process called noise. The deviation of a noise-contaminated signal from its ideal position can be viewed from two aspects: time-deviation (jitter) and amplitude-deviation (amplitude noise). Figure 2-13 illustrates the two deviations:  $\Delta t$  and  $\Delta v$ .

Figure 2-13: Timing and amplitude deviations in an actual data signal.

At the receiver side, the CDR samples the actual data signal at sampling instance  $t_s$  and compares the sampled value with a threshold voltage  $V_t$ . If the value is bigger than  $V_t$ , logic "1" is received; otherwise, logic "0" is received. An ideal receiver samples data in the middle of each data bit. Without amplitude noise, the receiver can always correctly recover the transmitted bit. Under the presence of jitter and noise, the transition edge of the signal can fluctuate horizontally across the sampling point (along the time axis), and

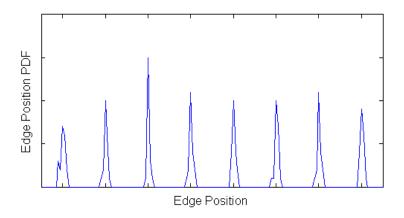

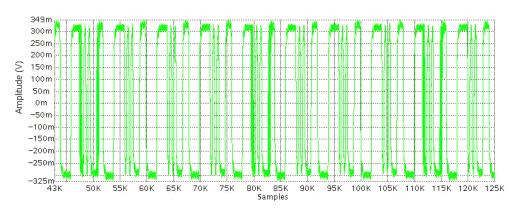

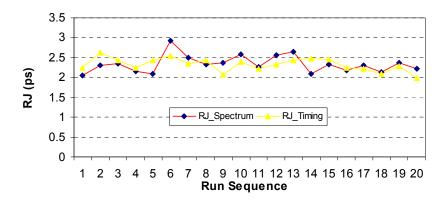

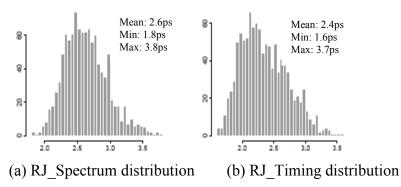

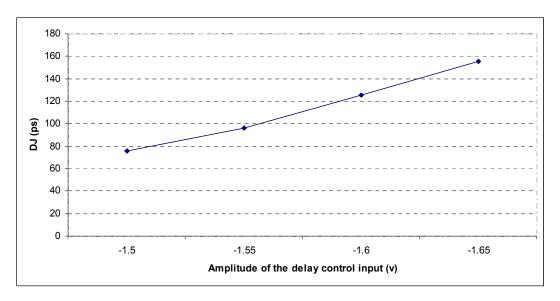

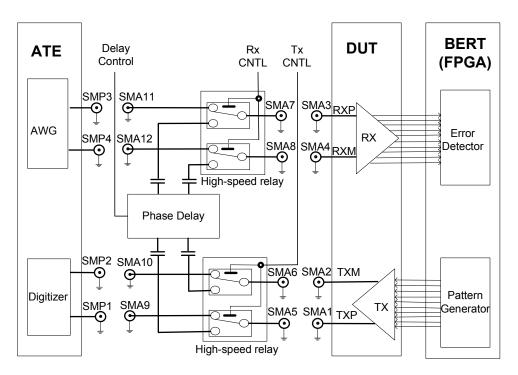

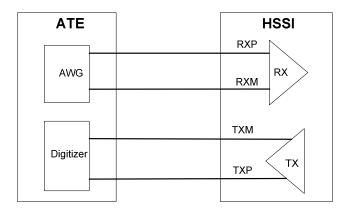

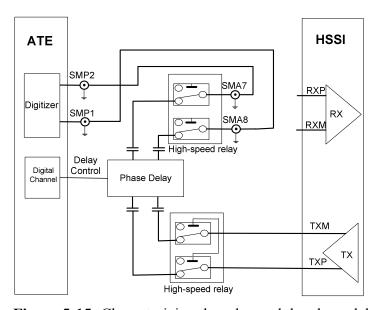

the signal voltage can fluctuate vertically across the sampling point (along the voltage axis). Both the time deviation and amplitude deviation can cause a bit error – bit "0" is received as bit "1" or bit "1" is received as bit "0".