**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# PERFORMANCE MODELLING OF THE TERABIT FREE SPACE OPTICAL BACKPLANE

## Ka Veng Ho

Department of Computer Science McGill University, Montréal

**April 1997**

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfilment of the requirements of the degree of Master of Science in Computer Science

© KA VENG HO, MCMXCVII

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-29715-2

## ABSTRACT

The Canadian Institute for Telecommunication Research (CITR) has undertaken a five year "Major Project" in Optical Systems and Devices. As part of this project, researchers in the Microelectronics and Computer System (MACS) Laboratory at McGill University are developing a reconfigurable free-space optical backplane architecture capable of supporting terabits per second (Tbps) throughput [21]. The optical backplane can be dynamically reconfigured to support the switching schemes used in both multiprocessor systems and in telecommunication systems. In this thesis, we will consider the performance of the optical backplane when it is configured to support a 160 Gigabit per second (and a 640 Gigabit per second) ATM switch in a standard telecommunication environment.

The optical backplane with 160..640 Gigabits per second throughput will have a far higher throughput than any ATM switching system yet developed. This throughput advantage will be negated if severe congestion within the backplane degrades performance. Hence, it is very important to consider queueing schemes which control congestion within the backplane, and to build an accurate simulator model to predict the behavior of the backplane before the actual implementation takes place. In this thesis, we assume that the backplane is configured to support a traditional 3-stage crossbar switching system, with electrical switches in the first and third stages, and optical switches in the second stage. A discrete event simulation model is developed to analyze numerous architectural variations of this opto-electronic switching system.

Through simulations, we illustrate the tradeoffs between the complexity of the optical switches in the second stage and the performance of the system, measured in terms of the throughput, delay and loss rate. In particular, we illustrate that large optical switches in the second stage yield the highest performance, at the expense of relatively complex logic in the opto-electronic integrated circuits ("smart pixel arrays"). These relationships form a guideline which can be used for designing the smart pixel arrays for the optical backplane.

## **RÉSUMÉ**

L' Institut Canadien de Recherches en Télécommunication (CITR) a entrepris un "important projet" de cing ans dans le domaine de Systèmes et d'Appareils Optiques. Prenant part à ce projet, des chercheurs en Micro-Electronique et du Laboratoire de Systèmes d'Informatiques (MACS) de l'Université de McGill ont developpé une architecture de système optique d'interconnexions librement espacées reconfigurable pouvant supporter Terabits par seconde (Tb/s) de transfert [21]. Le système optique d'interconnexions peut être dynamiquement reconfiguré pour supporter les schémas de switch utilisés pour les deux systèmes de multiprocesseurs et de télécommunication. Dans cette thèse, nous allons considérer la performance du système optique d'interconnexions quand il est configuré pour supporter un ATM switch de 160 Gigabits par secondes (et de 640 Gigabits par secondes) dans un environnement de télécommunication standard.

Le système d'interconnexions avec 160..640 Gigabits par seconde de tranfert permettra un plus grand transfert que le système de switch ATM déjà développé. L'avantage de ce transfert sera moindre si plusieurs congestions dans le système d'interconnexions détériorent la performance. Donc, il est très important de considérer les schémas de la file d'attente qui contrôlent la congestion dans le système d'interconnexions et de construire un modèle de simulateur précis pour prévoir les réactions du système d'interconnexions avant que l'implémentation soit faite. Dans cette thèse, nous assumons que le système d'interconnexions est configuré pour supporter un système de switch de bar croisé traditionnel à 3-phases avec des switchs électriques au première et au troisième phase et des switchs optiques dans la seconde phase. Un modèle de simulation d'évènement discret est développé pour analyser plusieurs variations d'architectures de ce système de switch Opto-Electronique.

A travers des simulations, nous illustrons les avantages et les désavantages entre la complexité des switchs optiques dans la seconde phase et la performance du système mesurée en terme de transfert, délai et taux de perte. En particulier, nous illustrons que ces grands

switchs optiques dans la seconde phase apportent une très grande performance en dépit de la logique relativement complexe dans les circuits intégrés d'Opto-Electronique. "Tableaux de pixel intelligent" ces relations forment une règle de base qui peut être utilisée pour concevoir des tableaux de pixel intelligent pour le système d'interconnexions optiques.

## **ACKNOWLEDGEMENTS**

I wish to thank my supervisor, Professor Ted Szymanski, of the Department of Electrical Engineering for introducing me to research in general, and to network simulation in particular. His enthusiasm and encouragement, which have made this thesis possible, is most appreciated.

I also wish to thank my co-supervisor, Professor David Avis, for his help and suggestions whenever I needed them.

Thanks are due to my colleague, Boonchuay Supmonchai, who spent countless hours to answer my questions whenever I ran into difficulties. Thanks to Thomas Obenaus, Sherif Sherif, Michael Kim, and Palash Desai who warmly welcomed me to the lab and showed me its social side when I started in the summer of 1994. The friendships I formed made my stay in the lab an enjoyable one.

I also thank Pung Hay Chitra for helping to translate the abstract into French.

Finally, I thank my dear friend, Owen Cheung, for his companionship over the last two years, and my family for their constant support, encouragement, and guidance.

vi

# TABLE OF CONTENTS

| ABSTRACT                                         | ii |

|--------------------------------------------------|----|

| RÉSUMÉ i                                         | ii |

| ACKNOWLEDGEMENTS                                 | v  |

| LIST OF FIGURES                                  | x  |

| LIST OF TABLES                                   | κi |

| CHAPTER 1. Introduction                          | 1  |

| 1.1. Switches and Queues                         | 1  |

| 1.2. Multistage Interconnection Switching System | 2  |

| 1.3. Author's Contribution                       | 3  |

| 1.4. Network Simulation and Thesis Overview      | 4  |

| CHAPTER 2. Literature Review                     | 5  |

| 2.1. Computer Simulation                         | 5  |

| 2.2. The Free-Space Optical Backplane            | 6  |

| 2.3. Bus-based Switches                          | 7  |

| 2.3.1. Standard Crossbar                         | 7  |

| 2.3.2. Dilated Crossbar                          | 9  |

| 2.4. Queueing Disciplines                        | 9  |

| 2.4.1. Input Queueing                            | 11 |

| 2.4.2. Output Queueing                           | 12 |

|                                                  | 13 |

|                                                  | 14 |

| CHAPTER 3. Architecture                          | 15 |

| 3.1. Problem Formulation                         | 15 |

| 3.2.  | Set  | ing Objectives                                                           |

|-------|------|--------------------------------------------------------------------------|

| 3.3.  | Sys  | tem II                                                                   |

| 3.3   | 3.1. | System II with External Queues 1                                         |

| 3.3   | 3.2. | Switch Designs                                                           |

| 3.3   | 3.3. | Terminology                                                              |

| 3.3   | 3.4. | Queueing                                                                 |

| 3.3   | 3.5. | Packet Routing                                                           |

| 3.4.  | Unl  | palanced Traffic Pattern using Straight Through Routing in Stage One . 2 |

| 3.5.  | Oth  | ner Network Architectures                                                |

| 3.    | 5.1. | System I 2                                                               |

| 3.    | 5.2. | System III                                                               |

| 3.6.  | Sur  | nmary 2                                                                  |

| СНАР' | TER. | 4. Software Simulation                                                   |

| 4.1.  |      | jectives and Methodology                                                 |

| 4.2.  |      | sumptions                                                                |

| 4.3.  |      | e Simulator                                                              |

| 4.4.  |      | ta Structure                                                             |

| 4.    | 4.1. | Packets                                                                  |

| 4.    | 4.2. | Queues                                                                   |

| 4.    | 4.3. | External Input Queues                                                    |

| 4.    | 4.4. | Switches                                                                 |

| 4.5.  | Net  | twork Modelling                                                          |

| 4.    | 5.1. | Interconnection of Switches in the Model                                 |

| 4.    | 5.2. | Packet Routing                                                           |

| 4.6.  | Mo   | delling Parallel Events in a Serial Simulator                            |

| 4.    | 6.1. | Processing Order of Switches within a Stage                              |

| 4.    | 6.2. | Processing Order of External Queues in Stage One                         |

| 4.    | 6.3. | Stage Processing Order                                                   |

| 4.7.  | Sta  | atistical Evaluation                                                     |

| 4.8.  | De   | scription of Major Functions                                             |

| 4.9.  |      | eudo-code for the Simulator                                              |

| 4.10  | . O  | rganization of the Software Simulator                                    |

| 4.11  | . V  | erification Criteria                                                     |

| 4.12  | . U  | ser Interface                                                            |

| 4.13. Compile Time Variables                                       | 51         |

|--------------------------------------------------------------------|------------|

| 4.14. Compiling and Executing the Software Simulator               | <b>52</b>  |

| 4.15. Output of the Software Simulator                             | 52         |

| 4.16. Maintenance and Possible Extension to the Software Simulator | 53         |

| 4.17. Approximate Duration of the Research                         | 53         |

| 4.18. Summary                                                      | 54         |

| CHAPTER 5. Experimental Results                                    | 55         |

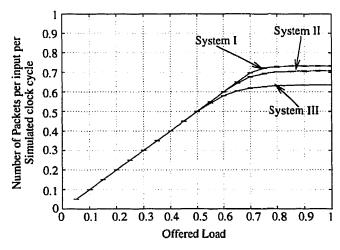

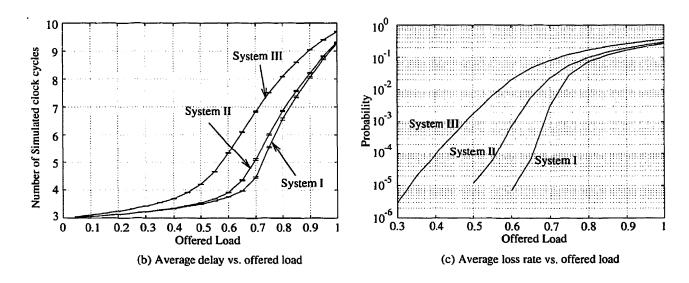

| 5.1. The Three Systems                                             | 55         |

| 5.1.1. Simulation Configurations                                   | <b>56</b>  |

| 5.1.2. Simulation Results                                          | <b>56</b>  |

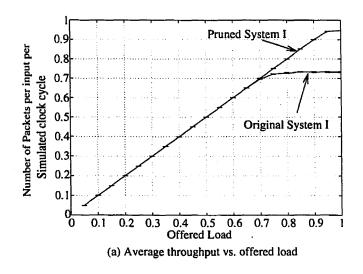

| 5.2. System I with Different Server Speeds                         | 60         |

| 5.2.1. Original System I versus Pruned System I                    | 60         |

| 5.2.2. Simulation Configurations                                   | 61         |

| 5.2.3. Adjustments for the Simulation of Pruned System I           | 61         |

| 5.2.4. Simulation Results                                          | 64         |

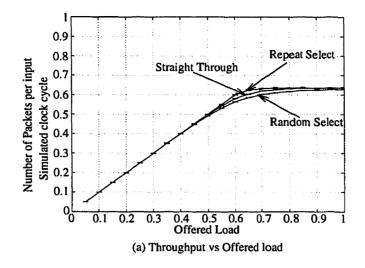

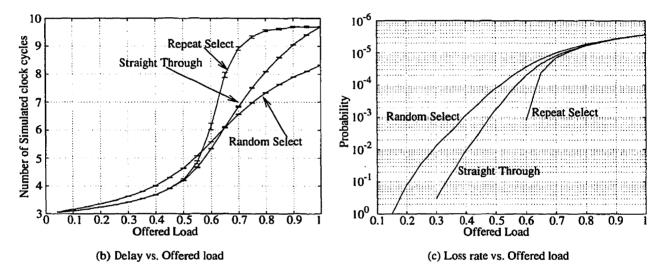

| 5.3. System III with Different Switching Strategies for Stage One  | <b>6</b> 5 |

| 5.3.1. Simulation Results                                          | 66         |

| 5.4. Examples of the Backplane's Capacity                          | 70         |

| 5.5. Summary                                                       | 70         |

| CHAPTER 6. Conclusion                                              | 73         |

| 6.1. Recommendations                                               | <b>7</b> 5 |

| 6.2. Future Work                                                   | 75         |

| REFERENCES                                                         | 76         |

| APPENDIX A. System Configurations for the Experimental Results     | 79         |

| APPENDIX B. Sample Output from the Simulator                       | 82         |

| B.1. Abbreviations used in the Simulator Standard Output           | 82         |

| B.2. Sample Output from the Simulator                              | 83         |

# LIST OF FIGURES

| 1.1 | Graphical representations of: (a) a switch, and (b) a queue            | 2  |

|-----|------------------------------------------------------------------------|----|

| 1.2 | Graphical representation of a multistage switching network             | 3  |

| 2.1 | Free-space optical backplane                                           | 6  |

| 2.2 | Structures of standard crossbar                                        | 8  |

| 2.3 | Structure of dilated crossbar (input-dilation=2, output-dilation = 2). | 10 |

| 2.4 | Input queueing.                                                        | 11 |

| 2.5 | Output queueing                                                        | 13 |

| 2.6 | Central queueing.                                                      | 14 |

| 3.1 | Modelling the free-space optical backplane as a 3-stage switching      |    |

|     | network                                                                | 16 |

| 3.2 | Interconnection of switches in System II                               | 18 |

| 3.3 | Designs of switches for System II                                      | 20 |

| 3.4 | Examples for routing packets                                           | 24 |

| 3.5 | Example of an unbalanced traffic pattern in System II using straight   |    |

|     | through routing in stage one                                           | 27 |

| 3.6 | Interconnection of switches in System I                                | 28 |

| 3.7 | Interconnection of switches in System III.                             | 30 |

| 4.1 | Software development model                                             | 32 |

| 4.2 | Graphical representation of entities in the network system             | 35 |

| 4.3 | Pre-defining packets as a stack                                        | 36 |

| 4.4 | Software architectures of unbuffered crossbar switches for System II.  | 41 |

|     |                                                                        | ix |

| 4.5 | Example of packet routing                                                 | 42 |

|-----|---------------------------------------------------------------------------|----|

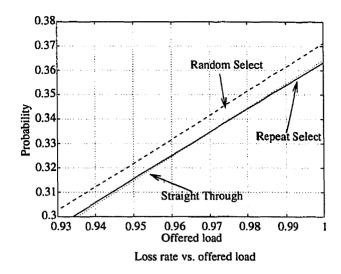

| 5.1 | Throughput, delay and loss rate of Systems I, II, and III                 | 58 |

| 5.2 | Structure of Pruned System I                                              | 62 |

| 5.3 | Throughput, delay and loss rate of System I with different server speed.  | 64 |

| 5.4 | Throughput, delay and loss rate of the different switching strategies for |    |

|     | stage one.                                                                | 67 |

| 5.5 | Loss rate of the different switching strategies for stage one             | 68 |

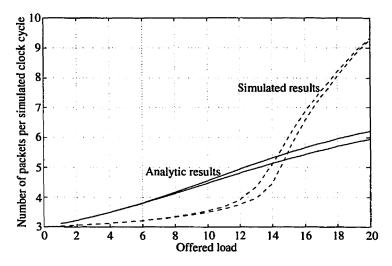

| A.1 | Comparsion of results from the analytic model and the simulator for       |    |

|     | System I at light load.                                                   | 80 |

| 3.1 | Summary of the switch architectures for System II                       | 21    |

|-----|-------------------------------------------------------------------------|-------|

| 3.2 | Summary of queues for System II. Assuming unbuffered switches in        |       |

|     | stage two.                                                              | 23    |

| 3.3 | Summary of the system configurations                                    | 29    |

| 4.1 | Summary of the characteristics of switches in the simulator             | 43    |

| 5.1 | Configuration of the three systems.                                     | 57    |

| 5.2 | Configuration for simulating two different server speeds of System I    | 63    |

| 5.3 | Configuration for simulating System III for testing different selection |       |

|     | strategies                                                              | 66    |

| 5.4 | Maximum throughputs of systems using the OC-12/OC-48 telecommunic       | ation |

|     | rate                                                                    | 71    |

| A.1 | Variables for simulating System I, II, and III (Section 5.1)            | 79    |

| A.2 | Variables for simulating Pruned System I                                | 80    |

| A.3 | Variables for simulating different selection strategies                 | 81    |

## CHAPTER 1

## Introduction

The Canadian Institute for Telecommunications Research (CITR) [3] has undertaken a large project to develop a free-space optical backplane capable of supporting terabits per second (Tbps) bandwidth. The backplane is dynamically reconfigurable and can be used for parallel computing and communication applications.

To develop an efficient optical backplane, it is important to build an accurate model to predict its behavior before actual implementation takes place. Analytic models are accurate if they are built correctly; however, it is often quite cumbersome to develop such models due to the complexity involved. A good alternative is to simulate the model via computer programs and observe the statistical behavior of the system. Simulations, therefore, are able to give quick results and allow easy modification and generalization of the assumptions. Moreover, they can be used to validate the results of analytical network models.

The goal of this thesis is to describe a software tool that performs simulations of the free-space optical backplane. By studying the statistical behavior of the backplane, an efficient network configuration can be found, given the unique hardware constraints (e.g. size of switch and size of buffer).

## 1.1. Switches and Queues

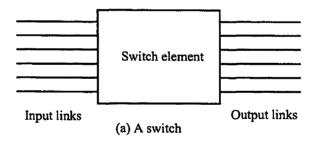

A switching network usually consists of switches, queues, and links. An  $N \times M$  switch (or switch element) is a device that has N inlets (or input links) and M outlets (or output links). Inlets are communication channels (e.g., wires or radio transmitters) for a switch to receive information from other devices (or simply from other switches). Outlets are communication channels for a switch to transmit information to other devices. The function of a switch is to "switch" messages from an inlet (out of N inlets) to an outlet (out of M outlets). A message is represented by long strings of bits and is broken into shorter bit strings called packets. A graphical representation of a switch is shown in Figure 1.1(a).

FIGURE 1.1. Graphical representations of: (a) a switch, and (b) a queue.

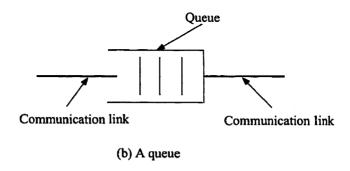

Queues are buffers that store packets. The well known "First In First Out" (FIFO) queue is one example. Packets in a FIFO queue are transmitted in the order that they arrive at the queue. A graphical representation of a queue is shown in Figure 1.1(b).

## 1.2. Multistage Interconnection Switching System

The networks which we consider in this thesis are constructed by interconnecting switch elements. The function of such a network is to transmit packets from input links of the source switches to output links of the destination switches, by traversing appropriate subsets of switch elements within the network. Furthermore, switch elements in a network can be organized into *stages*, in which the interconnections of the switch elements are restricted to switch elements in adjacent stages. Networks with switches organized into stages are known

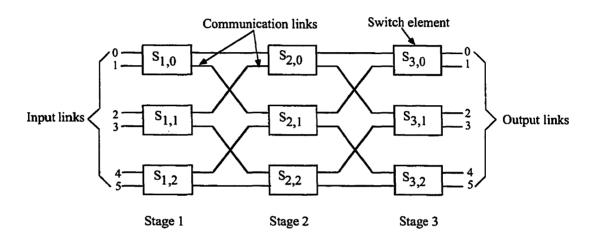

as multistage switching networks (see Figure 1.2) [4, 9]. In this thesis, the convention used for labeling switches is:

S<sub>stage</sub> #,switch #

For example,  $S_{2,1}$  refers to the second switch in stage 2.

In this thesis, we assume that the backplane is configured to support a *multistage* switching network. However, we would like to point out that there are many other possible variations that can be also supported by the backplane.

FIGURE 1.2. Graphical representation of a multistage switching network.

## 1.3. Author's Contribution

This thesis has three main contributions. The first is to specify a simulator model which could analyze numerous architectural variations of the switching system. The second contribution is in the implementation of the simulator model as a computer program that is capable of performing simulations with various configurations. In order to allow easy revision and expansion of the software, much effort was devoted to create a well structured and documented simulator. The third contribution is the experiments performed with this software. With the knowledge gained from the experiments, this thesis illustrates the tradeoffs between the complexity of optical switches and the performance of the backplane, measured in terms of throughput, delay and loss rate. These relationships form a guideline which can be used for designing a cost-efficient optical backplane.

## 1.4. Network Simulation and Thesis Overview

Network Simulation, as stated by Kheir in [7], involves the construction of a network's mathematical and logical model, followed by experimenting with the model on a computer. Therefore, our simulation study is organized into three phases: (1) system specification, (2) model development, and (3) experimentation. The discussion of the simulation study begins in Chapter 2, which presents an introduction to the optical backplane and other related topics that are intended to give the readers an adequate background in order to understand the material in the rest of this thesis.

Chapter 3 gives a detailed discussion of the multistage switching system to be modelled. Although the backplane can support many network configurations, we will only consider multistage networks in this thesis. The chapter begins with the description of how optical switches in the backplane and the electrical switches that are connected to the optical switches can be viewed as a multistage switching system [18]. Following this, an architecture for the system is described and its operation is revealed. In addition, two alternative configurations that employ different sizes and number of optical switch(es) are given at the end of the chapter.

Given the specification of the multistage switching system, the next objective is to describe how a model is constructed for the system. Chapter 4 documents how the essential features of the system are captured in a computer program. The software development model and the validation criteria used for building the network model are also explained.

Having developed the software, Chapter 5 presents the numerical results of the experimentation. A thorough analysis and comparison of different configurations of the multistage network are presented. Moreover, the tradeoffs between the complexity of the optical switches and the performance of the system, measured in terms of the throughput, delay, and loss rate, are illustrated.

Finally, Chapter 6 draws the conclusion of the work, and some additional future work that could possibly arise from this research are discussed.

## CHAPTER 2

## Literature Review

## 2.1. Computer Simulation

Computer simulation involves the construction of a mathematical and logical model, followed by experimentation of the model on a computer [7, 11, 12, 14]. A model is an object that captures the essential features of the system under investigation [7]. The model must contain some representation of the entities in the system, and be able to reflect the activities in which these entities engage.

A system contains objects, called entities; a network system is a system that contains entities of a network. For example, the entities of a network system may include packets, switches, links and queues. Each entity has properties or attributes. The attributes of a switch include, for example, the number of input and output links (dimension of the switch), and the number of queues.

A simulation model describes the functionality of a system. The functionality is executed by processes called *activities*. Adding a packet to a queue and selecting a path for a packet are examples of activities in a network system.

In this thesis, the network system under consideration is an *open* system. Systems with activities in the environment that affect the system are considered as *open* [14]. For example, a network system is said to be an *open* system if packets are injected into the system at the input and are removed from the system at the output once they arrive at their destinations.

The simulation model in this thesis is also a *discrete* system model. A system model is said to be *discrete* when activities in the system only occur at fixed time intervals. Simulations conducted with discrete system models are, therefore, *discrete event simulations* [14].

Finally, the simulation model is interpreted as a computer program. This computer program resembles closely the behavior of the system and serves the following purposes:

- (a) to collect data and information about various quantities of interest, and

- (b) to obtain good estimates of the desired performance measures.

## 2.2. The Free-Space Optical Backplane

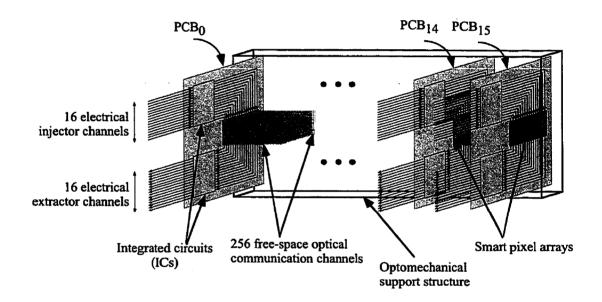

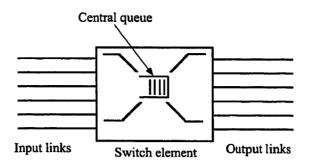

The goal of this thesis is to conduct a simulation study of the free-space optical backplane. As described in [21] (see Figure 2.1), a free-space optical backplane consists of optical communication channels (OCCs) that connect printed circuit boards (PCBs). The OCCs are created by smart-pixel arrays (SPAs) [21]. A SPA is an optoelectronic device mounted on a PCB that processes optical and electrical inputs and outputs (I/Os).

FIGURE 2.1. Free-space optical backplane.

To communicate with other PCBs, a PCB transmits electrical signals to its SPA through electrical channels. The SPA then converts the electrical signals to optical signals and transfers them to the destination PCB via the optical channels. At the destination PCB, the SPA extracts the optical signals and converts them back to electrical signals. The connectivity provided by a unique combination of optical channels and electronic channels creates a design space called the "HyperPlane" [21]. The backplane is predicted to offer

over 10,000 high-performance connections per PCB yielding an aggregate bandwidth of over 1 Tbps.

The PCBs also contain integrated circuits (ICs) used for specific applications. As described in [21], the ICs could be elements of parallel computing machines for distributed computing. In this thesis, the ICs are high performance switching elements for telecommunication applications.

## 2.3. Bus-based Switches

As stated in [22], by programming the SPA appropriately, a HyperPlane with k unidirectional optical channels in each direction can embed a number of conventional point-topoint graphs of degree  $k^{-1}$ . A crossbar switch [1] is one example of a network which can be embedded. In this thesis, we assume that the HyperPlane has 256 bidirectional optical channels and each optical channel is 8 bits wide. In the following sections, the standard crossbar and the dilated crossbar switches will be discussed in detail.

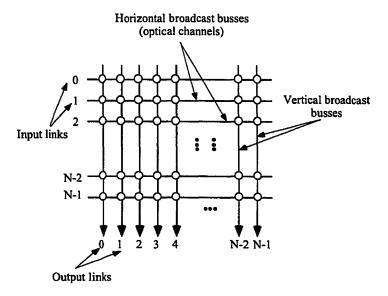

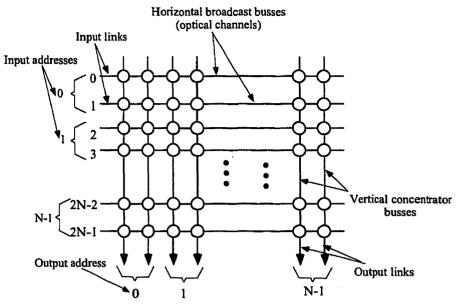

#### 2.3.1. Standard Crossbar

Standard crossbar switches, also referred to as matrix and fully connected <sup>2</sup> switches [17], provide  $N^2$  paths between N inputs and N outputs. In a standard crossbar switch, busses which connect to the inputs and outputs are assumed to run at the same speed. A bus is a data path for two devices to communicate. Figure 2.2 shows the structure of a crossbar switch with two different architectures. In both architectures, each input can send a packet over a horizontal broadcast bus, and each output may receive from one of the N inputs at each clock cycle by using vertical concentrator busses. In fact, when a standard crossbar is embedded in the HyperPlane, the horizontal broadcast busses are the optical channels in the backplane.

#### 2.3.1.1. Architecture

Figure 2.2(a) shows the structure of a standard crossbar switch with distributed concentrators 3. In this architecture, each vertical concentrator bus uses a distributed concentrator to select one of the inputs to forward to the output, when two or more inputs are simultaneously trying to send a packet to the same output.

<sup>&</sup>lt;sup>1</sup> Any graph in which the number of edges incident to a vertex is upper bounded by some constant k is a k-degree graph.

<sup>2</sup>A graph where each vertex connects to every other vertex is a fully connected graph.

<sup>&</sup>lt;sup>3</sup>A concentrator is a device that reduces the number of input links to a smaller number of output links.

## Standard Crossbar

(a) Standard crossbar with distributed concentrators

(b) Standard crossbar with centralized concentrators

FIGURE 2.2. Structures of standard crossbar.

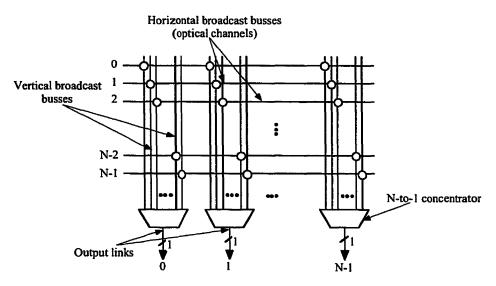

Figure 2.2(b) illustrates an alternative structure for a standard crossbar switch with centralized concentrators. As shown in the figure, there are vertical concentrator busses connecting each input and output. Vertical concentrator busses that are connected to the same output are grouped and connected to an N-to-1 concentrator, in which the concentrator is used to select one packet for the output when contention occurs because more than one input are simultaneously trying to send a packet to the same output. The number of vertical broadcast busses used in this structure is N times more than that used in the structure containing distributed concentrators.

#### 2.3.1.2. Non-Blocking Property

Blocking occurs when two or more packets contend for the same output link and only one of them can get through. A switch is said to be *internally non-blocking* [4] when it is guaranteed to deliver any permutation of packets without blocking. Since every input link in the crossbar switch has a direct path to every output, it will not suffer from packets competing for the same resource (i.e., switching path) internally, when the traffic forms a permutation. In other words, this architecture will not lose packets internally, but only at the outputs; therefore, all crossbar switches are internally non-blocking switches.

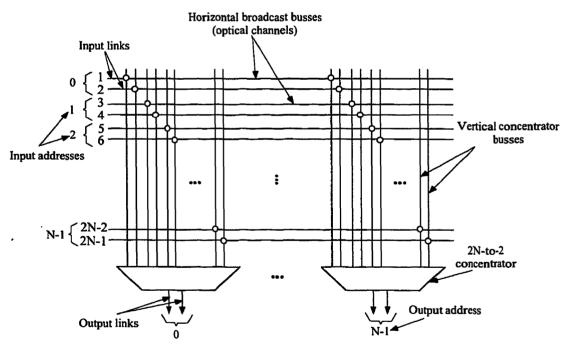

## 2.3.2. Dilated Crossbar

The performance of a standard crossbar switch can be improved by allowing more than one input link to have the same address (see Figure 2.3) [8, 20, 27]. Similarly, it can also be improved by allowing more than one output link to have the same address. Crossbar switches of this kind are known as dilated crossbar switches. For example, if a switch has aN input links consisting of N groups of a input links each, a is referred to as the input-dilation of the switch. Similarly, if a switch has bN output links consisting of N groups of b output links each, b is referred to as the output-dilation of the switch. A dilated crossbar switch is, therefore, similar to the standard crossbar, except that input-dilation and/or output-dilation is greater than one. Figure 2.3 shows an example of a  $2N \times 2N$  dilated crossbar switch with input-dilation = 2 and output-dilation = 2.

## 2.4. Queueing Disciplines

Given a random traffic model, in every clock cycle it is possible that the number of packets arriving at an output is greater than its output-dilation, causing packet loss. To reduce packet loss, buffering (or queueing) can be used. There are three main queueing strategies that can be implemented in a switch, namely: input queueing, output queueing,

## Dilated Crossbar

(a) Dilated crossbar with distributed concentrators (input-dilation = 2, output-dilation=2)

(b) Dilated crossbar with centralized concentrators (input-dilation=2, output-dilation=2)

FIGURE 2.3. Structure of dilated crossbar (input-dilation=2, output-dilation = 2) [20].

and central queueing [4]. These strategies differ by the physical location of the buffers, i.e., at the input, at the output, or inside of the switching element. Since only input queueing and output queueing are used in the simulation model developed in this thesis, the reader may wish to skip the section on central queueing (Section 2.4.3).

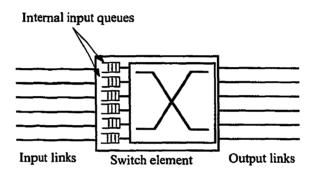

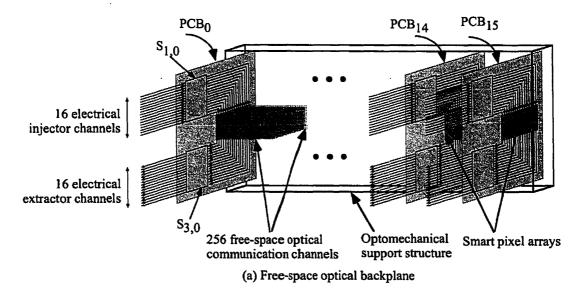

#### 2.4.1. Input Queueing

The first strategy solves the contention problem by input queueing. As shown in Figure 2.4, each input link contains a queue (referred to as *input queue*), and arriving packets are stored in the queue until the selection policy (such as round robin or random) determines that the packet may be transferred. Hence, packets will be sent from the input buffer to their destination outputs without contention.

(a) Buffered switch element with internal input queues

(b) Unbuffered switch element with external input queues

FIGURE 2.4. Input queueing.

Input queues can be implemented either within or outside a switch, as shown in Figure 2.4. Input queues implemented within switches are referred to as internal input queues; otherwise, they are said to be external input queues.

#### 2.4.1.1. Head-of-Line Blocking

Suppose packet i at the head of a  $FIFO^4$  (first in first out) queue is blocked because some other packets are also destined for packet i's destination. Moreover, suppose packet j is right behind packet i and is destined to an output where no other packets are destined. Packet j cannot be transferred even though its destined output is idle because packet i is blocking its transmission. This type of blocking is referred to as Head-of-Line (HOL) blocking [4], and is a major disadvantage of input queueing.

#### 2.4.1.2. Performance

It is known that switching elements based on the input queueing principle are limited in performance. This limitation is mainly due to HOL blocking. According to [13], the maximum obtainable load of this type of queueing is only 58.6%. Nevertheless, the performance of input buffered switches can be improved by

- increasing the speed of the input/output channels [8, 28],

- increasing the output-dilation [27], or

- using an alternate input queueing approach (e.g., random discipline) other than FIFO discipline [16].

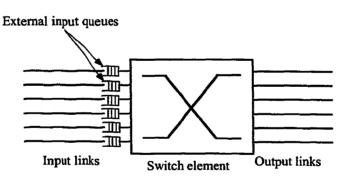

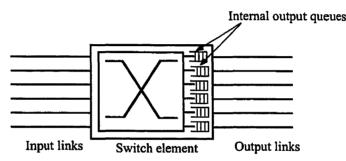

## 2.4.2. Output Queueing

As shown in Figure 2.5, contention can also be solved by placing queues at each outlet of the switch. At an output link, packets arriving from different input links are queued in the output queue in FIFO manner. In each clock cycle, the maximum number of packets that may leave an output queue is equal to the output-dilation of the switch. One classic example of a switch that adopts this method is the knockout switch proposed by Yeh, Hluckyj and Acampora in 1987 [26].

Similar to input queues, output queues can also be implemented within or outside a switch. Output queues implemented within switches are referred to as internal output queues; otherwise, they are said to be external output queues (see Figure 2.5).

#### 2.4.2.1. Performance

In order to ensure that packets remain in the correct sequence, simple FIFO discipline is used to control the output queues. Moreover, since HOL blocking will not occur in output queueing, the mean queue length (or mean waiting time) will be lower and the mean

<sup>&</sup>lt;sup>4</sup> FIFO is a service discipline of a queue [2]. Packets in a FIFO queue will be transmitted in the order that the arrive at the queue.

(a) Buffered switch element with internal output queues

(b) Unbuffered switch element with external output queues

FIGURE 2.5. Output queueing.

throughput will be higher for output queueing switches than for input queueing switches. An analytical performance comparison of input and output queueing is given in [13].

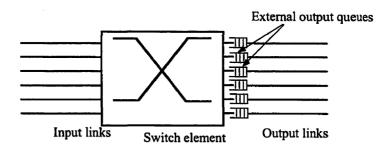

#### 2.4.3. Central Queueing

Central queueing [5] (see Figure 2.6) uses a shared buffer for all inputs and outputs. In other words, all incoming packets to a switch are stored in a central queue, and every output will select the packets destined for itself from the central queue in the FIFO discipline.

#### 2.4.3.1. Performance

It can be intuitively explained that the mean waiting time and mean throughput of central queueing is similar to that of output queueing [4]. Moreover, since the buffer is shared, a more effective use of the buffer can be achieved. Because all packets are stored in one shared buffer, the FIFO discipline in central queueing will be much more complicated than that of output queueing. Also, there is a limitation to the maximum achievable size of a shared-memory type switch [10].

FIGURE 2.6. Central queueing.

## 2.5. Summary

In this chapter, an introduction to the free-space optical backplane have been given, and the standard crossbar and dilated crossbar switches which can be embedded into the backplane has been described. In addition, an overview of queueing disciplines for the switches has been given. The topics discussed in this chapter are intended to give the reader an adequate background for understanding the rest of the thesis.

## Architecture

#### 3.1. Problem Formulation

In the optical backplane, PCBs communicate by sending packets through optical channels (see Figure 3.1(a)). In this way, the backplane is functioning as a *switch* (or switches). Since packets are transported by means of optical channels, this kind of switch is referred to as an *optical switch* [25].

As mentioned in Chapter 2, the ICs on the PCBs are high performance switch elements. These switch elements are referred to as *electrical switches* because switching is performed electrically. Furthermore, these electrical switches are used for sending and receiving packets to and from the optical switch(es).

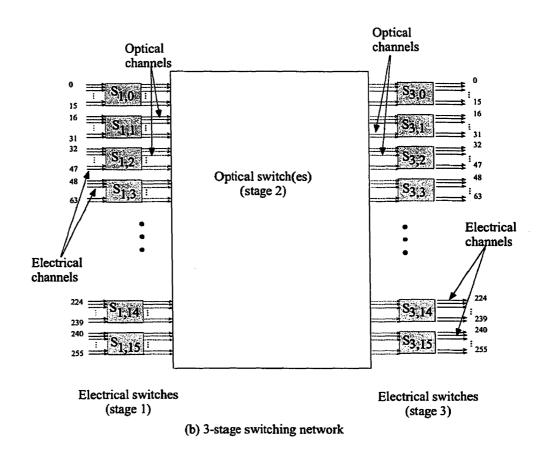

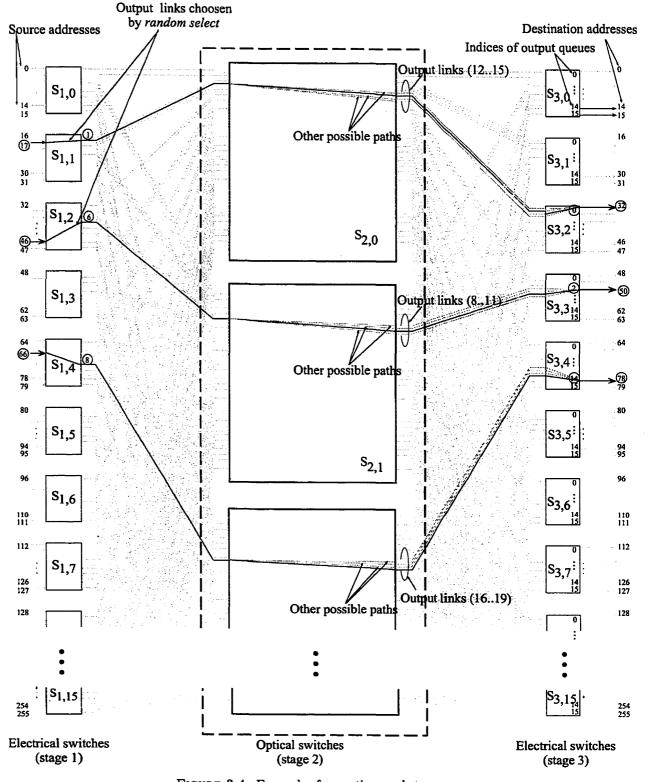

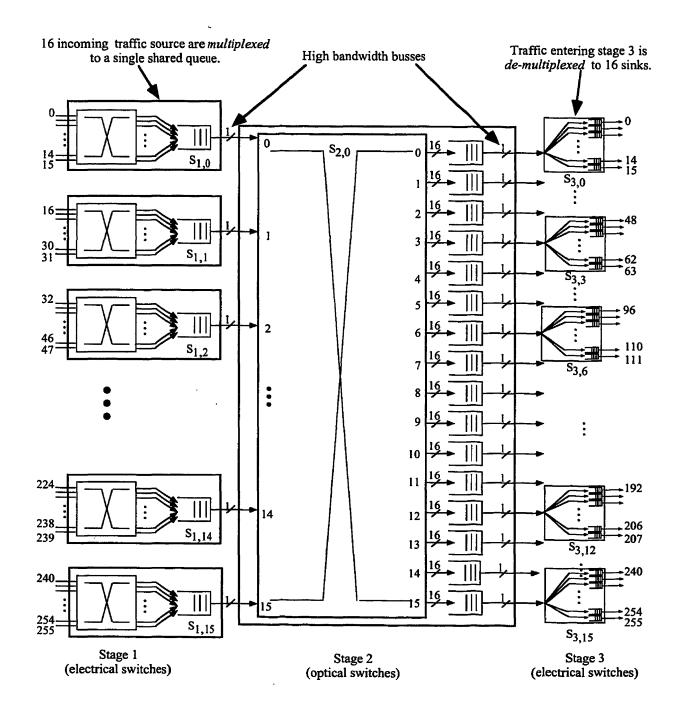

Figure 3.1(b) illustrates the interconnection between the electrical switches and optical switch(es) in the optical backplane [18]. One may note that these switch elements are organized into three stages. The first stage consists of electrical switches for sending packets to the optical switch(es), the second stage consists of optical switch(es), and the third stage consists of electrical switches for receiving packets from the optical switch(es). With this connectivity, the switch elements in the optical backplane and the PCBs can be viewed as a 3-stage switching network (refer to Section 1.2) [18].

In our simulation, we will model the optical switches in the backplane and the electrical switches that are connected to the optical switch(es) as a 3-stage switching network. Specifically, three different configurations of this network, namely, System I, System II and System III, are investigated. These systems have different optical and SPA complexities; as such, they have different number of optical switches in the second stage. Through simulations, we find that the use of different numbers of optical switches with different complexities translate into different throughputs, delays and loss rates of the network. The results of these simulations will be used to obtain the relationships between the number/complexity

FIGURE 3.1. Modelling the free-space optical backplane as a 3-stage switching network.

of the switches used and the performance of the network. These relationships can be used as a guideline for building an efficient backplane.

In addition, the simulated network will be constrained to be an *open network*, wherein packets are injected to the network and are always removed from the network once they arrive at their destination. This network is also *internally non-blocking*, so packets can only be lost at the inputs of the first stage. For the rest of this chapter, the specification of this model will be discussed in detail.

## 3.2. Setting Objectives

In [20], several internally nonblocking switches based on multiple channels are proposed for embedding into the backplane. In this thesis, we will focus on studying the performance of three-stage switching networks with dilated crossbar switches embedded in the backplane. In particular, we will restrict our studies to systems that have sixteen PCBs and 1, 4 or 16 optical switches embedded in the backplane [18]. Furthermore, each PCB are constrained to have two electrical switches, with one for sending packets to the optical switch(es) and the other for receiving packets from the optical switch(es). We will refer to the opto-electronic switching systems that we are going to investigate as Systems I, II and III, respectively. Since these three systems are very similar, it would be redundant to discuss all of them in detail. In this chapter, we will first discuss the characteristics of System II, and then the structures of Systems I and III will be presented.

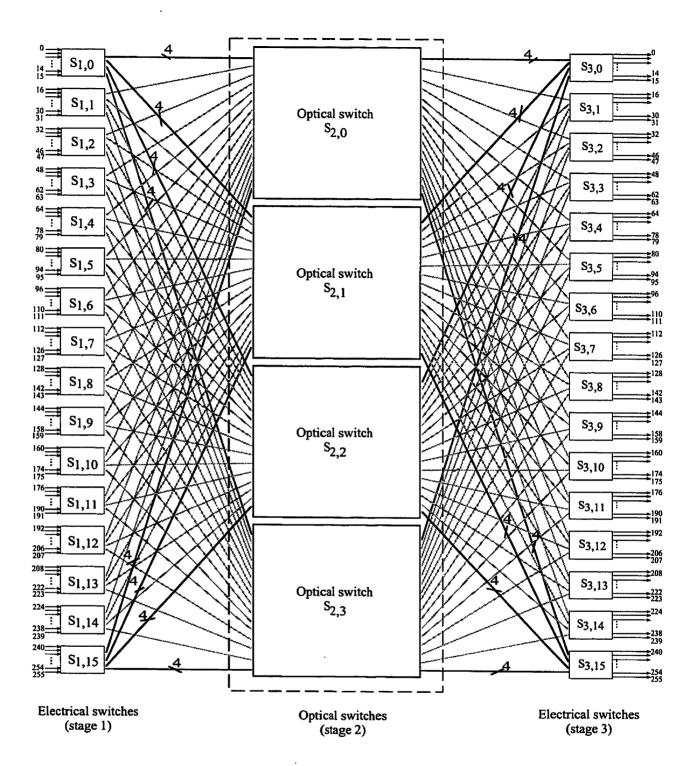

## 3.3. System II

As mentioned in Section 3.2, each PCB on the backplane consists of one electrical switch for sending data to the optical switch, one electrical switch for receiving data from the optical switch, and a smart pixel array <sup>1</sup> for processing optical and electrical I/O's (see Figure 3.1(a)). In System II, four optical switches are embedded in the backplane. Each optical switch has sixty-four input links and sixty-four output links, and each electrical switch has sixteen input links and sixteen output links. Moreover, each switch in this system consists a dilated crossbar switch.

Figure 3.2 illustrates the interconnection of the switches in System II. The first stage consists of sixteen electrical switches, the second stage consists of four optical switches, and the third stage consists of sixteen electrical switches. Every switch in stage one has 4 channels communicating with every optical switch in stage two, thereby using up all 16

<sup>&</sup>lt;sup>1</sup>A smart pixel array is an optoelectronic device mounted on a PCB that processes optical and electrical inputs and outputs (I/Os).

FIGURE 3.2. Interconnection of switches in System II [18].

output links of the stage one switch. Groups of 4 channels interconnect every optical switch in stage two to every electrical switch in stage three, thereby using up all 16 input links of the stage three switch. The way that the switches are connected in this network system, together with the fully-connected property of crossbar switches, enables packets from any input link of a switch in stage one to reach any output link of a switch in stage three.

#### 3.3.1. System II with External Queues

Owing to the performance advantages offered, output queueing [4, 6, 13] is employed in this thesis. However, practical output queue size limitations may require additional queueing at the inputs. Therefore, we allow the option of adding external queues at the input links in the first stage of the systems.

## 3.3.2. Switch Designs

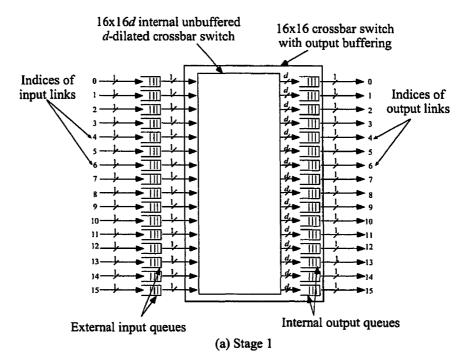

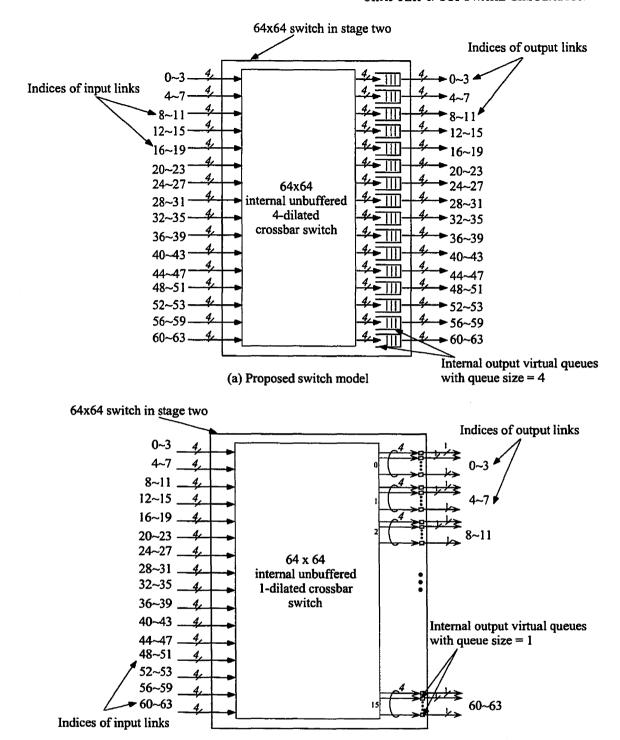

Figure 3.3 shows the architectures of the switches for each of the three stages in System II. This figure, together with Figure 3.2 on page 18, provides a precise picture for the architecture of System II. In the following subsections, the switch architecture of each stage will be described in detail. Furthermore, Table 3.1 (on page 21) provided at the end of this section gives a summary of the switch architectures for System II in each stage.

## 3.3.2.1. Stage One

As shown in Figure 3.3(a), each switch in stage one has sixteen input links and sixteen output links. Each switch element in stage one is output buffered.

The crossbar switches in stage one have sixteen input links and d times sixteen output links. Each of these switches is 1 input-dilated and d output-dilated  $^2$  (where  $1 \le d \le 16$ ). Moreover, groups of d output links from the crossbar switch are connected to a single output queue, and the output of this queue is connected to an output link of the overall switch element.

## 3.3.2.2. Stage Two

The architecture for the switches in stage two is shown in Figure 3.3(b). A switch in stage two has sixty-four input links and sixty-four output links. Each of these switch elements has an input-dilation of one and an output-dilation of four.

Furthermore, switch elements in stage two can be either buffered or unbuffered <sup>3</sup>. If switches are buffered, queues within each switch are "real"; otherwise, queues within each

<sup>&</sup>lt;sup>2</sup>Dilation "d" is a user-defined parameter.

<sup>&</sup>lt;sup>3</sup>Buffered or unbuffered switch(es) in stage two are defined as a user option.

FIGURE 3.3. Designs of switches for System II.

(assuming switches are unbuffered in this stage)

switch are "virtual." A "real" queue is a buffer that can store packets; whereas, a virtual queue is an imaginary queue that represents the occupancy of a communication link<sup>4</sup>.

If the switches in stage two are *buffered*, the crossbar switches within each of these switches are assumed to have an input-dilation of one and an output-dilation of  $d^{5}$  (where  $1 \le d \le 16$ ).

If the switches in stage two are *unbuffered*, the crossbar switches within each of these switches are assumed to have an input-dilation of one and out-dilation of four, in order to keep the blocking probability low. The output queues are "virtual" and each of them has a capacity of four. As mentioned before, a virtual queue is an imaginary queue which represents the occupancy of the link(s) to which it is connected. Therefore, even if the switches in stage two contain virtual queues, they are still unbuffered.

## 3.3.2.3. Stage Three

Figure 3.3(c) on page 20 shows the architecture of the switches in stage three. A switch in stage three has sixteen input links and sixteen output links. Every switch element in stage three is output buffered.

The architecture of switches in stages one and three are essentially identical.

| Summary of the Switch Designs for System II |                  |                  |                  |  |

|---------------------------------------------|------------------|------------------|------------------|--|

|                                             | Stage 1          | Stage 2          | Stage 3          |  |

| Type of switch                              | dilated crossbar | dilated crossbar | dilated crossbar |  |

| # of input links                            | 16               | 64               | 16               |  |

| # of output links                           | 16               | 64               | 16               |  |

| Input-dilation                              | 1                | 1                | 1                |  |

| Output-dilation                             | 1                | 4                | 1                |  |

| # of External input queues                  | 0 or 16          | 0                | 0                |  |

| # of Internal output queues                 | 16               | 16               | 16               |  |

TABLE 3.1. Summary of the switch architectures for System II.

<sup>&</sup>lt;sup>4</sup>A more detail explanation of virtual queue is given in Section 3.3.4.

<sup>&</sup>lt;sup>5</sup>Dilation "d" is a user-defined parameter.

## 3.3.3. Terminology

Before discussing queueing and packet routing in this switching system, it is vital that various terms are clearly defined. In this chapter and the next, we will repeatedly make references to several terms to describe packets, links, and queues. These terms are:

- Full: When a queue reaches its maximum capacity for storing packets, the queue is said to be "full".

- Space: A queue is said to have "a space" or "spaces" when it has not reached its maximum capacity for storing packets.

- Availability: An "available" link is a link that is currently idle.

- Move: A packet is "moved" when it is removed from a queue and put into an available link, making the link unavailable in the process.

- Forward: A packet is "forwarded" when it is stored into a queue that has a space.

- Move forward: A packet "moves forward" when it is removed from a queue and is stored into its next destination queue that has a space.

#### 3.3.4. Queueing

In this thesis, we allow switch elements in stage two to be either buffered or unbuffered. For a system with buffered switches in stage two, queues are real and each packet will stay in each stage for at least one clock cycle before moving to the next stage. For a system with unbuffered switches in the second stage, queues in that stage are virtual and packets arriving will attempt to move to stage three in the same clock cycle. Table 3.2 provides a summary of the characteristics of queues for System II with virtual queues in stage two.

When queues in stage two are *virtual*, they are not able to buffer packets. Packets that fail to move forward in the same clock cycle as they arrive at stage two will be removed from the queues at the end of each clock cycle. To prevent this kind of internal packet loss, the following method is used to simulate unbuffered stage two:

- First, in stage one, create a copy of each packet that attempts to move forward.

- Attempt to forward the copied packet to the destination virtual queue in stage two.

- (a) If the copied packet is forwarded to stage two, an attempt is made to transmit the copied packet to stage three immediately. (b) Otherwise, the copied packet is removed from the network, leaving the original packet in stage one.

• If the copied packet is forwarded to its destination queue in stage three, an acknowledgement message is returned along the open path through which the copied packet had passed, and the original copy of the packet in stage one is removed upon receiving the acknowledgement.

| Summary of the Queues for System II |                                     |                                        |         |                                        |  |

|-------------------------------------|-------------------------------------|----------------------------------------|---------|----------------------------------------|--|

|                                     | External Input Queues               | Internal Output Queues                 |         |                                        |  |

|                                     |                                     | Stage 1                                | Stage 2 | Stage 3                                |  |

| Queueing Discipline                 | FIFO                                | FIFO                                   | FIFO    | FIFO                                   |  |

| Queueing Capacity                   | $b\ (1\leqslant b\leqslant \infty)$ | $s \ (1 \leqslant s \leqslant \infty)$ | 4       | $s \ (1 \leqslant s \leqslant \infty)$ |  |

| Maximum # of arrivals               | 1                                   | d                                      | 4       | d                                      |  |

| (packets per clock cycle)           |                                     |                                        |         |                                        |  |

| Maximum service rate                | 1                                   | 1                                      | 4       | 1                                      |  |

| (packets per clock cycle)           |                                     |                                        |         |                                        |  |

TABLE 3.2. Summary of queues for System II. Assuming unbuffered switches in stage two.

#### 3.3.5. Packet Routing

In this system, each packet carries its own destination address and is routed through the system independently. This way, packets of the same source input link and destined for the same output link may have different paths through the system. Since this system is composed of 16 PCBs, each containing 16 inlets and outlets, there are a total of 256 possible destinations. In order to have a *unique* destination address, outlets in stage three are labeled from 0 to 255. Therefore, an outlet's address is its corresponding label. Similarly, inlets in stage one are labeled from 0 to 255. These labelings are shown in Figure 3.2 on page 18. Furthermore, Figure 3.4 illustrates some examples of the routing of a packet.

## 3.3.5.1. Switching Packets in Stage One

In the case when there are external input queues for each inlet in stage one and a packet is generated by an external process, the packet will be buffered in the external input queue if the queue is not full; otherwise, it will be removed from the network, i.e., there will be overflow.

FIGURE 3.4. Examples for routing packets.

Three routing methods are considered to route packets from an external input queue to an output queue in the first stage.

#### • Straight Through:

- (a) An attempt will be made to forward the packet in the *i*th external queue of a switch to the *i*th output queue of the switch in stage one (i.e., "straight-through").

- (b) If the attempt fails, (a) is repeated in the next clock cycle.

#### • Random Select:

- (a) An output link of the stage one switch is randomly selected.

- (b) An attempt is made to forward the packet to the selected output queue.

- (c) If the attempt fails, (a) and (b) are repeated in the next clock cycle.

#### • Repeat Select:

- (a) An output link of the stage one switch is randomly selected.

- (b) An attempt is made to forward the packet to the selected output queue.

- (c) If the attempt fails, (a) and (b) are repeated in the same clock cycle until the packet is forwarded, or until all output links have been tried and failed.

- (d) If all output links have been tried and failed, the process is repeated in the next clock cycle.

When there are no external input queues, a packet arriving at an input link will attempt to move into an output queue in stage one immediately. In this case, the methods used for routing packets to the output links in stage one are the same as above, with the exception that a packet will be "dropped" if it is unable to be buffered in stage one in the same clock cycle in which it was generated.

Repeat select maximizes the use of queueing capacity in the output queues but consumes more processing time than random select. Note that both random select and repeat select do not depend on the packet's destination. The primary purpose of the two strategies is to randomize the incoming traffic in order to prevent unbalanced traffic in switches of stages two and three [19].

## 3.3.5.2. Switching Packets in Stage Two

The purpose of switching in stage two is to switch packets to appropriate switches in stage three.

#### 3.3.5.3. Switching Packets in Stage Three

Packets arriving at an input in stage three are switched to their destination output links. Packets which arrive at their destined output queues in stage three will be removed from the network using the FIFO discipline.

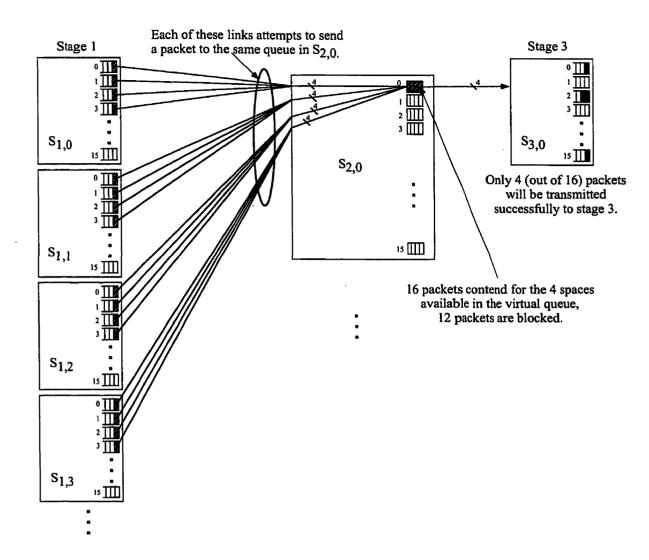

# 3.4. Unbalanced Traffic Pattern using Straight Through Routing in Stage One

In stage two, a packet will be routed to an output link that connects to the packet's destination switch in stage three. In the case where the straight through routing method is used for stage one, there will be some traffic patterns in which more than four packets with the same destination will attempt to route to the same output queue (or communication channel) in stage two, while other output queues (or communication channels) that connect to the same switch remain available or not fully utilized.

Consider the example in Figure 3.5: each of the first four links of switches  $S_{1,0}$ ,  $S_{1,1}$ ,  $S_{1,2}$ , and  $S_{1,3}$  attempts to send a packet through stage two to the same destination switch  $(S_{3,0})$  in stage three. According to the interconnection of switches for System II (Figure 3.2), all packets will be routed along to one of the first four output links of  $S_{2,0}$ . Therefore, 16 packets will contend for four links, resulting in the blocking of 12 packets, while other links (in other switches of stage two) that are connected to the packets' destination switch will remain available or not fully utilized.

Such kind of traffic pattern increases average packet delay and decreases the throughput of the network. It is, therefore, not desirable to have traffic patterns that cause unbalanced utilization of communication links. The routing options "random select" and "repeat select" will eliminate this unbalanced traffic pattern by "randomizing" the traffic [19].

## 3.5. Other Network Architectures

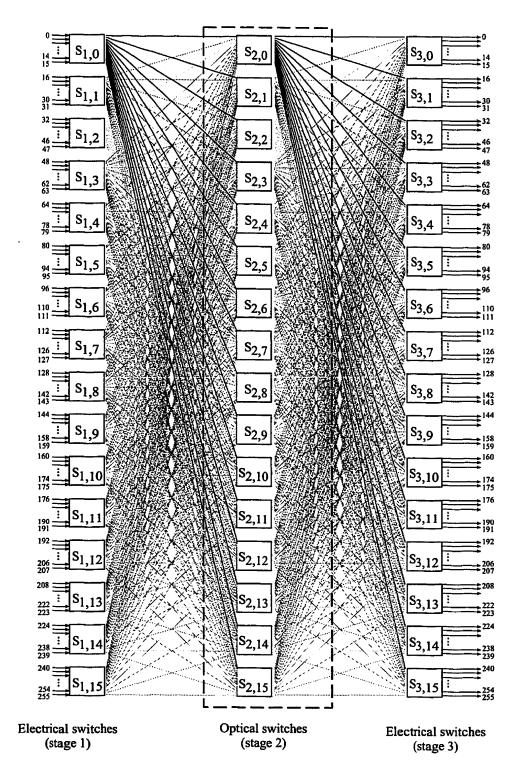

In this thesis, the three systems differ by the number and size of optical switches used. The following two sections will give a brief description of Systems I and III [18]. Table 3.3 on page 29 summarizes the configurations of the three systems.

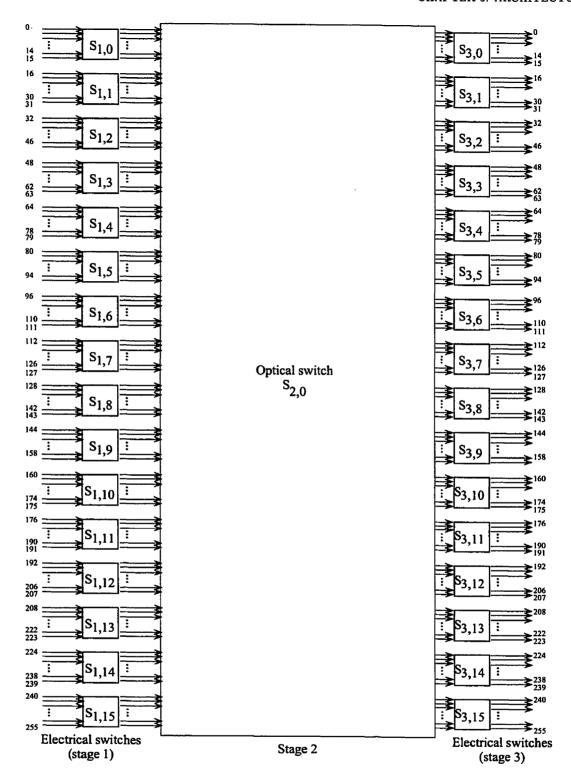

#### 3.5.1. System I

In this system (refer to figure 3.6 on page 28), a dilated crossbar switch is embedded in the backplane. In other words, there is only one big optical switch in the second stage of

FIGURE 3.5. Example of an unbalanced traffic pattern in System II using straight through routing in stage one.

the network. Moreover, the switch is  $256 \times 256$  unbuffered, 1 input-dilated, and 16 output-dilated. Therefore, all traffic going out of the first stage will go to the same switch in the second stage. There is no unbalanced traffic pattern in this system. Figure 3.6 shows the interconnection of switches in System I.

FIGURE 3.6. Interconnection of switches in System I.

#### 3.5.2. System III

The interconnection of this system is shown in figure 3.7 on page 30. In this system, sixteen smaller crossbar switches are embedded in the backplane. In order to create 256 inputs and 256 outputs for stage two, each of the sixteen switches in the second stage has sixteen input links and sixteen output links.

| Summary of the system configurations. |                          |           |                          |           |                          |           |

|---------------------------------------|--------------------------|-----------|--------------------------|-----------|--------------------------|-----------|

|                                       | stage 1                  |           | stage 2                  |           | stage 3                  |           |

|                                       | # of electrical switches | dimension | # of optical<br>switches | dimension | # of electrical switches | dimension |

| system i                              | 16                       | 16x16     | 1                        | 256x256   | 16                       | 16x16     |

| system ii                             | 16                       | 16x16     | 4                        | 64x64     | 16                       | 16x16     |

| system iii                            | 16                       | 16x16     | 16                       | 16x16     | 16                       | 16x16     |

TABLE 3.3. Summary of the system configurations.

# 3.6. Summary

In this chapter, we have described the modelling of the switches in the optical backplane and the PCBs as a 3-stage switching network. Specifically, three systems (referred to as Systems I, II and III) with 16 PCBs and 1, 4, or 16 optical-crossbar switches are discussed. These three network models share the same routing and queueing strategies and differ by the number of optical-crossbar switches used. Therefore, the interconnections of switches in each system are different. In the actual implementation, these three systems differ by the complexity of the smart pixel arrays used [18]. The purpose of this chapter is to provide the specifications for the preparation of a computer program, so that when run, the program will exhibit the behavior of the system.

FIGURE 3.7. Interconnection of switches in System III.

## CHAPTER 4

### **Software Simulation**

# 4.1. Objectives and Methodology

As described in the previous chapter, the goal of this thesis is to develop a software simulation model to predict the behavior of the 3-stage crossbar switching network that can be supported by the backplane. In terms of software engineering, the process of building this software simulation model is a software maintenance activity. This activity involves the reverse engineering and re-engineering of a banyan network simulator developed by Prof. Ted Szymanski and graduate students at Columbia University, to a 3-stage crossbar network simulator. In order to maintain a systematic, sequential approach in re-engineering the software, the classic water fall software development model is followed [15].

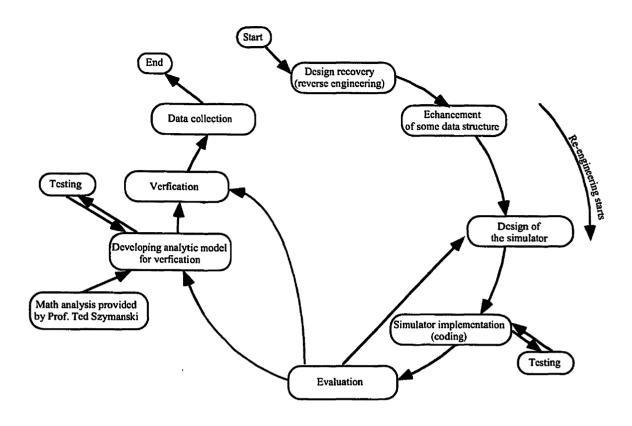

The development cycle of the simulator begins with design recovery and enhancement of the data structures in the original simulator (i.e., the bayan network simulator), as shown in Figure 4.1. This is followed by the simulator design and implementation stages. In order to ensure correctness of the code, testing is performed during the implementation stage. Once the design has been completely implemented and the code has been thoroughly tested, the simulator is evaluated. During evaluation, we may discover that changes to the design would be necessary. If this is the case, the simulator is refined by implementing and testing these changes, after which evaluation is again performed. When no more changes to the design are necessary, an analytic model of the switching network is built and used in verifying the correctness of the simulator design. This model is based on the mathematical analysis which was provided by Prof. T. Szymanski [18]. Just as in the implementation of the simulator design, testing is performed during model building. Finally, after the correctness of the simulator has been verified, the development cycle ends with the collection of data from simulations of the switching network. The complete simulator development cycle is illustrated in Figure 4.1.

FIGURE 4.1. Software development model.

The fundamental goal in designing this software simulator is to investigate the effects that various parameters have on the 3-stage crossbar switching model described in Chapter 3. Specifically, three different configurations of this network, namely, System I, System II and System III, are investigated. These systems are of different optical and SPA complexities. The tradeoffs between the complexity of the optical switches in the second stage and the performance of the system, measured in terms of throughput, delay and loss rate will be discussed. These relationships form a guideline which can be used for designing the smart pixel array of the optical backplane.

The following sections discuss in detail how the features and characteristics of the proposed model are captured in the software simulator in order to achieve the goal.

# 4.2. Assumptions

Before we describe the simulator, we summarize the assumptions used in this chapter. We assumed that input and output links to a switch are of the same speed. Packets are assumed to have a constant length, and the channel time is slotted with a slot size equal to the length of a packet transmission time. Arrival of packets at each input link follows a Binomial process [24], wherein the probability of a packet arrival in a clock cycle is p, and the probability of no arrivals in a clock cycle is 1-p=q. Since we use the slot length as the unit of time, p also corresponds to the input traffic load ( $\lambda$  packets per clock cycle) to the input link.

Moreover, we assume that transient traffic pattern will not occur after 400,000 packets have been transmitted through the network [7]. Finally, uniform random assignments <sup>1</sup> are used in any decision making that might otherwise lead to biased statistical results of the simulator.

## 4.3. The Simulator

In this chapter, a discrete-event simulator of the 3-stage crossbar switching network will be described. The simulator is written in the C-programming language on a UNIX platform. The gcc compiler is used for compilation. Moreover, approximately 15 Megabytes of disk memory and 3000 kilobytes of shared memory are needed to run the simulator.

The discrete event simulations are driven by a global clock. In general, packets are transmitted from one stage to another in each clock cycle. Since this is an open network, packets are injected into the input links of stage one and removed from the network from output links in stage three.

#### 4.4. Data Structure

The entities<sup>2</sup> of the network system considered in this thesis consist of packets, queues, and switches. In this section, the data structures of these entities will be described.

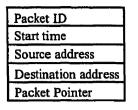

#### 4.4.1. Packets

Since packets are of fixed length in this network system, each packet is represented as a record<sup>3</sup> with the following fields <sup>4</sup>:

<sup>&</sup>lt;sup>1</sup> Uniform random assignments means that the N sample points are equiprobable with probability equal to 1/N. [24]

$<sup>^{2}</sup>$ An entity is an object, item, or component of the system that requires explicit representation in the model [7].  $^{3}$ A record is a collection of some values under a single name.

<sup>&</sup>lt;sup>4</sup>Fields are values of different types within a record.

- Packet ID

- Start time

- Source address

- Destination address (which is also the routing tag)

- Packet pointer

Figure 4.2(a) gives a graphical representation of a packet record. Each packet record contains a unique Packet ID to distinguish it from other packets. When a packet is inserted into the network, its start time (i.e., the time it enters the network), source address and destination address are recorded in the packet. A source address is the address of the input link (in stage one) at which a packet enters the network. As described in Section 3.3.5, each input link in stage one is uniquely addressed from 0 to 255. Similarly, a destination address is the address of the output link (in stage three) from which a packet leaves the network. As described in Section 3.3.5, each output link in stage three is uniquely addressed from 0 to 255.

A packet also contains a packet pointer <sup>5</sup> used for referencing in a linked list, which represents a queue.

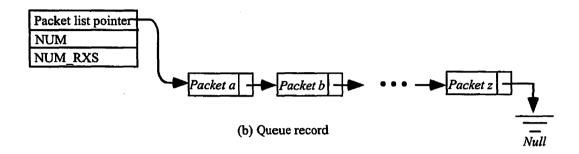

#### 4.4.1.1. Pre-defining Packets as a Stack

Since the packet capacities for all queues in this network system are finite, there is an upper bound for the number of packets  $(MAX\_PACKETS)$  that can circulate within the network at any time.  $MAX\_PACKETS$  can be calculated by summing up the packet capacities of all queues (excluding virtual queues) in the network system. For example, in systems with external queues and unbuffered switches in stage two, there are  $16 \times 16 = 256$  external queues before stage one,  $16 \times 16 = 256$  output queues in stage one and  $16 \times 16 = 256$  output queues in stage three. Note that, in this example, since the switches in stage two are unbuffered, there are no real queues in stage two. Given an external queue capacity of 8 and an output queue capacity of 16, there will be a maximum of  $(8+16+0+16) \times 256 = 10,240$  packets (i.e., total capacity of external queues plus total capacity of output queues in stages one, two and three) circulating within the network at any time.

In order to avoid the need for allocating memory to a packet every time a packet is injected into the network, a stack of packets (referred to as *Packet Stack*) with size equal to *MAX\_PACKETS* (or probably a bit larger) is defined and is initialized with unique *PacketID*'s before the simulation starts. During a simulation, when packets are popped

<sup>&</sup>lt;sup>5</sup>A pointer is defined as a reference (or pointing) to a location of a particular type.

## (a) Packet record

(c) Switch record

FIGURE 4.2. Graphical representation of entities in the network system.

out from the stack, their start time, source address and destination address are initialized and they are injected into the network. Packets removed from the network are labelled as "idle" and are pushed back to the stack. This way, processing time for the allocation of memory to packets during the simulation are saved. Figure 4.3 illustrates this concept graphically.

FIGURE 4.3. Pre-defining packets as a stack.

### **4.4.2.** Queues

Although there are three different types of queues, namely: external input queues, internal output queues, and internal virtual queues, in this switching system, they have the same data structure in this model. Each queue is a record that contains the following fields:

- NUM

- NUM\_RXS

- Packet list pointer

Figure 4.2(b) on page 35 gives a graphical representation of a queue. *NUM* stores the total number of packets in a queue, and *NUM\_RXS* is a counter that counts the number

of packets that have entered the queue during a clock cycle. Consequently, a queue is said to be "full" when NUM is equal to the size of the queue, otherwise, it is said to have "space". Also, an "available" link to a queue can be found when NUM\_RXS is less than the maximum number of packets a queue can receive in each clock cycle. Therefore, a packet may move forward to a queue if there is an available link to the queue and the queue has space.

The packet list pointer points to the first element of a linked list of packets. The linked list represents a queue and is referred to as a packet list. The first element of the list is referred to as the head-of-queue packet. In order to achieve the FIFO property of queues, packets are added to the tail of the list and are removed from the head of the list.

#### 4.4.3. External Input Queues

For a system with external input queues, the queues are modelled as an array (*Ext\_Queue*) with a size equal to the total number of input links in stage one (i.e., 256). Therefore, *Ext\_Queue*[i] corresponds to the external input queue in the ith input link of the network.

#### 4.4.4. Switches

In this system model, both electrical switches and optical switches share the same data structure. Figure 4.2(c) on page 35 provides a graphical representation of a switch. An  $N \times N$  switch is represented as a record that contains the following fields:

- Output\_Queue[N]

- Output\_Link[N]

Output\_Queue is an array of queue records, and Output\_Link is an array of switch pointers. Since each output queue connects to a link and each link connects to a switch in the next stage, each of the queue records in Output\_Queue has a corresponding pointer to a switch in the next stage, which is stored in Output\_Link.

#### 4.4.4.1. Organizing Switches in the Model

As described in Section 3.1, switches in this network system are organized into three stages. The first stage has 16 switches, the second stage has 1, 4 or 16 switches (depending on which system is selected), and the third stage has 16 switches. Switches can, therefore, be organized into a 3x16 two dimensional array, and are referred to by using the following notation:

Switch[Stage #][Switch #]

For example, Switch[2][4] refers to the fourth switch in stage 2.

# 4.5. Network Modelling

With the description of the data structure in the last section, the modelling of the network is described in this section.

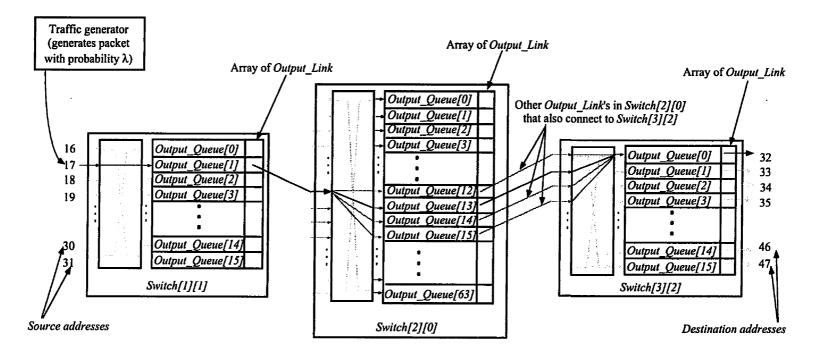

### 4.5.1. Interconnection of Switches in the Model

The switches in this model have to be properly connected before a simulation can start. Each element in the array of switch pointers, *Output\_Link*, in every switch is assigned according to the interconnectivity of the system specified in Chapter 3.

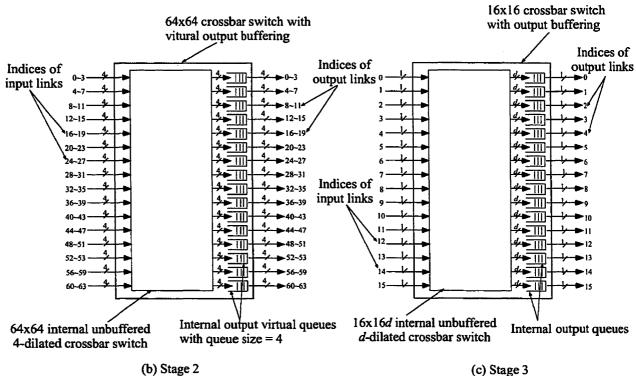

In System II, for example, there are sixteen 16x16 switches in stage one, four 64x64 switches in stage two and sixteen 16x16 switches in stage three. Each of the switches in stage one has 4 output links connected to each switch in stage two, and groups of 4 output links interconnect every switch in stage two to every switch in stage three. Therefore, the first four  $Output\_Links$  of a switch in stage one point to the first switch in stage two  $(S_{2,0})$ , the next four  $Output\_Links$  point to the second switch in stage two  $(S_{2,1})$  and so on. Similarly, the first four  $Output\_Links$  of a switch in stage two point to the first switch in stage three  $(S_{3,0})$ , the next four  $Output\_Links$  point to the second switch in stage three  $(S_{3,1})$  and so on. Queues in stage three are connected to some external devices and point to NULL.

In fact, we can calculate Output\_Link[k] of Queue[k] in Switch[stage #i][switch #j] with the following formulas:

| Computing Output_Link[k] for System I, II, and III |          |           |            |  |

|----------------------------------------------------|----------|-----------|------------|--|

|                                                    | System I | System II | System III |  |

| Stage 1 $(Switch[1][j].Output\_Link[k])$           | 0        | k mod 4   | k          |  |

| Stage 2 $(Switch[2][j].Output\_Link[k])$           | k mod 16 | k mod 4   | k          |  |

| Stage 3 $(Switch[3][j].Output\_Link[k])$           | NULL     | NULL      | NULL       |  |

#### 4.5.2. Packet Routing

## 4.5.2.1. Packet Entering and Exiting the Network

The traffic of the simulator is generated by means of traffic generators. Traffic generators generate packets at the inputs of stage one according to a binomial probability distribution. The probability of generating a packet per clock cycle at an input link is equal

to the offered load ( $\lambda$ ). In fact, a traffic generator at an input will pop a packet from the Packet Stack and inject it into an input link in stage one of the network whenever two conditions are satisfied:

- (i) A sampling of a uniform random variable from [0,1) produces a value less than or equal to the offered load  $\lambda$ , and,

- (ii) (a) for simulating a system that has external queues, there is space in the corresponding queue for the packet, or (b) for those without external queues, there is space in the packet's destination output queue in stage one. A packet is considered dropped (or loss) if this condition is not met. A dropped packet is labelled idle and returned to the packet stack.

Before the packet is injected into the network, the *Start time* and the *Source address* are recorded, and the *Destination address* of the packet is assigned the address of a randomly chosen output link in stage three. Upon arrival of the packet at its destination output, it is pushed back into the *Packet Stack* after statistics are recorded.

#### 4.5.2.2. Switching in Stage One