# Optimization techniques for distributed Verilog simulation

Lijun Li

Doctor of Philosophy

School of Computer Science

McGill University

Montreal,Quebec

March 2008

A thesis submitted to McGill University in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Copyright©2008 Lijun Li

## DEDICATION

To my parents, my dear wife and my lovely daughter.

#### ACKNOWLEDGEMENTS

I'd like to thank my parents first. My father never forgets to mention my PhD progress whenever he has chance to talk with me over the phone. My mum, who almost spoils me, would punish me if I skipped the school. I still remembered how she dragged me to the school when I tried to avoid an exam in a blizzard since I cannot walk in the snow deep as my knee. But my mum said deep snow cannot be an excuse for absence from the school. My father has been working in the elementary school for over 30 years. He thinks of high education over anything else. In the early 1990s, the money spent on my high school and my university education ate up all of our family savings. I could never pay back the debt I own to my parents.

I need to give my sincere thanks to my supervisor, Carl Tropper. Without his financial support and emotional encouragement, I could never finish my PhD thesis. He even allows me to continue my PhD study part-time after I got a job in AMD. Carl will become my role model in his academic seriousness and creative research methodologies.

I'd like to thank to the members of my PhD committee, who steer my research direction and monitor my research progress. Their constructive feed-back made my PhD dream come true.

Thanks to my friends, David Xu, Jun Wang and Hai Huang. It's really nice to work with them in the distributed simulation lab. The laughter after solving the problems in the lab will become a lifetime happy memory. A special thanks need to give to Hai Huang. He developed a nice partitioning framework, based on which life was much easier for my partitioning algorithm research. I would like to thank our system staff. Ron always gave me prompt support when I had problem with the machines and Myrinet in lab 107 and the Linux software tools, eg, latex. Diti Anastasopoulos, Lucy St-James and Lise Minogue gave me full support for my PhD study such as organizing my comprehensive exam, proposal and progress report. Lise Minogue even agreed to be my daughter's guarantor when she applied for her Canadian passport.

Thanks to Steve Williams, who developed the Icarus Verilog simulator and made it public as open source code. Thanks to Lijuan Zhu and his supervisor from Rensselaer Polytechnic Institute, who generously lend us Verilog source code with 1 million gates to facilitate our partitioning experiments.

I am so happy that my daughter (Xinyi Li) came into our life during my PhD study. She slowed down my PhD study but she also brought much happiness to my family. She constantly shifted my attention from my computer to her smiling or crying face. Thanks, my little angel. You keep your dad rejuvenated.

The last but not the least, my wife (Xin Ji), deserves my sincere thanks. She endured the poor but busy life of a PhD student without any complains.

#### **Contribution of Authors**

The results in Chapter 4 have been published in Parallel and Distributed Simulation(PADS), 2003[1]. The extended result has been published in International Journal of Simulation, Systems, Science & Technology, 2003[2]. My coauthors are Hai Huang and Carl Tropper. Hai Huang designed and implemented a framework for the partitioning of DVS, distributed Verilog simulator. He also implemented the classical FM[3] algorithm and the CLIP[4] algorithm. We are grateful to Carl Tropper for suggesting distributed simulation for Verilog language. The experiment result on ISPD98 benchmark circuit did not appear in the thesis since it was done by Hai Huang.

The results in Chapter 5 has been published in Parallel and Distributed Simulation (PADS) 2004. My coauthor is my supervisor, Carl Tropper.

The results in Chapter 6 has been submitted to SCS SIMULATION journal. The preliminary results has been published in Parallel and Distributed Simulation (PADS) 2007[5]. My coauthor is Carl Tropper. All portions of this thesis that have been published were originally written by myself and carefully corrected and reviewed by coauthors. All algorithms mentioned in the thesis are designed on my own and complemented through discussion with Carl Tropper.

#### ABSTRACT

Moore's Law states that computational power will roughly double every 18 months. To the semiconductor designer, this means the never-ending challenge of bringing increasingly larger and more complex ICs (Integrated Circuits) to market. It is well known that the principle bottleneck in circuit design is simulation. Uniprocessor simulators may not be able to keep up with increased demands on them for both speed and memory.

This thesis has three main contributions.

The first contribution is a distributed Verilog simulation environment which can be executed on a cluster of workstations using a message-passing library such as MPI (Message Passing Interface). It employs OOCTW as the synchronization backend and takes advantage of the open source code of Icarus Verilog simulator. It is designed to be flexible for future extension and optimization. To our knowledge, DVS is the first distributed Verilog simulator.

The second contribution is event reconstruction, a technique which reduces the overhead caused by event saving. As the name implies, event reconstruction reconstructs input events and anti-events from the differences between adjacent states, and does not save input events in the event queue. Memory consumption and execution time of event reconstruction are compared to the results obtained by dynamic checkpointing revealing that event reconstruction yields a significant reduction in memory utilization and leads to a faster simulation.

The third contribution is a multiway design-driven iterative partitioning algorithm for Verilog based on module instances. We do this in order to take advantage of the design hierarchy information contained in the modules and their instances. A Verilog instance is represented by one vertex in a circuit hypergraph. The vertex can be flattened into multiple vertices in the event that an adequate load balance is not achieved by instance based partitioning. In this case the algorithm flattens the largest instance and moves gates between the partitions in order to improve the load balance. The algorithm produces a 4.5 fold reduction in cutsize compared to the hmetis [6] partitioning algorithm. The reduction in cut size and the preservation of locality in the design hierarchy lead to a speedup of 1.91 on four machines compared to the sequential simulation.

#### ABRÉGÉ

La Loi de Moore stipule que la puissance des processeurs double approximativement tous les 18 mois. Pour le constructeur de semi-conducteurs, cela équivaut à un constant problème d'apporter des CI (Circuits Integrés) de plus en plus larges et complexes sur le marché. Il est bien connu que le goulet d'étranglement dans la conception de circuits réside dans la simulation. Les simulateurs à simple processeur peuvent ne pas suivre les demandes croissantes pour plus de vitesse et de mémoire. Cette thèse présente un environnement de simulation Verilog avec plusieurs techniques d'optimization. Verilog est une langue de conception digitale couramment utilisée. Une simulation distribuée Verilog peut être exécutée sur un groupe de postes de travail en utilisant une librarie passant des messages telle que IPM (Interface Passant des Messages).

Nous décrivons la reconstruction d'événements, une technique qui réduit l'en-tête causé par une sauvegarde d'événements, et comparons sa consommation de mémoire et son temps d'exécution avec les résultats obtenus par checkpointing dynamique. Comme son nom l'indique, la reconstruction d'événements reconstruit la saisie d'événements et d'anti-événements à partir de la difference entre les états adjacents, et ne sauvegarde pas la saisie d'événements dans la queue des événements.

Nous proposons un algorythme partionné redondant à plusieurs voies et orienté vers le design pour Verilog basé sur des instances de modules. Nous faisons cela afin de profiter de l'information hiérarchique de conception contenue dans les modules et leurs instances. Une instance Verilog est représentée par un vertex dans un circuit hypergraphique. Ce vertex peut etre écrasé en plusieurs vertexs dans le cas où une charge adéquate n'est pas produite par une instance basée sur des partitions. Dans ce cas là l'algorythme écrase la plus grosse instance et déplace les portes entre les partitions afin d'améliorer la charge. Nous présentons nos resultats en utilisant cet algorythme sur un circuit possédant un million de portes décrit sur Verilog.

#### TABLE OF CONTENTS

| DE  | EDICATI   | N                                                                 | ii  |

|-----|-----------|-------------------------------------------------------------------|-----|

| AC  | CKNOWI    | LEDGEMENTS                                                        | iii |

| Co  | ntributio | n of Authors                                                      | v   |

| AE  | BSTRAC    | Γ                                                                 | vi  |

| AE  | BRÉGÉ     |                                                                   | iii |

| LIS | ST OF TA  | ABLES                                                             | XV  |

| LIS | ST OF FI  | GURES                                                             | vii |

| 1   | Introdu   | ction                                                             | 1   |

|     | 1.1       | Motivation of Distributed Verilog Simulation                      | 3   |

|     | 1.2       | Objectives of Distributed Verilog Simulation                      | 4   |

|     | 1.3       | Overview of the Thesis                                            | 4   |

| 2   | Backgro   | ound                                                              | 6   |

|     | 2.1       | A brief history of the semiconductor electronic design automation | 6   |

|   | 2.2     | Modern ASIC design flow                                        | 7  |

|---|---------|----------------------------------------------------------------|----|

|   | 2.3     | The hardware description language                              | 10 |

|   |         | 2.3.1 Verilog                                                  | 10 |

|   | 2.4     | Continuous and discrete event simulation                       | 13 |

|   | 2.5     | Logic Simulation                                               | 16 |

|   |         | 2.5.1 The Logic Simulation Model                               | 18 |

|   |         | 2.5.2 Discrete Event Logic Simulation                          | 18 |

|   | 2.6     | Event-driven Verilog simulation                                | 20 |

| 3 | Paralle | /Distributed logic simulation                                  | 22 |

|   | 3.1     | PDES: Parallel/Distributed discrete event simulation           | 22 |

|   | 3.2     | Conservative Synchronization                                   | 24 |

|   | 3.3     | Optimistic Synchronization algorithm: Time Warp                | 26 |

|   | 3.4     | State of the art of Time Warp                                  | 29 |

|   |         | 3.4.1 Rollback reduction                                       | 29 |

|   |         | 3.4.2 GVT and fossil collection                                | 29 |

|   |         | 3.4.3 Other memory saving techniques                           | 33 |

|   | 3.5     | Parallel and distributed logic simulators                      | 34 |

|   |         | 3.5.1 Parallel and distributed Verilog/VHDL simulators         | 37 |

| 4 | DVS: A  | n object-oriented framework for distributed Verilog simulation | 38 |

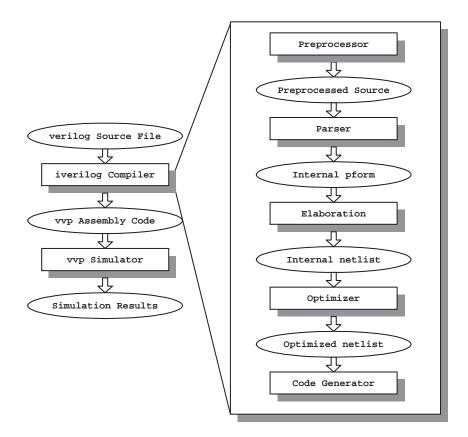

|   | 4.1     | Overview of Icarus Verilog                                     | 38 |

|   |         | 4.1.1 IVerilog Compiler                                        | 39 |

|   |         | 4.1.2 VVP Simulator                                            | 40 |

|   | 4.2     | Architecture of DVS                                            | 41 |

|   | 4.3               | VVP parser                                                                                                                                                                                                                                                                                                                         | 2                                              |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|   |                   | 4.3.1 Structural item: functor                                                                                                                                                                                                                                                                                                     | 3                                              |

|   |                   | 4.3.2 Behavioral item: vthread                                                                                                                                                                                                                                                                                                     | 3                                              |

|   | 4.4               | Partitioner                                                                                                                                                                                                                                                                                                                        | 4                                              |

|   |                   | 4.4.1 Design of Partitioner                                                                                                                                                                                                                                                                                                        | 4                                              |

|   |                   | 4.4.2 Partitioning functors and vthreads                                                                                                                                                                                                                                                                                           | 5                                              |

|   | 4.5               | OOCTW(Object-oriented CTW)                                                                                                                                                                                                                                                                                                         | б                                              |

|   |                   | 4.5.1 Motivation                                                                                                                                                                                                                                                                                                                   | б                                              |

|   |                   | 4.5.2 Class hierarchy of OOCTW                                                                                                                                                                                                                                                                                                     | 7                                              |

|   | 4.6               | Distributed Simulation Engine                                                                                                                                                                                                                                                                                                      | 9                                              |

|   | 4.7               | Optimization to distributed Verilog simulation engine                                                                                                                                                                                                                                                                              | 0                                              |

|   | 4.8               | Preliminary Experiments                                                                                                                                                                                                                                                                                                            | 1                                              |

|   |                   |                                                                                                                                                                                                                                                                                                                                    |                                                |

| 5 | Event F           | Reconstruction in Time Warp 5                                                                                                                                                                                                                                                                                                      | 5                                              |

| 5 | Event F<br>5.1    | Reconstruction in Time Warp       5         Introduction       5                                                                                                                                                                                                                                                                   |                                                |

| 5 |                   | -                                                                                                                                                                                                                                                                                                                                  | 5                                              |

| 5 | 5.1               | Introduction                                                                                                                                                                                                                                                                                                                       | 5<br>7                                         |

| 5 | 5.1<br>5.2        | Introduction                                                                                                                                                                                                                                                                                                                       | 5<br>7<br>8                                    |

| 5 | 5.1<br>5.2        | Introduction       5         Related work       5         Logic simulation and its characteristics       5                                                                                                                                                                                                                         | 5<br>7<br>8<br>8                               |

| 5 | 5.1<br>5.2<br>5.3 | Introduction       52         Related work       57         Logic simulation and its characteristics       57         5.3.1       Characteristics of logic simulation       57                                                                                                                                                     | 5<br>7<br>8<br>8                               |

| 5 | 5.1<br>5.2<br>5.3 | Introduction       52         Related work       57         Logic simulation and its characteristics       57         5.3.1       Characteristics of logic simulation       57         Implementation of Event Reconstruction       60                                                                                             | 5<br>7<br>8<br>0<br>0                          |

| 5 | 5.1<br>5.2<br>5.3 | Introduction       54         Related work       57         Logic simulation and its characteristics       57         5.3.1       Characteristics of logic simulation       57         Implementation of Event Reconstruction       66         5.4.1       Data structure       66                                                 | 5<br>7<br>8<br>0<br>1                          |

| 5 | 5.1<br>5.2<br>5.3 | Introduction       54         Related work       57         Logic simulation and its characteristics       57         5.3.1       Characteristics of logic simulation       57         Implementation of Event Reconstruction       66         5.4.1       Data structure       66         5.4.2       Event annihilation       67 | 5<br>7<br>8<br>8<br>0<br>0<br>1<br>1<br>2      |

| 5 | 5.1<br>5.2<br>5.3 | Introduction54Related work57Logic simulation and its characteristics575.3.1Characteristics of logic simulation57Implementation of Event Reconstruction605.4.1Data structure605.4.2Event annihilation605.4.3Port flag60                                                                                                             | 5<br>7<br>8<br>8<br>0<br>0<br>1<br>1<br>2<br>2 |

|   |        | 5.5.1   | Memory Usage                                                    | 68 |

|---|--------|---------|-----------------------------------------------------------------|----|

|   |        | 5.5.2   | Simulation Time                                                 | 71 |

| 6 | A mult | iway de | sign-driven partitioning algorithm for distributed Verilog simu | -  |

|   | lation |         |                                                                 | 74 |

|   | 6.1    | Introd  | uction                                                          | 74 |

|   | 6.2    | Metric  | cs of partitioning quality                                      | 76 |

|   |        | 6.2.1   | Communication                                                   | 76 |

|   |        | 6.2.2   | load balancing                                                  | 77 |

|   |        | 6.2.3   | Concurrency                                                     | 77 |

|   | 6.3    | Relate  | ed work                                                         | 78 |

|   |        | 6.3.1   | Non-iterative partitioning algorithm                            | 78 |

|   |        | 6.3.2   | Iterative partitioning algorithm                                | 79 |

|   |        | 6.3.3   | Iterative partitioning algorithm utilizing design hierarchy     | 82 |

|   | 6.4    | Motiv   | ation and objective                                             | 85 |

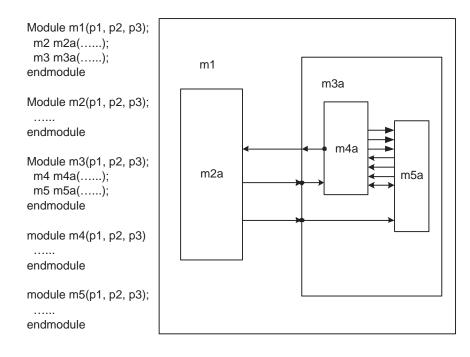

|   | 6.5    | Hiera   | chy in Verilog                                                  | 86 |

|   | 6.6    | Imple   | mentation                                                       | 88 |

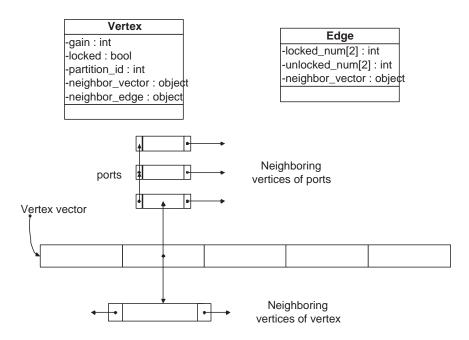

|   |        | 6.6.1   | hypergraph                                                      | 88 |

|   |        | 6.6.2   | data structure                                                  | 90 |

|   |        | 6.6.3   | Verilog parser and hypergraph builder                           | 91 |

|   |        | 6.6.4   | Cutsize and gain from the movement                              | 92 |

|   |        | 6.6.5   | Load balancing constraint                                       | 93 |

|   |        | 6.6.6   | Initial partitioning                                            | 94 |

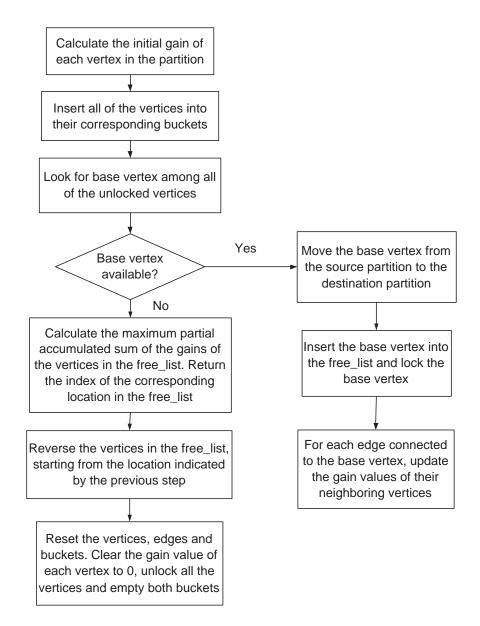

|   |        | 6.6.7   | Iterative moving                                                | 94 |

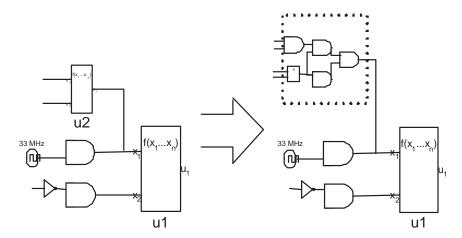

|   |        | 6.6.8   | Flattening                                                      | 98 |

|    |           | 6.6.9 Tie breaking                                           | 99  |

|----|-----------|--------------------------------------------------------------|-----|

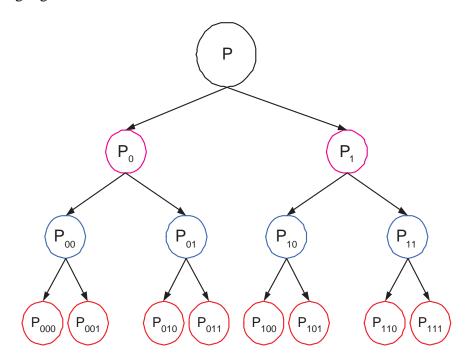

|    |           | 6.6.10 Pairwise multiway partitioning algorithm              | 100 |

|    |           | 6.6.11 Apply pre-simulation to find the optimum partitioning | 103 |

|    |           | 6.6.12 Putting it all together                               | 104 |

|    | 6.7       | Experiments                                                  | 105 |

|    |           | 6.7.1 Cutsize for Viterbi decoder                            | 106 |

|    |           | 6.7.2 Cutsize for ISCAS benchmark circuit                    | 107 |

|    |           | 6.7.3 Presimulation                                          | 109 |

|    |           | 6.7.4 Simulation time                                        | 110 |

|    |           | 6.7.5 Messages and Rollback                                  | 113 |

|    | 6.8       | Conclusion                                                   | 114 |

| 7  | Conclu    | isions and future directions                                 | 115 |

|    | 7.1       | Thesis Contribution                                          | 115 |

|    | 7.2       | Future Directions for Work                                   | 117 |

| Bi | ibliograp | Dhy                                                          | 121 |

| R  | EFEREN    | ICES                                                         | 121 |

#### LIST OF TABLES

| <u>Table</u> |                                                               | page  |

|--------------|---------------------------------------------------------------|-------|

| 2–1          | The logic state and its purpose                               | . 18  |

| 4–1          | Events in distributed Verilog simulation engine               | . 49  |

| 4–2          | Cost of operations in DVS                                     | . 53  |

| 5–1          | The memory usage ratio                                        | . 69  |

| 6–1          | Logic values and their purposes                               | . 89  |

| 6–2          | cutsize with design-driven partitioning algorithm             | . 107 |

| 6–3          | cutsize with hmetis partitioning algorithm                    | . 108 |

| 6–4          | cutsize on ISCAS benchmark circuit s39592                     | . 109 |

| 6–5          | cutsize on ISCAS benchmark circuit s38584                     | . 110 |

| 6–6          | Pre-Simulation time with design-driven partitioning algorithm | . 111 |

| 6–7 | Best partition produced by design-driven partitioning algorithm | • | • | • | <br>• | . 1 | 111 |

|-----|-----------------------------------------------------------------|---|---|---|-------|-----|-----|

|     |                                                                 |   |   |   |       |     |     |

| 6–8 | Simulation time with design-driven partitioning algorithm       |   |   |   | <br>• | . 1 | 111 |

#### LIST OF FIGURES

| Figure |                                                  | pa | ige |

|--------|--------------------------------------------------|----|-----|

| 1–1    | Bottleneck in the design cycle                   | •  | 2   |

| 2–1    | ASIC design flowchart                            | •  | 7   |

| 2–2    | Photograph of Power4 processor by IBM            | •  | 9   |

| 2–3    | Structural and behavioral description of Verilog | •  | 11  |

| 2–4    | Behavioral description of a flip-flop in Verilog | •  | 12  |

| 2–5    | Analog circuit                                   | •  | 14  |

| 2–6    | Analog simulation of the circuit                 | •  | 15  |

| 2–7    | Discrete event simulation algorithm              |    | 17  |

| 2-8    | Logic simulation of a digital circuit            | •  | 19  |

| 2–9    | Verilog simulation pseudo code                   | •  | 21  |

| 3–1    | Overview of the parallel/distributed system      |    | 23  |

| 3–2        | Components of a logical process with Time Warp                                                                                                        | 27             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3–3        | A time diagram with a cut                                                                                                                             | 32             |

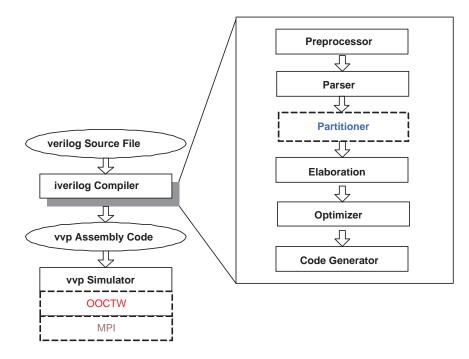

| 4–1        | Architecture for Icarus Verilog                                                                                                                       | 39             |

| 4–2        | Architecture of DVS                                                                                                                                   | 42             |

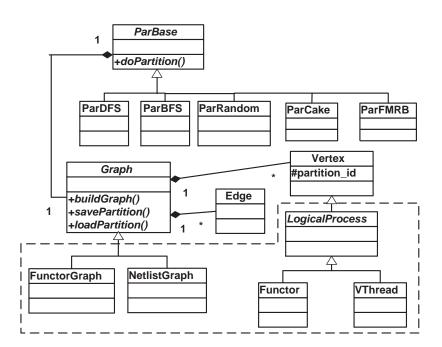

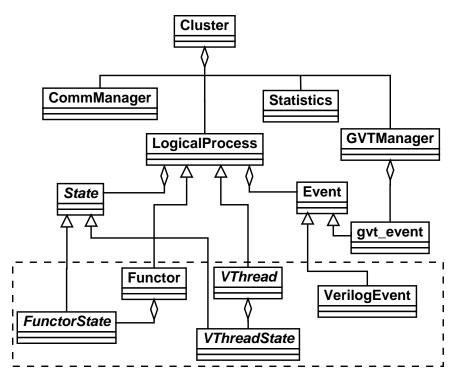

| 4–3        | UML description of partitioner                                                                                                                        | 44             |

| 4–4        | UML description of OOCTW                                                                                                                              | 48             |

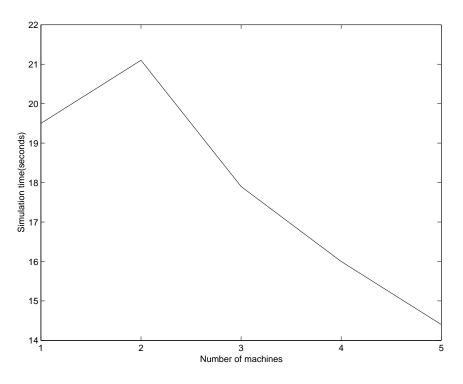

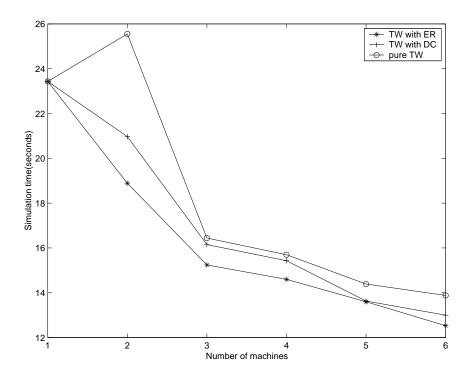

| 4–5        | Simulation time in seconds vs. number of machines                                                                                                     | 53             |

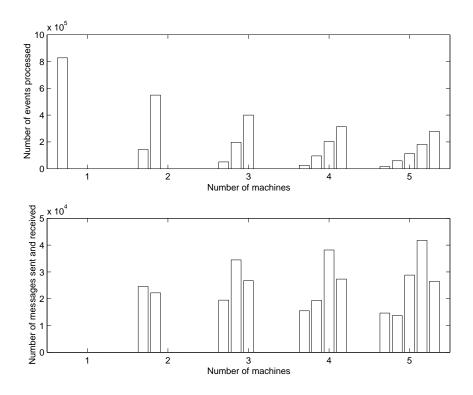

| 4–6        | Number of events processed by every machine(Upper part) and number of messages sent and received(Lower part) by every machine vs. number              |                |

|            | of machines. Note: The two figures use different scale                                                                                                | 54             |

| 5–1        |                                                                                                                                                       |                |

|            | of machines. Note: The two figures use different scale                                                                                                | 59             |

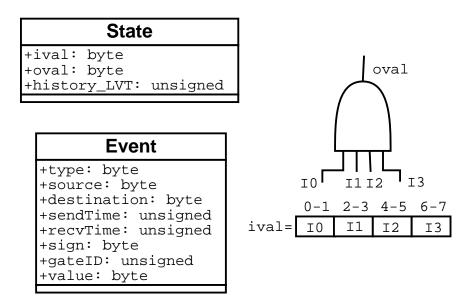

| 5–2        | of machines. Note: The two figures use different scale                                                                                                | 59<br>61       |

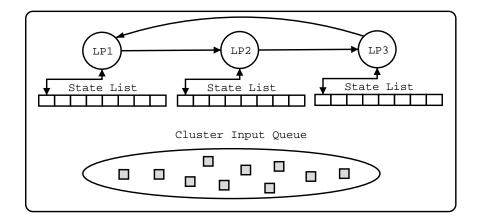

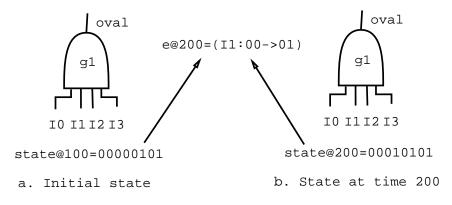

| 5–2<br>5–3 | of machines. Note: The two figures use different scale.       .         The size of the state and the event       .         Cluster structure       . | 59<br>61<br>63 |

| 5–6  | Optimistic LP simulation algorithm                | 67  |

|------|---------------------------------------------------|-----|

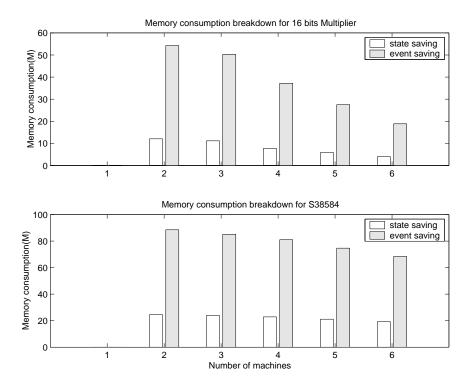

| 5–7  | Memory consumption breakdown                      | 69  |

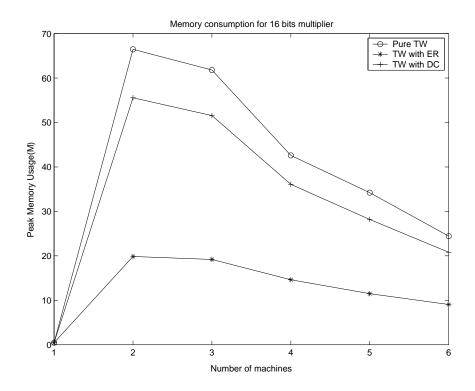

| 5–8  | Memory consumption for 16 bits multiplier         | 70  |

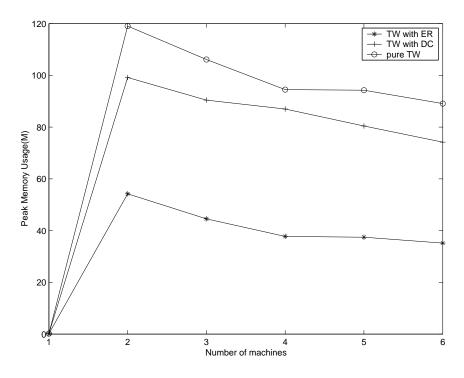

| 5–9  | Memory consumption for S38584                     | 71  |

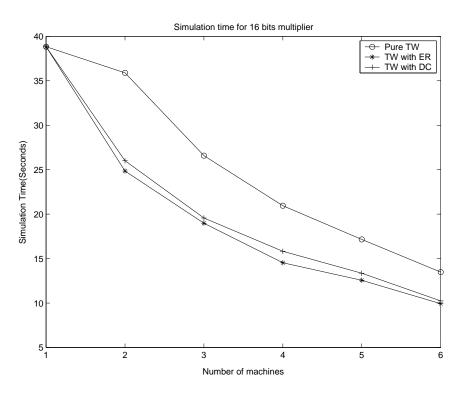

| 5–10 | Simulation Time for 16 bits multiplier            | 72  |

| 5–11 | Simulation Time for S38584                        | 73  |

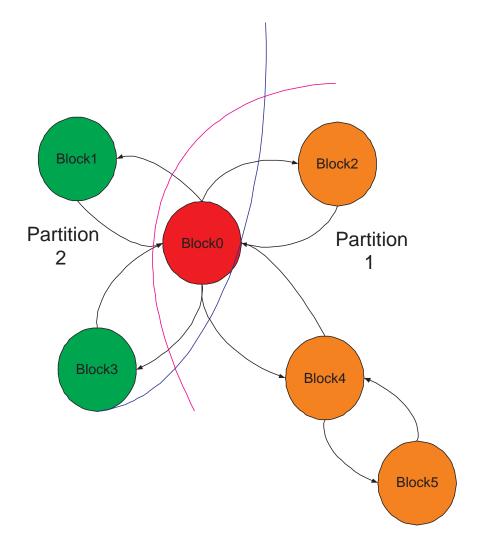

| 6–1  | Verilog module/instances and interconnection      | 87  |

| 6–2  | Hypergraph represented by Verilog                 | 89  |

| 6–3  | Data structure of the partitioning algorithm      | 91  |

| 6–4  | Bucket data structure for vertex movement         | 92  |

| 6–5  | Pseudo code of the initial partitioning algorithm | 95  |

| 6–6  | Initial partitioning result                       | 96  |

| 6–7  | The iterative moving of vertices                  | 97  |

| 6–8  | Flattening of the circuit hypergraph              | 98  |

| 6–9  | Recursive multiway partitioning algorithm         | .01 |

| 6–10 Pairwise multiway partitioning algorithm              | 102 |

|------------------------------------------------------------|-----|

| 6–11 Flowchart of the design-driven partitioning algorithm | 105 |

| 6–12 Simulation time                                       | 112 |

| 6–13 message number during the pre-simulation              | 113 |

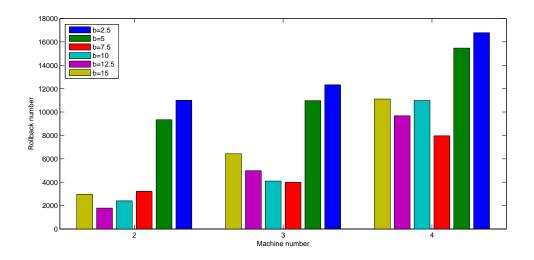

| 6–14 rollback number during the pre-simulation             | 113 |

| 7–1 Replicated logic in the partitioning                   | 118 |

# CHAPTER 1 Introduction

Moore's Law states that computational power will roughly double every 18 months. To the semiconductor designer, this means a never-ending challenge in bringing increasingly larger and more complex IC(Integrated Circuit) to market.

The complexity and size of digital systems described by Verilog continues to grow. The latest Intel dual-core processor has more than 400 million transistors while the Intel quad-processor has more than 800 million transistors. The introduction of the system-on-chip(SoC), which is intended for use in embedded systems and contains CPUs, memory and analog circuitry on a single chip has only served to exacerbate this problem.

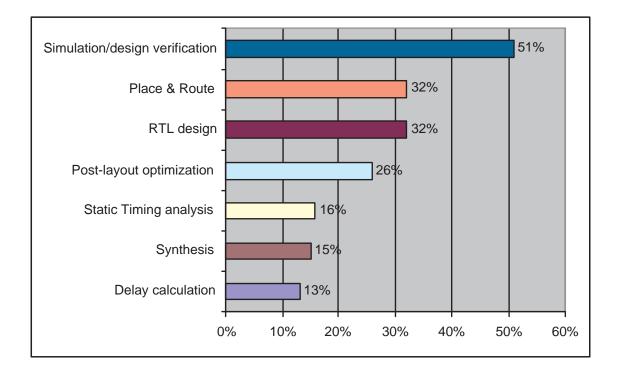

Post-project analysis shows that design and verification account for the majority of the chip development costs. According to a survey of 545 ASIC engineers conducted by EETimes (www.eetimes.com), simulation/verification takes 51% of the design effort on average, as shown in figure 1–1.

Sequential Verilog simulators, or even specialized hardware accelerators, cannot keep up with this pace, and has become a bottleneck of the design process. To accommodate the growing need for increased memory demands as well as the need

Figure 1–1: Bottleneck in the design cycle

for decreased simulation time, it is necessary to make use of distributed and parallel computer systems[7]. Networks of workstations provide a cost-effective environment for distributed simulation. Time Warp[8] is an appealing technique for parallel and distributed logic simulation of VLSI circuitry because it can potentially uncover higher degrees of parallelism.

Verilog[9] is a widely used language for digital circuit design. This thesis presents a description of our research to date on a distributed Verilog simulation framework and describes the next steps in our research program.

#### **1.1** Motivation of Distributed Verilog Simulation

The rewards for successfully developing a distributed Verilog simulator are substantial. Distributed simulation gives us the ability to simulate much larger circuits than is now possible on one workstation, and to do so in a cost-effective manner if we make use of a cluster of workstations as a simulation platform. We will also have the ability to execute simulations much faster than is possible at present, thereby decreasing the time to design a circuit. Moreover, a distributed Verilog simulation is able to overcome the memory bottleneck for very large logic simulations. With the advent of SoCs and the ever increasing number of transistors which can be packed on a chip, distributed simulation can make an important contribution to VLSI design automation. These contributions include:

• Reduced simulation time

By dividing a large simulation computation into many sub-computations that can execute concurrently one can reduce the execution time by up to a factor equal to the number of processors that are used. This may be important simply because the simulation takes a long time to execute, e.g., the simulation of millions gates could take days to finish the simulation in order to verify the correctness of the logic design.

• Overcome the physical limit of memory for 32bit computers As the ASIC design becomes more complex, the memory requirement for gatelevel simulation can easily exceeds the 4G bytes limits of 32bit computers and make the huge investment on the 32bit computing farms in ASIC design industry meaningless. Distributed simulation could take advantage of these 32bit machines and divide a whole design simulation into several partitions, each of which could be able to run in 4G memory limit.

### **1.2** Objectives of Distributed Verilog Simulation

We have four major objectives for our research in distributed Verilog simulation.

- 1. To construct a flexible platform which can make use of open source simulators and allow the addition of new algorithms for distributed Verilog simulation.

- 2. To investigate significant issues in distributed Verilog simulation.

- 3. To develop optimization techniques for optimistic simulations, e.g. memory consumption optimization.

- 4. To develop appropriate partitioning algorithms.

#### **1.3** Overview of the Thesis

In chapter 2, we briefly introduce logic simulation, circuit simulation, hardware design methodologies, hardware design description language and the discrete simulation algorithm employed in the Verilog language.

The chapter 3 is devoted to the introduction of PDES (Parallel Discrete Event Simulation). The two major categories of synchronization algorithm are mentioned, conservative algorithm and optimistic algorithm, also known as Time Warp, are described. The state of art of the Time Warp optimization algorithm is described at the end of this chapter.

The chapter 4 contains the description of DVS, the Distributed Verilog Simulator which we developed in Distributed Simulation Lab of McGill University. The detailed implementation of DVS is explained in this chapter and the preliminary experiment results are also presented. From the preliminary experiment result, we locate the significant issues inside the simulator and proposes our optimization techniques in the next chapters.

The chapter 5 proposes event reconstruction as a memory reduction techniques for DVS. Historically, most of the memory reduction techniques targets memory reduction for the state queue. Our event reconstruction technique targets event queue. This decision is based on our preliminary experiment result which revealed that the event queue actually consumes more memory than the state queue in distributed Verilog simulation.

The chapter 6 proposes a multi-way design driven iterative partitioning algorithms for distributed Verilog simulation, which could obtain a simulation speedup of 1.91 on 4 machines by taking advantages of design hierarchy information contained in the modules and their instances. A Verilog instance is represented by one vertex in the circuit hypergraph, which could be flattened into multiple vertices in the event that an adequate load balance is not achieved. In this case the partitioning algorithm flattens the largest vertex and move vertices between the partitions to improve the load balance.

The last chapter 7 is the conclusion of the thesis along with several suggestions for further research.

## **CHAPTER 2**

## Background

# 2.1 A brief history of the semiconductor electronic design automation

We give a brief introduction of the ASIC design history in the thesis. The readers should refer to [10] for detail information.

In the infancy of integrated circuit design in the 1960s, traditional prototyping and bread-boarding is dominant while software simulation gradually became accepted by the designers of integrated circuits.

In the 1970s and 1980s, the ASIC design industry gradually adopts standard cells as the building block of the integrated circuits. This allows the designers to design their chips in much shorter time periods.

In the 1990s, the logic synthesis tool became the milestone of the ASIC design history. For the first time, the logic synthesis tool abstracts the integrated circuits to higher level and hides the physics of the circuits. Thus, it reduces the design time significantly. The ASIC circuits and its application increases exponentially in this time.

In the 2000s, the ASIC design challenge is the even increasing complexities characterized by Moore's Law: integrated circuits complexity doubles approximately

every 18 months. This imposes difficulty for the verification of the ASIC design since the simulation for the ASIC circuit becomes the bottleneck of the ASIC design.

#### 2.2 Modern ASIC design flow

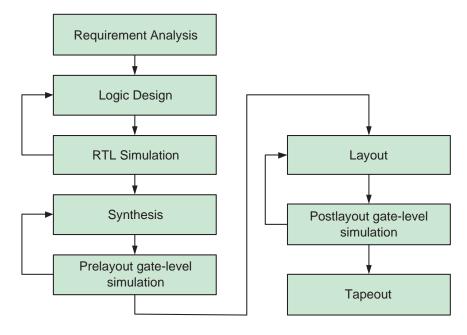

Figure 2–1 shows the steps in the modern ASIC design flow.

Figure 2–1: ASIC design flowchart

• Requirement analysis

The ASIC design starts with understanding of the required functions of the ASIC.

• Logic design

The design engineer constructs a description of an ASIC using a hardware description language such as VHDL[11] or Verilog[9]. This process is analogous to writing a computer program in a high-level programming language. This is usually called the RTL (Register transfer level) design.

• RTL simulation

Functional correctness is verified by simulation. The common way to verify logical correctness is to feed the input vectors to the digital circuit and compare the simulation result with the expected golden data. If the simulation result failed to match the golden data, we should know that something is wrong with the digital circuit design. Golden data is usually generated by the emulation program written in another programming language such as C language.

• Synthesis

A logic synthesis tool, such as Design Compiler[12], synthesizes the RTL design into a netlist of standard cells, such as 2 input NOR gate, 2 input NAND gate, inverters, etc.

• Pre-layout gate-level simulation

The pre-layout gate-level simulation[13] is to the verify the correctness of gate-level netlist generated by the synthesis tool.

Layout

The gate-level netlist is processed by a placement tool which places the standard cells onto a region representing the final ASIC. It attempts to find a placement of the standard cells based on the specified constraints such as area of the chip, wire length between blocks, etc.

The routing tool takes the physical placement of the standard cells and uses the netlist to create the electrical connections between them.

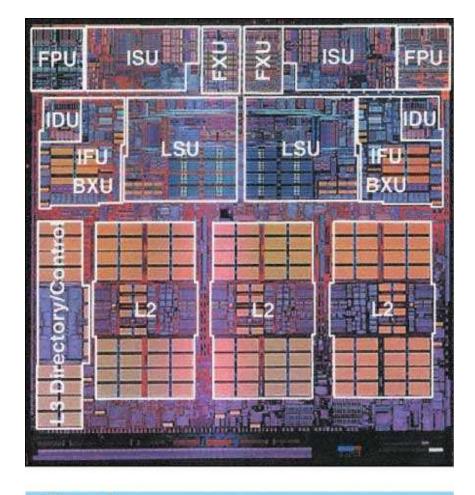

The final output of place and routing is a set of photo-masks enabling a semiconductor fabrication to produce physical ICs. Figure 2–2 shows photograph of Power4 processor by IBM after place and route, courtesy of IBM from http://www.research.ibm.com/journal/rd/461/warno1.jpg.

## Figure 1

POWER4 chip photograph showing the principal functional units in the microprocessor core and in the memory subsystem.

Figure 2-2: Photograph of Power4 processor by IBM

• Post-layout gate-level simulation

After the layout, the netlist is verified by running simulation again to get rid of the potential interconnection or timing problem introduced by layout.

#### 2.3 The hardware description language

"In electronics, a hardware description language or HDL is any language from a class of computer languages for formal description of electronic circuits. It can describe the circuit's operation, its design and organization, and tests to verify its operation by means of simulation."[14]

Contrary to the software programming language, an HDL includes syntax elements to express time, concurrency and connectivity which are the primary attributes of hardware.

A simulator is used to simulate the hardware behaviour described by the hardware description language. The simulator could employ either continuous simulation to simulate the analog circuit or discrete event simulation to simulate the digital circuit, as discussed in the section 2.4.

The two most widely-used hardware description languages are VHDL[11] and Verilog[9]. Since the thesis is about distributed Verilog simulation so we only focus on the introduction of Verilog language. The interested readers could read [11] about VHDL language for detail.

#### 2.3.1 Verilog

The Verilog Hardware Description Language is standardized in IEEE standard #1364-1995. It supports both a behavioral description and a structural description of a

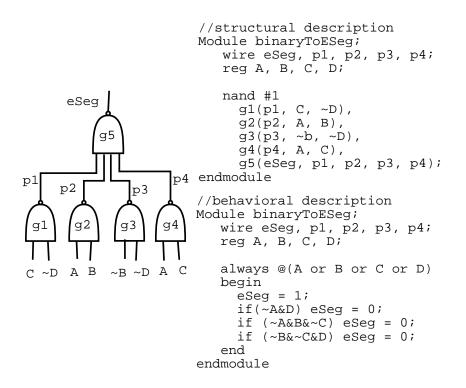

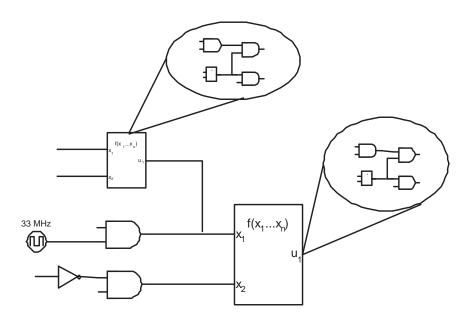

Figure 2–3: Structural and behavioral description of Verilog

digital system. Figure 2–3 shows an example of how Verilog describes an IC design[9]. The figure contains part of a binary to seven segment display driver.

The structural description shows the explicit structure of the circuit and contains all logic gates used and their interconnections. The behavioral description describes the input and output behavior of the circuit. Through the logic synthesis tool, both structural description and behavioral description could produce the same circuit. In Figure 2–3, the right top shows the structural description of the binary to seven segment display driver circuit while the right bottom shows the behavioral description.

A behavioral description of a flip-flop is shown in figure 2-4.

Verilog describes a digital system as a set of modules. Each module has an interface to other modules (referred to as port(s)) and represents a logical unit in a

```

module tff(input t, input clk, output q);

always @(posedge clk)

begin

if (t==1'b1) q<=~q;

else q<=q;

end

endmodule

R Q

```

Figure 2-4: Behavioral description of a flip-flop in Verilog

structural description or in a behavioral description. The modules are typically arranged in a hierarchical manner. The hierarchy can be made use of in partitioning in an effort to minimize inter-processor communication.

Verilog is a concurrent language. A digital system can be conceived of as a set of concurrent processes contained in initial blocks, always blocks and continuous assignments. Wait and event control statements can be used to synchronize the concurrent processes. The existence of concurrent processes in Verilog makes it suitable for distributed simulation[15]. A comprehensive description of Verilog can be found in [9].

A Verilog design consists of a hierarchy of modules. Modules are defined with a set of input, output, and bidirectional ports. Internally, a module contains a list of wires and registers. Concurrent and sequential statements define the behaviour of the module by defining the relationships between the ports, wires, and registers. Sequential statements are placed inside a begin/end block and executed in sequential order within the block. But all concurrent statements and all begin/end blocks in the design are executed in parallel. A module can also contain one or more instances of another module to define sub-behavior. Hierarchy is an important feature of Verilog. With the use of design hierarchy information, the partitioning algorithm do not have to go deep into the lowest level of the circuit if the load balance constraint could be met. Moreover, because of the encapsulation property of the module, the circuit graph is simplified so the partitioning efficiency could be improved. Our multiway design driven partitioning algorithm takes advantage of the module and hierarchy in Verilog and yields a significant reduction in cutsize compared to other partitioning algorithms working on the pure flat netlist. Details of the hierarchy feature of Verilog are described in section 6.5.

A subset of statements in the language is synthesizable. If the modules in a design contain only synthesizable statements, the logic synthesis tool can be used to synthesize the design into a netlist that describes the the logic gates and their connections. The netlist may then be transformed into the photo-mask for the final fabrication.

#### 2.4 Continuous and discrete event simulation

"Simulation[16] is the representation of operations and attributes of one system through the medium of another. The attribute set of the simulation model at any given instant is referred to as the simulation state. The simulation state actually consists of all the states at a particular time."

There are two main categories of simulation: discrete simulation[17] and continuous simulation[18].

In a continuous simulation[18], the simulation state changes continuously with simulation time. The simulation state is characterized by differential equations which describe their behaviour as a function of various parameters. For example, the circuit described at the transistor, resistor and capacitor level could be simulated by the

continuous simulator. The behaviour of all these electronic components are governed by the mathematical formula.

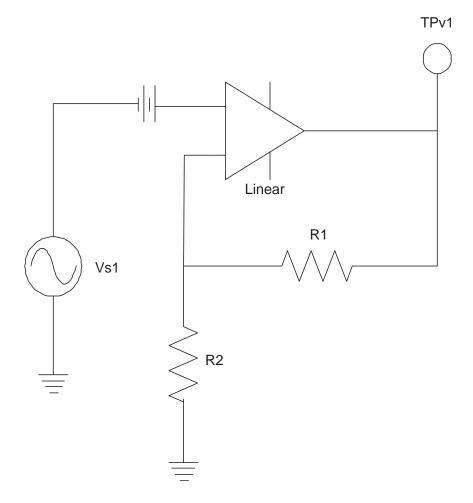

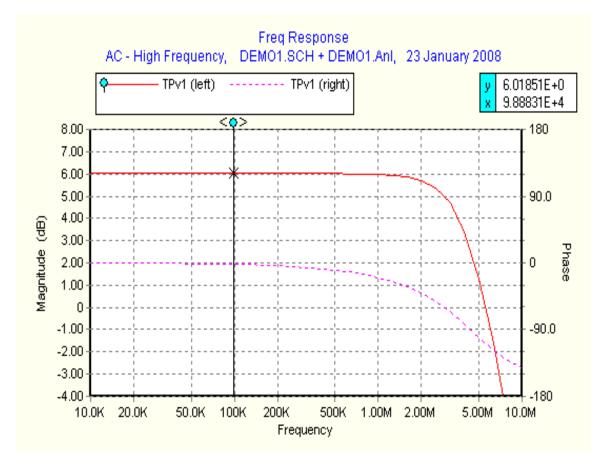

Figure 2–5 shows an example of circuit while figure 2–6 displays the result of continuous circuit simulation. The simulation is done in 5Spice circuit analysis software[19].

Figure 2–5: Analog circuit

Unfortunately the mathematical equations employed by a continuous simulation could be computationally intensive. Therefore, continuous simulation may be slow and

Figure 2–6: Analog simulation of the circuit

is only useful when simulating circuits which are described at a low abstract level such as analog level simulation[20].

In order to overcome the poor simulation speed of the continuous simulation, the discrete simulation is introduced, which is usually faster while providing a reasonably accurate approximation of a circuit system's behaviour.

Discrete simulation is divided into two subtypes, time-driven discrete simulation and event-driven discrete simulation.

Time-driven discrete simulation uses uniform time increments or ticks to advance simulation. Smaller time ticks could produce better precision while slowing down the simulation at the same time. At each simulation tick, the attributes of the models need to be evaluated. For example, in simulation of the trajectory of a projectile, the position and velocity are calculated in each tick by using the forces acting upon the projectile.

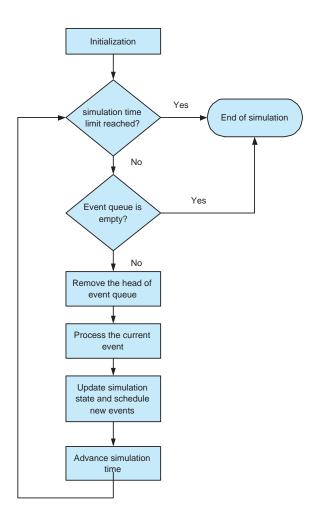

Discrete event simulation (DVES) [17] describes a simulation system in which only events can cause the simulation state to change. An event causes a change of the simulation state. In between events, the state of the simulation does not change. This allows a more efficient simulation than a continuous simulation (or time-driven discrete simulation) because the system state is only evaluated as the result of an event being executed.

Event scheduling normally uses two data structures. One is the state, while the other is the event queue, which is ordered by the timestamps of events. New events are inserted at the bottom of the event queue. An event scheduling algorithm operates by removing events from the event queue and processing them until the simulation finish time is reached or the event queue is empty. As a consequence of processing an event, new events can be scheduled and inserted into the event queue. The timestamp of the processed event is used to advance the simulation time. The simulation algorithm is shown in figure 2–7.

#### 2.5 Logic Simulation

We start the introduction of Verilog simulation from logic simulation of digital circuits since Verilog simulation is actually one type of logic simulation.

Figure 2–7: Discrete event simulation algorithm

Logic simulators are in widespread use as tools used to analyze the behavior of digital circuits. Logic simulators are used in hardware design verification to verify logical correctness and to perform simple timing analysis of logic circuits.

Logic simulators are also used for fault analysis[9]. The simulation could dump the waveform which logs the activity of the related signals in the digital circuits. With the waveform, the ASIC designers could locate the bug in the digital design from simulation without any electronic instrument such as oscilloscope and logic analyzer.

| value                                      | Purpose         | Value Encoding |

|--------------------------------------------|-----------------|----------------|

| 0                                          | Forcing zero    | 00             |

| 1                                          | Forcing one     | 01             |

| Х                                          | Forcing unknown | 10             |

| Ζ                                          | High impedance  | 11             |

| Table 2–1: The logic state and its purpose |                 |                |

#### 2.5.1 The Logic Simulation Model

The basic components of a logic circuit are predictably logic gates -AND, NAND, NOR and OR gates. The circuit is described by a graph or a hypergraph in which the nodes represent gates and the links represent wires. The nodes are modelled by software processes, referred to as logical processes (LPs) in the distributed simulation literature. Incoming channels of an LP correspond to the fanin list of a logic gate while the outgoing channels correspond to its fanout list.

The logic simulation model uses a finite set of values to represent the type of signal propagating throughout the circuit. The 4 values that a signal may have are presented in table 2–1.

A signal change is modelled as an update event containing a timestamp, source and destination gates, an identification and a value which corresponds to the new value of the wire. When an LP receives an update event, it sets its local clock to the the timestamp of the event, evaluates its output and schedules the resulting output change(s) as update events for its fanout list.

#### 2.5.2 Discrete Event Logic Simulation

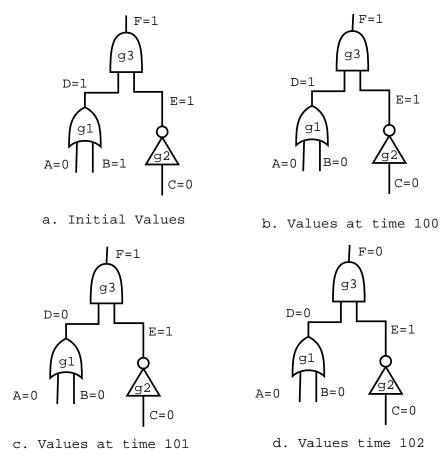

Figure 2–8 represents a simple logic circuit comprised of three gates. The circuit has three inputs (A, B and C), one output (F) and two internal wires (D and E).

Figure 2–8: Logic simulation of a digital circuit

Assume that each gate has a unit delay, i.e. the simulation advance time at each gate is one time unit for each event. Initially, the gates have the values shown in Figure 2–8.a. An event occurs on wire B at time 100, changing it from 1 to 0 as shown in Figure 2–8.b. At time 100, gate g1 is evaluated to see if there's a change on its output D. Since D will change from 1 to 0, this event is scheduled in the future.

At time 101, gate g1's output D will be set to 0 as indicated in Figure 2–8.c and this new value will be propagated to the gates on g1's fanout, g3. Then g3 is evaluated

to see if there will be an output change on F. As can be seen in Figure 2–8.d, F will change from 1 to 0.

# 2.6 Event-driven Verilog simulation

In Verilog, before simulation begins, the design hierarchy is first elaborated . This means all the pieces of the Verilog code (modules/primitives/instances) are put together. The elaboration is similar to linking of the C language. The simulation cycle is then continuously repeated during which events are processed and signals are updated. A Verilog simulation cycle consists of the steps as shown in figure 2–9. The pseudo code of Verilog simulation comes from the Verilog language reference manual[21]. The interested readers should refer [21] for the details.

Time in Verilog simulator has two dimensions, the simulation and delta cycle. Delta cycle is used to distinguish those event with the same timestamp.

In Verilog it is possible to assign a delay mechanism to an assignment statement. Transport delay is characteristic of wires and transmission lines. Inertial delay models the real behavior of logic gates. The timestamp of new scheduled events for a node is the current simulation time plus the delay of the node.

```

while (there are events) {

if (no active events) {

if (there are inactive events) {

activate all inactive events;

}

else if (there are nonblocking assign update events) {

activate all nonblocking assign update events;

} else if (there are monitor events) {

activate all monitor events;

} else {

advance T to the next event time;

activate all inactive events for time T;

}

}

E = any active event;

if (E is an update event) {

update the modified object;

add evaluation events for sensitive processes to event queue;

}

else { /* shall be an evaluation event */

evaluate the process;

add update events to the event queue;

}

}

```

Figure 2–9: Verilog simulation pseudo code

# CHAPTER 3 Parallel/Distributed logic simulation

# **3.1 PDES: Parallel/Distributed discrete event simulation**

Parallel and distributed simulations are widely used to speedup large scale simulation applications. They differ in the computing platform used. A parallel simulation runs on multiprocessor machines in which communication is fast and the memory is usually shared between processors. On the contrary, a distributed simulation runs on separated computer systems connected with network in which the communication overhead is significantly larger than multiprocessor and each computer has its own memory. In the thesis, our computing platform is computer systems connected with Gigabit network so we call our simulation system as distributed simulation system.

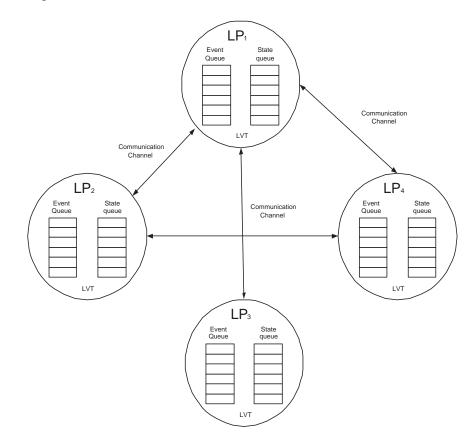

In general, parallel/distributed simulation consist of logical processes(LPs) that represent physical processes of the modelled system. Each LP simulating a portion of the modelled system generates, sends and receives events to and from each other. Thus each LP handles both events generated locally and events triggered by other processes. An LP has an input queue in which event are stored in increasing timestamp order. As in sequential simulation, events are processed in strictly increasing timestamp order. An LP stores its state and maintains the local virtual time (LVT) which is the current simulation time of the LP. The overview of a parallel/distributed system is depicted in figure 3–1.

Figure 3–1: Overview of the parallel/distributed system

Causality is the central issue of the distributed simulation. In order to guarantee the correctness of the distributed simulation, it is necessary to preserve the event causalities across LPs. Lamport[22] suggested the notion of a logical clock which is a monotonically increasing counter in order to maintain causality. Each logical process maintains its own logical clock whose value is used to add a timestamp to the events sent by the process. Lamport also introduced the happened-before relation. It is known as causal ordering which is based on the following two simple intuitive points.

- If two events occur in the same process, they should occur in the order in which the process observes them

- Whenever a message is sent between processes, the event of sending the message always occurs before the event of receiving the message

With the concept of the logical clock and the logical time, physical time can be abstracted since simulation could be guaranteed correct if causality order is maintained. According to how the causality constraint is dealt with, there are two major categories of parallel and distributed simulation protocols, the conservative and optimistic approaches. The conservative approaches process only those events that are guaranteed unable to affect other LPs while optimistic algorithms allow speculation and recover from any resulting causality violations.

# 3.2 Conservative Synchronization

The algorithms described in [23] were perhaps the first synchronization for parallel/distributed simulation. The conservative algorithms are distinguished by their blocking behavior when there are no safe events to process. Safe events are those events such that the simulator is guaranteed not to receive an event with a smaller timestamp. Conservative LPs can execute safe events in increasing timestamp order but must block when there is no safe events.

The advantage of this algorithm is that it is easy to implement and the overhead is very low. However, the blocking behavior somehow limits the concurrency of the parallel/distributed simulation. Another drawback of the algorithm is that deadlock may occur if a collection of LPs are all waiting for a message. Thus, conservative algorithms require a method to either avoid or to detect and break deadlock.

The most common approach to avoid deadlock is the use the null message[23]. Each time an LP sends a message to another, it also sends a "null message" to all other LPs with the same timestamp plus "lookahead".

Lookahead is critical to the performance of the distributed simulation with conservative synchronization. Fujimoto [24] defines lookahead as follows:

"Lookahead characterized the ability of a process to predict future messages that it will send based on knowledge of messages it has already received. In particular, if a process has received all messages with timestamp t or less, and can predict all future messages with timestamp t+lh or less, we say the lookahead of the process is lh"

If the lookahead is poor, the event population will be decreased in the simulation thus the parallelism is reduced since the event processing is delayed and few events are sent out.

The null message is used to notify the receiving LP that it will not receive any messages earlier than the null message from the source LP. Based on the knowledge of LVT plus lookahead from every neighboring LPs, the LP could determine which events are safe to execute.

Null message can create a huge communication overhead, especially in a distributed simulation environment. There have been many attempts to reduce the number of null messages. In [25], the approach is to only send null messages upon request. Whenever an LP is blocking, it sends a request message to its neighboring LPs and then waits for a responding null message which will unblock it. The authors of [26] proposed another approach in which the timestamp and lookahead values are stored separately within null messages. The lookahead value is then sent to other LPs in the piggyback mode. Both normal messages and null message could carry the lookahead value and relay it to the other LPs.

Deadlock detection algorithm[27] deadlock breaking algorithm[28] makes use of knot detection. A knot is defined as a subgraph such that every node in the subgraph can be reached from every other node in the subgraph and no node outside the subgraph is reachable. A knot in the subgraph implies a deadlock in distributed simulation system.

Deadlock breaking algorithm[28] forces the event with the smallest timestamp in all LPs inside the deadlock knot.

In order to overcome the excessive amount of performance-degrading communication caused by deadlock prevention algorithms[27, 28], [29] proposed a protocol that attempts to balance the need for deadlock prevention synchronization information with the cost of providing the information. The author [29] claimed that the protocol is not only more efficient but also can ensure time accuracy.

# 3.3 Optimistic Synchronization algorithm: Time Warp

The most widely known optimistic algorithm is Time Warp. Similar to conservative algorithms, the parallel/distributed system utilizing Time Warp consists of LPs which communicate by messages. Each LP advances its simulation until it detects a violation in local causality. LPs detect violations in causality when they receive a message with a smaller timestamp than their LVT. The message with the smaller timestamp is referred to as a straggler. In Time Warp, LPs perform a rollback operation in which the LP reverts its state to the most recent LVT which had a correct causality and then resumes the simulation from that point. In order to rollback to a previous state, the states of the LP need to be saved periodically (one possibility is after each event). This is referred to as checkpointing.

Time Warp also needs to save all of its output messages. When a rollback happens, the LP sends out "anti-messages" corresponding to the output messages which were previously sent. The anti-messages are used to annihilate the output messages at their destination LPs. Due to the overhead of state saving and output event queue, Time Warp requires a good deal of memory.

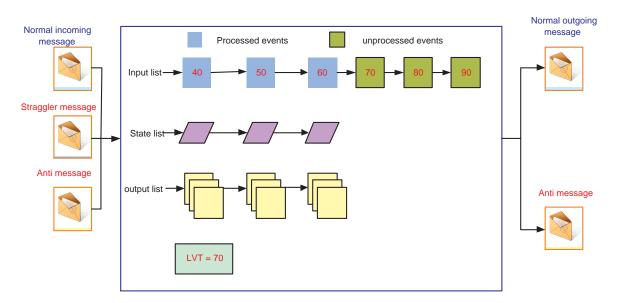

The following diagram 3–2 illustrates the components of a simulation system with Time Warp.

Figure 3–2: Components of a logical process with Time Warp

LPs detect violations in causality when receiving a message whose timestamp is smaller than their LVT. The message with the smaller timestamp is referred to as a straggler. When an LP receives a straggler, the rollback process begins. The process could be summarized as the following steps.

1. State restoration: The LP restores its state to an element in the history event list which has a smaller timestamp than the straggler. The LP then frees the memory occupied by the states which have timestamp larger than the restored state.

2. Anti-messages: The LP sends out anti-messages for each of the elements in the output event queue which were sent after the timestamp of the restored state. The anti-messages are used to annihilate the corresponding message in the destination LP or behave as a straggler to cause the destination LP to rollback.

3. Resume simulation: The LP resumes simulation from the timestamp of the restored state.

The overhead of rollback is huge in terms of inter-processor communication traffic and the computation related to state restoration and anti-messages. Furthermore, the rollback of one LP may cause further rollbacks of other LPs in a chained reaction. This phenomenon is known as cascading rollback[30]. Another interesting problem is called "dog chasing its tail"[31] which can be briefly explained as an erroneous computation wave circling among a few logical processes at a rapid rate. The rollback and cancellation wave is some distance behind the erroneous computation and is trying to outrun it. However, if the rollback and cancellation wave cannot spread faster than the erroneous computation wave, the erroneous computation may never be caught so the simulation will be stuck in the rollback wave

# 3.4 State of the art of Time Warp

Due to the memory overhead and rollback explosion associated with Time Warp, a lot of research[32, 33, 34, 35, 36] has been done to alleviate their effects.

#### **3.4.1 Rollback reduction**

The authors of [32] proposed lazy cancellation. In lazy cancellation, the propagation of anti-messages is delayed until the simulation is resumed after rollback and reaches the LVT of the earliest message in the output message list. At that point, if the newly generated messages differs from the messages in the output list, anti-messages are sent out. Since only the delta of the anti-messages are sent out, lazy cancellation avoids unnecessary anti-message traffic. The overhead of the lazy cancellation is the anti-message list.

#### 3.4.2 GVT and fossil collection

Memory consumption for the history states could be huge. In order to free the memory occupied by the history states which have no use anymore, Global virtual time (GVT) was introduced by Jefferson[8] as follows.

"The GVT at real time r is the minimum of (1) all virtual times in all virtual clocks at time r, and (2) the virtual send times of all events that have been sent but have not yet been processed at time r."

Since no LP would be able to rollback to a time prior to the GVT, each LP could release all states and events earlier than GVT. Events with timestamp less than GVT is referred to as committed events. The procedure to release memory occupied by the committed states and events is called fossil collection. The GVT algorithm is relatively easier in a shared-memory environment than in a distributed-memory environment since there are no events in transit that have been sent out by the source process and have not been received by the destination process. In the shared-memory environment, the minimum of the local virtual time of all logical processes is GVT. However, in a distributed-memory environment, the events in transit makes GVT calculation more difficult. The naive way of calculating GVT in distributed-memory environment is to stop the simulation and restart it after the calculation is done. But this is too expensive so the preferred solution is to obtain an estimate of GVT. The estimation of GVT provides a lower bound on the smallest time stamp of all events no matter they are in transit or waiting to be processed.

[37, 38] solve the problem of events in transit by acknowledging each received event. However, this approach results in large message traffic and could degrade the simulation performance significantly.

Asynchronous token-passing algorithms[39, 40, 41] have been proposed to address the message traffic problem. A token is passed around the processes and the distributed GVT calculation is divided into two phases: the start phase and the stop phase. In the start phase, an initiating process P0 initiates the GVT computation and sends out START token. When a process receives the START token, it forwards it to its successor in the virtual ring topology and starts keeping track of the smallest timestamp of all messages it is sending. After the START token returns to the initiator, the stop phase is launched. The initiator sends a STOP token containing its smallest timestamp which is the minimum of the LVT and the timestamps of events in transit since the START phase. When a process receives a STOP token, it compares its smallest timestamp with the timestamp of the STOP token and sends out the STOP token with the smaller timestamp to its successor. When the initiator receives back the STOP token, the timestamp associated with the STOP token is the new GVT, which will be broadcast to the rest of the processes.

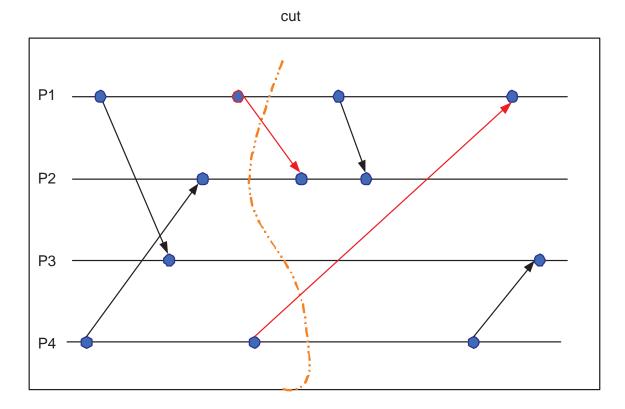

The decentralized GVT algorithm is described by [36], which is based on the distributed snapshots which utilizes the following elements:

- Cut point is an instant separating computation into past and future

- Cut is a set that consists of a cut point for each LP

- Cut message is a message that crosses a cut from past to future

- Cut value is the minimum among the timestamps of both cut messages and all cut points along a cut

Figure 3–3 depicts the relationship between processes and events with a cut for GVT computation. Each horizontal line shows the time of the processes. The circle represents an event and the arrows show the path of causality between events. A cutline divides the events into two disjoint sets, the events occurring before the cut line is defined to be the events in the past while the events occurring after the cut line events in the future.

The implementation of a cut in Mattern's algorithm[36] uses the colouring scheme. Initially all processors are coloured white. A white process sends only white events and a red process sends only red events. Every process counts the number of white events it sends and receives. A red process keeps track of the smallest timestamp of all red events it sends. The algorithm is described as follows,

• 1. The initiator start GVT computation by sending a cut event to its successor and change its color to red

Figure 3–3: A time diagram with a cut

- 2. The receiving process of the cut event will forward it to its successor in the ring and changes its color to red

- 3. When the initiator receives back the cut event, the timestamp of the cut event is the minimum of the LVT of all processes and the smallest timestamp of red events sent by each process

In order to avoid the possibility of an event causing a rollback after it reports its minimum time, at least two cuts are required. The second cut has to be placed "far enough" to the right of the first cut. Mattern[36] accomplishes this through the use of a vector counter. Every process Pi maintains a vector counter to keeps track of the number of white events it has sent to Pj. Every time a white event is received, the

process decrements its vector count V[i]. The cut event will accumulate the vector counters of each process as it goes around the ring of the processes. At the end of the first round, the accumulated vector counter indicates the number of events in transit. If some white events are still in transit, which means the accumulated vector counter is not zero, the second cut is initiated. In this round, the cut event waits at each process until all white events are due at that process. When the cut events returns again to the initiator, the GVT is calculated to be the minimum of the smallest LVT of all processes and the smallest red event timestamp as carried by the cut event.

#### 3.4.3 Other memory saving techniques

A lot of approaches have been developed in order to reduce memory consumption even more, besides the fossil collection. The details of periodic check pointing [42], incremental state saving[42], reverse computation[43] and rollback relaxation[44] will be described in chapter 5. In chapter 5, we also describe a new approach, event reconstruction to reduce memory consumption.

There are several approaches[8, 32] designed to recover the parallel/distributed simulation system when the system runs out of memory. All of them are based on the rollback model and are invoked when an optimistic simulation is either out of memory or cannot use fossil collection to reclaim memory anymore. Message Sendback[8] and Gafni's protocol[32] return messages whenever the distributed simulation system runs out of memory. Message sendback[8] returns the unprocessed input messages back to the sender thus releasing the memory occupied by the messages. [32] expands message list, output message list and history state list. The unprocessed input message

will be returned to the sender. The output messages are also removed by sending the corresponding anti-messages while the history state will also be purged.

Cancelback[45] and artificial rollback[45] are similar to Gafni's protocol[32] in that both of them reclaims memory from input/output event list and the history state list. Instead of sending back input messages, it forces the system to a previous state which has available memory, even if there is no causality violation. Artificial rollback[45] identifies the LPs that are further ahead in simulation time and rolls them back. Cancelback[45] rolls back the simulation indirectly by sending messages to senders indicating that they must reverse certain messages.

# 3.5 Parallel and distributed logic simulators

In his PhD thesis[46], Briner developed a parallel logic simulator based on Time Warp. He makes use of incremental state saving[34], a bounded time window[35] and different synchronization granularities in his simulator. Briner also points out the necessity of efficient partitioning algorithms. Briner achieved the speedup of 23 over sequential simulation on 32 processors of a BBN GP1000 system, running mixed level simulations.

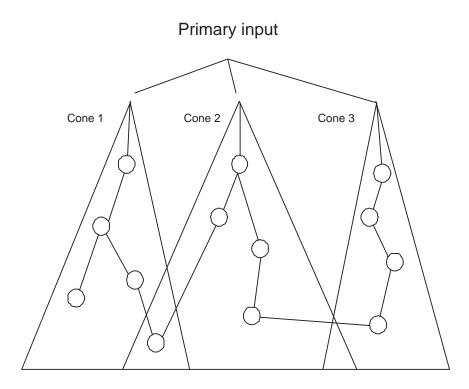

Matsumoto and Taki describe a parallel gate-level simulator[47] based on Time Warp, which obtained more speed-up compared to an asynchronous conservative algorithm and to a synchronous method. As a result, they argue that Time Warp is superior to these methods. An improvement to Time Warp is to send only one antimessage to the affected LPs during rollbacks. This message is the one with the smallest timestamp of all of the antimessages that are sent when using aggressive cancellation. Manjikian and Loucks[48] implemented a parallel gate-level simulator on a network of workstations. They used a hybrid approach for synchronization of the LPs. Individual LPs run in an optimistic way but event messages are only sent to other LPs when they are safe. According to the authors, an important role is played by partitioning algorithms. They used cone partitioning[49] with enhancements in order to incorporate estimated circuit behavior in the partitioning algorithm. Speedups between 2 and 4.2 are achieved on 7 processors from ISCAS89 benchmark circuits. The highest speedup of 4.2 was achieved through cone partitioning algorithm.

Bauer and Sporrer realized a parallel logic simulator[50] based on Time Warp. They used the sequential event-driven gate-level simulation LDSIM[51] as a base for their work. The authors propose incremental state saving to keep the memory overhead low. Luksch implemented a parallel version of LDSIM on the Intel iPSC/860 hypercube[52, 53]. The authors indicate that there may be a huge amount of state information that has to be stored during the course of a simulation. LDSIM achieved speedups between 2 and 4 over the sequential simulation on 12 processors on circuits with 3,500 to 19,200 gates on ISCAS89 benchmark circuits.

Bagrodia [54] developed a parallel gate-level circuit simulator in the Maisie simulation language [55] and implemented it on both distributed and shared memory parallel architectures. They achieved speedup of about 3 on 8 processors of a Sparc1000 for the conservative protocol and about 2 for the optimistic protocol on the four largest ISCAS85 benchmark circuits with gate numbers of 1193, 1667, 2307 and 2418. The K-FM[3] partitioning algorithms were used to partition the circuits.

L. Zhu implemented a parallel logic simulator for million-gate VLSI circuits[56]. The authors claimed that they achieved superlinear speedup for up to 17 processors. The circuit used is synthesized netlist of the Viterbi decoder and the partitioning algorithm is hMetis[6] developed at the University of Minnesota.

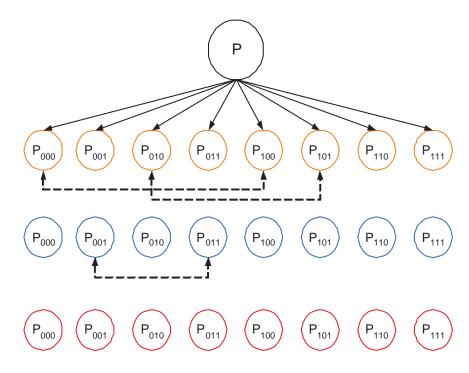

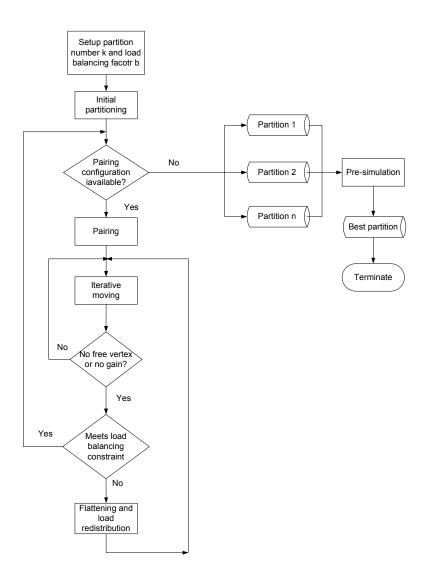

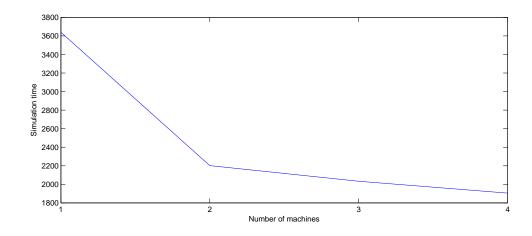

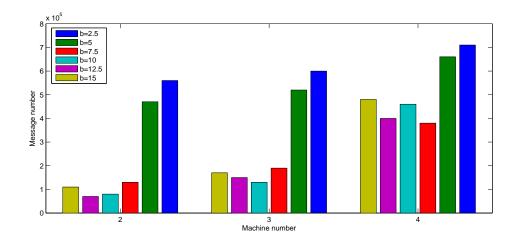

Avril's CTW(Clustered Time Warp)[57] is a hybrid algorithm which makes use of Time Warp between clusters of LPs and a sequential algorithm within the cluster. The authors claimed that CTW[57] is useful in logic simulation of digital circuit where there are a number of LPs having low computational granularity. In the thesis, we extended CTW into an object-oriented version[1] and integrated it with Icarus[58], an open source Verilog simulator.