## A Development Platform for Embedded Wireless Systems

Jean-Samuel Chenard

Department of Electrical & Computer Engineering McGill University Montreal, Canada

October 2005

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering.

© 2005 Jean-Samuel Chenard

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-22636-0 Our file Notre référence ISBN: 978-0-494-22636-0

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **Abstract**

This thesis presents the steps and design decisions followed to develop the architecture of a low-power wireless systems design platform. The design tradeoffs are based on the following characteristics: easy to program interfaces, flexibility, expandability, low cost and low power. The intended users are researchers or students interested in using a robust and reliable platform that enables rapid validation of ideas. A method to integrate printed planar antennas directly on the PCB is also presented along with the analysis of its performance and benefits that it provides to the architecture. Applications using the design platform are also detailed.

## Résumé

Ce mémoire de maîtrise présente les étapes de conception ainsi que les décisions prises dans le développement d'une architecture pour systèmes sans-fils à basse puissance. Les diverses contraintes fûrent : simplicité de programmation des interfaces, flexibilité, capacité d'expansion, faible coût et basse consommation d'énergie. Les utilisateurs ciblés sont des chercheurs ou des étudiants à la recherche d'une plate-forme robuste et éprouvée offrant la possibilité de valider rapidement leurs idées. Une méthode pour intégrer une antenne imprimée à même le circuit imprimé est aussi présentée suivie d'une analyse des performances ainsi que des bénéfices que cette méthode apporte à l'architecture. Finalement, des utilisations de la plate-forme de développement sont détaillées.

## Acknowledgments

First I would like to thank my parents and grand-parents for their dedication to education and moral support throughout my studies. Secondly, I would like to thank my supervisor Dr. Željko Žilić for his support and advice during my Master's degree program. His strong commitment to bring out the best in every publication and his thorough review and insightful advice was instrumental to bring our work to world-class recognition.

I thank my friend and colleague Milos Prokic for his help in writing firmware drivers and for all those fruitful discussions that sparked so many great ideas. I thank Chun Yiu Chu for his contribution and dedication on our joint project of developing a new design methodology for printing antennas on PCB. I also thank Chun Yiu's supervisor Dr. Milica Popović for her review of our antenna designs and support. My colleagues Ahmed Abdel-Ati, Attanu Chattopaday, Usman Khalid, Eugene Kim and Rong Zhang have all helped me in the implementation, debugging or integration of various elements of this project. I must acknowledge the help from our lab technicians Bob Thompson and Paul Peltola for handling the logistics of ordering the parts for the PCB kits and for their insightful suggestions. I wish to thank all the Microprocessor Systems students that provided constructive feedback and did amazing projects with our hardware. I am grateful towards the Fonds Québécois de la Recherche sur la Nature et les Technologies and towards my supervisor for their financial assistance during my degree.

Finally, I must deeply thank my wife Hsin Yun Yao for her support, guidance and help during my master's studies.

## Contents

| 1 | Intr | oducti                          | on                                                           | 1  |

|---|------|---------------------------------|--------------------------------------------------------------|----|

|   | 1.1  | Motiva                          | ation                                                        | 1  |

|   |      | 1.1.1                           | Overview                                                     | 1  |

|   |      | 1.1.2                           | Sensor Networks                                              | 2  |

|   |      | 1.1.3                           | Microelectronics Systems Education and Research Applications | 2  |

|   | 1.2  | Thesis                          | Overview                                                     | 3  |

| 2 | Lite | rature                          | Review                                                       | 5  |

|   | 2.1  | Wirele                          | ess Sensor Networks                                          | 6  |

|   |      | 2.1.1                           | Micro-controller Selection                                   | 6  |

|   |      | 2.1.2                           | RF Transceivers                                              | 8  |

|   |      | 2.1.3                           | Battery Technology                                           | 9  |

|   | 2.2  | Softwa                          | are Requirements                                             | 10 |

|   | 2.3  | Printe                          | d Circuit Board Design                                       | 11 |

|   |      | 2.3.1                           | General Design for Manufacture and Assembly                  | 11 |

|   |      | 2.3.2                           | Printed Antenna Design                                       | 12 |

|   | 2.4  | Educa                           | tion                                                         | 12 |

| 3 | Sys  | $\mathbf{tem} \ \mathbf{A}_{1}$ | rchitecture                                                  | 14 |

|   | 3.1  | System                          | n Overview                                                   | 14 |

|   | 3.2  | Labora                          | atory Setup                                                  | 16 |

|   | 3.3  | Main ?                          | Board                                                        | 17 |

|   |      | 3.3.1                           | Programmable Logic Integration                               | 18 |

|   |      | 3.3.2                           | Built-in Programmer                                          | 18 |

|   |      | 3 3 3                           | User Interface and Sensor Connection                         | 10 |

Contents

|   |     | 3.3.4  | Power Supply                                                   |

|---|-----|--------|----------------------------------------------------------------|

|   | 3.4 | Screen | Boards and Touch Panel                                         |

|   |     | 3.4.1  | Liquid Crystal Display (LCD) Technology                        |

|   | 3.5 | Radio  | Frequency Board                                                |

|   |     | 3.5.1  | 2.45 GHz Radio Transceiver                                     |

|   |     | 3.5.2  | Printed Antenna                                                |

|   | 3.6 | Softwa | are Support Requirements                                       |

|   |     | 3.6.1  | Memory Requirements                                            |

|   |     | 3.6.2  | Remote Debugging Capability                                    |

|   |     | 3.6.3  | Validation Suite                                               |

| 4 | Des | ign De | etails 28                                                      |

|   | 4.1 | Main 1 | Board                                                          |

|   |     | 4.1.1  | Power Source Details                                           |

|   |     | 4.1.2  | Microcontroller                                                |

|   |     | 4.1.3  | Microcontroller Peripherals                                    |

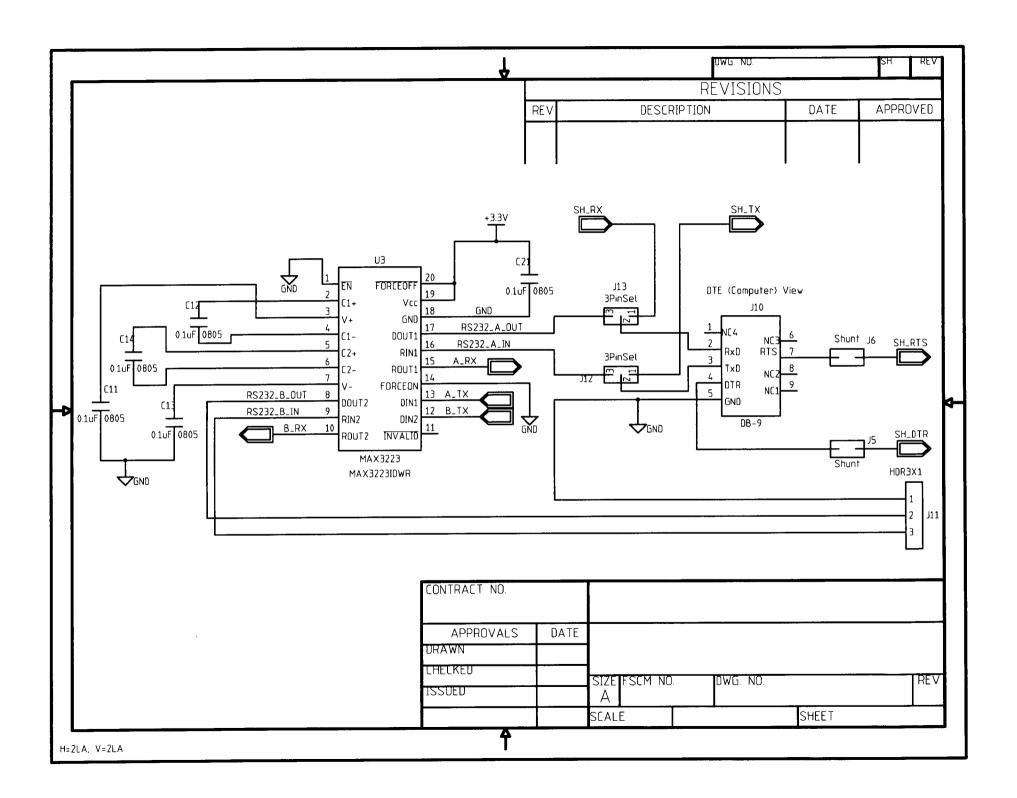

|   |     | 4.1.4  | Serial Interface                                               |

|   |     | 4.1.5  | Programmable Logic                                             |

|   |     | 4.1.6  | Integrated Device Programmer                                   |

|   |     | 4.1.7  | Multimedia Card and iButton                                    |

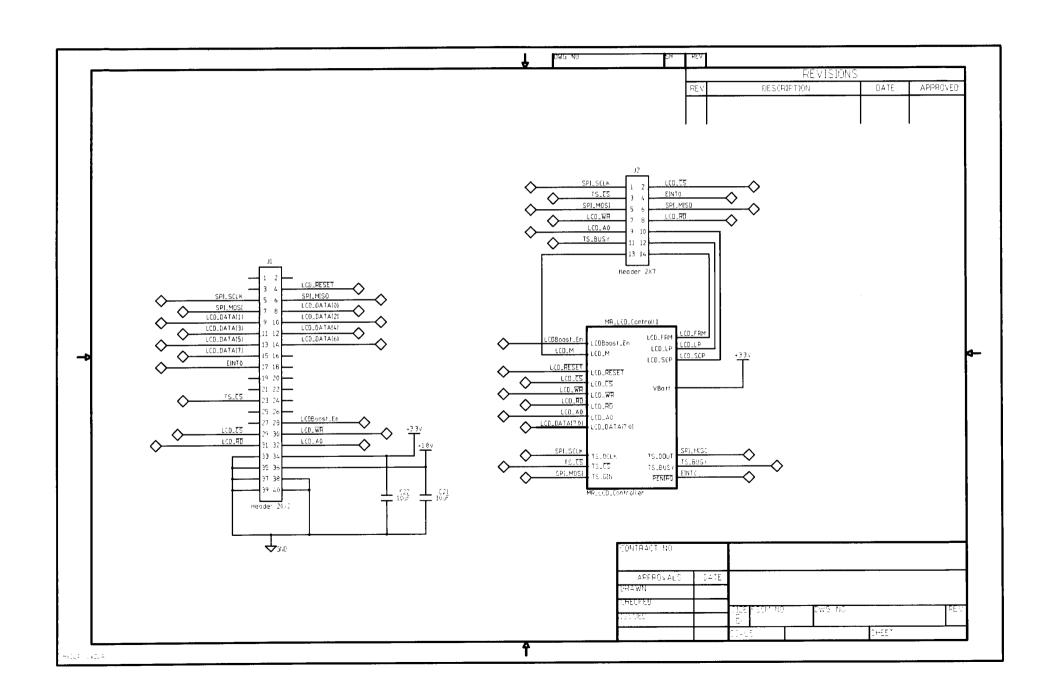

|   | 4.2 | Touch  | Screen Board and S1D13700 LCD Controller IC                    |

|   |     | 4.2.1  | Voltage Booster                                                |

|   |     | 4.2.2  | LCD Panel Interface                                            |

|   | 4.3 | RF Tr  | ansceiver Board                                                |

|   |     | 4.3.1  | Antenna Design Methodology                                     |

|   |     | 4.3.2  | Intrinsic Antenna Characteristics                              |

|   |     | 4.3.3  | Antenna Range                                                  |

|   |     | 4.3.4  | Balun Circuit                                                  |

|   |     | 4.3.5  | Balun Circuit Performance Degradation and Analysis 45          |

|   | 4.4 | PCB I  | Design                                                         |

|   |     | 4.4.1  | PCB Design Flow and Tools                                      |

|   |     | 4.4.2  | Design Methods to Reduce Electromagnetic Interference (EMI) 48 |

|   |     | 4.4.3  | Signal Integrity                                               |

| 4.5 Lithium-Ion-Polymer Ultra-Low Power Prototype 4.5.1 Lithium Battery and Charging Circuit 4.5.2 Current Measurement  5 Applications of the Wireless Systems Development Platform 5.1 Microprocessor Systems Teaching Kit 5.2 Microprocessor Systems Laboratory Course 5.2.1 Student Projects 5.3 Integrated Application - Conference Manager  6 Conclusion and Future Work 6.1 Summary 6.2 Future Work | vi    |                                                         |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------|------------|

|                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5   | Lithium-Ion-Polymer Ultra-Low Power Prototype           | 51         |

|                                                                                                                                                                                                                                                                                                                                                                                                           |       | 4.5.1 Lithium Battery and Charging Circuit              | 52         |

|                                                                                                                                                                                                                                                                                                                                                                                                           |       | 4.5.2 Current Measurement                               | 53         |

| 5                                                                                                                                                                                                                                                                                                                                                                                                         | App   | olications of the Wireless Systems Development Platform | 54         |

|                                                                                                                                                                                                                                                                                                                                                                                                           | 5.1   | Microprocessor Systems Teaching Kit                     | 54         |

|                                                                                                                                                                                                                                                                                                                                                                                                           | 5.2   | Microprocessor Systems Laboratory Course                | 54         |

|                                                                                                                                                                                                                                                                                                                                                                                                           |       | 5.2.1 Student Projects                                  | 56         |

|                                                                                                                                                                                                                                                                                                                                                                                                           | 5.3   | Integrated Application - Conference Manager             | 57         |

| 6                                                                                                                                                                                                                                                                                                                                                                                                         | Cor   | nclusion and Future Work                                | <b>5</b> 9 |

|                                                                                                                                                                                                                                                                                                                                                                                                           | 6.1   | Summary                                                 | 59         |

|                                                                                                                                                                                                                                                                                                                                                                                                           | 6.2   | Future Work                                             | 59         |

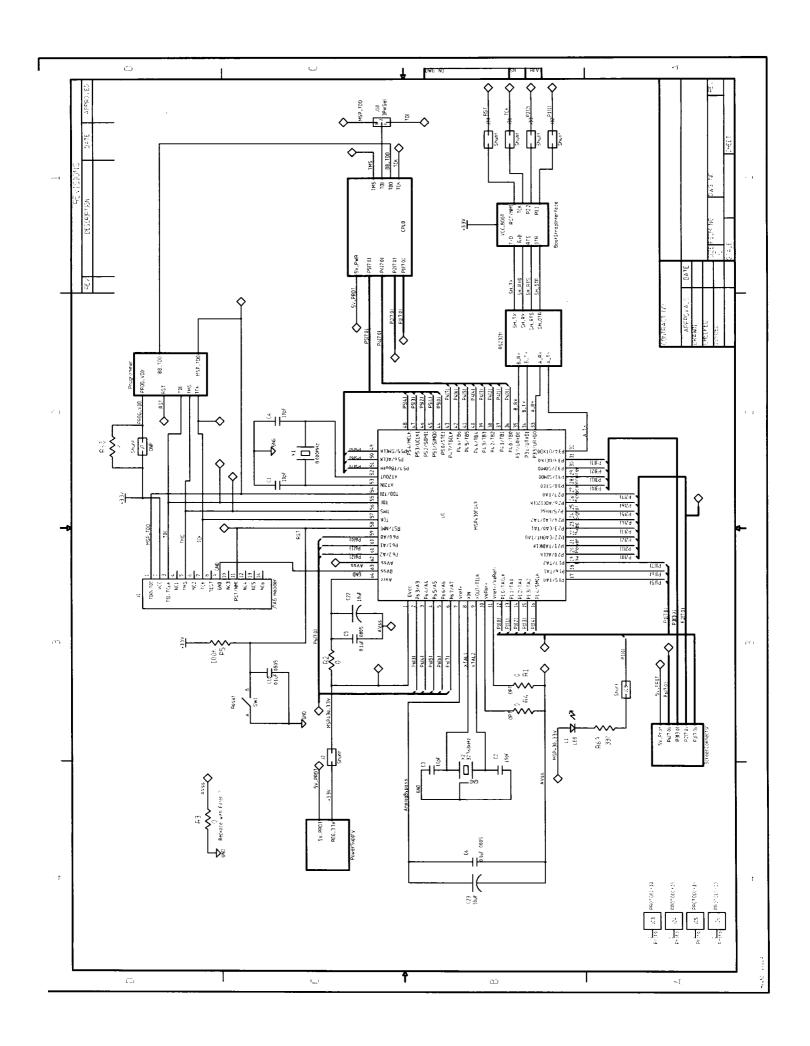

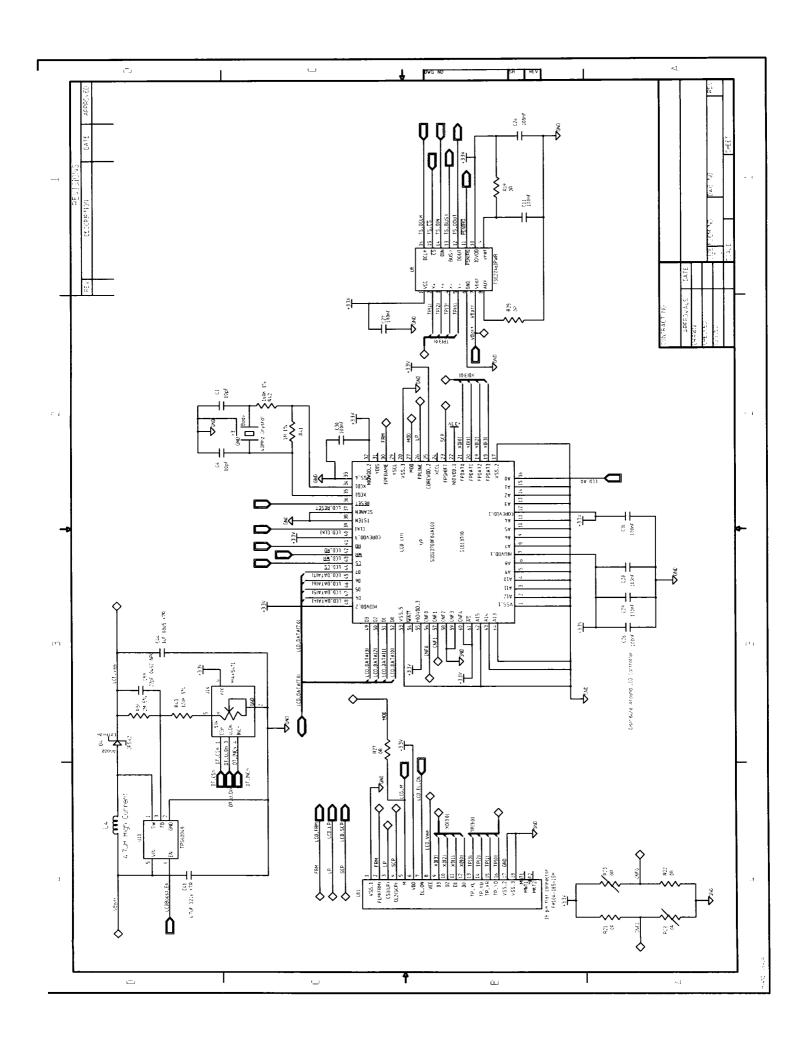

| A                                                                                                                                                                                                                                                                                                                                                                                                         | Mc    | Gumps Schematics                                        | 61         |

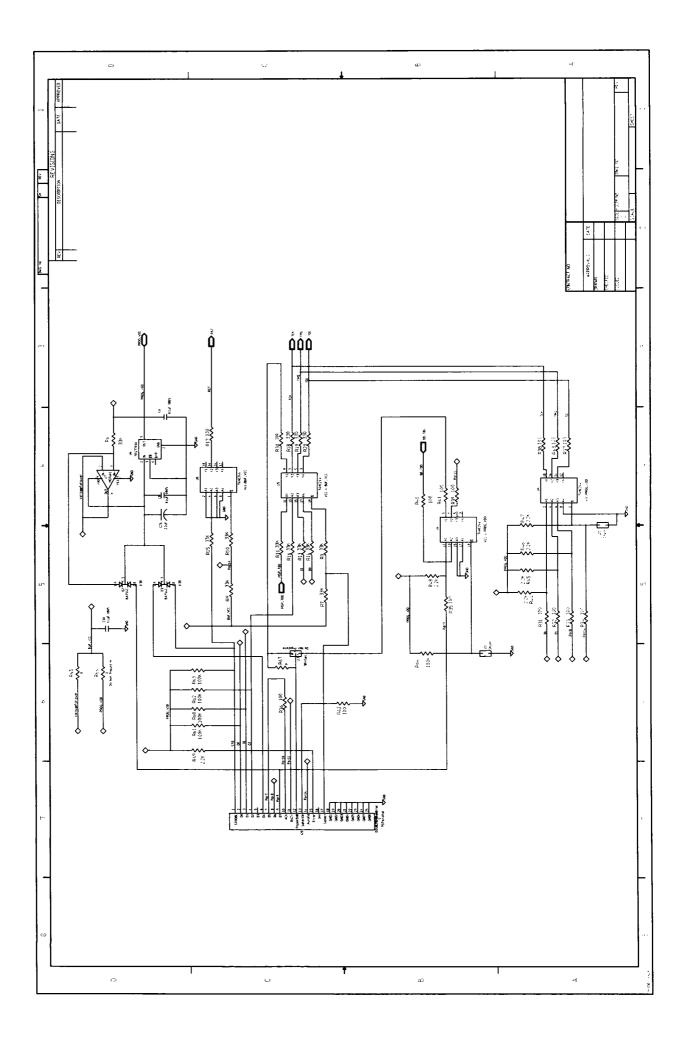

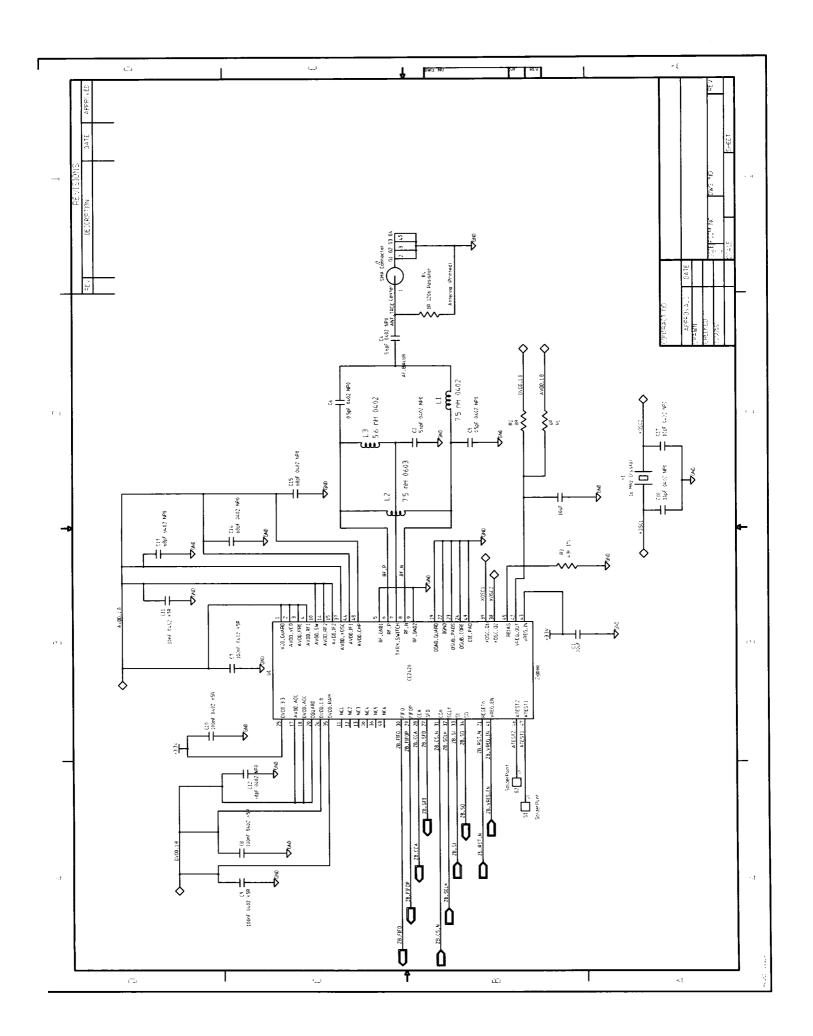

| В                                                                                                                                                                                                                                                                                                                                                                                                         | Eps   | son S1D13700 160x160 Screen Board Schematics            | 69         |

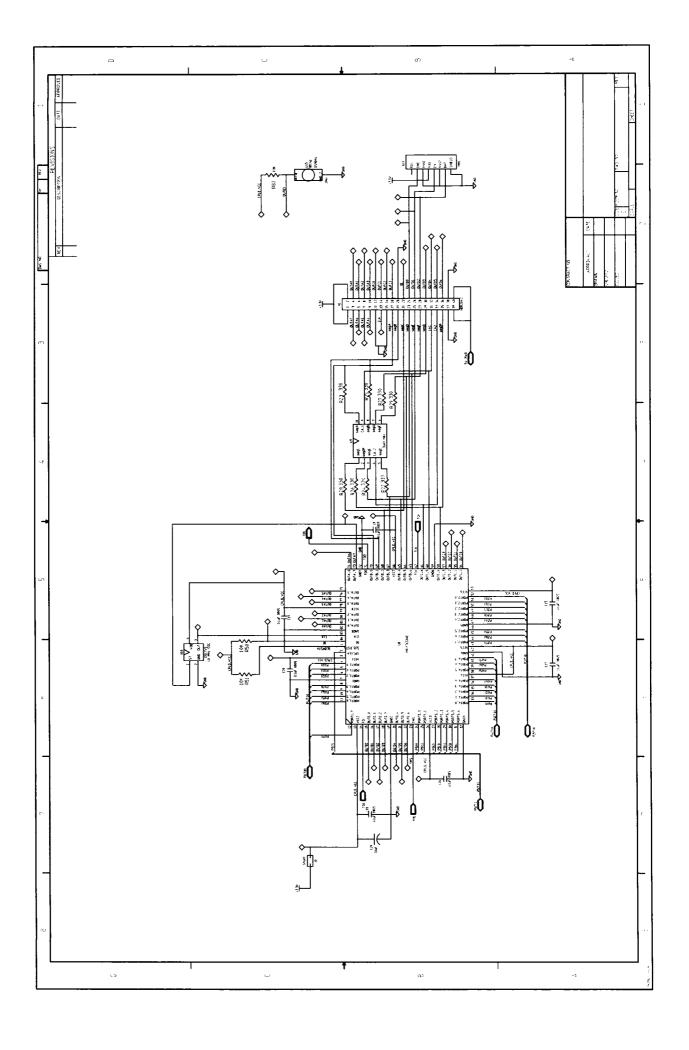

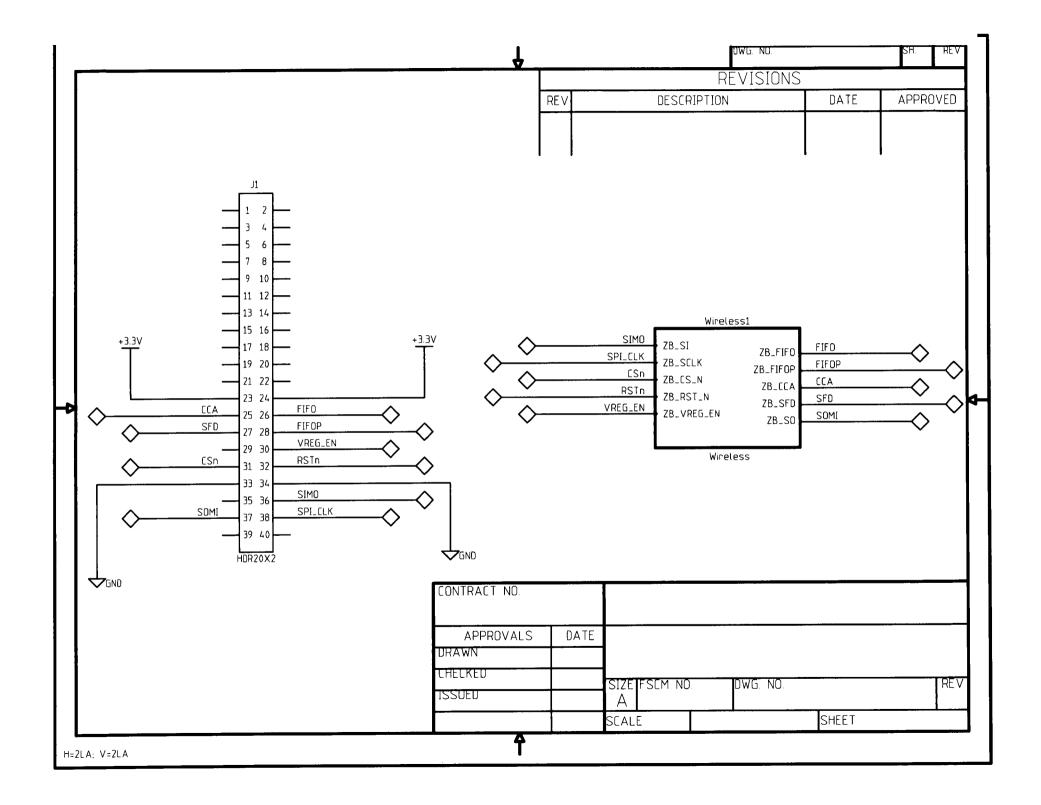

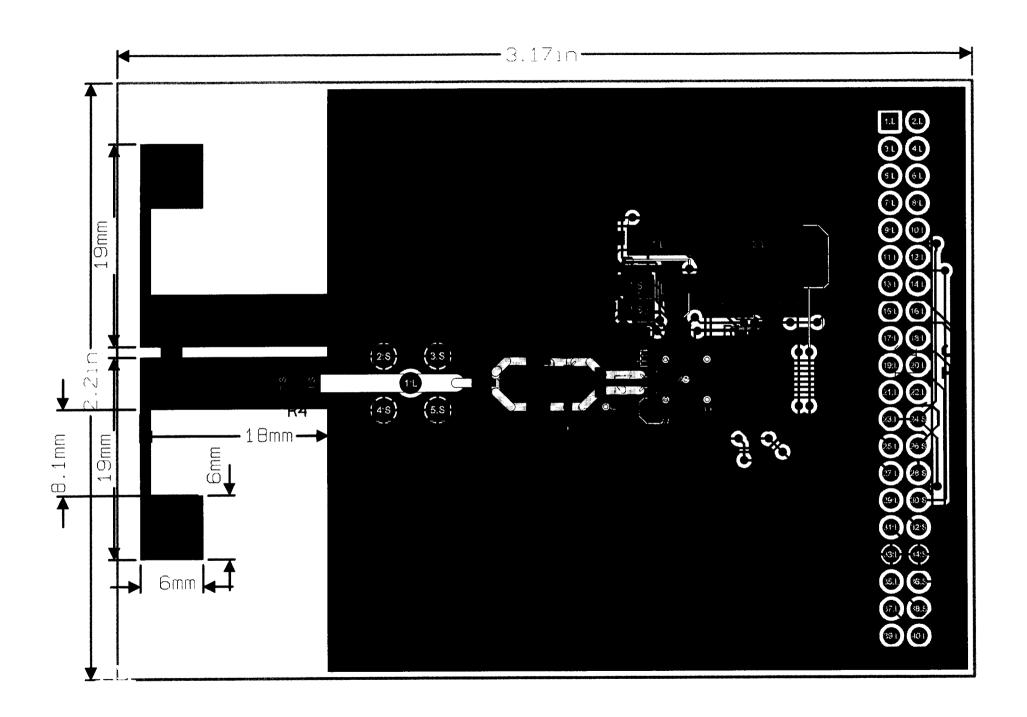

| $\mathbf{C}$                                                                                                                                                                                                                                                                                                                                                                                              | Mc    | Zig RF Screen Board Schematics and Layout               | 72         |

| $\mathbf{R}_{0}$                                                                                                                                                                                                                                                                                                                                                                                          | efere | nces                                                    | 76         |

# List of Figures

| 3.1  | Sensor Network Topology                                    | 15 |

|------|------------------------------------------------------------|----|

| 3.2  | Student Lab Setup                                          | 16 |

| 3.3  | LCD Segments and TAB LCD Unit                              | 21 |

| 3.4  | 802.15.4 Device Software Layers                            | 26 |

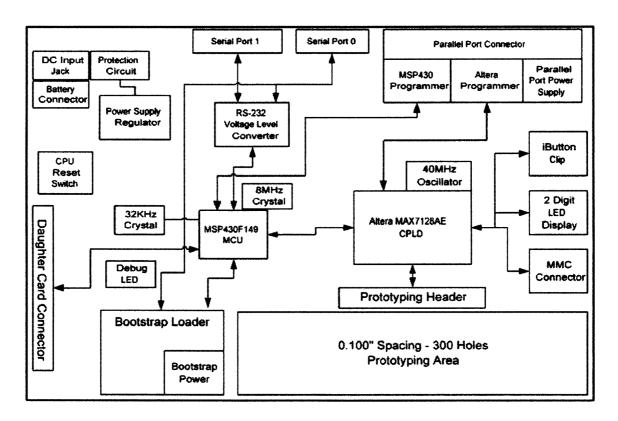

| 4.1  | Main Board (McGumps) Block Diagram                         | 29 |

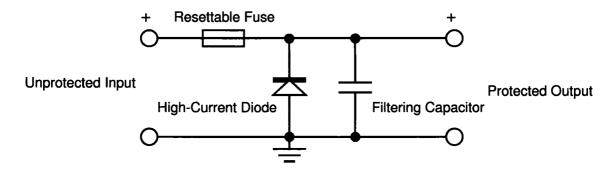

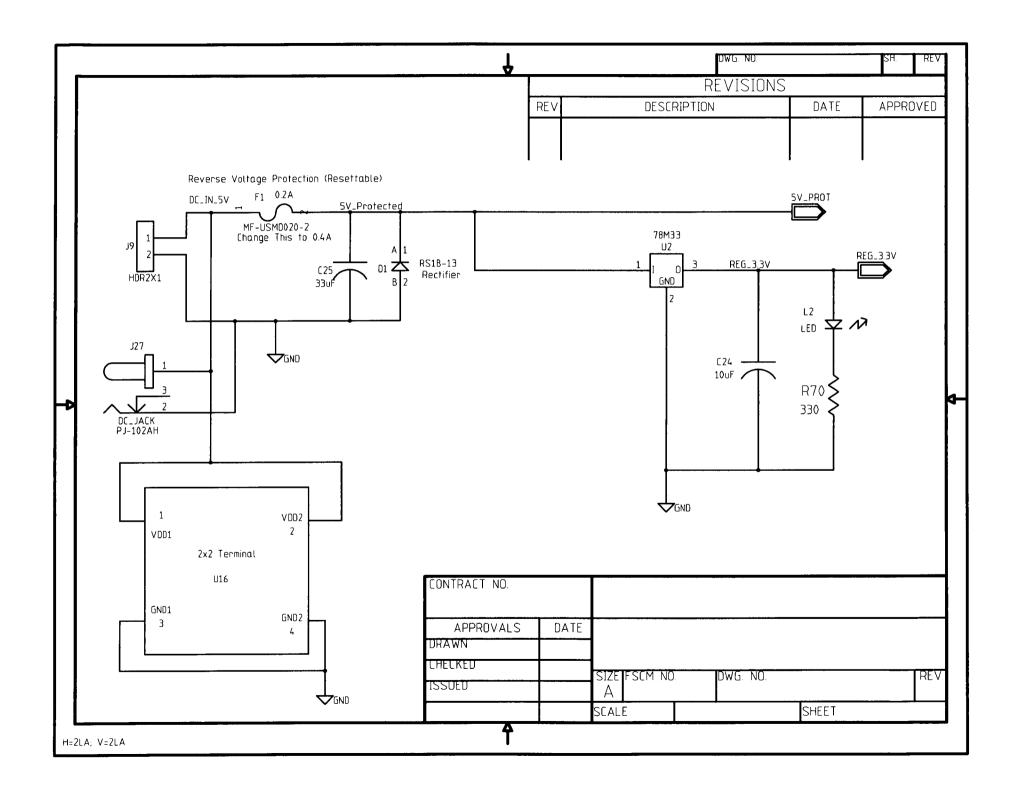

| 4.2  | McGumps Polarity Reversal Protection Circuit               | 30 |

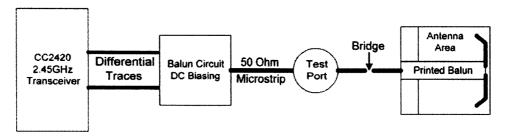

| 4.3  | System Level Balun Antenna Feed Network and Balun          | 40 |

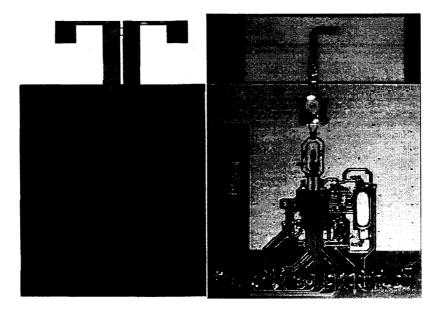

| 4.4  | McZig Simulation Model and Photograph                      | 41 |

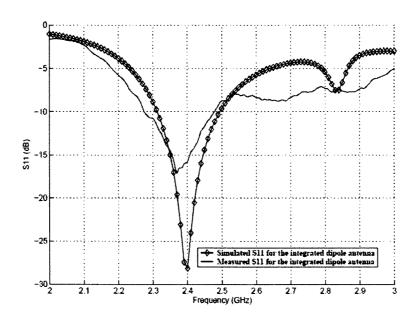

| 4.5  | Antenna predicted and Measured S11 Response                | 42 |

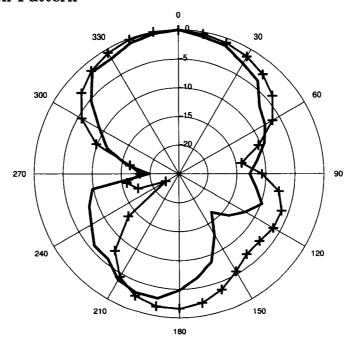

| 4.6  | Normalized E-Field Intensity Along the E-Plane (dB)        | 43 |

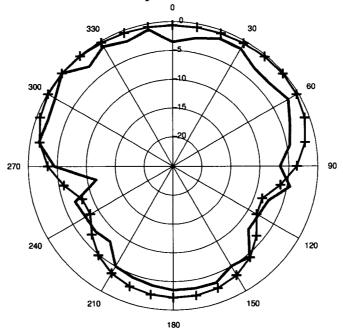

| 4.7  | Normalized E-Field Pattern on the H-Plane (dB)             | 44 |

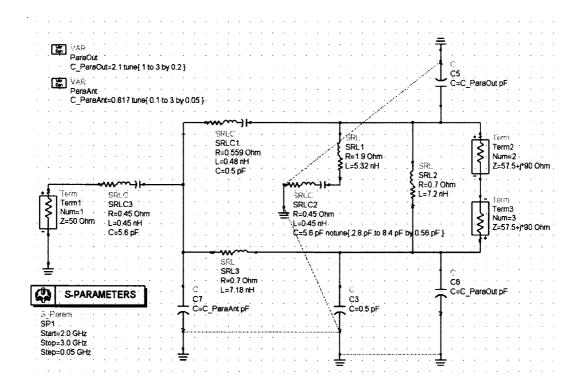

| 4.8  | ADS Model of the RF Transceiver Board Balun Circuit        | 46 |

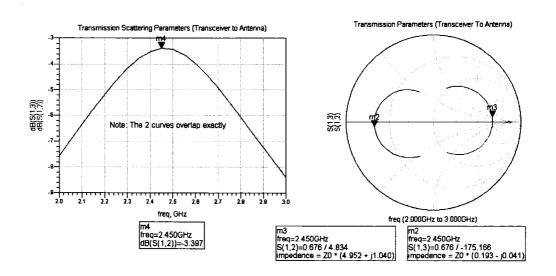

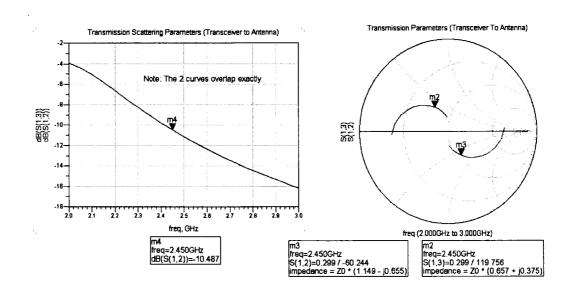

| 4.9  | Balun Circuit Simulation with 2.1 pF Parasitic Capacitance | 47 |

| 4.10 | Balun Circuit Simulation with 3.5 pF Parasitic Capacitance | 48 |

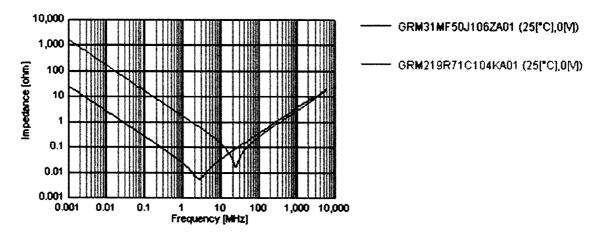

| 4.11 | Impedance of $10\mu F$ and $0.1\mu F$ versus frequency     | 49 |

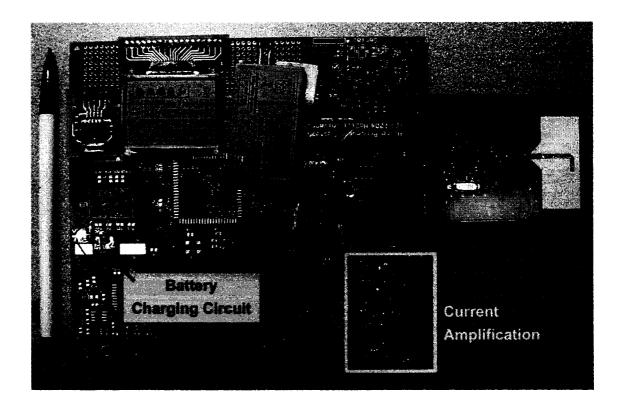

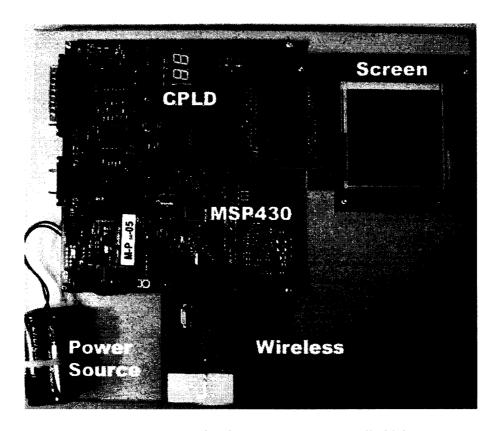

| 4.12 | Ultra-Low Power Version of McGumps with LCD Display        | 51 |

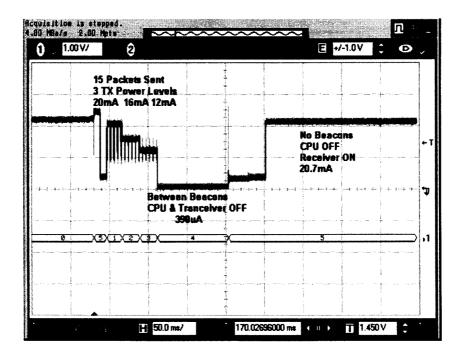

| 4.13 | Dynamic current consumption of Low-Power Sensor Node       | 53 |

| 5.1  | Microprocessor Systems Teaching Kit                        | 55 |

| 5.2  | Teaching Kit Packaging                                     | 56 |

| 5.3  | Wireless Conference Manager Handheld Unit                  | 58 |

## List of Tables

| 2.1 | Micro-controller Family Expansion Potential | 7  |

|-----|---------------------------------------------|----|

| 2.2 | Micro-controller Family Features            | 7  |

| 2.3 | Micro-controller Family Memory Limits       | 7  |

| 2.4 | Battery Technologies [1, Chapter 2]         | 10 |

| 4.1 | PCB Materials Electrical Properties         | 38 |

## Chapter 1

## Introduction

#### 1.1 Motivation

#### 1.1.1 Overview

Recent advances in semiconductor technologies have successfully reduced the cost and size of micro-controllers and increased their level of integration to complete system-on-chips (SoC). The recent telecommunication boom has pushed enormous research and development investment in creating sophisticated wired and wireless algorithms and silicon intellectual property. The mass market adoption of wireless networking by personal computer users has pushed prices down and advanced research into the combination of typical radio frequency components on the same CMOS process as common microprocessors. This is transforming the wireless communication field by bringing a tremendous level of integration in off-the-shelf devices now available at very low price.

In parallel, small micro-controllers targeted at embedded systems are experiencing a change in focus. Whereas before manufacturers were pushing for higher clock speed and larger memories, a point has been reached where the complexity of the software and execution speed is secondary to power usage. Some micro-controllers are now aggressively reducing power by stopping some core operation and by dynamically reducing the supply voltage. Power savings are also being integrated in the higher levels of software architecture and in the networking protocols. All of these efforts contribute to create more energy-efficient systems, benefiting the industry and consumers.

The rapid changes in the way embedded systems are designed and the recent addition of

1 Introduction 2

wireless networking capabilities create a need for undergraduate courses to expose students to new design trade-offs. This thesis proposes a flexible, robust and easy to use architecture that can be used for teaching low-power embedded micro-controllers and low-power interdevice wireless networking.

#### 1.1.2 Sensor Networks

Until now, most embedded systems collecting information have to be connected to the central computer with a physical wire to report their data. Alternatively, the data could be recorded locally and stored on a non-volatile media to be later collected by a person and brought back for analysis. The developments in integrated radio frequency integrated circuits (RFIC), coupled with intelligent routing protocols allow clusters of small embedded devices to communicate and report their collected data to a central location. Furthermore, advances in routing algorithms and the higher memory capacity of micro-controllers enable the propagation of the information to be fully automated and fault tolerant. New standards are emerging aiming at simplifying the interconnection of heterogeneous hardware based on a unified protocol designed to support the low-power constraints of sensor nodes. This revolution in how small embedded devices will be able to communicate with each other and the implications that this will have in the marketplace is limited only by the imagination of those that will implement the wireless systems of the future.

#### 1.1.3 Microelectronics Systems Education and Research Applications

Microelectronics systems eduction will have to adapt to new paradigms and ever increasing levels of complexity. Design goals change rapidly and undergraduate students need to know appropriate design methods to be be productive in the workforce. Knowledge of modern embedded systems with advanced networking capabilities must be introduced in the curriculum for the institution to maintain its competitive edge in a time of rapid international development and intense competition. The proposed architecture allows the teaching of the material to be ramped up rapidly while giving students all the required control of the hardware to build up their understanding of all key concepts of embedded systems programming. The platform is designed to support the design tools and hardware interfaces in an integrated fashion, allowing more time for application development and practical concepts assimilation.

1 Introduction 3

The ability to re-program the system at home with a regular PC has numerous advantages for a student with limited time resources. This feature was integrated very early in this design, helping to reduce the requirement for large laboratories. The students only need to use the school lab facilities when major design problems are encountered and sophisticated equipment such as oscilloscopes and logic analyzers are required.

Graduate students can also benefit from a simple and expandable hardware platform for the implementation of embedded wireless systems. This project was done with the intent that anyone interested would have the full access to the documentation and design files to re-use or improve any parts of the current architecture. Most commercial education kits provide enough information for people to use their design kits, but never enough if someone wants to actually modify it or improve it.

This project and the key ideas are for everyone to re-use and improve. The documentation available include schematics, printed-circuit design files, supplier information, bill of materials, design notes and basic application software and demo programs.

Finally, in the spirit of unfettered access to the architecture, the micro-controller was carefully chosen such that the C compiler and assembler are available as open source and are free of charge.

### 1.2 Thesis Overview

Following the introduction, this thesis will follow with a literature review of the various architectures in the field of sensor networks, the selection of microcontroller and radio transceiver. This work was inspired by the latest development in sensor network infrastructures and Low-Rate Wireless Personal Area Networks (LR-WPAN) standards. The literature review will also reveal which architectures are used in microelectronic system education and how they compare to the proposed solution.

Chapter 3 will cover the architectural details and trade-offs. The various boards used in the architecture will be presented and their high-level design details will be discussed. The requirements for the liquid crystal display and Radio Frequency (RF) board will then be elaborated. The design of the RF board will be presented with an emphasis on the method used to integrate the antenna to the transceiver circuit board.

Chapter 4 will detail the architecture and cover all the key decisions and their implication on the final product. The numerous trade-offs that were required in the implementa1 Introduction 4

tion of the final boards will be covered. Emphasis will be put on low-cost manufacturable prototypes and the methods developed for their assembly in an academic environment.

In Chapter 5 the resulting boards will be analyzed along with the various practical designs that were derived from this framework by undergraduate and graduate students.

Conclusion and suggestions for future work and improvements to the architecture and expansion modules will be given in Chapter 6.

## Chapter 2

## Literature Review

In creating the architecture for wireless embedded systems, the body of research in the field of wireless sensor network is a great source of inspiration. The newest architectures [2, 3] tend to use micro-controllers which consume little power during full-speed operation and also provide multiple control points to reduce the activity of the peripherals. The newest micro-controllers also support multiple clock sources as well as their dynamic selection during operation. Clock sources can be running at very low frequency allowing timers to continue their operation while the core of the micro-controller is completely disabled. Very long operating time, such as several years, is achievable using a simple coin cell battery if the software architecture is well designed for energy efficiency.

Recently, the term Motes or Smartdust have been used to describe tiny sensor devices attached with a power source, some controller and a wireless interface. While the devices are quite far from being the size of dust particles, the relentless pace of microelectronic development allows a steady reduction in size. The latest development in transceiver architectures available for commercial use include media access control built into the RFIC receiver allowing further power savings. This section will discuss the recent advances in the sensor network research field and will highlight the publications most relevant to this research. Following the sensor network discussion, the selection of micro-controllers and RF transceivers will be discussed based on relevant research in the field and evaluation of the devices available on the market. Finally, the use of wireless embedded systems in education will be reviewed.

6

### 2.1 Wireless Sensor Networks

Wireless Sensor Networks are small networking devices that can collectively interact together or report information through intelligent routing. The requirements for sensor networks are mostly focused on energy conservation and usually require low data rates which is an interesting aspect when used in teaching since they would not require expensive CPU resources to process the information.

Evolution in sensor network research have brought numerous potential applications and commercial products are available for research purpose such as Micaz [4] or Telos [5] which can be a source of inspiration for a platform used in teaching wireless embedded systems networking. Telos offers a better overall architecture due to its use of more modern 16-bit low-power micro-controllers and is thus a better system to adapt to a teaching environment. Recent use of Motes in undergraduate education [6] have shown that it is possible to use such devices in a classroom environment and get very encouraging and fruitful teaching opportunities.

#### 2.1.1 Micro-controller Selection

At the heart of the wireless sensor unit is the micro-controller. Care must be taken in choosing the proper unit for the application as the semiconductor process used in the fabrication of micro-controller vary from ultra-low power to ultra-high speed. The target market for a particular micro-controller can be cost-sensitive mass market applications, specialized media devices for consumer products, automotive controllers, biomedical devices with extreme reliability requirements or military sensors. With each category, a different set of metrics can be used to evaluate the micro-controller fit for the application. In the context of education and research, extreme temperature tolerance of the availability of volume pricing for millions of units is not relevant. The focus is on low development tool cost (free is even better), ease of use and family expandability. The micro-controller central processing unit (CPU) must follow a simple and textbook-like architecture so that students can relate their code to computer architecture classes. Low prototyping cost is decisive, so is the availability of small quantities of devices.

Table 2.1 shows the most relevant families of micro-controllers that were considered. In the table are the specifications for parts that can be bought directly from a retailer and do not include the items that the manufacturer carries in their official product line (some of which are nearly impossible to obtain for academic use). The distinction is important since the quantities for small production lots do not justify direct negotiations with the semiconductor vendor. Considering the technology evolution and the general trend 8-bit micro-controllers were not considered. This decision eliminated the Freescale HC11, Microchip PIC, Atmel AVR and the 8051 architecture. Pricing in the table is for quantities of 100 (in US dollar), which would be the typical volume an academic institution would purchase.

Table 2.1

Micro-controller Family Expansion Potential

| Family            | CPU Core | Price Range | Flash Range                        | RAM Range    |

|-------------------|----------|-------------|------------------------------------|--------------|

| Philips LPC21xx   | ARM7TDMI | 6.30-8.85   | 128kB – 512kB                      | 16kB – 64kB  |

| TI MSP430         | MSP430   | 1.45-11.90  | 2kB - 60kB                         | 128 B – 10kB |

| Freescale 68HCS12 | HCS12    | 7.40-15.30  | $64 \mathrm{kB} - 256 \mathrm{kB}$ | 4kB – 12kB   |

Table 2.2

Micro-controller Family Features

| Family            | GNU Compiler Support | CPU Debug    | CPU Architecture |

|-------------------|----------------------|--------------|------------------|

| Philips LPC21xx   | Yes                  | JTAG         | 32-bit RISC      |

| TI MSP430         | Yes                  | JTAG         | 16-bit RISC      |

| Freescale 68HCS12 | Yes (Limited)        | Motorola BDM | 16-bit CISC      |

Table 2.3 Micro-controller Family Memory Limits

| Family            | Architecture Max (Prog/Data) | Memory Space | Max Speed |  |

|-------------------|------------------------------|--------------|-----------|--|

| Philips LPC21xx   | 4 GB / 4GB                   | Linear       | 60 MHz    |  |

| TI MSP430         | 64 kB / 64 kB                | Linear       | 8 MHz     |  |

| Freescale 68HCS12 | 4 Mb / 1 Mb                  | Paged        | 25 MHz    |  |

Table 2.2 shows the high-level feature support of various micro-controllers that were researched. The support for GNU C Compiler (GCC) tool chain is deemed crucial because it brings tool vendor independence if desired, is freely downloadable and has no usage restrictions. For the TI MSP430 and Philips LPC21xx the GCC support is well established and widely used [7, 8]. The Freescale HCS12 support by GCC is very limited and buying the compiler suite from specialized compiler vendor is recommended. The antiquated architecture of the HCS12 and its small register count also limits the efficiency of 'C' programs.

All of the processors support freely available real-time operating systems (RTOS) such as FreeRTOS [9] or  $\mu$ COS-II [10]. The Philips architecture further benefits from the support of the royalty-free eCOS operating system [11] which has a very large user base and is another open-source project. Table 2.3 illustrates the vast range of offerings in terms of addressable and available memory, the LPC21xx family from Philips leading the group because it is based on a 32-bit architecture and uses a very advanced manufacturing process. The MSP430 has limited addressing space mainly due to its internal architecture targeting the utmost in energy efficiency. Reduced size buses and limited RAM memory allow this device to offer the best low-power performance.

The Telos Mote from UC Berkeley uses the MSP430 since it is a natural fit for low-power sensor network. In addition, the architecture is suitable for relatively large software programs. Those need to use hardware abstraction layers to maintain portability of the upper application layers [3], which translates in more memory usage.

### 2.1.2 RF Transceivers

The frequency of operation of the RF Transceiver impacts the range of transmission that can be obtained using simple resonant antennas. Radio transceivers are available for operation in the 400MHz, 800MHz, 900MHz and 2.4GHz ranges. The higher the frequency, the smaller the antenna will be and the less energy it may capture. Therefore, with higher frequency transceivers, the range obtainable is consequently reduced. International regulations also play a major role in the selection of operating frequency of the transceiver. At this time, the 2.4 GHz industrial, scientific, and medical (ISM) band offer the best international operation due to the uniformity of the standard across the world. This is also the frequency band that offers the best data rate and the largest number of channels.

In wireless communications, power usage and bandwidth are always traded. While each design problem could use a specific modulation and coding scheme, a standard that allows inter-operation of various devices is preferable. WiFi (802.11) and Bluetooth are both very popular wireless standard, but are not suitable for sensor network [2] due to the complexity of the control software and their high data rate. Both of those factors contribute to higher power consumption and increased node price. The 802.15.4 standard [12] from the IEEE aims at promoting a way to inter-operate various transceivers from multiple vendors and set a level of performance which will make compliant devices useful in a variety of applications

requiring low power operation.

Ideally, the micro-controller die would integrate the RF transceiver and the complete system would be on a single chip. At this time, such solution is only beginning to appear in common-off-the-shelf (COTS) parts [13], but the micro-controller unit is very limited in its scope of possible applications due to its tiny amount of code space and RAM resources. It is mainly directed at low-cost, very simple applications such as wireless mouse and keyboard.

The only integrated 802.15.4 COTS transceiver available on the market at the time the architecture was conceived was the Chipcon CC2420 [14]. Only recently did other manufacturers release integrated and 802.15.4 compliant transceivers, but still only the CC2420 meets all the requirements in the 2.4 GHz band [15] while keeping the RF section simple with a single-antenna setup.

Other education platforms have used the older and more popular 802.11b standard in their architecture [16], but this standard does not target low-power systems. The modulation, data rate and beacon rate is targeted at high-speed wireless personal computer networking. Furthermore, the use of Bluetooth or 802.11b in an entry-level embedded systems course would overwhelm the students with the very complex software layers. 802.15.4 allows most of the concepts of wireless networking to be experienced while limiting the cost, complexity and overhead associated with higher speed protocols.

### 2.1.3 Battery Technology

As electronic devices are getting smaller and more portable, their power source must also scale down. While in microelectronics, the rate at which transistor can be shrinked is an impressive technological feat, the chemical and metallurgical elements of battery chemistry cannot follow that pace. There are numerous possible battery chemistries that can be considered for their use in wireless sensor networks. Older battery such as lead-acid or nickel-cadmium have some cost advantages due to their very well known characteristics and large production volume. However, their low energy density and low cell voltage make them less attractive for this project. Nickel Metal Hydride (NiMH) batteries offer very good charge density. Their main problem is a high self-discharge rate resulting in an empty battery after just a few months [1]. Their discharge rate is further worsened by higher ambient temperatures. Lithium and lithium-ion batteries offer some of the best charge density in the realm of widely used chemistries.

2 Literature Review 10

|                            | NiCd      | NiMH      | Li-ion    | Li-ion Polymer |

|----------------------------|-----------|-----------|-----------|----------------|

| Energy Density (Wh/kg)     | 45-80     | 60-120    | 110–160   | 100-130        |

| Overcharge Tolerance       | moderate  | low       | very low  | low            |

| Self-Discharge (per Month) | 20%       | 30%       | 10%       | ≈ 10%          |

| Cell Voltage (V)           | 1.25      | 1.25      | 3.6       | 3.6            |

| Peak Current               | 20C       | 5C        | >2C       | >2C            |

| Operating Temp (°C)        | -40 to 60 | -20 to 60 | -20 to 60 | 0 to 60        |

| Used Since                 | 1950      | 1990      | 1991      | 1999           |

**Table 2.4** Battery Technologies [1, Chapter 2]

Lithium-ion and Lithium-ion polymer batteries come out as more technically advanced batteries when Table 2.4 is studied. Lithium-ion polymer batteries further offer the advantage of being very thin thus allowing them to be included in sensor nodes while occupying very little space. The very high energy density [17] of the newest lithium-based batteries require some protection circuit to be implemented to avoid potential destruction of the battery and risks of fire. The table also shows that lithium-ion polymer batteries cannot provide as large currents as NiCd or NiMH. Wireless sensor nodes may draw large current spikes when the transceiver and all the circuitry of the node is activated during a very short time. Some lithium batteries may actually perform better under those conditions [18]. If the current spike is very large when compared to the average current required for operation, supercapacitors can supplement the peak current, resulting in a smaller battery for the application.

## 2.2 Software Requirements

With any system-level design, the software requirements must be considered early in the process to ensure problem free integration. This thesis focuses mainly on the hardware design, but the resulting system must provide support for a substantial amount of software to fulfill its goals.

In order to guide the hardware decisions, the baseline standard of IEEE 802.15.4 [12] was considered early in the process and estimates were gathered on the code and RAM memory requirements. In the early phases of the project, the upper software layers requirements were based on the various design kits targeted at supporting the Reduced Function Device (RFD) of the Zigbee Specification [19]. The use of those standards as guidelines ensured

2 Literature Review 11

that the hardware architecture could support an advanced set of features while setting realistic guidelines for the amount of on-chip resources required.

## 2.3 Printed Circuit Board Design

The electronics components of the hardware platform rely on the Printed Circuit Board (PCB) for support, electrical connectivity and thermal dissipation. Since the PCB unites all the components of the hardware architecture, the design must ensure that the overall architecture is not compromised by bad design practices. PCB design rely on a set of rules [20, 21] that will not only fulfill the electrical requirements of the design, but also limit electromagnetic emissions and preserve the signal integrity along the various interconnections.

### 2.3.1 General Design for Manufacture and Assembly

The board must be fabricated in multiple copies for groups of students to benefit from it. Therefore, volume production of the PCB required special attention to the design-formanufacturing aspects. Within the PCB design tool, a set of clearance such as trace to trace, pad to pad, hole to pad, hole to trace have to be defined based on the capabilities of the PCB manufacturer. The selection of the connecting structures between the layers (the vias) have to be selected such that the hole size is not too small (increase cost) or too big (increase the area wasted on the PCB). Publications [22] explaining the terminology and requirements of the PCB industry greatly helped in setting up the design tools to obtain satisfactory results.

Design-for-assembly is another very important element of mass produced hardware. While a single prototype can usually be made to work without any assembly considerations, the use of automated assembly equipment and the cost associated with each assembly step can significantly impact the project if the limitations and restrictions of the machinery is not considered in the design phase. Examples of considerations for automated assembly include the location of parts (top side only is cheaper), placement on a grid and size of the passive components. The use of surface mount parts allow fully-automated assembly, further reducing cost. Provision for optical alignment marks called fiducial on the PCB is important for accurate and reliable placement. A full list of constraints and requirements is available in reference material [23, 22, 20] on PCB design.

## 2.3.2 Printed Antenna Design

Printed antennas bring extra constraints on the PCB dielectric material and therefore require extra attention. Printed antennas are sensitive to variations in thickness and uniformity of the dielectric material, therefore using specialized material can reduce the design risks and improve the performance significantly. Numerous publications exist describing printed antennas and their radiation patterns. However, few or none of the publications proposed a proper method to integrate the printed antenna with the RF transceiver. To fill up this void, a comprehensive analysis of the design process and a design methodology [24] was published by our group at the 2005 International Design Automation Conference (DAC 2005). Our method combined the analysis from 2.5D and 3D electromagnetic simulators with the PCB design tools to create predictable nodes with printed antennas that meet stringent power and data transmission range goals.

### 2.4 Education

The use of practical hardware and micro-controllers in teaching wireless systems is still very limited. Future engineers will need adequate knowledge in this area to remain competitive. Attempts at using hardware infrastructure in wireless teaching has brought good results with 802.11b [16]. Some instructors have approached the problem using Motes [6] in their courses. The availability of complete networking layers made the approach more manageable for students with no previous background in programming embedded systems. We chose to avoid the Atmel AVR micro-controllers used in the Motes environment, because of their 8-bit architecture which we found to be outdated. Modern 16-bit micro-controllers do not support Dual In-Line Packages (DIP) and solder-less breadboards as it was the case with the 8-bit AVR-based Motes [6], so an alternative has to be explored in order to future-proof our architecture.

To solve the problem over the extinction of DIP packages in the marketplace, we designed a board with a soldered micro-controller and use a CPLD for prototyping some of the hardware features. With this approach, students do not build their design totally "from scratch", but they benefit from a similar level of flexibility from the integration of the CPLD. It also represent a more realistic approach since typical modern industrial designs rarely rely on breadboarding as a method of prototyping projects. With higher clock

speeds and smaller technology, this trend is not about to be reversed.

We found that our method offer many advantages to quickly bring students up-to-speed with the hardware. A detailed description of the education platform and its use was published in the 2005 International Conference on Microelectronic Systems Education [25] (MSE 2005). This thesis focuses more on the design details and architectural decisions.

## Chapter 3

## System Architecture

This chapter presents the overall architecture of the platform for embedded low-power wireless systems. The focus of this section is to explain the key decisions taken in designing the architecture of the system, leaving for the next chapter the implementation details.

## 3.1 System Overview

The system was designed with modularity and expandability in mind. By adding to the architecture of a typical sensor network node, a platform can be built for students to explore the various trade-offs in building a complete system. Add-ons such as keypads, touch screen panels with graphical displays, audio processing devices and more can later be designed to accompany the main board. Students can define and program the hardware abstraction layer firmware, the user interface, the communication protocol stack and core scheduling algorithm. At the same time, the limitations of an small embedded micro-controller with power, memory and speed constraints will contribute to illustrate the trade-offs always present in engineering designs. When the design platform is used to teach the laboratory classes, students must be able to complete their designs within a 4 months semester. Due to cost and time constraints, students cannot be taught to build PCB and design hardware expansion modules in such a short time. This architecture is meant to provide ample flexibility and eliminate the hardware and fabrication issues, while leaving to students the ability to make hardware decisions through the integration of programmable logic.

On the firmware and software side, a complete implementation of a standard like Zigbee would be too demanding. However, building an understanding of the underlying mecha-

nisms by which modern low-power wireless sensor network operate is achievable and can provide a rewarding experience. A standard such as Zigbee can be used as a reference and a subset containing the important characteristics can be worked out during a semester.

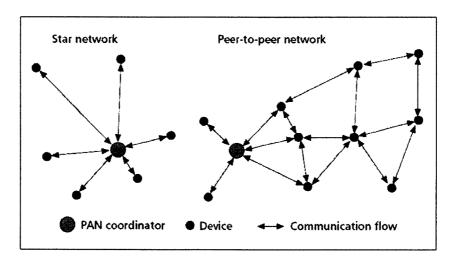

Fig. 3.1 Sensor Network Topology

Typical embedded sensor networks operate using a star or mesh topology with a central unit responsible for collecting, processing and forwarding the information as shown on Figure 3.1 [26]. The device in the center of the star network is called the Personal Area Network (PAN) coordinator and regulates the traffic within its immediate domain. The PAN coordinator is responsible for sending regular beacons. Inside those data frames, some network command can be sent to the nodes. This approach is a fundamental method implemented in low-power sensor network for saving energy and regulating the data flow. Simpler exercises and lab experiments can be done using the Star Network topology as it reduces the complexity on the routing algorithms and are therefore suitable as laboratory exercises.

The main concepts in sensor network technology such as beacon frames, sleep periods and association with the network coordinator can be taught in a short time frame without requiring the coding of very complex data structures. Having a single board that can implement either the network coordinator or the reduced function device offers the advantage of re-using the equipment. In a real industrial application, power considerations, price sensitivity and the complexity level difference between the PAN and the reduced function device will lead to two different architectures.

## 3.2 Laboratory Setup

Previously, the microprocessor systems laboratory had a setup for teaching on a Motorola 68HC12 platform. The first objective of the new architecture was to replace this outdated platform with one that can be used to introduce wireless embedded systems design and a more modern CPU architecture. Care was taken to avoid any unnessary capital expenditure by adapting the new design to the existing laboratory equipment infrastructure as much as possible.

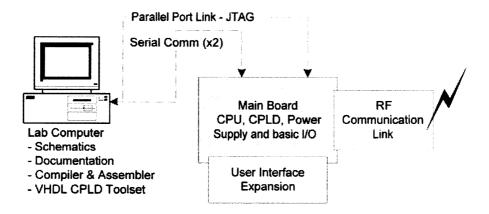

Fig. 3.2 Student Lab Setup

A typical student setup in the lab was envisioned to look like the one presented in Figure 3.2. The personal computer only requires 2 serial ports (RS-232 interface) and one parallel port, exactly like the previous lab configuration. The main board contains the required hardware for the device re-programming and debugging. Two serial channels are preferable, the first one is a direct connection to the PC acting as a terminal interface to the micro-controller board. The second channel allows extra information to be sent out for debugging or alternatively as a communication channel between two micro-controller boards to experiment with simple wired networks. For debugging wireless embedded systems, one of the serial channel would typically be used as a terminal interface and the second channel would be used to log a trace of the packets (a summarized version since the data rate on the wireless port will be higher than capacity of the RS-232 serial interface).

#### 3.3 Main Board

In the initial phases of the research, a main board including a low-power micro-controller was developed. The purpose of this board is to bring students up to speed with embedded systems programming in assembler and in 'C'. The hardware was also designed to be used in a graduate research environment. This board would be a base platform that students would use to build their projects on and would be re-used at each semester. The microcontroller family was chosen to be the MSP430 by Texas Instruments.

In Chapter 2, the comparison between the Philips LPC21xx family and the MSP430 family suggests the use of the Philips ARM-based architecture instead of the MSP430. From a purely economical and performance point of view, the Philips ARM solution was better, having higher speed of operation (60 MHz compared to 8 MHz) and a future-proof 32-bit architecture.

However, the MSP430 is more suitable for battery operated devices when battery life is calculated in months instead of hours. Its architecture aiming for the highest energy efficiency and the energy savings of a 16-bit architecture make it a better candidate for wireless sensor device type of applications.

Furthermore, from an education perspective, the ARM architecture adds a layer of complexity due to the structure of the ARM processor Intellectual Property (IP) cores and their integration by different semiconductor companies. The documentation is divided into two main sets, one coming from ARM and the other coming from the semiconductor manfacturer, in our case Philips. The microcontroller manufacturer describes the operation of their microcontroller and cross-reference the ARM documentation for the details on the CPU core. This creates a complex set of documents that would delay the lab work and hamper the completion of the student's projects in a semester's time. In the laboratory course objectives, the students start with no code other than trivial examples and build all the device drivers, hardware abstraction layers and software architecture from the ground up. This offers a better teaching opportunity and through supervision allow for a better understanding of the methods used to architect embedded software. The MSP430 also benefit from a simplified interrupt mechanism, predictable code execution (no instruction or data caches) and simpler CPU register set.

Previously, the Microprocessor Systems lab used the MC68HC12 8-bit Complex Instruction Set Computer (CISC) architecture. It was not very power efficient and had numerous reliability issues related to the socketed part on the development kit from Motorola. That problem made it compelling to solder the CPU permanently in the new architecture. The cost of sockets for small-pitch Surface Mount Technology (SMT) being so high that simply desoldering a damaged CPU and replacing it with a new one is more economical even when the manpower cost is included. The newer 16-bit Reduced Instruction Set Computer (RISC) architecture offered by the MSP430 is more in-line with the computer architecture courses students took and also offers more efficient support for higher-level languages such as 'C'.

### 3.3.1 Programmable Logic Integration

One very important aspect of learning to program embedded systems is the ability to make decisions on the partitionning of computations between hardware and software. The integration of programmable logic in the main board allows students to make those design decisions based on their estimate of the complexity and speed requirements of the problem they are solving. In a graduate research environment the programmable logic allows rapid prototyping of ideas and flexibility in designing expansion modules.

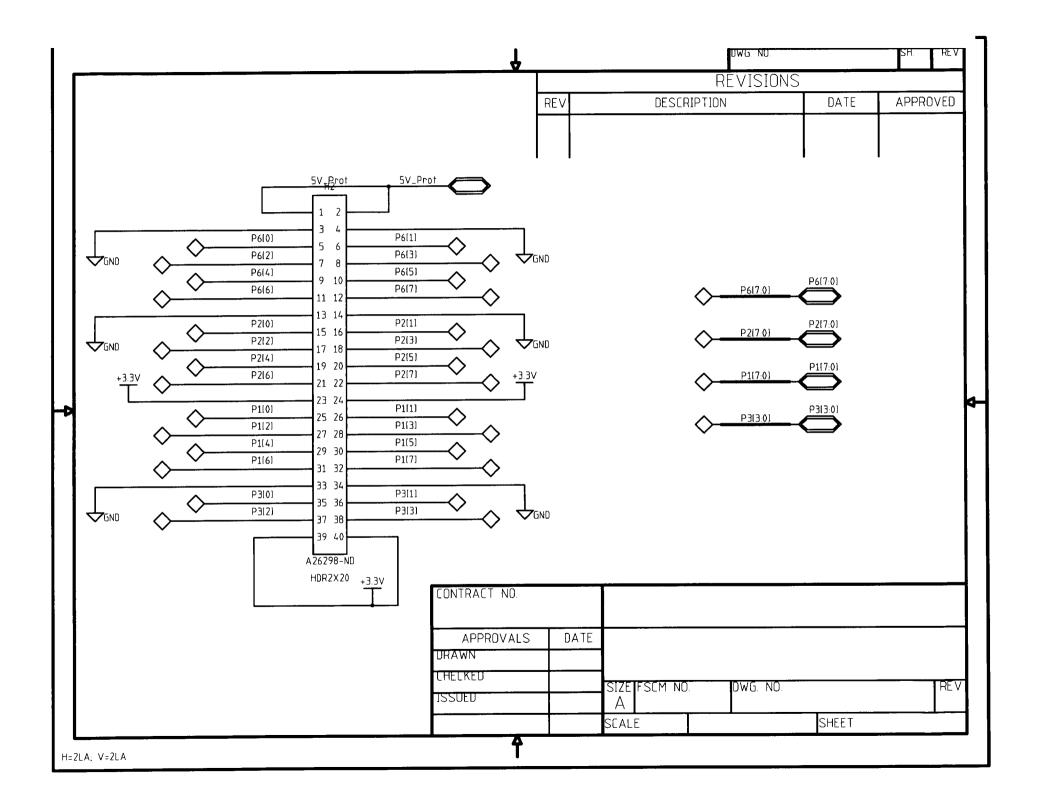

For this architecture, the 0.18um CoolRunner-II family [27] from Xilinx Inc. could have been a great programmable device. It combined flash-based programmable logic, low static and dynamic power consumption and was using a modern process technology. However, the laboratory has to re-use course pre-requisites, therefore the Altera MAX7000AE family [28] Complex Programmable Logic Device (CPLD) was chosen based on the student's previous experience with that particular family in the Digital Systems Design course. This older technology, despite its higher power usage and larger package size, have the benefit of 5V tolerance at the I/O pins with a core running at 3.3V. Therefore, it is compatible with older technology still using a 5V power supply, yet interface directly with the MSP430 running at 3.3V. This choice shows the design constraints imposed by the educational aspect of the architecture include requirements that are not necessarely based solely on technical considerations.

#### 3.3.2 Built-in Programmer

A CPLD device programmer (Byteblaster MV [29]) and a JTAG programming adapter for the MSP430 (MSP430-JTAG [30]) were integrated to the design. This programming hardware allows the re-configuration of the CPLD macrocells and perform in-system debugging and re-programming of the MCU. This reduces the cost of the kits and simplifies the user interface. It becomes possible to reprogram either the CPLD or the microcontroller through the same parallel port just by using the proper software on the PC.

### 3.3.3 User Interface and Sensor Connection

To allow variations in the design of laboratories, extra hardware was put on the main board. A simple 2-digit 7-segments LED display can offer a great introduction to hardware multiplexing by sharing the same LED segment lines, but rapidly alternating power to the common anodes of the display. The board also features a Multimedia Card [31] (MMC) connector allowing the possibility of an expansion card for this popular flash memory standard. An iButton [32] connector is also present on the main board allowing a number of modules to be connected such as temperature sensor or encryption keys. The iButton is a small metallic container that encloses an IC. The interface to the IC is done through a single pin which carries both the power and the bidirectional data signal. This interface is interesting because it is very robust and is a good fit for sensor network environments.

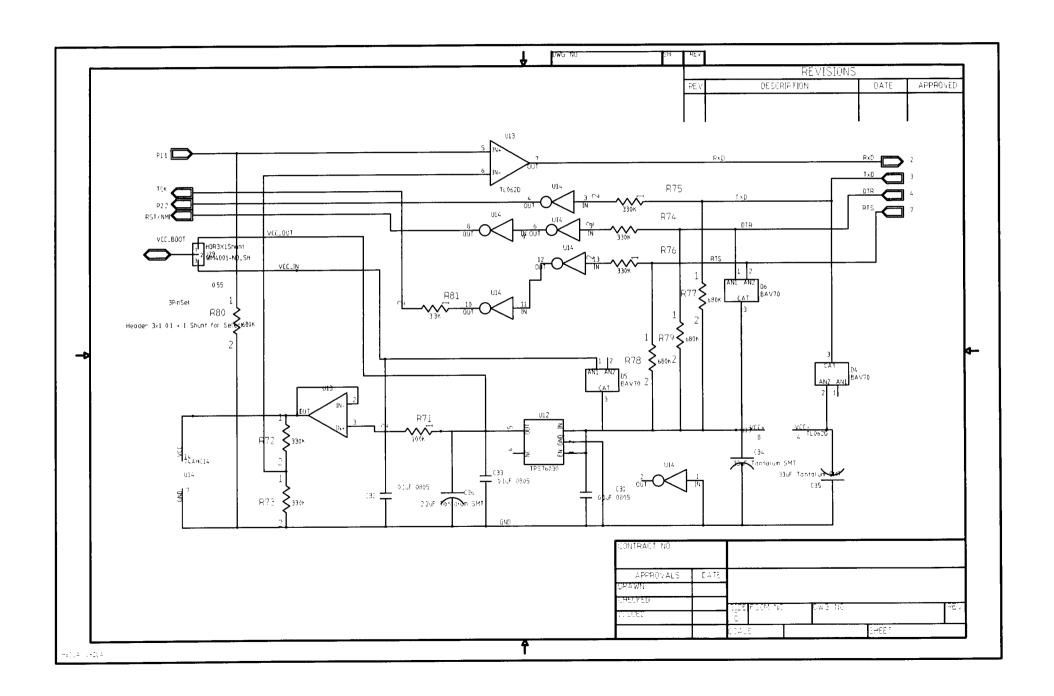

### 3.3.4 Power Supply

The main board includes the power supply regulation circuit and is responsible for powering the expansion cards. Three power supply modes are supported:

- External AC adapter providing regulated 5V DC through a 2.1mm center positive barrel jack.

- Battery or Power Supply. This option is very flexible, but carries the risk of burning the microcontroller and CPLD if the polarity is accidentally reversed. To prevent damage, a fused circuit was designed to protect the board's electronic components.

- Parallel port. This mode is reserved for low-current operation (typically the CPU alone) and the power comes from the parallel port interface. It allows students to re-program the microcontroller without having to supply additionnal power to the board. Power is parasitically taken from a selection of parallel port pins. It allows a convenient way to re-program the MCU using a laptop and a parallel cable.

A green LED indicate the proper operation of the power supply circuit. While this contributes to an increase in the standby power consumption, teaching material require this kind of visual feedback for rapid troubleshooting of power supply issues.

### 3.4 Screen Boards and Touch Panel

For the design of user interfaces, the 2-digit 7-segment LED display present on the main board is very limiting. A daughtercard featuring a graphical screen and touch panel interface was designed to improve the range of laboratories that can be generated using the development platform.

### 3.4.1 Liquid Crystal Display (LCD) Technology

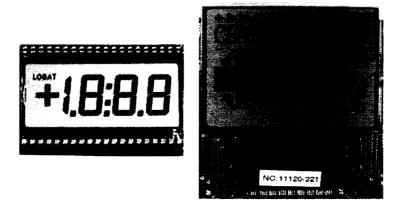

LCD panels come in a variety of different technologies and form factors. In its simplest form, the LCD segments are connected directly to the Micro-Controller Unit (MCU) through conductive rubber (elastomeric connection) or pins as shown in the left side of Figure 3.3. The MCU can integrate a controller which will alternatively polarize the segment that need to be visible. The liquid crystal material can be damaged by DC currents, therefore, the MCU must constantly change the current direction. Typically, a hardware module within the MCU does this alternating current waveform, leaving processing power for other tasks. Alternatively such circuit can be implemented in a CPLD.

As the number of segments become larger, for example in a 128x64 graphical display (8192 segments), the number of pins required to drive the LCD matrix becomes overwhelming. Therefore, specialized IC can be attached to the display panel to handle the control and the multiplexing of all the segments. Newer technology called Tape Automated Bonding (TAB, see Figure 3.3 – Right) integrate the LCD segment driver and an intelligent controller directly in the ribbon connecting the MCU to the LCD panel. This considerably reduces the price of the LCD unit. The trade-off is that the assembly is more fragile since the ribbon contains a bare die and has very fine copper traces.

For larger LCD panels, such as a 160x160 display, the module may integrate only the segment drivers and no controller, leaving the selection and tradeoffs for the controller to the circuit designer. Data is then fed continuously to the LCD module with the help of a dedicated controller which can be an external IC or in high-end microcontrollers is integrated on the same die as the CPU. The controller can include static memory or an external

memory interface, character generators, graphic accelerations such as block copying and bit masking, gray scale support, and other advanced options. All those would contribute to reduce the load that the CPU has to handle for advanced graphical user interfaces.

Fig. 3.3 LCD Segments and TAB LCD Unit

A 128x64 TAB LCD with integrated touch panel is designed for the initial laboratories since together they represent a complete embedded system and multiple laboratories can be built upon this platform [25]. The user interface board also included extra serial memory that could be used for students to store graphical items. The external memory shares the same SPI bus as other on-board peripherals such as the touch panel controller and serve as a good introduction to resource sharing and bus conflict resolution.

For our graduate research, a more powerful daughtercard screen board including a larger LCD panel (160x160) was designed. The larger panel however only had LCD segment drivers. An external controller (EPSON S1D13700) with 32kB of on-chip static RAM memory dedicated to buffer the display information was added to the board providing advanced graphical capabilities. This daughtercard also featured LCD bias voltage generation and a touch screen controller.

## 3.5 Radio Frequency Board

To preserve a certain independance and allow more experimentation to be performed in the wireless design, a RF daughter card was designed to integrate the wireless transceiver and antenna in an efficient and easy-to-use unit. This card can be attached to the Main Board

to turn the system into a complete wireless sensor node or PAN coordinator depending on the firmware programmed into the MCU.

This board required the most research and time to develop when compared to the other ones. First, selecting the transceiver while following the low-power constraints and embedded sensor network aspects required careful consideration of the devices available on the market since it would have the biggest impact in the design of the transceiver board. Secondly, we have decided that the antenna should be integrated on the PCB for cost and reliability reasons. However, to the author's knowledge, there was no literature available on the process of designing the antenna and then integrating it with a PCB design tool. Most publications in the antenna field focus only on the antenna itself, leaving the integration and board effects on the radiation pattern as an exercise for the readers. Most publications on PCB focus on reducing Electromagnetic Interference (EMI) problems and on how to avoid creating antennas into circuit boards. Our initial goal was thus to establish a methodology for integrating printed antennas on PCB while understanding the effects of the PCB on the antenna radiation pattern. Furthermore, we were also interested in analyzing how the printed antenna could exacerbate EMI produced by a microcontroller or clock generation circuit [24].

#### 3.5.1 2.45 GHz Radio Transceiver

The main technique for the wireless operation to be low-power is to use of long sleep periods which are synchronized with beacon frames sent periodically by the network coordinator. During the sleep period, the power consumption is dominated by leakage current from the RF transceiver, the CPU, the sensors and peripherals.

It is well known from communication theory that the lower the data rate, the lower the power consumption, but one must be careful not to use an architecture which would require too much time to receive the information. As the data rate go down, the power consumption for the receiver and transceiver also scale down. At a certain point, the biasing required to power the analog and demodulation circuit consumes much of the power. From that point, lower transmission rate will actually increase the amount of energy required to transfer the information. It was found that in small and low-power wireless sensor radio frequency integrated circuits, the power consumption in receive mode is counterintuitively higher than in transmit mode. Since the sensor node is in receive mode for long periods,

the receiver energy consumption is a critical design characteristic.

Furthermore, most of the time sensor nodes are either in sleep mode or in receiving mode, listening to beacon messages from the PAN coordinator. The beacons duration must be short thus the importance of a high data rate. A lower data rate would keep the receiver active for longer periods and have a negative impact on the energy efficiency of the whole system.

In the study of RF transceivers, the nRF2401A [33] from Nordic VLSI stand out as an interesting candidate for wireless sensor networking. It uses high speed (1 Mbps) bursts of data to reduce the potential for packet collision as well as reduce the transceiver time to complete a transaction. The nRF2401A also features dual receiver capability which allows it to receive information from two sources at the same time. However, it is not compatible with the IEEE 802.15.4 standard due to its different modulation method. It also cannot support hardware acceleration of encryption, which we feel is important for research in secure wireless network deployment. Finally, while the nRF2401 can filter network addresses and perform hardware CRC computations, it cannot handle automatic acknowledgment of packets, which in sensor network is very beneficial as it reduces the energy used by the microcontroller and increases network reliability.

The CC2420 from Chipcon [14] addresses most of the above issues with a fully compliant IEEE 802.15.4 transceiver. The receive power consumption is slightly higher (19.7mA versus 18mA for the nRF2401), but the automatic packet acknoledgement, hardware encryption (AES-128) and the precise received power analysis features of this device make it an ideal candidate for wireless systems education and research. This transceiver was chosen for our wireless architecture.

To further reduce cost and board complexity, we have decided that the transceiver board would be on a 2-layer PCB instead of the recommendation that the PCB be 4-layers [14]. We used electromagnetic simulation tools when designing the PCB to avoid potential issues caused by the reduction in the number of layers.

Abstracting the RF circuitry and integrating it in a robust and low-cost manner was our primary intent. We aimed at providing seamless integration of the radio modules in the laboratories without the need for students to understand the intricacies of RF design. The radio transceiver unit is thus build on a separate printed circuit board to allow future upgrades of the RFIC while reducing the main board complexity and cost.

By building the antenna feed line using a microstrip line shielded with the bottom

grounding plane and a barrier of vias, we avoided EM waves from propagating into the dielectric near the digital connections [24]. The RF section of the design is thus isolated from the digital input lines. Therefore, the radio frequency board can be connected to the main board without significantly affecting the high frequency operation or the antenna radiation pattern.

Specialized dielectric materials were successfully used to integrate the transceiver and antenna, as will be shown in the next chapter. The laboratory measurements matched theoretical values, which validated the accuracy of the antenna model.

#### 3.5.2 Printed Antenna

The true potential for wireless sensor networks and their application in large scale deployments can only be realized if one addresses the cost issues. The relatively high cost of coaxial cable, RF connectors and antennas capable of handling the 2.4GHz signal with minimal attenuation were identified as major cost elements in our design. For example, a single coaxial connector of the SubMiniature Version A (SMA) type such as those used to connect the coaxial cable to the antenna costs the same as the CC2420 transceiver IC. If one ever wishes to use wireless sensors to address practical problems, the mass production cost of the sensor nodes has to be as low as possible. This is the main motivation for printing the antenna directly on the circuit board.

System-level analysis is required to determine the network density as a function of antenna cost. Since sensor networks are spread over an area, a small increase in the link budget will translate into a quadratic decrease in the required number of sensor nodes to cover that area.

#### **Key Antenna Parameters**

The three key parameters in evaluating the coverage of a wireless link are the receiver sensitivity, the antenna gain and the antenna radiation pattern. Since we are using a commercial transceiver, the receiver sensitivity is a given parameter and we can only provide adequate power supply filtering based on the manufacturer's recommendations. On the other hand, the antenna gain and radiation patterns are all under the designer's control if the antenna is printed on the PCB.

Since our architecture targets the largest possible range of uses, we aimed for an omni-

directional antenna (power is radiated uniformly around the antenna) with a few decibels of gain in the horizontal plane. As mentioned previously, this small gain on the horizontal plane will translate in lower node density at the system level and will result in lower system costs.

## 3.6 Software Support Requirements

In embedded systems design, the software requirements must be taken into consideration to ensure that the hardware architecture aligned with the code that will be running on it. Instead of defining a new network architecture, we decided to follow an existing network protocol for Wireless Personal Area Network (WPAN). Following a standard provided a baseline for the memory and speed requirements and allowed hardware design trade-offs to be taken early in the design stages. As a baseline for the node capabilities, the Reduced Function Device (RFD) specifications from the IEEE 802.15.4 [12] standard was followed. This standard originates from the integration of the efforts of HomeRF and the IEEE 802 Working Group 15 and targets low-power and low-cost wireless networking [26]. Its focus is on low complexity and efficient energy usage. The data throughput is much lower than for protocols aimed at data communication such as those covered by the IEEE 802.11 standards. The low data rates are unlikely to be a limiting factor in the type of applications targeted by this architecture.

Furthermore, in the context of research and teaching, the IEEE 802.15.4 has been made publicly available at no fees for download. This contributes to making the research platform more affordable since access to standards is not typically purchased by university or libraries. The availability of a very complete technical standard will provide a great learning opportunity for anyone not familiar with the way standards are written and organized.

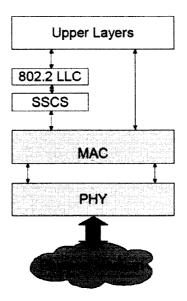

Figure 3.4 [12] illustrate the layers of the 802.15.4 protocol stack. The standard only covers the lower layers namely the Physical layer (PHY) and the Media Access layer (MAC). The upper layers are outside the scope of the standard, but could consist of a research or a student project such as testing a new routing algorithm or a novel application running on top of the MAC layer. The Chipcon CC2420 supports all the PHY requirements of the standard. Some of the MAC requirements are supported by the hardware, thus limiting the software cost and complexity. This allows small microcontrollers to perform quite complex

Fig. 3.4 802.15.4 Device Software Layers

operations on top of the PHY and MAC networking layers.

### 3.6.1 Memory Requirements

### RAM Memory

In order to maintain the content in the memory, some static power must be supplied to the micro-controller even in sleep mode. This small current is integrated over long periods of time since the micro-controller in low-power wireless systems spends most of the time in a sleep state. This pose a significant challenge for the architecture since the RAM becomes the dominant energy user. As a consequence, ultra-low power microcontrollers typically have very little of it (a few kilobytes is typical). The small packet size (128 bytes) defined in the 802.15.4 standard ensure that a minimal amount of RAM is needed to handle incoming transactions. The memory requirements to support the MAC and PHY layers is further reduced since a large portion of the standard is handled by the transceiver IC, including the buffering and validation of incoming packets.

## Flash Memory

The microcontroller on-board flash memory can be supplemented by external serial flash memory to further extend the capabilities of the system. For a small cost, the external flash memory can be much larger than the internal memory of the controller. It can be used to store firmware updates temporarely before the MCU Flash memory is updated. It can also be used to log data in the event of a disruption of the network. Counterintuitively, programming a byte of flash in an external device is less energy efficient than sending the same byte of information through the radio interface [34]. Therfore, for the longest battery life, the use of the wireless network is always preferred.

From our experience, around 20kB of flash memory and 1kB of RAM is sufficient for the sensor node to operate as a reduced function device. A few more kilobytes of flash memory would be sufficient to hold simple application software. However, the RAM requirements for supporting a PAN coordinator vary mostly on how many nodes can connect to the coordinator. Since the coordinator node has to build and maintain a table of the connected node, their internal addresses, pending messages and some routing information, the RAM memory requirements surpass the limits of low-power MCU for large networks. Our research group thus developed a dedicated PAN coordinator [35] using the Philips LPC2106 ARM-based microcontroller.

## 3.6.2 Remote Debugging Capability

The flash and debugging operations can be carried out through the JTAG chain. The processor choice in an environment requiring remote controlling of its operation was explored in the initial phases of this project. The architecture requirements for remote testing of the components in a network environment is detailed in the 2004 International Test Conference proceedings [36].

#### 3.6.3 Validation Suite

A set of firmware drivers was developed to quickly test the board features. They were used to validate the correct operation of the boards after their manufacturing and is still used in between semesters to ensure that they still operate properly. The firmware framework also provides a base code structure for teacher assistants to quickly illustrate various board features and for class demonstrations.

# Chapter 4

# **Design Details**

This chapter will cover the design details and the various aspects considered for the development of the circuit boards of the wireless systems development platform. First, the Main Board, LCD Board and RF Transceiver Board will be detailed. Then, the PCB Design methods and their impact on the boards design will be elaborated.

## 4.1 Main Board