### Design and Scheduling of Efficient Real-Time Embedded Systems

Zaid Al-bayati

Department of Electrical and Computer Engineering McGill University Montréal, Québec, Canada

January 2017

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

© 2017 Zaid Al-bayati

#### Abstract

Computer systems have gone through tremendous changes in the past few decades. Relatively large general purpose computers dominated the early days of computers. With time, demand increased for smaller, more dedicated computer systems, called *embedded systems*. These systems perform a specific set of functions interacting with the physical environment, often in real-time. Real-time embedded systems are found today in many application domains such as the automotive domain, avionics, and control systems. Real-time systems differ from traditional computer systems in their dependence on time as a correctness criteria, i.e., a late correct answer is useless for these systems.

Embedded real-time systems today are more integrated, more parallel, and more complex than ever before. In this thesis, we discuss limitations that affect the applicability of real-time models, analysis methods, and scheduling approaches to the realities of today's embedded systems and propose solutions to address these challenges.

We first look into the issue of shared resources and its effect on the mapping and scheduling of software tasks in a real-time system. Most task mapping approaches proposed in the literature perform task mapping assuming independent tasks that do not share resources. Managing shared resources and their protection mechanisms is performed later. However, this approach might require several rounds of iteration and can lead to inefficient results. In this thesis, we explore the possibility of using different resource protection mechanisms within a single system, and propose to tackle the design problem more efficiently by jointly performing task allocation, scheduling, and resource pro-

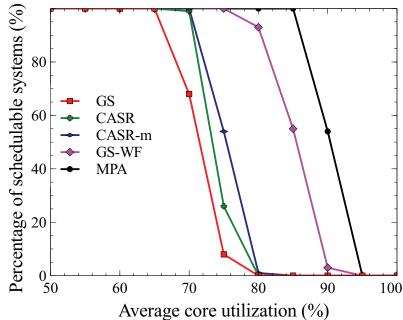

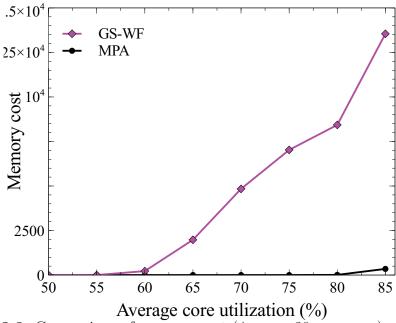

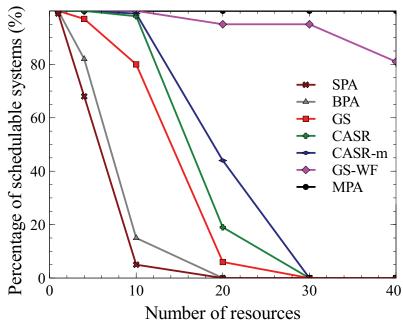

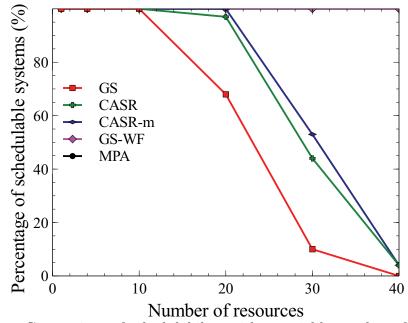

tection mechanism selection. Two approaches are presented to solve this optimization problem: an optimal Mixed Integer Linear Programming (MILP) approach and an efficient heuristic. The proposed work is shown to significantly improve system schedulability. Experimental results indicate that the minimum utilization at which at least 95% of systems become schedulable can be improved from 65%–70% for the best published task allocation algorithms to 76%–85% using our heuristic with minimal memory cost. Even better results can be achieved using the MILP approach.

Next, we look into the design of systems composed of components that have different levels of criticality. *Mixed-Criticality Systems* (MCS) received much attention recently to due their industrial relevance. We focus on three challenges in MCS design: task allocation, fault-tolerance, and model-based design. For task allocation, we show that traditional task allocation algorithms can be inefficient in a mixed-criticality context, and propose an alternative that we call *dual-partitioned* task allocation. Experiments show that for systems that have a utilization of 80% or higher, we can schedule 17% more systems on a given multicore platform using the dual-partitioned approach.

Fault-tolerance is an important issue for MCS since these systems contain a safety critical part. To design MCS that tolerate hardware transient faults, we propose a new mixed-criticality model that simultaneously addresses criticality, reliability, and Quality of Service (QoS). A schedulability test for the new model is derived. Furthermore, to allow designers to incorporate the new model and analysis in their design process, we propose a design space exploration framework based on the new model that supports various fault-tolerance

mechanisms. QoS improvements of up to 42.9% can be achieved using the new model compared to the traditional MCS model extended to support transient faults. To overcome more serious faults that can cause a processor in the system to fail, we present a new design approach for MCS. The standard MCS model operation and analysis are extended to cover this failure scenario. Mapping and scheduling is performed using a new MILP formulation. Experiments show that the proposed approach achieves a 3.2X increase in the number of schedulable systems compared to a baseline design process.

Model-based design is used in many domains for designing complex systems starting from high level models. We focus specifically here on the Synchronous Reactive (SR) model since it is widely used for control-dominated applications. A major challenge when systems designed using the SR model are implemented is the preservation of the model semantics. Sometimes, the model semantics can not preserved unless blocks known as functional delays are added to the system, with negative effects on system performance. In this thesis, we propose algorithms to generate optimized semantic-preserving implementations for MCS specified using the SR model, with minimal functional delay addition. An optimal Branch-and-Bound based algorithm and an efficient heuristic are proposed for this purpose.

#### Abrégé

Les systèmes informatiques ont subi des changements énormes au cours des dernières décennies. Dans leurs débuts, les ordinateurs, de grande taille et à usage général, étaient dominants. Avec le temps, la demande pour des systèmes informatiques plus petits et dédiés pour des tâches plus spécifiques, appelés systèmes embarqués, a augmenté. Ces systèmes exécutent un ensemble de fonctions spécifiques interagissant avec l'environnement physique, souvent en temps réel. Les systèmes embarqués temps-réel se trouvent aujourd'hui dans de nombreux domaines d'application tels que l'automobile, l'avionique et les systèmes de contrôle. Les systèmes temps-réel diffèrent des systèmes informatiques traditionnels dans leur dépendence au temps qui est utilisé comme critère de correction. C'est-à-dire qu'une réponse correcte tardive est inutile pour ces systèmes.

Les systèmes embarqués temps-réel sont aujourd'hui plus intégrés, plus parallèles et plus complexes que jamais. Dans cette thèse, nous discutons des limites qui affectent l'applicabilité des modèles temps-réel, des méthodes d'analyse et des approches d'ordonnancement aux réalités des systèmes embarqués d'aujourd'hui et nous proposons des solutions pour relever ces défis.

En premier lieu, nous examinons la question des ressources partagées et leurs effets sur la cartographie et l'ordonnancement des tâches logicielles dans un système temps-réel. La plupart des approches de cartographie des tâches proposées dans la littérature effectuent la cartographie des tâches en assumant des tâches indépendantes qui ne partagent pas les ressources. La gestion des ressources partagées ainsi que leurs mécanismes de protection sont ef-

fectués plus tard. Cependant, cette approche peut nécessiter plusieurs cycles d'itération et peut mener à des résultats inefficaces. Dans cette thèse, nous explorons la possibilité d'utiliser différents mécanismes de protection des ressources au sein d'un même système et proposons d'aborder plus efficacement le problème de conception en exécutant conjointement l'attribution des tâches, l'ordonnancement et la sélection des mécanismes de protection des ressources. Deux approches sont présentées pour résoudre ce problème d'optimisation: une approche doptimisation linéaire à nombres entiers mixtes optimale (MILP) et une heuristique efficace. Le travail proposé permet d'améliorer considérablement lordonnançabilité du système. Les résultats expérimentaux indiquent que l'utilisation minimale à laquelle au moins 95% des systèmes deviennent ordonnançables peut être améliorée de 65%-70%, dans les meilleurs algorithmes d'allocation de tâche publiés, à 76%-85% en utilisant notre heuristique avec un cot mémoire minime. Des résultats encore meilleurs peuvent être obtenus en utilisant l'approche MILP.

Ensuite, nous examinons la conception de systèmes formés de composants qui ont différents niveaux de criticité. Les systèmes de criticité mixte (MCS) ont récemment reçu beaucoup d'attention en raison de leur pertinence industrielle. Nous nous concentrons sur trois défis en matière de conception MCS: lattribution des tâches, la tolérance aux pannes et la conception basée sur modèle. Pour l'attribution des tâches, nous montrons que les algorithms traditionnels, d'allocation de tâches peuvent être inefficaces dans un contexte de criticité mixte et proposer une alternative que nous appelons allocation de tâches à double partition. Les expériences montrent que pour les systèmes

dont l'utilisation est supérieure ou égale à 80%, qu'on peut ordonnancer 17% de systèmes sur une plate-forme multicœur donnée en utilisant l'approche à deux partitions.

La tolérance aux pannes est un problème important pour les MCS puisque ces systèmes contiennent une partie critique pour la sécurité. Pour concevoir des MCS qui tolèrent les défauts transitoires, nous proposons un nouveau modèle de criticité mixte qui aborde simultanément la criticité, la fiabilité et la qualité de service (QoS). Un test d'ordonnançabilité pour le nouveau modèle est déduit. En outre, pour permettre aux concepteurs d'intégrer le nouveau modèle et l'analyse dans leur processus de conception, nous proposons un cadre d'exploration d'espace de conception basé sur le nouveau modèle qui prend en charge divers mécanismes de tolérance de pannes. Des améliorations de la qualité de service jusqu'à 42.9% peuvent être obtenues en utilisant le nouveau modèle comparé au modèle MCS traditionnel qui peuvent supporter les pannes transitoires. Pour surmonter les pannes plus graves qui peuvent entraner l'échec d'un processeur dans le système, nous présentons une nouvelle approche de conception pour MCS. Le fonctionnement et l'analyse du modèle MCS standard sont élargis pour couvrir ce scénario de défaillance. La cartographie et l'ordonnancement sont effectuées en utilisant une nouvelle formulation MILP. Les expériences montrent que l'approche proposée permet d'obtenir une augmentation de 3.2 fois du nombre de systèmes ordonnançables comparé à un processus de conception de base.

La conception basée sur modèles est utilisée dans de nombreux domaines pour concevoir des systèmes complexes à partir de modèles de haut niveau. Nous focalisons, ici, spécifiquement sur le modèle réactif synchrone (SR), car il est largement utilisé pour les applications dominées par les systèmes de contrôle. Un défi majeur lorsque les systèmes conçus à l'aide du modèle SR sont implementés est la préservation du modèle sémantique. Parfois, le modèle sémantique ne peut pas être conservé à moins que des blocs connus comme des retards fonctionnels soient ajoutés au système, avec des effets négatifs sur la performance du système. Dans cette thèse, nous proposons des algorithmes pour générer des implémentations de conservation sémantique optimisées pour MCS spécifiées à l'aide du modèle SR, avec un minimum d'ajout de retard fonctionnel. Un algorithme optimal basé sur Branch-and-Bound et une heuristique efficace sont proposés à cet effet.

#### Acknowledgements

Although the cover of this document bears my name alone, the reality is far from that. The work in this thesis would not have been possible without the contribution and support of my supervisors, family, and colleagues whom I owe alot.

First of all, I would like to thank my supervisors: Dr. Haibo Zeng and Dr. Brett Meyer. I am deeply grateful to you for your guidance, advice, continuous support, and encouragement. I learned a lot from you throughout this journey as supervisors, as teachers and as persons. I am thankful for the countless hours you contributed to this work and for your support when things were not going so well. I am glad to have worked with you and will always be indebted to you.

I would like also to thank members of the supervising committee: Dr. Zeljko Zilic and Dr. Jörg Kienzle for their insightful comments and feedback which helped improve this work.

I am also thankful to Dr. Marco Di Natale for his guidance and insights while I was working on multicore resource sharing. I would also like to thank Qingling Zhao for her contribution and collaboration on mixed-criticality systems, Jonah Caplan for his contributions to fault-tolerance in mixed-criticality systems, and Dr. Zonghua Gu for his contribution to model-based design in mixed-criticality systems. Many thank to my colleagues at the Reliable Silicon System Lab (RSSL) at McGill University for your support and insightful discussions.

I am also grateful to the Fonds de Recherche du Québec - Nature et Tech-

nologies (FRQNT) and to McGill University for financially supporting this work.

This work would not have been remotely possible without the support of my family. First, my mother, whom no word in the English language can justly thank enough for her support and prayers throughout this journey. My father, who has always supported and encouraged me. My fiancée, Ruaa, who has been a constant source of support and encouragement, and has been patient with my absence. My brother, Dr. Mustafa, my source of strength. My sister, Mariam, the brightest product of the family. I am deeply grateful to you.

## Contents

| 1        | Intr | oduction                                                            | 1 |

|----------|------|---------------------------------------------------------------------|---|

|          | 1.1  | Timing in Embedded System Design                                    | 2 |

|          | 1.2  | Motivation                                                          | 4 |

|          | 1.3  | Thesis Statement                                                    | 8 |

|          | 1.4  | Thesis Contributions                                                | 9 |

|          |      | 1.4.1 Mapping and scheduling in resource-sharing multicore          |   |

|          |      | systems                                                             | 9 |

|          |      | 1.4.2 Task mapping in multicore mixed-criticality systems 10        | 0 |

|          |      | 1.4.3 Fault-tolerance in mixed-criticality systems                  | 1 |

|          |      | 1.4.4 Implementing synchronous reactive models of mixed-criticality | У |

|          |      | systems                                                             | 2 |

|          | 1.5  | Related Publications                                                | 2 |

|          | 1.6  | Thesis Outline                                                      | 6 |

| <b>2</b> | Bac  | kground and Related Work                                            | 7 |

|          | 2.1  | System Model: Basic Definitions                                     | 7 |

|          | 2.2  | Scheduling                                                          | 0 |

|          |      |                                                                     |   |

Contents xiii

|   |      | 2.2.1   | Scheduling in multicore architectures                               | 22 |

|---|------|---------|---------------------------------------------------------------------|----|

|   |      | 2.2.2   | Task allocation: related work $\ \ldots \ \ldots \ \ldots \ \ldots$ | 23 |

|   |      | 2.2.3   | Schedulability analysis                                             | 23 |

|   | 2.3  | Resour  | ce Sharing                                                          | 25 |

|   |      | 2.3.1   | Multiprocessor priority ceiling protocol                            | 26 |

|   |      | 2.3.2   | Multiprocessor stack resource policy                                | 28 |

|   |      | 2.3.3   | Wait-free methods                                                   | 30 |

|   | 2.4  | Mixed   | Criticality Systems                                                 | 31 |

|   |      | 2.4.1   | Basic MCS model                                                     | 32 |

|   |      | 2.4.2   | Schedulability analysis                                             | 34 |

|   |      | 2.4.3   | MCS on multicores: related work $\ \ldots \ \ldots \ \ldots$        | 35 |

|   | 2.5  | Fault-  | Tolerance in MCS                                                    | 37 |

|   |      | 2.5.1   | Lockstep execution and on-demand redundancy $\dots$                 | 38 |

|   |      | 2.5.2   | Transient faults in MCS: related work                               | 40 |

|   |      | 2.5.3   | Permanent faults in MCS: related work                               | 42 |

|   | 2.6  | Model-  | -Based Design Using Synchronous Reactive Models                     | 43 |

|   |      | 2.6.1   | SR semantics preservation                                           | 45 |

|   |      | 2.6.2   | Model-based design: related work                                    | 50 |

| 3 | Tacl | z Alloc | cation in Multicore Real-Time Systems                               | 52 |

| J |      |         | v                                                                   |    |

|   | 3.1  | System  | n Model                                                             | 54 |

|   | 3.2  | Resour  | ce-Aware Task Allocation                                            | 55 |

|   | 3.3  | Proble  | m Formulation with MILP                                             | 56 |

|   |      | 3.3.1   | General system variables and constraints                            | 56 |

|   |      | 3.3.2   | MSRP response time formulation                                      | 58 |

xiv Contents

|   |            | 3.3.3        | MPCP response time formulation                  | . 65                |

|---|------------|--------------|-------------------------------------------------|---------------------|

|   |            | 3.3.4        | Objective function                              | . 73                |

|   | 3.4        | Heuris       | stic Algorithms                                 | . 73                |

|   |            | 3.4.1        | Extending greedy slacker with wait-free methods | . 74                |

|   |            | 3.4.2        | Memory-aware partitioning algorithm             | . 74                |

|   | 3.5        | Exper        | imental Results                                 | . 80                |

|   |            | 3.5.1        | Schedulability analysis                         | . 82                |

|   |            | 3.5.2        | General evaluation of heuristics                | . 84                |

|   |            | 3.5.3        | Effect of different parameters                  | . 87                |

|   |            | 3.5.4        | Evaluation with ILP                             | . 93                |

|   | 3.6        | Concl        | usion                                           | . 95                |

| 4 | Tas        | k Allo       | cation in Mixed-Criticality Systems             | 96                  |

|   | 4.1        | Syster       | m Model                                         | . 97                |

|   |            | 4.1.1        | Elastic Mixed-Criticality (EMC)                 | . 97                |

|   |            | 4.1.2        | Task model                                      | . 99                |

|   |            | 4.1.3        | System behavior                                 | . 100               |

|   | 4.2        | Dual-l       | Partitioned Mixed-Criticality Scheduling        | . 101               |

|   |            | 4.2.1        | Schedulability Analysis                         | . 107               |

|   |            |              |                                                 |                     |

|   | 4.3        | Exper        | imental Evaluation                              | . 108               |

|   | 4.3<br>4.4 | -            | rimental Evaluation                             |                     |

| 5 | 4.4        | Concl        |                                                 |                     |

| 5 | 4.4        | Conclinating | usion                                           | . 114<br><b>116</b> |

Contents xv

|   |      | 5.2.1  | Task model                                          | 120 |

|---|------|--------|-----------------------------------------------------|-----|

|   |      | 5.2.2  | Failure probabilities for transient faults          | 121 |

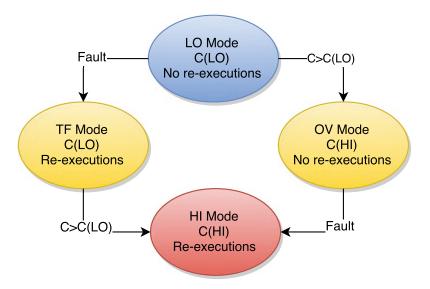

|   | 5.3  | The Fo | our-Mode System Model                               | 121 |

|   |      | 5.3.1  | Re-execution requirements in lockstep cores         | 123 |

|   |      | 5.3.2  | System operation                                    | 124 |

|   |      | 5.3.3  | Providing QoS to LO-criticality tasks               | 125 |

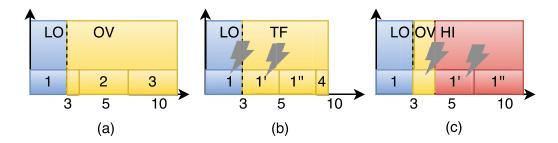

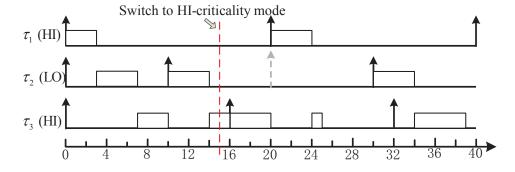

|   |      | 5.3.4  | An illustrative example                             | 125 |

|   | 5.4  | Schedu | ılability Analysis with Transient Faults            | 127 |

|   |      | 5.4.1  | Reducing model pessimism                            | 131 |

|   | 5.5  | Genera | alization to ODR                                    | 132 |

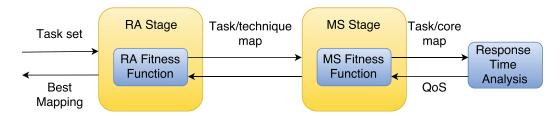

|   | 5.6  | DSE w  | vith Transient Faults                               | 136 |

|   | 5.7  | Experi | imental Results: Transient Faults                   | 139 |

|   |      | 5.7.1  | Experiments on single core architectures            | 140 |

|   |      | 5.7.2  | Experiments on multicore architectures              | 142 |

|   | 5.8  | Schedu | uling MCS with Permanent Faults: Motivation         | 145 |

|   | 5.9  | System | n Operation with Permanent Faults                   | 146 |

|   | 5.10 | Schedu | ulability Analysis with Permanent Faults            | 148 |

|   | 5.11 | MILP-  | Based DSE with Permanent Faults                     | 152 |

|   |      | 5.11.1 | General system variables and constrains             | 152 |

|   |      | 5.11.2 | Schedulability constrains                           | 154 |

|   | 5.12 | Experi | imental Results: Permanent Faults                   | 157 |

|   | 5.13 | Conclu | asion                                               | 160 |

| 6 | Imp  | lemen  | ting Synchronous Reactive Models of Mixed-Criticali | ity |

|   | Syst | ems    | 1                                                   | 162 |

xvi

|   | 6.1     | Schedu                                                      | ulability vs Functional Delay Tradeoff: Example 164 |

|---|---------|-------------------------------------------------------------|-----------------------------------------------------|

|   | 6.2     | System                                                      | n Model                                             |

|   |         | 6.2.1                                                       | Task model                                          |

|   |         | 6.2.2                                                       | EMC model with no mode change task dropping 167     |

|   |         | 6.2.3                                                       | System operation                                    |

|   | 6.3     | Schedu                                                      | ılability Analysis                                  |

|   | 6.4     | Priorit                                                     | by Assignment with Audsley's Algorithm              |

|   | 6.5     | Optim                                                       | ization Algorithms                                  |

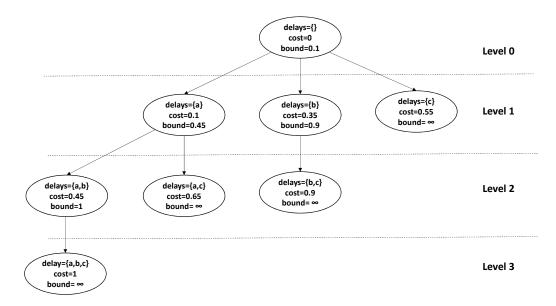

|   |         | 6.5.1                                                       | The Branch-and-Bound algorithm                      |

|   |         | 6.5.2                                                       | The heuristic algorithm                             |

|   | 6.6     | Experi                                                      | imental Results                                     |

|   | 6.7     | Conclu                                                      | asions                                              |

|   |         |                                                             |                                                     |

| 7 | Con     | clusio                                                      | n and Future Work 198                               |

| 7 | Con 7.1 |                                                             | n and Future Work 198<br>contributions              |

| 7 |         |                                                             |                                                     |

| 7 |         | Key C                                                       | ontributions                                        |

| 7 |         | Key C 7.1.1                                                 | ontributions                                        |

| 7 |         | Key C 7.1.1 7.1.2                                           | Ontributions                                        |

| 7 |         | Key C<br>7.1.1<br>7.1.2<br>7.1.3                            | Ontributions                                        |

| 7 |         | Key C<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4                   | Resource-sharing multicores                         |

| 7 | 7.1     | Key C<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4                   | Resource-sharing multicores                         |

| 7 | 7.1     | Key C<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4                   | Resource-sharing multicores                         |

| 7 | 7.1     | Key C<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>Summ<br>Future | Resource-sharing multicores                         |

| xvii |

|------|

|      |

| 7.3.4 | Considering and quantifying migration overheads $\dots 203$ |

|-------|-------------------------------------------------------------|

| 7.3.5 | MCS under multiple processor failure                        |

| 7.3.6 | A holistic fault-tolerant MCS model                         |

## List of Tables

| 2.1 | Max errors for delays on the sensor and actuator paths                  | 49  |

|-----|-------------------------------------------------------------------------|-----|

| 3.1 | Task parameters for the ILP example system                              | 61  |

| 3.2 | Remote priority ceiling calculation                                     | 68  |

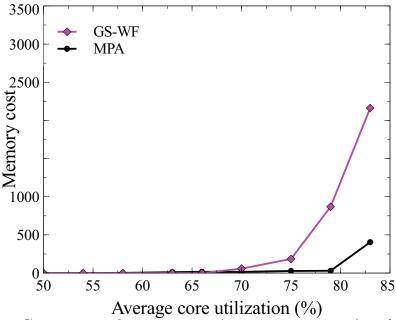

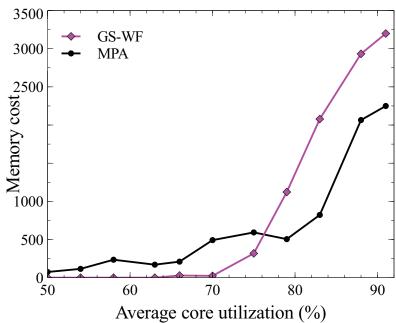

| 3.3 | Schedulability/average memory cost (GS-WF and MPA only, in              |     |

|     | bytes)                                                                  | 83  |

| 3.4 | Average runtime (in seconds)                                            | 84  |

| 3.5 | MPCP schedulability/average memory cost (GS-WF and MPA $$               |     |

|     | only, in bytes) for different sharing factors                           | 92  |

| 3.6 | $\operatorname{MSRP}$ schedulability/average memory cost (GS-WF and MPA |     |

|     | only, in bytes) for different sharing factors                           | 93  |

| 3.7 | MPCP Schedulability/average memory cost (in bytes) at differ-           |     |

|     | ent utilizations                                                        | 94  |

| 3.8 | MSRP Schedulability/average memory cost (in bytes) at differ-           |     |

|     | ent utilizations                                                        | 94  |

| 4.1 | Task Parameters for The Example System                                  | .04 |

| 5.1 | An Example Task Set                                                     | 26  |

| T · · C CD 11  | •   |

|----------------|-----|

| List of Tables | XIX |

| Dist of Tables | AIA |

| 5.2 | An Example Task Set                                           |

|-----|---------------------------------------------------------------|

| 5.3 | Transformation parameters for the four fault-tolerance mecha- |

|     | nisms                                                         |

| 5.4 | Task set transformation                                       |

| 5.5 | Rules for generating unique MS configurations from an integer |

|     | x for $n$ cores                                               |

| 5.6 | An Example Task Set                                           |

| 6.1 | Timing parameters for the example in Figure 6.2 169           |

| 6.2 | Notations used in this chapter                                |

| 6.3 | Timing parameters for the example in Figure 6.5               |

|     |                                                               |

## List of Figures

| 1.1  | The main components in an embedded systems design flow        |    |

|------|---------------------------------------------------------------|----|

|      | from a timing viewpoint                                       | 3  |

| 2.1  | Basic job parameters                                          | 19 |

| 2.2  | Classification of scheduling algorithms                       | 21 |

| 2.3  | Writer and readers stages in wait-free methods                | 30 |

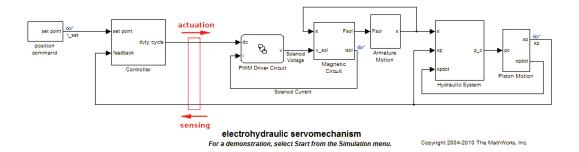

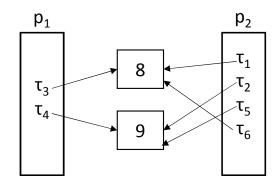

| 2.4  | Architectures for multicore fault-tolerant systems            | 39 |

| 2.5  | Supported fault-tolerance mechanisms                          | 40 |

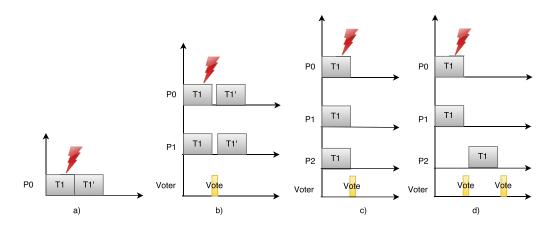

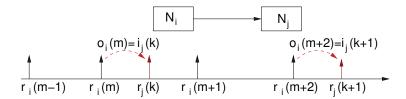

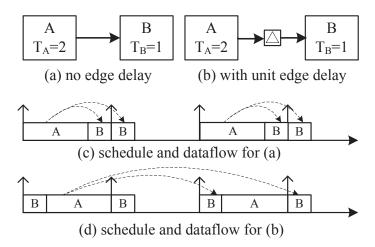

| 2.6  | Input/output relation with no edge delay                      | 47 |

| 2.7  | Input/output relation with unit edge delay                    | 47 |

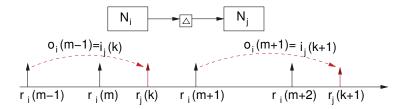

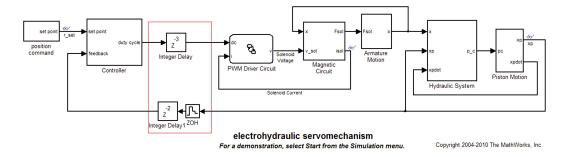

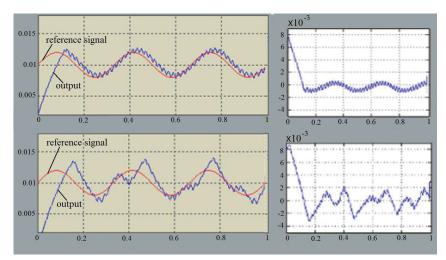

| 2.8  | A Simulink example of an hydraulic servomechanism (represen-  |    |

|      | tative of a suspension control)                               | 48 |

| 2.9  | Hydraulic servo with additional communication delays          | 48 |

| 2.10 | Actuator position and error for the hydraulic servo without   |    |

|      | (top) and with (bottom) delays                                | 49 |

| 3.1  | MPCP remote ceiling example                                   | 68 |

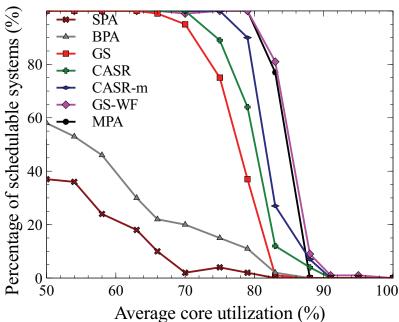

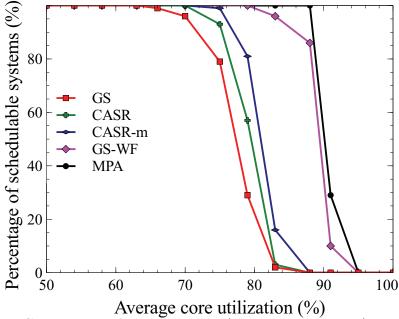

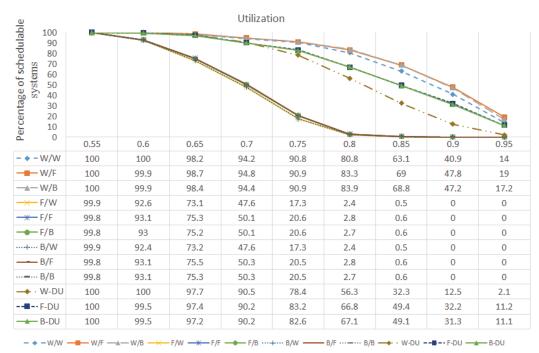

| 3.2  | Comparison of schedulability (8 cores, 4 resources) with MPCP | 85 |

| 3.3  | Comparison of schedulability (8 cores, 4 resources) with MSRP. 85        |

|------|--------------------------------------------------------------------------|

| 3.4  | Comparison of memory cost (8 cores, 4 resources) with MPCP . $86$        |

| 3.5  | Comparison of memory cost (8 cores, 4 resources) with MSRP $$ . 86       |

| 3.6  | Comparison of schedulability (4 cores, 20 resources )- MPCP 89 $$        |

| 3.7  | Comparison of schedulability (4 cores, 20 resources) - MSRP $$ 89        |

| 3.8  | Comparison of memory cost (4 cores, 20 resources) - MPCP $$ 90           |

| 3.9  | Comparison of memory cost (4 cores, 20 resources) - MSRP $$ 90           |

| 3.10 | Comparison of schedulability with a variable number of resources         |

|      | - MPCP                                                                   |

| 3.11 | Comparison of schedulability with a variable number of resources         |

|      | - MSRP                                                                   |

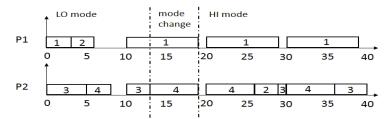

| 4.1  | Example system execution trace                                           |

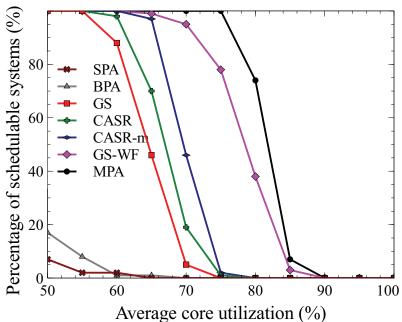

| 4.2  | Percentage of schedulable systems at different LO-utilizations           |

|      | for various heuristics (before applying DPM)                             |

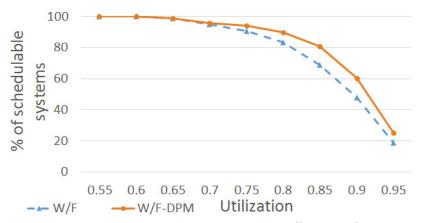

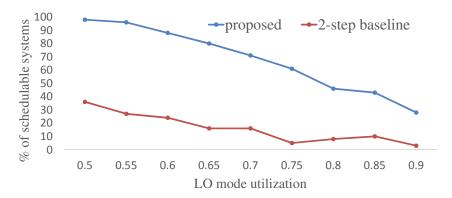

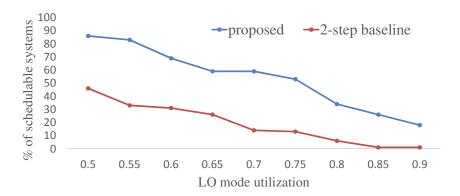

| 4.3  | Improvement on schedulability at different LO-utilizations 111           |

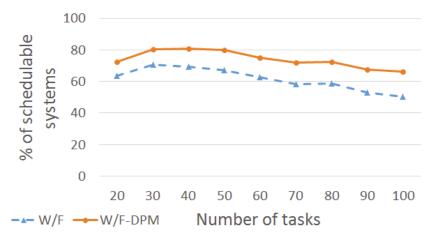

| 4.4  | Improvement on schedulability at different tasks counts 111              |

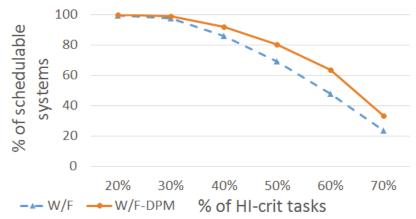

| 4.5  | Improvement on schedulability at different percentages of HI tasks $112$ |

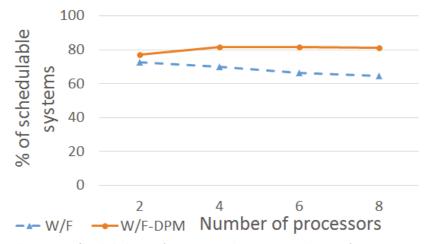

| 4.6  | Scalability of DPM to larger numbers of processors                       |

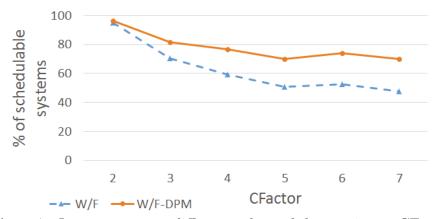

| 4.7  | Improvement at different values of the maximum CF<br>actor 113 $$        |

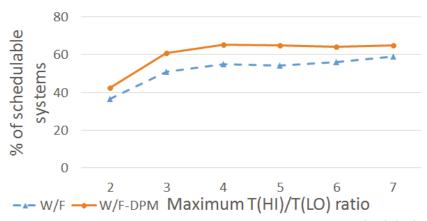

| 4.8  | Improvement at different values of the maximum $\mathrm{T(HI)/T(LO)}$    |

|      | ratio                                                                    |

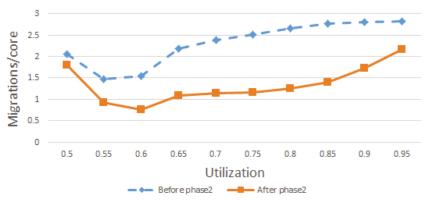

| 4.9  | Impact of Phase 2                                                        |

| 5.1  | The four-mode system model                                               |

| 5.2  | An execution trace for the task set in Table 5.1 when (a) an    |

|------|-----------------------------------------------------------------|

|      | overrun occurs; (b) a fault occurs; (c) both occur              |

| 5.3  | DSE workflow using nested genetic algorithms                    |

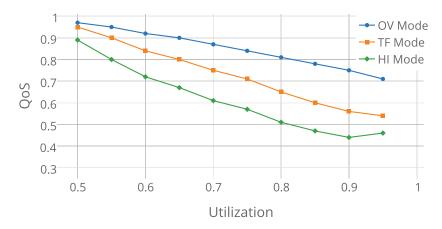

| 5.4  | Modes OV and TF achieve better QoS than HI for all utiliza-     |

|      | tions ( $F$ not bounded)                                        |

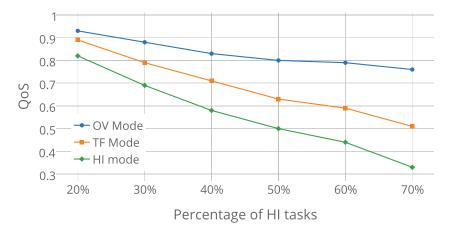

| 5.5  | Modes OV and TF achieve better QoS than HI for different        |

|      | percentages of HI tasks ( $F$ not bounded)                      |

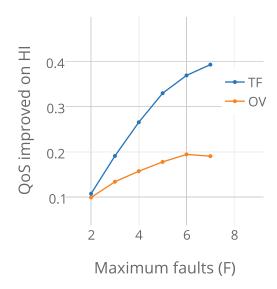

| 5.6  | Average improvement over all system utilizations for OV and     |

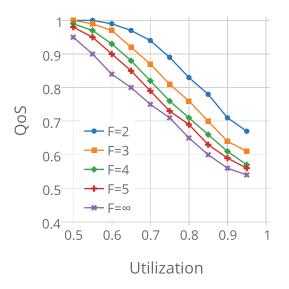

|      | TF modes compared to HI mode                                    |

| 5.7  | Performance of TF mode for different $F.$                       |

| 5.8  | ODR provides better QoS in multicore systems as utilization     |

|      | increases                                                       |

| 5.9  | ODR provides better QoS in multicore systems as the percent-    |

|      | age of HI tasks increases                                       |

| 5.10 | Combining ODR techniques improves QoS                           |

| 5.11 | Combining ODR techniques improves schedulability                |

| 5.12 | An example system to illustrate the different scenarios to be   |

|      | considered in the schedulability analysis with failures         |

| 5.13 | Schedulability at different utilizations (N=20, L=4) 159        |

| 5.14 | Schedulability at different utilizations (N=12, L=3) 159        |

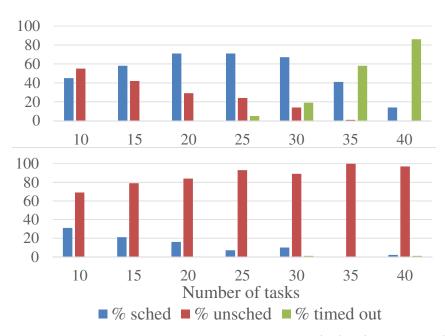

| 5.15 | Schedulability at different task set sizes $(U(LO)=0.7, L=4)$ : |

|      | proposed (top), 2-step baseline (bottom)                        |

| 6.1  | Multirate SR models without edge delay, shown in (a), and with       |

|------|----------------------------------------------------------------------|

|      | unit edge delay, shown in (b), and the corresponding schedules,      |

|      | shown in (c) and (d)                                                 |

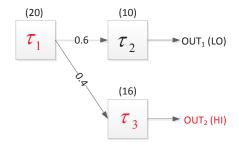

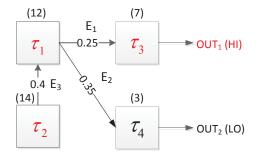

| 6.2  | An example mixed-criticality SR model. The number in paren-          |

|      | theses above a block denotes its period, and the number along        |

|      | the edge denotes its cost                                            |

| 6.3  | An example of EMC                                                    |

| 6.4  | Example of a Branch-and-Bound search tree                            |

| 6.5  | An example mixed-criticality synchronous program. The num-           |

|      | ber in parentheses above a block denotes its period 186              |

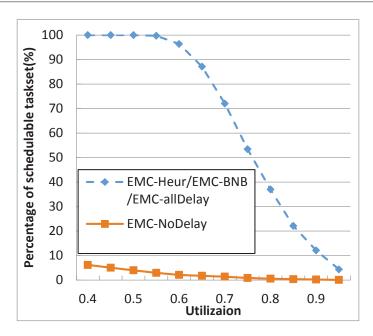

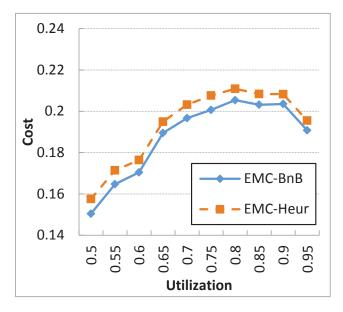

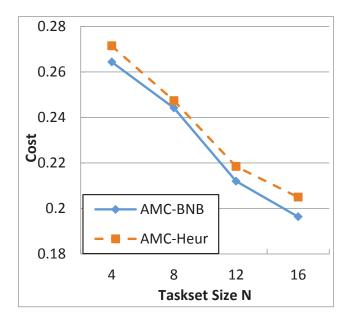

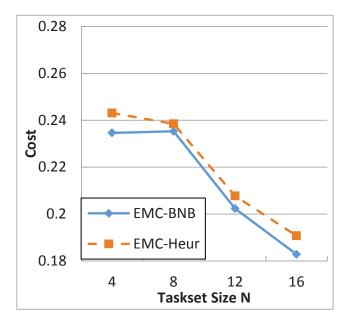

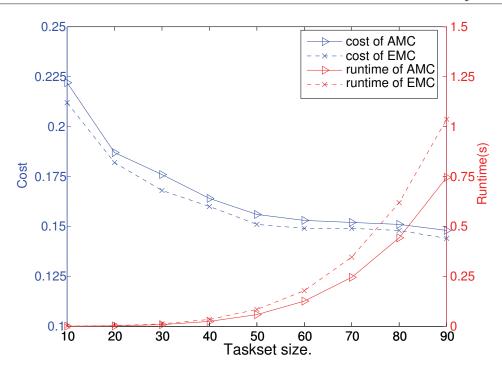

| 6.6  | Schedulability of different algorithms vs. $U_{LO}$ for AMC 189      |

| 6.7  | Schedulability of different algorithms vs. $U_{LO}$ for EMC 190      |

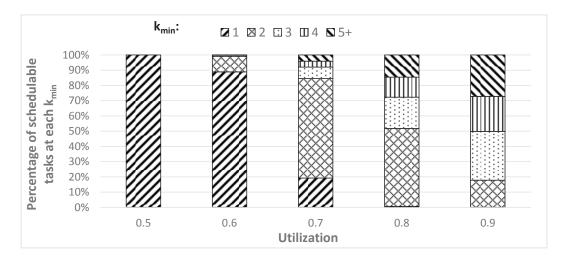

| 6.8  | Schedulability of EMC vs. minimum period scaling factor $k_{\min}$ , |

|      | for different $U_{LO}$                                               |

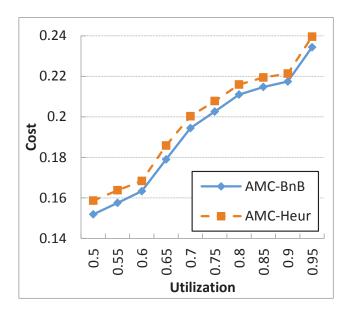

| 6.9  | System cost vs. $U_{LO}$ for AMC                                     |

| 6.10 | System cost vs. $U_{LO}$ for EMC                                     |

| 6.11 | System cost vs. taskset size for AMC                                 |

| 6.12 | System cost vs. taskset size for EMC                                 |

| 6.13 | System cost and runtime of the heuristic for larger systems 196      |

### Chapter 1

### Introduction

Embedded systems have become prevalent in all aspects of our lives today. Approximately 98% of the microprocessors sold today are used in embedded systems [1]. Embedded systems are already present in cars, airplanes, implantable medical devices, TVs, etc. They are also central to many emerging technologies such as wearable devices and the Internet of Things. Many of these systems are real-time embedded systems that have to interact with the environment within predefined timing constraints. "A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced" [2].

When designing such systems, the designer must make sure that the system always respects its timing constraints even for a worst case combination of internal and external events. This differs from traditional computing where emphasis has usually been on improving average case performance. In many real-time applications, a reaction that occurs too late could be useless or even

dangerous [3]. The emphasis on providing enough resources for the worst case behavior often has to be balanced with efficiency and other design constraints. Managing this tradeoff is not a trivial task, and designers need to handle often conflicting objectives of safety, efficiency, cost, and time-to-market.

In this dissertation, we focus on the design process of embedded real-time systems and propose new system models, analysis methods, and scheduling approaches. Our objective is to enable the design of efficient real-time systems that maximize the usage of the available hardware resources without compromising other system requirements such as timing and reliability constraints.

#### 1.1 Timing in Embedded System Design

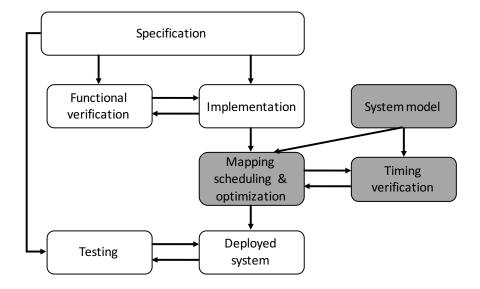

Figure 1.1 shows the main components of an example embedded design process from a timing viewpoint. The starting point for any design is a high level specification given as one or more documents describing the intended functionality of the system and the design requirements. Designers then convert this high level specification to a more refined implementation. This implementation needs to be deployed on a hardware platform. We focus on single core and homogeneous multicore hardware platforms where the implementation consists of one or more software programs or tasks that can execute on any core.

When multiple tasks run on a processor, the processor time allocated to each task must be determined. On a multicore platform, an additional complication is determining a suitable allocation of tasks to processors. This step is known as task mapping (also known as task allocation or partitioning). The set of rules that at any time, determines the order in which tasks are executed

Fig. 1.1: The main components in an embedded systems design flow from a timing viewpoint

on a particular processor is called a scheduling algorithm [3].

This mapping and scheduling operation therefore takes an implementation consisting of a set of software tasks and a particular hardware platform and produces a deployed system. This is typically an iterative procedure where mapping and scheduling decisions are made and then revisited again and again to optimize one or more design objectives.

Before a fully deployed system is produced, the system must undergo comprehensive verification to ensure that the system's implementation matches the specification and requirements. For real-time systems, we need to both verify that the system produces the correct outputs (functional verification) and that it produces these outputs on time without violating the system's timing constraints (timing verification). Finally, the product goes through final testing.

Timing verification is typically done through formal analysis, often referred to as schedulability analysis, on abstract models of the system. This abstract system model focuses on those aspects that impact the timing verification process such as the number of processors, the number of tasks and their timing parameters. The system model also specifies other system features that can affect the timing analysis, for example: are tasks independent, or do they share resources? Do tasks have fixed priorities, or does a task's priority change over time? Are faults modeled, and if so, what is their impact on tasks? We will describe a basic timing model in Chapter 2 and adapt it in each of the remaining chapters, abstracting away details not relevant to the problem described in the chapter and adding new details.

In this work, we focus on the three "real-time related" components in Figure 1.1: a) the system model, b) timing verification, and c) mapping, scheduling and optimization. We propose new system models, associated analysis methods for verifying timing constraints, and new approaches for mapping and scheduling real-time systems.

#### 1.2 Motivation

Designing real-time embedded systems is becoming an increasingly difficult task as consumers demand more features leading to more complex designs than ever before. This complexity accompanied with the pressure from increased competition is causing a reduction in the quality of the final products released to the market. Companies are often being forced to recall products leading to billions of dollars of losses, and sometimes unfortunately, it leads to tragic loss

1.2 Motivation 5

of lives. The automotive industry, for example, where cost is a very important design constraint, is one of the most prominent examples of these problems. According to the National Highway Traffic Safety Administration [4], in 2013 the auto industry recalled 22 million cars, more than the number of cars sold that year [5]. This figure went up to 51 million in 2015 [6].

As the number of lines of code in a modern vehicle is rapidly increasing, software errors, whether due to functionally wrong code or timing errors, will constitute a significant part of design problems. This is also true for other industries such as avionics, medical devices, and consumer electronics. Our focus here is on timing-related errors. Many real-time system models and analysis methods have been proposed over the years. [7] provides a survey of some of the prominent real-time models for single core platforms. Tools such as Symtavision [8] and aiT [9] have been developed allowing designers to perform timing analysis of real-time systems.

However, there is always a need to adapt real-time models and propose new ones to accommodate emerging design and architecture trends such as the use of multicore architectures in real-time systems [10], and the integration of tasks with different criticalities on a common platform [11].

We will give special attention in this thesis to multicore architectures. Multicore architectures are becoming more common in real-time systems. The computational demands of application are increasing at a rapid pace. To address these demands, chip manufacturers have focused previously on increasing clock speeds. However, due to heating issues, this approach has become problematic. Instead, there is now an increasing trend towards using multiprocessor

platforms for high-end real-time applications [10].

Today's embedded systems are also more integrated than ever before. Another increasingly important trend in real-time systems is the integration of components of different levels of criticality onto a common hardware platform [12]. This led to the emergence of the concept of *Mixed-Criticality Systems* (MCS) [12]. The critical part of the system is often subject to certification requirements from certification authorities while the less critical tasks are not. Current certification standards, such as ISO26262 in the automotive domain and DO-178C in the avionics domain, define several criticality levels according to the level of assurance required for a given function.

Focusing on these design trends, we observe the following limitations in previous real-time models and scheduling techniques:

• Mapping and scheduling in resource-sharing multicore systems: tasks in real embedded systems often share resources such as shared variables, data structures, I/O resources, and peripherals. When real-time tasks allocated on different cores cooperate through the use of shared communication resources, they need to be protected by mechanisms that guarantee access in a mutually exclusive way with bounded worst-case blocking time. While exclusive access guarantees data consistency for the shared resource, it has a direct impact on scheduling and task allocation because of blocking delays. The problem of finding a feasible task allocation is known to be NP-hard (even in the case of no shared resources) [13]. Most works on task allocation and scheduling in multicore ignored the effect of shared resources. However, resource-agnostic task

1.2 Motivation 7

allocation algorithms can introduce bottlenecks in the system through unnecessary distribution of tasks that share global resources across different processors [14].

- Task mapping in multicore mixed-criticality systems: MCS bring new and interesting challenges to the mapping problem. MCS can have multiple operational modes and inherently provide different guarantees to tasks in these modes. This complicates the mapping and scheduling problem as tasks can have different execution times in different modes. Traditional mapping and scheduling approaches do not extend to or become inefficient when applied to mixed-criticality systems.

- Fault-tolerance in mixed-criticality systems: MCS contain a safety critical part. That part of the system must be made reliable and should be able to survive transient or permanent faults occurring in the system. The problem of designing fault-tolerant MCS, however, has not yet received much attention [12]. Faults are typically tolerated using temporal and spatial redundancy. This redundancy imposes additional constraints on the design of the mixed-criticality system. System models, analysis techniques, and mapping and scheduling approaches for MCS should be adapted to take into account tasks' reliability requirements.

- Model-based design for mixed-criticality systems: model-based design is among the best practices for software development, especially in the automotive and aeronautic industry [15]. In a model-based design process, software implementations can be automatically generated from high

level models, reducing the number of errors injected by the design team. When a system implementation is generated automatically, the implementation might not be schedulable unless the designer modifies the model by adding functional delays. These delays have a negative impact on the system's cost and performance and should be avoided when possible. While there has been substantial focus on developing expressive functional models and languages, this has not been matched by a similar effort on the selection of the best mapping and the generation of optimized implementations. This is especially true in the case of mixed-criticality systems where efficient solutions to the problem of implementing a system developed using a model-based design process are still lacking

#### 1.3 Thesis Statement

This thesis studies emerging trends in real-time system design. State-of-the-art real-time systems are composed of more functions that have different criticalities, share more resources, and are executing on more cores than ever before. With this observation in mind, we propose new mapping and scheduling approaches for resource-sharing multicore real-time systems. For mixed-criticality systems, we propose new system models and analysis methods for fault-tolerant MCS. We also propose new mapping and scheduling approaches for MCS that take into account the redundancy required for fault-tolerance. Moreover, we investigate generating MCS implementations in a model-based design flow. A persistent theme throughout the thesis is efficiency, i.e. pro-

ducing solutions that preserve design requirements while maximizing the use of available resources and/or minimizing implementation cost.

#### 1.4 Thesis Contributions

To address the limitations in real-time models and design techniques discussed in Section 1.2, we make the following contributions in this thesis:

# 1.4.1 Mapping and scheduling in resource-sharing multicore systems

To overcome problems with resource-agnostic task allocation, we propose two novel resource-aware task allocation approaches for multicore real-time systems. Shared resources in a multicore system can be protected by lock-based mechanisms such as the Multiprocessor Priority Ceiling Protocol (MPCP) [16] and the Multiprocessor Stack Resource Policy (MSRP) [17], or by wait-free resources. Lock-based mechanisms have a negative impact on the schedulability of the system by forcing tasks to incur blocking while they wait for the resource to be unlocked. Wait-free methods can improve schedulability at the expense of additional memory. We exploit the tradeoff between lock-based and waitfree mechanisms and propose to consider the selection of the protection mechanism as an additional design variable. A more general design problem than previously explored is formulated through jointly performing task allocation, scheduling, and resource protection mechanism selection. The problem is formulated as a Mixed Integer Linear Program (MILP) for both MPCP and MSRP to find an optimal solution. Moreover, a heuristic algo-

rithm is proposed to solve the problem more quickly with good sub-optimal solutions for large systems where an MILP solution might take a long time to find. The solutions proposed produce more efficient task configurations than previously proposed algorithms, significantly extending the range of systems that can be scheduled on a particular platform. Experimental results indicate that state-of-the-art algorithms deteriorate quickly for systems beyond 65% utilization capacity and almost cease to schedule any systems beyond 80% utilization. Our proposed heuristic continues to schedule almost all systems at 80% utilization. The MILP achieves even better results. Section 3.5 provides a detailed comparison.

#### 1.4.2 Task mapping in multicore mixed-criticality systems

As mentioned in Section 1.2, traditional task allocation algorithms can become inefficient in a mixed-criticality context. To preserve the guarantees provided to the critical tasks while efficiently executing non-critical tasks in the systems, we strike a balance between global and partitioned scheduling approaches and propose a novel semi-partitioned scheduling approach tailored for MCS. To this end, we propose the dual-partitioned mixed-criticality task allocation algorithm. Our experiments (Section 4.3) indicate that the dual-partitioned algorithm can schedule 17% more systems than traditional task allocation algorithms at system utilizations of 80% or higher.

#### 1.4.3 Fault-tolerance in mixed-criticality systems

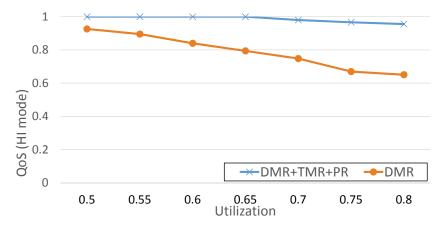

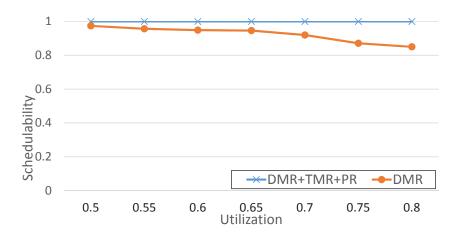

To incorporate concerns about reliability under hardware transient faults into MCS design, we propose a new MCS system model that jointly addresses both reliability and criticality requirements. In the new model, critical tasks are guaranteed sufficient service under transient faults to satisfy reliability requirement from standards such as DO-178C [18]. We derive schedulability analysis for the new model. The model and analysis support various fault-tolerance mechanisms such as re-execution, Dual Modular Redundancy (DMR), Triple Modular Redundancy (TMR), and passive replication. Moreover, we present a design space exploration approach that explores different task mappings and fault-tolerance mechanisms. The proposed exploration approach aims to find designs that satisfy criticality and reliability requirements while also addressing efficiency by maximizing the service provided to non-critical tasks.

We also consider permanent hardware faults in MCS and present a design approach for multicore MCS that can survive a processor failure. To this end, we extend the system operation description and schedulability analysis of the standard MCS model to incorporate the failure of one of the processors. An MILP-based mapping and scheduling approach is proposed to produce MCS designs that are efficient, tolerant to permanent faults, and adhere to criticality requirements. The possibility of processor failures is taken pro-actively into account when making the initial mapping and scheduling decisions. We show that this design approach improves schedulability significantly (for example a 3.2X improvement is observed for systems composed of 20 tasks and 4 cores)

over a design approach that adds reliability on top of an initial reliabilityagnostic system design.

# 1.4.4 Implementing synchronous reactive models of mixed-criticality systems

Various models of computation have been used in model-based design for embedded systems. We focus here on the Synchronous Reactive (SR) model of computation which is used extensively for control applications and is the underlying model of computation for many formalisms and languages such as Simulink, Esterel, LUSTRE, and SIGNAL. We propose efficient solutions to the problem of implementing synchronous reactive models of MCS. Our objective is to ensure the preservation of the model semantics in the implementation while minimizing the use of functional delays. An optimal branch-and-bound based algorithm and a heuristic algorithm are proposed for this purpose. Our experimental evaluation in Section 6.6 shows that the heuristic algorithm produces close to optimal results (only about 3% higher cost) while being scalable to large systems.

#### 1.5 Related Publications

The work in this thesis resulted in several publications which are listed below.

[19] Z. Al-bayati, Y. Sun, H. Zeng, M. Di Natale, Q. Zhu and B. H. Meyer, "Task placement and selection of data consistency mechanisms for real-time multicore applications," 21st IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS'15), pp. 172-181.

In this paper, we propose a resource-aware task allocation algorithm for systems that use MSRP to protect shared resources. Furthermore, we leverage the additional opportunity provided by wait-free methods and propose an algorithm that performs both task allocation and data consistency mechanism selection (MSRP or wait-free). Results show that the selective use of wait-free methods can significantly extend the range of schedulable systems at the cost of memory. This paper is covered in Chapter 3.

[20] Z. Al-bayati, Q. Zhao, A. Youssef, H. Zeng and Z. Gu, "Enhanced partitioned scheduling of Mixed-Criticality Systems on multicore platforms," The 20th Asia and South Pacific Design Automation Conference (ASPDAC'15), 2015, pp. 630-635.

In this paper, the efficient partitioning of MCS on multicore architectures is discussed. A novel mixed-criticality partitioning algorithm, the Dual-Partitioned Mixed-Criticality (DPM) algorithm, is presented. Experimental results show that DPM consistently outperforms existing mixed-criticality partitioning algorithms, for example, at utilizations of 0.8 or higher, DPM is able to schedule 17% more systems. This paper is discussed in Chapter 4.

3. [21] Z. Al-bayati, J. Caplan, B. H. Meyer and H. Zeng, "A four-mode model for efficient fault-tolerant mixed-criticality systems," 2016 Design,

14 Introduction

Automation and Test in Europe Conference & Exhibition (DATE'16), 2016, pp. 97-102.

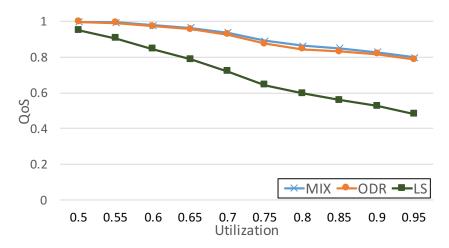

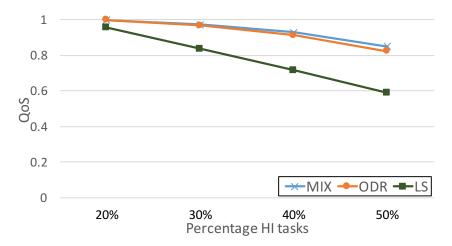

In this paper, we consider the problem of designing and scheduling certifiable fault-tolerant mixed-criticality systems under transient faults. We propose a new four-mode model that addresses faults and execution time overruns with separate modes. This model, combined with the selective continuation of low-criticality tasks, improves the Quality of Service (QoS) to these tasks while providing the same guarantee to high-criticality tasks. Experimental results show that QoS improvements of up to 42.9% can be achieved by the new model. This paper is discussed in Chapter 5.

4. [22] Z. Al-bayati, B. H. Meyer and H. Zeng, "Fault-tolerant scheduling of multicore mixed-criticality systems under permanent failures," 2016 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT'16), 2016, pp. 57-62.

In this paper, we present an approach to design multicore mixed-criticality systems that can survive permanent processor failures. Critical tasks executing on the failing cores are migrated to other cores to allow them to continue execution. Schedulability analysis for the extended model is developed. Then, the problem of finding a mixed-criticality system configuration on a multicore architecture is formulated as a MILP. This paper is discussed in Chapter 5.

[23] Q. Zhao, Z. Al-bayati<sup>1</sup>, H. Zeng, and Z. Gu, "Optimized Implementation of Multi-Rate Mixed-Criticality Synchronous Reactive Models,"

ACM Transactions on Design Automation of Electronic Systems (TO-DAES). Volume 22 Issue 2, Article 23. January 2017.

The paper considers model-based design using SR models for MCS. The paper presents a branch-and-bound procedure and a heuristic algorithm to minimize the total system cost of functional delays in the implementation. This paper is discussed in Chapter 6.

Two other journal papers are still under review:

Z. Al-bayati, Y. Sun, H. Zeng, M. Di Natale, Q. Zhu and B. H. Meyer, "Partitioning and Selection of Data Consistency Mechanisms for Multicore Real-Time Systems".

This paper extends [19] with support for the MPCP suspension-based protocol. An MILP-based solution method is also presented to perform task allocation and data consistency mechanism selection in an optimal way for both MPCP and MSRP. The paper is discussed in Chapter 3.

7. J. Caplan, Z. Al-bayati<sup>2</sup>, H. Zeng, and B. H. Meyer, "Mapping and Scheduling Mixed-Criticality Systems with On-Demand Redundancy".

This paper extends the model and analysis in [21] to support on-demand redundancy with various fault tolerance mechanisms. A design space

<sup>&</sup>lt;sup>1</sup>My contribution for this paper was being the main developer of the branch-and-bound based algorithm and phase 2 of the heuristic with input from Ms. Zhao. I also implemented the parts I contributed.

<sup>&</sup>lt;sup>2</sup>For this paper, the core model was co-developed with Mr. Caplan. I also contributed the derivation of the generic re-execution profiles.

16 Introduction

exploration approach based on the improved analysis is also presented. The paper is discussed in Chapter 5.

## 1.6 Thesis Outline

Chapter 2 presents background information essential to the understanding of the rest of the thesis and discusses related works.

Chapter 3 presents our resource-aware mapping and scheduling approaches for mulitcore real-time systems. An optimal MILP-based solution is presented followed by a sub-optimal heuristic. Experimental results comparing these approaches to state-of-the-art algorithms are also presented.

Chapter 4 presents a novel efficient task allocation approach specific for MCS. Experimental results are presented comparing this approach with traditional task allocation approaches.

Chapter 5 presents our solutions for designing fault-tolerant MCS under both transient and permanent faults. For both types of faults, an MCS model, its analysis, and accompanying design space exploration approaches are presented.

Chapter 6 presents two algorithms for implementing MCS designed using a model-based design process. Experiments exploring the performance and scalability of both algorithms are presented.

Chapter 7 concludes the thesis highlighting the main findings and outlining areas for future improvement.

# Chapter 2

# Background and Related Work

In this chapter, we present background information on system models and analysis in real-time systems focusing especially on resource-sharing multicore systems and Mixed-Criticality Systems (MCS). We also discuss relevant related works. The chapter starts by presenting a basic model for real-time systems in Section 2.1. In Section 2.2, we discuss scheduling and task allocation. In Section 2.3, we discuss the effect of introducing shared resources into the scheduling problem. In Section 2.4, we give a brief introduction to MCS. In Section 2.5, we discuss fault-tolerance in the context of MCS. Finally, in Section 2.6, we give a brief overview of model-based design.

## 2.1 System Model: Basic Definitions

In this section, we describe a generic (from the timing viewpoint) system model. We consider a system in which the functionality can be divided into a set of schedulable units called tasks. A system consists of a set of N tasks

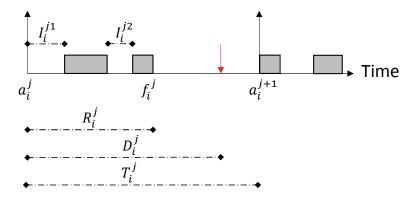

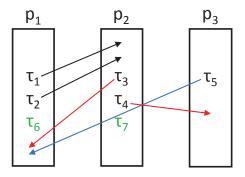

$\Gamma = \{\tau_1, \tau_2, ..., \tau_N\}$ , and M homogeneous processors  $P = \{p_1, p_2, ..., p_M\}$ . For single core architectures, M=1. A task is the smallest entity scheduled by the operating systems. Each instance of a task is called a job. Tasks can generate an infinite sequence of jobs. We denote the jth instance (job) of a task  $\tau_i$  by  $\tau_{i,j}$ . A job  $\tau_{i,j}$  can be characterized by the following parameters (summarized in Figure 2.1):

- Arrival time  $(a_i^j)$ : the time instant at which the job becomes ready to execute.

- Finish time  $(f_i^j)$ : the time instant at which the job finishes its execution.

- Execution time  $(C_i^j)$ : the total amount of time that the job spends executing on the processor (sum of the two shaded regions in Figure 2.1).

- Interference  $(I_i^j)$ : the total amount of time that the job spends waiting for other jobs to finish their execution (sum of  $I_i^{j1}$  and  $I_i^{j2}$  in Figure 2.1).

- Relative deadline (D<sub>i</sub><sup>j</sup>): the amount of time that the task is given to complete after its arrival. This is typically the same for all jobs of task (i.e. ∀ jobs j, k of task τ<sub>i</sub>: D<sub>i</sub><sup>j</sup> = D<sub>i</sub><sup>k</sup> = D<sub>i</sub>).

- Response time  $(R_i^j)$ : the total amount of time the job takes from arrival until it finishes execution including interference from other tasks .  $R_i^j = f_i^j a_i^j$

- Inter-arrival time or period  $(T_i^j)$ : the amount of time between the arrival of the job and the arrival of the subsequent job of the task  $T_i^j = a_i^{j+1} a_i^j$ .

Fig. 2.1: Basic job parameters

Tasks that release jobs in an irregular manner (arrival times of the task's jobs are unrelated) are called *aperodic tasks*. Tasks that release jobs at regular intervals are called *periodic tasks*. For periodic tasks, the amount of time between the arrivals of two subsequent jobs is constant. Between the two types is another type of tasks that releases jobs with a minimum inter-arrival time. After this time passes, a new job can arrive at any instant. These tasks are called *sporadic tasks*. In this work, we are concerned with the more common periodic and sporadic task sets.

In real-time scheduling, we are interested in the worst case behavior of systems. Therefore, we characterize a task by deriving the worst case parameters across all job instances. A task  $\tau_i$  in the simplest case can be fully characterized by the tuple  $\langle C_i, D_i, T_i \rangle$  where

•  $C_i$ : the Worst Case Execution Time (WCET) of the task given by  $C_i = \max_j(C_i^j)$ . The WCET of the task is usually derived using static code analysis tools or measured by simulation.

- $T_i$ : the minimum inter-arrival time of the task  $T_i = \min_j (a_i^{j+1} a_i^j)$ .

- $D_i$ : the task's relative deadline. This is typically dependent on the application requirements.

The deadline of the task could be smaller, equal to, or greater than its period. To simplify the discussion we will restrict our scheduling discussion to implicit deadline systems (D = T) and constrained deadline systems  $(D \le T)$ . The ratio  $C_i/T_i$  is referred to as the task utilization  $u_i$ .

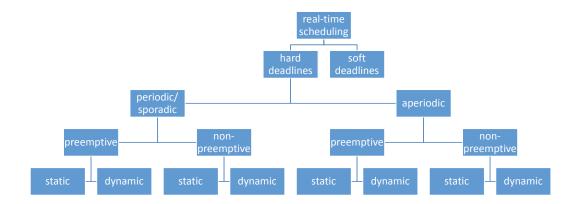

## 2.2 Scheduling

Scheduling is one of the key issues in real-time systems design. The scheduling problem consists of determining which tasks execute on the processors at each time instant. The scheduling problem in the general sense is known to be NP-complete [24]. The different properties of real-time designs and the different assumptions used by systems' developers led to the development of a large number of scheduling algorithms. There are different criteria to classify scheduling algorithms. Figure 2.2 [25] shows one possible classification.

As mentioned in Section 2.1, we are interested here in periodic and sporadic hard real-time systems that are common in many applications and domains today such as control, automotives, and avionics. A preemptive scheduling algorithm can suspend a running job to allow a high priority job to run. We will focus here on preemptive algorithms since they allow higher efficiency [3]. A static scheduling algorithm makes scheduling decisions at deign time, for example the scheduler is given a table of task start and and end times which

Fig. 2.2: Classification of scheduling algorithms

the scheduler enforces. Dynamic scheduling algorithms make their decisions at runtime. Static scheduling is efficient, however, it lacks the flexibility to deal with possible runtime scenarios. Furthermore, generating the schedule tables might be difficult for large systems with non-harmonic parameters, and these tables if found could be long and have high memory requirements. We will focus here on dynamic scheduling.

Dynamic scheduling of real-time systems is typically based on priorities assigned to tasks. The priority of the task can remain constant during the system's operation (fixed priority scheduling) or the priority of the task can change dynamically at runtime (dynamic priority scheduling). Each type of scheduling has its own advantages and disadvantages. Fixed priority scheduling algorithms such as the Rate Monotonic (RM) scheduling algorithm are simpler to implement and more predictable. Dynamic priority scheduling algorithms such as Earliest Deadline First (EDF) can potentially schedule more systems, however, they are hard to implement and in many instances are not supported by standards. [3] provides a more detailed comparison.

## 2.2.1 Scheduling in multicore architectures

When multicore architectures are the implementation target, another dimension to the scheduling problem is the selection of the processor on which a given job is executed. There are two general approaches:

- Global Scheduling: jobs are allowed to migrate freely between processors.

A job can start execution on one processor and end its execution on another processor

- Partitioned Scheduling: Tasks are allocated to a certain processor. All

jobs of the task must start and finish execution on this processor and no

migration is allowed

Global scheduling has the potential to achieve better utilization for the overall systems. Partitioned scheduling can be implemented more easily and predictably, also it has the practical advantage that once a task allocation is found, a wealth of real-time scheduling techniques and analyses for uniprocessor systems can be used [10].

Therefore, in this thesis we focus on partitioned fixed-priority scheduling where tasks are statically assigned to cores and each core is scheduled by a local fixed-priority scheduler. This is widely used in embedded multicore real-time systems today. Such scheduling policies are supported by the AUTOSAR standard for automotive systems [26], as well as most commercial RTOSes, including VxWorks, QNX, LynxOS, and all POSIX-compliant ones.

For fixed-priority partitioned systems, we denote the priority of a task  $\tau_i$  by  $\pi_i$  and the processor to which  $\tau_i$  is assigned by  $P_i$ . Lower priority values

2.2 Scheduling 23

indicate a higher priority task i.e. if  $\pi_i < \pi_j$  then  $\tau_i$  has a higher priority. Designers of these systems must determine an appropriate allocation of tasks to processing cores as well as assign priorities on each core. At runtime, the highest priority task at each time instance executes on the processor. Designers need to ensure that all tasks finish their execution before their deadlines. This is done using schedulability analysis (discussed in Section 2.2.3).

#### 2.2.2 Task allocation: related work

Allocation problems are very common in multicore systems, and in most cases they are proven to be special instances of the general bin-packing problem [27]. For real-time systems without considering shared resources, several heuristics are proposed, e.g., [13, 28, 29]. Baruah and Bini presented an exact ILP (Integer Linear Programming) based approach [30]. Chattopadhyay and Baruah showed how to leverage lookup tables to enable fast, yet arbitrarily accurate partitioning [31]. Baruah presented a polynomial-time approximation scheme [32]. Other results for partitioned scheduling of independent sporadic tasks can be found in a recent survey [10]. The work in Chapter 3 of this thesis differs from these works by considering the impact of shared resources when performing task allocation.

#### 2.2.3 Schedulability analysis

Schedulability analysis is used to check that all tasks in the system meet their deadline requirements. For fixed priority systems, one of the most common methods to check whether a system is schedulable is response time analysis [3, 33]. For the model presented in this chapter, the worst case response time of a task  $\tau_i$ , denoted by  $R_i$  occurs when the task is released simultaneously with all higher priority tasks and is given by:

$$R_i = C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i}{T_j} \right\rceil \cdot C_j \tag{2.1}$$

where hp(i) is the set of tasks that have higher priority than  $\tau_i$ . Note that  $R_i$  appears on both sides on the equation. The response time is the smallest value that satisfies Equation (2.1). This value can be found iteratively as illustrated by the following equation:

$$R_i^{n+1} = C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i^n}{T_j} \right\rceil \cdot C_j \tag{2.2}$$

The iterations start by setting a suitable initial value for  $R_i^n$  (e.g.  $C_i$  since  $R_i \geq C_i$ ). The right hand sides is then evaluated and the result is assigned to  $R_i^{n+1}$ . In the second iteration, this result is used on the right hand side as  $R_i^n$  and a new  $R_i^{n+1}$  is calculated. The process continues until no increase in  $R_i^{n+1}$  occurs for two consecutive iterations (i.e.  $R_i^{n+1} = R_i^n$ ). This result represents the response time. The iterations also stop if  $R_i^{n+1}$  grows larger than the deadline  $D_i$  as this indicates that the task is not schedulable.

Once the response times for all tasks are calculated, a system is schedulable if and only if:

$$\forall \tau_i \in \Gamma : R_i < D_i \tag{2.3}$$

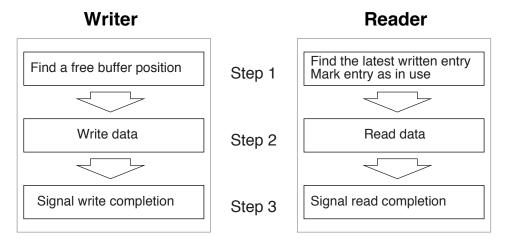

## 2.3 Resource Sharing

A resource is a software structure used by a task to advance its execution such as a variable, a data structure, or a set of registers on a peripheral device [3]. When a resource is shared between tasks, it might be possible that more than one task attempts to access the resource concurrently. This can be dangerous as these accesses might leave the shared resource in an inconsistent state. Protection mechanisms must be introduced to ensure that the resource remains in a consistent state. This is typically done through synchronization locks. Before getting access to the resource, a task must first attempt to lock the shared resource. If the locking operation is successful, the task is granted access to the resource. Once done, the task releases the lock. If the locking operation is not successful, the task must wait for the resource to be released and is said to be blocked on the resource. In a multicore architecture, the resource can be local (accessed by tasks allocated to the same processor) or global (accessed by tasks allocated to different processors).

The period of time a task  $\tau_i$  spends accessing a shared resource is typically referred to as a *critical section*. The execution of task  $\tau_i$  is composed of a set of alternating critical sections and sections in which  $\tau_i$  executes without using a (global or local) shared resource, defined as *normal execution segments*. The WCET is defined by a tuple  $\{C_{i,1}, C'_{i,1}, C_{i,2}, C'_{i,2}, ..., C'_{i,s(i)-1}, C_{i,s(i)}\}$ , where s(i) is the number of normal execution segments, and s(i) - 1 is the number of critical sections.  $C_{i,j}$  ( $C'_{i,j}$ ) is the WCET of the j-th normal execution segment

(critical section) of  $\tau_i$ . The WCET  $C_i$  of  $\tau_i$  is then

$$C_i = \sum_{1 \le j \le s(i)} C_{i,j} + \sum_{1 \le j < s(i) - 1} C'_{i,j}$$

(2.4)

The time a given task  $\tau_i$  spends waiting for a shared resource to become free is commonly referred to as blocking time,  $B_i$ . If  $\tau_i$  accesses more than one resource, then  $B_i$  is simply the sum of the blocking times encountered across all resources. To ensure resource accesses proceed with bounded blocking times and without deadlocks, resource access protocols have been proposed. These protocols manage access to the shared resources and determine task priorities during their critical sections. On multicore architectures, two prominent protocols have been used extensively in academia and industry: suspensionbased Multiprocessor Priority Ceiling Protocol (MPCP) [16], and spin-based Multiprocessor Stack Resource Policy (MSRP) [17].

MPCP and MSRP have been compared in a number of research works (with respect to their worst-case timing guarantees), with a general consensus that MSRP performs best for short (global) critical sections and MPCP for long ones [34]. We will describe these two protocols next.

## 2.3.1 Multiprocessor priority ceiling protocol

MPCP [16] is a multiprocessor extension of the Priority Ceiling Protocol (PCP) [35]. In MPCP, tasks use assigned priorities for normal executions, and inherit the ceiling priority of the resource whenever they execute a critical section. The ceiling priority of a local resource is the highest priority of any task that can possibly use it. For a global resource, its remote priority ceiling is required to be higher than any task priority in the system. For this purpose,

a base priority offset higher than the priority of any task is applied to all global resources. Jobs are suspended when they try to access a locked global resource and added to a priority queue. The suspension of a higher priority task blocked on a global critical section allows other (possibly lower priority) tasks to execute and may even try to execute local or global critical sections. We briefly review the schedulability analysis of MPCP [14, 36].

The normal section of a task can be blocked by the critical section of lower priority tasks on the same core. For each of the s(i) normal sections, the worst case local blocking time  $B_i^l$  that  $\tau_i$  may suffer is the longest critical section among all the lower priority local tasks:

$$B_i^l = s(i) \times \sum_{k: \pi_k > \pi_i \& P_k = P_i} \max_{1 \le m < s(k)} C'_{k,m}. \tag{2.5}$$

$\tau_i$  can only be interfered with by critical sections with a higher remote priority ceiling once it enters its critical section. Also, since the critical section has higher priority than the normal section, in a critical section  $\tau_i$  will only suffer one such interference from each task on the same core. Thus, the response time of the j-th critical section is bounded by:

$$W'_{i,j} = C'_{i,j} + \sum_{k \neq i: P_k = P_i} \max_{1 \le m < s(k) \& \Pi_{k,m} < \Pi_{i,j}} C'_{k,m}.$$

(2.6)

where  $\Pi_{i,j}$  is the priority ceiling of the critical section  $C'_{i,j}$ . The remote blocking time  $B^r_{i,j}$  suffered in the j-th critical section is:

$$B_{i,j}^{r} = \max_{\pi_{k} > \pi_{i} \& \mathcal{S}_{k,m} = \mathcal{S}_{i,j}} W_{k,m}'$$

$$+ \sum_{\pi_{h} < \pi_{i} \& \mathcal{S}_{h,n} = \mathcal{S}_{i,j}} \left( \left\lceil \frac{B_{i,j}^{r}}{T_{h}} \right\rceil + 1 \right) W_{h,n}',$$

$$(2.7)$$

where  $S_{i,j}$  denotes the resource accessed by the critical section  $C'_{i,j}$  and  $S_{k,m} = S_{i,j}$  indicates that the critical sections  $C'_{i,j}$  and  $C'_{k,m}$  access the same resource.

The initial value for the iterative procedure can be set as the first term on the right hand side. The total remote blocking time is then:

$$B_i^r = \sum_{1 \le j < s(i)} B_{i,j}^r. \tag{2.8}$$

In [14], the worst case response time  $R_i$  of  $\tau_i$  is then calculated by the following iterative formula:

$$R_{i} = C_{i} + B_{i}^{l} + B_{i}^{r} + \sum_{\pi_{h} < \pi_{i} \& P_{h} = P_{i}} \left\lceil \frac{R_{i} + B_{h}^{r}}{T_{h}} \right\rceil C_{h}.$$

(2.9)

Recently, Chen et al. [36] showed that Eq. (2.9) is optimistic, and proposed a fix by replacing  $B_h^r$  with  $R_h - C_h$  when  $R_h \leq T_h$ . The response time calculation becomes:

$$R_{i} = C_{i} + B_{i}^{l} + B_{i}^{r} + \sum_{\pi_{h} < \pi_{i} \& P_{h} = P_{i}} \left\lceil \frac{R_{i} + R_{h} - C_{h}}{T_{h}} \right\rceil C_{h}.$$

(2.10)

## 2.3.2 Multiprocessor stack resource policy

MSRP (Multiprocessor Stack Resource Policy) [17] is a multiprocessor extension of the Stack Resource Policy (SRP) [37]. The local shared resources are managed in the same way as MPCP. The global resources are assigned with a ceiling that is higher than that of any local resource. A task that fails to lock a global resource *spins* on the resource lock until it is freed, keeping the processor busy. (In the MPCP protocol, for comparison, the task is *suspended* and yields the CPU.) To minimize the spin lock time (wasted CPU time), tasks cannot be preempted when executing a global critical section, so as to free the resource as soon as possible. MSRP uses a FIFO queue (as opposed to a priority-based queue in MPCP) to manage the tasks waiting on a lock for

a given busy resource. MSRP maintains the same basic property of SRP: once a task starts execution it cannot be blocked.