# Design and Implementation of a 1.8 Volt Wide Band CMOS Fractional-N Frequency Synthesizer for the Complete 5 to 6 Giga-Hertz Band

Alexandre Marsolais

Department of Electrical and Computer Engineering

McGill University

Montréal, Canada

November 2003

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements of the degree of Master of Engineering

©Alexandre Marsolais

Library and Archives Canada

Branch

Published Heritage

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-98553-9 Our file Notre référence ISBN: 0-612-98553-9

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **CONTENTS** .....2 **ABSTRACT** .....4 SOMMAIRE ACKNOWLEDGMENTS.....6 LIST OF FIGURES.....8 CHAPTER 1 CHAPTER 2 SYNTHESIZER THEORY......27 CHAPTER 3 SYNTHESIZER DESIGN ......47 TESTING, MEASUREMENTS AND RESULTS......88 **CHAPTER 4** CHAPTER 5

## **Abstract**

The demand for wireless devices is increasing, new standards are constantly evolving and the operating frequencies are spreading towards higher spectrums. The stress on lowering the voltage supply, the power consumption, the cost and increasing level of integration are the driving forces behind today's RF microelectronics research.

The goal of this thesis is to show the possibility of standard CMOS technology replacing the traditional technologies in RFIC applications, specifically in the design and implementation of frequency synthesizers for 5GHz WLAN applications. The frequency synthesizer is a key building block of WLAN transceivers. To generate multiple frequencies with the resolution required by 5GHz WLAN standards, a fractional-N frequency synthesizer architecture was successfully implemented in 1.8V 0.18µm CMOS technology. To be able to cover the lower and upper 5GHz bands of both HiperLan and 802.11a standards, a wide tuning range quadrature voltage controlled oscillator (VCO), providing a 4-phase output and operating from 5GHz to 6GHz, was used in the phase lock loop (PLL) design. The 5GHz WLAN standards are targeted since they are the most promising, they have few interferers and large data throughputs.

This thesis presents one of the few frequency synthesizers having a large bandwidth of operation and a small resolution reported to-date for this type of application. Also, the digital components used in this frequency synthesizer, namely the fractional-N divider and prescaler have the lowest power consumption reported to-date.

## **Sommaire**

La demande pour de nouveaux appareils de télécommunication sans fil ne cesse d'augmenter. De nouveaux standards évoluent très rapidement et cela toujours à des bandes de fréquences de plus en plus hautes. La recherche est poussée à ses limites par l'incessante demande pour des appareils disposants de sources de tension, consommation en puissance et de coûts toujours plus bas, tout en augmentant le niveau d'intégration RF de l'appareil.

Le but ultime de cette thèse est de démontrer la possibilité de la technologie standard CMOS à remplacer les technologies traditionnelles pour les applications RFIC, tout spécialement pour la conception et la fabrication de synthétiseurs de fréquence pour les applications WLAN à 5GHz. Le synthétiseur de fréquence est un des blocks clé dans la conception d'émetteur- récepteur radio. Pour obtenir la résolution requise par les standards WLAN 5GHz, une architecture de synthétiseur N-fractionnel fut implémentée avec succès en utilisant la technologie CMOS 0.18µm à 1.8V. Il utilise un oscillateur en quadrature, contrôlé par voltage (VCO), pouvant générer des fréquences couvrant les deux bandes de fréquences, basse et haute, des standards HiperLan et 802.11a. Il fut utilisé avec une boucle en verrouillage de phase pour couvrir la bande de fréquence allant de 5GHz à 6GHz. Les standards WLAN 5GHz sont la cible de cette recherche, car ils sont les plus prometteurs, ils ont des capacités de transfert de données très élevées et ne font face qu'à très peu d'interférence.

Cette thèse présente un synthétiseur de fréquence ayant une des plus large bande de fréquence opérationnelle et une des résolutions en fréquence les plus petite rapportée jusqu'à ce jour pour ce type d'application. De plus, les composantes numériques de la boucle en verrouillages de phase, soit le diviseur N-fractionnel et le pré-diviseur consomment la plus base puissance rapporté jusqu'à ce jour.

## **Acknowledgments**

First of all, I would like to thank the Canadian Microelectronics Corporation (CMC), the Natural Sciences and Engineering Council of Canada (NSERC) and the Regroupement Stratégique en Microéléctronique du Québec (ReSMiQ) for funding this research project. Without their support this research would not have been possible. Second of all, I would like to thank my supervisor, Professor Mourad El-Gamal, for providing such an exciting and challenging learning environment. His help and guidance during my research is very much appreciated.

Special thanks to Francis Beaudoin, Koon Hung Lee, Rola Abdul Baki and Tommy Tsang for sharing their knowledge and design experience so generously. Their input in terms of circuit design, chip packaging, and testing contributed greatly to the success of this work. I would also like to thank George El-Bacha, David Hong and Frédéric Nabki for their help in the design and layout of subcircuits and side projects. With their help I was able to save greatly needed time. I would like to extend my appreciation to all my colleagues in the RFIC Group and the MACS Lab for their patience, friendship, and hospitality.

I would like to take this opportunity to thank my family, my father Jacques, my mother Pauline, my brother Rock, my sister Josée and her husband Dany, and

also my in laws; Gilles, Lise, Ginette, Genevieve, Eric, Pierrette, Julien and Simon for their support. For being there when I needed inspiration, motivation and friendship. They supported me through the good and the hard times. I would like to give special thanks to the members of the NLF Society; Charif, Francis, Jay, Joe, and J-G, for their patience and support.

Last but not least, I would like to thank my beloved wife, Jacinthe, for her love, patience and understanding. I would like to thank her for the motivation and inspiration s he brought. I would like to thank her for her support and her every single thoughts and wishes which came from the bottom of her heart.

## **LIST OF FIGURES**

| FIGURE 1.1 DIRECT DOWN CONVERSION RECEIVER ARCHITECTURE                             | 13         |

|-------------------------------------------------------------------------------------|------------|

| FIGURE 1.2 CONVENTIONAL DIRECT DIGITAL SYNTHESIZER ARCHITECTURE [7]                 |            |

| FIGURE 1.3 CONVENTIONAL DELAY LOCKED LOOP ARCHITECTURE [9]                          |            |

| FIGURE 1.4 A) CONVENTIONAL PLL, B) CHARGE PUMP BASED PLL [10]                       |            |

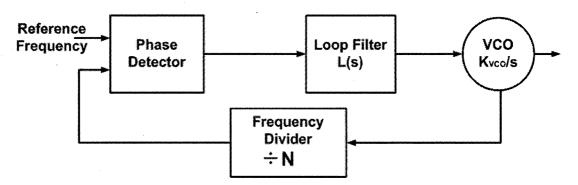

| FIGURE 2.1 STANDARD PLL ARCHITECTURE.                                               |            |

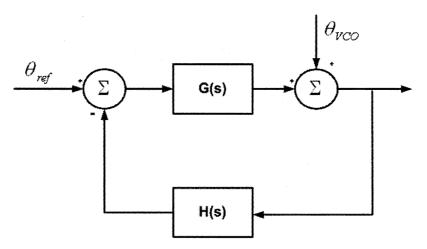

| FIGURE 2.2 SYNTHESIZER AS A FEEDBACK SYSTEM.                                        |            |

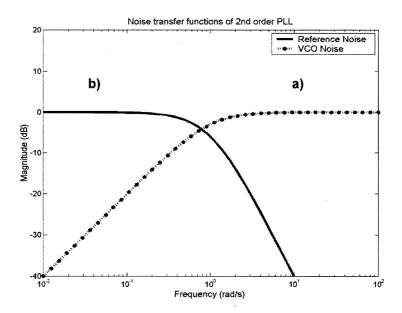

| FIGURE 2.3 NOISE TRANSFER FUNCTIONS: A) VCO NOISE, B) REFERENCE NOISE               |            |

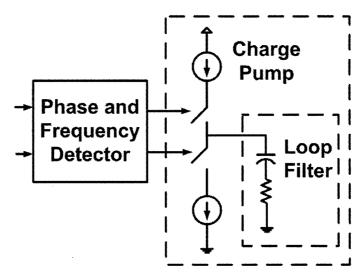

| FIGURE 2.4 PFD AND CHARGE PUMP                                                      |            |

| FIGURE 2.5 NOISE SHAPING EXAMPLE FOR AN OPTIMIZED SECOND-ORDER SYNTHESIZER          |            |

| FIGURE 2.6 INTEGRATOR PHASE NOISE OPTIMIZATION                                      |            |

| FIGURE 2.7 EXAMPLE OF SPURS IN A SYNTHESIZER OUTPUT POWER SPECTRUM                  |            |

| FIGURE 2.8 HIPERLAN/2 AND 802.11A SPECTRUM REGULATIONS                              |            |

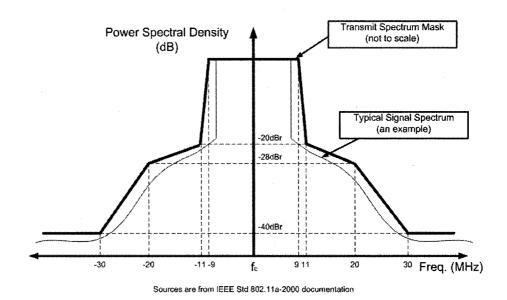

| FIGURE 2.9 TRANSMIT POWER SPECTRAL MASK                                             |            |

| FIGURE 2.10 SPECTRUM MANAGEMENT METHOD TO REDUCE CCI                                |            |

|                                                                                     |            |

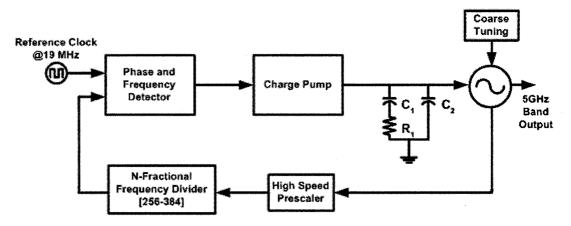

| FIGURE 3.1 SYNTHESIZER ARCHITECTURE                                                 |            |

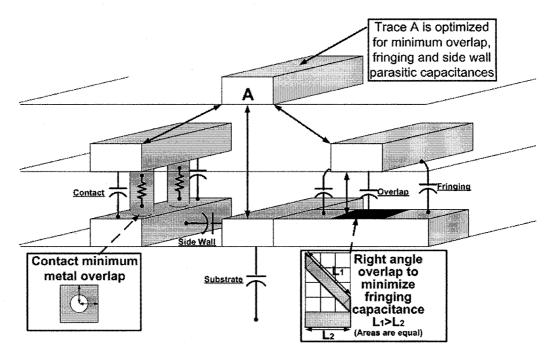

| FIGURE 3.2 DESCRIPTION OF LAYOUT ISSUES                                             |            |

| FIGURE 3.3 TRANSISTOR LAYOUT ISSUES                                                 |            |

| FIGURE 3.4 DCVSL NAND LOGIC GATE                                                    | 56         |

| FIGURE 3.5 A) DIVIDE-BY-TWO CIRCUIT BUILDING BLOCK, B) D-FLIP FLOP TRANSISTOR LEVEL |            |

| CIRCUIT                                                                             |            |

| FIGURE 3.6 HIGH-SPEED PRESCALER DESIGN RESPECTING RULES 1 TO 6.                     |            |

| FIGURE 3.7 DUAL MODULUS DIVIDER                                                     |            |

| FIGURE 3.8 DUAL MODULUS DIVIDER OUTPUT                                              |            |

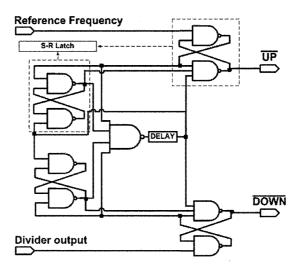

| FIGURE 3.9 CONVENTIONAL PFD BLOCK IMPLEMENTATION                                    |            |

| FIGURE 3.10 PFD CHARACTERISTIC RESPONSE                                             |            |

| FIGURE 3.11 PFD GATE LEVEL IMPLEMENTATION                                           |            |

| FIGURE 3.12 PFD RESPONSE TO PHASE ERRORS AND CAPTURE RANGE                          |            |

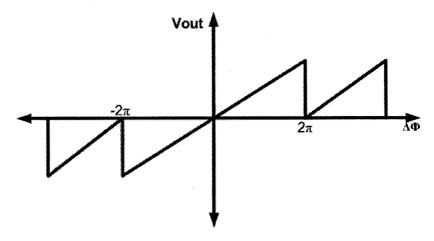

| FIGURE 3.13 A) DEAD ZONE IN PFD AND B) ITS EFFECT ON SYNTHESIZER OUTPUT             |            |

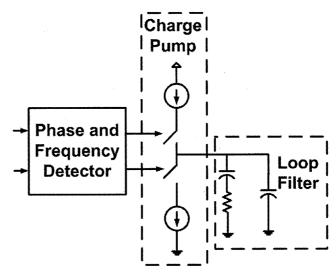

| FIGURE 3.14 PFD/CP/LPF CIRCUITS                                                     |            |

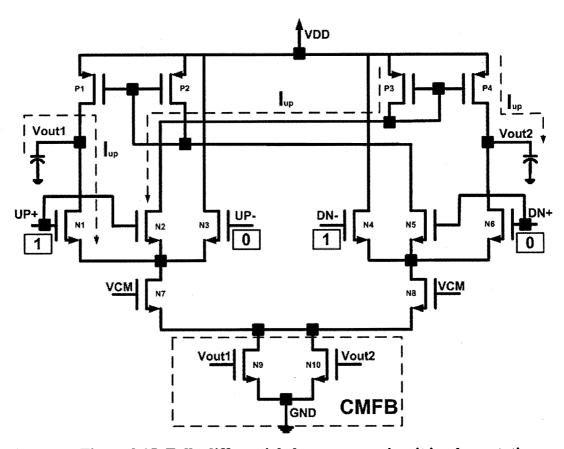

| FIGURE 3.15 FULLY DIFFERENTIAL CHARGE PUMP CIRCUIT IMPLEMENTATION                   |            |

| FIGURE 3.16 SIMULATED MINIMUM LINEAR OUTPUT OF PFD AND CP                           |            |

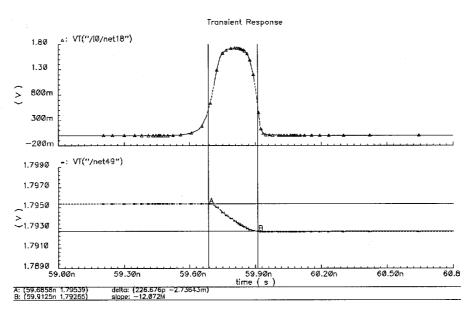

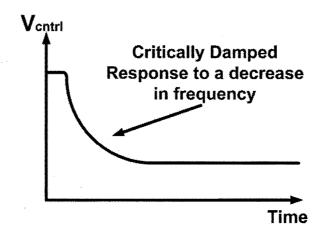

| FIGURE 3.17 SIMULATED OSCILLATOR CONTROL VOLTAGE LOCKING TRANSIENT FOR A FIRST-ORD  |            |

| FILTER                                                                              | 70         |

| FIGURE 3.18 SIMULATED OSCILLATOR CONTROL VOLTAGE LOCKING TRANSIENT FOR A SECOND     |            |

| ORDER FILTER                                                                        |            |

| FIGURE 3.19 FFT OF A SIMULATED LOCKING TRANSIENT                                    | 73         |

| FIGURE 3.20 THEORETICAL DAMPED TRANSIENT RESPONSE                                   |            |

| FIGURE 3.21 TYPICAL LC TUNED OSCILLATOR                                             |            |

| FIGURE 3.22 A) INDUCTOR DESIGN USING CADENCE LAYOUT TOOLS, B) FABRICATED INDUCTORS  | IN         |

| CMOS 0.18µм                                                                         |            |

| FIGURE 3.23 TYPICAL RESONANT TANK COMPONENTS FOR THE CIRCUIT IN FIGURE 3.21         | 77         |

| FIGURE 3.24 DIFFERENTIAL VARACTOR CONTROL                                           |            |

| FIGURE 3.25 A) PMOS INVERSION MODE VARACTOR, B) PMOS CAPACITANCE REGIONS VERSUS V   | /BG        |

| TUNING [45]                                                                         |            |

| FIGURE 3.26 QUADRATURE VCO CIRCUIT AND ITS FOUR OUTPUT PHASES                       |            |

| FIGURE 4.27 CHIP MICROGRAPH OF THE SYNTHESIZER                                      |            |

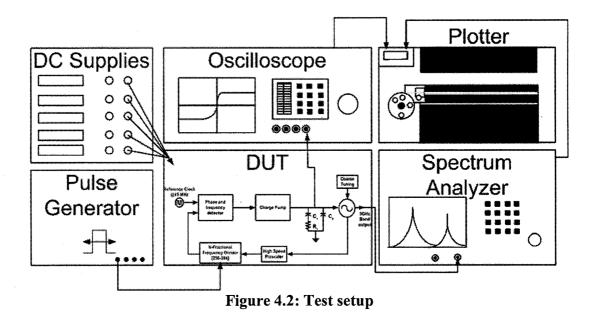

| FIGURE 4.28: TEST SETUP                                                             | <b>9</b> 0 |

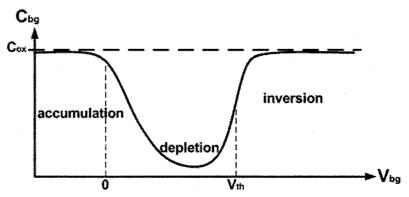

| FIGURE 4.29 THEORETICAL PMOS VARACTOR BEHAVIOUR [45]                                |            |

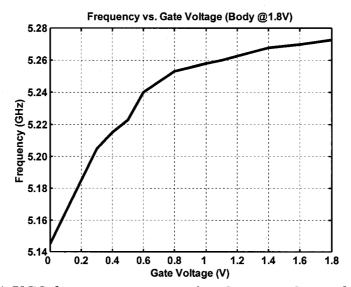

| FIGURE 4.30 VCO FREQUENCY VERSUS TUNING THE GATE VOLTAGE OF THE VARACTOR            |            |

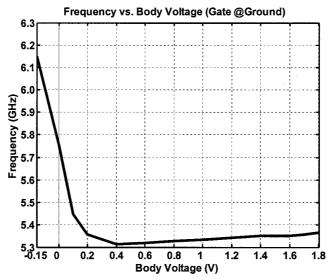

| FIGURE 4.31 VCO FREQUENCY VERSUS TUNING THE BODY VOLTAGE OF THE VARACTOR            | 94         |

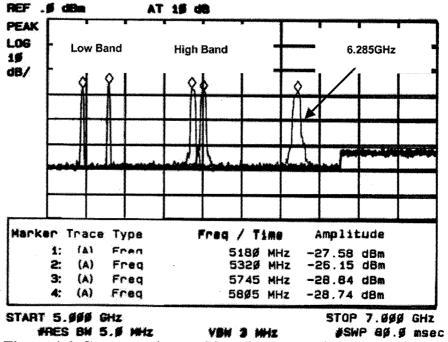

| FIGURE 4.32 COARSE TUNING ENABLES WIDE SYNTHESIZER CAPTURE RANGE                    | 96         |

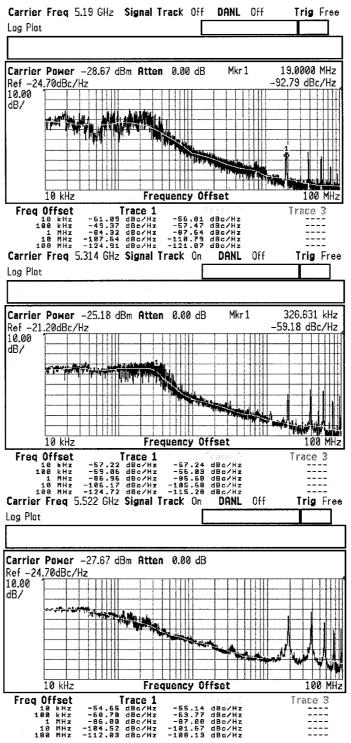

| FIGURE 4.33 PHASE NOISE @5.19GHz, @5.314GHz, AND @5.522GHz                          | 97  |

|-------------------------------------------------------------------------------------|-----|

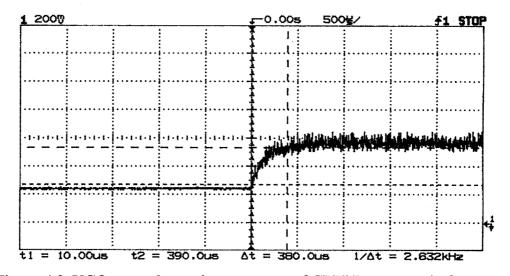

| FIGURE 4.34 VCO CONTROL TRANSIENT RESPONSE OF CPPLL TO A STEP IN FREQUENCY          | 99  |

| FIGURE 4.35 SPURIOUS TONES OF FRACTIONAL-N SYNTHESIS                                | 102 |

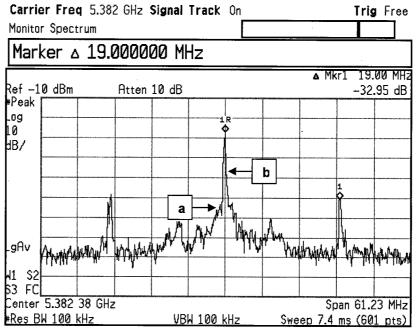

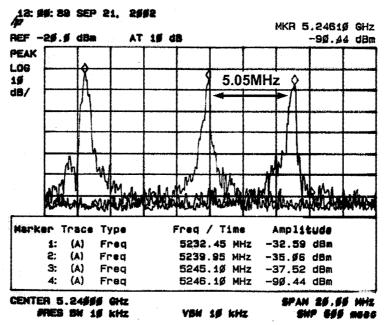

| FIGURE 4.36 CPPLL FREQUENCY RESOLUTION @ 5.24 GHz of 5.05 MHz, AND PHASE NOISE OF - |     |

| 92 DBC/Hz @ 1 MHz OFFSET                                                            | 103 |

## **LIST OF TABLES**

| TABLE 1.1 | EXAMPLE OF HIGH PERFORMANCE FREQUENCY SYNTHESIZERS | 19  |

|-----------|----------------------------------------------------|-----|

| TABLE 1.2 | STATE-OF-THE-ART CMOS SYNTHESIZERS                 | 20  |

| TABLE 2.1 | NOISE IN INTEGRATED CIRCUITS                       | 28  |

|           | SUMMARY OF THE LOOP BEHAVIOR                       |     |

| TABLE 4.2 | COMPARISON TO OTHER PUBLISHED SYNTHESIZER          | 104 |

| TABLE 4.3 | COMPARISON TO OTHER PUBLISHED CMOS DIVIDERS        | 105 |

| TABLE 5.1 | SUMMARY OF MEASURED SYNTHESIZER PERFORMANCE        | 111 |

| СНАРТ | ER 1 INTRODUCTION                     | 12 |

|-------|---------------------------------------|----|

| 1.1   | MOTIVATION                            | 14 |

| 1.2   | STATE-OF-THE-ART SYNTHESIZERS DESIGNS | 15 |

| 1.3   | RESEARCH CONTRIBUTIONS                | 20 |

| 1.4   | THESIS ORGANIZATION                   | 22 |

| 1.5   | REFERENCES                            | 24 |

## **Chapter 1** Introduction

In wireless telecommunications, the radio spectrum is allocated by different organizations that govern the use of the spectrum in the areas they have control over. The International Telecommunication Union (ITU) has the responsibility of maintaining and extending the cooperation between its members in regulating the radio spectrum and the standardization of telecommunication as a whole [1]. The main players in this organization, or at least its most influential members, are the US Federal Communication Commission (FCC) [2], and the European Conference of Postal and Telecommunications Administrations (CEPT) [3]. These organizations regulate the use of the frequency spectrum, and divide the spectrum into frequency bands that are allocated to different applications and standards [4].

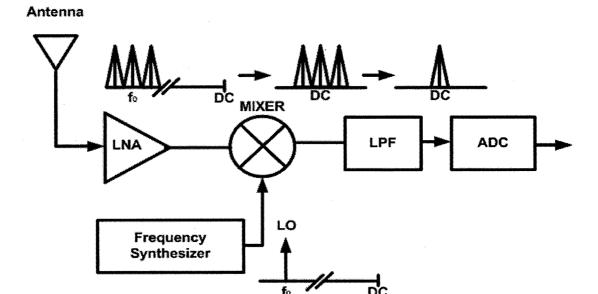

In wireless telecommunication systems, the allocated frequency spectrum is subdivided into multiple channels in order to maximize efficiency [5]. The data is transmitted over the channels, and then processed at baseband. Figure 1.1 shows how data is down converted in a receiver using a mixer. Generating the proper local oscillator (LO) signals is a key element in down converting the data from a specific channel to baseband. The LO signals are generated through the use of frequency synthesizers. They consist of a voltage controlled oscillator (VCO) in a feedback loop. This type of loop is better known as a phase locked loop (PLL), where the error signal is the phase difference between a reference signal and the VCO. A

synthesizer must be able to generate multiple frequencies with the resolution needed to meet the required number of channels in a system.

The mobile phone and wireless local area network (WLAN) vendors have recently seen an increasing demand for smaller hardware. These new smaller devices must support multiple features such as basic voice over multiple frequency bands, multiple high-speed wireless data transfer standards, GPS location technology, and multi-media applications. To keep the devices small, while at the same time increasing the number of features available, the hardware size of individual components must be reduced.

Figure 1.1.1 Direct down conversion receiver architecture

The first step toward making the devices smaller was to reduce the battery size. This effectively reduced the possible available power. The second step was to

reduce the space occupied by the hardware. The continuous development of integrated circuit (IC) technologies and new circuit techniques is enabling low power and small area designs. One of the most popular IC technologies is the standard planar CMOS. Its continuous dimension down scaling is enabling low voltage supplies, high frequency operation, an unprecedented high level of integration, low power consumption, and low cost. To further reduce the space occupied by the hardware, the transceiver architecture trend is toward the use of direct conversion schemes to bring signals from the radio frequency (RF) bands (i.e. in the GHz range) to baseband. By using direct conversion, instead of the more traditional super heterodyne architecture, intermediate frequency (IF) filter circuits, such as expensive off chip image reject and channel select filters, can be removed, and a single frequency synthesizer operating at the RF frequency is required. Direct conversion offers a solution that is both highly integrated and which potentially consumes lower power. The direct conversion architecture is the de-facto standard for many mobile phone and RFIC vendors such as Alcatel, Nokia, Ericsson, Samsung, Siemens, Infineon, Conexant, Analog Devices, Phillips, Qualcomm, and TI to name a few [6].

## 1.1 Motivation

The IC industry is constantly trying to reduce costs, while at the same time improving the chip's performances. The technology of choice to achieve these two requirements is CMOS. Mainstream CMOS technology is normally optimized for digital applications. The continuous transistor dimension downscaling of CMOS technologies has led to an increase in the maximum operating frequencies. Research has demonstrated the potential of CMOS as a real contender for RF

designs [9], [14]-[17], [20]-[23]. Standard CMOS now competes with traditional RF technologies, such as GaAs, InP, HEMT, HBT, and BJT. The use of CMOS for both a nalog and digital circuitry will bring devices to an unprecedented level of integration, enabling the implementation of single-chip RF transceivers. An RF frequency synthesizer is a critical building block in direct conversion communications systems. It is the only single circuit that is capable of generating multiple LO signals to directly down/up convert the data signals between the multiple RF channels and baseband, while introducing as little noise and interference as possible. The spectral purity of the synthesized frequency will affect the overall performance of the system, for instance, the number of available channels. Also, a lower phase noise will introduce less noise in the system thus improving receiver sensitivity and reducing the bit error rate (BER), which in turn will improve the maximum possible throughput of the system.

## 1.2 State-of-the-Art Synthesizers Designs

In this section, examples of synthesizers, both from research laboratories and from industry, will be presented. The most recent work on CMOS synthesizers reported in the literature is summarized and compared. The applications considered are limited to the 2.4GHz and 5GHz frequency ranges. The standardization of these frequency bands has been the most sought after, for current and future WLAN commercial products.

The three most popular frequency synthesis techniques are the direct digital synthesis (DDS), delay locked loop (DLL), and the PLL. The PLL is also subdivided into two types, the conventional PLL and the charge pump based PLL.

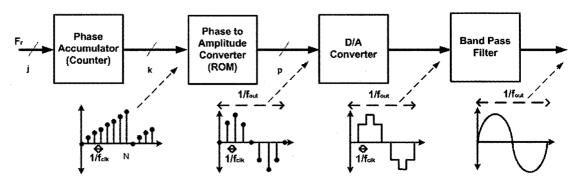

Figure 1.1.2 Conventional direct digital synthesizer architecture [7]

Figure 1.1.2 displays the conventional direct digital synthesizer architecture. This architecture is based on a rather simple four-step technique. First, a counter is set to count up to N, where N is an integer. Then a ROM look up table converts the counter value [0, N] into a voltage level. The resulting voltage level goes through a digital-to-analog (D/A) converter, the output of which is then filtered into a pure sinewave signal. The main draw back of this synchronous architecture is that the system clock must be highly stable, but since stable clocks are only available at rather low frequencies, the system will be limited. In [8], a 9.2GHz clock rate was taken from a high speed clock generator, and due to the Nyquist rate limitation, the highest frequency that could be generated was less than half the clock rate. Also, note that in order to achieve very low phase noise, the output filter needs to be of very high quality and highly selective. This filter is required to operate at high frequency as well, adding to the already large complexity of the transistor level implementation.

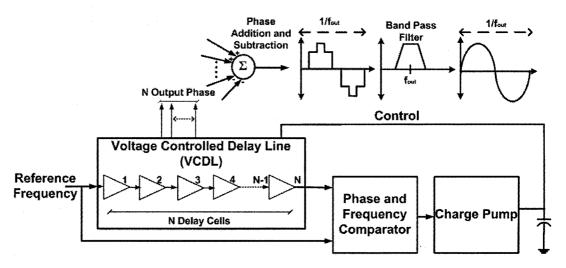

Figure 1.1.3 Conventional Delay Locked Loop Architecture [9]

Figure 1.1.3 shows the conventional delay locked loop architecture. A voltage controlled delay line is placed in a phase locked loop. The phase and frequency are compared with the reference frequency and are kept in lock by the feedback loop. The different phases generated are processed by a phase selector, an add/subtract circuit, and a bandpass filter that generates the output signal. The limitation of this circuit for high frequency synthesis is its need for a stable and high frequency reference. The possible output frequency and operating range are also limited by the minimum/maximum achievable delay through each delay element. The complexity of the digital circuitry (i.e., N delay cells, phase and frequency detector, phase selector, add/subtract circuit and bandpass filter) is also one of its main drawbacks.

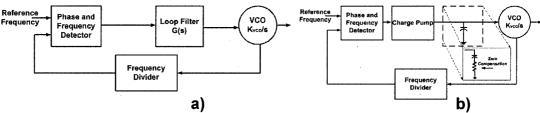

Figure 1.1.4 a) Conventional PLL, b) charge pump based PLL [10]

Figure 1.1.4 presents the two main types of PLLs, the conventional and the charge pump based. They are also known as frequency multipliers. This architecture enables high frequency synthesis using a relatively lower reference frequency. Compared to the DDS technique, which is only able to synthesize fractions of the reference clock, this architecture multiplies the reference frequency by the value of the divider. This can be either an integer or a fraction. There is one main difference between the two types of PLL. The transfer function of the charge pump based PLL includes an extra pole introduced by the charge pump. In order to stabilize the charge pump PLL, the capacitive load of the charge pump must be modified as shown in Figure 4 b. The main advantage of a charge pump PLL is its wide capture range, which is only limited by the VCO output frequency range, rather than being limited by the loop bandwidth as is the case for a conventional PLL. We will see in Chapter 2 that the charge pump PLL also adds a third degree of freedom in the loop behavior design by including the charge pump current into the design equations.

High performance frequency synthesizers are often implemented in technologies other than CMOS, such as the compound III-V processes. The main reason for this is their superior 1/f noise, and high frequency of operation compared with CMOS. The 1/f noise is the dominant factor in VCOs close in phase noise.

|                       | DDS[8]                     | PLL[11]                    | PLL[12]                      | PLL[13]                       |

|-----------------------|----------------------------|----------------------------|------------------------------|-------------------------------|

| Technology            | InP<br>(DHBT)              | Si B6HF<br>(BJT)           | SiGe BiCMOS<br>(HBT/CMOS)    | GaAs<br>(MESFET)              |

| Frequency             | 36MHz-4.62GHz              | 6.4-6.75GHz                | 4.85-5.325GHz                | 2.3-2.55GHz                   |

| Phase Noise<br>dBc/Hz | -140@2.5GHz<br>offset@1kHz | -103@6.7GHz<br>offset@1MHz | -101@5.075GHz<br>offset@1MHz | -102@2.488GHz<br>offset@10kHz |

| Supply                | ~5V                        | <b>3V</b>                  | 3.3V                         | <b>5V</b>                     |

| Settling<br>Time      | -                          | 170µs                      | 10 μs                        | 150ns                         |

| Power                 | 15W                        | 82mW                       | 255mW                        | 300mW                         |

| Area (mm²)            | 8x5                        | 0.776x0.776                | 2                            | 2                             |

Table 1.1 Example of high performance frequency synthesizers

Table 1.1 is a summary of some existing high frequency synthesizers [8], [11]-[13]. Note that all the frequency synthesizers operate in the 2.4GHz and 5GHz WLAN frequency bands, which enables a fair comparison between the different implementations. The main drawbacks of these synthesizers are their high voltage supplies and power consumption, which makes them unsuitable for small, lightweight portable devices. Also, these are rather expensive processes, which make them unsuitable for low-cost commercial devices. These technologies are more suitable for high-end, high performance applications, such as satellites.

|                       | [14]                        | [15]                        | [16]                        | [17]                        |

|-----------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Technology            | 0.4μm CMOS                  | 0.25μm CMOS                 | 0.24μm CMOS                 | 0.25μm CMOS                 |

| Frequency             | 2.6/5.2GHz                  | 5.25-5.54                   | 4.840-4.994GHz              | 5.14-5.70GHz                |

| Phase Noise<br>dBc/Hz | -100@5.2GHz<br>offset@10MHz | -88@5.46GHz<br>offset@40kHz | -101@4.96GHz<br>offset@1MHz | -122@5.18GHz<br>offset@1MHz |

| Supply                | <b>2.6V</b>                 | 1.5V                        | 2.0V                        | 2.5V                        |

| Settling<br>Time      | 40μs                        | · <u>-</u>                  | 7.3 μs                      | 100 μs                      |

| Power                 | 47mW                        | 23mW                        | 35mW                        | 13.5mW                      |

| Area (mm²)            | 1.75x1.15                   | -                           | 1.6                         | -                           |

Table 1.2 State-of-the-art CMOS synthesizers

Table 1.2 presents state-of-the-art CMOS frequency synthesizers operating in the 5GHz WLAN band. The three circuits require low supply voltages (1.5-2.6V). As a result, their power consumption is very low (13.5-47mW). The CMOS technology down-scaling enables these low supply, low power circuits. When compared with the entries in Table 1.1, it is clear that the phase noise is much higher, thus making CMOS much less attractive for high-end applications.

## 1.3 Research Contributions

This thesis discusses research concentrated on the design of frequency synthesizers. The purpose of this research is to take advantage of the state-of-the-art 0.18µm CMOS technology in the implementation of RF wireless frequency synthesizers operating in multiple channel 5GHz WLAN applications. Even though CMOS could not match the ultra high-speed operation of the well established RF

technologies mentioned earlier, it is to date the most cost-effective technology. Wireless transceiver circuits (including frequency synthesizers) implemented in a CMOS technology can be integrated with microprocessor and memory on the same chip. In an effort to optimize the performance of wireless frequency synthesizer circuits, different circuit topologies and layout techniques were used. To meet the low power requirements of battery operated devices, minimum size transistors were used whenever possible. This permitted the synthesizer digital circuitry to be driven by very small currents. This required the use of high density low parasitic layout techniques.

The following is a summary of the contributions of this thesis:

a) It describes a design methodology and layout techniques to minimize the parasitic capacitances and power consumption in digital circuitry. These methods and techniques have many useful properties: 1) High density layout and floor-planning reduces chip area and loading caused by long interconnects. 2) Low parasitic layout techniques will increase the maximum operating frequency and enable the use of smaller transistors. 3) A smaller transistor width reduces power consumption by decreasing the current through the devices. 4) Current reduction means smaller fluctuations on the supply lines, reducing unwanted digital noise, as well as the MOSFET generated noise in the case of thermal and shot noise.

- b) It includes a design methodology to meet the required specifications for a frequency synthesizer and the fundamentals needed to fully understand the subject at hand. Mathematical modeling of well known PLL structures is also discussed.

- c) It presents a successful chip implementation one of the *first* reported 0.18µm CMOS differential frequency synthesizer capable of generating frequencies over the complete 5-6GHz unlicensed frequency spectrum and with the best resolution reported in this frequency band. Lower phase noise measurements are obtained compared with results presented for example by Lam et al [22].

- d) It describes a very low power, high frequency prescaler and fractional-N divider combination for high frequency resolution performance in frequency synthesis. The lowest reported power consumption for this type of circuit in the literature, 4.5mW. Also, it reports a very low power consumption for a PFD and CP combination, 2.7mW.

## 1.4 Thesis Organization

This thesis consists of five chapters. The first chapter discusses the motivation for frequency synthesizer's research in CMOS technology. It gives an introduction to spectrum regulation mechanisms and to the pressing need for high

resolution frequency synthesizers in wireless communications. A discussion of the research contributions is included. Chapter 2 covers CMOS frequency synthesizer fundamentals, such as the basic theory of the noise sources present in RF integrated circuits (RFICs). The mathematical modeling of a PLL and its different noise sources and noise transfer functions are discussed. Design equations and constraints necessary to meet specific requirements are presented, along with a brief introduction to the HiperLan/2 and 802.11a standards.

Chapter 3 presents the design of each building block of the frequency synthesizer. Design issues to be considered, in order to meet the requirements of both the HiperLAN/2 and 802.11a standards are discussed. Layout considerations to minimize noise, power consumption, and area are presented for each block. A specific discussion is included on improving the VCO resonating tank quality factor by proper varactors' and inductors' design.

Chapter 4 presents a successful implementation of a dual standard frequency synthesizer for direct conversion transceivers. Measured results demonstrate very low power, a wide range of operation, a high frequency resolution, and a phase noise that compares very well with what has been reported in the literature to date. Testing and measurement procedures are described.

Chapter 5 summarizes the results of this work, presents possibilities for future improvement, and suggests combinations with other circuitry to create a complete direct conversion transceiver.

## 1.5 References

- [1] "The International Telecommunication Union (ITU) web page", URL: <a href="http://www.itu.int/home/">http://www.itu.int/home/</a>

- [2] "The US Federal Communication Commission (FCC) web page", URL: <a href="http://www.fcc.gov/">http://www.fcc.gov/>

- [3] "The European Conference of Postal and Telecommunications Administrations (CEPT) web page", URL: <a href="http://www.cept.org/">http://www.cept.org/</a>

- [4] "The US Federal Communication Commission Strategic Plan 2003-2008", URL: <a href="http://www.fcc.gov/omd/strategicplan/strategicplan2003-2008.pdf">http://www.fcc.gov/omd/strategicplan/strategicplan2003-2008.pdf</a>

- [5] A. Leon-Garcia and I. Widjaja, "Communication Networks, fundamental concepts and key architectures", McGraw-Hill, Chap.4, pp 192-251, 2000.

- [6] F. Ali, "Direct conversion receiver design for mobile phone system-challenges, status and trends", *IEEE Radio Frequency Integrated Circuits Symposium*, pp. 21-22, May 2002.

- [7] J. Vankka, M. Waltari, M. Kosunen, K.A.I. Halonen, "A direct digital synthesizer with an on-chip D/A-converter", *IEEE Journal of Solid-State Circuits*, Vol. 33, No. 2, pp. 218-227, February 1998.

- [8] A. Gutierrez-Aitken, J. Matsui, E.N. Kaneshiro, B. Oyama, D. Sawdai, A. Oki D. Streit, "Ultrahigh-speed direct digital synthesizer using InP DHBT technology", *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 9, pp. 1115-1119, September 2002.

- [9] A. Spataro, Y. Deval, J.-B. Bégueret, P. Fouillat, D. Belot, "A VLSI CMOS delay oriented waveform converter for polyphase frequency synthesizer", *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 3, pp. 336-341, March 2002.

- [10] B. Razavi, Monolothic phase-locked loops and clock recovery circuits, theory and design, IEEE Press, pp. 1-41, 1996.

- [11] G. Ritzberger, H. Knap, J. Bock, M. Rest, L. Treitinger, A. Scholtz, "6.7GHz frequency synthesizer in 0.8µm silicon bipolar production technology", *IEEE Microwave Theory and Technique Digest*, pp. 701-704, 2001.

- [12] H. Ainspan and M. Soyuer, "A fully-integrated 5-GHz frequency synthesizer in SiGe BiCMOS", *IEEE Bipolar/BiCMOS Circuits and Technology Meeting*, pp.165-168, 1999.

- [13] W. Baumberger and M. Schmatz, "A GaAs single chip 2.4GHz PLL frequency synthesizer multiplier", *IEEE Microwave and Millimiter-Wave Monolithic Circuits Symposium*, pp. 39-42, 1996.

- [14] C. Lam and B. Razavi, "A 2.6-GHz/5.2-GHz frequency synthesizer in 0.4µm CMOS technology," *IEEE Journal of Solid-State Circuits*, Vol. 35, No. 5, pp. 788-794, May 2000.

- [15] C.M. Hung and K. K.O, "A fully integrated 1.5-V 5.5-GHz CMOS phase-locked loop," *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 4, pp. 521–525, April 2002.

- [16] H. R. Rategh, H. Samavati, and T. H. Lee, "A 5GHz, 32mW CMOS frequency synthesizer with an injection locked frequency divider," *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, pp. 113-116, 1999.

- [17] S. Pellerano, C. Samori, S. Levantino, A.L. Lacaita, "13.5 mW, 5GHz WLAN, CMOS frequency synthesizer using a true single phase clock divider", *IEEE Symposium on VLSI Circuits Digest of Technical papers*, pp. 145-148, 2003

- [18] K.H. Lee, M.N. El-Gamal, "A Very low-voltage (0.8V) CMOS receiver frontend for 5 GHz RF applications", *IEEE International Symposium on Circuits and Systems*, Vol. 1, pp. 125-128, May 2002.

- [19] D. A. Neamen, Semiconductor Physic: Basic Principles, second edition, McGraw-Hill, 1997.

- [20] J. Craninckx, M. Steyaert, "A fully integrated CMOS DCS-1800 Frequency Synthesizer," *IEEE Journal of Solid-State Circuits*, Vol. 33, No. 12, pp. 2054-2065, December 1998.

- [21] R. Ahola, K. Stadius, K. Halonen, "Design Of a Fully Integrated 2 GHz CMOS Frequency Synthesizer", *IEEE International Symposium on Circuits and Systems*, Vol. 2, pp. 160-163, 1999.

- [22] C. Lam, B. Razavi, "A 2.6-GHz/5.2-GHz Frequency Synthesizer in 0.4-um CMOS Technology," *IEEE Journal of Solid-State Circuits*, Vol. 35, No. 5, pp. 788-794, May 2000.

- [23] B. De Muer, M. Steyaert, "A CMOS Monolithic ΔΣ-controlled Fractional-N Frequency Synthesizer for DCS-1800", *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 7, pp. 835-844, July 2002.

| CHAPTER 2 SYNTHESIZER THEORY                                        | 27 |

|---------------------------------------------------------------------|----|

| 2.1 NOISE                                                           | 28 |

| 2.1.1 Noise in Integrated Circuits                                  |    |

| 2.1.2 Phase Noise in Voltage Controlled Oscillators                 |    |

| 2.1.2.1 Definition of Phase Noise                                   |    |

| 2.1.2.1 Definition of Phase Noise  2.1.2.2 VCO Phase Noise Modeling |    |

| 2.2 SYNTHESIZERS FUNDAMENTALS                                       | 30 |

| 2.2.1 Synthesizer Second Order Noise Analysis                       | 31 |

| 2.2.2 Noise Transfer Functions Example                              | 33 |

| 2.2.3 Charge Pump Synthesizer Noise Analysis                        |    |

| 2.2.4 Loop Behavior                                                 |    |

| 2.2.4.1 Noise Shaping in Phase Locked Loop Systems                  |    |

| 2.2.4.2 Settling Time in Second-Order Systems                       |    |

| 2.3 STATIC VERSUS FRACTIONAL-N TOPOLOGIES                           | 40 |

| 2.3.1 Fractional Spurs                                              | 41 |

| 2.4 IEEE STANDARD 802.11A & HIPERLAN/2                              | 42 |

| 2.4.1 Spectrum                                                      | 42 |

| 2.4.2 Transmit Power Spectral Mask                                  |    |

| 2.5 REFERENCES                                                      |    |

## **Chapter 2** Synthesizer Theory

As introduced in Chapter 1, the frequency synthesizer is the circuit that enables the implementation of multiple channel communication systems. Its purpose is to synthesize frequencies over a specified frequency spectrum with the required resolution. The synthesized tones are used to drive the down/up converting mixers that allow bringing the information signal to the desired frequency b and. Synthesizers enable a multi-channel communication system to maximize its data throughput by using the allocated spectrum to its maximum.

The noise introduced by a synthesizer will impede the performance of the communication system, hence increasing the bit error rate of the system. This will decrease the sensitivity of a receiver. Noise is not the only unwanted effect that a synthesizer may introduce. In a fractional-N synthesizer implementation, undesired spurs are also introduced in the output. These spurs may appear in the vicinity of the actual desired channel or in a djacent ones. They may cause interference and might down/up convert unwanted interferers with the data signal. It is important that in a transmitting system these spurs be minimized and placed at a large offset away from the center frequency. One must keep in mind that the output power spectrum of any transmitting system is regulated by standards. The reduction in the power of these spurs is necessary to achieve high data rates and to respect the guidelines given by the regulating authority.

In this chapter, different sources of noise are presented. This is followed by an in-depth noise analysis of frequency synthesizers, fundamental synthesizer theory and different PLL topologies. Finally, a brief introduction to the IEEE standards 802.11a and HIPERLAN is given in order to increase the awareness to application specific designs of synthesizers for multiple band compliant devices.

#### 2.1 NOISE

#### 2.1.1 Noise in Integrated Circuits

|                   | Thermal Noise<br>(Johnson Noise)           | 1/f Noise<br>(Flicker Noise)             | Shot Noise                          |

|-------------------|--------------------------------------------|------------------------------------------|-------------------------------------|

| RMS Noise Current | $\overline{i_n^2} = \frac{4kT\Delta f}{R}$ | $\overline{i_n^2} = K \frac{I^a}{f^b} f$ | $\overline{i_n^2} = 2qI_D \Delta f$ |

**Table 2.1 Noise in Integrated Circuits**

Table 2.1 presents the different types of noise occurring in integrated circuits. The theory of each type of noise is well covered in reference [24]. Thermal noise is associated with the thermal excitation of charge carriers in conductors (i.e., R the resistors), where k is the Boltzmann constant, T is the absolute temperature, and  $\Delta f$  is the noise bandwidth. The 1/f noise is known for its spectral density decay following a 1/f roll-off near DC, where a, b and K are empirical constants, I is the biasing current, and f is the operating frequency. Finally, shot noise is related to the DC current flow in semiconductor devices, where f is one electronic charge, f is the biasing current, and f is the noise bandwidth.

#### 2.1.2 Phase Noise in Voltage Controlled Oscillators

#### 2.1.2.1 Definition of Phase Noise

Phase noise is characterized by its frequency domain spectrum. The manner in which the power spectrum decreases as it moves away from the center frequency  $f_0$  characterizes the phase noise performance of the oscillator. The sharper the power spectrum, the closer the oscillator is to an ideal Dirac impulse. Poor phase noise directly degrades a system's overall performance and reduces its throughput.

$$\mathcal{L}\{\Delta\omega\} = 10\log\left(\frac{\text{noise power in a 1Hz bandwidth at }\omega_0 + \Delta\omega}{\text{center frequency power}}\right) \qquad \text{Eq. 2.1}$$

Eq. 2.1 is used to quantify the phase noise performance of a voltage controlled oscillator (VCO). Phase noise is quantified by comparing the power residing in the sidebands to the power of the center frequency. A unit bandwidth at an offset of the center frequency is used in the comparison. The power in this unit bandwidth is calculated, giving an amount of power per Hertz, and then divided by the center frequency power. This ratio is then converted into dBc/Hz.

#### 2.1.2.2 VCO Phase Noise Modeling

A major figure of merit of VCO design is phase noise. A model known as "Leesson's equation" can be used to approximate the output phase noise at a frequency offset  $\Delta\omega$  from  $\omega_o$ , the VCO center frequency [25]-[27].

$$\mathcal{L}\left\{\Delta\omega\right\} = k \cdot T \cdot Z_0 \cdot \frac{1}{Q_{\tan k}} \cdot \left[1 + A\right] \cdot \left(\frac{\omega_0}{\Delta\omega}\right)^2 \cdot \frac{1}{V_{rms}^2}$$

Eq. 2.2

Eq. 2.2 is Leesson's equation, where k is the Boltzmann constant, T is the absolute temperature, A is the excess noise factor (a safety margin to ensure oscillation start-up),  $Z_0$  is the VCO's tank characteristic impedance, and  $Q_{tank}$  is the overall quality factor of the tank.  $V_{rms}$  is the VCO output root-mean square voltage. This approximation will fairly describe the free running VCO phase noise when neglecting other noise sources such as the close in 1/f noise.

## 2.2 Synthesizers Fundamentals

A synthesizer consists of a local oscillator in a phase locked loop (PLL). The loop controls the frequency and the phase of the oscillator in order to stabilize it at a specific frequency. Frequency acquisition, settling time, noise, and spectral purity are all performance metrics that will be discussed in this section. In the following section, noise analysis will be performed for a basic 2<sup>nd</sup> order synthesizer system, including the case of a charge pump PLL. Sections on loop design, 2<sup>nd</sup> order settling time and fractional synthesis will also be presented.

#### 2.2.1 Synthesizer Second Order Noise Analysis

Figure 2.1 Standard PLL architecture

Figure 2.1 illustrates a typical phase-locked loop system consisting of a phase detector, loop filter, voltage controlled oscillator, and a frequency divider. It is easy to translate this system into a feedback system representation.

Figure 2.2 Synthesizer as a feedback system

Noise modeling in a synthesizer is analogous to modeling noise in a feedback system. Figure 2.2 displays the input noise sources as  $\theta_{ref}$  and  $\theta_{VCO}$ . These

sources are the major noise entry ports. Other noise inputs come from the substrate and the power supplies. From Figure 2.2, the open loop transfer function can be derived as follows:

$$G(s) \cdot H(s) = \frac{K_F \cdot L(s)}{N \cdot s}$$

Eq. 2.3

where

$$G(s) = \frac{K_F \cdot L(s)}{s}$$

,  $H(s) = \frac{1}{N}$ , and  $K_F \approx K_{VCO}$  Eq. 2.4

Eq. 2.3 is the open-loop transfer function, and Eq. 2.4 is used modeling the synthesizer. The 1/s term comes from the VCO transfer function. N is the frequency divider ratio.  $K_F$  is the forward gain, in this case the combined gains of the VCO, the phase detector, and the low pass filter. The VCO gain is the dominant term. L(s) is the low-pass filter transfer function with a pole at  $\omega_{LP}$ . The following two noise transfer functions represent the two most important sources of noise in a PLL:

$$\frac{\theta_{out}(s)}{\theta_{VCO}(s)} = \frac{1}{1 + GH(s)} = \frac{N \cdot s}{N \cdot s + K_F \cdot L(s)} = \frac{s(\omega_{LP} + s)}{s^2 + \omega_{LP} s + \frac{\omega_{LP} K_F}{N}}$$

Eq. 2.5

$$\frac{\theta_{out}(s)}{\theta_{ref}(s)} = \frac{G(s)}{1 + GH(s)} = \frac{N \cdot K_F \cdot L(s)}{N \cdot s + K_F \cdot L(s)} = \frac{\omega_{LP} K_F}{s^2 + \omega_{LP} s + \frac{\omega_{LP} K_F}{N}}$$

Eq. 2.6

Eq. 2.5 is the noise transfer function due to the presence of VCO phase noise. Eq. 2.6 is the noise transfer function due to an introduced reference phase noise. Note that both transfer functions are affected by the factor N, and that their noise magnitude increases with N. Eq. 2.7 and Eq. 2.8 represent the natural

frequency of the synthesizer and damping factor respectively. They both depend on the values of N,  $\omega_{LP}$ , and  $K_{VCO}$ .

$$\omega_n = \sqrt{\frac{\omega_{LP} K_{VCO}}{N}}$$

Eq. 2.7

$$\zeta = \frac{1}{2} \sqrt{\frac{N \cdot \omega_{LP}}{K_{VCO}}}$$

Eq. 2.8

## 2.2.2 Noise Transfer Functions Example

Figure 2.3 Noise transfer functions: a) VCO Noise, b) Reference Noise

Figure 2.3 corresponds to the VCO and reference noise transfer functions obtained with equations similar to Eq. 2.5 and Eq. 2.6. For simplicity, in both cases the damping factor and N are set equal to 1. The VCO noise transfer function behaves as a high-pass filter and the reference noise transfer function has a low-

pass filter response. Effectively, the high-pass behavior of the VCO noise transfer function will shape the free running VCO phase noise by removing noise in the vicinity of the VCO center frequency. By increasing the loop bandwidth, the VCO noise transfer function will enclose less noise. Since both transfer functions are interdependent more reference noise will be introduced. However, a smaller loop bandwidth comes at the expense of a slower locking transient. In commercial implementations, the use of low noise crystals as reference sources enables the use of large loop bandwidths. These crystals introduce negligible amount of noise.

#### 2.2.3 Charge Pump Synthesizer Noise Analysis

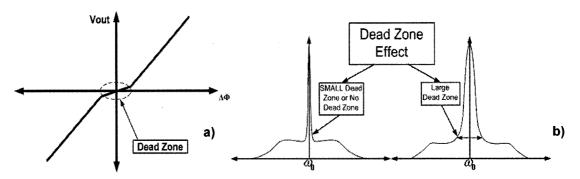

Figure 2.4 PFD and Charge Pump

Figure 2.4 illustrates a PFD and charge pump implementation. Synthesizers implemented with the use of a phase and frequency detector charge pump combination are quite popular in today's state-of-the-art designs. It has two main

advantages: the capture range is only limited to the VCO frequency range, and the static phase error is zero assuming negligible charge pump mismatches and offsets [29]. The modeling of such designs is different than the standard models previously discussed, but they can still be looked at as second-order systems. The open loop transfer function is modified and the loop filter is included in the model of the charge pump gain as shown by Eq. 2.9 and Eq. 2.10 respectively.

$$G(s) \cdot H(s) = \frac{K_F \cdot G(s)}{N \cdot s} \xrightarrow{\text{for PLL with Charge Pump}} \frac{K_{CP}(s)K_{VCO}}{N \cdot s^2}$$

Eq. 2.9

$$K_{CP}(s) = \frac{I_{CP}}{2\pi} \left( R + \frac{1}{C_p \cdot s} \right)$$

Eq. 2.10

Eq. 2.10 describes the transfer function of the charge pump  $K_{CP}(s)$  where  $C_p$  and R represent the added zero needed for stabilizing the PLL. Without the series resistor, the charge pump PLL would be inherently unstable. The charge pump current is represented by  $I_{CP}$ .

$$\frac{\theta_{out}(s)}{\theta_{in}(s)} = \frac{\frac{I_{CP}}{2\pi C_p} (RC_p s + 1) K_{VCO}}{s^2 + \frac{I_{CP}}{2\pi} \frac{K_{VCO}}{N} Rs + \frac{I_{CP}}{2\pi C_p} \frac{K_{VCO}}{N}}$$

Eq. 2.11

$$\omega_n = \sqrt{\frac{I_{CP}}{2\pi C_p} \frac{K_{VCO}}{N}}$$

Eq. 2.12

$$\zeta = \frac{R}{2} \sqrt{\frac{I_{CP}C_p}{2\pi} \frac{K_{VCO}}{N}}$$

Eq. 2.13

The overall synthesizer transfer function is described by Eq. 2.11. The addition of the charge pump current term in the transfer function adds more control to the loop behavior, which is desirable. Eq. 2.12 and Eq. 2.13 are the charge pump synthesizer's natural frequency and damping factor equations respectively. Note that they both depend on the value of  $I_{CP}$ .

#### 2.2.4 Loop Behavior

The loop design is set mostly by the loop filter, VCO gain and charge pump current. Each application has its own specifications. This section will deal with noise shaping in PLL's, integrator phase noise optimization and second-order PLL settling time.

#### 2.2.4.1 Noise Shaping in Phase Locked Loop Systems

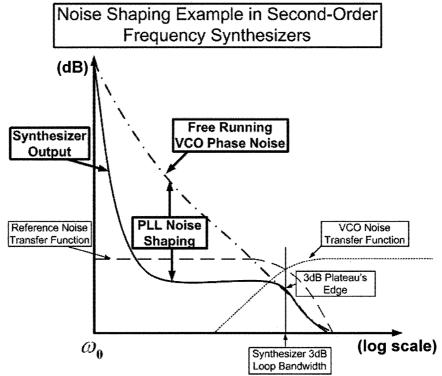

Figure 2.5 Noise shaping example for an optimized second-order synthesizer

Figure 2.5 illustrates how PLL noise shaping occurs. First, consider each of the curves of this figure. These are the free running VCO phase noise, the reference noise transfer function, the VCO noise transfer function, and the synthesizer output. The free running VCO phase noise is an almost straight line. The reference noise transfer function has a lowpass behavior and is characterized by its natural frequency. In this case, having a damping factor of one, the 3 dB loop bandwidth coincides with the natural frequency. Due to the very high quality of reference sources, the noise they introduce is negligible. In the case of the VCO transfer function its behavior is highpass. This particular behavior is the main mechanism of PLL noise shaping. Low frequency phase variations (i.e. phase noise) are removed

by the highpass filtering behavior. Figure 2.5 illustrates the change from a free running VCO to a synthesizer output. The VCO close-in phase noise is removed by the PLL noise shaping. The noise contribution of the PLL is called integrator noise and creates a plateau as shown. This plateau is due to the noise generated by the PLL and will be as wide as the designer sees fit. The 3 dB width of the plateau is controlled by the loop design and VCO noise transfer function.

Figure 2.6 Integrator phase noise optimization

Figure 2.6 illustrates the three possible design outcomes for synthesizer output. Case 1 displays an under-designed loop bandwidth. This has the effect of not removing all of the VCO close-in phase noise. A characteristic side lobe is present in the synthesizer output where noise removal starts to fail. Case 2 has an over-designed loop bandwidth. In this case, the integrator noise plateau, introduced by the PLL, extends beyond the point of equal noise contribution. This point is where both the PLL noise and free running VCO phase noise contribute equally. A larger than necessary loop bandwidth will introduce more undesired noise in the system. The loop bandwidth in the optimized case is made so that the 3 dB

plateau's edge coincides with the point of equal noise contribution. This has the effect of maximizing the noise removal while also generating the fastest settling time possible. The settling time is controlled by the loop bandwidth. The larger the loop bandwidth, the faster the settling time will be.

# 2.2.4.2 Settling Time in Second-Order Systems

The settling time is the time the PLL takes to shift from one frequency to another. It is one of the most important figures of merit in PLL design. The settling time can be calculated for a specific loop design, giving rise to a transient response. The settling time requirement is application specific. To obtain the settling time, a few assumptions and derivations need to be made. The first assumption is that we have a linear time invariant system, which implies a constant settling time regardless of the value of the voltage step. The second necessary assumption is that the desired damping factor is equal to one ( $\zeta$ =1). This assumption actually optimizes the loop for fast response. This optimized response allows the fastest rise time without overshoot and consequently the shortest settling time [30]. The step response in this case is given by the following equation:

$$V_{out} \pm \Delta = \left(1 - e^{-\omega_n t} - \omega_n \cdot t e^{-\omega_n t}\right) \cdot V_{step}$$

Eq. 2.14

This expression models a second-order step response with respect to a change in voltage.  $V_{out}$  is the final VCO control voltage,  $V_{step}$  is the voltage step corresponding to the frequency jump, t is the required settling time,  $\Delta$  is the required accuracy to be considered in lock condition, and  $\omega_n$  is the natural frequency of the synthesizer. The voltage values are obtained from the VCO

frequency vs. control voltage characteristics. What needs to be determined now is the time it would take for the system to reach the final value within a specific accuracy  $\Delta$ . This equation can be solved graphically in order to find  $\omega_n$  corresponding to the desired settling time t and required accuracy  $\Delta$ . Once the natural frequency is obtained, the loop filter can be designed to meet the requirements. One must make sure that the behavior of the system is second order to use the method described above. It can also be used to provide a first approximation for a third-order system when its behavior follows closely that of a second-order model. Such a case is presented in the following chapter.

# 2.3 Static versus Fractional-N Topologies

A static design would have a specific integer divider value for each channel needed by the application. The disadvantage of this is that the minimum frequency resolution is set by the reference frequency. To obtain good resolution, the reference frequency has to be kept small. This will force the use of a large value of dividers (N). As noted earlier, the noise magnitude increases as N increases.

In the case of a fractional-N implementation, a single dual divider circuit is needed. The implementation is capable of generating fractions of the reference frequency such that it can be increased. This effectively reduces the value of N. As previously mentioned, this reduces the noise in the system. The only compromise to this approach is the fractional spurs that appear at the synthesizer's output.

## 2.3.1 Fractional Spurs

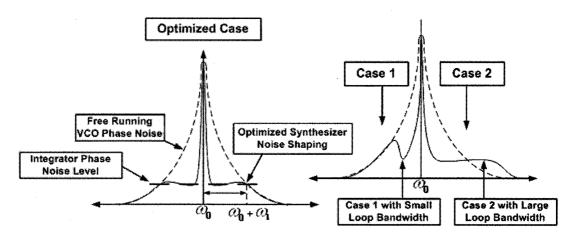

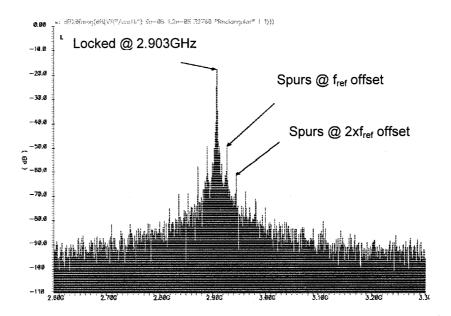

Figure 2.7 Example of spurs in a synthesizer output power spectrum

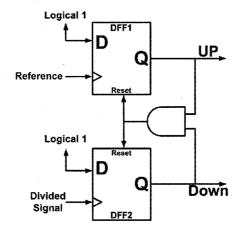

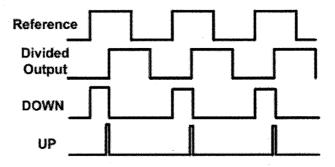

Figure 2.7 is an example of fractional spurs present in the synthesizer output spectrum. These spurs are due to the periodicity of the control signal of the dual modulus divider. They appear in the spectrum at a specific frequency offset away from the main tone of the synthesizer. This frequency offset is M times the reference frequency, where M is an integer.

# 2.4 IEEE Standard 802.11a & HIPERLAN/2

#### 2.4.1 Spectrum

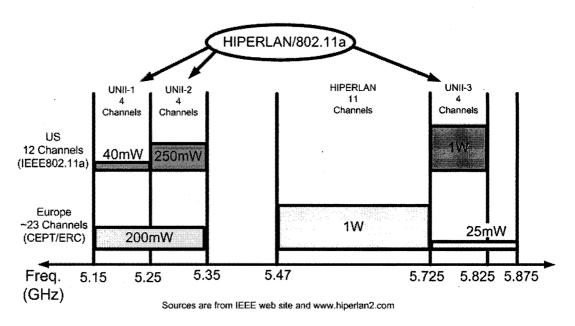

Figure 2.8 HIPERLAN/2 and 802.11a spectrum regulations

Figure 2.8 illustrates two main operating specifications, namely the allowed power levels and the sub-divisions of the 5 GHz frequency band. Note that the number of channels available in Europe is almost twice that in the US. Figure 2.8 also presents an overlap in specific channels where a WLAN system could operate both in Europe and in the US. The information has been gathered from references [31]-[33]. The WLAN is available now in the US from vendors such as Atheros, Intel, Cisco, and Proxim. Note that they only operate in the lower and mid bands from 5.15 to 5.35 GHz. It can be observed that over these particular bands, it can operate in Europe as well.

## 2.4.2 Transmit Power Spectral Mask

Figure 2.9 Transmit power spectral mask

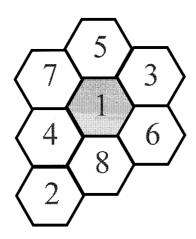

Figure 2.9 illustrates the transmit spectrum mask of the IEEE 802.11a standard [31]. It shows a clear bandwidth of a little less than 20 MHz. The adjacent channels are exactly 20 MHz away on each side. To reduce co-channel interferences (CCI), two adjacent channels should not be used in the same cell. In fact, the company Atheros presents a spectrum management method in reference [34], where a single channel is used per cell.

Figure 2.10 Spectrum management method to reduce CCI

Figure 2.10 illustrates the spectrum management method that minimizes the CCI. This method is used in office environments and is referred to as non-overlapping channels. The throughput can be maximized by reducing the cell radius. This approach reduces the requirements on distortion such as those caused by fractional-N PLL spurs, and power amplifier distortion.

# 2.5 References

- [24] D. A. Johns and K. Martin, Analog integrated circuit design, Wiley, 1997.

- [25] J. Craninckx, M. Steyart, and H. Miyakawa, "A fully integrated spiral-LC CMOS VCO set with prescaler for GSM and DCS-1800systems," *Proc. International Custom Integrated Circuits Conf.*, pp.403-406, 1997.

- [26] P. Kinget, "A fully integrated 2.7V 0.35um CMOS VCO for 5GHz wireless applications," *IEEE International Solid-state Circuits Conference Dig. Tech. Papers*, pp. 226-227, 1998.

- [27] B. Razavi, RF microelectronics, Prentice Hall, 1998.

- [28] J. Craninckx, and M. Steyart, Wireless CMOS Frequency Synthesizer Design, Kluwer Academic, May 1998.

- [29] B. Razavi, B., Monolithic phase-locked loops and clock recovery circuits, IEEE Press, 1996.

- [30] A.V. Oppenheim, A.S. Willsky, and S.H. Nawab, Signals and systems, 2nd ed., Prentice Hall, p. 454, 1997.

- [31] IEEE, IEEE Standard 802.11a-2000.

- [32] P. Karlsson, "H2GF comments on allocation for wireless access systems operating in the frequency range 5150MHz to 5875MHz", <a href="www.hiperlan2.com">www.hiperlan2.com</a>, <a href="www.hiperlan2.com">www.hiperlan2.com</a>, HiperLAN2 Global Forum, June 2nd 2000.

- [33] A. Troy, "Deploying Wireless LANs", www.cisco.com, 2002

- [34] R. Redelfs, "IEEE802.11a Advanced Wireless LANs Realizing Ubiquitous Connectivity", <a href="https://www.atheros.com">www.atheros.com</a>, November 15<sup>th</sup>, 2001.

| CHAPTER 3 SYN                           | THESIZER DESIGN                                                | 47 |

|-----------------------------------------|----------------------------------------------------------------|----|

| 3.1 SYNTHES                             | SIZER BUILDING BLOCKS                                          | 47 |

|                                         | er                                                             |    |

|                                         | terconnections Design Rules.                                   |    |

|                                         | Rule 1- Interconnection Dimensions                             |    |

|                                         | Rule 2- Substrate Parasitic Capacitance                        |    |

|                                         | Rule 3- Overlap and Fringing Parasitic Capacitances            |    |

|                                         | Rule 4- Side-Walls Parasitic Capacitance                       |    |

|                                         | Rule 5- Metal Contacts Parasitic Resistances and Capacitances. |    |

|                                         | Rule 6- Required Current Densities                             |    |

|                                         | ansistor Layout Design Rules                                   |    |

|                                         | ılly Differential Circuit Architectures                        |    |

|                                         | escaler Transistor Level Implementation                        |    |

| 3.1.2 Fraction                          | nal-N Divider                                                  | 59 |

| 3.1.2.1 Du                              | ıal Modulus Divider                                            | 59 |

|                                         | nd Frequency Detector (PFD)                                    |    |

| 3.1.3.1 Lo                              | ogic Gate Implementation Using DCVSL                           | 64 |

| 3.1.4 Charge                            | Pump (CP)                                                      | 65 |

| 3.1.4.1 Cl                              | narge Pump Layout Considerations                               | 69 |

| 3.1.5 Loop Fi                           | ilter                                                          | 69 |

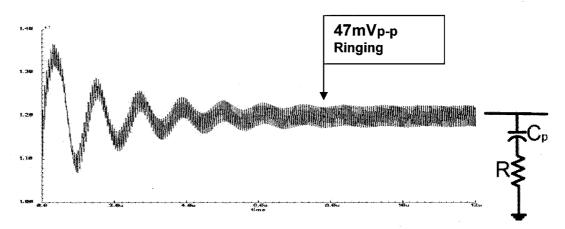

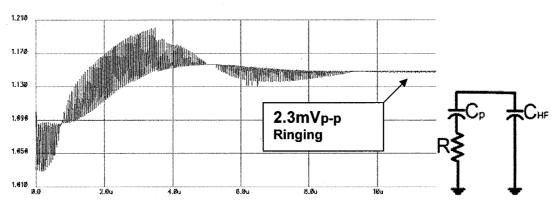

| 3.1.5.1 Lo                              | oop Filter for Low Power Design                                | 71 |

| 3.1.5.2 Lo                              | pop Transient Response Example                                 | 73 |

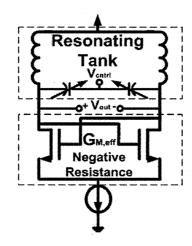

| 3.1.6 The VC                            | O                                                              | 74 |

| 3.1.6.1 LC                              | C-Tuned VCO Design                                             | 75 |

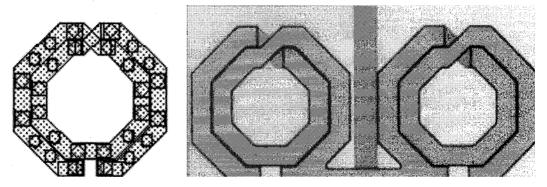

| 3.1.6.2 Inc                             | ductor Design                                                  | 76 |

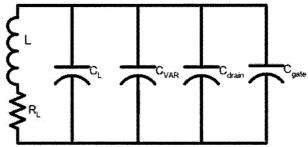

| 3.1.6.3 Th                              | ne LC Tank Resonator                                           | 77 |

| 3.1.6.4 Th                              | ne Cross-Coupled Amplifier                                     | 78 |

| 3.1.6.5 Va                              | aractor Tuning                                                 | 79 |

| 3.1.6.5.1 Inversion Mode PMOS Varactors |                                                                | 80 |

|                                         | CO Coarse Tuning                                               |    |

| 3.1.7 Quadrature VCO's                  |                                                                |    |

| 32 REEEREN                              | ICEC                                                           | 25 |

# **Chapter 3** Synthesizer Design

# 3.1 Synthesizer Building Blocks

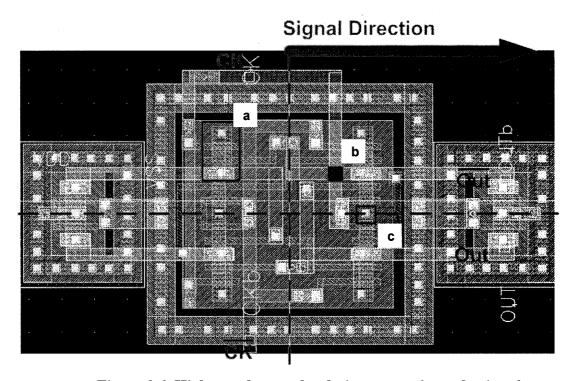

Figure 3.1 Synthesizer architecture

To meet the requirements of multiple band coverage and of the high-frequency resolution needed to enable every channel, a fractional-N PLL architecture is employed. Figure 3.1 shows the synthesizer architecture in detail. It allows the use of a relatively high-frequency reference signal, enabling higher loop bandwidth and faster locking time, while reducing the VCO phase noise. An external control provides coarse tuning of the VCO, while the PLL provides the fine automatic tuning.

The following sections present the building blocks used in the implementation of the frequency synthesizer. The choice of each block structural design will be discussed in detail. Their individual effect on the overall behavior of the system and the specific characteristics involved in their design and layout will also be presented.

#### 3.1.1 Prescaler

The prescaler needs to operate at the highest frequency of the circuit. It will perform frequency division of the VCO signal so that the more complex divider circuit be able to operate at lower frequencies, where its performance is optimal. These devices are not only the bottleneck in the maximum operating frequency, but they also consume a relatively high dynamic power.

$$P_{dyn} = C_{Load} V_{DD}^2 f$$

Eq. 3.1

Eq. 3.1 illustrates the relation of the dynamic power consumption  $P_{dyn}$  to the operating frequency f, supply voltage  $V_{DD}$ , and capacitive load  $C_{Load}$  in digital circuits [35]. This equation was used as a guideline to optimize the prescaler for low-power operation. Since the frequency is set by the application, reducing the supply voltage and the capacitive loading of the circuit are the only two parameters available for setting the dynamic power consumption.

It is well known that the two main limiting factors in high-speed designs are the series resistances of the interconnections and the loading of the parasitic capacitances. These two combine to form dominant parasitic poles in circuits, limiting the maximum operating frequency. To optimize for high-frequency operation, it is very important to follow specific layout guide lines.

Also, it should be noted that parasitic capacitances occur between metal traces carrying different signals, ground/supply lines, and other biasing interconnects. It is know that these capacitances couple noise and signals between any of the aforementioned structures, and as frequency increases their impedances are reduced resulting in even greater signal and noise coupling. Therefore, as the supply voltage is reduced, it becomes very important to minimize coupling between structures to maximize signal integrity.

From the above mentioned issues, a list of specific guidelines were established to optimize the circuit layout for low-power, low-supply voltages, and high-speed operation. In short, a reduction in parasitic capacitances improves all of these issues. This approach will be the main focus of the following layout guidelines.

#### 3.1.1.3 Interconnections Design Rules

Figure 3.2 Description of layout issues

#### 3.1.1.3.1 Rule 1- Interconnection Dimensions

$$\lambda_{Physical\_Dimension} << \lambda_{Operating\_Frequency}$$

Eq. 3.2

The lengths of the interconnects must be kept as short as possible to reduce the non-desirable high-frequency effects, and to keep the modeling of the interconnection as ideal wires. Failure to do so will turn a long trace into an inductor, and it will have more resistance, resulting in an increase in signal loss. Large traces also increase capacitive loading effects. Eq. 3.2 is a rule of thumb in high-frequency design in order to maintain ideal wire behavior of interconnections. By keeping the physical dimensions of the circuitry much smaller than the operating wavelength, the absence of standing waves and wave reflections can be

assumed. There are only very small losses due to the interconnects left, and no high-frequency modeling is necessary.

$$\alpha = \frac{\omega\sqrt{\mu\varepsilon}}{\sqrt{2}} \left[ \sqrt{1 + \left(\frac{\varepsilon''}{\varepsilon'}\right)^2} - 1 \right]^{\frac{1}{2}}$$

Eq. 3.3

$$\beta = \frac{\omega\sqrt{\mu\varepsilon}}{\sqrt{2}} \left[ \sqrt{1 + \left(\frac{\varepsilon''}{\varepsilon'}\right)^2} + 1 \right]^{\frac{1}{2}}$$

Eq. 3.4

$$E_x^+(z,t) = E_m^+ e^{-\alpha z} \cos(\omega t - \beta z)$$

Eq. 3.5

Eq. 3.3 to Eq. 3.5 from reference [38], illustrate the effects of frequency on a forward traveling wave in a conductor, where  $\alpha$  represent the attenuation,  $\omega$  the frequency and  $\beta$  the phase shift. An increase in frequency introduces an increase in loss and phase shift. The phase shift is usually modeled by introducing capacitors and inductors in the transmission line model. It can be observed that by keeping the dimensions small, the term  $\beta z$  has limited effects on the traveling wave. This proves the veracity of the aforementioned rule of thumb.

## 3.1.1.3.2 Rule 2- Substrate Parasitic Capacitance

$$C = \frac{\varepsilon \cdot Area}{d}$$

Eq. 3.6

The width of the traces close to the substrate must be kept as small as possible to prevent generating large substrate capacitances. This will prevent large

capacitances to couple signals to the substrate and slow down the circuit. Figure 3.2 illustrates this layout issue. Eq. 3.6 represents the well known parallel plate capacitance equation, where the plate area Area, multiplied by the effective permittivity of the insulator  $\varepsilon$ , in this case the substrate, is divided by the distance d between the two plates.

#### 3.1.1.3.3 Rule 3- Overlap and Fringing Parasitic Capacitances

Parasitic capacitances between two overlapping traces must be minimized in order not to degrade the circuit operation. The distance between the two overlapping structures must be kept as wide as possible, and the overlap area must be minimized. The fringing capacitances must also be minimized. One key technique is to always run overlapping traces at right angles. Figure 3.2 demonstrates that a right-angle overlapping minimizes fringing capacitance for two different parallel plates having equal areas. It is clear that  $L_I$  is much larger than  $L_2$ ; therefore  $L_I$  is more prone to generating fringing capacitances.

#### 3.1.1.3.4 Rule 4- Side-Walls Parasitic Capacitance

When carrying out the floor planning of the circuit it is important to keep in mind a few key points. Having two wires running too close to each other gives rise to cross-talk. Cross-talk is due to parasitic capacitances of the traces side walls. The side walls act as parallel plate capacitors and couple AC signals. To prevent cross-talk, the distance between side walls must be relatively large. When this is not possible, two different metal layers should be used to increase the effective distance.

# 3.1.1.3.5 Rule 5- Metal Contacts Parasitic Resistances and Capacitances

$$\delta = \frac{1}{\sqrt{\pi f \mu \sigma_{conductor}}}, R_{AC} = R_{DC} \frac{a}{2\delta}, R_{DC} = \frac{1}{\pi a^2 \sigma_{conductor}}$$

Eq. 3.7

When using contacts to connect two metal layers, contacts should be placed as frequently as possible to reduce the added contact resistance and to increase the amount of current the connection can sustain. Individual contacts are limited in their current carrying capacity. A safety factor is often necessary to overcome process variation. In this work a safety factor of at least 15% was used. The number of contacts needs to be optimized to decrease series resistance while not degrading the frequency response by introducing large parasitic capacitances. To minimize the metal overlap parasitic capacitances, the minimum metal-contact overlap area must always be used. This minimum metal-contact overlap area is guided by the DRC rules of each specific process. Figure 3.2 illustrates this issue. Eq. 3.7 from reference [39] describes the skin depth  $\delta$  as a function of frequency f, permeability  $\mu$ , and conductivity  $\sigma_{conductor}$ . Also described, is the AC resistance  $R_{AC}$  of a cylindrical conductor as a function of the skin depth, conductor radius a, and DC resistance  $R_{DC}$ . Note that  $R_{DC}$  is also a function of  $\sigma_{conductor}$  and a. Also note that the expression clearly illustrate that an increase in frequency will increase the resistance. Therefore, as the frequency of operation is increased, the current handling capacity of the contact will be reduced due to skin effects. This is very important for the interconnect design of metal contacts for high frequency of operation. The same issue applies to all shapes of conductors with different modeling equations.

#### 3.1.1.3.6 Rule 6- Required Current Densities

It is required to keep the traces large enough to satisfy their rated current densities capabilities. Failure to do so will increase the resistance seen by the signal, resulting in signal loss and heating of the conductor (and eventually the entire chip). Excessive heating will affect the behavior of the circuitry, possibly rendering it unusable or enduring permanent damage. Traces can be modeled: Their resistive behavior as a function of frequency would be very similar to Eq. 3.7, i.e. their current density handling capacity will decrease with frequency.

Rules 1 to 6 will minimize the loading effect of the interconnections and, as mentioned earlier, this will dramatically reduce the dynamic power consumption. If a low supply voltage is used, the dynamic power consumption will decrease even further. Note that the reduced capacitive loading will improve the operating frequency very rapidly if all rules are satisfied. Also, limiting signal and noise coupling between traces improves the overall noise immunity of the circuit.

#### 3.1.1.4 Transistor Layout Design Rules

To optimize the power consumption and the operating speed of the transistors some design rules must be followed. The optimized minimum width and length of the transistor channel must be used. Using the smallest featured dimensions for the gate length allowed by the process will enable the fastest operating frequency. Optimizing the transistor width will give rise to the maximized current drive for minimum parasitic capacitance, thus enabling the highest frequency of operation possible.

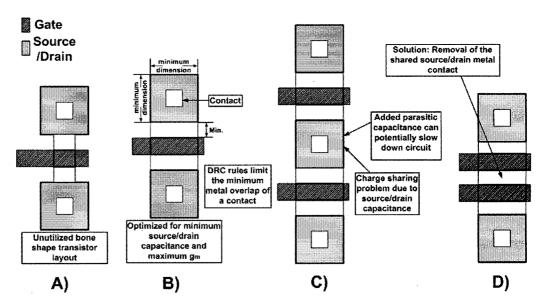

Figure 3.3 Transistor layout issues

Figure 3.3 illustrates many key points in transistor layout. Transistor A illustrates the bone-shaped transistor. This type of structure is not optimized, having large capacitances compared to their current drive. The only case when they may be useful is when they are not required to switch quickly, and when it is necessary for them to have very little current drive. On the other hand, transistor B is the optimized layout for maximum drive and frequency. Also, using the minimum optimized width, as the standard transistor cell, enables small currents to be used, effectively lowering the overall power consumption. Transistor C has a useless source/drain capacitance often forgotten when using transistors directly from a standard device library. In the case of pushing the edge of the process frequency of operation, custom layout of transistors is necessary. Transistor D illustrates a proper layout for high-speed transistors. It reduces the problem of charge sharing. Also, it enables less interconnections and a more compact layout. Note that the gate to gate distance is also limited by the DRC rules, i.e., the process characteristics.

To improve signal isolation, the sharing of guard rings around specific groups of devices is necessary. One of the most important elements in minimizing the parasitic capacitances in a layout is to maximize the sharing of the source/drain contacts and the metal of common node transistors. This is even more important in multi-finger layouts, where interdigitization is used to maximize transistors matching.

#### 3.1.1.5 Fully Differential Circuit Architectures

Fully differential circuit architectures must be used to improve noise immunity. Since supply voltages are considerably reduced to minimize power consumption, this type of architectures is necessary. They may result in an increase in transistor count, but this is easily justified by a dramatic supply voltage reduction. To prevent forming mismatches in signals delays, high symmetry of the circuit layout is required. At high speeds, timing of digital circuitry is crucial for optimal performance of synchronous and asynchronous switching.

Figure 3.4 DCVSL NAND logic gate

Figure 3.4 shows the differential cascode voltage switch logic (DCVSL) gate transistor level implementation for high speed digital logic [35]. The fast response of this circuit is mainly attributed to the feedback provided by the two PMOS loads. These two PMOS transistors are designed to be as small as possible to minimize their parasitic capacitances, and further maximize speed. The NMOS transistors can also be kept small, since they only drive small capacitive loads. An added advantage to this logic family is the absence of static power consumption. The minimum sizing of the transistors results in further reduction of the power consumption. For this same reason, minimum size transistors were used whenever possible throughout the other designs in this work.

#### 3.1.1.6 Prescaler Transistor Level Implementation

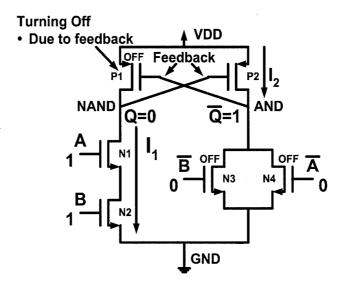

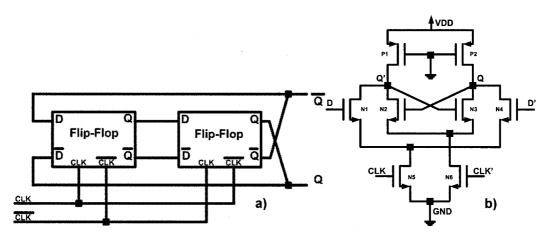

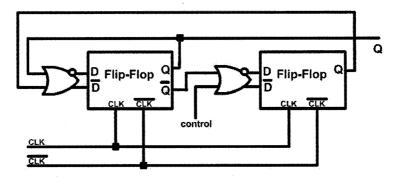

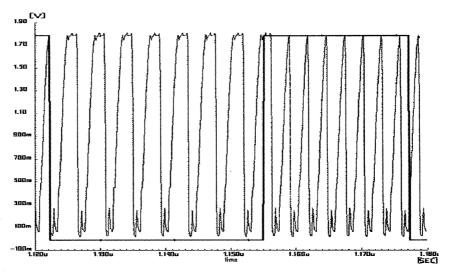

Figure 3.5 a) Divide-by-two circuit building block, b) D-flip flop transistor level circuit

The implementation consists of a conventional two D-flip-flop counter design [35], [42]. Figure 3.5 shows the implementation of the divide-by-two

prescalers and the DFF circuit level implementation. The DFF is fully differential. It uses a small PMOS active load and an optimized transistor layout for high speed operation. It also has a memory feedback element composed of  $N_2$  and  $N_3$ , which effectively stores the output during the second half cycle, i.e., when CLK' is asserted high.

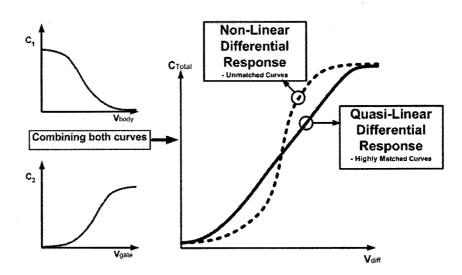

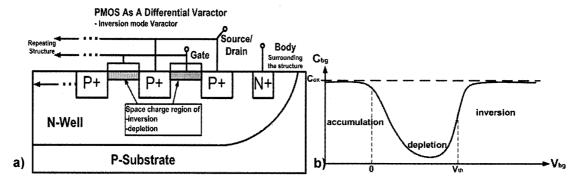

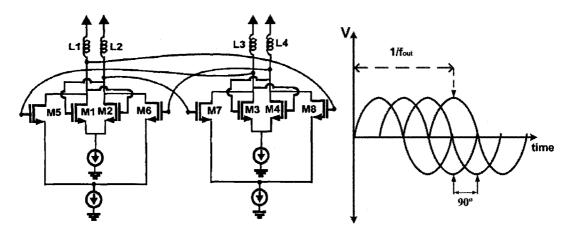

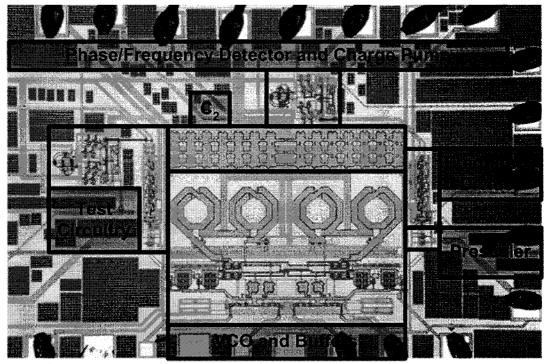

Figure 3.6 High-speed prescaler design respecting rules 1 to 6.