# A Novel Electrical-Optical Interconnect

#### Behnam Banan

Department of Electrical & Computer Engineering

McGill University

Montreal, Canada

2016

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

© Behnam Banan 2016

#### Abstract

The need for high bandwidth is rapidly increasing mainly due to the adoption of data-hungry services such as online streaming of high-definition videos, online gaming, and cloud services. Further, end-users want to access data from anywhere and as fast as possible. This has created a momentum in telecommunication industry to push for higher bandwidth and low latency communication links. So far, this goal has been achieved by expanding data centers infrastructure and increasing the number of components as well as developing high bandwidth optoelectronic circuitry. The advances in downsizing integrated circuits (ICs) is supporting the latter, resulting in the implementation of faster and smaller central processing units (CPUs). In other words, the number of bits generated within a given footprint area of an IC chip is continuously increasing. To keep up with this trend, interconnect links between electronic chips (e.g., between memory and CPU) and boards (e.g., between a motherboard and an external graphics card) need to carry a larger amount of data while ensuring a low loss interconnect with low latency. In such context, the interconnect has become the bottleneck of the overall system performance. Indeed, its technology has not evolved in performance as quickly as the IC technology. To address this bottleneck, optical interconnects for chip-to-chip data communication are extensively investigated due to their advantages regarding their large transmission bandwidth capacity at low loss, low latency, and low crosstalk. This thesis proposes a novel electrical-optical interconnect structure for chip-to-chip communication which is capable of transmitting optical and electrical signals, simultaneously. The demonstration of such structure is significant as it utilizes existing metal waveguides in electronics and merges two layers of communications (i.e., electrical and optical) onto the same structure towards increased aggregated bandwidth. The hybrid link discussed here has the potential to be implemented as an interposer between chips on a board that are bonded via micro-bumps. The proposed structure consists of a few millimeters long finite-ground coplanar waveguide (FGCPW) supporting radio frequency (RF) signals. Thin ground stripes are designed to support long-range surface plasmon polaritons (LRSPP) at optical frequencies. The use of LRSPPs on thin gold stripes is the key to the structure as it provides the interface enabling transmitting RF and optical signals, simultaneously. In this thesis, I provide details of the design methodology using analytical formulation as well as commercial electromagnetic solvers. Then, I explain the customized fabrication process of the proposed structure where gold and copper stripes are embedded in a Cytop polymer. Next, I thoroughly discuss characterization and validation methods. Finally, I present the measurement results of high-speed system-level performance of the structure. The performance of the proposed hybrid link achieves an error-free (bit-error-rate < 10<sup>-9</sup>) transmission of a 12 Gbps microwave signal with 0.65 dB/mm loss as well as of 40 Gbps optical signal with 1.8 dB/mm loss. Additionally, I demonstrate error-free transmission of a 49 Gbps single channel and 40 Gbps wavelength division multiplexed (WDM) optical signals over a 3.6 mm long LRSPP waveguides. The demonstrated hybrid link provides a new paradigm for inter-chip connectivity with further potential to be implemented for chip-to-chip communication. This innovative link approach reduces the number of interconnection layers (i.e., less complexity) with increased bandwidth density.

## Résumé

Les besoins pour de larges bandes passantes grandissent rapidement en raison des services qui consomment beaucoup de données tels que la diffusion en continu de vidéos à haute définition, les jeux en ligne and les services infonuagiques. De plus, les consommateurs veulent avoir accès à leurs données partout et rapidement. Cela a créé un élan dans l'industrie des télécommunications pour prôner des bandes passantes plus larges et des liens de communications à faible temps de latence. Jusqu'à maintenant, cet objectif a été atteint par l'expansion des infrastructures des centres de données, l'augmentation du nombre de composantes ainsi que le développement de circuits optoélectroniques à larges bandes passantes. Les avancées dans la réduction de la taille des circuits intégrés ont aidé se qui a permis l'implémentation d'unités centrales plus rapides et plus petites. En d'autres mots, le nombre de bits générés par une aire de circuits intégrés donnée augmente constamment. Pour suivre la tendance, les liens d'interconnexion entre les circuits électroniques (ex : entre la mémoire et l'unité centrale) et les cartes (ex : entre une carte mère et une carte graphique externe) doivent acheminer une grande quantité de données tout en minimisant les pertes et la latence. Dans ce contexte, les liens d'interconnexion sont devenus le goulot d'étranglement de toute la performance du système. En effet, cette technologie n'a pas évolué en performance aussi rapidement que la technologie des circuits intégrés. Pour y remédier, les liens d'interconnexion pour la communication de données entre puces sont grandement examinés en raison de leur capacité de transmission à large bande passante avec un minimum de perte, de latence et de diaphonie. Dans cette thèse, une nouvelle structure d'interconnexion électriqueoptique pour la communication entre puces qui peut transmettre des signaux optiques et électriques simultanément est proposée. La démonstration d'une telle structure est pertinente puisqu'elle utilise des guides d'ondes électroniques en métal déjà existants and regroupe deux niveaux de communications (électrique et optique) sur la même structure pour augmenter la bande passante commune. Le lien hybride présenté dans cette thèse pourrait être réalisé comme liaison entre les puces d'une carte qui sont liées par micro-billes. La structure est un guide d'onde coplanaire avec conduite à la terre limité de quelques millimètres de long qui fonctionne aussi pour les signaux en radiofréquences. De minces bandes mises à la terre sont conçues comme support pour des plasmon polaritons de surface à longue portée (LRSPP) à des fréquences optiques. L'utilisation de LRSPPs sur de minces bandes d'or est l'élément important de la structure puisque ces derniers créent l'interface qui permet la transmission de radiofréquences et de signaux optiques simultanément. Dans cette thèse, je fournis les détails de la méthode de conception en utilisant des formules analytiques ainsi que des solveurs électromagnétiques commerciaux. J'explique ensuite le processus de fabrication de la structure proposée où les bandes d'or and de cuivre sont incorporés dans un polymère Cytop suivi d'une discussion minutieuse sur les méthodes de caractérisation et de validation. Finalement, je présente les résultats sur la performance à haute vitesse de la structure au niveau du système. La performance du lien hybride proposé effectue une transmission sans erreur (taux d'erreurs binaires < 10<sup>-9</sup>) d'un signal micro-onde de 12 Gbps avec une perte de 0.65 dB/mm ainsi qu'un signal optique de 40 Gbps avec une perte de 1.8 dB/mm. De plus, je démontre une transmission sans erreur d'un canal unique à 49 Gbps et un signal optique en multiplexage en répartition par longueur d'onde de 40 Gbps dans un guide d'onde LRSPP de 3.6 mm de long. La démonstration de ce nouveau lien hybride permet un nouveau paradigme pour les connexions sur puces avec le potentiel d'être réalisé pour des communications entre puces. Cette approche innovatrice réduit le nombre de niveaux d'interconnexion (moins complexe) en augmentant la densité de la bande passante.

## Acknowledgments

First and foremost, I would like to express my genuine appreciation to Prof. Odile Liboiron-Ladouceur for her tireless supports and encouragement throughout the course of my Ph.D. research. I am thankful of her for trusting me and accepting me in her research group. During my years at McGill, I was able to perform research in the area that I was very enthusiastic about. I had access to the very well-equipped labs at the photonic systems group (PSG) at McGill University, and I had the opportunity to acquire theoretical and experimental knowledge in the field of optics, and I am very thankful of Prof. Liboiron-Ladouceur for this experience.

Secondly, I wish to express my gratitude to Prof. Pierre Berini for accepting to collaborate in this project and for his support and guidance during my Ph.D. It was an honor for me to have Prof. Berini as my collaborator and be able to work with him.

I would like to acknowledge Prof. R. Niall Tait, Ewa Lisicka-Skrzek, Sa'ad M. Hassan, Norman R. Fong, Martin Dussault, and Carleton University Microfabrication staff: Rob Vandusen and Angela McCormick for their help and support for the fabrication of my design.

I am grateful to all the professors in the PSG for building a world-class research laboratory infrastructure and creating a professional and friendly work environment. I am thankful to all the staff at PSG: Ms. Maru Basanez, Ms. Carrie Serban, Chris Rolston, and Brent Snow for their administrative and technological support. As well, I would like to thank Dr. Phil Roche for his help in troubleshooting experimental setups.

Last but not least, many thanks to my friends and colleagues at PSG: Monir Moayedi, Mehrdad MirShafiei, Ali Salehiomran, Farhad Shokraneh, Md Shafiqul Hai, Chris Williams, Rubana Pariti, Vernon Elmo Paul, Yule Xiong, David Patel, and Venkat Veerasubramania, who worked alongside me in the labs. I would like to acknowledge Sandrine Filion Côté for her constant encouragements and help with the French translation of the abstract.

To my beloved mother and late father

To my dearest brothers

To my beloved wife, my life partner

# **Contents**

| 1. | Introduction                                          | 1    |

|----|-------------------------------------------------------|------|

|    | 1.1. Motivation                                       | 1    |

|    | 1.2. Thesis outline                                   | 2    |

|    | 1.3. Literature review                                | 4    |

|    | 1.3.1. Introduction                                   | 4    |

|    | 1.3.2. Electrical interconnect                        | 4    |

|    | 1.3.3. Optical interconnects                          | 7    |

|    | 1.3.4. Conclusion                                     | . 13 |

| 2. | Background                                            | . 14 |

|    | 2.1. Introduction                                     | . 14 |

|    | 2.1.1. Surface plasmon polaritons (SPPs)              | . 15 |

|    | 2.1.2. SPPs excitation                                | . 17 |

|    | 2.1.3. Long-range surface plasmon polaritons (LRSPPs) | . 18 |

|    | 2.2. Plasmonic interconnects                          | . 23 |

|    | 2.3. Conclusion                                       | . 29 |

| 3. | Plasmonic stripe waveguide                            | . 30 |

|    | 3.1. Introduction                                     | . 30 |

|    | 3.2. Design of the LRSPP waveguide                    | . 30 |

|    | 3.3. Fabrication of the LRSPP waveguide               | . 34 |

|    | 3.4. Measurement                                      | . 34 |

|    | 3.4.1. Single NRZ-OOK Channel at 40 and 49 Gbps       | . 34 |

|    | 3.4.2. Multiple NRZ-OOK Channel at 49 Gbps                             | 38 |

|----|------------------------------------------------------------------------|----|

|    | 3.4.3. Multiple NRZ-DPSK Channel at 10 Gbps                            | 40 |

|    | 3.5. Transmission distortion analysis                                  | 42 |

|    | 3.6. Conclusion                                                        | 44 |

| 4. | Simultaneous optical and microwave data transmission                   | 45 |

|    | 4.1. Introduction                                                      | 45 |

|    | 4.2. Proposed structure                                                | 45 |

|    | 4.2.1. LRSPP waveguide design and optimization                         | 46 |

|    | 4.3. Microwave performance optimization                                | 49 |

|    | 4.3.1. Characteristic impedance calculation based on conformal mapping | 49 |

|    | 4.3.2. Microwave performance analysis using HFSS software              | 53 |

|    | 4.4. Fabrication process for the FGCPW                                 | 56 |

|    | 4.4.1. Bottom cladding and first metal layer deposition                | 56 |

|    | 4.4.2. Top cladding and signal stripe formation                        | 58 |

|    | 4.4.3. Microscopy and AFM                                              | 60 |

|    | 4.5. Measurements                                                      | 61 |

|    | 4.5.1. Optical insertion loss measurement                              | 61 |

|    | 4.5.2. Electrical S-parameters measurement                             | 63 |

|    | 4.5.3. Optical and electrical modulated data transmission              | 64 |

|    | 4.6. Conclusion                                                        | 66 |

| 5. | Electrical performance analysis of the proposed FGCPW                  | 68 |

|    | 5.1. Introduction                                                      | 68 |

|    | 5.2. Structure                                                         | 68 |

|    | 5.3. Characterization of the FGCPW waveguide                           | 69 |

|    | 5.4. Circuit models and transmission parameters extraction             | 71 |

| 5.4.1. Conventional distributed circuit model | 71 |

|-----------------------------------------------|----|

| 5.4.2. Lumped circuit model                   | 74 |

| 5.5. Conclusion                               | 78 |

| 6. Conclusion and future works                | 79 |

| 6.1. Conclusion                               | 79 |

| 6.2. Future works                             | 80 |

| 6.3. Contributions                            | 82 |

| 6.3.1. Main contributions                     | 82 |

| 6.3.2. Other contributions                    | 84 |

| 7. References                                 | 85 |

# **List of Figures**

| Fig. 1.1. a) Electrical interconnects on motherboard, b) flexible electrical interconnects [6] 6                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

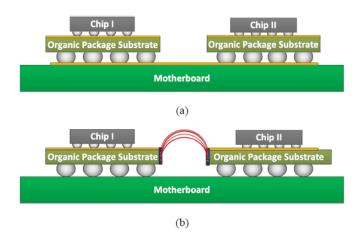

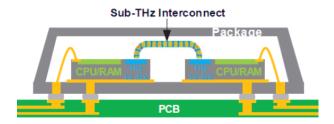

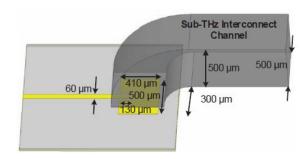

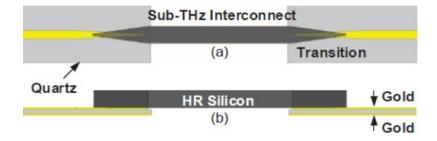

| Fig. 1.2. Sub-THz interconnect using the advantages of both optical and electrical interconnects                                                     |

| [5] © [2016] IEEE                                                                                                                                    |

| Fig. 1.3. Far field transition of MSL-to-DWG [5] © [2016] IEEE                                                                                       |

| Fig. 1.4. a) Top view of sub-THz interconnect using near-field transition, b) side view of the                                                       |

| dielectric channel [5] © [2016] IEEE                                                                                                                 |

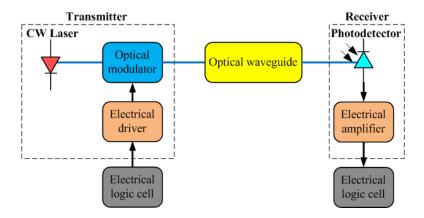

| Fig. 1.5. An optical interconnect system                                                                                                             |

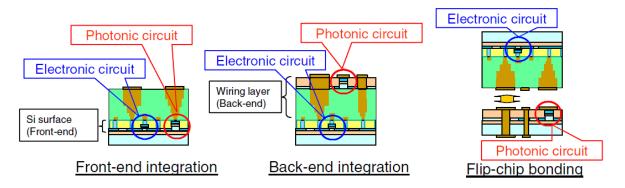

| Fig. 1.6. Schematic cross sections of integration between photonics and electronics [10] 9                                                           |

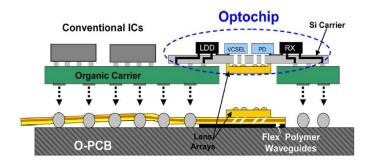

| Fig. 1.7. Schematic of the Terabus architecture with polymer waveguide at board level [11] ©                                                         |

| [2012] IEEE                                                                                                                                          |

| Fig. 1.8. A photonics-electronics convergence platform for inter-chip interconnects using silicon                                                    |

| interposer [12]                                                                                                                                      |

| Fig. 1.9. Silicon interposer as the photonics-electronics convergence system for inter-chip                                                          |

| interconnects [10]                                                                                                                                   |

| Fig. 1.10. a) Diagram of multilayer optical circuit board including multiple layers of $Si_3N_4$                                                     |

| waveguides, an optical interposer, and an electrical chip, b) diagram of evanescent interlayer                                                       |

| coupling: a waveguide in an intermediate runs parallel to layer 1, coupling light evanescently, and                                                  |

| then bends such that it runs parallel to layer 2 [13]. © [2016] IEEE                                                                                 |

| Fig. 2.1. Operating speeds and critical dimensions of various chip-scale device technologies 15                                                      |

| Fig. 2.2. SPP propagation along a metal-dielectric interface                                                                                         |

| Fig. 2.3. Dispersion diagram of the metal-dielectric interface using a Drude model with no loss                                                      |

| [18]                                                                                                                                                 |

| Fig. 2.4. Schematics of different schemes to excite SPP                                                                                              |

| Fig. 2.5. Metal slab with a thickness of $t$ bounded by semi-infinite dielectrics, supporting two                                                    |

| bound SPP modes, $s_b$ and $a_b$                                                                                                                     |

| Fig. 2.6. Normalized phase and attenuation constant of sb and ab modes of an asymmetric Ag                                                           |

| metal slab at $\lambda_0 = 632.8 \text{ nm}$ with $\varepsilon_0 = (0.0657 - i4)^2$ , $\varepsilon_1 = 1.5^2$ , and $\varepsilon_2 = 1.55^2$ [19] 20 |

| Fig. 2.7. Cross section of the metal stripe waveguide with a thickness of $t$ , and width of $w$ bounded                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| by semi-infinite dielectrics                                                                                                                                           |

| Fig. 2.8. Contour and 3D plots of $\operatorname{Re}\left\{S_{z}\right\}$ of $ss_{b}^{0}$ mode for $w=1 \ \mu m$ (a) $t=80 \ \text{nm}$ , (b) $t=20 \ \text{nm}$ , (c) |

| <i>t</i> =100 nm, (d) <i>t</i> =40 nm [19].                                                                                                                            |

| Fig. 2.9. Longitudinal cross-sectional view of edge coupling between the fiber and the structure                                                                       |

| input                                                                                                                                                                  |

| Fig. 2.10. (a) Schematic diagram of an Au stripe waveguide based on LRSPP and (b) the pigtailed                                                                        |

| LRSPP waveguide [24]                                                                                                                                                   |

| Fig. 2.11. The flexible plasmonic waveguide connecting transmitter and receiver ICs [26] 25                                                                            |

| Fig. 2.12. The mobile phone camera records HD digital image then the image data is transmitted                                                                         |

| to the LCD using the LRSPP interconnect [26]                                                                                                                           |

| Fig. 2.13. On-board chip-to-chip optical interconnect using polymer based Au LRSPP waveguide                                                                           |

| [27]                                                                                                                                                                   |

| Fig. 2.14. The layout of the LR-DLSPP waveguide structure [29]                                                                                                         |

| Fig. 2.15. Assembled chip-to-chip optical interconnection system installed with 10-cm-long silver                                                                      |

| stripe waveguide, (a) Coupling between TM-VCSEL and silver stripe optical waveguide, (b)                                                                               |

| coupling between silver stripe optical waveguide and photodetector (PD) [23]. © [2009] IEEE.27                                                                         |

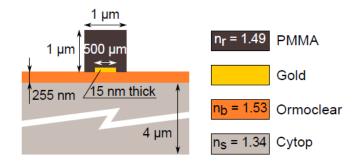

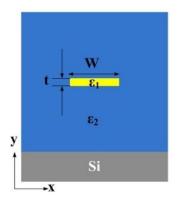

| Fig. 3.1. Schematic of the plasmonic stripe waveguide cross section © [2013] IEEE31                                                                                    |

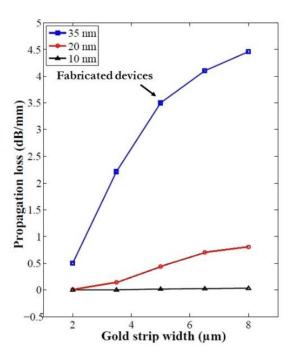

| Fig. 3.2. Simulated propagation loss as a function of gold stripe width $w$ and thickness $t$ . © [2013]                                                               |

| IEEE                                                                                                                                                                   |

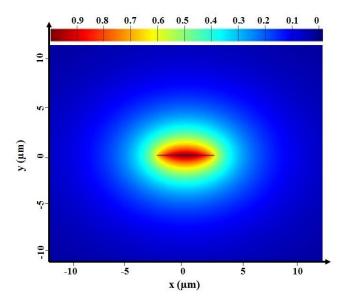

| Fig. 3.3. The near-field image of the electric field ( ${\rm Re}\{E_y\}$ )distribution of the 5- $\mu$ m-wide and                                                      |

| 35 nm-thick gold stripe. (These dimensions were used for the fabricated devices.) © [2013] IEEE.                                                                       |

|                                                                                                                                                                        |

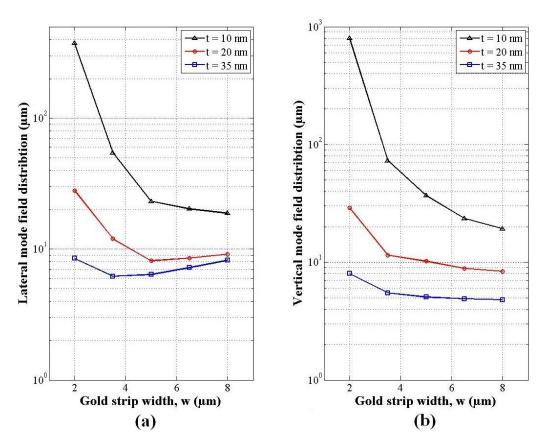

| Fig. 3.4. Simulated (a) lateral and (b) vertical MFD as a function of gold stripe width (w) and                                                                        |

| thickness (t). © [2013] IEEE                                                                                                                                           |

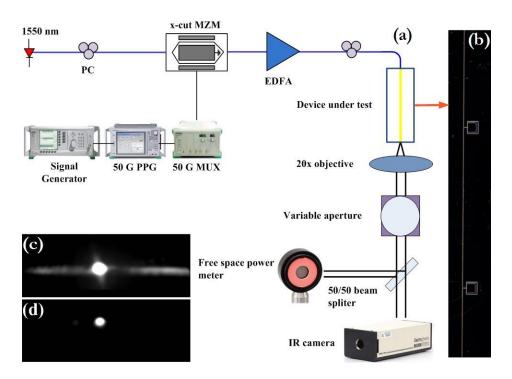

| Fig. 3.5. (a) Schematic of the setup to measure the insertion loss and capture the mode profile. (b)                                                                   |

| Fabricated devices, (c) Far-field captured LRSPP and scattered light from the cladding layer (open                                                                     |

| aperture), (d) Far-field captured LRSPP (partially closed aperture and attenuated). © [2013] IEEE.                                                                     |

|                                                                                                                                                                        |

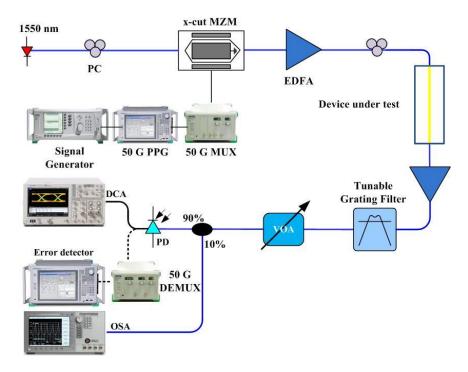

| Fig. 3.6. Schematic of the setup for a single channel at 1550 nm to measure the BER. © [2013]                         |

|-----------------------------------------------------------------------------------------------------------------------|

| IEEE                                                                                                                  |

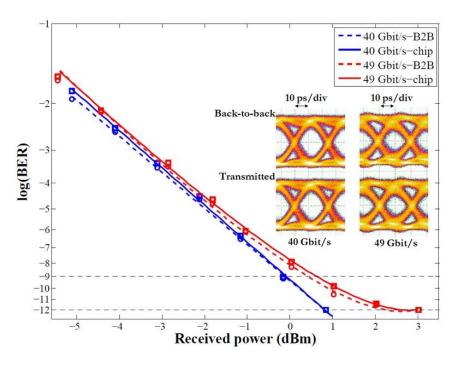

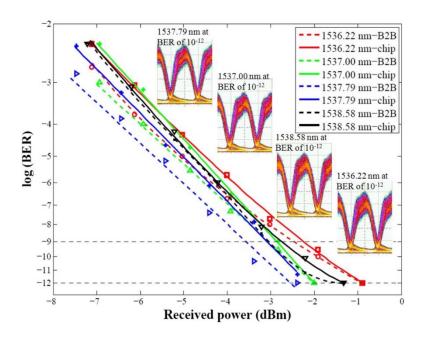

| Fig. 3.7. Measured BER versus the received power for a single channel at 40 and 49 Gbps. (The                         |

| inset shows the eye diagrams). © [2013] IEEE                                                                          |

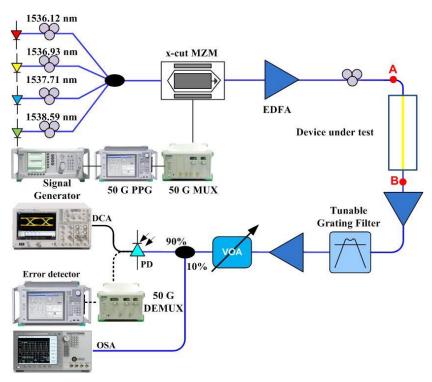

| Fig. 3.8. Schematic of the setup for four channels OOK signals transmission to measure the BER.                       |

| © [2013] IEEE                                                                                                         |

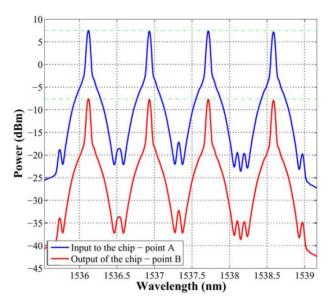

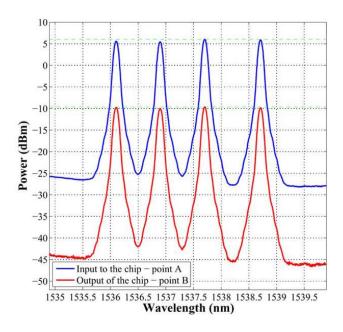

| Fig. 3.9. Input (blue) and output (red) signals of the chip with OOK modulation at 49 Gbps                            |

| corresponding respectively to points A and B in Fig. 3.8. © [2013] IEEE                                               |

| Fig. 3.10. (a) Measured BER and (b) eye diagrams for the back-to-back and transmitted signals for                     |

| four channels with OOK modulation at 49 Gbps. $©$ [2013] IEEE                                                         |

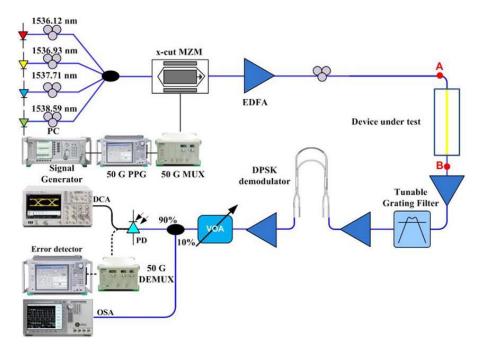

| Fig. 3.11. Schematic of the setup for four channels DPSK signals transmission to measure the                          |

| BER. © [2013] IEEE                                                                                                    |

| Fig. 3.12. Input (blue) and output (red) signals of the chip with DPSK modulation at 10 Gbps                          |

| corresponding to points A and B in Fig. 3.11, respectively. $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                   |

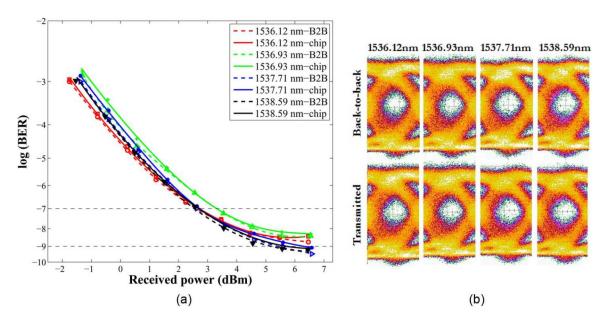

| Fig. 3.13. Measured BER for four channels with DPSK modulation at 10 Gbps. The insets show                            |

| eye diagrams of the transmitted signal for all channels at BER of $10^{-12} \odot$ [2013] IEEE42                      |

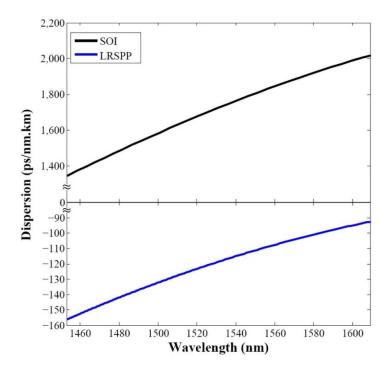

| Fig. 3.14. Calculated dispersion for silicon on insulator (SOI) waveguide with 525-nm width and                       |

| 226-nm thickness and embedded gold stripe with 5- $\mu m$ width and 35-nm thickness in Cytop                          |

| polymer© [2013] IEEE                                                                                                  |

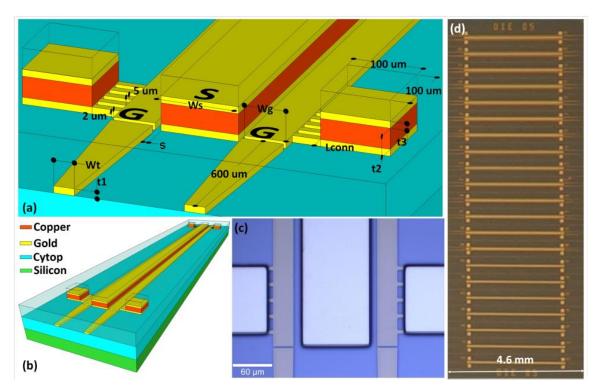

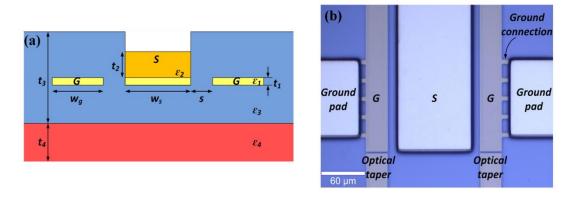

| Fig. 4.1. (a) and (b): Schematic of the structure of interest, and (c) $20 \times$ magnification microscope           |

| image of one of the fabricated structures at one end. The pad area is $100 \times 100 \ \mu m^2$ with a $100 \ \mu m$ |

| wide signal stripe $(W_s)$ , and two 30 $\mu m$ wide ground stripes $(W_g)$ separated by 2 $\mu m$ gap from           |

| optical tapers. (d) Image of a 4.6 mm long fabricated die which includes 21 different microwave-                      |

| optical transmission lines with straight optical reference waveguides in between 46                                   |

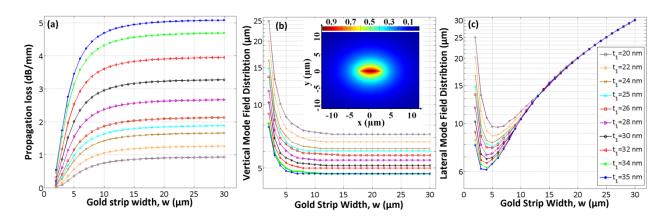

| Fig. 4.2. Computed (a) propagation loss, (b) vertical and (c) lateral mode field diameter as a                        |

| function of gold ground stripe width ( $W_g$ ) and thickness ( $t_1$ ) for a single gold stripe waveguide in          |

| a homogenous medium, The inset in (b) shows a near-field image of the electric field ( $\operatorname{Re}\{E_y\}$ )   |

| distribution of the 5 µm wide and 35 nm thick gold stripe                                                             |

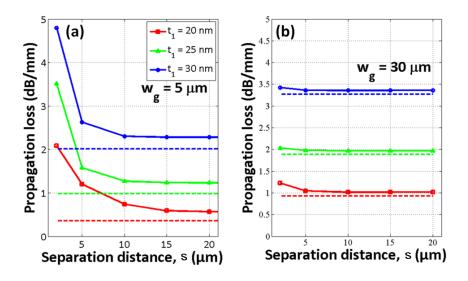

| Fig. 4.3. Computed propagation loss versus separation distance (s) and thickness ( $t_1$ ), for ground                          |

|---------------------------------------------------------------------------------------------------------------------------------|

| stripes (a) 5 $\mu$ m and (b) 30 $\mu$ m wide ( $W_g$ ). The signal stripe width ( $W_s$ ) and thickness ( $t_2$ are 50 $\mu$ m |

| and 500 nm, respectively. Cytop thickness is assumed to be 15 $\mu m$ on a thick silicon substrate.                             |

| Dashed lines show propagation loss when Cytop thickness is 100 μm                                                               |

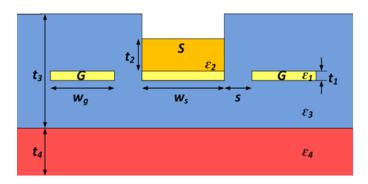

| Fig. 4.4 Schematic cross-section of the proposed structure excluding the ground pads with                                       |

| connections as well as optical tapers                                                                                           |

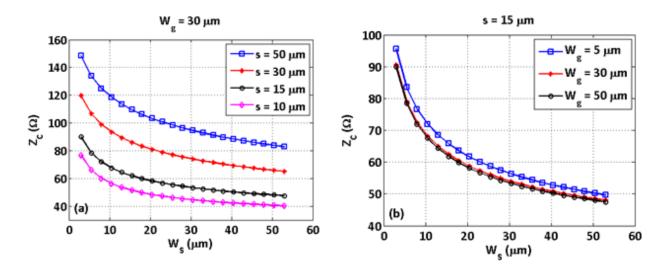

| Fig. 4.5. Calculated characteristic impedance of the FGCPW at 40 GHz as a function of signal                                    |

| stripe width ( $W_s$ ) for (b) $s=15~\mu m$ and different ground stripe widths, and (a) $W_g=30~\mu m$ and                      |

| different gap sizes                                                                                                             |

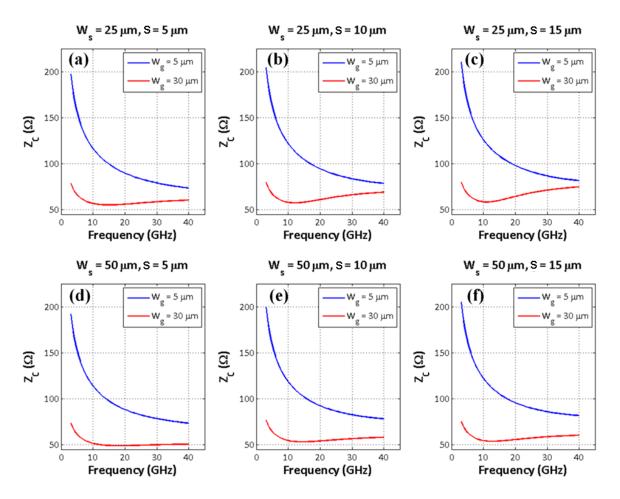

| Fig. 4.6. (a)-(f) Computed electrical characteristic impedance $Z_c$ of the proposed structure as a                             |

| function of frequency for different ground $(W_g)$ and signal $(W_s)$ stripe widths, and separation (s).                        |

| 54                                                                                                                              |

| Fig. 4.7. Computed electrical response of structures comprised of a 50µm wide signal stripe and                                 |

| 30 μm wide ground stripes for different separation sizes (s) and lengths                                                        |

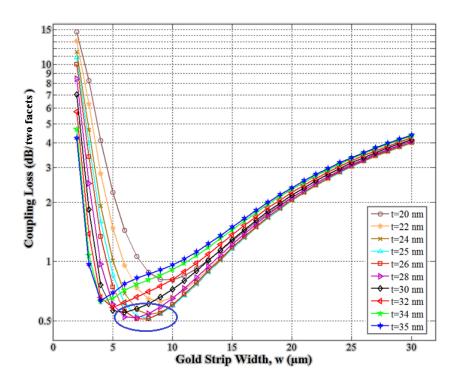

| Fig. 4.8. Computed coupling loss per two facets as a function of gold ground stripe width ( $W_g$ )                             |

| and thickness $(t_1)$ for a single gold stripe waveguide in a homogenous medium                                                 |

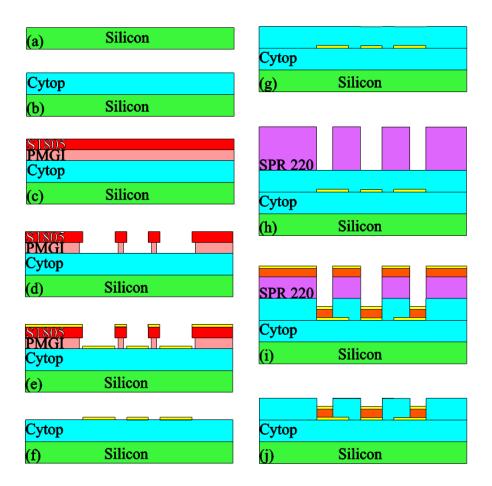

| Fig. 4.9. Schematic of the fabrication process flow. (a) Cleaning of a silicon wafer (10% HF and                                |

| O <sub>2</sub> plasma), (b) sequential spin coating of Cytop bottom cladding, (c) surface preparation followed                  |

| by PMGI and S1805 spin coating, (d) UV patterning and developing, (e) gold deposition via                                       |

| thermal evaporation, (f) lift-off, cleaning, and dehydration, (g) Cytop top cladding spin coating                               |

| with slow thermal treatment, (h) surface preparation, SPR 220 spin coating, patterning, and                                     |

| developing, (i) etching followed by copper and gold deposition, and (j) lift-off and cleaning. $\dots$ 57                       |

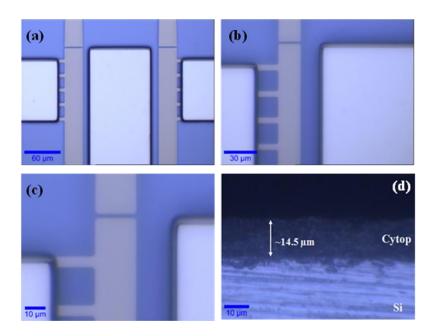

| Fig. 4.10. The effect of top cladding thermal processing on the first metal layer of the device (50 $\times$                    |

| magnification) where Cytop is hard-baked at 90 °C: (a) without a thermal ramp, (b) with a 10 °C/hr $$                           |

| thermal ramp, and (c) with a 5 °C/hr thermal ramp                                                                               |

| Fig. 4.11. (a) $20 \times$ , (b) $40 \times$ , and (c) $40 \times$ with digital zoom-in microscope images of a fabricated       |

| structure near one end of a device comprising two optical tapers, two pads $100 \times 100 \ \mu\text{m}^2$ in area,            |

| a 50 µm wide signal stripe, and 30 µm wide ground stripes separated by 2 µm long gaps from the                                  |

| optical tapers. (d) Microscope image of a device cross-section with 40× magnification and digital                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| zoom-in. 60                                                                                                                   |  |  |  |

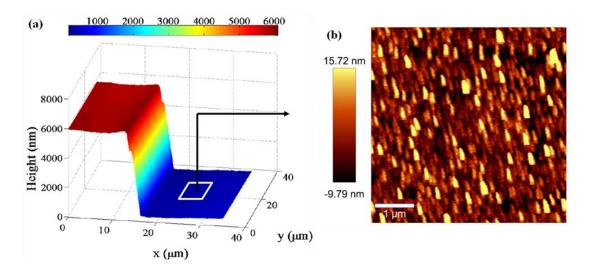

| Fig. 4.12. AFM measurement of a final structure indicating (a) the etch profile and (b) surface                               |  |  |  |

| roughness of a $5\times5~\mu\text{m}^2$ area of a signal line.                                                                |  |  |  |

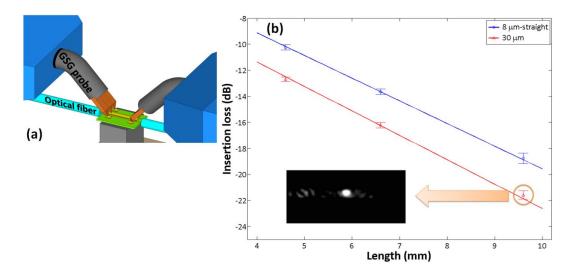

| Fig. 4.13. (a) Illustration of the experimental set-up for the simultaneous excitation of LRSPP and                           |  |  |  |

| microwave modes. (b) Measured insertion loss versus waveguide length for 8 and 30 $\mu m$ wide, 25 $^\circ$                   |  |  |  |

| nm thick gold stripe waveguides. The inset shows a far-field image of the LRSPP mode output.                                  |  |  |  |

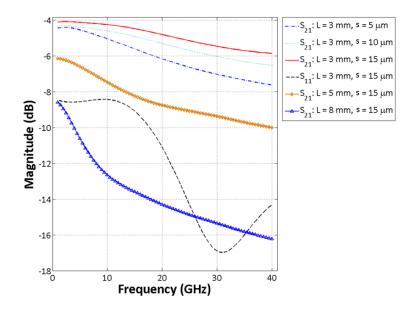

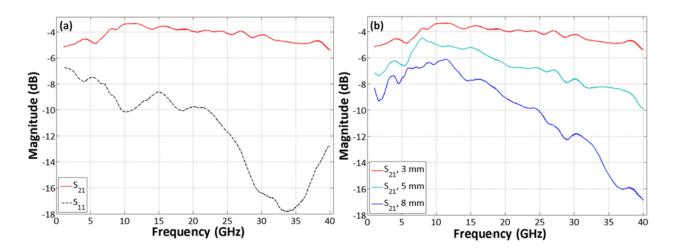

| Fig. 4.14. (a) S-parameter magnitude for a 3 mm long waveguide, and (b) $S_{21}$ for different lengths.                       |  |  |  |

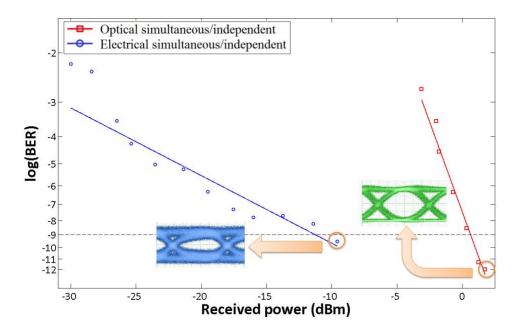

| Fig. 4.15. BER measurements of simultaneous and independent 40 Gbps optical and 12 Gbps                                       |  |  |  |

| electrical signals. The insets show captured eye diagrams. The solid lines are exponential fit curves                         |  |  |  |

| to measured values                                                                                                            |  |  |  |

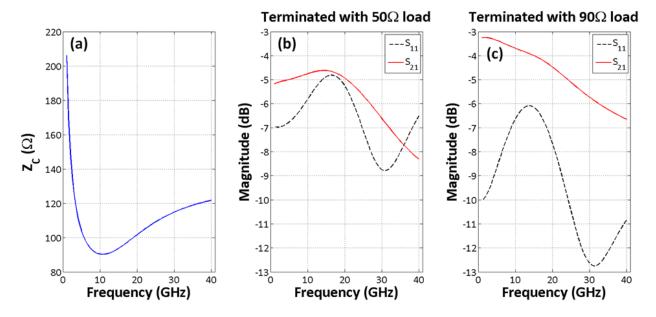

| Fig. 4.16 Computed (a) characteristic impedance and S-parameters when terminated with a (b)                                   |  |  |  |

| $50\Omega$ load, and (c) $90\Omega$ load for a structure comprised of a 1 μm wide signal stripe ( $W_s$ ), a 30 μm            |  |  |  |

| wide ground stripe ( $W_g$ ), and a gap of 4 $\mu$ m (s).                                                                     |  |  |  |

| Fig. 5.1. (a) Schematic cross section of the proposed structure excluding the ground pads with                                |  |  |  |

| connections as well as optical tapers. (b) Microscope image of a fabricated structure at one end of                           |  |  |  |

| the transmission line                                                                                                         |  |  |  |

| Fig. 5.2. Schematic of the experimental setup for the S-parameter measurements                                                |  |  |  |

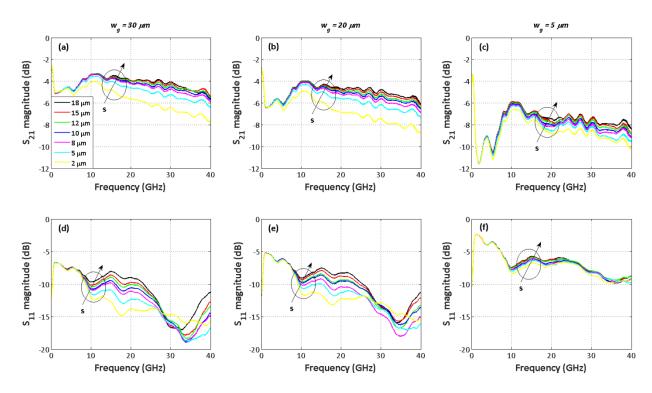

| Fig. 5.3. Measured transmission ( $S_{21}$ ) and reflection ( $S_{11}$ ) parameters of the 3 mm long waveguides               |  |  |  |

| with $W_s = 50 \mu\text{m}$ for different $W_g$ and $s$ .                                                                     |  |  |  |

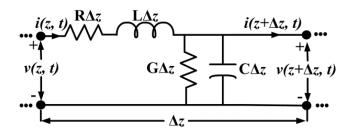

| Fig. 5.4. The distributed element model applied to the FGCPW                                                                  |  |  |  |

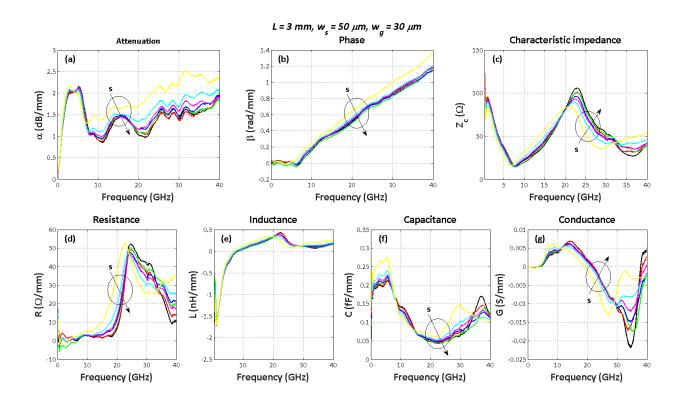

| Fig. 5.5. Extracted distributed parameters as a function of frequency for a 3 mm long waveguide                               |  |  |  |

| structure with $W_s = 50  \mu \text{m}$ , $W_g = 30  \mu \text{m}$ , and seven different separation distances s (direction of |  |  |  |

| arrow refers to an increase in separation). (a) Attenuation, (b) propagation constant, (c)                                    |  |  |  |

| characteristic impedance, (d) resistance, (e) inductance, (f) capacitance, and (g) conductance 74                             |  |  |  |

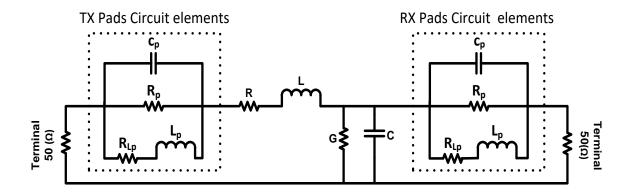

| Fig. 5.6. Equivalent lumped circuit of the FGCPW transmission line in which the effects of the                                |  |  |  |

| pads and their connections are considered                                                                                     |  |  |  |

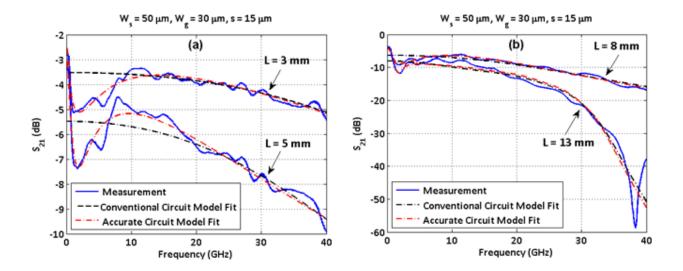

| Fig. 5.7. The measured $S_{21}$ parameter (solid line) along with the modeled transmission response   |

|-------------------------------------------------------------------------------------------------------|

| (with and without considering the parasitic elements) for the conventional circuit model (dashed      |

| line) and the accurate circuit models (dash-dot) for 3, 5, 8, and 13 mm long waveguides with 50 µr    |

| signal stripe width, 30 μm ground stripe widths, and 15 μm separation distance7                       |

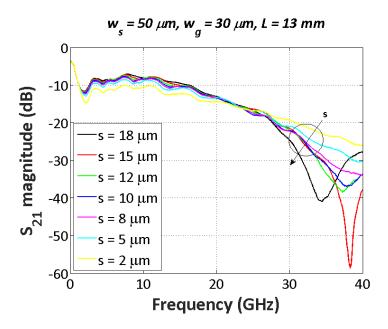

| Fig. 5.8. Measured transmission of 13 mm long lines with $W_s$ of 50 $\mu$ m and $W_g$ 30 $\mu$ m for |

| different separation distances                                                                        |

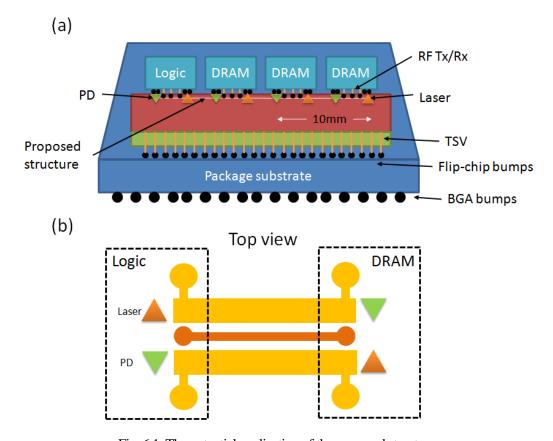

| Fig. 6.1. The potential application of the proposed structure                                         |

# **List of Tables**

| Table 1.1 Comparison of different interconnect solutions               | 12                |

|------------------------------------------------------------------------|-------------------|

| Table 2.1 Different demonstrations of modulated data transmission thro | ough a plasmonic  |

| waveguide                                                              | 28                |

| Table 5.1 Extracted lumped parameters from measured S-parameters based | on lumped circuit |

| model                                                                  | 75                |

# **List of Acronyms**

ADS Advanced Design System

AFM Atomic Force Microscopy

ASE Amplified Spontaneous Emission

ASIC Application Specific Integrated Circuit

BER Bit-Error-Rate

CMOS Complementary Metal–Oxide–Semiconductor

CPW Co-Planar Waveguides

DLSPPW Dielectric-Loaded SPP Waveguides

DPSK Differential Phase Shift Keying

DSP Digital Signal Processing

DWG Dielectric Waveguides

EDFA Erbium-Doped Fiber Amplifier

EM Electromagnetic

EO Electrical-to-Optical

EPB Energy Per Bit

FEM Finite Element Method

FGCPW Finite Ground Co-Planar Waveguide

GSG Ground-Signal-Ground

HMDS Hexamethyldisilazane

HR silicon High Resistivity Silicon

IC Integrated Circuits

IL Insertion Loss

IPA Isopropyl Alcohol

ISP Internet Service Provider

ITU International Telecommunication Union

LCD Liquid Crystal Display

LD Laser diode

LR-DLSPPWs Long-Range DLSPPWs

LRSPPs Long-Range SPP

LRSPPWs Long-Range SPP Waveguides

LSI Large-Scale Integration

MFD Mode Field Diameter

MoL Method of Line

MSL Microstrip Lines

MZM Mach–Zehnder Modulator

NA Numerical Aperture

NRZ Non-Return-to-Zero

OE Optical-to-Electrical

OOK On-Off-Keying

OSA Optical Spectrum Analyzer

PCB Printed Circuit Boards

PD Photo Detector

PEC Perfect Electrical Conductor

PMGI Polymethylglutarimide

PM-SMF Polarization-Maintaining Single Mode Fiber

PPG Pulse Pattern Generator

PRBS Pseudorandom Binary Sequence

RF Radio Frequency

SOI Silicon on Insulator

TE Transverse Electric

TEM Transverse Electric and Magnetic

TM Transverse Magnetic

VCSEL Vertical-cavity-surface-emitting-laser

WDM Wavelength Division Multiplexing

This chapter explains the motivation for this thesis research, and provides a literature review of different interconnect technologies and discusses the electrical and optical interconnects. Finally, an introduction of plasmonics as the interface between electronics devices and photonics components are presented.

#### 1.1. Motivation

The popularity of mobile devices such as smartphones and tablets, running data-intensive applications, online high-definition video streaming, online gaming, cloud services, and high-speed wireless networks (4G/LTE) are a few of the driving forces for internet service providers (ISPs) to demand higher bandwidth. There are two solutions to this issue. One solution is to increase the bandwidth by adding more equipment in data centers. Alternatively, the telecommunications networking equipment suppliers must increase the bandwidth in their existing form factors (i.e., higher bandwidth density). The latter is more attractive to the industry compared to the former, mainly due to its lower cost per bit. However, this approach requires tackling some challenges such as designing high bandwidth optical-to-electrical and electrical-to-optical (OE/EO) converters (e.g., modulators and receivers), advanced modulation formats, complex

digital signal processing (DSP) algorithms, high-speed application-specific integrated circuits (ASICs), and high bandwidth interconnects. The focus of this thesis is to investigate the high bandwidth interconnects.

In recent years, by the advance of CMOS technology where high-speed ICs with multi- and many-core architectures are built, the discussion on using optical interconnects for off-chip and board-to-board communication has gained much interest. The concept of "partition length," above which information transports more efficiently by photons rather than electrons, assesses the feasibility of optical interconnects compared to their electrical counterpart. In [1] it was discussed that for channel width of below 1  $\mu$ m the partition length for high frequencies (> 40 GHz) is in range of several millimetres.

In this context, researchers have extensively investigated multiple technologies such as multicore optical fibers, polymer waveguides, silicon waveguides, and plasmonic-based waveguides. Each of these technologies inherits some advantages and disadvantages, which I will discuss in more details in this chapter

In this thesis, I propose, design, fabricate and characterize a new structure for chip-to-chip communication where metal interconnects embedded in a polymer are deployed to transmit both microwave and optical signals simultaneously. The envisioned application for the hybrid link discussed in this thesis is in architectures where an electrical interface between chips is implemented using ball-grid arrays (BGAs) or micro bumps. The goal of this structure is to provide efficient and low energy consumption chip-to-chip interconnects by sending high data rate via optical section, and switching to low data rate electrical signal when the required bandwidth demand is not at its full capacity. Measurement results of the hybrid link are promising and show comparable performance with recent works, and justify future analysis to further improve the performance of the structure and achieve practical chip-to-chip implementation.

## 1.2. Thesis outline

Chapter 2 explains the principles of plasmonics and reviews different demonstrations of optical signal transmission through plasmonic waveguides. Since the proposed electrical-optical interconnect comprises of a plasmonic waveguide, chapter 2 provides the background information on the plasmonic waveguides and the design of plasmonic interconnects.

Chapter 3 explains the design and modeling of an LRSPP waveguide made of thin gold stripes embedded in Cytop. The fabricated device is characterized and the transmission of multiple OOK (4×49 Gbps) and differential phase shift keying (DPSK) (4×10 Gbps) modulated data is experimentally demonstrated. The signal transmission is further verified by performing bit-error-rate (BER) measurements.

Chapter 4 proposes a novel metal waveguide structure, which simultaneously transmits optical and microwave signals. The design and optimization of optical and electrical waveguides are explained. Moreover, the fabrication steps for implementation of the designed structure are described. And finally, the measurement results of the fabricated devices are presented.

In chapter 5, circuit model analysis is performed to provide more insight into the RF performance of the proposed structure in chapter 4.

Chapter 6 gives a conclusion of the thesis and provides a list of the possible future works. Finally, chapter 7 gives a list of the references of this thesis.

## 1.3. Literature review

#### 1.3.1. Introduction

Interconnects are the physical connections enabling the intra-chip (within a chip), inter-chip (chip-to-chip), and board-to-board data transfers. As the increasing bandwidth demand is pushing computing modules to work at higher speeds, the interconnection between different computing modules has become the bottleneck limiting the performance of the system. Consequently, interconnects with high bandwidth density and energy efficiency are of great interest.

Interconnects are evaluated based on multiple factors including delay, noise, bandwidth density, power dissipation, and cost. The bandwidth density or the bisectional bandwidth is the data transmission bandwidth per unit width and is expressed in the unit of Gbps/mm or Gbps/ $\mu$ m. This section gives a brief review of different types of interconnects and discusses the drawbacks and advantages of different approaches.

Conventionally, the chip-to-chip and board-to-board connections only included electrical interconnects. However, as it will be discussed in the next sections, the conventional copper-based electrical interconnects can no longer satisfy the essential requirements of the interconnection. Hence, researchers have explored other types of electrical links. Moreover, optical and plasmonic interconnects have been proposed as the alternative solutions. The next sections give a brief review of electrical and optical interconnects.

#### 1.3.2. Electrical interconnect

On-chip electrical interconnects consist of copper wires surrounded by a low-k dielectric. The effective time constant (RC) of a conventional electrical interconnect, where R and C are the total resistance and capacitance of the line, determines its delay time. Downsizing the minimum feature size of integrated circuits (ICs) has enabled the transistors to work at higher speed and therefore perform more computations per second [2,3]. As the interconnect dimensions are scaled down, the metal wire cross section reduces which consequently increases the wire resistivity. However, the capacitance per unit length of the metallic wire is not significantly affected. By scaling down the metallic wire interconnection, its effective time constant (RC) increases. Hence, while transistors

delay decreases with scaling, the delay of interconnects increases [4], and the delay due to the communication between the parts of the chip becomes comparable to the computation delay itself. This is called the "interconnect bottleneck" which refers to IC performance constraint due to connections between components instead of their internal speed.

There are different types of electrical interconnects including transmission lines (e.g., coplanar waveguides and microstrip lines), dielectric waveguides (DWGs), and wireless (i.e., air is the dielectric medium). They all have the advantage of compatibility with silicon processes. However, each scheme suffers from different restrictions on transmission loss, electromagnetic interferences (EMI), etc. [5]. This section provides some examples of different types of electrical interconnects.

Fig. 1.1(a) shows a motherboard based electrical interconnect [6]. The metallic transmission line interconnects suffer from high conduction loss at high operating frequencies. A complementary metal—oxide—semiconductor (CMOS) microstrip line (MSL) at 100 GHz has 1 dB/mm loss which increases with the operating frequency [5]. By using differential transmission lines in the printed circuit boards (PCB), the data transmission speed increases at the expense of doubling the number of signal lines [7]. The typical pitch of a high-density differential stripline is 600 μm and assuming 10 Gbps data transmission per channel, the maximum bandwidth density of 16 Gbps/mm can be achieved [6, 7]. Higher bandwidth channels are limited by dispersion and need more equalization taps and hence produce more power dissipation [6]. In [7] three patterns of the cross-sectional shape of differential transmission lines are studied to reduce the cross-talk noise and consequently improve the wiring density of the transmission line. Using square shape cross section instead of conventional wide rectangle cross section for the conductor, the wiring density of the differential transmission line improves by up to 12.5 % (from 600 μm to 525 μm).

An alternative approach is to use low-loss ribbon cables instead of FR4 boards as depicted in Fig. 1.1(b) [6]. In [8], four different flex circuit constructions have been studied which consist of microstrip lines embedded in a polyimide substrate. The measurement results show that the raw bandwidth on low-loss flex ribbons is three times larger than FR-4 boards. The measurement results also show that the attenuation constant at the frequency of 20 GHz for microstrip transmission line on FR4 is 1 dB/cm while in the case of differential microstrip line implemented in the flex circuit; it is 0.3 dB/cm [8].

Fig. 1.1. a) Electrical interconnects on motherboard, b) flexible electrical interconnects [6].

In 2012, Park et al. proposed a wireless link operating at 260 GHz which can be especially useful for routing between chips when a physical interconnection is not feasible [9]. At the given frequency, the dimensions of the on-chip antenna for chip-to-chip communications can be comparable to the device dimensions and does not incur a large area penalty. However, the wireless interconnects suffer from large path loss and channel interferences.

In [5] by Yu et al. in 2016, a sub-THz dielectric interconnect channel is proposed and implemented as depicted in Fig. 1.2. The dielectric waveguide structure is made of high resistivity (HR) silicon because of its low loss of 0.1 dB/m at 200 GHz. Two configurations of dielectric interconnect are proposed and implemented [5]. In the first structure, the signal is excited through a coplanar waveguide (CPW) and tapered to an MSL. The signal from MSL then feeds a patch antenna. The waves radiated by the patch antenna couple to the HR silicon DWG propagating at the sub-THz wavelength. At the other end of DWG, waves are collected by another patch antenna. The bending loss at the DWG deteriorates the performance of the proposed sub-THz interconnect channel. Moreover, the limited bandwidth of the patch antenna limits the transmission bandwidth of the fabricated interconnect. The second configuration uses a near-field excitation scheme. In this approach, a tapered DWG and a tapered MSL are overlapped with each other. Hence the quasi-TEM mode of MSL is transitioned to the first order mode of the dielectric interconnect channel. The measured minimum insertion loss (IL) for the interconnect with far-field transitions is 8.4 dB with a 3-dB bandwidth of 12.6 GHz, while the near-field configuration has 4.0 dB IL with 3-dB bandwidth of 59 GHz [5].

Fig. 1.2. Sub-THz interconnect using the advantages of both optical and electrical interconnects  $[5] \odot [2016]$  IEEE.

Fig. 1.3. Far field transition of MSL-to-DWG [5] © [2016] IEEE.

Fig. 1.4. a) Top view of sub-THz interconnect using near-field transition, b) side view of the dielectric channel [5]  $\odot$  [2016] IEEE.

## 1.3.3. Optical interconnects

#### 1. Introduction

Due to the inherent low loss, high bandwidth, low latency, and low mutual interference of optical waveguides, researchers have investigated optical interconnects for the implementation of low loss

and high-speed interconnections and substituting conventional electrical interconnects. Additionally, optical links have the ability to send multiple wavelengths in a single waveguide using wavelength division multiplexing (WDM) which further increases the data transmission bandwidth. However, the implementation of optical interconnects requires the electrical-to-optical and optical-to-electrical conversion which increases the total energy consumption per bit of transmitted data (Energy per bit (EPB)). Silicon photonics is a promising optical interconnect solution due to the advantage of using the industrial resources in the electronics industry and compatibility with CMOS process. Fig. 1.5 depicts the diagram of an optical link system which consists of four primary optical elements: laser, an optical modulator, waveguide, and an optical detector. In addition to the required EPB of an optical interconnect, the integration of a laser with the CMOS process is another challenge.

Fig. 1.5. An optical interconnect system.

#### 2. Photonic and electronic circuit integration techniques

The implementation of an optical interconnection system as depicted in Fig. 1.5, requires multiple functions such as light generation, modulation, and detection. These functionalities can only be performed using different materials, which must be combined using either monolithic or hybrid integration. In monolithic integration, different functionalities are all fabricated on the same wafer substrate. While in the case of hybrid integration, different devices are fabricated on separate substrates and then mechanically integrated to make the final system.

Due to its compactness and compatibility with large scale integration (LSIs) chips, Silicon Photonics is believed to be the most suitable technology for the integration of electronic and photonic circuits [10]. Fig. 1.6 depicts three types of silicon photonic and electronics integration. In front-end integration, the electronic and photonic circuits are integrated near the surface of a silicon substrate, while in back-end integration the photonic circuit is integrated on the wiring layer. In the case of flip-chip bonding, electronics, and photonic chips are fabricated separately and then stacked by the flip-chip bonding technique [10]. The front-end and back-end techniques are monolithic integration method, and the flip-chip techniques is a hybrid integration method.

Fig. 1.6. Schematic cross sections of integration between photonics and electronics [10].

Monolithic integration provides higher speed and lower cost than hybrid integration. However, it requires very strict CMOS compatibilities for the design, fabrication, and test processes. On the other hand, hybrid integration provides the opportunity to integrate the most suitable technology for photonics and electronics circuits and is the most practical choice for implementation of optical interconnects by photonic and electronic integration [10].

In [11] by Doany et al., a highly integrated module-to-module board-level optical interconnect is demonstrated (see Fig. 1.7). The electrical signal in converted to an optical signal using a silicon-based chip. The optical signal is then transmitted to the polymer waveguides at the motherboard using an optical lens array. The polymer waveguides on the PCB have a 62.5 µm pitch. There are 24 transmitter, receiver, and waveguide channels on the board each operating at 15 Gbps which provide a bandwidth density of 240 Gbps/mm [11].

Fig. 1.7. Schematic of the Terabus architecture with polymer waveguide at board level [11]  $\bigcirc$  [2012] IEEE.

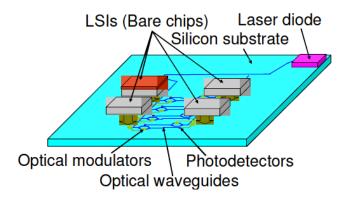

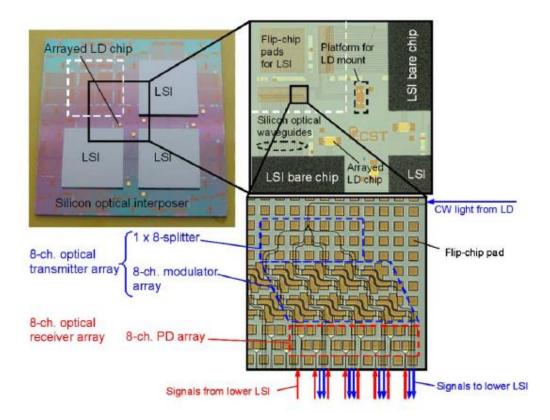

In [12] by Urino et al., a high density optical interconnect using silicon photonics is implemented using a combination of monolithic and hybrid integration techniques. The optical modulators, waveguides, and photodetector (PD) are monolithically integrated on a single silicon substrate (depicted in Fig. 1.8). LSI bare chips and a laser diode (LD) are hybridly integrated on the silicon substrate using flip-chip bonding. The optical interconnection replaces the conventional electronic wires on a printed circuit board (PCB), and the silicon substrate is called the "Silicon interposer" [12]. In this case, since the entire optical link (i.e., array of optical sources, interconnects, and receivers) is implemented, it is more beneficial to describe the data transmission per unit area of the chip which is equal to 3.5 Tbps/cm<sup>2</sup>. Fig. 1.9 shows another implementation of optical interconnection using a silicon interposer [10]. The results show that the silicon interposer is capable of 2.1 Tbps bandwidth of optical interconnection [10].

Fig. 1.8. A photonics-electronics convergence platform for inter-chip interconnects using silicon interposer [12].

Fig. 1.9. Silicon interposer as the photonics—electronics convergence system for inter-chip interconnects [10].

Table 1.1 summarizes the data transmission density of the three different interconnect solutions discussed. The first type belongs to a single layer differential stripline realized on the motherboard for implementation of chip-to-chip electrical interconnect [6 and 7]. The second type correspond to the implementation of optical interconnects using polymer waveguides [11], and the last type achieves high data transmission density of optical interconnect implementation using a silicon interposer. All of the compared technologies consist of single layer interconnect boards.

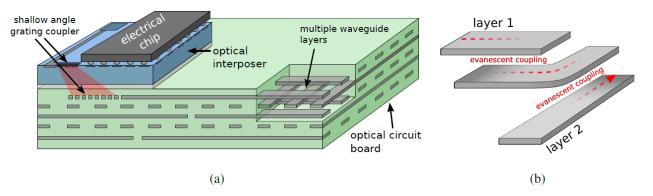

In [13] by Michaels and Yablonovitch, a multilayer optical communication fabric similar to modern electrical circuit boards is proposed. The structure consists of a passive optical circuit board, a silicon photonic optical interposer, and an electrical chip as depicted in Fig. 1.10(a). Unlike the configurations introduced in [6] and [12], the optical signal is transmitted through the passive optical board and not the silicon interposer. Each electrical chip is flip-chip bonded to a silicon photonic optical interposer which handles electrical-to-optical (E/O) and optical-to-electrical (O/E) conversion for high-bandwidth optical signals. Light couples vertically between

the optical interposer and the passive optical circuit board using inverse designed grating couplers. While the light propagating in the optical circuit board evanescently couples between layers as shown in Fig. 1.10(b) [13].

Table 1.1 Comparison of different interconnect solutions

| Ref          | Affiliation (year)     | Technology                                                          | Data<br>transmission<br>density |

|--------------|------------------------|---------------------------------------------------------------------|---------------------------------|

| [6 and 7]    | Kuwahara et al. (2015) | Single layer differential stripline on motherboard                  | 16 Gbps/mm                      |

| [11]         | Doany et al. (2012)    | Optical interconnects with polymer waveguide at board level         | 240 Gbps/mm                     |

| [12]         | Urino et al. (2011)    | Chip-to-chip interconnection using a silicon interposer             | 3.5 Tbps/cm <sup>2</sup>        |

| This<br>work | Banan et al.(2016)     | Electrical-optical chip-to-chip interconnection using metal stripes | 1 Tbps/mm                       |

Fig. 1.10. a) Diagram of multilayer optical circuit board including multiple layers of  $Si_3N_4$  waveguides, an optical interposer, and an electrical chip, b) diagram of evanescent interlayer coupling: a waveguide in an intermediate runs parallel to layer 1, coupling light evanescently, and then bends such that it runs parallel to layer 2 [13]. © [2016] IEEE.

## 1.3.4. Conclusion

This chapter discussed the concepts of electrical and optical interconnects. First, different types of electrical interconnects were introduced, and the limitations of each approach were explained. Then, pros and cons of optical interconnect as well as their implementation challenges were discussed. Moreover, using different examples of optical interconnect implementations, the evolution of optical interconnect was explained. The next chapter discusses plasmonics as another technology to consider for implementation of high bandwidth and low loss interconnects.

## 2. Background

## 2.1. Introduction

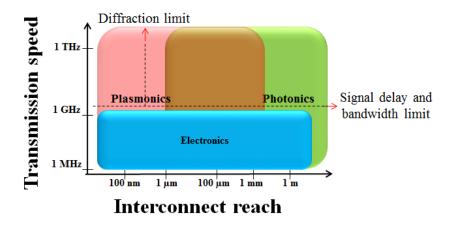

As described in the previous chapter, the ever-increasing demand for fast data transmission and processing has driven a continuous progress towards smaller, faster, and more efficient electronic chips. This trend has created a bottleneck for chip-to-chip interconnects. Optical interconnects, with their large data carrying capacity may offer new solutions for resolving the power dissipation and signal delay issues of electronics [14]. However, the size of photonic devices is limited by the diffraction law to about half a wavelength of light which is at least one or two orders of magnitude larger than their electronic counterparts. Therefore, there is a size mismatch between nanoelectronics and dielectric photonic components, making the integration of these technologies challenging. On the other hand, plasmonic structures adopt different shapes and sizes from nanoparticles to stripe and slab waveguides. This feature enables the routing and manipulation of light at different technology feature sizes. Fig. 2.1 shows the operating speeds and critical dimensions of different chip-scale device technologies. As illustrated, electronics cover feature sizes from nanometers to several meters, but their operating speed can only go up to few tens of gigahertz. The signal delay as well as bandwidth limit the reach of electrical waveguides (e.g., coaxial cables). The former is related to the signal propagation speed which is limited by the permittivity of the dielectric material used in the waveguide. The latter is limited by conductor loss in which propagation loss increases by increasing frequency or length. Therefore, photonics seems to be an appealing technology for applications requiring high operating speeds or long distances (up to several thousand kilometers) reach. Optical waveguides inherently offer lower loss and signal delay mainly due to the different waveguide material and propagation mechanism. However, as mentioned before, optical waveguide feature size hits a limit due to the diffraction law. Plasmonics

can break this limit, and provide access to electromagnetic wave confinement at nanometer scales with the same operating speed as photonics. Though, due to the interaction of EM waves with lossy metal, the propagation length of the plasmonic structures ranges from few microns to several centimeters depending on the geometry and material properties.

Fig. 2.1. Operating speeds and critical dimensions of various chip-scale device technologies.

In this chapter, first, fundamentals of plasmonics and its excitation methods are briefly reviewed. Then, the metal slab/stripe waveguides are discussed in more details. This thesis mainly focuses on this structure, since it provides propagation lengths of up to several millimeters and even centimeters, which is desired for the target application of chip-to-chip communication. Finally, this chapter presents a review of few previous works on this topic.

## 2.1.1. Surface plasmon polaritons (SPPs)

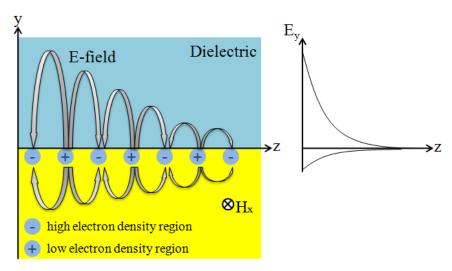

It is mathematically proven that the interface between two semi-infinite materials with positive and negative dielectric constants guides transverse magnetic (TM) surface waves. Since the dielectric constant of many metals is negative near optical wavelengths, the metal-dielectric interface at optical wavelengths can also propagate TM surface waves. These waves are electromagnetic excitation of surface plasmons (surface plasma oscillations comprised of conduction electrons in the metal) which are called surface plasmon polaritons (SPPs). The metallic interconnects that support SPPs are called plasmonic waveguides [15 and 16]. Fig. 2.2 shows the SPP propagating in the z-axis along the interface of a semi-infinite metal and a semi-

#### Background

infinite dielectric. The SPP field is mostly confined to the metal-dielectric interface with exponential decay into both media at the interface. Due to high confinement to the metal surface, SPP is very sensitive to surface irregularities and therefore has been used for surface analysis applications [17].

Fig. 2.2. SPP propagation along a metal-dielectric interface.

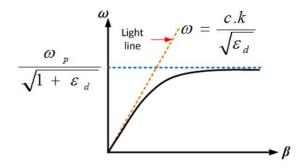

The dispersion relation of the SPP mode propagating at the metal-dielectric interface with relative dielectric permittivity of  $\varepsilon_d$  and  $\varepsilon_m$  is

$$\beta = k_0 \sqrt{\frac{\varepsilon_m \,\varepsilon_d}{\varepsilon_m + \varepsilon_d}} \tag{1}$$

In this equation,  $\beta$  (radians/meter) is the propagation constant in z direction, and  $k_0$  (radians/meter) is the free space wave number. In the optical wavelength range, the dielectric permittivity of a loss-less metal can be defined using the Drude model

$$\varepsilon_m = 1 - \frac{\omega_p^2}{\omega^2} \tag{2}$$

where  $\omega_p$  is the plasma angular frequency and  $\omega$  is the optical angular frequency of light. Using equations (1) and (2), the dispersion can be plotted as demonstrated in Fig. 2.3. The light line shown in the figure divides dispersion diagram into non-guiding (left) and guiding regions (right). The SPPs dispersion relation completely resides to the right of the light line which means the SPP mode has a greater momentum than a free photon at the same frequency. A crossing between dispersion curve and light line only occurs in the limit of  $\omega = 0$ ,  $\beta = 0$ . For small angular

frequencies, the dispersion diagram follows the light line, however, as the angular frequency reaches  $\omega_{sp} = \frac{\omega_p}{\sqrt{1+\varepsilon_d}}$ ,  $\beta$  approaches infinity (in other words, it becomes asymptotic with  $\omega = \omega_{sp}$  line). The angular frequency of  $\omega_{sp}$  is called surface plasmon polariton resonance, near which the wave slows down and the area of its field on the two sides of the interface becomes infinitesimal.

In reality, metals are lossy with complex dielectric permittivity ( $\varepsilon_m = \varepsilon_m' + j\varepsilon_m''$ ), hence, the propagation constant of SPP also includes an imaginary part. In this case, the propagation distance  $\delta_{SP}$  is the distance over which the power of SPP wave drops to 1/e of its initial magnitude and is given by

$$\delta_{SP} = \frac{c}{\omega} \left( \frac{\varepsilon_d + \bar{\varepsilon}_m}{\varepsilon_d \varepsilon_m'} \right)^{3/2} \frac{(\varepsilon_m')^2}{\bar{\varepsilon}_m'}$$

(3)

Fig. 2.3. Dispersion diagram of the metal-dielectric interface using a Drude model with no loss [18].

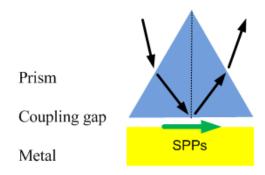

#### 2.1.2. SPPs excitation

SPPs cannot be excited by direct illumination of light, as energy and momentum conservation (i.e.,  $\omega_{incident} = \omega_{spp}$  and  $k_{incident} = k_{spp}$ ) cannot be fulfilled at the same time. Instead, in order to excite SPPs, a momentum transfer has to be established. Techniques to achieve this will be discussed in this section. It is possible to excite SPPs by means of a high energy electron beam hitting the metal surface. The electrons which hit the metal surface get scattered to different directions and provided that they have the correct momentum they excite the SPP modes.

The most common methods to excite SPPs are by the prism or grating coupling in which the mismatch between wave numbers of SPPs and light is compensated. Fig. 2.4 shows coupling light to SPPs using a prism. By placing the prism at a few hundred nanometer distance off the metal

surface, light enters the prism such that total internal reflection happens at the prism-air interface. The evanescent field at this interface then excites SPPs at the metal surface [18].

Fig. 2.4. Schematics of different schemes to excite SPP.

# 2.1.3. Long-range surface plasmon polaritons (LRSPPs)

Using a thin metal film embedded in a dielectric material, the attenuation of SPPs is reduced, mainly due to the small overlap of EM field with the lossy metal, resulting in longer propagation distances. Thus, this mode is called long-range SPPs (LRSPPs). The LRSPP modes of thin metal films are less confined than the single-interface SPP mode. This section discusses the LRSPPs properties of thin metal films of infinite and finite width.

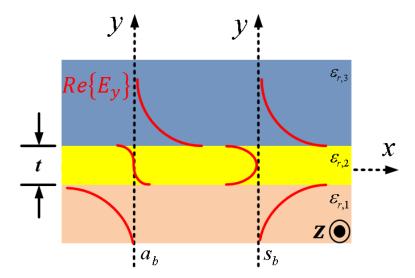

## 1. Metal slab with infinite width

The configuration consists of the metal film with a thickness of t embedded between two semi-infinite dielectrics, and infinite width which is called a metal slab (Fig. 2.5). In the case of symmetric metal slab, two bound single-interface SPPs propagate at the two metal—dielectric interfaces. By reducing the thickness of the metal slab, due to field tunneling through the metal, the two SPP modes couple together and form bound TM-polarized symmetrical and asymmetrical supermodes that exhibit dispersion with metal thickness. As the mode propagates in z direction (perpendicular to the plane), the transverse electric field component  $E_y$  of the first two modes of the structure, have symmetric and asymmetric distribution (relative to y axis) and are demonstrated as  $s_b$  and  $a_b$ , (the symmetric bound and asymmetric bound mode) where  $s_b$  mode is the LRSPP mode [19].

Fig. 2.5. Metal slab with a thickness of t bounded by semi-infinite dielectrics, supporting two bound SPP modes,  $s_b$  and  $a_b$ .

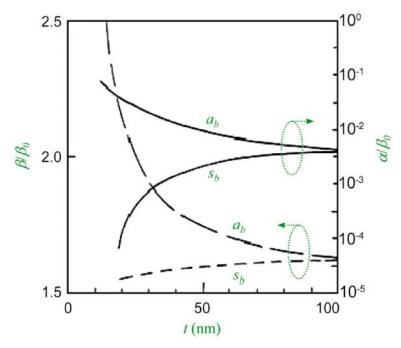

The  $H_x$  component of the modes has the same symmetry as  $E_y$  field, but the longitudinal electric field  $E_z$  has the opposite symmetry. As the thickness of metal slab decreases, the attenuation and effective index of the  $s_b$  mode and the mode confinement are also reduced. However, the  $a_b$  mode attenuation increases by reducing the thickness of metal slab. Fig. 2.6 shows the normalized propagation and attenuation constant of  $s_b$  and  $a_b$  modes of an asymmetric sliver (Ag) metal slab at the wavelength of  $\lambda_0 = 632.8 \, nm$  with a relative dielectric permittivity of  $\varepsilon_{r2} = (0.0657 - j4)^2$  for the metal and a relative dielectric permittivities of  $\varepsilon_{r1} = 1.5^2$  and  $\varepsilon_{r3} = 1.55^2$  of the surrounding dielectrics [19].

Fig. 2.6. Normalized phase and attenuation constant of  $s_b$  and  $a_b$  modes of an asymmetric Ag metal slab at  $\lambda_0=632.8~nm$  with  $\varepsilon_{r2}=(0.0657-j4)^2$ ,  $\varepsilon_{r1}=1.5^2$ , and  $\varepsilon_{r3}=1.55^2$  [19].

## 2. Metal stripe

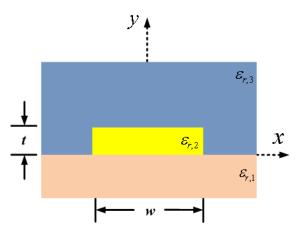

A metal slab with finite width creates the metal stripe structure. The finite width of metal stripe waveguide provides lateral confinement of the LRSPP mode. Consequently, the LRSPP mode of the metal stripe has lower attenuation than the LRSPP mode of the slab waveguide (as discussed in 1). Contrary to the metal slab configuration, the field distribution of metal stripe cannot be analytically derived from Maxwell's equations and must be calculated using numerical methods. Fig. 2.7 shows the cross section of a metal stripe waveguide in which the metal stripe with dielectric permittivity of  $\varepsilon_{r2}$  is bound by dielectrics with permittivity of  $\varepsilon_{r1}$  and  $\varepsilon_{r3}$ .

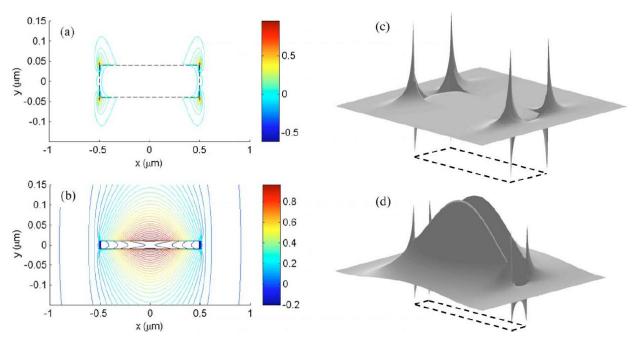

The modes of a metal stripe plasmonic waveguide were first calculated using Method of Line (MoL) by Berini [19]. The metal stripe has four fundamental modes which are defined by the distribution of  $E_y$  component as  $aa_b^0$ ,  $as_b^0$ ,  $sa_b^0$ , and  $ss_b^0$ . In this definition, a and s stand for asymmetric and symmetric mode. The first letter in each of  $aa_b^0$ ,  $as_b^0$ ,  $sa_b^0$ , and  $ss_b^0$  definitions refer to the symmetry or asymmetry of the mode in the horizontal direction (x), while the second letter defines the symmetry or asymmetry of the mode in the vertical direction (y). In the case of thin symmetric metal stripe, the  $ss_b^0$  mode is the fundamental LRSPP mode. Fig. 2.8 shows the

#### Background

contour and 3D plots of the real part of Poynting vector (Re  $\{S_z\}$ ) of  $\mathrm{ss}_b^0$  mode for Ag stripe with relative dielectric permittivity of  $\varepsilon_{r2}=-19-j0.53$  and width of  $w=1~\mu\mathrm{m}$ , surrounded by dielectrics of relative permittivity of  $\varepsilon_{r1}=\varepsilon_{r3}=4$  at four different waveguide thicknesses and wavelength of  $\lambda_0=633~nm$  [19].

Fig. 2.7. Cross section of the metal stripe waveguide with a thickness of *t*, and width of *w* bounded by semi-infinite dielectrics.

The finite-width embedded metal structure provides 2D mode confinement in the transverse plane and therefore can be exploited to implement passive optical components [16]. As the thickness of embedded metal decreases, the attenuation of SPP mode also decreases which leads to increased propagation length. Using long-range SPP waveguides (LRSPPWs), the propagation losses due to the metal absorption is reduced by minimizing the longitudinal component of the electric field in the metal [16].

### Background

Fig. 2.8. Contour and 3D plots of  $\text{Re}\{S_z\}$  of  $ss_b^0$  mode for  $w=1 \mu\text{m}$  (a) t=80 nm, (b) t=20 nm, (c) t=100 nm, (d) t=40 nm [19].

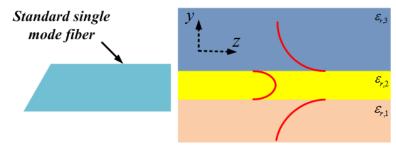

For sufficiently thin metal films, the mode field diameter of LRSPP becomes large enough to enable the excitation of LRSPPs to TM-polarized Gaussian-like beams in an edge coupling arrangement [19]. Fig. 2.9 shows a longitudinal cross-sectional view of edge coupling between fiber and the structure. Edge coupling can be achieved with a polarization-maintaining single mode fiber (PM-SMF) or tapered SMF as well as the polarization aligned mode of a SMF.

Burke et al. first proposed the edge coupling of LRSPPs [20]. Then Charbonneau et al. experimentally demonstrated the edge coupling to thin gold stripes embedded in silica glass [21]. Moreover, Nikolajsen et al. demonstrated LRSPP excitation with coupling loss of 0.5 dB, and 6–8 dB/cm propagation loss at telecom wavelengths along 10-nm-thin gold stripes embedded in polymer [22]. Fortunately, LRSPP edge-coupling to SM-fiber is achievable with more than 90% efficiency [19].

Fig. 2.9. Longitudinal cross-sectional view of edge coupling between the fiber and the structure input.

# 2.2. Plasmonic interconnects

Plasmonic provides a platform for the realization of low-cost and power efficient optical interconnect [23]. The metallic dielectric interface of SPP waveguides provides an efficient interface between electrical and optical signals, which can merge broadband optical links with intelligent electronic processing [23].

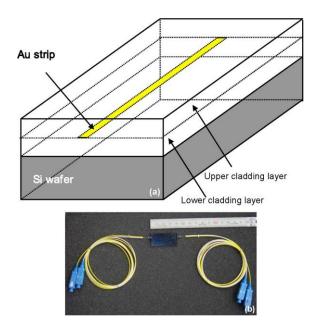

Polymer-based LRSPP devices are of great interest for implementation of plasmonic waveguide optical interconnects due to low absorption loss of polymer materials and their large thermo-optic coefficient (e.g., switching applications) [23]. In [24] by Ju et al., the LRSPP waveguide consists of a gold stripe of 14 nm thickness, 2.5 μm width, and 4 cm length embedded in a UV curable polymer. The LRSPP waveguide has 3 dB/cm propagation loss. The optical chip was diced, and the facets were pigtailed and polished with V-grooved single mode fibers. The authors experimentally demonstrated the transmission of 10 Gbps optical signal through a pigtailed 4-cm Au stripe LRSPP waveguide. In the 10 Gbps data transmission experiment, the device has 1.7 dB power penalty at 10<sup>-9</sup> BER and 2.2 dB power penalty at 10<sup>-12</sup> BER.

Fig. 2.10. (a) Schematic diagram of an Au stripe waveguide based on LRSPP and (b) the pigtailed LRSPP waveguide [24].

In [25] by Ju et al., a 4 cm LRSPP waveguide consisting of gold metal stripe embedded in a low loss polymer is fabricated, and the authors experimentally demonstrated 40 Gbps optical signal transmission through the device. In [26] by Ju et al., a flexible optical interconnect based on LRSPP waveguides is demonstrated. The interconnect length is 7 cm with 2.5 Gbps data rate. The LRSPP waveguide consists of an 8 nm thick silver stripe embedded in a free-standing multilayer polymer film composed of a 10 µm thick inner cladding (refractive index = 1.432), and a pair of 20 µm thick outer claddings (refractive index = 1.422). At a wavelength of 1310 nm, the insertion loss of the fabricated LRSPP waveguide does not dramatically change by bending the waveguide to a radius of 2 mm or twisting it to 90°. After transmission of a digital signal through the fabricated waveguide, an eye pattern of 2.5 Gbps is measured. The authors demonstrate the transmission of the high definition (HD) image captured by a mobile phone camera into the liquid crystal display (LCD) using LRSPP optical interconnect [26].

Fig. 2.11. The flexible plasmonic waveguide connecting transmitter and receiver ICs [26].

Fig. 2.12. The mobile phone camera records HD digital image then the image data is transmitted to the LCD using the LRSPP interconnect [26].

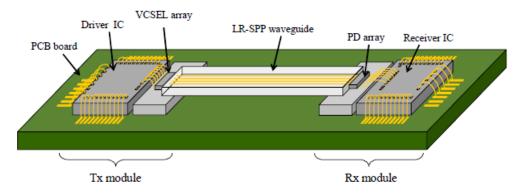

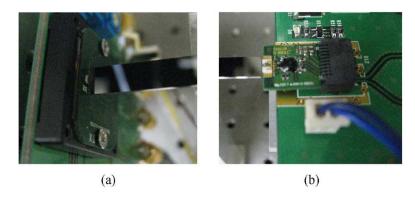

In [27] by Kim et al., an on-board chip-to-chip optical interconnect using LRSPP waveguide is implemented. As illustrated in Fig. 2.13, the structure consists of driver IC and a vertical-cavity-surface-emitting-laser (VCSEL) array chip as the optical transmitter module, a photodiode array chip as the receiver module, and a polymer-based LRSPP waveguide. Data transmission of four channels of 2.5 Gbps is accomplished at a wavelength of 1.3 µm. As the width of the metal stripe is reduced the propagation loss reduces, however, this comes at the cost of increased mode field diameter and consequently higher coupling loss between LRSPP and VCSEL modes.

Fig. 2.13. On-board chip-to-chip optical interconnect using polymer based Au LRSPP waveguide [27].

In [28] by Kalavrouziotis et al., the transmission of twelve WDM-enabled channels of 40 Gbps Non-Return-to-Zero (NRZ) modulated data through a 60 µm long straight dielectric-loaded SPP waveguides (DLSPPW) is demonstrated. DLSPPWs consist of a dielectric stripe deposited on top of a metallic film which demonstrates sub-wavelength confinement of SPPs with the typical propagation distance of 50 µm at 1550 nm wavelength [29]. The propagation length of DLSPPW can be significantly improved to mm-long SPP guiding using the long-range DLSPPWs (LR-DLSPPWs). In [29], the authors experimentally demonstrate the transmission of 10 Gbps on-off keying (OOK) modulated signal through the LR-DLSPPWs. Fig. 2.14 illustrates the cross-section of the fabricated waveguide which has a length of 300 µm.

Fig. 2.14. The layout of the LR-DLSPP waveguide structure [29].

To reduce the propagation loss of gold-based LRSPP waveguides at 1.3 µm wavelength, one can reduce the thickness of the metal layer. However, this comes at the cost of mode field diameter (MFD) increase and larger coupling loss to the SPP waveguide. In [23] due to the lower absorption

### Background