# Dual reference signal post-silicon reconfigurable clock distribution networks

## Atanu Chattopadhyay

Department of Electrical and Computer Engineering

McGill University, Montreal

## February 2009

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Doctor of Philosophy.

Copyright © Atanu Chattopadhyay, 2009

#### Abstract

This thesis investigates the use of averaging techniques in the development of clock distribution networks and an on-chip clock skew measurement circuit. Our flexible clock distribution network can be used in both single clock and multiple clock integrated circuit applications. The design moves away from clock trees, using a pair of reference clocks traveling in opposite directions to perform clock synchronization on a *daisy-chained* (serial) clock distribution line. By synchronizing each local clock edge to a position directly in between the forward and reverse reference clock edges, we demonstrate that sub-10 ps variance in clock arrival times can be achieved between local clocks. The design provides a scalable and simple-to-layout solution with multipoint skew compensation useful for large designs. The system provides the benefits of a closed-loop clock de-skewing solution by compensating for process, temperature and power supply variations, with the power savings of an open-loop solution at run-time.

Our technique allows routing switches to be included in the clock path, permitting the post-silicon re-sizing and re-shaping of clock domains. Localized clock switches or a complete chip-wide switch mesh can be used to re-route clock signals – a capability that is impossible without our daisy-chained clock network. We investigate a clock network that emphasizes flexibility and reconfigurability without sacrificing tolerance to clock skew. We show that this approach is realizable with transistor-level schematic and extracted circuit structures in TSMC's 180 nm standard process. We also develop a

modeling infrastructure from which we can create a variety of clock network configurations and synthesizable clock network controllers for arbitrary applications using ModelSim and Quartus II.

An on-chip clock skew management system to detect and potentially correct clock skew between selected points on an IC is also investigated. Our system, BICSS, aids in the debugging of timing errors that may be discovered during testing due to the added visibility of the on-chip clock signals and can repair otherwise defective dies using high-resolution delay lines in the clock path. BICSS is unique in its ability to detect, measure and compensate for clock skew using a single all-in-one solution.

## Abrégé

Cette thèse étudie une technique de moyennes pour créer un système de distribution d'horloge et un circuit pour mesurer le désalignement de phase d'horloge sur circuit intégré. Notre circuit de distribution d'horloge est polyvalent et peut être employé pour les systèmes avec une horloge simple ou des horloges multiples. La conception s'éloigne des circuits de distribution par arbres, utilisant une paire de signaux de référence voyageant en directions opposées pour corriger le déphasage de chaque horloge répartie linéairement sur la puce. En synchronisant chaque front ascendant d'horloge locale directement entre ceux des signaux de référence, on démontre que le déphasage peut-être réduit en dessous de 10 picosecondes. La conception permet une distribution d'horloges qui est simple à appliquer et extensible. Cette démarche corrige les variations de processus, d'alimentation et de température, fournissant la correction du désalignement de phase systématique de chaque tranche de la distribution d'horloge.

Notre technique permet l'introduction des commutateurs de cheminement pour commuter les trajets d'horloge et changer la grandeur et forme des domaines d'horloge après la fabrication d'un circuit intégré. Des commutateurs localisés ou un réseau de commutateur en maille qui couvre le circuit au complet peuvent être utilisés – deux possibilités qui sont impossibles sans notre réseau connecté en série. Notre recherche souligne la flexibilité et la reconfiguration dynamique d'un réseau d'horloge sans sacrifier l'alignement de phase des signaux d'horloges locaux. Nous prouvons que cette

approche est réalisable avec des conceptions niveau schémas et niveau circuitsextraites utilisant le processus de fabrication de 180 nanomètre de TSMC. Nous avons également conçu avec ModelSim et Quartus II un modèle pour étudier des diverses configurations de réseaux d'horloges et pour créer des contrôleurs réalisables.

Un système sur circuit intégré qui peut détecter, mesurer et corriger la différence de phase entre les horloges d'endroits présélectionnés dans le circuit est aussi conçu. Notre système, BICSS, peut réparer les puces autrement défectueuses utilisant des lignes à retard à haute résolution. BICSS peut aider à éliminer des erreurs de synchronisation qui peuvent être difficilement découvertes pendant l'essai grâce à la visibilité supplémentaire que le système permet.

## Acknowledgements

I would first like to thank my parents for helping me, supporting me and being there for me. I would also like to thank my sister and her kids for providing me with an easy and enjoyable excuse to get away from things in California.

I would next like to thank my supervisor Dr. Zeljko Zilic. He provided me insight and direction while giving me all the freedom I needed to explore my ideas as far as I could take them. I would also like to thank Dr. Frank Ferrie for teaching me the ins and outs of running a class.

Next, I would like to acknowledge the financial and material support of Altera Corporation, the Fonds québécois de la recherche sur la nature et les technologies (FQRNT), CMC Microsystems and McGill University.

I also appreciate the advice and comradery of all of the graduate students, past and present, in the department. Particularly, Marc Boulé, Henry Chan, Jean-Samuel Chenard, Nathaniel Azuelos, Bojan Mihajlovic and Mona Safi-Harb. I can't imagine how quiet things would have been without you guys around to talk to and brainstorm with.

Finally, I would like to thank all my friends: Mario, Peter, Nadia, Catherine, Vishal, all the Marks, Andras, Jordanna, Eric, Geoff and Neil. Time flies by so quickly, it is hard to fathom how long we have all been friends.

I feel lucky that I have had whatever I needed, whenever I needed it. I don't think

I could have come this far without a little something that each of you has provided.

## Table of contents

| Abstract                                           |      |

|----------------------------------------------------|------|

|                                                    |      |

| Abrégé                                             | iii  |

| Acknowledgements                                   | V    |

| Table of figures                                   | xi   |

| Table of tables                                    | xvii |

| Chapter 1: Introduction                            | 1    |

| 1.1. Problem description                           | 3    |

| 1.2. Thesis objectives                             | 5    |

| 1.3. Statement of original contributions           | 7    |

| 1.3.1. Single clock averaging network              | 7    |

| 1.3.2. Multiple clock reconfigurable clock network | 8    |

| 1.3.3. On-chip clock skew detection circuitry      | 9    |

| 1.3.4. Custom circuitry                            | 9    |

| 1.4. Thesis organization                           | 10   |

| Chapter 2: Background                              | 11   |

| 2.1. Introduction                                  | 11   |

| 2.2. Clock characteristics                         | 12   |

| 2.3. Clock uncertainty                             | 15   |

| 2.4. Clock networks                                | 20   |

| 2.4.1. Symmetric clock tree                        | 21   |

| 2.4.2. Asymmetric buffered clock trees             | 23   |

| 2.4.3. Clock mesh                                  | 24   |

| 2.4.4. Resonant clocking                           | 25   |

| 2.4.5. Standing and traveling wave network         | 26   |

| 2.4.6. Hybrid structures                           | 27   |

| 2.4.7. Serial clock distributions                      | 28 |

|--------------------------------------------------------|----|

| 2.4.8. Reconfigurable clocks networks                  | 30 |

| 2.5. Skew compensation                                 | 31 |

| 2.6. Clock power                                       | 34 |

| 2.7. Conclusion                                        | 38 |

|                                                        |    |

| Chapter 3: A dual reference signal averaging single    | 39 |

| clock distribution network                             | 39 |

| 3.1. Introduction                                      | 39 |

| 3.2. Implementation approach                           |    |

| 3.2.1. Synchronization                                 |    |

| 3.2.2. Calibration                                     |    |

| 3.2.3. Operation                                       | 45 |

| 3.3. Wire length savings                               | 46 |

| 3.4. Architecture variants                             | 49 |

| 3.4.1. Architecture with 2 <i>n</i> delay lines        | 50 |

| 3.4.2. Architecture with <i>n</i> +1 delay lines       | 51 |

| 3.4.3. Architecture with <i>n</i> delay lines          | 53 |

| 3.4.4. Hotspot tolerant architecture                   | 55 |

| 3.5 Clock jitter and skew.                             | 56 |

| 3.5.1. Jitter sources                                  | 57 |

| 3.5.2. Skew                                            | 58 |

| 3.5.3. Temperature variation                           | 62 |

| 3.5.4. Dynamic operation                               | 64 |

| 3.6. Controller requirements                           | 65 |

| 3.6.1 Synchronization time                             | 66 |

| 3.7. Simulation results                                | 70 |

| 3.8. Conclusion                                        | 74 |

| Chapter 4: Skew-tolerant reconfigurable clock networks | 77 |

| based on averaging                                     |    |

|                                                        |    |

| 4.1. Introduction                                      |    |

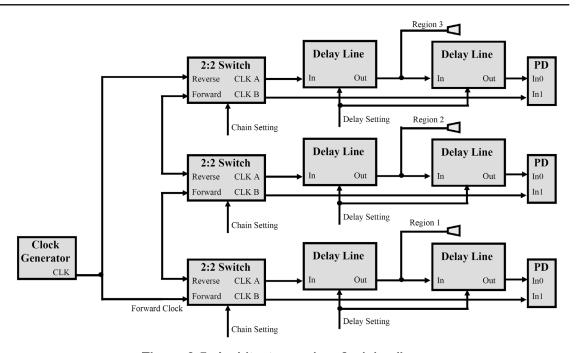

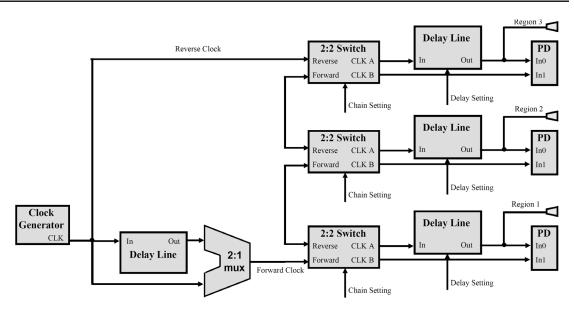

| 4.2. Multiple clock architectures                      |    |

| 4.2.1 Static clock network with multiple clocks        | 70 |

| 4.2.2 Locally-reconfigurable clock network                     | 81  |

|----------------------------------------------------------------|-----|

| 4.2.3. Globally-reconfigurable clock network                   | 82  |

| 4.3. Versatility of a programmable multiple clock mesh network |     |

| 4.4. Controller requirements                                   | 86  |

| 4.5. Single clock fixed methodology                            | 90  |

| 4.6. Reconfigurable methodology                                | 92  |

| 4.7. Simulation results                                        | 94  |

| 4.8. Conclusion                                                | 100 |

| Chapter 5: A built-in system for online clock skew             | 101 |

| debug and correction                                           | 101 |

| 5.1. Introduction                                              | 101 |

| 5.2. Background                                                | 102 |

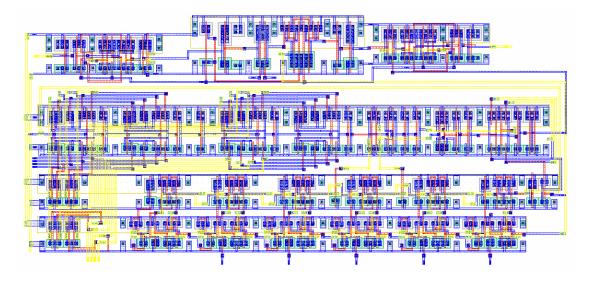

| 5.3. System architecture                                       | 107 |

| 5.4. Operating characteristics                                 | 112 |

| 5.5. Conclusion                                                | 117 |

| Chapter 6: System-level modelling                              | 121 |

| 6.1. Introduction                                              | 121 |

| 6.2. Implementation approach                                   | 122 |

| 6.3. Configuration memory requirements                         | 124 |

| 6.4 Synchronization controllers                                | 127 |

| 6.4.1 Single clock domain controller                           | 128 |

| 6.4.2 Reconfigurable clock domain controller                   | 132 |

| 6.4.3 Built-in clock skew system controller                    | 134 |

| 6.5 System models                                              | 137 |

| 6.5.1. Single clock model                                      | 138 |

| 6.5.2. Reconfigurable clock network model                      | 139 |

| 6.5.3. BICSS model                                             | 142 |

| 6.6 Operating behaviour of the systems                         | 143 |

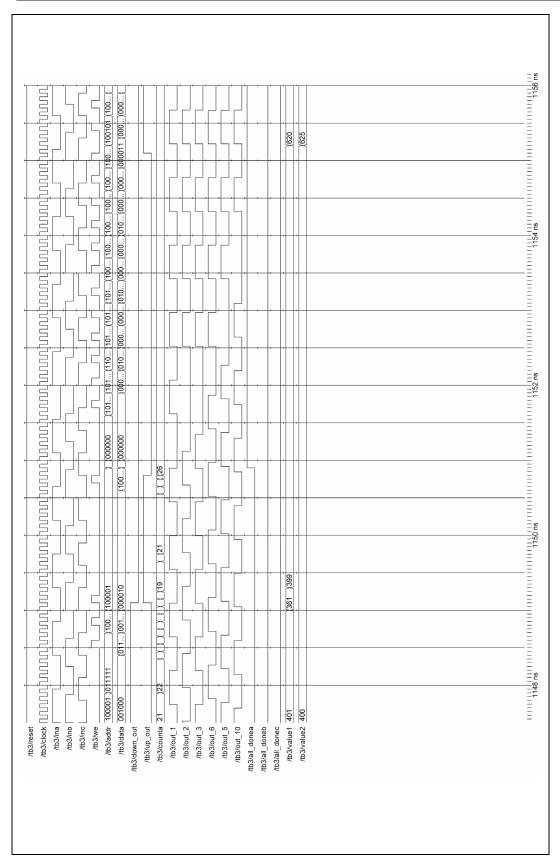

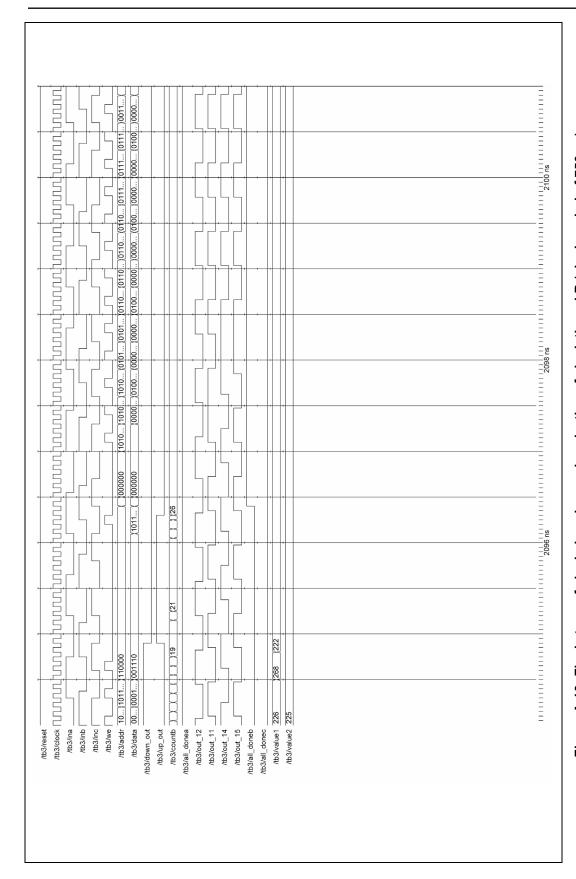

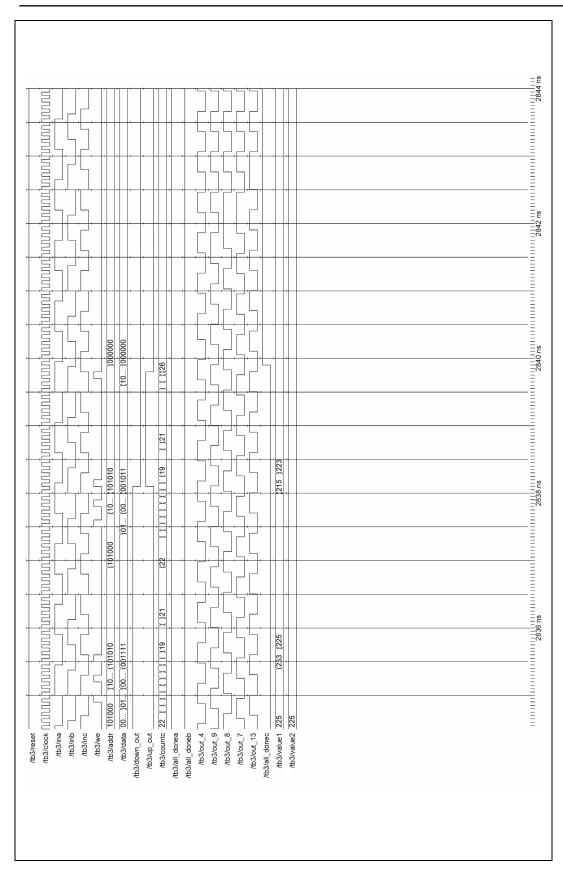

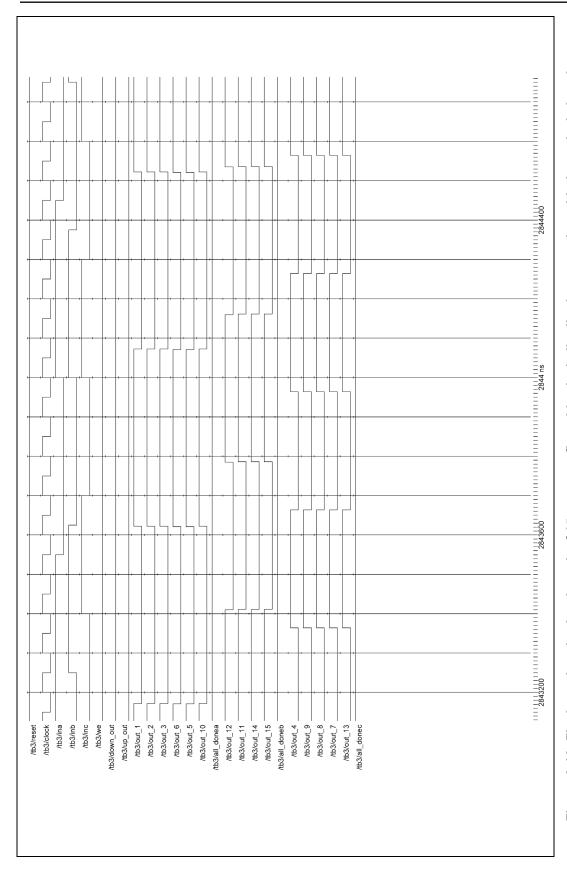

| 6.6.1 Single clock domain system                               | 144 |

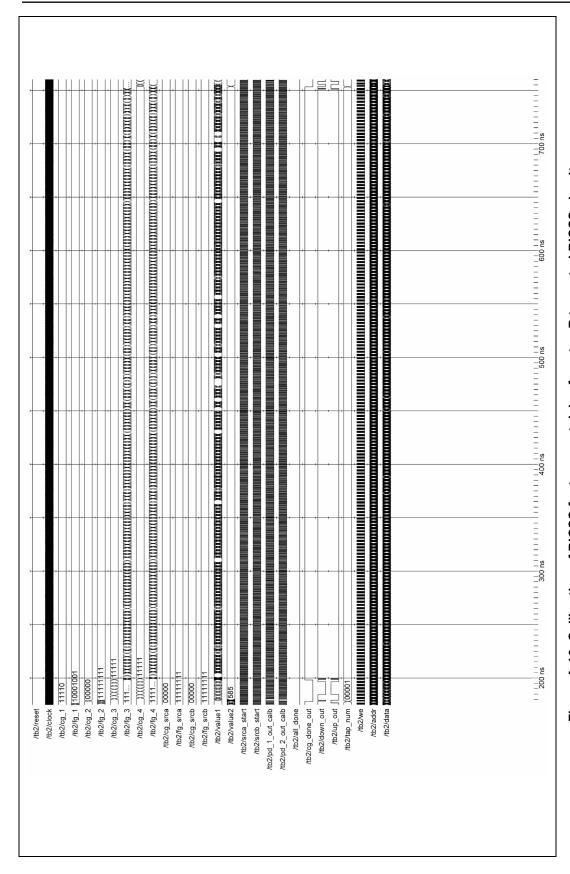

| 6.6.2. Reconfigurable clock domain system                      | 147 |

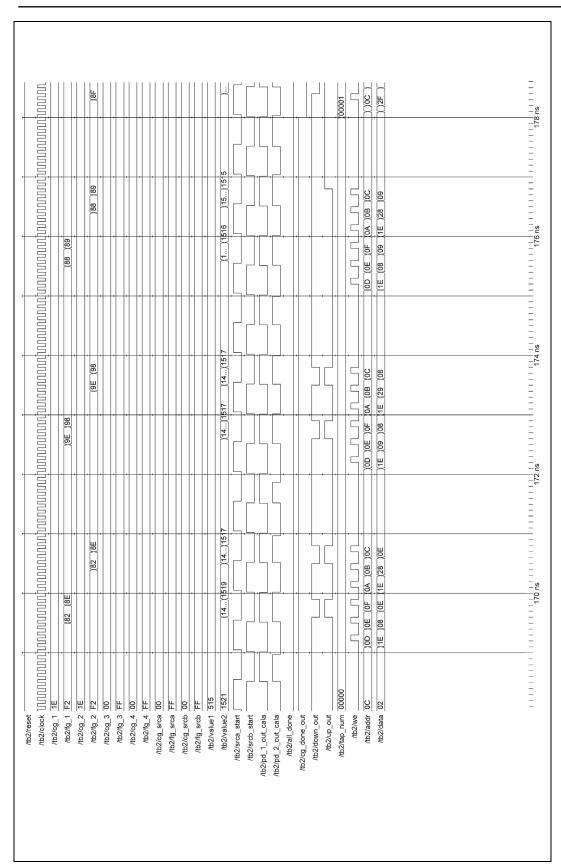

| 6.6.3. Built-in clock skew system                              | 149 |

| 6.6 Conclusion                                                 | 151 |

| Chapter 7: Core circuit components                                  | 153 |

|---------------------------------------------------------------------|-----|

| 7.1. Introduction                                                   | 153 |

| 7.2. Delay lines                                                    | 155 |

| 7.2.1 Coarse grain delay lines                                      | 156 |

| 7.2.2 Fine grain delay lines                                        | 158 |

| 7.2.3 Performance                                                   | 163 |

| 7.3. Clock switches                                                 | 167 |

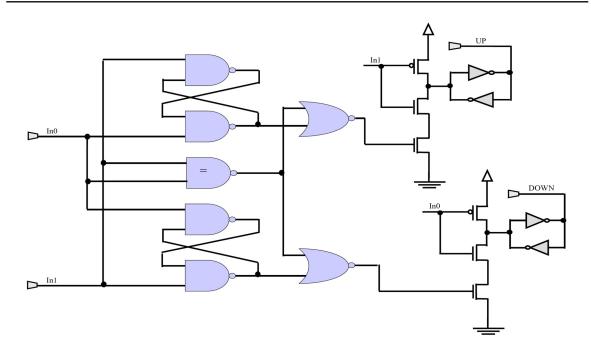

| 7.4. Phase detectors                                                | 170 |

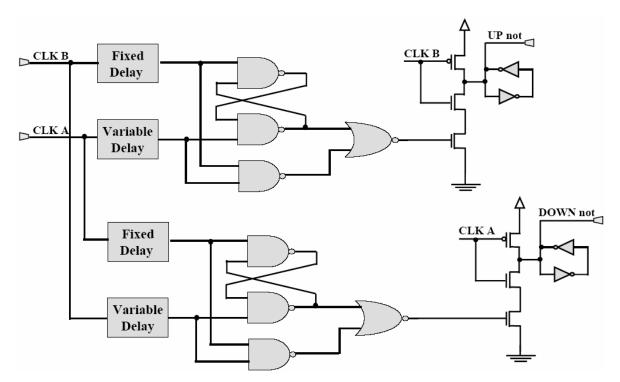

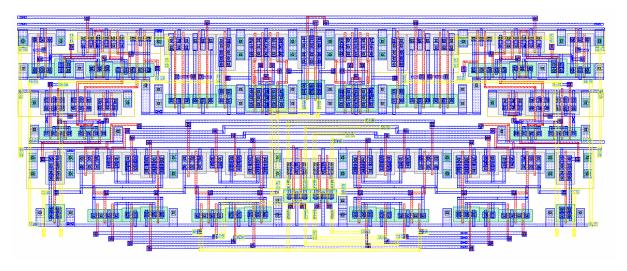

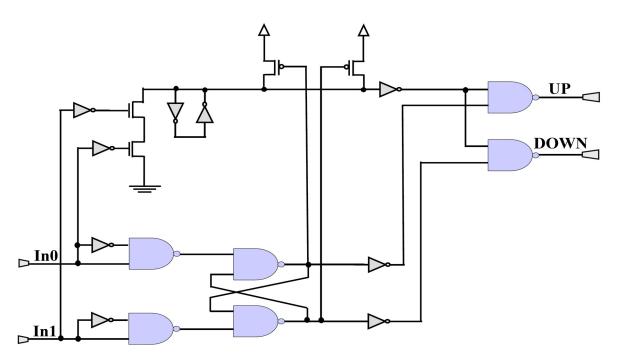

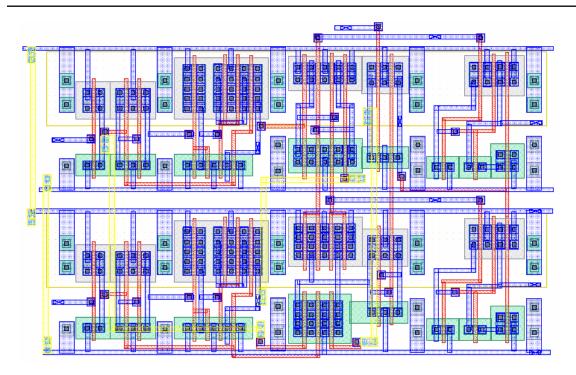

| 7.4.1 Fixed tolerance phase detector                                | 171 |

| 7.4.2 Variable-tolerance phase detector                             | 174 |

| 7.4.3 Modified phase detector for shared delay line implementations | 176 |

| Chapter 8: Conclusions and future work                              | 179 |

| 8.1. Summary                                                        | 179 |

| 8.1.1. Single clock averaging network                               | 181 |

| 8.1.2. Reconfigurable multiple clock averaging network              | 182 |

| 8.1.3. Built-in clock skew system                                   | 183 |

| 8.1.4. Circuit implementations                                      | 184 |

| 8.2. Future work                                                    | 185 |

| 8.2.1. On-chip clock networks                                       | 185 |

| 8.2.2. Automate system implementation                               | 186 |

| 8.2.3. Alternative applications                                     | 187 |

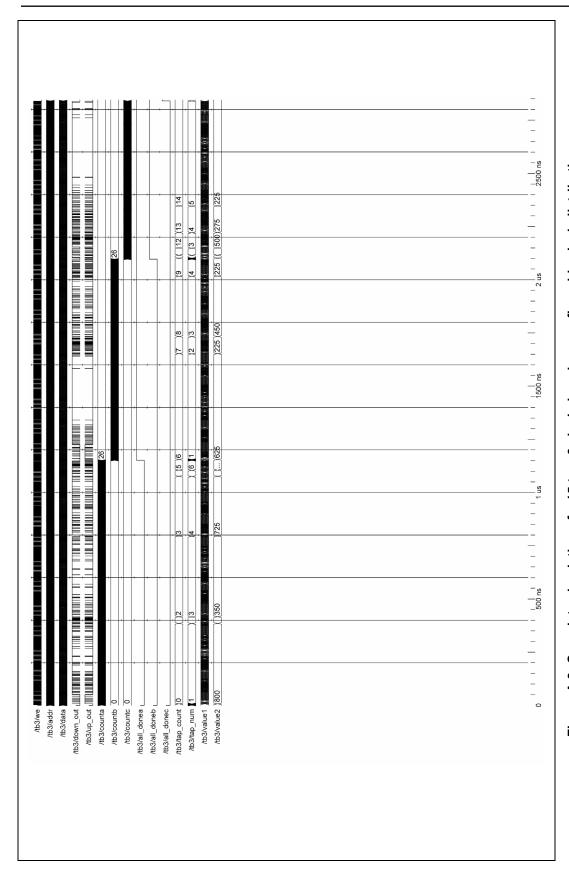

| Appendix A: System-wide simulations                                 | 189 |

| Appendix B: Selected circuit drawings with transistor sizes         | 211 |

| List of references                                                  | 219 |

# Table of figures

| Figure 2.1:  | Summary of relevant measurements                                 | 13 |

|--------------|------------------------------------------------------------------|----|

| igure 2.2:   | 3-register clock routing                                         | 16 |

| Figure 2.3:  | 2-level symmetric clock trees                                    | 22 |

| igure 2.4:   | Asymmetric buffered clock tree                                   | 24 |

| igure 2.5:   | Grover's linear clock distribution                               | 28 |

| Figure 2.6:  | Banu and Prodanov's bufferless approach                          | 30 |

| igure 2.7:   | Kapoor's skew-tolerant clock tree                                | 35 |

| igure 2.8:   | Lee's skew compensation scheme                                   | 36 |

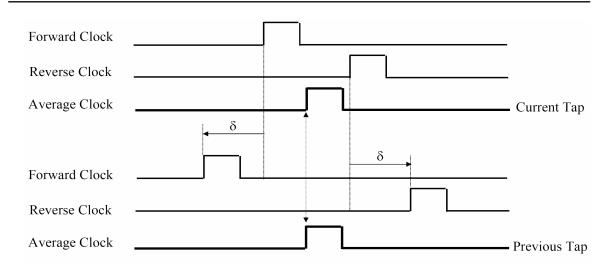

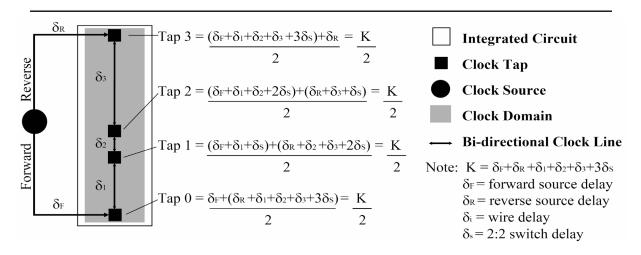

| Figure 3.1:  | Underlying concept of averaging                                  | 40 |

|              |                                                                  |    |

| Figure 3.2:  | Reference-based clocking for a single clock domain               | 43 |

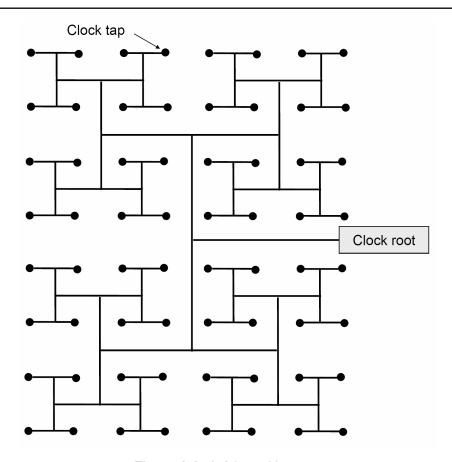

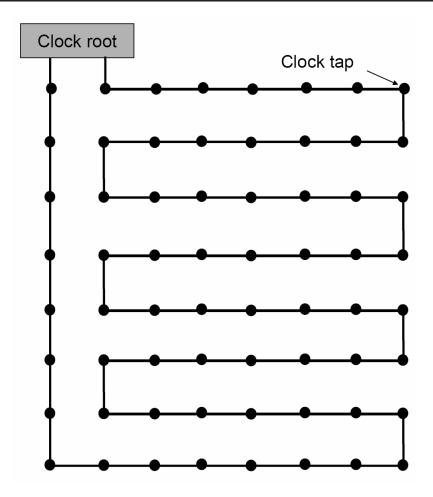

| Figure 3.3:  | A 64-tap H-tree                                                  | 47 |

| igure 3.4:   | A 64-tap reference based clock distribution                      | 48 |

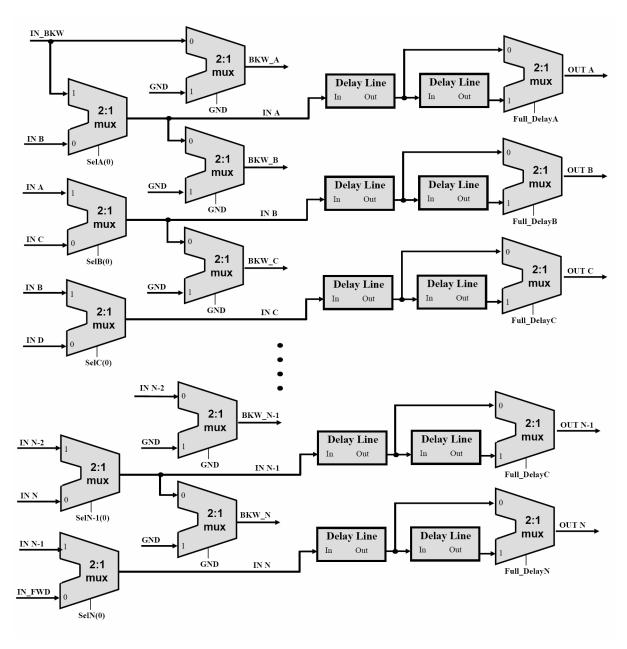

| igure 3.5:   | Architecture using 2n delay lines                                | 50 |

| igure 3.6:   | Architecture using <i>n+1</i> delay lines                        | 51 |

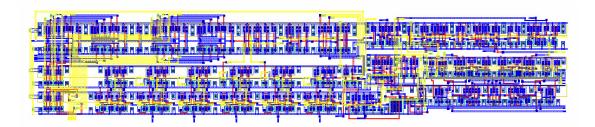

| igure 3.7:   | Circuit layout of <i>n+1</i> delay line tap                      | 52 |

| igure 3.8:   | Circuit layout of <i>n+1</i> delay line clock selector           | 52 |

| igure 3.9:   | Architecture using <i>n</i> delay lines                          | 54 |

| igure 3.10:  | Circuit layout of <i>n</i> delay line tap                        | 55 |

| igure 3.11:  | Dual reference line hot-spot tolerant configuration              | 56 |

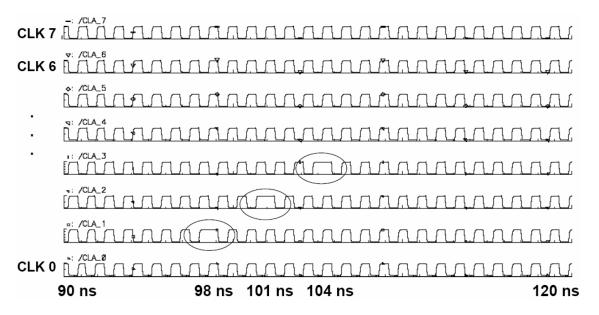

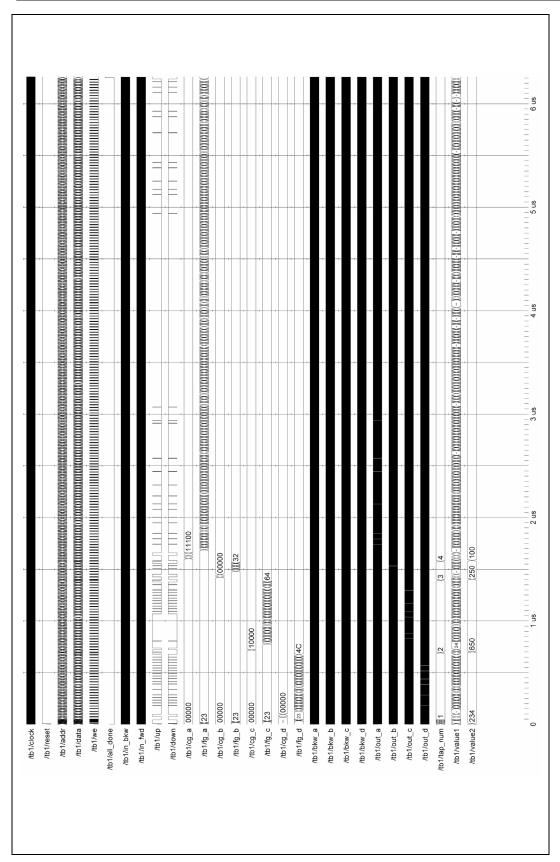

| igure 3.12:  | First 3 synchronization steps for an 8-tap CDN                   | 72 |

| Figure 3.13: | Calibration phase to align polarity of resulting clocks          | 72 |

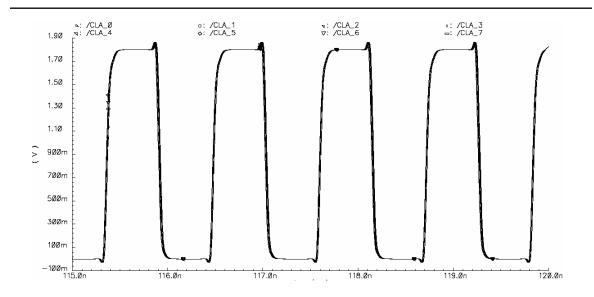

| Figure 3.14: | Resulting low-skew output clocks for an 8-tap system             | 73 |

| Figure 3.15: | Using pulses to align clocks in <i>n</i> delay line architecture | 74 |

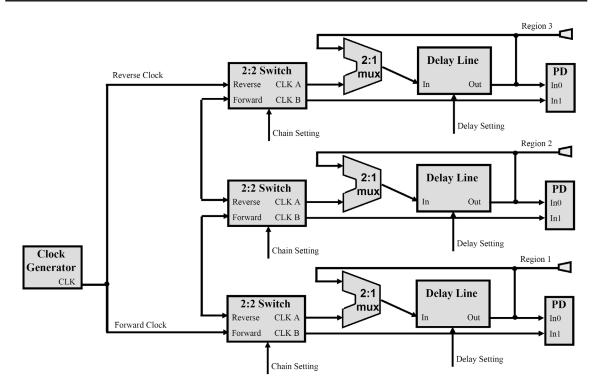

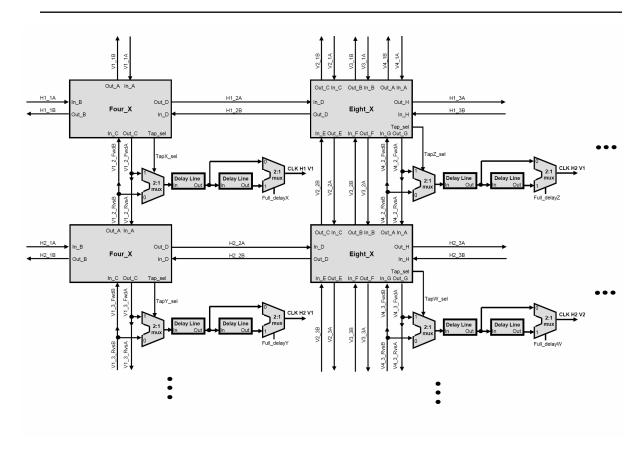

| Figure 4.1:  | A 3-clock domain static clocking solution                                             | 79  |

|--------------|---------------------------------------------------------------------------------------|-----|

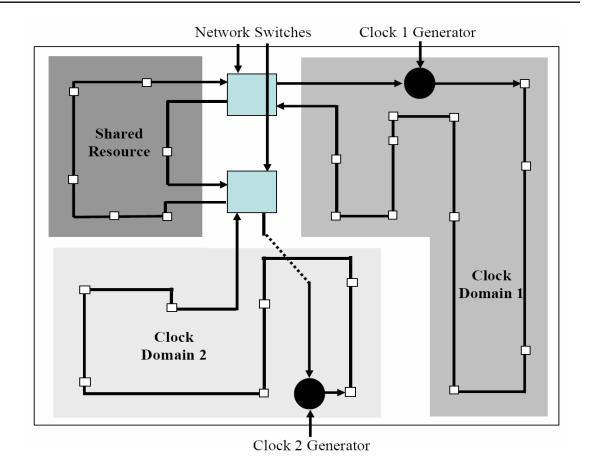

| Figure 4.2:  | Sharing a resource with reference-based clocking                                      | 81  |

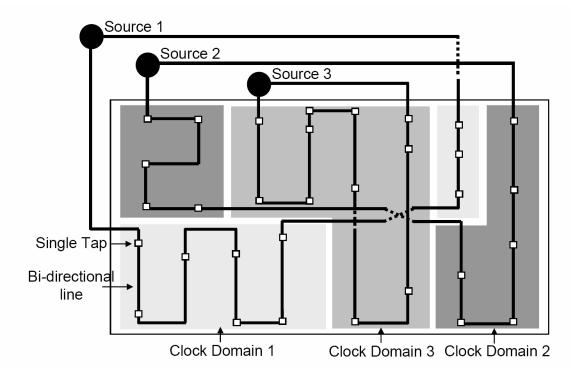

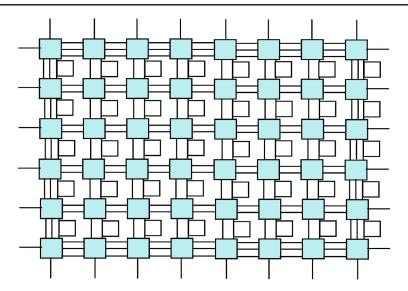

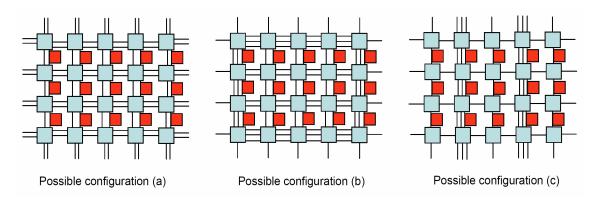

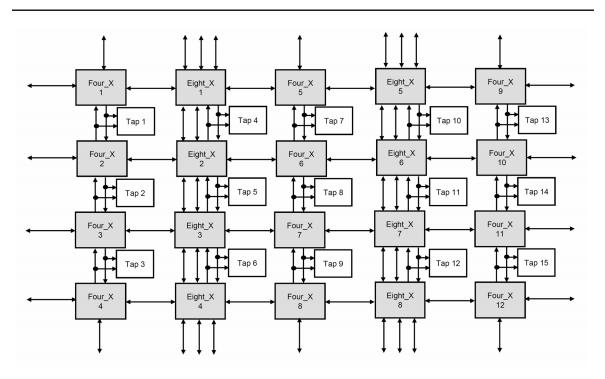

| Figure 4.3:  | A potential fully programmable clocking architecture                                  | 82  |

| Figure 4.4:  | 3 potential 15-tap clock distributions                                                | 83  |

| Figure 4.5:  | The mesh mapping problem                                                              | 87  |

| Figure 4.6:  | Mesh architecture incorporating express paths                                         | 89  |

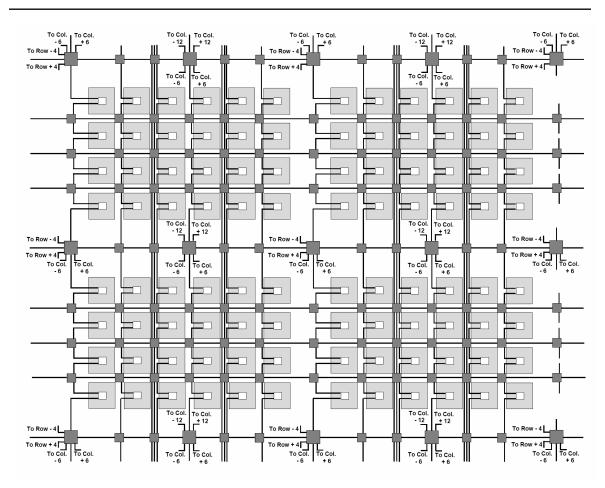

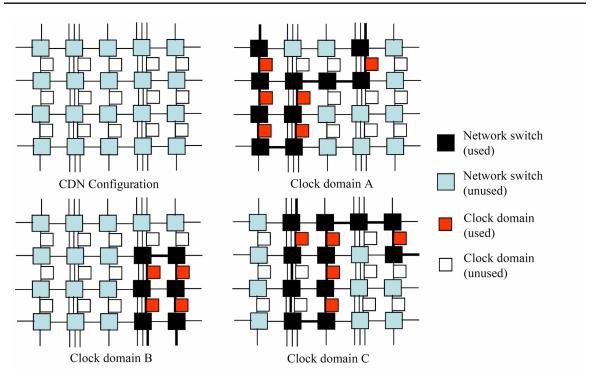

| Figure 4.7:  | Potential fully programmable clocking architectures                                   | 95  |

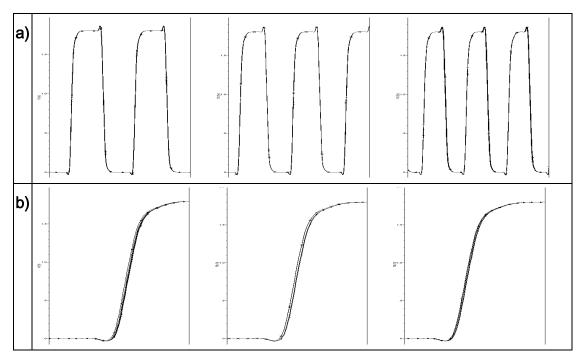

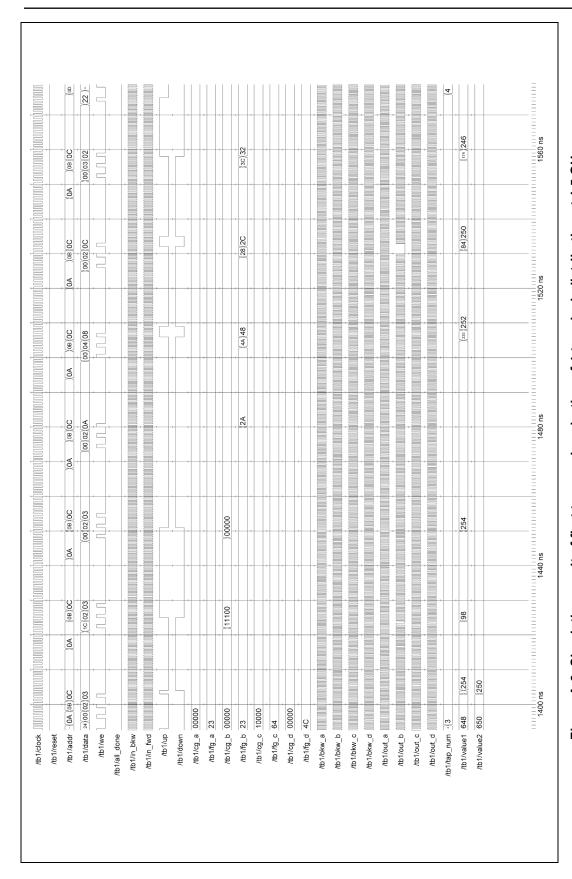

| Figure 4.8:  | Simulation of a 3-clock domain reconfigurable clock network                           | 96  |

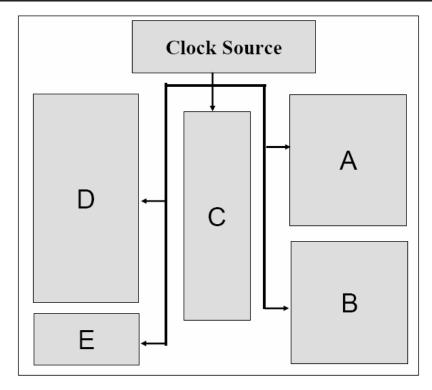

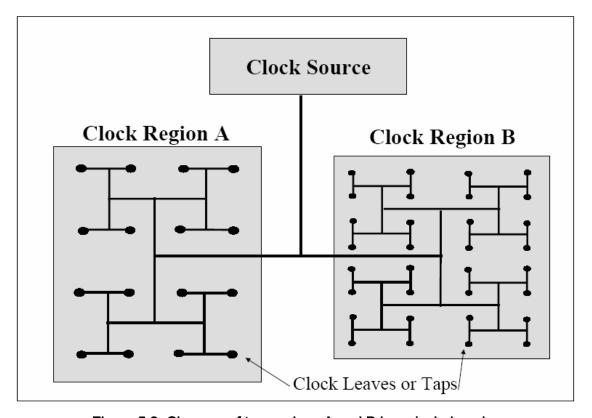

| Figure 5.1:  | Modular design of ICs with regions A-E in a given clock domain                        | 106 |

| Figure 5.2:  | Close up of two regions A and B in a clock domain                                     | 106 |

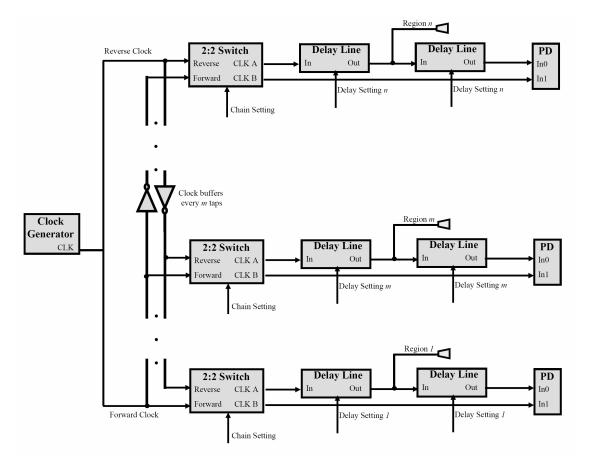

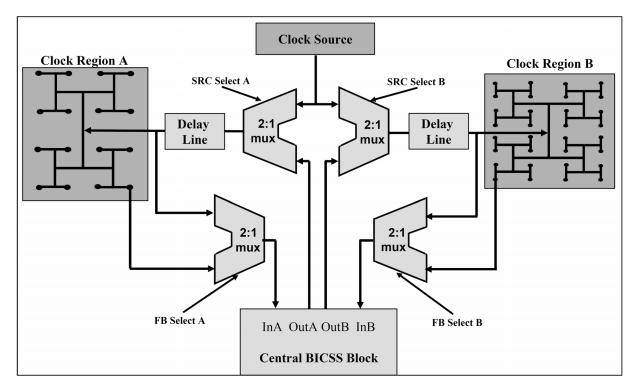

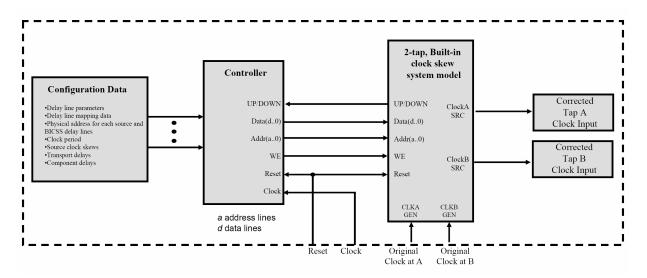

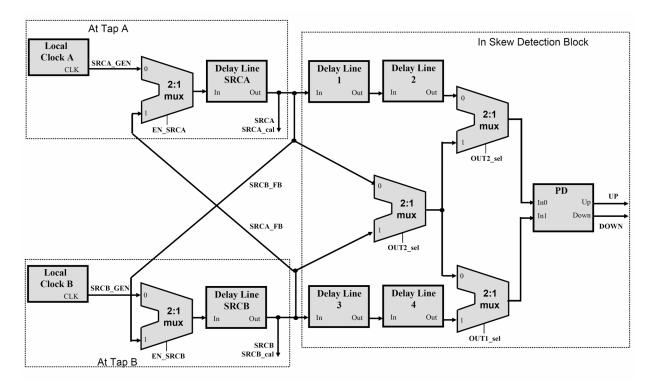

| Figure 5.3:  | The Built-in Clock Skew System (BICSS)                                                | 107 |

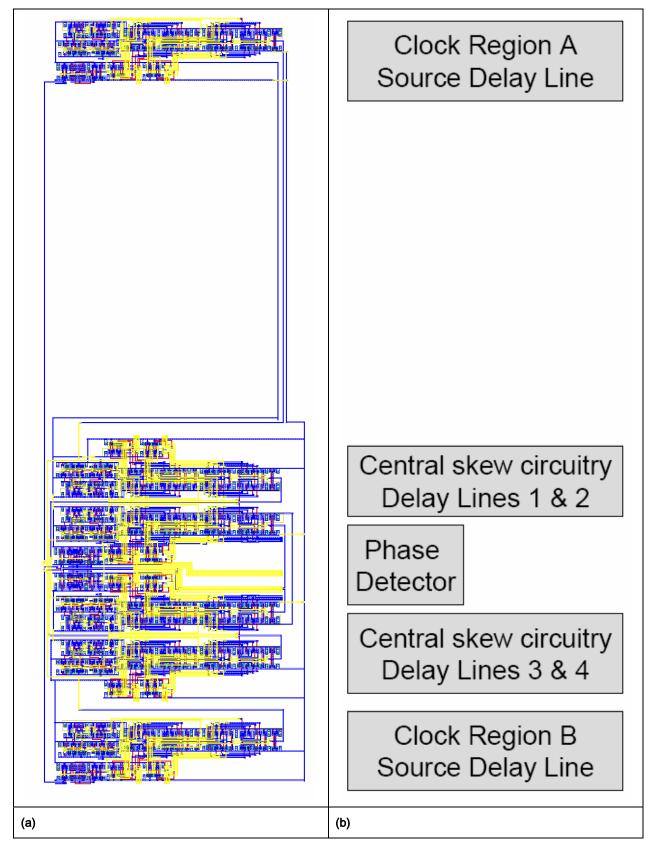

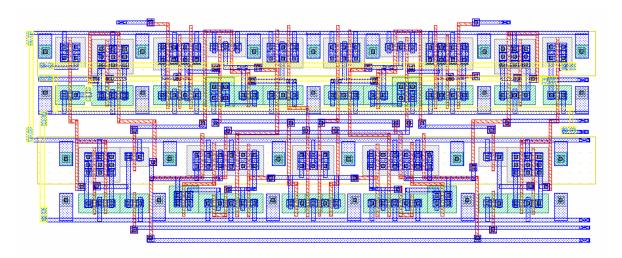

| Figure 5.4:  | Central BICSS circuitry                                                               | 108 |

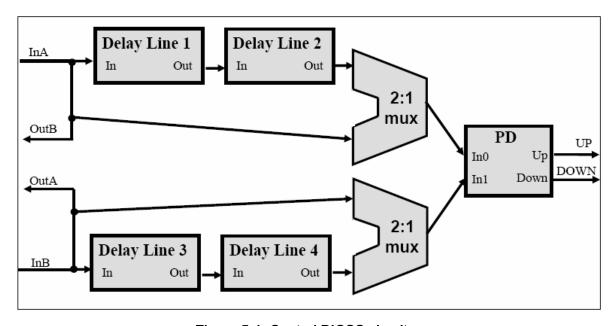

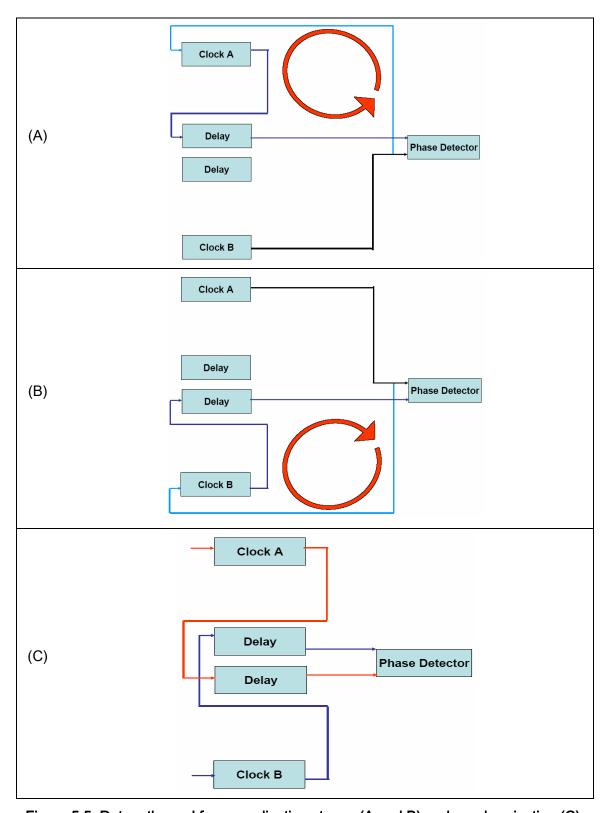

| Figure 5.5:  | Datapath used for normalization stages and synchronization                            | 111 |

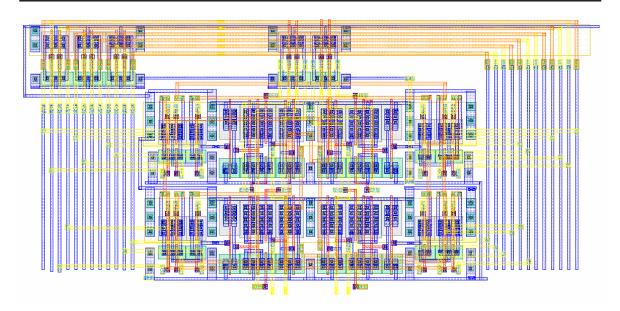

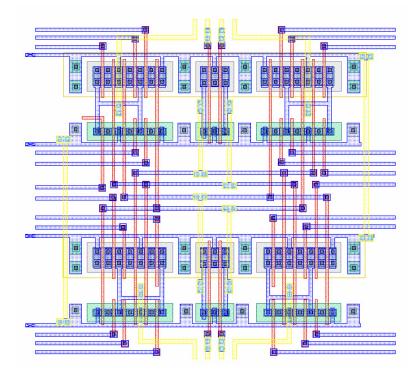

| Figure 5.6:  | The layout of a 2-clock region BICSS implementation                                   | 113 |

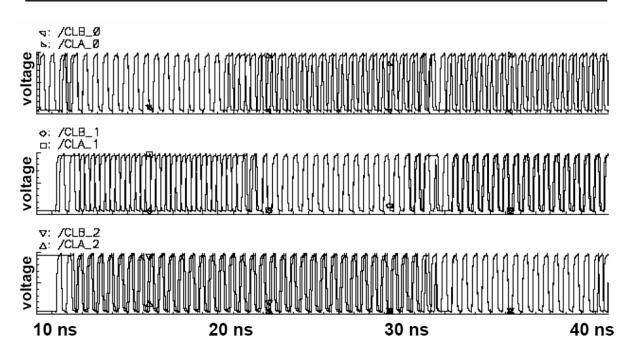

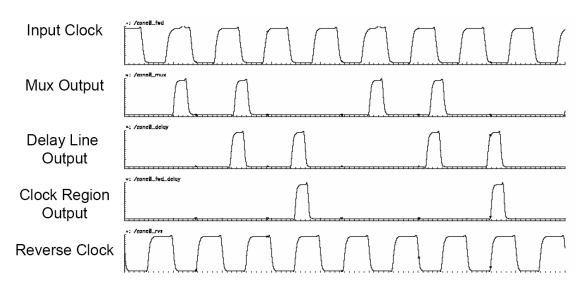

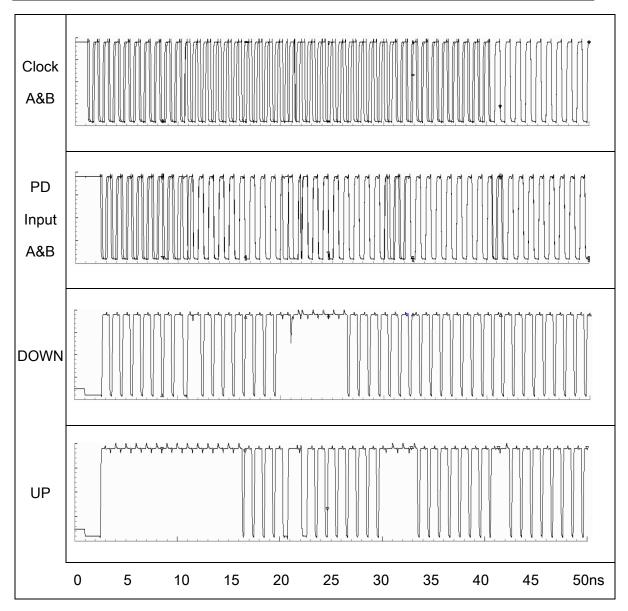

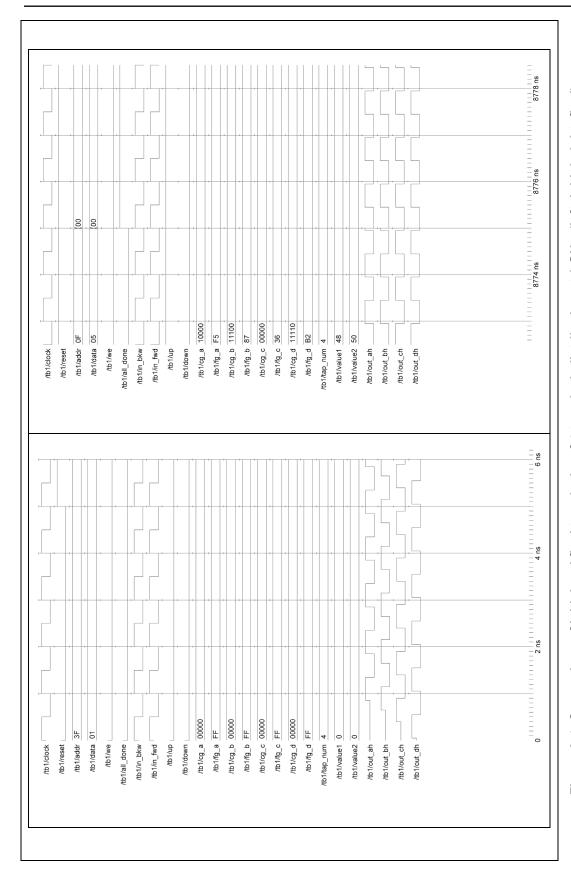

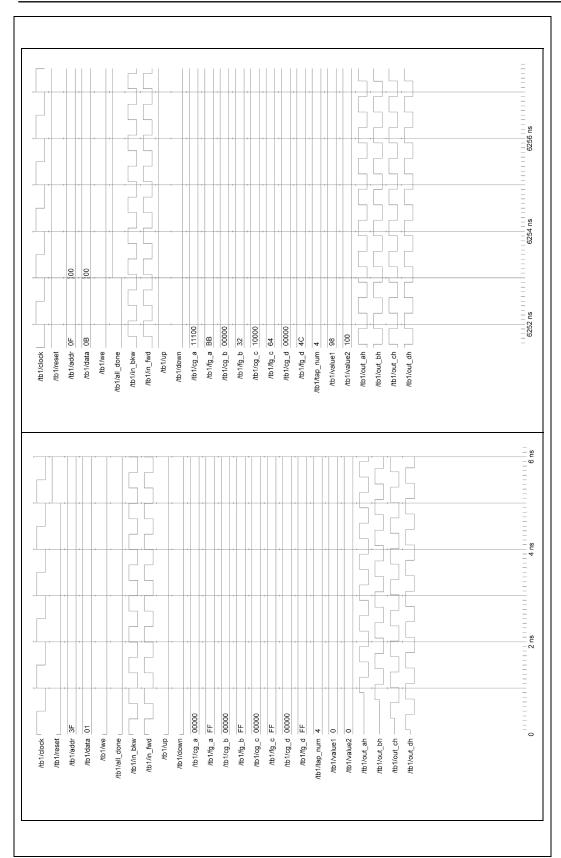

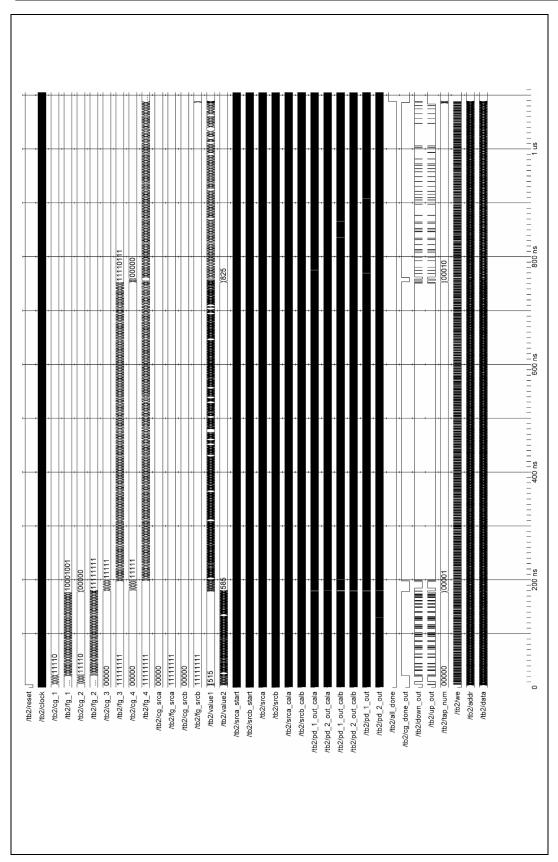

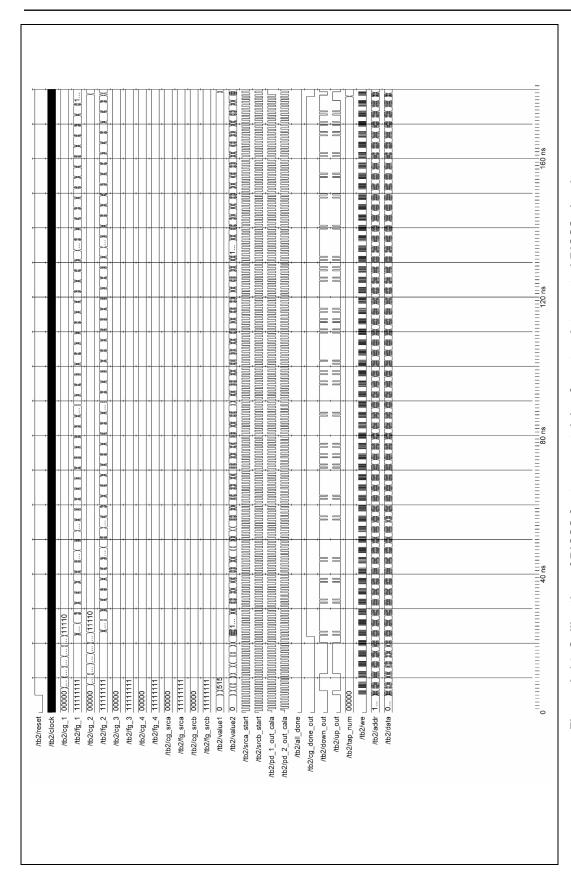

| Figure 5.7:  | Waveforms showing operation of the BICSS circuitry                                    | 116 |

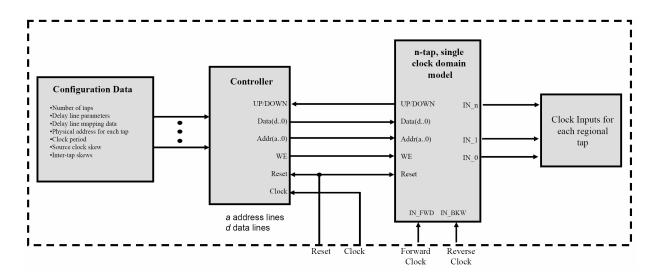

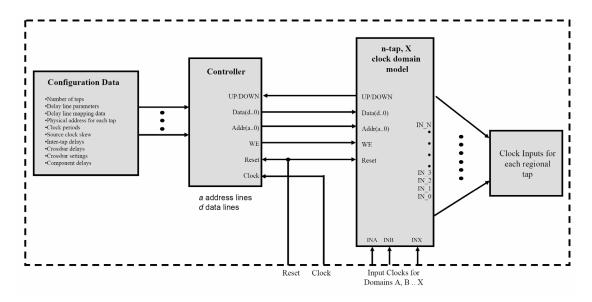

| Figure 6.1:  | The single clock domain, <i>n</i> -tap controller and model                           | 129 |

| Figure 6.2:  | Controller used for single clock domain model                                         | 129 |

| Figure 6.3:  | Controller component used to select and update taps in clock distributions            | 130 |

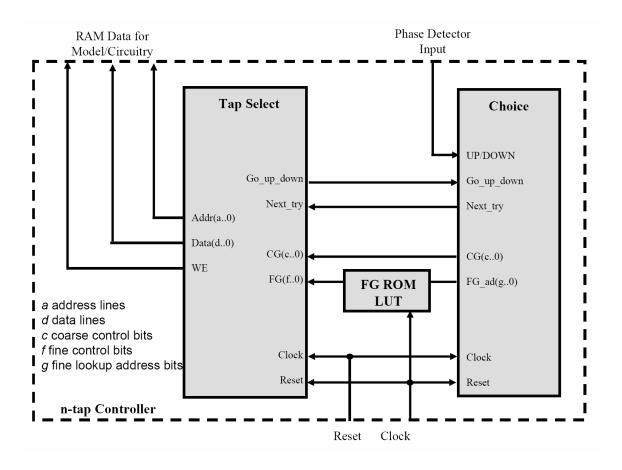

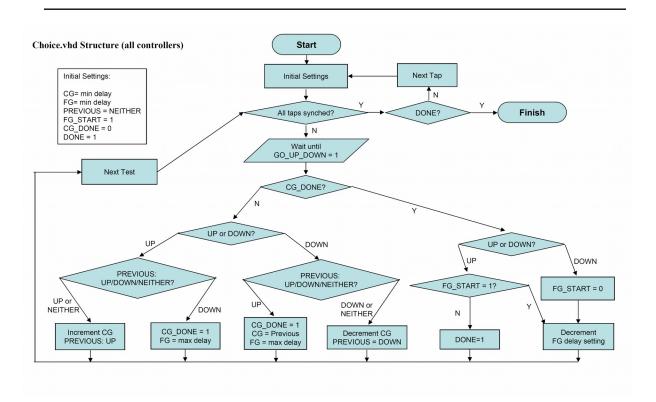

| Figure 6.4:  | Controller unit structure used to choose delay settings                               | 131 |

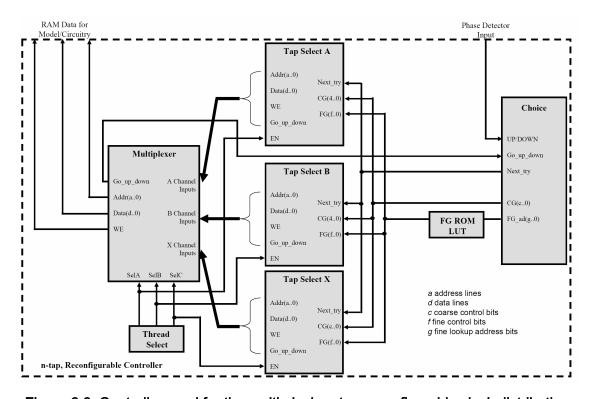

| Figure 6.5:  | The multi-clock, <i>n</i> -tap clock distribution controller and model                | 133 |

| Figure 6.6:  | Controller used for the multi-clock, <i>n</i> -tap reconfigurable clock distribution. | 133 |

| Figure 6.7:  | The built-in clock skew system model and controller                                   | 134 |

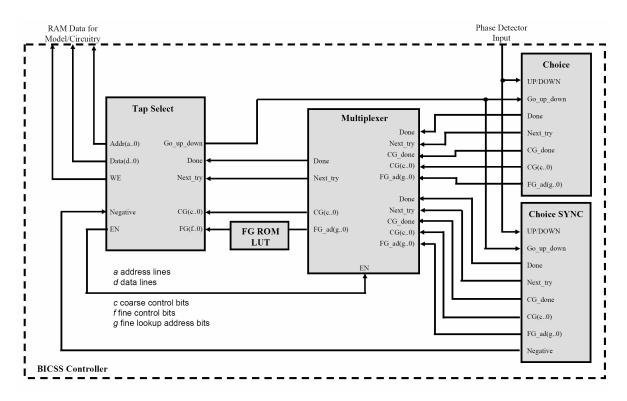

| Figure 6.8:  | The controller used for the Built-in clock skew system                                | 135 |

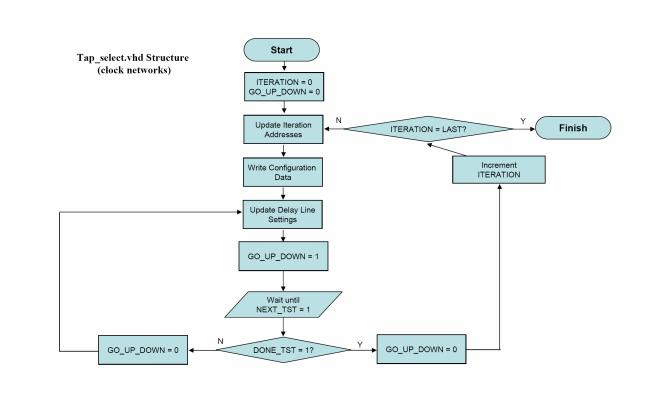

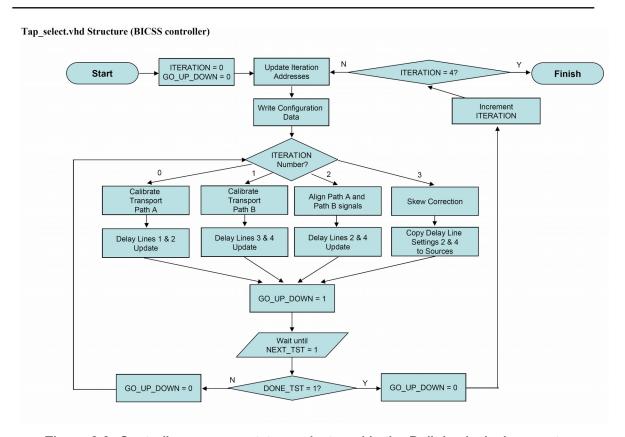

| Figure 6.9:  | Controller component <i>tap_select</i> used in the Built-in clock skew system         | 136 |

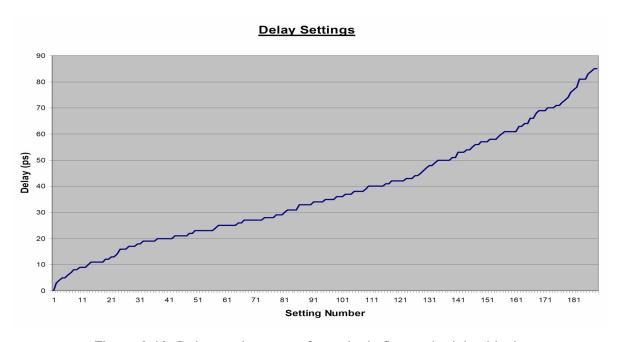

| Figure 6.10: | Delay setting range for a single fine grain delay block                               | 137 |

| Figure 6.11: | The n-tap clock distribution model                                         | 138 |

|--------------|----------------------------------------------------------------------------|-----|

| Figure 6.12: | An enlarged section of a multi-clock mesh                                  | 141 |

| Figure 6.13: | The built-in clock skew system model                                       | 142 |

| Figure 6.14: | The multi-clock domain, 15-tap reconfigurable clock network model          | 147 |

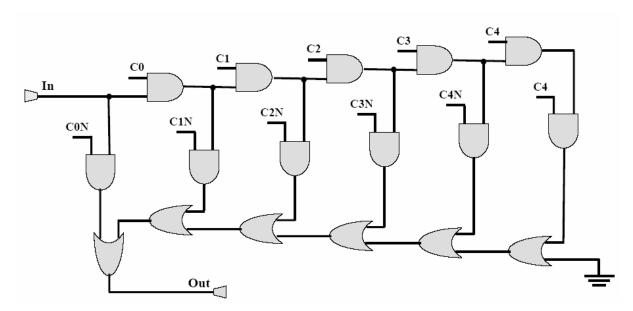

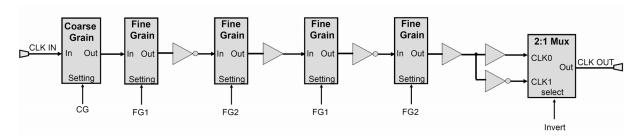

| Figure 7.1:  | Coarse grain delay line                                                    | 157 |

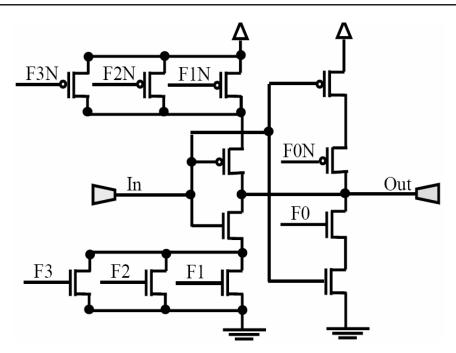

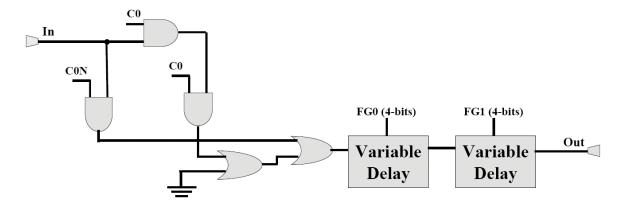

| Figure 7.2:  | Fine grain variable delay inverter                                         | 158 |

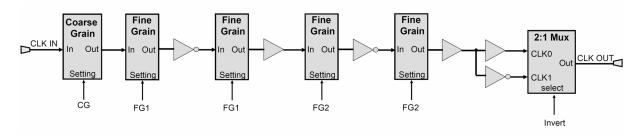

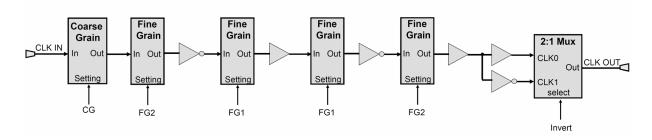

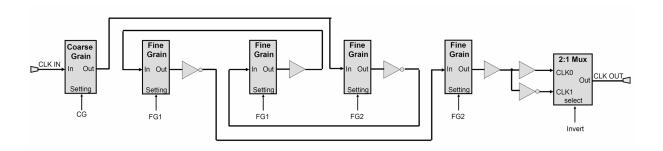

| Figure 7.3:  | 1-1-2-2-fine delay configuration                                           | 161 |

| Figure 7.4:  | 1-2-1-2-fine delay configuration                                           | 161 |

| Figure 7.5:  | 1-2-2-1-fine delay configuration                                           | 161 |

| Figure 7.6:  | Grouped fine delay configuration                                           | 162 |

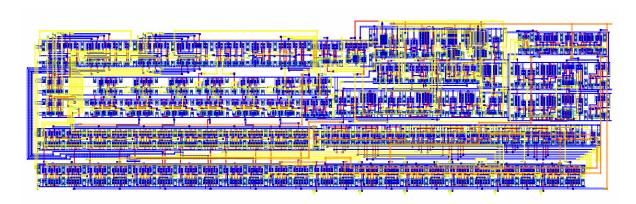

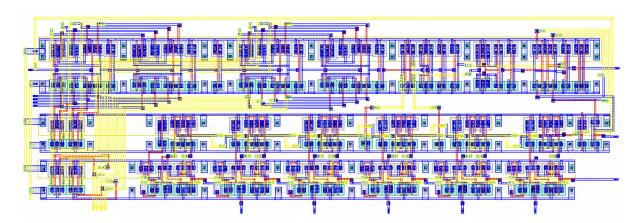

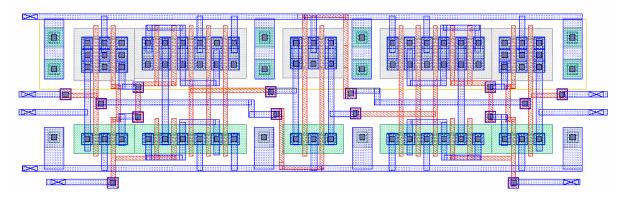

| Figure 7.7:  | Layout of complete delay line                                              | 164 |

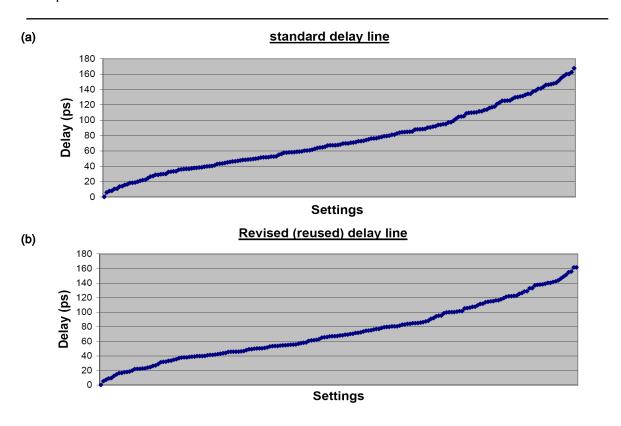

| Figure 7.8:  | Delay range of extracted grouped and shared delay lines                    | 166 |

| Figure 7.9:  | Simplified delay line used in BICSS system                                 | 166 |

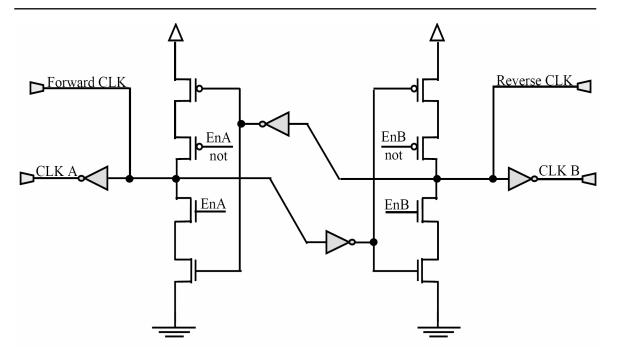

| Figure 7.10: | Tap bypass switch                                                          | 168 |

| Figure 7.11: | Layout of tap bypass switch                                                | 168 |

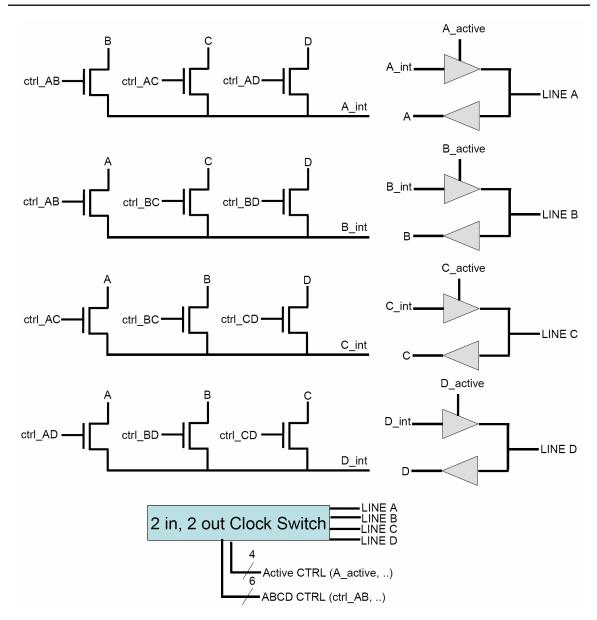

| Figure 7.12: | 4-port clock routing switch                                                | 169 |

| Figure 7.13: | Layout of 4-port clock routing switch                                      | 170 |

| Figure 7.14: | Layout of unidirectional 4-port clock routing switch                       | 171 |

| Figure 7.15: | Fixed tolerance phase detector                                             | 172 |

| Figure 7.16: | Layout of fixed tolerance phase detector                                   | 173 |

| Figure 7.17: | Variable tolerance phase detector                                          | 174 |

| Figure 7.18: | Layout of variable tolerance phase detector                                | 175 |

| Figure 7.19: | Modified phase detector for shared delay line systems                      | 176 |

| Figure 7.20: | Layout modified phase detector for shared delay line system                | 177 |

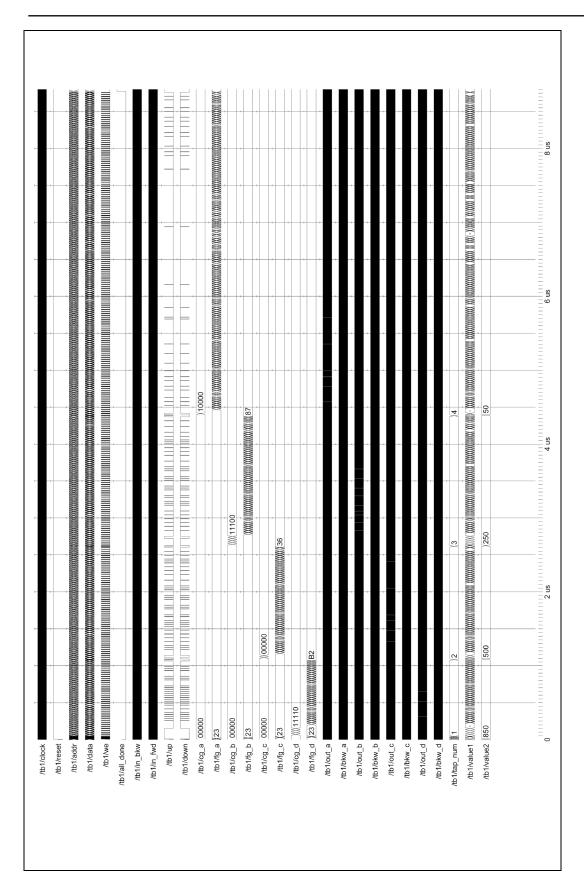

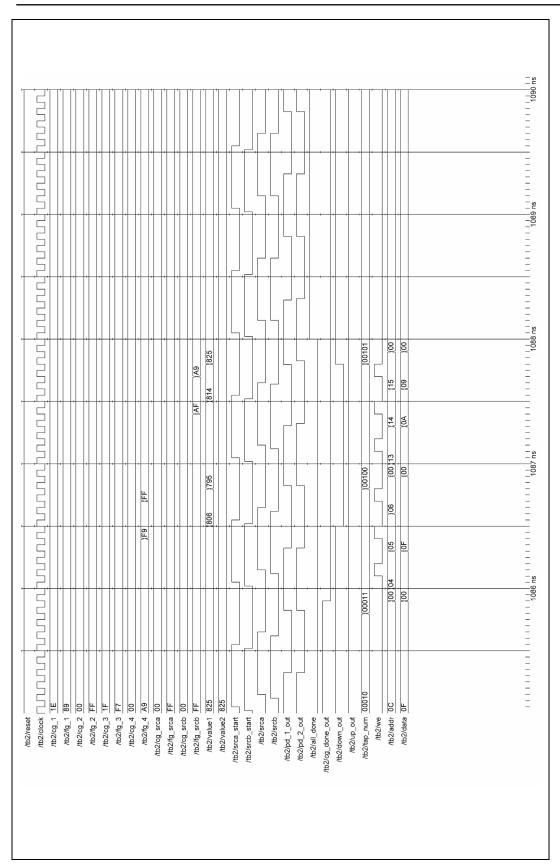

| Figure A.1:  | Complete simulation of a 4-tap distribution at 1 GHz                       | 190 |

| Figure A.2:  | Result of clock thread initialization of 4-tap clock distribution at 1 GHz | 191 |

| Figure A.3:  | Simulation result of first tap synchronization of 4-tap clock distribution at 1 GHz.                         | 19 |

|--------------|--------------------------------------------------------------------------------------------------------------|----|

| Figure A.4:  | Comparison of initial and final tap clocks of 4-tap clock distribution at 1 GHz                              | 19 |

| Figure A.5:  | Complete simulation of a 4-tap distribution at 1.5 GHz                                                       | 19 |

| Figure A.6:  | Simulation result of first tap synchronization of 4-tap clock distribution at 1.5 GHz.                       | 19 |

| Figure A.7:  | Comparison of initial and final tap clocks of 4-tap clock distribution at 1.5 GHz                            | 19 |

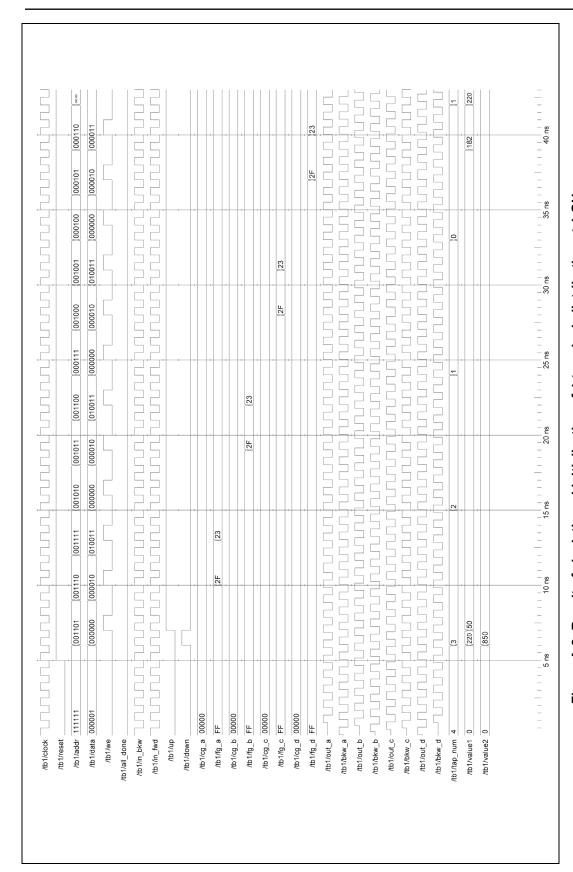

| Figure A.8:  | Complete simulation of a 15-tap, 3 clock domain reconfigurable clock distribution                            | 19 |

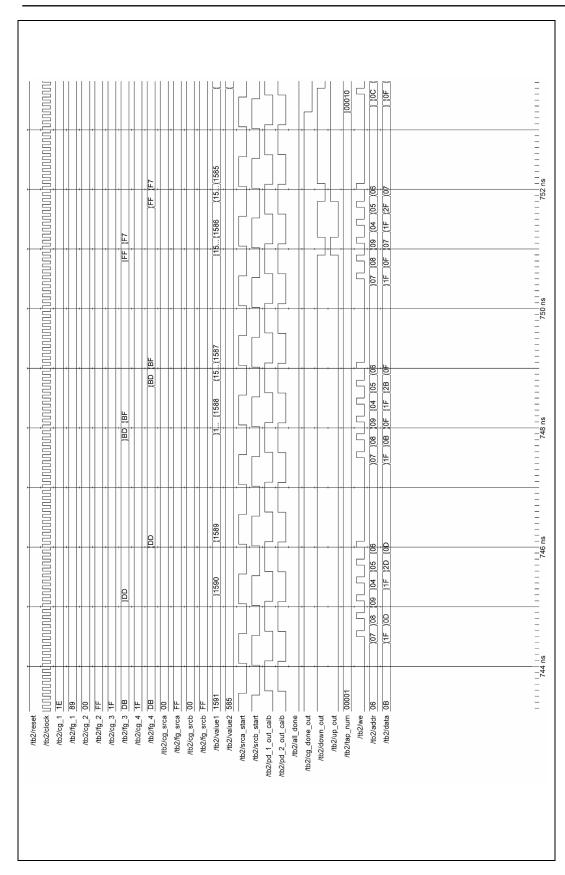

| Figure A.9:  | Final stage of clock domain synchronization of clock thread A (clock period of 900 ps)                       | 19 |

| Figure A.10: | Final stage of clock domain synchronization of clock thread B (clock period of 750 ps)                       | 1  |

| Figure A.11: | Final stage of clock domain synchronization of clock thread C (clock period of 600 ps)                       | 20 |

| Figure A.12: | Final synchronized end result of 15-tap reconfigurable clock distribution operating with three clock domains | 20 |

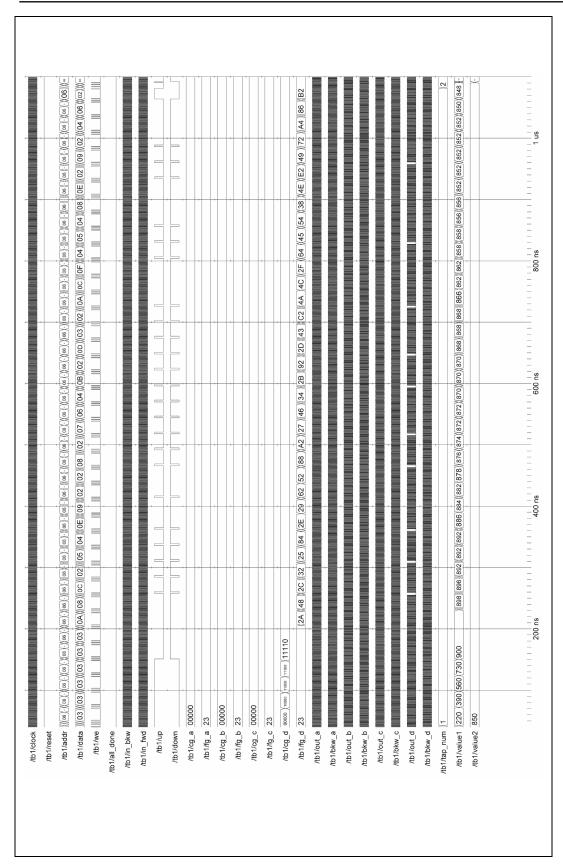

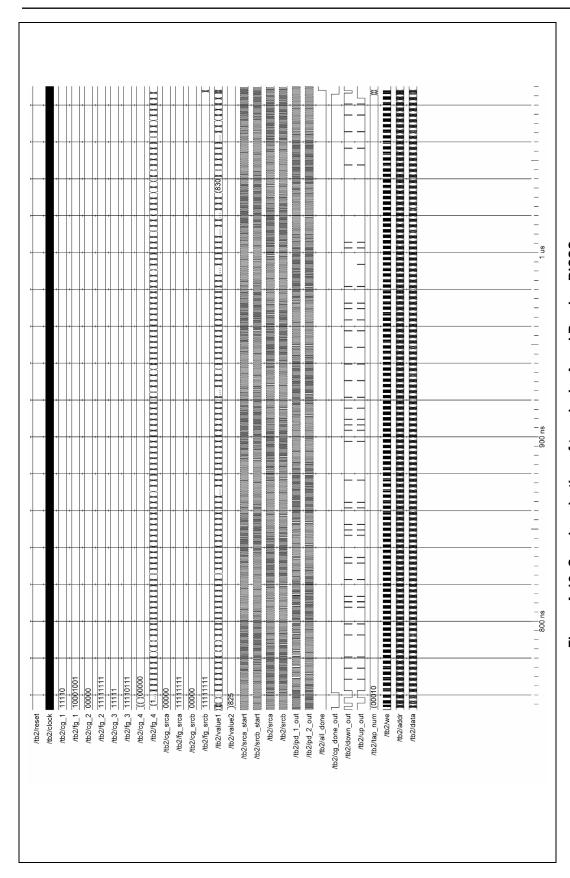

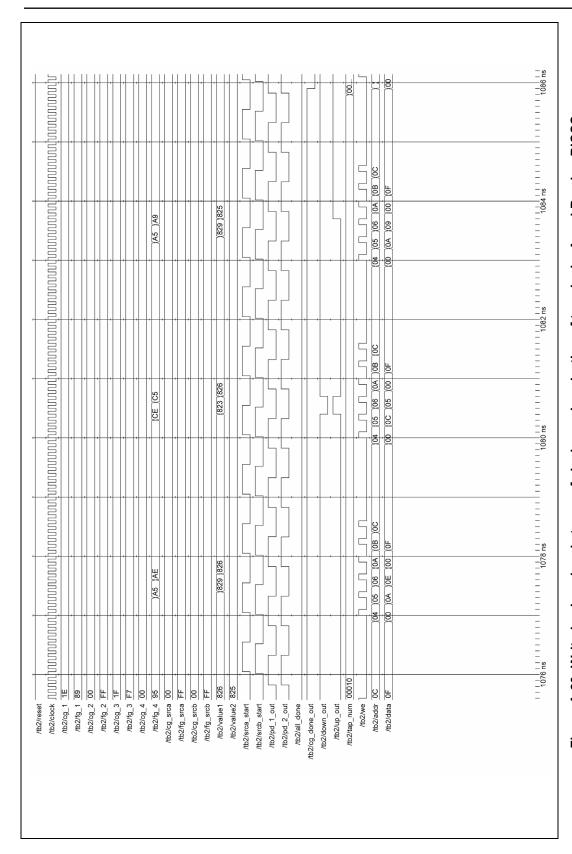

| Figure A.13: | Complete calibration and synchronization of two clock taps using BICSS                                       | 20 |

| Figure A.14: | Calibration of BICSS for transport delay from tap A to central BICSS circuitry                               | 20 |

| Figure A.15: | Enlarged final stage of calibration of BICSS for transport delay from tap A to central BICSS circuitry       | 20 |

| Figure A.16: | Calibration of BICSS for transport delay from tap B to central BICSS circuitry                               | 2  |

| Figure A.17: | Final end stage of calibration of BICSS for transport delay from tap B to central BICSS circuitry            | 2  |

| Figure A.18: | Synchronization of tap clocks A and B using BICSS                                                            | 20 |

| Figure A.19: | Enlarged final stage of synchronization of tap clocks A and B using BICSS                    | 208 |

|--------------|----------------------------------------------------------------------------------------------|-----|

| Figure A.20: | Write-back and end stages of clock synchronization of tap clocks A and B using BICSS         | 209 |

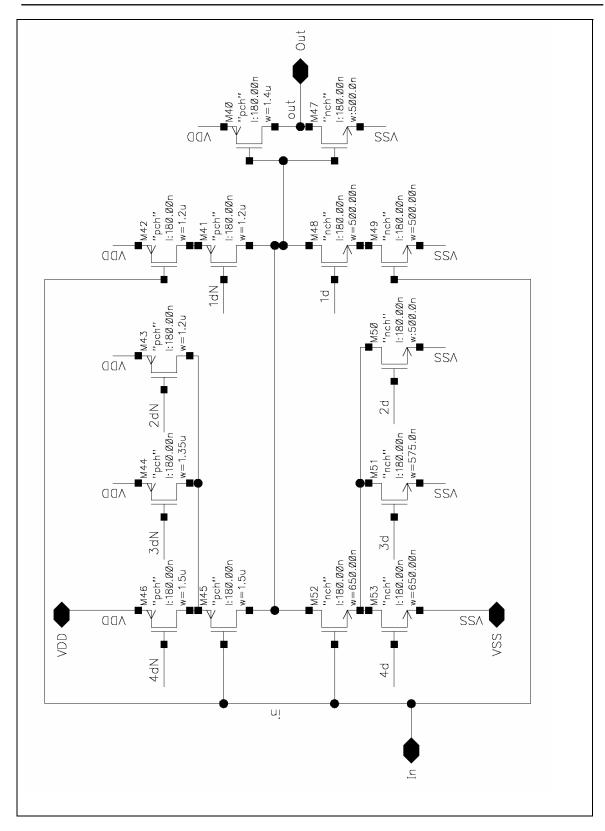

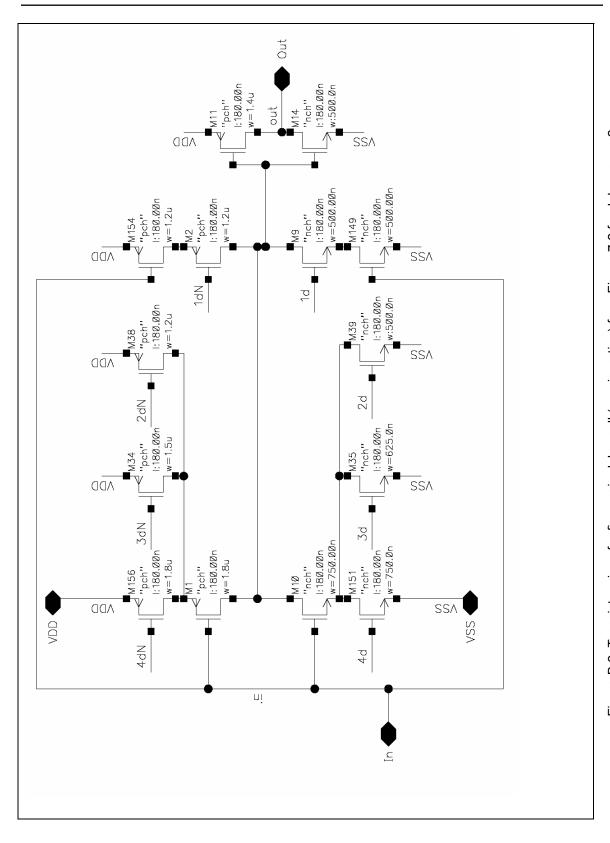

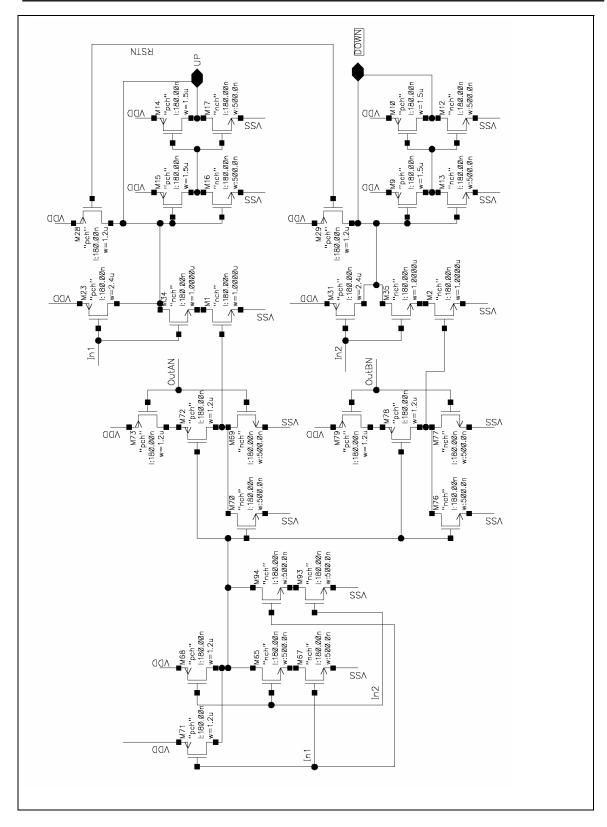

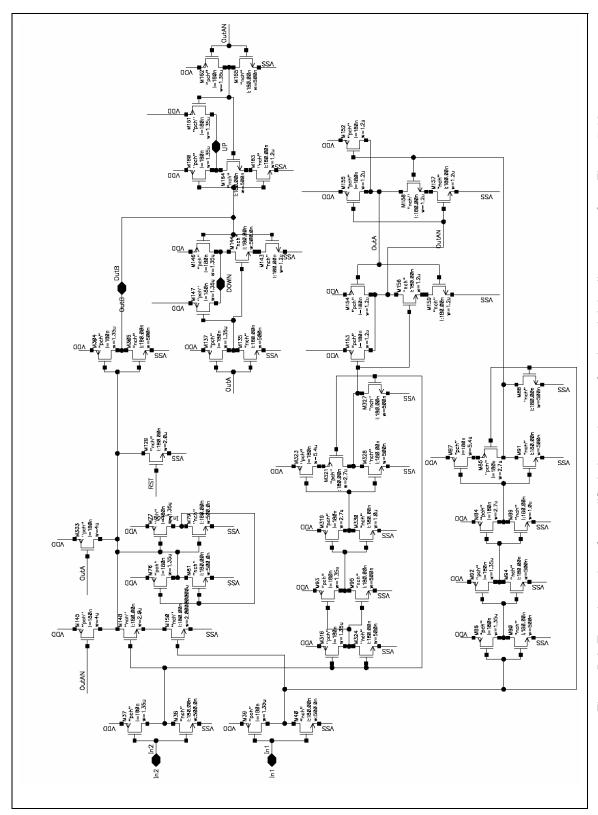

| Figure B.1:  | Transistor sizes for fine grain delay cell (non-inverting) from Figure 7.2 for delay range 1 | 212 |

| Figure B.2:  | Transistor sizes for fine grain delay cell (non-inverting) from Figure 7.2 for delay range 2 | 213 |

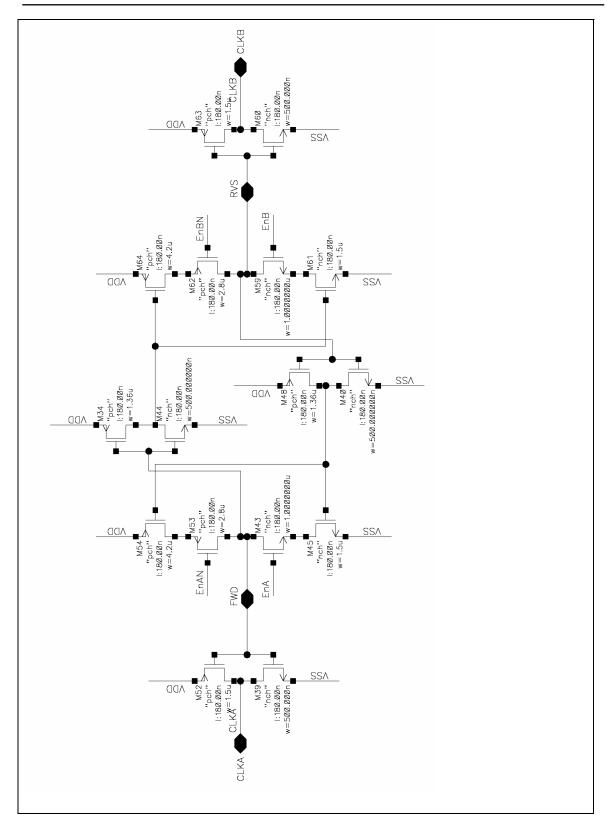

| Figure B.3:  | Transistor sizes for tap bypass switch from Figure 7.10                                      | 214 |

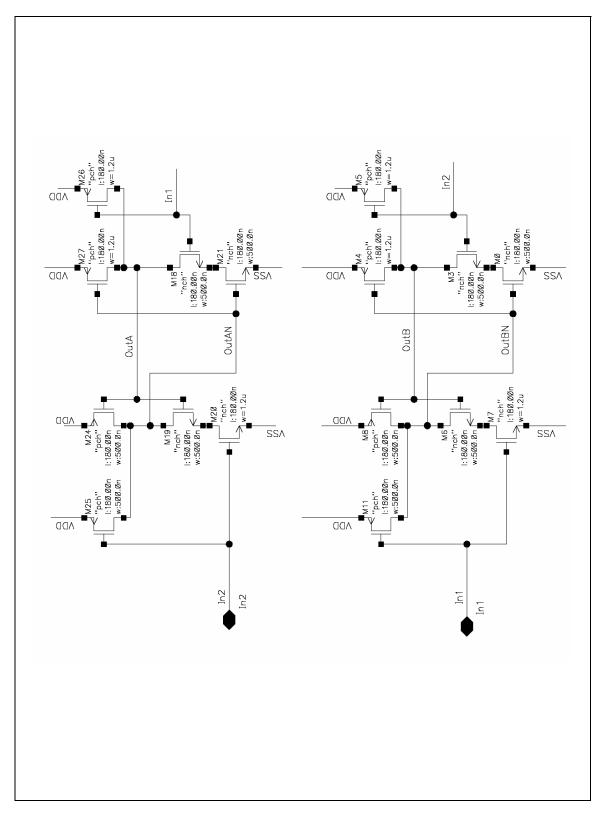

| Figure B.4:  | Transistor sizes for input section of the fixed tolerance phase detector from Figure 7.15    | 215 |

| Figure B.5:  | Transistor sizes for memory section of the fixed tolerance phase detector from Figure 7.15   | 216 |

| Figure B.6:  | Transistor sizes for modified phase detector for shared delay line system from Figure 7.19   | 217 |

# Table of tables

| Table 3.1: | Wire length comparison                                 | 49  |

|------------|--------------------------------------------------------|-----|

| Table 3.2: | Sum of squares distance component of variance relation | 61  |

| Table 4.1: | Temperature effect on synchronized network             | 99  |

| Table 4.2: | Effect of voltage variance on taps                     | 99  |

| Table 4.3: | Effect of voltage variance on synchronized network     | 99  |

| Table 4.4: | Effect of voltage supply noise on jitter               | 99  |

| Table 6.1: | Number of possible clock domain configurations         | 148 |

# **Chapter 1:**

## Introduction

"Much may be done in those little shreds and patches of time which every day produces, and which most men throw away."

- Charles Caleb Colton [1]

Coordinating activity in a digital integrated circuit is a fundamental problem in circuit design. Modern integrated circuits (ICs) use a *clock* as a common synchronization signal to coordinate events within the device's datapath. Among their many uses, clocks can be used by functional blocks to indicate when the data it requires is ready to be processed, to divide a task into smaller ones requiring more processing cycles but

permitting faster execution of each individual step, or to avoid *signal races* by preventing data from being used before it is stable. Traditionally, high performance circuits are designed to have the highest clock frequency possible, but with newer technologies, more emphasis has been placed on the amount of *work* or operations that can be done in a given amount of time. However, as clock frequencies continue to increase due to newer integrated circuit process technologies, the percentage of unused time in each clock period continues to increase largely due to timing uncertainty in the circuitry designed to transport clock signals to each circuit block. Any uncertainty in clock arrival times must be reserved within a clock period to ensure the correct operation of the device. Since no computation can take place during this reserved time, it is important to minimize the amount of unused computation time, making the *clock distribution network* (CDN) in an IC among the most important components in any synchronous digital system due to its direct effect on circuit performance and functionality.

Clock networks must broadcast a clock signal throughout an IC minimizing clock uncertainty, consuming as little power as possible and providing consistent signal characteristics such as rise time and duty cycle. Further, the system must be robust and easy to implement. Currently, the most common design approach for clock networks relies on automated clock tree synthesis methods that are tailored to a fixed silicon implementation with a rigid clock network using user-specified parameterization. The outcome is a fixed layout clock tree that is difficult to modify once created, often requiring complete re-implementation of the network for every iteration of the design. Once fabricated, absence of flexibility in the clock distribution poses a problem on two major

fronts: first, errors or process variation in the silicon cannot be corrected; second, adapting a design to a variety of configurations and applications become limited by the lack of flexibility in the clock network. This is especially true with the ever-increasing shift to flexible design methodologies that use programmable devices for reconfigurable computing applications.

#### 1.1. Problem description

With the decreased cost and increased availability of silicon area, ICs have become significantly more complex in recent years. With the increase in popularity of "system-on-chip" designs, a single modern IC is capable of doing the job of many of its predecessors and the potential versatility of a system today is unparalleled. However, it is difficult for today's clock distribution networks to cope with flexible, reconfigurable and multi-application integrated circuits due primarily to the fixed tree-based methodologies used to minimize clock arrival time variation, or *clock skew*. With modular design strategies, circuit components may derive from many distinct sources such as intellectual property (IP) blocks [2] with little knowledge concerning the internal circuit characteristics available to IC architects. Field-programmable gate arrays (FPGAs) allow flexible logic and clock domains and avoid the upfront design costs of application specific designs, but when compared to the application specific integrated circuits (ASICs), they require larger devices, consume more power and cannot achieve the same performance. In addition, to create flexibility in their clock networks, FPGAs must allow for more significant variation in

clock signal arrival times, which is unexploited computation time. Balancing flexibility and low skew can pose a significant challenge to clock networks and has not been extensively explored in existing designs.

Today, an ever increasing amount of the ASIC design flow is spent on testing and verification challenges due to the complexity of the problem: every 10% increase in design complexity increases the test problem 100% [3]. This figure becomes even more significant when one considers that a typical design flow places 70% of the effort on verification, compared to 30% for design [4]. According to Collett International Research, the first iteration success rate for ICs had decreased from 48% to 34% between 2000 and 2003 due to the added complexity of designs [5]. Approximately 45% of devices fail based on logic errors, 33% of devices fail due to fast or slow signal paths and 10% of devices fail due to errors in the clock network. It then makes sense to take advantage of the low cost of silicon area to consolidate multiple designs into one, validate them together, effectively distributing development costs over multiple product lines. This silicon reuse application is similar to platform-based design methodologies and allows personalization of a single device for a number of possibly unrelated applications. ICs with defective sections can be binned to applications that do not require the defective component. Some small changes can be performed after silicon implementation to existing clock networks with simple "pruning" or removing of clock branches, but the modifications required will usually alter the loading of the clock or the frequency required, which necessitates the creation of a new CDN. Instead, when a single silicon design is used for multiple applications through the use reprogrammable components and processors, the availability of flexible clock distribution networks is useful.

#### 1.2. Thesis objectives

The goal of this doctoral project was to create a flexible clock distribution network that could be used in ASICs, FPGAs or other applications without sacrificing the low clock skew performance achievable with today's clock networks. The desired result is a clock network where every region can be connected to and disconnected from one-of-many clock regions post-silicon, introducing significant flexibility to the clock distribution network. In FPGAs, the benefit of flexibility in the clock network could add additional functionality to current designs. In ASIC applications, the goal is to create a single design that can be reconfigured dynamically for different tasks or programmed at the factory for different applications. Consider the implementation of a single processor design with multiple components such as Bluetooth, USB, Firewire, JTAG, floating point arithmetic units and video encoders. The idea was to not only create blocks which could be included and discarded, but potentially shared between multiple clock domains, all while maintaining adequate skew compensation for all the leaves in a clock domain. Such a configuration would also allow micro-clock regions, where every component could operate at or near their minimum frequency considering its operating requirements resulting in a decreased average clock frequency for the design - a helpful trait in minimizing overall energy consumption [6].

One challenge in creating such a system is moving away from clock trees and finding other approaches to distributing a clock signal on an IC: one that allows routing switches to be included in the clock path to connect clock subregions together easily and arbitrarily. A switch mesh can be used to re-route clock signals, but this method requires a daisy-chained approach that will create skew between every clock region and will call for a complete change in the approach used to minimize skew in clock networks. No longer would balancing global clock trees be sufficient. We want to first develop a methodology to make serially-distributed clock domains possible, and next want to show that this approach was realizable with transistor-level circuit structures and we finally want to create a modelling infrastructure from which we could create a variety of clock network configurations for arbitrary applications. We explore both single clock and multiple clock reconfigurable systems. This is the first investigation of a clock network that emphasizes flexibility and reconfigurability without sacrificing tolerance to clock skew. Finally, given that process variance can occur between ICs (inter-die) and across a single IC (intra-die) for any clock distribution network, we want to look at a low-cost method to determine the quality of a clock network using an on-chip skew measurement approach known as BICSS. BICSS provides post-silicon debug capability of clock distribution networks that can aid in diagnosing timing errors that may be discovered during testing. Both BICSS and our serial dual reference signal clock distribution networks can improve yield by providing post-silicon repair capability to the clock networks of integrated circuits suffering from certain timing errors.

#### 1.3. Statement of original contributions

#### 1.3.1. Single clock averaging network

We present a single clock distribution scheme using a dual reference signal approach and a single bi-directional conductor between clock taps. We use an averaging technique to allow serialization of clock networks. Daisy-chaining the clock decreases the clock interconnect load by eliminating the redundant paths used to equalize delays in traditional H-tree distributions. Clock skew is accounted for by actively synchronizing each local clock to a position directly between forward and reverse-moving reference clocks. The design provides simple-to-layout and scalable multi-point skew compensation useful for large designs. Our design is unique in its use of a truly bi-directional line and buffering in an averaging distribution. This approach compensates for process, temperature and power supply variations, eliminating systematic skew in the clock distribution network. In addition, a dual reference line averaging approach is explored to maximize the system's tolerance to device mismatch. Device mismatch is a key contributor to clock skew in traditional clock distribution networks due to the large distances between ideally-matched devices. We show that our serial clock distribution is much better able to cope with mismatch since the distances between ideally-matched devices in greatly minimized in our system. Tree-based clock distribution networks are also susceptible to skew from cross-chip temperature variation due to the distributed buffers that they employ. We also explore a serial clock distribution that is highly tolerant to intra-die temperature changes. This work was initially disclosed in 2006 [7]. Additional configurations for performing the averaging of the forward and reverse reference signals were first disclosed in 2007 [8]<sup>1</sup>.

#### 1.3.2. Multiple clock reconfigurable clock network

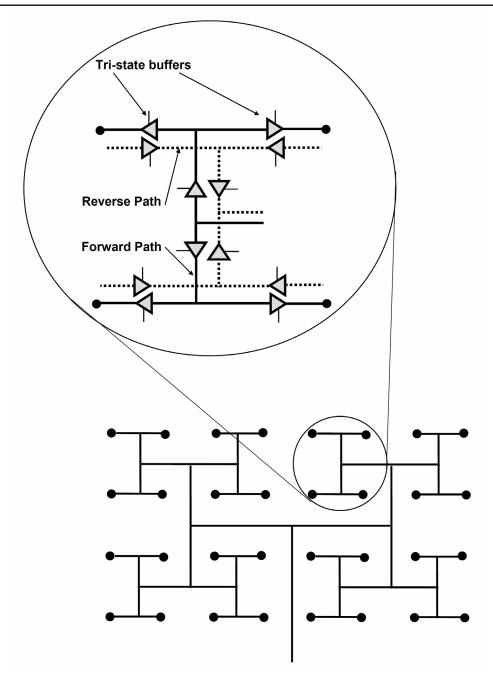

We present a multiple clock distribution scheme by expanding our single clock design, adding clock routing structures into an averaging clock network to enable reshaping clock domains, post-silicon. These reconfigurable, reprogrammable clock networks can be used in ASICs, SoCs and FPGAs. The technique is useful for reconfigurable computing applications to connect the programmable logic to the clock domains of the surrounding logic. The proposed design allows for more flexibility in clock networks than current designs such as those used in Altera and Xilinx FPGAs. It simplifies layout for irregularly-shaped clock domains and provides flexibility to designers by enabling post-fabrication changes to the clock distribution network. This work was initially disclosed in 2007 [9].

<sup>&</sup>lt;sup>1</sup> While the other listed disclosures were in peer-reviewed publications, the TEXPO poster and extended abstract submission were by open invitation.

#### 1.3.3. On-chip clock skew detection circuitry

To verify the characteristics of arbitrary clock networks, we present a Built-In Clock Skew System (BICSS) that uses a centralized approach to identify, quantify and correct skew using a two-step method. The first step is to assess the time-of-flight between the central debug circuitry and each region, or tap under test to account for the measurement error due to differences in path length. This measurement error is common in existing techniques. Typically, timing errors due to faulty clock networks can be very difficult to diagnose due to the intermittent nature of the errors that they may cause. The result is a scalable solution that provides silicon debug and repair capability of on-chip clock skews. This work was disclosed at the 2008 Design, Automation and Test in Europe conference [10].

#### 1.3.4. Custom circuitry

We present the schematic and extracted designs of the required custom circuit components in a 180 nm standard process. Of particular interest are the phase detectors and delay lines that we explored. The phase detectors are unique due to their use in an all-digital application with finite skew bound. This application allows the phase detector to create and to use a dead-zone period to speed up resolution time. For the delay lines, different configurations are explored to emphasize delay matching through multiple delay line pairs, signal characteristics and duty cycle retention. A current-starved all-digital approach with good linearity between settings and zero static current consumption is

chosen. The circuits involved in creating our clock distribution networks were primarily disclosed in 2007 [11], and partially disclosed in [7]-[10].

#### 1.4. Thesis organization

Chapter 2 describes background on clock networks and some de-skew approaches, Chapter 3 describes implementation of a single clock domain network using our method, Chapter 4 describes a reconfigurable multiple clock network using a clock mesh and our averaging approach, Chapter 5 describes an on-chip approach to detecting, measuring and compensating for clock skew in an integrated circuit environment, Chapter 6 describes a system-level overview of these components including HDL models and the required synchronization controllers, and Chapter 7 highlights some of the circuitry required to implement these systems in a TSMC 180 nm technology.

# **Chapter 2:**

# **Background**

### 2.1. Introduction

This chapter outlines the conventions and definitions that we have adopted. It also describes some of the existing work and techniques in the area of clock distribution and highlights some of the benefits and drawback of each. The information is compiled from sources that include [12]-[16]. Other sources are used as indicated.

#### 2.2. Clock characteristics

The clock is a periodic signal, usually viewed as having the shape of a sine or square wave used to synchronize two or more events at different locations using a single signal in a synchronous circuit. While clocks are used in other applications such as in printed circuit board designs, we limit our discussion here to clocks used on integrated circuits such as microprocessors, field-programmable gate arrays and application specific integrated circuits. Typical high performance analog circuits use sinusoidal clocks due to the large number of high frequency harmonics present the near infinite slope of a square wave's edge. Some circuits trigger only on the rising or the falling edge of the clock (single clock edged devices) and some trigger events on both rising and falling edges (dual clock edged devices). We will use the term *multiple clock circuit* to describe a circuit which has a plurality of clock domains, whether these domains be for rising, falling or dual edged circuitry.

Definition 2.1: Clock period: the time, **T**, between rising or falling edges of a clock signal, usually measured as the signal crosses its 50% voltage level. The inverse of the clock period is the clock frequency, **f**, with units Hertz (Hz), or 1/seconds.

Definition 2.2: Slew rate: The slew rate is the rate of change of a signal's output voltage level at any given point. The slew rate should usually be kept to less than 15% of the clock cycle. [16]

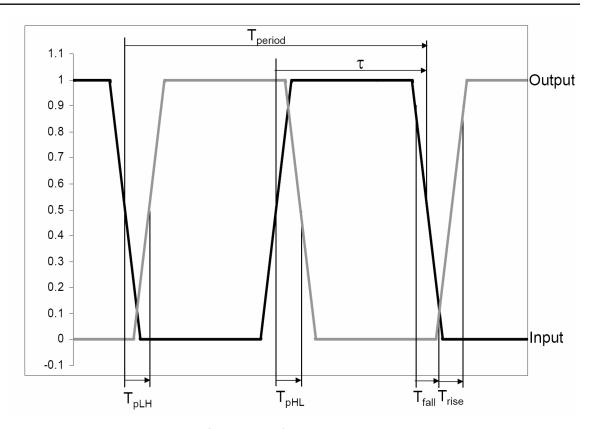

Figure 2.1: Summary of relevant measurements.

In digital circuits, sinusoidal clocks have low slew rates and these sloped edges create delay uncertainty in most logic families including complementary metal-oxide semiconductor (CMOS) devices, which is the most widely used digital logic family. In practice, the clock for digital devices is usually shaped as a non-ideal square wave with finite sloped edges, Figure 2.1.

Definition 2.3: Duty cycle: for a periodic signal, the duty cycle D represents the percentage of time  $\tau$  that the signal spends in a certain state. For digital circuits, this state usually refers to the logical "1" state.

$$D = 100 \cdot \frac{\tau}{T} \tag{2.1}$$

We utilize the logical "1" convention for our duty cycle purposes, and further specify that the logical "1" state includes all of the time that the signal spends above the 50% voltage level. Clocks are usually assumed to have 50% duty cycles, spending half the time above the 50% voltage level and half the time below. Ideal square waves are impossible to achieve on a physical device due to the non-zero resistance and capacitance in any and every portion of the clock network. Ideal square waves would have zero rise and fall times.

Definition 2.4: Rise time: the rise time  $t_{rise}$  of a signal is the time interval between a signal at location X transitioning from 10% to 90% of the high voltage level.

Definition 2.5: Fall time: the fall time  $t_{fall}$  of a signal is the time interval between a signal at location X transitioning from 90% to 10% of the high voltage level.

Transition times are affected by a device's inherent drive strength, the load being switched and external factors such as coupling noise. Higher temperatures and lower power voltage will slow down delay through a device.

Definition 2.6: Propagation delay: If X and Y are two logically connected points on a circuit, and  $\mathbf{s}_X$  and  $\mathbf{s}_Y$  are signals at locations X and Y, respectively, then the signal propagation delay  $\mathbf{t}_{pXY}$  is the time (either positive or negative) between the 50% signal transition at X and the 50% signal transition at Y. [12]

While signal propagation delay can sometimes refer to the time between the input of a gate reaching its switching point to the time that the output of the gate reaches

its switching point, the more generic definition of Definition 2.6 is used exclusively. For a clocked element, the signal propagation refers to its clock-to-output delay ( $t_{CQ}$ ) since it represents the delay between the clock input passing 50% of its assertion value and the data reaching the 50% signal transition at the output. For both clocked and unclocked elements, the signal propagation can be taken separately for a high-to-low transition ( $t_{pHL}$ ) and for a low-to-high transition ( $t_{pHL}$ ). Unless otherwise stated, the propagation delay is the arithmetic average between  $t_{pHL}$  and  $t_{pLH}$  [13]. This elaboration is necessary due to the asymmetry between pull-up and pull-down transistor blocks in complementary logic design, and the inherent physical differences between the devices used in the circuitry, PFET (p-type metal–oxide–semiconductor field-effect transistor) for pull-down. For signals which are required to have 50% duty cycle,  $t_{pHL}$  and  $t_{pLH}$  must be equal. If they are not, the duty cycle will get shorter if  $t_{pHL} < t_{pLH}$  or it will get longer if  $t_{pHL} > t_{pLH}$ . These measures are summarized in Figure 2.1.

## 2.3. Clock uncertainty

Since the clock is used to synchronize events across a circuit, their arrival times at all event points  $t_i$  need to be well-controlled [12]. Preventing uncertainty in clock arrival times can add significant complexity to designing robust circuitry since errors could render a circuit unusable. Any signal traveling through a given circuit will have a finite

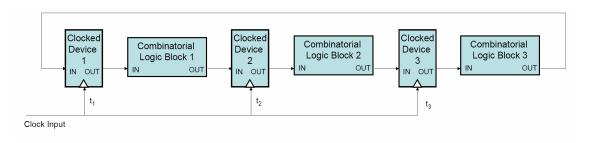

Figure 2.2: 3-register clock routing.

propagation delay. As a clock is broadcast through the IC, each path from clock source to  $t_i$  will be slightly different due to manufacturing and environmental differences. Figure 2.2 shows how a clock signal can be routed to three clocked devices (R1, R2 and R3) within a clock domain. The arrival times of clock and data at a register must be properly coordinated for a system to function correctly, since setup or hold time violations can occur if the arrival time of either varies from the expected time [13].

Definition 2.7: Sequentially adjacent registers: A pair of arbitrary registers connected by a signal path consisting exclusively of unclocked components without any other registers directly in the path. [12]

Definition 2.8: Setup time: The setup time (tsu) is the minimum time that data must be stable before a clock signal is asserted.

Definition 2.9: Hold time: The hold time ( $t_H$ ) is the minimum time that data must be kept stable after a clock signal is asserted.

Often, hold time is satisfied as the input data propagates from the previous register to the one in question. The time between active clock edges must be long

enough for data to propagate between sequential registers while satisfying the setup and hold times. The *minimum clock period* will be the longest such time between any pair of sequentially adjacent registers in the system. Due to fan-out and fan-in, there are usually many sequentially adjacent registers to any given register in the datapath and every pair must be considered. If the propagation delay of a given combinatorial block is  $t_{CLi}$  and the propagation delay of a given register is  $t_{CQi}$ , the clock period required between register Ri and Ri is:

$$t_{pii} = \max(t_{COi} + t_{CLi}, t_{Hi}) + t_{SUi}$$

(2.2)

For the circuit in Figure 2.2, the minimum clock period will be the maximum between  $t_{p(1,2)}$ ,  $t_{p(2,3)}$  and  $t_{p(3,1)}$ . In a typical synchronous system, there will be many sequentially adjacent paths and they must all be considered when choosing a clock frequency, f, for a specific clock domain.

Definition 2.10: Clock domain: a collection of all sequentially-adjacent registers connected to a single clock source. We will consider mutually exclusive sets of sequentially-adjacent registers (with no logical connections between them) to be in different clock domains even if they connected to the same source clock. [12]

Definition 2.11: Clock skew: The clock skew between two clock registers  $\mathbf{R}_i$  and  $\mathbf{R}_j$  is the difference between the clock arrival times  $\mathbf{t}_i$  and  $\mathbf{t}_j$  respectively. The times  $\mathbf{t}_i$  and  $\mathbf{t}_i$  are taken with respect to an arbitrary, but identical reference point.

Generically, skew is the variation in arrival times for two signals that are supposed to arrive simultaneously. [12],[14],[15]

$$t_{skew\ ij} = t_i - t_j \tag{2.3}$$

Clock skew is especially important between sequentially adjacent registers since it can affect the clock time required between registers.

$$t_{pii} = \max(t_{COi} + t_{CLi}, t_{Hi}) + t_{SUi} + t_{skew\ ii}$$

(2.4)

When the skew is negative ( $t_{skew} < O$ ), the data can arrive at register  $R_i$  (the destination register) early, potentially violating the hold time constraint or causing a race condition where incorrect data is latched. This phenomenon can be useful in certain datapaths since it increases the time available between clock assertions for  $t_{CO}$ ,  $t_{CL}$  and  $t_{SU}$ , permitting longer datapaths between registers with negative skew [14]. This is sometimes called *beneficial skew*. The opposite is true when  $t_{skew} > O$ , this decreases the time available between registers. If not taken into account, this can lead to setup time violations and potential loss of data. Clock skew can occur due to different line lengths, buffer delays, device parameters, noise or environmental variation. *Passive* parameter variations can include changes in resistivity, fringing capacitance and line dimensions. *Active* parameter variation can include changes in transistor threshold voltages (when a device switches) and electron and hole mobility of devices (how quickly a device changes).

For Figure 2.2, the clock is traveling in a left to right direction. It will arrive at *R2* after *R1* and *R3* after *R2*. This creates beneficial skew for these paths. However, between *R3* and *R1*, there will be positive skew. Beneficial clock skew can be designed into a system and used to increase a system's clock frequency, but only when clock and data are moving in the same direction. In a modern synchronous circuit, there are many complex inter-dependent register-to-register paths, where it is difficult to provide beneficial skew in one area of the circuit without creating harmful skew in another [12],[14].

Definition 2.12: Clock jitter: Clock jitter is the deviation of a clock's output from its ideal position. Deterministic jitter is bounded in amplitude and originates from non-random specific sources such as device imperfections, cross-talk or power-supply or grounding problems. Random jitter originates from Gaussian noise components in a system such as from substrate or power noise. [15],[17]

The term jitter applies to a change in amplitude, phase or frequency in a clock that occurs from *cycle-to-cycle* or over longer periods of time [15]. Under the broadest definition of jitter, early or late clock arrival times can be considered a form of jitter, but the jitter is usually viewed as a *temporary* phenomenon. This deviation can be periodic in nature as long as the behaviour varies from cycle-to-cycle for a given operating condition. This interpretation creates a non-overlapping distinction between clock skew and jitter. We will apply the term clock skew to a fixed deviation in a clock arrival time, caused by process variation, defects, a change in operating temperature or other such

occurrence. This skew can affect rising edges and falling edges asymmetrically. We will apply the term *clock jitter* to a temporary phenomenon that causes a non-static variation in clock arrival time caused by random or predictable phenomena such as a momentary drop in the voltage of the power line [15]. It is important to have well-controlled clock arrival times throughout an integrated circuit to ensure correct behaviour. The primary sources of jitter are the clock generator (usually a phase-locked loop, PLL) and the effect of power supply and coupling noise on the clock buffers [18].

# 2.4. Clock networks

Definition 2.13: Clock distribution network: A circuit pathway that delivers a clock signal to every segment of a synchronous circuit that requires it to ensure the correct operation of the system.

In modern integrated circuits, the clock distribution problem is becoming increasingly difficult since device behaviour is becoming increasingly variable, both from chip-to-chip (inter-device) and from device-to-device (intra-device) within an IC. In deep-submicron technologies, wire delays do not shrink as quickly as device delays due to their thin and tall wires having higher resistance and higher capacitance. Consequently, wire delay consumes a greater portion of the clock period and the transportation of any signal across a typical die requires longer than one clock period [19]. This fact and the ever-increasing fan-out of the clock make distributing clock signals even more

challenging. Clock power can range from 30-50% [20],[21] in standard high-performance integrated circuits, and up to 70% [22] in some specialized devices like FPGAs. The most common approach is for synchronous systems to have zero skew between all clock arrival points to simplify the timing specification required for the datapath. Even with systems designed for zero skew, it is necessary to design in a safety margin to maintain correct circuit behaviour in the presence of clock and data uncertainty, a 10% of the clock period rule of thumb is common here [23],[24]. Timing violations that occur at the edge of this range are difficult to detect, as they may be device-dependent and intermittent, only occurring under certain conditions. Many circuits have had to increase tolerances to assure proper operation, which has a negative effect on the performance of the system. Modern devices contain many clock domains, which all must be routed properly, which adds further complexity to the problem.

## 2.4.1. Symmetric clock tree

Symmetric clock trees are the most commonly studied approach to distribute a clock signal to a large number of clocked elements in a synchronous circuit. This structure takes a source clock and fans it out into n points using a constant wire length to every point. From each of these points, the signal branches out again into n wires resulting in  $n^2$  intermediate end points. This structure continues recursively until all clock destinations are reached. The number of branches required along a single path represents the number of *levels* in the clock tree [14]. In a binary or Y-tree, each branch

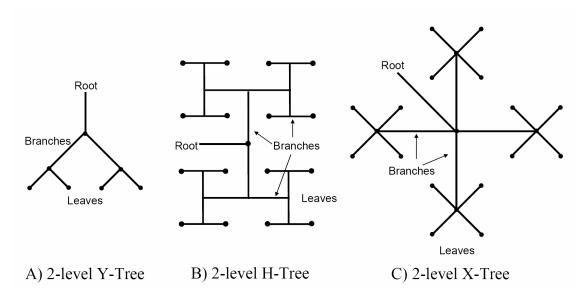

Figure 2.3: 2-level symmetric clock trees.

point splits into 2 branches with the same size and shape, but possibly different orientation. Every branch at a given level should be the same size with similar geometry. In an H-tree, the source clock is split into two, twice per level. At every split, the outgoing wire is placed at a right angle to the incident wire, creating an "H"-like structure. The length of wire is constant for every segment at a level and is halved for each subsequent level. Each H-structure fans out to 4 branches and uses Manhattan routing since every wire is either vertical or horizontal. In an X-tree structure [25], the horizontal and vertical wires are replaced by diagonal wires saving interconnect length, provided diagonal wires are possible in the technology.

Examples of these three symmetric tree structures are shown in Figure 2.3. Within a clock tree, the clock source is known as the *root*, the single path that transports the signal to the first branching point is known as the *trunk*, the distribution paths are known as *branches* and the individual clock destinations (usually registers) are known as

leaves. These trees may be completely passive with no buffering in the signal path but in practice, the fan-out is too large to do so effectively. Clock buffers are almost always required on the path and they are placed symmetrically across the clock network. They may be placed at every level or at arbitrary (symmetric) intervals in the tree. This creates an active tree with inline buffers or repeaters to regenerate weak signals along the clock path. To maximize signal integrity, impedances need to be matched at every branching point to minimize reflections. Each branch at level i in the tree must fan-out into n branches at level i+1 each with n times the impedance of the line entering the branch point [22]. This configuration is known as a tapered tree. The clock signal travels from root-to-leaf in this network following congruent paths both in wire geometry (width and length of all wire segments) and the clock buffer configuration (size, number and location) so barring any manufacturing and environmental variation in the paths, the total clock delay for each path will be constant, resulting in zero skew between any two paths.

## 2.4.2. Asymmetric buffered clock trees

An asymmetric buffered clock tree is the most commonly used form of clock distribution for ASICs [14]. The majority of modern clock networks are designed with this approach using specialized CAD tools. These tools start with the location of each of the clocked elements and generate a suitable tree structure by varying the wire length, the buffer sizing and the fan-out at each branch point to achieve near-zero clock skew between all of the sequentially adjacent registers. Figure 2.4 shows a typical asymmetric

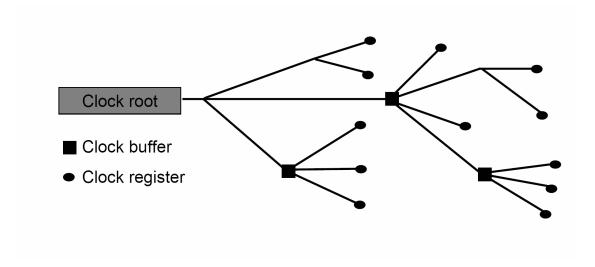

Figure 2.4: Asymmetric buffered clock tree.

clock tree. It is also possible for an automated clock tool to use the design specification for each of the clocked elements, specifically the acceptable range of clock arrival times considering its dependencies on a device's sequentially adjacent components. The clock layout tool will take this information, also known as a *skew schedule*, and create a suitable clock tree. While this approach can make use of beneficial skew to increase performance, it also creates dependencies on the clock arrival time of many registers so that changing one portion of the design could require complete regeneration of the clock network.

## 2.4.3. Clock mesh

Since devices and interconnect across an IC will exhibit variances in characteristics due to manufacturing discrepancies, clock skew might occur due to the mismatched clock delays from clock root-to-leaves. The primary sources of the

mismatch are the clock buffers, specifically the mismatch between buffers that cause devices at a given level of the network to switch at different times [26]. One approach to counteract this is to shunt all of the buffer outputs at a given level, creating a *clock mesh* [16]. These shunts delay the switching of buffers that are too fast, and speed up the switching of buffers that are too slow. The primary drawback of this approach is the increased power consumption caused by the short circuit currents that will exist in the presence of device variation. An additional drawback is the large interconnect cost of connecting points that get progressively further from one another for every additional tree level. Due to the transport delay of the shunt signals, this methodology cannot completely eliminate clock uncertainty. However, due to its ability to compensate for some variation in the clock network, this is the most commonly applied clock architecture in high performance microprocessors despite its cost. This approach usually requires a global clock tree to feed the different portions of the mesh with quasi-simultaneous clocks [27].

## 2.4.4. Resonant clocking

Resonant clocking is a newer approach to clock networks that requires removing all the clock buffers and creating an LC-tank to allow a natural oscillation in the clock signal that requires less energy to maintain than a traditional network [28],[29],[30]. In an ideal configuration, the energy consumption would be zero, but due to the resistance of the metal lines in the network, the configuration is lossy. The LC-tank is formed by

adding an inductor and using the capacitance of the clock leaves. Resonant clock networks have demonstrated power savings of over 50% and IC core power savings of between 20-35% when compared to conventional networks [31],[32]. One of the drawbacks of the system is its use of sinusoidal clock signals, which can create short circuit currents because their long rise and fall times, and are much more susceptible to clock jitter when compared to clocks with sharper edges. Resonant clocking requires modified registers and latches that are compatible with sinusoidal clocks [33],[34]. Current research in resonant clocking deals with approaches and techniques to minimize jitter and noise [30],[35].

## 2.4.5. Standing and traveling wave network

A *standing* wave clock network presents another approach to distribute clock signals [36]. A standing wave is formed by superimposing a forward clock produced by an AC voltage source with a return clock, produced by reflecting the forward clock back from a ground termination at the opposite end of the conductor. This approach ideally creates a zero skew set of clocks along the length of the line with amplitudes that vary between 0 and the initial amplitude of the AC source depending of the position of sampling [37]. The resulting clocks then need to be regenerated and possibly converted to a square wave for use. Certain portions of the clock line's output will be unusable since the low amplitude signal in that area will render it unrecoverable.

Travelling waves are used in clock networks to create clocks that allow full voltage swing at all sampling points. These networks usually use a rotary clock ring [38],[39],[40] to create the traveling wave along a pair of conductors separated by a series of cross-coupled inverters to regenerate the signals and maintain the oscillations. The frequency of each of these rings will vary depending on the line length, so a number of these rings are usually interconnected to create a mesh with greater tolerance to variability [41]. The primary drawback of this approach is that unlike with standing wave clock networks, the phase of the clock signal will vary depending on the location of the sampling and every point in a ring will only be in phase with its corresponding point in every other ring. This leads to significant difficulty in designing synchronous circuitry using this technology.

## 2.4.6. Hybrid structures

Modern clock networks usually use a mixed clocking strategy, pairing one global clock routing technique to another local routing technique [42]. A common pairing would be a global H-tree followed by a local mesh [16],[43], minimizing the power consumption of the mesh while maintaining low local variability. Link insertion [44]-[47] is another approach used to shunt selected portions of the clock networks that should have zero skew, thereby realizing many of the benefits of clock meshes. Transport delay through the shunt wires will prevent this method from eliminating all skew. Typically, the global distribution can be constructed using a mesh or tree, and the local network can use a

Figure 2.5: Grover's serial clock distribution [48].

tree, mesh or fishbone structure [16]. A fishbone structure has a clock trunk with leaves arbitrarily attached orthogonally to the trunk wherever the clock is needed. We will denote any connection point between a global and local clock domain as a *clock tap*.

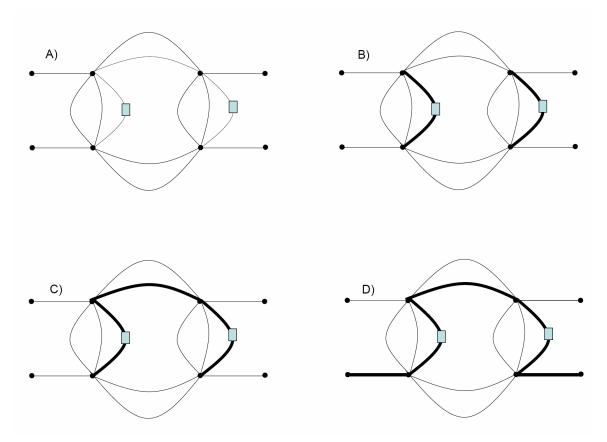

### 2.4.7. Serial clock distributions

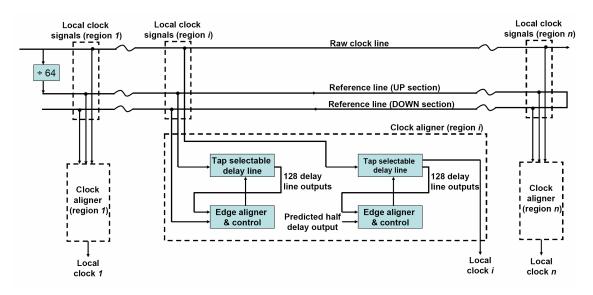

Serial clock distributions are a less common form of clocking that aligns each tap clock to a position directly in between two reference clocks traveling in opposite directions (with respect to their phase). This *averaging* technique was first proposed by Grover et al. [48], Figure 2.5. Their scheme uses a 3-wire method with separate raw clock, forward reference line and reverse reference line, with the reference lines tied at the far end of the clock distribution. However this technique requires two distinct clock alignments to synchronize each local tap. First, the pulse interval between the forward

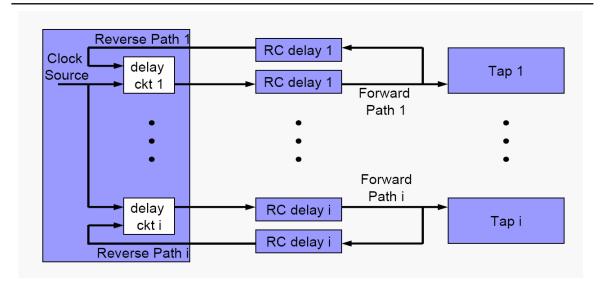

and reverse signal is found by delaying the forward (UP) signal to align with the reverse (DOWM) signal. This interval is halved to create a local half pulse reference signal  $P_{nalf}$ . The  $P_{nalf}$  signals in every clock region will be ideally synchronized due to averaging. Next, the raw clock is aligned to the region's  $P_{half}$  signal to generate the local clock. The delay is created using a 128-element non-inverting buffer chain. A 128:1 multiplexer is used to choose the appropriate tap, setting the accuracy of each alignment to the propagation delay through the non-inverting buffer. Another drawback is that reference clock lines may exhibit different propagation delay than the raw clock line due to differences in geometry and signal frequency. As such, [48] is susceptible to skew from wire mismatches between the reference and the raw clock lines. The system's lack of buffering in the clock path also limits the total load, the distance between taps and the number of taps that the reference line can spawn.

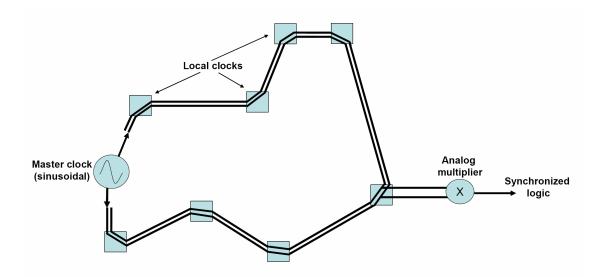

Work in [49] uses an averaging approach for synchronizing digital signals using a two-wire method. This technique has recently been employed by Banu and Prodanov [50] in another configuration that uses a serially distributed layout that is similar to our own<sup>2</sup>, but the averaging technique they use is distinct, using analog multipliers at each tap to create the required averaging, Figure 2.6. Their technique provides low skew, but creates a set of sinusoidal clocks that are not of full swing and require level shifting blocks at each tap to be useful in most designs, similar to standing wave systems.

\_

<sup>&</sup>lt;sup>2</sup> Banu and Prodanov's work [50] was published September 10, 2006, shortly after our initial publication [7] on August 6, 2006.

Figure 2.6: Banu and Prodanov's bufferless approach [50].

Because of the transmission line nature of their clock network, their method does not permit the use of buffers or logic within the clock network, making the system very rigid. The analog components can consume more power than the digital components employed by our system due to non-zero static bias currents. They describe their system as one that uses *bi-directional* signalling, which differs from our use of the term. The authors of [50] use the term to describe the transport of signals propagating in opposite directions along *two* wires, where we will use the *same* conductor (time-multiplexed).

## 2.4.8. Reconfigurable clocks networks

All of the previously described networks must be created following the design of the logic, and once established cannot be modified since changing the clock delay to one register will affect the clock skew between it and every one of its sequentiallyadjacent registers. Present day designs incorporate many clock domains on the same die and special consideration is needed when communicating between them. Many integrated circuits are designed by combining a number of different blocks from different sources and require that these components work flawlessly with one another for an array of different applications [51]. Connecting these components together in different configurations based on the specific application is not an easy task for standard IC clock networks. Field programmable gate arrays (FPGAs) are generalized devices that may be used for a variety of applications, so their clock domains must be flexible to work for a variety of applications. For example, the Altera Stratix IV series of FPGAs can support up to 16 global clocks that can be routed anywhere on the device and up to 88 regional clocks [52]. For the most part, FPGAs use a spine-and-ribs (fishbone) structure to connect regional and local registers, so the flexibility created by this approach comes at the expense of skew tolerance.

# 2.5. Skew compensation

Deep submicron technologies exhibit an ever-increasing susceptibility to process variation [53]. When comparing the effect that process variance has on a clock network, the variation between individual devices must be examined. While a certain amount of die-to-die variation is always present, this does not create skew since every device on a die will be equally affected. There is also a discrete component that will exist between

every distinct device on a die that is roughly proportional to the effective size of the transistors [54]. Discrete mismatch will always be present no matter how closely located two devices are. With smaller transistor sizes, there is a discretization of the dopant levels in each device leading to greater fluctuations in threshold voltage and subsequently in delay through a device. Electron mobility and mismatch between devices are also phenomena, which can be deemed statistically independent for different devices [55]. Finally there is a distance-related component for variation that will increase depending on how far devices are from one another. This usually occurs gradually, with the possible difference between the behaviour of two devices increasing the further apart they are. Two devices located very close to one another will not be greatly affected by proximity dependent mismatch. While a 10% of clock period rule of thumb has traditionally been assumed for clock skew, this number is easy to surpass with process variance in today's newest technologies [56].

Programmable clock buffers and interconnect which require post-silicon tuning have been introduced to compensate for process variation for selected regions of a clock network [57]. Die temperature can also cause significant variation in the behaviour of buffers in a clock distribution network. Worse, the die temperature will vary depending on local switching activity leading to temperature gradients across the die that will change over time. Increased power density in ICs amplifies this problem by making modern ICs run hotter than before. Localized temperature spikes, or *hotspots* can severely impact the skew in a clock network [58]. Temperature and process variance can result in delay

changes of over 50% for sub-65 nm devices [59]. The authors of [60] have developed a clock network with self-adjusting delay buffers to cope with temperature variation, but their methodology is designed to only cope with intra-die temperature fluctuations and not localized temperature gradients. Traditional dynamic temperature management techniques are limited by the accuracy of their temperature sensors [61].

Traditionally, clock network generation tools distribute clock buffers according to user-defined specifications using a combination of matching wire length and adjusting the placement and sizing of clock buffers to achieve the desired delay [14], but variability is making this passive skew reduction technique less effective. Some clock networks use active clock skew reduction techniques to reduce the effect of process variation [14]. Active clock skew reduction techniques use controllers and feedback structures to modify the local clocks and provide de-skewing capability, usually using delay lines to perform the adjustment. This technique can use significant system resources during operation due to the large number of local clocks that must be synchronized in a clock distribution network. Some active techniques do not therefore operate on all of the clock taps, limiting their use to de-skew only two clocks with respect to one another [62], such as with two halves of a clock tree. Multi-point skew reduction techniques have become more popular since they are better able to cope with the large die and high-speed clocking environments that are common [63], but any controllers required must typically be either re-used or replicated for each tap. The overhead of active skew reduction techniques translates to higher power consumption than their passive counterparts.

Some schemes simply employ skew reduction techniques on existing tree distributions [64],[65], but can require extra wiring or a power overhead due to their heavy resource usage. The configuration of Kapoor's approach [66] uses a distribution tree and a co-located feedback tree and employs skew compensation at every leaf as shown in Figure 2.7. Some schemes perform root-to-leaf skew compensation at the root or leaf for each local area on the IC [67],[68]. This configuration creates a need for a feedback line from every synchronization point to the source. These feedback lines are subject to the same trace matching discrepancies present with H-trees, introducing error to the skew compensation technique [64]. The star configuration of Lee's system [67] employing skew compensation at the root for every leaf is shown in Figure 2.8.

# 2.6. Clock power

Increased die size and device density of integrated circuits has led to a marked increased in the power consumption of deep submicron designs. The clock can consume the largest portion of on-chip power, often over 25% of the total power [69]. There are three broad sources of power consumption in a device: short-circuit power  $P_{sc}$ , leakage power  $P_{leak}$  and dynamic switching power  $P_{dyn}$ . All three of these also contribute to clock power  $P_{clk}$ . Short-circuit power results from crow-bar currents that occur when both pull-up and pull-down portions of a gate simultaneously conduct while the input voltage is transitioning.

Figure 2.7: Kapoor's skew-tolerant clock tree [66].

Short circuit power is proportional to  $V_{dd}$ - $|V_{tn}|$ - $|V_{tp}|$ , the clock frequency, and the rise and fall times of the input signals.  $V_{dd}$  is the supply voltage, and  $V_{tn}$  and  $V_{tp}$  are the threshold voltages of the pull-down and pull-up devices, respectively. There is no short-circuit current when either pull-up or pull-down blocks are not conducting and it is

Figure 2.8: Lee's skew compensation scheme [67].

impossible for both of these to conduct when the sum of their threshold voltages exceeds the supply voltage. Since current technologies rely on decreased supply voltage, short circuit power is decreasing as  $V_{dd}$  approaches  $|V_{tn}| + |V_{tp}|$ . Another useful design approach is to use signals with high slew rates, ensuring that input signal transition times are not much longer than the output signal transition time.

Leakage power creates non-zero static current in an IC. There are three major contributors to leakage power: *gate oxide leakage* which allows current to flow through the gate of devices, *sub-threshold threshold* which allows current between transistor drain and source when devices are supposed to be in a non-conducting state and *junction leakage* across the reverse-biased diodes in the diffusion area of the transistors [13],[70],[71]. Generally speaking, leakage power is increasing in newer technologies due to a decrease in threshold voltage and an increase in operating temperature. However, the total power consumption decreases overall due to lower supply voltages. Clock networks are less affected by leakage power than logic circuits since clock power is

dominated by the dynamic power of the clock buffers due to the large capacitances involved. As a result, clock networks are better able to take advantage of decreased supply voltages and the proportion of device power consumed by clock networks will decrease in future process generations [69].

Dynamic power consumption is the dominant factor in overall power consumption in an integrated circuit, decreasing relative to the total power consumed, typically around 80%, but increasing absolutely due to the greater number of devices on an IC and the increase in the operating frequency of newer devices. The dynamic power in an integrated circuit is:

$$P_{dyn} = K \cdot C_L \cdot V_{dd}^2 \cdot f \tag{2.5}$$