# Krylov Subspace Techniques on Graphic Processing Units

# Maryam Mehri Dehnavi

Doctor of Philosophy

Department of Electrical and Computer Engineering

McGill University

Montreal, Quebec, Canada

July 02, 2012

To my parents and Farhad

#### ABSTRACT

Computations related to many scientific and engineering problems spend most of their time in solving large, sparse linear systems. Improving the performance of these solvers on modern parallel architecture enables scientists to simulate large accurate models and manipulate massive amounts of data in reasonable time frames. Krylov subspace methods (KSM) are iterative techniques used to solve large sparse systems. The main time consuming kernels in KSMs are sparse matrix vector multiplication (SpMV), vector operations (dot products and vector sums) and preconditioner manipulation. This work presents techniques and algorithms to accelerate some of these kernels on a recent generation of parallel architecture called manycore processors. The performance of the proposed optimizations are tested on graphic processing units (GPUs) and compared to previous work.

The SpMV kernel is accelerated on GPUs and speedups of up to 3.3 times are achieved compared to previous GPU implementations of the algorithm. The conjugate gradient iterative solver is accelerated on NVIDIA graphic cards and a 12.9 fold speedup is achieved compared to optimized implementation of the kernel on multicore CPUs. The sparse approximate inverse preconditioner is accelerated on GPUs and used to enhance the convergence rate of the BiCGStab iterative solver. The preconditioner is generated on NVIDIA GTX480 in the same time as it takes 16 AMD 252 Opteron processors to generate the same preconditioner.

Communicating data between levels of a memory hierarchy and processors is time consuming and costly in KSMs. Communication-avoiding (CA) Krylov solvers take k steps of a KSM for the same communication cost as one step to reduce the communication overhead in standard KSMs. The matrix powers kernel in communication-avoiding Krylov solvers is accelerated on NVIDIA GPUs and

speedups of up to 5.7 are achieved for the tested problems compared to the standard implementation of k SpMV kernels.

## **ABRÉGÉ**

Les calculs liés à de nombreux problèmes scientifiques et techniques demandent qu'on consacre beaucoup de temps à la résolution de grands systèmes linéaires creux. Améliorer la performance de ces résolveurs sur l'architecture paralléle moderne permet aux scientifiques de simuler de grands modèles précis et de manipuler une quantité massive de données dans des délais raisonnables. Les méthodes sous-espaces Krylov (KSM) sont des techniques itératives utilisées pour résoudre de grands systèmes creux. Les noyaux principaux qui demandent beaucoup de temps dans les KSMs sont la multiplication matrice-vecteur creuse (SpMV), les opérations sur les vecteurs (produits scalaires et sommes vectorielles) et la manipulation de préconditionneur. Ce travail présente les techniques et les algorithmes pour accélérer certains de ces noyaux sur une génération récente d'architecture parallèle appelée processeurs multicoeurs. La performance des optimisations proposées est testée sur des processeurs graphiques (GPU) et comparée aux travaux antérieurs.

Le noyau SpMV est accéléré sur les processeurs graphiques et des accélérations jusqu'à 3.3 fois plus rapides sont atteintes par rapport aux implémentations de l'algorithme des processeurs graphiques précédents. Le gradient conjugué du résolveur itératif est accéléré sur des cartes graphiques NVIDIA et une accélération 12.9 fois plus rapide est réalisée par rapport à l'implémentation optimisée du noyau sur des processeurs multicœurs. Le préconditionneur approximatif inverse creux est accéléré sur les processeurs graphiques et utilisé pour améliorer le taux de convergence du résolveur itératif BiCGStab. Le préconditionneur est généré sur un NVIDIA GTX480 pour la même durée nécessaire à 16 processeurs AMD Opteron 252 pour générer le même préconditionneur.

La communication de données entre les niveaux d'une hiérarchie de mémoire et des processeurs est longue et coûteuse en KSMs. Les résolveurs sans communication (communication-avoiding ou CA) de Krylov n'utilisent qu'un nombre k d'étapes d'une méthode de sous-espace de Krylov (KSM) pour un coût de communication équivalent comme une étape qui permet de réduire les frais généraux des communications dans les KSMs standards. Le noyau des pouvoirs de matrice dans les résolveurs de Krylov sans communication est accéléré sur les processeurs graphiques NVIDIA et des accélérations jusqu'à 5.7 plus rapides sont atteintes pour les problèmes testés par rapport à l'implémentation standard de k des noyaux SpMV.

## **ACKNOWLEDGMENTS**

I would like to express my greatest gratitude to my supervisor Prof. Dennis Giannacopoulos for his priceless feedback, inspiration and guidance throughout my PhD. His great interest and inspiration in initiating collaboration with other research groups has allowed me to work with world renowned research groups which has opened great windows to my future and work. I would also like to thank Professor Jean-Luc Gaudiot for his guidance and support during my visit to the parallel systems & computer architecture laboratory (PASCAL) in UC-Irvine.

I am very grateful to Professor James Demmel and members of the Berkeley benchmarking and optimization (BeBOP) group which I collaborated with during my six month visit to UC-Berkeley. Finally I would like to greatly thank David Fernandez a very talented colleague of mine whom I have collaborated with throughout my studies.

# TABLE OF CONTENTS

| TABLE OF  | F CONTENTS                                           | vi |

|-----------|------------------------------------------------------|----|

| LIST OF T | ABLES                                                | ix |

| Chapter 1 | Introduction                                         | 1  |

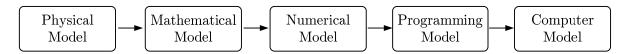

| 1.1       | Scientific Computing                                 | 2  |

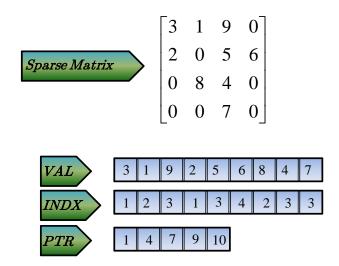

| 1.2       | Systems of Linear Equations                          | 3  |

| 1.2.1     | The Solution of Linear Systems of Equations          | 4  |

| 1.2.2     | Krylov Subspace Techniques                           | 5  |

| 1.2.3     | Kernels in Krylov Methods                            | 6  |

| 1.2.4     | Preconditioning                                      | 8  |

| 1.2.5     | Reducing Communication in Krylov Techniques          | 9  |

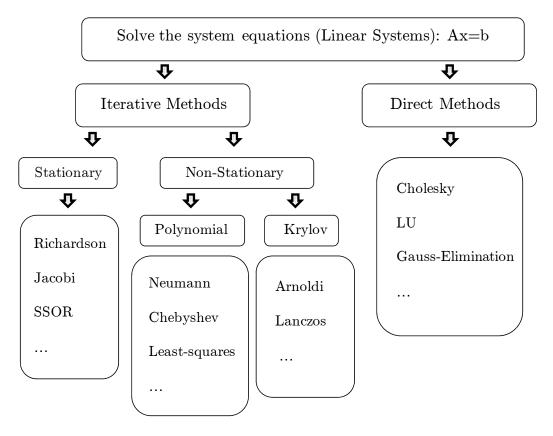

| 1.3       | Sparse Matrices                                      | 10 |

| 1.3.1     | Types of Sparse Matrices                             | 10 |

| 1.3.2     | Sparse Matrix Storage Formats                        | 10 |

| 1.4       | Parallel Scientific Computation                      | 12 |

| 1.5       | Summary                                              | 14 |

| 1.6       | Thesis Outline and Contributions                     | 14 |

| Chapter 2 | Parallel Computing and Graphic Processing Units      | 17 |

| 2.1       | Classification of Computer Architectures             | 17 |

| 2.2       | Parallel Memory Architectures and Programming Models | 18 |

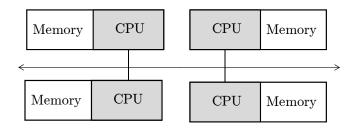

| 2.2.1     | Distributed Memory                                   | 18 |

| 2.2.2     | Shared Memory                                        | 18 |

| 2.2.3     | Hybrid Distributed-Shared Memory Model               | 19 |

| 2.3       | Graphic Processing Units                             | 19 |

| 2.4       | NVIDIA GPUs                                          | 22 |

| 2.5       | CUDA Programming Model                               | 23 |

| 2.5.1     | CUDA Threads and Kernel Execution on GPUs            | 24 |

| 2.5.2     | Thread Scheduling                                    | 24 |

| 2.6       | Performance Optimization in CUDA                     | 26 |

| 2.6.1     | Memory Coalescing                                    | 26 |

| 2.6.2     | Avoiding Shared Memory Bank Conflicts                | 27 |

| 2.6.3     | Increasing Occupancy                                 | 28 |

| 2.6.4     | Avoiding Thread Divergence                           | 29 |

| 2.6.5     | Identifying Performance Limiters                     | 29 |

| 2.6.6     | Other optimizations                                  | 29 |

| 2.7       | CUDA Libraries                                       | 31 |

| 2.8       | Summary                                              | 32 |

| Chapter 3 | Finite Element Sparse Matrix Vector Multiplication on Graphic Processing Units $34$ |                  |

|-----------|-------------------------------------------------------------------------------------|------------------|

| 3.1       | Introduction                                                                        | 34               |

| 3.2       | GPU Architecture                                                                    | 35               |

| 3.3       | Sparse Matrix Vector Multiplication                                                 | 36               |

| 3.4       | PCSR (Prefetch-Compressed Row Storage Format)                                       | 37               |

| 3.4.1     | Previous Work                                                                       | 38               |

| 3.4.2     | The PCSR Algorithm                                                                  | 39               |

| 3.4.3     | Prefetching                                                                         | 42               |

| 3.5       | Results                                                                             | 42               |

| 3.6       | Conclusion                                                                          | 46               |

| Chapter 4 | Enhancing the Performance of Conjugate Gradient Solvers on Gr                       | aphic Processing |

| Units     |                                                                                     | 48               |

| 4.1       | Introduction                                                                        | 48               |

| 4.2       | GPU Architecture                                                                    | 49               |

| 4.3       | Preconditioned Conjugate Gradient                                                   | 50               |

| 4.4       | Implementing PCG on GPUs                                                            | 53               |

| 4.5       | Results                                                                             | 56               |

| 4.6       | Conclusion and Future Work                                                          | 60               |

| Chapter 5 | Parallel Sparse Approximate Inverse Preconditioning on Graphic Proc                 | essing Units 62  |

| 5.1       | Introduction                                                                        | 63               |

| 5.2       | Sparse Approximate Inverse (SAI) Preconditioning                                    | 66               |

| 5.3       | Parallel SAI in NVIDIA GPUs                                                         | 70               |

| 5.3.1     | GSAI Steps                                                                          | 72               |

| 5.3.2     | Memory Allocation                                                                   | 77               |

| 5.4       | Results                                                                             | 80               |

| 5.4.1     | The GSAI Preconditioning Method                                                     | 81               |

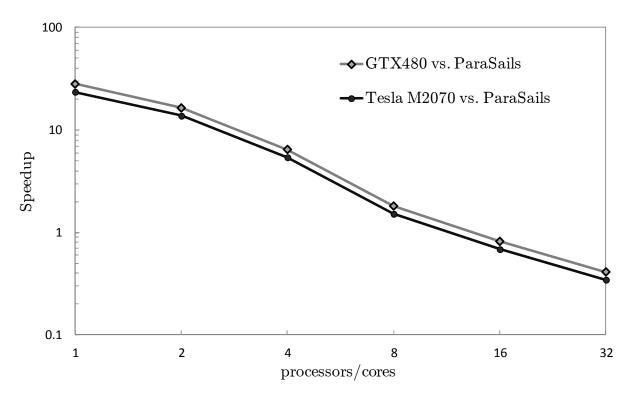

| 5.4.2     | GSAI vs. ParaSails                                                                  | 83               |

| 5.5       | Conclusion and Future Work                                                          | 84               |

| Chapter 6 | Communication-avoiding Krylov Techniques on GPUs                                    | 93               |

| 6.1       | Introduction                                                                        | 93               |

| 6.1.1     | Communication-avoiding Krylov techniques                                            | 93               |

| 6.1.2     | NVIDIA GPUS                                                                         | 94               |

| 6.2       | Previous Work                                                                       | 95               |

| 6.3       | Implementation Details                                                              | 97               |

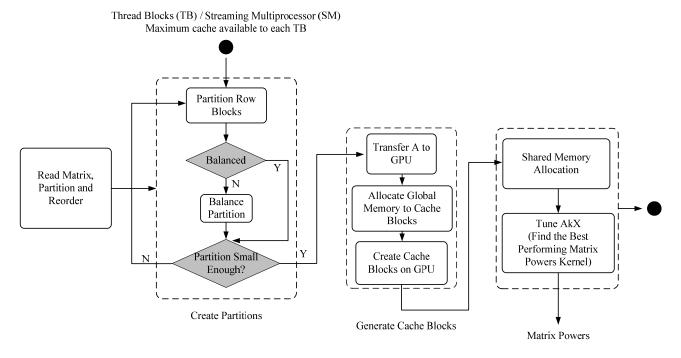

| 6.3.1     | Matrix Powers on GPU Global Memory                                                  | 97               |

| 6.3.2     | Matrix Powers on GPU Shared Memory                                                  | 99               |

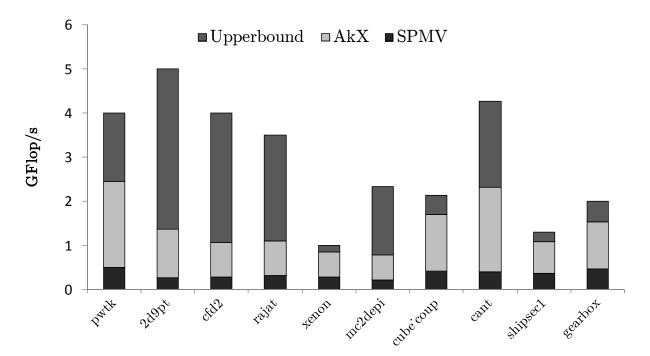

| 6.4       | Results                                                                             | 101              |

| 641       | Matrix Powers on GPII Global Memory                                                 | 102              |

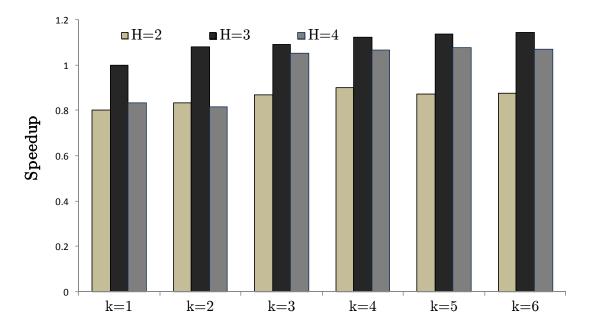

| 6.4.2       | Matrix Powers on GPU Shared Memory | 105 |

|-------------|------------------------------------|-----|

| 6.5         | Conclusion and Future Work         | 107 |

| Chapter 7   | Conclusion and Future Work         | 109 |

| 7.1         | Conclusion                         | 109 |

| 7.2         | Future Work                        | 111 |

| References  |                                    | 112 |

| Appendix I  | The BiCGStab Iterative Technique   | 118 |

| Appendix II | NVIDIA GPU Specifications          | 119 |

# LIST OF TABLES

| Table 2.1: CUDA Math Libraries                                                                       |

|------------------------------------------------------------------------------------------------------|

| Table 2.2: Application-Specific Libraries                                                            |

| Table 3.1: Non-zeros (nnz) and filling ratio percentage for different padding factors (n) in         |

| matrices                                                                                             |

| Table 3.2: Speedup of PCSR compared to the row-per-thread and row-per-warp methods or                |

| GT8800, the CPU and the Cell architectures42                                                         |

| Table 4.1: Sparse matrices used for testing                                                          |

| Table 4.2: Speedup of the optimized PCG compared to PCG row-per-warp (RW) on GPU                     |

| vectorized and non-vectorized CPU                                                                    |

| Table 5.1: The number of elements in each of the data structures involved in GSAI and their siz      |

| based on their data                                                                                  |

| Table 5.2: The effect of increasing tolerance ( $\tau$ ) on the number of iterations (GSAI or        |

| GTX480)                                                                                              |

| Table 5.3: Properties of sparse matrices used to test the GSAI preconditioning method86              |

| Table 5.4: The effect of increasing tolerance $(\tau)$ on the total execution time involving both th |

| preconditioner construction time and the solve time (GSAI on GTX480)8                                |

| Table 5.5: The effect of increasing tolerance $(\tau)$ in the GSAI algorithm (on GTX480) on the      |

| preconditioner construction time                                                                     |

| Table 5.6: The time spent in computing the stages in Fig. 5.2 for $\tau = 0.9$ on GTX48090           |

| Table 5.7: Preconditioned and unpreconditioned BiCGStab iterative solver on GTX480 and               |

| TESLA 207090                                                                                         |

| Table 5.8: ParaSails execution time compared to GPU results                                          |

| Table 6.1: The best speedup of the matrix powers kernel compared to naïve SpMV, fraction of          |

| total time spent in communicating data in the naïve SpMV implementation and extra computed           |

| flops in the matrix powers kernel performing $k$                                                     |

| Table 6.2: The extra floating point operations performed in the matrix powers kernel for shared      |

| memory compared to naïve the SpMV implementation and the total number of thread block                |

| launched for each $k$ .                                                                              |

# LIST OF FIGURES

| Fig. 1.1: Hierarchy of high performance scientific computing [1]                                     |

|------------------------------------------------------------------------------------------------------|

| Fig. 1.2: Solvers for linear systems of equations                                                    |

| Fig. 1.3: Compressed sparse row storage format                                                       |

| Fig. 1.4: Compressed format representation of diagonal matrices                                      |

| Fig. 1.5: The Ellpack-Itpack format of the A matrix from Fig. 1.4                                    |

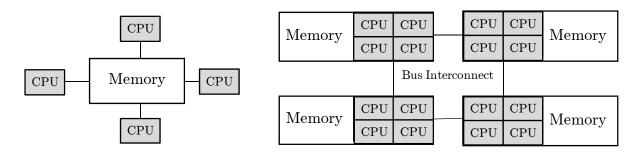

| Fig. 2.1: The general memory model of distributed parallel architecture [35]                         |

| Fig. 2.2: Uniform Memory Access (left figure) and Non-Uniform Memory Access (right figure)           |

| shared memory architecture [35]                                                                      |

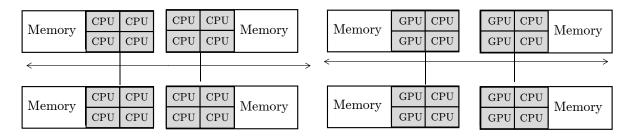

| Fig. 2.3: A hybrid CPU memory model (left figure) and a hybrid CPU-GPU memory model (right           |

| figure) [35]                                                                                         |

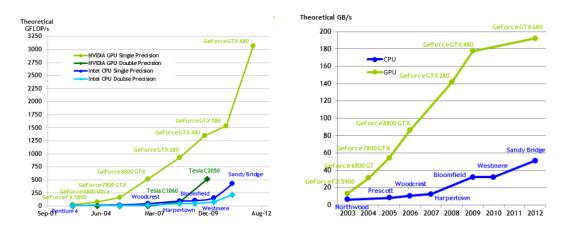

| Fig. 2.4: CPU and GPU floating point operations per second and memory bandwidth (from                |

| NVIDIA programming guide [42])20                                                                     |

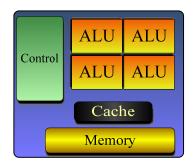

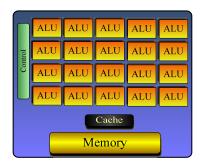

| Fig. 2.5: Compute (ALU) control and memory resources in CPU (left figure) and GPUs (right            |

| figure)                                                                                              |

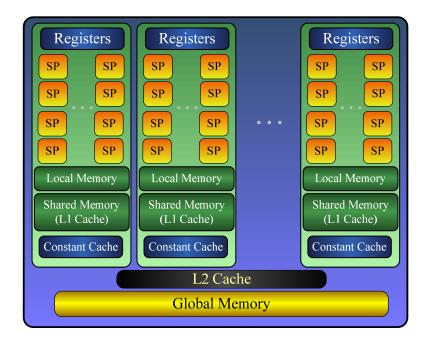

| Fig. 2.6: The underlying architecture of NVIDIA Fermi GPUs                                           |

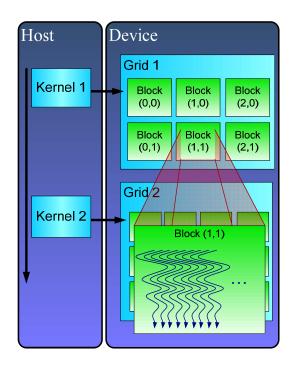

| Fig. 2.7: Kernel/thread execution model on NVIDIA GPUs (SM represents the streaming                  |

| multiprocesors on the graphic card, the host and the device are the CPU and GPU respectively).       |

| 25                                                                                                   |

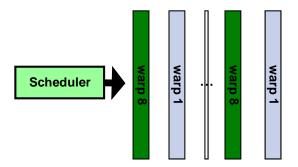

| Fig. 2.8: The warp scheduler chooses the next warp ready for execution                               |

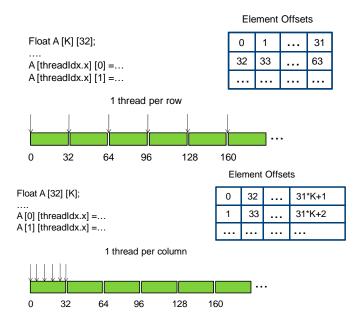

| Fig. 2.9: The first figure shows threads within a warp accessing data in the 2D array $A$ in strided |

| pattern, when the array is transposed (second figure) data is accesses contiguously allowing for     |

| coalesced memory accesses                                                                            |

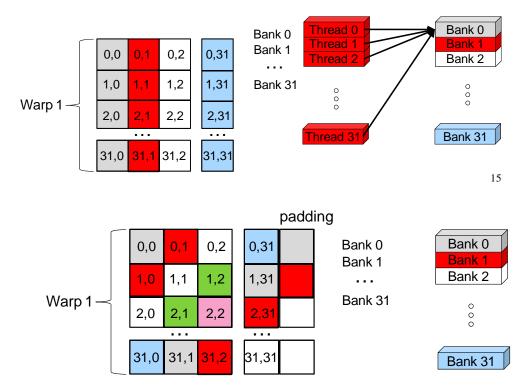

| Fig. 2.10: Row major storage of a $32 \times 32$ matrix in shared memory when each warp accesses one |

| column causes bank conflicts (first figure) which can be resolved by padding the matrix with an      |

| extra column (second figure)                                                                         |

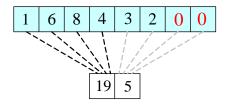

| Fig. 2.11: Padding a vector to be a multiple of 4 and reducing it in parallel30                      |

| Fig. 3.1: The GT8800 underlying architecture.                                                        |

| Fig. 3.2: The CSR SMVM algorithm.                                                                    |

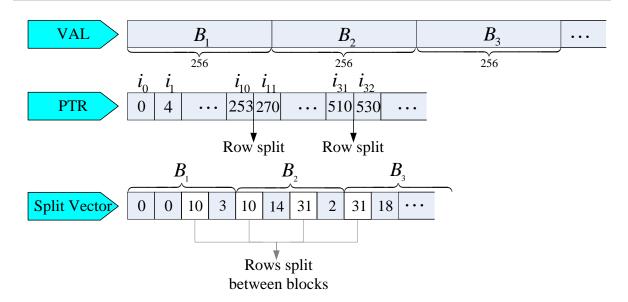

| Fig. 3.3: PCSR partitioning scheme, (e.g. row 10 is partitioned between blocks 1 and 2 $(B1$ and     |

| B2); the <i>split vector</i> shows that 3 elements of row 10 are stored in B1 and 14 in B2)40        |

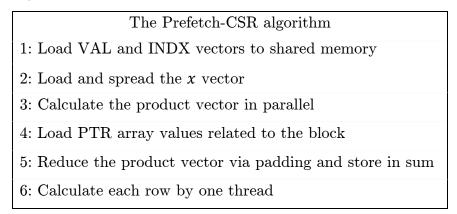

| Fig. 3.4: The Prefetch-CSR algorithm.                                                                |

| $Fig. \ 3.5: \ Prefetching \ data \ in \ PCSR \ (a) \ without \ prefetching, \ (b) \ with \ prefetching. \\ \dots \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

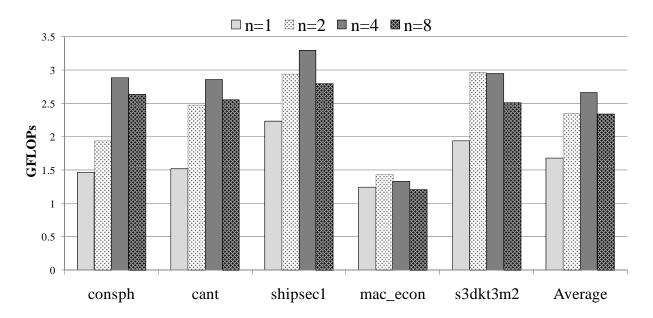

| Fig. 3.6: The effect of the padding factor (n) in PCSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

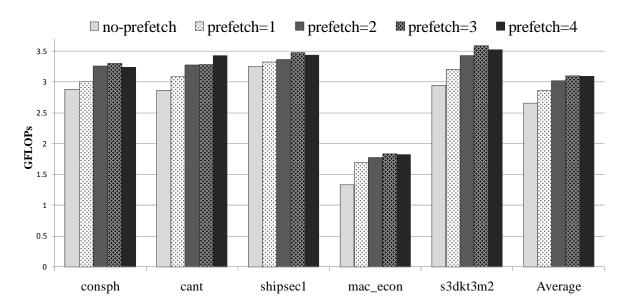

| Fig. 3.7: Varying the number of prefetches in PCSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

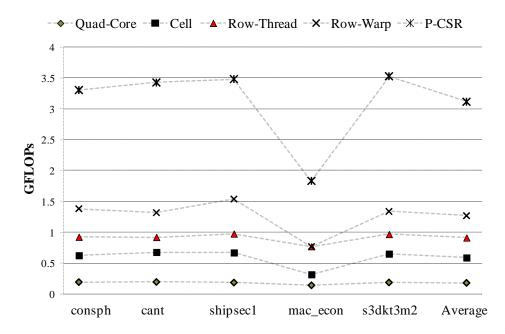

| Fig. 3.8: PCSR performance compared to the row-per-thread and row-per-warp methods on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GT8800 as well as the QUAD-Core CPU and Cell architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

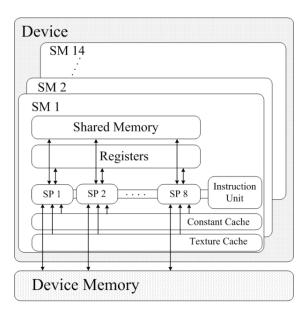

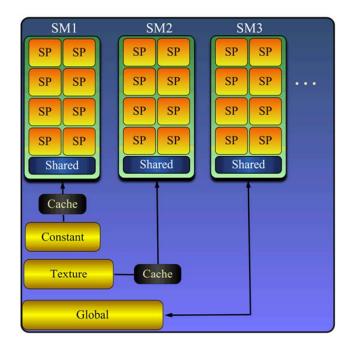

| Fig. 4.1: NVIDIA GPU architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

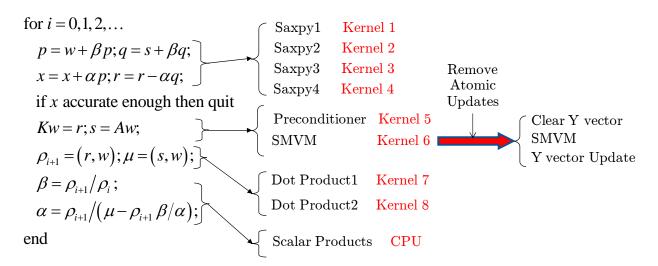

| Fig. 4.2: Highlighting several bottleneck operations in PCG Shewchuk [7] vs. PCG Chronopoulos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [8]51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Fig. 4.3: PCG Chronopoulos $[8]$ algorithm implemented on the GPU, optimizing PCSR $[53]$ adds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| two new kernels to the implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

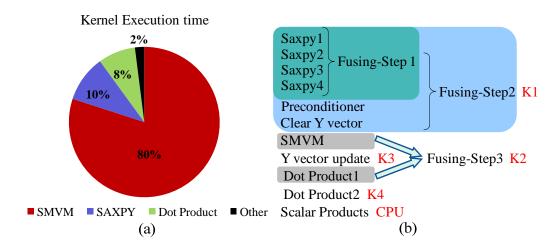

| Fig. 4.4: (a) Percentage of the average execution time of kernels in the PCG Chronopoulos, (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fusing kernels in PCG (K1 to K4 represent the kernels in optimized PCG). $$ 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

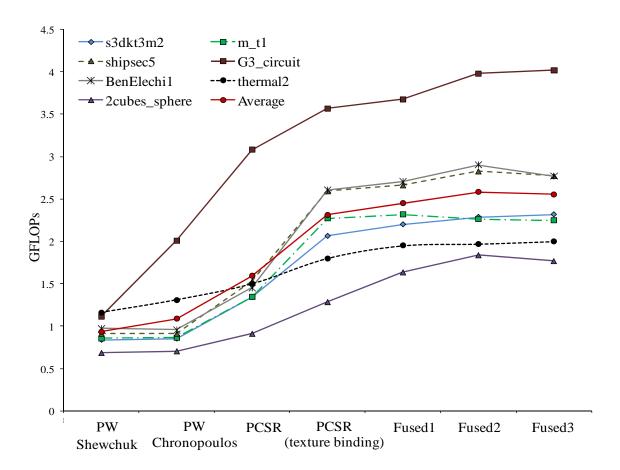

| Fig. 4.5: The effect of the optimizations proposed in Section 4.4 in increasing the performance of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| the PCG algorithm on GT8800.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

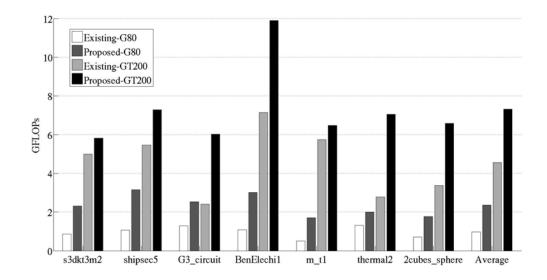

| Fig. 4.6: Performance of the PCG-Row-per-warp [49] method compared to proposed optimized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCG Chronopoulos [8] algorithm on G80 and GT200.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Fig. 5.1: Steps involved in constructing static sparse approximate inverse preconditioners68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

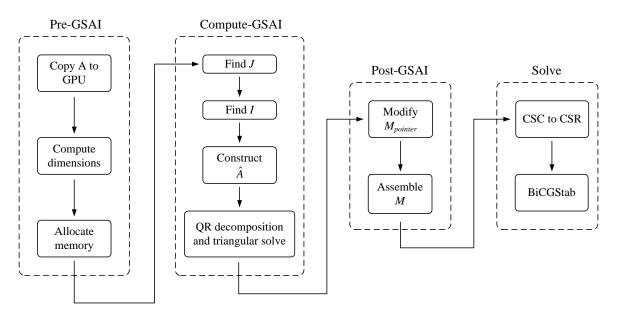

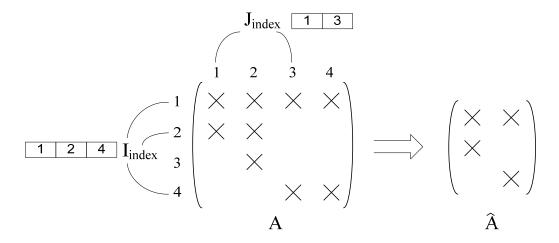

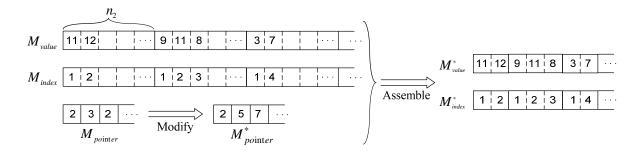

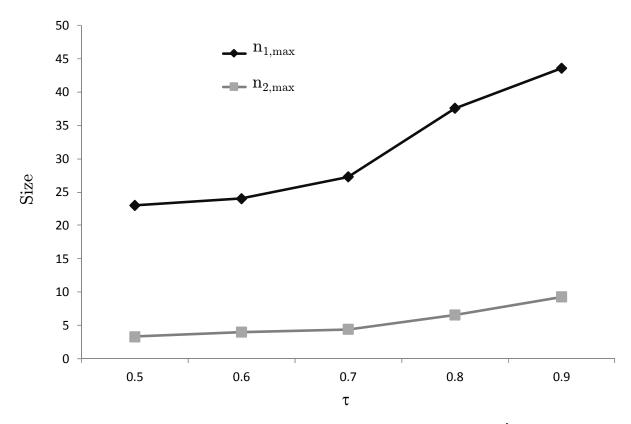

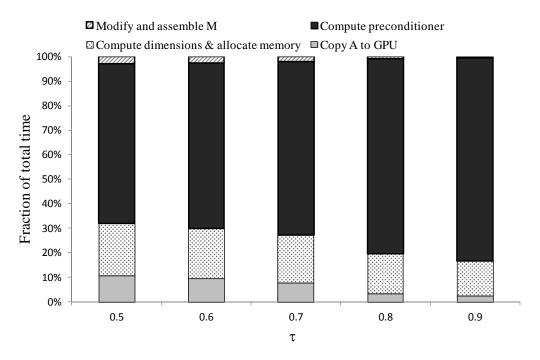

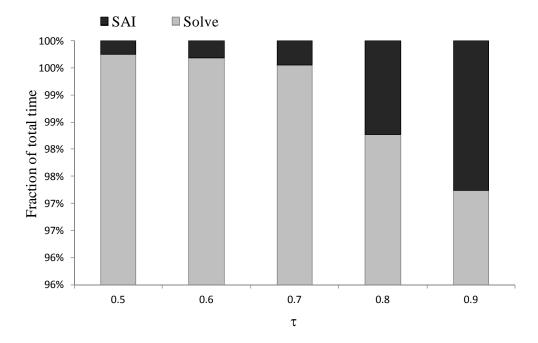

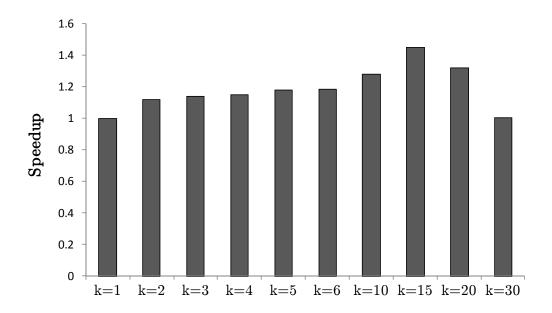

| Fig. 5.2: The four stages in implementing SAI preconditioners using GSAI on NVIDIA GPUs $\dots$ 70 $\dots$ 71 $\dots$ 71 $\dots$ 71 $\dots$ 71 $\dots$ 72 $\dots$ 73 $\dots$ 70 $\dots$ 70 $\dots$ 70 $\dots$ 71 $\dots$ 71 $\dots$ 71 $\dots$ 71 $\dots$ 72 $\dots$ 73 $\dots$ 70 $\dots$ 71 $\dots$ 72 $\dots$ 73 $\dots$ 74 $\dots$ 75 $\dots$ 75 $\dots$ 75 $\dots$ 75 $\dots$ 75 $\dots$ 76 $\dots$ 76 $\dots$ 76 $\dots$ 77 $\dots$ 78 $\dots$ 78 $\dots$ 79 $\dots$ 79 $\dots$ 79 $\dots$ 79 $\dots$ 79 $\dots$ 70 $\dots$ |