# Energy-Efficient Decoding of Low-Density Parity-Check Codes

Kevin Cushon

Doctor of Philosophy

Department of Electrical and Computer Engineering

McGill University

Montreal, Quebec, Canada

August 2014

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Doctor of Philosophy

©Kevin Cushon, 2014

# **DEDICATION**

For my family, whose unconditional love and support made this work possible.

# TABLE OF CONTENTS

| DED  | ICATI  | ON                                  |

|------|--------|-------------------------------------|

| LIST | ΓOF ′  | <b>ΓABLES</b>                       |

| LIST | ΓOF    | FIGURES vii                         |

| KEY  | то А   | BBREVIATIONS xi                     |

| ABS  | TRAC'  | $\Gamma$                            |

| ABR  | ÉGÉ    |                                     |

| ACK  | NOWI   | LEDGEMENTS                          |

| PRE  | FACE   |                                     |

| 1    | Introd | uction                              |

|      | 1.1    | Motivation                          |

|      | 1.2    | Objectives                          |

|      | 1.3    | List of Publications                |

|      | 1.4    | Dissertation Outline                |

|      | 1.5    | Summary                             |

| 2    | Backgr | round and Literature Review         |

|      | 2.1    | Introduction                        |

|      | 2.2    | LDPC Codes                          |

|      |        | 2.2.1 Tanner Graphs                 |

|      | 2.3    | Decoding Algorithms                 |

|      |        | 2.3.1 Gallager A and B Algorithms   |

|      |        | 2.3.2 The Sum-Product Algorithm     |

|      |        | 2.3.3 The Min-Sum Algorithm         |

|      |        | 2.3.4 Normalized and Offset Min-Sum |

|      |        | 2.3.5 A Note on Quantization        |

|   | 2.4   | Literature Review of LDPC Decoder Architectures                | 22  |

|---|-------|----------------------------------------------------------------|-----|

|   |       | 2.4.1 Early Attempts and Decoder Architectures                 | 22  |

|   |       | 2.4.2 Efficiency Improvements                                  |     |

|   | 2.5   | Energy Consumption in Digital CMOS Circuits                    | 30  |

|   | 2.6   | Energy Reduction Strategies for LDPC Decoders                  | 32  |

|   | 2.7   | Summary                                                        | 34  |

| 3 | A M   | ulti-Mode LDPC Decoder Interleaver Based On Transmission Gates | 35  |

|   | 3.1   | Introduction                                                   | 35  |

|   | 3.2   | LDPC Interleaving                                              | 37  |

|   | 3.3   | System Architecture                                            | 40  |

|   | 3.4   | Circuit Design                                                 | 44  |

|   | 3.5   | Energy Analysis                                                | 50  |

|   | 3.6   | Summary                                                        | 52  |

| 4 | Pulse | e Width Modulated Min-Sum Decoding                             | 54  |

|   | 4.1   | Introduction                                                   | 54  |

|   | 4.2   | Pulse Width Message Encoding                                   | 55  |

|   | 4.3   | Low Complexity Architecture of PWM-MS Decoders                 | 57  |

|   |       | 4.3.1 Degree-2 Variable Nodes                                  | 61  |

|   |       | 4.3.2 Augmented Early Termination Check                        | 61  |

|   | 4.4   | Design Results                                                 | 62  |

|   |       | 4.4.1 Energy Impact of Loading and Interfacing                 | 70  |

|   | 4.5   | Summary                                                        | 72  |

| 5 | Deco  | oders Based On Differential Binary Message Passing Algorithms  | 74  |

|   | 5.1   | Introduction                                                   | 74  |

|   | 5.2   | FG-LDPC Codes and the DD-BMP Algorithm                         | 75  |

|   | 5.3   | Architectural Description                                      | 78  |

|   | 5.4   | Design Results                                                 | 82  |

|   | 5.5   | Use With Other LDPC Codes                                      | 89  |

|   | 5.6   | Trapping Sets                                                  | 93  |

|   | 5.7   | An Improved Differential Binary Algorithm                      | 94  |

|   |       | 5.7.1 Parameter Selection                                      | 97  |

|   | 5.8   | Design Results For IDB                                         | 103 |

|   | 5.9   | Summary                                                        | 113 |

| 6    | Gear-   | Shift Decoder Designs                         |

|------|---------|-----------------------------------------------|

|      | 6.1     | Introduction                                  |

|      | 6.2     | Efficiency of Gear-Shift Decoding             |

|      | 6.3     | The GSP and IGSP Decoding Algorithms          |

|      |         | 6.3.1 Parameter and Schedule Design           |

|      | 6.4     | Circuit Architecture of GSP and IGSP Decoders |

|      | 6.5     | Design Results                                |

|      | 6.6     | Summary                                       |

| 7    | Concl   | usion and Future Work                         |

|      | 7.1     | Advances                                      |

|      | 7.2     | Possibilities for Future Research             |

|      |         | 7.2.1 Ultra-Low Voltage Circuits              |

|      |         | 7.2.2 Asynchronous Decoders                   |

|      |         | 7.2.3 Statistical Computing                   |

| App  | endix A | A: Decoder Design Flow                        |

| Refe | erences |                                               |

# LIST OF TABLES

| <u>Table</u> |                                                                                       | p | age |

|--------------|---------------------------------------------------------------------------------------|---|-----|

| 3-1          | Synthesis results                                                                     |   | 47  |

| 3–2          | Logic utilization                                                                     |   | 48  |

| 4-1          | Post-Layout Results and Comparison With Bit-Serial Min-Sum $\ .$                      |   | 67  |

| 5–1          | Post-Layout Design Results and Comparisons With Other Works                           |   | 86  |

| 5–2          | Decoding Schedule For IDB With Relaunching                                            |   | 99  |

| 5–3          | IDB Decoder Critical Path (Typical Operating Conditions)                              |   | 106 |

| 5–4          | Post-Layout Design Results for IDB and Comparisons With Other Works                   |   | 108 |

| 5–5          | Wiring Complexity of the Designed Decoders                                            |   | 109 |

| 6–1          | GSP decoding schedule                                                                 |   | 123 |

| 6–2          | IGSP decoding schedule                                                                |   | 123 |

| 6–3          | Post-Layout Results for GSP and IGSP Decoders, Including Comparisons With Other Works |   | 136 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                  | page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2–1    | The parity check matrix of a (16,8) regular LDPC code with column weight 2 and row weight 4                                                                      | 10   |

| 2-2    | A communication system showing LDPC encoding and decoding                                                                                                        | 12   |

| 2–3    | Tanner graph representation of the (16,8) LDPC code whose parity check matrix is shown in Figure 2–1                                                             | 13   |

| 2-4    | Example of an ${\bf H}$ matrix for a quasi-cyclic (QC)-LDPC code, showing its construction from blocks of circularly shifted identity matrices                   | 23   |

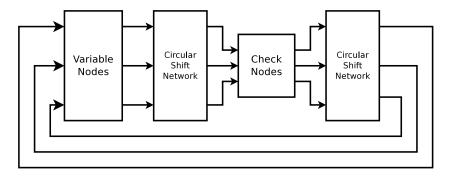

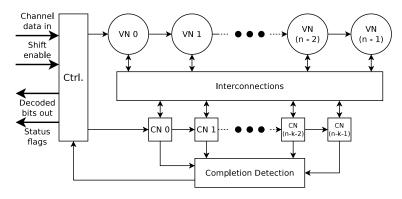

| 2-5    | Basic architecture for a partially parallel decoder of QC-LDPC codes.                                                                                            | 24   |

| 3-1    | Canonical LDPC decoder architecture                                                                                                                              | 37   |

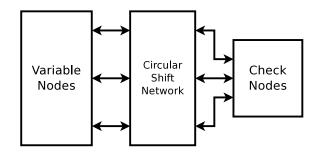

| 3-2    | LDPC decoder architecture with a bidirectional interleaver                                                                                                       | 37   |

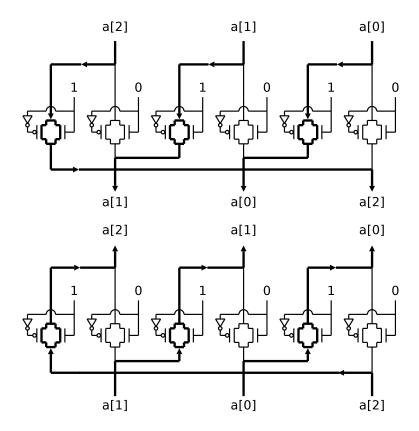

| 3–3    | A circular shift network composed of transmission gates performs both the forward and reverse circular shift, depending on which direction the signal is driven. | 40   |

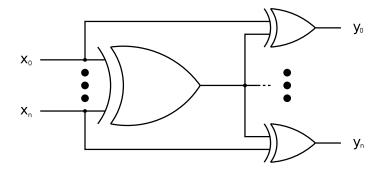

| 3-4    | Schematic of a check node with $n$ bits                                                                                                                          | 41   |

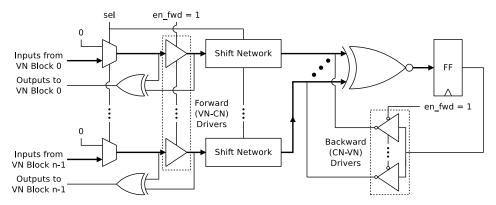

| 3–5    | Top level block diagram of our bidirectional system, in VN-to-CN (forward) operation with the data flow highlighted                                              | 42   |

| 3–6    | Top level block diagram of our bidirectional system, in CN-to-VN (reverse) operation with the data flow highlighted                                              | 42   |

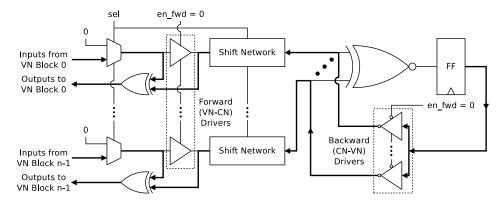

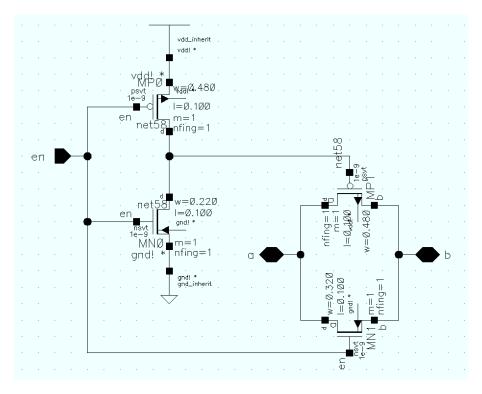

| 3-7    | Schematic view of the transmission gate cell, showing transistor sizes.                                                                                          | 45   |

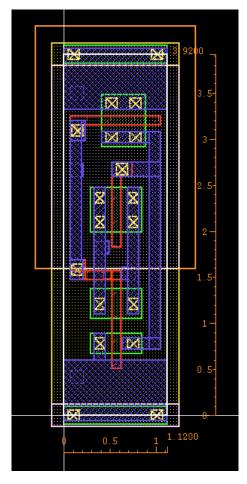

| 3–8    | Layout of the transmission gate cell, with rulers showing the cell's overall dimensions (1.12 $\mu$ m $	imes$ 3.92 $\mu$ m)                                      | 46   |

| 3-9    | SPICE circuit used to determine timing                                                                                                                           | 49   |

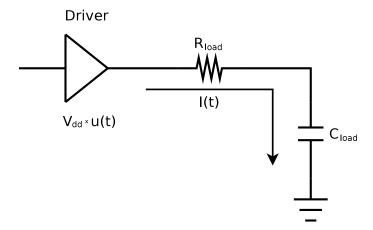

| 3–10 | Interconnect model used to estimate energy consumption                                                                                                                     | 50 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

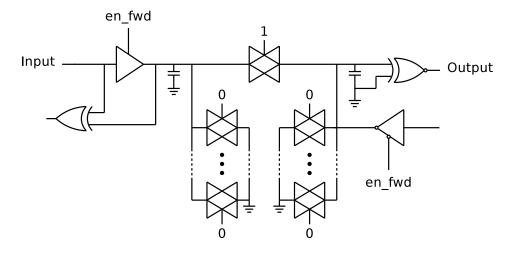

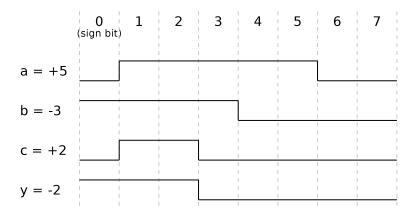

| 4–1  | Some examples of pulse width encoded messages. The message $y$ is the check node result produced from the inputs $a, b,$ and $c$                                           | 55 |

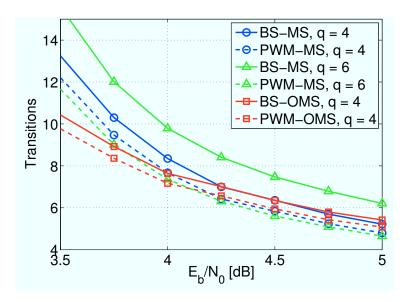

| 4–2  | The average number of transitions per edge per decoded codeword, for the (660, 484) LDPC code used in this work                                                            | 57 |

| 4–3  | PWM-MS check node of degree $d_c = 4$                                                                                                                                      | 58 |

| 4–4  | PWM-MS variable node of degree $d_v = 3$                                                                                                                                   | 59 |

| 4-5  | Special architecture for PWM-MS variable node with degree $d_v=2$                                                                                                          | 61 |

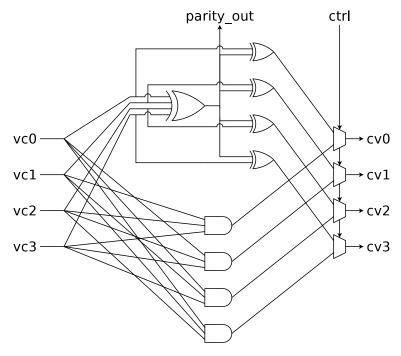

| 4–6  | Sign-checking circuit for PWM-MS variable nodes                                                                                                                            | 62 |

| 4-7  | Block diagram of the designed decoder                                                                                                                                      | 63 |

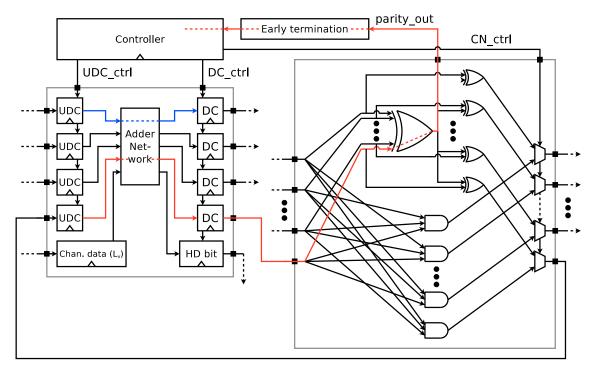

| 4-8  | Detailed block diagram of the PWM-MS decoders showing the critical paths of the unpipelined decoders (in red) and the pipelined decoder (in blue)                          | 64 |

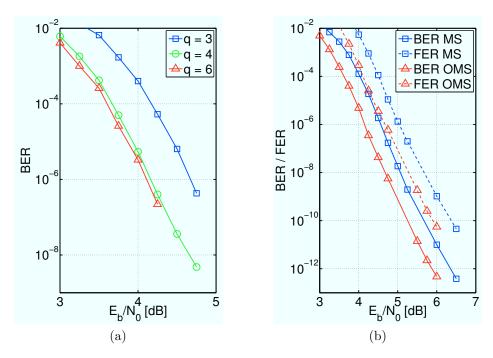

| 4–9  | Decoding performance for different quantization levels of offset min-<br>sum with an offset of 1 (a), and for 4-bit PWM-MS and PWM-OMS<br>decoders implemented on FPGA (b) | 65 |

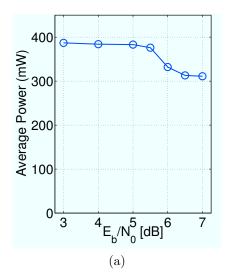

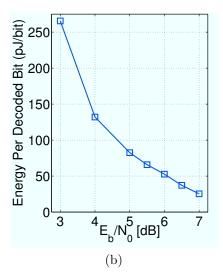

| 4–10 | Average power consumption (a) and energy efficiency (b) for a PWM-OMS decoder with $q=4$                                                                                   | 68 |

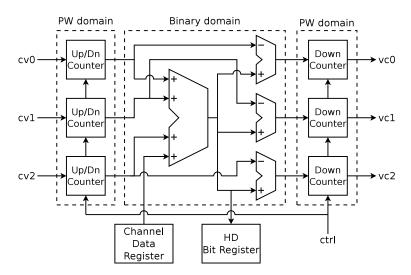

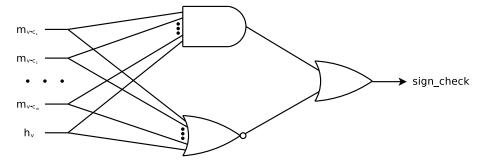

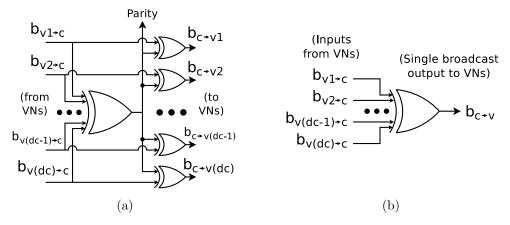

| 5–1  | DD-BMP check node schematics for non-broadcast (a) and broadcast (b) versions                                                                                              | 79 |

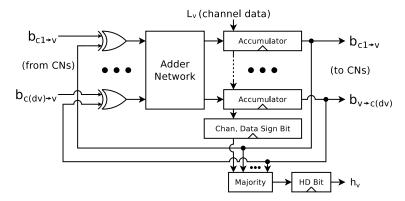

| 5–2  | DD-BMP variable node schematic                                                                                                                                             | 80 |

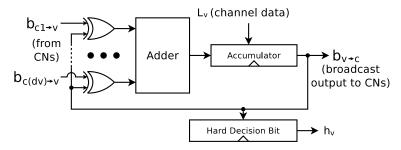

| 5–3  | MDD-BMP variable node schematic                                                                                                                                            | 80 |

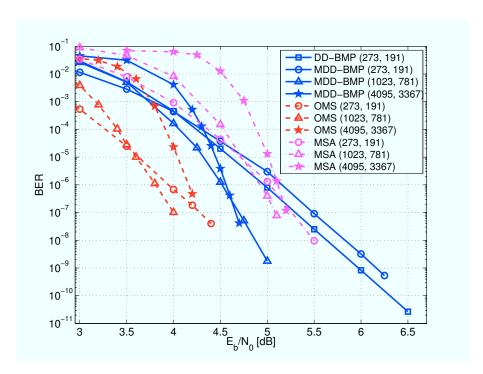

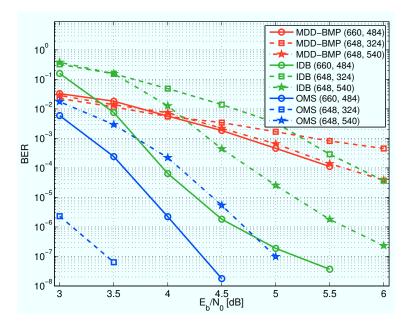

| 5–4  | BER performance of the codes in this work decoded with DD-BMP, MDD-BMP, offset MSA (OMS), and MSA. All simulations use 6 quantization bits and 31 maximum iterations       | 83 |

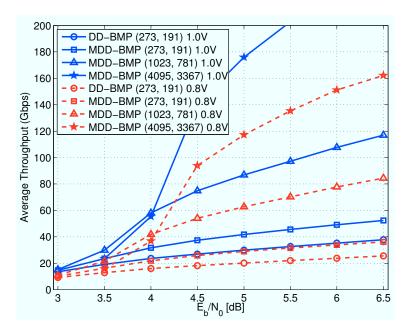

| 5–5  | Average throughput for the designed decoders                                                                                                                               | 85 |

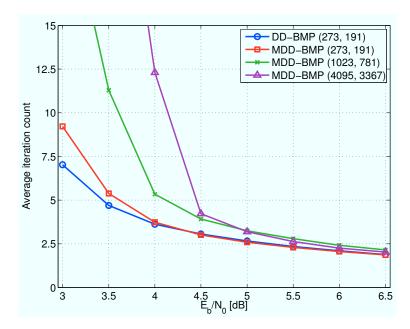

| 5–6  | Average iteration counts for the designed decoders                                                                                                                         | 87 |

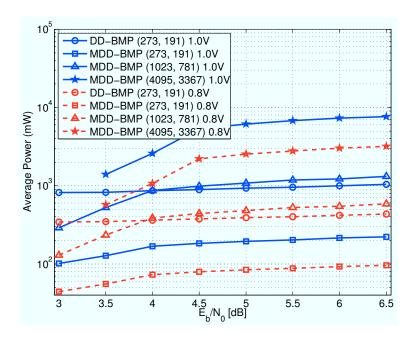

| 5-7  | Average power for the designed decoders                                                                                                                                                                                                                        | 88  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

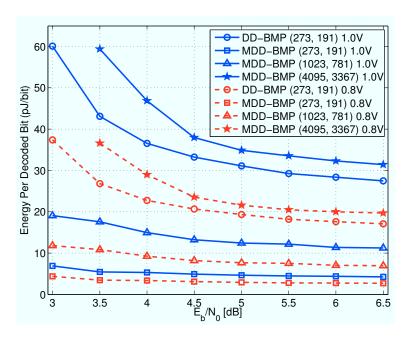

| 5-8  | Average energy per decoded bit for the designed decoders                                                                                                                                                                                                       | 89  |

| 5-9  | BER/FER performance of IDB with the (2048, 1723) RS-LDPC code, compared to the original MDD-BMP algorithm with 100 iterations, and 4-bit OMS with 20 iterations                                                                                                | 90  |

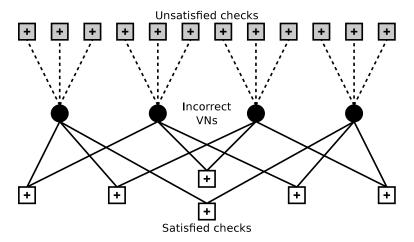

| 5-10 | The dominant (4, 12) trapping set of the (2048, 1723) RS-LDPC code under MDD-BMP decoding                                                                                                                                                                      | 93  |

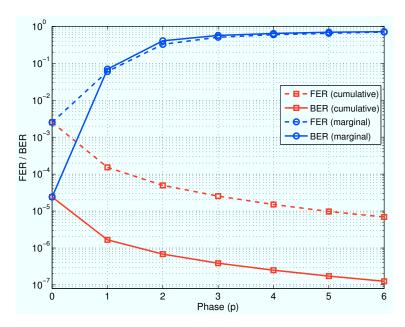

| 5–11 | Cumulative and marginal FER/BER performance of IDB with relaunching, at $E_b/N_0=4.5{\rm dB}$ , using the schedule shown in Table 5–2                                                                                                                          | 100 |

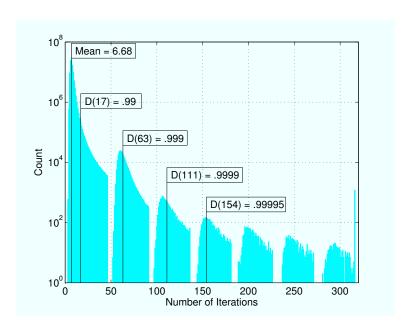

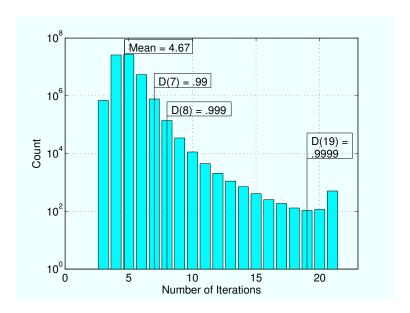

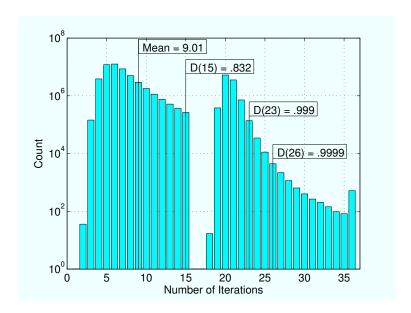

| 5–12 | Histogram showing the distribution of decoding iterations required for convergence for IDB, using the schedule shown in Table 5–2. A total of $10^8$ frames at $E_b/N_0 = 4.5 \text{dB}$ were sampled                                                          | 102 |

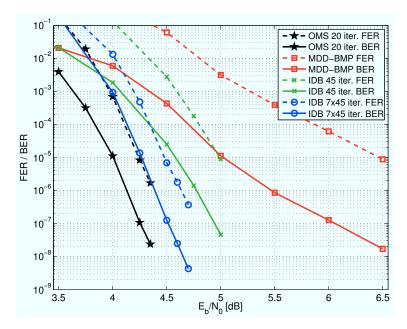

| 5–13 | BER performance of IDB decoding with other LDPC codes, along with MDD-BMP and OMS for comparison. All decoders use 6 bits of quantization. IDB uses the decoding schedule from Table 5–2, OMS and MDD-BMP use 20 and 45 maximum iterations respectively.       | 103 |

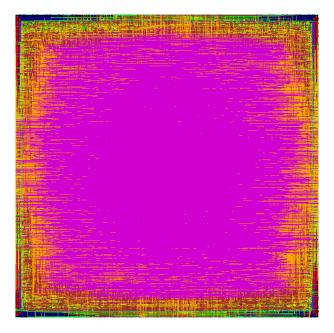

| 5–14 | Layout view of the IDB decoder design                                                                                                                                                                                                                          | 104 |

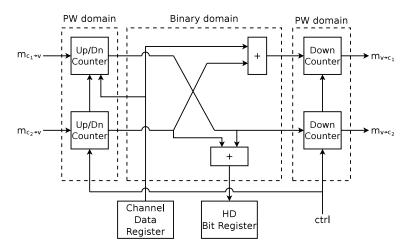

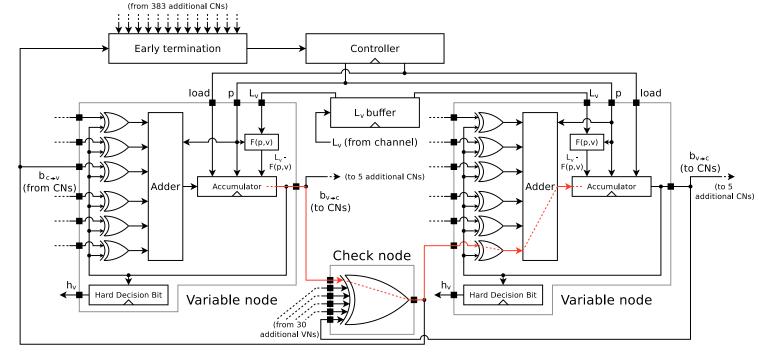

| 5–15 | Top level block diagram of the IDB decoder, showing a check node, 2 neighbouring variable nodes, and other top-level components. The critical path is traced in red                                                                                            | 105 |

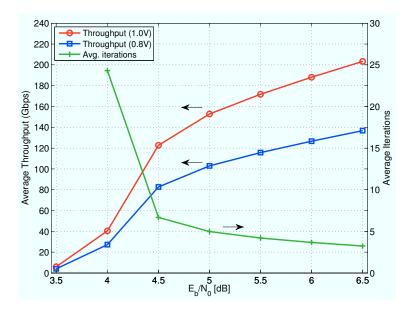

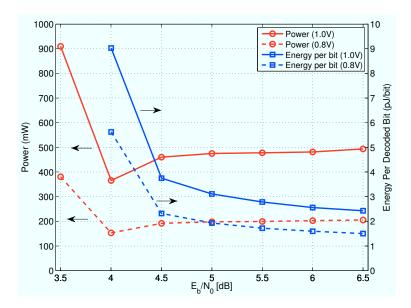

| 5-16 | Average throughput and iteration count for the designed IDB decoder.                                                                                                                                                                                           | 110 |

| 5–17 | Average power consumption and energy per decoded bit for the designed IDB decoder                                                                                                                                                                              | 111 |

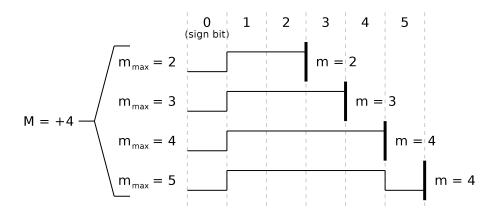

| 6–1  | Example waveforms of inter-node messages in GSP decoding. A low value for $m_{max}$ truncates high-magnitude messages, thus reducing information exchange and error correction performance, but also reduces the number of clock cycles per decoding iteration | 121 |

| 6–2  | Iteration count histogram for GSP, using the decoding schedule in Table 6–1. The bar at 21 iterations shows frames that failed to decode within 20 iterations, and are counted as 20 in statistical calculations                                                                              | 126 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6–3  | Iteration count histogram for IGSP, using the decoding schedule in Table 6–2. The bar at 36 iterations shows frames that failed to decode within 35 iterations, and are counted as 35 in statistical calculations                                                                             | 127 |

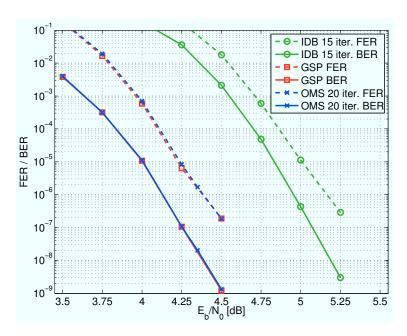

| 6–4  | BER/FER for GSP, standard OMS, and the IDB phase of IGSP. The overall BER/FER performance of IGSP is equivalent to GSP                                                                                                                                                                        | 128 |

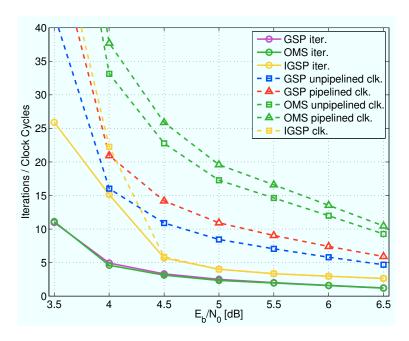

| 6–5  | Average number of decoding iterations and clock cycles per decoded frame for GSP, IGSP, and standard OMS                                                                                                                                                                                      | 129 |

| 6–6  | Schematic for an IGSP variable node with degree $d_v = 3.$                                                                                                                                                                                                                                    | 130 |

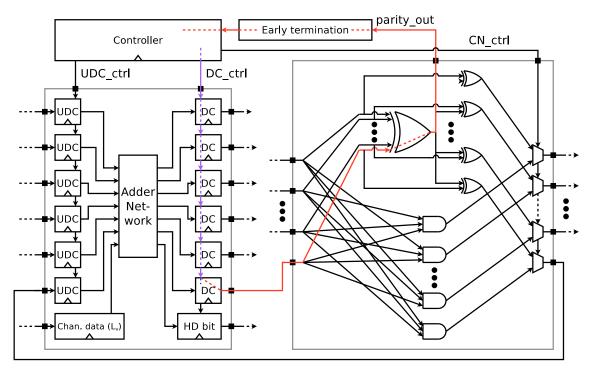

| 6–7  | Detailed block diagram of the GSP decoders showing the critical paths of the unpipelined decoders (in red) and the pipelined decoder (in blue). A purple line is used where the two intersect                                                                                                 | 133 |

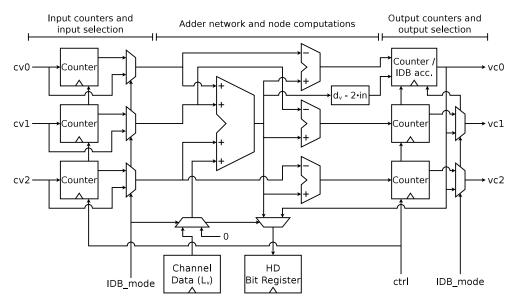

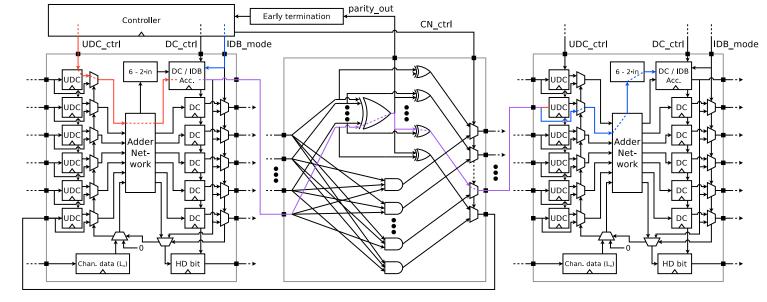

| 6-8  | Top level block diagram of the IGSP decoder, showing a check node, 2 neighbouring variable nodes, and other top-level components. The critical path in GSP mode is traced in red, while the IDB mode critical path is traced in blue. A purple line is used for segments where they intersect | 134 |

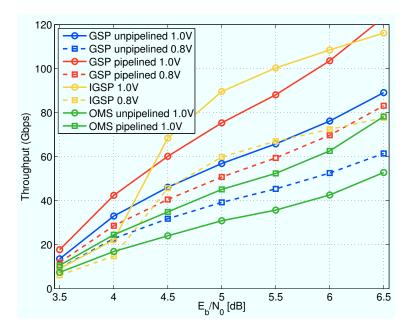

| 6–9  | Average throughput for GSP, IGSP, and standard OMS                                                                                                                                                                                                                                            | 138 |

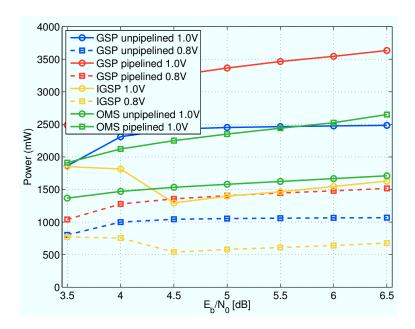

| 6–10 | Average power consumption for GSP, IGSP, and standard OMS                                                                                                                                                                                                                                     | 139 |

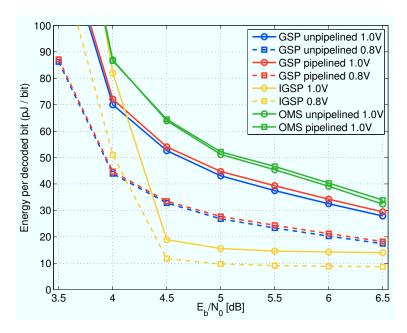

| 6–11 | Average energy per decoded bit for GSP, IGSP, and standard OMS. $$ .                                                                                                                                                                                                                          | 140 |

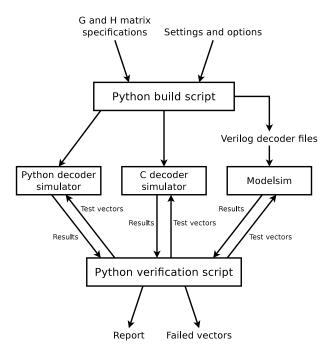

| A-1  | LDPC decoder design and verification flow                                                                                                                                                                                                                                                     | 147 |

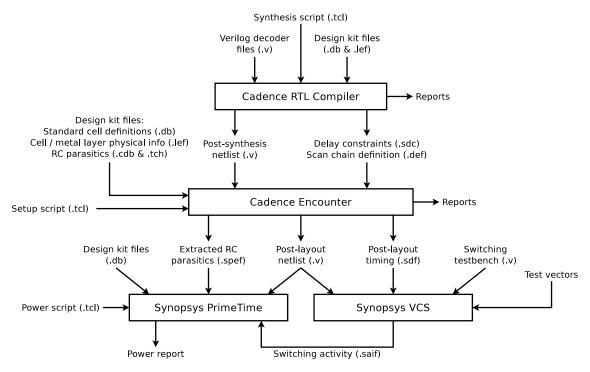

| A-2  | LDPC decoder ASIC design and power characterization flow                                                                                                                                                                                                                                      | 148 |

#### KEY TO ABBREVIATIONS

ASIC: Application-Specific Integrated Circuit

AWGN: Additive White Gaussian Noise

BER: Bit Error Rate

BPSK: Binary Phase-Shift Keying

BS-(O)MS: Bit-Serial (Offset) Min-Sum

CMOS: Complimentary Metal-Oxide Semiconductor

CN: Check Node

DB: Differential Binary

DC: Decoding Cycle or Down Counter

DD-BMP: Differential Decoding with Binary Message Passing

EG: Euclidean Geometry

EMD: Extrinsic Message Degree

FER: Frame Error Rate

FG: Finite Geometry

FPGA: Field-Programmable Gate Array

Gbps: Gigabits per second

GSP: Gear-Shift Pulse-width min-sum

HDL: Hardware Description Language

IDB: Improved Differential Binary

IEEE: Institute of Electrical and Electronics Engineers

IGSP: IDB with GSP

ITU: International Telecommunication Union

LDPC: Low-Density Parity Check

LLR: Log-Likelihood Ratio

MDD-BMP: Modified Differential Decoding with Binary Message Passing

MS(A): Min-Sum (Algorithm)

MTFM: Majority Tracking Forecast Memory

NMS(A): Normalized Min-Sum (Algorithm)

OMS(A): Offset Min-Sum (Algorithm)

PG: Projective Geometry

PWM-(O)MS: Pulse-Width Modulated (Offset) Min-Sum

QC: Quasi-Cyclic

RHS: Relaxed Half-Stochastic

RIS: Random Initial State

RNG: Random Number Generator

RS: Reed-Solomon

RSF: Random Sign Flip

SAPTL: Sense Amplifier with Pass Transistor Logic

SBF: Soft Bit Flipping

SNR: Signal-to-Noise Ratio

SoC: System on Chip

SP(A): Sum-Product (Algorithm)

TCL: Tool Command Language

TSMC: Taiwan Semiconductor Manufacturing Company

UDC: Up-Down Counter

VFS: Voltage and Frequency Scaling

VLSI: Very Large Scale Integration

VN: Variable Node

WPAN: Wireless Personal Area Network

#### ABSTRACT

Low-density parity-check (LDPC) codes are a type of error correcting code that are frequently used in high-performance communications systems, due to their ability to approach the theoretical limits of error correction. However, their iterative soft-decision decoding algorithms suffer from high computational complexity, energy consumption, and auxiliary circuit implementation difficulties. It is of particular interest to develop energy-efficient LDPC decoders in order to decrease cost of operation, increase battery life in portable devices, lessen environmental impact, and increase the range of applications for these powerful codes.

In this dissertation, we propose four new LDPC decoder designs with the primary goal of improving energy efficiency over previous designs. First, we present a bidirectional interleaver based on transmission gates, which reduces wiring complexity and associated parasitic energy losses. Second, we present an iterative decoder design based on pulse-width modulated min-sum (PWM-MS). We demonstrate that the pulse width message format reduces switching activity, computational complexity, and energy consumption compared to other recent LDPC decoder designs. Third, we present decoders based on differential binary (DB) algorithms. We also propose an improved differential binary (IDB) decoding algorithm, which greatly increases throughput and reduces energy consumption compared to recent decoders of similar error correction capability. Finally, we present decoders based on gear-shift algorithms, which use multiple decoding rules to minimize energy consumption. We propose gear-shift pulse-width (GSP) and IDB with GSP (IGSP) algorithms, and

demonstrate that they achieve superior energy efficiency without compromising error correction performance.

### ABRÉGÉ

Les codes LDPC sont un type de code correcteur d'erreurs qui sont fréquemments utilisés dans les systèmes de communications à haute performance. Cependant, leurs algorithmes de décodage iteratifs à décisions souples souffrent d'une complexité de calcul et d'une consommation d'énergie élevée, ainsi que des difficultés auxiliaires d'implementation en circuit électronique. Il est d'intérêt particulier de mettre au point des décodeurs des codes LDPC à basse consommation d'énergie afin de diminuer le coût de l'opération, augmenter l'autonomie des appareils portables, réduire l'impact sur l'environnement, et augmenter le nombre d'applications pour ces codes puissants.

Dans ce manuscrit, nous proposons quatre conceptions nouvelles de décodeur de codes LDPC pour lesquelles le but primaire est la réduction de la consommation d'énergie par rapport aux designs précédents. Premièrement, nous présentons un entrelaceur bidirectionnel basé sur les portes de transmission, qui réduit la complexité de filage et les pertes d'énergie parasitaires associées. Deuxièmement, nous présentons une conception de décodeur iteratif basée sur l'algorithme min-somme avec modulation de largeur d'impulsion. Nous démontrons que le format des messages de largeur d'impulsion réduit l'activité de commutation, la complexité informatique, et la consommation d'énergie par rapport aux autres conceptions de décodeur les plus récentes. Troisièmement, nous présentons des décodeurs basés sur les algorithmes binaires différentiels. Nous préposons aussi un algorithme binaire

différentiel amélioré (IDB), qui augmente grandement le débit et réduit la consommation d'énergie par rapport aux décodeurs récents avec une capacité de correction d'erreurs similiaire. Finalement, nous présentons des conceptions de décodeur basées sur les algorithmes de changement de braquet, qui utilisent les règles de décodage multiples pour minimiser la consommation d'énergie. Nous proposons les algorithmes de largeur d'impulsion avec changement de braquet (GSP) et IDB avec GSP (IGSP), et démontrons qu'ils atteignent une efficacité d'énergie supérieure sans compromettre la capacité de correction d'erreurs.

#### **ACKNOWLEDGEMENTS**

Scientific progress is made in steps, with the new discoveries growing from the old ones. I would like to express my gratitude towards the following people for laying the foundations of this work:

My supervisors Warren Gross and Shie Mannor, for their sage guidance and instruction.

Saied Hemati, for his kind and patient mentorship.

Camille Leroux, Naoya Onizawa, Saeed Sharifi Tehrani, Ali Naderi, and Guy-Armand Kamendje, for helping me out with the technical side of things.

Fabrice Labeau and Zeljko Zilic, for taking the time to serve on my advisory committee.

And last but not least, my family and friends, for their relentless moral and material support.

#### **PREFACE**

This dissertation presents several novel designs that advance the state of the art of LDPC decoding.

The first design we present is a bidirectional interleaver based on transmission gates for multi-mode LDPC codes. This design uses transmission gates to implement a multi-mode circular shift network, which allows a decoder to support multiple LDPC codes. The transmission gates both save silicon area relative to unidirectional multiplexing, and allow the processing nodes to exchange messages over the same wires on successive clock cycles, thus reducing the number of interleaver wires by half. While this design is not greatly successful in reducing energy consumption (due to the need for inefficient tristate buffers), it reduces silicon area by 28% relative to a reference unidirectional interleaver.

In PWM-MS, we propose encoding belief messages in a sign-magnitude pulse width format. Doing so offers four major advantages in the energy domain: low switching activity, reduced routing congestion, simple computational units, and offset min-sum (OMS) implementable for negligible cost over standard min-sum. A PWM-MS decoder designed in 0.13µm CMOS for a (660, 484) LDPC code has an area of 5.76 mm<sup>2</sup>. At an SNR of 5.5 dB, this decoder has an average throughput of 5.71 Gbps, average power consumption of 376 mW, and energy consumption of 65.8 pJ per information bit. Compared to bit-serial min-sum (BS-MS), a similar decoder architecture implementing the same code with the same technology, this represents a 19% improvement in energy efficiency. Notably, this design improves

energy efficiency without using any algorithmic heuristics, or otherwise sacrificing error correction performance.

We also present circuit layout designs of LDPC decoders based on differential binary (DB) algorithms. The first of these algorithms, called differential decoding with binary message passing (DD-BMP), and its modified variant (MDD-BMP), were described in prior works. When used with a certain class of LDPC code called finite geometric (FG) codes, these algorithms have been shown to produce good error correction performance, despite their low computational complexity - within 0.75 to 1 dB of floating point SPA, and up to 0.5 dB better than the standard min-sum algorithm (MSA). This dissertation presents the first hardware designs of these algorithms. We designed decoders of (273, 191), (1023, 781), and (4095, 3367) FG-LDPC codes in 65 nm CMOS, which achieve respective areas of 0.28 mm<sup>2</sup>, 1.38 mm<sup>2</sup>, and 15.37 mm<sup>2</sup>, average throughputs of 37 Gbps, 75 Gbps, and 141 Gbps, and energy efficiencies of 4.9 pJ/bit, 13.2 pJ/bit, and 37.9 pJ/bit. These designs challenge the common belief that FG codes are too complex for efficient hardware implementation.

We also present a new DB algorithm called IDB, for "improved differential binary", which has improved error correction performance for non-FG codes, and created a circuit design for the (2048, 1723) LDPC code specified in the IEEE 802.3an (10GBASE-T) standard. This decoder achieves an area of 1.44 mm², average throughput of 172 Gbps, and an energy efficiency of 2.8 pJ/bit, which represent major improvements over previous decoders of this code with similar error correction performance.

Finally, we present novel decoding algorithms based on gear-shift decoding, along with accompanying hardware designs. In gear-shift decoding, multiple decoding rules may be applied at different stages of decoding a frame. This can be applied to energy-efficient decoding by first attempting low-complexity decoding algorithms, then switching to high-complexity algorithms if decoding fails. In this way, energy efficiency can be increased without sacrificing error correction performance. We show that PWM-MS and IDB are naturally amenable to this strategy, and use them as the basis of two gear-shift algorithms: gear-shift pulse-width (GSP), and IDB with GSP (IGSP). We again implement these algorithms for the (2048, 1723) LDPC code in 65 nm CMOS. Our unpipelined GSP decoder achieves an area of 5.29 mm<sup>2</sup>, average throughput of 65.8 Gbps, and an energy efficiency of 37.5 pJ/bit, while a pipelined GSP decoder achieves the same area, 88.1 Gbps throughput, and energy efficiency of 39.3 pJ/bit. These represent slight improvements in energy efficiency and major improvements in throughput over previous decoders with the same level of error correction performance. Our IGSP decoder circuit layout design achieves an area of 6.00 mm<sup>2</sup>, average throughput of 100.3 Gbps, and an energy efficiency of 14.6 pJ/bit, which are even larger improvements, albeit at the expense of higher silicon area.

As this dissertation is based on previously published works, some of the work presented herein was performed by the co-authors.

Camille Leroux performed the simulations used to measure the switching activity data plotted in Fig. 4–2. He also wrote the FPGA testbench and hardware

AWGN channel emulator used for deep BER/FER measurements in Chapters 4 and 5, and performed simulations of the decoders described therein. The results of these simulations appear in Figs. 4–9b and 5–4.

Saied Hemati developed the pulse-width modulated message exchange concept that forms the basis of our PWM-MS LDPC decoder, and was a co-developer of the DD-BMP and MDD-BMP algorithms, for which we present hardware designs in Chapter 5. He also contributed the degree-2 variable node design for PWM-MS decoders described in Section 4.3.1, and the PWM-MS check node design shown in Fig. 4–3.

All of the listed co-authors participated in the development of ideas and editorial aspects of the papers in which they are credited, but did not perform any further design or experimentation work.

#### CHAPTER 1 Introduction

#### 1.1 Motivation

Error control coding is a discipline of information and coding theory used to ensure reliable transmission of information over an unreliable channel. In the most basic sense, this is accomplished by adding structured redundancy to the information to be transmitted, thus allowing the receiver to detect (and possibly correct) errors induced by corrupting noise. It has many uses in computing and communications, and has become an indispensable part of modern applications in these fields [1].

Low density parity check (LDPC) codes are one such type of error control code. Originally described by Robert Gallager in 1962 [2] [3], their proposed iterative decoding algorithms were too computationally complex to be practical at the time. As such, they were largely forgotten until the 1990s, when the discovery of Turbo codes in 1993 [4] led to renewed interest in iterative decoding algorithms.

The major motivating factor behind this interest was that Turbo codes, with a decoding algorithm consisting of iterative soft-decision message-passing, could achieve error correction performance approaching the theoretical limit. This limit, called the "Shannon limit" after its discoverer Claude Shannon, is a hard upper bound on the information-carrying capacity of a channel [5]. In other words, this limit states the maximum achievable efficiency of an error control code. The practical implications of getting closer to the Shannon limit are that a higher information

throughput becomes possible, spectral bandwidth is used more efficiently, and less power can be used in signal transmission compared to other error correction codes. LDPC codes were soon re-discovered, and like Turbo codes, were found to achieve near-capacity performance under iterative message-passing decoding [6] [7] [8].

Since then, LDPC codes have been a topic of great interest in multiple fields, especially information theory, signal processing, communications, and very large-scale integration (VLSI). Proof of the popularity of LDPC codes can be seen in their selection for use in several current and upcoming standards for communications systems:

- For terrestrial wireless communications, WiMax (IEEE 802.16e) [9], Wi-Fi (IEEE 802.11n), [10], and wireless personal area networks (WPAN) (IEEE 802.15.3c) [11].

- For satellite communications, DVB-S2 [12].

- For wireline communications, 10 gigabit per second Ethernet (IEEE 802.3an-2006) [13], and broadband over power lines (IEEE 1901) [14].

- For long-haul fibre-optic communications, ITU G.975.1 [15].

In addition to communications systems, LDPC codes have also been proposed for error correction in data storage, particularly Flash memory [16].

However, despite their popularity, LDPC codes face a number of implementation difficulties owing to the high computational complexity of their decoders. Practical LDPC codes generally have block lengths ranging from a few hundred to a few thousand bits, all of which require recomputing at every iteration of the decoding process. Another major implementation challenge for a decoder is the communication

structure necessary to support the message passing. Straightforward fully parallel architectures require thousands of interconnections, leading to congested routing networks, and significant energy loss due to wiring parasitics [17].

Because many applications of LDPC codes require energy consumption to be as low as possible, there is a high demand for energy efficient decoders. Thermal management is a limiting factor in many systems, particularly large systems-onchip (SoCs) and microprocessors in which performance is temperature- or hotspotlimited [18]. This is especially true in the emerging field of three-dimensional chip stacks [19]. Energy efficiency is key in embedded systems, which typically have highly constrained power budgets and limited thermal management options [20]. Perhaps the greatest source of demand is from battery-powered gadgets, such as laptop computers, smartphones, and tablets - these all have large and highly competitive markets, and require energy efficiency to be a top design priority in order to extend battery life. Another application is datacenter servers, as the cost of operation is primarily dependant on power consumption [21] [22], and the increasing popularity of decentralized computing is driving higher demand for datacenter resources. Emerging or niche fields requiring energy efficient communications exist as well, such as sensor networks, building monitoring, smart warehouses, and implantable medical devices [23]. Finally, increased efficiency leads to lower cost of operation, and in aggregates of large numbers of devices, also reduces the need for energy generation infrastructure and associated environmental costs.

To address this problem, this dissertation proposes four novel energy-efficient LDPC decoder designs. The first is a bidirectional interleaver based on transmission gates, which attempts to address energy consumption by reducing interconnect complexity. The second is a pulse width modulated min-sum (PWM-MS) decoder. The third is a series of decoders based on differential binary (DB) algorithms: the previously proposed differential decoding with binary message passing (DD-BMP) algorithm and its modified variant (MDD-BMP) [24]. We also propose an improved differential binary (IDB) decoding algorithm, and present an accompanying hardware design. Finally, the fourth design is a series of decoders based on energy-efficient gear-shift decoding algorithms, which are algorithms that use multiple update rules. Our previously mentioned PWM-MS and IDB decoders are highly adaptable to this concept. We propose two gear-shift algorithms based thereupon called gear-shift pulse-width (GSP) and IDB with GSP (IGSP) and their hardware designs.

#### 1.2 Objectives

The primary goal of this research is to produce LDPC decoder designs with improved energy efficiency compared to previously published designs. Secondary design goals are hardware efficiency, high throughput, and good error correction performance. Recently published LDPC decoder designs, particularly those that are designed for energy efficiency, are used as benchmarks. However, as trade-offs between conflicting goals are a necessary part of design, justifiable trade-offs that increase energy efficiency are given the highest consideration.

#### 1.3 List of Publications

The work presented in this dissertation has been published in the following peer-reviewed scholarly publications:

- K. Cushon, W. J. Gross, and S. Mannor. Bidirectional interleavers for LDPC decoders using transmission gates. In *Proceedings of the IEEE Workshop on Signal Processing Systems*, pages 232–237, Tampere, Finland, 2009.

- K. Cushon, C. Leroux, S. Hemati, S. Mannor, and W. J. Gross, "A Min-Sum Iterative Decoder Based on Pulsewidth Message Encoding," *IEEE Transactions* on Circuits and Systems-II: Express Briefs, vol. 57, no. 11, pp. 893–897, Nov. 2010.

- K. Cushon, C. Leroux, S. Hemati, S. Mannor, and W. J. Gross, "High-Throughput Energy-Efficient LDPC Decoders Using Differential Binary Message Passing," *IEEE Transactions on Signal Processing* vol. 62, no. 3, pp. 619–631, Mar. 2014.

- K. Cushon, S. Hemati, S. Mannor, and W. J. Gross, "Energy-Efficient Gear-Shift LDPC Decoders," in *Proceedings of the 2014 IEEE International Conference on Application-Specific Systems, Architectures and Processors (ASAP)*, pp. 219–223, Zürich, Switzerland, Jun. 2014.

#### 1.4 Dissertation Outline

The remainder of this dissertation is structured as follows.

Chapter 2 provides background for the material presented in the later chapters. It contains a review of LDPC codes, including commonly-used decoding algorithms, as well as the problems and strategies of hardware decoder implementation.

It also reviews energy consumption in micro-electronic circuits, and strategies used in energy-efficient digital circuit design. Finally, this chapter also provides a literature review of energy-efficient LDPC decoders, including state-of-the-art designs.

Chapter 3 proposes a bi-directional interleaver and circular shift network for multi-mode quasi-cyclic (QC) LDPC codes. This interleaver halves the number of required wires and occupies less area than the equivalent unidirectional design. This chapter is based in part on material from our conference paper [25].

Chapter 4 proposes an LDPC decoder design based on pulse-width encoded message exchange, which we refer to as a *pulse-width modulated min-sum* (PWM-MS) decoder. This message encoding increases energy efficiency by reducing switching activity and computational complexity. We also present an ASIC layout design of a PWM-MS decoder. This chapter is based in part on material from our journal paper [26].

Chapter 5 describes a series of LDPC decoders based on differential binary (DB) algorithms. We present the first hardware designs of the DD-BMP and MDD-BMP algorithms [24], as well as the first fully parallel implementations of FG-LDPC codes. We also present an improved differential binary (IDB) decoding algorithm, and design it in hardware for the (2048,1723) LDPC code from the IEEE 802.3an (10GBASE-T) standard [13]. Post-layout results for these decoders are compared with other state-of-the-art energy-efficient LDPC decoder designs. This chapter is based in part on material from our journal paper [27].

Chapter 6 explores decoders based on gear-shift algorithms that are capable of decoding using multiple algorithms. We show that the PWM-MS and IDB algorithms from the previous chapters can be extended or combined to create gear-shift algorithms with little hardware overhead. We introduce and GSP and IGSP algorithms, and show that they achieve energy efficiency comparable to low-complexity decoding algorithms, and the error correction performance of offset min-sum. We also propose hardware designs for these decoders that take advantage of architectural commonalities to attain good area efficiency. As before, we present circuit layout results and perform comparisons with previously proposed decoder designs. Material from this chapter also appears in our conference paper [28].

Finally, Chapter 7 discusses possible avenues for future research, and concludes the dissertation.

#### 1.5 Summary

Many applications exist for energy efficient LDPC decoders - there are current applications in communications, and emerging applications in fields such as implanted biomedical devices. However, the high complexity of the required computations and message passing clashes with the low energy requirement. Many different approaches have been taken to make energy efficient LDPC decoders. Dynamic energy dominates total energy consumption in published decoder designs down to 65 nm, though static energy is an important consideration with smaller processes. The goal of this research is to improve energy efficiency over previously published LDPC

decoder designs by addressing the factors contributing to dynamic energy consumption - computational complexity, switching activity, interconnect parastitics, and supply voltage.

# CHAPTER 2 Background and Literature Review

#### 2.1 Introduction

This chapter will provide background information and a review of relevant prior literature.

First, a brief overview and tutorial on LDPC codes will be given, followed by descriptions of the most well-known decoding algorithms: the Gallager A and B algorithms, the sum-product algorithm (SPA), and the min-sum algorithm (MSA) and its variants. The next section will review the evolution of LDPC decoder design and complexity management strategies, with examples from the literature. This review will emphasize designs intended to be energy-efficient. Finally, this section will be concluded with an overview of general strategies for energy reduction in digital CMOS circuits, and how they were applied to the designs presented in this dissertation.

#### 2.2 LDPC Codes

An LDPC code is defined by a parity check matrix  $\mathbf{H}$ . An (n, k) LDPC code has a parity check matrix with dimensions k rows by n columns. The elements of  $\mathbf{H}$  describe the relationships between n received symbols, which are represented by the columns, and k parity checks, which are represented by the rows. As this

Figure 2–1: The parity check matrix of a (16,8) regular LDPC code with column weight 2 and row weight 4.

dissertation is heavily focused on practical circuit implementation, we will restrict our consideration to binary LDPC block codes.\*

A bit *i* participates in parity check *j* if  $H_{i,j} = 1$ , otherwise  $H_{i,j} = 0$ . The name "low-density parity check" comes from the sparsity of non-zero entries in **H**. The row and column weights of *H* are defined as the number of non-zero entries in a given row or column, respectively. If all rows have equal weight and all columns have equal weight, then the code is said to be regular; otherwise, it is irregular. Figure 2–1 shows an example parity check matrix for a (16, 8) regular LDPC code.

A frame  $\mathbf{d} = (d_0, d_1, ..., d_{n-1})$  constitutes a valid codeword if and only if:

<sup>\*</sup> Non-binary definitions of LDPC codes date back to the original Gallager thesis [2], but have failed to gain popularity among implementors due to obnoxiously high decoding complexity and low throughput compared to binary codes [29] [30] [31]. Likewise, LDPC convolutional codes have also been investigated in the literature [32], but have been largely ignored in favor of block codes for practical implementations.

$$\mathbf{dH}^{\mathrm{T}} = \mathbf{0}.\tag{2.1}$$

This is defined as the syndrome of  $\mathbf{d}$ . If the syndrome computed over GF(2) is a zero vector, then all parity checks are satisfied. A non-zero syndrome implies one or more unsatisfied checks.

Encoding, which is typically performed by the transmitter, is done using a generator matrix G in which:

$$\mathbf{G}\mathbf{H}^{\mathrm{T}} = \mathbf{0}.\tag{2.2}$$

The matrix **G** has dimensions of  $k \times n$ . Given a vector **b** of k arbitrary information bits  $\mathbf{b} = (b_0, b_1, ..., b_{k-1})$ , a frame, or valid codeword  $\mathbf{x} = (x_0, x_1, ..., x_{n-1})$ , can be generated as follows:

$$\mathbf{x} = \mathbf{bG}.\tag{2.3}$$

Alternatively,  $\mathbf{x}$  is equivalent to the concatenation of  $\mathbf{b}$  with a vector of n-k parity bits  $\mathbf{p}$ , i.e.  $\mathbf{x} = (x_0, x_1, ..., x_{n-1}) = (b_0, b_1, ..., b_{k-1}, p_0, p_1, ..., p_{n-k-1})$ . Thus,  $\mathbf{G}$  consists of a  $k \times k$  identity matrix and a  $k \times (n-k)$  non-systematic portion. The non-systematic portion of  $\mathbf{G}$ ,  $\mathbf{G}_{\mathbf{p}}$ , can be used without the systematic portion to generate  $\mathbf{p}$ :

$$\mathbf{p} = \mathbf{b}\mathbf{G}_{\mathbf{p}}.\tag{2.4}$$

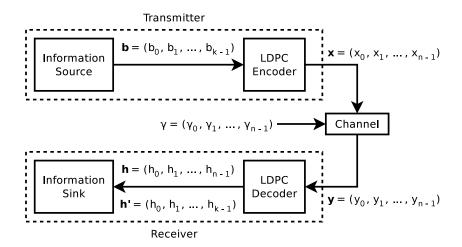

Figure 2–2: A communication system showing LDPC encoding and decoding.

After the frame  $\mathbf{x}$  is constructed, it is then transmitted through a channel, where it may be corrupted by noise  $\gamma$ . The receiver acquires the noisy frame  $\mathbf{y} = (y_0, y_1, ..., y_{n-1})$ , which serves as input to the decoder, which in turn produces as output the decoded frame  $\mathbf{h}$ . At this point, the parity portion of  $\mathbf{h}$  can be discarded, since it serves no use to the receiver, leaving  $\mathbf{h}' = (h_0, h_1, ..., h_{k-1})$ . If decoding is successful, then  $\mathbf{h}' = \mathbf{b}$ . Figure 2–2 illustrates the process of encoding, transmission, and decoding.

#### 2.2.1 Tanner Graphs

An LDPC code can also be described using a graphical model called a Tanner graph [33]. These graphs provide a generic realization and decoding framework for many codes. In particular, LDPC and Turbo codes can both be described using Tanner graphs, and decoded using iterative message-passing algorithms operating on these graphs [34] [35].

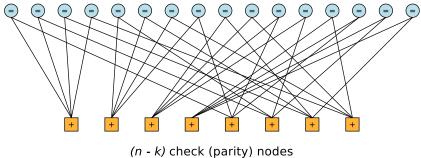

#### n variable (equality) nodes

Figure 2–3: Tanner graph representation of the (16,8) LDPC code whose parity check matrix is shown in Figure 2–1.

Figure 2–3 shows a Tanner graph representation of the (16,8) LDPC code from Figure 2–1. A Tanner graph is a bipartite graph that describes the constraints or parity check equations of a linear block code, and thus is an alternate representation of the parity check matrix **H**. One set of vertices, called the variable nodes (VNs),<sup>†</sup> represent the variables, or estimations of the decoded message. They are equivalent to the columns of **H**. The other set of vertices, called the *check nodes* (CNs),<sup>‡</sup> represent the parity check constraints, or the rows of  $\mathbf{H}$ . An edge between VN i and CN j exists if and only if symbol i participates in parity check j. Edges are thus equivalent to non-zero elements in H. The number of edges incident to a node is called the degree of the node. The variable node degrees  $(d_v)$  and check node degrees  $(d_c)$  are equivalent to the column and row weights of **H**, respectively.

$<sup>^{\</sup>dagger}$  Also called "bit", "equality", and in general (non-binary) cases, "digit" or "symbol" nodes.

<sup>&</sup>lt;sup>‡</sup> Also called "parity" or "subcode" nodes.

#### 2.3 Decoding Algorithms

While many reasonable message-passing algorithms for decoding LDPC codes have been devised, this section will describe the most prominent and important ones: the Gallager A and B algorithms, the sum-product algorithm (SPA), the min-sum algorithm (MSA), and MSA variants offset min-sum (OMS) and normalized min-sum (NMS).

#### 2.3.1 Gallager A and B Algorithms

Gallager originally proposed two different algorithms for decoding LDPC codes [2]. The first is a low-complexity bit-flipping algorithm which is better known today as the "Gallager B" algorithm.

#### I. Initialization

This algorithm operates entirely in the binary domain and takes as input a block of n bits from the channel:

$$y_v \in \{0, 1\} \,\forall \, 0 \le v < n \tag{2.5}$$

The initial variable-to-check messages are set to the received bits:

$$m_{v \to c} = y_v \tag{2.6}$$

#### II. Check node computations

Next, the check-to-variable messages are computed as the modulo-2 sum of all inputs to the check node, excluding the input from the edge for which the output is being calculated:

$$m_{c \to v} = \bigoplus_{v' \in N_c \setminus v} m_{v' \to c}, \tag{2.7}$$

where  $N_c$  is the set of VNs neighbouring check node c, and the  $\bigoplus$  symbol signifies modulo-2 addition.

## III. Variable node computations

Now the variable-to-check messages are re-computed using the messages received from the check nodes:

$$m_{v\to c} = \begin{cases} \overline{m_{v\to c}}, & \text{if } |\{c : m_{c\to v} = \overline{m_{v\to c}}\}| \ge b_k, \\ m_{v\to c}, & \text{if otherwise.} \end{cases}$$

(2.8)

Put differently, the variable node flips the value of an outgoing message if at least  $b_k$  of the incoming messages suggests that it should. The threshold  $b_k$  can vary with the iteration number k, and can take any integer value in the range  $\frac{d_v-1}{2} \leq b_k \leq d_v-1$ .

The Gallager A algorithm is, in fact, a special case of Gallager B in which  $b_k = d_v - 1$ . In other words, an outgoing message flips only when all incoming messages disagree with its current value.

### IV. Output

The estimation of the decoded codeword **h** can be computed by majority vote of each variable node's outputs:

$$h_v = \begin{cases} 0, & \text{if } \sum_{c \in N_v} m_{c \to v} \le \frac{d_v}{2}, \\ 1, & \text{if otherwise.} \end{cases}$$

(2.9)

Some alternative ways of computing  $\mathbf{h}$  are to assign  $h_v$  a random bit if the sum is exactly zero, or to leave  $h_v$  unassigned until all outputs of variable node v are in agreement.

Equations 2.7 - 2.9 are then iteratively repeated until some criterion for stopping is met. Usually, this is when a valid codeword is detected (i.e.,  $\mathbf{h}\mathbf{H}^{\mathrm{T}} = \mathbf{0}$ ), or when a maximum iteration limit  $k_{max}$  is reached.

In both the variable and check node computations, the calculation for a given outgoing edge excludes the input from that edge. This is because this information is intrinsic to the calculation, while the contributions from the other edges are extrinsic information. Including the intrinsic information would create feedback loops between neighbouring nodes that bias the message update calculations in favour of their current values. This reduces the error correction performance of the algorithm. However, as will be shown in later chapters of this dissertation, this can be used as a heuristic to reduce computational complexity, particularly in the check node.

### 2.3.2 The Sum-Product Algorithm

In addition to the simple bit-flipping algorithm described above, Gallager also proposed a decoding algorithm which operated on probabilities, which he called "probabilistic decoding" [2]. While much more computationally complex, this algorithm gives much better error correction performance, as it can take into account the level of confidence in which a bit is correct. This algorithm turned out to be a form of the sum-product algorithm [34], which is itself a special case of Pearl's belief propagation algorithm [36].

Like the Gallager A & B algorithms, the basic principle of this algorithm is the exchange of messages, or "beliefs", between the variable and check nodes. When a processing node is activated, it reads the messages from neighbouring nodes over the graph's edges, and updates its belief based on these messages. Unlike the Gallager A & B algorithms, which are "hard decision", the sum-product algorithm is "soft decision" - the exchanged messages and internal node computations operate on multilevel likelihood estimations rather than a hard estimation of the decoded bit.

The modern formulation of the sum-product LDPC decoding algorithm is as follows.

### I. Initialization

The variable nodes are initialized with soft information from the channel. The n-element vector  $\mathbf{L}$  contains the real-valued log-likelihood ratios (LLRs) of each of the n received symbols:  $\S$

$$L_v = \ln \left[ \frac{P(x_v = 0|y_v)}{P(x_v = 1|y_v)} \right] \in \mathbb{R} \ \forall \ 0 \le v < n \,. \tag{2.10}$$

In most studies of LDPC decoder performance, a binary phase-shift keying (BPSK) channel with additive white Gaussian noise (AWGN) is used. In this special case, it can be shown that the LLRs are a function of the received values  $\mathbf{y}$  and channel noise variance  $\sigma^2$ :

<sup>§</sup> The SPA works in the logarithmic domain as a matter of computational simplification, as products of raw probabilities become sums of LLRs.

$$L_v = \frac{2}{\sigma^2} \cdot y_v \in \mathbb{R} \ \forall \ 0 \le v < n \,. \tag{2.11}$$

The initial VN-to-CN messages are set to  $\mathbf{L}$ , while the iteration number (indicated by the superscript on m) is initialized to 0:

$$m_{v \to c}^0 = L_v \tag{2.12}$$

# II. Check node computations

Next, the CN-to-VN messages are computed. The SPA check node operation is:

$$m_{c \to v}^k = 2 \cdot \operatorname{atanh} \left( \prod_{v' \in N_c \setminus v} \operatorname{tanh} \left( \frac{m_{v' \to c}^k}{2} \right) \right).$$

(2.13)

# III. Variable node computations

Now, the iteration number k is incremented, and the new VN-to-CN messages are computed based on the previous iteration's CN-to-VN messages:

$$m_{v \to c}^k = L_v + \sum_{c' \in N_v \setminus c} m_{c' \to v}^{k-1},$$

(2.14)

# IV. Output

To generate the estimation of the decoded block **h**, a hard decision for each bit is computed at the VNs based on a sum of all incoming messages from neighbouring VNs:

$$h_v^k = \begin{cases} 0, & \text{if } L_v + \sum_{c \in N_v} m_{c \to v}^{k-1} \ge 0, \\ 1, & \text{if otherwise.} \end{cases}$$

(2.15)

As before, Equations 2.13 - 2.15 are repeated iteratively until a stopping criterion is met, such as detection of a valid codeword or reaching the maximum iteration limit  $k_{max}$ .

In practical implementations, SPA-based decoders face major implementation problems owing mainly to two factors. The first is the difficulty of computing the transcendental functions tanh and atanh [17]. The second related problem is the imprecise representation of real numbers in systems with a finite number of quantization bits, which can lead to major degradations in error correction performance particularly due to numerical saturation in the output of tanh and atanh [37].

However, SPA is still widely accepted as the "gold standard" of LDPC decoding algorithms, as it has been proven to be optimal on cycle-free graphs [7] [38] [39]. Practical LDPC codes are not cycle-free, although SPA decoding with high-precision floating-point computations often results in the best attainable error correction performance - cases where it does not are usually noted in the literature when discovered.

### 2.3.3 The Min-Sum Algorithm

The MSA can be considered a heuristic variant of the SPA in which the transcendental functions in the check nodes are replaced with simpler computations. Like the SPA, the MSA is a belief propagation algorithm operating over a graphical model of the code [40]. They are, in fact, highly similar - the only difference is the check node

operation, in which the magnitude of the outgoing messages is set to the minimum of the incoming messages.

Thus, Equation 2.13 above is replaced with:

$$m_{c \to v}^{k} = \prod_{v' \in N_c \setminus v} \operatorname{sgn}\left(m_{v' \to c}^{k}\right) \cdot \min_{v' \in N_c \setminus v}\left(\left|m_{v' \to c}^{k}\right|\right). \tag{2.16}$$

The initialization, VN update, and hard decision equations are the same as in the SPA.

# 2.3.4 Normalized and Offset Min-Sum

As the MSA check node operation is an approximation of the optimal SPA operation, there is a loss in error correction performance compared to the SPA. However, as the MSA CN messages consistently have higher magnitude than in SPA [41], correction factors can be applied to minimize this loss [42].

In the normalized min-sum algorithm (NMSA), the output of the check node is scaled by a constant factor  $\alpha$ , with  $0 < \alpha < 1$ :

$$m_{c \to v}^{k} = \alpha \cdot \prod_{v' \in N_{c} \setminus v} \operatorname{sgn}\left(m_{v' \to c}^{k}\right) \cdot \min_{v' \in N_{c} \setminus v}\left(\left|m_{v' \to c}^{k}\right|\right). \tag{2.17}$$

In the offset min-sum algorithm (OMSA), a subtractive offset  $\beta$ , with  $\beta > 0$ , is applied to the magnitude:

$$m_{c \to v}^{k} = \prod_{v' \in N_{c} \setminus v} \operatorname{sgn}\left(m_{v' \to c}^{k}\right) \cdot \min_{v' \in N_{c} \setminus v} \left(\operatorname{max}\left(\left|m_{v' \to c}^{k} - \beta\right|, 0\right)\right). \tag{2.18}$$

The correction factors  $\alpha$  and  $\beta$  can also be applied simultaneously, in which case the algorithm is known as normalized offset min-sum. Typical values for  $\alpha$  and

β are 0.75 and 1, respectively, although the optimal values depend on the LDPC code, channel, and internal number representation of the decoder. A carefully tuned NMSA/OMSA decoder can generally achieve error correction performance within 0.1 dB of an SPA decoder [43]. With certain codes, NMSA/OMSA can actually outperform SPA due to the effects of cycles in the code's graph [44].

## 2.3.5 A Note on Quantization

Until now, we have only considered decoding algorithms operating over the range of real numbers. However, any practical decoder implementation must necessarily have a finite number of quantization levels, which will have a negative impact on the decoder's performance due to numerical saturation and quantization error. LDPC decoder implementations in software generally use high-precision floating point numbers; however, 4 to 7 bits of quantization is generally sufficient to achieve negligible (or at least justifiable) performance loss compared to floating-point numbers [45]. VLSI decoder implementations generally use as few quantization bits as possible to reduce memory and computational unit complexity.

Quantization schemes generally involve clipping LLR values above a certain threshold  $T_{clip}$ , and dividing the range  $[-T_{clip}, T_{clip}]$  into  $2^q$  uniform intervals, where q is the number of quantization bits [46]. Some more advanced quantization techniques have been proposed to increase error correction performance, such as adaptively varying  $T_{clip}$  based on channel noise estimations or the number of unsatisfied parity checks [47].

### 2.4 Literature Review of LDPC Decoder Architectures

This section will review the progression and current state of LDPC decoder hardware architectures, with an emphasis on energy-efficient design.

## 2.4.1 Early Attempts and Decoder Architectures

The first VLSI implementation of an LDPC decoder was presented by Blanksby and Howland in 2002 [17], and was a fully-parallel SPA-based design, with the check node computations performed via look-up tables. This design soon became emblematic of the difficulties of implementing LDPC decoders, particularly with the interconnections required to support fully parallel message passing. Routing congestion caused this design to be quite area-inefficient, with 50% utilization. High wiring delay and parasitics also caused it to have a longer critical path and higher power consumption than expected.

While the check node computation problem could be eased by MSA-based decoders, the routing problem was (and remains) a serious issue affecting the viability of LDPC codes. This led to the co-development of architecture-aware LDPC codes - i.e., LDPC codes in which the parity-check matrix **H** has a regular structure that can be exploited in hardware implementations [48] - and partially-parallel decoder architectures for these codes [49].

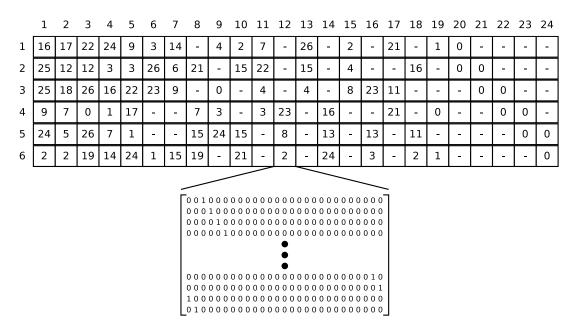

The most important and prominent type of architecture-aware LDPC code is the quasi-cyclic (QC)-LDPC code [50]. In these codes, the **H** matrix is composed of sub-blocks of circulant permutation matrices - usually in the form of circularly shifted identity matrices. Figure 2–4 shows an example of one such code. This (648, 486)

Figure 2–4: Example of an **H** matrix for a quasi-cyclic (QC)-LDPC code, showing its construction from blocks of circularly shifted identity matrices.

QC-LDPC code from the IEEE 802.11n standard [10] is made up of  $27 \times 27$  sub-blocks that are either an identity matrix circularly shifted to the right  $\rho$  places, or a zero matrix (indicated by a dash). The expanded block illustrates how the model matrix of sub-blocks translates to a conventional binary **H** matrix.

QC-LDPC codes became popular standard codes because they lend themselves well to efficient partially parallel implementations, allowing designers to avoid the problems faced by early fully parallel decoders. Partially parallel architectures implement a subset of the overall graph, and multiplex the message passing and node computations over time. At the extreme end of this concept are serial decoders [51], which implement a single processing element and compute each entry in **H** serially like a microprocessor. However, serial decoding results in throughput too low for

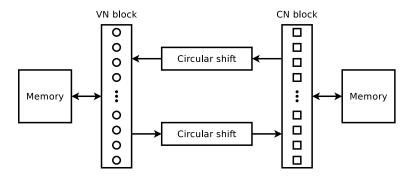

Figure 2–5: Basic architecture for a partially parallel decoder of QC-LDPC codes.

most modern communications applications. Partially parallel architectures aim for a good trade-off between hardware complexity and throughput.

Figure 2–5 shows a straightforward (though inefficient) partially parallel decoder architecture for QC-LDPC codes. The **H** matrix is processed one sub-block at a time, with the partial results stored in memory. The VN and CN blocks are connected through circular shift networks, which implement all the necessary sub-block permutations in **H**.

# 2.4.2 Efficiency Improvements

While these early efforts established the basic algorithms and decoder architectures, a great deal of research effort has since gone into improving upon them. Improvements in hardware and algorithmic efficiency generally also improve energy efficiency, either by reducing the amount of computational "work" needed to decode a frame, or lessening auxiliary circuit implementation issues (such as high parasitic losses in wiring due to routing congestion).

Layered decoding algorithms are one such improvement. Conventional decoding uses a strict two-phase-per-iteration message-passing schedule, in which all VN messages are computed and transmitted, followed by all CN messages (this is sometimes referred to as a "flooding" schedule). Layered decoding algorithms encompass a range of algorithms in which subsets of the graph (referred to as "layers") update their beliefs in sequence, which are then immediately made available to successive layers. For instance, in row-layered decoding [52], subsets of CNs (i.e., rows of H) update in sequence, with the neighbouring VNs immediately updating their beliefs before the next layer of CNs is processed. As a result, the VNs update their beliefs several times per iteration. Column-layered decoding [53] is the same concept with the layers divided into columns. Layered decoding is very popular in modern partially-parallel VLSI implementations, since it significantly reduces the average number of iterations required for convergence to a valid codeword - generally by about a factor of 2. Other message passing schedules similarly yield faster convergence. Turbo-decoding message passing is a special case of row-layered decoding in which each sub-matrix "layer" has a column weight of 1 - this allows VN and CN circuitry to be significantly simplified [54]. An interesting area of ongoing work is residual belief propagation, which uses a type of informed dynamic message passing [55].

In spite of all the interest in partially-parallel decoders, a number of highly-parallel and fully-parallel decoder designs have been proposed. These generally make use of more efficient circuit architectures or heuristics to avoid the hardware complexity and routing issues made famous in [17].

One example, called broadcasting, reduces computational and routing complexity by computing only one outgoing message per node, and broadcasting it to all neighbouring nodes. A half-broadcasting min-sum decoder is proposed in [56], in which broadcasting is applied to the CNs, while the VNs compute unique messages for each outgoing edge as in Equation 2.14. While this is a heuristic, the error correction performance loss can be mostly recovered with local computations in the VN, i.e., if a VN detects that it produced the minimum message, it increases the magnitude of the corresponding message slightly. In this way, the performance loss can be reduced to approximately 0.1 dB. A non-heuristic variant of broadcasting is presented in [57], in which the VNs broadcast a single message, and CNs broadcast 4 messages: first and second minima, the index of the input that produced the first minimum, and the one-bit product of the signs of all incoming messages. The "true" min-sum CN-to-VN messages can then be recovered without any loss via local computations in the VN.

Bit-serial architectures are proposed specifically as energy-efficient LDPC decoder designs in [58] and [59]. In these designs, the messages are exchanged bit-serially over single wires. This not only reduces routing congestion, but also computational complexity, as the primary operations of the MSA (i.e., addition and minimum-finding) are very amenable to bit-serial computation. Despite being fully

parallel, these decoders avoid routing congestion and impractical size due to these characteristics.

The authors of [58] further argue that higher parallelism can be used to improve energy efficiency through voltage and frequency scaling (VFS). Reducing the supply voltage greatly reduces the energy use of a circuit, as dynamic energy consumption scales with  $V_{DD}^2$ . A fully parallel decoder can achieve a given throughput with a lower clock frequency than a less parallel decoder, and can therefore use a lower supply voltage.

Some partially parallel decoders (albeit with a high degree of parallelism) have also been proposed as energy-efficient architectures. One example is [60], which proposes decoders of the (2048, 1723) 10 Gbps Ethernet LDPC code. This code is made up of  $64 \times 64$  permutation sub-matrices, which is exploited using techniques the authors refer to as node grouping and wire bundling. In the implemented decoder, all VNs are implemented in parallel. Each sequentially transmits a single VN-to-CN message, then receives the returning messages from the CNs (as  $d_v = 6$  in this code, a decoding iteration thus takes 12 clock cycles). The computations are non-heuristic offset min-sum, with a post-processing phase for improving error correction

<sup>¶</sup> There is an argument that bit-serial architectures are not fully parallel, as they multiplex computation and message passing over time. However, the cited designs are generally considered fully parallel as they implement the entire graph in parallel - every edge and processing node maps to a unique instance in the circuit. In this dissertation, we use the term "fully node-parallel" when a distinction between the two is required.

performance in the high SNR region by lowering error floors. As this decoder achieves high throughput, VFS is applied to dramatically increase energy efficiency.

A similar architecture called "shift-structured decoding" is presented in [61]. In this design, each VN has fixed connections to a subset of its neighbouring CNs. The CNs are connected together in a circular shift register, which is used to pass messages directly between the CNs for intra-iteration computations. A second inter-iteration communication network between the CNs is used to complete the CN computations. Originally proposed for QC-LDPC codes, this architecture has also been applied to RS-based codes, including the 10 Gbps Ethernet code [62].

Split-row min-sum is another proposed energy-efficient decoding architecture [63]. Split-row decoding uses a heuristic algorithm that divides the **H** matrix into several columns, or sub-codes. Check node computations for each sub-code are performed separately, using limited information from other columns. In other words, the "global" CNs are replaced with several "local" ones with considerably reduced complexity. While the original split-row algorithm had a significant loss in error correction performance, a revised version presented in [64] gained back most of this loss with improved inter-column communication and offsetting computations. A fully-parallel implementation of improved split-row for the 10 Gbps Ethernet LDPC code achieved very high throughput and area efficiency. Prior to the designs presented in this dissertation, split-row also had the best reported energy efficiency for this code.

$<sup>^{\</sup>parallel}$  The topic of error floors is covered in more detail in Chapter 5.

Another approach to energy efficient LDPC decoding is to use a simpler decoding algorithm, thus trading off error correction performance for reductions in complexity and energy cost. There are many decoding algorithms across the performance/complexity range of LDPC decoding. At the low-complexity end of this range are hard decision algorithms, such as the aforementioned Gallager A and B algorithms, bit flipping [65], and majority-based algorithms [66]. At the high-complexity end are SPA and MSA. In the middle are a variety of different decoding algorithms, each offering a different balance between complexity, speed, and error correction performance. Some notable examples are the heuristic variants of MSA mentioned above, hybrid hard-soft algorithms like bootstrap decoding [67], and weighted bit flipping [68]. However, it is generally not desirable to give up significant (or even any) error correction performance, as near-capacity performance is the main reason for using LDPC codes in the first place. Furthermore, communication standards generally include stringent requirements for frame (FER) or bit error rate (BER) that the less complex algorithms cannot achieve.

Two notable examples of reduced-complexity algorithms that achieve error correction performance similar to MSA are stochastic algorithms [69] and differential decoding with binary message passing (DD-BMP) [24]. In stochastic decoding, internode communication is performed with stochastic Bernoulli streams wherein the statistical properties constitute the information being exchanged. These streams are transmitted over single wires, as in bit-serial min-sum, so these decoders do not face routing congestion problems. VN and CN computations are also greatly simplified in the stochastic domain, although additional memory elements are needed to

"decouple" the stochastic streams. Fully parallel stochastic LDPC decoder designs can be found in [70] and [71]. Relaxed half-stochastic (RHS) decoding is a variant in which VN computations are performed in the definite number domain, while message passing and CN computations are performed in the stochastic domain [72].

DD-BMP is a decoding algorithm in which the VNs and CNs exchange binary messages, and the VNs update their beliefs by applying the differential sum of their inputs to their previous states. This algorithm is discussed in more detail in Chapter 5, in which we present VLSI designs of DD-BMP decoders, along with an improved version of this algorithm (called "improved differential binary", or IDB).

Finally, various analog iterative decoders have also been proposed and built [73], [74]. As they operate in the analog domain, these decoders compute continuously and settle into a steady-state equilibrium as they converge, thus avoiding the unnecessary message exchanges that occur in digital decoders. In theory, these characteristics give them very good energy efficiency, potentially much better than digital decoders. However, they are considerably limited by practical factors, especially device mismatch and on-chip process variation. As such, block sizes longer than a few dozen bits are not currently practical. These analog decoders also have much lower throughput compared to digital decoders, in part due to their small block lengths.

# 2.5 Energy Consumption in Digital CMOS Circuits

In digital CMOS circuits, causes of energy consumption can be classified as either static or dynamic [75]. Static energy refers to constant leakage currents that are present even when the circuit is inactive, such as subthreshold conduction in switched-off transistors, electron tunnelling through transistor gates, and leakage

through reverse-biased diodes. Dynamic energy refers to energy dissipated when circuit nodes switch from one voltage level to another. This causes energy to be consumed charging parasitic capacitances, as well as through short-circuit currents caused when an input to a logic gate transitions.

Although static energy consumption has been observed to increase as a share of total energy at smaller manufacturing process sizes, dynamic energy is the dominant factor in LDPC decoder ICs. For instance, in [64], which presents a fully parallel split-row min-sum LDPC decoder in 65 nm CMOS, static power accounts for only 0.5-1% of the total power. Our own research projects, also fully parallel LDPC decoders implemented in 65 nm technology, affirm this number, with leakage accounting for 0.5-3%. Furthermore, recent developments in manufacturing processes have shown that gate leakage currents can be greatly reduced - [76] demonstrates 45 nm transistors with gate leakage currents reduced 2-3 orders of magnitude compared to 65 nm transistors. At even smaller process sizes, emerging devices like fin-FETs have proven successful in keeping leakage currents below practical limits [77] [78].

Leakage can also be controlled using standard circuit design techniques. Subthreshold currents, for instance, can be reduced by using transistors with high threshold voltages. Power gating is another effective technique for eliminating leakage currents in parts of the circuit that are not in use.

Since dynamic energy is the dominant factor, it is a much better target for reduction efforts than static energy. The dynamic energy of a circuit can be approximated by:

$$E_{\rm dyn} = \sum_{\rm nodes} \alpha_{\rm node} C_{\rm node} V_{\rm DD}^2 , \qquad (2.19)$$