# **NOTE TO USERS**

This reproduction is the best copy available.

$UMI^{\circ}$

•

# Analysis and Design of a Gated Envelope Feedback Technique for Automatic Hardware Reconfiguration of RFIC Power Amplifiers, with Full On-Chip Implementation in Gallium Arsenide Heterojunction Bipolar Transistor Technology

by

Nicolas Gérard David Constantin

Department of Electrical & Computer Engineering McGill University, Montreal

McGill University

Montreal, Quebec, Canada

January 12, 2009

A thesis submitted to McGill University in partial fulfilment of the requirements of the degree of Doctor of Philosophy

©Copyright Nicolas G.D. Constantin, 2009. All rights reserved.

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-66275-5 Our file Notre référence ISBN: 978-0-494-66275-5

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### **DEDICATION**

À ma mère, Renée, en remerciement pour son dévouement pour notre famille

### **ABSTRACT**

In this doctoral dissertation, the author presents the theoretical foundation, the analysis and design of analog and RF circuits, the chip level implementation, and the experimental validation pertaining to a new radio frequency integrated circuit (RFIC) power amplifier (PA) architecture that is intended for wireless portable transceivers.

A method called Gated Envelope Feedback is proposed to allow the automatic hardware reconfiguration of a stand-alone RFIC PA in multiple states for power efficiency improvement purposes. The method uses self-operating and fully integrated circuitry comprising RF power detection, switching and sequential logic, and RF envelope feedback in conjunction with a hardware gating function for triggering and activating current reduction mechanisms as a function of the transmitted RF power level. Because of the critical role that RFIC PA components occupy in modern wireless transceivers, and given the major impact that these components have on the overall RF performances and energy consumption in wireless transceivers, very significant benefits stem from the underlying innovations.

The method has been validated through the successful design of a 1.88GHz CDMA RFIC PA with automatic hardware reconfiguration capability, using an industry renowned state-of-the-art GaAs HBT semi-conductor process developed and owned by Skyworks Solutions, Inc., USA. The circuit techniques that have enabled the successful and full on-chip embodiment of the technique are analyzed in details. The IC implementation is discussed, and experimental results showing significant current reduction upon automatic hardware reconfiguration, gain regulation performances, and compliance with the stringent linearity requirements for CDMA transmission demonstrate that the gated envelope

feedback method is a viable and promising approach to automatic hardware reconfiguration of RFIC PA's for current reduction purposes. Moreover, in regard to on-chip integration of advanced PA control functions, it is demonstrated that the method is better positioning GaAs HBT technologies, which are known to offer very competitive RF performances but inherently have limited integration capabilities.

Finally, an analytical approach for the evaluation of inter-modulation distortion (IMD) in envelope feedback architectures is introduced, and the proposed design equations and methodology for IMD analysis may prove very helpful for theoretical analyses, for simulation tasks, and for experimental work.

### **ABRÉGÉ**

Dans cette thèse de doctorat, l'auteur présente les fondements théoriques, l'analyse de circuits analogiques et hyperfréquences, la réalisation de circuits microélectroniques, et les vérifications expérimentales se rattachant à une nouvelle architecture d'amplificateur de puissance intégré RFIC fonctionnant aux hyperfréquences, et dédié aux transmetteurs pour communications sans fil.

Une méthode intitulée Rétroaction d'Enveloppe Conditionnée est proposée afin de rendre possible la reconfiguration automatique d'un amplificateur de puissance RFIC en conditions hardware multiples, dans le but d'améliorer son efficacité énergétique. Cette méthode utilise des circuits entièrement intégrés sur puce et fonctionnant de façon autonome, permettant de déclencher et d'appliquer des mécanismes de réduction de courant dépendamment du niveau de la puissance transmise.

Étant donné le rôle critique qu'occupe un amplificateur de puissance RFIC dans un transmetteur-récepteur pour communications sans fil, ainsi que l'impact important de ses caractéristiques sur les performances électriques et sur la consommation d'énergie, des avantages considérables découlent des concepts innovateurs qui s'y rattachent.

Cette méthode a été validée à travers la conception d'un amplificateur de puissance RFIC à reconfiguration hardware automatique pour transmetteurs CDMA et fonctionnant à 1.88 GHz, en utilisant l'un des procédés de semi-conducteur GaAs HBT appartenant à Skyworks Solutions, Inc., États Unis.

Les techniques de circuits qui ont permis la réalisation complète et réussie de ce système sur puce sont analysées en détails. Les résultats expérimentaux qui sont présentés démontrent la possibilité d'une diminution importante de la consommation de courant suite à la

reconfiguration automatique des circuits, ainsi qu'une compensation automatique du gain avec un taux de régulation attrayant, tout en respectant les normes sévères qui concernent le niveau de distorsion dans les signaux hyperfréquences émis.

Les résultats de ce travail de recherche permettent de mieux positionner la technologie GaAs HBT en ce qui a trait à l'intégration sur puce de fonctions complexes pour le contrôle des amplificateurs de puissance RFIC.

Finalement, une méthode pour l'évaluation de la distorsion dans un amplificateur hyperfréquence utilisant la rétroaction d'enveloppe est introduite dans cette thèse. Les équations qui sont proposées peuvent s'appliquer à des analyses théoriques, à des problèmes de simulation, et à des travaux pratiques.

### **ACKNOWLEDGMENTS**

I am very grateful to Dr. Kenneth Weller, Division Director for RF Integrated Circuits product development at Skyworks Solutions, Inc., Newbury Park, California, USA, for granting me the special favour of having access, under confidentiality agreement, to the fabrication of GaAs HBT Integrated Circuits at Skyworks during my doctoral studies. His trust in my abilities to carry out research work in the RFIC field, since I was a design engineer working in his division in Newbury Park, California, has been a source of encouragement in undertaking my doctoral studies.

I am also very grateful to Dr. Peter J. Zampardi, Technical Director of the Semi-conductor Device Design and Modelling Group at Skyworks Solutions, Inc., Newbury Park, California, for his help in the interpretation of Skyworks' proprietary IC design specifications and procedures, and for interesting discussions and suggested readings on the topic of semi-conductor theory.

Dr. Hongxiao Shao, Systems Administrator at Skyworks Solutions, Inc., Newbury Park, California, has provided me an indispensable support in administrating (remotely from California by internet) the stand-alone computer that I have used for my PhD. research work, and on which he has installed and continuously updated the Skyworks' proprietary computer aided design suite for my GaAs HBT IC designs. I want to express my gratitude to him as well, for this excellent support.

I want to thank Dr. Christos Tsironis, president of Focus Microwaves, Inc., Montreal, Canada, for providing a Focus Microwaves computerized load-pull system, as well as technical support from Focus Microwaves for setting up a load-pull characterization test bench, which has been extremely beneficial to my research work.

I am also grateful to a few members of the technical staff at Skyworks Solutions, Inc., Newbury Park, California: Mr. Tin Ko, for managing the processing of my electronic files for the GaAs HBT RFIC fabrication; Mrs. Jan Blake and Mrs. Theresa Leyva, for their help in managing the inspection, selection and shipment of the IC components; and Mrs. Judi Ulmer for her advice on printed circuit board layout design.

I am thankful to a few staff members at McGill University: Mr. Andrew Bogecho, Senior System Programmer, and Mr. Ron Simpson, System Administrator, for their well appreciated help in solving Unix related problems on my stand-alone computer in several occasions; Mr. Bob Thompson, Electronics Technician, for his help in printed circuit board design and advice in assembly work; and Mr. Don Pavlasek, Machine Shop Supervisor, for the design of the mechanical support for the test jig used during my experimental work.

Finally, I was able to count on the unfaltering support, infinite patience and continuous encouragement from my wife, Elvyra, during my PhD. studies, and I am deeply grateful to her.

## TABLE OF CONTENTS

| DEDICATION                                                                           | i          |

|--------------------------------------------------------------------------------------|------------|

| TABLE OF CONTENTS                                                                    |            |

| LIST OF TABLES                                                                       |            |

| LIST OF FIGURES                                                                      |            |

| Chapter 1                                                                            |            |

| NTRODUCTION - Front-end RFIC power amplifiers for wireless transceivers              |            |

| Generalities: wireless transceivers and their applications                           |            |

| 1.1 The critical role and key technological aspects of front-end RFIC power amplifie | rs         |

| in modern wireless transmitter architectures                                         | 2          |

| 1.1.1. Gain and phase variations in the modulation schemes                           |            |

| Constant envelope modulation                                                         |            |

| Non-constant envelope modulation                                                     | 5          |

| 1.1.2. Power added efficiency                                                        | 5          |

| 1.1.3 The trade-off between efficiency and linearity                                 | 7          |

| 1.1.4. Efficiency improvement in the upper range of the transmitted power levels     | 11         |

| 1.1.5. The importance of current reduction at low to mid-range transmitted power     |            |

| levels                                                                               | 13         |

| 1.2 GaAs HBT technology for linear RFIC PA applications                              | 14         |

| 1.3 The rationale and objectives of this research work                               | 15         |

| 1.4 Thesis outline                                                                   | 16         |

| 1.5 Contributions to research from this work                                         |            |

| (i) RF systems design                                                                | 17         |

| (ii) RF systems analysis                                                             | 17         |

| (iii) RFIC Power amplifier techniques                                                | 18         |

| (iv) RF transmitter front-end architecture design                                    | 18         |

| (v) Gallium Arsenide (GaAs) IC circuit integration                                   | 18         |

| 1.6 Publication                                                                      | 19         |

| CHAPTER 2                                                                            | 20         |

| Scope of research, objectives and theoretical foundation                             | 20         |

| Section 2.1                                                                          | 21         |

| A review of the techniques proposed for current reduction in RFIC power              |            |

| amplifiers at low power levels                                                       | 21         |

| 2.1.1 On the efficiency and linearity improvement methods using digital signal       |            |

| processing techniques and advanced hardware architectures                            | 21         |

| 2.1.2 Proven current reduction techniques at low and mid-range power levels          | 21         |

| Transistor array reconfiguration                                                     | 22         |

| Transistor array switching and bias switching                                        | 22         |

| Output impedance matching control                                                    | 23         |

| Dynamic biasing                                                                      | 24         |

| 2.1.3 Drawbacks and limitations with the state of the art techniques proposed for    |            |

| current reduction at low power levels                                                | 24         |

| Number of control lines                                                              |            |

| Requirement for synchronization                                                      |            |

| Calibration requirements                                                             | 25         |

| Restrictions in regard to the semi-conductor technology                              | 26         |

| Section 2.2                                                                          | 27         |

| Scope and specific research objectives in this work                                  | 27         |

| 2.2.1 The need for novel power amplifier architectures that better address the       | <b>~</b> - |

| demands of wireless communication systems                                            | 27         |

| 2.2.2 Specific research objectives                                                   | 28         |

| Section 2.3                                                                          | 30         |

| A new approach to hardware reconfiguration of RFIC power amplifiers                  |            |

| 2.3.1 Increased PA autonomy                                                          | 30         |

| 2.3.2 Increased PA adaptability through feedback                                     | 30         |

| 2.3.3 Architecture to suit the low integration capability of GaAs technologies     | 31 |

|------------------------------------------------------------------------------------|----|

| 2.3.4 Technological challenges and pertinence to RF System-On-Chip integration     | 31 |

| Section 2.4                                                                        | 33 |

| Some system level considerations pertaining to regulations on RF transmission      | ıs |

| for CDMA2000 wireless equipment                                                    | 33 |

| 2.4.1 Linearity metrics                                                            |    |

| Adjacent channel power rejection (ACPR)                                            | 31 |

| Waveform quality ( $\rho$ )                                                        |    |

|                                                                                    |    |

| Error vector magnitude (EVM)                                                       |    |

| 2.4.2 Transient metrics                                                            |    |

| Power control step response                                                        |    |

| Incremental step precision                                                         |    |

| Section 2.5                                                                        |    |

| Envelope feedback and its practical implementation                                 | 36 |

| 2.5.1 Gain pre-distortion as a building block of envelope feedback                 | 36 |

| Limitations in AM-AM pre-distortion                                                |    |

| Limitations in AM-PM performances                                                  |    |

| Design guidelines for an AM-AM only RFIC pre-distortion circuit embodiment         | 40 |

| 2.5.2 Linear envelope feedback analysis                                            | 41 |

| Section 2.6                                                                        | 47 |

| Introducing a Gated Envelope Feedback technique for automatic hardware             |    |

| reconfiguration of RFIC PA's                                                       |    |

| 2.6.1 Problem statement and motivations                                            |    |

| 2.6.2 Hardware reconfiguration at stepped thresholds within a limited power range. | 48 |

| 2.6.3 Gated Envelope Feedback                                                      | 49 |

| Gating OFF state                                                                   |    |

| Gating ON state with automatic switching                                           |    |

| Effective feedback operation range and crossover range                             | 52 |

| Calibration requirements                                                           | 52 |

| Multi-state conditioning capability with a single control line                     | 53 |

| 2.6.4 Block diagram description                                                    |    |

| Open loop operation                                                                |    |

| Feedback operation                                                                 | 56 |

| Activation of the gating ON condition                                              | 57 |

| Automatic hardware reconfiguration                                                 | 58 |

| 2.6.5 Design specifics for an embodiment in GaAs HBT technology                    |    |

| Gain variations with power                                                         | 60 |

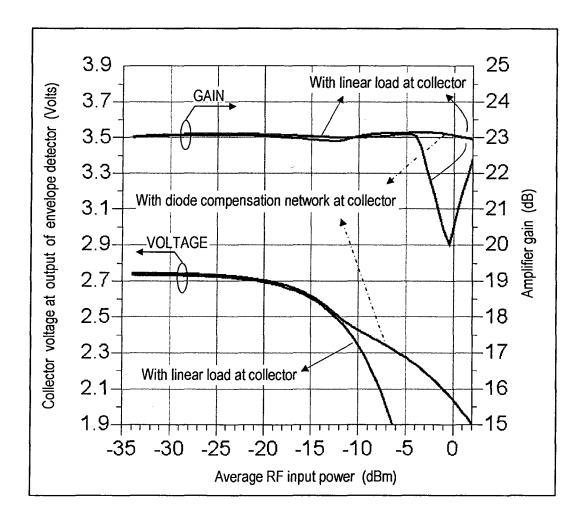

| Nonlinearity introduced by the RF power detectors                                  | 61 |

| Design guidelines for optimally flat gain response over power                      | 61 |

| Section 2.7                                                                        | 63 |

| Multi-tone IMD analysis of an envelope feedback system                             | 63 |

| 2.7.1 The need for simulation independent linearity analysis methods               | 63 |

| The pertinence of design equations in the design and simulation phases             | 64 |

| The pertinence of design equations in an experimental environment                  | 65 |

| 2.7.2 The use of the Volterra series and power series for the analysis of weakly   |    |

| nonlinear systems                                                                  | 66 |

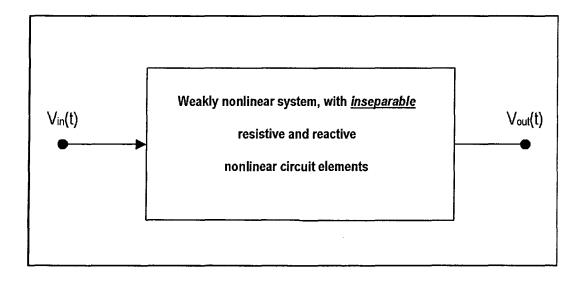

| Systems with inseparable linear reactive elements and memoryless nonlinear         |    |

| elements                                                                           | 66 |

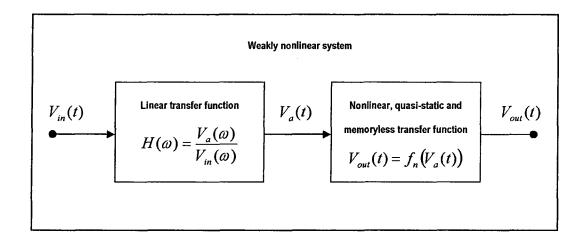

| Systems with separable linear reactive elements and memoryless nonlinear           |    |

| elements                                                                           | 69 |

| Discussion on the general application of the Volterra and power series             | 70 |

| Discussion on the application to an envelope feedback system                       | 72 |

| 2.7.3 Introducing a behavioural model and a design equations based                 | 74 |

| methodology for estimating the IMD performance requirements in the                 | 74 |

| error signal path of an envelope feedback amplifier system                         |    |

| Behavioural model for IMD analysis of an envelope feedback system                  |    |

| Memoryless and quasi-static behaviour assumption                            | 76         |

|-----------------------------------------------------------------------------|------------|

| Approximation for the gain control function                                 | 77         |

| The a priori assumptions made in the proposed methodology                   | 80         |

| Test criterion sought for the circuit blocks in the error signal path       | 81         |

| Degree of nonlinearity for the PA block                                     | 82         |

| 2.7.4 Derivation of the design equations                                    | 83         |

| Summary of design equations for IMD calculation function of the multi-tone  |            |

| amplitudes and system parameters, and under the a priori assumptions        | 90         |

| CHAPTER 3                                                                   | 91         |

| Design of a Gated Envelope Feedback RFIC PA with automatic hardware         |            |

| reconfiguration in GaAs HBT technology                                      | 91         |

| Section 3.1                                                                 | 93         |

| Brief description of Skyworks Solutions' 4th generation                     | 93         |

| GaAs HBT semiconductor technology                                           | 93         |

| 3.1.1 Skyworks Solutions' 4th generation GaAs HBT process                   | 93         |

| Section 3.2                                                                 | 94         |

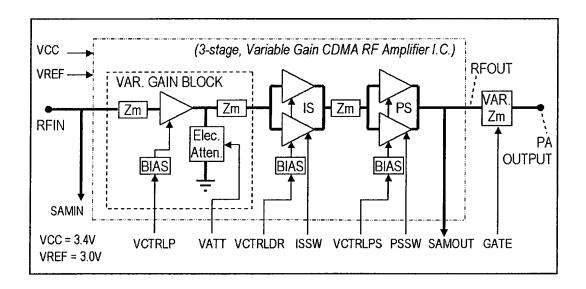

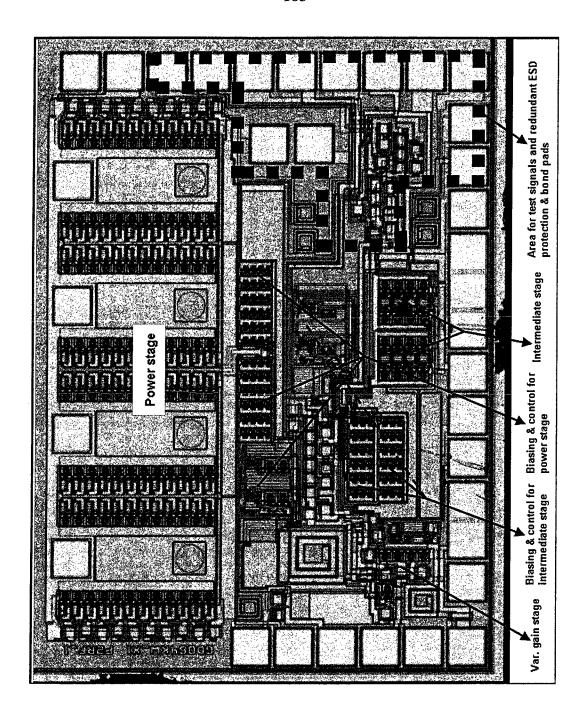

| RF amplifier chain IC                                                       | 94         |

| 3.2.1 RF amplifier chain architecture                                       |            |

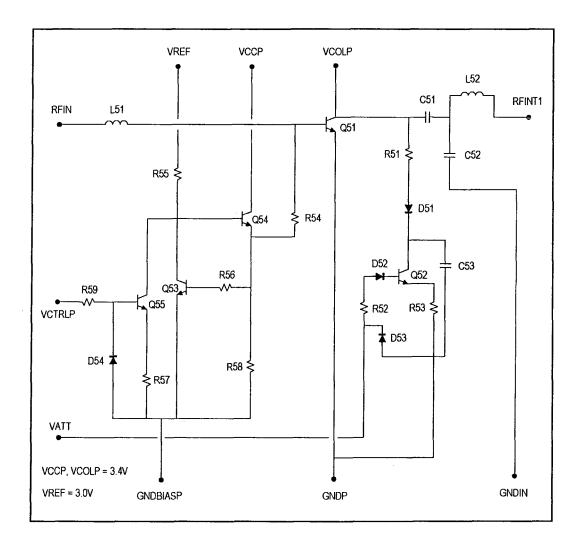

| 3.2.2 Variable gain stage                                                   | 95         |

| Circuit description                                                         | 96         |

| Simulated dynamic range performance                                         | 97         |

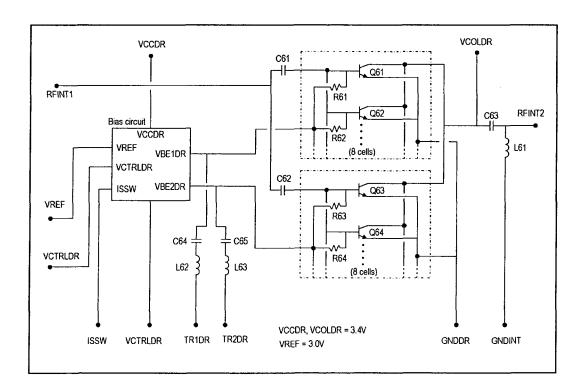

| 3.2.3 Intermediate stage                                                    | 90         |

| RF section                                                                  | 100        |

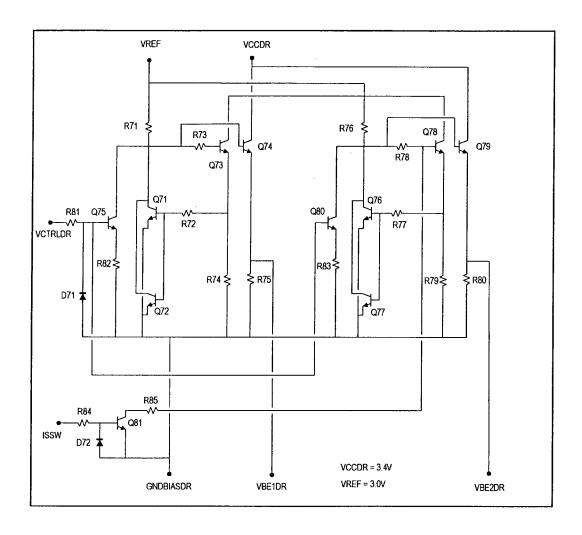

| Bias circuit.                                                               |            |

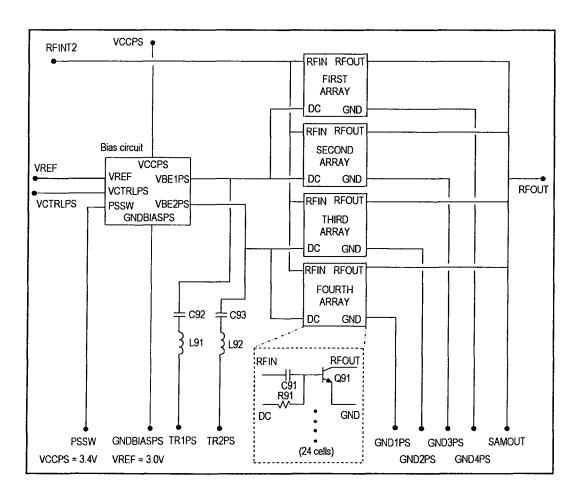

| 3.2.4 Power stage                                                           |            |

| RF section                                                                  | 102        |

| Bias circuit                                                                | 103        |

|                                                                             |            |

| 3.2.5 Output multi-harmonic impedance matching network                      | 104        |

| 3.2.6 IC embodiment of the RF amplifier chain                               | 100        |

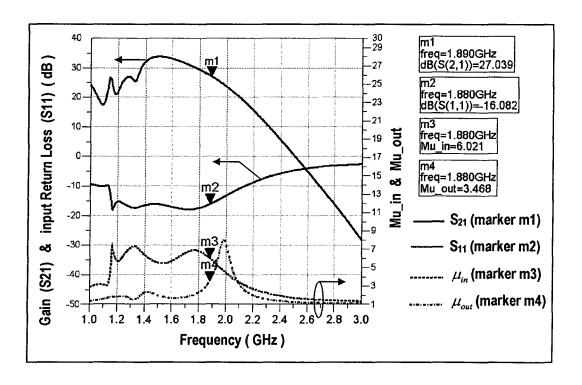

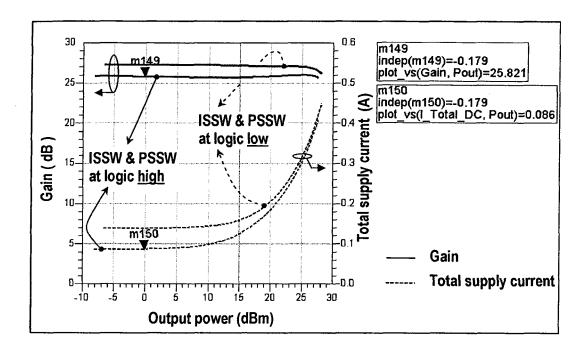

| 3.2.7 Amplifier chain simulated performances                                | 400        |

| Small signal performance                                                    |            |

| Large signal performance                                                    |            |

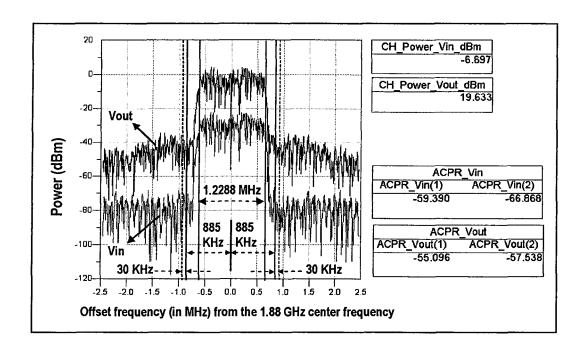

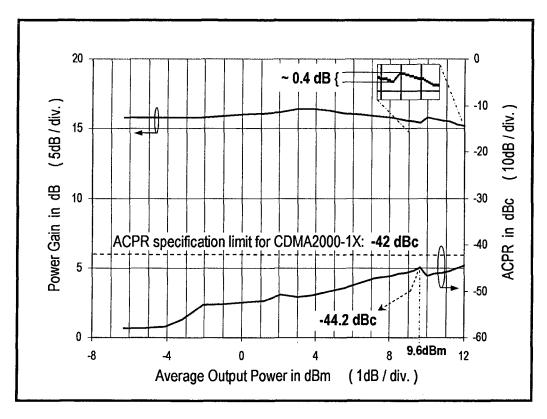

| ACPR performance with CDMA2000 modulation                                   |            |

| Section 3.3                                                                 | 113<br>442 |

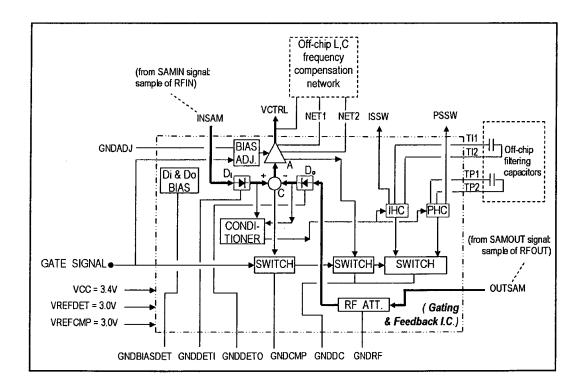

| The gating and feedback controller IC                                       | 113        |

| 3.3.1 Block diagram of the gating and feedback circuitry, and the automatic | 440        |

| reconfiguration circuitry                                                   | 113        |

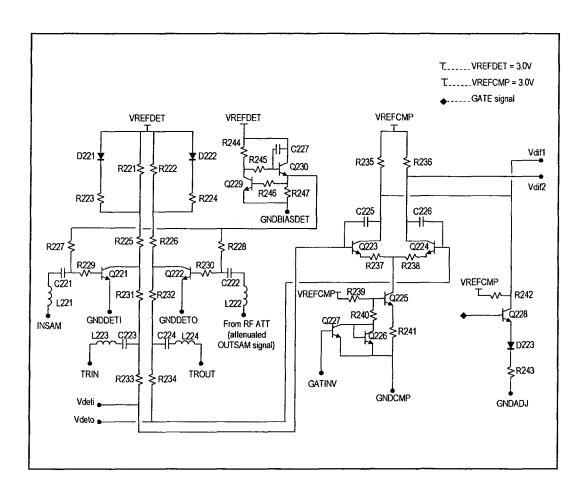

| 3.3.2 Envelope detector and envelope comparator circuits                    | 114        |

| Circuit description                                                         | 115        |

| Nonlinear compensation                                                      | 170        |

| Error comparator circuitry                                                  | 118        |

| DC offset adjustment for small signal gain control                          | 118        |

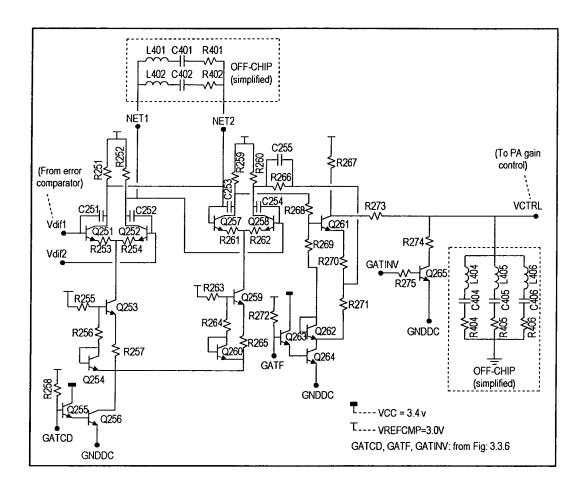

| 3.3.3 The error amplifier and the phase compensator                         | 118        |

| Circuit topology for optimum rejection of noise and perturbations           | 118        |

| Design for optimum gain regulation                                          | 120        |

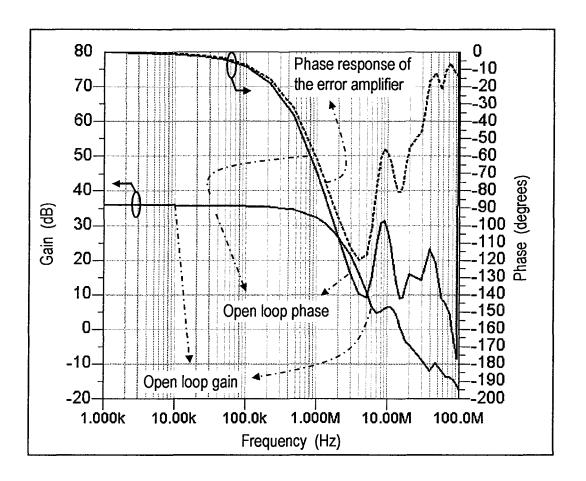

| Simulated open loop envelope frequency response                             | 121        |

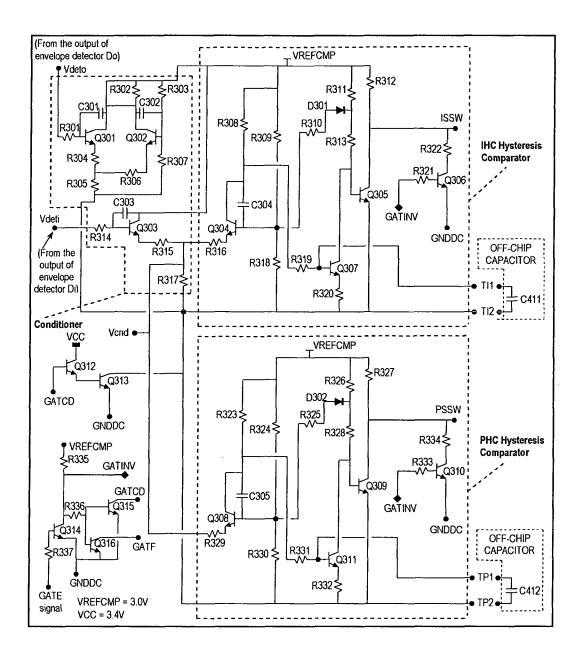

| 3.3.4 Envelope signal conditioner and hysteresis comparator circuits        | 122        |

| Circuit topology                                                            | 123        |

| Switching circuit logic                                                     | 124        |

| Hysteresis function                                                         |            |

| Hysteresis window and time constant adjustment                              | 127        |

| 3.3.5 The RF attenuator circuit                                             | 127        |

| 3.3.6 IC embodiment of the gating and feedback circuitry, and the hardware  |            |

| reconfiguration control circuitry                                           |            |

| Section 3.4                                                                 | 130        |

| Simulation results for closed loop operation and IMD analysis based on the                                                                                         |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| proposed design equations                                                                                                                                          |            |

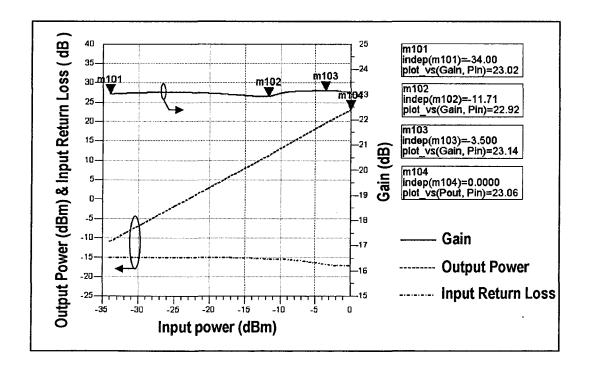

| 3.4.1 Gain, output power, and input return loss performances                                                                                                       | .130       |

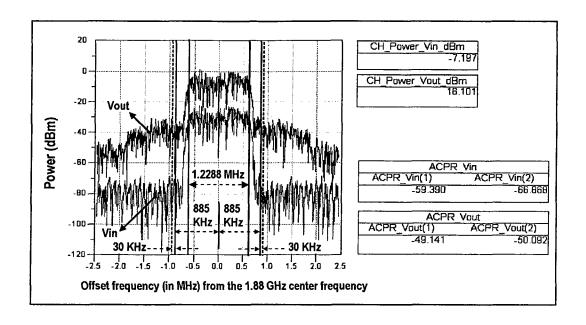

| 3.4.2 ACPR performance with a CDMA2000-1X excitation                                                                                                               | .131       |

| 3.4.3 Analysis of localized linearity performances of the RF envelope detectors                                                                                    | . 132      |

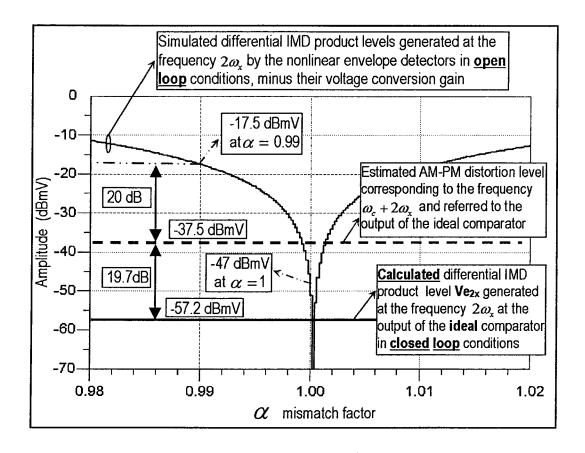

| Localized nonlinearity effect introduced by the envelope detector compensation circuitry                                                                           | . 133      |

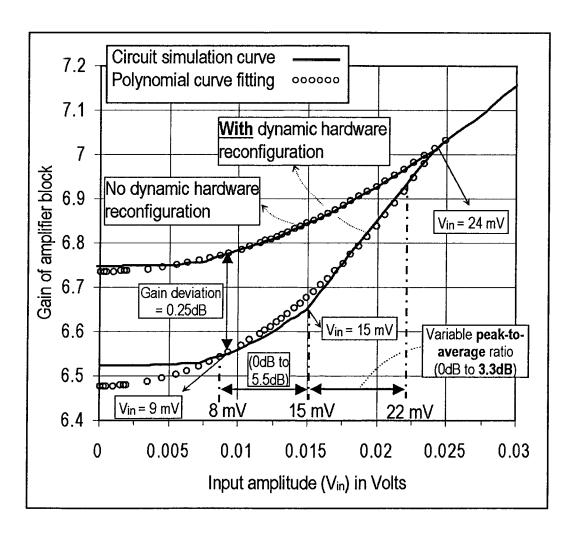

| Approximation for the gain control element                                                                                                                         | .134       |

| Small signal open loop parameters                                                                                                                                  | . 137      |

| Power series representation of the amplifier block                                                                                                                 | .138       |

| Calculation of AM-AM closed loop bench-marking distortion levels from the                                                                                          |            |

| solutions to the system of nonlinear equations (2.7.23)                                                                                                            | .140       |

| Verification of the convergence for computation with MATLAB'                                                                                                       | . 142      |

| Validation of the results through simulation with an envelope signal path model. Solutions for different excitation amplitudes and gain parameters in the feedback |            |

| pathpath                                                                                                                                                           | `<br>146   |

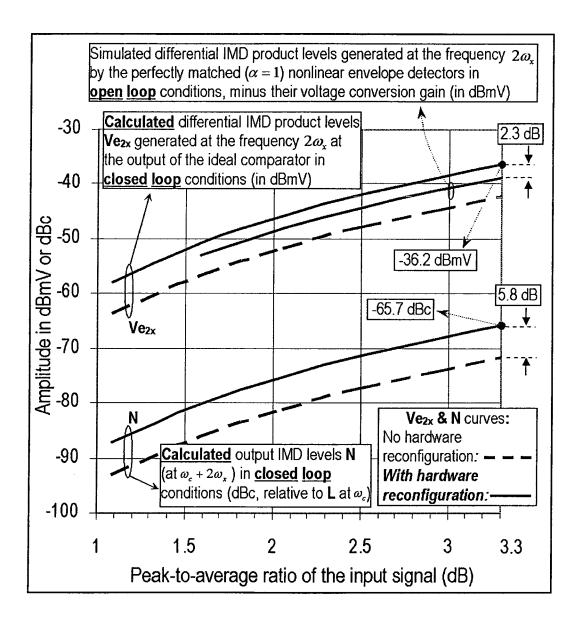

| Pertinence of analyzing the Ve <sub>2x</sub> IMD level at the frequency $2\omega_x$ in the                                                                         |            |

| error signal path, and the output distortion at $\omega_c^{}\pm2\omega_x^{}$                                                                                       | . 147      |

| Estimation of the output AM-PM distortion level at $\omega_c \pm 2\omega_x$                                                                                        |            |

| Validation of the design methodology through a comparison between                                                                                                  |            |

| the calculated $\mathit{Ve}_{2x}$ IMD levels and simulation results using the actual                                                                               |            |

| RF amplifier chain circuitry                                                                                                                                       | . 149      |

| Bench-marking of the detectors' linearity performance against the calculated IMI                                                                                   |            |

| levels in the error signal path                                                                                                                                    |            |

| Design trade-offs based on the solutions to the design equations                                                                                                   |            |

| An insight into the uncertainty due to the dependency of $P$ on $V_i$                                                                                              |            |

| Conclusion from the analysis                                                                                                                                       | .161       |

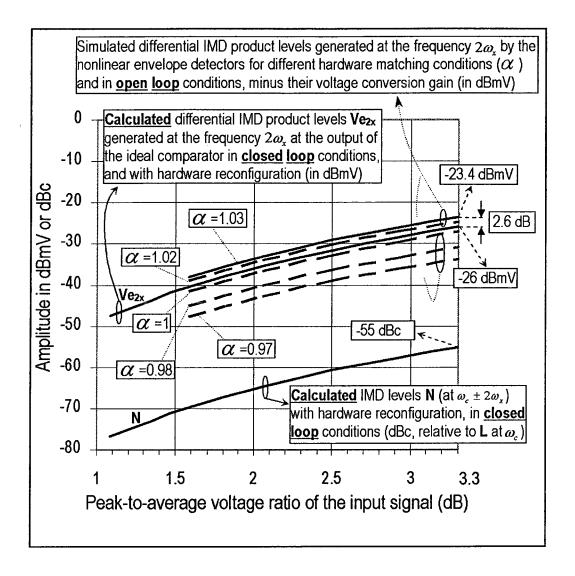

| 3.4.4 Gating design example using the design equations: distortion analysis of dynamic hardware reconfiguration - with no hysteresis function - within the soft    |            |

| crossover range                                                                                                                                                    |            |

| Hardware reconfiguration scheme                                                                                                                                    |            |

| Small signal envelope feedback parameters                                                                                                                          | . 165      |

| Calculated AM-AM closed loop distortion, and simulated detector linearity                                                                                          | 166        |

| performance in open loop Output AM-PM distortion level                                                                                                             |            |

| Comparison with the detectors' linearity performance                                                                                                               |            |

| IMD performance optimization and design requirements for the detectors' lineari                                                                                    | tv         |

| performance and the analog amplifier gain                                                                                                                          | 171        |

| Approximate IMD design goal                                                                                                                                        | 171        |

| Solving for the minimum value of $A_{v}$                                                                                                                           |            |

| Solving for the IMD performance with the optimized analog amplifier gain                                                                                           |            |

| Linearity performance requirements for the envelope detectors                                                                                                      |            |

| The uncertainty due to the approximation in the gain control function                                                                                              |            |

| Conclusion from the analysis                                                                                                                                       | 178        |

| 3.4.5 Discussion on the use of the design equations                                                                                                                | 179        |

| Extension to analyses with higher degree polynomials                                                                                                               | 179        |

| Synthesis of the gain profile in a dynamic hardware reconfiguration, function of                                                                                   | 401        |

| linearity performances                                                                                                                                             |            |

| Chapter 4 IC implementation and experimental results                                                                                                               | 103<br>122 |

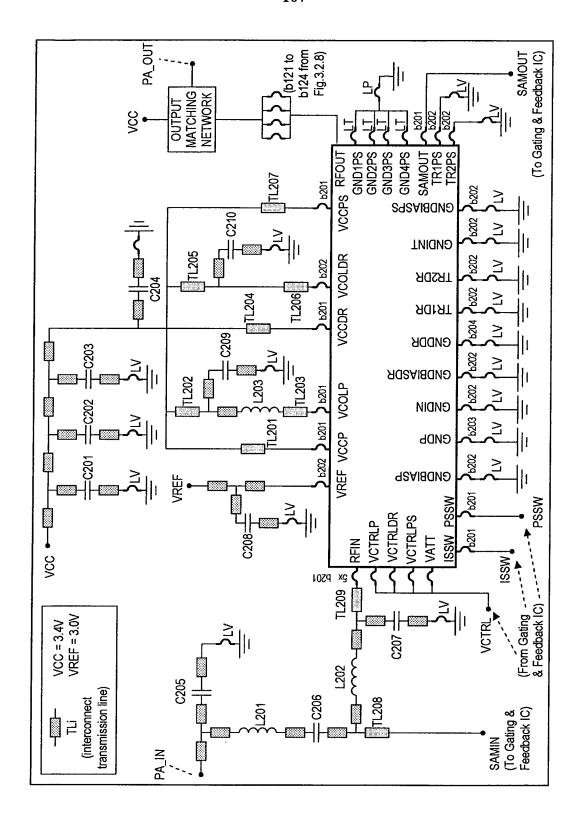

| Section 4.1                                                                                                                                                        |            |

| OVORON TELESCOPE                                                                                                                                                   | , 54       |

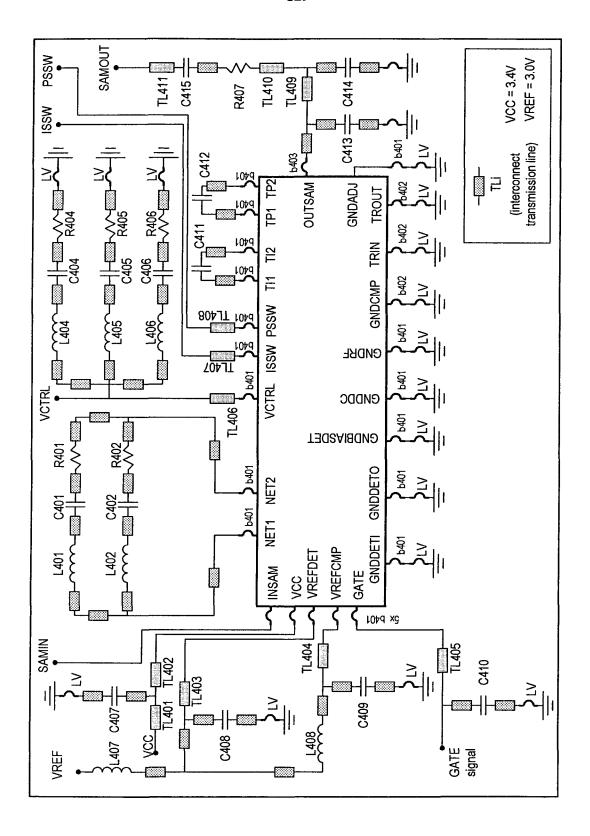

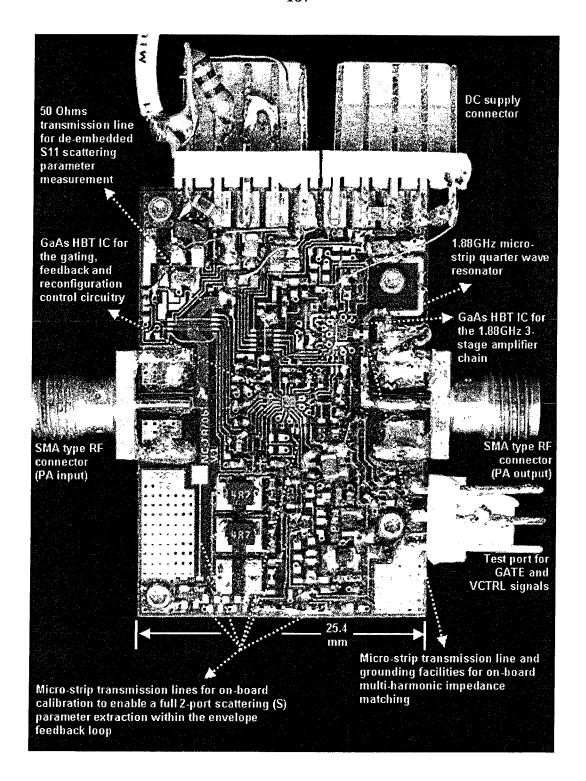

| IC Layout partitioning in GaAs HBT technology and implementation on the test board                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

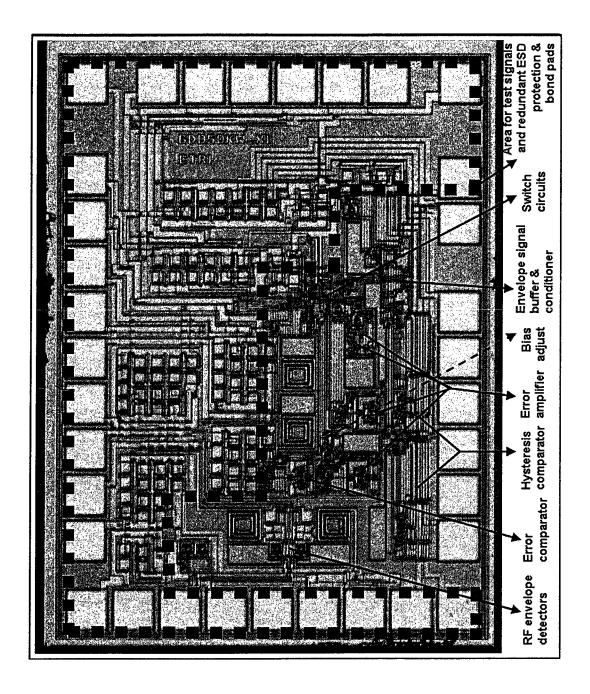

| 4.1.2 GaAs HBT die for the gating, feedback and automatic reconfiguration control circuits                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1.3 Implementation on the printed circuit test board                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Section 4.2188Experimental results1884.2.1 Gain deviation upon hardware reconfiguration1884.2.2 Gain regulation upon automatic hardware reconfiguration1894.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198 |

| Experimental results1884.2.1 Gain deviation upon hardware reconfiguration1884.2.2 Gain regulation upon automatic hardware reconfiguration1894.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198               |

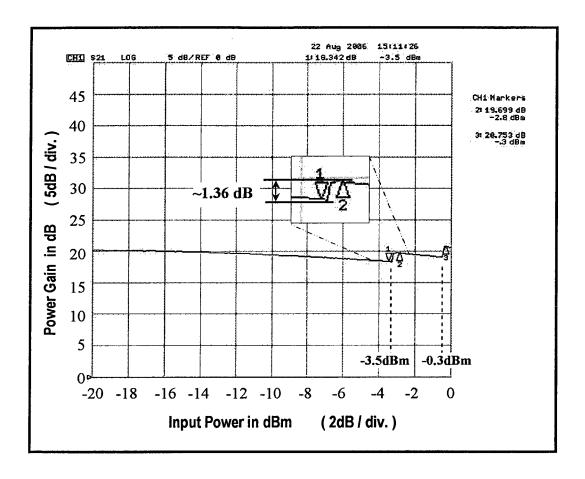

| 4.2.1 Gain deviation upon hardware reconfiguration1884.2.2 Gain regulation upon automatic hardware reconfiguration1894.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                      |

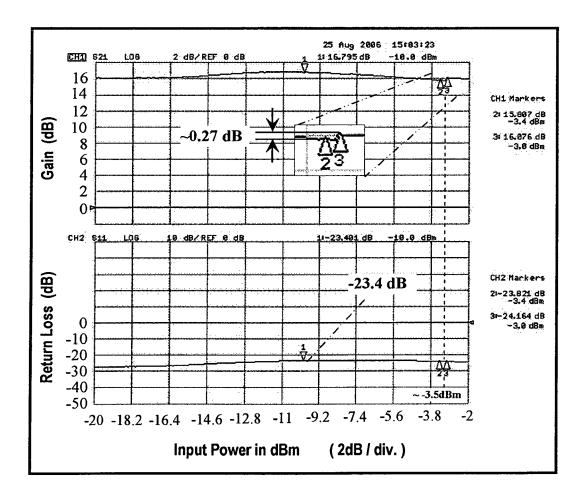

| 4.2.2 Gain regulation upon automatic hardware reconfiguration1894.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                           |

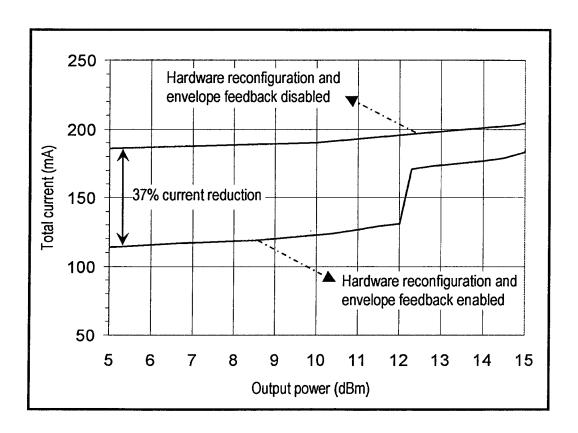

| 4.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                           |

| 4.2.3 Current reduction1914.2.4 ACPR performance with CDMA2000-1X modulation for an192average input power within the effective feedback operation range1924.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                           |

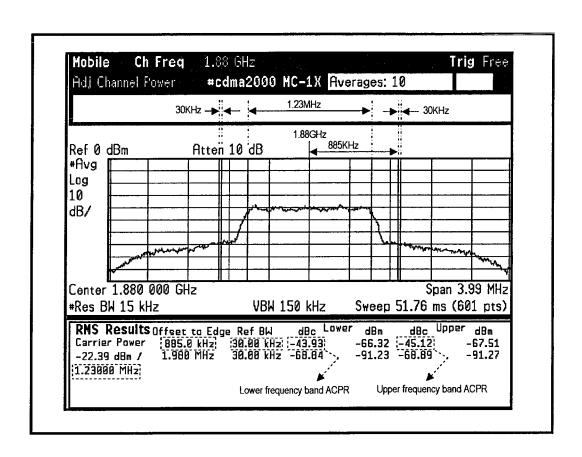

| average input power within the effective feedback operation range                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2.5 ACPR and gain regulation versus power1934.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                                                                                                                                                                                     |

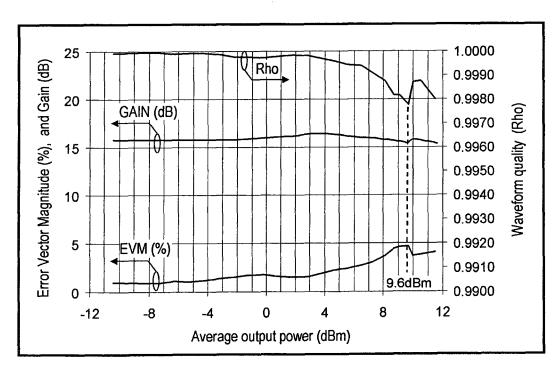

| 4.2.6 Waveform quality versus power1944.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                                                                                                                                                                                                                                   |

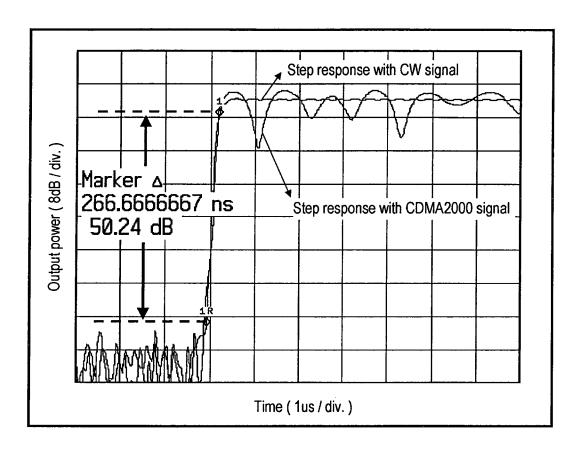

| 4.2.7 Stability and transient performances1954.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2.8 Discussion on the experimental results196Power gain197Gain regulation198                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Gain regulation198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Current reduction and power added efficiency198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Adjustment of the power thresholds199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Difference in the power thresholds between the CW modulation case and the                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CDMA modulation case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The importance of on-chip isolation design techniques201                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CONCLUSION & FUTURE WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Demonstrated multi-state hardware reconfiguration capability,                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| increased RFIC PA autonomy, and flexibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Envelope feedback gating, hardware reconfiguration circuitry, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| design guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Demonstrated suitability for GaAs HBT technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Demonstrated functionality and performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Design equations and a methodology for IMD analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.2 Topics for future research 207                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Circuit techniques for better on-chip isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Integration in GaAs BiFET technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Envelope feedback IMD analysis and characterization209                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Some electrical specifications for the active and passive devices in Skyworks' HBT4-                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P401 GaAs HBT library210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Appendix II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Components values 211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UST OF REFERENCES 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### LIST OF TABLES

| Table 3.0.1: Targeted functional and performance specifications                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

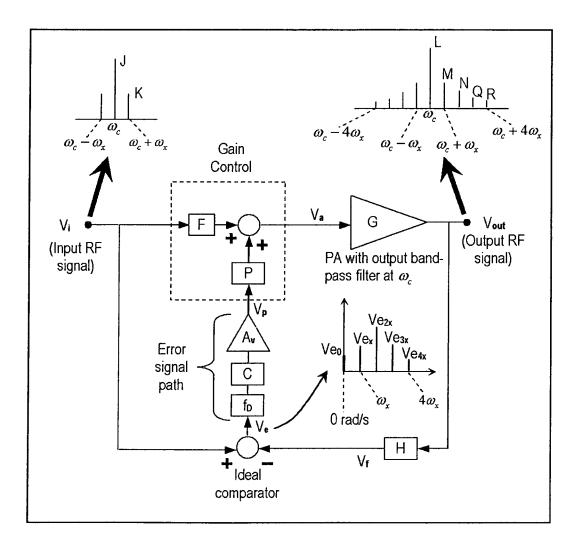

| system of Fig. 2.7.3, as well as the envelope error signal components $\mathit{Ve}_{\scriptscriptstyle{0}}$ , $\mathit{Ve}_{\scriptscriptstyle{x}}$ , $\mathit{Ve}_{\scriptscriptstyle{2x}}$ ,                                                                                                                                                                                                                                                |

| $Ve_{3x}$ and $Ve_{4x}$ 140                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 3.4.2: Amplitudes of the mixing products $L,M,N,Q,$ and $R$ at the output of                                                                                                                                                                                                                                                                                                                                                            |

| the amplifier system, and of the mixing products $\mathit{Ve}_{0}$ , $\mathit{Ve}_{x}$ , $\mathit{Ve}_{2x}$ , $\mathit{Ve}_{3x}$ , and $\mathit{Ve}_{4x}$ of the                                                                                                                                                                                                                                                                              |

| error signal at the output of the ideal comparator of Fig. 2.7.3                                                                                                                                                                                                                                                                                                                                                                              |

| Table 3.4.4: Comparison between the solutions to the input variables and system conditions set in Table 3.4.1, and obtained from the design equations (2.7.23) and from the simulation set-up of Fig. 3.4.5                                                                                                                                                                                                                                   |

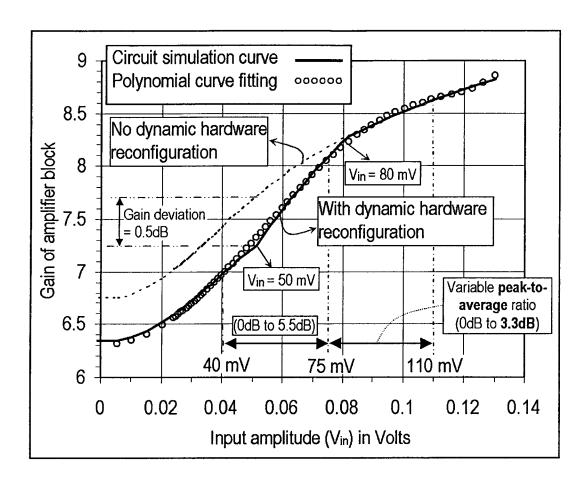

| system of Fig. 2.7.3, for the two cases of Fig. 3.4.7, i.e. case (i): with no dynamic hardware reconfiguration, and case (ii): with dynamic hardware reconfiguration166 Table 3.4.6: Solutions to the system of equations (2.7.23) with the parameters of case (ii) in Table 3.4.5 (with dynamic hardware reconfiguration) as input variables, and for an envelope peak-to-average voltage ratio of 3.3dB (i.e. $J = 15$ mV, $K = 3.5$ mV)170 |

### LIST OF FIGURES

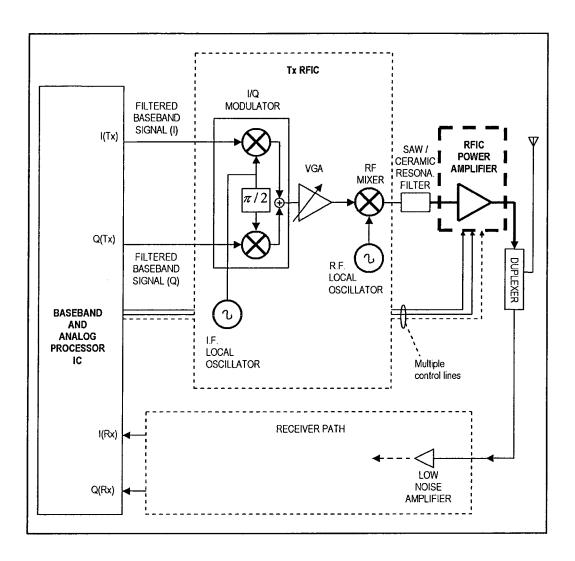

| Figure 1.1.1: Block diagram of the transmitter path in a typical modern super-heterodyne                                                                              |                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| wireless transceiver employing orthogonal modulation                                                                                                                  |                  |

| Figure 1.1.2: Block diagram of a typical RF power ampliner section                                                                                                    | J                |

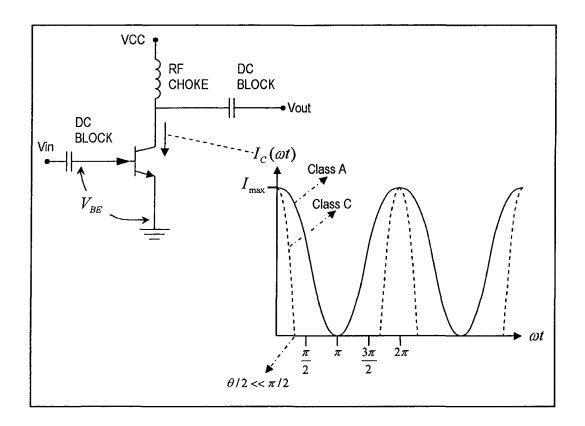

| excitation for different collector current conduction angles.                                                                                                         | 2                |

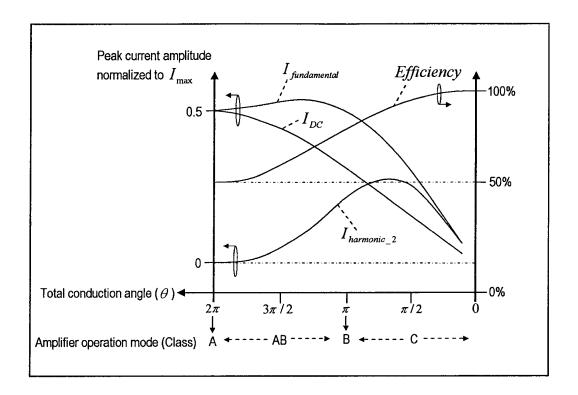

| Figure 1.1.4: Normalized current amplitudes of the average current and the current                                                                                    | ,                |

|                                                                                                                                                                       |                  |

| harmonic content, and the output efficiency as a function of the total conduction angle (from [8])                                                                    | `                |

| (from [8])                                                                                                                                                            | ,                |

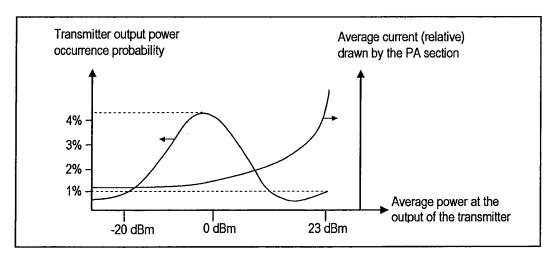

|                                                                                                                                                                       | 2                |

| and the typical associated average current consumption on a relative scale (from [5]) 13                                                                              | ,                |

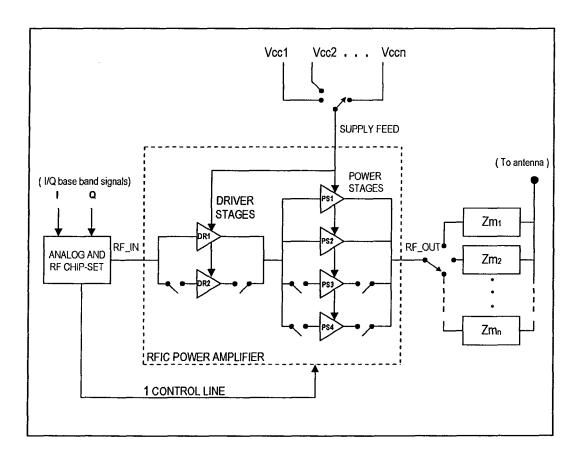

| Figure 2.2.1: Illustration of an RFIC power amplifier architecture, which describes the                                                                               |                  |

| hardware flexibility and automatic reconfiguration capabilities addressed during the course of this research work                                                     | 1                |

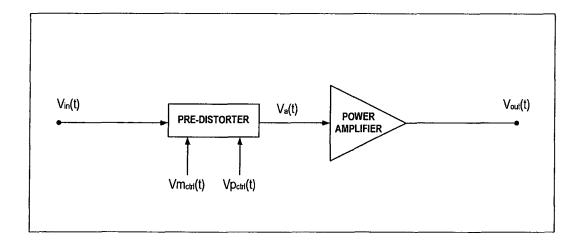

| course of this research work29 Figure 2.5.1: Block diagram illustrating the pre-distortion of an amplifier                                                            |                  |

|                                                                                                                                                                       | ,                |

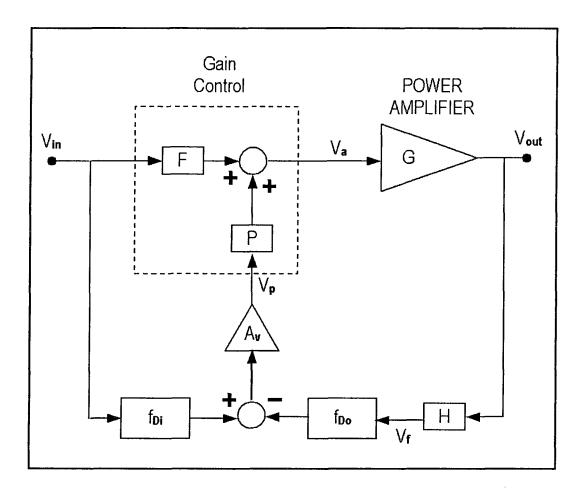

| Figure 2.5.2: Small signal representation of the envelope signal path in an envelope<br>feedback amplifier system42                                                   | ,                |

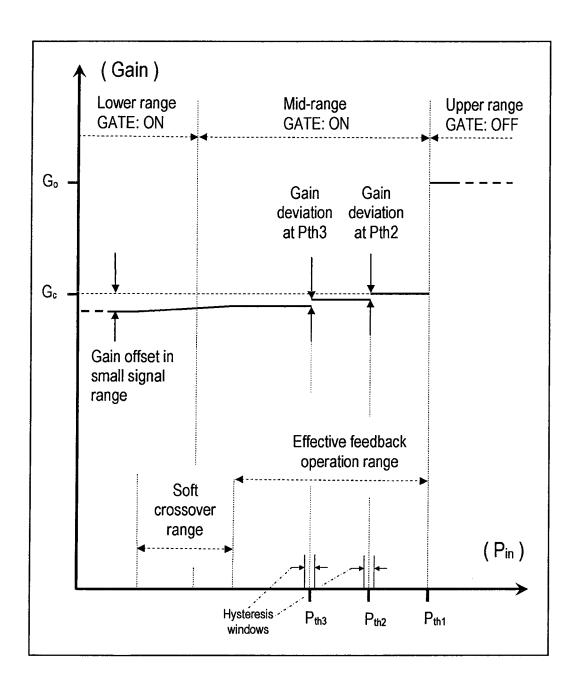

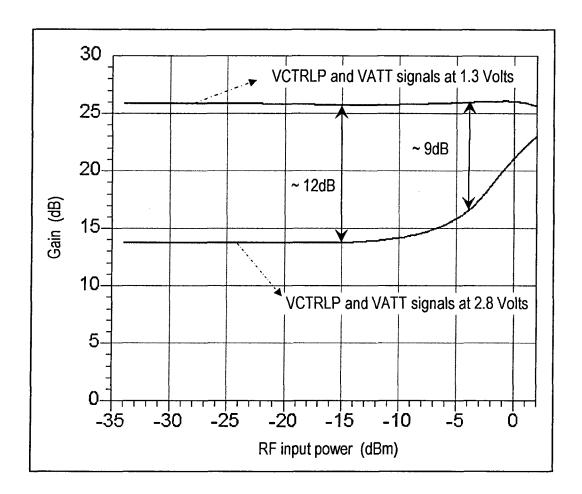

| feedback amplifier system42 Figure 2.6.1: The gated envelope feedback concept illustrated on a gain versus average                                                    | -                |

|                                                                                                                                                                       | ١                |

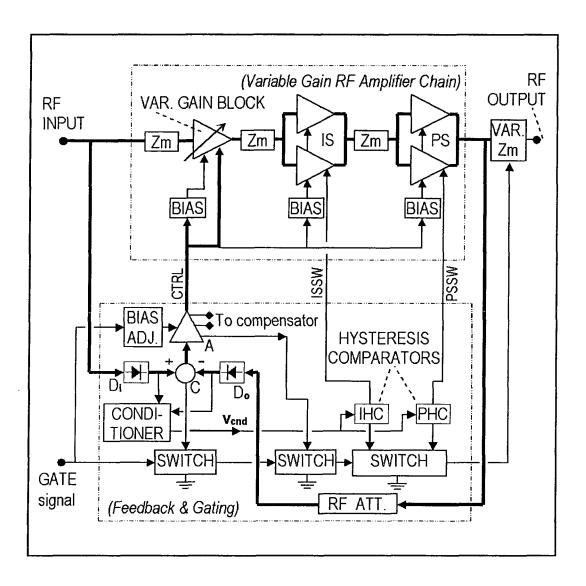

| input power curve50 Figure 2.6.2: Block diagram of a gated envelope feedback implementation54                                                                         |                  |

|                                                                                                                                                                       | t                |

| Figure 2.7.1: Weakly nonlinear system with inseparable resistive and reactive elements.                                                                               | :                |

| Figure 2.7.2: Representation of a weakly nonlinear system as a circuit block with all                                                                                 | ,                |

| reactive elements of the system, followed by a circuit block containing quasi-static and                                                                              |                  |

| memoryless nonlinear elements only69                                                                                                                                  | 1                |

| Figure 2.7.3: Block diagram representing a behavioural model for multi-tone IMD analysis                                                                              |                  |

| of an envelope feedback based RF amplifier76                                                                                                                          | :                |

|                                                                                                                                                                       | ,                |

|                                                                                                                                                                       |                  |

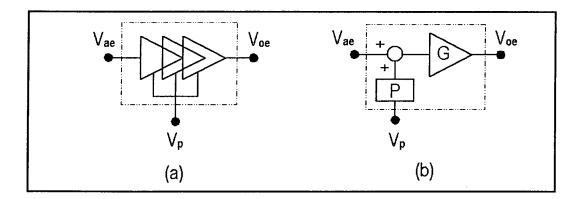

| Figure 2.7.4: A variable gain amplifier chain in (a), with a gain control signal $V_p^{}$ , and an                                                                    |                  |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$ 77                                                                                          |                  |

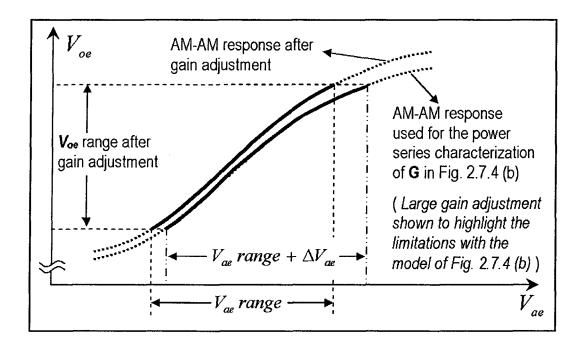

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$ 77 Figure 2.7.5: AM-AM curves illustrating the limitations of the model in Fig. 2.7.4 (b)78 | 3                |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 1                |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 1                |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3                |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3                |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 4 5            |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 3 3            |

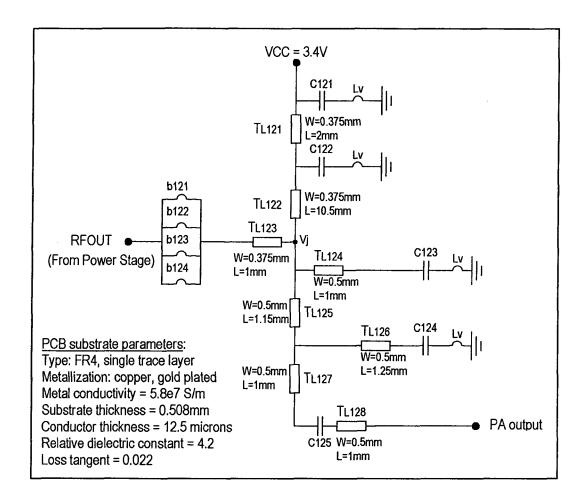

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 3 9 1 2        |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 3 9 1 2        |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 3 3 1 2 1      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 3 3 3 1 2 1      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121        |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121        |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121        |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121 5      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121 5      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121 5      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121 5      |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39124 5 7    |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39124 5 7    |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39124 5 7    |

| approximate model in (b), assuming small variations in $V_{ae}$ and $V_p$                                                                                             | 315 39121 5 7 9) |

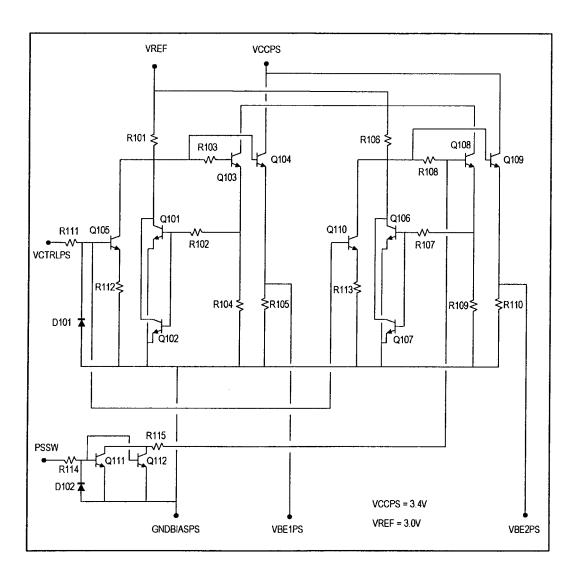

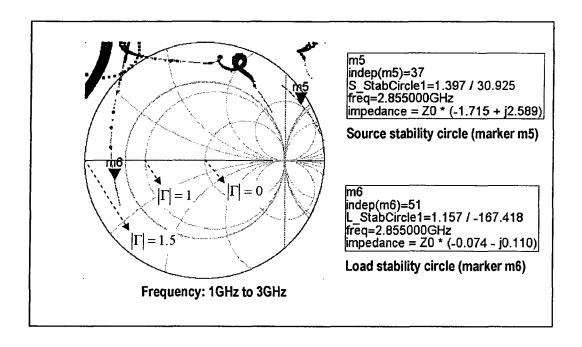

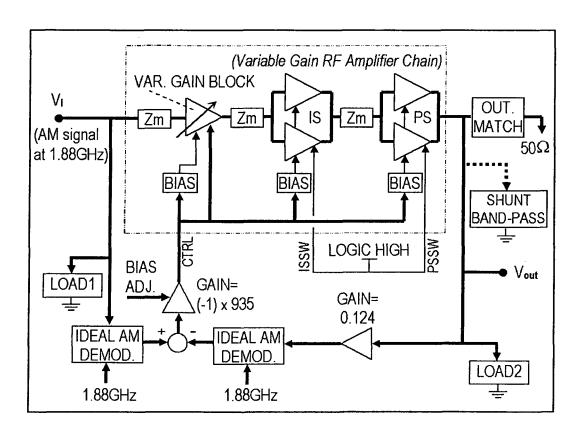

| Figure 3.3.1: Block diagram of the gating, envelope feedback and hardware                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| reconfiguration control circuitry113                                                                                                           |

| Figure 3.3.2: Schematic of the RF envelope detectors with their separate bias circuit, the                                                     |

| envelope comparator, and the d.c. offset adjustment circuitry114                                                                               |

| Figure 3.3.3 The simulated dynamic range of the envelope detector and the gain of the                                                          |

| amplifier system, versus the average input power117                                                                                            |

| Figure 3.3.4: Schematic of the error amplifier119                                                                                              |

| Figure 3.3.5: Simulated open loop envelope gain and phase response of the amplifier                                                            |

| system in the condition where ISSW and PSSW are at logic high (see also Fig. 3.2.12).                                                          |

| The phase response that is required in the analog error amplifier to achieve the stability                                                     |

| and transient performance goals is also shown122                                                                                               |

| Figure 3.3.6: Schematics of the envelope signal conditioner, the two hysteresis                                                                |

| comparators, and the GATE signal buffering.                                                                                                    |

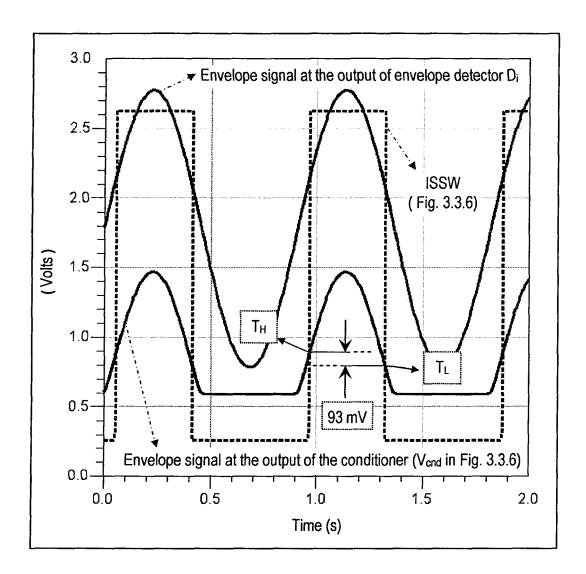

| Figure 3.3.7: Simulation results showing the signal conditioning of the envelope signal                                                        |

| and the output activation signal of one of the hysteresis comparators (IHC), for automatic                                                     |

| hardware reconfiguration                                                                                                                       |

| Figure 3.3.8 IC embodiment of the gating, envelope feedback and hardware                                                                       |

| reconfiguration control circuitry.                                                                                                             |

| Figure 3.4.1: Simulated gain, output power and return loss performance of the amplifier                                                        |

| system in closed loop operation as a function of the input power                                                                               |

| Figure 3.4.2: Simulated linearity performance (V <sub>out</sub> ) in closed loop operation with a                                              |

| CDMA2000-1X input excitation.                                                                                                                  |

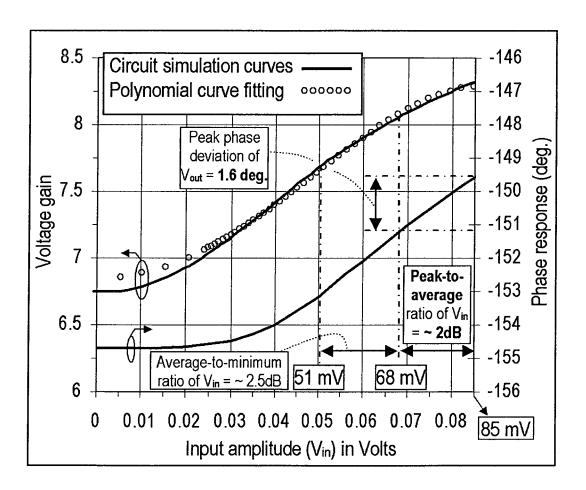

| Figure 3.4.3: Simulation results for the amplifier block's band-limited input to output gain                                                   |

| and phase relationship together with a 5 <sup>th</sup> degree polynomial curve fitting based on the                                            |

| and phase relationship, together with a 5 <sup>th</sup> degree polynomial curve fitting based on the coefficients $a_1$ , $a_3$ ', and $a_5$ ' |

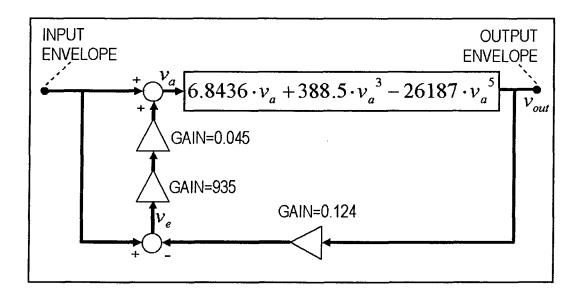

| Figure 3.4.4: Block diagram used for simulation and validation of the computed solutions                                                       |

| reported in Table 3.4.2.                                                                                                                       |

| Figure 3.4.5: Simulation set-up using the complete RF amplifier IC circuitry for the                                                           |

| validation of the IMD product solutions obtained from the design equations and which                                                           |

| were reported in Table 3.4.2                                                                                                                   |

| Figure 3.4.6: Simulated amplitude of the $2\omega_x$ frequency component in the differential                                                   |

| ···                                                                                                                                            |