# Design and implementation of a gigabit-rate optical receiver and a digital frequency-locked loop for phase-locked loop based applications

Francis Beaudoin

Department of Electrical and Computer Engineering

McGill University

Montréal, Canada

October 2003

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements of the degree of Master of Engineering

© Francis Beaudoin, 2003.

Library and Archives Canada

Bibliothèque et ada Archives Canada

Published Heritage Branch

Direction du Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-98510-5 Our file Notre référence ISBN: 0-612-98510-5

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

## **Table of Content**

| Table of    | Content | ****** |                                         | , ,   | ·<br>• • • • • • • • • • • • • • • • • • • |   |

|-------------|---------|--------|-----------------------------------------|-------|--------------------------------------------|---|

| List of F   | igures  |        | • • • • • • • • • • • • • • • • • • • • | ••••• |                                            | 4 |

|             |         |        |                                         |       |                                            |   |

|             |         |        |                                         |       |                                            |   |

| Remerci     |         |        |                                         |       |                                            |   |

| C H         |         |        |                                         |       | Introduction                               |   |

| 1.1         |         |        |                                         |       |                                            |   |

| 1.2         |         |        |                                         |       |                                            |   |

| 1.3         |         |        |                                         |       |                                            |   |

| 1.4         |         |        |                                         |       |                                            |   |

| 1.5         |         |        |                                         |       |                                            |   |

| 1.6         |         |        |                                         |       |                                            |   |

| C H         | A P     |        |                                         |       | Optical Receivers Basics                   |   |

| 2.1         |         |        |                                         |       |                                            |   |

| 2.1.        |         |        |                                         |       |                                            |   |

| 2.1.        |         |        |                                         |       |                                            |   |

| 2.1.        |         |        |                                         |       | ······                                     |   |

| 2.2         |         |        |                                         |       | tion systems                               |   |

| 2.3         |         |        |                                         |       |                                            |   |

| 2.4         |         |        |                                         |       |                                            |   |

| 2.5<br>2.5. |         |        |                                         |       |                                            |   |

| 2.3.        |         |        |                                         |       |                                            |   |

| 2.6         |         |        |                                         |       |                                            |   |

| 2.7         |         |        |                                         |       | •••••                                      |   |

| 2.7.        |         |        |                                         |       | JRZ data stream                            |   |

| 2.7         |         |        |                                         |       | vice data su vani                          |   |

| 2.8         |         |        |                                         |       |                                            |   |

| 2.9         |         |        |                                         |       |                                            |   |

| 2.10        |         |        |                                         |       |                                            |   |

| 2.11        |         |        |                                         |       |                                            |   |

| 2.12        |         |        |                                         |       |                                            |   |

| C H         | A P     |        |                                         |       | Transimpedance and Limiting                |   |

|             |         |        |                                         |       |                                            |   |

| <i>-</i>    |         |        |                                         |       |                                            |   |

|   | 3.1     | Receiver front-end                          | 35  |

|---|---------|---------------------------------------------|-----|

|   | 3.2     | Type of preamplifier                        |     |

|   | 3.2.1   | High-impedance amplifiers                   | 37  |

|   | 3.2.2   |                                             |     |

|   | 3.3     | TIA Design.                                 | 38  |

|   | 3.3.1   |                                             |     |

|   | 3.4     | TIA noise analysis                          | 41  |

|   | 3.4.1   | Generic TIA noise derivation                | 42  |

|   | 3.5     | 5Gb/s TIA with a resonant network           | 44  |

|   | 3.6     | Limiting amplifier design                   | 47  |

|   | 3.6.1   | Offsets                                     | 48  |

|   | 3.6.2   | 2 Offset-induced jitter                     | 50  |

|   | 3.6.3   | 5.0Gb/s Limiting amplifier                  | 51  |

|   | 3.7     | Noise analysis (NF) of a limiting amplifier | 53. |

|   | 3.8     | Conclusion                                  | 54  |

|   | 3.9     | References                                  | 54  |

| C | H       | A P T E R 4 TIA and LA Simulations and      |     |

| M | easurer | ment Results                                |     |

|   | 4.1     | Test circuit                                | 56  |

|   | 4.2     | Bandwidth                                   | 58  |

|   | 4.2.1   | Results analysis                            | 60  |

|   | 4.3     | Eye diagram                                 | 61  |

|   | 4.3.1   | Simulated eye diagram                       |     |

|   | 4.3.2   | , U                                         |     |

|   | 4.4     | Noise                                       | 66  |

|   | 4.5     | Sensitivity calculation                     |     |

|   | 4.6     | Layout, packaging, and PCB                  |     |

|   | 4.7     | Conclusion                                  |     |

|   | 4.8     | References                                  |     |

| C |         | A P T E R 5 Digital Frequency-Locked Loop   |     |

|   | 5.1     | CDR basics                                  |     |

|   |         | 1 CDR basic operation                       |     |

|   |         | 2 Analog phase detector limitations         |     |

|   | 5.2     |                                             |     |

|   | 5.2.    | , 0                                         |     |

|   | 5.2.2   | 3.                                          |     |

|   | 5.2.3   | 1 1                                         |     |

|   | 5.2.4   | 1                                           |     |

|   | 5.3     | DFLL design                                 |     |

|   | 5.3.    | · · · · · · · · · · · · · · · · · · ·       |     |

|   | 5.3.2   | <u> </u>                                    |     |

|   | 5.3.3   | <i>D</i> 1 <i>J</i>                         |     |

|   | 5.3.4   | 1.                                          |     |

|   | 5.3.5   |                                             |     |

|   | 5.3.6   |                                             |     |

|   | 5.4     | Conclusion                                  | 95  |

|    | 5.5   | Refe | erence  | s      |         |                   |                                       |                                         | 95  |

|----|-------|------|---------|--------|---------|-------------------|---------------------------------------|-----------------------------------------|-----|

| C  |       |      |         |        |         |                   |                                       | DFLL Simulation and Measuremen          |     |

| Re | sults |      |         |        |         |                   |                                       |                                         | 97  |

|    | 6.1   | Ring | g-inter | polat  | tive v  | oltage            | -controlle                            | ed oscillator                           | 97  |

|    | 6.2   |      |         |        |         |                   |                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |

|    | 6.2.1 | -    |         |        |         |                   |                                       | of the DFLL                             |     |

|    | 6.2.2 | 2    | DFL     | L VC   | CO Ch   | aracte            | eristics                              |                                         | 108 |

|    | 6.2.3 | 3    | DC c    | harac  | cterist | tics              | :                                     |                                         | 110 |

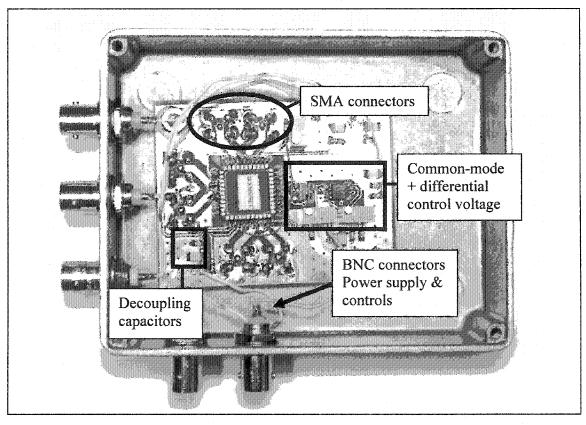

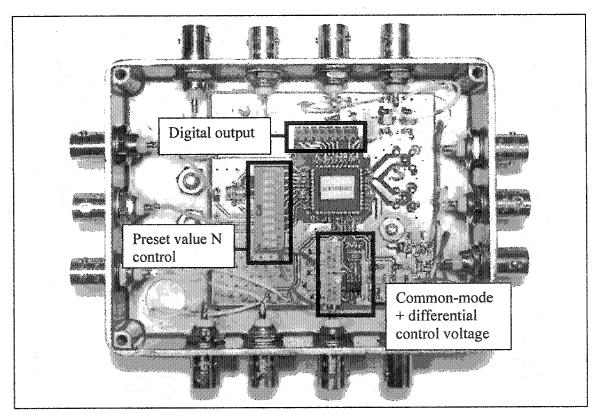

|    | 6.3   | Phy  | sical t | est se | etup    |                   | , , , , , , , , , , , , , , , , , , , |                                         | 111 |

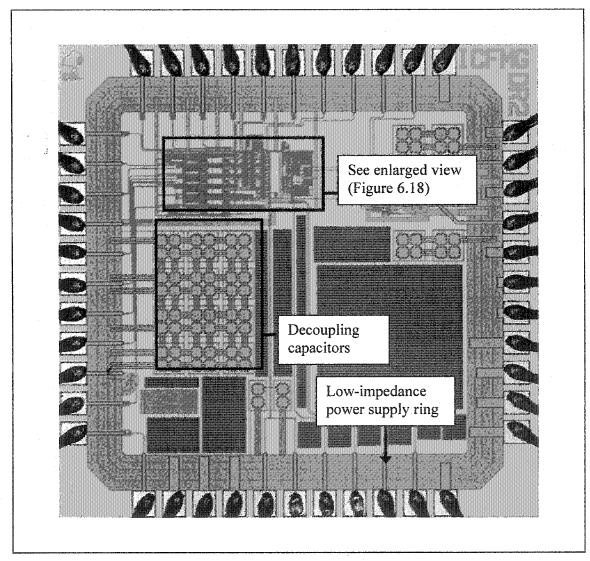

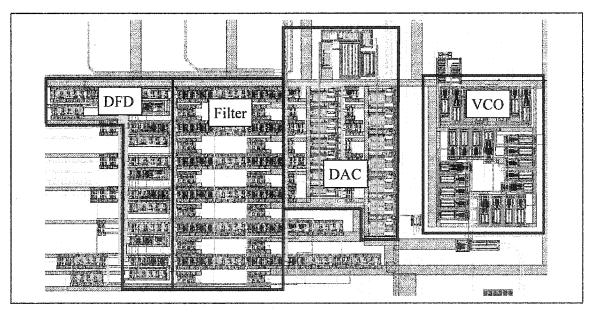

|    | 6.4   | Mic  | ropho   | togra  | ph      |                   |                                       |                                         | 114 |

|    | 6.5   | Con  | clusio  | n      |         |                   | ,                                     |                                         | 116 |

|    | 6.6   | Refe | erence  | s      |         | • • • • • • • • • |                                       |                                         | 116 |

| C  | H     | Α    | P       | T      | E       | R                 | 7                                     | Conclusion                              | 118 |

|    | 7.1   | Futu | ıre dir | ectio  | ns      | • • • • • • • • • |                                       |                                         | 119 |

| C  | H     | Α    | P       | T      | E       | R                 | 8                                     | Appendix                                | 120 |

|    | 8.1   | CM   |         |        |         |                   |                                       | ······                                  |     |

|    | 8.1.1 |      |         |        |         |                   |                                       |                                         |     |

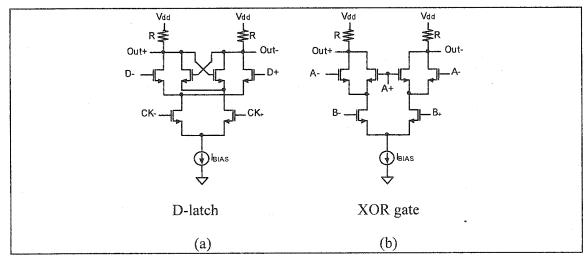

|    | 8.1.2 | 2    | Othe    | r CM   | L gat   | es                |                                       |                                         | 122 |

|    | 8.2   | PRE  | S and   | l eye  | diagr   | am sc             | ripts                                 |                                         | 123 |

|    |       |      |         |        |         |                   |                                       |                                         |     |

## **List of Figures**

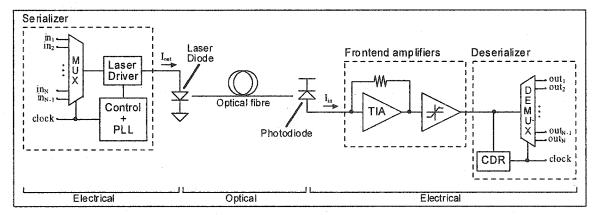

| Figure 1.1 Generic optical system.                                               | 10 |

|----------------------------------------------------------------------------------|----|

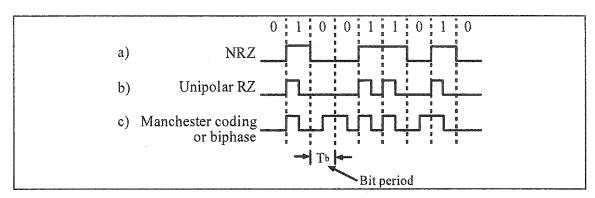

| Figure 2.1 Different line coding formats.                                        |    |

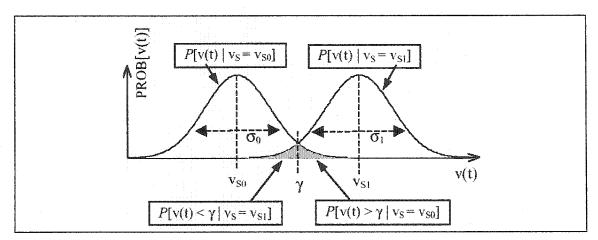

| Figure 2.2 Probability distribution for a binary signal                          |    |

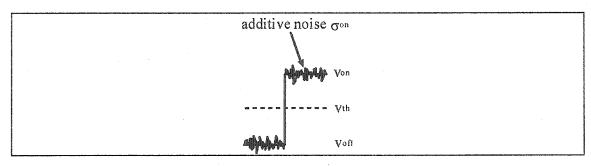

| Figure 2.3 Signal with additive noise.                                           | 19 |

| Figure 2.4 Bit-error-rate versus Q factor.                                       |    |

| Figure 2.5 Optical power versus the injected current in a laser diode            | 22 |

| Figure 2.6 First-order response and noise equivalent bandwidth                   | 24 |

| Figure 2.7 Autocorrelation of a random NRZ data stream.                          | 27 |

| Figure 2.8 Power spectrum of random NRZ signal                                   | 28 |

| Figure 2.9 Cumulative power spectrum.                                            | 29 |

| Figure 2.10 Optimum bandwidth for a NRZ system.                                  | 31 |

| Figure 2.11 Example of a simple optical link budget.                             | 32 |

| Figure 2.12 Typical receiver performance plot                                    | 33 |

| Figure 3.1 Typical front-end amplifier.                                          | 36 |

| Figure 3.2 High impedance front-end                                              | 37 |

| Figure 3.3 Basic transimpedance amplifier structure                              |    |

| Figure 3.4 Noise representations in a resistor and a MOS device.                 | 42 |

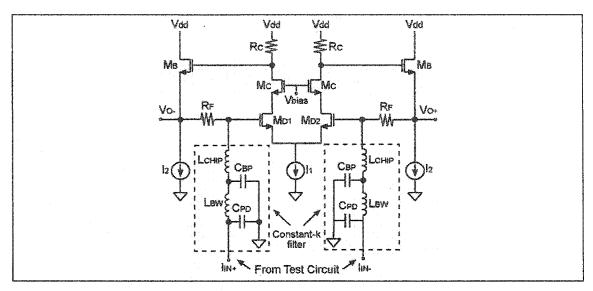

| Figure 3.5 Transimpedance amplifier circuit.                                     | 45 |

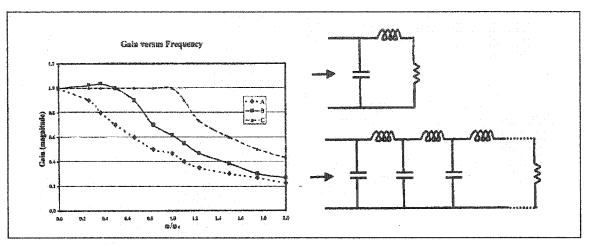

| Figure 3.6 Frequency response using a constant-K filter                          |    |

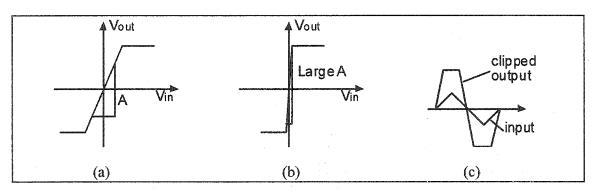

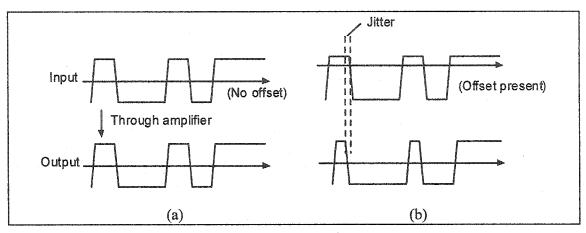

| Figure 3.7 Limiting amplifier transfer function                                  | 48 |

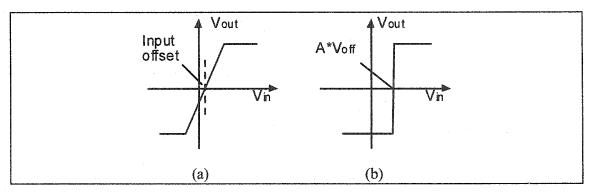

| Figure 3.8 Effect of input offset on an amplifier string.                        |    |

| Figure 3.9 Offset-induced jitter                                                 |    |

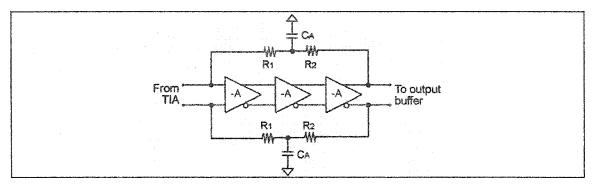

| Figure 3.10 Block diagram of the limiting amplifier with passive DC bias control | 52 |

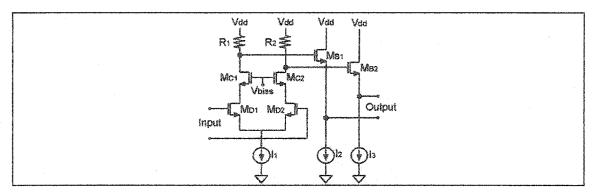

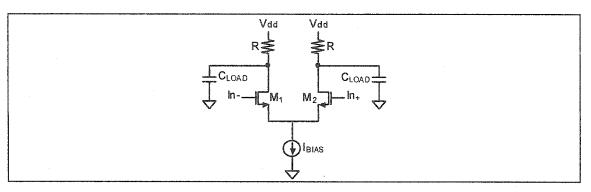

| Figure 3.11 Limiting amplifier cell.                                             |    |

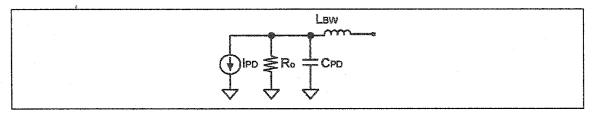

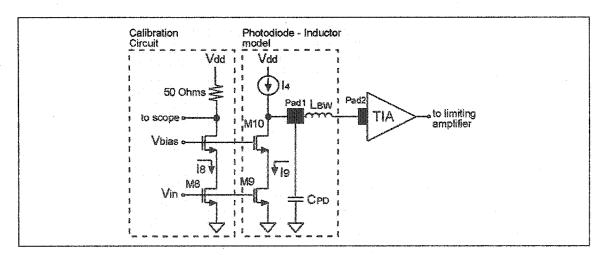

| Figure 4.1 Photodiode model.                                                     | 57 |

| Figure 4.2 The input test circuit.                                               |    |

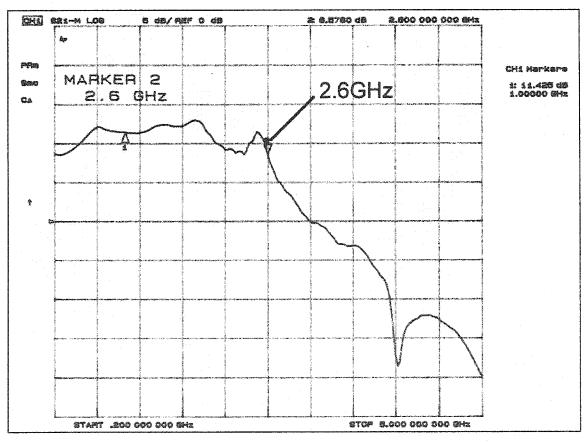

| Figure 4.3 Measured TIA transimpedance transfer function.                        |    |

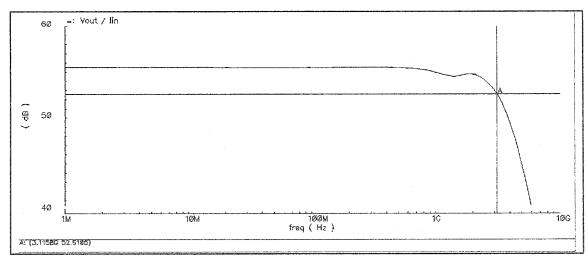

| Figure 4.4 Simulated TIA transimpedance prototype transfer function              |    |

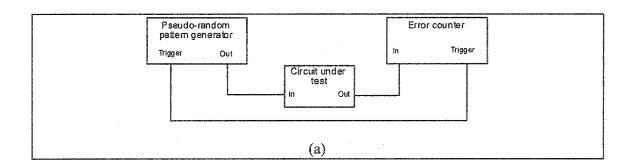

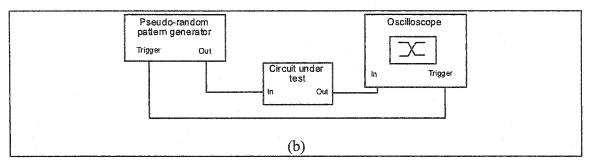

| Figure 4.5 Different test setup when using a BERT.                               |    |

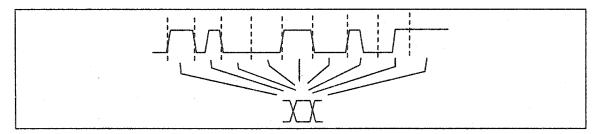

| Figure 4.6 Creation of an eye diagram                                            |    |

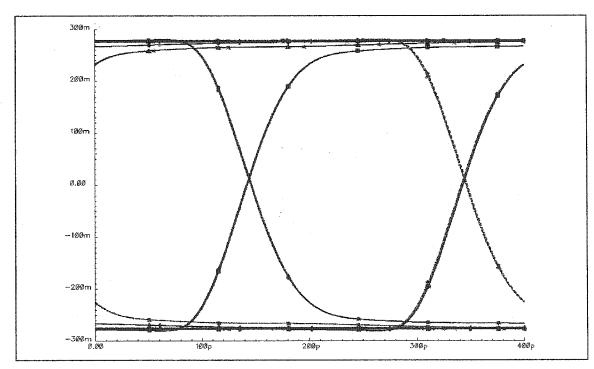

| Figure 4.7 Simulated eye diagram at the output.                                  | 63 |

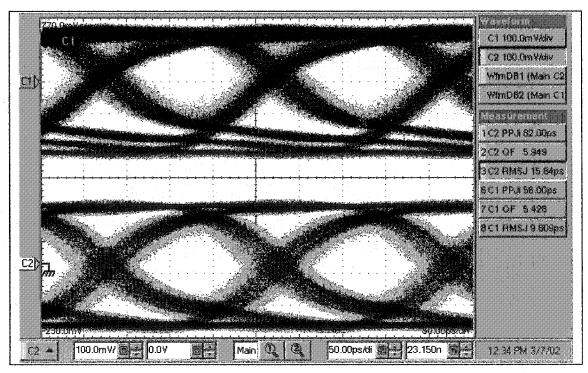

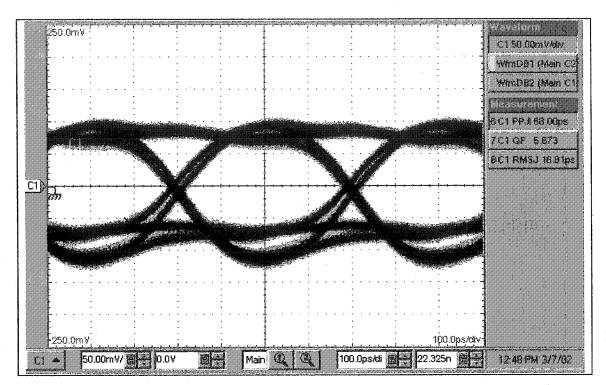

| Figure 4.8 Complete receiver eye diagram at 5Gb/s                                | 64 |

| Figure 4.9 2.5G TIA output.                                                      |    |

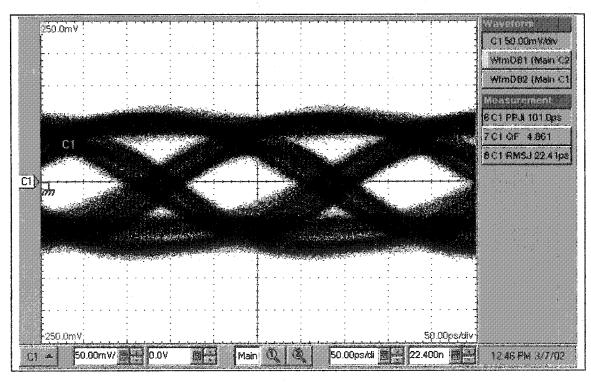

| Figure 4.10 5.0Gb/s TIA output                                                   |    |

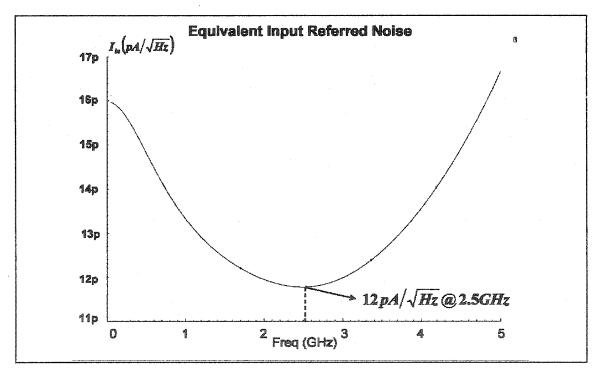

| Figure 4.11 Simulated input referred current noise.                              |    |

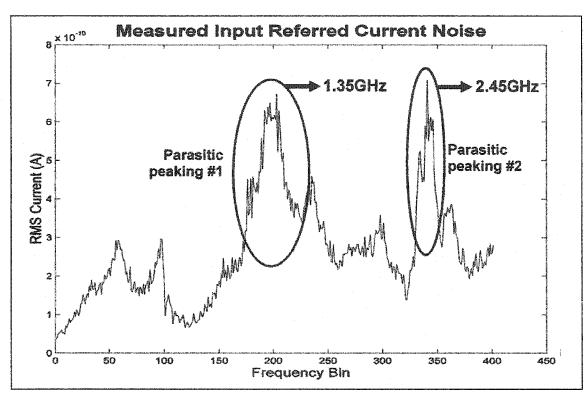

| Figure 4.12 Measured input referred current noise.                               | 67 |

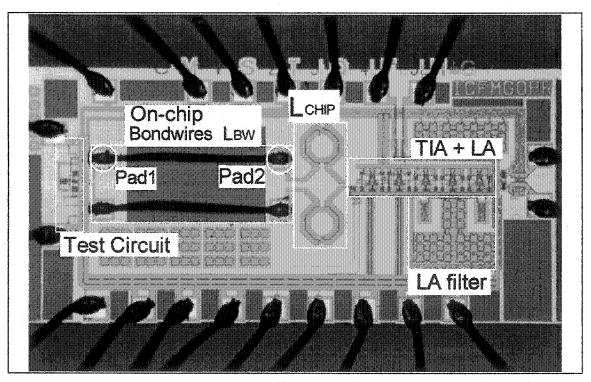

| Figure 4.13 The 5Gb/s optical front-end chip microphotograph            | 68  |

|-------------------------------------------------------------------------|-----|

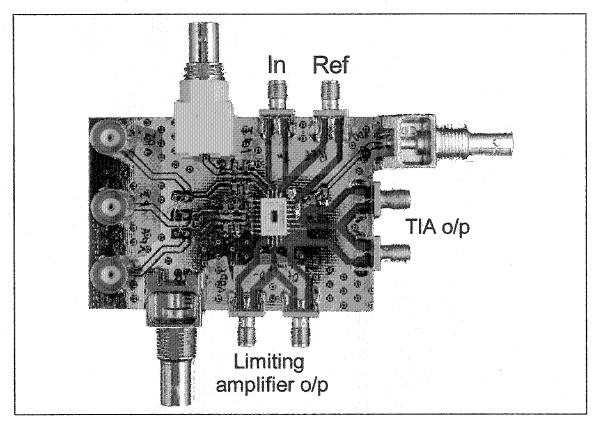

| Figure 4.14 The PCB used for testing the chip.                          | 70  |

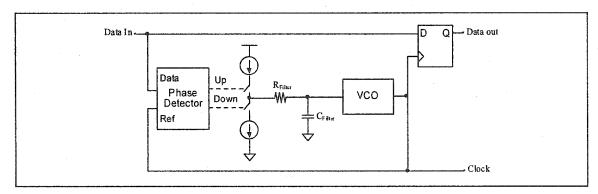

| Figure 5.1 Generic CDR structure.                                       | 74  |

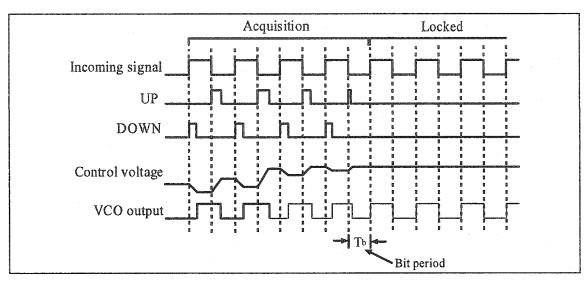

| Figure 5.2 Acquisition example.                                         | 75  |

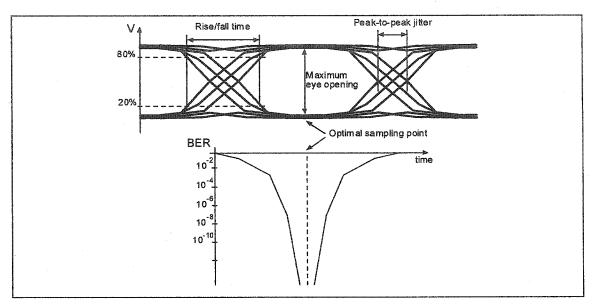

| Figure 5.3 Optimal sampling point.                                      | 76  |

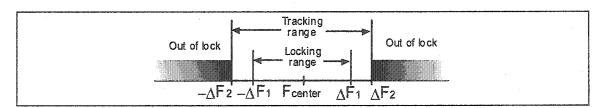

| Figure 5.4 Locking range.                                               |     |

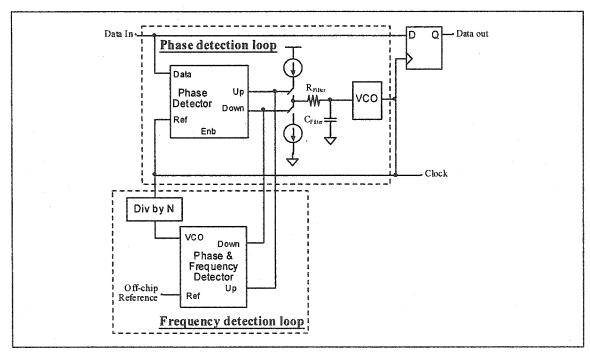

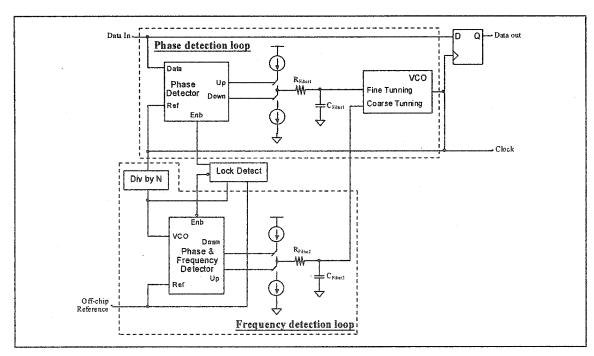

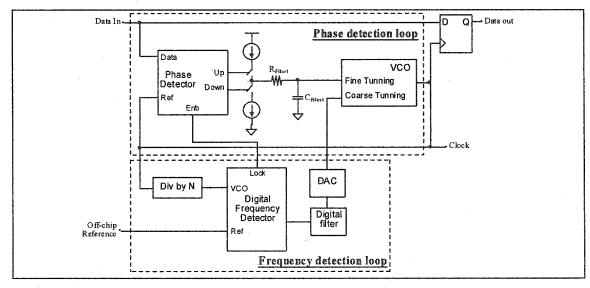

| Figure 5.5 Dual loop CDR with shared VCO control                        | 78  |

| Figure 5.6 Dual loop with split VCO control.                            |     |

| Figure 5.7 Dual loop with digital frequency detection.                  | 81  |

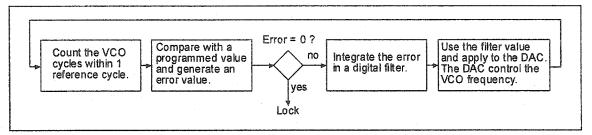

| Figure 5.8 State flow operation of the DFLL                             | 83  |

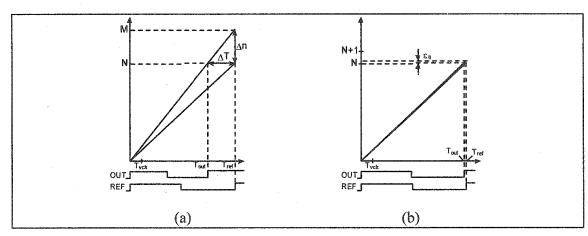

| Figure 5.9 (a) Frequency difference measurement. (b) Quantization error |     |

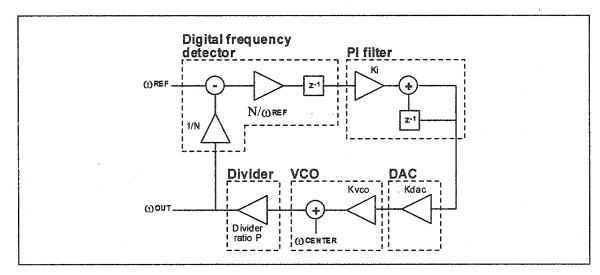

| Figure 5.10 DFLL linear model.                                          |     |

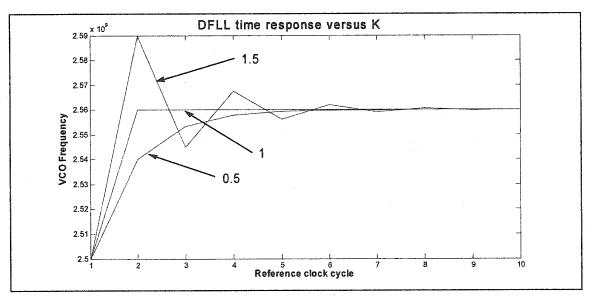

| Figure 5.11 DFLL time response vs. K                                    |     |

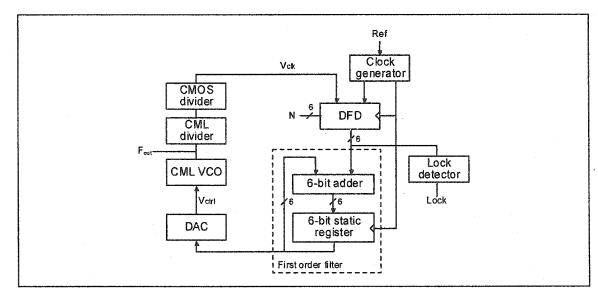

| Figure 5.12 Block diagram of the DFLL.                                  |     |

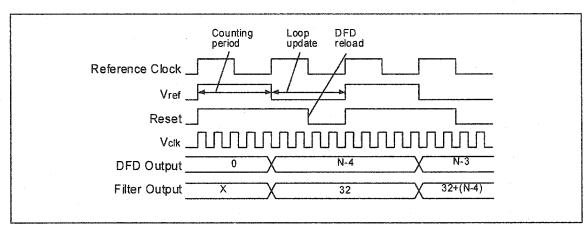

| Figure 5.13 Time domain operation of the DFLL.                          |     |

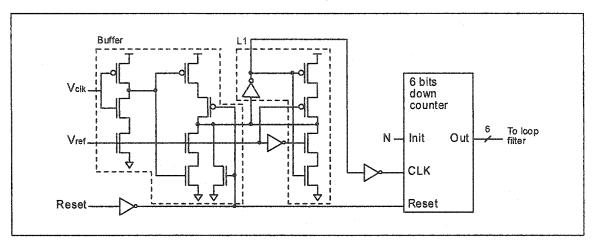

| Figure 5.14 Digital frequency detector.                                 | 90  |

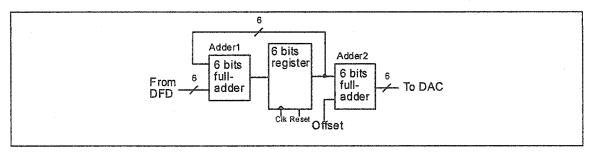

| Figure 5.15 Digital first order filter.                                 | 91  |

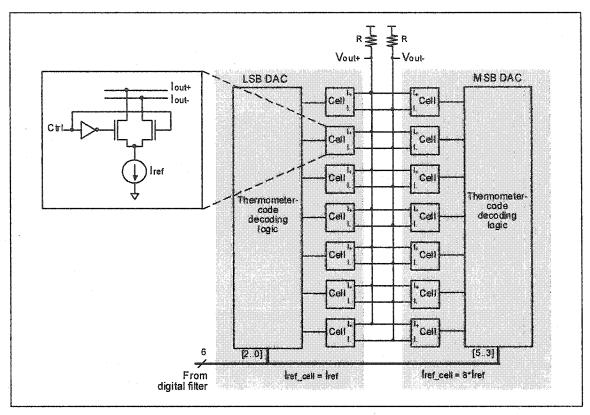

| Figure 5.16 Block diagram of the DAC with cell details.                 |     |

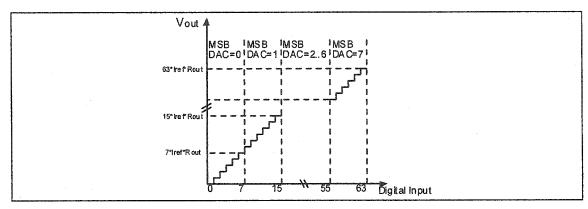

| Figure 5.17 Operation of the DAC.                                       |     |

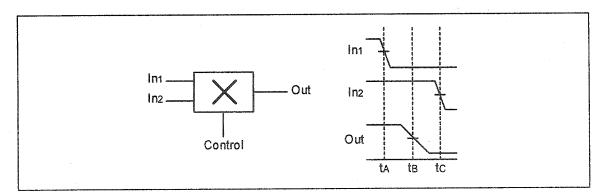

| Figure 5.18 Edge mixing.                                                |     |

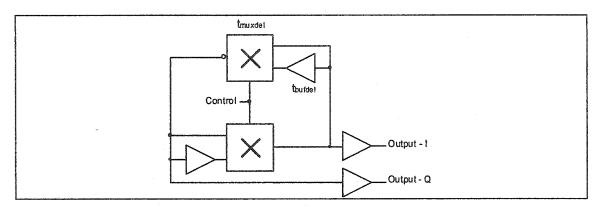

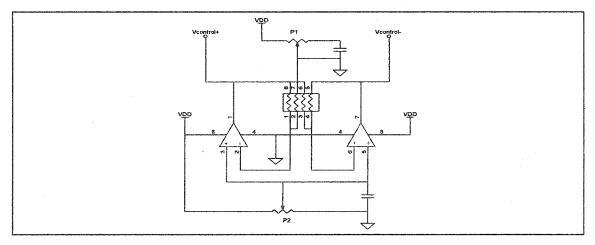

| Figure 5.19 A two-stage interpolative VCO.                              |     |

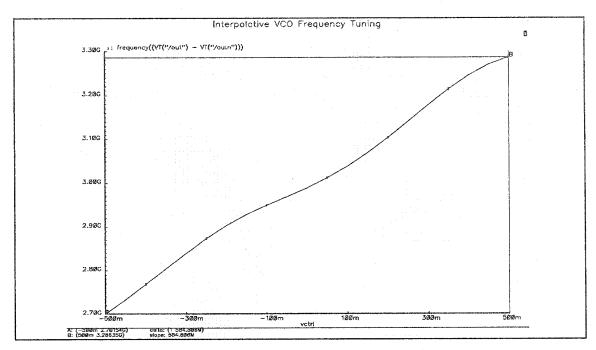

| Figure 6.1 Stand-alone VCO tuning (simulated).                          |     |

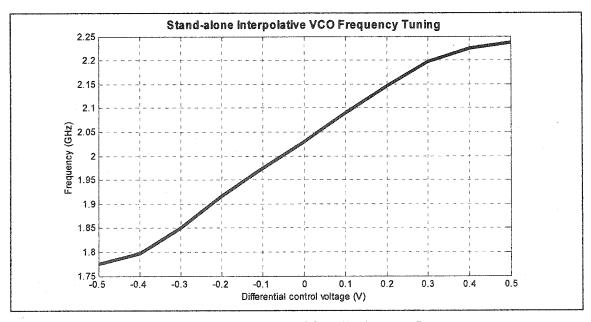

| Figure 6.2 Stand-alone VCO tuning (measured).                           |     |

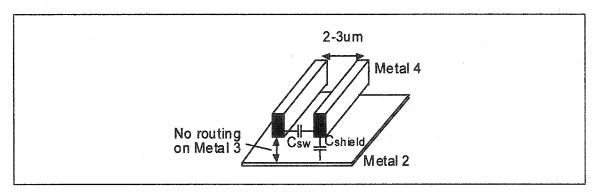

| Figure 6.3 Proper shielding example of differential signals.            |     |

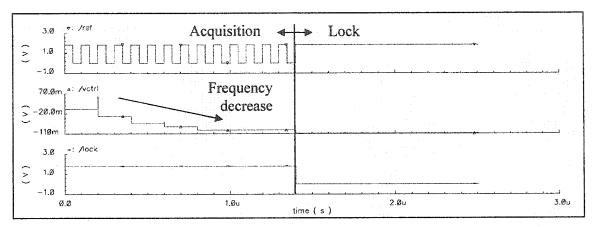

| Figure 6.4 Simulation of locking when the VCO frequency is too high     |     |

| Figure 6.5 Simulation of locking when the VCO frequency is too low      |     |

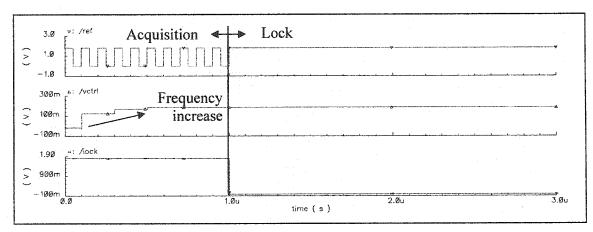

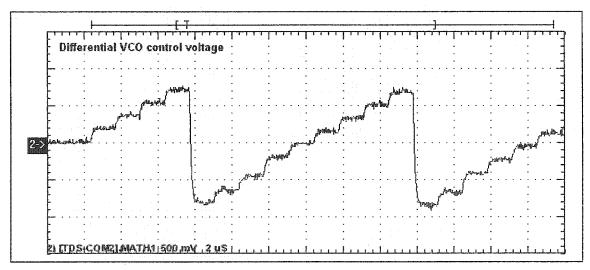

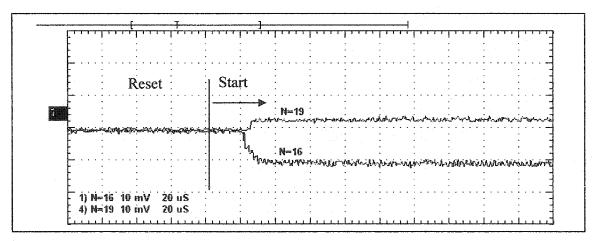

| Figure 6.6 Measurement: invalid preset frequency setting                |     |

| Figure 6.7 Measurement: different control setting.                      |     |

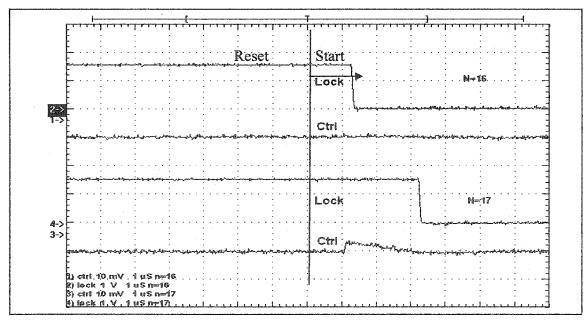

| Figure 6.8 Measurement: control and lock signals.                       |     |

| Figure 6.9 Measurement: invalid frequency setting.                      | 105 |

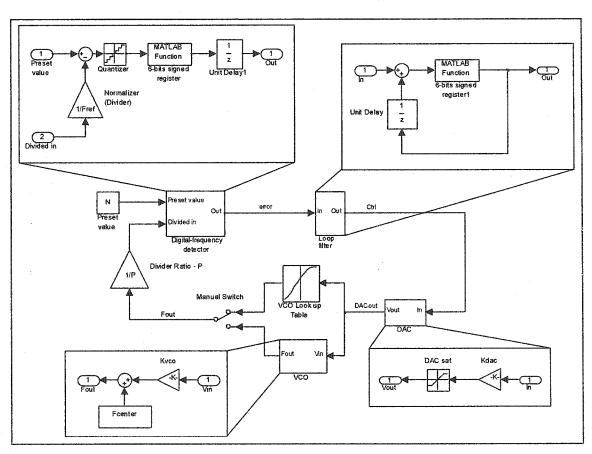

| Figure 6.10 Non-linear model used in Matlab.                            |     |

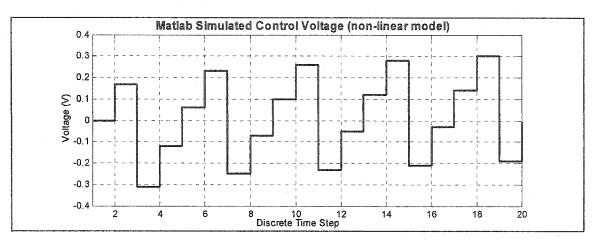

| Figure 6.11 Non-linear loop effect.                                     |     |

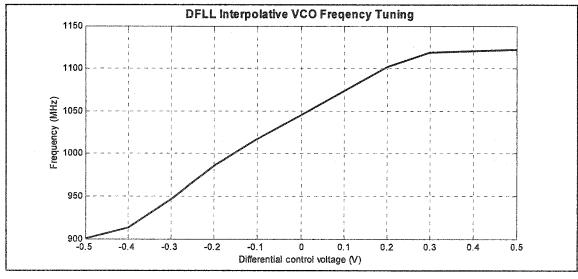

| Figure 6.12 DFLL interpolative VCO frequency tuning.                    |     |

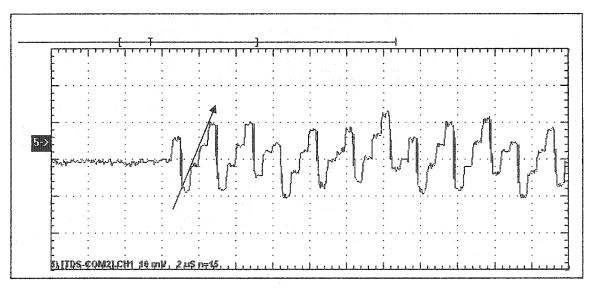

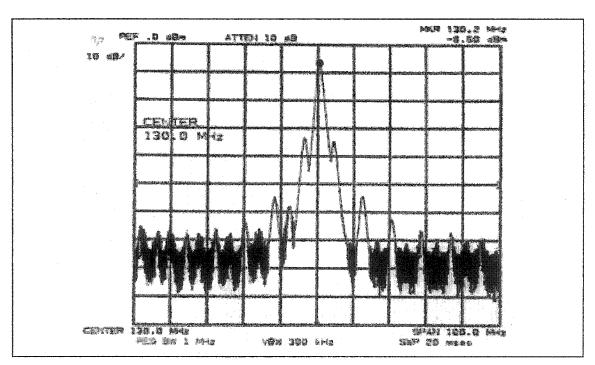

| Figure 6.13 Divided-by-8 power spectrum when locked                     |     |

| Figure 6.14 The VCO chip test setup                                     |     |

| Figure 6.15 Active control voltage setting.                             |     |

| Figure 6.16 The DFLL chip test setup.                                   |     |

| Figure 6.17 Chip microphotograph of DFLL chip.                          |     |

| Figure 6.18 DFLL chip zoom on the digital circuitry                     |     |

| Figure 8.1 CML inverter.                                                |     |

| Figure 8.2 Basic CML gates.                                             | 122 |

### **Abstract**

The large demand for high-bandwidth communication systems has brought down the cost of optical system components. To be competitive in a crowded market, implementation of the different systems of an optical transceiver on a single chip has become mandatory.

CMOS technologies, especially state-of-the-art processes like the 0.18µm CMOS, permit integration of huge amounts of transistors per millimiter square. Furthermore, deep-submicron CMOS processes have similar RF performances to their tradionnal bipolar equivalent. It is therefore a small footstep to go to congregate high-speed analog circuits with digital cores on a single die.

This thesis adresses two of the building blocks found in an optical communication receiver, namely the analog front-end receiver and a digital frequency-acquisition based clock-and-data recovery circuit. The latter reduces the headcount of bulky passive components needed in the implementation of the loop filter by porting the analog loop to the digital domain. This circuit has been successfully fabricated and tested.

Finally, an optical front-end, comprising a transimpedance amplifier and a limiting amplifier is proposed and fabricated using a standard 0.18µm CMOS process. The speed of this circuit has been pushed up to 5Gb/s. Different techniques have been employed to increase the effective bandwidth of the input amplifier, namely the use of a constant-k filter.

## **Sommaire**

Une demande sans cesse grandissante pour la bande passante fait tomber le prix des diverses composantes des systèmes optiques. Pour être compétitif dans un marché déjà saturé, l'intégration des différents systèmes électroniques des récepteurs optiques est maintenant obligatoire.

Les procédés à la fine pointe de la technologie, comme les transistors CMOS, permettent l'intégration de quantité impressionnante de transistors pour une surface donnée. Ces mêmes technologies commencent de plus en plus à avoir des caractéristiques similaires au traditionnel procédé bipolaire. Des lors, il est possible d'intégrer des systèmes analogiques à hautes vitesses ainsi que des circuits numériques sur une même puce.

Cette thèse présente deux blocs contenus dans les récepteurs optiques, plus précisément un pré-amplificateur et ainsi qu'un circuit numérique d'aide à l'acquisition de fréquence pour les systèmes de boucle asservie en phase. Ce dernier type de circuit réduit substantiellement le nombre de composantes passives requises. Cette réduction est attribuable à la conversion d'une partie de circuit analogique par son équivalent numérique.

Pour conclure, cette thèse discute d'un pré-amplificateur pour circuit optique, composé d'un amplificateur à transimpedance ainsi que d'un amplificateur limiteur. De plus, un prototype, utilisant la technologie CMOS avec une longueur de grille de 0.18um a été fabriqué. La vitesse d'opération maximale à être démontré pour ce circuit est de 5Gb/s. Différentes techniques pour augmenter la bande passante du circuit ont été utilisé, plus particulièrement l'utilisation d'un filtre a impédance constante.

## Remerciements

À mes parents, Marie-Paule et Bernard, je leur dédie avec humilité cette thèse. À jamais je ne serai suffisamment reconnaissant de leur soutien et de leur amour.

À mon mentor Michel, pour sa guidance éclairée, son écoute attentive et son propos tempéré.

À tout mes amis d'avoir été présents.

Mon directeur de thèse Mourad El-Gamal, pour cette opportunité.

La Société canadienne de micro-électronique (CMC) et RESMIQ pour leurs supports financiers.

## CHAPTER 1

## Introduction

#### 1.1 Motivation

With today's high speed networks, where concentrations of voice, video, text and other media is accelerating, capacity limit has never ceased of increasing. The major problem with electrical communication links is the capacity limit. To increase this capacity limit, the carrier frequency needs to be pushed higher in frequency. However, electrical circuitry can hardly cope with frequencies beyond few tens of gigahertz. With the recent invention of laser, the carrier has been changed from an electrical format to an optical format. Commercial communication systems using electrical carriers (RF systems) use frequencies up to 100GHz (mainly for satellite applications). In today's optical links, where the wavelength of the laser is 1.55µm, the carrier frequency is about 192 THz. This is approximately three orders of magnitude larger.

Network backbones are currently built from OC-192 links (10Gb/s), and soon OC-768 links (40Gb/s). With the use of wavelength-division multiplexing, a process of using different wavelengths for each channel, can boost the transmission capacity of the link [Keiser99]. Transfer rates in excess of 1Tb/s can be achieved on a single fibre [Chraplyvy98].

Before getting into the design of an optical receiver, it is important to know the requirements of the system. Optical communication systems are digital communication

systems working at very high speeds. In addition of using digital communication theory to characterize the link, knowledge of RF design, random signals, and transceiver architectures must also be mastered.

#### 1.2 System Architecture

A typical optical system is shown in Figure 1.1. This system is used to convert an electrical stream of information to light. The modulated light is then propagated in a channel (i.e. an optical fibre). At the receiving end, a circuit converts back the light to the original electrical stream.

Figure 1.1 Generic optical system.

To produce a light equivalent to the electrical information, the electrical signal needs to be conditioned. The serializer converts a number of low speed parallel data to a high-speed serial stream. It is done using a multiplexer and a phase-locked loop (PLL). The PLL helps to synchronize the sampling of the incoming data by means of a reference clock. A laser driver then creates a current proportional to the serial bit stream. The control block is used to regulate the current conversion. The light produced by the laser diode is proportional to the current injected in it. The light is coupled to a propagation medium (i.e. an optical fibre).

To recover the information, the previous steps are done in a reversed order. The photodiode will create a current proportional to the light applied to it. This current is

converted to voltage using a transimpedance amplifier (TIA). Because the voltage produced by the TIA is still very small, a string of limiting amplifiers (LA) is needed to further amplify the voltage to digital level. By the help of a clock-and-data recovery circuit (CDR), the high-speed bit stream and the clock can be recovered. Finally, a demultiplexer will split the serial bit stream to a low speed parallel bit stream.

In today's modern IC CMOS processes, components characteristics variations can be as large as  $\pm 20\%$  over process and temperature. Such high variations can change significantly the operation of a circuit. Good designs should be able to be as insensitive as possible to these extreme changes.

#### 1.3 State-of-the-art frontend designs

In order to achieve low-cost fiber-optic links, CMOS technology is a very good candidate. Both digital and analog circuits can be implemented on the same die when implemented in CMOS. Cost reduction is possible, since the number of packages is reduced (e.g. 1 package for the complete system compared to two or more packages for the front-end and the digital circuitry). Power reduction is also reduced since power-hungry buffers, needed at the chip interface, are not necessary. Power consumption of buffers is particularly high for high bit rates.

CMOS optical receivers with bit-rates varying from 50MBits/s up to 10Gbits/s have already been reported in the literature [Pietruszynski88] [Nakamura98] [Ingels94] [Ingels99] [Tanabe98] [Mitran02] [Kiziloglu02]. CMOS front-ends are by their nature noisier than their bipolar or GaAs equivalent counterpart. Of interest is the transimpedance amplifier (TIA) proposed by Razavi [Razavi00]. Using capacitive feedback, instead of the traditional resistive shunt feedback, the noise generation has been brought to an equivalent level with respect to that of bipolar TIA.

CMOS front-ends are limited in speed because of the relatively large gate capacitances of the transistors. Different techniques can be employed to overcome this bandwidth limitation. Mohan [Mohan99] proposes using inductors placed in series with the resistance used to produce the amplifier gain. Called "inductive peaking", this method can extend the bandwidth of the amplifier by an extra few percents. Limiting amplifiers also used the inductive peaking technique to broaden their bandwidths. However, the use of passive inductances is prohibited, because of the large number of inductors required. Also, the area of a passive inductance cannot be mitigated (e.g. 400µm x 400µm). Active inductors, built from a single transistor and a resistor, can be used in circuits with good results [Sackinger00]. It should be noted that active inductors are noisier than their passive equivalent. Their use in transimpedance amplifiers is not common, but by they can be used, with proper optimization, in limiting amplifiers.

Other techniques, such as applying a constant-k filter at the input [Beaudoin02], can be used to increase the bandwidth of the amplifier, or to reduce the noise generation of the TIA. A good analysis of the different topologies that can be used in the building a TIA is described in [Park97]. Common-source and common-gate input amplifiers are compared and noise analysis is done.

#### 1.4 Thesis outline

This thesis consists of seven chapters. The first chapter is an introduction that discusses the motivations behind this research. The second chapter discusses the basic metrics used in optical communications. Chapter 3 presents the mathematical derivation of the equations used by a generic transimpedance amplifier. These equations account for the bandwidth and noise of the amplifier. The limiting amplifier is presented, as well as the issues associated with this type of amplifier. A circuit design is presented. Chapter 4 presents the measurement results and methodology. A comparison with the simulation results is done. A simple analysis of the package effect is presented. In chapter 5, the issues associated with the limited locking range of clock-and-data recovery circuits are discussed. A circuit is presented to broaden the acquisition range. Chapter 6 presents the measurement results of the circuit proposed in chapter 5. In addition, the measurement techniques are presented. Finally, chapter 7 concludes this research work and possible future work is proposed.

#### 1.5 Thesis contributions

The following is a summary of the contributions of this thesis:

- The design, implementation and testing of a 5.0Gb/s optical front-end receiver [Beaudoin02].

- A. A method to extend the bandwidth of the amplifier was used. Instead of extending the frequency at the output employing techniques such as inductive peaking, the bandwidth was increased at the input with the help of a constant impedance filter.

- B. An investigation of the causes of the observed discrepancies between the simulation and measured performances was carried out. In addition, a method to easily perform the necessary measurements was presented in details.

- The design, implementation, and testing of a digital frequency locked-loop circuit used to broaden the acquisition range of PLL based circuits in general.

- A. A comparative study of the different types of loops available to simplify the frequency locking of PLL based circuits is presented. The theory and the governing equations of a digital frequency locked-loop (DFLL), based on its analog equivalent, are discussed.

- B. A DFLL implementation example is described. Each building block employed in the DFLL is discussed, with its associated requirements.

- C. The measurements results from a fabricated prototype are summarized, and the differences from simulations are thoroughly analyzed, along with a careful study of the on-chip loop dynamics.

#### 1.6 References

[Keiser99] G. E. Keiser, A review of WDM technology and applications, Opt. Fiber Technol, vol. 5, pp.3-39, Jan 1999.

[Chraplyvy98] A. R. Chraplyvy, R. W. Tkach, "Terabit/second transmission experiments," IEEE J. Quantum Electron., vol. 34, pp. 2103-2108, Nov. 1998.

[Beaudoin02] F. Beaudoin, M. N. El-Gamal, "A 5-Gbit/s CMOS optical receiver frontend," The 2002 45th Midwest Symposium on Circuit and Systems, Volume 3, pp. 168-171, August 2002.

[Mitran02] P. Mitran, F. Beaudoin, and M. El-Gamal, "A 2.5 Gbit/s CMOS Optical Receiver Frontend," Proc. IEEE International Symposium on Circuits and Systems, Phoenix, May 2002.

[Pietruszynski88] M. Pietruszynski, J. M. Steininger, E. J. Swanson, "A 50-Mbit/s CMOS Monolithic Optical Receiver," IEEE J. Solid-State Circuits, vol. 23, pp. 1426-1432, Dec. 1988.

[Nakamura98] M. Nakamura, N. Ishihara, Y. Akazawa, "A 156-Mb/s Optical Receiver for Burst-Mode Transmission," IEEE J. Solid-State Circuits, vol. 33, pp. 1179-1187, August 1998.

[Ingels94] M. Ingels, G. van der Plash, J. Crols, and M. Steyaert, "A CMOS 18 THz Ohm 240Mb/s Transimpedance Amplifier and 155 Mb/s LED-driver for Low Cost Optical Fibre Links," IEEE J. Solid-State Circuits, vol. 29, pp. 1552-1559, Dec 1994.

[Ingels99] M. Ingels, M. Steyaert, "A 1Gb/s 0.7µm CMOS Optical Receiver with Full Rail-to-Rail Output Swing," IEEE J. Solid-State Circuits, vol. 34, pp. 971-977, July 1999.

[Tanabe98] A. Tanabe, M. Soda, Y. Nakahara, T. Tamura, K. Yoshida, A. Furukawa, "A Single-Chip 2.4-Gb/s CMOS Optical Receiver IC with Low Substrate Cross-Talk Preamplifier," IEEE J. Solid-State Circuits, vol. 33, pp. 2148-2153, Dec. 1998.

[Razavi00] B. Razavi, "A 622Mb/s 4.5pA/rt Hz CMOS Transimpedance Amplifier," ISSCC Digest of Technical Papers, pp. 162-163, Feb. 2000.

[Park97], S. M. Park, C. Toumazou, "Gigahertz low noise CMOS transimpedance amplifier," Proc. of IEEE International Symposium on Circuits and Systems, vol. 1 pp. 209-212, Jun. 1997.

[Mohan99] S. S. Mohan, T. H. Lee, "A 2.125 Gbaud 1.6 k $\Omega$  transimpedance preamplifier in 0.5  $\mu$ m," Proc. of IEEE CMOS Custom Integrated Circuits, pp. 513 -516, May 1999.

[Sackinger00] E. Sackinger, W. C. Fischer, "A 3 GHz, 32 dB CMOS limiting amplifier for SONET OC-48 receivers," Tech. Digest of International Solid-State Circuits Conference, pp. 158-159, Feb. 2000

[Kiziloglu02] A. K. Kiziloglu, K. Ty Yoon, F. Jr. Williams, M. R. Sandor, "Front-end CMOS chipset for 10 Gb/s communication," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, pp. 93 -96, Jun. 2002

## CHAPTER 2

## **Optical Receivers Basics**

This chapter covers the basics about channel-coding and how it relates to optical receivers. A derivation of the optimum bandwidth of the receiver amplifier is also performed. Some important metrics used in optical communication systems, such as bit-error rate and sensitivity are introduced. Finally, a brief overview of an optical link budget analysis and of a receiver performance plot are presented.

#### 2.1 Channel coding

Formatting the information to be transmitted over an optical link is a critical consideration in system design. By using proper coding, the system speed and transmission length can be increased substantially. Optical communication systems transmits information mainly in a digital form. At the receiving end, a decision circuitry must be able to extract precise timing information from the received signal for data recovery. Such timing information is normally incorporated in the transmitted signal. It is generally achieved by rearranging or adding extra data in the stream. This process is called channel-coding.

From Shannon's channel-coding theory [Shannon48], it can be shown that channel-coding introduces coding gain. Coding gain is a measure of the increase in signal-to-noise ratio (decrease in bit-error rate) for different types of coding schemes. An increase in the

coding gain can be used to increase the length of a transmission link, or relax the design constraints for the receiver. A detailed mathematical analysis of channel-coding falls outside the scope of this thesis.

Three basic channel-coding methods for binary level signals are used in optical systems: non-return-to-zero (NRZ), return-to-zero (RZ), and phase-shift-keying (PSK). Both the NRZ and RZ coding schemes are simple extensions of the simplest form of encoding: on-off keying (OOK).

The simplest method to encode a binary stream is the NRZ coding. The signal representing a logic-one is on for the complete bit period T<sub>b</sub>. Conversely, a logic-zero is off for the same period (Figure 2.1 (a)). Long strings of logic-zeros and ones need a highly stable clock in the clock-recovery circuit in order to be recovered properly. This results in an increase in both cost and complexity. However, by using scrambling or block coding (section 2.1.1), it is possible to reduce the number of consecutive zeros and ones. This is called the DC balance strategy, as explained in section 2.1.2.

The second type of line coding is the RZ, with a variety of code types existing. Figure 2.1 (b) shows the unipolar RZ code. A logic-one is represented by a half-period being at one, and the other half being off. A logic-zero is represented by no signal during the bit period. If long strings of zeros are sent, the same synchronization problem exists as for the NRZ coding. A type of coding not having this limitation is the biphase or Manchester coding.

Biphase or Manchester coding is a combination of RZ and PSK coding. From Figure 2.1 (c), one can see that a logic-zero is phase inverted compared to a logic-one. This coding has the advantage of having timing information (clock) embedded in the data stream, making timing recovery an easier task. However, the main drawback of RZ coding is the amount of bandwidth required. Compared to NRZ, RZ requires twice the amount of bandwidth. On the other hand, using a reduced bandwidth, NRZ requires very stable oscillators at the receiver. To improve the reliability of the communication system, extra

data need to be added to the stream: this includes block coding, DC balance strategies and forward-error correction, which are briefly described in the following subsections.

Figure 2.1 Different line coding formats.

#### 2.1.1 Block coding

Block coding is based on using redundant binary codes. Such codes transform a block of m binary bits to a longer block of length n (n>m). Block coding also reduces the disparity between the number of zeros and ones (it tends to have the same number of zeros and ones). This is a desired feature, since long strings of ones and zeros are eliminated. At the expense of an increase in the required bandwidth, block coding provides an adequate way of introducing timing information in the data stream.

#### 2.1.2 DC balance strategy

Block coding is a powerful way to change the power spectrum shape of the information stream, while transmitting approximately the same amount of information. By having a limited number of consecutive zeros or ones, the necessary complexity of the clock recovery circuit will be reduced. In addition, AC coupling between the different stages of the receiver is possible since the low frequency components are present. DC balance is a desired feature for digital transmission system.

#### 2.1.3 Error correction

To improve the reliability in optical communication systems, forward error correction (FEC) is added to reduce the overall bit-error-rate. The SONET standard uses Reed-

Solomon codes to implements FEC. With a little overhead (normally 7.1% for RS (255,239) code), the BER can be improved by more than 10000 times [Sklar01].

#### 2.2 Metrics used in optical communication systems

Many standards exist to quantify the performance of a system. The following paragraphs describe the main metrics used for optical communication receivers. Receivers are mostly quantified by the amount of noise they introduce, or by the amount of noise they are capable of dealing with. Time domain analysis is not critical for receiver amplifiers. However, time domain analysis (e.g. jitter) becomes a critical issue for clock-and-data recovery circuits.

#### 2.3 Signal-to-noise ratio

One of the most important measures in analog systems in general is the signal-to-noise ratio (SNR). As the name suggests, it is a measure of how stronger is the signal power compared to the noise power at a node in a system. It can be expressed as a ratio of powers (in this case: optical powers), or also as a ratio of currents or voltages, depending on the system under analysis.

Because optical frontends amplify currents, it is more practical to define the SNR as a ratio of currents at the input node. The corresponding optical power actually received by the photodiode can then be estimated. All the noise introduced by the optical link and by the photodiode itself can be accounted for using a single equivalent current noise source.

#### 2.4 Bit-error-rate (BER)

Several standard methods to measure the rate of error occurring in digital streams exist. A common one is to divide the number of errors occurring ( $N_e$ ) by the number of received bits ( $N_b$ ) each over a period of time (t) (equation 2.1). This gives the bit-error rate (BER). For example, for a BER of  $10^{-9}$ , one bit will be erroneous for every one billion of bits sent.

$$BER = \frac{N_e}{N_b t}$$

Eq. 2.1

Since the BER is the probability of getting an erroneous bit, it is important to know the probability distribution of the received bits.

Figure 2.2 Probability distribution for a binary signal.

Figure 2.2 shows the probability distributions of a logic-zero and a logic-one at the output of a receiver. The threshold voltage  $\gamma$  is normally fixed at the middle of the intersection of the probability distribution functions in order to achieve optimum sampling. If the input voltage v(t) is greater than  $\gamma$ , then the system treats the received signal as a logic-one. On the other hand, if the input voltage v(t) is smaller than  $\gamma$ , the system treats the received signal as a logic-zero.

Figure 2.3 Signal with additive noise.

The BER is directly related to the signal-to-noise ratio of the receiving system. From Figure 2.3, we can define the parameter Q:

$$Q = \frac{v_{on} - v_{th}}{\sigma_{on}} \approx \frac{1}{2} \frac{S}{N}.$$

Eq. 2.2

The variance  $\sigma_{on}$  is the RMS amount of noise present for a logic-one and  $v_{on}$ - $v_{th}$  is the peak-to-threshold voltage for a logic-one. The same relationship can be defined from a logic-zero. Assuming a Gaussian probability density function, it is possible to compute the probability of error for which a logic-zero will be interpreted as a logic-one. In this case, the probability of error that noise will exceed the threshold voltage  $v_{th}$  is given by:

$$P_{0}(v_{th}) = \int_{v_{th}}^{\infty} p(y|0) dy = \frac{1}{\sqrt{2\pi\sigma_{off}}} \int_{v_{th}}^{\infty} \exp\left[-\frac{(v - v_{off})^{2}}{2\sigma_{off}^{2}}\right] dv$$

Eq. 2.3

where  $\sigma_{off}^2$  is the noise variance for a logic-zero and  $v_{off}$  is the corresponding voltage for a logic-zero. Similarly, the probability of error of a logic-one is given by:

$$P_{1}(v_{th}) = \int_{-\infty}^{v_{th}} p(y|1) dy = \frac{1}{\sqrt{2\pi\sigma_{on}}} \int_{-\infty}^{v_{th}} \exp\left[-\frac{(v_{on} - v)^{2}}{2\sigma_{on}^{2}}\right] dv.$$

Eq. 2.4

If the probabilities of a logic-zero and a logic-one are equally likely, then, using equations 2.3 and 2.4, the BER becomes [Keiser00]:

$$BER = P_e(Q) = \frac{1}{\sqrt{\pi}} \int_{Q/\sqrt{2}}^{\infty} e^{-x^2} dx$$

Eq. 2.5

Performing the integration, equation 2.5 can be approximated by 2.6 [Keiser00]:

$$BER = \frac{1}{2} \left[ 1 - erf\left(\frac{Q}{\sqrt{2}}\right) \right] \approx \frac{1}{\sqrt{2\pi}} \frac{e^{-Q^2/2}}{Q}$$

Eq. 2.6

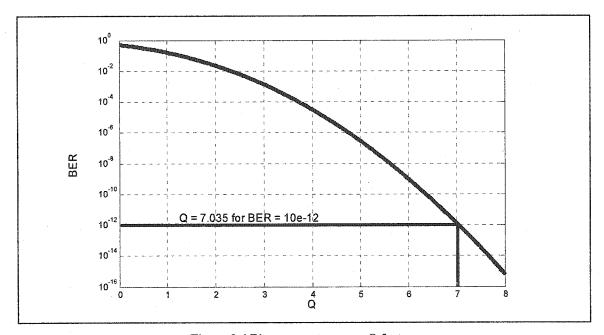

Figure 2.4 shows the dependence of the BER given by equation 2.6 on the parameter Q. For example, a Q of 7.035 is required to get a BER of  $10^{-12}$ . The corresponding SNR is twice the value of Q, i.e. 14.07 or 11.48dB. So as predicted, in order to have a lower biterror rate, the required system SNR needs to be increased.

Figure 2.4 Bit-error-rate versus Q factor.

#### 2.5 The extinction ratio

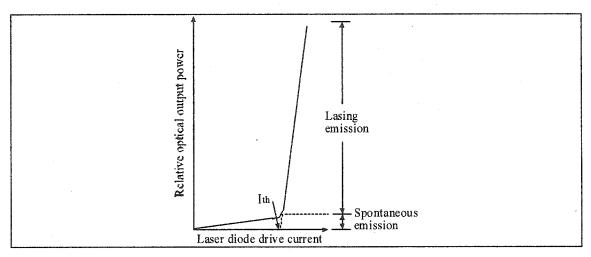

The extinction ratio is an effect introduced by laser diodes at the transmitter side, that are biased close to their lasing threshold (Figure 2.5) to reduce chirping. The extinction ratio has a significant impact on the receiver sensitivity [Keiser00]. The extinction ratio is defined as the ratio of a logic-one power level  $(P_1)$  relative to a logic-zero power level  $(P_0)$ :

$$e_r = \frac{P_1}{P_0}$$

Eq. 2.7

Instead of hard driving the laser diode i.e.  $I_{laser} = 0$  for logic-zero and  $I_{laser} = I_{max}$  for logic-one, it is preferable to chose the biasing current to be close to the lasing threshold (Figure 2.5).

Figure 2.5 Optical power versus the injected current in a laser diode.

#### 2.5.1 Chirping

Laser diodes may experience dynamic change of frequency when the injection current is directly modulated. This leads to significant dispersion effects in the optical fibre and an increase in the eye closure at the receiver [Keiser00]. The effect can be more easily seen in the time domain as it introduces jitter. If the laser diode is biased above the lasing threshold, the injection current becomes much less susceptible to direct modulation.

Having the laser diode always biased, some optical power is now emitted for a logic-zero. Because the signal now available excursion is reduced, a power penalty is introduced due to the smaller signal-to-noise ratio available at the receiver. This penalty is defined by:

$$P_{loss-e_r} = \frac{e_r + 1}{e_r - 1}$$

Eq. 2.8

For a typical power penalty of 1dB, the extinction ratio needs to be 8.7 or 9.4dB. The power penalty introduced by the extinction ratio can be reduced at the price of an increase in chirping. However, the designer does not have control over this parameter since this is a system design issue.

#### 2.6 Sensitivity

In optical communication systems, sensitivity is a measure of the average power needed to achieve a specified bit-error rate. For example, the SONET standard for OC-48 requires a sensitivity of -18dBm for the receiver for links shorter than 15km. The objective here is to achieve a BER of less than  $10^{-10}$  with the specified minimum power.

Sensitivity can be expressed as an average power, or as an optical modulation amplitude (OMA) in W<sub>pp</sub>. Measuring the peak-to-peak power amplitude of a laser diode can be quite difficult, and requires expensive equipments. However, measuring the average power can be done more easily. The sensitivity is given by [MAXIM01]:

Sensivity =

$$10\log\left(\frac{\overline{i_n^2}SNR(r_e+1)}{2\rho(r_e-1)}1000\right)dBm$$

, Eq. 2.9

where  $\overline{i_n^2}$  is the average integrated noise, SNR is the required SNR for a given BER,  $\rho$  is the photodiode responsitivity in (A/W), and  $r_e$  is the extinction ratio. The sensitivity can also be expressed in terms of the OMA:

Sensivity =

$$10\log\left(OMA\frac{(r_e+1)}{2(r_e-1)}1000\right)dBm$$

Eq. 2.10

Sometimes, sensitivity is expressed as the smallest current that can be detected and amplified by a transimpedance amplifier. Rewriting equation 2.9 and expanding the SNR, the minimum current corresponding to a given sensitivity is:

$$I_{signal} = \frac{2\rho(r_e - 1)}{i_n^2(r_e + 1)1000} 10^{Sensitivity/10}$$

Eq. 2.11

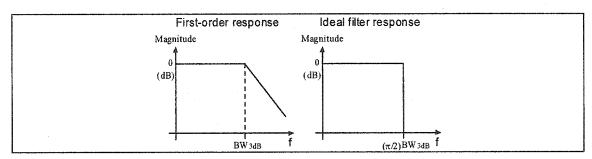

#### 2.6.1 Noise equivalent bandwidth

Before computing the required receiver sensitivity, it is important to be able to estimate the correct amount of integrated noise. The concept of noise equivalent bandwidth (NEB) is explained in Figure 2.6 [Johns97].

Figure 2.6 First-order response and noise equivalent bandwidth

The noise contribution of an amplifier at high frequency is low because of its decreasing gain response. The NEB is the bandwidth of an ideal rectangular low-pass filter that would produce the same amount of noise as the original amplifier. The NEB is found by integrating the magnitude response of an amplifier over the complete band of frequency. For a first-order system or a system with a dominant single pole, the magnitude response is described by:

$$|A(jf)| = \frac{1}{\left(1 + \left(\frac{f}{BW_{3dB}}\right)^2\right)^{1/2}}$$

where  $BW_{3dB}$  is the 3 dB bandwidth of the system. Applying a white source of noise  $V_{nw}$  to equation 2.12, the total output noise RMS value of the system would be:

$$V_{no(rms)}^{2} = \int_{0}^{\infty} \frac{V_{nw}^{2}}{1 + \left(\frac{f}{BW_{3dB}}\right)^{2}} df = V_{nw}^{2} BW_{3dB} \arctan \left(\frac{f}{BW_{3dB}}\right) \Big|_{0}^{\infty} = \frac{V_{nw}^{2} BW_{3dB} \pi}{2}$$

$$. \text{ Eq. 2.13}$$

Eq. 2.12

If this same noise signal is applied to an ideal rectangular low-pass filter, the total output noise would equal:

$$V_{ideal}^2 = \int_{0}^{BW_{ideal}} V_{nw}^2 df = V_{nw}^2 BW_{ideal} = V_{nw}^2 NEB$$

. Eq. 2.14

Finally, equating 2.13 and 2.14, the noise equivalent bandwidth of a first-order system is therefore given by:

$$NEB = \frac{\pi}{2}BW_{3dB}$$

Eq. 2.15

Thus, the total amount of noise present at the output of an amplifier having a first-order frequency response is equivalent to the noise of an ideal rectangular low-pass filter with a 3 dB bandwidth 1.57 times higher than the amplifier signal bandwidth.

The photodiode responsitivity can change significantly the sensitivity of a system. For example, a typical PIN photodiode has a responsitivity of 0.5 A/W to 0.95 A/W. For avalanche photodiodes, responsitivity is in the range of 5-10 A/W. By simply using an avalanche photodiode instead of a PIN photodiode, the sensitivity can be improved by more than 10 dB (10x). However, the noise produced by the avalanche photodiode is substantially higher and needs to be added to the input-referred current noise term  $(\overline{i_n^2})$ .

Finally, the power loss introduced by the extinction ratio also plays an important role in sensitivity computation. However, the designer does not have control over its value.

#### 2.7 Signal spectra

Prior to the receiver design, it is mandatory to know the power spectrum of the signal to be amplified. By knowing the signal power spectrum, the designer will be able to carefully optimize the design for low noise operation, while respecting the bandwidth requirements. The receiver bandwidth has a significant impact on the sensitivity, and on the bit-error-rate.

The most common line-coding used in optical communication systems is the NRZ coding, because it requires low bandwidth (half of the RZ coding). Because NRZ coding normally includes DC balancing, the low frequency of the spectrum is shaped differently than the regular NRZ coding. We can still work with the unmodified NRZ spectrum since we are mainly interested by the high frequency component. Before finding the optimum receiver bandwidth, we need to have a mathematical representation for the NRZ random stream data.

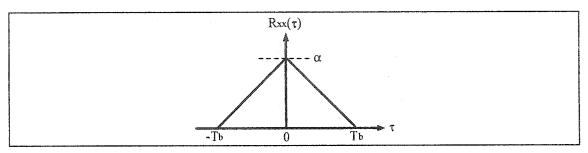

#### 2.7.1 Autocorrelation of a random NRZ data stream

The Wiener-Khinchin theorem states that, for a random process that is at least wide-sense stationary, the power spectral density of the process is equal to the Fourier transform of its autocorrelation function. Using this theorem, we can compute the power spectral density of a random NRZ data stream by first determining the autocorrelation function, and then calculating its Fourier transform.

The autocorrelation of a function can be computed by multiplying it by a time-shifted version of itself. The later result is then integrated over all values of time shifts. Autocorrelation is defined by:

$$R_{XX}(\tau) = \int_{-\infty}^{\infty} X(t)X(t-\tau)d\tau$$

Eq. 2.16

For random data, the limit of integration for the autocorrelation function can be changed from  $+\infty$  and  $-\infty$  to  $+T_b$  and  $-T_b$ , where  $T_b$  is the period of a single bit [MAXIM01]. Using this fact, the autocorrelation computation is greatly simplified, leading to the function shown graphically in Figure 2.7.

Figure 2.7 Autocorrelation of a random NRZ data stream.

The power spectral density is then found by applying the Fourier transform on the triangular function of Figure 2.7. The result is given by:

$$PSD = \alpha T_b \left[ \frac{\sin(\pi T_b f)}{\pi T_b f} \right]^2,$$

Eq. 2.17

where f is the frequency, and  $\alpha$  is a normalization coefficient.

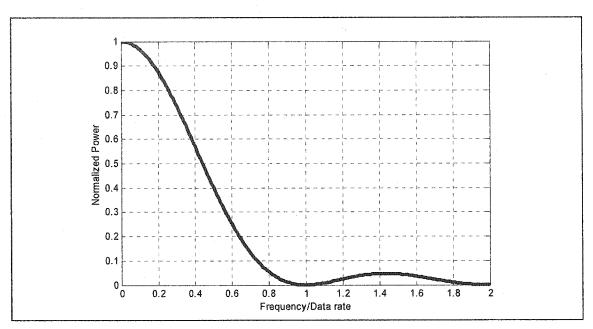

A graphical representation of the resulting power spectral density is shown by Figure 2.8. The y-axis is the normalized power, while the x-axis is the frequency normalized to the data rate (frequency/data rate). It is worth noting that no power exists at any integer multiple of the data rate frequency. In addition, the content of frequency extends to  $+\infty$ , but has no significant impact above 2 times the bit rate frequency.

Figure 2.8 Power spectrum of random NRZ signal.

Knowing the power spectrum of a NRZ data stream, it is now possible to find the optimum bandwidth necessary for the system receiver.

#### 2.8 Optimum bandwidth

As described in section 2.7, the power spectrum of a NRZ data stream extends to infinity. However, real systems have a limited bandwidth. Therefore, we have to choose a cutoff frequency to limit the bandwidth of an optical receiver.

The lowest possible cutoff frequency equals half the bit rate. This comes from the fact that the fastest transition in a NRZ stream is a repeating zero-one pattern, creating a square wave with half the bit rate frequency. However, to limit inter-symbol interference and account for possible variations, the cutoff frequency needs to be higher. On the other hand, a cutoff frequency being too high will lead to a large amount of integrated noise at the receiver, degrading its performance.

#### 2.8.1 Inter-symbol interference

Inter-symbol interference (ISI) is introduced by the dispersion effect in the optical fibre, and by the transfer function of the receiver amplifier. Dispersion comes from the non-constant group delay of a transmission medium or a filter. ISI introduces significant amount of jitter at the receiving end. Dispersion introduced by the optical fibre link can be compensated using dispersion-shifted fibres, or dispersion-compensated fibres. Again, the receiver designer does not have control over this since this is a system design issue. As will be described in section 3.3, the transfer characteristic of the receiving amplifier has a significant impact on dispersion. Also, if the cutoff frequency of the amplifier is made too small, significant ISI will be produced since not enough power will be present to accurately reconstruct the original signal.

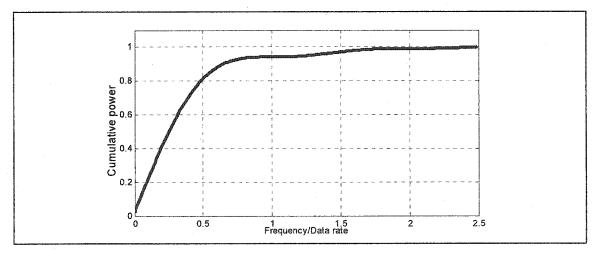

It is interesting to observe the cumulative (integrated) power spectrum of a random NRZ data stream, as that shown in Figure 2.9.

Figure 2.9 Cumulative power spectrum.

The majority of the signal power is included in frequencies lying between 0 to 0.9 times the data rate. At a frequency around 1 times the data rate, the cumulative signal power levels off. It then starts to increase by a small amount at frequencies between 1.2 to 1.8 times the data rate. After frequencies which are 2 times the data rate, 99.9% of the signal power is already recovered. Table 2.1 illustrate the gain signal power values versus the bandwidth.

Table 2.1 Tabulated values for cumulative power in a random NRZ signal.

| Frequency /<br>Data rate |       |

|--------------------------|-------|

| 0,5                      | 81.4% |

| 0.6                      | 87.8% |

| 0.7                      | 91.7% |

| 0.8                      | 94.3% |

| 0.9                      | 95.0% |

| 1.0                      | 95.1% |

| 1.1                      | 95.2% |

| 1.2                      | 95.5% |

| 1.3                      | 96.2% |

| 1.4                      | 97.1% |

| 1.5                      | 98.1% |

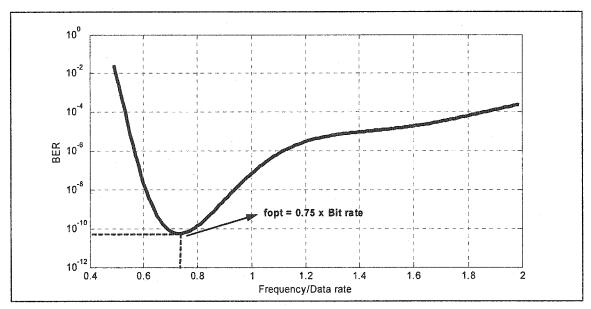

The optimum bandwidth to be used with a NRZ signal is a trade-off between inter-symbol interference and SNR. If the bandwidth is too low, the signal will be distorted and ISI will be severe. However, the noise contribution will be reduced. Alternatively, if the bandwidth is excessively large, no ISI will appear at the output of the amplifier. However, the noise contribution will be high due to the wide bandwidth. There exists an optimum bandwidth that guarantees to have the lowest noise and minimum ISI.

The optimum bandwidth can be found by optimizing the SNR as a function of frequency. As explained earlier, the minimum bandwidth allowed is 0.5 times the data rate. As the cutoff frequency increases, the signal power shift increases non-linearly, then changes by negligible amounts for high frequencies. On the other hand, the noise power (assumed white) increases linearly as the frequency increases. For example, by increasing the bandwidth by 33%, the signal power increases only by 1.5% while the noise power would increase by 33%. Thus, for an increase of 33% in bandwidth, the SNR becomes 0.76 times the original SNR, resulting in a reduction of the BER by a factor of more than 7000.

The maximum SNR is found by differentiating the SNR function with respect to frequency, then equating to zero.

$$SNR|_{MAX} = \frac{d}{df} \frac{\alpha T_b \left[\frac{\sin(\pi T_b f)}{\pi T_b f}\right]^2}{\overline{i_n^2} f} = 0$$

Eq. 2.18

From equation 2.18, it can be shown that the optimum bandwidth is **0.75 times the data** rate frequency. Since the BER is directly related to the SNR, it is interesting to plot the relationship between the BER versus the bandwidth of the system (Figure 2.10).

Figure 2.10 Optimum bandwidth for a NRZ system.

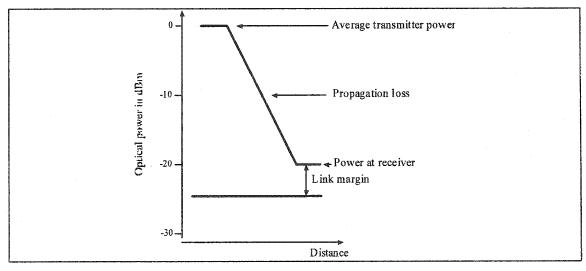

#### 2.9 Link budget

The system level performance of an optical communication system can be easily quantified in terms of a link budget. A link budget being either tabulated or plotted provides a quick summary of the system constraints. All link budgets have three entries: one for the transmitter, one for the propagation path, and one for the receiver. A simple graphical link budget for optical power is shown in Figure 2.11. The transmitter power is 0 dBm or 1 milliwatt. Over the optical fibre, 20 dB of power is lost (fibre attenuation,

fibre splices, couplers, etc.). The power arriving at the receiver is -20 dBm. Assuming a receiver sensitivity of -25 dBm, the link margin will be +5 dBm. The link margin is the amount of headroom available at the receiver to meet the system BER. For example, if some fibre splices introduce more loss than predicted, the system will still be able to operate properly and within specification.

Link budgets are normally more complex than this simple example. They usually account for all the second order effects that can affect the operation of the link. A link budget can also be written for noise power. These budgets are helpful for determining if a specific component in a system would introduce too much noise and degrade the BER. Noise budget for optical communication systems are similar to noise budgets in RF systems [Alexander97].

Figure 2.11 Example of a simple optical link budget.

#### 2.10 Receiver performance plot

Digital systems are characterized by the amount of erroneous bits sent in a given time frame (BER). Similar to analog receivers, a plot showing the performance for an optical communication receiver can be generated. The frontend components of receivers, such as transimpedance amplifiers, do suffer from dynamic range overload. Such overloads can be quantified using the same analysis used in RF communication systems. For example, a

large input power applied to a transimpedance amplifier will saturate and distort the output signal.

BER is to digital systems what SNR is to analog systems. Figure 2.12 shows the BER of a receiver as a function of the optical input power. For very low input power, the BER is limited because of the low SNR due to insufficient power at the input. To meet the user quality-of-service (QoS) requirements, the receiver needs to be operated within its dynamic range. Operation in this region will produce very low BER, and sometime error-free operation of the receiver. For large input powers exceeding the dynamic range, the BER will increase. This is owed to the overload and signal compression in the transimpedance amplifier.

Figure 2.12 Typical receiver performance plot.

Consequently, the optical power received by the receiver should always remain within its dynamic range. Optical amplifiers or attenuators can be added at the input of the photodiode to either amplify or attenuate the optical power. However, if the receiver is to operate with wide input current variations, the receiver can be modified to cope with this

by changing the gain of the transimpedance amplifier [Alexander97]. However, this requires extra circuitry and is more complex to design.

#### 2.11 Conclusion

Metrics used to characterize the receiver of an optical communication system were defined in this chapter. These metrics relate the signal power to the noise power in order to quantify the reliability of a link. From the link budget, one can learn many things about the overall system design and performance. It gives an overall system insight on whether the system will meet comfortably, marginally, or not the requirements. In addition, optimum bandwidth for the receiver amplifier resulting in the best operation was demonstrated to be at 0.75 times the bit rate frequency. This is an important starting point in designing the transimpedance and limiting amplifiers, both being at the front of an optical receiver.

#### 2.12 References

[Shannon48] C. E. Shannon, "A Mathematical Theory of Communication," BSTJ, vol 27, pp.379-423, 623-657, 1948.

[Sklar01] B. Sklar, "Digital Communication, Fundamental and Applications," Second Edition, Upper Saddle River: Prentice Hall, 2001.

[Keiser00] G. E. Keiser, "Optical Fiber Communications," Third Edition, New York: McGraw-Hill, 2000.

[Johns97] D. A. Johns, K. Martin, Analog Integrated Circuit Design. New York: Wiley, 1997.

[Alexander97] S. B. Alexander, Optical Communication Receiver Design. IEE Telecommunications Series, Volume 37, 1997.

[MAXIM01] Maxim, HFAN-03.0.0: "Accurately Estimating Optical Receiver Sensitivity," <a href="https://www.maxim-ic.com">www.maxim-ic.com</a>, Application Note 607, Oct. 2001.

# CHAPTER 3

# Transimpedance and Limiting Amplifiers Design

#### 3.1 Receiver front-end

Even if the optical communication receivers treat digital information, analog techniques are needed to amplify the weak signal (around -20dBm of optical power) of the photodiode. Low noise analog techniques, similar to the one used in RF designs, are needed to optimize the amplifiers design.

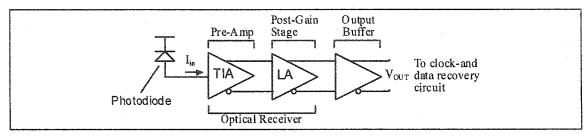

The basic receiver front-end is composed of a transimpedance amplifier (TIA) followed by a limiting amplifier (LA) (Figure 3.1). The role of the TIA is to transform the weak photodiode current to a voltage. One might think that using a simple resistor to perform the current-to-voltage conversion could be simpler than using a complex amplifier. This approach would not work well. The transimpedance gain needs to be stabilized over frequency. This is done by using an inverting amplifier and closing the loop with a resistive network.

Figure 3.1 Typical front-end amplifier.

A clock-and-data recovery circuit normally follows the receiver front-end. Since this block accepts digital level voltages, the receiver front-end should also output digital voltage levels. One solution would be to have a TIA with a very large transimpedance gain. This solution is not viable because the designer will quickly reach the limit of the technology. As described in section 3.3.1, the bandwidth of a TIA is inversely proportional to the transimpedance gain. As a result, it is not possible to optimize both the gain and the bandwidth. To meet the TIA bandwidth requirements, the transimpedance gain can be reduced. In order to make a TIA electrically compatible with a clock-and-data recovery/demultiplexer circuit, its output needs to be amplified to digital levels. In addition, the output must be independent of the input voltage and it has to operate over a wide dynamic range. The two most common approaches to achieve this function is by employing (1) an automatic gain control (AGC) amplifier or using (2) a string of limiting amplifiers (LA) after the TIA.

Controlled by a peak detector, the variable gain amplifier will reduce or enlarge its gain to amplify the TIA signal to a digital level suitable for the CDR. The peak detector time constant needs to be very large in order to catch only the envelope of the amplitude of the input signal. Choosing a time constant too small will result in gain modulation. This kind of amplifier is not very suitable for on-chip integration since it requires off-chip capacitances to achieve the large time constant required.

On the other hand, the non-linearity of a simple differential amplifier can be used to perform the limiting function. By cascading a number of limiting amplifiers, the output voltage will eventually reach digital levels, independently of the input voltage. Limiting

amplifiers are by their nature easy to design, since no automatic-gain control circuit is needed. Also, their power consumption is low, and no external components are needed.

### 3.2 Type of preamplifier

Preamplifiers in optical communication receiver can be classified into two categories. These categories are not distinct and intermediate designs are possible. The two categories are high input impedance and transimpedance amplifiers.

#### 3.2.1 High-impedance amplifiers

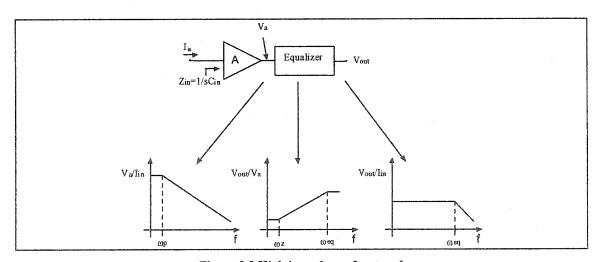

The goal of the high-impedance amplifier is to reduce all sources of noise to an absolute minimum. This is accomplished by reducing the input capacitance. Such amplifiers are normally built using GaAs or JFET transistors. The same techniques used for LNA design are applied here. Since the input impedance is high, the input RC time constant is large as well as the low frequency gain. Therefore, the front-end bandwidth is less than the signal bandwidth. To overcome this limitation, equalization techniques need to be employed. Figure 3.2 shows a typical high impedance bandwidth with the typical transfer functions.

Figure 3.2 High impedance front-end

Equalization is normally done by inserting a zero at the high frequency amplifier pole location. Exact compensation of the pole by the zero is hard to achieve, and external adjustment is generally needed.

#### 3.2.2 Transimpedance amplifiers

Transimpedance amplifiers (TIA's) provide the low noise characteristics of high-impedance amplifiers when used in conjunction with a resistive shunt feedback (current feedback) [Alexander97] [Sedra98]. This shunt feedback has the advantage of reducing the input impedance of the receiver, while stabilizing the gain of the overall amplifier. In addition, low noise and a large dynamic range are possible. The next section describes the mathematical details for this type amplifiers.

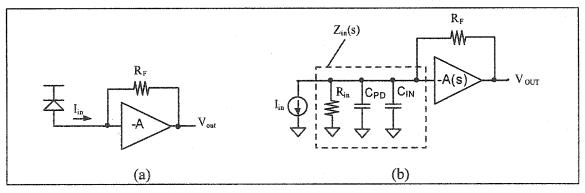

#### 3.3 TIA Design

A generic transimpedance amplifier is shown in Figure 3.3.a. It consists of a high-gain, high-impedance amplifier, shunted with a resistive feedback. To properly complete the model, the impedance of the photodiode should be included. Some TIAs use a circuit to compensate for the DC current created by the photodiode. This current is present in systems where the extinction ratio is non-zero (section 2.5). The input impedance of this type of circuit should also be modeled. It yields the model shown in Figure 3.3.b. This section presents the mathematical development of the TIA transfer function.

Figure 3.3 Basic transimpedance amplifier structure.

#### 3.3.1 Basic

Using the small signal equivalent model, the transfer function of the loop presented in Figure 3.3.b is given by equation 3.1.

$$Z_{t}(s) = \frac{v_{out}(s)}{i_{in}(s)} = \frac{-R_{f}}{1 + \frac{1}{A(s)} \left[1 + \frac{R_{f}}{Z_{in}(s)}\right]},$$

Eq. 3.1

where  $R_f$  is the feedback resistor, A(s) is the gain transfer function of the amplifier and  $Z_{in}(s)$  is the impedance seen at the input of the amplifier (the combination of the photodiode output resistance, the parasitic capacitance and the TIA input capacitance).

Suppose that the amplifier gain A is constant over the complete range of frequency, the transfer function of 3.1 can be simplified to:

$$Z_{t}(s) = \frac{-1}{1 + s \frac{R_{f}C_{m}}{A}}$$

Eq. 3.2

One can conclude that the pole created by the capacitance present at the input and the feedback resistor can be moved to higher frequency when the gain A is increased, thus increasing the bandwidth of the overall amplifier.

The bandwidth of the TIA is set by the first pole of its closed-loop transfer function and is given by:

$$BW \approx \frac{A+1}{2\pi R_F C_{_{in}}}$$

Eq. 3.3

where A is the small-signal gain, R<sub>F</sub> the feedback resistance and C<sub>in</sub> the equivalent input capacitance of the amplifier. The feedback resistance and amplifier gain A should be selected such that the bandwidth is 0.75 times the bit rate. However, optimization needs to be done to reduce the noise created by the amplifier.

The input impedance of a TIA is given by the following equation:

$$Z_{in}(s) = \frac{R_f}{1+A} Z_{in}(s),$$

Eq. 3.4

If the gain A could be increased to infinity, the input impedance of the amplifier would be 0. In practice, the gain A is limited by the technology used.

An ideal TIA used in high-speed applications would have high transimpedance gain and wide bandwidth. However, it is not possible to maximize both transimpedance gain and bandwidth at the same time. If one increases the gain, the bandwidth will decrease. On the other hand, if the bandwidth needs to be increased, the gain needs to be reduced. The tradeoff can be better explained by the following equation [Sanduleanu01]:

$$R_f * BW = \frac{A}{2\pi C_{in}}.$$

Eq. 3.5

Because negative feedback is used, the amplifier must be kept stable. The TIA is built around a high-impedance amplifier. This amplifier can be modeled by equation 3.6:

$$A(s) = \frac{A}{1 + \frac{s}{\omega_p}},$$

Eq. 3.6

where  $\omega_p$  is the location of the dominant amplifier pole. This is a simplified model of a real amplifier. Real amplifiers have complex transfer functions with many poles located higher in frequency. To model an amplifier as a first order system, the second dominant pole must be around 2 to 3 times higher in frequency than the dominant pole.

From [Sanduleanu01], a limit on the transimpedance gain can be set. The transimpedance gain should be lower than:

$$R_f = \frac{A\omega_p}{C_m BW^2},$$

Eq. 3.7

in order to keep the amplifier stable. As it will be explained in section 3.4.1, it is better to have a large feedback resistance to reduce the noise transfer characteristic of the TIA. At the same time, the sensitivity of the amplifier is increased.

The next section describes the sources of noise present in a transimpedance amplifier.

#### 3.4 TIA noise analysis

Every electronic circuit is by its nature noisy. The amount of noise tolerable in a system is defined by the application specifications. For radio-frequency communication system, the front-end amplifier has tight noise specifications [Alexander97]. In optical communication system, the front-end circuit is generally a TIA. The amount of noise generated by the TIA will set a lower limit on the sensitivity (smallest detectable signal) achieved by the system. Other stages, such as the limiting amplifier (LA) are also subject to noise degradation. This is most important when the input signal is small and comparable to the noise amplitude.

This section only present a quick overview of the noise sources present in optical frontends. Excellent presentations/chapters of noise present in electronic systems are available throughout the literature. Of great interest is the chapter of Gray/Meyer [Gray01]. This chapter presents all the basic noise sources contributors in modern IC processes. Also, thorough examples of noise analysis are presented in other interesting books [Razavi98].

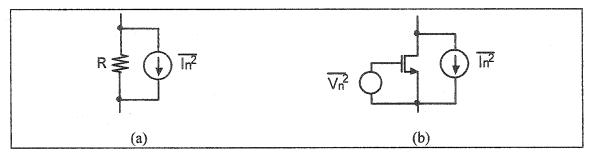

To analyse the noise generated by a TIA, it is important to define the main contributors. Such contributors are the channel noise of the transistors and the thermal noise of the feedback resistor. As the transistor size is shrinking (due to advances in process development), the channel noise is becoming more significant. Figure 3.4 illustrated the resistor and MOS transistor noise models used for mathematical analysis.

Figure 3.4 Noise representations in a resistor and a MOS device.

Only thermal noise is generated by a resistor. Thermal noise can be considered as a white noise source [Gray01]. It can be represented by a current source in parallel with the actual resistance. The magnitude of the current source is given by:

$$\overline{I_n^2} = 4kT \frac{1}{R} \Delta f$$

Eq. 3.8

where k is the Boltzmann's constant, T the absolute temperation, R the value of resistance and  $\Delta f$  is the bandwidth used for integration. From this equation, a large resistance will produce less current noise. This is important for TIA design, since the input is in the form of current.

MOS transistors have different noise contributors [Razavi98]. The channel of a transistor exhibits thermal noise. It can be defined as:

$$\overline{I_n^2} = \frac{8}{3}kTg_m$$

, Eq. 3.9

where  $g_m$  is the transconductance of the device. Flicker noise, also called the 1/f noise, can be an important noise contributor. It is normally represented by a voltage source connected in series with the gate. However, for circuits such as a TIA, where the frequencies of interest are above DC, it can be omitted in the analysis.

#### 3.4.1 Generic TIA noise derivation

Many analysis of the noise present in a TIA have been reported [Ingels99] [Kim01] [Ingels94] [Tanabe98]. This section summarizes these studies. Before presenting the

mathematical derivation, one assumption has to be made: the noise of the amplifier A (Figure 3.3) is mainly due to one transistor, the input transistor. Other noise sources present in the amplifier should be smaller, and therefore neglected.

The equivalent input-referred current noise spectral power density for the TIA presented in Figure 3.2 is given by:

$$I_{n,eq}^2(s) \cong \frac{8}{3} \frac{kT}{g_m R_f^2} (1 + sR_f C_m)^2 + 4 \frac{kT}{R_f},$$

Eq. 3.10

where  $g_m$  is the transconductance of the input transistor,  $R_f$  is the feedback resistor,  $C_{in}$  is the equivalent input capacitance, T is the absolute temperature in Kelvin, and k is the Boltzmann's constant. As stated previously, equation 3.10 does not include the flicker noise because it is located below the frequency range of interest. The first term of the equation is the input transistor noise contribution, where as the second term is the feedback resistor's noise contribution.

At medium frequency, the main source of noise is the feedback resistor noise and the MOS channel thermal noise. The spectral noise density starts increasing at higher frequencies because of the zero present in the transfer function. Assuming that the  $g_m R_f$  product is greater than 1 (the channel noise being smaller than the feedback resistor noise), equation 3.10 can be simplified to:

$$I_{n,eq}^{2}(\omega) \cong \frac{8 kT\omega^{2} C_{in}^{2}}{3 g_{m}} + 4 \frac{kT}{R_{f}}.$$

Eq. 3.11

The total integrated input-referred current noise power for a TIA is calculated by integrating 3.11. For the complete range of frequencies:

$$I_{n,eq}^2 \cong \int_{\omega=0}^{\omega=\infty} \left( \frac{8}{3} \frac{kT\omega^2 C_m^2}{g_m} + 4 \frac{kT}{R_f} \right) d\omega.$$

Eq. 3.12

The upper integration limit, set to infinity, can be replaced by its noise equivalent bandwidth, as defined in section 2.6.1. The integrated input-referred current noise becomes:

$$I_{n,eq}^2 \approx \frac{1}{9} \frac{kTC_{in}^2 \left(\frac{\pi}{2}BW\right)^3}{g_m} + 2\frac{kT\left(\frac{\pi}{2}BW\right)}{R_f},$$

Eq. 3.13

where BW is the 3dB bandwidth of the amplifier. This is valid for an amplifier approximated with a first order transfer function.

The equations derived in this section can be applied, with some variants, to almost any transimpedance amplifier with resistive feedback.

#### 3.5 5Gb/s TIA with a resonant network

This section describes the design of a 5Gb/s transimpedance amplifier used as part of an optical front-end.