## WIDE-TEMPERATURE RANGE CMOS INTERFACE CIRCUITS FOR CAPACITIVE MEMS SENSORS

## Yucai Wang

# Department of Electrical and Computer Engineering McGill University, Montreal, Canada June, 2015

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Doctor of Philosophy

## **ACKNOWLEDGEMENTS**

I would first and foremost like to thank my advisor, Dr. Vamsy P. Chodavarapu, for his supervision, guidance, constant encouragement and inspiration during my Ph.D. studies. Without his support, this work would not have gone through. It was my great honor and pleasure to work with him.

I would also like to thank my Ph.D. supervisory committee members, Dr. Zetian Mi and Dr. Ishiang Shih, for their valuable comments and help towards my Ph.D. research projects.

I would like to thank all my previous and current colleagues in the Sensor Microsystems Laboratory for their assistance during the past four years. Special thanks go to Adel Merdassi for his help in the French abstract.

I acknowledge the financial support provided by the Natural Sciences and Engineering Research Council of Canada (NSERC) and McGill Engineering Doctoral Awards (MEDA) program. I would like to thank the fabrication service and CAD tool support provided by Canadian Microelectronics Corporation (CMC).

I am deeply indebted to my parents for their everlasting support and encouragement. Finally, the most important, I would like to thank my wife Mingqin for her constant love and patience. I wish to dedicate this thesis to my newborn daughter, Helene. I wish her a joyful life ahead with liberty, freedom, and dignity.

## TABLE OF CONTENTS

| Abstract                                                    | VI   |

|-------------------------------------------------------------|------|

| Résumé                                                      | VIII |

| List of Figures                                             | X    |

| List of Tables                                              | XIII |

| Publications                                                | XIV  |

| Contributions of authors                                    | XVI  |

| Chapter 1 Introduction                                      | 1    |

| 1.1 Introduction to MEMS                                    | 1    |

| 1.1.1 Brief History of MEMS                                 | 1    |

| 1.1.2 Advantages of MEMS                                    | 3    |

| 1.2 Examples of MEMS Sensors                                | 4    |

| 1.3 MEMS Sensors for Wide-Temperature Applications          | 12   |

| 1.4 Interface Electronics for Wide-Temperature MEMS Sensors | 15   |

| 1.5 Challenges for Wide-Temperature CMOS Circuits Design    | 19   |

| 1.5.1 Intrinsic Carrier Concentration                       | 19   |

| 1.5.2 Carrier Mobility                                      | 21   |

| 1.5.3 Threshold Voltage                                     | 23   |

| 1.     | 5.4 | Leakage Current                                          | 26 |

|--------|-----|----------------------------------------------------------|----|

| 1.6    | Hi  | gh Temperature Circuit Design Techniques                 | 28 |

| 1.     | 6.1 | High Temperature Tolerant Circuit Architectures          | 30 |

| 1.     | 6.2 | Constant-Gm Biasing Technique                            | 30 |

| 1.     | 6.3 | Analog Switch Optimization                               | 31 |

| 1.7    | Th  | esis Objectives and Organization                         | 33 |

| 1.8    | Cla | aims of Originality                                      | 34 |

| Chapte | r 2 | Design Overview and Basic Circuit Building Blocks        | 36 |

| 2.1    | Ciı | cuit Design Overview and Testing Environments            | 36 |

| 2.2    | Co  | nstant-Gm Biasing Technique                              | 39 |

| 2.3    | Ge  | neral Purpose High-Temperature Amplifiers                | 45 |

| 2.4    | Ex  | perimental Results                                       | 51 |

| 2.5    | Su  | mmary and Conclusions                                    | 55 |

| Chapte | r 3 | CMOS Differential Capacitance to Voltage Readout Circuit | 56 |

| 3.1    | Ciı | cuit Architecture                                        | 56 |

| 3.2    | De  | tailed Circuits Design                                   | 58 |

| 3.3    | Ex  | perimental Results and Discussion                        | 59 |

| 3.4    | Su  | mmary and Conclusions                                    | 67 |

| Chapte | r 4 | CMOS Capacitance to Frenquency Readout Circuit           | 68 |

| 11     | C:  | rauit Arabitaatura                                       | 69 |

| 4.2     | Design of  | of Detailed Circuits                                | 71  |

|---------|------------|-----------------------------------------------------|-----|

| 4.2     | 2.1 Integ  | grator Design                                       | 71  |

| 4.2     | 2.2 Com    | nparator Design                                     | 72  |

| 4.2     | 2.3 Digit  | ital Conversion Circuit                             | 73  |

| 4.2     | 2.4 Layo   | out of The Capacitance to Frequency Readout Circuit | 75  |

| 4.3     | Experime   | ental Results and Discussion                        | 76  |

| 4.4     | Summary    | y and Conclusions                                   | 80  |

| Chapter | 5 CMC      | OS Capacitance to Digital Readout Circuit           | 81  |

| 5.1     | Circuit A  | Architecture                                        | 81  |

| 5.2     | Detailed 1 | Design of Circuits                                  | 86  |

| 5.3     | Simulation | on Results                                          | 87  |

| 5.4     | Experime   | ental Results and Discussion                        | 89  |

| 5.5     | Summary    | y and Conclusions                                   | 96  |

| Chapte  | 6 Conc     | clusions and Future Work                            | 97  |

| 6.1     | Conclusio  | ons                                                 | 97  |

| 6.2     | Future W   | Vork                                                | 99  |

| Referer | ces        |                                                     | 102 |

## **ABSTRACT**

Many applications require MEMS sensors to operate over wide temperature range, typically from -55 °C to 225 °C. It is desirable to place the sensor readout circuits in close proximity to the sensor devices to improve signal-to-noise ratio and system reliability. Therefore, the sensor readout circuits must also be able to function over the same temperature range as the sensor devices. The main challenges for designing CMOS sensor readout circuits working over wide-temperature range (especially at the high temperature end) include: 1) increased junction leakage current, 2) reduced carrier mobility, and 3) decreased threshold voltage in MOS transistors. In this thesis, constant-g<sub>m</sub> biasing and other design techniques are used to mitigate the circuit performance degradation at high temperatures and three readout circuits for capacitive MEMS sensors are developed using standard CMOS process which can operate over wide temperature range from -55 °C to 225 °C.

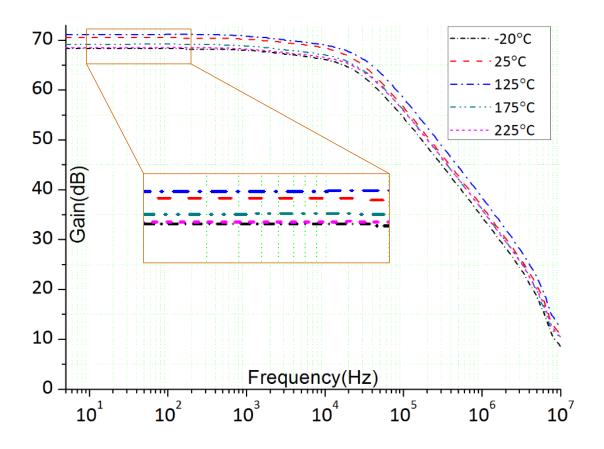

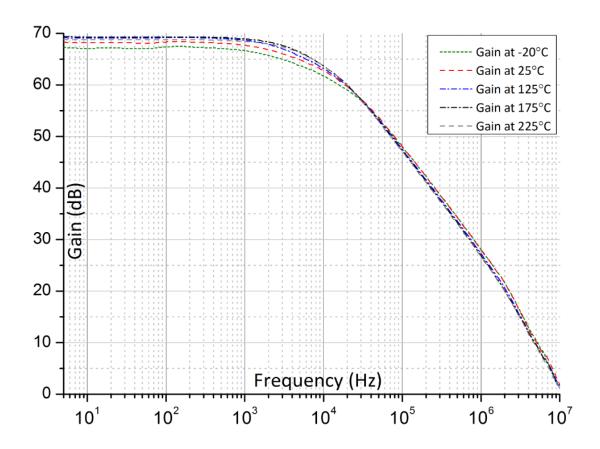

First, several proof-of-concept core building blocks are designed and tested, including a constant-g<sub>m</sub> biasing circuit, a single-ended folded-cascode amplifier, and a fully-differential folded-cascode amplifier with a switched capacitor common mode feedback circuit. The single-ended folded-cascode amplifier showed DC gain of 68.5 dB at 225 °C and DC gain variation of 2.8 dB from -20 °C to 225 °C. The fully-differential folded-cascode amplifier with the switched capacitor common mode feedback circuit showed a DC gain of 68.9 dB and DC gain variation of 2.1 dB from -20 °C to 225 °C.

Then, using these core building blocks, three readout circuits for capacitive MEMS sensors were constructed, including: 1) a differential capacitance to voltage readout circuit for sensors with a wide range of the steady-state capacitance values from 0.5 pF to 10 pF, 2) a capacitance to frequency readout circuit which converts the sensor capacitance into digital pulse signal modulated in frequency, and 3) a capacitance to digital readout circuit which uses a sigma-delta technique to convert the input ratio between sensor capacitance and reference capacitance into a high-accuracy digital output. All these three capacitive sensor readout circuits are simulated over temperature range from -55 °C to 225 °C and tested over temperature range from -20 °C to 225 °C. Measurement results show that these circuits have good accuracy and temperature stability over the wide temperature range.

All the circuits developed in this thesis are implemented using IBM 0.13 µm standard CMOS technology which incorporates a 2.5 V power for the advantages of high level of integration and low power consumption. The design techniques used here are universal and they can be readily ported to other standard CMOS processes and even SOI processes. Future improvement and development for these circuits are proposed. More sophisticated sensor readout circuits could be built based upon the prototypes developed in this thesis.

## **RÉSUMÉ**

De nombreuses applications nécessitent des capteurs MEMS pour fonctionner sur une large plage de température, typiquement entre -55 °C à 225 °C. Il est souhaitable de placer les circuits de conditionnement des capteurs à proximité des dispositifs de détection afin d'améliorer le rapport signal sur bruit et la fiabilité du système. Par conséquent, les circuits de conditionnement des capteurs doivent également être en mesure de fonctionner sur la même plage de température que les dispositifs de détection. Les principaux défis pour la conception de circuits de conditionnement pour capteur CMOS fonctionnant sur une large plage de température (surtout à la fin haute température) sont : 1) courant de fuite de jonction croissant, 2) réduction de la mobilité des porteurs de charge, et 3) diminution de la tension de seuil des transistors MOS. Dans cette thèse, la polarisation constante g ainsi que d'autres techniques de conception sont utilisées pour atténuer la dégradation des performances du circuit à des températures élevées ainsi que trois circuits de conditionnement dédiés à des capteurs capacitifs MEMS ont été développés en utilisant le procédé standard CMOS qui peut fonctionner sur une large plage de température de -55 °C à 225 °C.

En premier lieu, quelque blocks de construction de base preuve de concept sont conçus et testés, y compris un circuit de polarisation à base de constante-g<sub>m</sub>, un amplificateur en amont mis en cascade avec un amplificateur différentiel sont entièrement repliées en cascade avec un circuit de rétroaction à capacités commutées de mode commun. L'amplificateur replié en cascade en amont a montré un gain DC de 68.5 dB à 225 °C et une variation de gain DC de 2.8 dB à partir de -20 °C jusqu'à 225 °C. L'amplificateur différentiel est entièrement replié en cascade avec un

circuit de rétroaction à capacités commutées en mode commun a montré un gain DC de 68.9 dB et une variation de gain DC de 2.1 dB de -20 °C à 225 °C.

Ensuite, en utilisant ces blocs de construction de base, trois circuits de conditionnement pour capteurs MEMS capacitifs ont été construits, notamment: 1) un circuit de conditionnement des capteurs à base de conversion capacité-tension (C-V) avec un large éventail de valeurs de capacité à l'état stable de 0.5 pF à 10 pF, 2) un circuit de conditionnement à base d'un convertisseur capacité-fréquence permettant la conversion de la capacité du capteur en un signal numérique à impulsions modulées en fréquence, et 3) un circuit de conditionnement à base d'un convertisseur de capacité en un signal numérique en utilisant une technique d'acquisition sigmadelta pour convertir le taux d'entrée entre la capacité du capteur et de la capacité de référence en une sortie numérique à haute précision. Tous ces trois circuits de conditionnement pour capteurs capacitifs sont simulées sur toute la plage de température de -55 °C à 225 °C ainsi que testés sur toute la plage de température de -50 °C à 225 °C. Les résultats des mesures montrent que ces circuits ont une bonne précision et une stabilité de température sur une large plage de température.

Tous les circuits développés dans cette thèse sont implémentés en utilisant la technologie standardisée d'IBM (CMOS à base de 0.13 µm) qui intègre une puissance de 2.5 V grâce aux avantages de haut niveau d'intégration et de faible consommation d'énergie. Les techniques de conception utilisées ici sont universelles et ils peuvent être facilement portés à d'autres procédés CMOS standard et même aux procédés SOI. L'amélioration et le développement futur de ces circuits sont proposés. Plus de circuits de conditionnement sophistiqués pour capteurs pourraient être construits sur la base des prototypes actuellement développés dans cette thèse.

## **LIST OF FIGURES**

| Figure 1.1 A schematic of a capacitive MEMS accelerometer ( taken from [13])                 | 5      |

|----------------------------------------------------------------------------------------------|--------|

| Figure 1.2 Schematic of a piezoresistive MEMS pressure sensor. (a) top view (b) side view    | N      |

| without applied pressure (c) side view with external pressure. (taken from [14])             | 6      |

| Figure 1.3 Schematic of a piezoelectric MEMS accelerometer (taken from [16])                 | 7      |

| Figure 1.4 Schematic of a MEMS resonant accelerometer (taken from [17])                      | 8      |

| Figure 1.5 Schematic of a MEMS thermal sensor (taken from [18])                              | 9      |

| Figure 1.6 Schematic of a MEMS resonant magnetic field sensor (taken from [19])              | 10     |

| Figure 1.7 Intrinsic carrier concentration $(n_i)$ of Si and GaAs versus temperature         | 20     |

| Figure 1.8 Carriers (electron and hole) mobility of silicon versus temperature               | 23     |

| Figure 1.9 Schematic of an NMOS transistor with parasitic diodes                             | 26     |

| Figure 1.10 A constant-g <sub>m</sub> biasing circuit.                                       | 31     |

| Figure 1.11 CMOS transmission gate with the leakage diodes and the hold capacitor            | 32     |

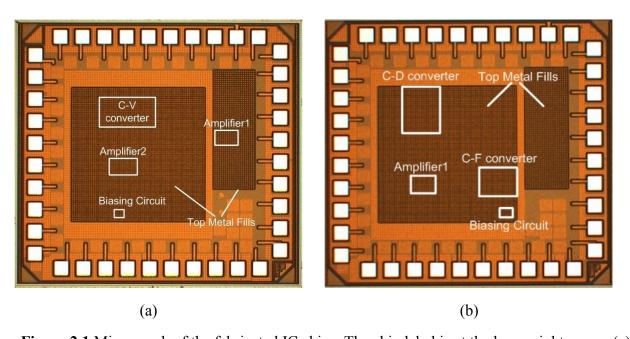

| Figure 2.1 Micrograph of the fabricated IC chips. The chip label is at the lower right corne | er (a) |

| the chip with chip label BLV32E (b) the chip with chip label ALV38C                          | 37     |

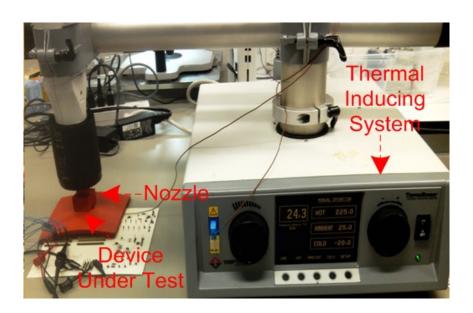

| Figure 2.2 The chip testing setup                                                            | 38     |

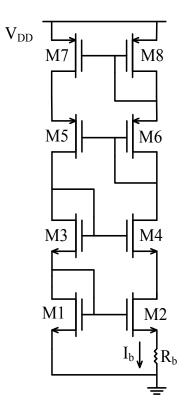

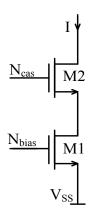

| Figure 2.3 Constant-g <sub>m</sub> biasing circuit                                           | 40     |

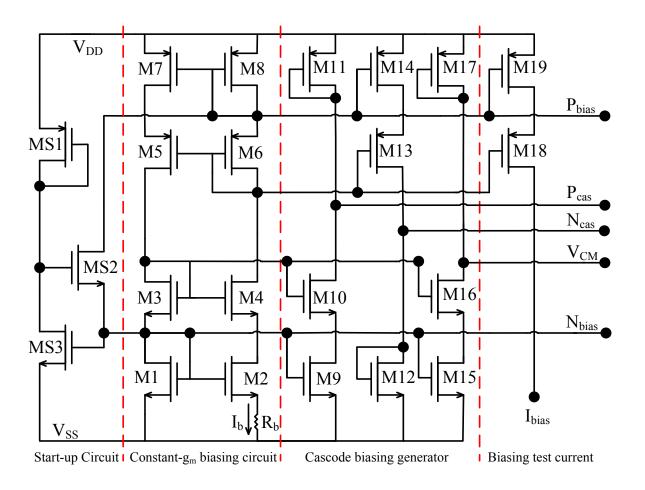

| Figure 2.4 Detailed constant-g <sub>m</sub> biasing circuit                                  | 44     |

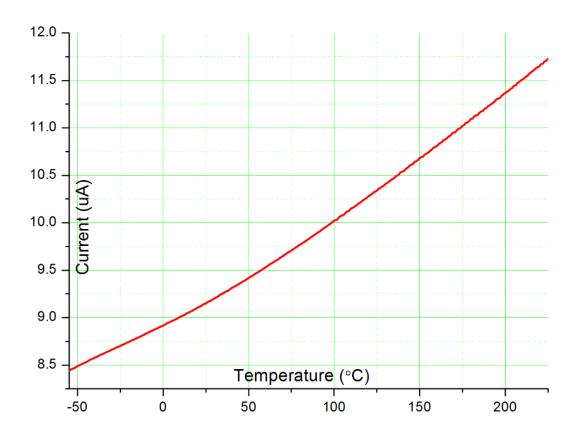

| Figure 2.5 Simulated constant-g <sub>m</sub> biasing current I <sub>b</sub>                  | 45     |

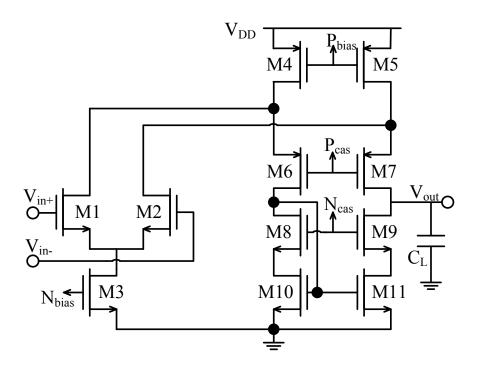

| Figure 2.6 Schematic of the folded-cascode amplifier                                         | 46     |

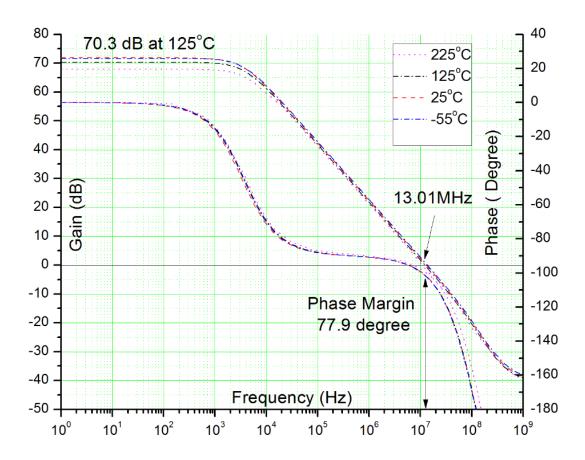

| Figure 2.7 Simulated open-loop frequency response of the folded-cascode amplifier            | 47     |

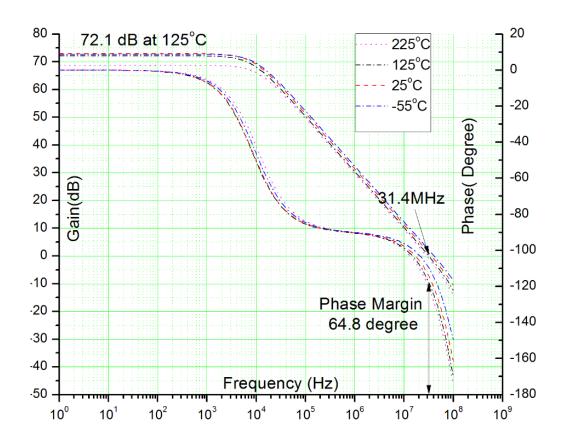

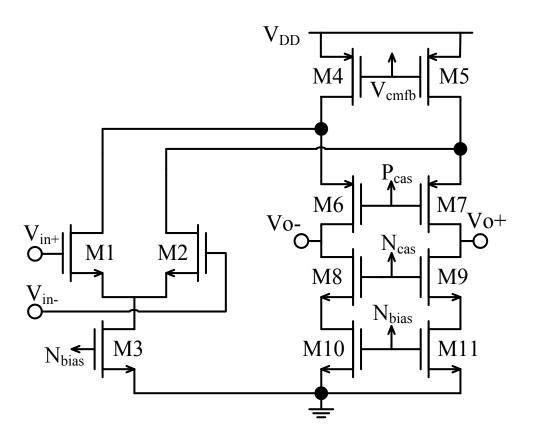

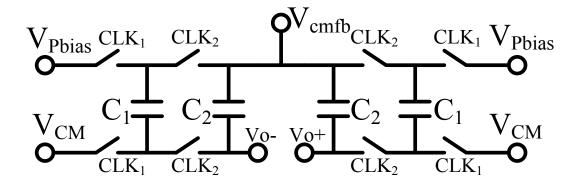

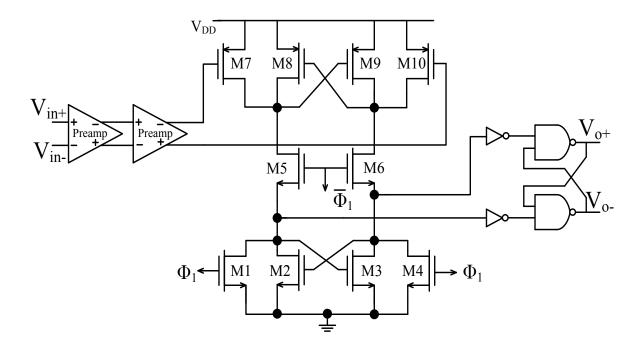

| Figure 2.8 Schematic of the fully differential folded-cascode amplifier                               | 48 |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2.9 Schematic of the SC CMFB circuit                                                           | 49 |

| Figure 2.10 Simulated single-ended open-loop frequency response of the fully differential             |    |

| folded-cascode amplifier with CMFB                                                                    | 50 |

| Figure 2.11 Simulated transient response of the fully differential folded-cascode amplifier with      | th |

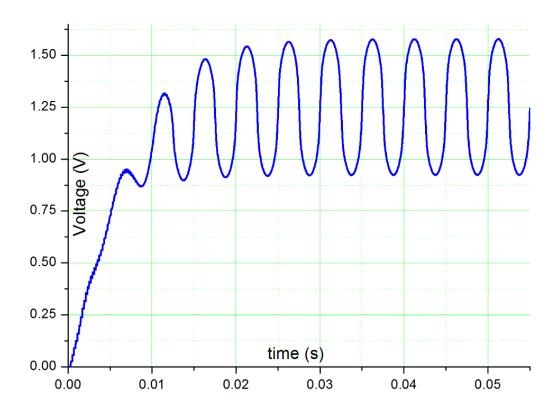

| CMFB circuit at 125 °C                                                                                | 51 |

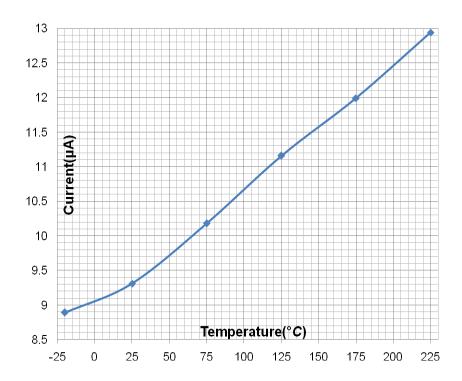

| Figure 2.12 Measured constant-g <sub>m</sub> biasing current I <sub>b</sub> at different temperatures | 52 |

| Figure 2.13 Measured open-loop frequency response of the single-ended Folded-cascode                  |    |

| amplifier (with 2 pF load capacitance)                                                                | 53 |

| Figure 2.14 Measured open-loop frequency response of the fully-differential folded-cascode            |    |

| amplifier (single-ended output with 2 pF load capacitance)                                            | 54 |

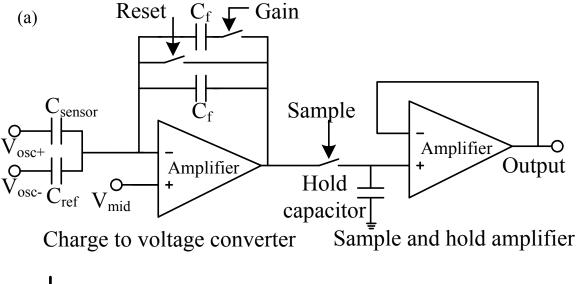

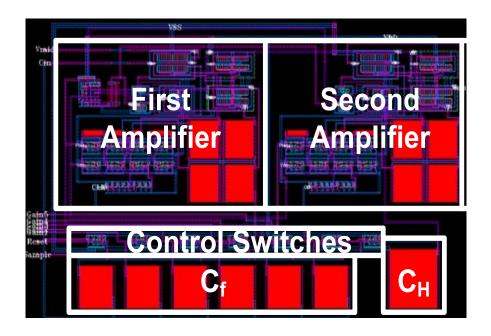

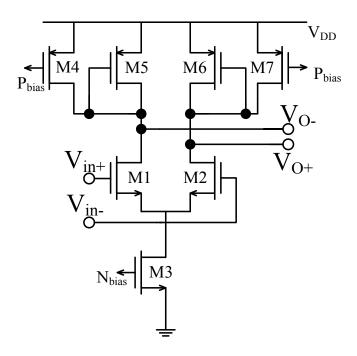

| Figure 3.1 (a) Schematic diagram of the CMOS capacitance to voltage readout circuit; (b)              |    |

| Waveforms of the control and output signals for the CMOS circuit.                                     | 57 |

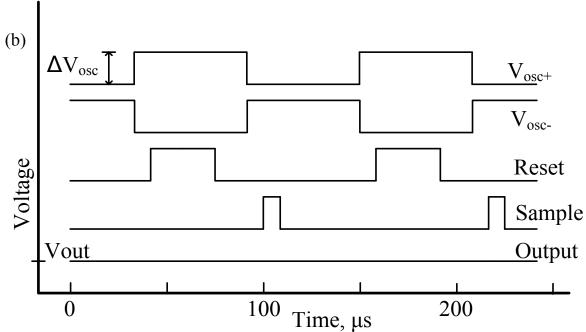

| Figure 3.2 Layout of the capacitance to voltage readout circuit                                       | 59 |

| Figure 3.3 Simulated output voltages of the converter circuit at different temperatures               | 60 |

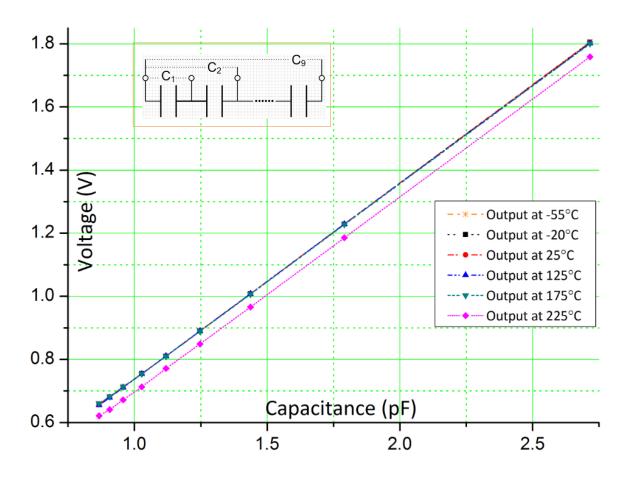

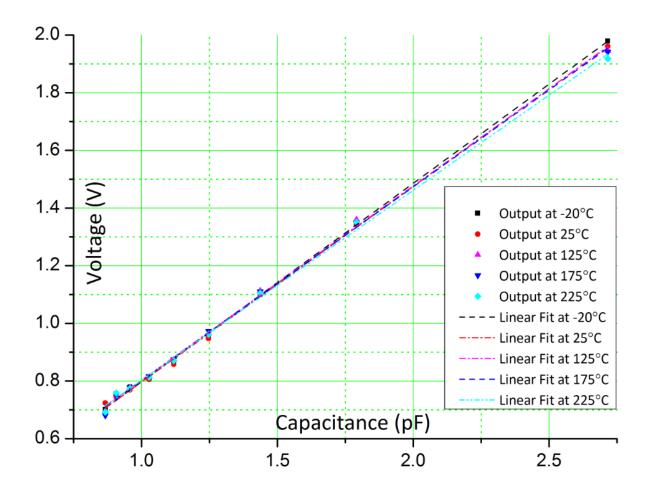

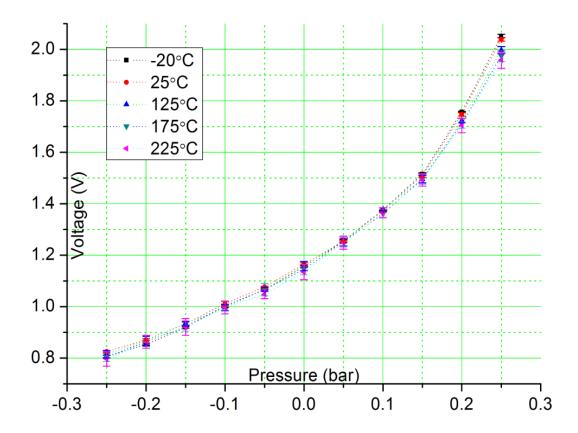

| Figure 3.4 Measured output voltages of the converter circuit at different temperatures                | 61 |

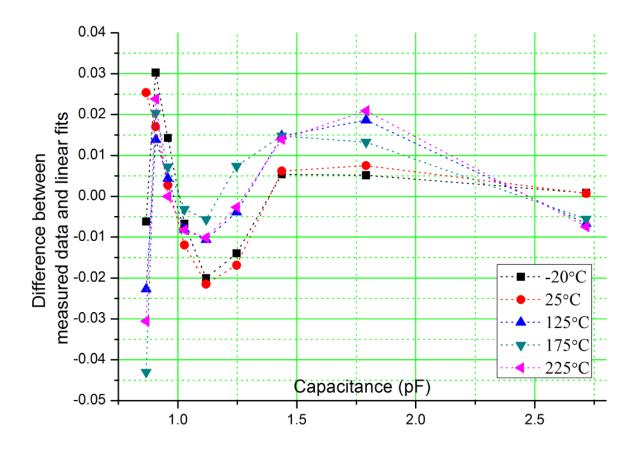

| Figure 3.5 Difference between measured results and linear fits                                        | 62 |

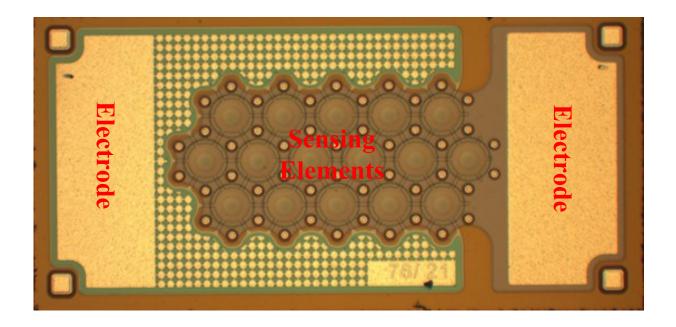

| Figure 3.6 Micrograph of the capacitive MEMS pressure sensor                                          | 63 |

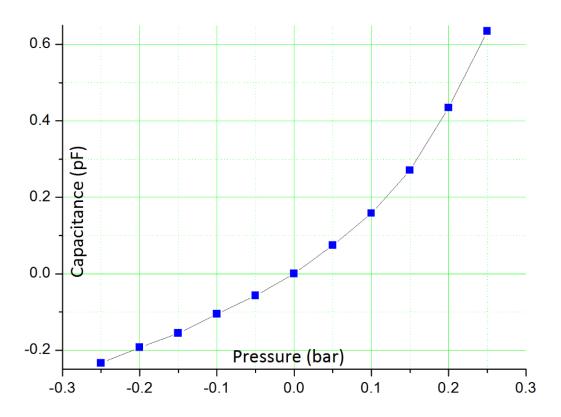

| Figure 3.7 Measured Capacitance output change versus pressure change for the capacitive               |    |

| MEMS pressure sensor                                                                                  | 64 |

| Figure 3.8 Measured output response of the capacitance to voltage readout circuit with a              |    |

| capacitive MEMS pressure sensor                                                                       | 65 |

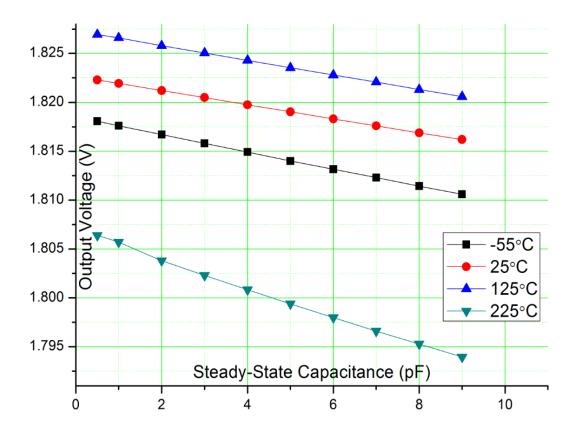

| Figure 3.9 Simulated output voltage for different steady-state canacitance                            | 66 |

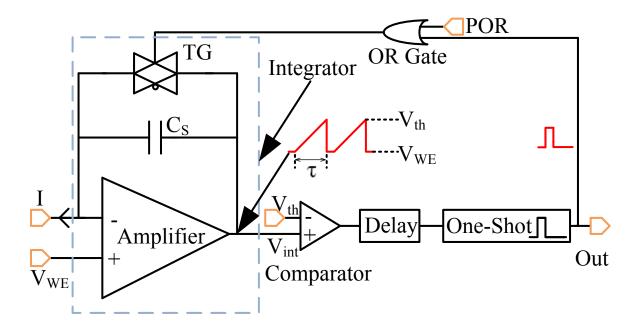

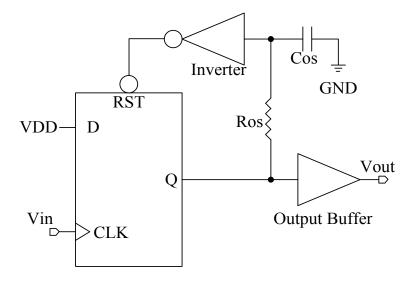

| Figure 4.1 Schematic diagram of the capacitance to frequency readout circuit                      | 69 |

|---------------------------------------------------------------------------------------------------|----|

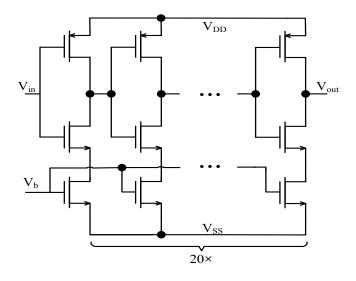

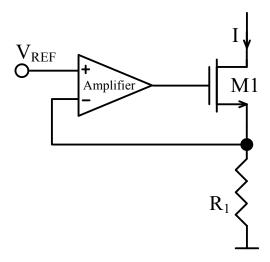

| Figure 4.2 Schematic of the current sink which provides the integration current I                 | 71 |

| Figure 4.3 Schematic of the comparator                                                            | 72 |

| Figure 4.4 Schematic of the pre-amplifier in the comparator                                       | 73 |

| Figure 4.5 Schematic of the delay module                                                          | 74 |

| Figure 4.6 Schematic of the one-shot circuit                                                      | 74 |

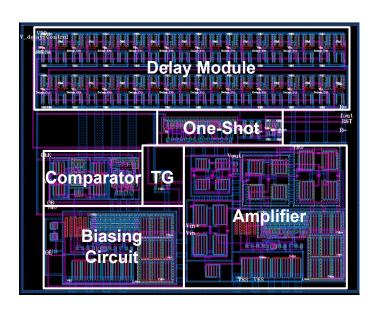

| Figure 4.7 Layout of the capacitance to frequency readout circuit.                                | 75 |

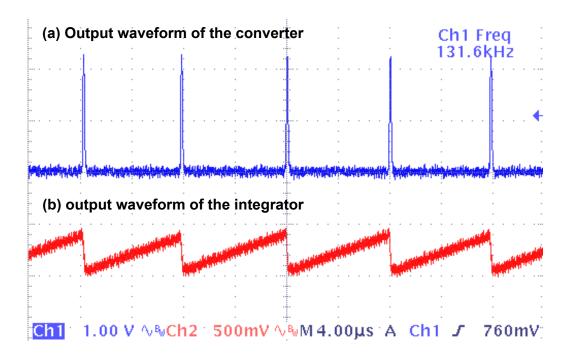

| Figure 4.8 (a) Output waveform of the converter, and (b) output waveform of the integrator        | 76 |

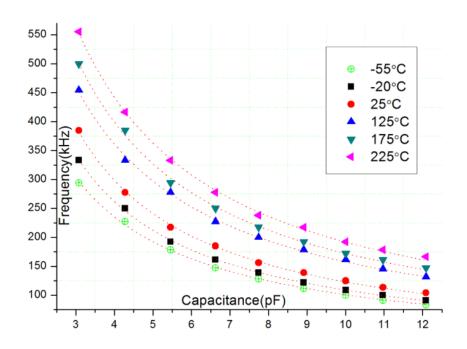

| Figure 4.9 Simulated output frequency of the frequency readout circuit                            | 77 |

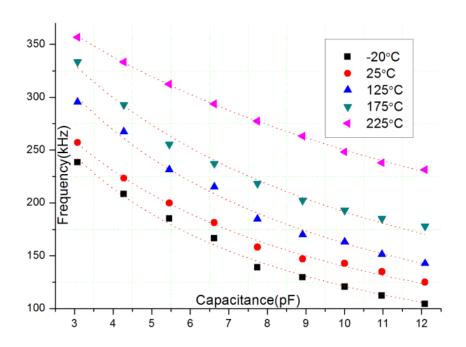

| Figure 4.10 Measured output frequency of the frequency readout circuit                            | 77 |

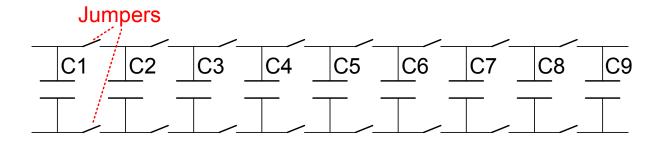

| Figure 4.11 Construction of the sensor capacitor C <sub>s</sub>                                   | 78 |

| Figure 4.12 Schematic of the constant circuit sink                                                | 80 |

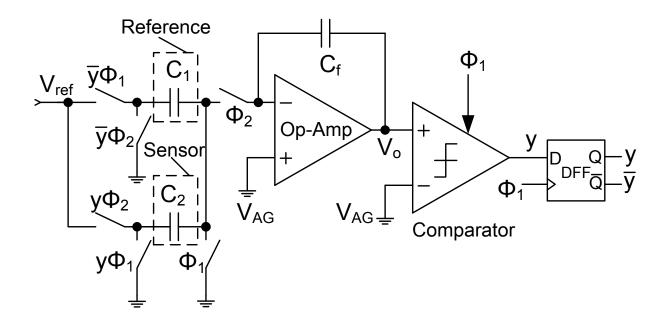

| Figure 5.1 Schematic of a basic capacitance to digital readout circuit                            | 82 |

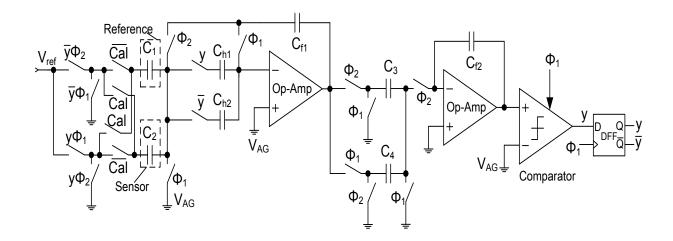

| Figure 5.2 Schematic of the improved capacitance to digital readout circuit                       | 84 |

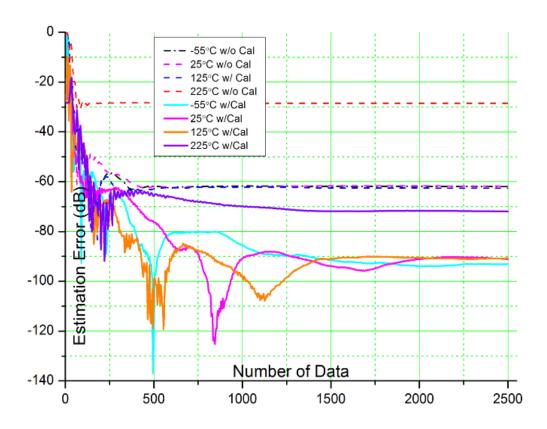

| Figure 5.3 Estimation error of the capacitance to digital readout circuit for different number of | of |

| data points at various temperatures                                                               | 88 |

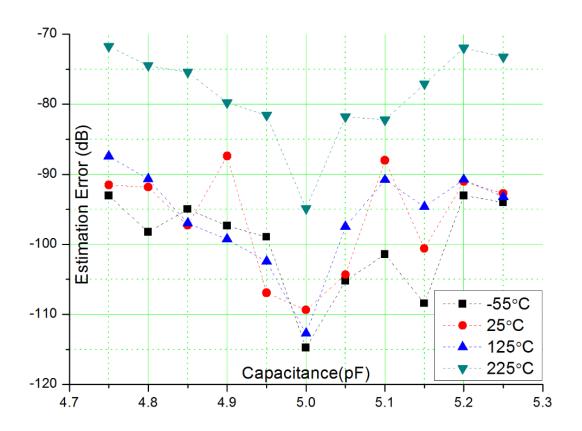

| Figure 5.4 Estimation error versus C <sub>2</sub> values                                          | 89 |

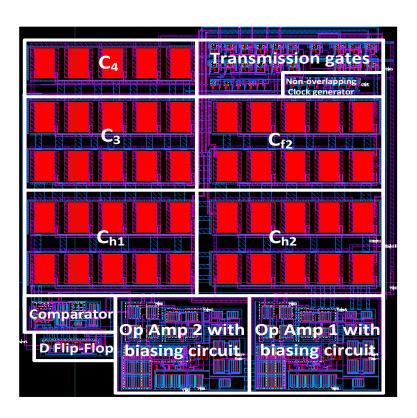

| Figure 5.5 Layout of the capacitance to digital readout circuit                                   | 90 |

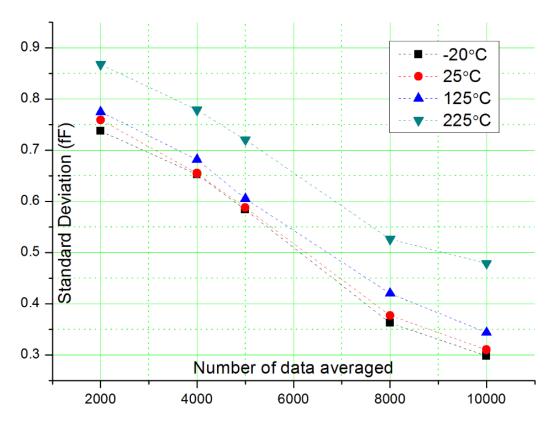

| Figure 5.6 Standard deviation of C <sub>2</sub> versus temperatures                               | 92 |

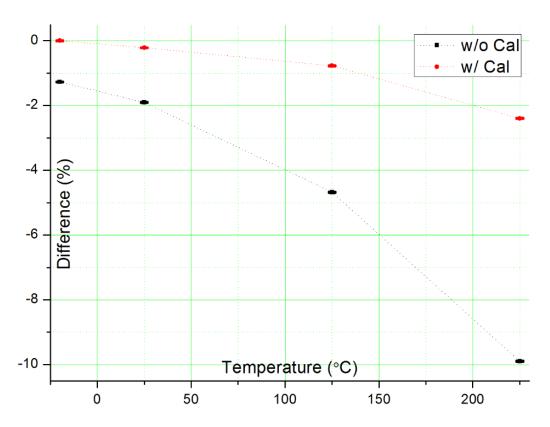

| Figure 5.7 Measurement errors versus temperatures                                                 | 93 |

| Figure 5.8 Measured response of the capacitance to digital readout circuit with a MEMS            |    |

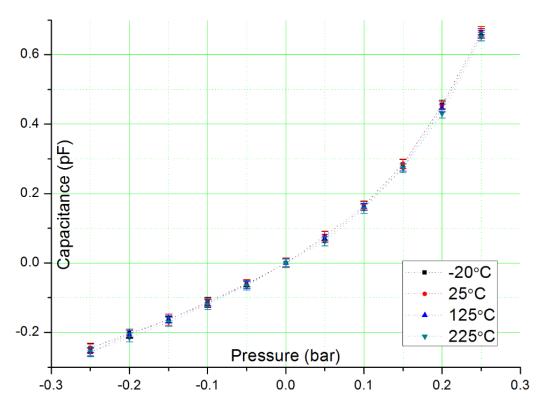

| capacitive pressure sensor                                                                        | 94 |

## LIST OF TABLES

| Table 1.1 Comparison of various sensors (taken from [11])                               | 12 |

|-----------------------------------------------------------------------------------------|----|

| Table 1.2 Temperature range for typical wide-temperature applications (taken from [46]) | 16 |

| Table 5.1 Overview of the capacitance to digital readout circuit                        | 93 |

## **PUBLICATIONS**

#### **JOURNAL PUBLICATIONS:**

- Y. Wang, V. P. Chodavarapu, "Differential Wide Temperature Range CMOS Interface Circuit for Capacitive MEMS Pressure Sensors", Sensors, vol. 15, iss. 2, pp. 4253-4263, 2015.

- Y. Wang, V. P. Chodavarapu, "Wide-Temperature Range CMOS Capacitance to Digital Convertor for MEMS Pressure Sensors", Sensors and Actuators: A Physical, vol. 233, pp. 302-309, 2015.

#### **CONFERENCE PUBLICATIONS:**

- **Y. Wang**, V. P. Chodavarapu, "Design of a sigma-delta modulator in standard CMOS process for wide-temperature applications", Proceedings of IEEE 2015 16<sup>th</sup> International Symposium on Quality Electronic Design (ISQED), Santa Clara, California, March 2015.

- Y. Wang, V. P. Chodavarapu, "High-Temperature General Purpose Operational Amplifier in IBM 0.13μm CMOS Process", Proceedings of IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Chengdu, China, June 2014.

- **Y. Wang**, V. P. Chodavarapu, "Design of a CMOS Readout Circuit for Wide-Temperature Range Capacitive MEMS Sensors", Proceedings of IEEE 2014 15<sup>th</sup> International Symposium on Quality Electronic Design (ISQED), Santa Clara, California, March 2014.

- A. Merdassi, **Y. Wang**, G. Xereas and V. P. Chodavarapu, "Design and fabrication of 3-axis accelerometer sensor system for harsh environment applications using semi-custom process", Proceedings of SPIE MOEMS-MEMS Conference, San Francisco, Feb 2014.

- Y. Wang, V. P. Chodavarapu, "Design of CMOS Capacitance to Frequency Converter for High-Temperature MEMS Sensors", Proceedings of IEEE Sensors Conference, Baltimore, November 2013.

**Y. Wang**, C. Allen, S. AL-Qahtani, A. Merdassi, V. P. Chodavarapu, E. Harvey, and J. Henderson, "Towards Wireless Implantable Pressure Sensor to Monitor Compartment Syndrome in Trauma Victims", Proceedings of NanoTech Conference, Washington DC, May 2013.

## **CONTRIBUTIONS OF AUTHORS**

This thesis is based on four published manuscripts. The candidate, Yucai Wang, is the primary author for all these manuscripts.

Chapter 2 is based on the published paper entitled "High-Temperature General Purpose Operational Amplifier in IBM 0.13µm CMOS Process", Proceedings of IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Chengdu, China, June 2014.

Chapter 3 is based on the published paper entitled "Differential Wide Temperature Range CMOS Interface Circuit for Capacitive MEMS Pressure Sensors", Sensors, vol. 15, iss. 2, pp. 4253-4263, 2015.

Chapter 4 is based on the published paper entitled "Design of CMOS Capacitance to Frequency Converter for High-Temperature MEMS Sensors", Proceedings of IEEE Sensors Conference, Baltimore, November 2013.

Chapter 5 is based on the published paper entitled "Wide-Temperature Range CMOS Capacitance to Digital Convertor for MEMS Pressure Sensors", Sensors and Actuators: A Physical, vol. 233, pp. 302-309, 2015.

## **CHAPTER 1 INTRODUCTION**

#### 1.1 Introduction to MEMS

#### 1.1.1 Brief History of MEMS

Microelectromechanical systems (MEMS), also referred to as microsystems technology (MST) or micromachines in different countries, are micro devices or systems which integrate electrical and mechanical components. They are fabricated using methods similar to integrated circuit (IC) batch-processing technologies and their physical dimensions can range from several tens of nanometers to several hundreds of millimeters [1]. Most MEMS have at least one mechanical element that is either movable or immovable, such as beams, cantilevers, springs, gears, membranes, channels, holes, cavities, valves, and other structures.

Starting in late 1950s and early 1960s, MEMS began to evolve when several pioneering researchers began to make micromechanical devices using microfabrication technology developed for the IC industry [2]. Piezoresistive effect was discovered in germanium and silicon and strain gauges based on that property began to be commercialized in 1958 [3]. The resonant gate transistor (RGT), a new type of transistor which was the earliest demonstration of microelectrostatic actuators, was developed in 1967 [4]. In the 1970s, diaphragm-type silicon pressure sensor was developed at the IBM research laboratory. In 1978, Hewlett-Packard developed the thermal inkjet technology where MEMS technology is used to manufacture arrays of inkjet printer nozzles. Around 1982, the term "micromachining" was introduced to name the fabrication of micromechanical sensors. In the late 1980s, researchers in the micromachining

field mainly used silicon (single-crystalline bulk silicon or thin film polycrystalline silicon) as processing material. The use of thin film silicon led to development of surface micromachining technology. In 1989, researchers at the University of California at Berkeley demonstrated the first silicon micromachined rotary micromotor driven by electrostatic forces [5]. By 1990s, the term "microelectromechanical systems (MEMS)" gained international acceptance as MEMS entered an era of tremendous growth. A number of MEMS devices became commercially successful, including the ADXL series accelerometers by Analog Devices Inc. for airbag deployment [6] and the digital light processing (DLP) chip by Texas Instruments Inc. for digital optical projector [7, 8]. From that period, many new MEMS spin-off branches emerged, including optical MEMS, BioMEMS, microfluidics, radio frequency (RF) MEMS, and Nano Electromechanical Systems (NEMS). A mature and sustainable MEMS ecosystem has been formed and the MEMS market is rapidly growing every year. In 2013, the annual MEMS revenue is 12 billion US\$, and it is expected to reach 22 billion US\$ by 2018 [9]. The top five players in MEMS industry in 2013 are Robert Bosch, STMicroelectronics, Texas Instruments, Hewlett-Packard, and Knowles. The top five applications are pressure sensors, accelerometers, digital compass, inkjet heads, and microfluidics [10].

MEMS devices now play an important role in our society and are ubiquitous in almost every aspect of our daily lives. We can find them in automobiles (accelerometers for crash detection and air-bag deployment, pressure sensors for tire pressure monitoring, chemical sensors for exhaust analysis), smartphones (accelerometers for automatic screen rotation, fingerprint sensors for identification, microphones for detecting audio signals), telecommunication systems (radio frequency switches for wireless communication, micromirrors for fiber optic switching), digital optical projectors (arrays of micromirrors for high definition optical displays), GPS navigation

systems (accelerometers and gyroscopes for orientation and rotation detection), inkjet printers (printer nozzles to eject ink droplets), biomedical applications (pressure sensors to monitor blood pressure and microprobes to record neural electropotentials).

#### 1.1.2 ADVANTAGES OF MEMS

While they can perform most of the same tasks as their macroscopic counterparts, MEMS devices offer three distinct advantages; First and foremost is miniaturization, the typical physical dimensions of MEMS devices range from micrometers to millimeters. Their small sizes allow miniaturization applications to be developed which are bulky when implemented using conventional sensors. For example, it is impractical to integrate bulky mechanical accelerometers, gyroscopes (with feature sizes of at least several centimeters) with smartphones and cameras. Also, due to their small sizes, MEMS devices require smaller amount of materials to produce, therefore making them less expensive than macroscopic devices. Moreover, small sizes offer other performance advantages including, higher accuracy, sensitivity, and resolution [11].

Ease of integration with microelectronics is another advantage of MEMS devices. Because they are fabricated with similar processes used in integrated circuit fabrication, MEMS devices can be readily integrated with microelectronic circuits which are used to control MEMS devices or process output signals from them, forming standalone monolithic microsystems. Systems integration can significantly reduce the length of signal path and wiring complexity, hence it offers improved signal quality and system reliability. A typical example of system integration of MEMS and microelectronics is the DLP chip by Texas Instruments, where more than 2 million micromirrors arranged in 11.93 mm diagonal array are controlled individually for 1920×1080

resolution [12], with each mirror controlled by a microelectronic circuit buried directly underneath. It would be impractical to separately address mirrors in such a large and dense array without monolithic integration with microelectronics.

Last but not least, MEMS devices can be batch fabricated with accurate dimension and good uniformity control guaranteed by lithographic processing. Many two or three dimensional microstructures, such as cantilevers, beams, membranes, inverted pyramid cavities, springs, gears, channels, through-wafer holes, and high aspect ratio trenches, can be made with combination of bulk micromachining, surface micromachining, and micromolding methods. As thousands of MEMS devices can be fabricated in the same time, batch fabrication can significantly reduce the cost of fabrication. As a result, the price of MEMS devices is much cheaper than their macro scale counterparts. It is one of the most important reasons why MEMS have gained unprecedented commercial success.

#### 1.2 EXAMPLES OF MEMS SENSORS

Most MEMS devices can be categorized as being either a sensor or an actuator. A sensor is a device which can detect or measure a physical quantity, property or condition such as pressure, temperature, light, and heat. An actuator is a device which can produce mechanical motion, force, or control a system. For example, an accelerometer is a sensor which measures mechanical acceleration and converts it to an output electronic signal. The DLP chip by Texas Instruments is an actuator which moves micromirrors under the control of electrical signals. Sensors and actuators are collectively called transducers, which convert power from one energy domain to

another. Energy domains include (but are not limited to) electrical, mechanical, chemical, radioactive, optical, magnetic, acoustic, and thermal [11].

Based on the principles of operation, MEMS sensors can be generally classified into the following categories:

Capacitive sensor: A capacitor is formed when two overlapping conductors are separated by a nonconductive material. Capacitance characterizes the ability of the capacitor to store an electrical charge and it is determined by the overlapping area and the gap size between the two conductors, and the permittivity of the nonconductive material in the gap. The capacitance will change when any of the above three parameters is changed by an applied stimulus, such as acceleration or pressure. By measuring the capacitance value, we can quantify the applied stimulus. Capacitive sensors can be used to measure acceleration, pressure, position or displacement, proximity, and humidity. Capacitive sensors often have static capacitance values on the order of picofarads (pF) and the capacitance change caused by an applied stimulus is

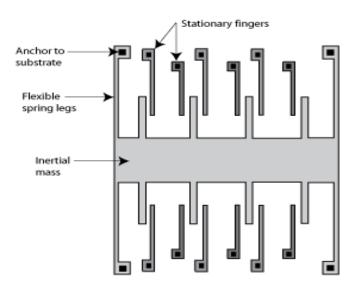

**Figure 1.1** A schematic of a capacitive MEMS accelerometer ( taken from [13])

usually on the order of femtofarads (fF). High resolution electronic circuits are needed to register such small capacitance changes. Figure 1.1 shows the schematic of a capacitive MEMS accelerometer. The applied acceleration causes a displacement of the inertial mass and changes the capacitance between the stationary and moving comb fingers.

Resistive sensor: The resistance R of a conductor is determined by its resistivity, length, and cross-sectional area. In resistive sensors, a material's resistance is changed by the applied stimulus and this resistance change is often detected using a circuit configuration called the Wheatstone bridge. Usually a piezoresistive material is used where its resistivity can be changed by an external applied force. Most materials have piezoresistive property, but it is particularly evident in some semiconductors like doped silicon. Piezoresistive sensors provide an easy and direct signal converting mechanism between the mechanical and electrical domains and they are widely used to measure physical quantities including acceleration, pressure, force, and flow rate. Some materials' resistance changes under a magnetic field. These magnetoresistive materials are used to build resistive sensors to measure magnetic field. Heating can also change a material's

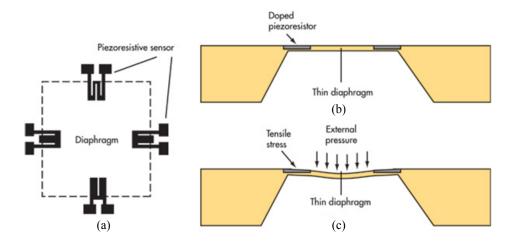

**Figure 1.2** Schematic of a piezoresistive MEMS pressure sensor. (a) top view (b) side view without applied pressure (c) side view with external pressure. (taken from [14])

resistance and some materials highly sensitive to heat are used to make temperature sensors [15]. Figure 1.2 shows the schematic of a piezoresistive MEMS pressure sensor. The external pressure causes a tensile stress on the thin silicon membrane and it changes the resistance of the piezoresistors on the membrane's surface.

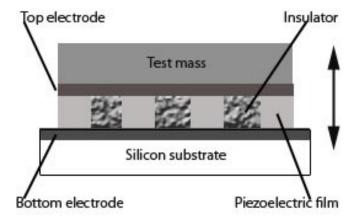

Piezoelectric sensor: Some materials can generate an electrical charge (or voltage) when an external force is applied. This is known as piezoelectric effect. When a piezoelectric material is pressed, positive ions get accumulated on the pressed side, and negative ions become more concentrated on the opposite side. The commonly used piezoelectric materials are quartz, lead zirconate titanate (PZT), polyvinylidene difluoride (PVDF), and zinc oxide (ZnO). Electrodes are placed on the piezoelectric material to collect the charge. As the piezoelectric materials are nonconductive, this configuration forms a capacitor where the piezoelectric materials are located in the gap between the two electrodes. The voltage between the electrodes can be measured by placing a charge amplifier before the subsequent measurement system. Piezoelectric sensors are used to measure physical quantities including acceleration, pressure, force, strain, flow rate, and temperature. Figure 1.3 shows the schematic of a piezoelectric MEMS accelerometer. A thin

**Figure 1.3** Schematic of a piezoelectric MEMS accelerometer (taken from [16])

piezoelectric film is placed between a test mass and a silicon substrate. When an acceleration is applied along its sensitive axis (marked using the arrow in Figure 1.3), the piezoelectric film is subject to stress due to coupling to the test mass and electrical charge is generated and can be converted to a voltage output.

Resonant sensor: At certain frequencies, a system vibrates with abnormally large amplitude than at other frequencies. This phenomenon is called resonance and the frequencies are called resonance frequencies. Resonant sensor, which contains a mechanical structure (called resonator) such as a beam that vibrates with small displacements, is based on the principle of resonance. The resonance frequency is determined by the mass, stiffness, and damping of the resonator. In resonant sensor, the physical quantities to be measured, such as pressure and acceleration, impose a strain on the resonator and change its stiffness. As a result, the resonance frequency of the sensor also changes in accordance with the physical quantities. In the application of sensing a magnetic field, the resonance frequency of the resonator is fixed and the amplitude of the vibration changes with the magnitude of the magnetic field. By measuring the resonance frequency or vibration magnitude, the physical quantities can be quantified. Figure 1.4 shows the

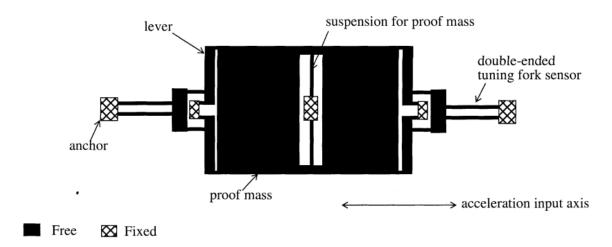

Figure 1.4 Schematic of a MEMS resonant accelerometer (taken from [17])

schematic of a MEMS resonant accelerometer. In this device, the tuning forks are actuated at resonant frequency using lateral comb drives and the resonance is maintained by incorporating the mechanical structure in the feedback loop of an oscillator circuit [17]. When an external acceleration is applied to the proof mass along the sensitive axis (marked using the arrow in Figure 1.4), a force is generated axially onto the double-ended tuning fork sensors, resulting in a shift in the resonant frequency of the double-ended tuning fork sensors.

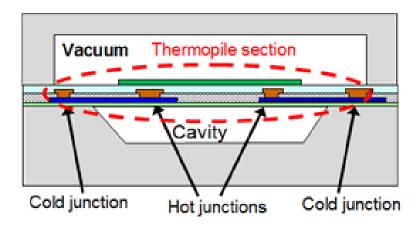

Thermoelectric sensor: For some materials, an electric voltage will be generated when a temperature difference is applied between the two points and the materials are called thermoelectric materials. This effect is called thermoelectric effect and it is the basis of the thermoelectric sensors. A thermocouple is a typical thermoelectric sensor which is used to measure temperature. It is built with two dissimilar thermoelectric materials which connect each other at their endpoints. When the temperature at one endpoint is different from the reference temperature at the other endpoint, a voltage output will be produced, which is determined by the two thermoelectric materials and the temperature difference between the two endpoints. In case of larger output voltage is desired, several thermocouple pairs can be connected in series to build

**Figure 1.5** Schematic of a MEMS thermal sensor (taken from [18])

a thermopile, which is primarily used to measure temperature and infrared radiation. Thermoelectrical sensors can be used to measure physical quantities including pressure, acceleration, position, flow rate, and displacement. Figure 1.5 shows the cross-section view of a MEMS thermal sensor. Thermopiles are constructed by serial connection of thermocouples consisting of N+ poly silicon and P+ poly silicon. Hot junctions are created on highly-resistant dielectric membranes and cold junctions are created on highly heat-conductive silicon [18]. The thermopiles are sealed in a vacuum to prevent the heat from dissipating into the air hence increasing sensitivity.

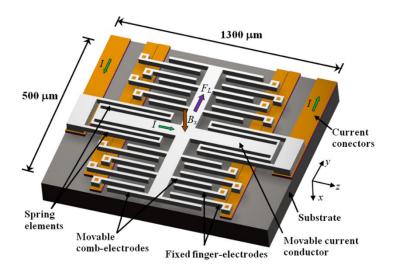

**Magnetic sensor**: Magnetic sensors use either reluctance sensing or inductive sensing principles. Reluctance is the inverse of permeance, which is used to describe magnetic field energy storage. The equation Q=CV is used for capacitive energy storage, where Q is the charge, C is capacitance, and V is voltage. Analogously, the equation  $\Phi$ =PM is used for magnetic field energy storage, where  $\Phi$  is magnetic flux, P is permeance, and M is magnetomotance (also called magnetomotive force). Similar to capacitance of a parallel plate capacitor, the value of

Figure 1.6 Schematic of a MEMS resonant magnetic field sensor (taken from [19])

permeance (and reluctance) is determined by the overlap area, the gap size, and magnetic permeability of the material in the gap. When a physical quantity (pressure or displacement) causes any of the three parameters changes, the magnetomotive force changes accordingly and it can be measured by the current it induces in a coil. If a physical quantity causes a conductive coil to move in a magnetic field, a current will be induced in the coil. The current can be measured to represent the input physical quantity. This is the underlying principle of inductive sensing [15]. Figure 1.6 shows the schematic of a MEMS resonant magnetic field sensor which contains a large movable conducting microbeam, movable comb electrodes and fixed finger electrodes. A Lorentz force ( $F_L$ ) is generated when an ac current (I) flows through the conducting beam under the presence of an external magnetic field ( $B_x$ ) [19]. As a result, the distance between the movable electrodes and the fixed electrodes is changed and the capacitance between them is changed consequently. The magnetic field can be measured by quantifying the capacitance variation.

Many physical quantities can be measured using more than one sensing principle. For example, pressure can be measured using all the above mentioned sensing principles. Sensor developers must assess the different sensing principles according to their performance characterizations and practicality characterizations to select the best sensing principle for a particular application. Performance characterizations describe sensor's technical performance, including but not limited to sensitivity, linearity, resolution, signal-to-noise ratio, dynamic range, bandwidth, drift, reliability, repeatability, cross-sensitivity, temperature stability, and response time [11]. Practicality characterizations refer to the feasibility to suit a sensor into a specific application, including but not limited to size, weight, sensing material, fabrication method, yield, cost, power consumption, manufacturing ease, packaging compatibility, robustness, and

intellectual property rights. Table 1.1 compares the advantages and disadvantages of four types of most commonly used sensors.

**Table 1.1** Comparison of various sensors (taken from [11])

| Sensors                  | Advantages                                                                            | Disadvantages                                                                                                                                          |

|--------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capacitive sensor        | Simplicity of materials     Low-voltage, low-current     operation     Rapid response | Large footprint of device necessary to<br>provide sufficient capacitance     Complexity of readout electronics     Sensitive to particles and humidity |

| Thermal sensor           | Simplicity of materials     Elimination of moving parts                               | Relatively large power consumption     Generally slower response than capacitive sensing                                                               |

| Piezoresistive<br>sensor | High sensitivity achievable     Simplicity of materials     (metal strain gauge)      | Requires doping of silicon to achieve high performance piezoresistors     Sensitive to environmental temperature changes                               |

| Piezoelectric<br>sensor  | Self generating-no power necessary                                                    | Complex material growth and process flow     Cannot sustain high-temperature operations                                                                |

## 1.3 MEMS SENSORS FOR WIDE-TEMPERATURE APPLICATIONS

In recent years, there is an increasing demand for the development of MEMS sensors capable of sustained operation at wide temperature range well beyond the military temperature specification (-55 °C to 125 °C) [20]. In particular, high operating temperatures can either result from high ambient temperature or due to difficulties of effective heat removal for high power dissipation. Typical high-temperature applications are found in automobile industry, oil and gas exploration, aerospace, and industrial process control, where different kinds of MEMS sensors are widely used to improve system performance, reliability, and reduce cost.

The automobile industry is considered the largest market for high-temperature MEMS sensors. Since 1970s, governments have been applying regulations mandating emissions control and fuel economy. These complex regulations could not be achieved using traditional mechanical systems, driving the automobile industry to migrate from purely mechanical system to MEMS sensor systems [21, 22]. As a result, a variety of MEMS sensors are being introduced in automobiles to help optimize engine operation, reduce emissions of exhaust pollutants, provide better fuel economy and enhance safety, comfort and convenience. The number of MEMS sensors used for engine control applications have increased from around ten in 1995 to more than thirty in 2010 [23]. Under the hood of an automobile, temperature is usually beyond 150 °C, and can even reach 200 °C [21, 24], depending on the specific location on the engine block or the exhaust system. Moreover, the trend towards hybrid electrical vehicles is driving MEMS sensors into even harsher environments, such as on or near the brakes, where temperatures can go up to 250 °C [25].

The oil and gas industry is another large user of high-temperature MEMS sensors, where sensors are extensively used to steer the drilling equipment and log the surrounding geologic information in oil, gas and geothermal wells. The parameters logged include temperature, pressure, flow rate, density, resistivity and chemical composition. These data enable the geologists to optimize the productivity of the well and, in extreme situation, prevent the well from being completely blocked [26]. In such applications, the operating temperature increases as the well goes deeper, with a typical geothermal gradient 25 °C per km of depth [27]. Currently, most deep-well drilling operation temperature is not over 200 °C [28]. As the easily accessible natural resources are being depleted, wells must go deeper, where operation temperature can reach up to 400 °C [29].

The aerospace industry now has a growing demand toward the high-temperature MEMS sensors. The main driving force is the desire for reduced weight, improved system performance and reliability. Conventionally sensors are used only in limited locations on engines to monitor propulsion component, and their use usually involve certain active and passive cooling techniques [30]. With high-temperature MEMS sensors, they can be used both sensing around the engine casing and in the hottest parts of the engine itself, where the temperature is 500 °C to 600 °C [31]. Improved combustor control offers substantial fuel saving and decreased engine emissions. Without the need for necessary peripheral cooling systems, high- temperature MEMS sensors enable significant reduction in weight, size and cost.

Currently most wide-temperature MEMS sensors use principles of capacitive sensing, piezoelectric sensing, and piezoresistive sensing [32-39]. As mentioned in Table 1.1, the piezoresistive coefficient of piezoresistive sensors has inherent temperature dependence and it has to be compensated. For piezoelectric sensors, as the operating temperature increases, piezoelectric effect of a piezoelectric material decreases, and ultimately complete and permanent depolarization will occur. Capacitive MEMS sensors are preferred in many of the wide-temperature applications because the physical quantities to be measured can be converted to an electrical signal by a capacitor placed in vacuum, which has no inherent temperature dependence [40]. Capacitive sensors also have other advantages including low thermal drift, good reliability, high accuracy and sensitivity, good noise performance, and low power consumption [41, 42].

### 1.4 Interface Electronics for Wide-Temperature MEMS Sensors

Sensor interface electronics are indispensable to MEMS sensors which provide power supply to the sensor, convert the sense signal to an electrical signal (usually a voltage or current), condition and digitize the electrical signal for easy transfer and storage. In wide-temperature range applications, the conventional sensor interface electronics will fail to work properly or their performance will degrade. Traditionally, these electronics had to be remotely placed in a cooler region or they must be actively or passively cooled, which inevitably introduce additional overhead in the form of longer wires, additional connectors, and/or bulky cooling system, resulting increased size, weight, complexity and accordingly increased potential for failure to the system [27, 43, 44]. Moreover, in some applications, due to constraint of size and weight, cooling is not a feasible option. Hence, it is more favorable for the interface electronics to reside in close proximity to sensors to reduce noise, interference, wiring complexity, system size, production cost, and improve system reliability [45]. For example, in automobile applications, sensor interface electronics are placed in the engine compartment to improve fuel economy, and reduce exhaust emission. In oil and gas exploration, electronics are mounted in deep bores to acquire data about the surrounding geologic formations and thereby identify possible oil or gas deposits. In modern aircrafts, electronics are placed near the engine and braking system to reduce component weight, cost and wiring complexity, and improve performance and reliability. In such wide-temperature applications, the sensor interface electronics must be subject to the same operating temperature as the MEMS sensors. Table 1.2 summarizes the operating temperature ranges for typical high temperature applications. As can be seen, the operating temperatures of a majority of applications are between -55 °C to 225 °C. For such wide temperature range, the

design of sensor interface electronics is challenging and requires special design considerations, especially at the high temperature end.

**Table 1.2** Temperature range for typical wide-temperature applications (taken from [46])

| Applications           |                  | Temperature Range (°C) |

|------------------------|------------------|------------------------|

|                        | Compartment      | -40 ~ 85               |

| Automotive Industry    | Engine/Gear Box  | -40 ~165               |

|                        | Brakes           | -40 ~250               |

|                        | Aircraft Surface | -40 ~80                |

| Avionics               | Engine Intake    | <b>-</b> 40 ∼185       |

|                        | Jet Engine       | -40 ~320               |

| Satellites             |                  | -150 ~ 200             |

| Space Exploration      |                  | -150 ~450              |

| Oil Exploration        |                  | <b>-</b> 40 ∼175       |

| Geothermal Exploration | 1                | <b>-</b> 40 ∼ 320      |

Most electronics fabricated today use bulk Complementary Metal-Oxide-Semiconductor (CMOS) processes, which offers numerous advantages including low power consumption, low fabrication cost, easy of technology scaling, and the ability to integrate analog and digital blocks on the same chip and thereby reducing the chip size. However, conventional electronics made in bulk CMOS technology suffer from many drawbacks at high temperatures, including degradations in electron/holes mobility, reduction in MOS transistors threshold voltage, increase of bulk junction leakage currents [47, 48], and increase in silicon intrinsic carrier density [49]. Among which, mobility reduction, threshold voltage drop are inherit to the physics of silicon material and field-effect transistor. Excess junction leakage current at high temperature is the

most harmful for bulk CMOS circuits, which can increase self-heating, shift analog operation points, reduce open loop gain and bandwidth of amplifier, increase offset, erase charge stored at dynamic node, and even cause chip failure due to latch-up [45]. The silicon intrinsic carrier density is comparable to doping level at temperature beyond 300 °C, which imposes the theoretical temperature upper limit for CMOS technology [49].

Fabricating circuits using silicon-on-insulator (SOI) technology can effectively address junction leakage current problem as the buried insulator layer in the SOI structure eliminate the p-n junction diodes between the source/drain and substrate/well. SOI technology also offers better latch-up immunity [50]. And circuit designs in CMOS technology can be easily migrated to SOI CMOS technology. SOI technology has been proven effective to extend operating temperature of electronics to 300 °C [51-54]. However, the threshold voltage drop and carrier mobility decrease at high temperatures which are innate to silicon still limit the circuits performance, and analog circuits in SOI technology have reduced performance due to hysteresis in the I-V characteristics of MOS transistors [49]. Furthermore, SOI technology is much more expensive than CMOS technology and is available from fewer suppliers [49].

Wide bandgap semiconductors such as silicon carbide (SiC) [55-58] and gallium nitride (GaN) [59] are promising materials for high temperature electronics which extends the operating temperature up to 600 °C [55, 57]. But they share the same cost problem with SOI technology and the fabrication processing is yet maturely developed. Further, reliable and durable interconnecting and packaging technologies are needed for electronics built of wide bandgap semiconductors to work at high temperature.

In recent years, various design techniques were developed to mitigate the aforementioned high temperature induced effects in bulk CMOS technology. Monolithic bulk CMOS circuits, including logic gates, memories, oscillators, amplifiers, and analog-to-digital convertors (ADC), have been demonstrated functional at temperatures beyond 200 °C [60-67]. Many of these previous works used technology with feature sizes of 1.5 µm and more and power supplies of 5 V. As the feature size of CMOS process continues to scale down, it is desirable to take advantage of process with smaller feature size for the benefits of low cost, low power consumption and high level of integration.

Many research groups have previously implemented high temperature interface circuits for piezoresistive and piezoelectric MEMS sensors. In 2000, Jong *et al.* [68] reported a high-temperature pressure-transducer interface for piezoresistive pressure sensors. This interface circuit uses an instrumentation amplifier with continuous auto-calibration and dynamic feedback and it can operate at temperatures up to 250-275 °C with 15-16 bit accuracy [61]. In 2006, Yu *et al.* [45] reported a high-temperature bulk CMOS data acquisition system for piezoresistive Wheatstone-bridge sensors which can operate at temperature up to 300 °C. In 2006, Levinzon [69] reported a silicon base hybrid charge amplifier for miniature piezoelectric accelerometer which can operate over temperature range from -55°C to 175°C. However, there are no available wide temperature range CMOS sensor interface circuits for capacitive MEMS sensors implemented to date. Further, commercially available capacitance readout circuits that interface with MEMS sensors from Analog Devices Inc. (Model: AD7152) [70] and ISC8 Inc. (Model: MS3110) [71] work only between the commercial temperature range from -40 °C to 85 °C.

The goal of this thesis is to develop various sensor interface circuits for capacitive MEMS sensors in IBM 0.13 µm bulk CMOS process which incorporates a 2.5 V power supply and

which can operate at temperature range between -55 °C to 225 °C. For wide temperature range from -55 °C to 225 °C, several key device parameters, including intrinsic carrier concentration, carrier mobility, threshold voltage, and junction leakage current, vary with temperature and limit the high temperature operation of CMOS devices and circuits. They must be properly investigated and accounted for before the circuit design. These key device parameters are studied in Section 1.5 shown below.

#### 1.5 CHALLENGES FOR WIDE-TEMPERATURE CMOS CIRCUITS DESIGN

#### 1.5.1 Intrinsic Carrier Concentration

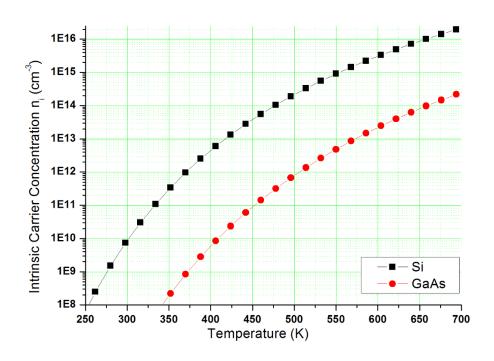

The concentration of intrinsic carrier  $n_i$  of a semiconductor is dependent upon the temperature and can be expressed by Equation (1.1) [72],

$$n_i(T) = \sqrt{N_C N_V} e^{-E_g/2kT}$$

(1.1)

where,  $N_C$  is the effective density of states for electrons in the conduction band,  $N_V$  is the effective density of states for holes in the valence band,  $E_g$  is the energy bandgap of the semiconductor, T is the temperature in Kelvin, and k is the Boltzmann constant (8.62×10<sup>-5</sup> eV/K). Most semiconductor devices create sufficient local free carrier concentration in excess of the thermal intrinsic carrier  $n_i$  through intentional introduction of impurities using doping process, and the typical doing level in CMOS process is between  $10^{14}$  to  $10^{18}$  atoms per cubic cm (cm<sup>-3</sup>). Maintaining the local free carrier concentration sufficiently larger than the intrinsic carrier  $n_i$  is vital to operation of any semiconductor device. In CMOS devices operating at room temperature, the dopant is fully ionized and the local free carrier concentration is almost equal to the doping level. Figure 1.7 shows the intrinsic carriers concentration  $n_i$  of silicon bandgap=1.12 eV at 300

K) versus temperature, calculated from Equation (1.1). The intrinsic carriers concentration of gallium arsenide (GaAs) (bandgap=1.42 eV at 300 K) is also shown for comparison. The Eg,  $N_C$ , and  $N_V$  of silicon have much less temperature dependence as compared with the temperature exponential term (-Eg/2kT) of Equation (1.1). Their temperature dependence is also taken into account in Figure 1.7. The detailed equations about the temperature dependence of Eg,  $N_C$ , and  $N_V$  can be found in [73]. From Figure 1.7, the silicon intrinsic carrier concentration at room temperature (300 K) is around  $10^{10}$  cm<sup>-3</sup>, which is negligible to the CMOS process doping levels ( $10^{14}$  to  $10^{18}$  cm<sup>-3</sup>). However, as the ambient temperature increases beyond 600 K, the silicon intrinsic carrier concentration is more than  $10^{15}$  cm<sup>-3</sup> and it is comparable to the device lighter doping level. Hence, the designed doping profile at lighter doping region of a given silicon device will be undesirably affected by the intrinsic carriers and the device performance will

**Figure 1.7** Intrinsic carrier concentration  $(n_i)$  of Si and GaAs versus temperature

inevitably deteriorate. The intrinsic carrier density dependence on temperature imposes an insurmountable theoretical limit for silicon devices to operate beyond 300 °C. From Equation (1.1) it can be seen that at the same temperature, the intrinsic carrier density is much lower for a semiconductor with larger energy bandgap  $E_g$ . This explains why wide bandgap materials like silicon carbide (SiC) and gallium nitride (GaN) with bandgaps around 3 eV are desirable for operation above 300 °C.

### 1.5.2 CARRIER MOBILITY

In the absence of an electrical field, free carriers (electrons and holes) in the semiconductor randomly move inside it and frequently change direction. When an electrical field E is applied across the semiconductor, the free carriers are subject to an electrostatic force F (F = -qE, q is the carrier charge) and electrons will move against the direction of electrical field, while holes will move following the direction of electrical field. The carriers acquire momentum under the electrostatic force F and will lose it when they are scattered after a period of  $\tau_c$ , which is called mean free time and defined as the average time between the scattering events. According to the law of momentum conservation, the average velocity  $\nu$  of the carriers during  $\tau_c$  can be obtained by Equation (1.2) [73],

$$-qE\tau_c = mv \quad (1.2)$$

where, m is mass of the carriers. The mobility  $\mu$  of the carrier is defined as the ratio of the velocity to the electrical field and given by Equation (1.3) [73],

$$\mu = \frac{q\tau_c}{m} \quad (1.3)$$

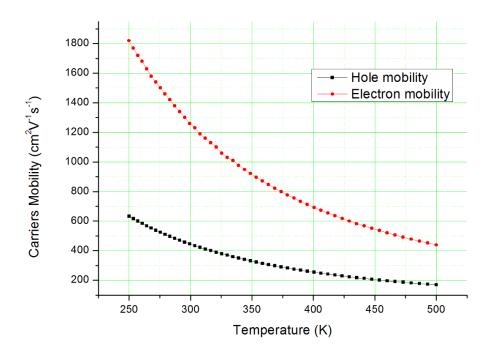

The mean free time  $\tau_c$  is affected by two scattering mechanisms: lattice scattering and impurity scattering. Lattice scattering is the scattering of carriers by lattice waves and includes the absorption or emission of phonons. The density of phonons in a semiconductor increases with temperature and the mean free time  $\tau_c$  will decrease. As a result, the mobility will decrease with a temperature dependence of  $T^{-3/2}$  [72]. Impurity scattering is the scattering of carriers by impurity atoms (such as ionized donors and acceptors) in the semiconductor. It depends on the velocity of the carriers and the concentration of the impurity atoms. Higher impurity concentration leads to a lower carrier mobility. When temperature increases, the velocity of carriers increases and the amount of scattering decreases, causing a mobility increase with temperature dependence of  $T^{3/2}$  [72]. The effect of impurity scattering becomes less significant compared to lattice scattering above certain temperature value, and the overall temperature effect cause carriers mobility to decrease as temperature increases. The temperature dependence of the carrier mobility can be expressed using a simplified model given by Equation (1.4) [74],

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{-1.5}$$

(1.4)

where,  $\mu(T_0)$  is the carrier mobility value at reference temperature  $T_0$ . Figure 1.8 shows the electron and hole mobility of silicon at different temperatures for doping level of  $10^{16}$  cm<sup>-3</sup> (data taken from [75]). As can be seen, from room temperature (300 K) to 500 K, the electron and hole mobility values reduce about by half.

Figure 1.8 Carriers (electron and hole) mobility of silicon versus temperature

## 1.5.3 THRESHOLD VOLTAGE

The threshold voltage  $V_T$  of a long-channel MOSFET (metal-oxide-semiconductor field-effect transistor) with 0 V substrate bias is given by Equation (1.5) [72],

$$V_{T0} = \phi_{ms} - \frac{Q_f}{C_{ox}} \pm 2\phi_F \pm \frac{\sqrt{4q\varepsilon_{si}N_{sub}\phi_F}}{C_{ox}}$$

(1.5)

where, + sign is for NMOS and - sign is for PMOS.  $Q_f$  is the fixed oxide charges due to surface states which may arise from dangling bonds at the oxide silicon interface.  $C_{ox}$  is the gate capacitance per unit area, q is the electronic charge,  $N_{sub}$  is the substrate doping concentration,  $\phi_F$  is the Fermi potential of the substrate and it is given by Equation (1.6) [72],

$$\phi_F = \frac{kT}{q} \ln(\frac{N_{sub}}{n_i}) \tag{1.6}$$

And  $\phi_{ms}$  is the work function difference between the gate material and substrate, which can be expressed by Equations (1.7) and (1.8) [45],

$$\phi_{ms} = -\frac{kT}{q} \ln(\frac{N_{sub}N_g}{n_i^2})$$

(for NMOS) (1.7)

$$\phi_{ms} = -\frac{kT}{q} \ln(\frac{N_g}{N_{sub}})$$

(for PMOS) (1.8)

where, N<sub>g</sub> is the gate doping level.

When a voltage  $V_{sb}$  is applied between the source and substrate, the threshold voltage can be expressed by Equation (1.9),

$$V_{T} = V_{T0} + \gamma_{n,p} \left[ \sqrt{2\phi_{F} + V_{sb}} - \sqrt{2\phi_{F}} \right]$$

(1.9)

where,  $\gamma_{n,p}$  is the body effect parameter.

The temperature dependence of  $\phi_{ms}$  and  $\phi_{F}$  can be expressed by Equations (1.10), (1.11) and (1.12) [76],

$$\frac{\partial \phi_{ms}}{\partial T} = \frac{1}{T} \left( \phi_{ms} + \frac{E_g}{q} + \frac{3kT}{q} \right)$$

(for NMOS) (1.10)

$$\frac{\partial \phi_{ms}}{\partial T} = \frac{\phi_{ms}}{T} \quad \text{(for PMOS)} \quad (1.11)$$

$$\frac{\partial (2\phi_F)}{\partial T} = \frac{1}{T} \left( 2\phi_F - \frac{E_g}{q} - \frac{3kT}{q} \right) \tag{1.12}$$

The second term in Equation (1.5) has no temperature dependence, so from Equations (1.5), (1.9), (1.10), and (1.12), the temperature dependence of the threshold voltage for an NMOS transistor can be expressed as Equation (1.13) [77],

$$\frac{\partial V_T}{\partial T} = \frac{\phi_{ms}}{T} + \frac{2\phi_F}{T} + \frac{\gamma_n}{\sqrt{2\phi_F}} \frac{\partial \phi_F}{\partial T}$$

(1.13)

Numerical calculation [77] using parameters for a typical CMOS process shows that at 300 K, the first term in Equation (1.13) is -3.10 mV/°C, the second is 2.70 mV/°C, and the last term is about -0.4 mV/°C. So the overall threshold voltage temperature dependence of an NMOS transistor is -0.8 mV/°C, i.e., the threshold voltage decreases when the temperature increases.

From Equations (1.5), (1.9), (1.11), and (1.12), the temperature dependence of the threshold voltage for a PMOS transistor can be expressed as Equation (1.14) [45],

$$\frac{\partial V_T}{\partial T} = \frac{\phi_{ms}}{T} - \frac{2\phi_F}{T} - \frac{\gamma_n}{\sqrt{2\phi_F}} \frac{\partial \phi_F}{\partial T} + \frac{1}{T} \left( \frac{E_g}{q} + \frac{3kT}{q} \right) \tag{1.14}$$

At 300K, the first term in Equation (1.14) is about -0.5 mV/°C, the second is -2.70 mV/°C, the third term is about 0.4 mV/°C, and the last term is about 4.3 mV/°C. The overall threshold voltage temperature dependence of a PMOS transistor is 1.5 mV/°C, i.e. the threshold voltage increases when the temperature increases, and the threshold voltage change of PMOS is faster than NMOS. Experimental results show that the threshold voltages of NMOS and PMOS almost halve from 25 °C to 250 °C for a typical CMOS process [74].

### 1.5.4 LEAKAGE CURRENT

Two sources of leakage current exist in a MOSFET: subthreshold channel current and junction leakage current. When the gate to source voltage V<sub>GS</sub> is below the threshold voltage, the MOSFET works in its subthreshold region and its channel is weakly inverted. The subthreshold channel current of a MOSFET has strong dependence on carrier mobility and threshold voltage, and it increases exponentially with temperature. Subthreshold channel current can be reduced significantly by biasing MOSFET in strong inversion region and it is not considered in this thesis.

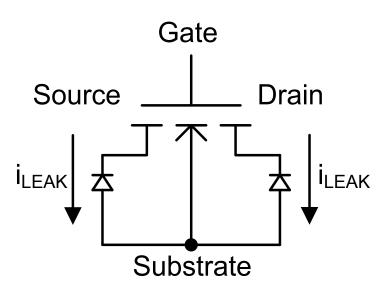

In bulk CMOS technology, P substrate is biased to most negative voltage and N well are connected to most positive voltage to form reverse biased diodes to isolate neighboring devices. Figure 1.9 shows two reverse biased diodes between the source/drain region and the P substrate. The leakage current from these diodes unfavorably limit high temperature operations of MOSFETs.

Figure 1.9 Schematic of an NMOS transistor with parasitic diodes

The junction leakage currents measured in the drain of an NMOS and a PMOS transistor is described by de Jong, *et al.* [61]. At room temperature, the leakage current is on the order of pA and is negligible with respect to the drain current in operation (usually on the order of μA). As temperature increases, electron/hole pairs are thermally generated in the depletion region and will be swept across the junction by electrical field, as a result, a drift current will flow. This drift current is proportional to the intrinsic carrier concentration and prevails at temperature up to 100-150 °C.

When temperature increases higher, minority carriers are thermally generated and diffuse away from the junction area. These carriers, which are proportional to the square of the intrinsic carrier concentration, will reach the edge of the depletion region and swept across the junction by electrical field. As a result, the diffusion current will flow and prevails at higher temperature. Because the concentration of minority carriers is inversely related to the doping concentration, PMOS transistor generally has much less leakage current than NMOS at the same temperature.

The total leakage current of a reverse biased diode, including the drift current and the diffusion current, can be expressed as Equation (1.15) [72],

$$I_{L} = I_{L,diffusion} + I_{L,drift} = qAn_{i} \left[ \frac{n_{i}}{N_{D}} \sqrt{\frac{D_{p}}{\tau}} + \frac{W}{2\tau} V_{A} \right] \left( e^{qV_{A}/kT} - 1 \right) \quad (1.15)$$

where, A is the area of the p-n junction,  $V_A$  is the voltage applied to the diode,  $N_D$  is the n-type doping level, W is the width of the junction depletion region under voltage  $V_A$ , Dp is the minority carrier diffusion constant, and  $\tau$  is the effective minority carrier lifetime. Equation (1.15) can be further simplified, assuming a negative  $V_A$  (reverse bias) greater than a few tenths of a volt and the temperature is lower than 1000 °C as given by Equation (1.16),

$$I_L = -qAn_i \left[ \frac{n_i}{N_D} \sqrt{\frac{D_p}{\tau}} + \frac{W}{2\tau} V_A \right] \quad (1.16)$$

From Equation (1.16), it can be seen that the intrinsic carrier concentration n<sub>i</sub> dominates the leakage current of a reverse biased diode. Recall from Equation (1.1) that n<sub>i</sub> has exponential temperature dependence, so the leakage current increases exponentially with temperature. As shown by de Jong, *et al.* [61], an NMOS transistor has drain leakage current of several μA at 300 °C. Excess leakage current causes adverse influence to circuits operate at high temperatures, including self-heating, shifting in the operating points in analog circuits, lowering of output resistance at high impedance nodes, loss of charge stored at dynamic nodes, latchup, and significant offset increase between matching devices [45]. Therefore, leakage current is one of the most difficult challenges to overcome in high temperature bulk CMOS circuits.

# 1.6 HIGH TEMPERATURE CIRCUIT DESIGN TECHNIQUES

Many circuit design techniques have been previously proposed to relieve the above mentioned high temperature induced effects. Notable techniques include zero temperature coefficient (ZTC) gate biasing, leakage current cancellation, and substrate biasing feedback.

As shown in Section 1.5, the threshold voltage  $V_T$  and the carrier mobility both decrease when the temperature increases. While the gate voltage is maintained constant, reduced threshold voltage leads to increased drain current, while reduced carrier mobility leads to decreased drain current. When the gate of a MOSFET is biased at a point where these two opposing effects are cancelled, the MOSFET has almost constant drain current at certain temperature range [47, 74, 77]. This gate biasing voltage is known as ZTC biasing point. The main limitations about ZTC

gate biasing are that it is highly process dependent and has poor reproducibility, it only works for a limited temperature range, and the ZTC biasing voltage is usually much larger than the threshold voltage, which leads to a large overdrive voltage and limits the output swing.

It is possible to cancel the leakage current using a matched leakage path with complementary diodes [74]. However, for the cancellation to be effective, the complementary diodes must have identical leakage current over temperature. So this method cannot work with a conventional single N-well CMOS process, where an NMOS has much larger leakage current than a PMOS at high temperature. An alternative leakage current cancellation method has been proposed where replica leakage generators are used to replace the complementary diodes. Nevertheless, this method requires leakage current matching between junctions and MOSFETs in the leakage generator to operate in the subthreshold region, which is difficult to achieve over a wide temperature range.

The threshold voltage of a MOSFET can be adjusted by applying a substrate bias voltage. So it is possible to reduce the temperature sensitivity of threshold voltage and could even be made constant over temperature by applying a proper substrate bias voltage [47]. However, this method is not applicable to the standard N-well bulk CMOS process, as all NMOS transistors are tied to the same substrate and it is difficult to apply substrate bias voltages to individual transistors considering practical and cost-effective chip sizes.

In recent years, researchers have proposed alternative techniques to design high temperature circuits using bulk CMOS process [45, 49, 60, 78]. These techniques acknowledge that the high temperature induced performance degradations will occur and it is not necessary to compensate individual devices, but use circuit architectures which are dependent on parameters (geometry,

capacitance) with little or no temperature sensitivity or on parameters (transconductance) where their temperature sensitivity can be stabilized. These high temperature circuit design techniques are summarized as follows and will be applied in the high temperature capacitance readout circuits described in this thesis.

### 1.6.1 HIGH TEMPERATURE TOLERANT CIRCUIT ARCHITECTURES

Generally speaking, single-ended circuits are more susceptible to high temperature induced noises and leakage currents, which usually appear in common mode and can be differentially rejected. Using fully-differential circuitry can effectively suppress these common mode errors and improve the circuit performance at high temperatures. The accuracy of switched-capacitor circuit mainly depends on the ratio of capacitors, which is largely insusceptible to temperature changes. Also, for circuits using sigma-delta modulating technique, the stringent requirement for high-precision analog components is relaxed due to the over-sampling principle.

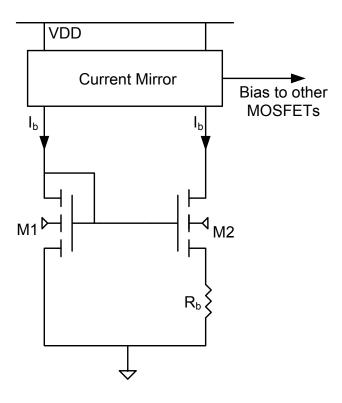

### 1.6.2 CONSTANT-GM BIASING TECHNIQUE

Transconductance (g<sub>m</sub>) is perhaps the most important parameter in CMOS analog circuits which affects gain, bandwidth, and stability of an amplifier. The constant-g<sub>m</sub> biasing technique has been proven effective to stabilize the impact of mobility degradation over wide temperature range. In the circuit shown in Figure 1.10, a current I<sub>b</sub> is generated with its magnitude inversely proportional to the carrier mobility [49]. When a MOSFET is biased using a copy of this current, its transconductance can be expressed as Equation (1.17),

$$g_{m} = \frac{2}{R_{b}} \sqrt{\frac{W}{L}} \left( \sqrt{\frac{L_{1}}{W_{1}}} - \sqrt{\frac{L_{2}}{W_{2}}} \right) \quad (1.17)$$

Figure 1.10 A constant-g<sub>m</sub> biasing circuit

where,  $R_b$  is the biasing resistor and W, L are the width and length, respectively, of the transistors. Because the transistor dimensions are independent of temperature, the transconductance is determined by the resistor  $R_b$ . When a resistor with low temperature coefficient is used, the transconductance is almost constant over temperature change. This is why it is called as constant- $g_m$  biasing circuit. This circuit will be discussed later with more details in this thesis.

### 1.6.3 ANALOG SWITCH OPTIMIZATION

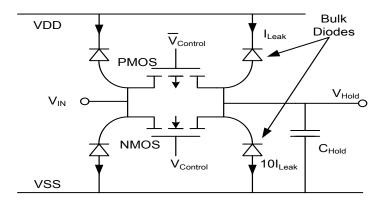

Transmission gates which are constructed by a pair of NMOS and PMOS transistors are often used as switches in sample/hold and switched-capacitor circuits. At high temperatures, the

junction leakage current in the switch can cause a voltage drop on the hold capacitor, which can be explained as follows.

Figure 1.11 shows a transmission gate including the leakage diodes and the hold capacitor [49]. When  $V_{Control}$  is high, the transmission gate is turned on and the voltage on the hold capacitor  $C_{Hold}$  is charged to  $V_{IN}$ . When  $V_{Control}$  is low, the transmission gate is turned off and the stored voltage on the hold capacitor  $C_{Hold}$  is supposed to be maintained. However, junction leakage current will flow from VDD to  $C_{Hold}$  in the PMOS transistor and from  $C_{Hold}$  to VSS in the NMOS transistor. And the leakage current in NMOS transistor is about 10 times larger than in PMOS transistor. Due to the leakage current mismatch, a net leakage current of 9x  $I_{LEAK}$  will drain charge from the hold capacitor  $C_{Hold}$ , causing a significant voltage drop on the stored voltage. Recall from Equation (1.15), the leakage current is proportional to the p-n junction area. To alleviate the voltage drop at high temperature, minimum size transistors should be used in the transmission gate and ring-shaped layout should be used to minimize the diode junction area and therefore limit the leakage current on the sample node. PMOS-based transmission gates should be used where applicable to reduce the leakage current. In this case, however, the range of the voltage to be passed through the transmission gate is limited by the PMOS transistor.

Figure 1.11 CMOS transmission gate with the leakage diodes and the hold capacitor

### 1.7 THESIS OBJECTIVES AND ORGANIZATION

The major objective of the work presented in this thesis is to develop various capacitance readout circuits for capacitive MEMS sensors in IBM 0.13 µm bulk CMOS process which includes a 2.5 V power supply. Three capacitance readout circuits, including capacitance to voltage, capacitance to frequency, and capacitance to digital circuits, are designed and tested. These proof-of-concept circuits are expected to operate at temperature range between -55 °C to 225 °C with temperature-stable performance. The detailed circuits design and measurement results will be introduced in the next chapters.

The organization of the thesis is as follows. In Chapter 2, the constant-g<sub>m</sub> biasing technique is studied in detail and the core building blocks in the readout circuits including the amplifiers are designed and tested. These building-block circuits will be used in the capacitance readout circuits in Chapters 3, 4 and 5.

Chapter 3 presents a differential capacitance to voltage interface circuit which offers the flexibility to interface with MEMS capacitive sensors with a wide range of the steady-state capacitance values from 0.5 pF to 10 pF. Simulation and experimental results from -55 °C to 225 °C are presented and discussed. This interface circuit is tested with a commercially available MEMS capacitive pressure sensor.

Chapter 4 describes a capacitance to frequency interface circuit where a current to frequency conversion circuit is used to convert the sensor capacitance into digital pulse signal modulated in frequency. Pulse width control is implemented using off-chip components to adjust the pulse width of the output digital signal. The pulse width is adjustable with off-chip components.

Simulation and experimental results over temperature range between -55 °C and 225 °C are provided and further improvement is proposed.