#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

[M]°

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# On-Chip Characterization of Charge-Pump Phase-Locked Loops

Benoît R. Veillette,

(B.Eng 1993, M.Eng 1995)

Department of Electrical Engineering

McGill University, Montréal

March 1998

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-44617-4

Arriver, c'est rien

t'occupe pas de ceux qui

se lamentationnent:

on arrive pas...

on arrive jamais à arriver...

Ça compte pas.

Partir! C'est ça qui compte.

D'ailleurs pour croire qu'on peut arriver

faut déjà être complètement parti!

Je m'égalomane à moi-même, Marc Favreau (Sol)

## **Abstract**

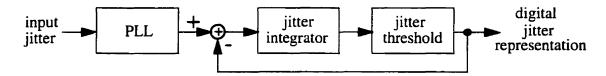

An all-digital technique for the measurement of the jitter transfer function of charge-pump phase-locked loops is introduced. Input jitter may be generated using one of three methods. They allow trade-offs between test clock frequency, hardware requirements and accuracy. All the methods rely on delta-sigma modulation to shape the unavoidable jitter quantization noise at high frequencies. This jitter noise is filtered by the lowpass characteristic of the device-under-test and has a minimal impact on the test results. For response measurement, the phase of the output signal is compared against a jitter threshold. As the stimulus generation and output analysis circuits are digital and do not require calibration, this jitter transfer function measurement scheme is highly amenable to built-in self-test. The technique can also be used to adaptively tune a PLL after fabrication. The validity of the scheme was verified experimentally with off-the-shelf components.

## Résumé

Une technique digitale pour mesurer la réponse de fréquence à la gigue de circuits de verrouillage de phase utilisant des pompes à charge est présentée. Le signal de phase servant de stimulus peut être généré à l'aide de trois méthodes. Elles permettent des compromis entre la vitesse d'horloge, le matériel requis et la précision. Toutes utilisent la modulation delta-sigma pour façonner l'inévitable erreur de quantization de telle sorte qu'elle apparaisse surtout dans les hautes fréquences. Cette erreur est filtrée en majeure partie puisque le circuit vérifié à une réponse de fréquence passe-bas. L'impact sur les résultats du test est donc réduit. Pour mesurer la réponse du circuit, la phase du signal de sortie est comparée à un seuil de détection. Puisque la génération du signal d'entrée et l'analyse du signal de sortie sont faits dans le domaine numérique et ainsi ne nécessitent pas de calibration, cette technique de mesure de la réponse de fréquence à la phase peut-être employée pour l'auto-vérification intégrée. Cette technique peut aussi être utilisée pour ajuster un circuit de verrouillage de phase après fabrication. La validité de la méthode est démontrée à l'aide d'expériences faisant appel à des composantes commerciales.

## **Acknowledgements**

I would first like to thank my supervisor Gordon W. Roberts. Not only did he provide direction and advice for my research work but he also gave me the chance to travel to numerous conferences where I had the opportunity to compare my work with others. I am convinced the last five years under his guidance will be very precious as I ready myself to enter the *real* world.

I must thank the Natural Sciences and Engineering Research Council (NSERC) and the Fonds pour la Formation de Chercheurs et l'Aide à la Recherche (Fonds FCAR) for supporting me financially, making sure I only worry about electrical engineering. The Canadian Microelectronics Corporation (CMC) is also acknowledge for supplying a large share of the equipment used for this work. Jacek Slaboszewicz and Thomas Obenaus deserve praises for maintaining a suitable computing work environment with limited resources. I also wish to acknowledge the moral support from fellow graduate students of the MACS laboratory. I am further grateful to Brian Gerson of PMC Sierra for suggesting alternative methods for testing phase-locked loops.

Je m'en voudrait de ne pas mentionner le support de mes amis de Québec et Montréal. Leur respect pour mon mode de vie étudiant m'a permis de questionner les dogmes scientifiques plutôt que de remettre en cause mon choix de carrière. Leur présence dans les bons moments comme dans les moments plus difficiles fut un ingrédient essentiel de ce travail. La recherche scientifique, pour être fructueuse, doit être accompagnée de soccer, de WiF, de discussions dans un café et de pic-nics dans une voiture sous la pluie.

Finalement, j'aimerais remercier sincèrement mes parents. Sans leur support financier et leurs encouragements constants, je n'aurais pu me rendre aussi loin. Mais je leur suis particulièrement reconnaissant pour la curiosité et l'éthique de travail qu'ils ont su m'inculquer.

## **Claim To Originality**

The core of the original work on the measurement of phase-locked loop characteristics is located in Chapters 4 and 5. Appendix A, Section A.4 introduces a new circuit required for the above purpose while Appendix B demonstrates an application.

- Chapter 4 introduces three methods for stimulating phase-locked loops for test purposes. Unlike prior art, these methods are almost entirely digital. Digital phase modulation using delta-sigma modulation, presented in Section 4.1.3, allows the creation of bandlimited phase jitter using a test clock frequency which is a small multiple of the phase-locked loop operating frequency. The use of delta-sigma modulation in the time-domain for digital-to-analog conversion is a first. The second method, presented in Section 4.2, has been presented before for communications purposes. Nevertheless, its use as a stimulus method has never been proposed before. Also, in this section appears the first report of the non-linearity inherent to this method. Then loop injection using a charge pump, another novel method, is described in Section 4.3. While it allows the use of a lower test clock frequency, it requires an additional charge pump in the phase-locked loop. Finally, an analysis of the effects of delta-sigma modulation on internal nodes of bandlimited circuits addresses an important concern of designers.

- Chapter 5 explains a method for evaluating jitter at the output. The jitter threshold circuits of Section 5.4 are adapted from a standard phase-locked loop test. Using this and one of the three stimulus method, the first comprehensive method for measuring the jitter transfer function of charge-pump phase-locked loops on-chip is introduced. Engineering trade-offs between the various implementations are discussed. Furthermore, the accuracy of the measurements is quantified.

- In Appendix A, Section A.4, a new type of delta-sigma modulator which has been labelled slope-limited is introduced. This device is used in a digital phase modulation scheme but could find its way in other applications.

- Appendix B presents a method for generating bandpass type analog signals using a

phase-locked loop tested as described in Chapters 4 and 5. This application could prove

useful in implementing BIST of wireless communications products.

# **Contents**

| Abstract  |            |                                     | iv  |

|-----------|------------|-------------------------------------|-----|

| Résumé    |            |                                     | v   |

| Acknowl   | edgement   | ts                                  | vi  |

| Claim To  | Original   | lity                                | vij |

| Chapter   | 1 : Introd | luction                             | 1   |

| 1.1       | Econom     | nics of Integrated Circuits Testing | 1   |

| 1.2       | Built-In   | Self-Test                           | 3   |

| 1.3       | Phase-L    | ocked Loop Testing                  | 5   |

| 1.4       | Disserta   | tion Goals                          | 6   |

| 1.5       | Small D    | bissertation Outline                | 7   |

| Chapter : | 2 : Mixed  | l-Signal Testing                    | 8   |

| 2.1       | Design V   | Validation Versus Production Test   | 8   |

| 2.2       | Producti   | ion Test Strategies                 | 10  |

|           | 2.2.1      | Functional Testing                  | 10  |

|           | 2.2.2      | Test Set Ordering and Trimming      | 11  |

|           | 2.2.3      | Inductive Fault Analysis            | 12  |

|           | 2.2.4      | Structural Testing                  | 13  |

|     | 2.3    | BIST for    | Analog and Mixed-Signal Circuits                    | 14 |

|-----|--------|-------------|-----------------------------------------------------|----|

|     |        | 2.3.1       | Instruments-on-a-Chip                               | 15 |

|     |        | 2.3.2       | MADBIST                                             | 16 |

|     | 2.4    | Summary     |                                                     | 18 |

| Cha | pter 3 | 3 : Charge  | -Pump Phase-Locked Loops                            | 19 |

|     | 3.1    | Charge-Pr   | ump Phase-Locked Loop Structure                     | 19 |

|     | 3.2    | Phase-Loc   | cked Loop Mathematical Model                        | 23 |

|     |        | 3.2.1       | Continuous-Time Model                               | 24 |

|     |        | 3.2.2       | Discrete-Time Modei                                 | 25 |

|     |        | 3.2.3       | Example: Second-Order Charge-Pump Phase-Locked Loop | 26 |

|     | 3.3    | Application | ons of Charge-Pump Phase-Locked Loops               | 28 |

|     |        | 3.3.1       | Timing Recovery                                     | 28 |

|     |        | 3.3.2       | Clock Distribution                                  | 30 |

|     | 3.4    | Phase-Loc   | cked Loop Metrics                                   | 31 |

|     |        | 3.4.1       | Transfer Function in Steady-State Operation         | 32 |

|     |        | 3.4.2       | Internal Noise Sources                              | 34 |

|     |        | 3.4.3       | Dynamic Operation                                   | 35 |

|     | 3.5    | Production  | n Test of Phase-Locked Loops: Literature Review     | 36 |

|     |        | 3.5.1       | Improving Automatic Test Equipment for PLL Test     | 37 |

|     |        | 3.5.2       | Integrated Circuits with PLL: Test Strategies       | 37 |

|     |        | 3.5.3       | Inductive Fault Analysis for PLL                    | 38 |

|     |        | 3.5.4       | Design For Test Techniques For Phase-Locked Loops   | 38 |

|     | 3.6    | Summary     |                                                     | 30 |

| Cha                           | Chapter 4: Stimulus Generation 40 |             |                                                    |    |  |

|-------------------------------|-----------------------------------|-------------|----------------------------------------------------|----|--|

|                               | 4.1                               | PLL Inpu    | t Test Signal                                      | 42 |  |

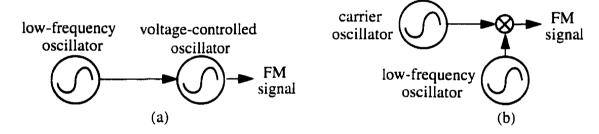

|                               |                                   | 4.1.1       | Analog Frequency Modulated Signal Generation       | 43 |  |

|                               |                                   | 4.1.2       | Digital Synthesis of a Frequency Modulated Signal  | 43 |  |

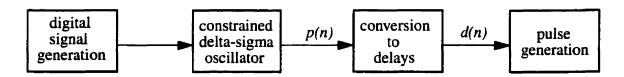

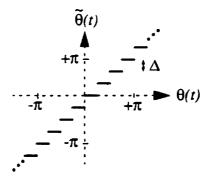

|                               |                                   | 4.1.3       | Delta-Sigma Digital Phase Modulation               | 45 |  |

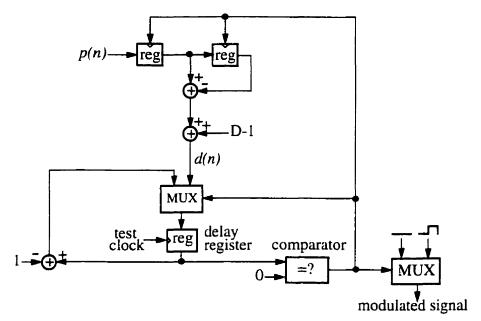

|                               |                                   | 4.1.4       | Improved Delta-Sigma Digital Phase Modulation      | 49 |  |

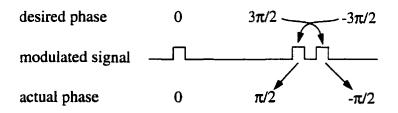

|                               | 4.2                               | Modulatio   | on of the PLL Feedback                             | 52 |  |

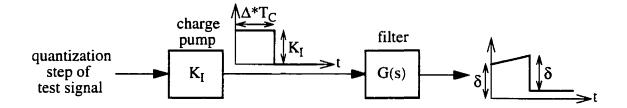

|                               | 4.3                               | Test Sign   | al Injection with a Charge Pump                    | 56 |  |

|                               | 4.4                               | Maximun     | n Jitter Amplitude in the Presence of Quantization | 58 |  |

|                               | 4.5                               | Summary     |                                                    | 61 |  |

| Chapter 5 : Response Analysis |                                   |             |                                                    |    |  |

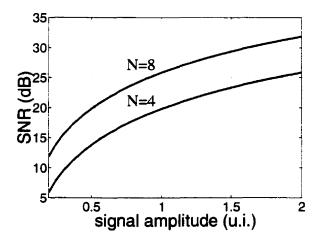

|                               | 5.1                               | Direct Jitt | ter Quantization                                   | 62 |  |

|                               | 5.2                               | Analog Pl   | hase Measurement                                   | 64 |  |

|                               | 5.3                               | Digital Ti  | me Interpolation                                   | 65 |  |

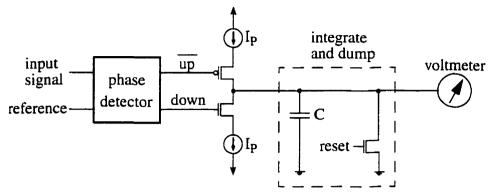

|                               | 5.4                               | Compari     | ng Jitter With a Threshold                         | 66 |  |

|                               | 5.5                               | Accuracy    | of Jitter Threshold                                | 68 |  |

|                               |                                   | 5.5.1       | Sources of Static Jitter Errors                    | 69 |  |

|                               |                                   | 5.5.2       | Sources of Random Jitter                           | 69 |  |

|                               |                                   | 5.5.3       | Effect of Random Jitter on Results Variability     | 71 |  |

|                               | 5.6                               | Summary     |                                                    | 74 |  |

| Cha                           | pter (                            | 6 : Experin | nents                                              | 75 |  |

|                               | 6.1                               | Experime    | ntal Set-up                                        | 75 |  |

|                               | 6.2                               | Experime    | nts Without a Counter in Feedback Path             | 78 |  |

|      | 6.3         | Experime   | nts With a Counter in Feedback Path  | 82  |

|------|-------------|------------|--------------------------------------|-----|

|      | 6.4         | Summary    |                                      | 85  |

| Cha  | pter 7      | : Conclus  | ion                                  | 86  |

|      | 7.1         | Short Sum  | nmary                                | 86  |

|      | 7.2         | Overhead   | for BIST Implementation              | 86  |

|      | 7.3         | Significan | ice of Original Results              | 87  |

|      | 7.4         | Future Wo  | ork                                  | 87  |

| App  | endix       | A: Delta-S | Sigma Modulation                     | 89  |

|      | <b>A.</b> 1 | Delta-Sign | ma Modulation Basics                 | 89  |

|      | A.2         | Mathemat   | ical Model of Delta-Sigma Modulators | 92  |

|      | A.3         | Second-O   | rder Lowpass Delta-Sigma Modulator   | 94  |

|      | A.4         | Slope-Lin  | nited Delta-Sigma Modulator          | 94  |

|      | A.5         | Noise-Sha  | ped Sinusoid Generation              | 96  |

|      |             | A.5.1      | Direct Digital Synthesis             | 96  |

|      |             | A.5.2      | Delta-Sigma Oscillator               | 96  |

|      |             | A.5.3      | Fixed-Length Bit Streams             | 97  |

| App  | endix       | B: Bandp   | ass Signal Generation                | 100 |

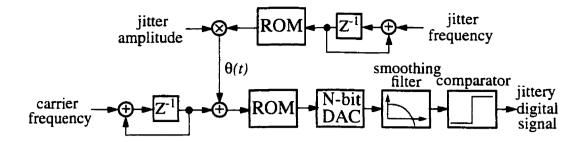

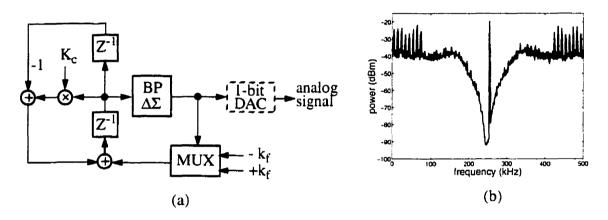

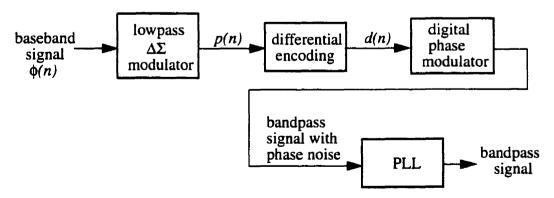

|      | B.1         | Bandpass   | Delta-Sigma Oscillator               | 100 |

|      | B.2         | Bandpass   | Signal Generation Using a PLL        | 102 |

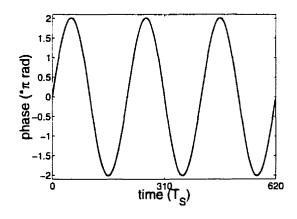

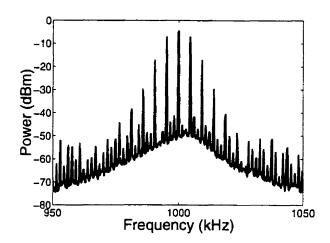

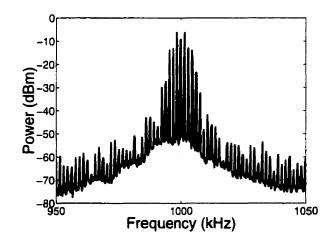

|      | B.3         | Experime   | ntal Results                         | 103 |

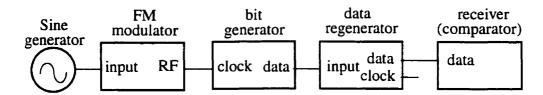

|      |             | B.3.1      | FM Signal Generation                 | 103 |

|      |             | B.3.2      | Complex Bandpass Signal Generation   | 104 |

| Dofo | rance       | ne .       |                                      | 107 |

# **List of Tables**

| 3.1 | Parameters for an OC-3 compliant phase-locked loop | 27 |

|-----|----------------------------------------------------|----|

| 5.1 | PLL without counter experiments parameters.        | 79 |

| 5.2 | PLL without counter results summary.               | 80 |

| 5.3 | PLL with counter experiments parameters.           | 83 |

| 5.4 | PLL with counter results summary.                  | 84 |

# **List of Figures**

| 1.1 | Cost of test: (a) Non-recurring costs. (b) Per manufactured unit               | 2    |

|-----|--------------------------------------------------------------------------------|------|

| 1.2 | Relative test cost vs. percentage of good chips shipped                        | 3    |

| 1.3 | (a) Traditional mixed-signal testing. (b) Built-in self-test                   | 4    |

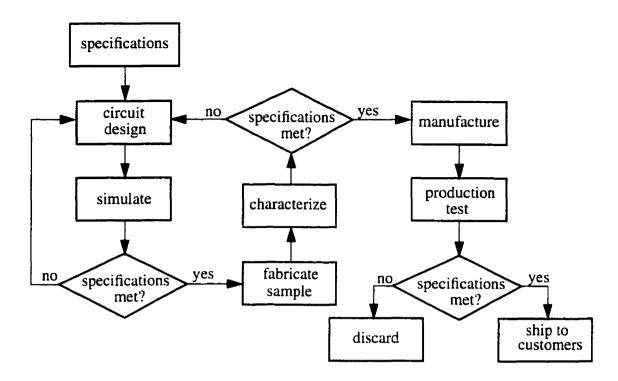

| 2.1 | Typical integrated circuit design flow.                                        | 9    |

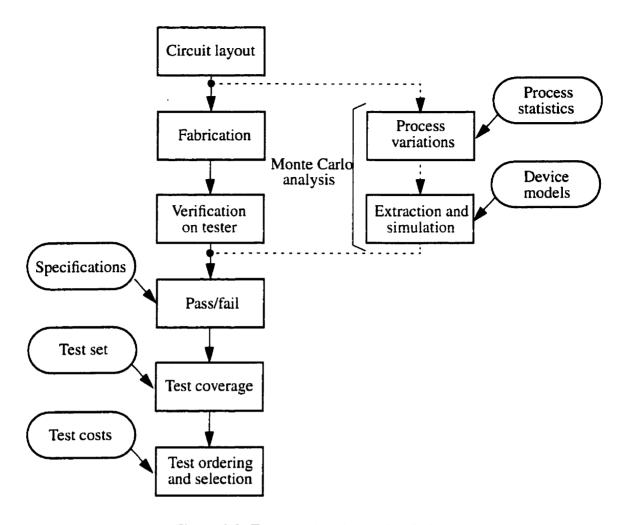

| 2.2 | Test set trimming and ordering.                                                | 12   |

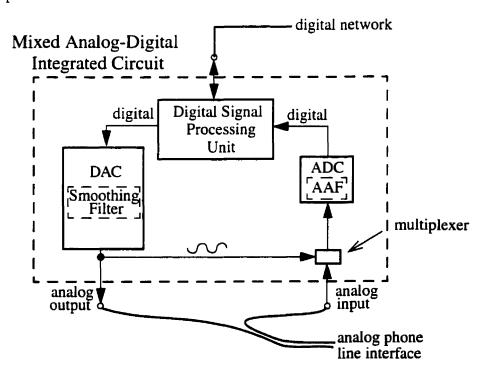

| 2.3 | A typical mixed-signal IC for telephony applications.                          | 14   |

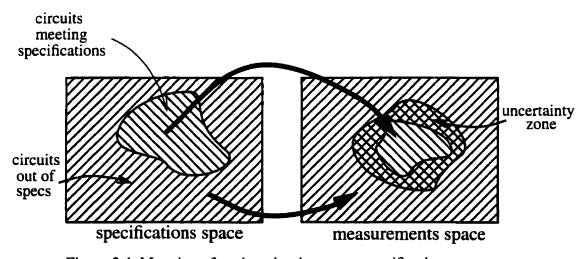

| 2.4 | Mapping of analog circuits to non-specification measures                       | 15   |

| 2.5 | MADBIST test of an analog-to-digital converter.                                | 16   |

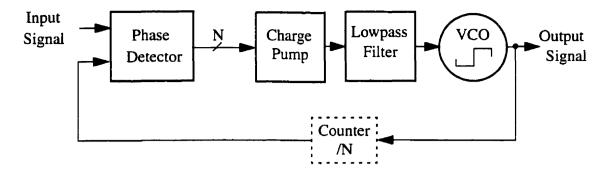

| 3.1 | Charge-pump phase-locked loop functional block diagram.                        | 20   |

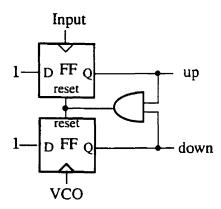

| 3.2 | Three-state phase-frequency detector.                                          | 21   |

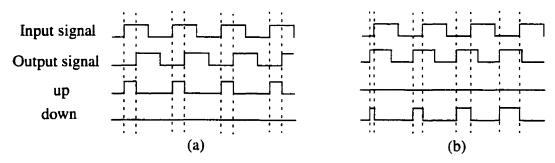

| 3.3 | Phase detector waveforms: (a) Output lagging. (b) Output has higher frequence  | y.21 |

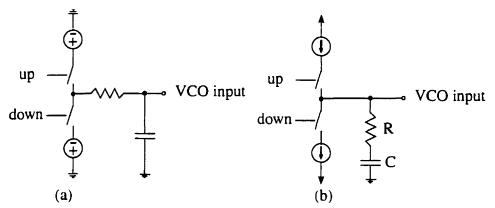

| 3.4 | Charge pumps with first-order filters (a) Voltage. (b) Current                 | 22   |

| 3.5 | Continuous-time model of a phase-locked loop.                                  | 24   |

| 3.6 | z-domain model of a phase-locked loop.                                         | 25   |

| 3.7 | (a) Continuous-time impulse response. (b) Impulse invariant transform          | 25   |

| 3.8 | Jitter transfer function (a) Up to Nyquist frequency. (b) Magnification of the |      |

|     | jitter peaking region.                                                         | 28   |

| 3.9 | Digital receiver using a phase-locked loop.                                    | 29   |

| 3.10 | Typical eye diagram.                                                 | 29 |

|------|----------------------------------------------------------------------|----|

| 3.11 | Power density of random signals using different line signal codings  | 30 |

| 3.12 | Clock tree on integrated circuits.                                   | 31 |

| 3.13 | Clock skew reduction using a phase-locked loop                       | 31 |

| 3.14 | Jitter transfer function test fixture                                | 32 |

| 3.15 | Jitter tolerance test setup.                                         | 34 |

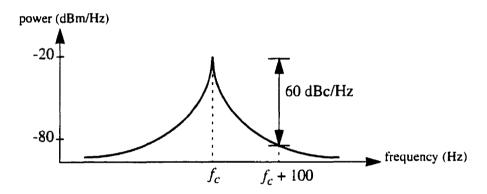

| 3.16 | Measurement of phase noise on a power density spectrum plot          | 35 |

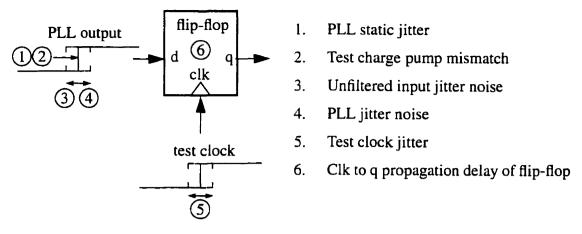

| 3.17 | Measurement using a vernier strategy.                                | 37 |

| 3.18 | Design for test strategy for ring oscillator (VCO).                  | 38 |

| 4.1  | Phase-locked loop continuous-time model.                             | 40 |

| 4.2  | FM signal generator: (a) With VCO. (b) With amplitude modulation     | 43 |

| 4.3  | ROM-based digital frequency synthesis.                               | 44 |

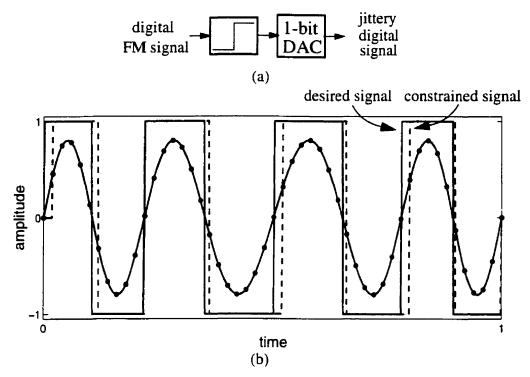

| 4.4  | Performing the comparison digitally: (a) Block diagram. (b) Signals  | 45 |

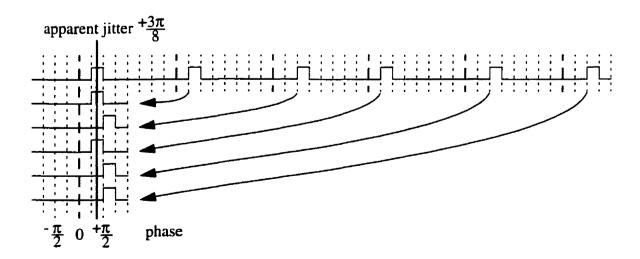

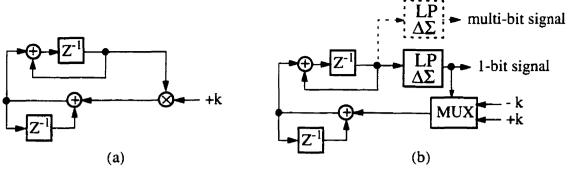

| 4.5  | Delta-sigma modulation of jitter.                                    | 46 |

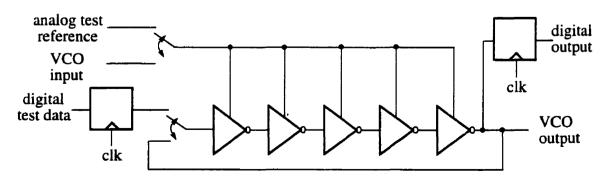

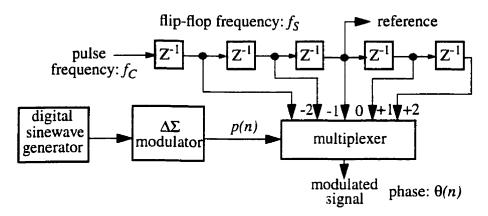

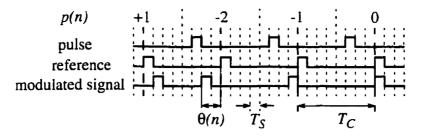

| 4.6  | Digital phase modulation circuit.                                    | 47 |

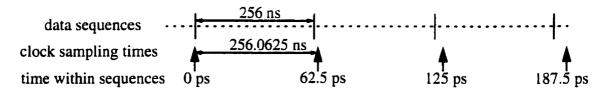

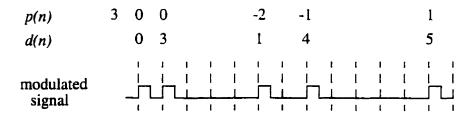

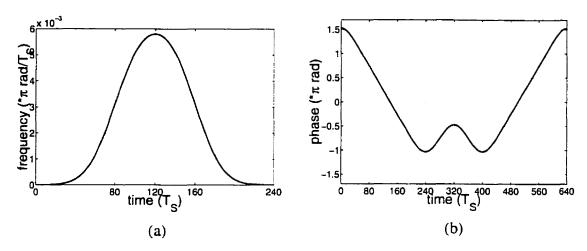

| 4.7  | Typical digital phase modulated circuit waveforms.                   | 48 |

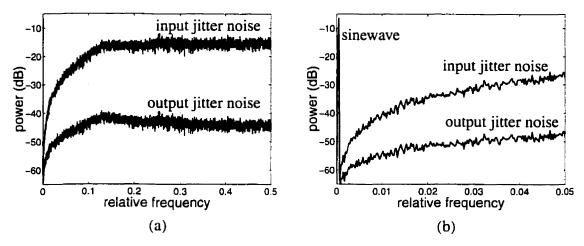

| 4.8  | Phase power density spectrums: (a) Nyquist interval. (b) Signal band | 49 |

| 4.9  | The effect of non-causal pulses                                      | 49 |

| 4.10 | Improved phase modulation method.                                    | 50 |

| 4.11 | Delay extraction and pulse generation circuits.                      | 51 |

| 4.12 | Example signals from improved phase modulation circuit               | 51 |

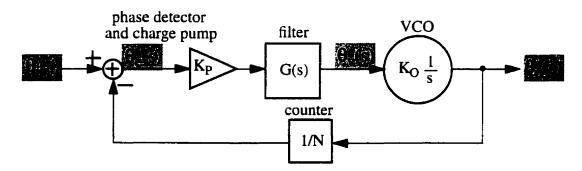

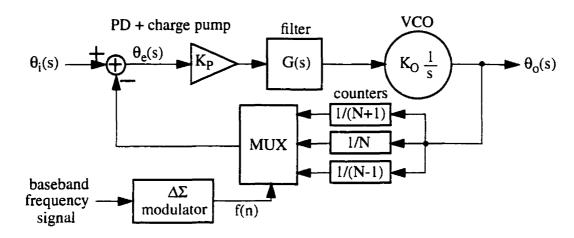

| 4.13 | Delta-sigma fractional-N synthesizer.                                | 53 |

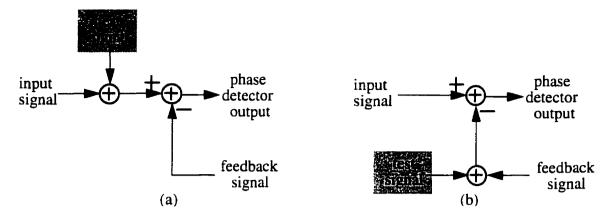

| 4.14 | Comparison of digital modulation methods: (a) input. (b) feedback    | 54 |

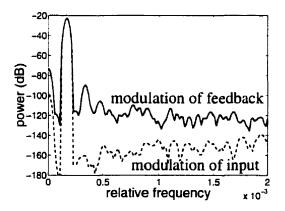

| 4.15 | Phase power density spectrums of two signals using different phase           |                |

|------|------------------------------------------------------------------------------|----------------|

|      | modulation techniques.                                                       | 55             |

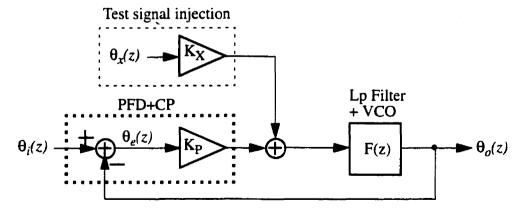

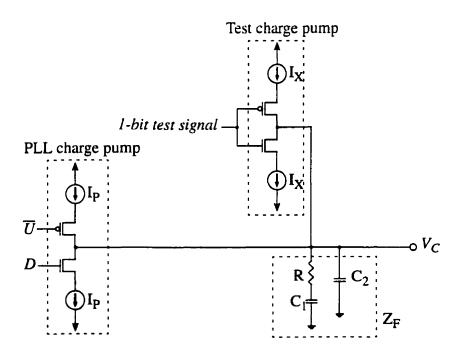

| 4.16 | Discrete-time model of phase-locked loop modified for signal injection       | 56             |

| 4.17 | Circuit modifications for signal injection in the phase-locked loop          | 57             |

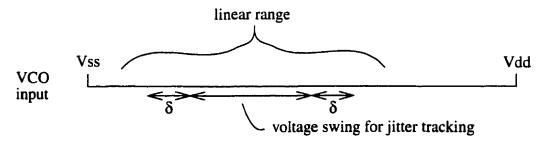

| 4.18 | Effect of quantization noise on the signal swing of sensitive nodes          | 58             |

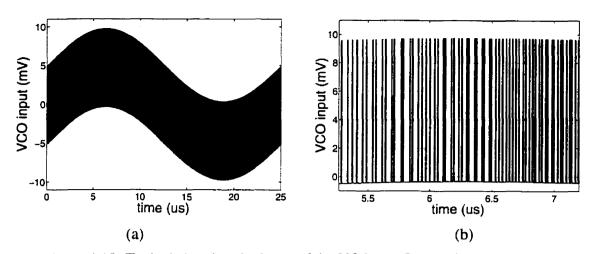

| 4.19 | Typical signal at the input of the VCO: (a) One cycle. (b) Zoom.             | 59             |

| 4.20 | Open loop model for voltage swing due to quantization.                       | 50             |

| 5.1  | Quantization of jitter in sampling measurements.                             | 52             |

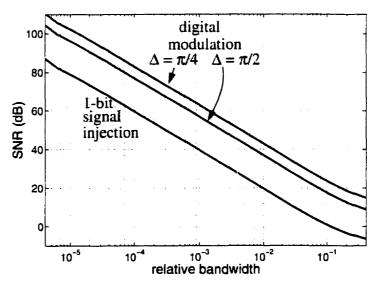

| 5.2  | Signal-to-noise ratio of measured jitter signal.                             | 53             |

| 5.3  | Analog phase measurement.                                                    | 55             |

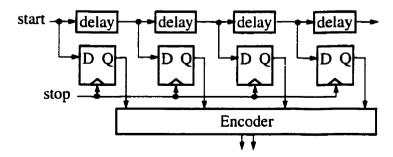

| 5.4  | Time digitization using a delay line                                         | <b>5</b> 5     |

| 5.5  | Comparing a square wave against a jitter threshold.                          | 66             |

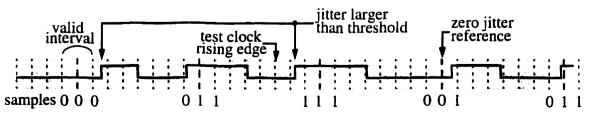

| 5.6  | (a) Circuit to evaluate a p rad jitter threshold. (b) Typical waveforms      | 57             |

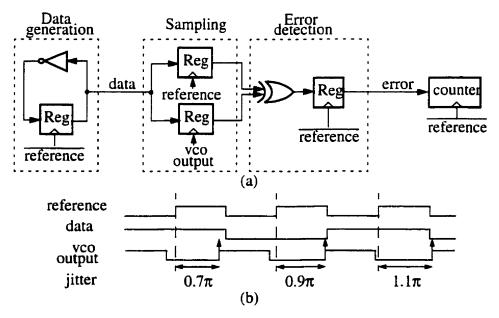

| 5.7  | Factors contributing to measurement accuracy                                 | 59             |

| 5.8  | Signal-to-noise ratio of the output jitter versus the PLL relative bandwidth | 'O             |

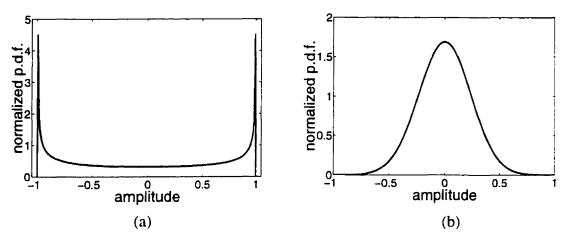

| 5.9  | Probability density functions: (a) Sinewave. (b) Gaussian noise.             | 12             |

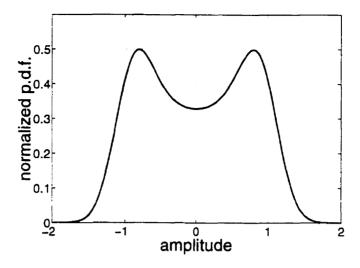

| 5.10 | Probability density functions of sum of sinewave and Gaussian noise          | 13             |

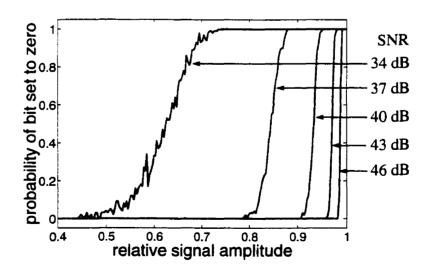

| 5.11 | Probability of threshold test succeeding versus signal amplitude.            | 13             |

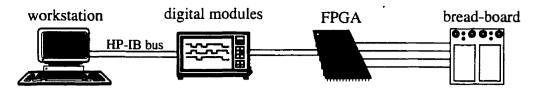

| 6.1  | Prototyping system hardware                                                  | <sup>1</sup> 6 |

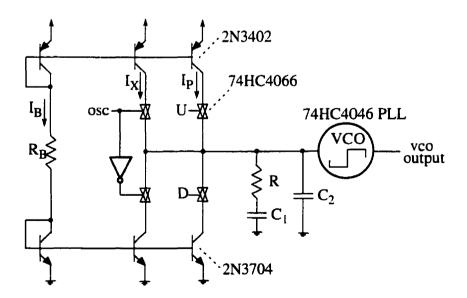

| 6.2  | Analog portion of experimental set-up on bread board                         | '6             |

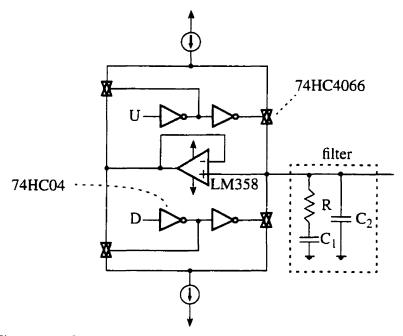

| 6.3  | Circuit to maintain the current sources in their linear region.              | 7              |

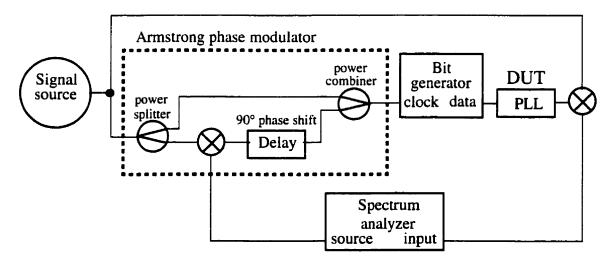

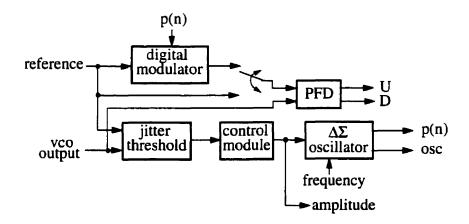

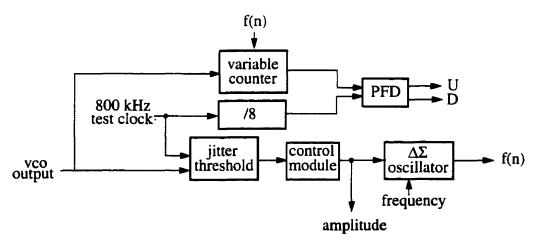

| 6.4  | Digital portion of first architecture.                                       | 78             |

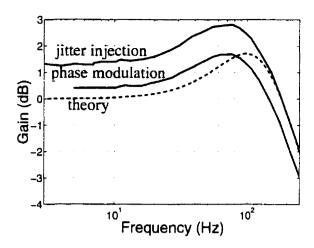

| 6.5  | Jitter transfer function: no counter, experiment 1                           | 30             |

| 6.6         | Jitter transfer function: no counter, experiment 2                          | 81  |

|-------------|-----------------------------------------------------------------------------|-----|

| 6.7         | Jitter transfer function: no counter, experiment 3                          | 81  |

| 6.8         | Digital portion of second architecture                                      | 82  |

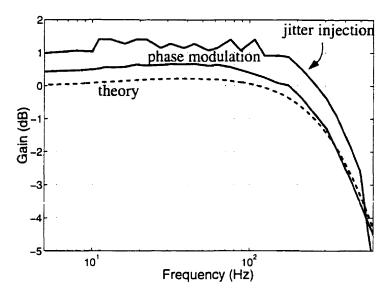

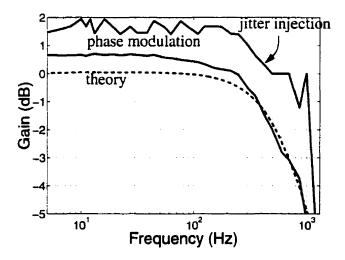

| 6.9         | Jitter transfer function: counter in feedback, experiment 1                 | 83  |

| 6.10        | Jitter transfer function: counter in feedback, experiment 2.                | 84  |

| 7.1         | Applying delta-sigma modulation concept to jitter measurement               | 88  |

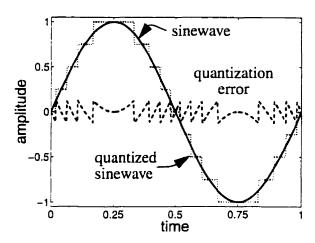

| A.1         | Quantized sinusoid and quantization noise                                   | 90  |

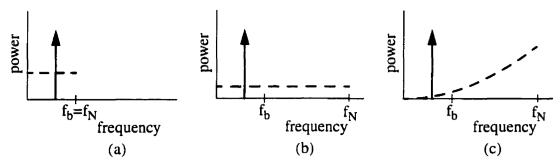

| A.2         | (a) Nyquist conversion. (b) Oversampling conversion (c) Noise shaping       | 91  |

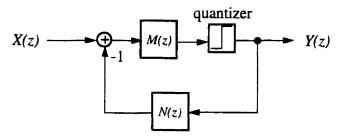

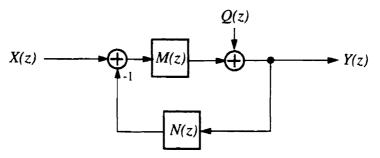

| A.3         | Generic delta-sigma modulator.                                              | 92  |

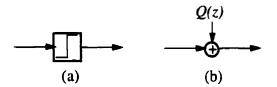

| A.4         | (a) One-bit quantizer (b) Linear model of quantizer                         | 92  |

| A.5         | Linear model of generic delta-sigma modulator.                              | 93  |

| A.6         | Second-order lowpass delta-sigma modulator.                                 | 94  |

| <b>A</b> .7 | Modified quantizer for slope-limited delta-sigma modulator                  | 95  |

| A.8         | Maximum amplitude of signal at input of slope-limited delta-sigma modulator | r95 |

| <b>A</b> .9 | ROM-based digital frequency synthesis.                                      | 96  |

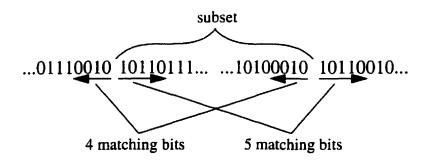

| A.10        | (a) Digital resonator. (b) Delta-sigma oscillator.                          | 97  |

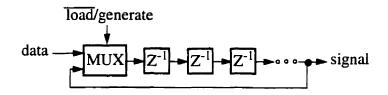

| <b>A.11</b> | Fixed-length periodic byte stream.                                          | 98  |

| A.12        | Matching of byte stream ends                                                | 98  |

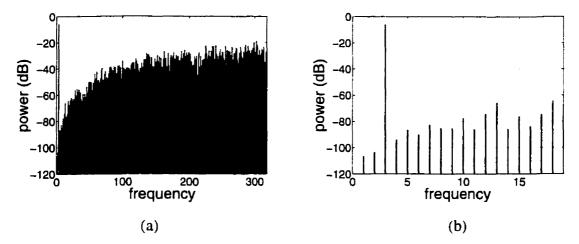

| A.13        | Spectral power density of finite length 3-bit stream: (a) Nyquist interval. |     |

|             | (b) Signal band.                                                            | 99  |

| <b>B</b> .1 | Bandpass delta-sigma oscillator: (a) Circuit. (b) Spectrum of the output    | 101 |

| B.2         | Bandpass signal generation with a phase-locked loop                         | 102 |

| B.3         | Phase of one cycle of frequency modulated sequence                          | 103 |

| B.4         | Measured spectrum of FM signal.                                    | 104 |

|-------------|--------------------------------------------------------------------|-----|

| B.5         | (a) GMSK frequency pulse. (b) Phase of one cycle of GMSK modulated |     |

|             | sequence                                                           | 105 |

| <b>B</b> .6 | Measured spectrum of GMSK signal                                   | 105 |

## **Chapter 1: Introduction**

Every manufactured product, from cars to computers, must be verified for correct operation before being shipped to buyers. Customers expect working products and therefore a bad part finding its way to the retail market will cost dearly both in repair costs and in damaged reputation. A well known illustration of this fact is in the auto market where Japanese car makers benefit from a good reputation for reliability and may thus set higher retail prices than their American counterparts [1]. In that respect, integrated circuits (ICs) are no different than any other manufactured good. However, in contrast to larger products, a sound fabrication process does not guarantee defect-free ICs at the end of the manufacturing line. Indeed, the extremely small size of the features, on the order of the diameter of a human hair, makes the fabrication process very sensitive to the environment. At critical times, a dust particle or minute vibrations are sufficient to ruin a device. As these conditions may only be controlled to a certain extent in the factory clean rooms, the electronic industry is accustomed to the idea that a portion of any production run will be defective. However, a method must exist to screen bad parts before they are shipped to costumers. This manufacturing step, called IC testing, is an important operation of the fabrication process and can account for a significant portion of the final cost of an IC.

## 1.1 Economics of Integrated Circuits Testing

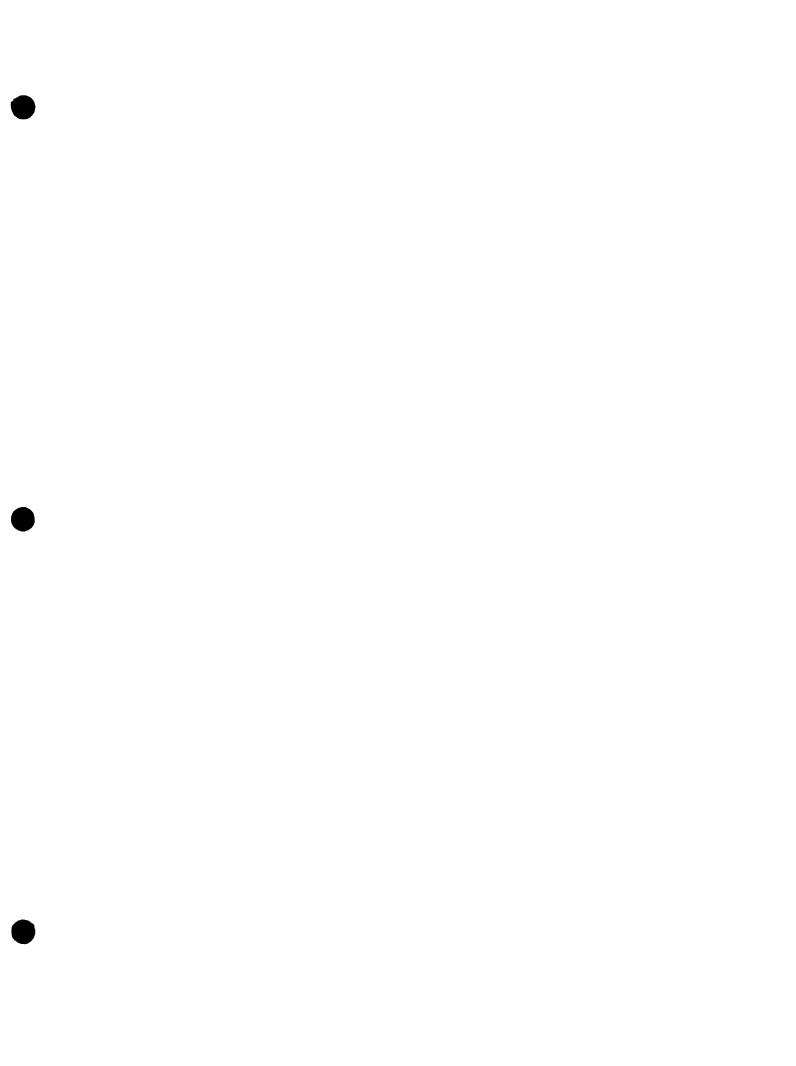

Contributions from a large number of factors, some of which are very difficult to quantize enter into the test cost of an IC [2]. These factors may be divided into two groups with respect to their recurring nature. In the first group are the non-recurring test costs which generally occur before full-scale production begins. They are charged once and are constant regardless of the number of devices eventually fabricated. Non-recurring engineering costs for test include the time spent by designers to make an IC easier to test, an activity which

#### Chapter 1 : Introduction

is labelled design for test (DFT). Also a significant responsibility for engineers is the planning of the test procedures after the design has been signed off. To these manpower expenses must be added the cost to operate the resources used in these tasks such as computers for simulations and testers for test debugging. Finally, a factor which is rather difficult to evaluate is the time-to-market delay incurred because of the development of the tests. While it is well known that delays with respect to competing products will result in lost revenue, it is hard to come up with a model to quantify this statement. On the other side are the costs associated with individual manufactured unit. The first contributor is the extra silicon area required for the DFT circuits. However, the largest portion of the test costs is generally the actual test operation. The price per chip is the test time of a device multiplied by the operating cost per unit time of the tester. Figure 1.1 illustrates the different contributions to the test cost of an IC.

Testers have now become the largest capital spending items of semiconductor manufacturers. This equipment manipulates wafers or packaged ICs, applies the test vectors and mon-

Figure 1.1: Cost of test: (a) Non-recurring costs. (b) Per manufactured unit.

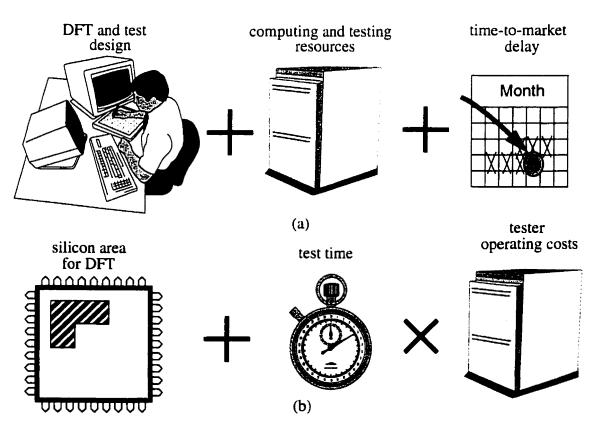

Figure 1.2: Relative test cost vs. percentage of good chips shipped [4].

itors the responses. Because of increased circuit performance, the cost of high-end automated test equipment is expected to reach ten million dollars half-way into the next decade [3]. Obviously, the test time of a single IC is an important parameter. However, it should not be considered in isolation from the other factors. Any test solution must address the whole test cost equation.

Another concept, fault coverage, is not represented in the above analysis but is pivotal to the economics of IC testing. It is defined as the number of faulty parts identified by the test procedure over the total number of defective devices. Obviously, it should be as close to 100% as possible. Undeniably, faulty parts not identified by the tester will result in repair or return cost. Nevertheless, silicon manufacturers usually settle for a fault coverage between 90% and 99.9% for a given test. This is because uncovering the remaining faults requires an inordinate amount of effort, both in test development and in test time as illustrated in Figure 1.2. The marginal cost of uncovering these hard-to-test faulty devices becomes larger than the penalty for letting them through.

### 1.2 Built-In Self-Test

With shrinking manufacturing costs and increasing performances, the significance of integrated circuit testing has ballooned. This issue has reached the critical level for a class of

#### Chapter 1 : Introduction

device referred to as mixed-signal ICs. These devices are usually composed mostly of digital circuits which perform signal processing. However, to interface these computing engines to the physical world, analog circuits are required. Common examples of this type of circuit are analog-to-digital converters, digital-to-analog converters, phase-locked loops and sensors. While these circuits typically occupy less than 10% of the total silicon area of a mixed-signal IC, their test cost is approaching half the total cost of the product [5].

A number of solutions have been proposed by researchers, most of them adaptations of digital testing ideas. In fact, digital test methods have succeeded so far in coping with the exponential growth in circuit size. The main reason for this success is the integration of these test solutions in computer-aided design (CAD) software. In contrast, analog test rely mostly on ad-hoc solutions. Yet, it should be mentioned that analog test CAD tools have emerged recently but they fall short of industry's expectations.

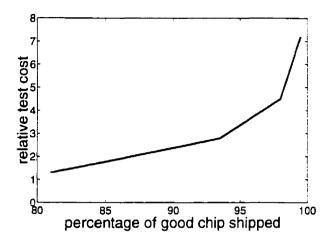

A DFT concept which offers great promises is built-in self-test (BIST) [6]. Though the expression is used for widely different schemes, it generally implies the inclusion of some or

Figure 1.3: (a) Traditional mixed-signal testing. (b) Built-in self-test.

all of the test functions on the same die as the device-under-test (DUT). Test can thus be repeatedly performed throughout the manufacturing process without requiring complex testers. Furthermore, as the output analysis circuitry is on the die, BIST also alleviates the need for complex buffers to drive signals off-chip. This feature is most important for high speed analog signals. Yet, this solution is not free as an IC which is BIST capable will usually require more silicon area for implementation. However the tester needs no longer to be capable of generating analog signals. Significant savings in capital costs are thus expected. Figure 1.3 illustrates these differences between traditional mixed-signal testing and an ideal BIST scheme.

Placing analog signal sources and measuring instruments on-chip is not an easy task. Indeed, the integrated circuits economics dictate a minimal silicon area overhead to prevent the gains on the tester from being written off by a more expensive fabrication cost incurred for BIST. Furthermore, as these circuits will be used to characterize others, their functionality must be guaranteed. Again, to prevent overhead costs from rendering a BIST solution unattractive, they should involve little or no calibration. Fortunately, digital circuits address this latest concern. In fact, the functionality of digital circuits can be tested easily and they exhibit excellent immunity to noise sources. Moreover they are more flexible than analog circuits as they can be handily programmed or reconfigured. While analog sources or instruments may not be built out of digital circuits only, most of the signal processing can be handled in the digital domain and consequently, the dependency on analog component reduced. Therefore, digital circuits will be preferred over analog circuits wherever possible for circuit blocks implementing BIST.

## 1.3 Phase-Locked Loop Testing

The phase-locked loop (PLL) is a mixed-signal block used in a large number of applications such as frequency synthesis, phase demodulation, clock distribution and timing recovery [7]. As such, it is essential for systems like wireless phones, optical fiber links and micro-computers. PLLs are even expected to appear soon on other purely digital circuits such as field-programmable gate arrays (FPGAs) and digital signal processors (DSPs).

PLL-based circuits are difficult to characterize because the parameters assessing their performance may not be extracted easily from the signals. Precision analog signal sources and measuring instruments are necessary [8]. This problem is recurrent to the characterization or testing of almost any mixed-signal or analog circuit. However, as a PLL is the only analog block on many mixed-signal chip, its test requirements directly translate into inflated product cost. Looking for solutions, test engineers are tempted to break the task and verify sub-blocks independently. This strategy has been successfully applied to digital testing problems. On the other hand, analog circuits are much more complex and do not lend themselves very well to this methodology [9]. Furthermore, the nature of the phase-locked loop renders this solution unattractive as the tight feedback makes it difficult to relate the specifications from the PLL level to the block level. Test development is further hampered by the computational power required by even simple simulations of the PLL. This is due to the order of magnitude spread in the time constants of the device. Behavioral simulation could reduce the computing burden but, because of the feedback around these blocks, complex models are required [10]. There is thus a serious need to address the issue of PLL testing from a different angle.

The work herein is limited in scope to the class of PLL operating on digital signals. The phase information of these signals is contained in the transition times. While these transitions are asynchronous, the signals are quantized to two levels, i.e. binary. These PLLs usually make use of sequential phase detectors which require charge pumps and are thus called charge-pump PLLs [11].

### 1.4 Dissertation Goals

This thesis will investigate techniques to integrate some of the PLL test functions on-chip, thereby reducing the requirements on the tester. In following the philosophy developed in the mixed-signal test group at McGill, the dependency of the testing scheme on analog components shall be reduced to a minimum. As a matter of fact, digital circuits are more reliable and benefit from established design and test methodologies. In this thesis we explore the verification of PLL characteristics using mostly synchronous digital circuits. It

#### Chapter 1 : Introduction

implies that the stimulus signals can only change at the clock edges and that the output signals may only be sampled at the same clock edges. This would seem like an unbearable constraint as jitter, both created and measured, is quantized to the test clock period. The results of any test would thus be severely limited in precision. Yet, it will be shown that this hurdle can be overcome using a technique called delta-sigma ( $\Delta\Sigma$ ) modulation. The ultimate aim is to propose a complete BIST scheme for PLLs integrating both a signal generator and the output analysis function alongside the DUT. Devices compliant to this method would be testable with a simple and inexpensive digital tester.

### 1.5 Small Dissertation Outline

Chapter 2 will explain the problem of IC testing. This will help locate the proposed scheme in the spectrum of solutions introduced in recent years. The phase-locked loop will be the topic of Chapter 3. There, the notation in use in the core chapters will be explained. Various specifications which apply to PLLs will be described. Also, the literature will be reviewed for testing solutions targeting specifically PLLs. Chapter 4 will examine stimulus generation. After discussing solutions ported from analog instruments, digital methods similar to those employed in current manufacturing tests will be investigated. Finally novel solutions suitable for BIST will be proposed. Then, Chapter 5 will explain output analysis and test methodology. Again, a number of methods will be examined, leading to a very simple solution. Experiments are described in Chapter 6 where results are displayed. A brief summary and a look a future research will compose Chapter 7. Appendix A will explain the key technique of delta-sigma modulation and will take a look at the problem of generating digital signals on-chip. A novel circuit, the slope-limited delta-sigma modulator will also be described in this Appendix. Finally, the use of the phase modulation and PLL test techniques for the generation of bandpass analog signals will be discussed in Appendix B.

## **Chapter 2: Mixed-Signal Testing**

While testing of digital circuits has matured to the point where most of the engineering work is performed by CAD tools, analog and mixed-signal testing solutions are mostly ad hoc. To understand the reasons for this lag, it is necessary to take a step back and look at the global issues of integrated circuits testing. First the distinction between design validation, or characterization, and production test must be clearly established. Following this, functional testing, a manufacturing test strategy which insures all the specifications are satisfied, will be presented. However its weakness lies in the test duration which sometimes make this solution inapplicable. Thus two methods for reducing the test time, test set ordering and inductive fault analysis, will be introduced. Finally, an introduction to analog and mixed-signal BIST for measuring specifications will be provided. It should be noted that improving controllability and observability of internal nodes, a significant topic of mixed-signal testing, will not be covered here as it is not relevant to this dissertation. A section in the following chapter will specifically address PLL testing.

### 2.1 Design Validation Versus Production Test

Figure 2.1 illustrates a typical integrated circuit design flow. From specifications, a design is created in schematic form and verified using a circuit simulator such as Spice. This design is modified a number of times until the simulations show it complies to the specifications. However, computer simulations rely on models which can only represent reality to a certain extent. Furthermore, as circuit simulation can be computationally intensive, only a subset of the specifications are verified. For example, transient analysis is performed for a small number of frequencies which are thought to capture the important aspects of the device behavior. It is thus necessary to fabricate a small number of devices before full-scale production. Functionality must then be fully verified to insure that the models used for the

Figure 2.1: Typical integrated circuit design flow.

design were accurate and that the extrapolations which were not verified through simulations are correct. This operation is called design validation or characterization. It requires accurate digital and analog instruments such as signal generators, oscilloscopes or spectrum analyzers.

Once validated the IC may be volume manufactured. However, even after thorough design characterization, the fabricated devices may fail to meet specifications. A number of problems inherent to the semiconductor manufacturing process can occur. A dust particle for example could prevent the deposition of a metal trace and cause an open circuit. Alternatively, bad process control could result in a thin gate oxide causing transistors to break down at abnormally low voltages. Also random variations in the distance between two polysilicon layers could result in intolerable mismatch between two capacitors. These issues are unavoidable and can only be reduced but not eliminated by semiconductor process improvement. Regardless of their origin, the above mentioned problems are labelled defects. However, it should be noted that defects do not necessarily result in a faulty circuit. In fact, a goal of IC designers is to desensitize their design to process variations and defects. This

#### Chapter 2: Mixed-Signal Testing

can be performed by leaving head room between the specifications and actual circuit performance, by employing circuit techniques such as negative feedback and by adding redundancy. Furthermore, multiple faults may cancel each others and have a reduced impact on performance. Hence searching for defects is sufficient for the purpose of testing but it is not the optimal strategy. It should be clear that the purpose of production test is to screen devices that no longer meet specifications because of defects, not to find defects per se.

Clearly, design validation and production test have different goals and different constraints. In design validation, all the specifications must be verified and, in case of failure, the location of the problem should be revealed. On the other hand, the cost of production test can be a significant part of the final device cost. The aim is therefore to minimize the total test cost while identifying most if not all defective parts. Verifying all specifications may not be necessary as a defect causing a circuit failure will likely affect many metrics and thus can be uncovered with any one of a number of measurements. This idea will be explained in more details in the following section.

## 2.2 Production Test Strategies

Various production test strategies may be called upon to reduce the test cost of an IC. As explained in Section 1.1, a large number of factors enter the test cost equation. Test time has traditionally received more attention as it impacts the number of expensive testers that must be bought by a manufacturer. However, the test cost equation should be studied globally.

#### 2.2.1 Functional Testing

As the first goal of production testing is to insure product quality, the basic strategy, referred to as functional testing is to verify the compliance of the device to all specifications. The device under test (DUT) is treated as a black box as only its input-output characteristics are of interest. This procedure is similar to device characterization except that the cause or origin of an error is usually not meaningful. Functional verification is generally the industry's choice for analog and mixed-signal testing.

#### Chapter 2 : Mixed-Signal Testing

The main advantage of complete functional verification is that the fault coverage is by definition 100%. Also, test development is relatively straightforward. However, this type of test requires complex signal sources and measuring instruments to extract performance metrics such as frequency, power or jitter. Expensive mixed-signal testers are thus necessary. Also, the number of test vectors required to perform the test is usually quite large and the test time may be very long. Consider for example the verification of an integrated service digital network (ISDN) transceiver [12]. A full activation from cold start requires convergence of the echo canceller, convergence of the decision feedback equalizer and recovery of the data clock. The worst case activation time specified by the underlying standard is 15 seconds, clearly an unacceptable test time in a production environment. Furthermore it would require the ATE to generate and analyze complex communication waveforms. Therefore, alternative test strategies must be employed.

#### 2.2.2 Test Set Ordering and Trimming

All the tests necessary to verify compliance to the specifications compose the test set of a DUT. Some of these tests will be failed more often as they are more sensitive to process variations. Since the test cost is directly proportional to the average time an IC spends on a tester, it makes sense to order the tests such that those with low yield are performed first. As soon as a device fails a test, it is dropped and another device begins the test sequence. Furthermore, some of the tests may be highly correlated. Intuitively, a fault (for example a short circuit) which degrades a measure will possibly affect negatively other measures. It is thus possible that a test will never uncover a fault if it is performed after other tests. They are thus dropped from the test set.

The procedure for modifying the test set is depicted on the left side of Figure 2.2. A layout of the DUT is the starting point. A large number of devices are fabricated and tested for all the specifications. Using the results obtained for the yield of the different tests, the test set may be ordered and trimmed. Algorithms for exact ordering [13] and heuristic ordering [14, 15] have been presented.

Figure 2.2: Test set trimming and ordering.

#### 2.2.3 Inductive Fault Analysis

The drawback with test set ordering and trimming is that a large number of devices must be tested for all specifications before statistically sufficient data is obtained. The first fabricated devices thus require very long test times. As an IC tester is very expensive, a large sum can be saved by doing the test set ordering and trimming before fabrication starts. The manufacturing process is instead emulated on a computer with defects injected in the layout according to process statistics. The resulting virtual devices are simulated to obtain the parameters relevant to the specifications instead of being placed on a tester as shown on the right side of Figure 2.2. This analysis is performed on a large sample of random process conditions in a Monte Carlo fashion. This procedure has been labelled inductive fault anal-

#### Chapter 2 : Mixed-Signal Testing

ysis (IFA) and was first introduced for digital circuits [16] before being extended to analog circuits [17].

The major drawbacks of this technique are that a comprehensive fault model is difficult to obtain and that in maximizing the fault coverage, a large number of simulations are required. Significant research work is going on to reduce the computational requirements, for example by using hierarchical models [10]. However, the only experimental work published to date shows that IFA for analog circuits results in unacceptably high number of escapes (faulty devices that succeeded the tests) because of unmodeled faults [18]. It can be concluded that IFA is not suitable for circuits with high specification complexity where faults from process tolerances play a significant role. Nevertheless, IFA has been successfully implemented in CAD tools for digital circuits where gates show little sensitivity to process variations. Proponents of this technique for mixed-signal circuits expect the ever increasing power of computing machines to allow more complex models and therefore better results.

The introduction of IFA and the concept of fault coverage have led to the appearance of benchmark circuits, first for digital applications [19] and now for analog and mixed-signal devices [20]. These benchmarks however are not meaningful for functional tests where the fault coverage is inherently 100%. As the test solutions in this dissertation are intended to measure specifications, benchmark figures are not appropriate.

#### 2.2.4 Structural Testing

An alternative to the black box approach of functional verification is to make use of the knowledge of the circuit to break down the verification problem into smaller, more manageable test problems. As most of the time the behavior of these sub-circuits may only be loosely related to specifications, IFA must be employed to compare the quality of the structural tests to the functional tests they intend to replace.

The advantage of this approach is that the number of test vectors is usually much smaller and therefore the test time and test costs are reduced. Also the stimulus and response signals may possibly be simpler thus requiring cheaper instruments. It does not come as a surprise

therefore that structural testing is the standard today in digital testing. Although it is still evolving, the fault model is relatively simple and digital simulations can be performed easily. In mixed-signal and analog verification, structural testing has been impeded in part by the excessive computational power required for simulations of faulty circuits but mostly by the difficulty in mapping physical defects to a set of analog faults [9].

## 2.3 BIST for Analog and Mixed-Signal Circuits

While BIST of memory arrays is widespread and BIST of datapath structures is finding its way into actual products, no commercial part yet integrates BIST for a mixed-signal circuit. This lag may be attributed to the large spectrum of analog circuits and specifications and also to the difficulty of performing reliable analog measurements on-chip. A number of schemes has nevertheless been proposed by researchers. However, most of them apply solely to a particular type of circuit such as switch-current or switch-capacitor filters and measure only a subset of the specifications. Because of their specialized applications, they will not be described here. However, the more general concept of instruments-on-a-chip deserves an explanation.

Figure 2.3: A typical mixed-signal IC for telephony applications.

#### 2.3.1 Instruments-on-a-Chip

A straightforward implementation of BIST is to move the analog instruments, both the signal sources and the measuring units, to the integrated circuit. This usually involves some digital circuits, a digital-to-analog converter (DAC) and an analog-to-digital converter (ADC). In fact, some IC may already include these circuits. Such is the case for a telephone line chip, illustrated in Figure 2.3, also dubbed a voice CODEC (coder-decoder). It serves to interface the analog phone line and the digital phone company switching network. The DAC and the ADC may be used to perform analog measurements. However, before they do so, they must be verified to insure accuracy.

In a scheme introduced by Ohletz and labelled H-BIST, it is proposed to connect the output of the DAC to the input of the ADC so that a digital-input digital-output circuit is obtained [21]. A pseudo-random input is applied and a digital signature is compacted at the output. After test completion, this signature is compared with the value expected from a fault-less circuit. This scheme is a straightforward application of digital BIST. However it suffers from two shortcomings. First, a fault in one of the block could be offset by a fault in the other block. This problem is called fault-masking. The second pitfall exists because of the very nature of analog circuits. Indeed, while digital circuit behavior may be described with discrete values, the performance of analog circuit must be explained with continuous variables. Therefore, specifications usually list a nominal response and a tolerance band. Be-

Figure 2.4: Mapping of analog circuits to non-specification measures.

#### Chapter 2: Mixed-Signal Testing

cause of this variance on the accepted behavior, there may be many signatures indicating correct circuits. Furthermore, some signatures may originate from both valid and faulty circuits. This situation is illustrated in Figure 2.4. It can be seen that the boundary between good and faulty circuits is clear when dealing with specifications. On the other hand, for measurements unrelated to specifications, there may exist a zone where a decision can not be made regarding the functionality of a circuit.

#### 2.3.2 MADBIST

The two shortcomings of the previous concept are addressed in a scheme called mixed analog-digital BIST (MADBIST) [22]. Fault masking is avoided by first verifying the ADC on its own before closing the loop. This, however, requires the generation of an analog signal to stimulate the ADC. Therefore, to implement the BIST capability in the mixed-signals IC of Figure 2.3, a lowpass delta-sigma ( $\Delta\Sigma$ ) oscillator and a multiplexer have been added. This lowpass  $\Delta\Sigma$  oscillator is an analog sinewave generator which is entirely digital except of a 1-bit DAC [23]. A description of this circuit may be found in Appendix A, Section A.5.2. A diagram of the test setup for the ADC is shown in Figure 2.5. A pulse density modulated (PDM) signal from the lowpass  $\Delta\Sigma$  oscillator is applied to the input of the ADC. In the PDM bit stream is a high-quality low-frequency sinewave and high-frequency quantization noise. This noise is removed by the anti-aliasing filter (AAF) leaving a spectrally-

Figure 2.5: MADBIST test of an analog-to-digital converter.

#### Chapter 2 : Mixed-Signal Testing

pure sinusoid to excite the remaining circuitry. The digital output of the ADC is then analyzed by the digital signal processor (DSP) to separate the signal and the noise using a fast Fourier transform (FFT) or a digital filter. Analog measures such as signal-to-noise ratio (SNR), gain tracking and frequency response may then be obtained. Furthermore, the low-pass  $\Delta\Sigma$  oscillator may be adapted to provide multi-tone signals [24]. This feature allows intermodulation distortion measurements [25] and rapid frequency response tests. A further advantage of MADBIST is that the results are digital representations of analog specifications. Therefore, the classification the devices or binning is straightforward, requiring only two digital comparators. The tolerance inherent to analog circuits is taken into account.

As most of the  $\Delta\Sigma$  oscillator is digital, it can be tested almost fully using well established digital methods. This leaves only the 1-bit DAC and the multiplexer unverified in series with the DUT. These analog circuits are very small and thus much less likely than the DUT to be hit by defects. Nevertheless, should this occur, then the effect will either be catastrophic and easily noticed or subtle but causing signal degradation. The test results would show lower performances and a rejection of a good device is possible. However the acceptance of a bad part is unlikely.

After the ADC has passed all the tests, the DAC may now be verified by placing them in cascade. A digital signal, generated by the  $\Delta\Sigma$  oscillator or the DSP, excites the DAC. The analog output is sent to the ADC which converts it back into digital form. A digital filter or FFT implemented by the DSP may then separate the noise from the signal. After the DAC is characterized, other analog circuits may be tested by placing them between the DAC and the ADC.

The MADBIST scheme illustrates the preeminent features to be found in a successful BIST. First, untested circuits should not be used to verify another circuit unless failure modes of the former are predictable and can be accounted for. Secondly, the continuous nature of analog specifications must be treated appropriately. That is, the tests must allow for a range of acceptance. Finally, digital circuits should be used as much as possible since they do not require calibration.

## 2.4 Summary

An overview of mixed-signal and analog production testing was provided. It was shown how, given a set of specifications, the functional test set of an IC is obtained. Test time may then be reduced by ordering and trimming the test set. As testers are expensive and because it is beneficial to optimize the test set before first silicon, inductive fault analysis is often used to simulate the fabrication and testing phases. However, this strategy has yet to gain acceptance for analog circuits. The concept of built-in self-test was explained and a solution for CODECs was described. Finally, desirable features of analog BIST schemes were reviewed.

# Chapter 3: Charge-Pump Phase-

# **Locked Loops**

The first description of phase lock appeared in the 1930's as a new method for radio reception [26]. However, the first widespread use of phase-locked loops (PLLs) was in the synchronization of horizontal and vertical scan in television receivers [27]. PLLs also proved useful early in receiving the weak signals subject to Doppler shift from spacecrafts [9].

The fundamental task of a PLL is to align the phase of an oscillator signal with the input signal. From this apparently simple behavior, important functions may be derived. Notably, PLLs are used for frequency multiplication and channel selection, as buffers and filters for clock signals and for recovering a periodic signal from a signal with missing transitions.

This chapter will first explain charge-pump phase-locked loops (PLLs) and study their mathematical model. Typical applications of these devices will then be presented. The metrics used in characterizing PLLs will be examined as well as the procedures for measuring them in a laboratory. Finally, the literature will be surveyed for papers related to PLL test.

## 3.1 Charge-Pump Phase-Locked Loop Structure

PLLs can be divided in two categories according to their input signal and consequently their phase detector. Historically, PLLs operated on sinusoids. They relied on combinational phase detectors such as analog multipliers and exclusive-or gates. Today, this type of PLL is employed mostly for high frequency applications such as frequency synthesis in wireless communication systems. The alternative is the use of a sequential phase detector. As the name implies, these phase detectors have some form of memory implemented with latches

Figure 3.1: Charge-pump phase-locked loop functional block diagram.

or flip-flops. Since these devices are built from digital logic, only the signal transitions between two binary states are significant. They are thus particularly suited for digital signals where the phase information is coded in these transitions. Because the output of sequential phase detectors is discrete and multi-valued, a charge-pump is required for digital-to-analog conversion. Hence PLLs equipped with sequential phase detectors are commonly labelled charge-pump phase-locked loops.

A block diagram of a simple charge pump PLL [11] is shown in Figure 3.1. To the left, a sequential phase detector (PD) compares the transitions of the input and output signals. The output of the phase detector is a multi-valued digital signal and thus a charge pump is required for digital-to-analog conversion. A lowpass filter removes short-term variations and shapes the PLL characteristics. This filter is usually first-order and is implemented with passive components. The voltage-controlled oscillator (VCO) in turn generates a signal (a square wave for charge-pump PLL) whose frequency depends on the amplitude of its analog input. With the help of negative feedback, the VCO frequency is slowed down or increased until the phase of the input and output signal align. A counter may be inserted in the feedback loop to lock the VCO to a lower frequency reference signal.

## Sequential Phase Detector

A number of sequential phase detectors have been introduced over the years. As PLL applications are numerous and diverse, different phase detector circuits are implemented in specific situations. A very popular one is the three-state phase-frequency detector (PFD)

Figure 3.2: Three-state phase-frequency detector.

[28] illustrated in Figure 3.2. It is composed of two flip-flops triggered by one of the two input signals. Their reset line is controlled by an AND gate to insure that only one output may be high at any time. The PFD compares the edges of the input signal and the voltage-controlled oscillator (VCO) output and asserts the *up* signal if the input signal is leading or the *down* signal if it is lagging the VCO output. The pulse duration is equal to the time difference between the signal edges. This type of phase detector is thus linear with respect to phase difference. Furthermore, it is sensitive to a frequency difference as well, resulting in increased acquisition range and lock speed for the PLL. Typical waveforms out of this PFD are shown in Figure 3.3. It is assumed here that the flip-flops are positive-edge triggered. In part (a), the VCO output is late and the phase detector places a pulse train on the *up* line to increase the VCO frequency. In part (b), the VCO frequency is too high and the *down* output is triggered. This PFD however cannot tolerate missing transitions which can occur in some applications.

Figure 3.3: Phase detector waveforms: (a) Output lagging. (b) Output has higher frequency.

#### Charge Pump

Charge pumps may be of two kinds: voltage and current. Their schematics are illustrated in Figure 3.4 with their respective first-order passive filters. Current charge pumps are usually preferred because voltage charge pumps are not as precise since the amount of charge injected depends on the voltage at the output node. This makes it difficult to predict the charge-pump gain and consequently the PLL behavior.

Figure 3.4: Charge pumps with first-order filters (a) Voltage. (b) Current.

#### Loop Filter

The purpose of the filter is two-fold. First it sets the closed loop behavior of the system. PLL characteristics such as jitter rejection and lock time will depend on the loop bandwidth. It must also filter high frequency components introduced by the charge pump.

The loop filter is traditionally implemented with passive components, as illustrated in Figure 3.4, except for rare implementations where DC gain is necessary. Its parameters are therefore dependent on the absolute value of resistors and capacitors which are very sensitive to process variations. In fact, for selected applications, filter components must be trimmed after the integrated circuit fabrication. The loop filter transfer function is typically first-order or second-order. However, the filter may also have to implement higher-order poles which have little influence on the loop characteristics but will remove the undesired high-frequency content of the pulses created by the charge pump.

#### Voltage-Controlled Oscillator

The voltage-controlled oscillator (VCO) generates a signal, either a square wave or a sinusoid, whose frequency is set by the input voltage. The characteristics of a VCO include the center frequency, the sensitivity, or frequency gain, and the linearity of its transfer function. VCO are also rated for their ability to reject power supply variations which is the mechanism accounting for most of the internal noise sources of the PLL.

The VCO must use some kind of unstable circuit to achieve oscillation. It is therefore no surprise that its characteristics will vary widely with process variations. For the purpose of this work, it is not required to understand its internal behavior. Interested readers are directed to the abundant literature on the subject. The two types of VCO used in charge-pump PLLs are the multivibrator [29,30] and the ring oscillator [31,32].

## 3.2 Phase-Locked Loop Mathematical Model

The PLL operation is generally non-linear. Nevertheless, a steady-state linear approximation is very useful in understanding its behavior and identifying the trade-offs involved. However, it should be remembered that any conclusion reached with the help of models must be validated with experimental results. This section will introduce the continuous-time and discrete-time model of the PLL. Then a simple example will be presented to compare the two models and highlight some performance measures.

The charge-pump PLL is a time-varying circuit because of the presence of switches. It seems therefore that the theory on linear time-invariant (LTI) networks may not be invoked. However, in most applications, the PLL changes state by only a small amount each cycle. As such it might be useful to average the behavior of the PLL over a few cycles so that LTI tools may be used. For this to give meaningful results, the bandwidth of the PLL must be significantly smaller than the input frequency [11].

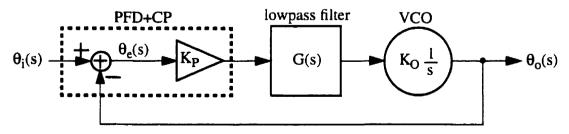

#### 3.2.1 Continuous-Time Model

The continuous-time model of a PLL, illustrated in Figure 3.5, is derived in a number of textbooks [7]. The terms  $\theta_i(s)$  and  $\theta_o(s)$  are the phase of the input signal and the output signal, respectively.  $K_P$  is the combined gain of the phase detector and charge-pump circuits given in A/rad or V/rad depending on the type of charge-pump. The gain of the VCO is denoted  $K_O$  and is stated in rad/V. If a counter is present then its effect is lumped into this constant by dividing the VCO intrinsic gain by the counter length (N in Figure 3.1). Using simple arithmetic, it can be found that the closed-loop equation governing the operation of the PLL is

$$H(s) = \frac{\theta_o(s)}{\theta_i(s)} = \frac{K \cdot G(s)}{s + K \cdot G(s)},\tag{3.1}$$

where  $K = K_P \cdot K_O \cdot H(s)$  is also labelled jitter transfer function since the input and output variables refer to the phase of the respective signals. The system is lowpass with order one larger than the filter transfer function G(s). The output of the phase detector is also called the phase error  $\theta_e(s)$  and is defined as  $\theta_i(s) \cdot \theta_o(s)$ . It may be useful to examine the relation between this value and the input phase signal. From the diagram shown in Figure 3.5, the following equation can be derived:

$$\frac{\theta_e(s)}{\theta_i(s)} = \frac{s}{s + K \cdot G(s)}.$$

(3.2)

This transfer function has a highpass nature owing to the fact that it reduces to zero as  $s \to 0$ .

Figure 3.5: Continuous-time model of a phase-locked loop.

Figure 3.6: z-domain model of a phase-locked loop.

#### 3.2.2 Discrete-Time Model

The continuous-time model yields satisfactory results for PLLs equipped with combinational phase detectors and therefore processing sinewaves. On the other hand, the phase of digital signals is contained in the signal transitions and is thus better represented as a discrete-time sequence. Therefore, the analysis of PLLs operating on digital signals should be performed using difference equations or z-transform tools. Indeed, it has been shown that the discrete-time model is more accurate for these devices, especially at high jitter frequency [33]. The z-domain representation of a charge-pump PLL is shown in Figure 3.6.

It should be noted that the gain of the phase detector  $(K_P)$  is scaled down by  $\frac{1}{f_{vco}}$ , the period of the VCO clock. The closed-loop equation is now

$$H(s) = \frac{\theta_o(z)}{\theta_i(z)} = \frac{K_P \cdot F(z)}{1 + K_P \cdot F(z)},$$

(3.3)

Figure 3.7: (a) Continuous-time impulse response. (b) Impulse invariant transform.

where F(z) is the impulse invariant transform of  $\frac{K_OG(s)}{s}$ . This transform preserves the values of the impulse response of the continuous-time system at the sample times of the discrete-time representation. Figure 3.7 illustrates this relationship between a continuous-time impulse response and its impulse invariant transform.

#### 3.2.3 Example: Second-Order Charge-Pump Phase-Locked Loop

From the equations presented above, it may be difficult to get a grasp on the PLL operation. To illustrate how this theory is applied, a simple PLL will be analyzed. A current charge pump and first order passive filter such as that seen in Figure 3.4 (b) are assumed. The filter transfer function is

$$G(s) = R + \frac{1}{sC}. ag{3.4}$$

Using Eq. (3.1), the jitter transfer function is found to be

$$H(s) = K_{P}K_{O}R \frac{s + \frac{1}{RC}}{s^{2} + K_{P}K_{O}Rs + \frac{K_{P}K_{O}}{C}}.$$

(3.5)

While the filter is first-order, the system is second-order because the VCO act as an integrator on phase. This continuous-time transfer function will be compared to the discrete-time model. First, note that

$$F(s) = \frac{K_O G(s)}{s} = \frac{K_O R C s + 1}{C} = \frac{K_O}{C} \left[ \frac{1}{s^2} + \frac{RC}{s} \right].$$

(3.6)

The impulse response of F(s) is found by taking the inverse Laplace transform, resulting in

$$h(t) = \frac{K_O}{C}[t + RC]u(t). \tag{3.7}$$

The impulse invariant property requires that

$$h[n] = \frac{K_O}{C}[nT + RC]u[n], \qquad (3.8)$$

where T is the VCO period. The inverse z-transform of Eq. (3.8) is then computed and the result is

$$F(z) = \frac{K_O}{C} \left[ \frac{Tz^{-1}}{(1-z^{-1})^2} + \frac{RC}{1-z^{-1}} \right] = RK_O z \left[ \frac{z - (1 - T/(RC))}{(z-1)^2} \right].$$

(3.9)

For simplification, let  $\alpha = 1$ -T/RC, resulting in

$$F(z) = RK_0 \frac{z(z - \alpha)}{(z - 1)^2}.$$

(3.10)

Substituting Eq. (3.10) into Eq. (3.3), the following transfer function describing the PLL in the discrete-time domain is obtained:

$$H(z) = \frac{K_P K_O R}{1 + K_P K_O R} \cdot \frac{z(z - \alpha)}{z^2 - \frac{2 - \alpha K_P K_O R}{1 + K_R K_O R} z + \frac{1}{1 + K_R K_O R}}.$$

(3.11)

| f              | 155 MHz                   |

|----------------|---------------------------|

| K <sub>P</sub> | 8x10 <sup>-7</sup> A/rad  |

| K <sub>O</sub> | 5x10 <sup>8</sup> rad/V*s |

| R              | l kΩ                      |

| С              | 220 nF                    |

Table 3.1: Parameters for an OC-3 compliant phase-locked loop.

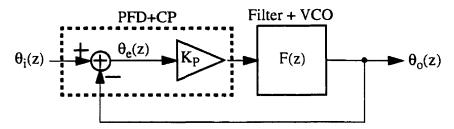

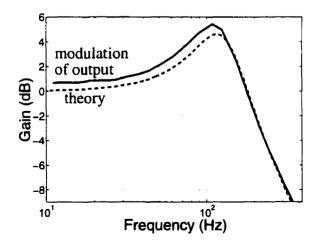

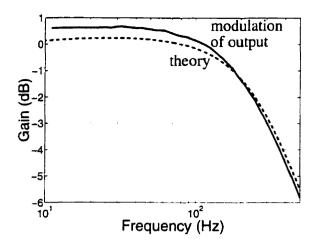

Typical parameter values for a device compliant with the OC-3 synchronous optical network (SONET) [34] specifications are shown in Table 3.1. Using these values in the expression for the continuous-time model (Eq. (3.5)), it is seen that the system is characterized by a pair of poles located at 730 Hz and 63 kHz. A left-hand-plane zero is also present at 723 Hz. The jitter transfer function using the continuous-time model (Eq. (3.5)) and the discrete-time model (Eq. (3.11)) are plotted in Figure 3.8. Both models yield similar results except at high frequencies. In Figure 3.8 (b), it can be seen that the jitter transfer function peaks before the roll-off. This can be attributed to the presence of a transfer function zero at a lower frequency than the poles. This behavior is unavoidable in classical PLL architectures. The maximum gain of the jitter transfer function is in fact called

jitter peaking. This is an undesirable feature as it leads to the accumulation of jitter in strings of repeaters for data communication networks [35]. For PLLs in these applications, a bound is placed on jitter peaking such as 0.1 dB for the OC-3 specification. The other parameter of interest in the magnitude response of the jitter transfer function is the PLL bandwidth defined as the frequency where the gain reduces by 3dB from the DC level.

Figure 3.8: Jitter transfer function (a) Up to Nyquist frequency. (b) Magnification of the jitter peaking region.

## 3.3 Applications of Charge-Pump Phase-Locked Loops

The design, and thus the test, of a particular PLL strongly depends on the application targeted. This section will thus examine the two foremost applications of charge-pump PLLs. They are the recovery of the clock signal in digital data transmission and the distribution of system clocks.

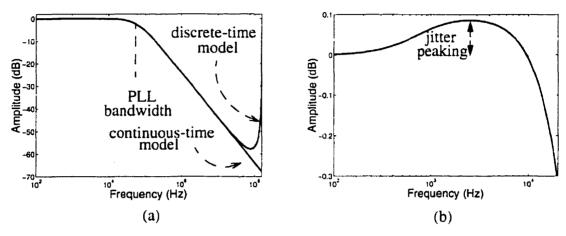

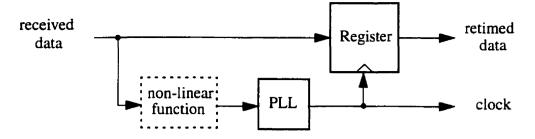

## 3.3.1 Timing Recovery

Most digital communications systems such as wireless phones, disk drives or fiber optic links transmit or store only data signals. Usually, it is not desirable or feasible to send or save the clock signal with the data. This clock signal is nevertheless embedded in the received signal through the data transitions. PLLs are essential in recovering this clock signal

Figure 3.9: Digital receiver using a phase-locked loop.

at the receiver. The clock signal thus obtained is then used to regenerate the data signal with the help of a register as illustrated in Figure 3.9.

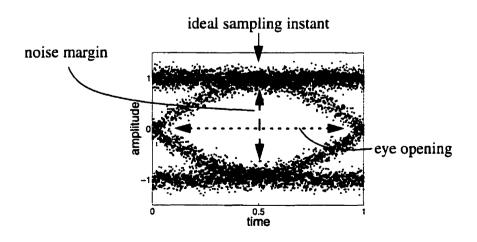

The received data signal may be strongly corrupted by the communication channel, adjacent symbols or noise. Furthermore, it may present long runs of the same symbol without transitions. Clock recovery thus necessitates state-of-the-art PLLs because of the high data rate and stringent jitter requirements. The effect of jitter for data regeneration can be visualized with the help of an eye diagram such as the one displayed in Figure 3.10. It is obtained with an oscilloscope triggered at the same frequency as the data rate. The four possible transitions of a binary alphabet are clearly visible on each side. These transitions are fuzzy lines as inter-symbol interference and noise from the communication channel are present. The PLL clock should be phase locked to the ideal sampling instant, where the noise margin is maximum. Any jitter is likely to reduce the tolerance on noise. In fact,

Figure 3.10: Typical eye diagram.

should the peak-to-peak jitter exceed the eye opening then errors will occur even in the absence of noise.

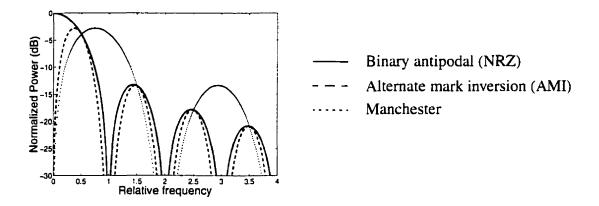

The data signal must exhibit significant power at the clock frequency or the PLL will not lock. Figure 3.11 shows the power spectral density of random signals for three different line signal codings [37]. The frequency scale is relative to the clock frequency of the transmitted signal. Two line signal codings have spectral null at the clock frequency. Therefore some non-linear processing would be performed before feeding this kind of signal to the PLL.

Figure 3.11: Power density of random signals using different line signal codings.

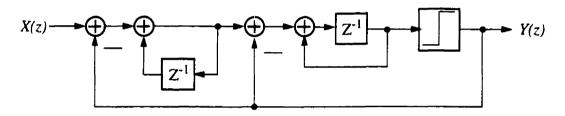

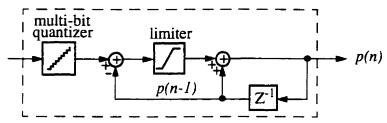

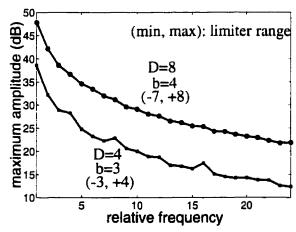

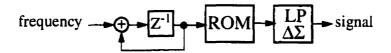

#### 3.3.2 Clock Distribution