## An Investigation of The Circuit Parasitics in Flexible Hybrid Electronics

Mohammad Muhtady Muhaisin

Master of Science in Engineering Electrical and Computer Engineering McGill University Montreal, Canada

May 2021

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Master of Science in Engineering.

© 2021 Mohammad Muhtady Muhaisin

## Dedication

To the front-line and mental health workers across the world who have served valiantly during the COVID pandemic.

### Acknowledgments

This thesis has come to fruition not only because of my contribution but also due to the presence and contribution of other people in my professional and personal life. I would like to take the opportunity to sincerely acknowledge their support and help.

First and foremost, I am grateful to God for blessing me with the success.

Secondly, I want to convey my sincere gratitude to Professor Gordon W. Roberts. Because of Professor Roberts, I got the opportunity to work in this exciting area and learned how to do research. His constant support and mentorship has been one of the biggest contributing factors behind the success of the thesis. In addition to being the student of a good researcher, I have been blessed to work with an excellent educator and a wonderful human being. His passion for research and teaching as well as his genuine concern for the betterment of his students make him the best advisor one can get.

I also want to thank Rafid Adnan Khan who has also shared the same journey with me and contributed immensely to my graduate career. Rafid and I joined in this lab and started our master's degree at the same time, in the same project. The majority of the thesis has been a collaborative work with him and so we have stayed and worked closely throughout a significant period of my graduate study. I have been inspired and motivated by his work ethic, brilliance, and dedication to the work which has helped me improve as a researcher and as a human being.

I must acknowledge the invaluable suggestions and guidance I have received from other members of the lab. Ahmed and Mahmood have helped me with their knowledge on the subject matter whenever I sought for their help and they have always voiced hope whenever projects got difficult. I wish them every success in life.

I am also grateful to the Bangladeshi graduate students' community at McGill who have been of great help here in Montreal. I have no words to express how grateful I am to have been blessed with wonderful friends here. Samin and Ferdous went beyond their ways to help me settle here and have since been there for me. Rinita, Galib, and Shovan have been my lifeline here with whom I have shared most of my highs and lows. They have helped me get back up and keep moving forward throughout the process. Thank you for being so awesome!

This thesis would not have been possible without the sacrifice and support of my parents and sisters. Their genuine care, concern, and love have been a source of motivation for me. Thank you for being so strong and supportive.

Lastly, I want to take a moment to thank everyone who has helped me come this far in life by being a part of it, even if for just a minute. My graduate life at McGill University has been a huge learning curve and a surreal experience. This institution and city have widened my eyes and made me a better person. I am truly grateful for this wonderful experience.

#### Abstract

This thesis investigates the parasitic elements present in the Flexible Hybrid Electronic (FHE) system. Parasitic resistance, inductance, and capacitance from the post-assembly FHE prototypes are extracted by introducing and employing measurement techniques. Subsequently, the proposed techniques are used to demonstrate the susceptibility and record the variation of the aforementioned parasitic components due to the application of the mechanical stress. In doing so, it is evinced that parasitic circuit components do vary due to the application of mechanical stress. Firstly, a modular bending machine is designed to perform Radius of Curvature test on the assembled prototypes. Secondly, a DC-based measurement technique is introduced to extract the individual parasitic contact resistances present between the individual pins of an IC package and the substrate of the post-assembly FHE system. Subsequently, using the measurement technique, variation of the contact resistance due to bending of the substrate is tracked. Thirdly, an AC measurement-based approach is propounded to extract the parasitic resistance, capacitance, and inductance present in the post-assembly FHE system. Variation of these parameters are documented using the method which shows that these parasitic elements are susceptible to the variation of the form factor of the substrate under mechanical stress. Finally, the impact of varying parasitics on the circuit performance and the significance of including varying parasitics in the circuit design are demonstrated. In doing so, the effect of the presence and variation of parasitic shunt capacitance in between the signal forward path at each node and the return path on the start-up of a second-order Wien Bridge oscillator are examined. At first, the steady state oscillation of a second-order Wien Bridge oscillator circuit is investigated using a piecewise linear approach to establish that a pair of right half plane complex conjugate poles is necessary for the oscillation to build up. Then, it is demonstrated that the position of this complex conjugate pole pair responsible for oscillation build-up is sensitive to the variation of the parasitic shunt capacitance. Thereafter, the results illustrate that an increase in the parasitic capacitance, caused by the change in the form factor due to bending, can lead to the failure of the oscillation build-up. Hence, the variation of the parasitics needs to be accounted for and assessed in the design of a flexible and hybrid electronic system.

### **ABRÉGÉ**

Dans cette thèse, les éléments parasites présents dans le système FHE ont été étudiés. Une machine à cintrer a été conçue pour exercer une contrainte mécanique sur les prototypes assemblés de manière contrôlée. Des techniques de mesure ont été introduites pour extraire la résistance parasite, l'inductance et la capacité des prototypes FHE post-assemblage. De plus, lors de l'enregistrement de la variation de ces composants parasites due à l'application de la contrainte mécanique, il a été montré que les éléments parasites varient en raison de l'effet de la contrainte mécanique appliquée. Ensuite, l'importance de considérer et d'inclure l'effet de la variation des parasites sur la conception d'un circuit fonctionnel a été démontrée en étudiant son effet sur le démarrage d'un système électronique omniprésent comme un circuit oscillateur. Le chapitre deux a fourni un flux de travail chronologique et détaillé de la construction de prototypes FHE et a également discuté des défis associés à chaque étape. Au chapitre trois, la conception de la machine à cintrer utilisée pour effectuer le test ROC a été définie. Le chapitre quatre a articulé une approche basée sur la mesure CC pour mesurer les résistances parasites individuelles présentes entre les broches individuelles d'un boîtier IC et le substrat du système FHE post-assemblage. Par la suite, en utilisant la technique de mesure, la variation de la résistance de contact due à la flexion du substrat a été suivie. Ensuite, le chapitre cinq a présenté une approche basée sur la mesure du courant alternatif pour extraire les trois composants parasites - résistance, capacité et inductance présents dans le système FHE post-assemblage. En utilisant la technique, il a été montré qu'en raison de la variation du facteur de forme du substrat sous contrainte, les trois éléments parasites varient. Dans le chapitre six, dans un premier temps, l'oscillation en régime permanent d'un circuit oscillateur WB de second ordre a été étudiée en utilisant une approche linéaire par morceaux qui a démontré qu'une paire de pôles conjugués complexes RHP est nécessaire pour que l'oscillation se développe. Plus tard, l'effet de la présence d'une capacité parasite shunt entre le trajet aller du signal à chaque nœud et le trajet de retour sur ces positions polaires et par la suite, sur le démarrage de l'oscillation a été examiné. Les résultats de la simulation ont déduit que la position de la paire de pôles conjugués complexes est sensible à la variation de la capacité de shunt parasite. Par conséquent, une augmentation de la capacité parasite, provoquée par le changement du facteur de forme dû à la flexion, peut conduire à l'échec de l'accumulation d'oscillation. Par conséquent, il est

évident que la variation des éléments parasites est critique pour les systèmes conçus pour une mise en œuvre dans un domaine flexible et hybride et c'est pourquoi elle devrait être incluse et prise en compte dans la conception de systèmes pour de telles applications.

#### List of Publications

- M. M. Muhaisin, R. A. Khan, J. Telfort, W. Heger, and G. W. Roberts, "Opportunities and challenges in desktop-inkjet based flexible hybrid electronics," in 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 746-749, IEEE, 2019.

- R. A. Khan, M. M. Muhaisin, and G. W. Roberts, "An in-situ technique for measuring the individual contact resistance between the pins of an ic package and the board of a flexible hybrid electronic system," in 2020 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, IEEE, 2020.

- R. A. Khan, M. M. Muhaisin, and G. W. Roberts, "Extracting RLC Parasitics from a Flexible Electronic Hybrid Assembly Using On-Chip ESD Protection Circuits." under peer-review in *IEEE Transactions on Circuits and Systems-1*.

### Contribution of Author

The contents of this thesis are the result of both collaborative and individual projects under the supervision of Professor Gordon W. Roberts. The contributions of the author of the thesis are:

- The author led the investigation of the workflow of developing FHE systems and identification of the opportunities and challenges that were subsequently investigated in the latter chapters of the thesis.

- The author led the project to design the in-lab built bending machine to perform mechanical tests on the developed prototypes.

- The author contributed to the verification and validification of the technique discussed in chapter four and led the design and execution of the experiments within the scope of this project.

- The author contributed to the design of the experiments and led the execution of the experiments to investigate the variation of the parasitic elements due to bending discussed in chapter five.

- The author individually explored and investigated the project discussed in chapter six.

# Contents

| 1 | Intr | oducti | on                                                                   | 1    |

|---|------|--------|----------------------------------------------------------------------|------|

|   | 1.1  | Backg  | round and Literature Review                                          | 1    |

|   | 1.2  | Resear | rch Scope                                                            | 10   |

|   | 1.3  | Thesis | o Outline                                                            | 11   |

| 2 |      |        | of The Workflow And The Challenges Associated With Build-<br>Systems | . 13 |

|   | 2.1  | Circui | t Design And Challenges                                              | 13   |

|   |      | 2.1.1  | Circuit Design                                                       | 13   |

|   |      | 2.1.2  | Challenges                                                           | 14   |

|   | 2.2  | Mater  | ial Selection and Challenges                                         | 14   |

|   |      | 2.2.1  | Substrate Selection And The Associated Challenges                    | 15   |

|   |      | 2.2.2  | Ink Selection And Associated Challenges                              | 15   |

|   |      | 2.2.3  | Adhesive Selection And Associated Challenges                         | 15   |

|   | 2.3  | Circui | t Printing And Challenges                                            | 16   |

|   |      | 2.3.1  | Desktop-Inkjet Based Additive Printing Mechanism                     | 17   |

|   |      | 232    | Challenges                                                           | 18   |

Contents x

|   | 2.4 | Circuit Assembly And Challenges                                                                           | 20 |

|---|-----|-----------------------------------------------------------------------------------------------------------|----|

|   |     | 2.4.1 Circuit Assembly                                                                                    | 20 |

|   |     | 2.4.2 Challenges                                                                                          | 20 |

|   | 2.5 | Electrical Testing of The Assembled Prototype And The Challenges                                          | 21 |

|   |     | 2.5.1 Post-Assembly Electrical Testing                                                                    | 21 |

|   |     | 2.5.2 Challenges                                                                                          | 22 |

|   | 2.6 | Post-Assembly Mechanical Testing And The Challenges                                                       | 23 |

|   |     | 2.6.1 Post-Assembly Mechanical Testing                                                                    | 23 |

|   |     | 2.6.2 Challenges                                                                                          | 24 |

|   | 2.7 | Chapter Summary                                                                                           | 24 |

| 3 | The | e Design of The Bending Machine                                                                           | 25 |

|   | 3.1 |                                                                                                           | 25 |

|   | 3.2 |                                                                                                           | 28 |

|   | 3.2 |                                                                                                           |    |

|   |     | 3.2.1 The Concept and Calculations                                                                        | 29 |

|   |     | 3.2.2 The Realized Design                                                                                 | 31 |

|   | 3.3 | Chapter Summary                                                                                           | 32 |

| 4 |     | raction of Inherent Parasitic Contact Resistance and Variation Thereof<br>e to Bending of an FHE Assembly | 33 |

|   | 4.1 | Measurement Methodology                                                                                   | 34 |

|   |     | 4.1.1 Modelling On-chip ESD Protection Circuit                                                            | 34 |

|   |     | 4.1.2 Measuring The Contact Resistance of a Single Pin                                                    | 36 |

|   | 4.2 | Experimental Setup                                                                                        | 38 |

Contents xi

|   |     | 4.2.1  | Validating The Measurement Technique                                                                                              | 39      |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------|---------|

|   |     | 4.2.2  | Determining The Variation of Contact Resistances as a Function of Bending Cycle                                                   | 40      |

|   | 4.3 | Result | 58                                                                                                                                | 40      |

|   |     | 4.3.1  | Extraction of Contact Resistance                                                                                                  | 41      |

|   |     | 4.3.2  | Variation of Contact Resistance as a Function of Bending Cycle                                                                    | 43      |

|   | 4.4 | Chapt  | ser Summary                                                                                                                       | 44      |

| 5 |     |        | n of The Inherent RLC Parasitics And Variation Thereof Due<br>g of an FHE Assembly                                                | e<br>45 |

|   | 5.1 | Trans  | mission Line Modelling                                                                                                            | 46      |

|   | 5.2 | Measu  | arement Methodology                                                                                                               | 49      |

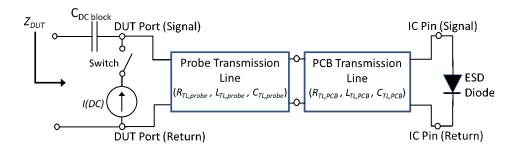

|   |     | 5.2.1  | Modelling On-chip ESD Protection Circuit                                                                                          | 49      |

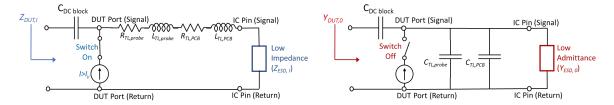

|   |     | 5.2.2  | Extracting RLC Parameters of a Transmission Line Bonded to an IC Chip                                                             | 50      |

|   |     | 5.2.3  | Isolating The Parasitic Resistance of an Individual Printed Conductor Bonded to an IC pin                                         | 52      |

|   | 5.3 | Exper  | imental Setup                                                                                                                     | 53      |

|   |     | 5.3.1  | Experimental Setup to Validate Extracted RLC Parameters of a Transmission Line                                                    | 54      |

|   |     | 5.3.2  | Experimental Setup to Validate The Isolation of Parasitic Resistance of an Individual Printed Conductor Bonded to a Single IC Pin | 55      |

|   |     | 5.3.3  | Experimental Setup to Track Variation of RLC Parasitics Due to Bending                                                            | 56      |

|   | 5.4 | Result | S                                                                                                                                 | 57      |

|   |     | 5.4.1  | Validity of Extracted RLC Parameters of a Transmission Line                                                                       | 57      |

Contents

|              |       | 5.4.2 Validity of The Isolated Parasitic Resistance of an Individual Printed Conductor Bonded to a Single IC Pin       | 62 |

|--------------|-------|------------------------------------------------------------------------------------------------------------------------|----|

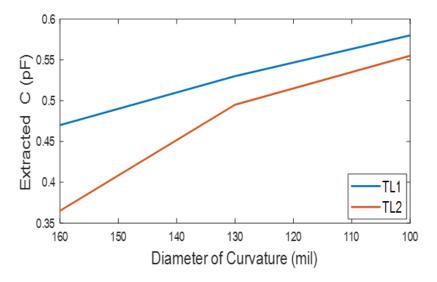

|              |       | 5.4.3 Variation of RLC Parasitics Due to Bending                                                                       | 63 |

|              | 5.5   | Chapter Summary                                                                                                        | 65 |

| 6            |       | estigation of The Effect of Parasitic Shunt Capacitance Variation on<br>e Start-up of a Wien Bridge Oscillator Circuit | 66 |

|              | 6.1   | Introduction                                                                                                           | 66 |

|              | 6.2   | Investigation of The Steady State Oscillation Behavior Using Piecewise Linear Model Approach                           | 68 |

|              | 6.3   | Investigation of The Start-up of Wien Bridge Oscillator                                                                | 74 |

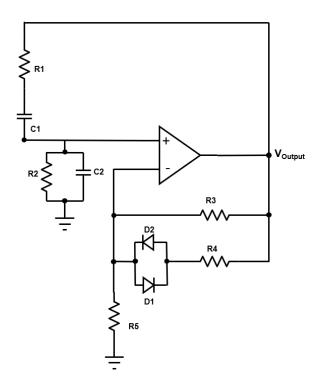

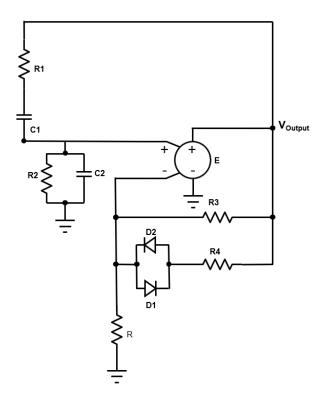

|              |       | 6.3.1 Start-up of Wien Bridge Oscillator Without Parasitics                                                            | 74 |

|              |       | 6.3.2 Start-up of Wien Bridge Oscillator With Parasitics                                                               | 76 |

|              | 6.4   | Simulation Test Benches                                                                                                | 80 |

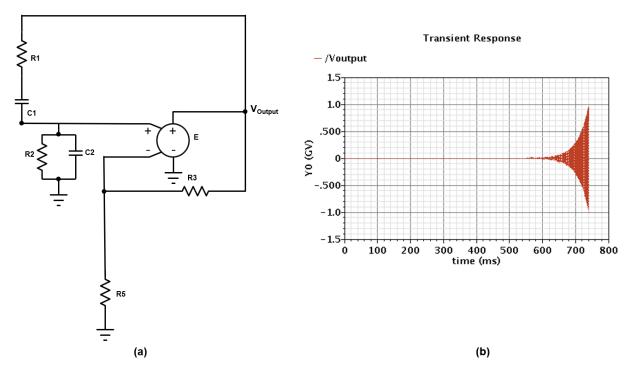

|              | 6.5   | Simulation Configuration And Results                                                                                   | 81 |

|              | 6.6   | Chapter Summary                                                                                                        | 83 |

| 7            | Cor   | nclusion                                                                                                               | 84 |

|              | 7.1   | Thesis Contribution                                                                                                    | 84 |

|              | 7.2   | Future Work                                                                                                            | 85 |

| $\mathbf{R}$ | efere | nces                                                                                                                   | 86 |

# List of Figures

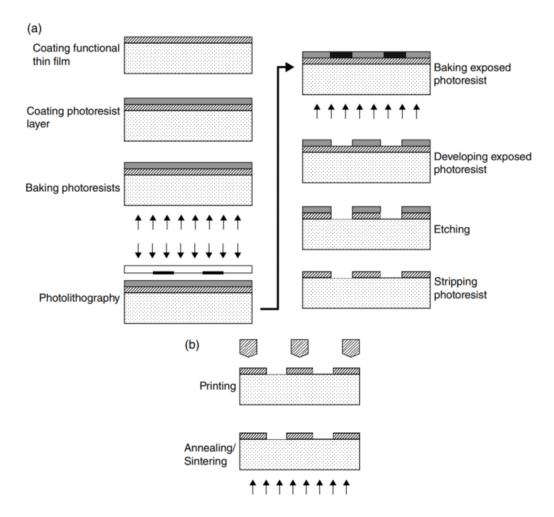

| 1.1 | Comparison of IC manufacturing and printing processes: (a) conventional                                                                                  |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | IC manufacturing process, (b) additive printing process                                                                                                  | 2  |

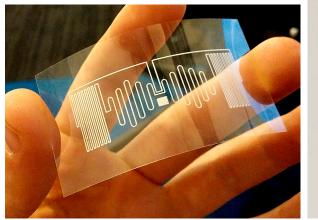

| 1.2 | Prototypes: (a)printed electronics, (b) flexible hybrid electronics                                                                                      | 4  |

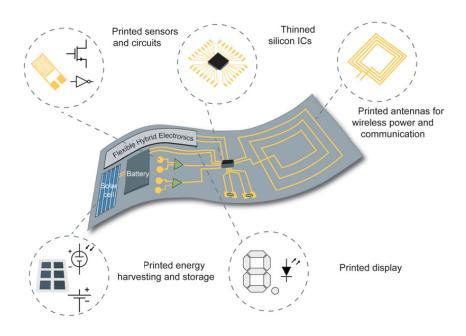

| 1.3 | Key building blocks that can be present in an FHE system                                                                                                 | 5  |

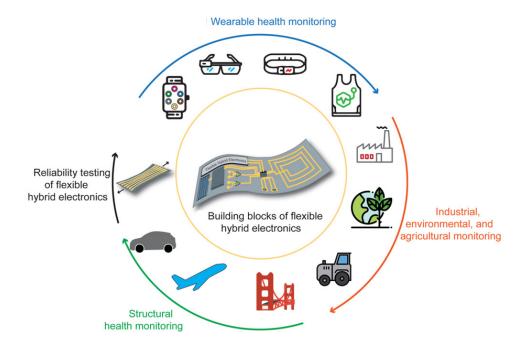

| 1.4 | Major research and application domains of FHE systems                                                                                                    | 6  |

| 1.5 | Formation of solder joint defect due to bending                                                                                                          | 8  |

| 1.6 | Impact of flexing an FHE assembly: a) stress induced on printed conductors b) change in dielectric separation and medium between two printed conductors. | 9  |

| 2.1 | (a) Continuous inkjet printing (CIJ) and (b) drop-on-demand (DOD) printing.                                                                              | 17 |

| 2.2 | Stringing effect                                                                                                                                         | 18 |

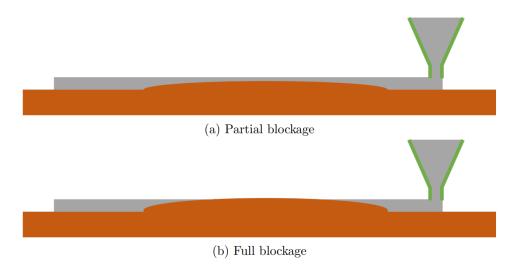

| 2.3 | Effect of partial and full blockages of the print nozzle caused by the curvature of the substrate                                                        | 19 |

| 2.4 | Test interface used to test printed circuits                                                                                                             | 21 |

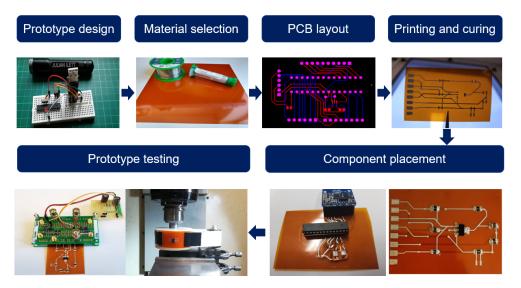

| 2.5 | Workflow of fabricating and testing FHE prototypes using additive manufacturing technology                                                               | 24 |

List of Figures xiv

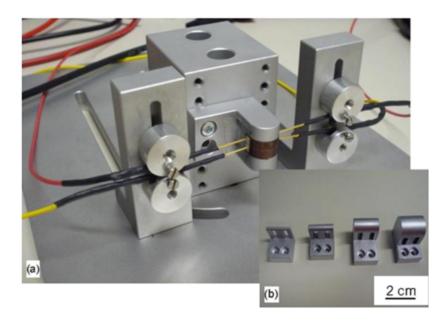

| 3.1 | (a) Bending setup containing Kelvin test measurement feature, (b) Bending accessories used for bending at different radii of curvature                                                                                                              | 26 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | The mandrel-based setup used to measure bent trace conductivity                                                                                                                                                                                     | 27 |

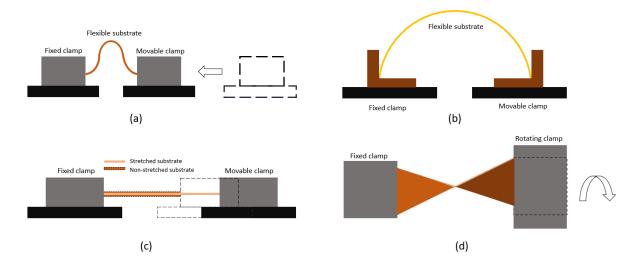

| 3.3 | Illustrations of the concept of the reviewed bending test methods for flexible electronic devices: (a) linear bending test setup using clamped ends, (b) linear bending test setup using free ends, (c) stretch test setup, (d) twisting test setup | 28 |

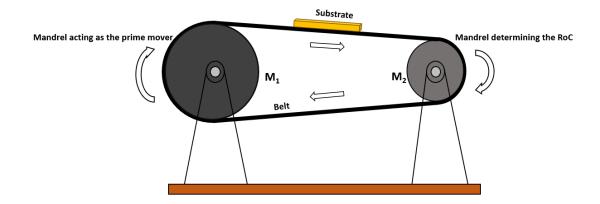

| 3.4 | Concept art of the bending setup                                                                                                                                                                                                                    | 29 |

| 3.5 | A geometric drawing of the bending machine                                                                                                                                                                                                          | 30 |

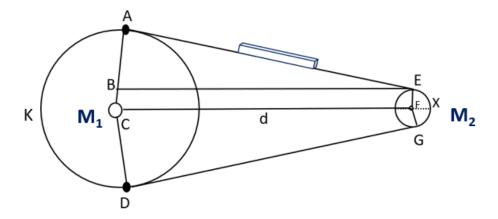

| 3.6 | (a) Realized version of the bending machine, (b) A close-up of the mandrel fashioned                                                                                                                                                                | 31 |

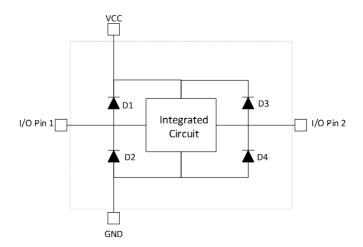

| 4.1 | Diode model for ESD protection circuit                                                                                                                                                                                                              | 35 |

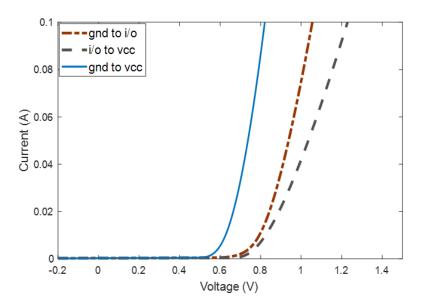

| 4.2 | I vs V Plot: (a) from GND pin to I/O pin, (b) I/O pin to VCC pin, (c) GND pin to VCC pin                                                                                                                                                            | 35 |

| 4.3 | Measurement of contact resistances of PUT after mounting an IC onto a substrate                                                                                                                                                                     | 37 |

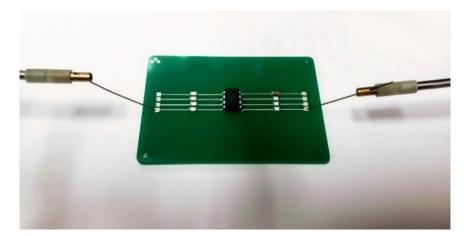

| 4.4 | Prototype for validating the measurement of the contact resistance associated with single IC pin: (a)electrical schematic (b) prototype under Kelvin test                                                                                           | 39 |

| 4.5 | Prototype under one-port measurement setup using the proposed technique.                                                                                                                                                                            | 40 |

| 4.6 | Photo of the prototype on Kapton polyimide                                                                                                                                                                                                          | 41 |

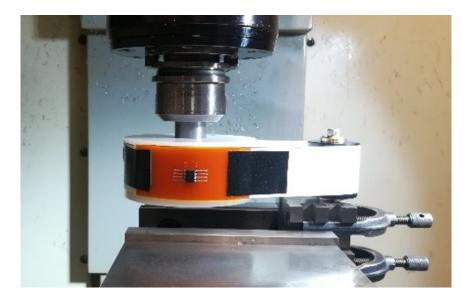

| 4.7 | Mechanical setup for bending the prototype                                                                                                                                                                                                          | 41 |

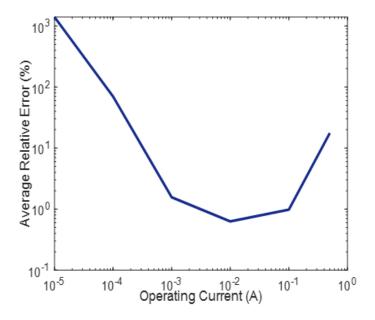

| 4.8 | Average relative error (%) vs operating current (A)                                                                                                                                                                                                 | 42 |

List of Figures xv

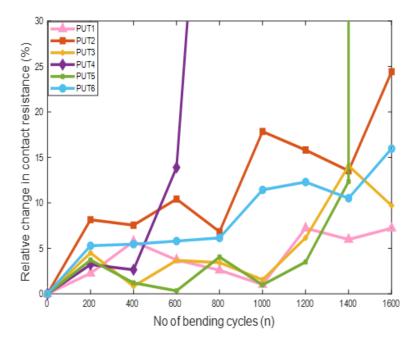

| 4.9  | Contact resistance variation with the number of bending cycles                                                                                  | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1  | Equivalent RLC Model with N number of T segments for a uniform transmission line on PCB (shown for N=4)                                         | 46 |

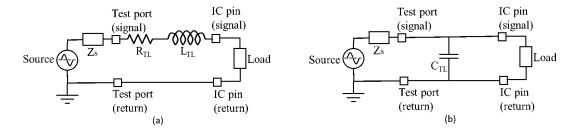

| 5.2  | Low frequency lumped equivalent models for transmission line: (a) Series RL model for small $Z_{load}$ , (b) shunt C model for large $Z_{load}$ | 46 |

| 5.3  | Normalized plot of extracted $R_{TL}$ and $L_{TL}$ as function of frequency from a transmission line terminated with small load impedance       | 47 |

| 5.4  | Transmission line lossless model                                                                                                                | 48 |

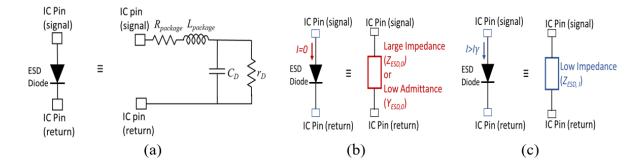

| 5.5  | Small signal representation of an ESD :(a) Equivalent circuit (b) Reverse Biased model c) forward biased model                                  | 49 |

| 5.6  | Measurement Setup for extracting the RLC parameters of a PCB transmission Line bonded to a commercial IC chip                                   | 51 |

| 5.7  | The equivalent circuit of DUT for: (a) Forward biased ESD diode (b) Reverse biased ESD diode                                                    | 51 |

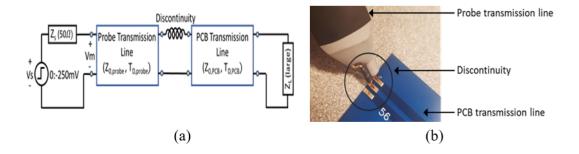

| 5.8  | (a) Setup for TDR measurement, b) Discontinuity at the interface                                                                                | 54 |

| 5.9  | Experiment to track the parasitic LC variation: (a) Prototype lying flat on the bending machine, (b) Bent prototype                             | 57 |

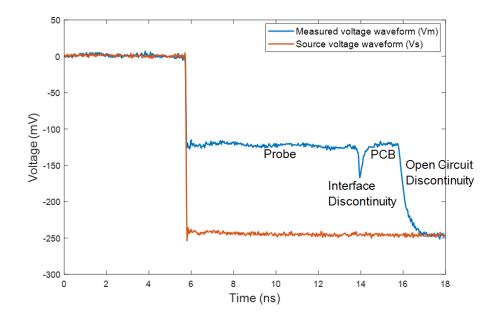

| 5.10 | Voltage waveform recorded from TDR measurement                                                                                                  | 58 |

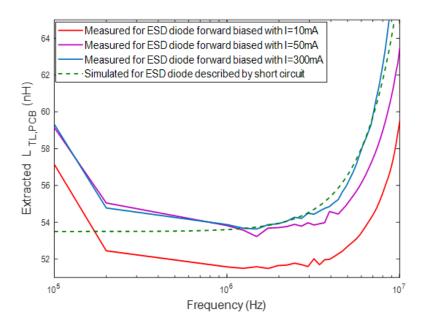

| 5.11 | Extracted $L_{TL,PCB}$ with the proposed measurement method                                                                                     | 59 |

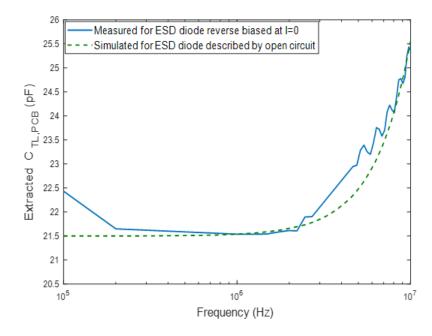

| 5.12 | Extracted $C_{TL,PCB}$ with the proposed measurement method                                                                                     | 60 |

| 5.13 | Extracted $R_{TL,PCB}$ with the proposed measurement method                                                                                     | 61 |

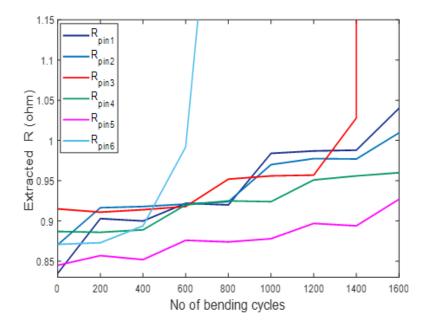

| 5.14 | Variation of extracted contact parasitic resistance with the number of bending cycles                                                           | 63 |

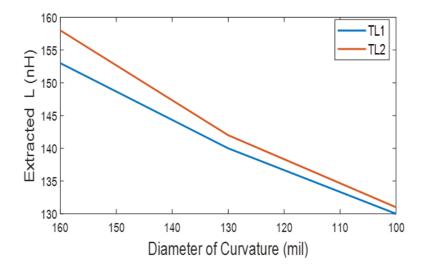

| 5.15 | Variation of extracted parasitic L with the number of bending cycles                                                                         | 64 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.16 | Variation of extracted parasitic C with the number of bending cycles                                                                         | 64 |

| 6.1  | A Wien Bridge oscillator circuit                                                                                                             | 69 |

| 6.2  | Wien Bridge oscillator implementation using a VCVS                                                                                           | 70 |

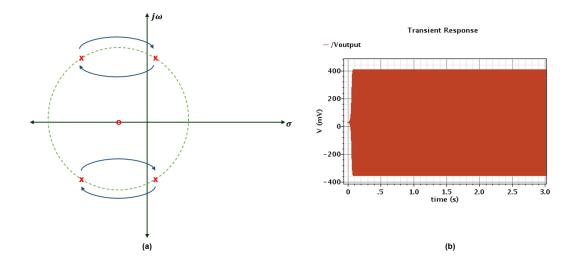

| 6.3  | (a) Small signal linear representation in the oscillation build up stage, (b) the transient response                                         | 71 |

| 6.4  | (a) Large signal linear representation in the oscillation decay stage, (b) the transient response                                            | 72 |

| 6.5  | (a) An illustration of complex pole transfer between LHP and RHP, (b) Corresponding sustaining oscillation                                   | 73 |

| 6.6  | (a) Pole arrangement in the absence of oscillation decay stage, (b) corresponding transient response                                         | 73 |

| 6.7  | (a) Pole arrangement in the absence of oscillation build up stage, (b) corresponding transient response                                      | 74 |

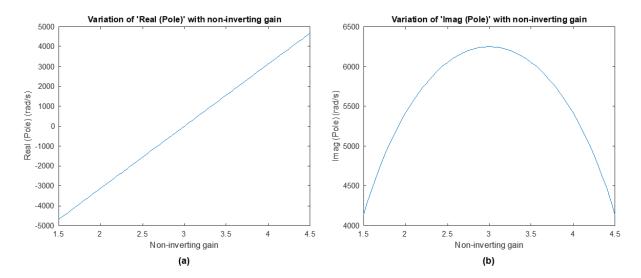

| 6.8  | Variation of the real and imaginary part of the pole with respect to the non-inverting gain                                                  | 76 |

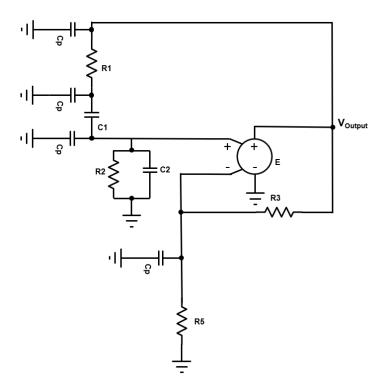

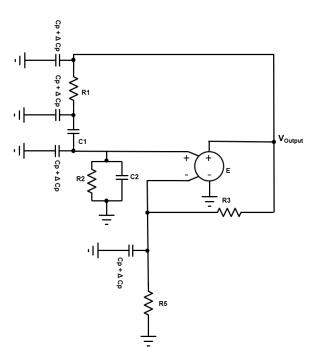

| 6.9  | Wien Bridge oscillator start-up circuit with parasitic shunt capacitance                                                                     | 77 |

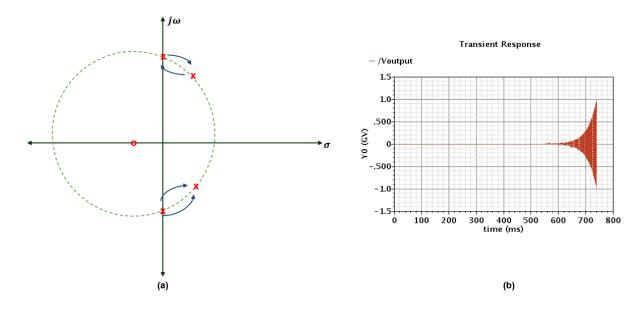

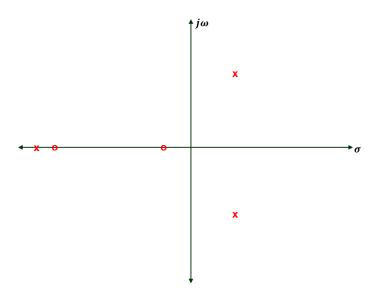

| 6.10 | Unscaled pole-zero plot of the third order system with three poles and two zeros                                                             | 77 |

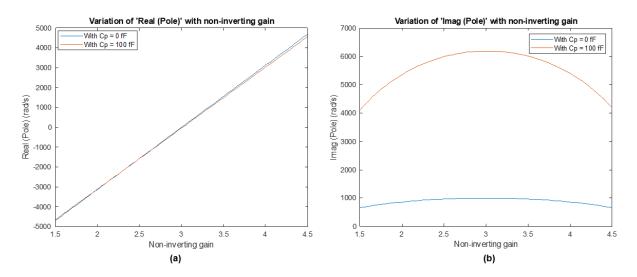

| 6.11 | Comparison of the variation of (a) real and (b) imaginary part of the poles with and without parasitic capacitance to the non-inverting gain | 78 |

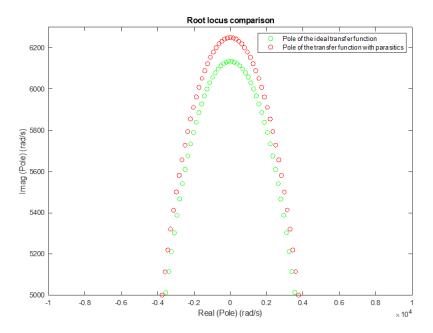

| 6.12 | Root locus comparison in the presence and absence of parasitic capacitance.                                                                  | 78 |

List of Figures xvii

| 6.13 | Wien Bridge oscillator start-up circuit with increased parasitic shunt capacitance.                                   | 79 |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

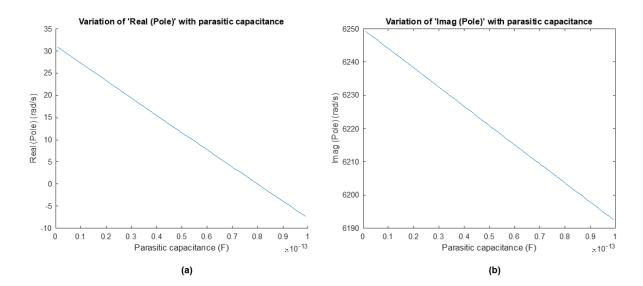

| 6.14 | Comparison of the variation of (a) real and (b) imaginary part of the poles due to variation of parasitic capacitance | 80 |

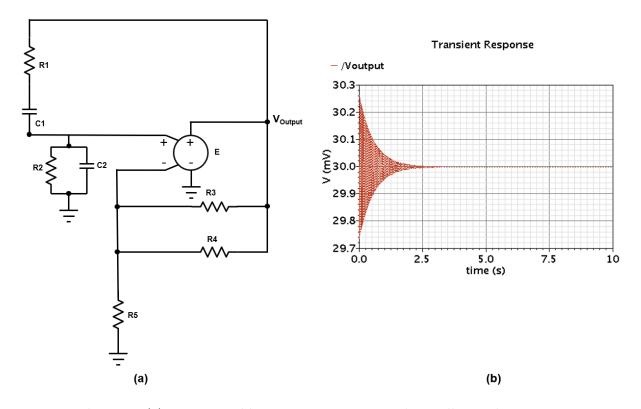

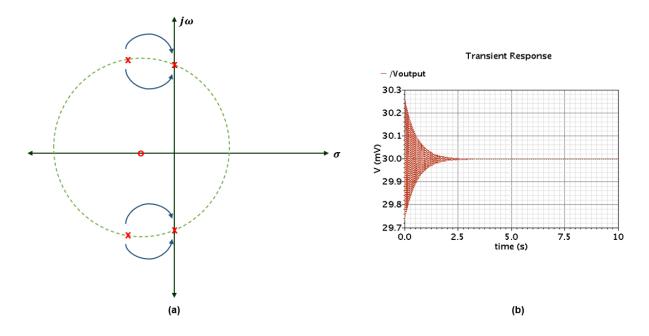

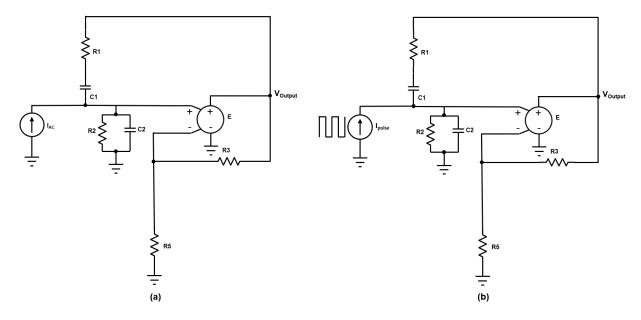

| 6.15 | Test bench: (a) to perform the pole-zero analysis, (b) to perform the transient analysis                              | 81 |

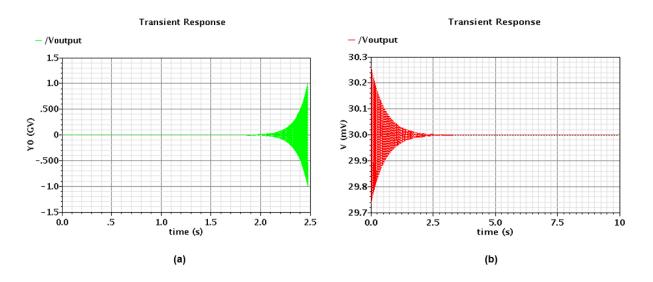

| 6.16 | Transient response of corresponding to pole placement in (a) RHP, (b) LHP.                                            | 82 |

# List of Tables

| 1.1 | Performance comparison of printed electronics and silicon ICs                                                      | 5  |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Summary of bending tests of interest from IPC-9204                                                                 | 23 |

| 4.1 | Normal distribution parameters of incremental diode resistances between particular pins for 33 samples of attiny85 | 36 |

| 4.2 | Relative error in the measurement of contact resistances using the proposed technique                              | 42 |

| 5.1 | Computed transmission line parameters from TDR measurement                                                         | 59 |

| 5.2 | Summary of extracted RLC parameters with proposed method with respect to other methods                             | 62 |

| 5.3 | Comparison of the resistance of individual printed conductors extracted by using proposed method and Kelvin test.  | 62 |

| 6.1 | Pole location corresponding to a parasitic capacitance value                                                       | 82 |

# List of Acronyms

AC Alternating Current

CMOS Complementary Metal Oxide Semiconductor

DC Direct Current

DUT Device Under Test

ESD Electrostatic Discharge

FHE Flexible Hybrid Electronics

FR4 Flame Retardant 4

GND Ground

IC Integrated Circuit

I/O Input and Output

LHP Left Half Plane

PCB Printed Circuit Board

PE Printed Electronics

PUT Pin Under Test

R2R Roll to Roll

RLC Resistance, Inductance, and Capacitance

RHP Right Half Plane

TDR Time Domain Reflectometry

UV Ultraviolet

TL Transmission Line

VCVS Voltage-Controlled Voltage Source

WB Wien Bridge

# Chapter 1

## Introduction

Flexible Hybrid Electronics is the unification of conventional rigid electronics and flexible, printed electronics. FHE platforms house Si-based integrated circuit (IC), packaged circuit components on flexible substrates that can have other printed components. As a result, it can feature the advantages of a flexible form factor as well as that of conventional circuit components. This combination of attributes has opened the door to a vast array of sensing applications in agricultural, environmental, and predominantly in healthcare sector [1–5]. IDTechEx, a renowned market research agency, forecasts that the worldwide demand for FHE will reach a value of over USD 3 billion in 2030 [6]. Similar market forecasts combining with already visible surge in the demand for FHE products are compelling indicators of the huge potential this technology possesses.

### 1.1 Background and Literature Review

The emergence of FHE technology is the result of a necessary compromise which aims to capture the beneficial features of rigid and flexible electronics and reduce the effect of their limitations. The concept of printed electronics came into being with a view to manufacturing integrated electronic systems using a technology similar to the conventional printing technology instead of much more expensive and complex integrated circuit (IC) manufac-

**Fig. 1.1** Comparison of IC manufacturing and printing processes: (a) conventional IC manufacturing process, (b) additive printing process.

turing technology [7]. As the IC fabrication industry is heavily investment intensive, the industry is comprised of only a few companies. Conversely, printing is a simple, additive manufacturing process similar to the deposition process in microfabrication. It deposits appropriate materials in form of inks on to a substrate and forms required patterns. This involves lesser steps in comparison to conventional IC fabrication technology as shown in Fig. 1.1 [7]. While fabricating ICs, conventional subtractive manufacturing process removes materials using lithographic patterning and etching. Although this process is very cost efficient, it wastes a lot of material and consumes a lot of energy. An additive process like printing can significantly reduce both the waste of material and energy consumption due to

the absence of thermal evaporation and sputtering deposition steps. Besides being additive in nature, another distinctive feature of printed electronics is that the functionality of the printed device is not restricted to any particular substrate material. As a result, many inexpensive materials can be used in place of silicon as substrates. Besides IC fabrication, subtractive process is also involved in the manufacturing of printed circuit board (PCB). Conventional PCB manufacturing process involves lithographic patterning and acidic etching of copper (Cu)-filled sheets to layout the conductive traces. Acidic etching generates a large amount of waste material detrimental to the environment and wastes most of the Cu. Subtractive etching, if replaced by additive printing to print the conductive traces, can not only reduce the amount of material waste generated and environmental pollution caused, but also reduce the cost of manufacturing due to lesser amount of stages involved. Hence, printed electronics is deemed to have the potential to pave the way to manufacturing low cost, large-area, and green electronic products.

Printed electronics technology can accommodate the use of a wide range of functional materials, both organic and inorganic, in form of inks to form patterns with conducting, semiconducting, dielectric, and optoelectronic properties that form a variety of electronic, optoelectronic, or photovoltaic devices. Wide selection of ink materials, in turn, opens up the possibility of using different kinds of substrates to print the device onto depending on the compatibility and application. As a result, heavier, rigid substrates can be replaced with biodegradable, thin, flexible, lighter substrates - and that is exactly what flexible electronics is. The flexible nature of the substrates allows the circuit to conform to a variety of shapes which contributes to an immense mechanical advantage. As opposed to rigid and bulky nature of the conventional substrates like FR4, flexible substrates like polyimides and elastomeric substrates are conformal by nature. Therefore, they offer better interfacing with arbitrary surfaces. This has resulted a huge surge in the wearable medical sensor research which has the potential to revolutionize healthcare [8–11].

Despite its unique advantages, printed electronics is far from being the ideal method to fabricate electronic devices. Some of the major drawbacks are-

• Poorer resolution of the printed features than that made by the subtractive fabrication method. For example, screen and inkjet printing can attain a maximum resolution of

$50 \ \mu m$  and  $20 \ \mu m$  respectively. On the other hand, current extreme UV lithography can attain  $20 \ nm$  of resolution [7].

- Materials deposited using printing technology lack sufficient surface smoothness which causes electric breakdown and charge leakage.

- In spite of having the potential for high throughput due to the roll-to-roll (R2R) feature of the printing technology, there is a dearth of alignment and overlay accuracy, which is essential to the device performance.

- Printed elements, especially transistors, show high process variations. The mismatch varies from 30% to 100% [12–14], which increases to 300% when the substrate is bent [15]. The mismatch severely impacts the circuit performance.

Due to these limitations, printed electronics are still largely confined to small functional blocks [16] such as electrodes [17,18], energy harvesters [19,20], flexible thin-film batteries [21], and very simple conditioning circuits [22]. Due to these major limitations in terms of low performance, high power consumption, and limited lifetime, printed electronics is yet to challenge the conventional Si-based rigid electronics. To overcome these limitations, and to leverage the unique advantage of printed electronics, FHE technology is seen as the key enabler. Figure 1.2 illustrates prototypes of a fully printed and a hybrid flexible electronic systems.

**Fig. 1.2** Prototypes: (a)printed electronics, (b) flexible hybrid electronics.

Fig. 1.3 Key building blocks that can be present in an FHE system.

FHE can utilize the flexibility and scalability of printed electronics without compromising the unparalleled performance provided by the Si-based ICs. This has paved a way for the next generation of electronics capable of conforming to the curves of a structure. Figure 1.3 shows the key constituent blocks of an FHE system and Table 1.1 shows a performance comparison of printed electronics with Si ICs [23].

Researchers are utilizing these flexibility features to interface electronics with biology and nature [24–26]. Healthcare is turning out to be one of the biggest application field of FHE as this technology is being utilized to build medical-grade wearable sensors [23]. Soft, conformal, high performance electronic system like FHE can travel around the barrier

**Table 1.1** Performance comparison of printed electronics and silicon ICs.

| Performance parameter                        | Silicon ICs                 | Printed electronics |

|----------------------------------------------|-----------------------------|---------------------|

| Charge carrier mobility $(cm^2V^{-1}s^{-1})$ | $\sim 1 \text{ (organics)}$ | ~ 1000              |

| Switching speed (MHz)                        | ~ 1                         | $\sim 5000$         |

| Operating voltage (V)                        | ~ 10                        | ~ 1                 |

| Lifetime (year)                              | $\sim 0.1$                  | ~ 10                |

Fig. 1.4 Major research and application domains of FHE systems.

of discomfort without compromising measurement accuracy. FHE have also spread to other application areas such as infrastructural, environmental, and agricultural monitoring. Figure 1.4 illustrates the major application and research domains of FHE systems [23].

Although FHE is capable of providing a more superior system-level performance than fully printed electronics at this stage, it is still an emerging technology. There are a number of design and technological challenges that are needed to be overcome. One of the most critical aspect that requires further research and development is the electrical and mechanical reliability concern of the system. The study of the mechanical reliability encompasses observation and evaluation of the undesired variation of the mechanical properties. Whereas, the study of electrical reliability is the study of observation and evaluation of the undesired variations in the electrical properties, for example, signal integrity of a designed system. As rigid electronic components are being assembled on flexible substrates for applications that assert mechanical stress on the assembly, structural, i.e., mechanical integrity of FHE devices vary hugely in their susceptibility to the effects of mechanical stress. Furthermore, different mechanical stresses also affect the electrical parameters of the system differently [15]. Structural integrity concerns that arise from one-time or repeated

application of mechanical stress transduces into signal integrity concerns of the system. For example, alteration of the form factor of the substrate as well as the integrity of the attachment of the circuit components with the substrate is a potential source of circuit parasitics, which can be detrimental to the circuit performance. Hence, investigation of the parasitic elements in assessing the electrical and mechanical reliability of an FHE assembly exposed to mechanical stress is important towards achieving success for this technology.

The technology being nascent, the literatures found on the electrical and mechanical reliability of FHE are limited in number. Most of the studies are centered around the study of mechanical reliability of printed conductive traces on thin, conformal substrates. Different printing processes have been employed [27–29] and the reliability of the printed traces have been evaluated by observing formation and propagation of cracks under different types of mechanical stresses such as bending, stretching, and torsion [30]. Furthermore, several numerical models have been developed to analyze different failure modes of the printed traces [31]. But these studies might lack accuracy in assessing the reliability of a fully assembled and fabricated FHE system. As these studies evaluate the reliability of the printed traces only, they do not take into account the additional thermal stress caused by the solder reflow process while assembling the electronic components on the substrates [32].

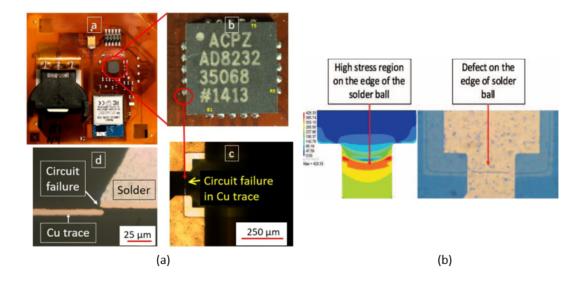

Fabrication of FHE involves printing of the conductive traces, necessary interconnects and subsequent attachment of electronic components on solder pads printed on the substrate. The process of mounting and attaching rigid electronic components on flexible substrates exerts mechanical and thermal stress on the printed pad and the substrate [32]. As a result, cracks are formed in the printed conductors and solder joints. Recurrent application of stress leads to the propagation of those cracks which ultimately leads to the loss of electrical connection [33, 34]. Furthermore, due to the presence of the assembled components on the substrate, impact and distribution of stress on the substrate are different from that of a substrate containing only the printed components [35]. Hence, from a practical viewpoint, post-assembly assessment of the impact of mechanical stress on FHE is more insightful and judicious. Varun et al. [32] has performed a system-level study on a fully assembled FHE platform to assess and improve the mechanical reliability parameters. In that study, as illustrated in Fig. 1.5 (a), optical inspection has been utilized to observe and track the formation and propagation of cracks in the printed copper (Cu) circuitry

**Fig. 1.5** Formation of solder joint defect due to bending.

and gradual loss of attachment of rigid components with printed traces. Although test vehicle array resistance has been measured after different manufacturing steps, points of attachments have not been assessed by any measurement technique individually. But a simulation carried out in this study identifies the solder joint or the point of contact of the electronic components with the substrate as the area under the highest amount of stress while bent, as shown in Fig. 1.5 (b). Hence, it is inferred that the solder joints are more prone to damage and critical to the proper functioning of the assembled FHE system which is why their susceptibility to the variation of the mechanical stress needs to be measured and assessed.

To quantify the effect of mechanical stress on printed traces using an electrical parameter, variation of the trace resistance is recorded and utilized. As ideally, traces are supposed to have zero resistance, this inherent resistance present in the traces can be termed as parasitic trace resistance. Additionally, due to attachment of electronic components on the substrate by means of soldering or applying adhesives, ancillary resistance forms named parasitic contact resistance. Several researches demonstrate that with repeated application of mechanical stress on printed traces, parasitic trace resistance shows an increasing trend which has been correlated with the formation and propagation of cracks in the traces under test. Hence, parasitic resistance can not only be used as an indicator of the mechanical

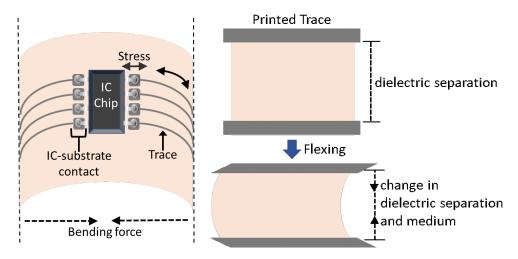

**Fig. 1.6** Impact of flexing an FHE assembly: a) stress induced on printed conductors b) change in dielectric separation and medium between two printed conductors.

reliability but also be used to evaluate the electrical reliability of the circuit, which is fundamental towards the successful operation of the system designed. Hitherto, post-assembly variation of the parasitic contact resistance formed by the solder joint in between the IC package and the substrate has not been been studied, to the best of our knowledge. Besides parasitic resistances, parasitic inductance and capacitance are also inherent in every electronic system. No study is found to have reported the effect of mechanical stress on other inherent circuit parasitics such as parasitic inductance and capacitance, to the best of our knowledge. On-board parasitic inductance and capacitance is dominantly dependent on the dimension of the printed conductors and the dielectric separation in between. As mechanical stress alters the physical dimension of the substrate which in turn changes the dielectric separation, as illustrated in Fig. 1.6, variation of parasitic inductance and capacitance is highly likely. Although negligible at lower frequencies, high frequency applications accentuate their presence which causes concerns to the signal integrity of a system. So, the measurement of all three parasitic components- resistance, inductance, capacitance (RLC) inherent in the circuit and their susceptibility to the application of mechanical stress is critical. In conjunction, the study of the impact of their susceptibility on the performance of the designed system will result in a more accurate and all-round assessment of mechanical and electrical reliability of the assembled FHE system.

#### 1.2 Research Scope

Circuit parasitics, although unavoidable, are very small quantities. As a result, their accurate measurement is challenging and more sensitive to external noise and probe parasitics. Two-port sensing, also known as Kelvin sensing, can eliminate the probe parasitics such as lead and contact resistance [36]. This is a huge advantage for precise measurement of small quantities, hence recommended and used in measuring circuit parasitics. However, at the post-assembly level, a two-port measurement of circuit parasitics is challenging to implement as this requires post-solder probing at the IC pins. This is difficult to accomplish as the IC pins are extremely small and often located underneath the IC package with no access. Even when the IC pins are accessible, repeated probing at the pins to track the parasitics from an FHE assembly can accumulate additional stress at the IC-substrate contact, thereby altering the measured quantity. Consequently, it is necessary to find a one-port, on-board measurement technique that eliminates the need for probing at the IC pins. Thereupon, a one-port measurement technique is needed to be devised and deployed to extract the parasitic elements. Then, the technique needs to be applied to record any change in the value of those respective elements when the assembly is subjected to mechanical stress. For that, a modular bending machine needs to be fashioned capable of subjecting the assembled prototype to controlled mechanical stress. Finally, if the parasitic elements vary, the varying parasitic elements are needed to be accounted for and incorporated in the circuit design.

In this research, at first, a detailed workflow of building FHE systems is provided along with the associated challenges. Then, the design of a new, in-lab built bending machine to perform bending test on the prototype is articulated. Next, a one-port, DC measurement-based method is presented for measuring the individual contact resistance between the pins of an IC package and a flexible substrate used in FHE systems. Afterwards, a one-port, AC measurement-based approach for post-assembly extraction of RLC parasitics from a flexible hybrid electronics prototype is presented. In both cases, on-chip ESD protection circuits inherent in ICs are exploited to perform one-port measurements at on-board test points. In their respective studies, the techniques are subsequently employed to investigate and reveal the susceptibility of these parasitic elements inherent in the assembled FHE prototypes to the variation of the form factor upon the application of mechanical stress.

Finally, to demonstrate the impact of varying parasitics on the circuit performance and the significance of including varying parasitics in the circuit design, the start-up of a second-order Wien Bridge oscillator circuit is investigated and the effect of variation of parasitic shunt capacitance present in between the signal forward path of each node and return path on the oscillation start-up is reported. So, the scope of this research can be laid out as follows:

- A review of the workflow and its associated challenges in building FHE systems.

- Design of the in-lab built, modular bending machine.

- Extraction of the inherent parasitic contact resistance between the IC pins and the board of an FHE system and the variation thereof due to mechanical stress in form of bending using a DC-based technique.

- Extraction of inherent parasitic resistance, inductance, and capacitance of an FHE assembly and the variation thereof due to mechanical stress in form of bending using an AC-based technique.

- Investigation of the impact of the presence and variation of parasitic shunt capacitance on the start-up of a second-order Wien Bridge oscillator circuit.

#### 1.3 Thesis Outline

This thesis contains seven chapters. Chapter 1 contains the necessary background, research motivation and its scopes. In Chapter 2, details of the workflow used to design, print, assemble, and test the FHE prototypes is discussed along with the associated challenges followed by the design of an in-lab built, modular bending machine built to perform Radius of Curvature (ROC) test on the assembled prototype in Chapter 3. Chapter 4 discusses the extraction of the inherent and varying individual contact resistance between the pins of an IC package and the board of an FHE system by delineating the DC-based, one-port measurement technique. Moving on, Chapter 5 discusses the extraction of the inherent and varying RLC parasitics from an FHE assembly using an AC-based, one-port

measurement method. Finally, **Chapter 6** investigates the steady stage oscillation of a second-order Wien Bridge oscillator and discusses the impact of varying parasitic capacitance on the start up of the oscillator. The thesis ends with the conclusion in **Chapter 7**.

# Chapter 2

# A Review of The Workflow And The Challenges Associated With Building FHE Systems

Creating functional FHE systems involves steps such as, circuit design, selection of materials, printing, assembly, and testing of the assembled system. In comparison to the workflow of conventional rigid PCBs, Flexible PCB (FPCB) workflow requires additional considerations at each of these stages and has supplementary challenges. This chapter chronologically delineates the steps involved and challenges associated with the workflow of realizing FHE systems.

### 2.1 Circuit Design And Challenges

#### 2.1.1 Circuit Design

The first step of the workflow is the design of the system that involves preparing the schematic and layout of the circuit. These are designed by using standard PCB design software, e.g., Altium PCB Designer. At each level, the circuit can be simulated to observe

the ideal behavior of the circuit and later, can be used as a reference to compare the performance of the prepared prototype with. The PCB layout upon passing the design rule checks (DRC) is then converted into gerber files, which is the standard file format being used in the industry for printing patterns. In addition to generating gerber files for each layer of the FPCB, Numeric Control (NC) drill files are also generated to specify the location of sizes of the thru-holes and vias.

#### 2.1.2 Challenges

Although there are no challenges in preparing the schematic of the circuit, the design of the layout of the respective schematic gets restricted by the limitations of the printing technology. Hence, the design rules of the circuit layout have to be set in accordance with the features attainable by the printing mechanisms. The design of the layout is challenged by, but not limited to, the following features:

- Minimum IC pin-to-pin clearance.

- Minimum trace width.

- Minimum trace separation.

- Minimum footprint dimension.

- Maximum dimension of the printable area.

### 2.2 Material Selection and Challenges

This step involves selection of substrate as well as material type for the ink and adhesives. Selection criteria of each of these along with the challenges associated with them are discussed below.

#### 2.2.1 Substrate Selection And The Associated Challenges

The substrate provides the physical structure of the PCB. In the context of FHE, in addition to being flexible, for a substrate to be deemed suitable, it must fulfill several other criteria, ranging from physical and chemical properties to manufacturing cost [37]. It is to be considered that, the selection of a substrate often dictates the maximum fabrication temperature as well as the flexibility or stretchability of the circuit, among other features. The selection of a substrate is also strongly dependent on and challenged by factors such as, dimensional stability, thermal stability, curing temperature of the ink and the adhesives, solvent compatibility, and moisture absorption [38].

#### 2.2.2 Ink Selection And Associated Challenges

Basing on the requirement, inks made up of either organic or inorganic material can be selected which can be conducting, semiconducting or nonconducting in nature. For example, in case of a conductive ink, the chosen ink must be suitable for use as a conductor and must also be compatible with the printing method employed, as well with the substrate chosen. The size of the particles must be much smaller than the nozzle used to dispense the ink. Should they be too large, there is a risk of clogging a nozzle, whose replacement can be costly and time-consuming. The selection of ink is also challenged by its curing temperature as prolonged exposure of the substrate to a heightened temperature beyond its compatibility can cause critical damage. Additionally, flexibility of the cured ink is another important criterion to consider as inability to maintain conductivity when flexed can critically impair the circuit performance.

#### 2.2.3 Adhesive Selection And Associated Challenges

The adhesives in form of solder paste or epoxy are applied at the contact point of the electronic component and the substrate and then sintered by applying heat. The basic purpose of using adhesives is to keep the electronic components attached to the substrate and maintain conductivity. Additionally, in its application in FPCB realization, adhesives

have to also be able to withstand the mechanical stress applied to the assembly. The challenge of selecting appropriate adhesive material lies in the trade off between its flexibility, conductivity, sintering temperature, and adhesion.

### 2.3 Circuit Printing And Challenges

This stage involves printing of the desired patterns according to the layout prepared. In this step, the substrate is cleaned and placed on the printing area of the machine. Then upon performing necessary steps such as, calibration, alignment, and height profile calculation to ensure appropriate and uniform deposition of the ink as per requirement, the pattern is laid out. Afterwards, the printed pattern is sintered by applying heat. If vias and thru-holes are required to be drilled, they are drilled after sintering the pattern. Later, the vias are filled with ink and cured to ensure conductivity among the different layers of the FPCB.

The printing process can be either additive or subtractive. In the additive process of printing, materials are printed onto the substrate as needed, yielding the final pattern in a single step. Whereas in subtractive process, layers of materials are deposited onto the substrate and etched away during subsequent steps. For the purpose of this thesis, both additive and subtractive printing processes have been used to lay out the pattern, as per requirement. The following discussion delineates the additive printing technology employed to print on FPCBs and the challenges associated. As subtractive process is a well-established technology and its challenges have been studied extensively, this topic has not been included in this discussion.

The recent surge in the additive printing research has resulted in development of different types of additive printing mechanisms such as, Gravure, Flexography, Aerosol Jet, and Inkjet printing. As for the purpose of this thesis, desktop-inkjet based additive printing mechanism has been used to additively print the prototypes with the help of Voltera V-One printing machine, this technology is delineated below.

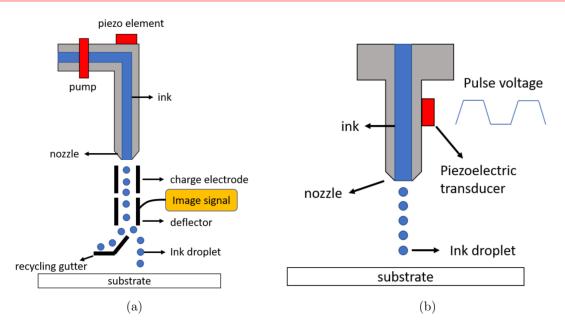

**Fig. 2.1** (a) Continuous inkjet printing (CIJ) and (b) drop-on-demand (DOD) printing.

# 2.3.1 Desktop-Inkjet Based Additive Printing Mechanism

In this printing mechanism, the prepared circuit layout is interpreted by converting it into a monochrome bitmap format. The pixels in that file then represent the areas where the ink is to be deposited. Ink deposition can be continuous or on demand. As both the techniques can deposit ink without coming in contact with the printing area, both of them can be used to generate patterns on rigid and flexible substrates [39]. Figure 2.1 illustrates the mechanisms behind these two inkjet printing techniques [40]. In case of Continuous Inkjet Printing (CIJ), the ink keeps on flowing continuously and the ink droplets are charged by an electrode to get deflected by a deflector. The image signal is applied to the deflector which enables it to deflect the unwanted droplets to the recycling gutter for reuse. On the other hand, in Drop on Demand (DOD) method, used by the Voltera V-One printing machine, the ink is deposited on the substrate only if the nozzle is switched on. A pulse voltage is applied on the piezoelectric transducer to convert the electrical signal to mechanical on-and-off signal. As a result, ink is deposited on appropriate locations based on the bitmap generated and the desired pattern is obtained.

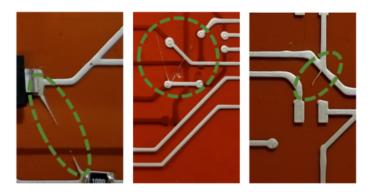

Fig. 2.2 Stringing effect.

# 2.3.2 Challenges

# **Stringing Effect**

Variation in the flow rate of the ink causes nonuniformity to the pattern printed using inkjet printing. As a result, the conductivity gets affected. For example, higher flow rate of conductive traces results in better conductivity. But it needs to be considered that this phenomenon can also lead to undesired shorts among closely spaced conductive traces due to the Stringing Effect, as illustrated in Fig. 2.2.

# Misalignment

Before printing begins, the substrate is placed manually on the printing area of the machine and attached to it using adhesives. The alignment step is required to be performed with a view to determining the position of the substrate on the printing area. It is done by holding the substrate down using clamps and then the measurement is taken by locating the diagonally separated fiducials. In case of double layer printing using this technology, the removal of the clamps and subsequent re-placement of the substrate to print on different layers is done manually. Accuracy of manual alignment with the position of the fiducials in the printing system is constrained by the limitation of visual inspection and step size in the movement of the probe. Furthermore, before moving ahead with printing on additional

**Fig. 2.3** Effect of partial and full blockages of the print nozzle caused by the curvature of the substrate.

layers, the first printed layer needs to be sintered. During sintering, the thermal expansion of substrate causes shift in alignment. To avoid this, a substrate with low CTE needs to be used, which is another challenge involved in the process.

### Miscalculation of The Height Profile

Immediately after the alignment step is performed, a probe is used to measure the height of multiple points on the substrate in order to create a height profile to ensure uniform deposition of the ink. Miscalculation in the height profile measurement can happen due to the presence of air bubbles underneath the substrate upon placing it on the printing area. If air bubble is trapped between the substrate and the platform underneath it, the bubble may be compressed by the probe until the height switch is triggered. The resulting measured height will be that of the compressed bubble, and not of its undisturbed height. During printing, this situation can lead to partial or full blockages of traces. An illustration of the phenomenon is provided in Fig. 2.3.

# 2.4 Circuit Assembly And Challenges

# 2.4.1 Circuit Assembly

After printing and sintering the desired layout, the components are assembled on the substrate. In the circuit design stage, the necessary footprints were designed which includes solder pads of appropriate dimensions onto which the electronic components are placed. In attaching the components, either metal epoxy or solder paste can be used. If solder paste is used, then the component is at first placed on the solder pad and then heat is applied locally using soldering iron to assemble the components. On the other hand, if metal epoxy is chosen to be applied, upon placing the components on the pad, epoxy is applied at appropriate places and the substrate is heated by placing it inside a heating chamber such as convection oven.

# 2.4.2 Challenges

# Thermal Treatment

While attaching the components by applying localized heat to the solder joints, the flexible substrate, materials, and electronic components undergo fast temperature transitions. Fast change of temperature increases the degradation of integrity of the component connection because of the high thermal gradient and mechanical stress imposed on the component-solder paste interface. This also has the potential to damage the substrate by forming undesired creases. On the other hand, if metal epoxy is used and subsequently cured by thermal reflow in a convection oven, then the substrate and the printed inks go through multiple thermal cycles. This might cause undesired variation to their structural integrity and also exerts additional thermal stress mostly along the solder-component interface. Moreover, the selection of the adhesive material should be made in such a way that the temperature required for the thermal reflow of the solder paste remains below the glass transition temperature,  $T_g$  of the substrate used. Also, depending upon the substrate used, mismatch of Coefficient of Temperature Expansion (CTE) among the adhesive, conductive ink, component, and substrate affects the respective interconnect interfaces, which is

Fig. 2.4 Test interface used to test printed circuits.

another challenge to be considered in this stage.

# 2.5 Electrical Testing of The Assembled Prototype And The Challenges

### 2.5.1 Post-Assembly Electrical Testing

In this stage, the assembled prototypes are tested to ascertain proper attachment of the components and measure critical circuit parameters such as circuit parasitics. Tests are needed to be performed both before and after the application of the mechanical stress for FPCBs. Post-assembly testing by means of electrical measurement allows for the verification of complex designs and offers a way to verify performance that is more reliable than mere visual or optical inspection.

In testing the assembled prototypes, electrical measurements are performed to identity any undesired shorts or opens, among other tests that might be required depending upon the application. One way to do this is by manually performing a short-circuit test on each node using a multimeter or source-meter. The resistant measured should be very close to the resistance of the printed trace. Another approach can be performing the tests using special test interfaces, as shown in Fig. 2.4 [38].

In this approach, a customized, modular test interface is built to create a bridge between the test equipment and the FPCB. Such interfaces use spring-loaded contacts to establish connection with the printed test pads on the circuit. An important feature of this type of test interface is the facility of the modular placement of the spring-loaded contacts which allows this interface to be used with a wide range of circuit designs. Using test interfaces also allows to perform all the measurements in just one step which is a tremendous advantage over performing manual measurements.

Another important post-assembly measurement criterion to assess the electrical reliability of the FHE system is that of measuring circuit parasitics. The details of their measurement methodologies along with their advantages and challenges will be delineated in chapters 3 and 4.

# 2.5.2 Challenges

One of the challenges associated with taking post-assembly electrical measurements is that the measurement probes exert pressure on the pads while establishing connections. Repeated exertion of pressure might damage the printed pads and open the circuit. Furthermore, if the probes are required to be placed on the IC pins to measure parameters such as solder joint resistance, that puts pressure on the solder joint which might cause damage to its integrity.

In addition to that, if post-solder probing is required at the IC pins, that can sometimes be very challenging to achieve for small-sized surface mount packages as their minute dimension limits the accessibility of the measurement probes. It can be even impossible to achieve for packages like QFN due to having pinouts underneath the structure.

As FPCBs are required to operate in bent conditions, their electrical performance has to be tested in such conditions as well. In these kinds of situations using test interfaces built to perform above-mentioned tests cannot be utilized because of their rigid and flat form factor which leads to assorting to manual testing of the desired electrical parameters.

**Table 2.1** Summary of bending tests of interest from IPC-9204.

| Name of the test        | Description                                               |  |

|-------------------------|-----------------------------------------------------------|--|

| name of the test        | Description                                               |  |

| Variable radius bending | Specimen is bent in a U-shape between two plates that     |  |

|                         | are then raised and compressed to cyclically change the   |  |

|                         | radius of the specimen                                    |  |

| Variable angle bend-    | Maintained under a specific tensile load, the specimen is |  |

| ing                     | flexed back and forth to a specific angle about a mandrel |  |

| Free arc bending        | Specimen is fixed horizontally to two fixtures. One fix-  |  |

|                         | ture moves back and forth, thus changing the bending      |  |

|                         | radius cyclically.                                        |  |

| Loop Bending            | Specimen is held in a looped fixture with fixed lateral   |  |

|                         | tension while a probe applies a strain on the center of   |  |

|                         | the specimen.                                             |  |

# 2.6 Post-Assembly Mechanical Testing And The Challenges

# 2.6.1 Post-Assembly Mechanical Testing

Post-assembly mechanical testing is required to be performed to evaluate the structural or mechanical integrity of the prototype. For FPCB, it is done by exerting desired mechanical stress, as demanded by the application, using a controlled setup in a controlled environment. It is done with a view to obtaining insight into the mechanical behavior of the assembled prototype under deformation for assessing its mechanical reliability and limitations.

Although there are no concrete standards that outline the mechanical testing of FHE systems, Institute of Printed Circuits (IPC) has compiled some "suggested test methods deemed appropriate for consideration in materials and properties testing" in a document titled "IPC-9204: A Guideline on Flexibility and Stretchability Test Methods for Printed Electronics". The mechanical parameters included in that document describes procedures for testing bending and stretchability among other types of tests [41]. Table 2.1 includes some of the bending tests that are relevant to the scope of this thesis.

**Fig. 2.5** Workflow of fabricating and testing FHE prototypes using additive manufacturing technology.

# 2.6.2 Challenges

A major challenge in performing mechanical tests on FHE systems is the appropriate mimicking of the mechanical stress that will be imposed on the system in real-life applications. Furthermore, there are limitations and challenges with regards to limiting the application of undesired stress on the FHE assembly while testing them in a controlled lab environment. Further review of the challenges of different types of tests and machines built to perform those tests have been provided in the following chapter while introducing the design of a bending machine capable of performing a modified version of variable radius bending test called ROC test, as required for the purpose of this thesis.

# 2.7 Chapter Summary

In this chapter, the workflow of building FHE systems is discussed. Moreover, the challenges associated with each of the stages have been mentioned. The summary of the workflow is illustrated in Fig. 2.5 which contains the sequential arrangement of each stages in the workflow from the beginning (prototype design) to the end (prototype testing).

# Chapter 3

# The Design of The Bending Machine

When designed to function in a bent condition such as in wearable devices and foldable display applications, it is necessary to test the performance and reliability of the fabricated prototype in such scenarios. That requires designing a setup which will be able to mimic the appropriate mechanical deformation and enable the researchers to observe and analyze the prototype's behavior. In this chapter, the design of a machine built and used to perform a type of bending test called the radius of curvature test, denoted in this thesis as the ROC test, is discussed. In this test, mechanical stress is applied to the assembled FHE prototype so that its contour takes the shape of the circumference of a circle with a certain radius. Then, that radius, i.e., radius of curvature is used as a metric that can be correlated to the stress applied. Moreover, this chapter contains a short literature review of the relevant bending setups that have been designed and implemented to achieve similar goals.

# 3.1 Literature Review

Several studies have been carried out to design devices which can apply one-time or repetitive mechanical stress on the prototypes in a controlled manner. The designs can broadly be categorized into two categories, namely, static bending setups and dynamic bending setups. Dynamic bending setups are designed to apply stress on the substrate to bend and

**Fig. 3.1** (a) Bending setup containing Kelvin test measurement feature, (b) Bending accessories used for bending at different radii of curvature.

flatten it in a repeatable manner whereas static bending setups are designed to bend the substrates once and hold it in that position.

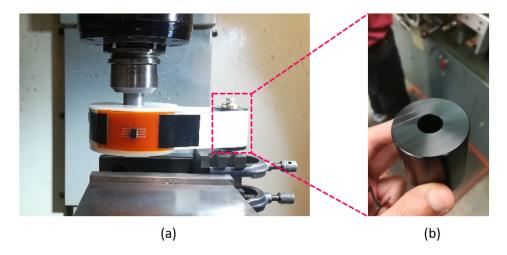

A static bending setup is most importantly comprised of a rigid structure having a desired contour. an FHE prototype is placed on and pushed against that structure to bend it accordingly. A static bending setup also contains arrangements in form of clamps or adhesives to hold the prototype in the bent shape. It might also have measurement probes built in the setup to enable performing electrical and optical measurements to assess the required parameters. Molina-Lopez et al. [42] built a static bending setup to measure the trace resistances, as shown in Fig. 3.1. This setup has modular curved surfaces which enables bending the flexible substrate to different radii of curvature. Moreover, the setup contains measurement probes to enable Kelvin test measurements on the bent substrate. Figure 3.2 illustrates the static bending mechanism used by Heger et al. [38] where mandrels were used to wrap the substrate around and apply mechanical stress; electrical measurements were taken after detaching the substrate from the mandrel and re-flattening it.

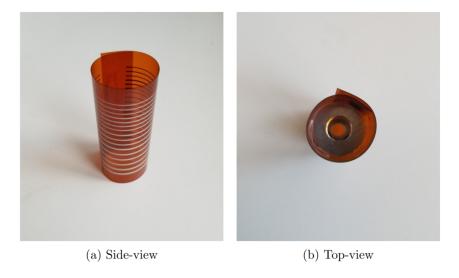

Fig. 3.2 The mandrel-based setup used to measure bent trace conductivity.