# A Fault Simulation Oriented Technique for Test Point Insertion

Michael Moscovitch

McGill University, Montreal

January 1992

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering.

## **Abstract**

With the ever increasing popularity of built-in self-test comes an increasing reliance on pseudo-random patterns for testing. Some faults within a circuit, however, may be hard to detect with pseudo-random patterns. One approach to improve the detectability of these faults involves modifying the circuit by adding test points so that it responds more favorably to the given test set.

A method for performing test point insertion in combinational circuits is presented. The method is based on a combination of fault simulation and probabilistic techniques.

An implementation of the test point insertion procedure is described and results are presented showing the effectiveness of this method on the ISCAS benchmark circuits.

## Résumé

Avec la popularité sans cesse croissante d'autovérification pour les circuits intégrés découle une dépendance sur la qualité des vecteurs pseudo-aléatoires pour fins de test. Étant donné que certains défauts de fabrication sont difficilement détectables par des vecteurs pseudo-aléatoires, il existe des méthodes pour améliorer la couverture de ces fautes. Une de ces approches consiste à modifier le circuit par l'ajout de points de test.

Une méthode pour insérer des points de test est presentée. Elle est fondée sur deux éléments: les probabilités et la simulation de fautes.

L'implémentation de la procedure est décrite. Aussi, des résultats qui démontrent l'efficacité de cette méthode sur les circuits étalons de l'ISCAS sont présentés.

# Acknowledgements

I would like to thank my thesis supervisor, Dr. Janusz Rajski for his guidance during the course of my studies. I would like to thank Fadi Maamari and Avrum Warshawski for their help with the TULIP fault simulation tool and Dimitrios Lambidonis and Eric Masson for proof reading sections of this manuscript.

I would also like to thank Jerzy Tyszer, Jacek Slaboszewicz, Michael Howells, Charles Arsenault, Rob Aitken, Henry Cox, Fidel Muradali, Ashish Pancholy and all the members of the VLSI Design Lab for their help and comments. Most of all, I would like to thank my parents for having confidence in me.

This work was supported by a scholarship from the Quebec Fonds pour la Formation de Chercheurs et l'Aide à la Recherche (FCAR) and grants from the Natural Sciences and Engineering Research Council of Canada (NSERC).

# **Contents**

| 1 | Intr                               | oduction                                     | I  |  |  |  |  |

|---|------------------------------------|----------------------------------------------|----|--|--|--|--|

| 2 | Testing and Design for Testability |                                              |    |  |  |  |  |

|   | 2.1                                | Fault Models                                 | 1  |  |  |  |  |

|   | 2.2                                | Test Pattern Generation                      | 5  |  |  |  |  |

|   | 2.3                                | Testability Assessment                       | 6  |  |  |  |  |

|   | 2.4                                | Fault Simulation                             | 7  |  |  |  |  |

|   |                                    | 2.4.1 Fault Injection                        | 7  |  |  |  |  |

|   |                                    | 2.4.2 Deductive and Concurrent Methods       | 8  |  |  |  |  |

|   |                                    | 2.4.3 Critical Path Tracing                  | 9  |  |  |  |  |

|   | 2.5                                | Testability Measures                         | 10 |  |  |  |  |

|   | 2.6                                | Design for Testability                       | 11 |  |  |  |  |

|   | 2.7                                | Fully Testable Design                        | 12 |  |  |  |  |

|   | 2.8                                | Testability Enhancement                      | 13 |  |  |  |  |

|   | 2.9                                | Test Points                                  |    |  |  |  |  |

|   | 2.10                               | Overview of the Test Point Placement Problem |    |  |  |  |  |

|   |                                    | Test Point Placement                         |    |  |  |  |  |

| 3 | Framework for Test Point Placement |                                              |    |  |  |  |  |

|   | 3.1                                | Test Patterns                                | 19 |  |  |  |  |

|   | 3.2                                | Fault Set                                    | 20 |  |  |  |  |

|   | าา                                 | Test Points                                  | 91 |  |  |  |  |

|   |                                    | 3.3.1   | Control Elements                              | . 21 |  |  |  |  |  |  |

|---|------------------------------------|---------|-----------------------------------------------|------|--|--|--|--|--|--|

|   |                                    | 3.3.2   | Simulation Models                             | . 22 |  |  |  |  |  |  |

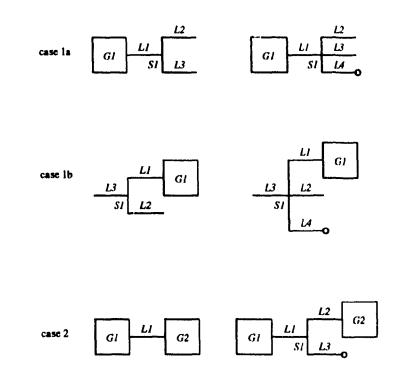

|   |                                    | 3.3.3   | Netlist Transformations                       | . 23 |  |  |  |  |  |  |

|   |                                    | 3.3.4   | Faults in Added Hardware                      | . 26 |  |  |  |  |  |  |

|   | 3.4                                | Test I  | Point Analysis Method                         | . 26 |  |  |  |  |  |  |

| 4 | Fault Detectability Information 27 |         |                                               |      |  |  |  |  |  |  |

|   | 4.1                                | The H   | Iybrid Method for Observation Points          | . 27 |  |  |  |  |  |  |

|   |                                    | 4.1.1   | Fault Simulation                              | . 28 |  |  |  |  |  |  |

|   |                                    | 4.1.2   | Calculation of Detection Probabilities        | . 30 |  |  |  |  |  |  |

|   | 4.2                                | The H   | Hybrid Method for Control Points              | . 34 |  |  |  |  |  |  |

|   |                                    | 4.2.1   | Line Selection Method                         | . 34 |  |  |  |  |  |  |

|   |                                    | 4.2.2   | Calculation of Signal Probability Values      | . 35 |  |  |  |  |  |  |

|   |                                    | 4.2.3   | Calculation of Detection Probabilities        | . 36 |  |  |  |  |  |  |

|   |                                    | 4.2.4   | Selection of Control Points                   | . 36 |  |  |  |  |  |  |

|   | 4.3                                | The F   | Cault Injection Method for Observation Points | . 37 |  |  |  |  |  |  |

|   |                                    | 4.3.1   | The Simulation Algorithm                      | . 3  |  |  |  |  |  |  |

|   |                                    | 4.3.2   | Observation Point Placement                   | . 38 |  |  |  |  |  |  |

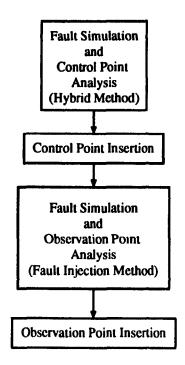

|   | 4.4                                | Test I  | Point Insertion Procedure                     | . 39 |  |  |  |  |  |  |

|   |                                    | 4.4.1   | Choice of Fault Set                           | . 39 |  |  |  |  |  |  |

|   |                                    | 4.4.2   | Stages of Analysis                            | . 40 |  |  |  |  |  |  |

| 5 | Exp                                | erime   | ental Results                                 | 42   |  |  |  |  |  |  |

|   | 5.1                                | Simul   | ation Experiment Environment                  | . 4: |  |  |  |  |  |  |

|   | 5.2                                | Bench   | ımark Circuits                                | . 4: |  |  |  |  |  |  |

|   | 5.3                                | Verific | cation of Observation Point Estimates         | . 4' |  |  |  |  |  |  |

|   | 5.4                                | Obser   | vation Points                                 | . 5  |  |  |  |  |  |  |

|   | 5.5                                | Test I  | Point Insertion                               | . 5  |  |  |  |  |  |  |

|   |                                    | 5.5.1   | Comparison with Other Methods                 | . 6  |  |  |  |  |  |  |

|   |                                    | 5.5.2   | Manual Placement of Test Points               | . 6  |  |  |  |  |  |  |

| 6  | Conclusions and Future Work | 67 |

|----|-----------------------------|----|

| Bi | liography                   | 69 |

# List of Tables

| 4.1  | Gate input/output mappings                                             | <b>3</b> 0 |

|------|------------------------------------------------------------------------|------------|

| 4.2  | Detection probability equations                                        | <b>3</b> 3 |

| 5.1  | Properties of the ISCAS 85 benchmark circuits                          | 43         |

| 5.2  | Prope ties of the ISCAS 89 benchmark circuits                          | 44         |

| 5.3  | ISCAS 85 benchmark circuits feult coverage                             | 45         |

| 5.4  | ISCAS 89 benchmark circuits fault coverage                             | 46         |

| 5.5  | Number of faults detectable at observation lines in C2670              | 47         |

| 5.6  | Fault coverage with varying number of observation points               | 50         |

| 5.7  | Coverage before and after observation point insertion (10240 patterns) | 53         |

| 5.8  | Observation point insertion with threshold of 2 faults                 | 56         |

| 5.9  | Coverage before and after test point insertion (10240 patterns)        | 58         |

| 5.10 | Test point insertion using collapsed fault set                         | 60         |

| 5.11 | Coverage before and after test point insertion (102400 patterns)       | 62         |

| 5.12 | Test point insertion with redundant faults removed                     | 63         |

| 5.13 | Test point insertion results from [STS91]                              | 64         |

# List of Figures

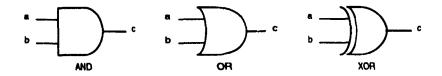

| 2.1 | Input/output signal probability relations                             | 11  |

|-----|-----------------------------------------------------------------------|-----|

| 2.2 | Fault coverage                                                        | 1.1 |

| 2.3 | Control point                                                         | 15  |

| 2.4 | Test cell                                                             | 16  |

| 2.5 | Simplified control/observe point for combinational circuit            | 16  |

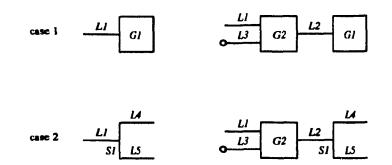

| 3.1 | Control element types                                                 | 21  |

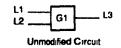

| 3.2 | Control point simulation model                                        | 23  |

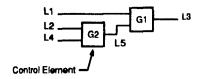

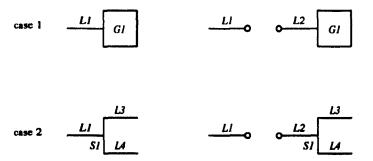

| 3.3 | Netlist transformations for observation point addition                | 21  |

| 3.4 | Netlist transformations for control point addition                    | 25  |

| 3.5 | Netlist transformations for control/observe point addition            | 25  |

| 4.1 | Gate input pattern counts                                             | 29  |

| 4.2 | Test point insertion process                                          | 41  |

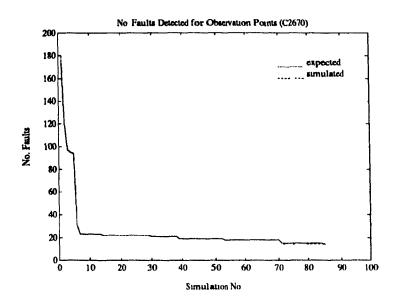

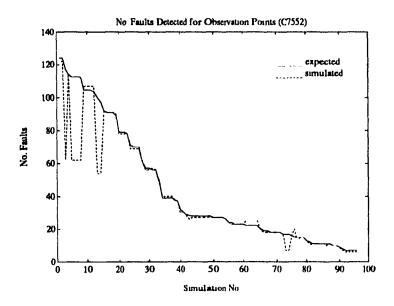

| 5.1 | Estimated vs simulated improvement for observation points             | 48  |

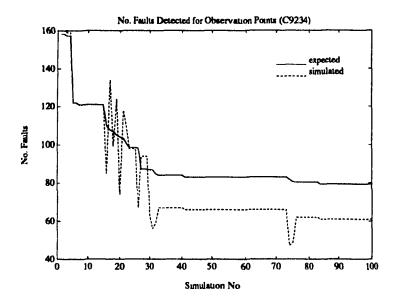

| 5.2 | Estimated vs simulated improvement for observation points             | 48  |

| 5.3 | Estimated vs simulated improvement for observation points             | 49  |

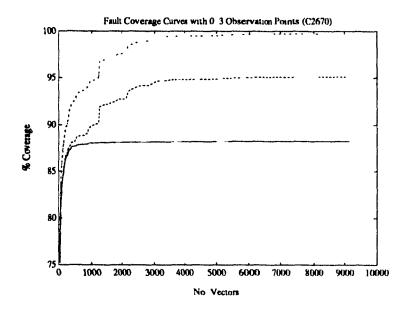

| 5.4 | Fault coverage curves for C2670 with 0 to 3 observation points        | 50  |

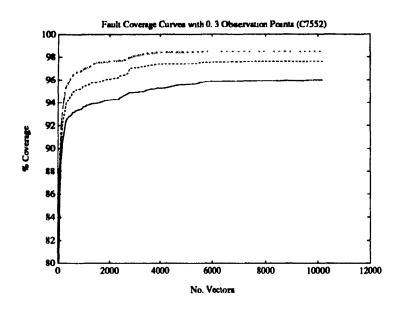

| 5.5 | Fault coverage curves for C7552 with 0 to 3 observation points        | 51  |

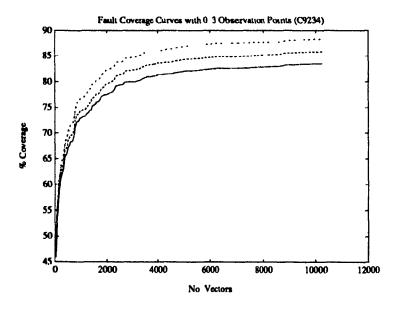

| 5.6 | Fault coverage curves for C9234 with 0 to 3 observation points        | 51  |

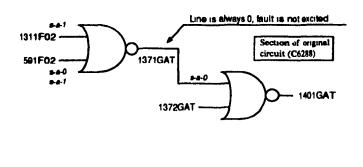

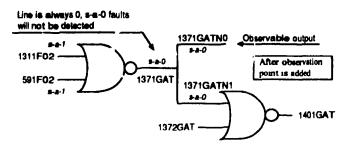

| 5.7 | Section of circuit C6288 before and after observation point insertion | 55  |

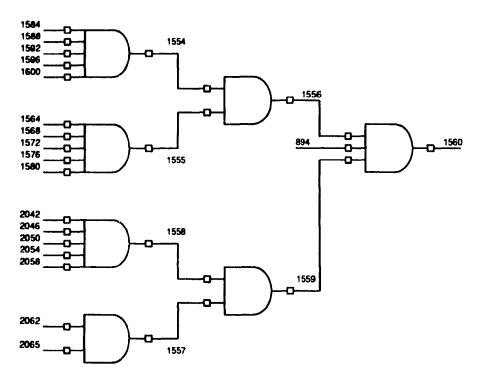

| 5 0 | Part of singuit C2670                                                 | GE. |

# Chapter 1

## Introduction

Improvements in technology are continually leading to increases in the level of integration possible for electronic circuits. Current commercial designs may include tens of millions of transistors on a single chip. The use of hardware description languages and synthesis tools has helped to manage the complexity in the design process.

As the complexity of VLSI circuits increase, the importance of testing procedures becomes more apparent. The marketplace not only demands more functionality but increased quality as well. To provide this quality at the system level, it is necessary to ensure that the individual components are of adequate quality.

The integrated circuit fabrication process is not perfect. Not all devices will function properly. The only way to guarantee a certain level of quality is through testing. The ideal testing procedure will identify all faulty parts.

The quality of a test can be evaluated in terms of the fault coverage that it provides. The higher the fault coverage, the better the test. Given the large circuits that may be designed today, it is no longer feasible to generate test vectors manually. Automated test pattern generation or random patterns must be used.

Unfortunately it requires more than just a desire to test chips after they are produced.

The chips themselves must be testable.

Traditionally, engineers entering the field of VLSI for the first time, were more concerned with design and function then with testing. This, of course, complicated the job of testing these integrated circuits.

Design for testability (DFT) techniques [WP83] have tried to address the issue of making chips more testable. DFT techniques such as scan design [And80, EW77, FKY89] are becoming increasingly popular. By linking all the registers of a chip into a scan chain, scan design allows a sequential circuit to be treated as a combinational one. This greatly simplifies the test generation process.

Deterministic test generation algorithms are exponential in time complexity and thus are costly in terms of cpu time. Alternatively, fault simulation may be used to select test vectors from a randomly generated sequence. Both of these methods require the storage of test patterns, typically in an external tester.

As an alternative to stored pattern testing, a pseudo random sequence may be generated on the fly within the tester or on the chip. Built-in self-test (BIST) [McC85, TS88] which integrates test vector generation and response compaction on chip reduces the need for expensive high speed external test equipment. A typical BIST implementation uses a pseudo random source, such as an linear feedback shift register (LFSR) to apply patterns to the circuit under test (CUT).

Not all circuits are susceptible to random patterns. Some faults within the circuit may be hard to detect with random patterns. One approach to improve the detectability of these faults is to adjust the test vectors using schemes such as weighted random patterns. Another approach involves modifying the circuit so that it responds more favorably to the given test set.

This thesis explores the latter approach in terms of the addition of control and observation points within the circuit. An approach to analyze the circuit and guide the placement of control and observation points is presented. Chapter 2 introduces some of the basic issues in testing and design for testability. Chapter 3 describes the overall framework for the test point insertion method. The method itself is described in chapter 4 along with a discussion of the implementation. Results are presented in chapter 5 followed by some concluding remarks in chapter 6.

# Chapter 2

# Testing and Design for Testability

#### 2.1 Fault Models

Integrated circuit fabrication is not a perfect process. The statistical nature of some of the processing steps removes any hope of obtaining a perfect device every time. Although a number of fault models exist, the stuck-at fault model [Eld59] is the most widely used. As the name implies, this model provides two failure modes for each line in the circuit. A line may be stuck-at 0 (stuck-at 1) in which case the line maintains the logic 0 (1) state in the faulty circuit.

Since each line in an n line circuit may have 3 states (fault free, stuck-at 1 or stuck-at 0), there are,  $3^n$  combinations to consider in general. To simplify this problem, it is assumed that only one fault is present in the circuit at a time. Under this single fault assumption, there are 2n possible faults. Although this assumption is not necessarily true, most multiple faults are detected by tests for single faults [AF81, HM86, JB87].

Stuck at faults do not model all of the failures that can occur in VLSI circuits [BART82, PRM90]. Many other fault models have been proposed including stuck open faults [Wad78] and transition faults [Koe86, WLRI87]. Stuck-at faults, however, are commonly used be-

cause of their simplicity compared to these other models.

A full fault set for a circuit contains a stuck-at-0 and stuck-at-1 fault for each line in the circuit. Some faults in this set may be equivalent. For example a stuck-at-0 fault on the inputs of an AND gate is indistinguishable from a stuck-at-0 fault on its output. Two types of equivalence relations can be observed between faults: structural equivalence and functional equivalence [MC71]. Faults are structurally equivalent when their resulting faulty circuits have identical structures, while they are functionally equivalent when their resulting faulty circuits realize the same logic function [MC71].

Equivalent faults can be grouped into equivalence classes, and only one fault per equivalence class needs to be considered. This processes, called fault collapsing, reduces the size of the fault set without any loss of information. Most structurally equivalent faults can be identified in a linear backward pass through the circuit [SM72], such as those local to a single gate. Other equivalent faults that are harder to identify are usually ignored as the non-linear algorithm required to find them would cost more than the savings achieved through their collapsing [SM72].

A fault is untestable or redundant if its presence causes no malfunction [Fuj85]. An untestable fault results when the fault cannot be excited or the fault effect does not propagate to an observable output.

#### 2.2 Test Pattern Generation

Integrated circuits are tested by applying stimuli to the circuit inputs and comparing the response at the outputs with the expected response. In digital circuits, the input stimuli and output responses normally consist of a sequence of binary logic values.

The combination of input and output values is known as a test pattern. The output values can be determined from the input values by logic simulation, thus the problem of test pattern generation is concerned with determining the input signal assignments.

For an n input circuit,  $2^n$  possible input signal assignments exist. An exhaustive test, in which every possible input signal assignment is enumerated, is impractical due to time constraints.

Practical considerations dictate that the time required to generate and apply test patterns should be reasonable. There are three methods which can be used to obtain test patterns [Bot86].

- 1. Manual generation

- 2. pseudo random pattern generation

- 3. algorithmic (or deterministic) test generation

Manual generation is usually impractical. Pseudo random patterns are easy to generate automatically. They can be generated off chip via software methods for random number generation or on chip with an LFSR.

Deterministic test pattern generation targets specific faults within the circuit. A number of algorithms exist, including the D-algorithm, PODEM [Goe81], FAN [FS83], SOCRATES [SA88], and Quest [RC90, Cox91]. The problem of algorithmic test pattern generation is NP-complete [FT82, GJ78] so heuristics are often used to improve the performance.

Test generation for sequential circuits is an even harder problem due to the memory elements in the circuit [Kau68, BHP+71].

#### 2.3 Testability Assessment

Given that all circuits are not always easily testable, it is necessary to have a method of assessing the testability of a circuit. In addition a suitable metric must be chosen. There are two possible types of circuit testability metrics, relative and absolute. Relative

metrics allow us to compare the testability of two or more circuits but do not give us any indication of how many faults are actually detected. A common metric of testability assessment is fault coverage. It provides an absolute measure of the percentage of faults detectable. Using fault simulation, an exact measure of fault coverage can be obtained.

#### 2.4 Fault Simulation

Fault simulation provides a means to evaluate test quality. Given a specific set of test patterns and faults a fault simulator will determine which faults are detected by the test set. The fault coverage is then expressed as the percentage of faults detected relative to the size of the initial fault set.

Many algorithms for fault simulation have been developed. The four major categories into which most of these algorithms can be classified are those that use: fault injection methods, deductive methods, concurrent methods and critical path tracing methods [AS88].

#### 2.4.1 Fault Injection

Fault injection is one of the most straight forward methods of fault simulation. To determine which faults are detectable by a specified test vector, a good machine simulation is performed for the test vector. The faulty circuit is simulated by injecting the fault effect at the fault site and propagating it towards the primary outputs. The fault injection process is repeated for each fault. Each fault is simulated independently of the others. The fault is considered to be detected if the fault effect reaches at least one of the primary outputs.

Once a fault has been detected, it can be removed from further simulation. This process, called fault dropping, is one of the techniques that can be used to increase the efficiency of fault simulation.

Word parallelism can also be exploited to improve the efficiency of fault simulation. During the fault simulation process, many boolean operations are performed in a repetitive manner on a large input set. Since most processors perform boolean operations in a bitwise fashion on the machine word, it is possible to use each bit to represent either a different faulty machine or a different input vector.

This technique can be applied to fault injection methods on two ways. In the parallel fault simulation method [Ses65, TS75] a computer word of w bits is associated with each line in the circuit. Each bit represents the circuit with a particular fault (or no fault). For f faults, only  $\lceil f/(w-1) \rceil$  passes per pattern are required.

Alternately, w input vectors can be processed in one computer word. Thus, on a 32 bit workstation, 32 input vectors can be processed simultaneously. This exploitation of parallelism is known as the parallel pattern evaluation technique. Parallel pattern evaluation takes advantage of the full width of the processor registers to speed up the simulation process. Using this technique, a class of fault simulation methods known as parallel pattern single fault propagation [WEF+85] (PPSFP) was developed.

#### 2.4.2 Deductive and Concurrent Methods

Deductive and concurrent fault simulation methods rely on the use of lists representing the effect of faults on each line in the circuit. This allows them to compute which faults are detected with only one pass per pattern. In a deductive fault simulator [Arm72], a list is maintained at each line of faults for which signals on the line are different from the fault free state. Fault lists are propagated by deducing the fault list on the output of a gate from the lists on its inputs using simple set operations (union and intersection).

In concurrent fault simulation [UB74] a list of faulty gates is maintained for each gate. It contains the effect of each fault on the gate if it differs from the fault free state.

#### 2.4.3 Critical Path Tracing

One of the goals of fault simulation is to determine the detectability of faults at the primary outputs in a given test set. A number of methods have been proposed to increase the efficiency of fault simulation. These methods exploit parallelism and structural properties of the circuit.

A scheme for speeding up fault simulation by partitioning the circuit in terms of its fanout free regions (FFRs) was described by Hong [Hon78]. A fanout-free region is defined as a maximal sub-circuit containing no internal fanout stems. The output of a FFR is either a primary output or a fanout stem. The inputs to a FFR are either primary inputs or fanout branches of fanout stems. Any fault in the circuit is detected if and only if:

- a) the fault is sensitized to the FFR output line and

- b) the fault is propagated from the FFR output to a primary output.

In Hong's method, the faults that propagate to their FFR output are determined using a single forward pass through the circuit. Surrogate faults are injected at the fanout stems and explicitly simulated to the primary outputs.

It was shown that criticality of lines within a FFR could be determined by a single backward pass from the output of the FFR to its inputs [AMM83]. Since explicit simulation of fanout stems is  $O(n^2)$  but critical path tracing is linear in complexity, a more efficient method of fault simulation was proposed in which critical path tracing within FFRs is performed before explicit simulation of stem faults [AS86]. If there are no faults critical to the fanout stem then explicit simulation is not needed. Further efficiency can be gained by stopping the propagation of surrogate faults at dominator lines [AS87].

These techniques reduced the amount of work required in the fault simulation process. The analysis of reconvergent fanout and the definition of stem regions bounded by exit lines results in a static reduction of the area of explicit simulation since it is performed only

within stem regions [MR90b]. In addition, the dropping of circuit areas from fault-free simulation provides a dynamic reduction in the fault simulation process [MR90a].

#### 2.5 Testability Measures

Testability measures provide information on circuit testability without the need for fault simulation. Deterministic testability measures such as the Sandia Controllability/Observability Analysis Program (SCOAP) [Gol80] are independent of the input patterns. SCOAP provides a relative measure of testability.

Probabilistic testability measures rely on primary input signal probabilities. The 0 (1) controllability of a node is defined as the probability of setting the node to a logical 0 (1) given a random input vector. Parker and McCluskey [PM75] showed and exact method of calculating the signal probabilities in a combinational circuit using exponent suppression.

It has been shown that computing the exact signal probabilities of the nodes in a general combinational circuit is NP-complete [Wun85]. Testability measures can trade off accuracy in the interest of speed. The Controllability/Observability Program (COP) [Big84] estimates detection probabilities in linear time by not taking into account the statistical dependence of signals at a reconvergent point. The 0 and 1 controllabilities, denotes by  $C_0(l)$  and  $C_1(l)$  respectively for a line l, are propagated from the primary inputs to the primary outputs using the gate input/output signal probability relations described in Figure 2.1.

The Probabilistic Estimation of Digital Circuit Testability (PREDICT) [SPA85] method uses a graph approach to compute signal probabilities exactly using Shannon's expansion.

An approximation procedure provides a tradeoff between accuracy and computational cost.

Statistical approaches rely on simulation data to obtain statistical estimates of controllability and observability. Statistical Fault Analysis (STAFAN) [JA84] computes signal

$$P_z = 1 - P \tag{2.1}$$

$$P_z = \prod_{i=1}^n P_i \tag{2.2}$$

$$P_z = 1 - \prod_{i=1}^{n} (1 - P_i)$$

(2.3)

Figure 2.1: Input/output signal probability relations

controllabilities from true-value simulation and then approximates observabilities deductively. The 0 and 1 controllabilities of a line l, obtained by counting the number of times *l* is at logic 0 or logic 1 during the true-value simulation of N vectors is:

$$C_0(l) = \frac{zero - count}{N} \tag{2.4}$$

$$C_0(l) = \frac{zero - count}{N}$$

$$C_1(l) = \frac{one - count}{N}$$

(2.4)

#### Design for Testability 2.6

To ease the test generation problem, design for testability techniques were developed. These techniques can be divided into two classes: ad hoc techniques and structured approaches [WP79].

Ad hoc techniques include circuit partitioning, and test point insertion. Structured approaches include scan design and build in logic block observation (BILBO) [KMZ79]. One of the more popular DFT techniques is scan design.

Scan design allows the registers in a sequential circuit to be connected into one or more

shift register type structures called scan chains. These scan chains can be used to serially shift data in and out of the registers thus providing observability and controllability.

Using scan design techniques, a sequential circuit can be treated as a combinational circuit for test generation purposes. This greatly simplifies the test generation problem

A natural extension of these methods is built in self-test (BIST). A typical implementation of BIST uses an LFSR to generate pseudo random patterns. The output of the circuit is compacted to form a signature. A faulty signature indicates a faulty device.

#### 2.7 Fully Testable Design

The ideal scenario for testing is to have a fully testable design. An number of methods have been proposed to accomplish this feat by modifying the circuit. Hayes showed that any circuit can be modified by embedding XOR gates so that the resulting circuit requires only five test patterns [Hay74]. The circuit is first decomposed into two input gates and all inverters are removed. XOR gates with controllable inputs and observable outputs are inserted in the input lines of every gate. A method was also given for determining the input patterns. Later in this chapter, it will be shown that XOR gates can be used to improve testability by providing a means to control the signal probabilities on specific lines in a circuit.

In general n+1 test patterns are required to detect all single and multiple stuck-at faults on any n-input AND, OR, NAND, NOR gate. At least 3 test patterns are required to test a 2-input AND gate. Thus 3 can be thought of as a lower bound on the number of test patterns needed to test all stuck at faults in a circuit. Saluja and Reddy [SR74] showed that any circuit can be modified such that three test patterns are sufficient to detect all single and multiple stuck-at faults in a circuit.

The main disadvantage of these methods is that they require a large amount of circuit area. The number of gates in the circuit can easily be doubled by these methods. In

addition, the number of extra primary inputs and outputs needed can be quite large. Most practical applications cannot afford this overhead.

#### 2.8 Testability Enhancement

With the ever increasing popularity of built in self test (BIST) and scan design, comes an increase in the reliance upon random patterns for testing. The appeal of random patterns lies in the ease with which a pseudo-random sequence can be generated on chip using an LFSR.

The effectiveness of the random patterns must be assessed. Using fault simulation to assess the coverage of randomly generated patterns we can determine if any untested faults remain. The issue of how to test the faults that are untested by the random patterns must then be addressed. Deterministic test pattern generation could be used to cover these random resistant faults, but that may require the use of two testing methods, external stored pattern testing and BIST. In fact, we may have used random patterns to avoid the use of costly deterministic test pattern generation in the first place.

BIST is one example of a methodology where a finite number of pseudo-random patterns are used to test a combinational circuit. Practical considerations such as time, limit the test length to some number of vectors  $N_{max}$ . The presence of random resistant faults, however, may require large test lengths to achieve the required coverage.

Given that the pseudo random source is in fact deterministic, such as an LFSR, the test set will always consist of the same vectors. Once a particular test set is decided upon, fault simulation can be performed on the circuit using these vectors and the coverage of single stuck-at faults can be determined. The coverage obtained, however, may not be sufficient to assure the required defect level. The problem facing us is how to improve the coverage of the given test set.

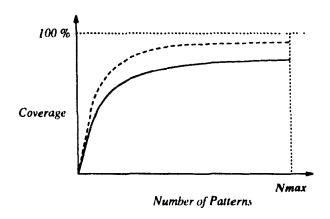

Figure 2.2 shows a typical fault coverage curve where the fault coverage is plotted as

Figure 2.2: Fault coverage

a function of the number of vectors simulated. The solid curve illustrates the coverage obtained for the circuit, which may not be as high as we would like after  $N_{max}$  patterns. If we cannot afford to apply more than  $N_{max}$  vectors then we must find ways to obtain a higher coverage with those same  $N_{max}$  vectors. One way to do this is to increase the testability of the circuit and thus obtain fault coverage similar to the dashed curve. The testability can be increased with test points that allow signals internal to the circuit to be observed or controlled. Observation test points are essential if we do not want to modify the circuit but are still interested in increasing observability as in contactless probing and increased observation techniques such as cross-check [STW89]

Using scan design techniques the circuit under test can be treated as a combinational circuit. In an effort to increase the testability of these circuits and/or reduce the test lengths the use of test points has been proposed [HF74, STS91, IB89, BT86, SYKK91].

These methods rely on determining the controllability of circuit nodes and the detectability of faults through probabilistic methods and/or simulation.

#### 2.9 Test Points

The term test point refers to a connection allowing a circuit node to be either observed, controlled or both. Fault detection requires that the fault be exited and the resulting fault effect propagated to an observable node in the circuit. It is not always possible to propagate the fault to existing observable nodes such as the primary outputs. Thus, it might be necessary to add a connection to some node in the circuit such that it becomes an observable output. A test point which performs this function is called an observation test point or observation point.

The function of a control test point or control point is to stimulate the propagation of faults through a gate. A control point consists of a control element which is inserted in the signal path of an input to a gate and increases the controllability of that gate input. A control point is typically used on lines that have poor controllability to adjust the signal probability to a value of 0.5. The control element consists of a gate, such as an AND, OR or XOR, of the appropriate type to affect the signal probability in the desired manner. Thus an OR gate would be used to increase the signal probability to 0.5 and an AND gate would be used to decrease it to 0.5. An XOR gate can be used to either increase or decrease the signal probability to an equiprobable state.

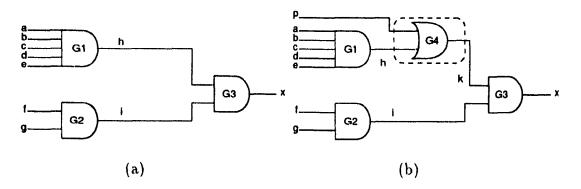

Figure 2.3: Control point

Figure 2.3a illustrates part of a circuit that contains random resistant faults. If output

h of gate G1 has a low signal probability or if there is some negative correlation between h and i then it may be difficult for faults to propagate through gate G3. To remedy this, a control point can be inserted as shown in figure 2.3b. Input p is driven by an equiprobable random source. The gate G4 serves to increase the signal probability of input k to gate G3. This will aid the propagation of faults from line i to line x.

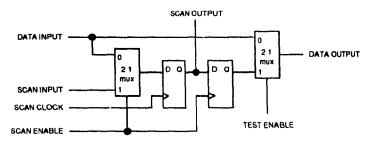

Figure 2.4: Test cell

To provide controllability and observability at a single node in the circuit, both a control point and observation point may be used. An alternative method is to use a test-cell [HHB89]. Figure 2.4 shows an implementation of a test-cell [HHB89].

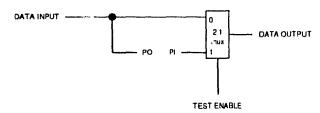

Figure 2.5: Simplified control/observe point for combinational circuit

This circuit shows some of the hardware used to construct the scan path. In the case of a combinational circuit, a more simplified method can be used as shown in Figure 2.5. The line to be observed is connected to a primary output and a multiplexor is used to select a primary input to drive the line when test mode is enabled. When test mode is disabled, the logic value on the line is unaffected. When scan design is used, the primary input and output shown in the figure will be connected to a register in the scan chain and thus the structure will be similar to Figure 2.4.

#### 2.10 Overview of the Test Point Placement Problem

When faced with testing an integrated circuit, a test engineer's main goal is to develop a test that will minimize the number of faulty chips that are ultimately shipped to customers. In many cases this means the test should provide 100% fault coverage.

In order to improved the testability of combinational circuits, they can be modified by the addition of control and/or observation test points. The main challenge is determining the number of test points needed and their placement. The benefit of the added test points is improved coverage at the cost of increased circuit area and computation time. An optimal solution to this problem will allow complete coverage of all detectable faults with a minimum number of test points.

Considerations such as processing time may make it impractical to obtain an optimal solution for large circuits. In a real life situation, we have a limited amount of CPU time and circuit area. Since high fault coverage is our main goal, we can relax our constraints on CPU time and circuit area. Rather than minimizing them, we will require that they fall within reasonable values.

#### 2.11 Test Point Placement

The problem of placing test points within a circuit to enhance its testability is an old one, although it is still the subject of continued research. One of the earliest methods was a labeling approach [HF74], however there were difficulties in obtaining minimal labeling for a general combinational circuit.

The placement of observation points can be determined from fault detectability information. The detectability of faults within a circuit can be determined through fault simulation or testability measures such as those described in section 2.5.

Simulation can be used to model the fault effects within a circuit. As a fault effect is

propagated through the circuit, the detectability information can be accumulated. After all the test patterns are simulated an exact measure of the detectability of each fault at each line is available. PPSFP type fault simulators have been used to guide the placement of test points [BT86, IB89].

Fault simulation can provide exact results, but has traditionally required large amounts of cpu time compared to probabilistic estimations. Probabilistic methods calculate the detectability of faults based upon some initial information such as the signal probabilities in the circuit. The signal probabilities can be determined through simulation or probabilisticly given the signal probabilities at the inputs. Probabilistic methods for computing the exact detection probability can be exponential in complexity, but, accuracy can be traded for speed.

In [STS91], the COP testability measure is use to guide the placement of test points A cost function is used to obtain a global measure for the entire circuit.

The COP testability measure is also used in [SYKK91]. Heuristics are used to solve the test point placement problem by grouping test points using the concept of fault sectors. A fault sector S is a set of faults of the same type (hard-to-control or hard-to-observe) and located in the fan-in or fanout of S. All the nodes for which the detection probability is enhanced by inserting a test point at S are grouped in a sector with its origin at S. Control (observation) points at the origin of the fault sector S cover faults in S in their fanout (fan-in) cone.

The method proposed in this thesis makes use of both fault simulation and probabilistic calculations. The techniques used are closely tied to the fault simulation framework on which the implementation is based.

# Chapter 3

# Framework for Test Point Placement

In this thesis, a framework for test point placement based upon fault simulation is developed. The test point placement relies on detectability information obtained from the circuit. This detectability information is obtained through simulation and probabilistic methods.

#### 3.1 Test Patterns

Before the analysis of the circuit can begin, the test patterns and fault set must be specified. In most real life testing situations, the test patterns are deterministic. This holds for both stored patterns or pseudo random patterns such as those generated by an LFSR. Thus, the test patterns are known in advance and can be used in the analysis.

For many types of pseudo random generators such as LFSRs the patterns applied to each input is dependent on the number of inputs. It is important to maintain the same set of test patterns throughout the test point insertion process, even if primary inputs

are added to the circuit. The test patterns should be determined keeping in mind that additional primary inputs will be needed for the addition of control points.

#### 3.2 Fault Set

The amount of memory needed for the analysis is related to the size of the fault set. It is desirable to have only those faults that we are interested in present in the fault set. Faults that are already detected can be removed from the fault set. The set of undetected faults should be used for the analysis.

This fault set is no longer valid once the circuit has been modified by the addition of control points. Control points may reduce the coverage by blocking the propagation of faults. Faults that were detected in the original circuit may be undetected in the modified circuit.

Fault collapsing can be used to reduce the size of a fault set. In a collapsed fault set, many equivalent faults can be represented by a single fault. Because of this, the coverage value obtained for a collapsed fault set may not be the same as that obtained for the full fault set. This also makes it difficult to compare the number of faults detectable by different test points. A lookup table can be used maintain the number of faults corresponding to each fault in the collapsed fault set.

#### 3.3 Test Points

To analyze the circuit, the effect of the test points within the circuit must be measured. Rather than actually modifying the circuit under analysis, a model is used for simulation purposes. To verify the results and to create a new testable netlist a series of netlist transformations are used to insert the test points into the circuit netlist.

#### 3.3.1 Control Elements

Figure 3.1: Control element types

The concept of a test point was introduced in section 2.9, where it was stated that a control point could be used to adjust the signal probability on a specific line. The three common types of control elements used for this purpose are the AND, OR and XOR gates, shown in Figure 3.1.

Each of these gates has a different effect on the signal probability of the line in which it is inserted. Using the labeling in Figure 3.1, the signal probability of the original line can be denoted by  $P_1^a$  and that of the modified line by  $P_1^c$ . The control input b will be driven by a equiprobable random source so that  $P_1^b = 0.5$ .

The signal probability at the output of an XOR gate is given by the following expression:

$$P_1^c = P_1^a P_0^b + P_0^a P_1^b$$

With  $P_1^b = 0.5$ , this reduces to

$$P_1^c = 0.5(P_1^a + P_0^a) = 0.5.$$

The XOR gate can be used to set the signal probability to 0.5 independently of the original value. An XOR gate, however, requires more area than an AND or OR gate. The AND gate can be used to lower the signal probability according to the following relation:

$$P_1^c = P_1^a P_1^b.$$

The OR gate, which has the relation

7

$$P_1^c = P_1^a + P_1^b - P_1^a P_1^b$$

can be used to raise the signal probability. Since the AND gate reduces the signal probability by 50%, the target value of 0.5 can only be reached if the original probability was 1.0. Thus it is desirable to use the AND gate only when the signal probability is close to 1. Similarly, an OR gate could be used if the signal probability is close to 0.

When control elements are inserted in a circuit, they may affect the detection probabilities of the faults that propagate through them. The effect depends on the type of control element. An XOR gate does not alter the detection probability. In the case of both AND and OR gates, the fault effect can only propagate when the other input is set to a non-controlling value. This means that the detection probability will be reduced. When a random source is used, the detection probability will be halved.

#### 3.3.2 Simulation Models

The simulation models are used to represent the effects of a test point within the circuit. In the case of an observation point, the model is very simple. An observation point provides full observability at a particular line in the circuit but does not disturb any of the logic values within the circuit. It can be modeled by the ability to access fault detectability information at a specific line. By providing access to fault detectability information on all lines, every possible observation point can be modeled at once.

Control points require a more complicated model. They affect the logic values within the circuit. It is necessary to do some form of re-analysis for each new combination of control points. The control point can be modeled by changing the signal probability values in the circuit at the affected point and recalculating within the affected cone. For simplicity, only a single control point is modeled at a time.

The following steps are used to model a control point as shown in Figure 3.2 for simulation purposes.

• Set signal probability on line L1

Figure 3.2: Control point simulation model

• Adjust detection probability of faults propagating through line L1

#### 3.3.3 Netlist Transformations

To physically insert a test point into the circuit netlist a series of netlist transformations are defined. These local transformations insert additional lines and gates into the circuit. Each of the transformations is illustrated by showing the original section of the circuit on the left of the figure and the result of the transformation on the right. For clarity, only the gates and lines that are involved in the transformation are shown.

Observation point insertion is accomplished by the addition of a fanout stem into the netlist, in which one of the branches becomes a primary output, the other branch connects to the original destination of the line which is being made observable. There are three possible cases, which are shown in Figure 3.3.

Case 1a: The line L1 is an input to a stem

Add one more fanout branch to stem S1 (L4) which is a primary output

Case 1b: The line L1 is fanout branch of a stem

Add one more fanout to stem S1 (L4) which is a primary output

Figure 3.3: Netlist transformations for observation point addition

Case 2: The line L1 is between two gates, G1 and G2.

Add stem S1 with input L1 and fanout lines L2, L3. L2 connects to G2 in place of L1 and L3 is a primary output.

Control point insertion is accomplished by the addition of an extra controlling gate having one input controlled by a primary input of the circuit. This gate serves to modulate the signal probability of the line. There are two possible cases to consider when inserting the control point, as shown in Figure 3.4.

Case 1: The line L1 is an input to a gate G1

Add input L3, gate G2 and line L2.

Case 2: The line L1 is an input to a stem S1

Add input L3, gate G2 and line L2.

Figure 3.4: Netlist transformations for control point addition

Inserting a combined control and observation point can be done as shown in Figure 3.5. The line is split into a primary input and output. This transformation models the circuit in test mode. Under normal operation the circuit should function as it did before the transformation. This can be accomplished with a multiplexor as shown in Figure 2.5.

Figure 3.5: Netlist transformations for control/observe point addition

Case 1: The line L1 is an input to a gate G1

L1 becomes output and add new input line L2 which becomes input to gate G1.

Case 2: The line L1 is an input to a stem S1

L1 becomes output and add new input line L2 which becomes input to stem S1.

#### 3.3.4 Faults in Added Hardware

Test point insertion requires the addition of circuit elements. With these additional elements come additional faults. When a circuit is modified in such a manner, its fault set should be updated to take these extra faults into account. Using the stuck-at fault model, the simplest way to accomplish this is to add a new pair of stuck-at-0 and stuck-at-1 faults on each new line added to the circuit.

#### 3.4 Test Point Analysis Method

In order to determine the best location for test points, an analysis of the circuit is performed. This analysis consists of determining fault detectability information. The fault detectability information actually gives us information about observability in the circuit. It tells us how many faults we can expect to detect if an observation point was placed at a particular line. It does not give us information on how a control point will affect the circuit. To determine the effect of a control point, the fault detectability information must be re-evaluated in the presence of the control point. Rather than repeating a costly fault simulation, this is performed by probabilistic methods. The effect of the control points is reflected in the fault detectability information at the primary outputs of the circuit.

Fault detectability information is available for every possible observation point. Determining this information for every possible control point would be computationally expensive. To reduce the CPU time requirement, only a select set of interesting lines are evaluated as possible control points.

# Chapter 4

# Fault Detectability Information

This chapter presents two methods for determining fault detectability information (FDI) within a combinational circuit, the Hybrid method and the Fault Injection method. Both methods involve fault simulation. The Hybrid method is based on a combination of fault simulation and probabilistic methods. It sacrifices accuracy for speed by providing estimates of the fault detectability information. This method is used for both control and observation point placement.

The Fault Injection method is based on a parallel pattern single fault propagation (PPSFP) fault simulator. It provides exact fault detectability information. It is only used for observation point placement. As this is a simulation based method, the multiple iterations that would be required to use this method for control point placement would be costly.

#### 4.1 The Hybrid Method for Observation Points

In this section we describe a method for estimating the number of faults detectable at a particular line in a combinational circuit. This information is then used to guide the placement of observation points. This method uses a hybrid of fault simulation and probabilistic methods. The method consists of two phases. First, fault simulation is performed to determine controllability and fault detectability within fanout-free regions of the circuit. The fault simulation is based upon the Tulip [MR90a] simulator. The detection probabilities are then propagated from the fanout stems towards the primary outputs using probabilistic methods.

Section 4.1.1 begins with a description of the fault simulation procedure and then describes the calculation of the detection probabilities in section 4.1.2.

#### 4.1.1 Fault Simulation

Efficient fault simulation techniques that avoid simulating parts of the circuit since they are concerned with detectability at the primary outputs, complicate the determination of detectability information within the circuit. Critical path tracing, performed within fanout-free regions from the fanout stems, does not explicitly guarantee the information on what faults are detectable and how far they propagate. The simulation of stem faults can be avoided in some cases by determining the detectability of exit lines first. Reduction of the fault-free simulation means that controllability information may not be determined in all areas of the circuit. In order to determine detectability information within FFRs, additional tracing is performed. Detectability information outside the FFRs is determined by probabilistic methods after the fault simulation is complete. As the fault simulation progresses, detected faults are dropped (fault dropping). Active FFRs are those that contain undetected faults or exit lines of an active stem. Fault-free simulation is performed on all active FFRs. Controllability information for inactive FFRs is not needed.

The fault simulation phase provides exact controllability values for the active areas of the circuit as well as detectability values within FFRs. The fault simulation is performed according to the following algorithm.

#### fault\_simulation{

Perform fault-free simulation and collect controllability information

- Trace active FFRs and simulate stem faults

- Determine detectability within active FFRs

}

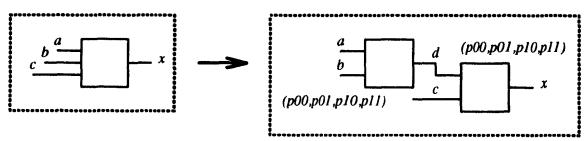

Fault simulation is used to capture the properties of reconvergent fanout, which may not be adequately modeled by probabilistic methods. The fault-free simulation provides exact controllability values throughout the circuit. To capture the correlation between signals, pattern counting is performed at each gate. In order to ease the storage requirements all possible combinations of signals on multi-input gates are not considered. Instead, only n-1 pairs of signals are considered for an n input gate. Moreover, the pairs that are considered are those that would arise if the network was transformed into an equivalent circuit with two input gates. The fault free patterns are counted for each pair to determine four probabilities  $(P_{00}, P_{01}, P_{10}, P_{11})$  as shown in Figure 4.1, where  $P_{xy}$  indicates the probability that an x will occur on the first input and a y will occur on the second.

Figure 4.1: Gate input pattern counts

Within each fanout-free region detectability information is collected for those faults internal to the region. Critical path tracing is performed within fanout-free regions with respect to each line to determine a count of the number of times a fault is detectable on that line.

To increase the diagnostic resolution, the polarity of faults is also captured. The detectability information is composed of two probabilities,  $P_D$  and  $P_D$ , representing the

probability of detecting a specific fault as a D or D on a particular line. A list is main tained on each line containing the fault identities and detection probabilities. A fault can propagate to a line in two forms, as a D or as a D. The D symbol represents a 1 in the fault-free circuit and a 0 in the faulty circuit.

### 4.1.2 Calculation of Detection Probabilities

Initial values of the detection probability within fanout-free region are determined from simulation as the ratio (f/T) of the detection count (f) to the total number of patterns simulated (T).

Probabilistic methods are then used to propagate the detectability information forward towards the primary outputs. Each fault is propagated in a levelized fashion starting from the output stem of the fanout-free region containing the fault.

The mappings in Table 4.1 describes the equations used to propagate the detection probabilities through a gate.

| AND     | 0 | $ar{D}$        | 1           | D | OR      | 0           | $\tilde{D}$ | 1 | D | XOR | U | Ď | 1 | D | NO | T |

|---------|---|----------------|-------------|---|---------|-------------|-------------|---|---|-----|---|---|---|---|----|---|

| 0       | 0 | 0              | 0           | 0 | 0       | 0           | Ď           | 1 | D | 0   | 0 | Ď | 1 | D | 0  | I |

| $ar{D}$ | 0 | $ar{	ilde{D}}$ | $ar{ar{D}}$ | 0 | $ar{D}$ | $\tilde{D}$ | $ar{ar{D}}$ | 1 | 1 | D   | D | 0 | D | 1 | D  | D |

| 1       | 0 | $ar{D}$        | 1           | D | 1       | 1           | 1           | 1 | 1 | 1   | 1 | D | 0 | D | 1  | 0 |

| D       | 0 | 0              | D           | D | D       | D           | 1           | 1 | D | D   | D | 1 | D | 0 | D  | D |

Table 4.1: Gate input/output mappings

We now derive the propagation equations for an AND gate. Consider one of the terms (T) required to produce a D for the AND gate in Table 4.1. The probability of a D on one input and a 1 on the other is indicated as  $T = P(A = D \cap B = 1)$ , where T is used as a shorthand notation and A and B represent the gate inputs. We can expand this to explicitly indicate the fault-free and faulty states and write  $P(A = 1 \cap A' = 0 \cap B = 1)$ .

$1 \cap B' = 1$ ). Using Bayes law, we can convert this to a conditional probability,

$$T = P(A = 1 \cap A' = 0 \mid B = 1 \cap B' = 1)P(B = 1 \cap B' = 1)$$

where the prime indicates the faulty state of the line.

During the simulation we collect information on the correlation of the fault-free signals, however, we do not have information about the correlation between faults on different inputs to a gate. At this point, we make the assumption that faults on the inputs to a gate are independent. This, of course, is not true when reconvergence is involved and will lead to errors in the estimation. Assuming faults on A and B are independent implies that

$$P(A = 1 \cap A' = 0 \mid B = 1 \cap B' = 1) = P(A = 1 \cap A' = 0 \mid B = 1 \cap B' = 0).$$

We then remove the dependence on B' and apply Bayes law to get,

$$T = P(A = 1 \cap A' = 0 \mid B = 1)P(B = 1 \cap B' = 1)$$

(4.1)

$$= \frac{P(A=1 \cap A'=0 \cap B=1)P(B=1 \cap B'=1)}{P(B=1)}$$

(4.2)

We can apply the same method to the first term of 4.2.

$$P(A = 1 \cap A' = 0 \cap B = 1) = P(B = 1 \mid A = 1 \cap A' = 0)P(A = 1 \cap A' = 0)$$

$$= P(B = 1 \mid A = 1)P(A = 1 \mid A' = 0)$$

$$= \frac{P(B = 1 \cap A = 1)P(A = 1 \cap A' = 0)}{P(A = 1)}$$

(4.3)

Substituting 4.3 back into 4.2,

$$T = \frac{P(B=1 \cap A=1)P(B=1 \cap B'=1)P(A=1 \cap A'=0)}{P(A=1)P(B=1)}$$

(4.4)

Given that  $P(B=1) = P(B=1 \cap B'=1) + P(B=1 \cap B'=0)$  we can substitute  $P(B=1 \cap B'=1) = P_{01} + P_{11} - P_D^b$  in 4.4 and get

$$T = \frac{P_{11}(P_{01} + P_{11} - P_D^b)P_D^a}{(P_{10} + P_{11})(P_{01} + P_{11})}$$

Note that T is dependent on the probability that both inputs are 1, a D type fault is present on the a input and the b input has no fault effect on it. The denominator can be simplified by representing the probability of a 1 on line a as  $P_1^a$ .

Using the above method, the equations for the AND gate are defined as,

$$P_D^c = P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 1) + P(A = 1 \cap A' = 1 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' = 1 \cap B' = 1 \cap B' = 0) + P(A = 1 \cap B' =$$

$$P_{D}^{c} = P(A = 0 \cap A' = 1 \cap B = 1 \cap B' = 1) + P(A = 1 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap B' = 1) + P$$

The equations for other gate types can be derived in a similar manner. Table 4.2 shows the equations needed for all the logic gates.

Using the equations defined above to propagate the detection probabilities, a list is associated with each line. This list contains fault identities and their detection probability. In order to provide a single measure of the relative merit of all potential observation points, the lines are ranked according to the average number of faults detectable at that line. The average number of faults detectable is calculated as,

$$N_{avg} = \sum_{i \in F} 1 - (1 - P_i)^n,$$

where n is the total number of patterns and F is the set of faults in the fault list at the line. The individual probabilities  $P_1 = P_D + P_D$  are the probabilities of detecting a fault as either D or  $\bar{D}$  on the line.

$$P_{D}^{c} = P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 1) + P(A = 1 \cap A' = 1 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B = 1 \cap B' = 1) + P(A = 1 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap B'$$

$$P_{D}^{c} = P(A = 0 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 0) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 0) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' = 0 \cap B' = 0) + P(A = 0 \cap A' =$$

OR.

$$P_D^c = P(A = 0 \cap A' = 1 \cap B = 1 \cap B' = 1) + P(A = 0 \cap A' = 0 \cap B = 1 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 1 \cap B = 0 \cap A' = 0 \cap B' = 0) + P(A = 1 \cap A' = 1 \cap B = 0 \cap B' = 1) + P(A = 1 \cap B = 0 \cap A' = 0 \cap B' = 0) + P(A = 1 \cap B' = 0) + P(A = 1 \cap B' = 0) + P(A = 1 \cap B' = 0) + P(A = 0 \cap B = 0 \cap A' = 1 \cap B' = 0) + P(A = 0 \cap B = 0 \cap A' = 0 \cap B' = 1) + P(A = 1 \cap B = 1 \cap A' = 1 \cap B' = 0) + P(A = 1 \cap B = 1 \cap A' = 0 \cap B' = 1) + P(A = 1 \cap B = 1 \cap A' = 0 \cap B' = 1) + P(A = 1 \cap B' = 0) + P(A' = 0 \cap B' = 1) + P(A' = 0 \cap B' = 0) +$$

$$P_D^c = P_D^a$$

$$P_D^c = P_D^a$$

Table 4.2: Detection probability equations

## 4.2 The Hybrid Method for Control Points

Improving the observability of a circuit is not always enough to guarantee 100% fault coverage. There may exist faults which are not exited by the particular test set. The addition of observation points will not help these faults. The problem is the controllability of nodes in the vicinity of the fault site.

This section discusses the placement of control points within the circuit to improve the controllability of specific nodes within the circuit.

The control points are used to adjust the signal probability of a specific line to a value close to 0.5. To determine which lines are good candidates for control points, a series of heuristics are applied. The process takes place in stages. First a rough selection criteria is used to create a set of lines. The lines in this set are then examined one at a time. The fault detection probabilities are recalculated based on the line having a probability of 0.5. An average value of faults detectable at the primary outputs is then determined. After all the lines are examined, the estimates of the average number of faults detectable due to each control point site is compared.

### 4.2.1 Line Selection Method

The initial set of lines is created based on the signal probabilities in the circuit. The signal probability information for each line is collected during the fault free simulation. Using this information, a set of lines is created. Each line is added to the set based upon the following heuristic.

- Perform levelized traversal of gates from inputs to outputs.

- Examine each gate G which has not been dropped from fault free simulation.

- For each input  $L_i$  to gate G with non-empty list of faults on the other inputs and probability of controlling value greater than or equal to a set threshold value

- add  $L_i$  to selected set

- trace backward through the circuit from line  $L_i$  and add the input line of the first stems encountered on each path to the selected set.

## 4.2.2 Calculation of Signal Probability Values

The signal probability values in the unmodified circuit are obtained through simulation as shown in the following equations, where  $P_{xy}$  represents the probability of obtaining the values xy on a pair of inputs to a gate.

$$P_1^a = P_{10} + P_{11}$$

$$P_1^b = P_{01} + P_{11}$$

$$P_0^a = P_{00} + P_{01}$$

$$P_0^b = P_{00} + P_{10}$$

To determine the effect of a control point at a particular line, the signal probability of that line is set to 0.5 and the signal probabilities are recalculated in the areas of the circuit that are affected. The signal probability values for the circuit with a control point added are calculated as in the COP testability measure. These calculations do not take into account any correlation between signals in the circuit.

$$P_{00}' = P_0'^a P_0'^b$$

$$P'_{01} = P'^{a}_{0} P'^{b}_{1}$$

$$P_{10}' = P_1'^a P_0'^b$$

$$P_{11}' = P_1'^a P_1'^b$$

### 4.2.3 Calculation of Detection Probabilities

The detection probabilities of faults are measured within each fanout-free region during simulation. Detection probabilities are calculated for the whole circuit using equations in Table 4.2 derived in section 4.1.2. These equations try to take into account some of the correlation between the inputs to a gate.

To determine the effect of a control point, the detection probabilities are recalculated assuming the presence of the control point. In this case, a simpler method is used. The contribution to the detection probability of a fault on line c due to a fault on line a is calculated as the probability that the fault is present at the input a to the gate and all the other inputs have non-controlling values.

$$P_D^c = (\text{Prob. non controlling value}) \times P_D^a$$

The total detection probability  $P_D^c$  is calculated as the sum of contributions from the fault on each of the inputs to the gate.

### 4.2.4 Selection of Control Points

For each of the candidate control points, an estimate of the average number of faults detectable at the primary outputs is computed. These values are used to rank the control points in a greedy fashion. The line which detects the highest number of faults is selected first. These faults are then removed from consideration and the process is repeated by selecting the next best line. A list of control points is generated showing the average number of faults detectable and the incremental average number of faults detectable. This list can be parsed by an external procedure to select the control points that provide some incremental benefit and insert them into the circuit.

To verify the actual improvement in testability, the circuit netlists can be modified by the addition of the control points and then fault simulated. The addition of control points is modeled by a set of netlist transformations described in Section 3.3.3.

## 4.3 The Fault Injection Method for Observation Points

One of the simplest simulation based methods for determining fault detectability is based upon the PPSFP fault simulation method. As each fault is propagated through the circuit, fault detectability information can be accumulated. Only one fault simulation run is necessary to obtain the fault detectability information necessary for observation point placement. Since fault simulation is usually performed once or more to evaluate the coverage of the test set, the cost of one extra fault simulation should be reasonable. The main advantage of this method is that the detectability information is exact.

## 4.3.1 The Simulation Algorithm

The simulation algorithm is based upon the parallel pattern single fault propagation (PPSFP) fault simulation method. The main steps in the simulation algorithm are outlined below.

- 1. Place the input values at the primary inputs.

- 2. Perform fault free simulation and count number of logical 1s on each line.

- 3. Perform fault simulation

- (a) Inject fault at fault site.

- (b) Propagate fault effect and update fault detectability counters on each line encountered.

- (c) If fault was detected then drop it from further simulation

In addition to the standard fault simulation, a series of fault lists and counters are maintained on each line to keep track of:

- The number of times a logical 1 was present on a particular line.

- The number of times each fault was detected on a particular line.

The fault list on each line is composed of a linked list of fault IDs and detection counts. The detection count indicates how many times the fault was detectable at that particular line. The amount of space required to store the fault lists is  $O(n^2)$  in the worst case, where n is the number of lines in the circuit. To reduce the storage requirement, a fault set containing only undetected faults can be obtained from a previous fault simulation.

#### 4.3.2 Observation Point Placement

Using fault detectability information, the placement of observation points that cover the undetected faults can be determined. A greedy algorithm is used to select each observation point in a iterative fashion. The point that covers the largest number of undetected faults is selected first. The faults that are detected by this observation point are marked. These marked faults are not considered when counting the number of faults detectable by an observation point. The process is repeated until all the undetected faults all covered, or a specified number of observation points is reached.

Once this process is complete, a list of observation points is generated. For each observation point, the number of faults detected and the incremental number of faults detected is listed. This list can be used to manually evaluate the benefit of each additional observation point. The list can be parsed by an external procedure to automatically add the observation points to the circuit netlist.

## 4.4 Test Point Insertion Procedure

This chapter described a set of algorithms which can be used to determine fault detectability and sites for test point insertion. This section describes how these methods can be combined to create a test point insertion procedure. The procedure consists of two main stages. In the first stage, the Hybrid method is used to determine the placement of control points. A second stage is then performed using the Fault Injection method to determine the placement of observation points. The procedure takes the following input: