#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# Dynamic Clock Management Circuits for Low Power Applications

Ian Brynjolfson, B. Eng. 1999

Department of Electrical and Computer Engineering

McGill Univeristy, Montreal

**April 2001**

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your life Votes rélérance

Our ille Naire référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-75264-X

# **Abstract**

Low power methods employing dynamically controlled clock rates offer potentially powerful energy saving capabilities. Dynamic clock management is a system level technique that benefits from the relationship between operating frequency and power consumption through the variation of clock speeds based on demand. This thesis provides robust and scalable clock management circuits for dynamic clock control. A complete Programmable Clock Manager (PCM) has been designed, implemented, integrated into a Systems-on-a-Chip and tested. The PCM incorporates two novel circuits who enable dynamic clock management, the Range Shifting Phase-Locked Loop (RSPLL) and the Dynamic Programmable Clock Divider (DPCD). The self-calibrating RSPLL extends operating bandwidth while reducing jitter. Such a Phase-Locked Loop design also provides easier system-level integration and range-independent usage. The design is scalable to the higher bandwidths and lower voltages, associated with future technologies. The DPCD is capable of dynamic clock division without exhibiting glitches. Both of these robust circuits are easier to use for all clock management purposes.

# Résumé

Le contrôle dynamique de fréquence d'horloge est une méthode de basse puissance qui permet de potentiellement économiser de l'énergie. La fréquence d'horloge et la consommation énergétique d'un système sont directement interdépendantes. Le contrôle dynamique de fréquence d'horloge est une technique qui utilise cette dépendance en variant la fréquence du système selon la demande. Cette thèse présente un circuit de gestion d'horloge dynamique qui est robuste et facilement transférable d'une technologie à l'autre. Pour cette thèse un Gestionnaire de Fréquence Programmable (GFP) est développé, implémenté, intégré sur un "System-on-a-Chip", et vérifié. Le GFP incorpore deux nouveaux circuits qui permettent la gestion dynamique de fréquence, une Boucle à Verrouillage de Phase à Plage de Fréquence Contrôlable (BVPPFC), et un Diviseur de Fréquence Programmable Dynamique (DFPD). Le BVPPFC auto-calibré augmente la bande de fréquence d'opération tout en réduisant la gigue de phase. Une telle boucle à verrouillage de phase permet une intégration plus aisée, puisqu'elle est indépendante de la bande de fréquence d'opération du système. Ces circuits sont facilement transférables pour des utilisations de haute fréquence et bas voltage, comme le requiert la tendance des technologies futures. Le DFPD est capable de dynamiquement diviser la fréquence d'horloge sans produire d'interférence. Les deux nouveaux circuits proposés sont robustes et facilement utilisables pour tout système de gestion d'horloge.

# **Acknowledgments**

I would first like to thank my supervisor Zeljko Zilic. He provided the direction, advice and attention to detail that propelled my work to a higher level of quality. I also appreciate the opportunity he gave me to pursue areas of research that interested me. I also want to thank him for sending me to several conferences to compare my work with others. His guidance has prepared me for this mysterious land they call, "the real world."

I thank Micronet for their financial support. Also, the Canadian Microelectronics Corporation (CMC) provided my with the unparalleled experience of fabricating custom chips through access to Taiwan Semiconductor's CMOS processes, free of charge. They also supplied a large share of the equipment used for this work.

There are several other people whom I would like to thank also. My parents have helped support me throughout this endeavor. I would not have made it this far without them. The other member of the Microelectronics and Computing Systems (MACS) lab have been indispensable throughout this work. Most notably, Nazmy Rasmi Danial Abaskharoun Paul Tadros (aka "the manual") seemed to know everything about anything you would need to know about all the tools and equipment in the MACS lab. I was impressed by his intensity. Another valuable asset is Arshan Aga for his technical help, advice and insight, both in the lab and at the pub. Mohamed Hafed also provided the additional experience and advice that comes with being a Ph.D. student. I would like to also thank all of the other members of the MACS lab, students and professors, that I had the privilege to work with: Henry Chan, Boris Polianskikh and Yanai Danan (the MCSoC team); Prof. G. W. Roberts, Prof. R. Negulescu, Prof. M. El-Gamal, Prof. N. Rumin, Sebastien Laberge, Lige "B" Wang, Ramez Rafla, Ahmed Mostafa, Yang Wu, Geoffrey Duerden, Naveen Chandra, Bardia "paper boy" Pishdad, Antonio Chan and Clarence Kar Lun Tam. I must also thank the system administrators who did so much with so little: Ehab Lotayef, Ben Mihailescu, and Weiwen Zhu. Also, thanks to Prof. J. Clark and Prof. F. Ferrie.

# **Contributions of Authors**

The core of the original work on the development of dynamic clock management circuitry is located in Chapters 3, 4, and 5. The work in Chapter 6 is a collaboration of four students: Henry H. Y. Chan, Boris Polianskikh, Yanai Danan and the author of this thesis, Ian Brynjolfson.

Chapter 3 presents dynamic clock management in its application to Field Programmable Gate Arrays (FPGAs). The development of the patent pending Dynamic Programmable Clock Manager (DPCD) enabled dynamic clock management to occur in FPGAs, in a glitchless on-the-fly manner. This method of power reduction was not previously employed in FPGAs. The ideas are also outlined in [1], coauthored with Prof. Zeljko Zilic.

Chapter 4 presents a Programmable Clock Manager (PCM) design that is based, in part, on the PCM developed by Lucent for use in the ORCA Series FPGAs, as discussed in Section 3.1.1.3. The Phase-Locked Loop (PLL) design used in the PCM was based on the original design presented in [38]. The novelty of the PCM design comes from the use of the DPCD in place of the clock dividers in Lucent's original design. Also, the PLL design was adapted for the requirements of dynamic clock management. Using the PCM for dynamic clock management is a novel application for the circuit.

Chapter 5 describes the design of a Range Shifting Phase-Locked Loop (RSPLL). The concept of optimizing PLL design for clock management application by the automatic variation of the length of the Voltage Controlled Oscillator (VCO), is to our knowledge original. The substitution of the RSPLL in the PCM design for a standard PLL is novel also. The patent pending RSPLL was presented in [2], coauthored with Prof. Zeljko Zilic.

The work in Chapter 6 describes the contribution of the thesis author towards the development of the Managed Clock System-on-a-Chip (MCSoC) project. Table 3 in Chapter 6, outlines the contributions of the other students working on the MCSoC project.

# **Table of Contents**

| Abstract                                                         |          |

|------------------------------------------------------------------|----------|

| Résumé                                                           | i        |

| Acknowledgments                                                  | ii       |

| Contributions of Authors                                         | i        |

| Table of Contents                                                |          |

| List of Figures                                                  | iy       |

| Chapter 1 - Introduction                                         | 1        |

| 1.1 - Motivation                                                 |          |

| 1.2 - Dynamic Clock Management                                   |          |

| 1.3 - Outline                                                    |          |

| Chapter 2 - Dynamic Clock Management                             | 6        |

| 2.1 - Clock Distribution                                         | 6        |

| 2.1.1 - Clock Distribution Concerns                              | <i>6</i> |

| 2.1.1.1 - Clock Skew                                             |          |

| 2.1.1.2 - Jitter                                                 | 8        |

| 2.1.1.3 - Waveform Deformation                                   | 9        |

| 2.1.2 - Solutions                                                | 9        |

| 2.1.2.1 - PLL and DLL Operation                                  | 9        |

| 2.1.2.2 - Skew Reduction                                         | 10       |

| 2.1.2.3 - Frequency Synthesis                                    | 10       |

| 2.1.2.4 - PLL and DLL Comparison                                 | 11       |

| 2.2 - Low Power Using Dynamic Clock Management                   | 11       |

| 2.2.1 - Voltage Scaling with Gating and Dynamic Clock Management | 13       |

| 2.3 - Dynamic Clock Management Implementations                   | 14       |

| 2.3.1 - Frequency Changes and PLL Response                       | 15       |

| 2.4 - Additional Applications of Clock Managers                  |          |

| 2.5 - Summary                                                    |          |

| Chapter 3 - FPGA Implementation                                  | 18       |

| 3.1 - Dynamic Clock Management in FPGAs                          | 18       |

| 3.1.1 - Examples of Existing Clock Managers                      |          |

| 3.1.1.1 - The Virtex FPGA Series by Xilinx                       |          |

| 3.1.1.2 - The APEX 20K by Altera                                 |          |

| 3.1.1.3 - The ORCA Series 3 by Lucent                            |          |

| 3.1.1.4 - Limitations of Existing Clock Managers              | 21         |

|---------------------------------------------------------------|------------|

| 3.2 - Dynamic Programmable Clock Divider                      | 22         |

| 3.2.1 - DPCD Operational Description                          | 23         |

| 3.2.1.1 - Preventing Glitches and Preserving a 50% Duty Cycle | 23         |

| 3.2.2 - DPCD Benefits                                         | 25         |

| 3.2.3 - Other Clock Dividers                                  | 25         |

| 3.2.4 - DPCD Applications                                     | 27         |

| 3.3 - Partitioning Issues                                     | 28         |

| 3.3.1 - Communication                                         | 29         |

| 3.3.2 - Control Logic                                         | 29         |

| 3.4 - Case Study                                              | 30         |

| 3.4.1 - Partitioning                                          | 31         |

| 3.4.2 - Communication                                         | 3 <i>1</i> |

| 3.4.3 - Control Logic                                         | 32         |

| 3.5 - Summary                                                 | 34         |

| Chapter 4 - Programmable Clock Manager                        | 35         |

| 4.1 - Functional Overview                                     | 35         |

| 4.2 - Phase-Locked Loop Design                                | 38         |

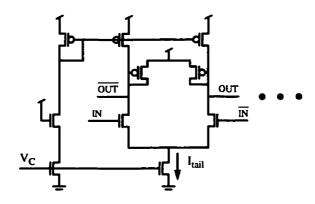

| 4.2.1 - Voltage Controlled Oscillator Design                  | 39         |

| 4.2.1.1 - Varying the Number of Taps                          |            |

| 4.2.2 - Charge-Pump Design                                    | 41         |

| 4.2.2.1 - Bandwidth and Peaking Compensation                  | 41         |

| 4.2.1.2 - Charge Sharing and Balanced Currents                |            |

| 4.2.3 - Phase-Frequency Detector                              |            |

| 4.2.3.1 - PFD Operation                                       |            |

| 4.2.3.2 - The Dead Zone                                       |            |

| 4.2.3.3 - Driving the Charge Pump                             |            |

| 4.3 - Experimental Results                                    |            |

| 4.3.1 - Tracking Jitter                                       |            |

| 4.3.2 - Duty Cycle                                            |            |

| 4.3.3 - Power Consumption                                     |            |

| 4.3.4 - Comparing Iterations                                  |            |

| 4.4 - Recommendations for Improvements                        |            |

| 4.5 - Summary                                                 | 56         |

| Chapter 5 - Range Shifting Phase-Locked Loop                  | 57         |

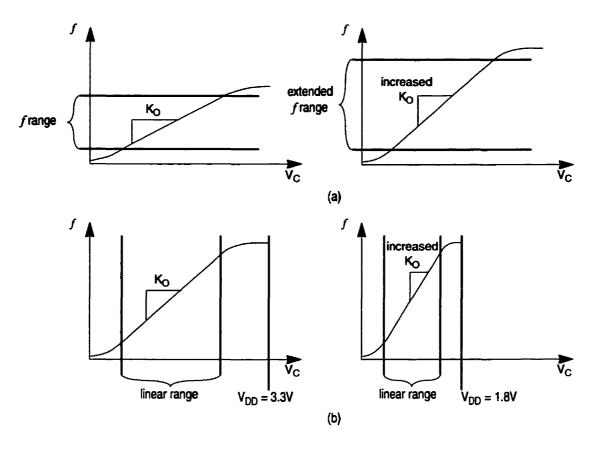

| 5.1 - PLL Design Concerns                                     |            |

| 5.1.1 - Meeting PLL Specifications                            | 58         |

| 5.1.2 - Increased Jitter                                      | 60         |

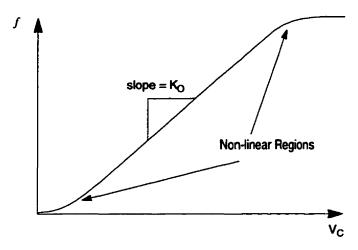

| 5.2 - RSPLL Architecture                                      | 60         |

| 5.2.1 - Reduced KO with a Variable Length VCO      | 61  |

|----------------------------------------------------|-----|

| 5.2.2 - RSPLL Operation                            | 62  |

| 5.3 - Loop Dynamics: Conditions for Range Shifting | 63  |

| 5.3.1 - Activating the Coarse Control Loop         |     |

| 5.3.2 - Deactivating the Coarse Control Loop       | 65  |

| 5.3.3 - Coarse Loop Induced Instability            |     |

| 5.4 - Variable Length VCO Implementation           | 67  |

| 5.5 - Length Controller                            | 69  |

| 5.6 - Additional Design Considerations             |     |

| 5.6.1 - VCO Design Considerations                  | 71  |

| 5.6.2 - Design Using Logical Effort                | 71  |

| 5.7 - Clock Manager Implementation                 |     |

| 5.7.1 - Experimental Results                       |     |

| 5.8 - Summary                                      | 77  |

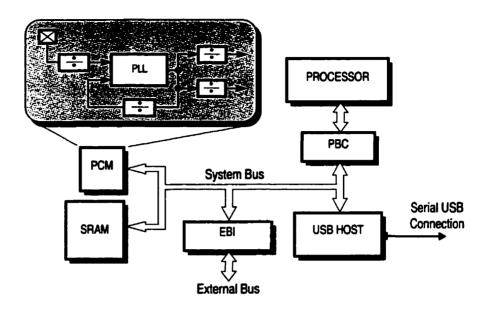

| Chapter 6 - SoC Implementation                     | 78  |

| 6.1 - MCSoC Organization                           |     |

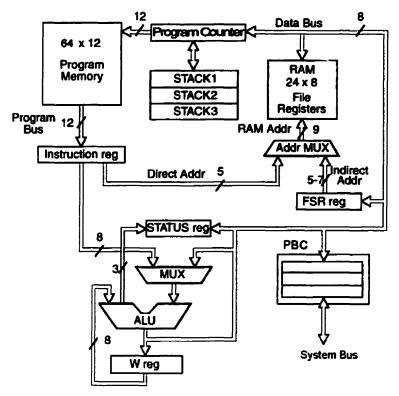

| 6.2 - Processor Design                             |     |

| 6.3 - System Bus and External Communication        |     |

| 6.4 - Development                                  |     |

| 6.5 - PCM Incorporation Into the SoC               |     |

| 6.5.1 - PCM Positioning Within MCSoC               |     |

| 6.5.2 - Driving the Clock Domains                  |     |

| 6.5.3 - The Feedback Signal                        |     |

| 6.5.4 - Control                                    |     |

| 6.6 - Testing, Verification and Implementation     |     |

| 6.6.1 - Test Plan                                  |     |

| 6.6.2 - The IEEE 488 and VXI Bus Measurement Setup |     |

| 6.6.3 - Printed Circuit Board Design               |     |

| 6.6.4 - Implementation                             |     |

| 6.7 - Summary                                      | 88  |

| Chapter 7 - Conclusion                             | 89  |

| Appendices:                                        |     |

| A Calculating PLL Design Parameters                | 01  |

| B PCM Register Configuration                       |     |

| C Jitter Measurements                              |     |

| D Clock Divider Simulations                        |     |

| E RSPLL Simulations                                |     |

| F PCB Layout Schematics                            | 108 |

| References                                         | 110 |

|                                                    |     |

# **List of Figures**

| Figure 2.1:  | Clocked Data Path                                                     | 7  |

|--------------|-----------------------------------------------------------------------|----|

| Figure 2.2:  | Time Domain Representation of Phase (a) Skew (b) Jitter               |    |

| Figure 2.3:  | Clock Waveforms (a) Desirable Waveform (b) Waveform                   |    |

| -            | Containing Glitches                                                   | 9  |

| Figure 2.4:  | (a) Phase-Locked Loop (b) Delay-Locked Loop                           | 10 |

| Figure 2.5:  | Clock Shutoff Circuitry used for Clock Gating                         | 12 |

| Figure 2.6:  | Embedded Application Using Clock Synthesis                            | 12 |

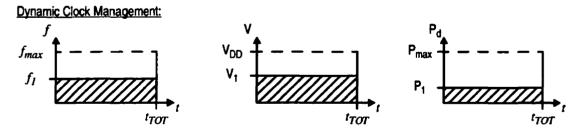

| Figure 2.7:  | The Frequency, Voltage, and Dynamic Power Resulting from              |    |

|              | Clock Gating                                                          | 13 |

| Figure 2.8:  | The Frequency, Voltage, and Dynamic Power Resulting from              |    |

| _            | Dynamic Clock Management                                              | 13 |

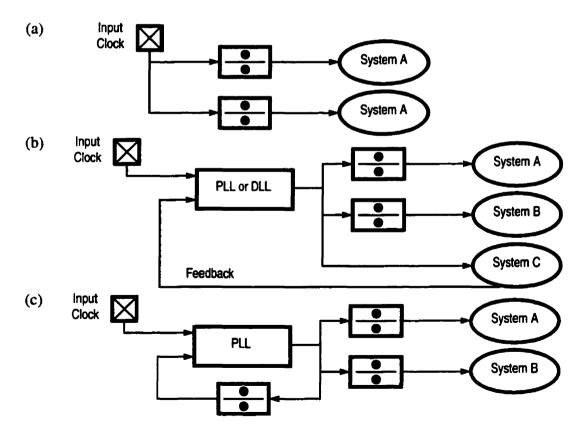

| Figure 2.9:  | Dynamic Clock Management Implementations                              | 14 |

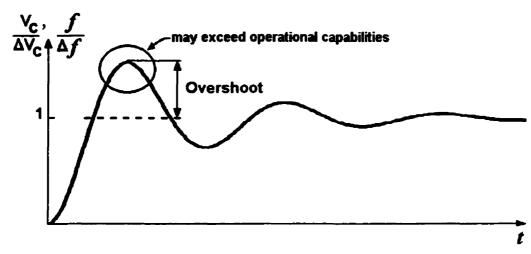

| Figure 2.10: | Step Response of Underdamped Second-Order System                      |    |

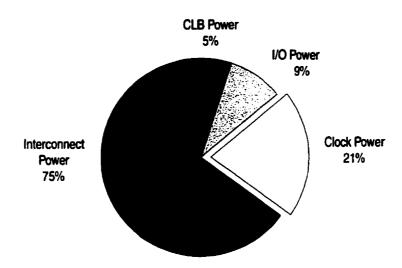

| Figure 3.1:  | Typical FPGA Power Breakdown                                          |    |

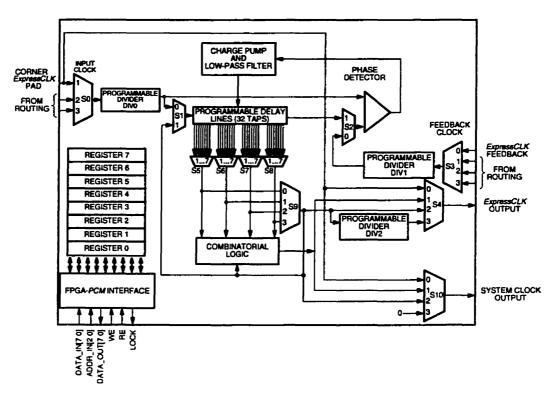

| Figure 3.2:  | ORCA Programmable Clock Manager - Functional Block Diagram            |    |

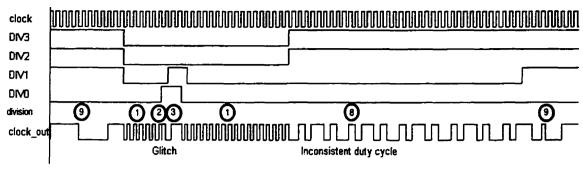

| Figure 3.3:  | Standard Clock Divider Operation                                      | 22 |

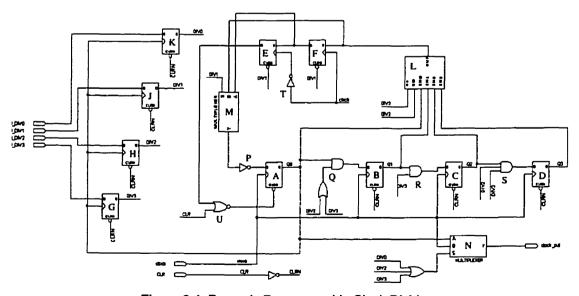

| Figure 3.4:  | Dynamic Programmable Clock Divider                                    | 22 |

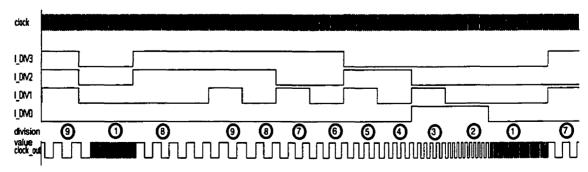

| Figure 3.5:  | DCPD Operation                                                        | 24 |

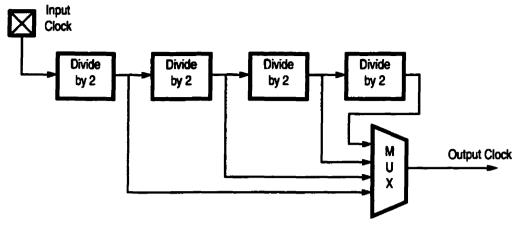

| Figure 3.6:  | Frequency Synthesis Using Divider Chain                               | 26 |

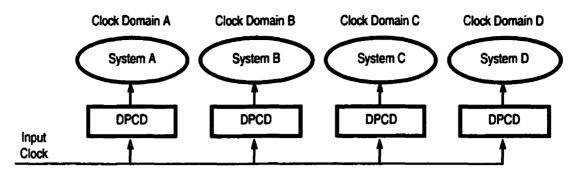

| Figure 3.7:  | Embedded Application Using DPCDs For Clock Synthesis                  |    |

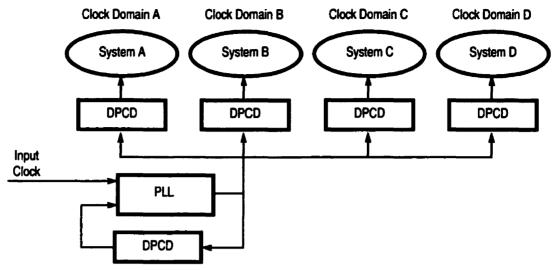

| Figure 3.8:  | Embedded Application Using DPCDs In Clock Synthesis                   |    |

|              | With a PLL for Clock Multiplication                                   | 28 |

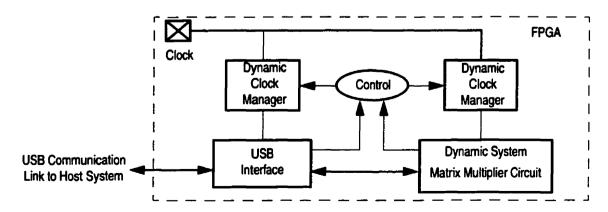

| Figure 3.9:  | USB/Matrix Multiplier System                                          | 30 |

| Figure 3.10: | Output Clock Waveforms Demonstrating Periodic Alignment of            |    |

|              | Rising Edges When a Clock Signal is Divided by Integer Values         | 32 |

| Figure 3.11: | ORCA Implementation                                                   |    |

| Figure 3.12: | Altera Implementation                                                 | 33 |

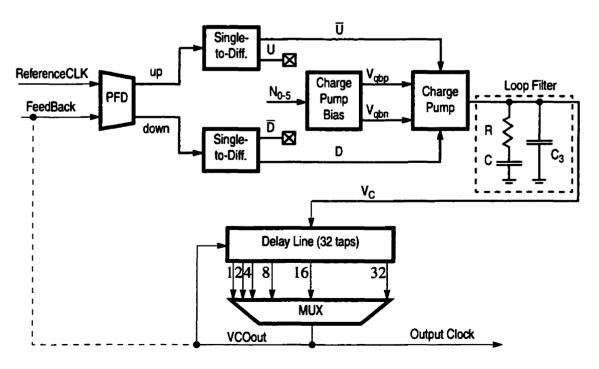

| -            | Programmable Clock Manager - Functional Block Diagram                 |    |

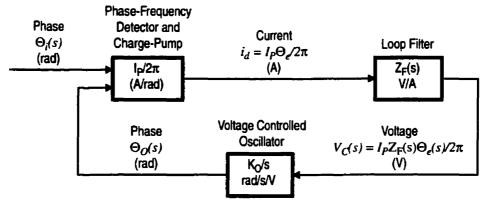

| Figure 4.2:  | Phase-Locked Loop Block Diagram                                       |    |

| Figure 4.3:  | Differential Delay Cell                                               |    |

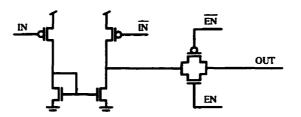

| _            | Differential-to-Single Ended Converter with Enabled Transmission Gate |    |

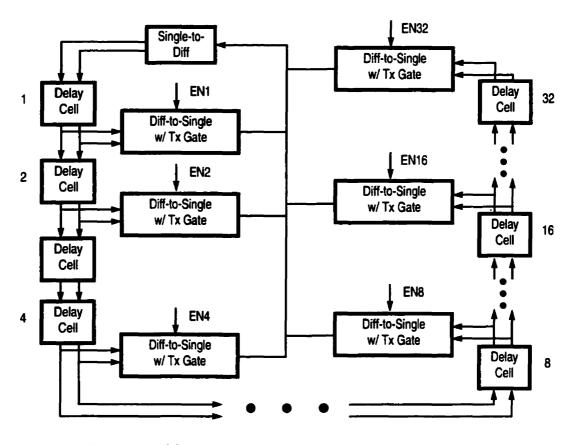

| Figure 4.5:  | VCO with Transmission Gate Multiplexer Implementation                 |    |

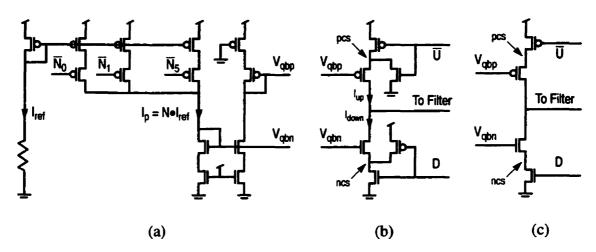

| Figure 4.6:  | (a) Current Multiplier Generating Charge-Pump Biasing            |    |

|--------------|------------------------------------------------------------------|----|

|              | Voltages Vqbn and Vqbp                                           | 42 |

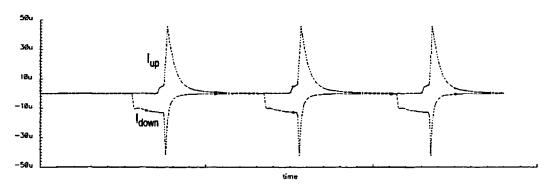

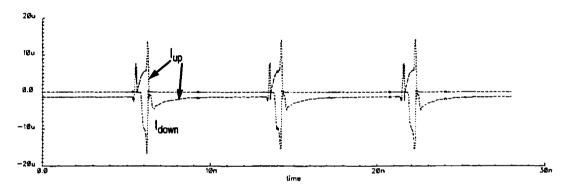

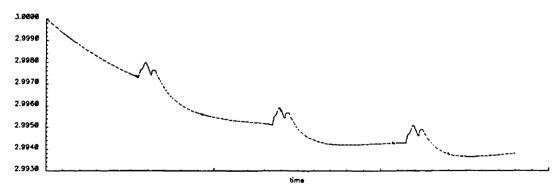

| Figure 4.7:  | Up (Iup) and Down (Idown) Currents in Charge Pump                |    |

|              | Without Charge Sharing Removal Transistors                       | 43 |

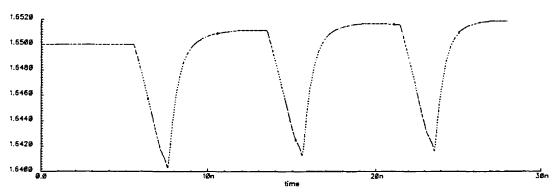

| Figure 4.8:  | Control Voltage (VC) Ripple Resulting From a Charge              |    |

|              | Pump Without Charge Sharing Removal Transistors                  | 43 |

| Figure 4.9:  | Up (Iup) and Down (Idown) Currents in Charge Pump                |    |

|              | With Charge Sharing Removal Transistors                          | 43 |

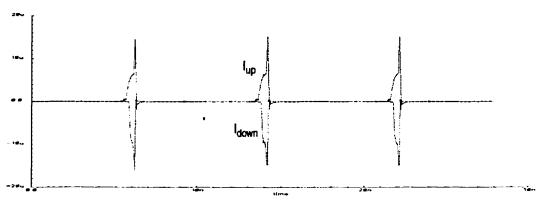

| Figure 4.10  | Up (Iup) and Down (Idown) Currents in Charge Pump with           |    |

|              | VC at 3.0V. Notice Iup Flows Negative Between Corrective         |    |

|              | Pulses from the PFD                                              | 44 |

| Figure 4.11: | Discharge of the Control Voltage (VC) due to Reverse Flow        |    |

|              | of Iup from VC at 3.0V                                           | 44 |

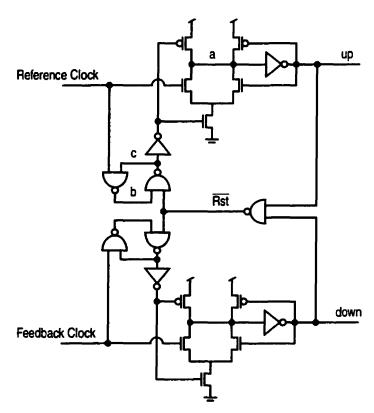

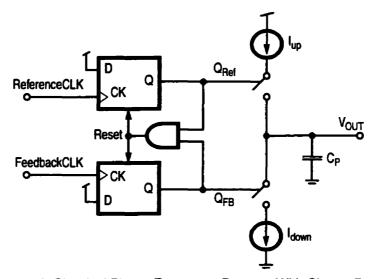

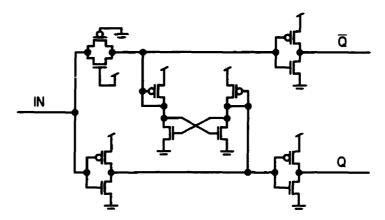

| Figure 4.12: | Phase-Frequency Detector                                         | 45 |

| Figure 4.13: | Classical Phase-Frequency Detector With Charge Pump              | 46 |

| Figure 4.14: | Dead Zone in a Phase Frequency Detector With a Charge Pump       | 47 |

| Figure 4.15: | Single-to-Differential Converter                                 | 49 |

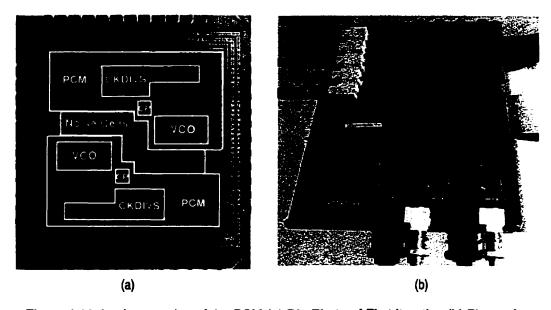

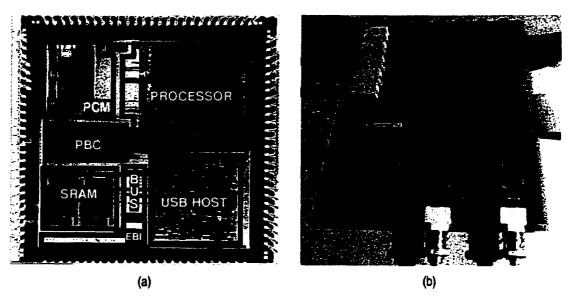

| Figure 4.16: | Implementation of the PCM (a) Die Photo of First Iteration       |    |

|              | (b) Photo of the Second Iteration of the PCM on a Printed        |    |

|              | Circuit Board                                                    | 50 |

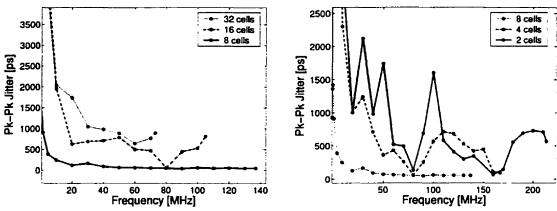

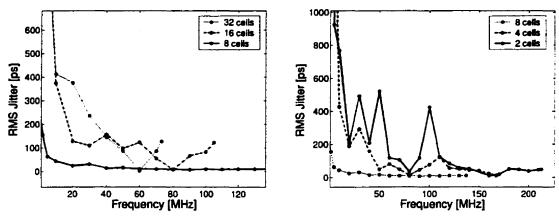

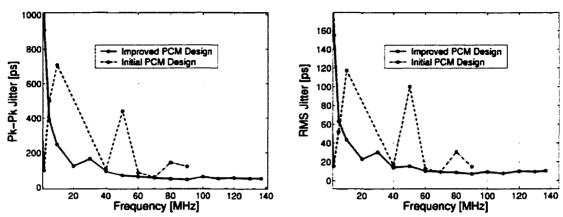

| Figure 4.17: | Tracking Pk-Pk Jitter [ps] plotted vs. Frequency [MHz] as a      |    |

|              | function of the number of taps in the VCO                        | 50 |

| Figure 4.18: | Tracking RMS Jitter [ps] plotted vs. Frequency [MHz] as a        |    |

|              | function of the number of taps in the VCO                        | 51 |

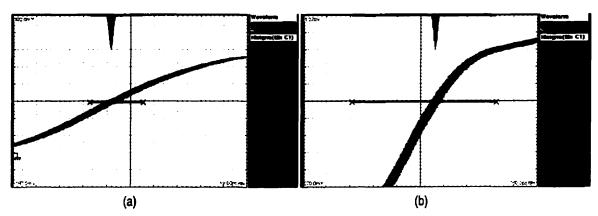

| Figure 4.19: | Jitter Tracking Histograms (a) Reference Clock @ 50 MHz          | 51 |

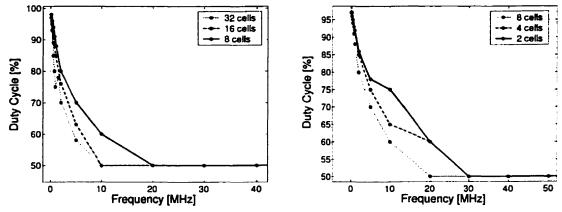

| Figure 4.20: | Output Duty Cycle [%] plotted vs. Frequency [MHz] as a           |    |

|              | function of the number of taps in the VCO                        | 52 |

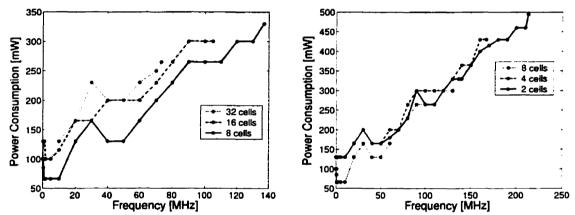

| Figure 4.21: | Power Consumption [mW] plotted vs. Frequency [MHz] as a          |    |

|              | function of the number of taps in the VCO                        | 53 |

| Figure 4.22: | Tracking RMS and Pk-Pk Jitter [ps] plotted vs. Frequency [MHz]   |    |

|              | comparing the initial PCM design to the improved version,        |    |

|              | length = 8 taps                                                  | 54 |

| Figure 4.23: | Output Duty Cycle [%] and Power Consumption [mW] plotted vs.     |    |

|              | Frequency [MHz] comparing the initial PCM design to the          |    |

|              | improved version, length = 8 taps                                |    |

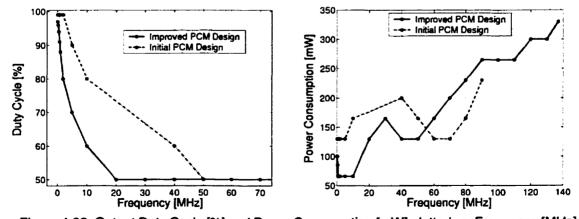

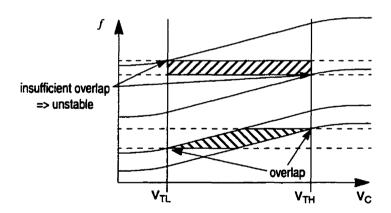

| Figure 5.1:  |                                                                  | 58 |

| Figure 5.2:  |                                                                  |    |

|              | (b) Decrease in Supply Voltage (VDD)                             |    |

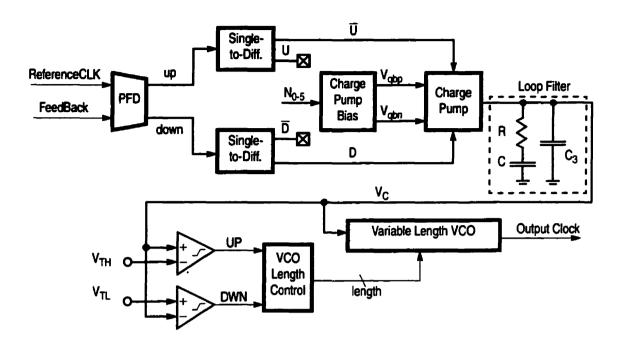

| Figure 5.3:  | Proposed PLL Architecture                                        |    |

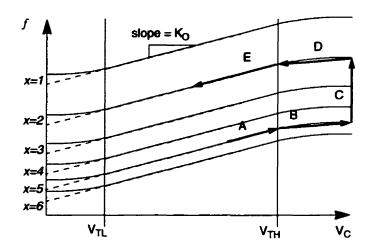

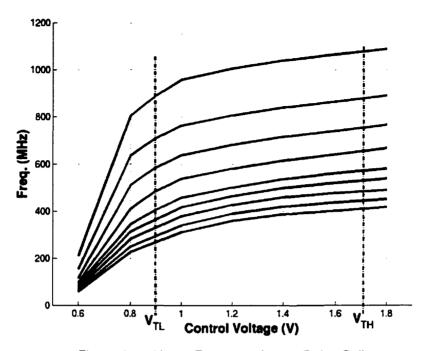

| Figure 5.4:  | Frequency vs. Control Voltage: Output of VCO for Varying Lengths | 62 |

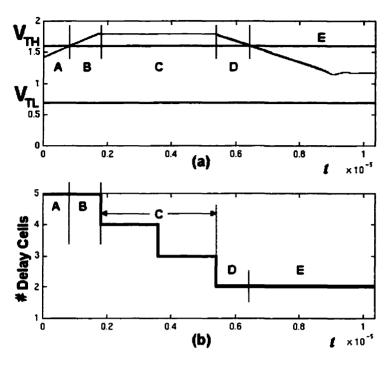

| Figure 5.5:  | (a) VC vs. Time (b) Length vs. Time                               | 63   |

|--------------|-------------------------------------------------------------------|------|

| Figure 5.6:  | _                                                                 |      |

| Figure 5.7:  | f vs. VC: Frequency Range Overlap                                 |      |

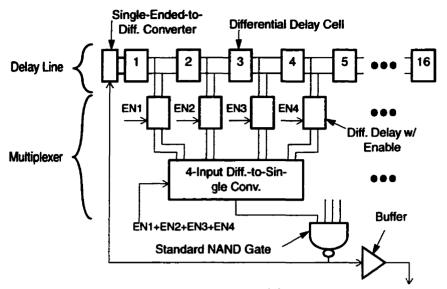

| Figure 5.8:  | Variable Length VCO Architecture                                  | 67   |

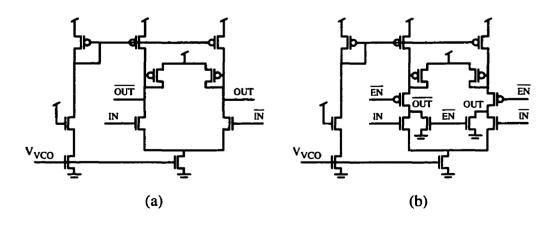

| Figure 5.9:  | Differential Delay Cell: (a) Basic (b) with Enable                | 67   |

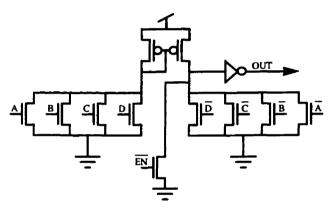

| Figure 5.10: | Four Input Differential-to-Single Converter                       | 68   |

| Figure 5.11: | A Single Cell in the Length Controller Comprised of Three         |      |

|              | Muller C-Elements                                                 | 69   |

| Figure 5.12: | Programmable Clock Manager With RSPLL                             | 72   |

|              | Die Photograph of Clock Manager With RSPLL Implementation         |      |

| Figure 5.14: | VC vs. Frequency for 1-9 Delay Cells                              | 74   |

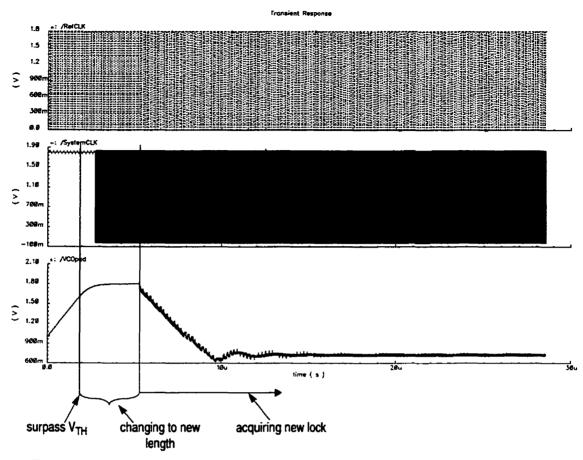

| Figure 5.15: | Simulation of the RSPLL Locking to a Frequency of 75 MHz.         |      |

|              | The Reference Frequency is 5 MHz and the Feedback                 |      |

|              | Multiplication Factor is 15                                       | 75   |

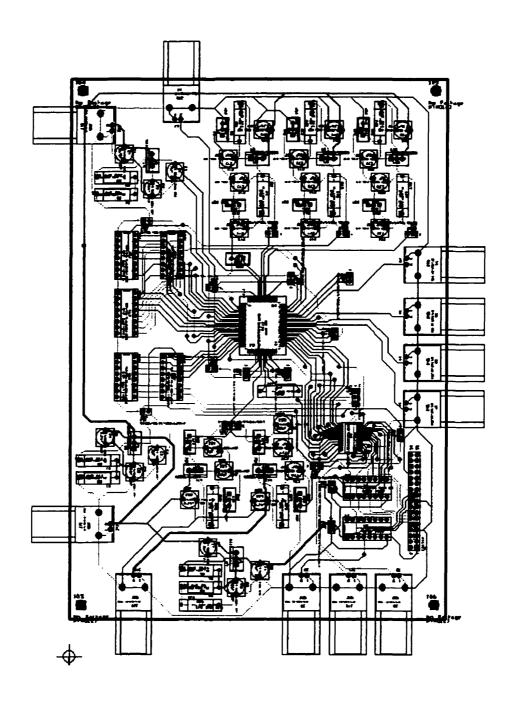

| Figure 5.16: | PCB Layout to Test the RSPLL Implementation                       | 76   |

| Figure 6.1:  | System Level Overview of MCSoC                                    | 79   |

| Figure 6.2:  | Processor Architecture                                            | 80   |

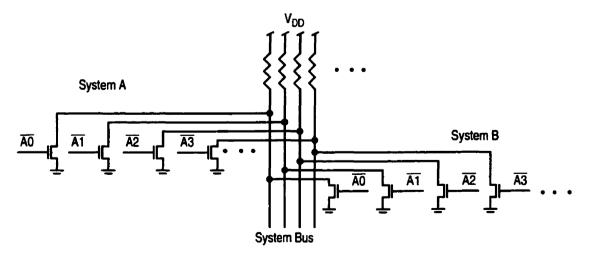

| Figure 6.3:  | Connections to System Bus With Pull-up Resistors to Maintain      |      |

|              | a Logical '1' and Pulled Down by NMOS Transistors                 | 81   |

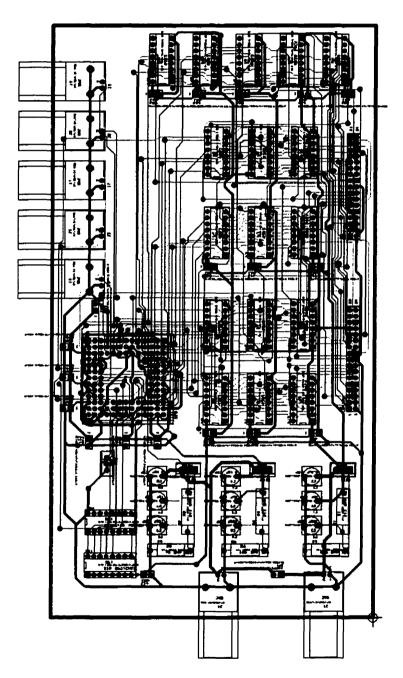

| Figure 6.4:  | Implementation of MCSoC (a) Die Photo (b) PCB Test Board          | 87   |

| Figure A.1:  | s-Domain Representation of a PLL                                  | 91   |

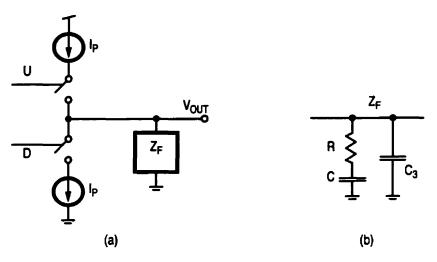

| Figure A.2:  | (a) Charge Pump Model Used in PLL Analysis                        | 92   |

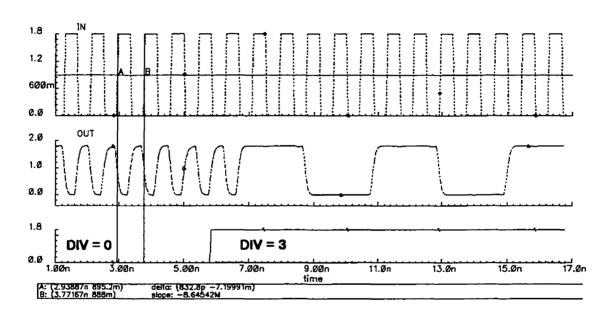

| Figure D.1:  | SImulation of Clock Divider Operation, Manufactured in the 0.18µm |      |

|              | 1.8V CMOS TSMC Process, Input Clock at a Frequency of 1.2GHz,     |      |

|              | The Output is Divided by Zero then Divided by Three               | .105 |

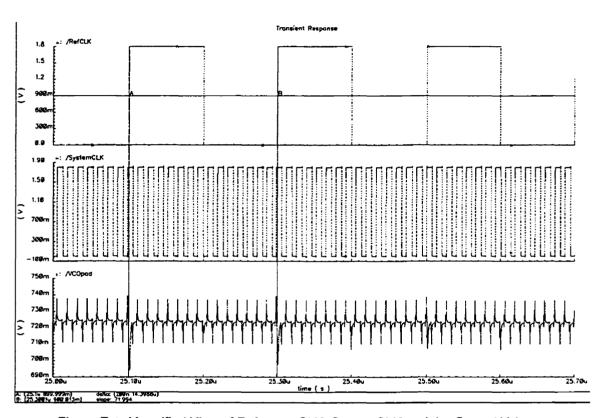

| Figure E.1:  | Magnified View of ReferenceCLK, SystemCLK and the                 |      |

|              | Control Voltage. ReferenceCLK is Measured to be 200 ns,           |      |

|              | Corresponding to 5 MHz.                                           | .106 |

| Figure E.2:  | Magnified View of ReferenceCLK, SystemCLK and the                 |      |

|              | Control Voltage. SystemCLK is Measured to be 13.3467 ns,          |      |

|              | Corresponding to ~75 MHz.                                         | .107 |

| Figure F.1:  | Printed Circuit Board Layout Schematic for MCSoC                  | .108 |

| Figure F.2:  | Printed Circuit Board Layout Schematic for RSPLL                  | .109 |

# **Chapter 1 - Introduction**

A major challenge facing today's system and circuit designers is to create a new generation of products which consume a limited quantity of power. Increasing the challenge to design, power reduction must be achieved without compromising area or performance. Traditionally, the main design constraints were high speed operation and minimal area consumption. State-of-the-art products were driven by lower delays and smaller chip area. All of the design tools and methodologies were geared towards achieving these two goals. Power dissipation was an afterthought and not a design criterion.

## 1.1 - Motivation

At the end of the last century, power dissipation had become a main design concern in many applications. Two contributing factors were portable electronics and high-performance designs that exceed power dissipation limits. Battery-powered systems such as laptop/notebook computers, cellular phones and electronic organizers, to name a few, create a need for an extended battery life. Although the battery industry has been making efforts to develop batteries with higher energy capacity, a strident increase does not seem imminent. Even with advanced battery technologies, the life time of the battery is still small. Therefore, low power design techniques are essential for portable devices.

Low power design is not only needed for portable applications, but also to reduce the power consumption in high-performance systems. With large integration density and reduced gate delays, higher clock frequencies are becoming more easily attainable. Microprocessor fabrication has seen significant increases in costs associated with packaging, cooling and fans to remove heat. There are also reliability problems due to circuit failures at high on-chip temperatures.

The rising importance and concerns regarding energy consumption are manifested by the amount of attention being paid to this issue, from both academics and industry. This fervour focused on power dissipation has resulted in the publication of numerous textbooks and publications. Most publications discussing power optimization primarily center on circuit level techniques [5,6,7,8,9,10,11]. These techniques range from architectural configurations that consume less power, to circuits capable of operating at lower voltage levels [5,6,7]. Several publications are devoted to low power synthesis methods [12] or power analysis at various hierarchical levels [13].

Processor developers, such as Intel, Transmeta, and Motorola, have developed some means to reduce power consumption. They outline their power reduction methods in much of their documentation and product briefs [14,15,16]. Intel has a thermal monitor to interrupt the processor when excessive heat is present, and uses clock gating as their primary power reduction mechanism. The approach used by Motorola and Transmeta is to vary the frequency. Where Motorola has three states, doze, nap and sleep, Transmeta uses on-the-fly clock frequency changes to "dynamically pick just the right clock speed" [16].

# 1.2 - Dynamic Clock Management

Circuit level techniques and reduced voltage levels have resulted in great reductions in power dissipation from the gates and logic of a system, but the clock distribution networks have received less attention. The clock distribution networks drive the largest numbers of gates in a circuit, and alone consume substantial power. Also, the dynamic power dissipated by the clock increases as the number of clocked devices and the chip dimensions grow. In CMOS microprocessors, a global clock may account for up to 40% of

the total system power dissipation [17]. To directly affect the power consumption in clock distribution networks, as well as in the system logic, *dynamic clock management* takes advantage of changing demand by supplying a variable frequency clock signal. Overall power is reduced without loss in performance.

Initially, most Integrated Circuits (ICs) had only one clock domain. Today, an increasing trend is to incorporate several independent systems in the same chip, each with their own clock domain. Most subsystems do not need to run at GHz frequencies to satisfy timing requirements. When many subsystems are incorporated into a larger system, they can be clocked at a power saving, reduced frequency. Possibly only one or a few subsystems need to be operated at maximal operating frequencies at any given moment.

In this thesis, we investigate dynamic clock management to better understand the large potential gains in power conservation by using this system-level technique. We also develop clock generation circuitry essential for performing dynamic frequency synthesis without endangering system operation. The clock generation circuitry must adhere to stringent requirements in order to be used in these applications where the clock frequency changes quickly and often. Transitions between frequencies must be fast and forestall glitching. The extent of possible frequencies should range from low idle speeds in kHz, to the maximum operating frequency of the system in the high MHz, or even GHz now. These traits should be exhibited by the on-chip dynamic clock generators, or *clock managers*, while producing nominal jitter.

## 1.3 - Outline

A brief introduction to dynamic clock management and its components is provided by Chapter 2. This includes a discussion of the relevant features, such as clock skew, jitter and the dynamic behavior of clock managers. The interesting low power benefits of dynamic clock management are demonstrated, followed by a brief discussion of its possible applications.

Our exploration into dynamic clock management begins with a Field Programmable Gate Array (FPGA) implementation in Chapter 3. The flexibility afforded by FPGA programmability leads to a high level of power consumption when compared to an equivalent Application Specific Integrated Circuit (ASIC) design. We see that existing FPGAs can perform dynamic clock management by including a novel clock divider in the user logic. The Dynamic Programmable Clock Divider (DPCD) is capable of performing clock division on-the-fly, without exhibiting negative effects such as glitches and inconsistent duty cycles. We also consider several of the methods and concerns when developing dynamic clock management as a program for reducing power consumption.

Although the DPCD enables dynamic clock management in existing FPGAs, a custom clock manager implementation would enlarge the clock frequency range. This range expansion would result in an increase in flexibility and thus increase the potential of dynamic clock management. A Programmable Clock Manager (PCM) was designed for this purpose and is described in Chapter 4. The PCM generates low jitter clock signals and includes DPCDs to satisfy the requirements of dynamic clock management. The PCM is also easy to use and a complete component. Therefore, the PCM may be placed in the clock distribution network along with controlling software, and does not require additional hardware for support.

The development of the PCM exposed several areas which have room for improvement. One of these areas consisted of the Phase-Locked Loop (PLL). A PLL with a wide operating range and limited jitter resulted in the contradictory design objectives. From these challenges, the Range Shifting Phase-Locked Loop (RSPLL) was developed, as seen in Chapter 5. This novel circuit is capable of supplying multiple operating ranges by changing the length of its Voltage Controlled Oscillator (VCO).

Last, in Chapter 6, we develop a research platform to advance exploration into dynamic clock management. A System-on-a-Chip (SoC) implementation includes a processor, a memory core, external communication subsystems, an internal asynchronous bus and the PCM to enable dynamic clock management.

Additional pertinent information is provided in the appendices. Appendix A develops the PLL model used throughout this document. The register configurations for the PCM are outlined in Appendix B. The numerical values for the measurements discussed in Chapter 4 can be found in Appendix C. Also, Appendix E shows additional simulations to support the claim of functional operation of the RSPLL. Finally, Appendix F contains the layout schematics for the printed circuit boards used during testing and debugging.

# Chapter 2 - Dynamic Clock Management

With the increased speed of Field Programmable Gate Array (FPGA) and Systems-on-a-Chip (SoC) designs, there is more focus on the creation of high quality clock management schemes and the comprehensive exploration of their applications. Initially, clock management concentrated on solving distribution concerns relating to skew and waveform shape. Many benefits can be obtained by dynamically scaling the frequency of a system, including interesting low power possibilities [19]. Dynamically altering clock frequencies can be performed in several ways; if not done properly, disastrous results can occur.

## 2.1 - Clock Distribution

Global clocks are essential in the operation of synchronous digital systems. They define a time reference for the transfer of data throughout such a system. As a result, a great deal of attention is paid to clock distribution networks [20].

#### 2.1.1 - Clock Distribution Concerns

There are many concerns when designing a clock distribution network, however two are of particular concern: clock skew, jitter and hazards (or glitching). An ideal clock is

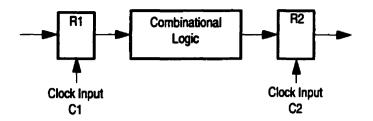

Figure 2.1: Clocked Data Path

distributed as a perfect square wave with matched transition times everywhere on a chip. Due to skew, this ideal clock is hard to achieve.

#### 2.1.1.1 Clock Skew

Clock skew is defined as the difference in transition times of two disjoint clock signals:

$$T_{Skew} = T_{C1} - T_{C2} (2.1)$$

where  $T_{CI}$  and  $T_{C2}$  are the times at which clocks CI and C2 transition, respectively. The cause of skew depends on location. With regards to Inputs/Outputs (I/Os), the asynchronous nature of external data communication inherently leads to alignment difficulties. On the other hand, skew within a chip is caused by delay incurred during propagation of the clock signal from its input pin to the distant points of the clock distribution network. Therefore, the clock-driven cells within close proximity to the network origin will transition before those cells further along the network.

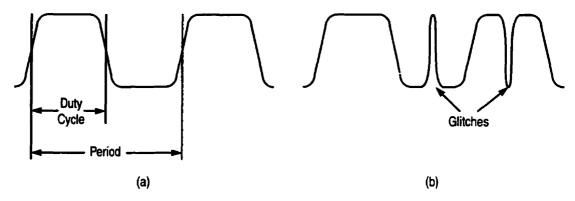

For registers and flip-flops to work properly, the following inequality must be satisfied:

$$T_{CP} > T_{Skew} + T_{Data} + T_{Setup} \tag{2.2}$$

where  $T_{CP}$  is the clock period,  $T_{Skew}$  is the clock skew,  $T_{Setup}$  is the setup time needed by the register for the incoming data to hold its state, and  $T_{Data}$  is the delay of the data path. The reduction of clock skew will directly influence the period of the clock and thus the speed of the design.

If clock skew is positive, then the clock signal at register R2  $(T_{C2})$  leads the signal at register R1  $(T_{C1})$ , in Figure 2.1. Skew becomes the amount of time that must be added to

the clock period in order for the second register to properly receive data. The solution is to simply slow down the frequency of the clock. In the case of negative clock skew, the clock signal at register R2 ( $T_{C2}$ ) lags the signal at register R1 ( $T_{C1}$ ). Negative skew can reduce the clock period, but the amount of allowed negative skew is limited. If there is excessive negative skew, then data will arrive at R2 before the clock signal. This implies that the data latched at R1 overwrites R1's past output before R2 had a chance to latch it. As a result, a race condition occurs. Slowing the clock frequency will not solve this problem. Only by ensuring that the skew is smaller than the data propagation delay will reliable operation be achieved.

#### 2.1.1.2 Jitter

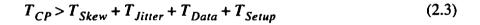

If skew is analogous to a DC condition, then jitter is considered to be AC. Skew is a consistent shift in phase by an amount  $\Delta \phi$ , shown over time in Figure 2.2(a). Whereas jitter is a fluctuation in frequency and phase around a desired value, or an inconsistent wandering of the clock edges, shown in Figure 2.2(b). The maximum jitter,  $T_{Jitter}$ , both positive and negative must be considered in design. If the tolerances do not incorporate jitter, the possibility of race conditions or the clock period being too short may occur. Therefore, Equation (2.2) must be altered to incorporate jitter.

Figure 2.2: Time Domain Representation of Phase (a) Skew (b) Jitter

#### 2.1.1.3 Waveform Deformation

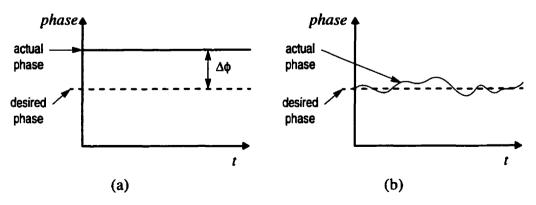

Skew and jitter only affect the phase of the clock waveform; hazards and glitches can cause distortions. If the waveform becomes sufficiently distorted, as in Figure 2.3, additional edges may appear within a clock period leading to faulty latch attempts or metastable states. As a result, hazards and glitches are very dangerous in clock distribution networks. A duty cycle, defined as the time in which a clock signal is high during its period, of 50% is also desirable.

Figure 2.3: Clock Waveforms (a) Desirable Waveform (b) Waveform Containing Glitches

#### 2.1.2 - Solutions

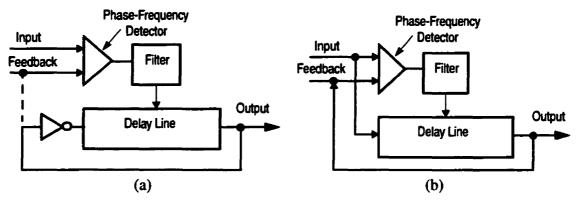

To reduce clock skew, one can utilize components that align clocks, implemented either as a Phase-Locked Loop (PLL) or a Delay-Locked Loop (DLL). Both circuits align the feedback clock edges, taken from any specific location in a system, with the edges of a reference clock. In clock distributions, the reference is either an external clock, or an internally generated clock. Figure 2.4 shows simplified diagrams of a PLL and DLL.

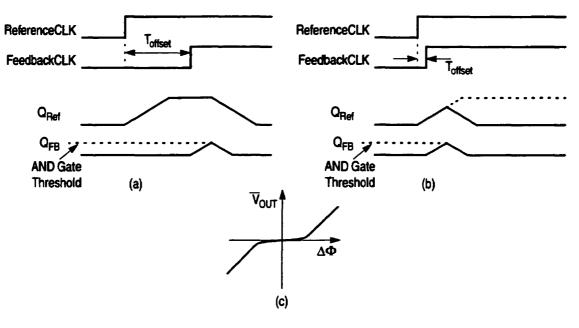

#### 2.1.2.1 PLL and DLL Operation

In the PLL, the phase-frequency detector determines the degree as to which the reference clock and internal clock are out of phase, and whether the internal clock is leading or lagging the reference clock. The low-pass filter is used to average the phase detector output, and hence remove high-frequency oscillations. This average value is then used to

Figure 2.4: (a) Phase-Locked Loop (b) Delay-Locked Loop

increase or decrease the frequency of the controlled ring oscillator. The DLL employs a controlled delay line whose delay is equal to one clock period.

PLLs are capable of reducing jitter, or frequency variations, in the reference clock. However, the oscillator introduces noise and thus jitter from internal circuitry. On the other hand, since DLLs output a delayed version of the reference clock, it cannot remove jitter, but introduces limited jitter.

#### 2.1.2.2 Skew Reduction

To reduce skew, PLLs and DLLs are introduced in the clock distribution networks. The feedback can come from any point on the chip; the clock edge at this point will be aligned to the input clocks. The dashed line between the PLL output and the feedback input in Figure 2.4(a) denotes this. In clock distribution networks, this feedback point should be selected to minimize overall clock skew while avoiding race conditions associated with negative skew between any points in the network.

#### 2.1.2.3 Frequency Synthesis

An important feature of PLLs is frequency synthesis, i.e. multiplication of the input clock rate by a rational number. By placing a clock divider in the feedback loop, the PLL will increase the output frequency until it matches the divided feedback frequency. If the feedback is divided by N, then the output clock rate will be multiplied by N. By

simultaneously dividing the clock rate of the reference or output clock by M, a clock ratio of N/M can be achieved.

#### 2.1.2.4 PLL and DLL Comparison

In the case where the reference clock is noisy or clock recovery is needed, a PLL is used. When choosing a circuit to use as a clock buffer or for skew reduction, a DLL is the best choice because it introduces limited jitter and is inherently stable, thus less complex and easier to design. However, a DLL is not used for frequency synthesis and is less desirable for applications involving varying frequencies.

## 2.2 - Low Power Using Dynamic Clock Management

There are four areas to consider when reducing the power consumption of systems implemented in an FPGA, an Application Specific Integrated Circuit (ASIC) or an SoC. Dynamic power consumption  $(P_d)$  is given by the equation:

$$P_d = kV_{DD}^2 C_L f (2.4)$$

where  $V_{DD}$  is the power supply voltage,  $C_L$  is the load capacitance, f is the frequency of switching and k is a switching activity factor. Low power techniques attempt to reduce the power supply voltage, the load capacitance, or switching activity in a circuit. One can also explore the direct proportionality between the operating clock rate and power consumption [21]. If the system clock is slowed to the minimum rate that will meet the computational requirements, both the instantaneous power and the overall energy consumption will be reduced without loss of performance.

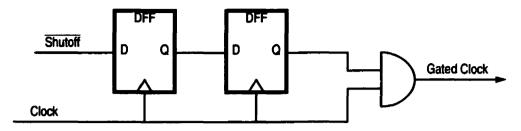

While the reduction of power consumption happens whenever the switching activity is reduced, only asynchronous design techniques [22] can use that reduction to the full. In synchronous systems, the existence of large clock distribution networks diminishes the effects of switching activity reduction in logic gates alone. Hence, the power reduction in synchronous systems can be realized to its full potential either by clock gating, with the

Figure 2.5: Clock Shutoff Circuitry used for Clock Gating

circuit shown in Figure 2.5, or by controlling the clock rate based on computational demand. While clock gating has been used widely, demonstrations of the latter technique for reducing power consumption have been presented only recently [23]. Studies [19,24] show that dynamic clock scaling is an efficient power reduction technique with large potential power savings.

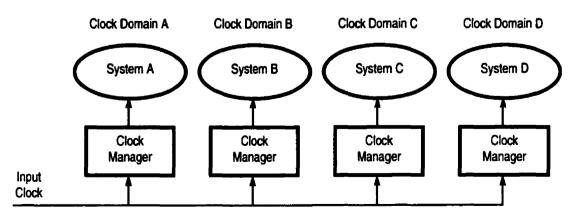

Clock management circuitry capable of performing clock synthesis include programmable frequency multipliers and dividers. As a result, scheduling algorithms [19,25] can be used to control the division/multiplication of the system clock to meet the demand, without wasting energy. As the computational demand in separate subsystems changes, each subsystem can operate independently at a speed that will allow it to satisfy current individual demands, as shown in Figure 2.6.

Dynamic frequency scaling can be used in conjunction with other methods, such as dynamic voltage scaling. When the clock is slowed, a controlled voltage source can reduce the system voltage level and still maintain the switching speed. For comparison, dynamic voltage scaling does not bring any benefit in conjunction with clock gating.

Figure 2.6: Embedded Application Using Clock Synthesis

## 2.2.1 - Voltage Scaling with Gating and Dynamic Clock Management

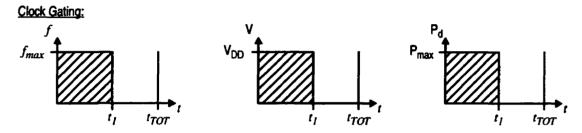

To better understand the benefits derived from voltage scaling and dynamic clock management in comparison to clock gating, consider the following example. Clock gating, represented in Figure 2.7, runs at the maximum frequency and full voltage for a specified period of time, represented in the time span from 0 to  $t_I$ . Then, the clock is gated and thus the frequency is dropped to 0. At this time, the voltage may also be shut off, however with the clock gated, f = 0 and  $P_d = 0$ , Equation (2.4).

Figure 2.7: The Frequency, Voltage, and Dynamic Power Resulting from Clock Gating

For clock gating, the total power consumption over time is represented by:

$$P_{dCG} = \int_0^{t_{rot}} P_d(t)dt = P_{max} \cdot t_1 = (kV_{DD}^2 C_L f_{max}) \cdot t_1$$

(2.5)

On the other hand, when we consider dynamic clock management, the system does not operate at full capacity over the time span, as shown in Figure 2.8. Because of this reduced frequency, the supply voltage can be also be reduced.

Figure 2.8: The Frequency, Voltage, and Dynamic Power Resulting from Dynamic Clock Management

In this case, for dynamic clock management, the total power consumption over time is:

$$P_{dDCM} = \int_0^{t_{TOT}} P_d(t)dt = P_1 \cdot t_{TOT} = (kV_1^2 C_L f_1) \cdot t_{TOT}$$

(2.6)

However, we should note:

$$f_1 = f_{max} \cdot \frac{t_1}{t_{TOT}} \tag{2.7}$$

So Equation (2.6) becomes:

$$P_{dDCM} = \left(kV_1^2 C_L \left(f_{max} \cdot \frac{t_1}{t_{TOT}}\right)\right) \cdot t_{TOT} = (kV_1^2 C_L f_{max}) \cdot t_1$$

(2.8)

Since  $V_1 < V_{DD}$  then  $P_{dDCM} < P_{dCG}$ . Therefore, voltage scaling performed concurrently with dynamic clock management has greater power savings than clock gating.

# 2.3 - Dynamic Clock Management Implementations

There are three scalable implementations of dynamic frequency scaling needed to perform the proposed low power methods. The simplest dynamic clock management circuit is an open-loop implementation with a clock divider inserted into the desired paths, shown in Figure 2.9(a). The maximum desired clock rate must be input to the system, which is then

Figure 2.9: Dynamic Clock Management Implementations

reduced dynamically using the clock divider. This circuit is inexpensive and simple, but cannot compensate for clock skew and may introduce excessive additional skew.

Skew can be compensated by introducing a Phase-Locked Loop (PLL) or Delay-Locked Loop (DLL) into the circuitry. The simplest dynamically scaled structure is obtained by taking feedback from a point that does not change frequency, as shown in Figure 2.9(b). This scheme can successfully apply dynamic clock division. For dynamic multiplication, the signal in the feedback path must be divided, as in Figure 2.9(c).

#### 2.3.1 - Frequency Changes and PLL Response

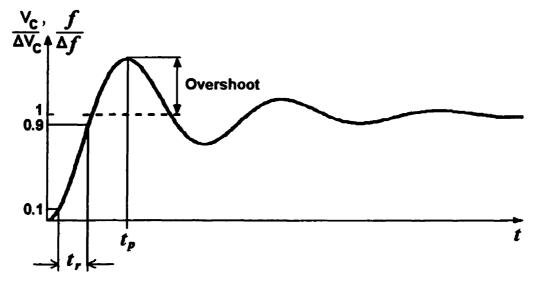

In the case of a large change in input or feedback frequency, the second-order step response of an underdamped PLL will exhibit the characteristics shown in Figure 2.10. If the overshoot of the lock frequency exceeds the maximum operational capabilities of the synchronous system, it may result in latching errors and possibly critical failures. The circuitry dependent on the output clock should then be stalled, or gated. To avoid an invalid output, the frequency transitions of the input of feedback path must be guaranteed to happen within the lock range [26]. If the PLL is designed for an overdamped step response to eliminate the possibility of an overshoot, the clock will not have to be gated, but will take longer to lock on to the new output frequency.

Figure 2.10: Step Response of Underdamped Second-Order System

Also, oscillations in the step response indicate that the output clock from the PLL may take some time to settle and regain a lock on the input signal. During this time, the output clock will not be properly aligned. In many cases, this frequency oscillation will not be of concern. However if the system is communicating with another that is expecting a known frequency, then communication should be temporarily suspended or the clock should be gated while the PLL is not in lock.

Appendix A discusses the dynamic behaviors and develops the mathematical formulae used to model the PLL. The design parameters are derived from this model and can be used to manipulate the PLL performance.

## 2.4 - Additional Applications of Clock Managers

Using a clock manager, the problems of clock distribution, mentioned in Section 2.1, are solved with the PLLs and DLLs. The FPGAs and SoCs now have built-in methods of clock skew reduction, frequency synthesis and phase alignment. If the clock manager is able to connect its output and feedback to I/O pads on the device, it can be used to synchronize with other devices and reduce skew on the board as well.

Frequency multipliers and dividers inside clock managers can be used for various applications of clock synthesis. By multiplying the clock rate, parts of the design inside Integrated Circuits (ICs) can be clocked at a rate higher than the board frequency. Multiple clock frequencies can be obtained by using several clock managers, or dividers. Similar to the current microprocessor based systems that run internal circuits and the I/O bus clock at different speeds, proper clock management is critical to realizing large systems on and off chip.

Time-domain multiplexing, that alternates between multiple sets of inputs, has been often considered in ICs for I/O multiplexing. The common design approach has been to use reduced frequency clocks with different phases. With a clock manager, both frequency division and phase shift can be programmed. Other applications, like duty cycle manipulation, can be programmed as well.

# 2.5 - Summary

Dynamic clock management and clock managers have many applications in FPGAs, SoCs and ASICs. They are used to solve clock distribution problems related to skew and jitter, but can also be used to reduce power consumption. Current low-power methods use circuit-based techniques at the penalty of performance. However, the system-level technique of dynamic frequency scaling can be used to reduce the average power consumption over time, while meeting the demands placed on the system. The basics of power reduction using dynamic clock managers have been presented in this chapter. Basic dynamic clock management solutions and alternative architectures have been outlined. The dynamic behavior of clock generation circuitry and its impact to proper functioning of dynamic clock management has been explained.

# **Chapter 3 - FPGA Implementation**

Until recently, Field Programmable Gate Array (FPGA) designs have focused on optimization for performance and area [27,28]. Due to their programmability, FPGAs are inherently more energy-inefficient than the equivalent Application Specific Integrated Circuit (ASIC) implementation. The research on reducing FPGA energy consumption has been directed at interconnect [27], the combinational logic architecture, and the clock distribution network [29]. In commercial FPGAs, effort was directed at operating the FPGA core at a reduced voltage level. The outlined approaches lead to power reduction at the expense of the interconnect speed. An alternative to these circuit-level techniques is the system-level technique of dynamic clock management.

## 3.1 - Dynamic Clock Management in FPGAs

Due to the existence of increasingly large clock distribution networks in synchronous systems, reducing switching activity in logic gates has a diminished effect on reducing overall power consumption. This phenomena is especially present in FPGAs because of large capacitances associated with routing switches, markedly for global signals such as a clock [30]. The actual loads on signals are not known in advance, causing buffers to be sized for the worst case scenario. Also, FPGAs achieve flexibility by adding many routing pass gates. These high capacitances can cause approximately 21% of the overall dissipation of energy in an FPGA to be generated by the clock signal. This ratio can rise

Figure 3.1: Typical FPGA Power Breakdown

above 50% in highly pipelined circuits [31,29]. Dynamic clock management can have a strong impact on the reduction of power consumption in FPGAs.

#### 3.1.1 - Examples of Existing Clock Managers

Most modern FPGAs have dedicated clock managers for solving high speed clock distribution problems in high density designs. They include Phase-Locked Loops (PLLs) and/or Delay-Locked Loops (DLLs) together with clock dividers and interface circuits. Several clock managers have been introduced in FPGAs. The three characteristic examples are by Xilinx [32], Altera [33] and Lucent [34].

#### 3.1.1.1 The Virtex FPGA Series by Xilinx

In the Virtex FPGA series, Xilinx Inc. decided to focus on DLL implementations and against the inclusion of PLLs. The clock manager is broken into four DLLs, with each being able to drive two global clock networks. Delay in the DLL is exactly one to four clock cycles and is therefore synchronized with the input clock edges. As a result, clock buffer delay is eliminated. Additional features of the Virtex clock manager include phase shifts, clock multiplication, and clock division. The reference clock can be shifted by 0°, 90°, 180° or 270°. The clock can also be doubled, the only multiplication factor a DLL can produce. The clock may also be divided by 1.5, 2, 2.5, 3, 4, 5, 8, or 16. In order to multiply

the clock by four, two DLLs can be used in series. The Virtex DLL can be programmed to exhibit a 50% duty cycle regardless of the input duty cycle. A lock signal will indicate when output clocks are valid. Until then, the output clocks can exhibit transients.

#### 3.1.1.2 The APEX 20K by Altera

Altera's APEX 20K and APEX 20KE FPGAs have a clock manager with ClockLock and ClockBoost features. The former uses a PLL with a balanced clock tree to minimize on-chip clock delay and skew. The later provides clock multiplication. On the APEX 20K, this multiplication factor is two or four. In the enhanced version, the APEX 20KE, the clock rate can be multiplied by a factor of  $m/(n \cdot k)$ , where m, n and k are integers ranging from 1 to 16. The ClockShift features a programmable delay and phase shift for the clock. The output clock delay is programmable to within the range of 2ns leading or lagging. The phase shift can be programmed to  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$  or  $270^{\circ}$ , similar to the Virtex FPGAs. The Altera clock manager also provides low jitter clocks to be used by external components. As a result, the clock manager can be used to synchronize with other components. The lock signal on the Altera APEX 20K and 20KE is set when the PLL is locked onto the input clock.

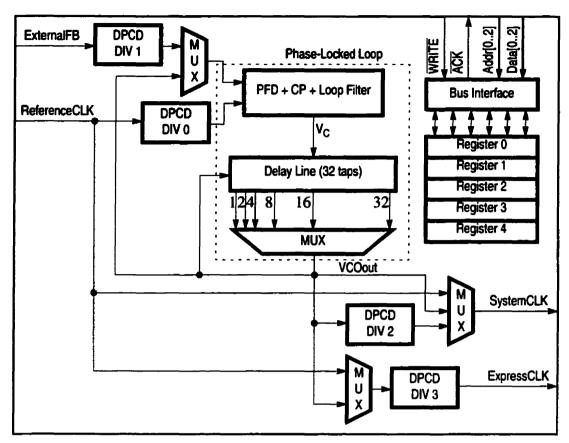

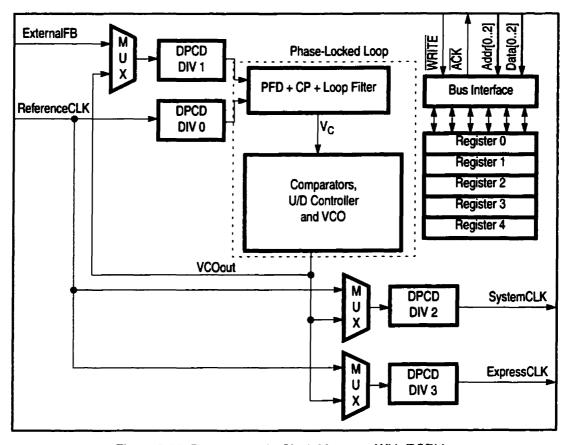

#### 3.1.1.3 The ORCA Series 3 by Lucent

Another family with a highly functional clock manager is the ORCA Series 3. These FPGAs contain two Programmable Clock Managers (PCMs), Figure 3.2, per chip. The ORCA PCM can be used for clock skew reduction (internally and externally), clock delay reduction, duty-cycle adjustment, clock phase adjustment, and clock rate multiplication and division. Each of the two PCMs on the FPGA contains a PLL and DLL. In DLL mode, the PCM can implement phase adjustment, clock doubling, and duty cycle adjustment. PLL mode performs clock skew reduction and multiplication.

Unlike the aforementioned clock managers, the ORCA PCM can be reconfigured during operation. With a simple read/write interface internal to the FPGA, the ORCA PCMs internal resources may be manipulated. By writing to the registers, multiplexers  $S_0$ - $S_{10}$  are

Figure 3.2: ORCA Programmable Clock Manager - Functional Block Diagram

directly manipulated to select PLL or DLL modes, as well as the clock dividers. The PCM also has a lock signal to indicate a stable output clock.

When incorporating the ORCA PCM into a design, the interconnection between the PCM and other components within the chip is highly flexible. There are dedicated pads for both an input clock and feedback, but general routing can be used as well. The dedicated paths are designed specifically for proper I/O buffering and low skew. Each PCM can drive two different, but interrelated clock networks. One output drives the Express Clock, specifically designed to distribute the fast clock signal, and the other system clock feeds the System Clock spine network through general routing. The output clock from the PCM can be connected directly to an I/O pad to drive external devices.

#### 3.1.1.4 Limitations of Existing Clock Managers

Although they accomplish their intended function, current FPGA clock managers are incapable of performing dynamic clock management because their dividers cannot execute dynamic division or multiplication. The Xilinx and Altera clock managers can

Figure 3.3: Standard Clock Divider Operation

only be programmed during initial configuration. The Lucent Programmable Clock Manager can be programmed during its operation, but this can lead to dangerous clock outputs if the clock is not gated.

# 3.2 - Dynamic Programmable Clock Divider

Changing the settings of existing clock dividers during their operation can lead to metastability and latching errors due to glitches, distortions, asymmetry, transient frequencies and additional clock edges of the output clock signal, as shown in Figure 3.3. Even shutting off the system during the change to the new frequency does not help in that case, as the inconsistent duty cycle clocks may be non-transient.

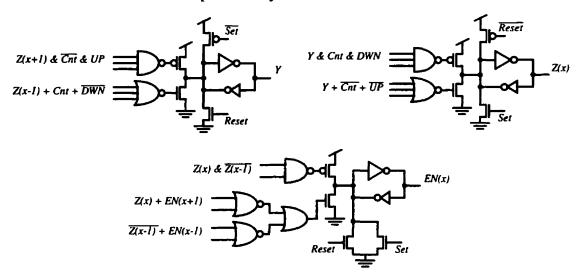

Figure 3.4: Dynamic Programmable Clock Divider

If dynamic clock dividers are added to the existing FPGA clock managers, they can be used for dynamic clock management. As a result, clean frequency changes can take effect within a clock cycle. The Dynamic Programmable Clock Divider (DPCD), of Figure 3.4, is capable of performing dynamic frequency division, for all integers from 1 to 9 inclusive, without undesired effects at the output.

#### 3.2.1 - DPCD Operational Description

Division of the input clock is performed by creating a loop of rising edge triggered D-flip-flops {A - D} driven by the input clock, and feeding the signal back into the loop through an inverter {P} to create the necessary clock level inversion. The length of the output clock period is varied by using a multiplexer {L} to change the number of flip-flops in the loop. The design may be easily expanded to provide a division value greater than 9 by increasing the number of flip-flops that can be placed in the loop. In order to perform odd division, flip-flops {E,F} extend the loop by half a period with an asynchronous clear of flip-flop {A} on the falling edge of the input clock. Multiplexer {M} is used to switch between the output of multiplexer {L} during even division, and the output of flip-flop {F} during odd division. For the divider output, multiplexer {N} chooses between the original input clock for a division value of one or zero, and the output of {A} when the division value is 2 or greater.

#### 3.2.1.1 Preventing Glitches and Preserving a 50% Duty Cycle

The output line of flip-flop {A} is labeled as Q0. One of the uses of line Q0 is to drive the clock inputs of flip-flops{G,H,J,K}. This implies that the value of I\_DIV0, I\_DIV1, I\_DIV2 and I\_DIV3 will be latched by flip-flops {K,J,H,G} respectively on the rising edge of the output signal generated by flip-flop {A}. As a result, the output lines of these flip-flops, labeled DIV0, DIV1, DIV2 and DIV3 will only change immediately after the rising edge of line Q0.

Between flip-flops {A - D} there exists combinational logic {Q,R,S} comprised of AND and OR gates. The purpose of this combinational logic is to cause a logical '0' to be input to the flip-flops in the chain that are not in the loop for the current division setting. They

also prevent irregular oscillations in the circuit, and eliminate unnecessary switching. For example, in the case of a division by two, a feedback loop is formed consisting of flip-flop {A}, multiplexers {L,M}, and inverter {P}. Logic components {Q,R,S} will only allow a logical '0' to be placed on the inputs of flip-flops {B,C,D}. This case also holds true when the division setting is also 3. As a result, flip-flops {B,C,D} will not transition to a '1' during the time when the division value is two or three. When the division setting is a value of 4 or 5, the logic components at {Q} will allow the logical signal of Q0 to pass through to the input of flip-flop {B}. However, logic components {R,S} will only pass a logical '0'.

In order to understand the reasoning behind the DPCD design, an example of operation will be explored for division value settings of 1 and then transitioned to 8. As mentioned previously, when the division value is one or zero, the output of multiplexer {N} is the original input signal and there is no alteration to the reference clock.

The continued oscillation of the output from flip-flop {A} is important even though the output of the DPCD is not affected by this signal. This is to ensure that flip-flops {G,H,J,K} will still have an oscillating input clock so they can latch the new division values placed on I\_DIV[3..0]. When the new division setting of 8 is placed on I\_DIV[3..0], the value of DIV[3..0] will continue to hold the previous division value until the rising edge of the output of flip-flop {A}. By waiting until this point in the operation to update the logical values of DIV[3..0], the reference clock and Q0 will be a logical '1'. The new division value will cause the output of multiplexer {N} to be Q0 instead of the reference clock as previously output. Since both Q0 and the reference clock are '1', the output will

Figure 3.5: DCPD Operation

not glitch. Also, this will force transitions at the beginning of each clock cycle, thus preventing the output from transitioning before the clock cycle is complete and ensuring a 50% duty cycle at all times.

This procedure of changing from a division of 1 to 8 exposes the critical path of the DPCD. The output of Q0 must force flip-flops {G,H,J,K} to latch the new values of DIV[3..0] and update the selector settings of multiplexer {N} before the output of the reference clock becomes low. Otherwise, a glitch could occur.

Also with this new division value, the loop now consists of flip flops  $\{A,B,C,D\}$ , multiplexers  $\{L,M\}$ , and inverter  $\{P\}$ . Therefore, logic  $\{Q,R,S\}$  must allow the output of each flip-flop in the loop to reach the input of the successive flip-flop in the loop. If this logic had not been forcing a logical '0' during the divide by one, then the periodic oscillation of flip-flop  $\{A\}$ , toggling on each rising edge of the reference clock, would propagate through flip-flops  $\{A - D\}$  and then be captured and fed back into the loop when the transition to the new division value occurs (such as in Figure 3.3, division by 8).

#### 3.2.2 - DPCD Benefits

As can be noted in Figure 3.5, all clock transitions are completely glitchless and require merely one clock cycle for the input division value to take effect. The duty cycle of 50% is maintained throughout operation, even during frequency transitions. Also, by preventing a logical '1' to propagate through flip-flops {**B** - **D**} when they are not included in the loop, unnecessary switching is prevented. This results in less power consumption

#### 3.2.3 - Other Clock Dividers

Another method of dynamic frequency synthesis is performed with a chain of dividers capable of only even divisions, shown in Figure 3.6 and described in [21]. Each divider would statically divide the clock to each successive frequency, and a multiplexer would be used to choose the desired frequency. In Figure 3.6, each divider halves the frequency with a divide by two, or toggle flip-flop. There is no additional circuitry to ensure that the multiplexer changes the output frequency in a manner that will prevent glitches. Also,

Figure 3.6: Frequency Synthesis Using Divider Chain

each delay stage in the divider will introduce additional skew equal to the propagation delay of the toggle flip-flop.

The design of a clock divider with the topology in Figure 3.6 results in an exponential divide ratio and the necessity for multiple static dividers. Also, the design does not shut off dividers that are not being currently used. However, the DPCD, being smaller and more power efficient, is a single circuit capable of performing divisions from 1 to 9. The DPCD design in Figure 3.4 is expandable to greater division ratios by simply adding more D-flip-flops in series.

Table 1: DCPD Performance

|                           | ORCA or3t55-6 ‡ | Altera EPF10K20-3 ‡ | <b>Custom</b> ♥  |

|---------------------------|-----------------|---------------------|------------------|

| Size                      | 4 PFUs          | 15 Logic Cells      | 13 DFF, 47 gates |

| Max Operating Frequency   | 251 MHz         | 76 MHz              | 1.2GHz           |

| Power Consumption @ 25MHz | 8.3 mW*         | 16.7 mW*            | 1.47mW           |

‡ compiled VHDL code with no specific optimization

\*Based on estimation formulae provided by manufacturers

♥ 0.18µm 1.8V CMOS TSMC process, capable of divisions up to 15,

simulations can be found in Appendix D

The DPCD improves upon the clock divider in Lucent's ORCA PCM [35,36] in the fact that it is fast, glitchless and does not require a reset. The divider can directly replace the current divider in the ORCA PCM without modification to the internal structure. The DPCD can also be implemented in the existing logic cells of both the Altera and Lucent FPGAs.

Figure 3.7: Embedded Application Using DPCDs For Clock Synthesis

#### 3.2.4 - DPCD Applications

As possible use of the DPCD is depicted in Figure 3.7. Multiple DPCDs may be used to divide an input clock for separate systems. Each system operates at the minimum clock frequency that still meets the performance objectives of that particular system. Therefore, while some logic blocks have high demand and need to run at a high frequency, other blocks will less demand may run at a lower frequency and conserve energy. This method allows flexibility and gained power efficiency over a large system that is not partitioned to allow independent clock management. Without partitioning, the minimum clock frequency would be limited to the subsystem with the highest demand, thus resulting in energy waste in those subsystems having less demand.

The DPCD can also be used in a PCM. With DPCDs as the clock dividers, the PCM would be quickly reprogrammed to a new division or multiplication value without glitching or transient errors that could cause failure in the PLL. A PLL, including a DPCD in its feedback, can be used for clock multiplication, then several other DPCDs can divide the PLL clock signal for all of the subsystems, as shown in Figure 3.8. By using DPCDs in these systems, they can be quickly reprogrammed to a new division or multiplication value without glitching or transient errors that could cause failure in the PLL or subsystems. This increases the flexibility of dynamic clock management.

Figure 3.8: Embedded Application Using DPCDs In Clock Synthesis

With a PLL for Clock Multiplication

# 3.3 - Partitioning Issues

Three issues arise from partitioning a large system into multiple subsystems for independent dynamic clock management. The first issue is the importance on each independent subsystem to perform a function that is not heavily temporally dependent on another subsystem. For example, say system B required data from system A every four clock cycles and it takes four clock cycles for system A to produce that data. Then running system A and B at different clock frequencies would produce either a constant wait for the data, or an over abundance of data that cannot be processed. However, system A and B may be dependent on data produced by the opposing system as long as the data may be accumulated and stored, or if the data is produced or required infrequently. In the case of an SoC, there are natural partitions already present in the integration of several systems that originally were completely independent. These systems should be partitioned so that they can communicate through a channel dedicated to passing data and a limited number of control signals. The communication channel may be common among several components in a bus structure, or may be dedicated with a standard or non-standard protocol.

#### 3.3.1 - Communication

A second issue is the communication between those systems operating at independent frequencies may be accomplished. This issue can be solved with synchronization techniques used in many systems. One technique is to bring the systems, that wish to communicate, to the same operating frequency. If the PCMs and/or the DPCDs are designed for limited and constant skew, then the skew between the clock signals for both systems will be negligible. Therefore, communication can continue in a synchronous manner without metastability concerns. For this technique, data must be accumulated by each system for a large data transfer, or small data segments should be passed infrequently, so that the systems are not consistently running at the same frequency to pass data. Another approach is to use an asynchronous FIFO. Each system can communicate with the FIFO at its own operating frequency and therefore do not have to be matched during communication. In addition, synchronizer circuits may be employed, as discussed in chapter 10 of [37]. They can consume less space, but they are more complex and must be extremely robust. These circuits can pass data from one synchronous circuit to another even if they are running at different frequencies and do not contain coincident clock edges.

#### 3.3.2 - Control Logic

The third partitioning issue concerns the control logic used to determine the setting for the current operating frequency. First, a circuit or method must be devised to determine the level of demand placed on the system. For example, in a microprocessor, this can be derived from the percentage of time running the idle process. Another method is to incorporate a FIFO on the input data stream that relays the number of data cells that are being used, thus conveying how full is the FIFO. Then based on the current frequency and the occupancy percentage of the FIFO, the next frequency setting can be computed. There are several published algorithms in existence that can compute the best frequency based on past demands and operating frequencies [25]. There are also publications concerning algorithms and systems that vary the voltage of a system based on demand, and similar methods can be applied to dynamic clock management [24].

A possible implementation of the previously mentioned scheduling algorithms is as follows. A FIFO is included in the input data path. After a specified time period, the demand of the system is measured based on the percentage of data cells occupied in the FIFO. If the number of cells that can be processed in the time period for a particular frequency is known, then the frequency setting for the next time period can be set to process all of the cells in the FIFO. After the time period, the situation is re-evaluated and a new setting is made. Another possible algorithm simply maps the number percentage of occupied cells in the FIFO directly to a frequency setting. As the percentage rises, the operating frequency is increased proportionally.

For added complexity and flexibility in the overall system, the control logic for each independent subsystem can be shared, or communicate with one another, in order to coordinate frequency settings or predict the future demand of each subsystem.

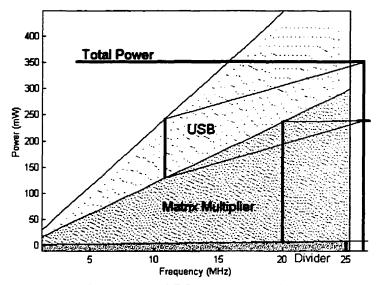

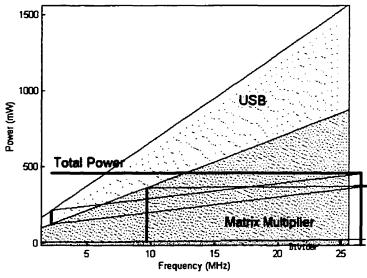

## 3.4 - Case Study

An embedded system coprocessor has been designed to speed up digital signal processing functions. The system takes advantage of dynamic clocking for reducing its power consumption. The system comprises a Universal Serial Bus (USB) client communication front-end and a reconfigurable signal processing unit. Here, we consider a matrix multiplication circuit. Power to the coprocessor is delivered by the USB cable from the host. Depending on the frame rate and data stream format, the bandwidth requirements of the multiplier will change. Therefore, the required clock rate is based on the bandwidth

Figure 3.9: USB/Matrix Multiplier System

demand. Also, the standard protocol for USB includes two operating speeds that can be changed on the fly.

#### 3.4.1 - Partitioning

The entire system was easily separated into the natural partitions of the USB client and the matrix multiplication unit. Each partition was assigned a clock domain and a DPCD in the user logic to divide the reference clock. The bandwidth of the USB client is the limiting factor in the operating speed of the matrix multiplication unit. With the advancement to USB 2.0 and the increased bandwidth the protocol provides, there is a large increase in the rate at which the communication client can transmit the data manipulated by the signal processing unit.

#### 3.4.2 - Communication

Several ideas for the communication channel between the matrix multiplier unit and the USB client were explored. First, an asynchronous FIFO was designed to bridge the gap between the two subsystems. This design worked well, but in order to increase flexibility in the timing of the data transmissions to the USB host and allow for large burst transmissions, the FIFO had to be sufficient in size to accumulate large quantities of data.

A second method was to store the data in registers within the matrix multiplier unit and then match the frequencies of the two subsystems for a data transfer to a set of registers in the USB client. Each register consumed less area than the asynchronous FIFO due to the reduction in control logic, but the requirement for a register in each subsystem created an increase in area for the final design. This also consumed much overhead during the data transfers and limited the autonomy of each subsystem.

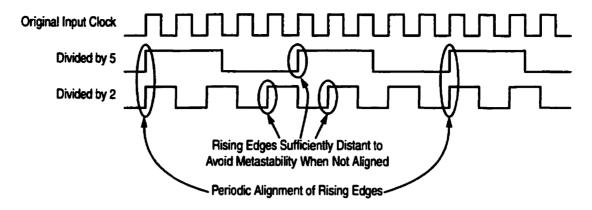

The third method takes advantage of the periodic alignment of rising clock edges from integer divisions of the reference clock. Both clock domains are generated with DPCDs driven by the same reference clock. Not only will rising edges be periodically aligned, but those rising edges that are not aligned will be spaced by at least one period of the input clock. Sample output waveforms demonstrating this method are displayed in Figure 3.10.

Figure 3.10: Output Clock Waveforms Demonstrating Periodic Alignment of Rising Edges When a Clock Signal is Divided by Integer Values

With the spacing of the unaligned rising edges, metastability errors will not occur due to violation of setup and hold times. If each subsystem knows its own speed and the speed of the subsystem it is communicating with, then all subsystems can be designed to latch data only when valid and to present new data after the previous data has been properly latched.

#### 3.4.3 - Control Logic