### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# Transmitter for an Adaptive Redundant Optical Interconnect

**Eric Bernier**

Department of Electrical and Computer Engineering McGill University Montreal, Quebec Canada August 2000

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the degree of Masters of Engineering

© Eric Bernier, 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérance

Our file Notre rélérence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-70221-9

# Canadä

### **Table of Content**

ABSTRACT IV

SOMMAIRE V

ACKNOWLEDGEMENTS VI

#### CHAPTER 1- INTRODUCTION

- 1.1. MOTIVATION 1

- 1.2. FREE SPACE OPTICAL INTERCONNECTION 3

- 1.3. COMPETING OPTICAL TECHNOLOGY 5

- 1.3.1. Parallel Fiber interconnection 5

- 1.3.2. Fiber image guides 6

- 1.4. THESIS ORGANIZATION 6

- 1.5. **REFERENCES** 7

#### CHAPTER 2- THE ADAPTIVE REDUNDANT OPTICAL INTERCONNECTION 9

1

- 2.1. INTRODUCTION

- 2.2. STATIC OPTICAL INTERCONNECTION 10

9

- 2.3. DYNAMIC OPTICAL INTERCONNECTION 12

- 2.4. **REDUNDANT INTERCONNECTION** 13

- 2.5. SYSTEM IMPLEMENTATION 17

- 2.5.1. Transmitter 18

- 2.5.2. Optical system 18

- 2.5.3. Receiver 21

- 2.5.4. Optical Feedback (Hunt mechanism) 22

- 2.5.5. Speed and Communication protocol 25

- 2.6. **Reference** 26

#### CHAPTER 3- SINGLE-MODE VCSEL FOR FSOI 28

- 3.1. INTRODUCTION 28

- 3.2. VCSEL TECHNOLOGY OVER VIEW 29

- 3.3. VCSEL USED FOR THE FSOI SYSTEM 32

- 3.4. PHYSICAL CHARACTERISTICS 33

- 3.5. ELECTRICAL CHARACTERISTICS 35

- 3.6. **UNIFORMITY** 37

- 3.7. MODULATION CHARACTERISTICS 38

- 3.8. TEMPERATURE DEPENDENCE ON VCSEL CHARACTERISTICS 41

- 3.9. VCSEL MODAL CHARACTERISTICS 42

- 3.10. BEAM DIVERGENCE AND GAUSSIAN OPTICS 47

- 3.11. CONCLUSION 49

- 3.12. REFERENCE 50

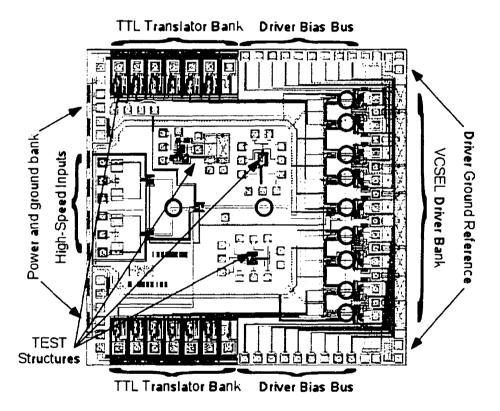

#### CHAPTER 4- DRIVER CHIP DESIGN52

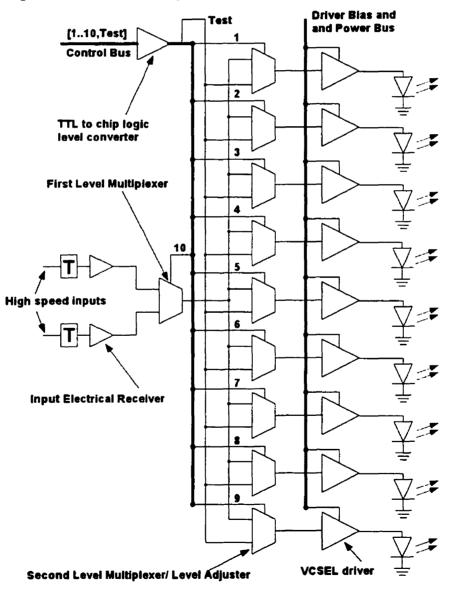

- 4.1. INTRODUCTION 52

- 4.2. ARCHITECTURE 54

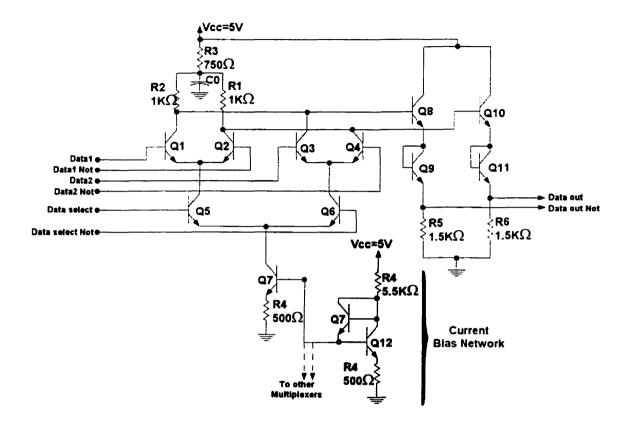

- 4.3. LOGIC ROUTING CIRCUITRY 56

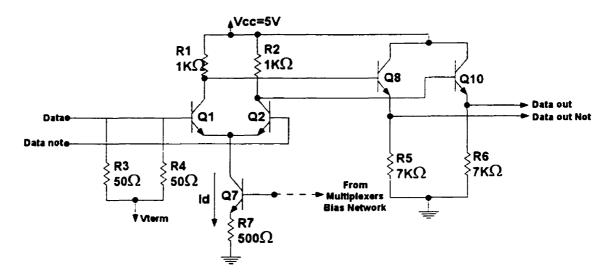

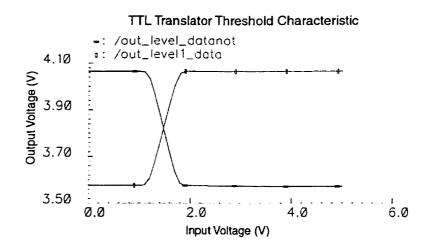

- 4.4. TTL INPUT TRANSLATOR 60

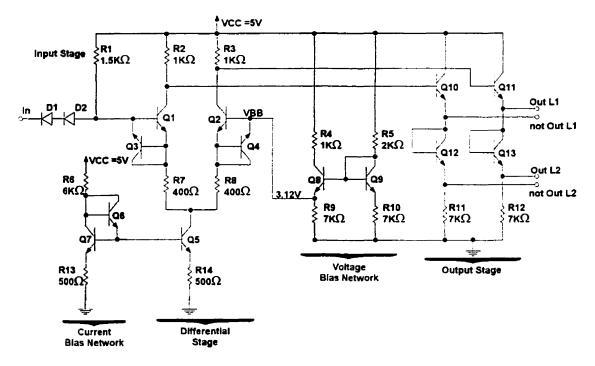

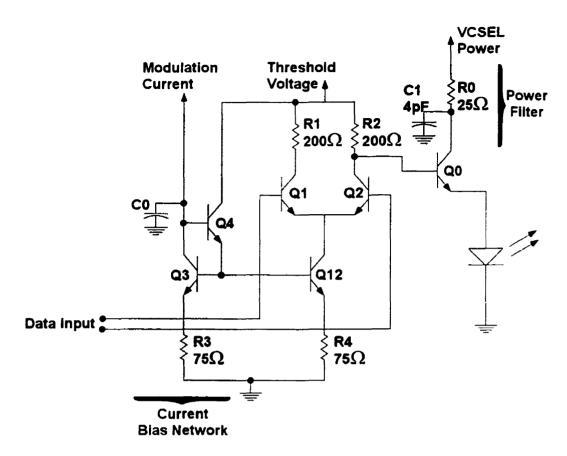

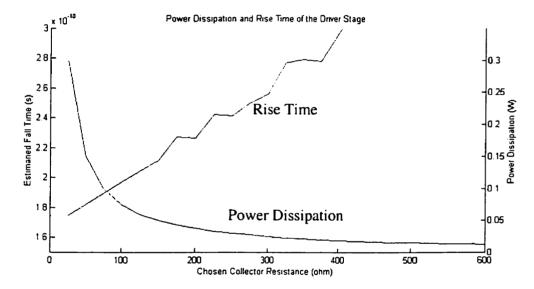

- 4.5. LASER DRIVER SECTION 64

- 4.6. LAYOUT AND FLOOR PLAN 68

- 4.7. TRANSMITTER PACKAGING 70

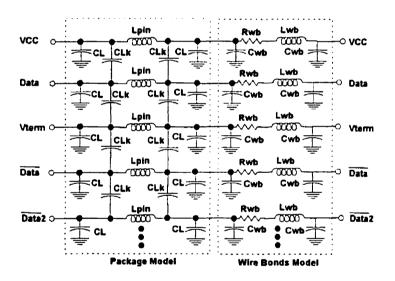

- 4.7.1. Introduction 70

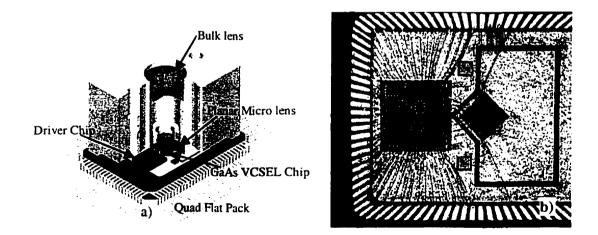

- 4.7.2. Package choice and modifications 70

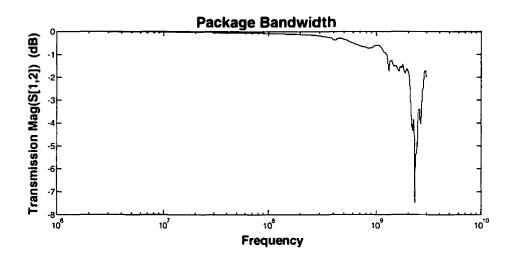

- 4.7.3. Electrical Modeling and Performance 73

- 4.7.4. Thermal considerations 74

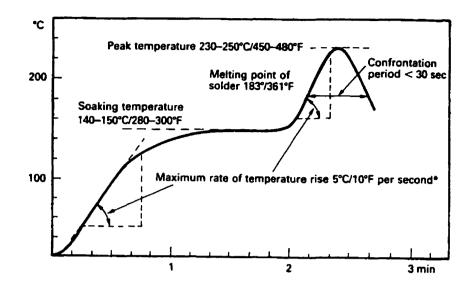

- 4.7.5. Package Assembly Process 76

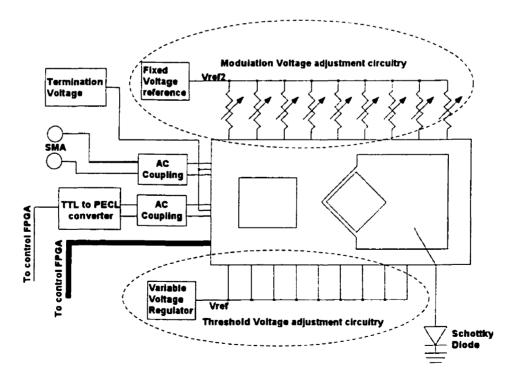

- 4.8. TRANSMITTER SURROUNDING ELECTRONICS 78

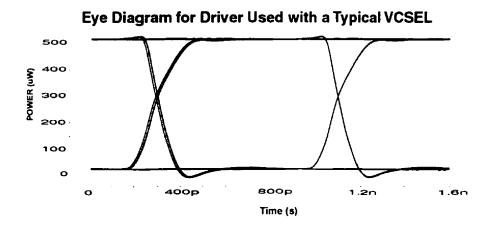

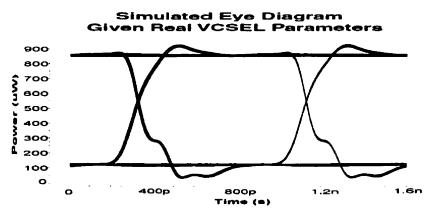

- 4.9. DRIVER CHIP SIMULATION AND RESULTS 82

- 4.10. CONCLUSION 83

- 4.11. References 83

#### CHAPTER 5- TESTING AND PERFORMANCE 86

- 5.1. INTRODUCTION 86

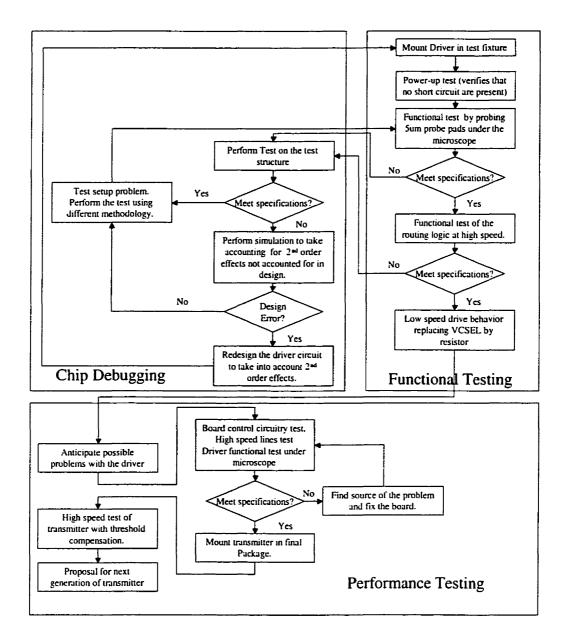

- 5.2. TEST PLAN 86

- 5.3. FUNCTIONAL TEST 89

- 5.4. PERFORMANCE TESTS 93

- 5.5. CONCLUSION 98

- 5.6. REFERENCES 99

#### CHAPTER 6- CONCLUSION AND FUTURE WORK 100

### Abstract

The ever-increasing demand for bandwidth places a more stringent demand on the interconnections within electronic systems. Free space optical interconnection (FSOI) is a technology that satisfies the bandwidth requirements of newer systems. The development of the Vertical Cavity Surface Emitting Laser (VCSEL), which provides high yields and low cost makes FSOI possible. However, the packaging and alignment of opto-electronic components still dominate the manufacturing costs. A solution to the problem of alignment is to use spatial redundancy. One way to accomplish this is by increasing the number of possible optical links and using only a subset of those links to provide a collection of reliable high-speed channels.

This thesis presents the implementation of a transmitter specially developed for a redundant channels alignment FSOI. The implementation consists of a 1.25Gb/s transmitter chip driving one element of a 3x3 VCSEL array. The driver chip was designed and fabricated from a commercial 25-Ghz Silicon bipolar process. The design, construction and integration aspects covering the microelectronics, opto-electronics and packaging for the transmitter are summarized. Characterization results are presented for a transmission rate of 1 Gbit/s per channel.

### Sommaire

La demande toujours grandissante pour la bande passante dans les circuits électroniques crée une forte pression sur les interconnexions. Les interconnexions optiques à l'air libre (IOAL) sont une technologie qui offre de satisfaire les besoins en bande passante des nouveaux systèmes. Vue le développement effectué sur les lasers de cavité verticale à émission de surface (VCSEL), ceux-ci ont maintenant de hauts rendements à moindre coût; ceci permet donc de faciliter la création des IOAL. Cependant, l'encapsulation et l'alignement des composants électroniques domine encore les coûts de fabrication. Une solution au problème de l'alignement est d'utiliser la redondance spatiale. Une façon d'accomplir ceci est d'augmenter le nombre de lien possibles et d'utiliser seulement un sous-ensemble de ces liens pour fournir des canaux de communication de haute qualité.

Cette thèse présente la réalisation d'un transmetteur spécialement développé pour une interconnexion optique à canaux redondants. Cette réalisation consiste en une puce de transmission de 1.25Gb/s actionnant un des VCSEL contenu dans une matrice de 3x3 VCSEL. La puce de transmission a été développée et fabriquée avec un procédé commercial de silicone bipolaire 25Ghz. Les aspects du développement, de la construction et de l'intégration couvrant la micro-électronique, l'optoélectronique et l'encapsulation du transmetteur sont résumés. Les résultats de la caractérisation pour une transmission de 1Gb/s sont présentés.

### Acknowledgements

I would like to thank my supervisor Dr. David Plant most sincerely. Without the constant support and guidance he has given me throughout the past two years my experience would not have been as interesting and rewarding. I thank him not only for caring about my technical development but also about my personal growth. I am also grateful to Professor Andrew Kirk for his constant support and continuous advice. Without them, most of that work would not have been possible.

I would like to thank all the other members of the team that worked on this project with me: Madeleine Mony, Mitch Salzberg, Eric Bisaillon, Daniel Brosseau, Charif Beainy and Rawiya Sharif without wohm that project would have been impossible to realize within the two year time frame. I have to dedicate a lot of gratitude to M. Tsuyoshi Yamamoto for having shared his unique expertise with me during his stay in Montreal.

I have to dedicate a special thanks to Dominic Goodwill, David Kabal and Petre Popescu for having participated with me in very rich discussions about the realization of this project. I would also like to thank them for giving me the opportunity to gain experience with them at Nortel Networks.

A few special words to Mike Ayliffe, Frederic Lacroix, David Rolston, Feras Michael and Alan Chuah. They participated with me on the McGill Photonics Backplane for the past 3 years. I have dedicated a lot of time to that project and I am sad that I have to leave before its completion. I know it is not always an easy task to takeover a team member departure and I would like to thank them in advance for their understanding.

I would also like to thank Keivan Razavi, Marc Chateauneuf, Mike Venditti, Xin Xue, Greg Brady, Fan Cheng, Julien Faucher, Emmanuelle Laprise, Julianna Lin, Tomasz Maj, Frederic Dupuis, Antoun Ghanem, Robert Varano, Guillaume Boisset, for their help support and friendship that has made this experience a great one.

Finally, I wish to thank my parents and my brother for their love and support, not only for the past two years, but since the day I was born. They are an integral part of the success I enjoyed through out my studies.

The work presented in this thesis was supported by Nortel Network and Le Fonds pour la Formation de Chercheurs et l'Aide à la Recherche (FCAR).

### Chapter 1- Introduction

#### 1.1. Motivation

The Semiconductor Industry Association (SIA) road map [1,2], indicates an increasing chip size, density, output pins and aggregate input/output pins for next decades. Clock rate for new high performance processors are forecasted to be in the range of 1600Mhz by 2002 and to reach 3000Mhz by 2011. Interconnects have been represented as the technology with the largest potential technology gaps [1]. Although metallic interconnections are relatively cheap for short distances and are constantly being improved, it is not clear that they could support the required interconnection rates at competitive costs.

In parallel with the evolution toward faster and more powerful digital processors, the communication industry is undergoing a boom in the demand for increased communication capacity [3]. The 30% annual growth in data traffic worldwide has been fueled by the Internet [4]. For the future, Internet is key to the development of new services where the convergence of data, video, voice and wireless technology will provide more flexibility and cost reduction but will demand increasing bandwidth. In the network centric computing age we are entering, the most important resource will be a powerful datacom network [5].

The demand increase will lead to the need to develop ATM and IP routers and switching products with throughputs of 1 Tb/s and beyond. The interconnection needs targeted for a 5 years time frame are in the order of 1-5 Tb/s bi-directional interconnect capacity at the backplane, inter-shelf and inter-frame levels [4].

Current electrical technology used for interconnecting PCBs include coaxial cables, twisted pair and flex microstrip circuits. Metal wire is by far the cheapest medium within its bandwidth and distance limitations. However, the limitations are becoming apparent as the system speeds continue to increase. Those limitations are [6]:

- High power dissipation from line drivers due to the capacitive loading effect of electrical line.

- Difficult power management for the increased power dissipation that comes with higher interconnection density.

- Signal distortion that occurs due to reflection from improperly terminated line.

- Capacitive and inductive cross-talk.

- Attenuation of electromagnetic waves from the finite resistance of the metal conductor.

- Sensitivity to electromagnetic interference.

- Clock and signal skew resulting from delay variation in separate clock and signal path.

- Cost.

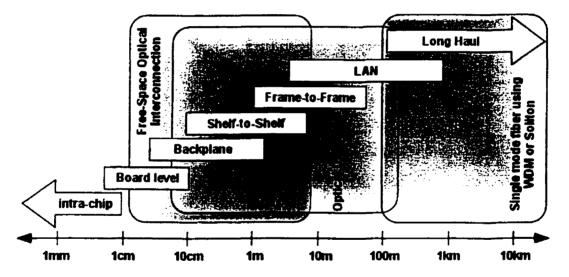

Figure 1.1 System packaging hierarchy vs. Optical interconnection technology

Traditionally, optical communication solutions have been successful in those areas that required longer unrepeated distances than can be provided by copper solutions. Figure 1.1 provides an overview of the conventional digital interconnection hierarchy and their typical lengths. Various optical interconnection alternatives are being researched, including free space optics, individual fiber based arrays, polymer waveguides, and fiber image guides. The cost for metal interconnect becomes a significant part of the

system cost as the bandwidth times distance factor increase. In comparison, the cost for optical interconnection as a function of distance is relatively flat with distance [7]. This explains why as increase in performance are needed, optical solutions become more attractive, the bandwidth time distance factor being higher for high performance systems. Optical interconnection do not only provide a way to reduce cost; they also provide higher interconnection density, less crosstalk, easier impedance matching, better skew performance and higher reliability [6].

#### 1.2. Free space Optical Interconnection

This thesis is concerned with the design and characterization of a transmitter for a Free Space Optical Interconnection (FSOI). FSOI has been the subject of much research in

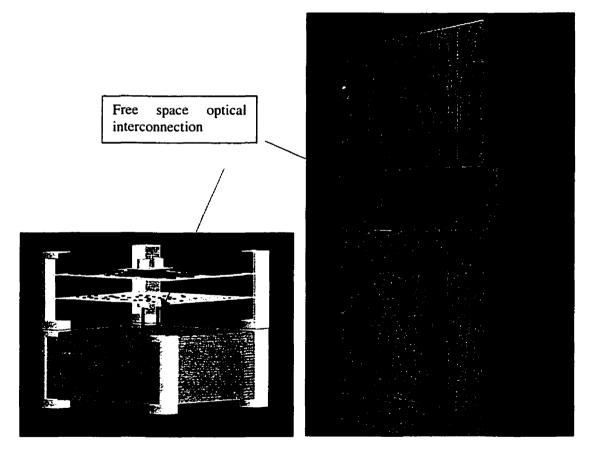

Figure 1.2 Example of usage of FSOI. Left: used in stackable modules type of systems. Allow for hot swap and "easy to install" high-speed interconnection between sub-systems. Right: FSOI used in between shelf of high performance system.

the past years; some of the best examples of interconnections systems can be found in the references [4,9-15]. FSOI offers evolutionary means of extending the performance of electronic technology. Rather than concentrating the light energy using waveguides, FSOI uses imaging systems and bulk material in order to allow for the propagation of the signal from the transmitter to the receiver. One advantage of FSOI is the use of three-dimensional propagation of information thus allowing the conception of very high density interconnections between the transmitter and receiver planes. Low crosstalk is present even for systems featuring thousands of multi-Gb/s I/O. It offers a scalability advantage since no cable or circuit board is needed between the transmitter and receiver; the same devices can be used for connecting system at the intra-shelf or inter-shelf level. FSOI systems do not use connectors and therefore no connector failure arises. In addition, FSOI can be used in order to retrofit existing product lines at low cost since the need for changing the principal back plane can be avoided.

However, FSOI systems present designs challenges in order to become a commercially viable solution. The most critical issues associated with free space optical interconnects are those of misalignment tolerance [8]. The packaging and alignment quality will affect the optical power loss along the optical path and can allow for optical crosstalk in between channels. Loss can compromise the low optical power and the density advantages of the FSOI. In order to increase the alignment quality, advanced manufacturing methods can be used. However, the optoelectronic transmitter and receiver cost might be adversely affected. Other methods of reducing misalignment sensitivity in free space optical interconnects will be introduced throughout this thesis.

FSOI interconnection length is limited principally by the unobstructed distance between the transmitter and the receiver, and the ease to which alignment can be established over the transmission distance. FSOI are best used in the medium-to-short distances as high performance interconnects in digital systems. The economical crossover point where FSOI can be used is principally in the inter-shelf PCB-to-PCB communication. Figure 1.2 shows applications in which FSOIs can be used. As an example, FSOI can become the principal communication trunk in a multi rack system, the optical link being used principally to offer inter-rack and inter-shelf PCB communication. Another application is as a high-speed bus in between modules of a stackable system. The ease by which free space optical interconnection is established makes the technology attractive to this application. Optical Bus for communications between PCBs are also another application being looked into by many research groups. However, immediate bandwidth/distance needs of electronic systems do not call for the use of the FSOI technology at this level for the moment [4,7].

#### 1.3. Competing optical technology

The following two sections present two selected optical technologies competing with Free space Interconnection. The major difference in interconnect solutions is the media used to propagate the light. This thesis is concerned with the transmitter section of a free space optical interconnection. Many sections of this thesis could also be used for competing technologies. As well, the development made in the competing technologies can help build better free space optical interconnections.

#### 1.3.1. Parallel Fiber interconnection

Parallel fiber interconnection has attracted many research group through out the past years [16-19]. This type of interconnection involves combining several fiber links in a parallel fashion. Parallel fiber interconnection is presently being offered in commercial versions using newly developed VCSEL arrays and parallel fiber connectors. One commercial solution is offering up to 30 Gb/s unidirectional [20]. These solutions are still far from the 5Tb/s demanded for high end applications as an example one would need to use a 167 link of that type in order to provide enough bandwidth. As an attempt to increase the link density, 2D transmission channels are being examined [19]. However, fiber array systems will face some problems in increasing the channel density. One of those problems is that fibers themselves are expensive and inflexible. The second problem is the one of alignment of the fiber to the emitter and detector. This alignment will become remarkably difficult as the number of channels increases. Free space optical interconnections are not affected by these problems since they do not require alignment to a fiber for every individual channel.

#### 1.3.2. Fiber image guides

One propagation medium that allows the desired density to be implemented is fiber image guides [21-23]. Fiber image guides were originally developed to be used as various imaging and sensing tools in medical diagnostics as well as in industrial inspection applications. A fiber image guide consists of a coherent bundle of individual step-index fibers. The core of the fibers can be as small as  $3\mu$ m and can be separated by as little as  $5\mu$ m [21]. This configuration allows fiber image guides to exactly copy the transmission pattern from the input end to the output end. By doing so, the alignment of dense link matrix could be eased; putting that technology in direct competition with free space interconnections.

#### 1.4. Thesis Organization

This thesis deals with the design and test of a fully packaged transmitter chip. The transmitter design included the choice and cauterization of the light emitting technology, the design, test and cauterization of a high-performance silicon driver chip and the design and test of the packaging and control circuitry for the transmitter chip. Chapter 2 will give an overview of the methods used to overcome the alignment problems within a free space optical interconnection. Following this overview, the architecture of a system using extra transmitters and detectors in order to account for misalignment will be described. This section contains work provided by the other contributors to the project. This an overview of the optics, receiver, and algorithms used in the project to give the reader a more global context for the transmitter use. Chapter 3 will give an overview of the emitter technology, which is mainly a VCSEL. Parallel optical interconnections would have been a lot harder to conceive without this technology. This overview will be presented along with the characterization of the VCSELs used for the implementation of the interconnection. Chapter 4 will present the architecture and the design of the transmitter. Also, the packaging of the transmitter will be discussed. Chapter 5 is concerned with the testing of the transmitter section of the optical interconnection. Finally, the last chapter will conclude the thesis and suggest idea for future work.

#### 1.5. References

- [1] The National Technology Roadmap For Semiconductors. Semiconductor Industry Association, p. B1, 1997.

- [2] International Technology Roadmap for Semiconductor 1998 Update, Semiconductor Association, p. 4, 1998.

- [3] R.C Willimason, "Overview of VCSEL Applications", Vertical-Cavity Surface Emitting Lasers, Cambridge University Press, p. 338, 1999.

- [4] D. J. Goodwill, D. Kabal, P. Palacharla, "Free space optical interconnect at 1.25Gb/s/channel using adaptive alignment," Optical Fiber communication (OFC/IOOC 99), SanDiego, CA, 1999.

- [5] C. DeCusatis, "Optical data communication: fundamentals and future directions", *Opt. Eng.*, Vol. 37, pp. 3082-3099, 1998.

- [6] F.B. McCormick, "Free-Space Interconnection Techniques," *Photonics in switching Volume II*, Academic Press, Sandiego, p.169-1255, 1993.

- [7] R. A. Nordin et al., "A System Perspective on Digital Interconnection Technology," J. Lightwave Technology, Vol. 10, p. 811-827, 1992.

- [8] F.A.P. Tooley,"Challenges in Optically Interconnecting Electronics", J.S.T.Q.E., Vol. 2, p. 3-13, 1996.

- [9] B. Robertson, "Design of an optical interconnect for photonic backplane application", *Applied Optic*, V. 37, p. 2974-2984, 1998.

- [10] F.B. McCormick, et al., "Design and Tolerancing Comparisons for s-seed-based free-space switching fabrics," *Optical Engineering*, Vol. 31, p. 2697-2711, 1992.

- [11] Y.S. Liu et al., "Design, implementation and characterization of a hybrid optical interconnect for a four-stage free-space optical backplane demonstrator", Applied Optics, Vol. 37, pp.2895-2914, 1998.

- [12] M. Yamaguchi et al., "Digital Free-Space Photonics Switching Structure Using Exciton Absorption Reflection Switch (EARS) Arrays," *Photonics technology letters*, Vol. 5, p.1203-1206, 1993.

- [13] K. Hirabayashi, et al., "Optical Beam Direction Compensation System for Boardto-Board Free Space Optical Interconnection in High-Capacity ATM Switch," J. Lightwave technology, Vol. 13, p.874-882, 1997.

- [14] K.S. Tewksbury, et al., "Cointegration of Optoelectronics and submicron CMOS," International Conference on Wafer Scale Integration, p.358-367, 1993.

- [15] K. Hirabayashi, et al., "Free-Space optical interconnections with liquid-crystal microprism array," *Applied Optics*, Vol. 34, p.2571-2580, 1995.

- [16] H. Karstensen, L. Melchior, V. Plickert, et. al., "Parallel Optical Link (PAROLI) for Multichannel Gigabit Rate Interconnections", 1998 Electronics Components and technology conference, p.747-754, 1998.

- [17] J. D. Crow, J. Choi, M. S. Cohen, G. Johnson, et al., "The Jitney Parallel Optical Interconnect," 1996 Electronics Components and technology conference, p.292-300, 1996.

- [18] L. J. Northon, F. Carney, N. Choi, C. K. Y. Chun, R. K. Denton Jr., D. Diaz, J. Knapp, M. Meyering, C. Ngo, S. Planer, G. Raskin, E. Reyes, J. Sauvageau, D. B. Schwartz, S. G. Shook, J. Yoder, Y. Wen, "OPTOBUS<sup>™</sup> I: A production Parallel Fiber Optical Interconnect," *1997 Electronics Components and technology conference*, p.204-209, 1997.

- [19] H. Kosaka, "Smart Integration and Packaging of 2-D VCSEL's for High-speed Parallel Links", J. S.T.Q.E., Vol. 5, p.184-192, 1999.

- [20] Correspondence with Infineon Technologies about the PAROLI 2.5Gb/s per channel.

- [21] H. Kosaka, M. Kajita, Y. Li,Y. Sugimoto, "A Two-Dimensional Optical Parallel Transmission Using a Vertical-cavity Surface-Emitting Laser Module and an Image Fiber," Photonics Technology Letters, Vol. 9, p. 253-255, 1997.

- [22] Y. Li, T. Wang S. Kawai, "Distributed crossbar interconnect with vertical-cavity surface-emitting laser multiplexing and fiber image guides," *Applied Optic*, Vol. 37 p. 254-263, 1998.

- [23] T. Maj, A.G. Kirk, D.V. Plant, J.F. Ahadian, C.G. Fonstad, K.L. Lear, K. Tatah, M.S. Robinson, J.A. Trezza, "Interconnection of a Two-Dimensional Array of Vertical-Cavity Surface-Emitting Lasers to a Receiver Array by Means of a Fiber Image Guide." Applied Optics, vol.39, p.683-910, 2000

# Chapter 2- The Adaptive Redundant Optical Interconnection

#### 2.1. Introduction

One of the most important challenges preventing the acceptance of free space optics is the skepticism concerning the issue of alignment [1]. In order to have a reliable free space optical interconnect, the emitters, detectors and optical elements have to be aligned to each other within very tight tolerances ( $10\mu$ m). The ability of creating such an alignment will determine the success of the interconnection. Failure to meet the tolerance budget normally impact the system performance. Poor bit error performance (lower than BER than  $10^{-9}$ ) can be a sign of misalignment. An optical data link should be reliable, low cost, eye safe, easy to install, easy to maintain and compatible to existing systems.

The ability with which one can control the alignment will directly affect the power budget of the optical interconnection. In addition, if a parallel interconnection is to be implemented, optical crosstalk could occurs between optical links adding noise to the transmission system. Both problems would have a non-desirable effect on the bit error rate (BER) of the interconnection. Considering that the bit error rate for today's datacom systems easily attain 10<sup>-15</sup> errors per transmitted bit [2], we do not have to stress how much the quality of alignment is important in a free space optical interconnection. The quality of this alignment does not only have to be achieved on the first time alignment of a system, but also has to be maintained during its lifetime despite vibration, shock, and environmental fluctuation.

The ease of the alignment is another factor that must be addressed. One cannot always have a team of highly trained researchers on hand to build and fix each systems one a time. The systems have to be simple to align to reduce installation and maintenance costs.

The goal of this chapter is to first review the techniques used in order to make free space optical interconnections tolerant to optical misalignment. The second part of the chapter will present a new free space optical interconnection architecture that proposes to make the alignment digitally adaptive using redundant optical links.

#### 2.2. Static optical interconnection

One possible solution to produce an aligned system is to have a rigid mechanical structure that will not allow the beams to drift out of alignment. Most interconnect systems demonstrated to date uses this kind of approach [3-10]. Boisset et al. used precision machine base-plates in order to keep the optical elements in place. Some of the elements are mounted in precision-machined cells and every cell are deposited on precision-machined slots. Typically, the alignment precision required for rigid systems are on the order of 10um. This kind of system is usually difficult to align and will be very susceptible to environment changes and shock. Also, the alignment mechanisms are not simple and require highly trained personnel in order to achieve the predicted performance.

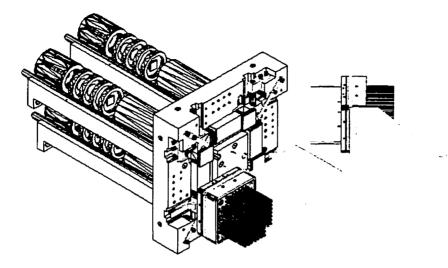

One solution to these problems is to make the optical system tolerant to misalignment at the design level. Robertson outlined this approach while describing the optical design of a free space optical interconnect [3]. However, even when ingenuity is used in order to increase the tolerances, the task of achieving the required alignments still poses many difficulties. Special alignment methods have to be put in place in order to make the system alignment realizable [4]. In order to realize the system described by Robertson; the optical system components have to be grouped into modules. Every module has to be assembled on an individual basis in specialized setups using interferometric methods [7]. The modularization process permits relaxed tolerances on the opto-mechanics and makes the assembly a more trivial task. The favored assembly method is to provide kinematic interfaces to every module. The complexity and the difficulty of implementation of such a system can easily be appreciated just by looking at Figure 2.1.

Figure 2.1 Final implementation for the interconnection presented in reference [3]

Even when using state of the art techniques in order to realize the alignment, rigid interconnection poses many problems to designers. The rigid interconnection technique becomes harder to implement as distances between stages increase. The manufacturing yield for the realization of mass produced systems might be problematic. Every part has to be perfect; any error in manufacturing makes the initial alignment many times harder to realize [4]. Rigid interconnection systems count on mechanical rigidity in order to provide reliable systems over time. Those systems have to be directed toward short distance interconnections like board-to-board or chip-to-chip applications. This is because alignment is easier to maintain on smaller distances since for the same mechanical defect the displacement of optical parts will be smaller on smaller distances.

Other types of static interconnections use a spread beam in order to create an alignment tolerance. By "spraying" the light from the transmitter to the receiver, they avoid complex imaging systems. This technique however wastes a lot of power which lead

to low receiver power limiting the possible speed. In the same way, the angle of divergence of the beam and the length of the link will limit the interconnection density. An example of this type of system is also the only product deployment of short-length FSOI to date. The diffuse link of the IRDA (Infra-red Data Association) permits links up to 4Mb/s. Another example of that type of interconnection using the techniques of spread beam is the interconnection presented by Goodwill [11]. This free space interconnection has a tolerance of  $\pm 1$ mm and  $\pm 1^{\circ}$ . However, this technique is not extendable to dense arrays and does not possess the main advantages claimed by FSOI: high speeds and extremely high densities.

#### 2.3. Dynamic optical interconnection

Another solution to the alignment problem is to have the system adapt the alignment to changes in the environment by using active steering elements [12-15]. Using this technique, the optical channels are positioned in alignment using optical MEMS (Micro Electro Mechanical Systems), liquid–crystals, adjustable liquid prisms, or any other beam steering devices. Normally, this type of interconnection will use a reference beam in parallel with the beam array of the optical link. The position of the reference beam is read by an xy-positioning sensor, and the output of the sensor is fed back to the controller of the optical beam deflector in order to optimize beam alignment. Results obtained by Hirabyashi [14] using an active realignment system look very promising. The system can correct for alignment error is maintained to  $\pm 10\mu$ m. The alignment error is maintained minimal despite multiple card insertions and extractions, or shocks on the order of hundreds of G. This demonstration is the proof that misalignment tolerance can be increased by an active control system.

#### 2.4. Redundant interconnection

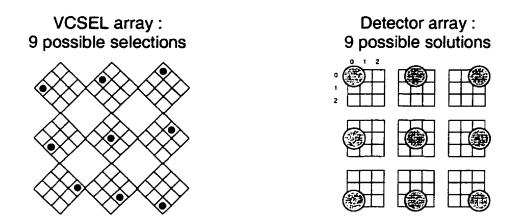

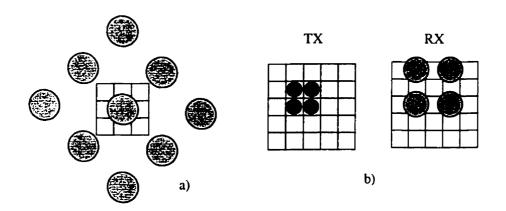

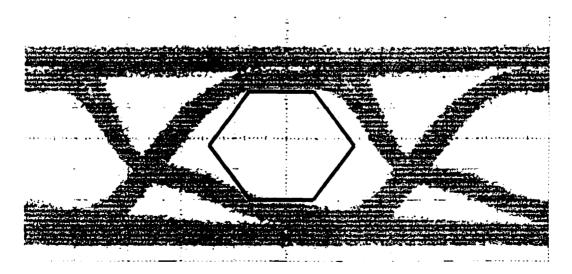

Dynamic alignment free space optical interconnections are attractive because of their robustness. However, reliability is still of concern. Moving parts, like the one used in dynamic alignment interconnections, are usually many times less reliable than today's electronics. In order to gain acceptance within electronic systems, those devices will have to prove their reliability over time and environmental conditions. A solution exists to make the alignment dynamic without having to use active steering elements. The solution is to use redundant detectors and emitters. The concept of redundancy has been introduced only recently by various authors [1, 16-17] as a possible solution for making free space interconnections a viable solution to the alignment problem. However, no system and chip set has ever been developed in order to explore the possibility offered by the concept. The idea is quite simple: by adding extra detector and transmitters, one can increase the number of degrees of liberty the emitter and detector can have in order to be aligned. By routing the transmitted signals in an ordered fashion through the aligned subset, one can ensure a greater tolerance to angular and lateral misalignment. As an example, in the system presented by Plant [17], only a single active transmission channel was available at all time; however, the detectors and emitters were using 3x3 arrays of laser and detectors. Figure 2.2 depicts the channel configuration. This arrangement gave 81 possible combinations of emitterdetector pairs in order to achieve a working communication channel. The alignment between the boards was as large as  $\pm 1^{\circ}$  and  $\pm 1$ mm across the combinations. If perfect alignment were to be realized, both the center elements of the emitter and detector arrays would be selected in order to produce the communication channel. The two arrays are allowed to drift out of alignment as long as one emitter-detector pair is available.

Figure 2.2 Emitter, detector redundancy concept

It is important to note that in the prefect alignment condition, the peripheral emitters and detectors in the array are not in alignment; the light from the edge of the emitter array falls outside the detector plane. In order to make the system as tolerant as possible, the optical system that is built in between the opto-electronic arrays is designed in such a way that the VCSEL light widely overfills the detector array area. This allows the detector switching to provide a fine alignment adjustment as the emitter switch corrects for larger displacement. The situation is depicted in Figure 2.3. The VCSEL array was at a 45° angle with respect to the detector array in the system. The available detector arrays and VCSEL arrays both had the same device pitch. By using an angled configuration, the horizontal pitch between the VCSEL and the detector was made different, which stabilized the channel coupling throughout displacement.

Figure 2.3 a) Image of the array of light from the VCSEL array with respect to the detector array when in perfect alignment. b) Example of a 2x2 interconnect.

Redundant interconnections were especially developed to increase the misalignment tolerances of dense optical interconnections. Scalability of redundant interconnection is therefore a subject that should be investigated. Figure 2.3 b) shows a method to scale to a redundant interconnection for a 2x2 interconnection. As can be seen in the figure, the optical beams do not fall on adjacent detectors. This architecture is necessary in order to take into account for crosstalk; enough space has to be maintained in between the optical beams in order to ensure that two optical channels will not fall on the same detector. The additional detectors ensure continuity in the signal coupling as the emitters and detectors fall out of alignment. Following this architecture, the number of extra emitter and detector that are needed for redundancy decrease as the array density increase. The number of emitter and detector needed for redundancy can easily be calculated using simple arithmetic.

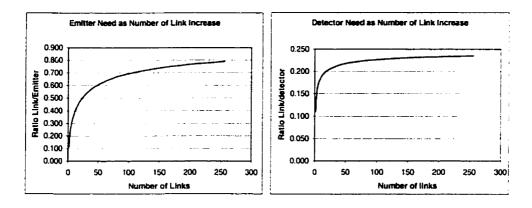

Figure 2.4 Emitter and detector need, as the interconnection is scaled

Figure 2.4 shows how the presented architecture scales as the number of links is increased. The link-to-emitter ratio needed for redundancy tends to 1 as the link density is increased. The link-to-detector ratio needed for redundancy tends to 0.25 as the link density is increased because of the extra detectors needed to minimize cross-talk. As the density of optical links is increased, the cost per link should decrease. This is because less detectors and emitters are needed in order to maintain the redundancy. In addition, the cost for adding intelligence to align the matrix is a fixed cost, therefore a lower cost as the density is increased.

Redundant interconnections provide a tradeoff between the static interconnections and the dynamic interconnections. By using only static electronic elements, they provide single elements reliability similar to the one provided by static interconnects. The channel redundancy and control systems allow for relaxed tolerances, making the alignment of the interconnect more easy to realize. Density is also preserved as dense interconnection can be achieved when using very large arrays. While providing a way to adjust the alignment dynamically, the redundant approach allows for the creation of a generic component that can be included in any system just like chips are included on a PCB board. By having very large misalignment tolerances, the redundant interconnection does not require a special rigid mechanical system to be developed in order to maintain the boards in a reasonable alignment. The standard methods used to mount boards in systems can be used. This removes many or all of the problems that an engineer would face when including a free space interconnection in their system. The modules are self-contained and only their position has to be planned such as holes are made in the electronic enclosure when designing a PCB. In conclusion, adaptive redundant FSOI are easy to use dense, rapid, and misalignment friendly, making them one of the ideal FSOI one could design for use in an industrial environment.

#### 2.5. System Implementation

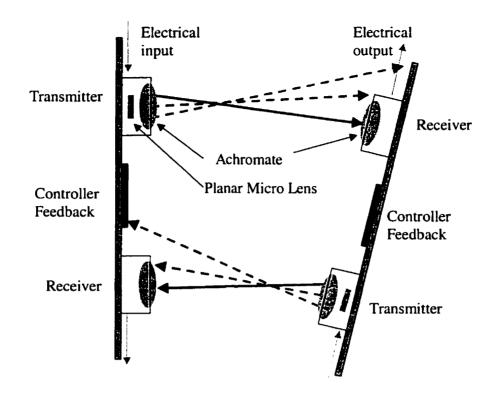

This thesis is aimed at describing the design and test of an optical transmitter that was developed especially for a redundant FSOI. In this section, the full interconnection system will be introduced to give the context in which the transmitter is to be used. The system is designed to interconnect two boards with two bi-directional optical channels operating at 1.25Gb/s each over a distance of 5cm to 22 cm [17]. The two boards can have a lateral misalignment tolerance of  $\pm 1$  mm and an angular tolerance of  $\pm 1^{\circ}$ . The tolerance provided by the redundancy is loose enough to enable the use of the interconnection with standard board insertion tolerances normally available in between board in a rack system or between stackable modules. The system developed for this thesis employed a 3 X 3 array of VCSELs and 3 X 3 array of photo diodes for each channel. The selection of the transmitter-receiver pair in the array that gives the optimum performance is determined by a feed back control mechanism. In this implementation of the system, the control information is transmitted optically such that the system can operate with no electrical connections (except for the power connection). For the system development, a transmitter, an optical system, a receiver, and an alignment controller were developed. A graphical representation of the FSOI system is illustrated in Figure 2.5.

Figure 2.5 Bi-directional redundant interconnect

#### 2.5.1. Transmitter

The transmitter Module consists of a 1 x 9 VCSEL driver, a 3x3 960nm VCSEL array, a ceramic carrier, a mount for a micro-lens array, and a bulk lens. The transmitter chip was designed using the NT25 technology. The transmitter takes two 1.25Gb/s PECL signals from two different sources and distributes them to nine VCSELs. This thesis gives a complete description of the transmitter.

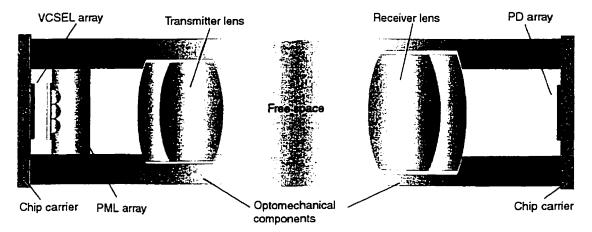

#### 2.5.2. Optical system

The design challenge addressed in developing the optical system for this free space optical interconnect based on redundancy was to provide the lateral misalignment of +/-1 mm and tilt tolerance of  $+/-1^{\circ}$  over a distance of 5 to 22 cm. The optical system is shown in Figure 2.6. It consists of a planar micro-lens array (PML) and a 12.77mm

focal length achromatic lens with 6.25mm diameter on the transmitter. A 250µm glass spacer was inserted between the VCSELs and the PML in order to maintain the optical distance between these two components while increasing the physical distance. This allowed for the large PML substrate to be fixed at a slightly larger distance from the VCSEL array allocating more space for the electronic packaging, wirebonds, and air flow. On the receiver side, only one lens is used: a 14.22mm focal length achromatic lens with a 13.00mm diameter.

Figure 2.6 Optical system[19]

The optical beams from the VCSEL array are collimated by the PML array and then distributed angularly by the transmitter bulk lens. The beams then propagate in free space for a distance of 5cm to 21.5cm depending on the distance between the PCBs. The beams are then collected by the receiver lens and "focused" onto the detector array. Note that the spots do not have to be exactly focused on the detectors; only the spot size at the detector is important in this optical system. The distance between the different components has been optimized through mathematical simulations in order to provide the best coupling between the emitters (VCSEL) and the detectors (PD) across misalignment conditions, emitter-detector combinations, and distance between the modules.

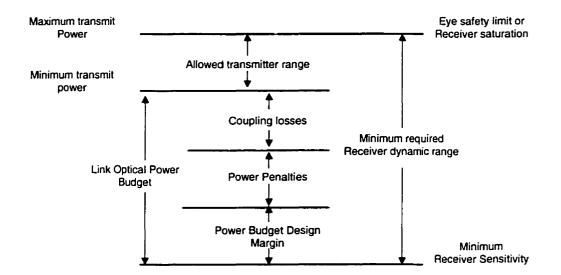

Figure 2.7 Power budget for an optical interconnection

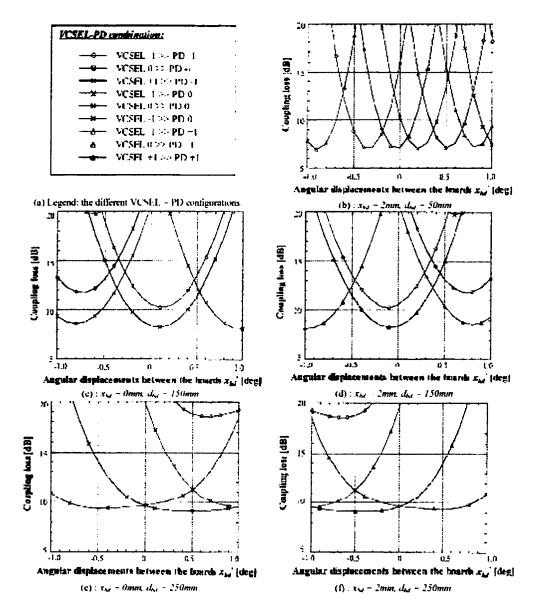

The alignment tolerance for the optical system is tightly linked to the power budget for the optical link. Figure 2.7 shows a picture representing the power budget for an optical interconnection. The minimum receiver sensitivity for the interconnection was established to be -23dBm. The minimum transmitted power is -6dBm. This allows a power budget of 17dB. Unlike fiber interconnections, the major part of the power budget is consumed in the coupling between the transmitter and the receiver. The coupling was optimized such that it would be minimal over the different VCSEL/PD combinations. Figure 2.8 shows that the calculated coupling loss for the interconnection is never over 14dB across the interconnection alignment tolerance range VCSEL/PD combination. The power penalties such as the inter-symbol interference, the relative intensity noise, and jitter penalty, which account for the signal degradation over the interconnection, are evaluated to less than 1dB due to the very short distance crossed by the interconnect. The design margin for the interconnection is 2dB guarantying valid system performance over the target tolerance.

Figure 2.8 Coupling behavior of the optical system. The distance between the boards  $(d_{bd})$  and the lateral misalignment  $(x_{bd})$  are given for every plot. [27] (Calculated using Gaussian beam formalism using Mathematica<sup>Im</sup>)

#### 2.5.3. Receiver

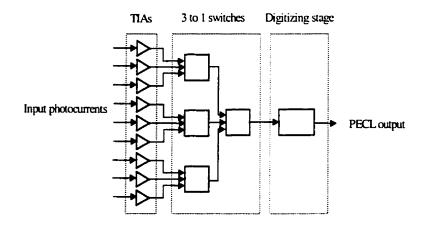

The receiver module consists of a 9x1 receiver array, a 3x3 photo detector array, a ceramic carrier, and an optomechanical mount for a bulk lens. The module receives the optical data at 960nm. The photocurrents from the photodiodes are all preamplified to a suitable voltage swing using 9 transimpedance amplifier single-ended gain stages.

From these nine signals, one is selected through two stages of 3-to-1 analog switches. The signal is then converted in a differential PECL compatible format through a last stage of amplification. The receiver block diagram is shown in Figure 2.9. A more detailed description of the receiver along with test results was described by the receiver designer Mony [18].

Figure 2.9 Receiver block diagram [18]

#### 2.5.4. Optical Feedback (Hunt mechanism)

Optical feedback is an integral part of the redundant adaptive interconnection. It is possible to determine which detector receives the most light using a simple algorithm for which all decision and control mechanisms reside only on the receiver side. However, knowing which set of transmitters is aligned to the detectors is more difficult. Controlling the transmitter plane requires communication between the transmitter and the receiver in order to determine which combination of emitters and detectors will give the optimum performance. The feedback task has to be achieved by a communication channel parallel to the main transmission links.

This transmission channel can take different shapes: a very tolerant infrared link (IrDA like link), twisted pair, or it could also use the main communication channel. The system can use the high-speed data channel in order to communicate the feedback information given that no data is transmitted at the same time. Even if the interconnect

is not yet aligned, the signals can pass through by transmitting on all possible communication channels. This is done by modulating all VCSELs at the same time. In this case, the links will have to be operated at lower speeds in order to compensate for the power surge created by transmitting on all the lasers at the same time.

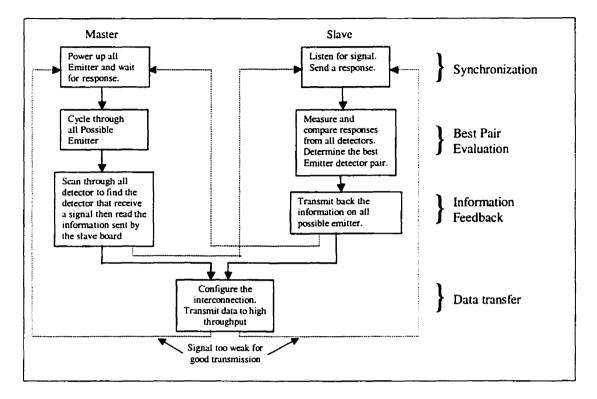

Figure 2.10 shows a simplified version of the algorithm used in the implementation of the interconnect system. The boards are first defined as master or slave by a hardware switch. This selection determines each boards state at the state of the algorighm. The first step is to synchronize the boards. To achieve the synchronization, the master board powers up all the VCSELs of the communication channel. As soon as the slave board detects the signal transmitted by the master board, it also powers up all available VCSELs. The master board detects the signal and as soon as the slave stops transmitting, both modules step into the second phase of the hunt algorithm. This movement will happen for both boards approximately at the same time; hence, the two boards are synchronized. Note here that the alignment will happen only if it is possible to align the two boards. Also, the synchronization tolerance will depend on the logic response time which is designed to be order of magnitudes faster than the circuit clock to make the synchronization inconsequential. If one link is too misaligned to produce at least one good communication channel, the algorithm will stop here since at least one board will never receive acknowledgement of the existence of a second board.

The next step involves finding the best VCSEL-PD pair by scanning through all the VCSELs on the master board and finding the receiver channel that received the highest power. The information about which VCSEL is providing the best transmission channel is known by the receiver plane since the scan pattern of the VCSEL plane and the time at which each VCSEL is exercised during the scan is predetermined. Based on the premises that both transmitters and receivers are synchronized, the information about the time at which the good transmission link occurred and therefore which VCSEL provides the best transmission media is sent back to the master board. At the end of a cycle, both the master and slave exchange roles to find the best VCSEL-PD pairs for the other direction. Once both VCSEL-PD pair have been found, the data is

transmitted across the two channels. If one of the receivers senses the power dropping on the channel used to sample the signal, all data transmission is stopped and the alignment algorithm begins again to find the new optimum value for transmission.

Figure 2.10 Flow diagram for the alignment algorithm [17]

The ability to adapt to changes in the interconnection alignment will greatly impact the robustness of the system. In the implementation presented here, the high-speed communication has to be stopped when the interconnection senses a misalignment. This occurs to allow the hunt algorithm to run again and calculate the new position of the emitter array with respect to the detector array. The communication channels used for the feedback only exist when no data is transmitted through the interconnection. There would be some advantages in using a permanent transmission medium for the feedback. If a permanent communication channel was used, a prediction algorithm could calculate the drift direction and allow for a seamless emitter-detector transition as the drift occurs, therefore causing no data disruption. In the case where the feed back information has to travel using the same communication link, a special communication

protocol would have to be used in order to allow for the coding of the drift information on top of the data. This would demand a considerable effort by itself and was therefore left for future investigations.

#### 2.5.5. Speed and Communication protocol

The communication channel speed targeted for the system was 1.25 Gb/s. This transmission rate is the same as Gigabit Ethernet and is large enough to accommodate a fiber channel compliant signal. By choosing a transmission rate the same as an already available standard, the access to commercially available communication protocol chip sets is guaranteed. This allowed the design effort to be concentrated on the media and not to be disturbed by the development a special communication protocol. The transmission rate was also the fastest for which our research group was capable of testing.

Gigabit Ethernet protocol might not be the best solution for an adaptive free space optical interconnection. The ideal protocol would allow for channel maintaining information encoded on top of the transmitted data. As an example, the data could be framed in a special packet allowing the link status to be transmitted with the transmitted data. Other functions like error correction could be taking place with that header making the link more tolerant to loss of packets accruing from interruptions caused by channel reconfiguration. The availability of a working adaptive redundant optical interconnection will allow for the exploration of this hypothesis.

#### 2.6. Reference

- [1] F.A.P. Tooley, "Challenges in Optical Interconnecting Electronics," *IEEE JSTQE*, Vol. 2, p. 3-13, 1996.

- [2] C. DeCusatis, "Optical Data Communication: Fundamentals And Future Directions", SPIE Opt. Eng., Vol. 37, p. 3082-3099, 1998.

- [3] B. Robertson, "Design Of An Optical Interconnect For Photonic Back Plane Application", *Applied Optics*, Vol.37, p. 2974-2984, 1998.

- [4] E. Bernier et al., "Implementation of a Compact, Four Stage, Scaleable Optical Interconnect", Optic in computing 2000, Quebec City, 2000.

- [5] Personal notes from the Third phase optical interconnection project. As responsible for system opto-mechanic and alignment.

- [6] K. Ghosh, "Alignability of Optical Interconnects", *Applied Optics*, Vol.29, p.5253-5261, 1990.

- [7] Robertson et al. "In Situ Interferometric Alignment Systems For The Assembly Of Microchannel Relay Systems", Applied Optics, Vol. 36, p.9253-9260, 1998

- [8] D.V. Plant et al., "4\*4 Vertical-Cavity Surface-Emitting Laser (VCSEL) and Metal-Semiconductor-Metal (MSM) Optical Backplane Demonstrator System," *Applied Optics*, vol.35, p.6365-8, 1996.

- [9] G.C. Boisset, et al. "Optomechanics for a Four-Stage Hybrid-Self Electro-Optic-Device-Based Free-Space Optical Backplane," *Applied Optics*, Vol. 36, p.7341-7358, 1997.

- [10] J.L. Brubaker, et al. "Optomechanics for a Free Space Photonic Switching: the Components," SPIE optomechanics and dimensional Stability, Vol. 1533, p.88-90, 1991.

- [11] D. J. Goodwill, et al., "Free Space Optical Interconnect at 1.25Gb/S/Channel Using Adaptive Alignment", OFC/IOOC '99. Technical Digest, p. 259 –261, 1999.

- [12] M. Yamaguchi et al., "High-Density Digital Free-Space Photonic-Switching Fabrics Using Exciton Absorption Reflection-Switch (EARS) Arrays and Microbeam Optical Interconnections," *IEEE JSTQE*, Vol. 2, p. 47-54, 1996.

- [13] G.C. Boisset, Robertson B., Hinton H.S., "Design and Construction of an Active Alignment Demonstrator for a Free-Space Optical Interconnect," *IEEE Photon. Technol. Let.*, Vol. 7, p. 676-678, 1995.

- [14] K. Hirabyashi, T. Yamamoto, S. Hino, Y. Kohama, K. Tateno, "Optical Beam Direction Compensation System for Board-to-Board Free Space Optical Interconnection in High-Capacity ATM Switch", J. Lightwave Technology, Vol.15, p.874-882, 1997.

- [15] K. Hirabayashi, et al., "Board-To-Board Free-Space Optical Interconnections Passing Through Board for Bookshelf-Assembled Terabit-Per-Second-Class ATM Switch," *Applied Optics*, Vol.37, p.2985-2995, 1998.

- [16] K.S. Tewksbury, et al., "Cointegration of Optoelectronics and Submicron CMOS," International Conference on Wafer Scale Integration, p.358-367, 1993.

- [17] D.V. Plant et al., "A 5 Gb/S, 2 Channel Bi-Directional Adaptive Redundant FSOI Demonstrator System," *Proceeding of Optic in Computing*, 2000.

- [18] M. Mony et al., "1Gb/S, 9'1 Optical Receiver Array, For An Adaptive Redundant Interconnect System, Using NT25", *Proceedings of Optics in Computing*, 2000.

- [19] E. Bisaillon et al, "Optical Link for an Adaptive Redundant Free-Space Interconnect", *Proceedings of Optics in Computing*, 2000.

- [20] Meeting notes from Tsuyoshi Yamamoto.

# Chapter 3- Single-mode VCSEL for FSOI

# 3.1. Introduction

Candidate transmitter technologies for free space optical interconnections have included both emitters and modulators: LEDs, PLZT modulators, VCSELs and electroabsorption (EA) modulators. Although many technologies are possible candidates to generate or modulate light in optical interconnections, not many have all the necessary qualities. The cutoff frequency of LED is much too low to be generating Gb/s data streams. Modulators require an external optical power supply which complicates alignment to the point where systems become very difficult to align. Arrayed single-mode high-speed VCSELs are a prerequisite for dependable, easy to align FSOI. VCSELs have some exceptional electrical and optical properties. As a result, they are quickly achieving market acceptance.

Some of the most attractive aspects of VCSEL versus edge emitter lasers lie in the elimination of the labor intensive fabrication steps such as wafer lapping, cleaving, dicing, and facet coating. The possibility to fabricate and test lasers on a wafer scale and perform non-intrusive testing is a differentiating factor of VCSELs over edge emitters. In addition, the possibility of making two-dimensional (2D) arrays from very small lasers makes VCSEL very attractive [1]. Optical interconnections, optical communication, optical recording, optical signal processing and sensor technology are only a small subset of all applications made possible by VCSELs.

This chapter will first give an overview of VCSEL structures and properties. Then, the VCSELs used for the redundant adaptive free space optical interconnection will be presented. Finally, the results from VCSEL evaluation will be commented.

# 3.2. VCSEL technology over view

Vertical-cavity emitting lasers were invented at the Tokyo Institute of Technology in 1978 [2] and achieved room-temperature continuous-wave operation for the first time in 1988 [3]. Since the mid 1990s, several companies have been launched in VCSEL manufacturing and many applications have penetrated the market place. The fundamental difference between VCSELs and conventional edge-emitting lasers is that the need to fabricate a facet mirror by either cleaving or dry etching is eliminated. Because of their perpendicular emission, VCSELs have several advantages over edge-emitting lasers such as low divergence, circular output beam, wafer-level device testing before packaging, and the feasibility of dense two-dimensional laser arrays. However, similar to the edge-emitting lasers, VCSELs need a mean to provide transverse confinement of photons and charge carriers within the cavity. Figure 3.1 shows schematically the primary VCSEL structures that are used to provide transverse optical and electrical confinement from which are based the VCSELs.

Modern VCSEL consist of two highly reflective DBR (distributed brag reflector) mirrors separated by an optical cavity. The DBR surrounding the optical cavity are required for the longitudinal confinement of light. The mirror reflectivity has to be greater than 99% because of the low round trip gain typically found in VCSELs. The DBR consist of alternating pairs of quarter-wavelength thick high and low refractive index layers. By spacing multiple high-to-low index interfaces at a distance  $\lambda/2$  apart, the reflectivity of each interface adds constructively to produce mirrors with a maximum reflectance greater than 99% [4]. The gain medium located between the mirrors is commonly composed of one or more very thin semiconductor layers that form quantum wells. The gain profile of the quantum well material and the cavity resonance wavelength determine the lasing wavelength of the VCSEL.

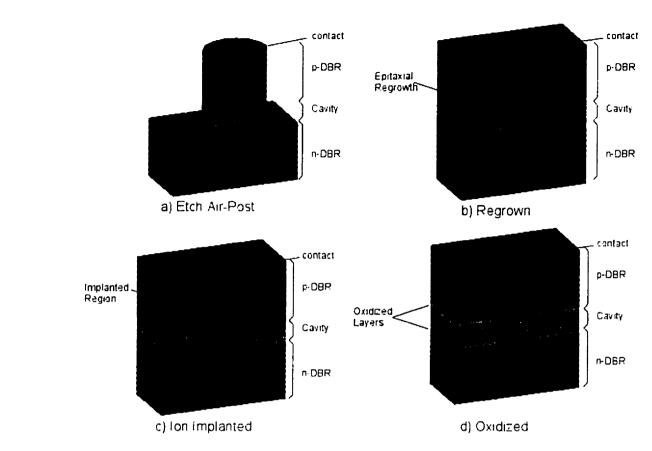

Figure 3.1 VCSEL Types (lateral confinement method)

Effectively limiting the cross-sectional areas of the electrical current and the optical mode near the gain region is important for achieving high efficiency or low threshold current. Figure 3.1 shows the four devices structure presently used for transverse electrical or optical confinement.

Shown in Figure 3.1 a), Etch Air-Post is the easiest structure elaborated for defining the lateral dimensions of the VCSEL. The pillar structures with small area and smooth vertical sidewalls are usually defined using dry etching techniques, such as chemically assisted ion beam etching or reactive ion etching [5]. Strong index and current guiding structures are present in air-post structures because of the large index at semiconductor-air interface. A disadvantage of the air-post structure is the high thermal impedance of the structure due to the absence of an effective heat sink in contact with the laser cavity. This problem accentuates the effect of temperature on the laser, which causes

pillar-etched type of VCSELs to perform poorly over ranging temperatures. Some etched air-post VCSEL implementations add a heat-spreading layer, which increases the thermal dissipation. These methods increase the maximum output power significantly [6]. In addition, the air-post VCSEL suffers from a high carrier loss due to recombination at the sidewall. The imperfections in sidewalls also increase the optical losses due to diffraction and scattering. These losses reduce the efficiency of the pillar-etched VCSEL when compared to the other types of VCSELs.

Planar VCSEL structures provide a better thermal dissipation [4]. The first planar structure is the regrown structure. Using similar a procedure as in the air post VCSEL case, the active region is first defined. The etched regions are then replaced by materials that have higher bandgap energies. The regrown regions provide both optical and electrical confinement, because of their higher bandgap and lower refractive indices. Regrowing techniques are usually very difficult to achieve and are not the preferred approach to VCSEL implementation. However, they allow for lateral current injection which greatly decreases VCSEL resistance allowing for easier laser driver design [4-5].

The two most popular planar VCSEL structures are the Ion-Implanted structure and the Oxide-Confined VCSEL. In Ion-Implanted VCSELs, ions are implanted at specific locations into the semiconductor material. This causes the implanted regions to be insulating and therefore controls the flow of the injected current [4-5]. The implantation does not provide an easy index guiding mechanism for the optical field like in the air-post, or regrown case. Instead, index guiding, to confine the optical modes is provided by the thermally induced index gradient creating a thermal lensing effect collecting the emitted light. Ion implanted VCSELs are limited to multilateral mode operation as the index guiding by thermal lensing is insufficient to allow single-mode operation. Also, the proximity to which the implanted regions can be positioned with respect to the active region is limited by the lateral scattering of the ions. These scattered ions could damage the active regions and reduce VCSEL reliability if the implantation is performed too close to the active region. Since small aperture

definition is limited, the Ion-Implanted VCSELs are unlikely to have optical characteristics superior to Etched Air-Post VCSELs. Oxide-Confined VCSELs provide index guiding and lateral electrical confinement through selective oxidation of the buried AlGaAs layer. Oxide-Confined VCSELs provide a significant improvement in laser performance. Current thresholds smaller than 150  $\mu$ A, wall plug efficiencies greater than 50%, and high-speed modulation greater than 20Ghz have been achieved by oxide-confined VCSELs [7-9].

### 3.3. VCSEL used for the FSOI system

When developing transmitter circuitry, it is imperative to know the characteristics of the VCSELs being used. The different types of VCSELs will have a range of parameters for which the driver has to be specifically developed in order to provide the best performance both electrically and optically. The VCSELs used for the transmitter implementation were provided by CSEM, a commercial corporation specialized in laser fabrication. They were specifically developed and fabricated to be used in the adaptive redundant FSOI. The capability of the VCSEL manufacturer restricted the achievable VCSEL specifications. Working from our ideal specifications, the VCSELs characteristics were provided by the manufacturer. Table 3.1 summarizes the final specifications used for the laser design and the laser driver design. Once the manufacturing process was performed on the VCSELs, their characteristics were measured to confirm the laser performances. The reader will be able to appreciate later that the VCSELs were out of specifications, probably due to a lack of experience on the part of the manufacturing company with single mode VCSEL technology. The following sections in this chapter will review the measured characteristics of the VCSELs used in the transmitter implementation. From these measurements, the design of the driver electronics and packaging had to be corrected in order to improve the performance. Chapter 5 will review some of the corrections brought to the design based on the following measurements.

| Design Parameter                          | Minimum | Typical | Maximum |

|-------------------------------------------|---------|---------|---------|

| Thershold voltage (V)                     | 2.0     | 2.1     | 2.5     |

| Threshold current (mA)                    | 3.0     | 4.0     | 6.0     |

| Resistance (ohm)                          | 83      | 200     | 250     |

| Voltage for Maximum Power output (V)      | 2.5     | 3.0     | 3.5     |

| Current for Maximum Power output (mA)     | 6.0     | 4.2     | 15.0    |

| Maximum Optical Power output (mW)         | 0.3     | 0.5     | NA      |

| Capacitance (dominated by rooting) (pf)   | -       | -       | 1.0     |

| VCSEL pitch (um)                          | -       | 250     | -       |

| Aperture size (µm)                        | 3       | -       | 4       |

| Wavelength (nm)                           | -       | 960     | -       |

| 1/e <sup>2</sup> Intensity half width (°) | _       | 15      | -       |

Table 3.1 VCSEL specifications (not actual VCSEL performance) [10]

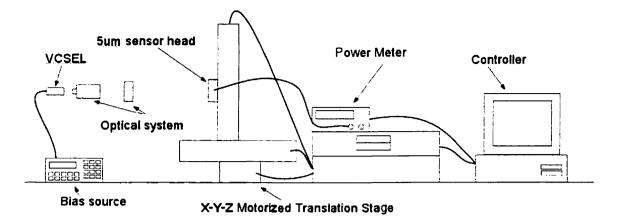

#### 3.4. Physical Characteristics

The VCSELs used for the FSOI were part of a 5x5 individually addressable array. The VCSELs in the array are of etched air-post type. Like the majority of the VCSELs to date, they are grown on an n-doped substrate with a lower n-type DBR and a p-type DBR on the top. The anode (p-contact) of every laser diode is electrically connected to the driving circuitry though the gold routing layer defined on the topside of the VCSEL array. The routing layer is designed to be connected through wire bonds onto a gold bonding pad located at the VCSEL die periphery. The current return path is provided though a broad-area ohmic contact created by a metal deposition on the backside of the wafer. This contact is designed to be fixed directly onto the bottom of the package cavity. The back contact is common to all VCSELs simplifying the routing for the array.

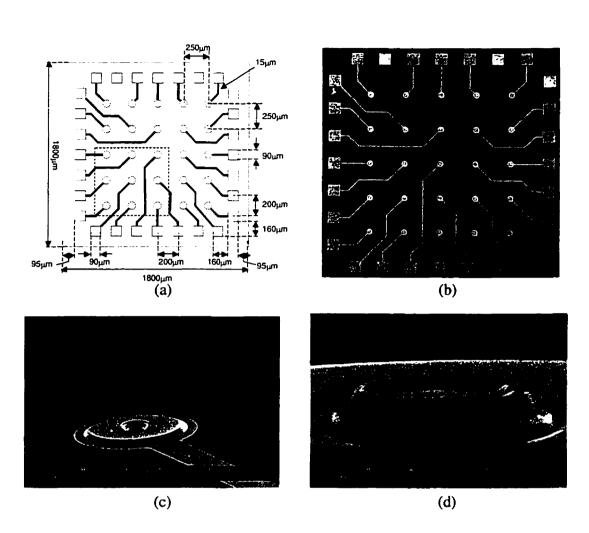

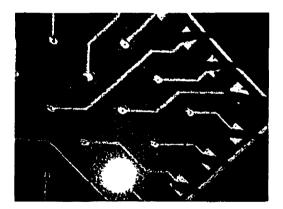

Figure 3.2 (a) shows the drawing describing the disposition of the VCSELs on the chip and the rouging layer. The resulting die shape can be seen on Figure 3.2 (b). The VCSEL die is square and measures 1800µm on the side. The VCSELs have a pitch of 250µm for which our FSOI optical system was specifically designed. The bonding pads are square, measure 90µm on a side and have a 200µm separation. These pad dimensions were made to be compatible with our wire-bonding equipment and to minimize the pad parasitic capacitance. The routing traces are 15µm in width and were disposed such as to allow for electrical access of a 3x3 sub-array from a unique die corner. The VCSEL array was designed to a 5x5 form factor in order to be able to develop a larger FSOI. The first step in the project realization was to build an FSOI using a 3x3 array and only 36% of the VCSELs on a die are to be used for the first phase of the project. Two more VCSELs out of the 3x3 sub-array are used as alignment targets for the opto-mechanic alignment; however, they are not to be used in normal FSOI operation.

Figure 3.2 (c) and (d) show a scanning electro-microscope picture of one VCSEL alone. On this picture, we can see the etched pillar and the annular ohmic contact to the top DBR VCSEL. We can also observe that the VCSEL top aperture is  $4.7\mu m$ . since the larger aperture was 117% larger than specified, the divergence angle also differs from the specification. These variations can be corrected for by changing the distance between the micro lens and the VCSEL array in the opto-mechanics.

Figure 3.2 VCSEL array used for FSOI. (a) top routing specification and laser position drawing. (b) Top view of the 5x5 individually addressable array showing metal interconnect metal and bonding pad around the periphery (c) VCSEL mesa structure and interconnect view (d) 10,000x scanning electron microscope picture of one of the pillar structure forming one VCSEL on the array.

# 3.5. Electrical characteristics

The LI and IV curves are key parameters in the characterization of VCSELs. An LI curve plots the intensity of light with respect to the injected current. From the LI curves, it is possible to find the threshold current and the slope efficiency ( $\Delta W$  of light produced/  $\Delta$  current injected). The voltage vs current curve (VI curve) helps determine

electrical characteristics of the laser diode such as the characteristic impedance. The third important curve calculates the electrical-to-optical power conversion efficiency of the diode with respect to the current.

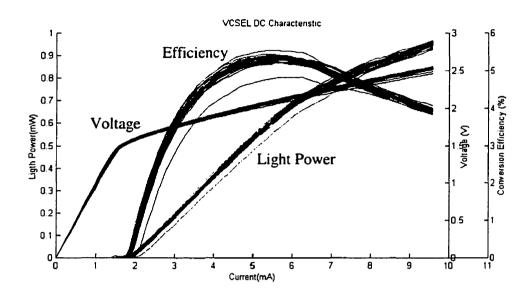

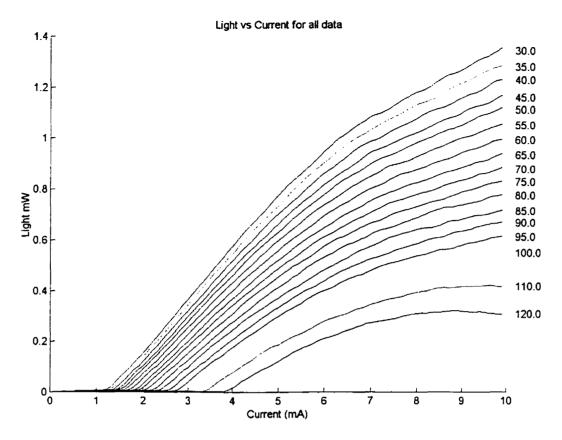

Figure 3.3 Ll, VI and conversion efficiency curves for one VCSEL array

The characteristics for all laser arrays were measured using an automated measurement setup. For every VCSEL, a probe current was injected and the voltage and light intensity were recorded. A computer program was used to compile the information for every point measured on the LIV curve for each VCSLE. Figure 3.3 shows an example for the measurements of one VCSEL array. The VCSELs have an average threshold voltage of  $1.58\pm0.07V$ . This is 0.4 Volts lower than the lowest voltage specified for the driver design. This lower voltage threshold caused some problems, as the silicon driver chip was not designed to drive such a low voltage laser. The threshold current is on average  $1.7mA\pm0.6mA$ . The current characteristics of the VCSELs are 50% lower than the specifications. The resistance featured by the VCSELs is  $130 \pm 15 \Omega$ . Lower resistance is beneficial for circuit performance as the discharge time for the circuit should be improved. Finally, the slope efficiency is measured to be  $0.170\pm0.020$  W/A. The laser featured a much larger maximum output power than anticipated although it

exhibits a maximum conversion efficiency of only 5.5%. Most of the electrical power is therefore thermally dissipated by the resistance of the DBRs.

## 3.6. Uniformity

VCSEL uniformity is an important factor to consider in designing an arrayed driver. As density of the transmitter array increases, it is essential to reduce the complexity of the driver circuitry. For instance, back facet monitoring with active adjustment of laser threshold and modulation levels have to be removed to make the driver more compact. Also, it is recommended that the laser array have a very good uniformity as this allows all drivers to use a common reference for modulation and threshold levels.

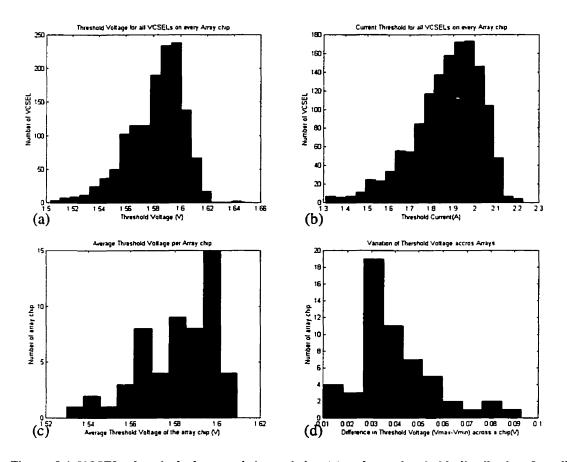

Investigation about VCSEL array uniformity was performed on the 50 arrays obtained for the realization of the projects. The voltage, current, light power curves were measured [11] for all VCSELs and the threshold current and voltage was extracted from the data. Figure 3.4 graphically shows the result from this study. For the case where the VCSEL driver development was concerned, the threshold voltage was most important since the driver developed for our FSOI was a voltage driver. The threshold voltage for the 1250 VCSELs measured had an average of 1.58V with a minimum voltage threshold of 1.5V and a maximum of 1.65V. This variation points that a driver development program has to include some way of adjusting the thresholds because of the non-negligible array-to-array variation in the threshold voltage. However, the perarray data Figure 3.4 d) shows that most of the arrays are very uniform in themselves as most of the arrays have a maximum of 0.03V variation in the threshold within an This allows all the driver levels to be set by a single reference source arrav. simplifying the driver design. The single source design would create a power nonuniformity of a maximum of  $43\mu$ W across an array (6% of the modulated power).

VCSEL uniformity is mainly based on the quality of the epitaxial growth. With today's manufacturing methods, VCSEL arrays are being produced to exhibit increasingly uniform behavior across the array allowing for simpler driver designs in the future [1,4,10].

Figure 3.4 VCSEL electrical characteristic statistics (a) voltage threshold distribution for all VCSELs (b) current threshold for all VCSELs (c) average threshold voltage per VCSEL array chip (d) difference between the maximum and minimum voltage threshold on a per-array basis

## 3.7. Modulation Characteristics

The modulation properties of the VCSEL can be predicted by the relaxation resonance. For bias currents sufficiently above threshold to ensure sufficient carrier clamping, the frequency of the resonance is given by equation 3.1 [4]. The small active volume of the VCSEL suggests that their potential modulation bandwidth might be quite high. In fact, if all the parameters in the equation were similar, aside for the volume, the VCSEL,s modulation frequency would be much higher than that of an edge-emitter. However, it is not possible to modulate a VCSEL nearly as much as an edge-emitter because of the VCSEL's high thermal impedance and series resistance. Nevertheless, the VCSELs exhibited a small-signal modulation response in excess of 4GHz even for very small currents just above threshold [8, 12].

$$f_{R} = \frac{1}{2\pi} \left[ n_{i} \frac{\Gamma v_{R}}{qV} \frac{\partial g}{\partial N} (I - I_{ih}) \right]^{\frac{1}{2}} = \frac{1}{2\pi} \left[ n_{i} \frac{\Gamma_{xy} \zeta v_{R}}{qL} \frac{\partial g}{\partial N} (J - J_{ih}) \right]^{\frac{1}{2}}$$

Equation 3.1

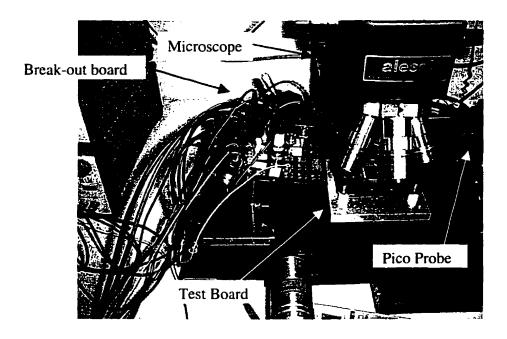

The bandwidth of the VCSEL used for the FSOI was predominantly limited by routing parasitics and not by the resonance frequency of the cavity. The capacitance of the traces was in the order of 1.0pf with an average resistance of 130ohm. This limits the current drive frequency to the GHz range. By using a voltage driven scheme, the layout parasitic effect can be damped allowing for larger VCSEL bandwidth. In this scheme, the routing capacitance is charged through overshoot in the driving current induced by the voltage source and is therefore charged faster than is a current driving technique was used.

It is important to know the modulation characteristics of the VCSEL in order to achieve the optimum transmitter performance. At high-speed, the extinction ratio, the turn-on delay, and the jitter depend on VCSEL modulation capability and on VCSEL bias.

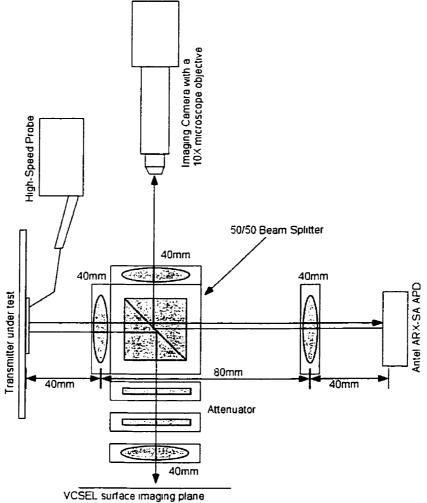

For experimental purposes, the VCSEL large signal modulation response was measured. The modulation voltage for the test was regenerated by a HP 8000 digital signal generator for which the voltage swing was set carefully so as to provide the same swing as presented by the FSOI driver circuitry. The VCSEL was directly mounted and wire-bonded to a female SMA connector to provide the best packaging performance possible. It is believed that the 3dB attenuation point for the signal was around 16GHz from the TDR measurement performed on the packaged device. The

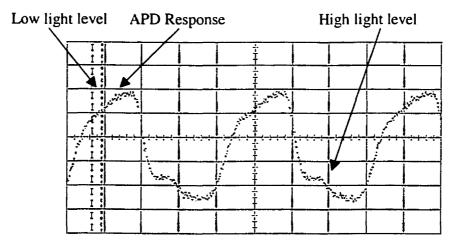

bias at the device was provided through a 15Ghz bias-tee. The VCSEL resistance was matched to the 50 $\Omega$  transmission line impedance using a 81-ohm resistance. Matching the impedance of the VCSEL is very important when driving the VCSEL through a long transmission line to reduce unwanted reflections which would add ringing on the VCSEL optical output not related to the VCSEL internal dynamics. However, when designing a driver chip to be used very close to the VCSEL, matching is not of much importance as the signal propagation time is much smaller than the rise/fall time, which makes the reflections negligible with respect to the driving signal. The optical signal was recorded by an ANTEL 2Ghz APD model ARX-SA. The resulting traces are shown in Figure 3.5. The source signal was modulated digitally to 1Gb/s. Note that the signal is inverted by the APD. The fall time is 380ps mainly due to the discontinuity in the edge caused by APD's the slow carrier response. The rising time was calculated to 590ps also due to a discontinuity in the edge. The discontinuity is most probably caused by VCSEL internal dynamics. Probing the electrical stimulus did not exhibit such discontinuities. Also, the discontinuity is dependent on the bias pointing to cavity dynamics as a probable cause. The rising edge kink is typical of single mode VCSELs or VCSELs with just a few modes. When the current attain a certain level in the cavity, it is diffused in the higher order mode even if these, mode do not laze due to high scattering. The stimulus signal was measured to have 87.4ps rise time and 127.8ps fall time at the VCSEL connection to the package.

Figure 3.5 Modulated signal from a VCSEL measured with a non-amplified APD 400ps/div.

## 3.8. Temperature Dependence on VCSEL Characteristics

One requirement for the transmitter is that it must operate in environments having a maximum of 70°C ambient temperature. This temperature is a largely accepted value in telecommunications. As the temperature increases, the laser output power decreases. The cavity resonance/laser gain alignment dominates the temperature dependence of VCSEL operation. As the temperature increases, both the cavity resonance and the laser gain shift to longer wavelengths owing to refractive index and bandgap temperature dependence. However, the laser gain shifts to a longer wavelength faster than the cavity resonance causing spectral misalignment between the cavity resonance and the peak gain, leading to degradation of the laser performance as temperature increases [4].

It is necessary to understand the effect of an increase in temperature on the VCSEL since this dictates the cooling strategy. Experimental measurements were performed to measure the temperature dependence of the L-I characteristic and the results are shown in Figure 3.6. These measurements were performed using a precision programmable current source and a precision power meter, both attached to a control computer using a GPIB interface. A temperature controller was used to set the temperature in a ceramic test package. The VCSEL was placed into the package and probed to acquire the temperature dependency curves.

The threshold current at 85°C is 2.3mA and the maximum power is 0.72mW. The VCSELs will therefore operate over the minimum acceptable power for system operation (0.5mW). However, in order to accommodate the change in the threshold without incurring a penalty in VCSEL speed, the driver threshold current must be set to around 2.4mA. This then reduces the contrast ratio at lower temperatures. Implementation of the driver should include threshold and modulation level compensation mechanisms to maintain an even output power and contrast ratio as temperature increases.

Figure 3.6 Effect of increasing the temperature on the L-I characteristics of the VCSEL. The number on the right of the graph represents the operating temperature in °C.

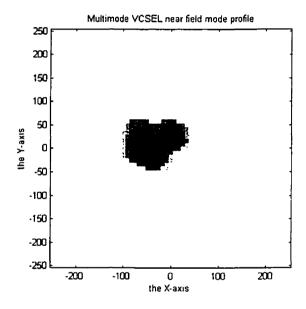

# 3.9. VCSEL Modal Characteristics

The single transverse mode VCSEL is an important component for the development of free space optical interconnections. The bit error rate (BER) can be adversely affected by the presence of multiple modes in the laser cavity. This tendency was noted in previous FSOI demonstrations [13] where strong correlation between the spatial mode opening and the mode quality was found. VCSELs that happen to be nearly single mode give markedly better error rate than lasers of more complex structures from the same manufacturing lot. Noise characteristics are also affected when using a multimode structured VCSEL. As current increases in the laser cavity, more modes can survive and therefore the power per mode gets redistributed as the current changes.

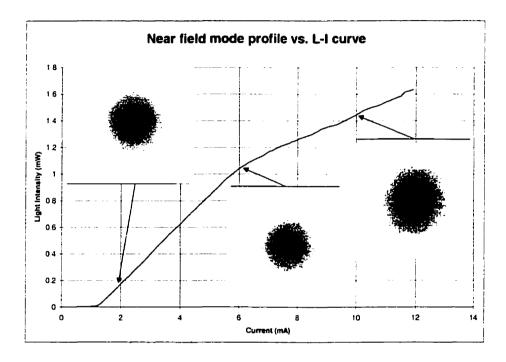

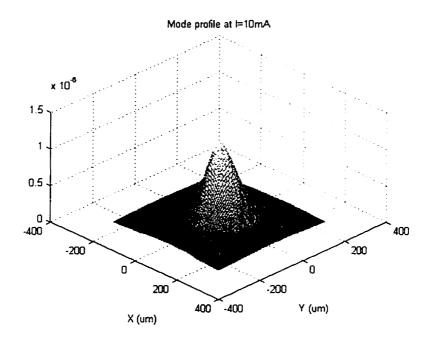

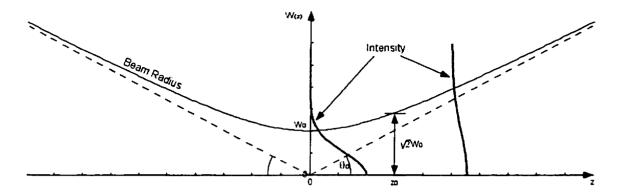

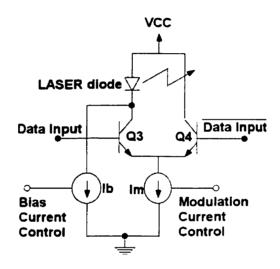

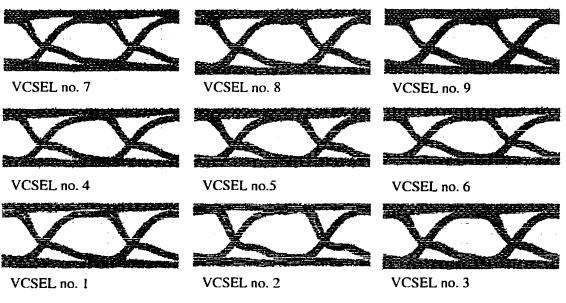

This dynamic effectively introduces switching noise in the interconnection when multimode VCSELs are used.