# Extraction of RLC Parasitics from a Flexible Electronic Hybrid Assembly

Rafid Adnan Khan

Department of Electrical and Computer Engineering

McGill University

Montreal, Canada

March 2021

#### **Abstract**

This thesis presents a technique for extracting the RLC parasitics from a Flexible Hybrid Electronics assembly. The presence of RLC parasitics is a signal integrity concern and their progression can lead to a catastrophic failure of an electronic system. Therefore, tracking the variation of RLC parasitics from a flexible hybrid electronics assembly is fundamental to assessing the success of the technology.

While the parasitics LC are extractable through one port reflection-based techniques such as time domain reflectometry; the parasitic series resistance R requires 2 port measurement such as a Kelvin test, which is extremely difficult to perform for printed conductors bonded to small surface-mount IC package devices. The proposed method exploits on-chip ESD (Electro-Static-Discharge) protection circuits in order to extract the RLC parameters of the printed conductors bonded to an IC chip through an on-board one-port access point.

The accuracy of the extracted RLC parameters with the proposed method is validated with a prototype developed on rigid FR4. Then, the proposed technique is utilized to track the variation of RLC parasitics for prototypes developed on Kapton Polyimide substrate subjected different forms of bending.

Further, the practical challenges and corresponding measures for applying the proposed technique to In-Circuit-Testing are discussed.

### Abrégé

Cette thèse présente une technique d'extraction des parasites RLC à partir d'un flexible hybride électronique assemblage. La présence de parasites RLC est un problème d'intégrité du signal et leur progression peut conduire à une défaillance catastrophique d'un système électronique. Par conséquent, le suivi de la variation des parasites RLC à partir d'un flexible hybride électronique assemblage est fondamental pour évaluer le succès de la technologie.

Alors que les parasites LC sont extractibles grâce à 1 port mesures basées sur la technique de réflexion, comme la réflectométrie du domaine du temps; le R parasite exige 2 port mesures telles que l'essai de Kelvin, qui est extrêmement difficile à exécuter pour les conducteurs imprimés collés aux petits dispositifs d'emballage IC de surface-montage. La méthode proposée exploite les circuits de protection ESD (Electro-Static-Discharge) sur puce afin d'extraire les paramètres RLC des conducteurs imprimés collés à une puce IC par un port d'accès aux points d'essai embarqués.

La précision des paramètres RLC extraits avec la méthode proposée est validée par un prototype développé sur FR4 rigide. Ensuite, la technique proposée est utilisée pour suivre la variation des parasites RLC pour les prototypes développés sur le substrat de Polyimide Kapton soumis à différentes formes de flexion.

En outre, les défis pratiques et les mesures correspondantes pour l'application de la technique proposée aux essais en circuit sont discutés.

## Acknowledgements

I would like to express my deepest gratitude to my supervisor Professor Gordon Roberts for his guidance and support. His exceptional teaching ability and contagious enthusiasm were strong driving forces behind this work.

I am immensely thankful to Natural Sciences and Engineering Research Council (NSERC) for providing financial support to this work. I am also greatly indebted to McGill University for supporting me academically and financially.

I would like to thank my fellow labmate Mohammad Muhtady Muhaisin for his contribution in developing the experimental prototypes pertaining to this work. I am grateful to my peers: Mahmood Mohammed, Ahmed Emara and Jonathan Telfort in the Integrated Microsystems Laboratory of McGill University for their teachings and companionship.

Also, I feel very fortunate to be surrounded by wonderful friends: Ferdous, Samin, Rokib and many others during my stay in Montreal.

Finally, I would like to thank my family members; specially my parents, Harunur Rashid Khan and Sabira Yesmin; my sister, Joyeeta Tahseen Khan; and my wife, Sidana Ahmed for their tireless support and encouragement.

# Contents

| 1 Introduction                                                            | 1  |

|---------------------------------------------------------------------------|----|

| 1.1 Motivation                                                            | 1  |

| 1.2 Thesis Outline                                                        | 4  |

| 1.3 Thesis Contribution                                                   | 4  |

| 2 Literature Review                                                       | 6  |

| 2.1 On Modelling and Extraction of PCB Parasitics                         | 6  |

| 2.2 On Variation of Parasitics in Flexible PCB                            | 9  |

| 2.3 Chapter Summary                                                       | 13 |

| 3 Transmission Line Modelling                                             | 14 |

| 3.1 Review on Lumped Element Model Analysis                               | 14 |

| 3.2 Approximations Utilized in this Work                                  | 20 |

| 3.3 Chapter Summary                                                       | 24 |

| 4 Proposed Measurement Methodology                                        | 25 |

| 4.1 Modelling On-chip ESD Protection Circuit                              | 25 |

| 4.2 Extracting RLC Parameters of a Transmission Line Bonded to an IC Chip | 28 |

| 4.3 Isolating the Parasitic Resistance of a Single IC Pin                 | 30 |

| 4.4 Verification of the Proposed Measurement Method                       | 32 |

| 4.5 Chapter Summary                                                       | 35 |

| 5 | In-Circuit-Test with the Proposed Method                                                | 37 |

|---|-----------------------------------------------------------------------------------------|----|

|   | 5.1 In-Circuit-Test: General Challenges and Measures                                    | 37 |

|   | 5.2 Application of the Proposed Measurement to In-Circuit-Test                          | 40 |

|   | 5.3 Chapter Summary                                                                     | 48 |

| 6 | Design of Experiments                                                                   | 50 |

|   | 6.1 Measurements Utilized to Validate the Proposed Method                               | 50 |

|   | 6.2 Experimental Setup to Validate Extracted RLC Parameters of a Transmission Line      | 54 |

|   | 6.3 Experimental Setup to Validate the Isolated Parasitic Resistance of a Single IC Pin | 55 |

|   | 6.4 Experimental Setup to Track Variation of RLC Parasitics due to Bending              | 56 |

|   | 6.5 Chapter Summary                                                                     | 59 |

| 7 | Results and Discussions                                                                 | 60 |

|   | 7.1 Validity of Extracted RLC Parameters of a Transmission line                         | 60 |

|   | 7.2 Validity of the Isolated Parasitic Resistance of a Single IC Pin                    | 65 |

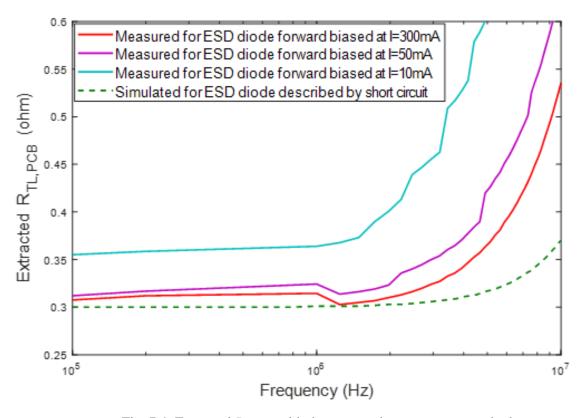

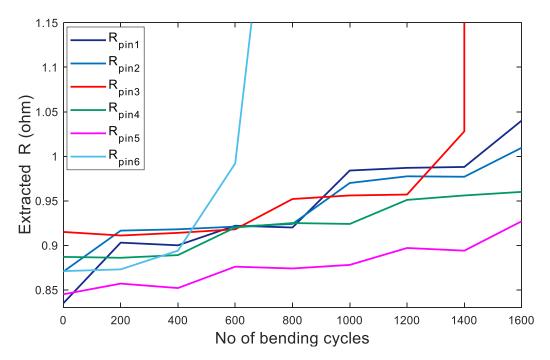

|   | 7.3 Variation of RLC Parasitics due to Bending                                          | 66 |

|   | 7.4 Chapter Summary                                                                     | 67 |

| 8 | Conclusion                                                                              | 69 |

|   | 8.1 Thesis Summary                                                                      | 69 |

|   | 8.2 Future Work                                                                         | 72 |

| R | eferences                                                                               | 73 |

# List of Figures

| Fig. 1.1: Projection of annual revenue from healthcare devices containing flexible electronics 1 |

|--------------------------------------------------------------------------------------------------|

| Fig. 1.2: Photograph of an FHE assembly                                                          |

| Fig. 1.3: Impact of flexing an FHE assembly: a) stress induced on printed conductors             |

| b) change in dielectric separation and medium between two printed conductors                     |

| Fig. 2.1: a) a PCB transmission line with two ports marked as P1 and P2 b) challenge in          |

| conducting two port measurement of the transmission line bonded to flat no lead IC chip          |

| Fig. 2.2: Relative change in resistance of a Cu trace against the number of bending cycles       |

| for different levels of bending strain                                                           |

| Fig. 2.3: Microscope image of a propagating crack on Cu trace                                    |

| Fig. 2.4: (a) Change in the resistance of Cu traces against number of bending cycles for         |

| different trace thickness b) Relative change in the resistance of Ag traces against number       |

| of bending cycles for different annealing temperature                                            |

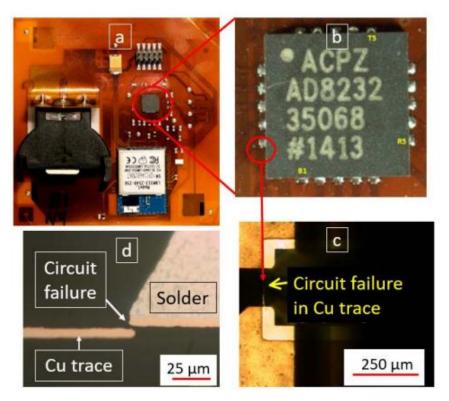

| Fig. 2.5: a) component side of a double-sided FHE assembly b) closeup view of the 20 pin         |

| Si-based rigid IC chip c) crack in Cu trace d) cross section showing failure in Cu trace         |

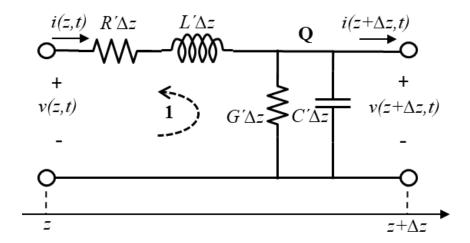

| Fig. 3.1: Lumped Element Model of transmission line of length Δz                                 |

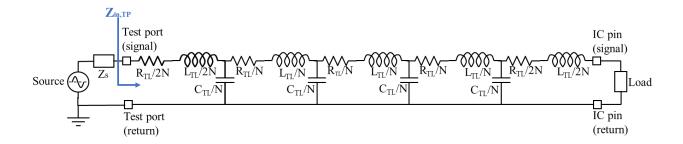

| Fig. 3.2: Equivalent RLC model with N number of T segments for a uniform transmission            |

| line on PCB (shown for N=4)                                                                      |

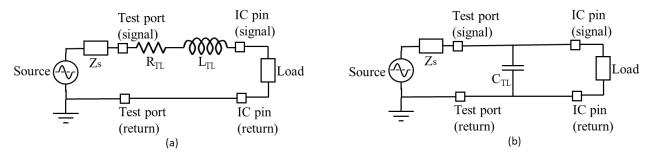

| Fig. 3.3: Low frequency lumped equivalent models for transmission line: a) series RL                                     |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| $model \ for \ small \ Z_{load} \ b) \ shunt \ C \ model \ for \ large \ Z_{load}$                                       | 21 |

| Fig. 3.4: Normalized plot of extracted $R_{TL}$ and $L_{TL}$ as function of frequency from a                             |    |

| transmission line terminated with small load impedance of $1\Omega$                                                      | 22 |

| Fig. 3.5: Transmission line lossless model at high frequency.                                                            | 23 |

| Fig. 4.1: Diode model for ESD protection circuit                                                                         | 26 |

| Fig. 4.2: I vs V plot (a) from GND (+) pin to I/O pin (-) (b) I/O pin (+) to VCC pin (-)                                 |    |

| (c) GND pin (+) to VCC pin (-) measured from Attiny85 chip                                                               | 26 |

| Fig. 4.3: Small signal representation of an ESD: (a) equivalent circuit (b) reverse Biased model c) forward biased model | 27 |

| model e/ for ward blased model                                                                                           | 21 |

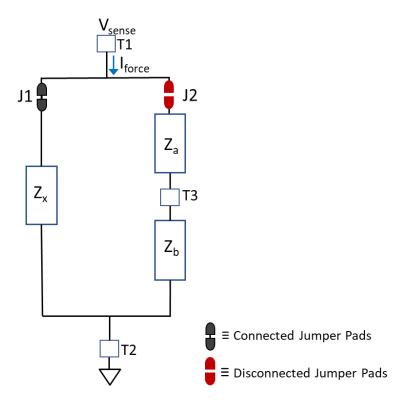

| Fig. 4.4: Measurement setup for extracting the RLC parameters of a PCB transmission  Line bonded to a commercial IC chip | 28 |

| Fig. 4.5: The equivalent circuit of DUT for: (a) forward biased ESD diode (b) reverse biased ESD diode.                  | 29 |

| Fig. 4.6: Extraction of parasitic resistance of an individual printed conductor bonded to a single IC pin                | 31 |

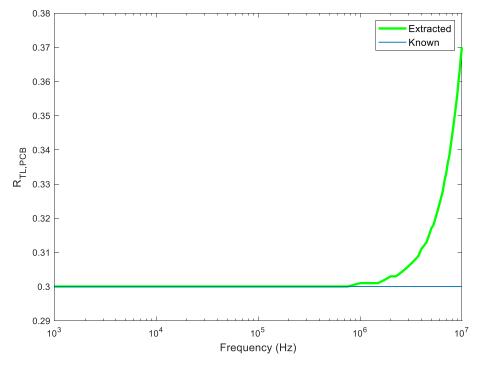

| Fig. 4.7: Extracted R <sub>TL,PCB</sub> from simulation using the proposed method compared to its known value            | 33 |

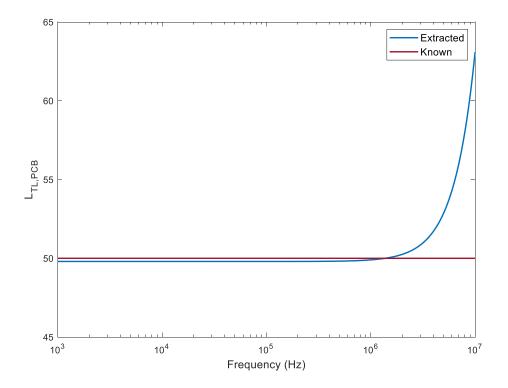

| Fig. 4.8: Extracted L <sub>TL,PCB</sub> from simulation using the proposed method compared to its known value            | 34 |

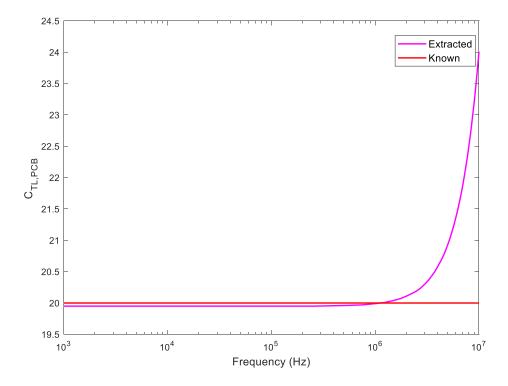

| Fig. 4.9: Extracted C <sub>TL,PCB</sub> from simulation using the proposed method compared to its known value            | 34 |

| Fig. 5.1: In-Circuit-Testing with a) Bed-of-Nail fixture and b) Flying-Probe fixture                                     | 38 |

| Fig. 5.2: Challenge in measuring impedance of an individual circuit element with                                                   |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| In-Circuit-Test.                                                                                                                   | 38  |

| Fig. 5.3: Zumper pad isolation to measure imedance of an individual circuit element with In-Circuit-Test                           | 30  |

| III-Circuit-Test                                                                                                                   | 37  |

| Fig. 5.4: Analog guarding to measure impedance of an individual circuit element with In-Circuit-Test                               | 40  |

| Fig. 5.5: Simplified schematic of an FHE multi-IC environment with associated series RL                                            |     |

| parasitics: a) without any additional test point (other than input, output and power supply access) b) with additional test points | 41  |

| Fig. 5.6: Division of measurement current in the parallel paths formed by two ESD diodes                                           | 42  |

| Fig. 5.7: Schematic of jumper pad isolation for extracting the series RL parasitics connected to IC2                               | 43  |

| Fig. 5.8: Adaptation of analog guarding in the proposed extraction method: (a) DUT with                                            |     |

| its parallel circuit path (b) implementation of analog guarding in parallel circuit path                                           |     |

| (c) simplified schematic of the implemented analog guarding                                                                        | 44  |

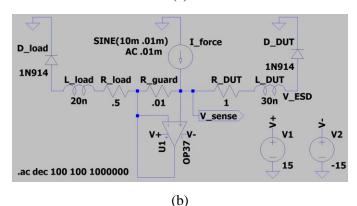

| Fig. 5.9: SPICE Implementation of analog guarding: (a) using Voltage Controlled Voltage Source (VCVS) b) using OP37 op-amp model   | 45  |

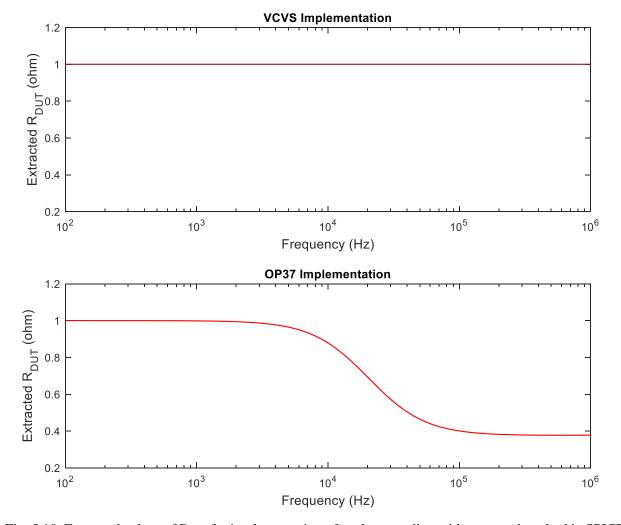

| Fig. 5.10: Extracted values of R <sub>DUT</sub> for implementation of analog guarding with proposed                                | 4 - |

| method in SPICE                                                                                                                    | 46  |

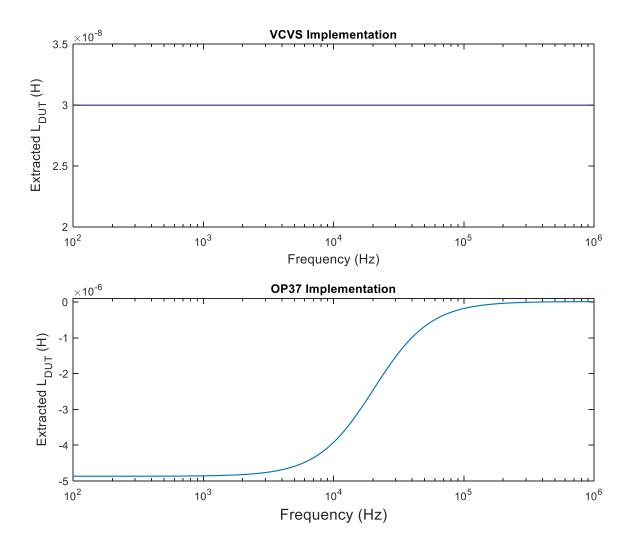

| Fig. 5.11: Extracted values of L <sub>DUT</sub> for implementation of analog guarding with proposed                                |     |

| method in SPICE                                                                                                                    | 47  |

| Fig. 6.1: Schematic for TDR measurement                                                                                            | 51  |

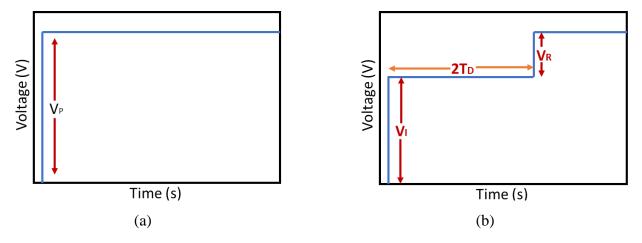

| Fig. 6.2: The voltage waveform in a TDR measurement for (a) step input $V_s(t)$ and                                                |     |

| (b) measured step response $V_m(t)$                                                                                                | 51  |

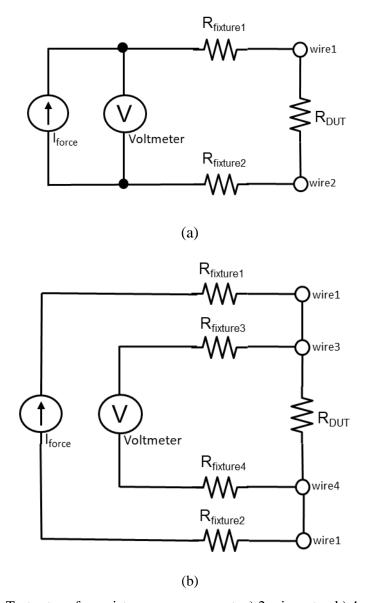

| Fig. 6.3: Test setups for resistance measurement: a) 2-wire setup b) 4-wire setup           | 53 |

|---------------------------------------------------------------------------------------------|----|

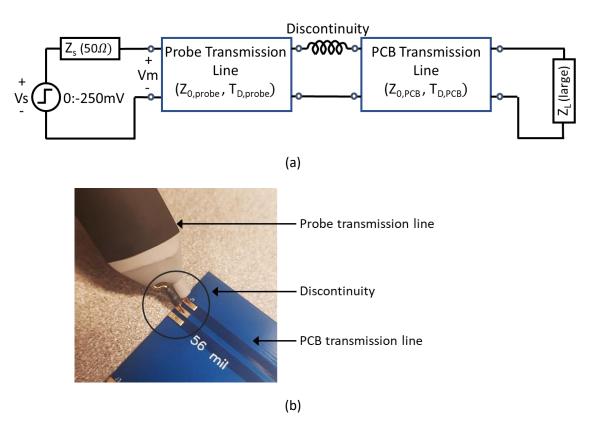

| Fig. 6.4: (a) Setup for TDR measurement b) discontinuity at the interface                   | 54 |

| Fig. 6.5: Prototype for validating isolation of parasitic resistance associated with single |    |

| IC pin: (a)electrical schematic (b) protype under Kelvin test                               | 56 |

| Fig. 6.6: Experiment to track the parasitic R variation: (a) prototype designed,            |    |

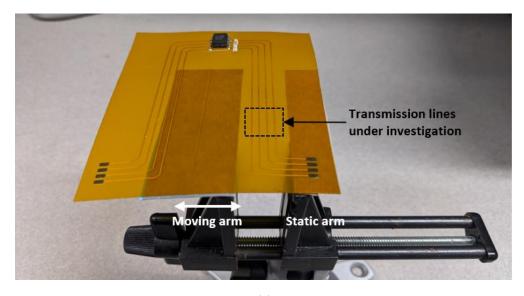

| (b) mechanical setup for bending the prototype                                              | 57 |

| Fig. 6.7: Experiment to track the parasitic LC variation: (a) prototype lying flat on the   |    |

| bending machine (b) bent prototype                                                          | 58 |

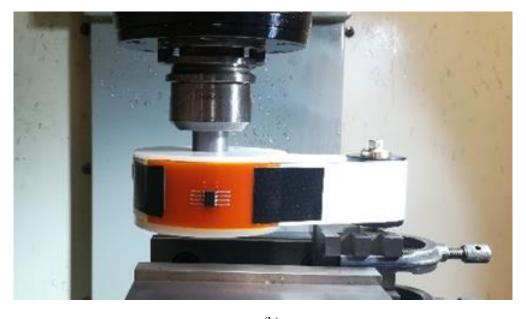

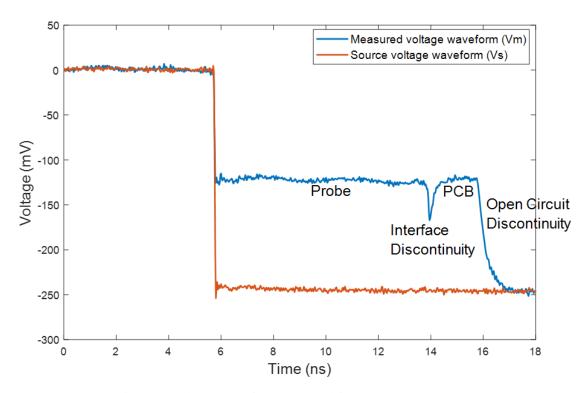

| Fig. 7.1: Voltage waveform recorded from TDR measurement                                    | 61 |

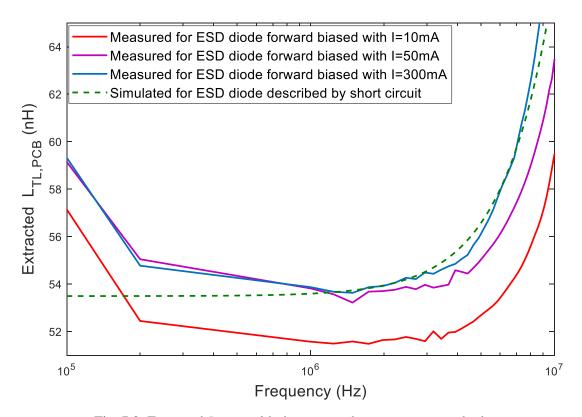

| Fig. 7.2: Extracted L <sub>TL,PCB</sub> with the proposed measurement method                | 62 |

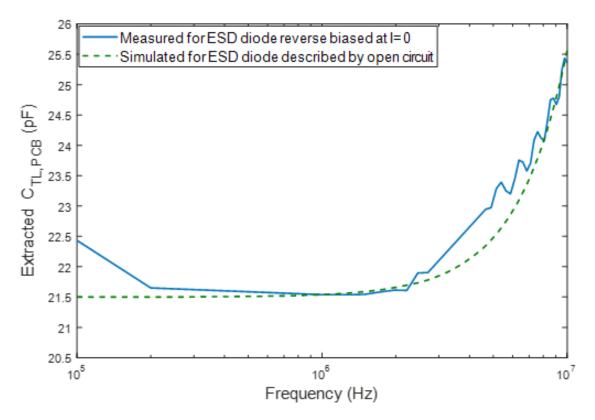

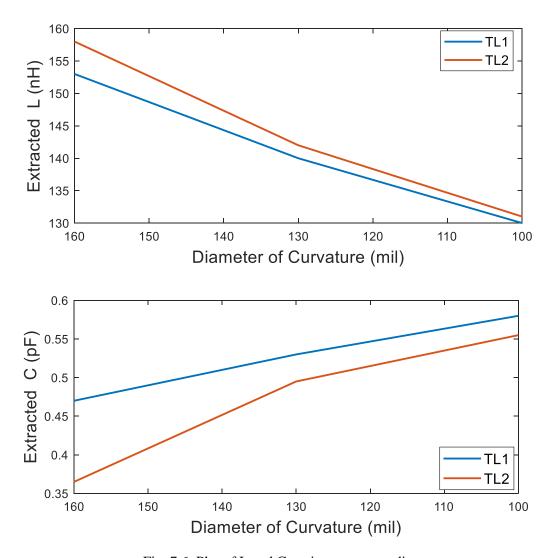

| Fig. 7.3: Extracted C <sub>TL,PCB</sub> with the proposed measurement method                | 63 |

| Fig. 7.4: Extracted R <sub>TL,PCB</sub> with the proposed measurement method                | 63 |

| Fig. 7.5: Plot of R against no of bending cycles                                            | 66 |

| Fig. 7.6: Plot of L and C against curvature diameter                                        | 67 |

# List of Tables

| Table 3.1: Summary of the transmission line descriptive parameters                                                     | 19 |

|------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1: Chosen parameter values for implementation for simulating the measurement setup of Fig. 4.4                 | 32 |

| Table 4.2: The chosen (known) and the simulated values of the resistances in the circuit of Fig. 4.6                   | 35 |

| Table 5.1: Chosen parameter values for SPICE implementation of Fig. 5.8(c)                                             | 45 |

| Table 7.1: Computed transmission line parameters from TDR measurement                                                  | 61 |

| Table 7.2: Summary of extracted RLC parameters with proposed method in contrast to other methods                       | 65 |

| Table 7.3: Comparison of the resistances of individual printed conductors extracted by proposed method and kelvin test | 65 |

# List of Acronyms

FHE Flexible Hybrid Electronics

RLC Resistance, Inductance, Capacitance

Si Silicon

Cu Copper

Ag Silver

IC Integrated Circuit

ESD Electro-Static Discharge

PCB Printed Circuit Board

AC Alternating Current

DC Direct Current

TDR Time Domain Reflectometry

ICT In-Circuit-Test

# Chapter 1

# Introduction

#### 1.1 Motivation

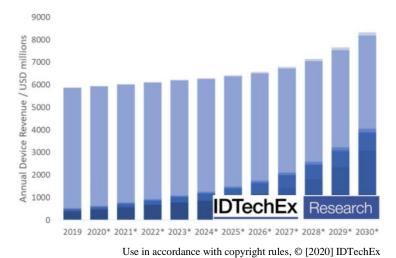

Flexible electronics features low cost of manufacturability and unconventional form factor. It is rapidly finding various main-stream applications in healthcare [1-3], agriculture [4,5], and structural health monitoring [6,7]. A research from IDTechEx projects exponential growth of the market for healthcare products containing flexible electronics and prognosticates this market to exceed 8.3 billion USD in terms of annual revenue by 2030 as depicted in Fig. 1.1 [8]. Notably, the COVID-19 pandemic necessitates rapid deployment of the healthcare services in remote form. In this regard, flexible electronics can facilitate remote health monitoring by better interfacing of the health monitoring devices with human body and enhancing long term comfort of the patients to the medical interventions [8].

Fig. 1.1: Projection of annual revenue from healthcare devices containing flexible electronics [8].

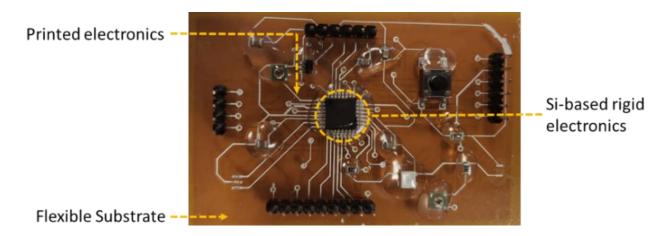

Employing technologies such as printing allows for low cost manufacturing of flexible electronic devices. Despite manifold advantages of printed electronics, it is still inferior to state-of-the-art Si-based electronics in terms of data rate, scalability, signal integrity and reliability. Flexible Hybrid Electronics (FHE) on the other hand integrates the printed electronics and Si-based rigid electronics on a flexible substrate as illustrated in Fig. 1.2. The rationale behind the integration of the two technologies is to exploit the superior performance of Si-based electronics and flexible form factor of printed electronics in a complementary manner [9].

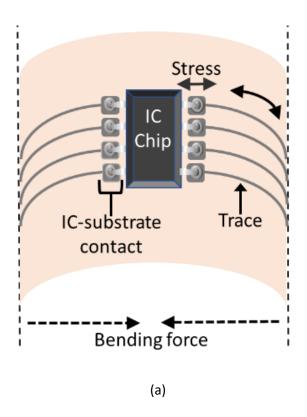

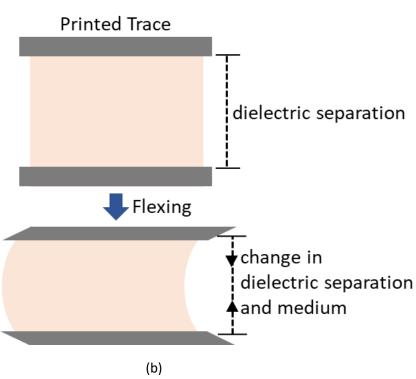

Structural conformation experienced by the printed conductors on an FHE assembly raises reliability and signal integrity concerns [10-14]. Flexing introduces stress in the printed conductors and connections as illustrated in Fig. 1.3(a). Recurrent stress causes formation and propagation of the cracks in the printed conductors [14]. The propagating cracks lead to increase in parasitic resistance R, which, in turn, culminate into ultimate loss of electrical connection [15,16]. Therefore, tracking these parasitic resistances is fundamental to the success of this technology. In addition, high frequency applications demand consideration of the parasitic inductance L and capacitance C associated with the printed conductors. These L and C on an FHE assembly can be subject to variation as well due to change in dielectric separation and medium as shown in Fig. 1.3(b).

Fig. 1.2: Photograph of an FHE assembly.

Fig. 1.3: Impact of flexing an FHE assembly: a) stress induced on printed conductors b) change in dielectric separation and medium between two printed conductors.

#### 1.2 Thesis Outline

This thesis aims to provide a means for extraction and tracking of the RLC parasitics from a flexible electronic hybrid assembly. In this work, printed conductors along with their return path is treated as transmission lines and the associated RLC parasitics are considered as the parameters of the transmission line model.

**Chapter 2** reviews the research works on the modelling and extraction of PCB parasitics and the variation of the parasitics on flexible PCB. The necessity of the proposed extraction method in contrast to the existing ones is also discussed in this chapter.

**Chapter 3** reviews the theory of transmission line modelling and delineates the approximations utilized in this work.

Next, in **Chapter 4**, a technique for extracting the RLC parameters of two printed conductors acting as a transmission line bonded to a commercial IC chip using the on-chip ESD protection circuit is proposed. Also, a way of isolating the parasitic R of an individual printed conductor bonded to a single IC pin is demonstrated. At the end of chapter, the verification of the proposed measurement method with simulations is presented.

In **Chapter 5**, the challenges and corresponding measures for applying the proposed technique to In-Circuit-Testing (test run on post assembled PCB) are discussed.

**Chapter 6** introduces the techniques based on different measurement principles which are utilized to validate the extracted parameters with the proposed method. The details of the experimental setups for validating the proposed measurement method and demonstrating its usefulness are included in this chapter.

In **Chapter 7**, the results of the experiments described in the preceding chapter are demonstrated and discussed.

Finally, in **Chapter 8**, the conclusions are drawn. Also, the scopes for future work are discussed in this chapter.

#### 1.3 Thesis Contribution

This thesis proposes a measurement technique for appropriate assessment of parasitic variation on an FHE assembly. It has following contributions to original knowledge.

#### • Transaction Submission:

"Extracting RLC Parasitics from a Flexible Electronic Hybrid Assembly Using On-Chip ESD Protection Circuits" Rafid Adnan Khan, Mohammad Muhtady Muhaisin, Gordon W. Roberts, IEEE Transactions on Circuits and Systems 1 (TCAS1), (under revision).

#### • Conference Submission:

"An In-Situ Technique for Measuring the Individual Contact Resistance Between the Pins of an IC Package and the Board of a Flexible Hybrid Electronic System" Rafid Adnan Khan, Mohammad Muhtady Muhaisin, Gordon W. Roberts, IEEE International Symposium on Circuits and Systems (ISCAS), 2020.

# Chapter 2

# Literature Review

This chapter is divided into two sections. The first section reviews the relevant research works on modelling and extraction of the PCB parasitics, and also focuses on the necessity of the proposed parasitic extraction method. The second section reports the research works on the variation of parasitics in a flexible PCB and discusses the scopes for further research works in this domain.

### 2.1 On Modelling and Extraction of PCB Parasitics

The parasitics associated with a printed conductor along with its return path are essentially the parameters of a transmission line model. As the spectral content of a signal approach higher frequencies, the treatment of printed conductors on a PCB as transmission lines is essential to consider the impact of parasitics on the signal integrity parameters (such as delay, reflection, attenuation, etc.) [17-19]. Transmission line models can be broadly classified into 2 types: lossy model and lossless model. A lossy transmission line model can be described in terms of a conductor series resistance  $R_{TL}$ , series inductance  $L_{TL}$ , shunt capacitance  $C_{TL}$  and a dielectric conductance  $G_{TL}$  ( $G_{TL}$  is negligible up to very high frequency). In contrast, a lossless transmission model ignores  $R_{TL}$  and  $G_{TL}$ , assuming they become negligible at high frequency compared to the series reactance ( $j\omega L_{TL}$ ) and shunt susceptance ( $j\omega C_{TL}$ ), respectively. The lossless model is a mathematical abstract, which is limited to certain high frequency applications only.

In order to extract transmission line parasitics on a PCB, majority of the efforts rely on high frequency reflection-based techniques. In this regard, Dascher demonstrated utilization of TDR (Time Domain Reflectometry) to find the PCB parasitics [20]. Here, characteristic impedance  $Z_0$  and end to end time delay  $T_D$  of a uniformly distributed PCB transmission line is determined first using TDR and then the determined values of  $Z_0$  and  $T_D$  are used to compute the  $L_{TL}$  and  $C_{TL}$  of the uniform PCB transmission line. Hashino et al. utilized TDR to determine parasitic  $L_{TL}$  and  $C_{TL}$  of a nonuniform transmission line on a power electronic PCB [21]. Lei et al. presented a built-in TDR test for monitoring discontinuity in the distribution of line parasitics on a flexible hybrid electronic system [22]. These TDR based approaches describe the parameters of the lossless transmission line model and their distribution exploiting reflection generated by a fast-edged signal. However, these methods cannot precisely describe the lossy parameters of the line.

Several research works stress on the importance of modelling and extraction of the lossy parameters of the line in addition to the lossless parameters for addressing important signal integrity concerns; such as signal attenuation at low frequency under small termination load [23], loss effect for long length [24], attenuation of the high frequency spectral contents [19], description of transmission line self-damping [25], determination of the electric and magnetic field variables [26] and determination of the chaotic circuit behavior [27]. Besides, in case of FHE assembly, the lossy parameter  $R_{TL}$  is subject to significant variations from the mechanical stress of flexing [28], and this variation can culminate into a catastrophic failure of electrical connection. Therefore, in case of an FHE assembly, the extraction of the lossy parameter  $R_{TL}$  is deemed essential for appropriate assessment of both the signal integrity and device reliability.

The lossy parameter  $R_{TL}$  can be extracted at low frequency using Four-Wire Kelvin Test [29] separately on the constituent printed conductors. This will require access to the two ports of a transmission line. While, at high frequency as the lossy parameter  $G_{TL}$  and frequency dependent increase of  $R_{TL}$  due to proximity effect (change in the conductor current distribution due to magnetic field resulting from the current in another conductor in proximity [30]) become considerable, the separate measurement of two constituent conductors do not completely account for the lossy behavior of the transmission line. The extraction of transmission line lossy parameters is achievable at high frequency using two-port S-parameter measurement [31,32].

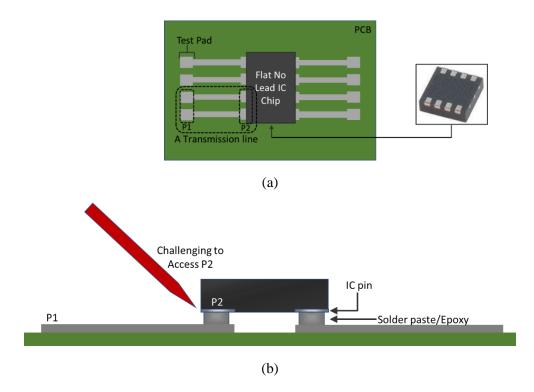

However, a two-port measurement of transmission lines bonded to IC chips on an FHE assembly is challenging to implement as this requires post solder probing at the IC pins. This is difficult to accomplish as the IC pins are extremely small and often located underneath the IC package with no access as depicted in the Fig. 2.1. Even when the IC pins are accessible, repeated probing at the pins to track the parasitics from an FHE assembly can accumulate additional stress at the IC-substrate contact, thereby altering the measured quantity.

Consequently, in order to extract the parameters of a lossy transmission line on an FHE assembly, it is necessary to find a one-port measurement technique that eliminates the need for probing at the IC pins. In the proposed approach, we exploit on-chip ESD protection circuitry in commercial ICs to extract the parameters of the lossy transmission lines bonded to an IC chip on an FHE assembly. The extraction technique obviates the need for post solder probing at the IC pins and relies on direct computation of the data from one-port impedance measurements. Notably, the measurement method also allows for the isolation of the parasitic resistance of an individual printed conductor bonded to single IC pin. This feature bears critical importance for an FHE assembly, as parasitic resistance of different printed conductors on the same substrate can vary differently due to the nonuniformity of fabrication and stress distribution.

Fig. 2.1: a) a PCB transmission line with two ports marked as P1 and P2 b) challenge in conducting two port measurement of the transmission line bonded to flat no lead IC chip.

#### 2.2 On Variation of Parasitics in Flexible PCB

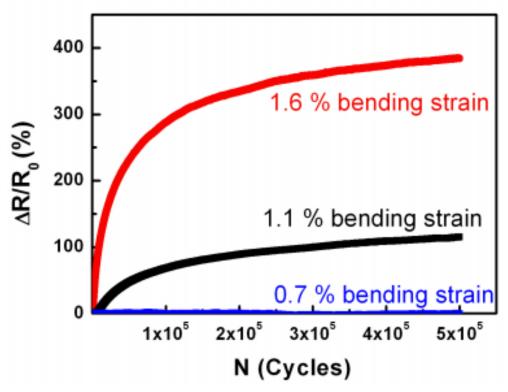

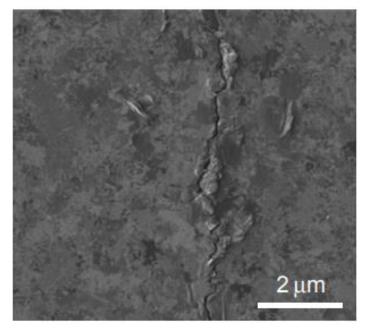

To detect and analyze the variation of parasitics on a flexible PCB, several efforts have been made. Kim et al. reported gradual rise in the R of printed Cu (copper) traces on flexible substrate with the increase in the number of bending cycles [33]. They varied the bending strain on the traces by changing the bending radius and demonstrated the variation in the R increase with the increase of bending strain due to reduction of bending radius, as depicted by the Fig. 2.2. They observed cracks as shown in Fig. 2.3 in the parts of the printed conductor presenting increased R and attributed the increase of R with bending cycles to the propagation of the cracks resulting from the bending strain. They also observed when the bending radius is large, the strain is so small that no cracks are formed in the conductive trace. Therefore, there is no significant change in the R of the conductive trace with the increase of bending cycles, as observed for 0.7% bending strain in the Fig. 2.2.

Use in accordance with copyright rules, © [2011] IEEE

Fig. 2.2: Relative change in resistance of a Cu trace against the number of bending cycles for different levels of bending strain [33].

Use in accordance with copyright rules, © [2011] IEEE

Fig. 2.3: Microscope image of a propagating crack on Cu trace [33].

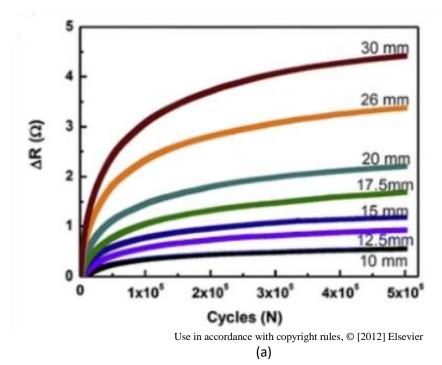

Also, Yi et. al. reported increase in the R of printed copper traces due to evolution of cracks upon bending strain [10]. They further demonstrated the increase in the R of printed traces depend on the thickness of the trace and annealing level during its fabrication as depicted in the Fig. 2.4. Fig. 2.4(a) shows higher increase in the R for Cu traces upon bending as the thickness of the traces are increased. This is due to increase of bending strain with the increase in thickness of the film. Fig. 2.4(b) shows as the annealing temperature to evaporate the composite materials (materials mixed with metal particles to obtain printable ink) of inkjet printed Ag (silver) traces is increased over a certain level, the R of the printed conductor shows larger variations with the increasing bending cycles. While, the pure Ag film of same dimension deposited directly by evaporation shows highest degree of R variation with the increase of bending cycles. Although the metal traces become more conductive as more of composite materials from the ink are evaporated out by higher levels of annealing temperature, they become more brittle at the same time. Consequently, conductive traces annealed at higher temperature show increased R variation upon bending. Several other research works demonstrate the degradation of electrical R as well as catastrophic failure of electrical connection due to formation and propagation of cracks upon subjecting conductive traces on flexible substrate to bending [34,35]. Majority of these research works investigating variation of parasitics on a flexible PCB focus on characterizing parasitic resistance of standalone printed traces subjected to stress.

140 Evaporated Ag Evaporated 350 °C 120 250 °C 100 ARVR<sub>0</sub> (%) 200°C 150 °C 80 60 40 Inkjet-printed Ag 20 1x10<sup>5</sup> 2x10<sup>5</sup> 3x10<sup>5</sup> 4x10<sup>5</sup> 5x10<sup>5</sup> Cycles (N) Use in accordance with copyright rules, © [2014] IOP Science

Fig. 2.4: (a) Change in the resistance of Cu traces against number of bending cycles for different trace thickness b) Relative change in the resistance of Ag traces against number of bending cycles for different annealing temperature [10].

(b)

A few studies involving Si-based rigid electronics on flexible substrates using optical techniques have inferred the variation in the stress distribution on the printed conductors due to the placement of the rigid parts [13,14]. As an impact of this, Soman et al. observes consistent cracking in flexible conductive traces close to solder joints of a rigid IC chip as shown in Fig. 2.5 [14]. Consequently, complex arrangements of commercial ICs on a flexible substrate is expected to have impact on the parasitic behavior, such as changes in R. Therefore, investigating the parasitic element variation of printed conductors bonded to an IC chip on an FHE assembly is essential for appropriate assessment of the reliability and signal integrity concerns of the technology.

In the available literature, no research work on electrical characterization of printed conductors bonded to IC chips on an FHE assembly has been reported. In addition, there has been no study investigating parasitic L and C and their variation on an FHE assembly. Thereby, this thesis aims to explore the variation of RLC parasitics of printed conductors bonded to IC chips on an FHE assembly employing the proposed measurement method.

Use in accordance with copyright rules, © [2016] IEEE

Fig. 2.5: a) component side of a double-sided FHE assembly b) closeup view of the 20 pin Si-based rigid IC chip c) crack in Cu trace d) cross section showing failure in Cu trace [14].

### 2.3 Chapter Summary

In this work, the PCB parasitics are treated transmission line parameters. Several issues such as signal attenuation and transmission line self-damping stress the importance of finding the lossy parameters ( $R_{TL}$  and  $G_{TL}$ ) of a transmission line in addition to the lossless parameters ( $L_{TL}$  and  $C_{TL}$ ). In case of FHE systems, the variation of the conductor resistance  $R_{TL}$  throughout the lifecycle of a device further accentuates the importance of its extraction. Several research works demonstrated extraction the PCB parasitics using one port TDR measurement. These TDR based measurements only extracts the lossless parameters of the line but do not extract the lossy parameters. The extraction of the lossy parameters is achievable with two port measurements such Kelvin test, S-parameter analysis. However, in case of an FHE system, two port access to a transmission line, which is bonded to an IC pin at one of its ports, is challenging to achieve. The proposed measurement circumvents the challenge, as it requires only one port access to the transmission line to extract both the lossy and lossless parameters.

On the other hand, research works on tracking the parasitics from an FHE assembly mostly focus on tracking parasitic R of standalone printed traces. In the available literature, no research work on tracking the variation of parasitic L and C has been reported. Also, as the placement of rigid ICs on a flexible substrate is expected impact the parasitic variation, tracking these parasitics for printed traces bonded to rigid ICs is essential for appropriate assessment of parasitic variation on an FHE assembly. In this regard, the proposed extraction method provides a scope to explore the parasitic variation of printed conductors bonded to IC chips.

# Chapter 3

# Transmission Line Modelling

A transmission line is a structure for guiding electromagnetic waves in a contained manner. In the simplest form, a transmission line is comprised of two conductors, one for propagation and the other for return of the electrical charges. As the length of the conductors becomes long enough such that it turns out to be comparable to the shortest wavelength of interest, the wave nature of the transmission needs to be considered. In this thesis, the PCB parasitics are treated as parameters of transmission line. The first section in the chapter reviews the transmission line analysis with Lumped Element Model. The next section focuses on the transmission line approximations, which are utilized in this work for extracting the line parameters and further validating the extracted parameters.

### 3.1 Review on Lumped Element Model Analysis

The nature of the electromagnetic wave is described by Maxwell's Equations [36]. To facilitate analysis, modelling and simulation the Lumped Element Model is derived from Maxwell's Equations. The Lumped Element Model links the distributed field theory and the circuit theory in describing the electromagnetic wave propagation through a transmission line. Fig. 3.1 depicts the Lumped Element Model for the propagation of electromagnetic waves through a small segment  $\Delta z$  of a 2-conductor transmission line.

Fig. 3.1: Lumped Element Model of transmission line of length  $\Delta z$ .

In the Fig. 3.1, as the length of the transmission line segment,  $\Delta z \rightarrow 0$ , the Lumped Element Model approximates the distributed behavior of the transmission line. The descriptive parameters of the Lumped Element Model are discussed below:

- R' represent the combined resistance of the two constituent conductors per unit length of the transmission line. The series resistance accounts for the ohmic loss of energy resulting from the conductor current in the transmission line.

- G' represent the conductance of the dielectric medium separating the two conductors in a unit length of the transmission line. The shunt conductance accounts for the dielectric loss of energy resulting from the leakage current through the dielectric medium.

- L' represent the loop inductance per unit length of the transmission line. The series inductance accounts for the energy stored in the magnetic field around the transmission line.

- C' represent the capacitance between the two conductors per unit length of the transmission line. The shunt capacitance accounts for the energy stored in the electric field between the two conductors.

Next, we intend to describe other important transmission line parameters (such as characteristic impedance, propagation constant, time delay) in terms of the lumped parameters R', L', G' and C'.

First, by applying Kirchhoff's Voltage Law (KVL) in the loop 1 of Fig 3.1 and taking the limit as  $\Delta z \rightarrow 0$ , we obtain:

$$\frac{\partial v(z,t)}{\partial z} = -R'i(z,t) - L'\frac{\partial i(z,t)}{\partial t}$$

(3.1)

Similarly, by applying Kirchhoff's Current Law (KCL) in the node Q of Fig. 3.1 and taking the limit as  $\Delta z \rightarrow 0$ , we get:

$$\frac{\partial i(z,t)}{\partial z} = -G'v(z,t) - C'\frac{\partial v(z,t)}{\partial t}$$

(3.2)

The Eqns. (3.1) and (3.2) are known as Telegrapher's Equations. By setting  $v(z,t) = Re[V(z)e^{j\omega t}]$  and  $I(z,t) = Re[I(z)e^{j\omega t}]$ , we obtain the time harmonic line equations as:

$$\frac{dV(z)}{dz} = -(R' + j\omega L')I(z)$$

(3.3)

and

$$\frac{dI(z)}{dz} = -(G' + j\omega C')V(z)$$

(3.4)

Combining the Eqns. (3.3) and (3.4), the line voltage and current can be expressed in terms of position z by the following differential equations:

$$\frac{d^2V(z)}{dz^2} - \gamma^2V(z) = 0 {(3.5)}$$

and

$$\frac{d^2I(z)}{dz^2} - \gamma^2I(z) = 0 {3.6}$$

where  $\gamma$  is the propagation constant, given by

$$\gamma = \sqrt{(R' + j\omega L')(G' + j\omega C')} = \alpha + i\beta \tag{3.7}$$

In the Eqn. (3.7),  $\alpha$  is the attenuation constant describing the attenuation per unit length of transmission line and  $\beta$  is the phase constant describing phase change per unit length of the transmission line.

The solutions to the differential Eqns. of (3.5) and (3.6) are known as:

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z}$$

(3.8)

and

$$I(z) = I_0^+ e^{-\gamma z} + I_0^- e^{\gamma z}$$

(3.9)

$V_0^+$ ,  $V_0^-$ ,  $I_0^+$  and  $I_0^-$  are constants and their values are determined by the boundary conditions imposed on the transmission line. Substituting Eqn. (3.8) into (3.3) yields:

$$I(z) = \frac{\gamma}{R' + j\omega L'} \left[ V_0^+ e^{-\gamma z} - V_0^- e^{\gamma z} \right]$$

(3.10)

Comparing the Eqn. (3.9) and (3.10), we note:

$$I_0^+ = \frac{\gamma}{R' + j\omega L'} V_0^+; I_0^- = \frac{\gamma}{R' + j\omega L'} (-V_0^-)$$

(3.11)

Now the characteristic impedance  $Z_0$  is defined as the ratio of the voltage and current waves propagating in a single direction at a certain point in the transmission line. Hence, we can express  $Z_0$  as:

$$Z_0 = \frac{V_0^+}{I_0^+} = \frac{-V_0^-}{I_0^-} = \frac{R' + j\omega L'}{\gamma} = \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}}$$

(3.12)

At high frequency it is plausible to take the lossless approximation by considering R'=0 and G'=0 as R' and G' turn out to be negligible with respect to  $\omega L$  and  $\omega C$  respectively. Under the lossless approximation, the  $Z_0$  becomes

$$Z_0 = \sqrt{\frac{L'}{C'}} \tag{3.13}$$

Now, we aim to find simplified expressions for  $\alpha$  and  $\beta$ . For this,  $\gamma$  from the Eqn. (3.7) is expressed as:

$$\gamma = j\omega\sqrt{L'C'}\left(1 + \frac{R'}{j\omega L'}\right)^{\frac{1}{2}}\left(1 + \frac{G'}{j\omega C'}\right)^{\frac{1}{2}}$$

(3.14)

Expanding the last two terms of the Eqn. (3.10) with Taylor series approximation and simplifying under the low loss approximation ( $0 < R' << \omega L'$  and  $0 < G' << \omega C'$ ) yields:

$$\gamma = \frac{1}{2} \left( R' \sqrt{\frac{C'}{L'}} + G' \sqrt{\frac{L'}{C'}} \right) + j\omega \sqrt{L'C'}$$

(3.15)

From the Eqn. (3.11), we obtain:

$$\alpha = \frac{1}{2} \left( \frac{R'}{Z_0} + G' Z_0 \right); \ \beta = \omega \sqrt{L'C'}$$

(3.16)

Whereas, under the lossless approximation (R'=0 and G'=0), the  $\gamma$  becomes:

$$\gamma = j\omega \sqrt{L'C'} \tag{3.17}$$

with

$$\alpha = 0 \; ; \; \beta = \omega \sqrt{L'C'} \tag{3.18}$$

So, the phase constant  $\beta$  remains same in case of both low loss and loss less approximations. The phase velocity  $v_p$  (the velocity of a single frequency wave) is expressed as:

$$v_p = \frac{\omega}{\beta} = \frac{1}{\sqrt{L'C'}} \tag{3.19}$$

Also, the group velocity  $v_g$  (the envelope velocity of a multiple frequency wave) is expressed as:

$$v_{g} = \frac{\partial \omega}{\partial \beta} = \frac{1}{\sqrt{L'C'}} \tag{3.20}$$

Thus, for any signal propagating through a low loss or loss less transmission line, the propagation velocity v can be expressed as:

$$v = v_p = v_g = \frac{1}{\sqrt{L'C'}}$$

(3.21)

The propagation delay or delay per unit length  $T'_D$  of the transmission line can be expressed as:

$$T_D' = \frac{1}{v} = \sqrt{L'C'}$$

(3.22)

So, the end-to-end delay  $T_D$  of a uniform transmission line of length l becomes:

$$T_D = l\sqrt{L'C'} \tag{3.23}$$

Another important parameter of the transmission line relevant to this work is fundamental resonance. At the frequency  $f_r$ , the reflected wave cancels out the incident wave at the front end of the transmission line, i.e., the incident and the reflected waves have a phase difference of  $180^{\circ}$  or half of a cycle. This implies,  $f_r$  is the frequency where the end to end time delay of the transmission line for a one-way travel is quarter of a cycle. Thus, we can express  $f_r$  of a uniform transmission line as:

$$f_r = \frac{1}{4T_D} = \frac{1}{4l\sqrt{L'C'}} \tag{3.24}$$

Table 3.1 summarizes the important descriptive parameters of the transmission line and compares these parameters for low loss and lossless lines:

Table 3.1: Summary of the transmission line descriptive parameters.

| Parameters:                             | Low loss (0 <r'<<ωl', 0<g'<ωc')<="" th=""><th>Lossless<br/>(<i>R</i> '=0, <i>G</i> '=0)</th></r'<<ωl',> | Lossless<br>( <i>R</i> '=0, <i>G</i> '=0) |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Characteristic Impedance ( $Z_0$ )      | $\sqrt{\frac{R'+j\omega L'}{G'+j\omega C'}}$                                                            | $\sqrt{rac{L'}{C'}}$                     |

| Attenuation Constant (α)                | $\frac{1}{2} \left( \frac{R'}{Z_0} + G' Z_0 \right)$                                                    | 0                                         |

| Phase Constant $(\beta)$                | $\omega \sqrt{L'C'}$                                                                                    | $\omega \sqrt{L'C'}$                      |

| Propagation Velocity (v)                | $\frac{1}{\sqrt{L'C'}}$                                                                                 | $\frac{1}{\sqrt{L'C'}}$                   |

| End-to-End Delay $(T_D)$                | $l\sqrt{L'C'}$                                                                                          | $l\sqrt{L'C'}$                            |

| Fundamental Resonance (f <sub>r</sub> ) | $\frac{1}{4l\sqrt{L'C'}}$                                                                               | $\frac{1}{4l\sqrt{L'C'}}$                 |

### 3.2 Approximations Utilized in this Work

The uniform transmission line extending from the test port to the IC pins on a PCB can be represented by a lumped equivalent circuit model [36] with N number of T segments as depicted in Fig. 3.2. In the model, total series resistance  $R_{TL}$ , total series inductance  $L_{TL}$  and total shunt capacitance  $C_{TL}$  between the test port and the IC pin are distributed among the N segments. As N becomes larger, the lumped equivalent circuit model approximates the distributed behavior of the transmission line over larger bandwidth. In the figure,  $Z_s$  is the source impedance. In the model of Fig 3.2, the total shunt conductance  $G_{TL}$  is neglected (as  $G_{TL}$  is insignificant within the bandwidth considered within the scope of this work). If the length of the uniform transmission model of Fig. 3.2 is assumed to be l, we can say  $R_{TL}=R'l$ ,  $L_{TL}=L'l$  and  $C_{TL}=C'l$ ; where, R', L' and C' are the parameters per unit length of the line as defined in the previous section.

When the load impedance  $Z_{load}$  becomes very small, the effect of  $C_{TL}$  can be neglected up to a certain bandwidth as long as the impedance due to  $C_{TL}$  is orders of magnitude larger than the sum of the impedance due to  $R_{TL}$ ,  $L_{TL}$  and the load. Hence, for a small  $Z_{load}$ , the transmission line from the test port to the IC pins on a PCB can be approximated within a certain bandwidth with  $R_{TL}$  and  $L_{TL}$  only. We refer to this approximation as a series RL model as depicted in Fig. 3.3(a). Conversely, as  $Z_{load}$  becomes very large, the effect of  $R_{TL}$  and  $L_{TL}$  can be neglected within a certain bandwidth as long as the admittance due to  $C_{TL}$  is orders of magnitude larger compared to sum of admittance due to  $R_{TL}$ ,  $L_{TL}$  and the load. Hence, for a very large  $Z_{load}$ , the transmission line from the test port to the IC pins can be approximated within a certain bandwidth with  $C_{TL}$  only, which we refer to this as the shunt C model depicted in Fig. 3.3(b).

Fig. 3.2: Equivalent RLC model with N number of T segments for a uniform transmission line on PCB (shown for N=4).

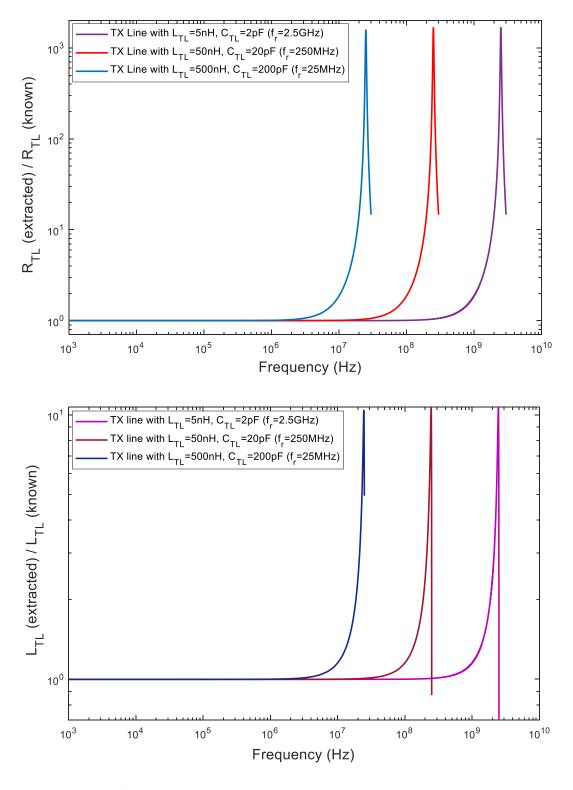

The bandwidth, up to which series RL and shunt C models are accurate under appropriate  $Z_{load}$ , is dependent on  $L_{TL}$  and  $C_{TL}$  of the transmission line. To demonstrate this bandwidth dependency for the series RL model, the input impedance  $Z_{in,TP}$  of the RLC transmission line model of Fig. 3.2 is simulated as a function of frequency using the Keysight Advance Design System (ADS) platform for varying the orders of  $L_{TL}$  and  $C_{TL}$ . The characteristic impedance is held constant at 50  $\Omega$  and parameters  $R_{TL}=1$   $\Omega$ ,  $Z_{load}=1$   $\Omega$  and N=100. From the simulation,  $R_{TL}$  is extracted as the real part of  $Z_{in,TP}$  minus  $Z_{load}$ . Also,  $L_{TL}$  is extracted as the slope of the imaginary part of  $Z_{in,TP}$  with respect to frequency. The extracted  $R_{TL}$  and  $L_{TL}$  are normalized by the corresponding known values inserted in the RLC model and plotted against frequency as shown in Fig. 3.4. It is observed that the extracted  $R_{TL}$  and  $L_{TL}$  remains constant and equal to their known values well below the resonant frequency. In other words, the series RL model is valid for at least one order of magnitude below the fundamental resonance  $f_r$ , given by the following expression:

$$f_r = \frac{1}{4\sqrt{L_{TL}C_{TL}}} = \frac{1}{4T_D} \tag{3.25}$$

Here,  $T_D$  is the end-to-end time delay for the wave propagation in the transmission line. The parameter  $T_D$  can be expressed in terms of line length l, velocity factor  $v_f$  and velocity of light c as follows:

$$T_D = \frac{l}{v_f \cdot c} \tag{3.26}$$

Similarly, it can be shown for a large  $Z_{load}$ , description of a transmission line by its equivalent shunt C model, holds as a reasonable approximation well below (at least one order of magnitude) the fundamental resonance.

Fig. 3.3: Low frequency lumped equivalent models for transmission line: a) series RL model for small  $Z_{load}$  b) shunt C model for large  $Z_{load}$ .

Fig. 3.4: Normalized plot of extracted  $R_{TL}$  and  $L_{TL}$  as function of frequency from a transmission line terminated with small load impedance of  $1\Omega$ .

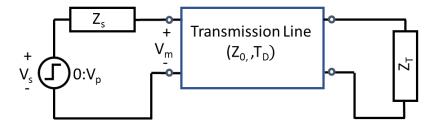

Isolating the lumped equivalent parameters of a transmission line is practically challenging at high frequency, due to distributed behavior of the transmission line [36]. One way to describe a transmission line at high frequencies is by using the two-port lossless transmission line model depicted in Fig. 3.5. This model makes use of the characteristic impedance,  $Z_0$  and end-to-end time delay parameter,  $T_D$ .

Considering the lossless approximation ( $R_{TL}$ =0 and  $G_{TL}$ =0) at high frequency, using the Eqns. (3.13) and (3.23) the total series inductance  $L_{TL}$  for a uniform transmission line can be described in terms of  $Z_0$  and  $T_D$  as:

$$L_{TL} = Z_0 \cdot T_D \tag{3.27}$$

Similarly, under lossless approximation, total shunt capacitance  $C_{TL}$  for a uniform transmission can be expressed in terms of  $Z_0$  and  $T_D$  as:

$$C_{TL} = Z_0 / T_D \tag{3.28}$$

This latter model provides a second method to extract the reactive elements of the transmission line. These will be used to compare the corresponding elements extracted by the series-RL and shunt-C models. In principle, they should be the same.

Fig. 3.5: Transmission line lossless model at high frequency.

# 3.3 Chapter Summary

First the Lumped Element Model of the transmission line is introduced. The derivations of the important descriptive parameters of the transmission line in terms of the lumped parameters are reviewed. Next, the Lumped Element Model is presented in a modified manner as the equivalent RLC model of the transmission line for utilization in the proposed extraction method. It is shown that the transmission line can be approximated by the series RL model and shunt C model up to a certain bandwidth for small and large load impedances, respectively. The bandwidth of the series RL and shunt C approximations is found to be well below (at least one order of magnitude) the fundamental resonance, which can be estimated with the length and velocity factor of the transmission line. The RLC parameters of the line are extractable within the appropriate bandwidth with these approximations and the proposed method will utilize them. Further, the high frequency lossless model of the transmission line is described. The lossless model provides another way of finding the LC parameters of the transmission line at high frequency through determination of the characteristic impedance and the end-to-end time delay. The extracted parameters from the lossless model will be utilized to validate the corresponding parameters extracted with the proposed method.

## Chapter 4

# Proposed Measurement Methodology

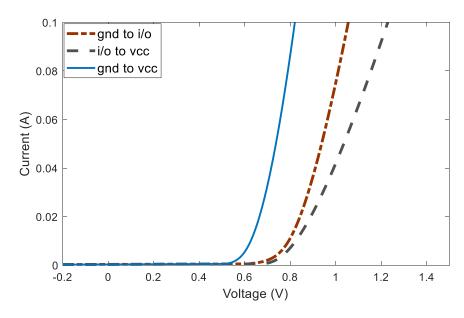

CMOS ICs include on-chip ESD protection circuitry in order to provide protection against large charge build up on high-impedance nodes [29]. The measurement method presented in this work utilizes the measured data from the on-chip ESD protection circuit before and after bonding the IC chip to a PCB transmission line in order to extract the RLC parasitics of the line. This chapter provides stepwise description of the proposed measurement method.

### 4.1 Modelling On-chip ESD Protection Circuit

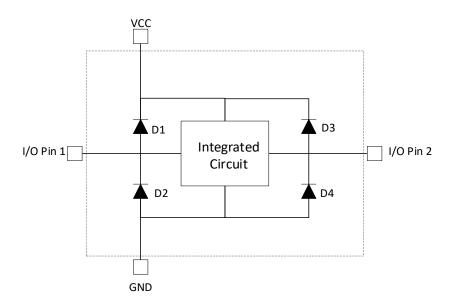

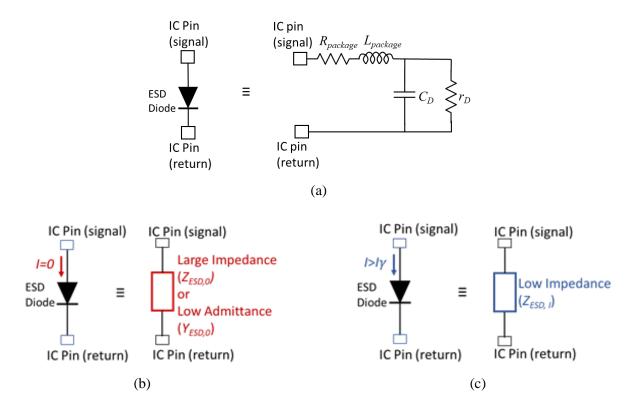

The ESD protection circuit located between I/O and power supply pins (GND or VCC) can be modelled as diodes [29]. Fig. 4.1 illustrates the ESD diode model of an IC with two I/O pins, power and GND. As a point of reference, the ESD *i-v* behavior for an I/O pin between GND and VCC corresponding to the 8-bit microcontroller ATTINY85 made by Microchip Technology are shown in Fig. 4.2. The shape of the *i-v* curves substantiates the depicted diode model. These curves are different for different pin combinations, as the ESD structures are different for different pin types, i,e., I/O and power supply.

The small-signal equivalent circuit for an ESD diode is depicted in Fig. 4.3(a). In the figure,  $r_D$  represents diode incremental resistance given by

$$r_D = \frac{\eta V_T}{I} \tag{4.1}$$

where,  $\eta$  is diode ideality factor,  $V_T$  is thermal voltage and I is diode forward current [37].

Also, in Fig. 4.3(a)  $C_D$  represents the diode capacitance given by

$$C_D = \frac{\tau_T I}{\eta V_T} + C_j \tag{4.2}$$

where  $\tau_T$  is diode transit time.  $C_j$  is junction capacitance, which can be considered as negligible in a forward biased diode [37].

Fig. 4.1: Diode model for ESD protection circuit [29].

Fig. 4.2: I vs V plot (a) from GND (+) pin to I/O pin (-) (b) I/O pin (+) to VCC pin (-) (c) GND pin (+) to VCC pin (-) measured from Attiny85 chip.

Fig. 4.3: Small signal representation of an ESD: (a) equivalent circuit (b) reverse Biased model c) forward biased model.

When the ESD diode is reverse biased (i.e., I=0), the diode presents a large impedance, or equivalently, a small admittance as shown in Fig. 4.3(b). Conversely, when the ESD diode is forward biased at  $I > I_{\gamma}$ , the diode presents a small impedance as shown in Fig. 4.3(c). In this work,  $I_{\gamma}$  is defined as the diode current where  $r_D$  is equal to 1  $\Omega$ .

The measurement technique presented in this paper requires prior knowledge of the impedance of the ESD diode (denoted here as  $Z_{ESD,I}$ ) at a chosen frequency  $\omega$  under a chosen forward bias current  $I>I_{7}$ . Also prior knowledge of the admittance of the ESD diode ( $Y_{ESD,0}$ ) at the same frequency under I=0 is required. In the case of the Attiny85 IC made by Microchip Technology, it was observed experimentally that the impedance and admittance of different ESD diodes across the same IC varied by more than 20%. In addition, the impedance and admittance of the same ESD diode varied very little (less than 1%) across 33 different samples of the same ICs. Hence, the ( $Z_{ESD,I}$ ) and ( $Y_{ESD,0}$ ) of a particular ESD diode in different samples of a given IC chip are assumed to be same.

# 4.2 Extracting RLC Parameters of a Transmission Line Bonded to an IC Chip

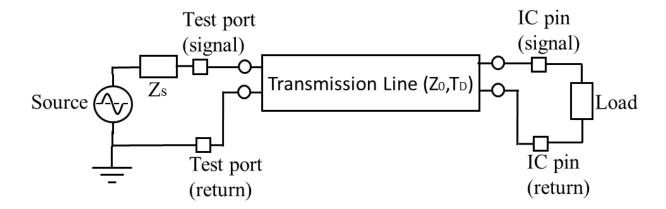

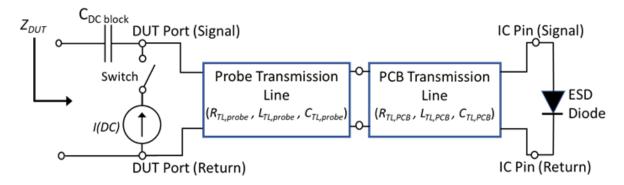

In this subsection, we will utilize the prior knowledge of the impedance and admittance parameters of an ESD diode in a given IC chip to extract the RLC parameters of a pair of conductors acting as a transmission line bonded to the IC chip. Fig. 4.4 shows the measurement setup for extraction of the RLC parameters of a PCB transmission line bonded to an ESD diode in a commercial IC chip. The proposed method requires identifying the input impedance  $Z_{DUT}$  of the DUT (Device-under-Test) at a particular frequency under a specific DC bias condition of the ESD diode. The DC bias point of the ESD diode is established with a current source connected to the DUT through a switch. The rationale behind using a current instead of a voltage source is to force the ESD diode into desired DC bias point regardless of the unknown parasitic resistance in series with the source and ESD diode. The capacitor  $C_{DC\ block}$  prevents any DC current from going into the impedance measuring instrument, while acting as a short circuit to the AC signals above a certain frequency.

From the discussions in the previous section, a transmission line terminated with small load impedance can be approximated with series RL model and for a large load impedance the transmission line can be approximated with shunt C model, up to a certain bandwidth, of course. In the proposed measurement, small and large load impedances for the PCB transmission line are achieved by forward or reverse biasing the ESD diode as illustrated by Fig. 4.5(a) and 4.5(b), respectively.

Fig. 4.4: Measurement setup for extracting the RLC parameters of a PCB transmission Line bonded to a commercial IC chip.

Fig. 4.5: The equivalent circuit of DUT for: (a) forward biased ESD diode (b) reverse biased ESD diode. From Fig. 4.5(a), the resistance of the PCB transmission line,  $R_{TL,PCB}$  can be found from:

$$R_{TL,PCB} = \text{Real}(Z_{DUT,I}) - \text{Real}(Z_{ESD,I}) - R_{TL,probe}$$

(4.3)

Also, from Fig. 4.5(a), the inductance of the PCB transmission line,  $L_{TL,PCB}$  can be found as:

$$L_{TL,PCB} = \frac{1}{\omega} \left[ \operatorname{Imag}(Z_{DUT,I}) - \operatorname{Imag}(Z_{ESD,I}) \right] - L_{TL,probe}$$

(4.4)

Here, the real and imaginary parts of  $Z_{DUT,I}$  is directly measured at a frequency  $\omega$  under a chosen bias current I. The real and imaginary parts of the ESD protection circuit  $Z_{ESD,I}$  is known by the separate measurement of the ESD diode at the same frequency  $\omega$  and bias current level I. Also, the probe parasitics,  $R_{TL,probe}$  and  $L_{TL,probe}$ , are known from a separate measurement.

From Fig. 4.5(b), the capacitance of the PCB transmission line,  $C_{TL,PCB}$  can be found from:

$$C_{TL,PCB} = \frac{1}{\omega} \left[ \operatorname{Imag}(Y_{DUT,0}) - \operatorname{Imag}(Y_{ESD,0}) \right] - C_{TL,probe}$$

(4.5)

Here the imaginary part of  $Y_{DUT,0}$ = $(1/Z_{DUT,0})$  is directly measured at frequency  $\omega$  and the imaginary part of  $Y_{ESD,0}$  is known by the separate measurement of the ESD diode at the same frequency  $\omega$ . The probe capacitance  $C_{TL,probe}$  is known from a separate measurement.

Thus, the direct input impedance measurement of a transmission line bonded to a commercial IC chip, augmented with the prior measurement of the on-chip ESD diode impedance under same frequency and DC bias current, allows one to extract the RLC parameters of the transmission line using the presented method.

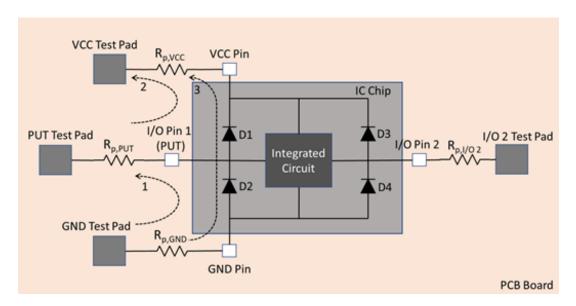

## 4.3 Isolating the Parasitic Resistance of a Single IC Pin

This subsection delineates the decomposition of extracted  $R_{TL,PCB}$  from the PCB transmission line into the constituent resistances of two printed conductors forming the transmission line. The parasitic resistance of an individual printed conductor bonded to a single IC pin can be isolated following the presented method within the same bandwidth constraint applicable for the extraction of  $R_{TL,PCB}$ .

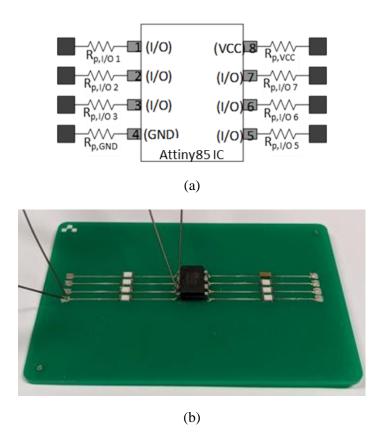

The circuit representation of an IC device with two I/O and power supply pins assembled on a substrate is illustrated in Fig. 4.6. In the figure, the parasitic resistance associated with each IC pin are shown. The I/O pin under test is referred as PUT (pin-under-test). The total series resistance  $R_{TLI,PCB}$  extracted from the transmission line 1 (between GND and PUT test pads) in the figure can be expressed as

$$R_{TL1,PCB} = R_{p,PUT} + R_{p,GND} \tag{4.6}$$

Likewise, the total series resistance  $R_{TL2,PCB}$  extracted from the transmission line 2 (between PUT and VCC test pads) in the figure can be expressed as

$$R_{TL2,PCB} = R_{p,PUT} + R_{p,VCC} \tag{4.7}$$

Fig. 4.6: Extraction of parasitic resistance of an individual printed conductor bonded to a single IC pin.

As there are three unknowns ( $R_{p,PUT}$ ,  $R_{p,GND}$  and  $R_{p,VCC}$ ) listed in the above two equations, we need to identify a third equation. This is found by recognizing that the total series resistance  $R_{TL3,PCB}$  extracted from transmission line 3 (between the GND and VCC pads ) in the figure.  $R_{TL3,PCB}$  can be expressed as

$$R_{TL3,PCB} = R_{p,GND} + R_{p,VCC} \tag{4.8}$$

Therefore, to isolate  $R_{p,PUT}$  from the power supply parasitic resistances  $R_{p,GND}$  and  $R_{p,VCC}$ , one needs to extract the  $R_{TL1,PCB}$ ,  $R_{TL2,PCB}$  and  $R_{TL3,PCB}$  from the transmission lines 1, 2 and 3, respectively. The extracted transmission line resistances can be expressed in matrix form as follows:

$$\begin{bmatrix} R_{TL1,PCB} \\ R_{TL2,PCB} \\ R_{TL3,PCB} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 \\ 1 & 0 & 1 \\ 0 & 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} R_{p,PUT} \\ R_{p,GND} \\ R_{p,VCC} \end{bmatrix}$$

or, more compactly as:

$$\mathbf{R}_{\mathrm{TL},\mathrm{PCB}} = \mathbf{C} \cdot \mathbf{R}_{\mathrm{p}} \tag{4.9}$$

From the measured transmission line resistance vector  $\mathbf{R}_{TL,PCB}$ , the unknown parasitic resistance associated with the given pins, designated by vector  $\mathbf{R}_{P}$ , can be found by inverting the matrix equation as follows:

$$\mathbf{R}_{\mathbf{P}} = \mathbf{C}^{-1} \cdot \mathbf{R}_{\mathbf{TL},\mathbf{PCB}} \tag{4.10}$$

Thus, the parasitic resistance associated with any IC pin can be isolated with the presented measurement method.

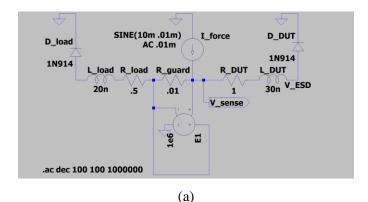

#### 4.4 Verification of the Proposed Measurement Method

For simulating the proposed method to extract the RLC parameters from a transmission line bonded to an IC chip, the measurement setup of Fig. 4.4 is implemented in Keysight's Advanced Design System (ADS) platform. In the ADS implementation, the probe and PCB transmission lines are realized by separate equivalent RLC models as shown Fig. 3.2. The number of segments, *N* for both the models are chosen to be 100. The ESD diodes are realized with 1N914 model for silicon diode (as the exact simulation model for an ESD diode is unavailable). The chosen parameter values for the ADS implementation are listed in the Table 4.1. The LC parameters of the probe and the PCB are chosen such that the characteristic impedance of the probe and the PCB transmission lines are equal. The range of the chosen RLC parameters for the probe and PCB are comparable to practical cases.

Table 4.1: Chosen parameter values for implementation for simulating the measurement setup of Fig. 4.4.

| Parameters              | Values |

|-------------------------|--------|

| $R_{TL,PCB}$            | 0.3 Ω  |

| $L_{TL,PCB}$            | 50 nH  |

| $C_{TL,PCB}$            | 20 pF  |

| $R_{TL,probe}$          | 0.7 Ω  |

| $L_{TL,probe}$          | 200 nH |

| $C_{\mathit{TL},probe}$ | 80pF   |

| $I_{DC}$                | 10 mA  |

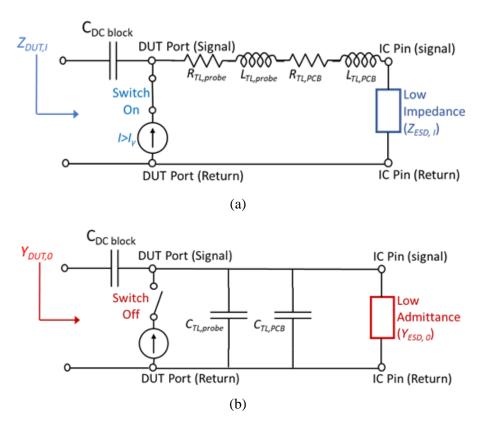

The impedance and admittance of the DUT (Device-under-Test: comprised of probe, PCB and connected diode) are simulated from 10 kHz to 10 MHz under the forward and reverse biased conditions of the diode, respectively. From the simulated results, the  $R_{TL,PCB}$ ,  $L_{TL,PCB}$  and  $C_{TL,PCB}$  are extracted following the proposed method. The extracted values of  $R_{TL,PCB}$ ,  $L_{TL,PCB}$  and  $C_{TL,PCB}$  are shown in Fig. 4.7, 4.8 and 4.9, respectively.

In the Fig. 4.7, 4.8 and 4.9, the extracted values of  $R_{TL,PCB}$ ,  $L_{TL,PCB}$  and  $C_{TL,PCB}$  agree with their known values up to a certain bandwidth. This bandwidth of the extraction depends on the bandwidth of the series RL and shunt C approximations. As discussed in the previous chapter, the series RL and shunt C approximations are valid well below the fundamental resonance  $f_r$  of a transmission line. As the probe and the PCB transmission lines are chosen to have the same characteristic impedance, we can assume they act as a single uniform transmission line. Hence,  $f_r$  of the entire uniform line can be found with the following expression (modified from Eqn. (3.25)):

$$f_r = \frac{1}{4(T_{D,probe} + T_{D,PCB})} = \frac{1}{4(\sqrt{L_{TL,probe}C_{TL,probe}} + \sqrt{L_{TL,PCB}C_{TL,PCB}})}$$

(4.11)

Where,  $T_{D,probe}$  and  $T_{D,PCB}$  are end-to-end delays for the probe and the PCB, respectively. The  $f_r$  found with Eqn. (4.11) is 50 MHz. From the simulated plots, the bandwidth for the accurate extraction of  $R_{TL,PCB}$ ,  $L_{TL,PCB}$  and  $C_{TL,PCB}$  is well below (one order of magnitude) the  $f_r$ =50 MHz.

Fig. 4.7: Extracted  $R_{TL,PCB}$  from simulation using the proposed method compared to its known value.

Fig. 4.8: Extracted  $L_{TL,PCB}$  from simulation using the proposed method compared to its known value.

Fig. 4.9: Extracted  $C_{TL,PCB}$  from simulation using the proposed method compared to its known value.

To verify the isolation of individual R of printed conductors bonded to a single IC pin, the circuit of Fig. 4.6 is simulated using SPICE. For the scope of this particular verification, the LC parameters associated with the printed conductors and the probe are neglected, as their impact in the bandwidth of the extracted R has already been discussed. It is assumed the extractions required for isolating R of a single IC pin are to be performed within the appropriate bandwidth. Here, the ESD diode is described with 1N914 SPICE model for silicon diode and the resistances associated to the IC pins are assigned different chosen values. An AC simulation is performed at 100 kHz. Applying the presented extraction method, the total R in series with each diode is extracted when the diode under test is forward biased at a 10 mA current level. Then, the extracted value is decomposed into R of individual printed conductors using the proposed technique of Section 4.3. Table 4.2 shows the chosen and the extracted values of the individual R for simulating circuit of Fig. 4.6. The table shows the values found in the simulation are same as their known values. Hence, the proposed method for isolating R of individual printed conductors bonded to a single IC pin is verified with simulation.

Table 4.2: The chosen (known) and the simulated values of the resistances in the circuit of Fig. 4.6.

| Resistances         | Chosen (known) Values (\Omega) | Extracted Values (12) |

|---------------------|--------------------------------|-----------------------|

| $R_{ ho,GND}$       | 2                              | 2                     |

| $R_{p,PUT}$         | 1                              | 1                     |

| $R_{p,VCC}$         | 0.67                           | 0.67                  |

| R <sub>p,1/O2</sub> | .5                             | .5                    |

## 4.5 Chapter Summary

In the proposed measurement method, the RLC parasitics associated with a transmission line bonded to an IC chip are extracted utilizing the on-chip ESD protection circuits. The on-chip ESD protection circuits can be modelled as diodes. First, for a given IC chip, the impedance and admittance of the ESD diodes under certain forward bias and reverse bias conditions need to be determined. Then, for having the IC chip bonded to printed conductors acting as a transmission line, the impedance and admittance parameters of the transmission line (loaded with a pre-measured on-chip ESD diode) are determined under the same biasing conditions as the

pre-measurement. From the determined impedance and admittance parameters of the ESD diode and the transmission line loaded the ESD diode, the RLC parameters of the line are extracted. Further, the extracted resistance of a transmission line can be decomposed into the resistances of the constituent printed conductors. This isolation of the resistance for a printed conductor connected to an arbitrary input/output pin is achieved using the extracted resistances from 3 transmission lines measurements involving the pin-under-test, Gnd pin and VCC pin. Finally, for verifying the proposed extraction method, ADS and SPICE simulations are performed with equivalent models for transmission line and diode. The simulation results show the extracted parameters with the proposed method agree with their corresponding known values well below the fundamental resonance of the measurand transmission line.

## Chapter 5

## In-Circuit-Test with the Proposed Method

This chapter introduces In-Circuit-Test with general challenges and measures in its application. Next, the practical challenges that may arise for applying the proposed measurement method to an In-Circuit-Test and the corresponding measures to circumvent these challenges are explored.

### 5.1 In-Circuit-Test: General Challenges and Measures

In-Circuit-Test (ICT) is run on a PCB after the components are assembled on the board. The objective is to identify defects as well as to address reliability, signal integrity and functionality of the assembled PCB. ICT is generally carried out using two different forms of test fixtures. One is Bed-of-Nail test fixture, where spring loaded pogo pins at customized locations on a rigid structure are pressed onto to test points in the board as shown in Fig. 5.1(a). Another is the Flying-Probe test fixture, where electromechanically controlled probes are programmed to access the test points on the board as shown in Fig. 5.1(b). Bed-of-Nail test fixture is relatively low cost and faster, but the fixture is customized for a particular PCB design. In contrast, the Flying-Probe test technique has a relatively higher cost and is slower, but it is adaptable to different PCB designs [40].

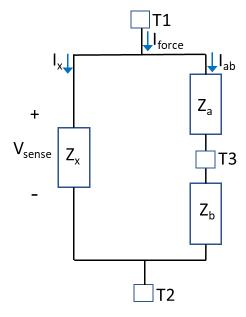

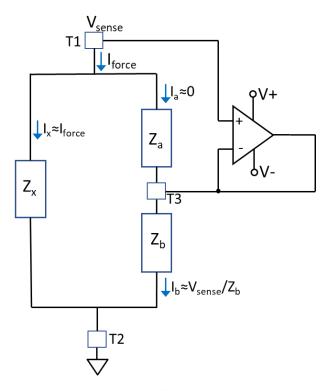

The general challenge in ICT is associated with access and isolation. Firstly, ICT requires additional test points at particular locations to be included in the design for allowing probe connection with the circuit. Secondly, when there are multiple parallel paths between two arbitrary test points, isolating an anomaly in an individual circuit path is challenging. Fig. 5.2 depicts the challenge in a simplified form, where we aim to measure the impedance of a particular element,  $Z_x$  between test point T1 and T2 in the circuit. In the figure,  $Z_a$  and  $Z_b$  are unknown impedances in

Fig. 5.1: In-Circuit-Testing with a) Bed-of-Nail fixture [38] and b) Flying-Probe fixture [39].

Fig. 5.2: Challenge in measuring impedance of an individual circuit element with In-Circuit-Test.

the path parallel to  $Z_x$ , and T3 is a test point in between them.  $V_{sense}$  is the voltage between the test points and  $I_{force}$  is the current forced through the test points. As the individual impedances of the parallel paths are unknown,  $I_x$  and  $I_{ab}$  are unknown as well. Hence,  $Z_x=V_{sense}/I_x$  cannot be determined, and an anomaly associated with it is challenging to isolate.

One way to test the impedance of a circuit element in parallel with other circuit elements on a PCB is temporary isolation of the circuit element under test from the rest of the circuitry. The temporary isolation is achievable by incorporating jumper pads into the PCB design [41]. Jumper pad connections and isolations can be implemented by placement and removal of solder paste

between the pads. However, this soldering/desoldering process for jumper pads can pose inconvenience in testing large circuits. To facilitate jumper pad isolation for testing large circuits a programmable test setup providing synchronized connection and isolation through solid state relays has been developed [42]. Fig. 5.3 depicts the jumper pad isolation in order to measure the impedance  $Z_x$  from the circuit of Fig. 5.2.

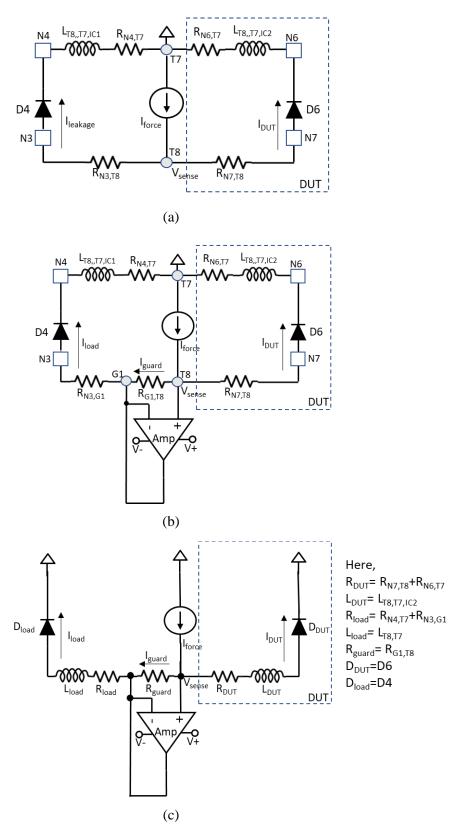

Another way to isolate measurement of a circuit element in parallel with other circuit elements on a PCB is restraining the measurement current through the parallel circuit elements by analog guarding [43,44]. Fig. 5.4 depicts the analog guarding scheme in order to measure the impedance  $Z_x$  from the circuit introduced before. In the figure, T2 is considered to be the common reference Gnd of the circuit. Here, the virtual short between the two input terminals of the op-amp restrains current through  $Z_a$ . The current through  $Z_b$  is supplied by the op-amp. Consequently, the current  $I_{force}$  flows through  $Z_x$  only, allowing its isolated measurement. However, non-idealities of an op-amp such as finite gain, bandwidth, parasitics will impose constraint on the ranges of impedances that can be measured and guarded [44].

Fig. 5.3: Zumper pad isolation to measure imedance of an individual circuit element with In-Circuit-Test.

Fig. 5.4: Analog guarding to measure impedance of an individual circuit element with In-Circuit-Test.

## 5.2 Application of the Proposed Measurement to In-Circuit-Test

The proposed method allows the post assembly extraction of the RLC parasitics of a transmission line, which is bonded to only a single IC chip at its one terminal. However, it is possible to have a transmission line with its two terminals bonded to two IC chips in an FHE circuit. In such cases, the in-circuit access to the transmission line under test and isolation of its series RL parameters is challenging to achieve.

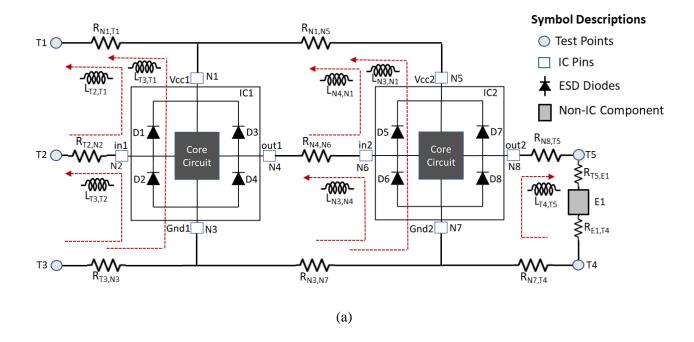

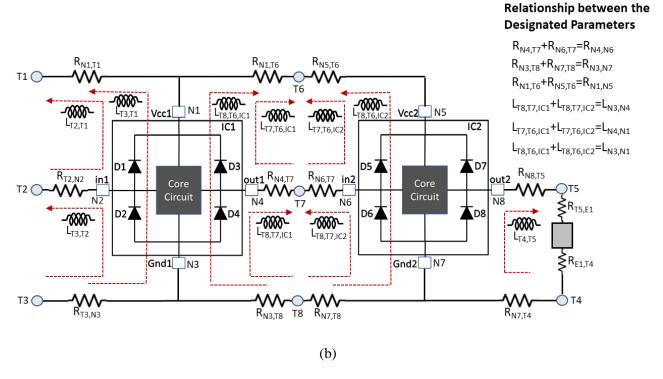

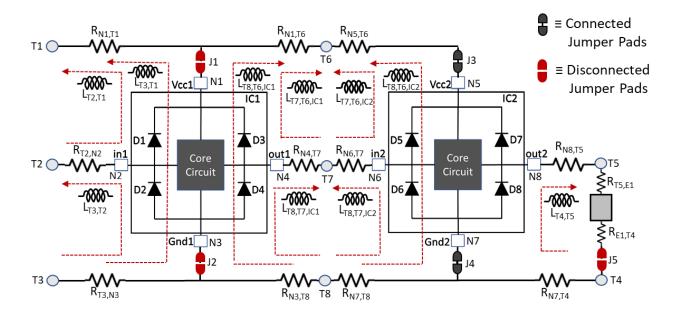

The Fig. 5.5 depicts an FHE assembly with multiple IC chips in a simplified form. In the figure, the series RL parameters associated with the printed conductors are shown as well. In the Fig 5.5(a), the input, output, and power supply of the PCB are the only access points in the design. Alongside the figure, the descriptions of the employed symbols are provided. Firstly, the extraction of the parasitics from the internal loops such as the extraction of  $R_{N4,N6}$ ,  $L_{N3,N4}$  will require additional test points. Fig 5.5(b) shows the modification of the design with additional test points. Alongside the figure, the relationship between the designated parameters of Fig. 5.5(b) with those of Fig. 5.5(a) are listed.

Fig. 5.5: Simplified schematic of an FHE multi-IC environment with associated series RL parasitics: a) without any additional test point (other than input, output and power supply access) b) with additional test points.

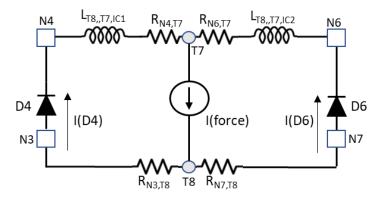

Now, in the Fig. 5.5(b), let us consider the extraction of the series RL parasitics between the test points T7 and T8, by applying the proposed method. Here, the total current  $I_{force}$  (combining both the DC bias and the small signal AC) injected through test points by the measurement setup will divide among the two parallel paths as shown in Fig. 5.6. Considering the series parasitics in both the paths as unknown, the divided currents,  $I_{D4}$  and  $I_{D6}$  will be unknown as well. With the unknown values of current through the individual paths, isolation of their individual impedances is not possible. Hence in such a case, the extraction of the series RL parasitics in the individual paths is not directly achievable with the proposed method. This issue of measurement current leakage through a parallel path is also present for implementing the measurement between the test points T7 and T6, T3 and T1, T8 and T6 as well as T4 and T5 in Fig. 5.5(b).

The transmission lines connected to the IC chips also posses shunt parasitic C (not shown in the Fig. 5.5). The extraction of the shunt parasitic C of a transmission line connected to two ESD diodes at the terminals is straight forward using the presented method. Since for this extraction, the on-chip ESD diodes are reverse biased with zero DC current, the issue of measurement current division through the parallel ESD diodes is not present. For the isolation of the shunt parasitic C from a transmission line bonded to two ESD diodes at the terminals, the parallel C from the two ESD diodes need to be accounted and compensated in the measurement.

The aforementioned challenge for in-circuit extraction of the series RL parasitics using the proposed method can be circumvented by providing jumper pad isolation. Fig. 5.7 shows the jumper pad isolation for extracting the series RL parasitics connected to IC2. Likewise, the series parasitics connected to IC1 can be extracted by connecting the jumper pads J1 and J2 and disconnecting the rest.

Fig. 5.6: Division of measurement current in the parallel paths formed by two ESD diodes.

Fig. 5.7: Schematic of jumper pad isolation for extracting the series RL parasitics connected to IC2.