National Library of Canada

Bibliothèque nationale du Canada

Direction des acquisitions et

des services bibliographiques

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file - Votre reference

Our file Notre reférence

### NOTICE

## AVIS

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

## SPECIFICATION DRIVEN ARCHITECTURAL MODELLING

## **ENVIRONMENT FOR TELECOMMUNICATION**

SYSTEMS SYNTHESIS

ORYAL TANIR

Department of Electrical Engineering

McGill University, Montreal

October 1994

A Thesis submitted to the Faculty of Graduate Studies and Research

in partial fulfilment of the requirements of the degree of

Doctor of Philosophy

© Oryal Tanir 1994

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontano) K1A 0N4

Your file - Votre reférence

Our file Notre référence

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS. L'AUTEUR À ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT À LÀ BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE À LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION. L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

ISBN 0-612-00138-5

#### SPECIFICATION DRIVEN ARCHITECTURAL MODELLING ENVIRONMENT FOR TELECOMMUNICATION SYSTEMS SYNTHESIS

. ·

Oryal Tanir Ph.D. Thesis May 1994 Department of Electrical Engineering

SHORT TITLE:

Architectural modelling environment for telecommunication systems

•

#### Abstract

Design automation has steadily contributed to improvements witnessed in the system design process. Initial applications were to address low level design concerns such as transistor layout and simulation; however the focus of tools has slowly been progressing up the design abstraction scale. The current state-of-the-art provides modelling capabilities at different levels of abstraction, but solutions for synthesis issues at the register-transfer and lower levels are the norm. The proliferation of design description languages at different abstraction levels has prompted the need for standardization (VHDL and Open-Verilog) to promote design migration and re-use.

While design automation has helped in reducing design time-lines and design churn, a major source of design difficulties is just recently being addressed and promise to be the next wave in design automation applicability. The problems arise within the architectural (or system) level of abstraction very early in the design cycle. The recent research in this field attempts to bridge the design process gap between specification and design, and provides a platform for experimenting with hardware and software trade-offs.

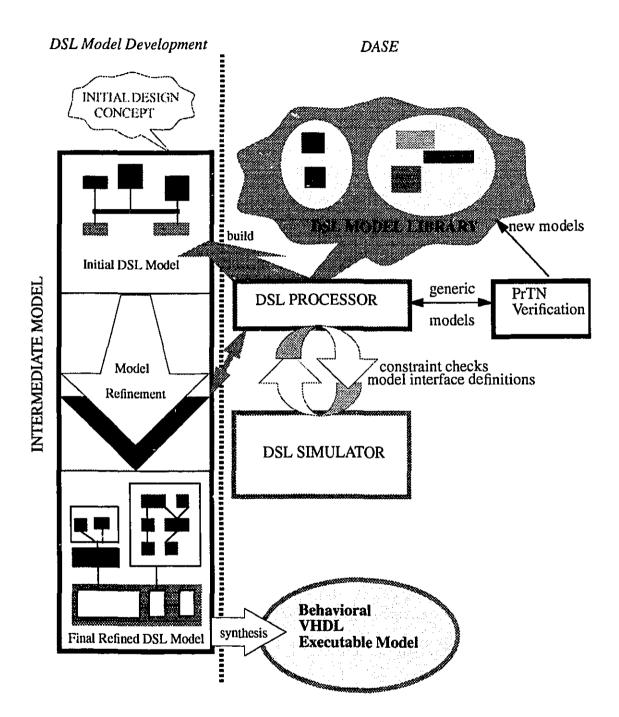

This dissertation studies the requirements for an environment for architectural design. In particular, an environment specific to the telecommunications domain is proposed in order to limit the potentially large design exploration space. An intermediate design language is also introduced to accommodate both high level modelling and synthesis driven by the user and environment. Finally a Design Analysis and Synthesis Environment (DASE) is described to facilitate the architectural level activities. The environment, a proof of concept, provides generic model library, simulation, synthesis and Petri-net analysis support. Realistic design examples are explored, to illustrate architectural design activities with the environment.

i

### Résumé

Les techniques d'autor atisation pour la conception des systèmes digitaux jouent un rôle important dans l'avancement du processus de développement de ces systèmes. Les premiers outils automatiques apparus s'adressaient surtout aux problèmes physiques et géométriques de la conception, c'est-à-dire les questions de bas niveau d'abstraction comme la simulation et l'emplacement des transistors. Cependant l'évolution des outils se marque par une progression du niveau d'abstraction employé par ceux-ci. Présentement les outils les plus sophistiqués offrent un éventail de niveaux d'abstraction variant des transistors jusqu'à la modélisation architecturale en passant par les abstractions au niveau des portes logiques, des transferts entre registres et des algorithmes. Non pas comme les outils de modélisation qui varient sur toute la gamme des niveaux d'abstraction, la grande partie des outils de synthèse se limite actuellement aux niveaux d'abstraction entre ceux des transistors et des transferts entre registres. L'apparition d'une panoplie de langages de spécification sur plusieurs niveaux d'abstraction souligne le besoin d'une standardisation (VHDL et l'Open-Verilog) pour faciliter la réutilisation et la migration des conceptions.

Même si l'automatisation de la conception a déjà produit des résultats pour la réduction de l'intervalle temporel requis pour la conception ainsi que la simplification des étapes itératives nécessitées par les rajustements, une source importante de difficultés retrouvées en conception n'a été adressée que récemment et les solutions sont prometteuses pour la prochaine génération des outils pratiques en conception automatisée. Les problèmes surviennent tôt dans le cycle de conception au niveau d'abstraction architectural. Les recherches récentes en ce domaine tente de faire le lien entre la spécification et la conception tout en permettant une expérimentation sur les conséquences de la division d'un système en une partie logiciel et une partie matérielle. Cette thèse étudie les exigences d'un environnement de conception au niveau architectural. Plus particulièrement, un environnement spécifique aux systèmes de télécommunications est introduit pour amoindrir les espaces de solutions vastes qui sont reliés au problème plus général. De plus un langage intermédiaire est présenté pour la modélisation et la synthèse exercées par l'utilicateur et son environnement. Finalement, un environnement d'analyse et de synthèse (DASE) est exposé pour faciliter les activités au niveau architectural. Cet environment est une preuve du concept émis dans la thèse et il soutient une librairie de modèles génériques, la simulation, la synthèse et l'analyse par réseau de Petri. Des exemples réalistes sont présentés pour démontrer l'efficacité de l'environnement au niveau architectural.

#### Acknowledgments

This dissertation would not have been possible without the support and guidance of many different individuals. First, I wish to thank and acknowledge my academic advisors Vinod K. Agarwal and Pramod C. P. Bhatt for their invaluable contribution to this work and my personal development. Their foresight and consistent entities has been a constant inspiration. Through numerous interactions, Prof. Agarwal has helped forge my reasoning and thinking processes that are essential in tackling current and future problems that I may encounter. Prof. Bhatt has been a relentless, organized and pragmatic mentor who has deeply influenced the way in which I now perceive problems.

I would also like to thank Eric Masson from the MACS laboratory for his help in the french translation of the abstract, as well as numerous information sessions which contributed to the development of my work.

On another level, none the less important, I would like to thank my parents for their love, support and sacrifices that have led me to the point I am at now. I am also indebted to my wife, who has contributed to my development as a person over the last few years. Her constant understanding and love has been a beacon of light to my work and will guide me brightly into the future. I would also like to thank someone very special, my son Dilhan, who's recent appearance to this world has inspired my work.

This work has been generously supported and made possible with the understanding of various people at Bell Canada. I would like to thank Francois Coallier's encouragement, and I would also like to thank Jim Holz and Martine Corriveau-Gougeon for their support and patience during the thesis work.

iv

# **Table of Contents**

| Abstract             | i    |

|----------------------|------|

| Résumé               | ii   |

| Acknowledgments      | iv   |

| Table of Contents    | v    |

| List of Figures      | viii |

| List of Tables       | x    |

| Claim of Originality | xi   |

|                      |      |

| Chapter 1 - Introduction                      | 1  |

|-----------------------------------------------|----|

| 1.1 Perspective                               | 2  |

| 1.2 Rapid system prototyping                  | 5  |

| 1.3 Architectural design and modelling        | 3  |

| 1.4 Dissertation outline                      | 10 |

| Chapter 2 - The Design Specification Language | 12 |

| 2.1 Introduction - Architectural Issues       | 12 |

| 2.1.1 System design                           | 13 |

| 2.1.2 Design execution                        | 14 |

| 2.1.3 Synthesis                               | 15 |

| 2.1.4 An Intermediate language                | 16 |

| 2.2 The DSL modelling primitives              | 18 |

| 2.2.1 Modules: DSL building blocks            | 19 |

| 2.2.2 Model composition                       | 21 |

| 2.2.3 Module behavioral description           | 24 |

| ii. Data manipulation                               |     |

|-----------------------------------------------------|-----|

| 2.2.4 Inheritance and hierarchy                     |     |

| 2.2.5 Module behavior as Predicate/Transition nets  | 36  |

| 2.3 Design development support                      | 43  |

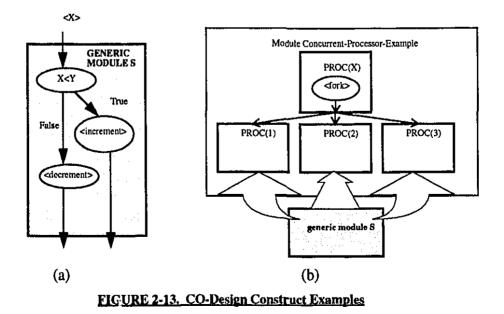

| 2.3.1 Co-design constructs                          | 14  |

| 2.3.2 Model refinement                              | 47  |

| 2.4 DSL modelling example                           | 50  |

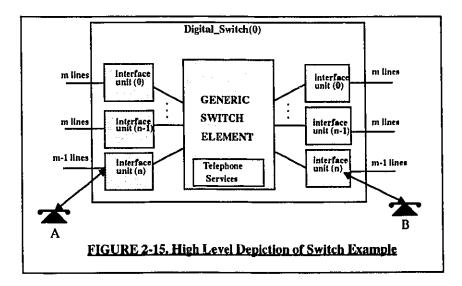

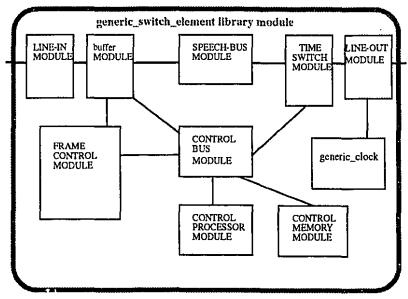

| 2.4.1 The Generic Switch element                    | 53  |

| 2.4.2 The Interface Unit(s):                        | 57  |

| 2.4.3 Software constructs - Telephone Services      | 58  |

| Chapter 3 - Design and Synthesis Environment (DASE) | 62  |

| 3.1 Introduction                                    | 62  |

| 3.2 DSL Processor                                   | 63  |

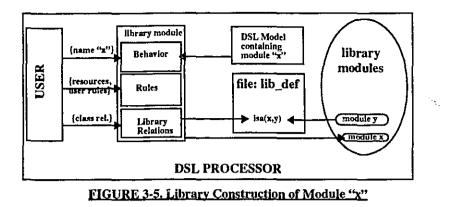

| 3.2.1 Library support                               | 64  |

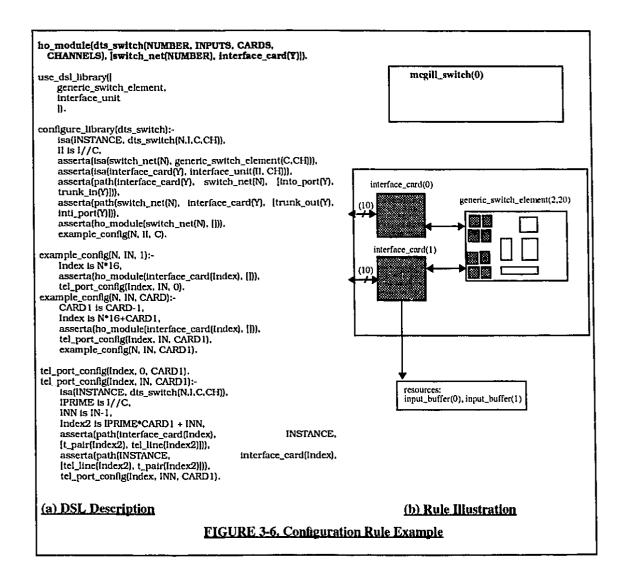

| 3 2.2 DTSS example revisited - library support      | 68  |

| 3.2.3 Modelling support                             | 70  |

| 3.3 Petri-Net analysis                              | 72  |

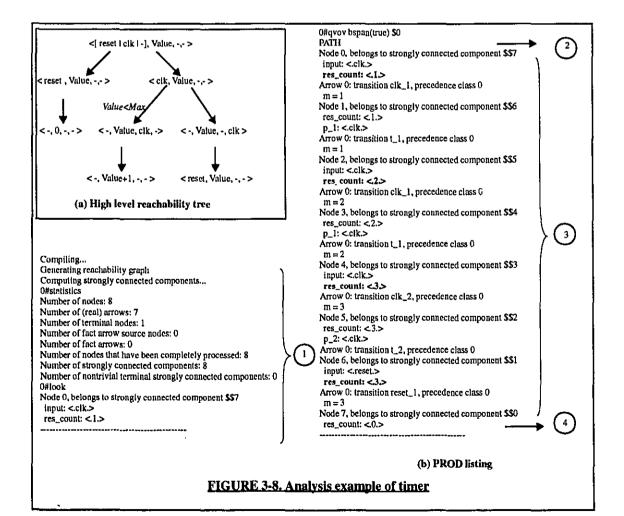

| 3.3.1 Module analysis                               | 72  |

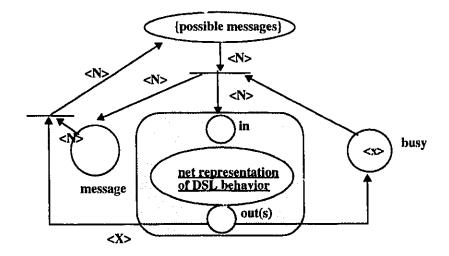

| 3.3.2 Higher-order analysis                         | 75  |

| 3.4 DSL simulator                                   | 75  |

| 3.5 Synthesis                                       | 78  |

| 3.5.1 Pre-synthesis support                         | 78  |

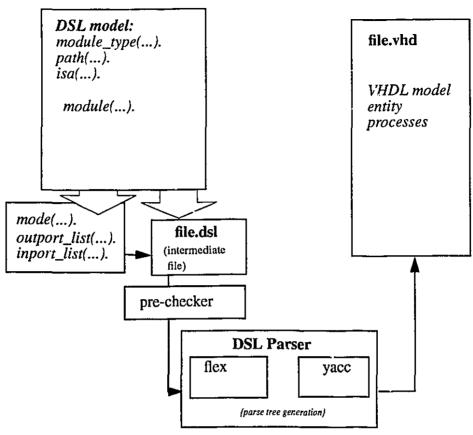

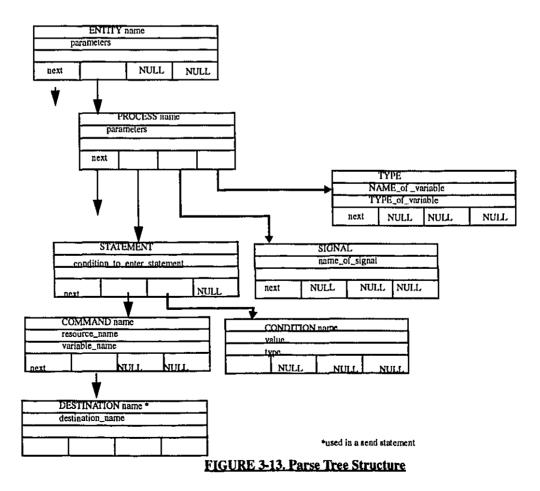

| 3.5.2 DSL to VHDL Parser                            | 82  |

| 3.5.3 DSL to VHDL translation                       | 83  |

| 3.5.4 DTSS example revisited - experimentation      | 89  |

| Chapter 4 - Case Studies                            | 94  |

| 4.1 ATM Switch Design                               | 95  |

| 4.1.1 Introduction                                  | 95  |

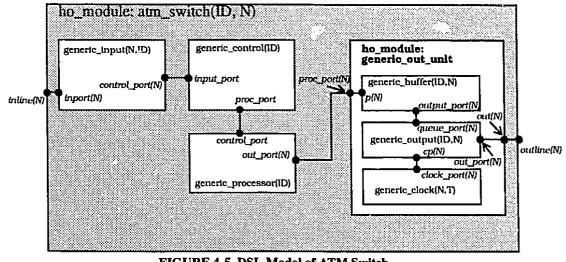

| 4.1.2 The DSL model:                                | 98  |

| 4.1.3 The Input module:                             | 99  |

| 4.1.4 The Control module:                           | 100 |

vi

| 4.1.5 The Processor module:                  | 101 |

|----------------------------------------------|-----|

| 4.1.6 The Output_unit module:                | 102 |

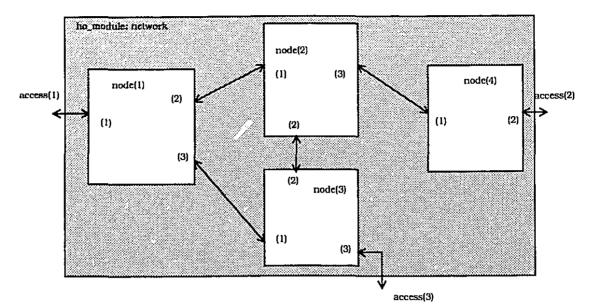

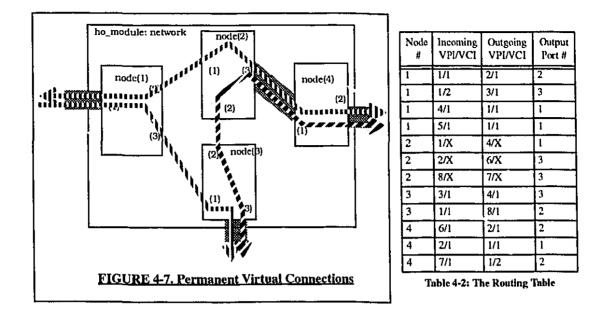

| 4.1.7 Network model - module reuse           | 103 |

| 4.2 Reliable distributed broadcast protocols | 106 |

| 4.2.1 The ABCAST protocol                    | 107 |

| 4.2.2 The CBCAST protocol                    | 114 |

| 4.2.3 The GBCAST protocol                    | 117 |

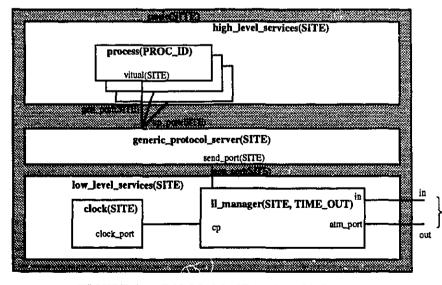

| 4.2.4 Node model                             | 127 |

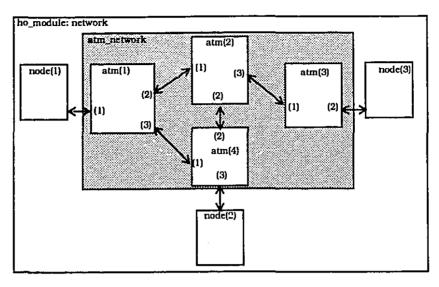

| 4.3 ATM - Broadcast system model             | 130 |

| Chapter 5 - Conclusions | 136 |

|-------------------------|-----|

| References              | 139 |

| Appendices              | 145 |

. . 1

# List of Figures

| FIGURE 1-1. Typical Design Flow for Large Telecommunication Systems2       |

|----------------------------------------------------------------------------|

| FIGURE 1-2. Typical Project Cost Demands                                   |

| FIGURE 1-3. Different Views of Design                                      |

| FIGURE 1-4. Architectural Design Automation Framework 10                   |

| FIGURE 2-1. The Typical Architectural Design Phase                         |

| FIGURE 2-2. DSL Constructs                                                 |

| FIGURE 2-3. Basic states of a module                                       |

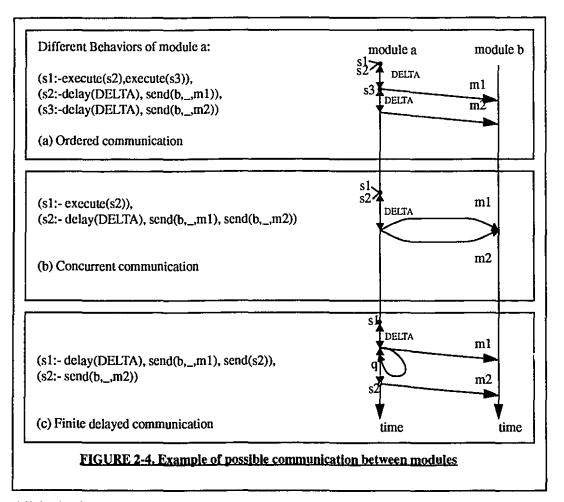

| FIGURE 2-4. Example of possible communication between modules              |

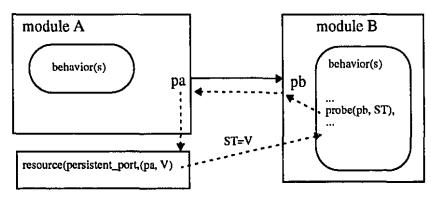

| FIGURE 2-5. Example of Persistent Port                                     |

| FIGURE 2-6. Examples of random number generation                           |

| FIGURE 2-7. Module inheritance and re-use                                  |

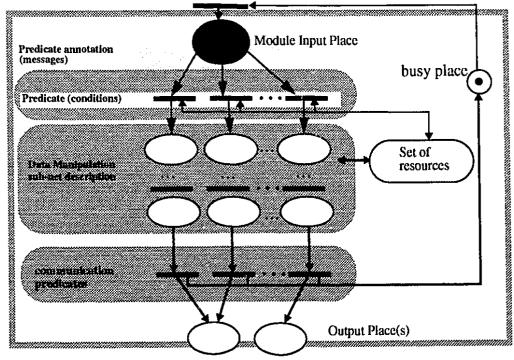

| FIGURE 2-8. Predicate Net Representation of a Module                       |

| FIGURE 2-9. Predicate/Transition Net correspondence with DSL statements 40 |

| FIGURE 2-10. DSL - PrTN translation algorithm                              |

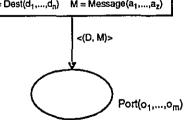

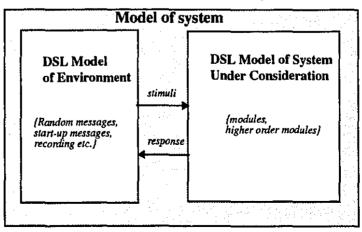

| FIGURE 2-11. PrTN representation of timer example                          |

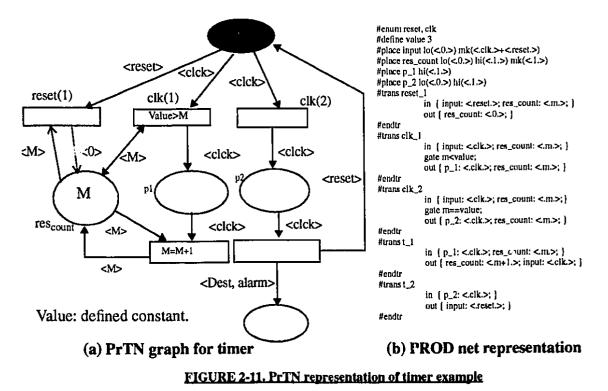

| FIGURE 2-12. Modelling of a System                                         |

| FIGURE 2-13. CO-Design Construct Examples                                  |

| FIGURE 2-14. DSL Model Refinement                                          |

| FIGURE 2-15. High Level Depiction of Switch Example                        |

| FIGURE 2-16. DSL Model of Generic Switch Element                           |

| FIGURE 2-17. DSL Model of the Interface Unit                               |

| FIGURE 3-1. DASE Organization                                              |

| FIGURE 3-2. Model Hierarchy in DSL                                         |

| FIGURE 3-3. Library Module Structure                                       |

|                                                                            |

| FIGURE 3-4. Sample Configuration Rule Structure                 |

|-----------------------------------------------------------------|

| FIGURE 3-5. Library Construction of Module "x"                  |

| FIGURE 3-6. Configuration Rule Example                          |

| FIGURE 3-7. Analysis setup for Module Behavior                  |

| FIGURE 3-8. Analysis example of timer                           |

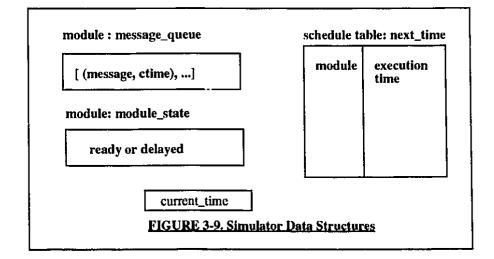

| FIGURE 3-9. Simulator Data Structures                           |

| FIGURE 3-10. Sample Output of List Command                      |

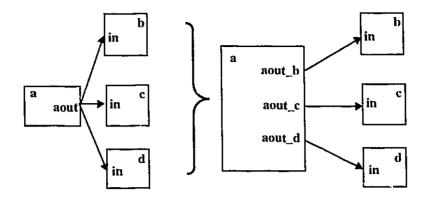

| FIGURE 3-11. Output Port Preparation for Synthesis              |

| FIGURE 3-12. The Synthesis Process                              |

| FIGURE 3-13. Parse Tree Structure                               |

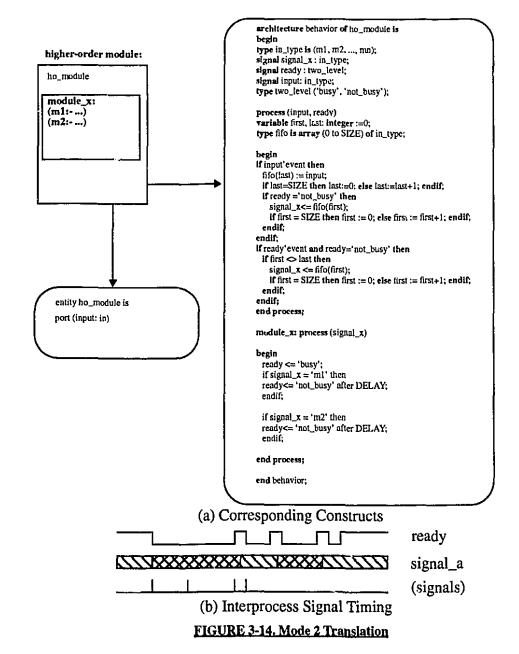

| FIGURE 3-14. Mode 2 Translation                                 |

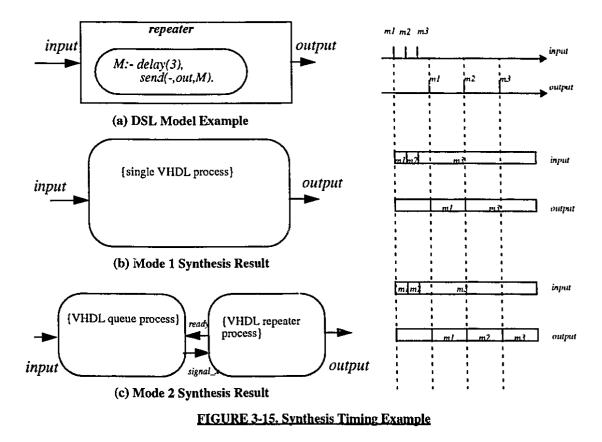

| FIGURE 3-15. Synthesis Timing Example                           |

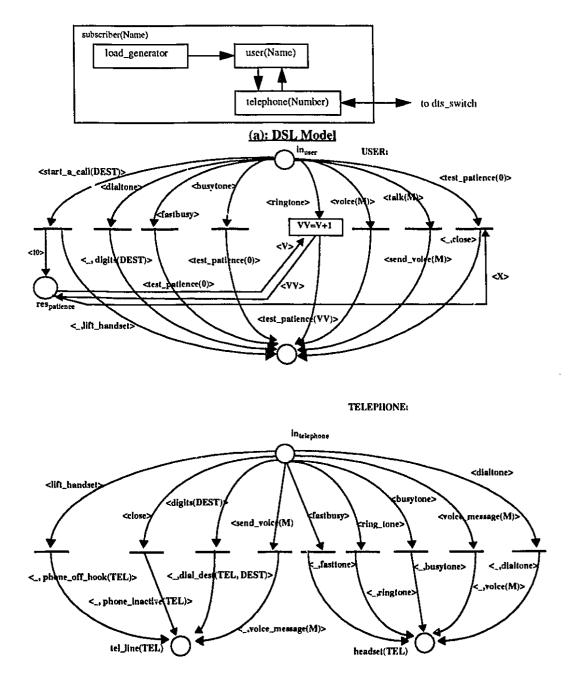

| FIGURE 3-16. Representation of Environment Elements             |

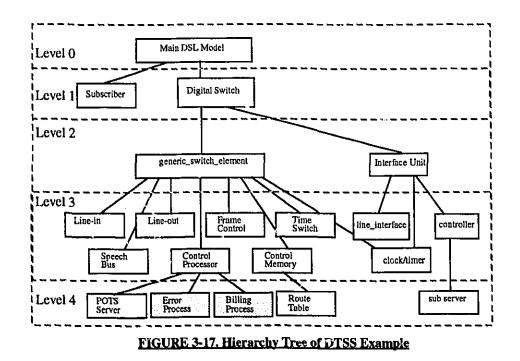

| FIGURE 3-17. Hierarchy Tree of DTSS Example                     |

| FIGURE 3-18. Sample Simulation Output for Call Set-up           |

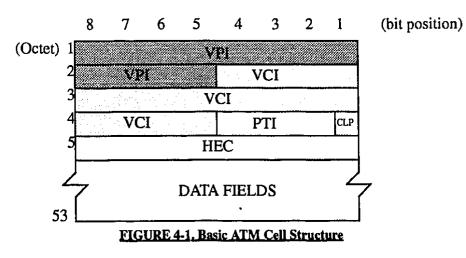

| FIGURE 4-1. Basic ATM Cell Structure                            |

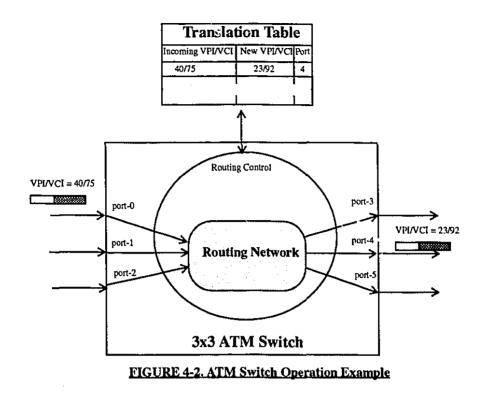

| FIGURE 4-2. ATM Switch Operation Example                        |

| FIGURE 4-3. ATM Modules                                         |

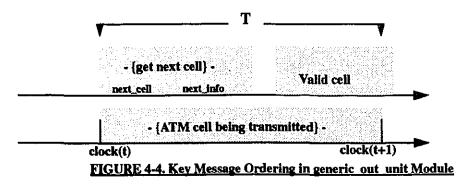

| FIGURE 4-4. Key Message Ordering in generic_out_unit Module 103 |

| FIGURE 4-5. DSL Model of ATM Switch 104                         |

| FIGURE 4-6. ATM Sample Network Configuration                    |

| FIGURE 4-7. Permanent Virtual Connections 106                   |

| FIGURE 4-8. Structural View of Node 107                         |

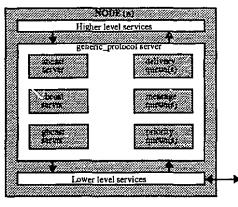

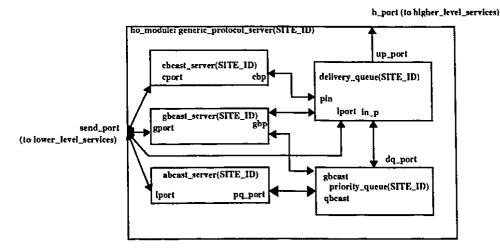

| FIGURE 4-9. DSL Representation of generic_protocol_server       |

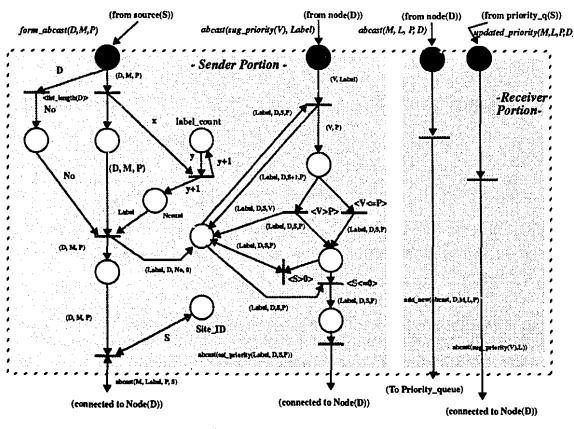

| FIGURE 4-10. PrTN Representation of abcast_server Module        |

| FIGURE 4-11. DSL Model of Broadcast Nodes 127                   |

| FIGURE 4-12. ATM-Broadcast Network Model 131                    |

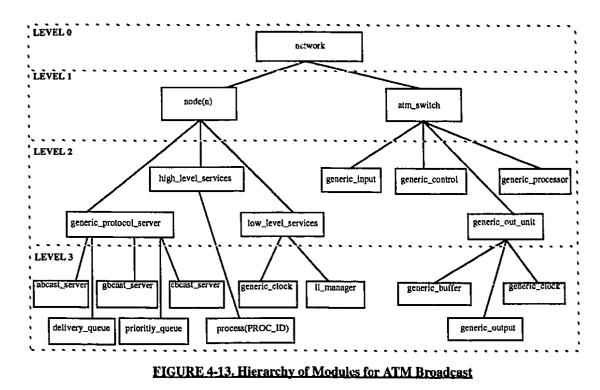

| FIGURE 4-13. Hierarchy of Modules for ATM Broadcast             |

| FIGURE 4-14. Sample Simulation Output                           |

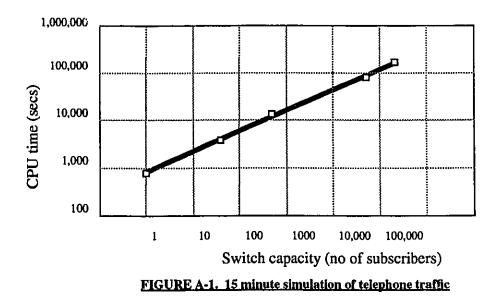

| FIGURE A-1. 15 minute simulation of telephone traffic           |

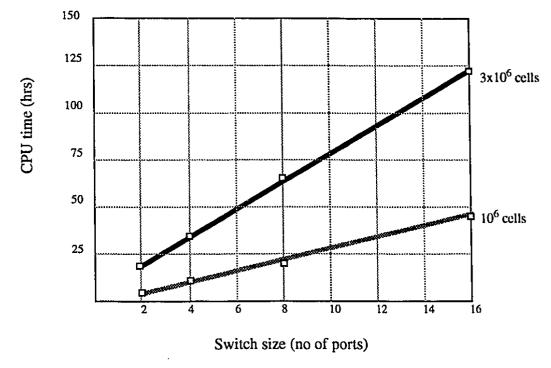

| FIGURE A-2. Simulation of different ATM switch sizes            |

# **List of Tables**

| Table 2-1: | Services Provided to Telephone    | 50  |

|------------|-----------------------------------|-----|

| Table 3-1: | DSL to VHDL Translation Rules     | 85  |

| Table 4-1: | Typical Service Characterizations | 95  |

| Table 4-2: | The Routing Table                 | 106 |

# **Claim of Originality**

The author claims originality for the following contributions of the dissertation.

- In chapters 1 and 3. The proposed environment for design automation of telecommunication systems (DASE) is original as it integrates modelling, analysis and synthesis at the architectural level of abstraction within one seamless framework. All components of DASE have been implemented as a proof of concept. These include: the DSL processor, simulator and synthesizer (DSL-VHDL translator).

- In chapter 2. The intermediate language DSL is an original contribution to architectural modelling. It's capability to permit definition of constructs that can evolve with additional design detail, permitting both abstract representation and synthesis, is novel.

- In chapter 2. The translation rules and algorithm for DSL modules to predicate/transition nets is novel.

- In chapter 2. The representation of software and hardware entities as an indistinguishable module is original. This permits the modelling of such entities before design partitioning.

- In chapter 4 and 2.4. The case studies are extracted from real world problems. In that sense they are not unique, however their representation as DSL modules is novel. Included is a generic module construction example (DTSS) providing substantial model re-use.

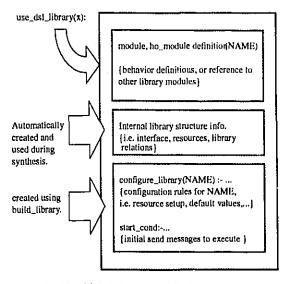

- In chapter 3. The library support description and implementation is original. In particular, the ability of library modules to configure their resources and interfaces to a given model environment permits generic models to be managed by the library.

In chapter 3. The translation algorithms presented for DSL to VHDL (both mode 1 and 2) are original contributions.

# **Chapter 1 - Introduction**

The telecommunication network is the largest manmade machine in the world - composed of an elaborate blend of hardware and software elements. As with other high technology driven fields, the market pressures force the telecommunication industry to produce higher quality products in shorter times. However, the increased complexity of telecommunication systems has made them very difficult to verify. Rapid system prototyping aids can automate different aspect of the design process and help address these concerns. This dissertation presents a rapid prototyping environment to help designers describe, model and explore design tradeoffs at the more abstract architectural level of representation and synthesize in the domain of telecommunication systems. In contrast, traditional environments have focussed on design support at abstractions that are at the register-transfer level or lower.

This chapter is divided into four sections. The first section is a perspective on the product design cycle for telecommunication systems. The section creates a premise for the use of rapid system prototyping and in particular, potential benefits of use early in the design cycle. In the second section an overview of current research in the rapid system prototyping field is presented. A need is defined for an internal architectural level modeling language which possesses synthesis constructs to permit model refinement to register-transfer level representations. The third section introduces such a language as part of a Design Analysis and Synthesis Environment (DASE), the core of this thesis. The final section concludes with an overview of the remainder of the dissertation.

### **1.1 Perspective**

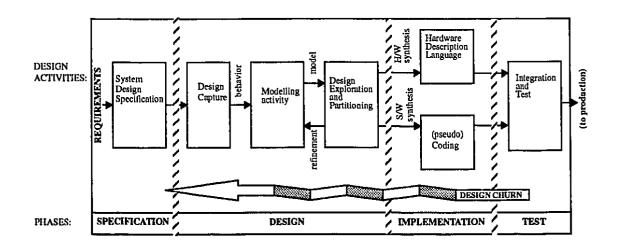

A typical design flow for large system design is represented in figure 1-1. The figure highlights the high level flow of information from design concept to implementation. Four phases of a product's early life-cycle are also shown: The specification, design, implementation and test phase. The phases do not necessarily have well-defined boundaries - for example specification and design may be considered as one phase within a given engineering group. Listed above each phase are the related design activities that contribute to the overall time to complete a phase. The activities represent a typical development process and may differ in each organization, depending upon their maturity level.

Initial system requirements in the specification phase generate design specifications that are input to the design phase. The design phase encompasses many activities related to modelling, design exploration and synthesis. The modelling activity can be composed of model creation and analysis. A design exploration activity can use the model to simulate different scenarios or apply formal verification methods to obtain an acceptable representation of the system. The designer can also partition the design into the respective hardware and software components and, through the use of synthesis tools, generate a prototype (or product) in the implementation phase. For hardware designers, description

languages exist which can represent systems at various level of abstraction. The proliferation of these languages has prompted the need for standardization (IEEE 1076 VHDL and Verilog) [VHDL 87] [Verilog 91] to promote design migration and re-use. Current commercial design environments permit synthesis of hardware described in a subset of VHDL or Verilog, where the initial design is at a register transfer level of abstraction. The software developers may utilize methodologies, such as Shlaer/Mellor [Shlaer 88] or Ward/Mellor [Ward 85], to describe the software constructs in more detail. Each phase in the product lifecycle can potentially flow back to the previous phase(s) indicating potential design revisions. This creates design churn and adds to the overall time to deliver a product.

Intuitively, the time period to create a product (from requirements to test) can be influenced with integrated tools to shorten various phases. The tools can either reduce the duration of activities (such as modeling) within phases or reduce the design churn time. Traditional design approaches have focussed upon such tools. Integrated across several design activities, the tools can form a Rapid System Prototyping (RSP) environment to quickly produce a prototype system - which is a scaled down version of the final product. The prototype is a model of a conceptual system to be fabricated and relies upon the environment to expeditiously produce sound systems.

Although automation is one way to affect design times, further motivation exists to apply this as early as possible in the product life-cycle. The progression of tool capabilities extending toward initial specifications promises to reduce design ambiguities and errors early in the product life-cycle. Such tools must be capable of design capture at increased levels of abstraction to support modelling at the architectural design level. The architectural level is the most abstract design level defined in [Bell 71] where system elements are viewed as communicating processes.

The desire to move tools up the abstraction scale is attractive for several reasons. It is well accepted that design errors uncovered early in the life-cycle are orders of magnitude less expensive to fix than those detected downstream [Boehm 81]. Early error detection can be

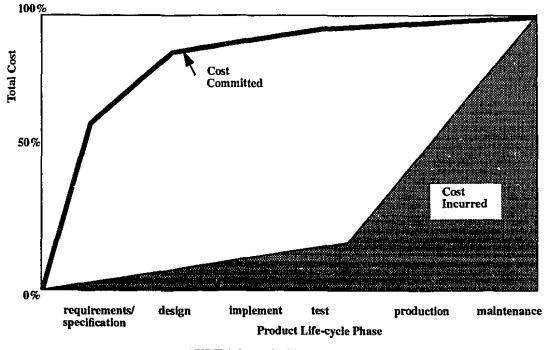

a significant benefit of architectural level automation. Figure 1-2 further emphasizes the impact of design choices made in the early phases. The figure depicts product development in terms of a project within a corporation [Saultz 92] and illustrates the typical resource and personnel effort requirements during a product life-cycle. The horizontal axis depicts the different phases that the product may progress through, whilst the vertical axis indicates a percentage total cost of the project in terms of total effort and resources (equipment, personnel, money). The diagram demonstrates that more than half of the total cost is already committed to the project after the specification phase whereas only 15% of the cost is incurred. It should also be noted that resources freed from previously completed phases may be allocated to other projects. This makes them difficult to access for potential design reworks. Before reaching the production phase, nearly 90% of all the total cost is already committed. As a result, significant design errors detected downstream can negatively impact the resource allocation to the project resulting in cost overruns and delays. Hence the resolution of design ambiguities at this early stage ensures that a project reduces potential design reworks and churn so that the product can be developed with the limited resources available. Hence, the point in time where design aids are used in the products' development, can significantly curb development costs [Hayes 88].

FIGURE 1-2. Typical Project Cost Demands

In summary, an RSP environment applied to architectural level design of large systems can have a significant impact upon the design cycle such as:

i. Shorter design cycle: Generating a quick yet reasonable design from the very conception of the product can weed out poor design decisions from good ones. This reduces expensive design reworks later in the design stage. As a result, the time from system conception to integration is greatly reduced.

ii. Verification of designs: Current designs are verified later in the design stage. At that point, poor architectural decisions can be hidden in the complexity of the complete design details. By synthesis of a system design one obtains a formal representation or model. Algorithms or rules can be applied at this level to test the correctness of the design versus the design specifications. Ideally, synthesis would generate designs that are correct by construction. These lead to less design errors later on in the design cycle.

iii. Solidification of design requirements: Vague or ambiguous design specifications can be identified and corrected during this early stage. Traditionally this has been an area where designers would interpret the specifications. This may not necessarily have been the intent of the specifications [Srivas 90] [Moore 90]. The level of abstraction in the architectural level is closest to the conceptual model a designer would work on, minimizing loss of information.

iv. Procedures for formal design specification: With the advent of system level synthesis tools, formal requirements for design specifications can be defined. Formal specifications following a well-defined structure or methodology is currently lacking in the design community.

v. More design alternatives: If design space exploration can be performed quickly, different design alternatives that may have otherwise not been feasible could also be explored. This helps guide designer in the conceptual creation or evaluation of their designs.

## 1.2 Rapid system prototyping

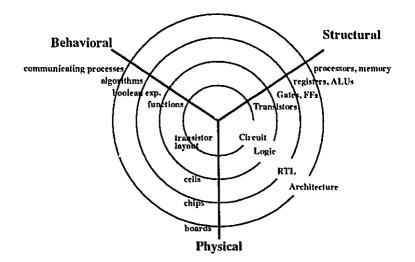

RSP environments provide support for at least three main activities: system design, execution and synthesis. The design support is typically through an internal modelling or specification language that can describe a given system at the desired level of abstraction. The language must also be sufficiently versatile to accommodate the other two key activities. Execution of the design entails the exploration of the design space and further refinements to the design - in the case of architectural modelling, this would also involve design partitioning and co-design. This activity may utilize simulation and formal methods as design tools. Finally a synthesis activity uses the refined design to produce the target product. The source and target model for synthesis reflects the level of synthesis being undertaken in the design. Four different design abstraction levels are commonly depicted as concentric circles radiating from the center of a three-dimensional graph [Gajski 92] as shown in figure 1-3. The intersection of these circles with the three axises represents three possible views of design domains (behavioral, structural and physical) at a given level of abstraction. As the circles move away from the center, the level of representation becomes more abstract. Synthesis can typically occur from a given behavioral representation to a structural one.

Prototyping systems have been developed mostly to address synthesis at register-transfer and lower levels. For example, IDEAS [Kumar 89] is an environment that allows RTL synthesis of designs. CATHEDRAL [Lanneer 91], ISPS [Barbaci 81], and HIS [Bergamaschi 93] are examples of high level synthesis tools. As the lower level design tools have matured, research focussed on architectural level synthesis (transforming a system level design specification into an algorithmic level specification of the behavior) is finally starting to become feasible and is drawing more attention. Some success for reasonably complex systems has been obtained with systems dedicated to specific problem domains such as Digital Signal Processing where the design space is relatively homogeneous [Lanneer 91].

**FIGURE 1-3. Different Views of Design**

With the increased level of abstraction, the design space for a "general purpose" architectural level RSP tool is heavily heterogeneous making it infeasible to derive a model from most initial specifications [Ramming 93]. As a result, it is generally agreed that successful architectural level RSPs will be domain specific (exhibiting a reasonably homogeneous design space) or support a wide variety of specification paradigms.

The demands upon the modelling capabilities of an RSP environment imply that the internal representation or design language employed by the environment can greatly affect the acceptance of the tool within a given domain of application. At the architectural abstraction, design partitioning and co-design are major activities involving both software and hardware designers. Therefore a design language is needed to accommodate both disciplines transparently. In the hardware community, design languages have evolved from logic gate oriented formalisms to those capable of modelling up to the algorithmic abstraction level. However they rarely support architectural level representation (although attempts are being made to extend VHDL into this level [Jerraya 91]). Most hardware description languages are simulation oriented and interleave simulation and modelling semantics - making them difficult for use in synthesis systems. An example is VHDL - where only subsets of the language are applicable for synthesis by commercial tools.

Within the software design area, the trend has been toward a parallel and concurrent programming view. This has made the use of specification paradigms, that support communicating processes, highly amiable. A similar trend can also be observed within the hardware design community, with their desire to find better ways to specify the existing parallelism inherent in hardware. Hence at the architectural level, where software and hardware design concerns are first addressed, a formalism based upon communicating processes appears natural to designers of both disciplines [Koomen 91]. For example, the Specification and Description Language (SDL) [CCITT 88] is based upon communicating processes and is in use in telecommunication software development groups [Klick 91][Jacobson 92]. Although descriptive, the language is undergoing revisions to adopt object-oriented views and a timing model. Another language is Statecharts [Harel 87] that allows description of systems in terms of hierarchical communicating finite state machines expressed in a graphical notation.

Apart from facilitating co-design, there is an added onus on the architectural design language: the output of the internal representation must also be synthesized to the desired target model. This implies that synthesis constructs be part of the internal representation from the onset, with added modelling support to refine the models. Economic considerations also justify the re-use of components in a modelling framework. Such an environment requires a flexible library support system capable of management of models. Typically, abstract models must be capable of being stored, retrieved, configured and organized hierarchically with object oriented capabilities (such as inheritance) to facilitate model construction and re-use.

#### **1.3** Architectural design and modelling

The Design Specification Language (DSL) introduced within this dissertation, is the internal representation language used within the Design Analysis and Synthesis Environment (DASE). The language addresses the representation issues identified in the

preceding section and provides a platform for architectural modelling of telecommunication systems as well as support for synthesis constructs. The restricted domain permits the use of a model library within DASE to aid in the DSL model refinement through simulation. Although described in detail in the dissertation, DSL is internal to the environment and is not necessarily the language that must be used by a user. A language translator can be employed between an existing specification language and DSL - reducing the need for training the user on a new language. The DSL representation can then be used to facilitate the refinement of the design.

DSL is currently implemented in Prolog. This implies that model behavior can be described as a set of clauses, communicating processes or finite state machines - suitable to represent both hardware and software at the architectural level. Prolog also provides a suitable implementation platform for facilitating model refinements during the development of a DSL model. Refinements are carried out under environment support until the model achieves a state where it can be translated to a corresponding VHDL representation.

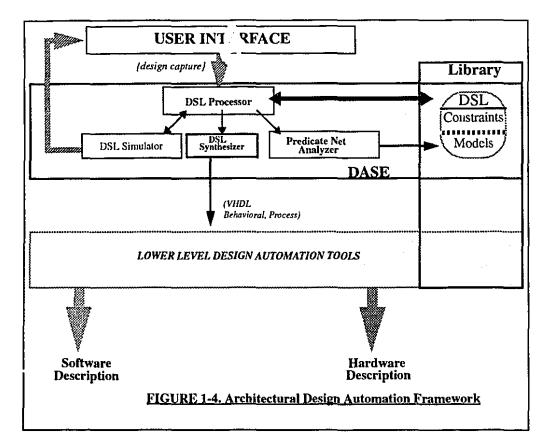

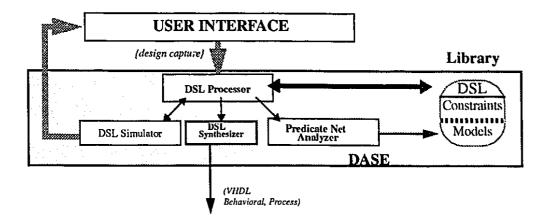

The DASE environment is shown in figure 1-4 as part of an architectural design automation framework being developed by the MACS laboratory [Tanir 92]. The implemented environment provides the necessary support for DSL to bridge the gap between specification and synthesis. Designers can conveniently create architectural models in a top-down fashion, incorporating further detail as required through a model library or during design exploration using simulation.

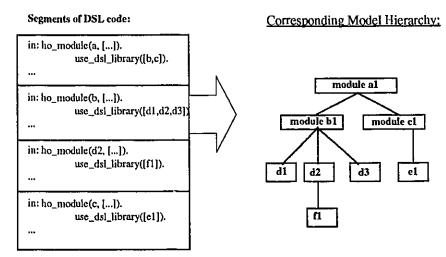

A DSL design is input to the environment through a user interface that is then interpreted by a DSL processor unit. This unit interacts with all other components as well as managing a DSL model library [Tanir 93a]. The model library is organized to allow design exploration within the identified domain of telecommunication system [Tanir 93b] [Tanir 93c] [Tanir 93d]. Models within the library are termed generic and can be re-used and reconfigured with a large degree of freedom. During model execution, the initial DSL model may undergo refinements under the guidance of the DSL processor as necessary model

details are configured through the library.

An interface is defined with a Predicate Transition Net tool to allow the verification of properties of DSL model components. Design exploration is achieved by using a simulator which provides the timing model for DSL and permits observation of events at different levels of detail. Finally a synthesis component allows the DSL models to be synthesized to an RTL behavioral VHDL model. The VHDL model can then be used by lower level design aids to optimize and eventually synthesize to hardware.

### **1.4 Dissertation outline**

This dissertation presents an architectural rapid prototyping environment for telecommunications systems. It does not claim to resolve all design support issues at this level. However this is a good starting point for constructing a potential environment that can be amiable to system design.

The dissertation is divided into five chapters. The following chapter will present the DSL language used by the environment. The chapter will also introduce an example of a design of a digital telephone switch using DSL, demonstrating the modelling capabilities of the language. Chapter 3 will describe the environment support capabilities for automation including simulation and synthesis. The switch example will be used to demonstrate the use of the different elements of DASE to impact model development. Chapter 4 will provide two detailed case studies demonstrating the further capabilities and features of the proposed environment. The examples are based upon the design of an ATM switching network and an implementation of a distributed broadcast protocol executing over the ATM network. Finally, chapter 5 will provide conclusions and suggestions for further extensions to this work.

# **Chapter 2 - The Design Specification Language**

Design languages exist for a myriad of different applications. As opposed to registertransfer / circuit level design, the architectural level blurs the distinction between software and hardware, therefore requires elements common to languages applied in both fields. Furthermore, the design language must be able to facilitate the three RSP activities introduced in chapter 1; systems design, execution and synthesis.

To emphasize the architectural RSP needs for a design language, the first section of this chapter will address language issues for each of the three RSP activities and their implications on architectural design. An overview of the applicable research is also provided for each RSP activity. The overview provides the motivation for the use of an internal design specification language: DSL. The language description is initiated in section 2.2 with an introduction to several modelling constructs. The language is presented in a BNF notation along with a corresponding formal Predicate net model. Section 2.3 introduces the design support related constructs of DSL that aid in architectural design exploration and synthesis. The chapter concludes with an example of a design of a digital telephony switch to illustrate the DSL modelling approach. This example is also utilized in subsequent chapters to reaffirm various features of the DASE environment.

#### 2.1 Introduction - Architectural Issues

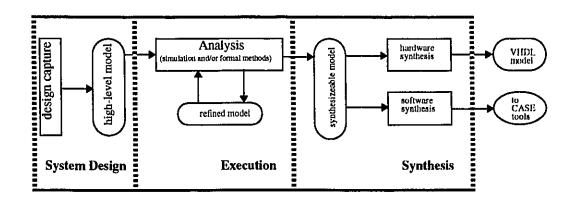

As introduced in the first chapter, RSP can impact the design of a product mainly within the design phase of its life-cycle. The various activities (for the design phase) that are typically

pursued within the context of architectural design are shown in figure 2-1. The three major RSP activities are broken into more detailed ones to highlight the progression of the design. The design flow is from design capture to synthesis. The execution phase may undergo several iterations that are a part of a model refinement exercise. This requires the support of a model library capable of providing refinements to progress the model to a more detailed one which is suitable for synthesis [Booch 91].

#### 2.1.1 System design

The system design activity is generally the starting point within the design phase of a product life-cycle. The activity involves the design capture of specifications into a model which can then be executed. Hence the language requirements at this stage encompass modelling capabilities. A model represents an abstraction of a domain under study and a large body of knowledge exists with respect to this abstraction. In the context of architectural level design, an abstraction is closely linked to specification capture, re-usability, and object-oriented features.

Specification capture has been an evolving discipline in system engineering. Today's system engineer will find many different mechanisms for design capture [Rattray 89]. Of these, an underlying formal basis is desirable to ensure consistent properties of a model

FIGURE 2-1. The Typical Architectural Design Phase

[Jacobson 92]. For example, LOTOS [ISO 88] and SDL utilize a process algebra based formalism [Milner 80] [Hoare 85] and have been developed to specify telecommunication systems. They have gained a considerable degree of attention in the protocol specification field. Hardware oriented formalism, such as HOP [Ganesh 89], exist based upon a functional programming paradigm. More general formalisms such as Petri-Nets (and their extensions) [Peterson 81], Temporal Logic [Moszkowski 85] and queueing networks [Kleinrock 76] are also applied to capture and analyze different aspects of a design. Additional paradigms can be found in [Gupta 92].

Most of the above formalisms have object-oriented capabilities or extensions permitting the modelling of high level communication paradigms. However, model re-use is still a significant shortcoming in this area. Although the theoretical notions exist, in practice the languages appear to require more consideration.

#### 2.1.2 Design execution

After a suitable model is defined, the language must provide support for experimentation and analysis. These execution activities are crucial for a designer to explore a given design space, make appropriate trade-offs and partition the design to different hardware/software configurations. Such activities can be supported through design simulators and formal methods.

Formal methods refer to the application of techniques to prove properties of a system model (such as the existence of deadlocks). Whereas it is highly desirable to use formal analysis in all aspects of design, current methods make it very difficult to formally analyze large systems defined at detailed levels - where possible states in the system are just too large to manage. Additional problems also persist within current formal verification approaches. The formal techniques apply to the verification of a model of the system - not the system itself. The relevance of the verification is always dependant upon how well the model represents all aspects of the system. A considerable effort can be placed upon formally verifying a model, yet the model may not adequately describe the behavior of the system in sufficient detail as to address all design queries. The amount of time to formally verify a complex system is currently unacceptably long.

Simulation is another technique for understanding system behavior where a given model is executed through predefined test scenarios depicting typical (and worst case) operations the system may encounter. For large systems, the scenarios are not exhaustive and provide a limited degree of confidence in the system. Hence the validity of simulation results are heavily dependent upon the assumptions the designer provides. Simulation can be employed in cases where insufficient detail is available for a formal method to be used effectively.

Simulation is widely deployed as a major aid and many general purpose simulators exist such as GPSS [Schriber 74], SLAM-II [Pritsker 86], and SIMSCRIPT [CACI 87] to provide reasonable queuing based system simulation. Other systems such as Designers Workbench also provide analysis support for small systems [Thomas 91]. Large complex simulation that require parallel or distributed processors and techniques like Time-Warp [Jefferson 83] have been utilized in generating speed-ups in most cases [Reed 87]. Petrinet based simulators such as Voltaire [Parent 91] and Loopn [Lakos 91] are also applicable for modelling concurrency.

With the assortment of simulation languages, model re-use becomes very difficult. Model interchange between different tools is generally not available and no standard exists for these languages to permit such an operation - although work is under way within the IEEE standards working groups to alleviate this problem and define requirements for a standard simulation environment [Tanir 94a].

#### 2.1.3 Synthesis

Model execution activities are repeated, refining the model until a final model is derived which meets the designer's expectations and can also be synthesized. Synthesis implies taking a set of behaviors, constraints and goals and generate a suitable structure that can implement the behavior while satisfying the constraints and goals. At the architectural level, synthesis can implicate both hardware and software. Software synthesis at this point requires significant research to integrate high-level specifications towards computer aided software environments and methodologies. The hardware field has seen a proliferation of design languages (along with the IEEE standard VHDL), which can be used as potential target languages for hardware synthesis.

The hardware design community has actively defined many design description languages pre-dating the standard VHDL. For example CASCADE [Borrione 93], CONLAN [Piloty 80], ELLA [Morrison 93] and Verilog [Verilog 92] are samples of languages available. Synthesis has been one of the most important applications of hardware description languages. Initially targeted to circuit level synthesis, tools and methodologies have evolved to synthesize designs from the algorithmic level.

Although highly significant, synthesis has played a secondary role to the design language definition. For example, only restricted subsets of VHDL and Verilog are suitable for synthesis. These languages have powerful constructs for simulation of hardware, however (due in part to their low level modelling features) automatic refinement of models has proven to be elusive at the very high levels of abstraction used within architectural level of design.

#### 2.1.4 An Intermediate language

System designers have typically utilized many different languages to capture relevant aspects of a system. It is also generally agreed that one "unified" language or methodology is not capable of representing systems for all levels of design abstraction. It is also observed in the milieu that as the abstraction level increases, the analysis methods used in tools shift from a simulation oriented one to a formal basis [Ward 85]. Hence it is difficult to use an existing paradigm to address RSP concerns across a broad range of activities at the architectural level of design.

The issues reflected in the previous sections indicate an applicability of different paradigms at different stages of design. Consequently a possible solution to support architectural design is an intermediate language within the RSP to obtain the various input and output forms. Such a language would support inputs in the form of specifications (possibly defined in an existing specification language) and output a lower level synthesized design in a usable representation (such as VHDL). The intermediate language would also require modelling capabilities for high level description to facilitate specification input, as well as design exploration and synthesis constructs to produce the outputs.

This dissertation presents the Design Specification Language (DSL) as a potential intermediate language for architectural RSP within the DASE environment. The language primarily captures specifications by use of abstractions and is free from rigid disciplines of simulator oriented hardware languages. In addition, since the language must bridge the abstraction gap between high level system design notions to low level hardware descriptors, it must also possess the flexibility of re-defining and altering its model interfaces during design exploration.

This function of the language helped motivate the use of Prolog as the language for implementation of DSL. It may be noted that DSL is a meta-language in the sense that it is based upon Logic programming semantics, utilizing built-in predicates to define its own constructs. A major contribution of DSL is in its ability to capture high level specifications within a re-usable model and, with the aid of a library support system, refine the model to a state where it can be synthesized into an executable lower level representation language such as VHDL (refer to appendix D for DSL and VHDL differences).

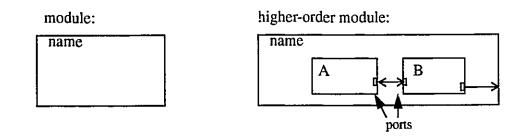

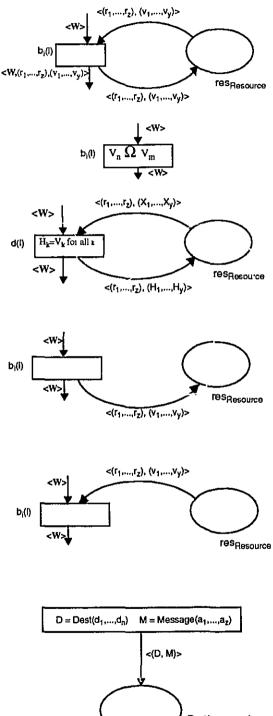

DSL borrows the typeless notation to provide facilities for powerful abstraction and data manipulation. The language is designed to have a corresponding structural graphical correspondence. The graphical representations of the main constructs are shown in figure 2-2 and will be further elaborated in the upcoming sections. The language description is partitioned in two sections: sections 2.2 and 2.3. The first describes the modelling primitives (for design capture) of the language whereas the second section focuses upon

the experimentation and synthesis constructs to support design development.

## 2.2 The DSL modelling primitives

This subsection presents the DSL modelling primitives required for design capture, addressing the design input concerns. The basic syntax is presented in BNF notation with some regular expression shorthand to ease legibility. The shorthand symbols are:

- {} : encloses comments.

- \* : any number of sequences of the preceding expression.

- + : at least one or more sequences of a preceding expression.

- []: Sets of characters enclosed by square brackets imply that any one of the characters within the brackets are applicable. A range of possibilities is indicated with "-" within square brackets: i.e. [0-9a-z] indicates any single digit and lower case alphabet characters can be satisfied.

Characters in bold fonts are reserved words in DSL.

DSL adheres to Prolog's naming and syntax conventions. Hence the language primitives are defined by:

```

integer ::= [0-9][0-9]^*

real ::= integer \cdot integer

number ::= integer | real | float

rel_op ::= <|>|==|=<|>=

num_op ::= +|-|*|///| is

operator ::= rel_op | num_op | |

literal ::= [a-z][a-z0-9]^*

atom ::= literal | number

list ::= [ member* ] | [ member | member ]

member ::= <null> | dsl_name | variable | number

variable ::= [A-Z][A-Za-z0-9]^* | [_][A-Za-z0-9]^*

```

```

dsl_name ::= literal ( parameter<sup>+</sup> )

| literal

parameter ::= atom

| variable

```

A DSL program consists of a combination of DSL constructs defined as: dsl\_program ::= dsl\_model\_constructs<sup>+</sup> dsl\_experiment\_constructs<sup>\*</sup>

The *dsl\_model\_constructs* constitute the applicable commands that are used for model description and the *dsl\_experiment\_constructs* represent the commands used for experimentation and synthesis support. The former is defined below whereas the latter is visited in section 2.2.

dsl\_model\_constructs ::= module\_definition | resource\_definition

ho\_module\_definition inheritance\_definition persistent\_port\_definition path\_declaration

Each one of the possible DSL modelling primitives are described in the following subsections.

#### 2.2.1 Modules: DSL building blocks

The basic construct within DSL is a modular object oriented design entity called *module* - the primitive building block of the language (refer to figure 2-2 for the graphical depiction). These are constructs that possess a name, a set of possible behaviors, and resources. Modules communicate with one another through messages - which trigger a defined behavior within destination modules.

The basic DSL notation for a module is: module\_definition ::= module( dsl\_name ,[ behavior<sup>\*</sup>]). where dsl\_name within the module\_definition represents a unique identification of a mod-

ule and is used extensively by DSL to resolve communication issues within a model. *behavior* is a list of different behavior(s) the module is capable of interpreting. The behavior(s) of the module represent the actions undertaken by the module when an event occurs. The occurrence of an event implies the arrival of a message from one module to the other module - which then attempts to execute the behavior associated with the message.

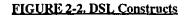

Modules operate within three conceptual states: *ready*, *busy* and *delayed* which are depicted in figure 2-3. *Ready*, indicates that the module can process a message. *Busy* implies that it is currently processing a message, and a *delayed* state indicates that a module is suspended (delayed) and will commence processing the message after a time period

FIGURE 2-3. Basic states of a module

(t). When a module is in the *busy* or *delayed* state, arriving messages are queued within an input message queue to be processed in turn by the module. Message execution within a module in the *busy* state is atomic. However, pre-defined interrupt messages (described later) can interrupt the execution process if the module is in a *delayed* state.

The description of behavior and the respective possible actions will be deferred until a later section on behavioral description. However, some actions may use or manipulate data structures local to a module to model states, local variables etc. Such local data structures are facilitated within DSL with the *resource* statement. Adhering to the Prolog philosophy, local variables can also be lists - facilitating the management of structures such as arrays and queues. DSL commands to manipulate resources are defined in the data manipulation section later in the chapter. A resource is (a predicate) of the form:

resource\_definition ::= resource( dsl\_name , dsl\_name , values ). values ::= variable | atom | ( values<sup>+</sup> ) | list

For example, a statement such as resource( $module_name$ , res(P1,...Pn), (V1,...,Vn)) describes a resource local to a module (with name  $module_name$ ). The resource (res) may be parameterized as above, and defines a set of variables (Vn) where Vn can be any Prolog element such as integer, lists and strings. The applicable operations that can be performed upon resources will be described within the behavioral modeling section.

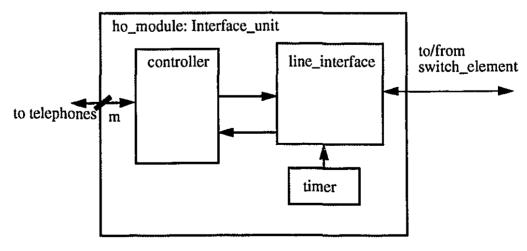

#### 2.2.2 Model composition

DSL permits composition of modules into higher-order (HO) modules. Connections between modules are established through the use of "ports". A port is a virtual communication channel between the module and its environment. The language deduces direction from information flow across ports. Port specification is not typed so that different levels of abstract information may flow through the same port.

The graphical representation of a higher order module (refer to figure 2-2) is similar to that of a module. The underlying subtlety is that higher order modules encapsulate a set of modules and define specified interconnections. Hence using these constructs, more complex (higher-order) models can be composed from simpler ones. Higher order modules possess no pre-defined behavior of their own - however the interaction of modules composed through such a higher order module establish the underlying behavior. A DSL model defines a higher order module in the form

ho\_module\_definition ::= ho\_module( ho\_name , module\_list ).

ho\_name ::= dsl\_name

module\_list ::= [ dsl\_name\*]

The *ho\_name* is a *dsl\_name* (Prolog structure) and the *module\_list* is a list of modules composed within the higher order module. Composition is not restricted just to modules, but is also applicable to higher-order modules. Hence members of a higher-order module may contain other higher-order modules as well as modules - however when referring to the constituent members of a given higher-order module, the term *module* will be used loosely to imply both. The interconnection of the constituent modules is achieved through a path declaration:

path\_declaration ::= path( module\_x , module\_y ,[ port\_x , port\_y ]).

module\_x ::= dsl\_name | variable

module\_y ::= dsl\_name | variable

port\_x ::= dsl\_name | variable

port\_y ::= dsl\_name | variable

port\_x and port\_y are port names used to define a communication path between the two named modules. The connection implies a default direction from port\_x to port\_y - hence module\_x is the name of a source module. The port names can also be written as variables, in which case no direction or specific port name is defined. In this case, the existence (or need) for a communication path between the two modules is conveyed to the environment. The details of the connection manipulation by the environment will be elaborated in chapter 3.

Port names can also be associated to local variables - which result in *persistent* ports. Such a port is maintained as a resource within a module under the reserved resource name: persistent\_port:

# persistent\_port\_definition::= resource(persistent\_port, ( port\_name , values )). port\_name::= dsl\_name

This capability permits ports to assume a value or state dictated by the most recent message that was sent from the port. Hence a state or value is said to persist on the port (similar to the behavior of a wire in hardware design). Persistent ports are suitable to model lower level constructs such as wires and buses where the value of the entity (voltage levels or high impedance) may be of concern. This also permits different levels of representation to coincide within a given model.

Since paths are equivalent to Prolog predicates, unification and variable instantiation can provide compact notation in defining some structures. For example, in the case of symmetrical connections, the path statement can be used concisely to define all module interconnections with a statement such as:

path(proc(X), mem(X), [port(X), mem\_port(X)]).

This statement will interconnect all modules named proc(X) and mem(X) through their respective ports (i.e. proc(1) will connect to mem(1) etc.).

Relations can also be established through the port definitions. For example,

$path(proc(X), mem(X+1), [port(X), mem_port(X+1)]),$

indicates that proc(1) is connected to mem(2) through their respective ports. The path statements help define the necessary interconnections desired by the designer.

### 2.2.3 Module behavioral description

A module's list of behaviors describe all possible actions that may be undertaken by the module in response to a given message. The resultant behavior of a higher-order module composed of modules is a result of all possible interactions between the modules. Module behavior is a procedural description of actions which, within satisfaction of a set of constraints, may consist of:

i). communication initiation with other modules or internally,

ii). modification of resources or temporary variables associated with the module, and

iii). timing related directives.

More precisely, the form is defined as:

Behaviors can be viewed as a set of Prolog clauses where each behavior can also be multiple clauses - applicable under different conditions. The head of a clause consists of the behavior name ( $b_name$ ) - a unary or N position predicate. The body is a set of conditions and actions which are compound sub-goals of the clause. It should also be noted that DSL conditions are Prolog sub-goals to be satisfied, and the actions are sub-goals that are always satisfied, resulting in some desired side effects (such as message generation and resource manipulation).

For a given behavior, a set of conditions can be evaluated before further execution of the behavior is attempted. This facilitates the description of if-then-else type constructs as well as supporting state oriented behavioral description. The behavior selection may be based on built-in DSL predicates or Prolog conditional operators. Formally conditions are

described as:

The *check\_res* statement is used to test for a resource ( $dsl_name$ ) or its value. For example, *check\_res*(*counter*, X) will return the value (X) of a resource named *counter*. Alternatively *check\_res*(*Caller*, *telephone*(5551211)) could return the name of a subscriber (*Caller*) associated with a specific telephone number. In either case, if there is no match the predicate will fail and another satisfaction of the behavior will be attempted.

DSL uses the Prolog programming style for resolving ambiguities and testing conditions. Hence a declarative and procedural style of writing behavior is possible. A behavior with the name b(X) for example is an unconditional attempt to satisfy the behavior statements. However, code in the form:

b(1):-c1, a1. b(wait):-c2, a2. b(X):-c3, a3.

are multiple behavior names that DSL will attempt to satisfy for the arguments "1", "wait" or otherwise. In addition a set of conditions c1, c2 and c3 determine if the action (a1, a2, a3) for the given clause will be attempted (since actions are always true - the conditions act as guards against erroneously selecting actions).

Having introduced the basic behavioral styles, the possible actions available within a behavioral description are described below:

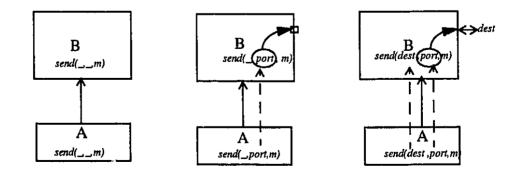

#### i. Communication primitives

Communication is the main means for changing state within DSL models. The main action that invokes communication is the *send* statement. It's format is as follows:

destination ::= dsl\_name | variable | list / [\*]

port ::= dsl\_name | variable

message ::= dsl\_name

The first form of the *send* statement has three possible parameters: *destination*, *port* and *message*. The *destination* is the name of a destination module. The destination may be a multiple one, expressed as a list such as [a, b]. In this example the respective module will send the same message to modules a and b. An empty list [] will result in a message sent to the first module capable of interpreting the message. The destination can also be an [\*] which has the potential effect of sending a message to all modules capable of processing the message.

The *port* is the name of a communication port of the source module that is identified as the desired source point from which the communication is to initiate. The *message* is the name of the message to be sent. This can be any valid behavior name that is comprehensible by the receiving module.

The second form of send is for internal messages, and is essentially a short notation of the first - where the destination is the source module.

The first two fields for the first form of *send* are optional, which provides extreme flexibility in the way communication can be initiated. The possible actions are described by the following cases (parameters are undefined unless they begin with a lower case letter):

Case 1. All parameters are given: send(dest, port, message).

- Action: *message* will be sent from the source module to the module with a name *dest*, through the source's port called *port*. A special case is when the destination is [\*]. In this situation, the message will be sent to all modules that are connected to the source's port. This is equivalent to a broadcast message in some systems.

- Case 2. No destination name is given: send(-, port, message).

- Action: *message* will be sent to the first module capable of executing it and is connected directly or indirectly to the source module's *port*.

- Case 3. No port name is given: send(dest,\_, message).

- Action: Essentially the same as case1. Ports are not necessary for communication, only for synthesis later in the process. This type of send statements will generate pseudo-communication channels within the DSL environment which can be used by a synthesizer to construct data paths.

- Case 4. No port or destination given: send(\_,\_, message).

- Action: This is similar to case 2. however any module that can interpret the message will be selected. This mode is an aggressive one and should be used with caution - since the communication paths are determined solely by the environment and not by the designer.

A message generated through a send statement will always be placed in the input (message) queue of the destination module. Hence there is an implicit causality associated with message communication.

The other communication primitive available is the *execute* statement. This statement is similar to an internal send statement, however it by-passes the input message queue of the module. Consequently the message will be processed immediately.

By using the send and execute primitives, different message ordering can be implicitly

established. Figure 2-4 presents some possible message combinations. The figure assumes that two modules (A and B) are communicating. In particular, module A is actively sending two types of messages and the diagram indicates the relative times at which the messages arrive at module B's input queue.

The first case shown is the effect of multiple execute and send statements. Three sets of behavior, each with a discrete delay of *delta* is assumed. The first behavior (s1) generates two execute statements for behaviors s2 and s3. The latter two behaviors use send statements to generate messages m1 and m2 respectively. The destination module will receive the two messages *delta* time units apart in the order they are sent.

The second case depicts a concurrent transmission of messages m1 and m2. This is achieved through behavior s2. Although message m1 is listed before m2 within the

behavior, the order of arrival at the destination is non-deterministic.

The final case shows the use of a combination of send statements. Behavior s1 sends message m1 after a *delta* delay, then sends an internal message (s2). The latter will be queued and processed after a finite queueing time (q) and s2 will generate message m2. The effect of the internal send is to schedule m2 after m1, but with an unknown delay (q) between the two.

## ii. Data manipulation

Data manipulation actions can change values of internal variables defined by resources or temporary variables local to a module. The actions can utilize any valid arithmetic and list operators defined in Prolog. In addition, data values used within resources can also be manipulated within defined DSL statements. The following comprises a description of all the actions.

*data\_manipulation* ::= *set\_definition*

| create\_definition

| remove\_definition

| probe\_definition

| arithmetic

| built\_ins

set\_definition ::= set\_res( dsl\_name, values )

create\_definition ::= create( resource\_definition )

remove\_definition ::= remove( resource\_definition )

probe\_definition ::= probe( dsl\_name , variable )

arithmetic ::= variable operator expression

expression ::= number

( expression operator expression )

The first four data manipulation statements are those related to resources. The *set\_res* statement permits the assignment of a value to the respective resource. For example, *set\_res(state, busy)* will associate *busy* to the resource *state*. The *create* action will instantiate a new resource. Hence, *create(buffer(1), empty)* will define a new resource named buffer(1) with contents *empty*. The *remove* action will remove (or disassociate) a resource from a module. For example, *remove(buffer(1), full)* will remove the named resource whose contents are defined to be full. It should be noted that this operation has the effect of removing a defined fact from the underlying Prolog database. Hence if there are multiple entries with the same resource name, only the oldest and least used copy of the resource will be removed.

The probe action is reserved for resources defined as persistent ports. The invocation of the action results in the variable to be bound to a local value maintained for the persistent port. The statement permits a module connected to another module's persistent port to obtain the state of the port. The nuance of this representation is illustrated in figure 2-5. In the example, module (A) has a persistent port (pa) connected to another module (B). The implication is that there is a resource associated with module A, containing a state variable V. At some point in module B's behavior, a probe statement is encountered. The effect of this is to access the value V from the persistent port and bind it to the local variable ST. Persistent ports can only be read by other modules. Changing the value can only be performed by the module associated with the port (in this case module A).

The probe statement is useful for depicting lower level interactions. For example consider

FIGURE 2-5. Example of Persistent Port

a model of a processor connected to a bus and memory. Assume that significantly detailed operations of the memory is of interest and the processor model generates messages representing a state of the bus (for example read\_memory could imply a "0010" bit level on the control bus). If the bus were to be represented by a bus with a persistent port, the processor could affect the state of the port with its messages to the bus, and the memory module could utilize probe statements to latch onto the required values.

There are additional behavior predicates defined with DSL to help within the manipulation of data and creation of standard data structures such as queues. These are summarized below:

#### built\_ins::=

| not( dsl_name )                            | : negation of X (as in Prolog).                      |  |

|--------------------------------------------|------------------------------------------------------|--|

| member(literal, list)                      | : true if literal is a member of the list List.      |  |

| remove_element( literal , list , new_list) | : Removes the first occurrence of an element         |  |

|                                            | literal within the list list and returns the         |  |

|                                            | sub-list new_list.                                   |  |

| list_length(list, variable )               | : determines the number of elements variable         |  |

|                                            | within the list <i>list</i> .                        |  |

| append(atom, list, new_list)               | : appends atom to the end of the list List to create |  |

|                                            | the new_list (as in Prolog).                         |  |

| iqsort( list, new_list)                    | : a quick-sort algorithm for the sorting of the      |  |

|                                            | elements of List. Elements are sorted in             |  |

|                                            | ascending order an placed in new_list.               |  |

| l last_list( list, atom)                   | : identifies the last element atom from a queue      |  |

|                                            | named list.                                          |  |

## iii. Timing

Up until now timing has not been elaborated upon. Timing behavior in DSL is encountered through simulation, hence there is no explicit formal timing model within the language semantics. However module delays can be simulated with the use of the *delay*  action. A *delay* action suspends the module for a given period of simulated time. After the elapsed time, the next consecutive action in the behavior is executed. The syntax of this action is:

The action can utilize a numeric value explicitly, or implicitly (as an unbound variable). The former simply implies the use of a numeric parameter such as delay(5.4) which will suspend further operation within a module for 5.4 time units. The latter is a case where a variable may be dependent upon an externally passed parameter - for example (Behavior\_name(T1):- delay(T1),.). Here T1 is passed to the module as a delay parameter.

The *call\_c* action can also be used in conjunction with a delay action to access random variables from a C library. Two examples of how random messages may be generated are given in figure 2-6. The first uses a list (RANDIREST) to select a random number (a table look up scheme could also have been used), suspend operation for that time period, generate a message (stimuli) and then access the next number. This structure has the advantage of replicating the same sequence of random numbers for every modelling scenario. The second example is that of a random number generation. A system call to C is used to access a random number generator (rand) and obtain a number between 0 and 1

| <pre>module(random, [   (start([]):-         print('Finished random messages')),   (start([RANDOMIREST]):-         delay(RANDOM),         send(_,_,stimuli),         send(start(REST))) ]).</pre> | <pre>module(random, [  (start:-</pre> |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| (a) Predetermined random numbers                                                                                                                                                                  | (b) Utilizing function calls          |  |

| FIGURE 2-6. Examples of random number generation                                                                                                                                                  |                                       |  |

(which is scaled afterwards). A Prolog predicate call\_c(Function, X) is used to pass the random value from C to Prolog (some implementations of Prolog have predefined random value predicates that can be used directly). The value is then used to delay and generate a message as before. The difference here is that each simulation scenario will utilize different random values and the timing delays will not be identical.

Timing issues for modules are resolved through scheduling during simulation. The execution of a communication statement within a module's behavior is handled directly through the simulator after the destination name has been resolved (chapter 3 describes the simulator data structures in detail). Similarly, a delay statement will cause a re-schedule of the current message being processed, until a specified time period. During this period no further messages may be processed (the module's delayed state). There is however one exception to this rule. A default class of messages are defined within DSL to act as interrupt messages. These are defined through the statement:

#### interrupt\_declaration ::= isa( message ,dsl\_interrupt).

In this declaration, *message* is defined as a priority message. If a module is in a delayed state, such a message will cause the simulator to immediately remove the current message, and schedule it after the priority message. After completion of the priority message, the interrupted message will once again delay the module. In the busy state, messages cannot be interrupted. A priority message can be interrupted by another priority message (there is no notion of levels of priority).

## 2.2.4 Inheritance and hierarchy

DSL permits modules to inherit behavior (and structure) from other modules (and higher order modules) - which expedites model re-use. A module that is written to be sufficiently generic and can be re-used by different parents is termed a *generic* module. By convention, such module names are superseded with a "generic\_" to stress this property.

33