# Three-Dimension Integrated Circuit Design and Through-Silicon Via Characterization

Shudong Lin

Department of Electrical & Computer Engineering McGill University Montreal, Canada

August 2012

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Master of Engineering.

© 2012 Shudong Lin

#### Abstract

This thesis presents the design of a prototype chip of a 3D IC made in the Tezzaron Process. As this work is the first of its kind at a Canadian University, this thesis is focused on the characterization of the one of the key components of this technology, that being, the Through-Silicon Via or TSV for short. The TSV is modeled as a lumpedequivalent RC circuit, whereby embedded instruments have been constructed to measure the R and the C of a TSV. Specifically, a Kelvin four-point probe has been devised to measure the series resistance of a TSV and several versions of a parasitic capacitance meter has been constructed to measure the effective shunt capacitance of a TSV. One approach to measuring the shunt capacitance makes use of a frequency-based approach whereby the frequency of two ring oscillators, one loaded by a TSV, the other left opened, are measured and used to predicted the capacitive load difference. The other approach makes use of a charge-based method whereby the average difference in the amount of charged transferred in any one charging cycle is measured using a current meter. To ease the measurement control and data capture, an analog JTAG test bus was developed and used to extract the test data in a manner that is compatible with that used in the semiconductor industry. An extension to the JTAG analog boundary scan cell is proposed that reduces the silicon overhead required when used in a 3D-IC.

#### Résumé

Cette thèse presente la conception d'une puce prototype d'un IC 3D réalisés dans le processus Tezzaron. Comme ce travail est le premier de son genre dans une université canadienne, cette thèse se concentre sur la caractérisation de l'un des éléments clés de cette technologie, que l'être, la Via biais de silicium ou TSV pour faire court. Le TSV est modélisée comme un circuit RC équivalent-localisées, dans lequel les instruments embarqués ont été construits pour mesurer la R et C d'un TSV. Plus précisément, un Kelvin quatre points de sonde a été conçue pour mesurer la résistance série de quelques versions TSV et plusieurs d'in compteur de capacité parasite a été construit pour mesurer la capacité shunt efficace d'un TSV. Une méthode pour mesurer la capacité de shunt utilise une approche de fréquence basée sur la fréquence selon laquelle des deux oscillateurs en anneau, l'un chargé par un TSV, l'autre gauche ouverte, sont mesurées et utilisées pour prédire la différence de charge capacitif. L'autre approche faire usage d'une méthode de charge à base de sorte que la différence moyenne dans la quantité de particules chargées transféré cours d'un cycle de charge est mesurée à l'aide d'un courantomètre. Pour faciliter le contrôle de mesure et de capture de données, un bus de test analogique JTAG a été développé et utilisé pour extraire les données d'essai d'une manière qui est compatible avec celle utilisée dans l'industrie des semi-conducteurs. Une extension de la cellule JTAG boundary scan analogique est proposé qui permet de réduire les frais généraux du silicium nécessaire lorsqu'il est utilisé dans un 3D-IC.

### Acknowledgments

Foremost, I would like to express my sincere gratitude to my supervisor Professor Gordon W. Roberts for the continuous support and guidance of my master study and research, and also for his enthusiasm, vision, immense knowledge and patience. It was him who lead me into the analog and mixed-signal design and test world, and offered me the great opportunity to work with.

Besides my supervisor, I would like to thank McGill University and CMC Microsystems for the opportunity to design the first prototype 3D chip in Canada. I am grateful to Hsu L.Ho, Jim J. Quinn and Hudson An from CMC Microsystems, for the technical support in the design and fabrication process.

My sincere thanks also goes to my dear colleagues in Integrated Microsystems Lab (IML) for their corporation and help. Especially Marco Macedo, George Gal, Omar Abdelfattah, Tsung-Yen Tsai, Azhar Ahmed Chowdhury, Pufeng Chen, Kun Chuai, Sadok Aouini, Mohammad Ali Bakhshian and Ali Ameri.

Last but not the least, I also would like to thank my parents Daoguang Lin and Weimin Chen for their love, support and sacrifices for me.

# Contents

| 1 | Inti | Introduction 1 |                                                        |    |  |  |  |

|---|------|----------------|--------------------------------------------------------|----|--|--|--|

|   | 1.1  | 3D IC          |                                                        | 3  |  |  |  |

|   |      | 1.1.1 SoC a    | and SiP                                                | 3  |  |  |  |

|   |      | 1.1.2 3D-IC    | C with TSV                                             | 7  |  |  |  |

|   | 1.2  | 3D Integration | on Process                                             | 9  |  |  |  |

|   | 1.3  | Tezzaron 3D-   | -IC Technology Description                             | 10 |  |  |  |

|   | 1.4  | Test Challeng  | ges                                                    | 10 |  |  |  |

|   | 1.5  | Thesis Overv   | riew                                                   | 12 |  |  |  |

| 2 | TS   | V Characteri   | zation                                                 | 14 |  |  |  |

|   | 2.1  | TSV Resistar   | nce Measurement                                        | 15 |  |  |  |

|   | 2.2  | Measuring Ca   | apacitor Mismatch                                      | 15 |  |  |  |

|   |      | 2.2.1 Ramp     | p-Based Capacitor Mismatch Measurement                 | 16 |  |  |  |

|   |      | 2.2.2 Frequ    | ency-Based Capacitor Mismatch Measurement              | 17 |  |  |  |

|   | 2.3  | Frequency-Ba   | ased TSV Capacitor Measurement                         | 18 |  |  |  |

|   |      | 2.3.1 TSV      | Capacitor Formation                                    | 21 |  |  |  |

|   |      | 2.3.2 FBCN     | M Using The Single-VCO Approach                        | 21 |  |  |  |

|   |      | 2.3.3 FBCN     | M Using The Two-VCO Approach                           | 31 |  |  |  |

|   |      | 2.3.4 Exter    | nal Access To Frequency-Based Capacitance Measurements | 32 |  |  |  |

|   |      | 2.3.5 Exam     | ple Simulation and Discussion                          | 37 |  |  |  |

|   | 2.4  | Charge-Based   | d TSV Capacitor Measurement                            | 41 |  |  |  |

|   |      | 2.4.1 CBCN     | M Principle                                            | 41 |  |  |  |

|   |      | 2.4.2 CBCN     | M Method Circuit Design                                | 43 |  |  |  |

|   |      | 2.4.3 Exam     | ple Simulation and Discussion                          | 45 |  |  |  |

Contents

|   | 2.5 | Conclu | ısion                                           | 50 |

|---|-----|--------|-------------------------------------------------|----|

| 3 | 3D- | IC Tes | et Access and DfT Techniques                    | 51 |

|   | 3.1 | Digita | l Logic Gates Designs                           | 53 |

|   |     | 3.1.1  | Inverter Design                                 | 53 |

|   |     | 3.1.2  | NAND Gate Design                                | 53 |

|   |     | 3.1.3  | NOR Gate Design                                 | 55 |

|   |     | 3.1.4  | True-Single-Phase Clock D-Type Flip-Flop Design | 55 |

|   |     | 3.1.5  | MUX Design                                      | 56 |

|   | 3.2 | Suppo  | rt Circuits For FBCM                            | 58 |

|   |     | 3.2.1  | Frequency-to-Digital Converter                  | 58 |

|   |     | 3.2.2  | PISO Shift Register                             | 61 |

|   | 3.3 | Bound  | lary Scan                                       | 61 |

|   |     | 3.3.1  | Boundary Scan Cell                              | 61 |

|   |     | 3.3.2  | JTAG Architecture                               | 62 |

|   |     | 3.3.3  | JTAG Interconnect Test Example                  | 64 |

|   | 3.4 | Analog | g and Mixed-Signal Boundary Scan                | 66 |

|   |     | 3.4.1  | IEEE 1149.4 Architecture                        | 66 |

|   |     | 3.4.2  | Analog Boundary Module Architecture             | 66 |

|   |     | 3.4.3  | Analog ABM Switch Design                        | 70 |

|   | 3.5 | On-Ch  | nip Test Tier for 3D IC                         | 71 |

|   |     | 3.5.1  | Internal Analog Scan                            | 72 |

|   |     | 3.5.2  | Modified Analog ABM For 3D Testing              | 74 |

|   | 3.6 | Simula | ation and Discussion                            | 77 |

|   |     | 3.6.1  | Analog Switch Characterization                  | 77 |

|   |     | 3.6.2  | ABMs with Analog Switch                         | 77 |

|   | 3.7 | Conclu | asion                                           | 82 |

| 4 | Chi | p Over | rview Using The Tezzaron 3D Technology          | 85 |

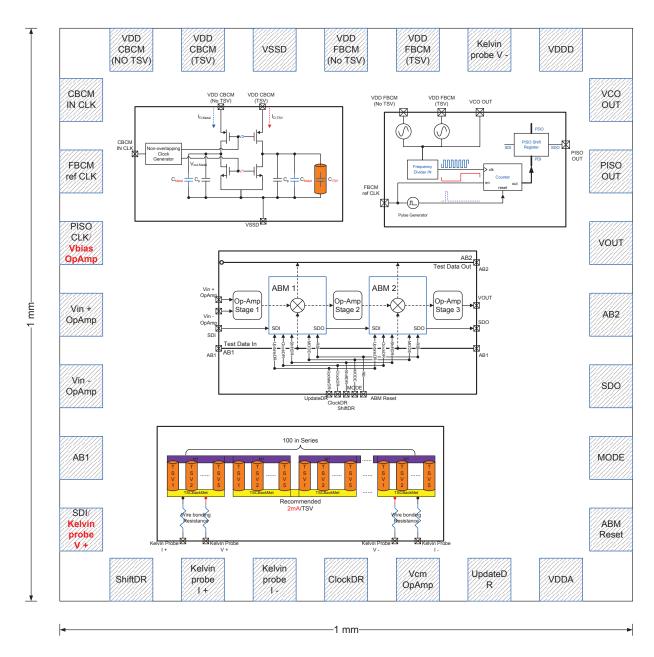

|   | 4.1 | Chip ( | Overview                                        | 85 |

|   |     | 4.1.1  | WTOP Tier Layout                                | 87 |

|   |     | 4.1.2  | WBOTTOM Tier Layout                             | 88 |

|   | 4.2 | User F | Pad/Pin Connections                             | 94 |

|             | •   |

|-------------|-----|

| Contents    | VI  |

| 0 011101100 | · - |

|              | 4.3   | Conclusion                                                | 94  |

|--------------|-------|-----------------------------------------------------------|-----|

| 5            | Exp   | perimental Setup And Measured Results                     | 96  |

|              | 5.1   | Reason For Chip Delay                                     | 96  |

|              | 5.2   | Experimental Setups                                       | 97  |

|              |       | 5.2.1 TSV Resistance Measurement                          | 97  |

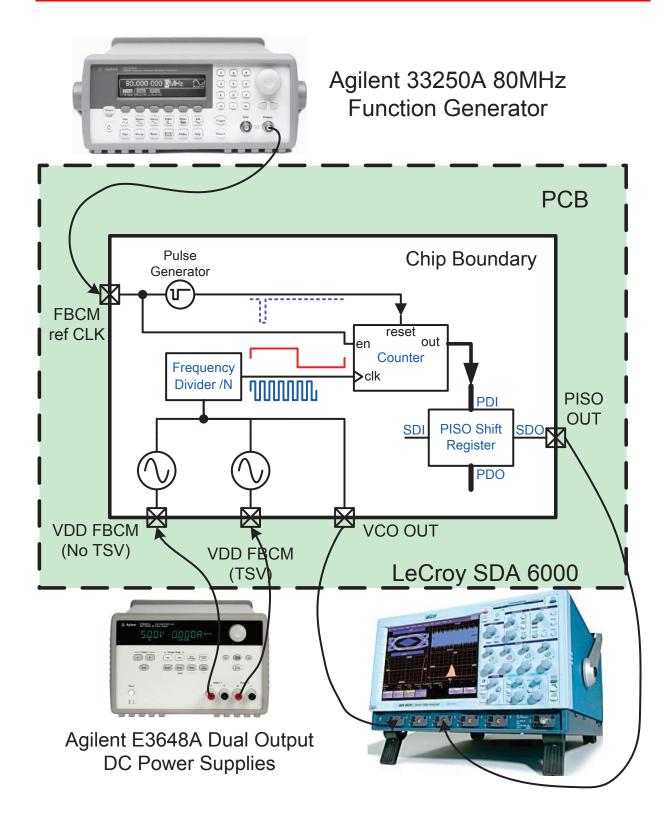

|              |       | 5.2.2 Frequency-Based TSV Capacitance Measurement         | 97  |

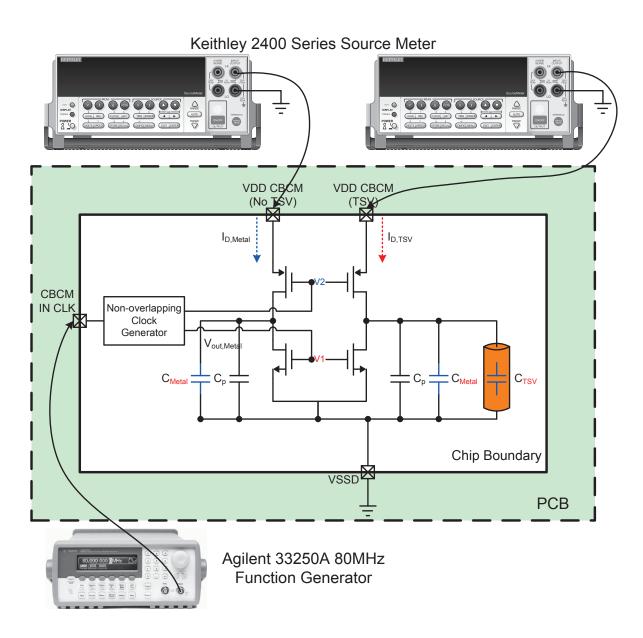

|              |       | 5.2.3 Charge-Based TSV Capacitance Measurement            | 99  |

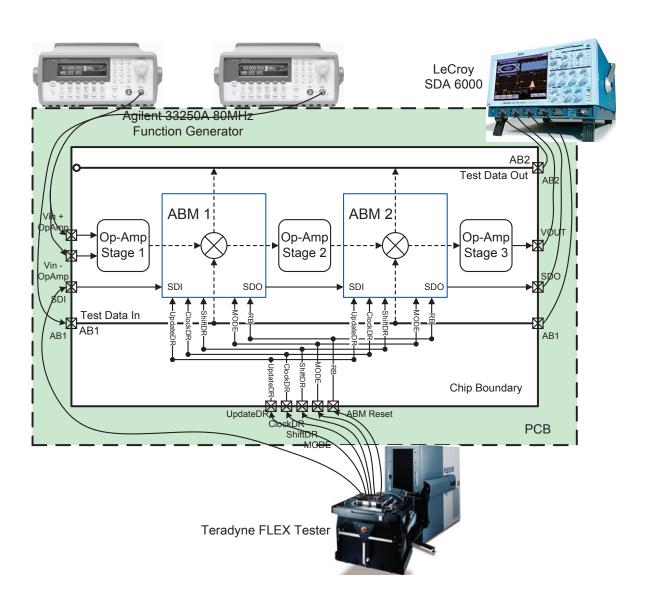

|              |       | 5.2.4 Analog Boundary Scan Module Measurement             | 99  |

|              | 5.3   | Summary                                                   | 99  |

| 6            | Con   | aclusion                                                  | 103 |

|              | 6.1   | Thesis Summary                                            | 104 |

|              | 6.2   | Future Work                                               | 104 |

| $\mathbf{A}$ | Test  | Bench Schematics                                          | 106 |

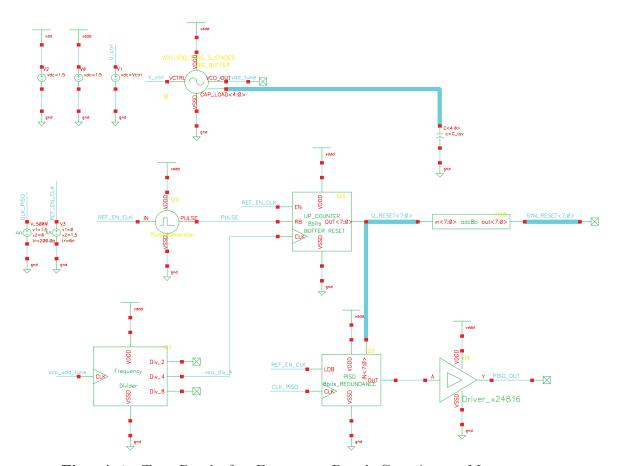

|              | A.1   | Frequency-Based Capacitance Measurement Method Test Bench | 106 |

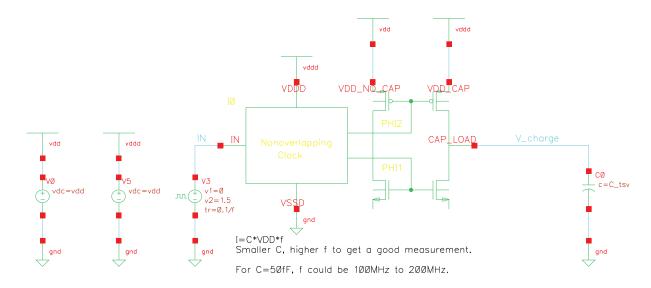

|              | A.2   | Charged-Based Capacitance Measurement Method Test Bench   | 106 |

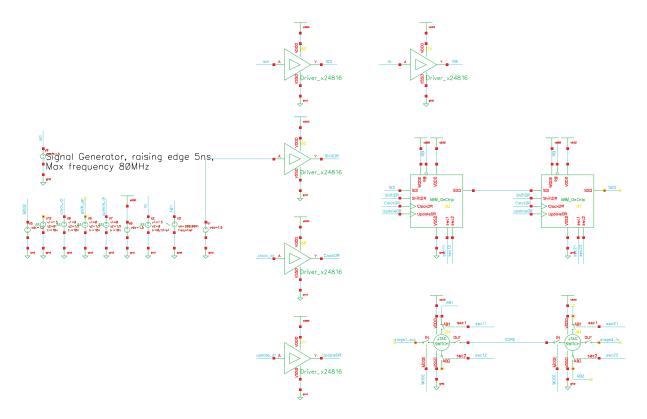

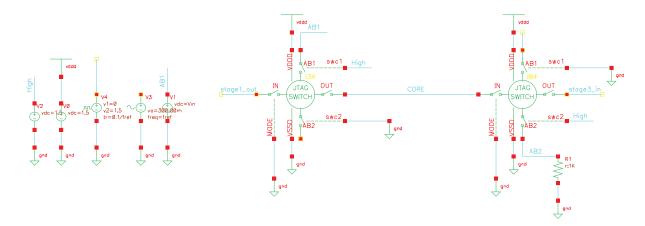

|              | A.3   | Analog Boundary Scan Module Test Bench                    | 106 |

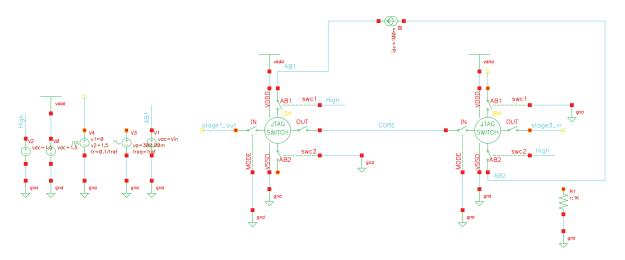

|              | A.4   | ABM Switch DC Analysis Test Bench                         | 109 |

|              | A.5   | ABM Switch AC Analysis Test Bench                         | 109 |

| Re           | efere | nces                                                      | 110 |

# List of Figures

| 1.1  | Moore's Law 2011                                                             | 2  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | The Virtuous Circle of the Semiconductor Industry                            | 3  |

| 1.3  | The Trends In Electronic Miniaturization                                     | 4  |

| 1.4  | Virtuous Circle with More than Moore                                         | 5  |

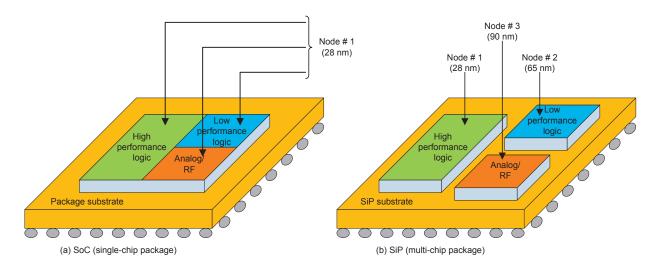

| 1.5  | SoC VS SiP                                                                   | 6  |

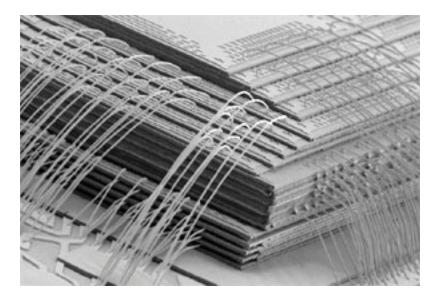

| 1.6  | 24 Stacked Dies In A Single Package By Amkor Technology                      | 6  |

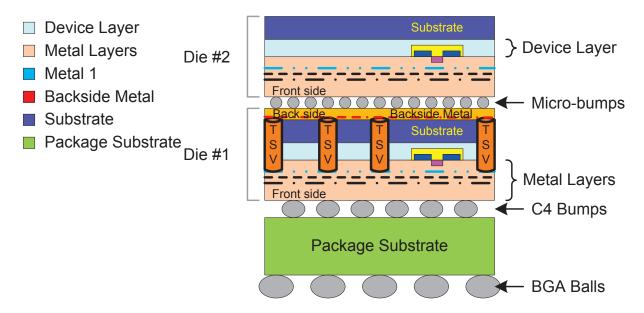

| 1.7  | Back-to-face bonding 3D-IC                                                   | 7  |

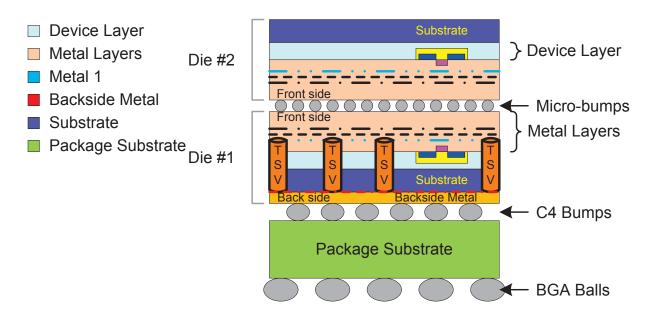

| 1.8  | Face-to-face bonding 3D-IC                                                   | 8  |

| 1.9  | The Metal Layers and TSVS in Teazzaron 3D-IC technology                      | 11 |

| 2.1  | TSV Lumped RC Model                                                          | 14 |

| 2.2  | Kelvin Probe for TSV Resistance Measurement                                  | 16 |

| 2.3  | Ramp-Based Capacitor Measurement Approach                                    | 17 |

| 2.4  | Frequency-Based Capacitor Mismatch Measurement Approach                      | 18 |

| 2.5  | Five-Stage VDD-Tuned Ring Oscillator                                         | 18 |

| 2.6  | VCO Output Frequency Vs. Load Capacitance $f_{out} = g(C_L)$ Nonlinear Curve | 20 |

| 2.7  | Two-VCO Frequency-Based Capacitance Measurement Flow Chart                   | 22 |

| 2.8  | TSV Formation With Grounded Dummy Structures                                 | 23 |

| 2.9  | Single-VCO FBCM with Programmable-TSV Loads                                  | 23 |

| 2.10 | A Voltage Buffer For Driving A Ring Oscillator Signal Off-Chip               | 24 |

| 2.11 | Analog Switch                                                                | 25 |

| 2.12 | Single-VCO-Based with Switches In ON State Comparison                        | 27 |

| 2.13 | Single-VCO-Based with Switches In ON State Comparison Details                | 28 |

| 2.14 | Single-VCO-Based with Switches In OFF State Comparison                       | 29 |

| 2.15 | Single-VCO-Based with Switches In OFF State Comparison Details               | 30 |

List of Figures viii

| 2.16 Parasitics Analysis Of The TEE-Connected Switch                      |

|---------------------------------------------------------------------------|

| 2.17 Two VCOs FBCM Approach Without Analog Switches                       |

| 2.18 Frequency Count VS Load Capacitance                                  |

| 2.19 Frequency-To-Digital Converter With External Access                  |

| 2.20 FBCM Counter and PISO Output Waveform Details                        |

| 2.21 FBCM Counter and PISO Output Two Full Cycle Waveform                 |

| 2.22 Load Capacitance VS Frequency Count                                  |

| 2.23 Timing Diagram Corresponding To An Unloaded And Loaded VCO Output. 4 |

| 2.24 Charge-Based Capacitance Measurement                                 |

| 2.25 Averaged Difference Current VS TSV Capacitance                       |

| 2.26 Non-Overlapping Clock Signal Generator Schematic                     |

| 2.27 A Spectre Simulation Of The Non-Overlapping Clock Signals            |

| 2.28 Averaged Difference Current VS. Frequency                            |

| 2.29 Time Domain Charging and Discharging Current Comparision             |

| 2.30 Averaged Difference Current VS. Supply Voltage                       |

| 3.1 Wafer Probe                                                           |

| 3.2 Wafer Probe of 2D VS 3D                                               |

| 3.3 NAND Gate                                                             |

| 3.4 NOR Gate                                                              |

| 3.5 TSPC DFF Without Reset                                                |

| 3.6 TSPC DFF with Reset                                                   |

| 3.7 Multiplexer                                                           |

| 3.8 Frequency-To-Digital Converter                                        |

| 3.9 Frequency Divider                                                     |

| 3.10 Up Counter                                                           |

| 3.11 Pulse Generator                                                      |

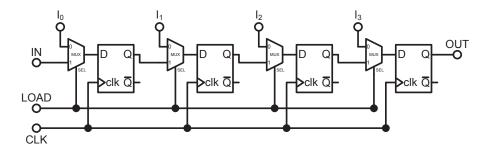

| 3.12 Parallel-In Serial-Out Shift Register                                |

| 3.13 Boundary Scan Cell Architecture                                      |

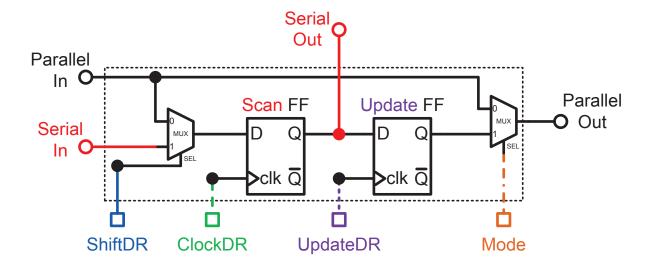

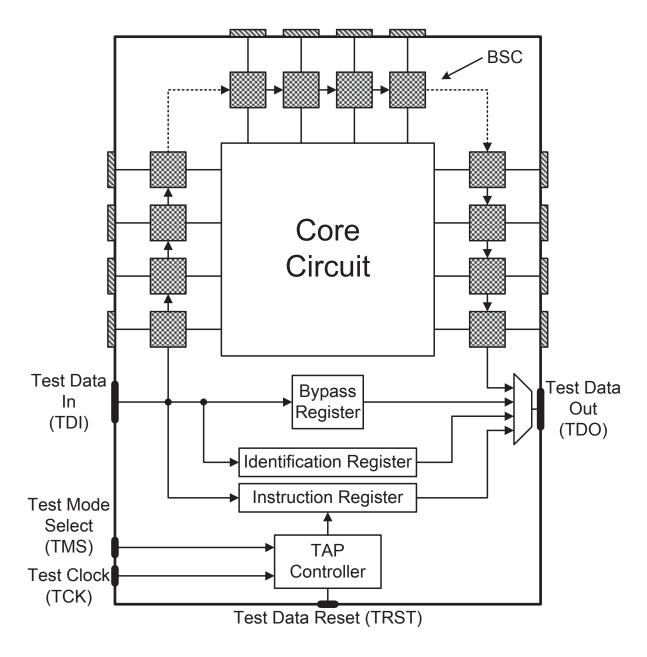

| 3.14 IEEE 1149.1 Boundary Scan Architecture                               |

| 3.15 Boundary Scan Architecture with Chip-to-Chip Interconnect Testing 6  |

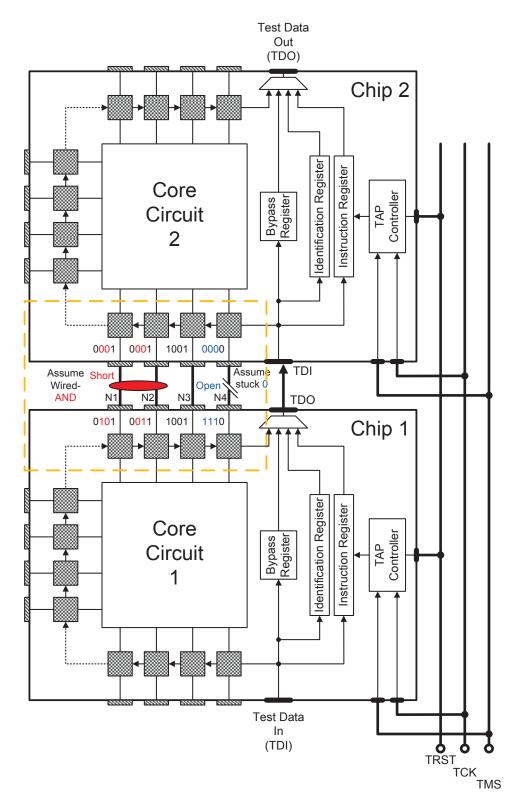

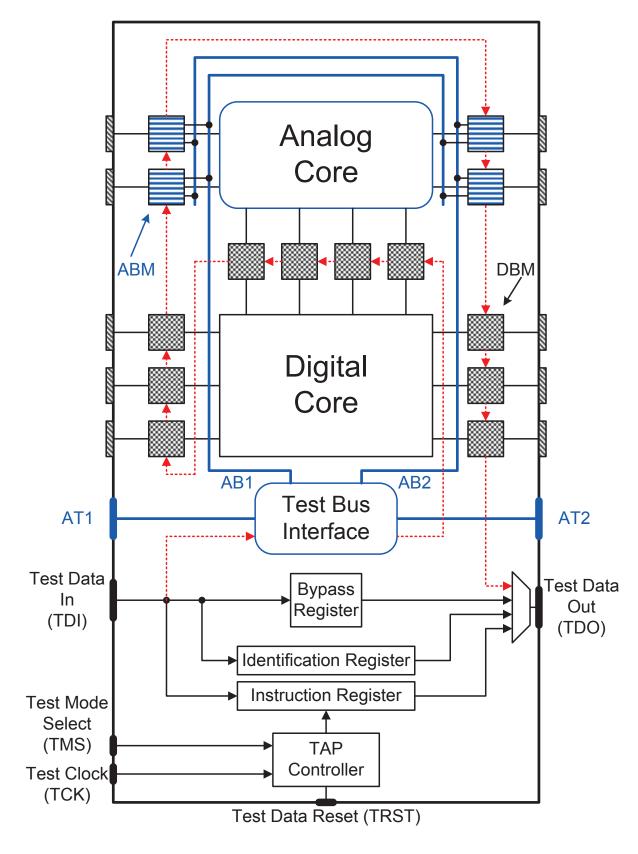

| 3.16 IEEE 1149.4 Architecture                                             |

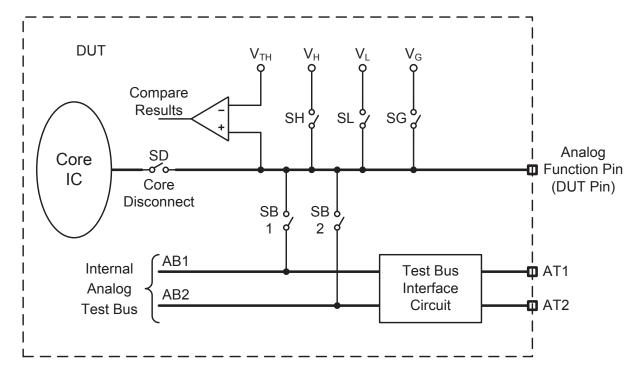

| 3.17 IEEE 1149.4 Standard Analog Boundary Module Architecture 6           |

List of Figures ix

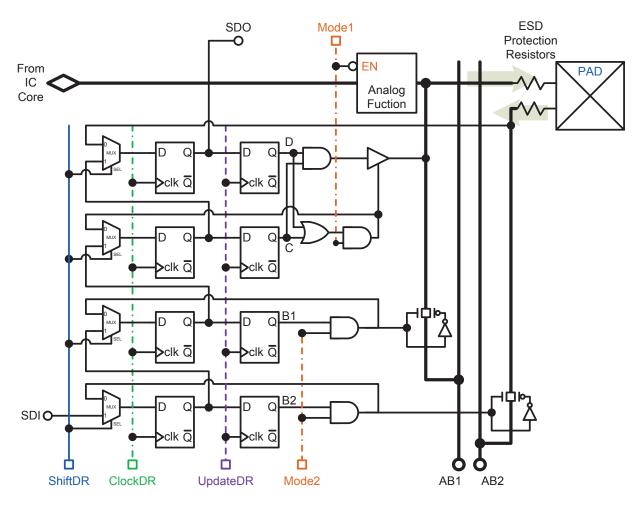

| 3.18 | IEEE 1149.4 Implementation - Analog Boundary Module Schematic         | 69  |

|------|-----------------------------------------------------------------------|-----|

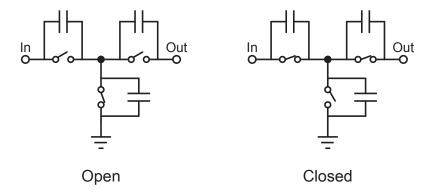

| 3.19 | T-switch Topology to Avoid Crosstalk                                  | 71  |

| 3.20 | T-switch Schematic                                                    | 71  |

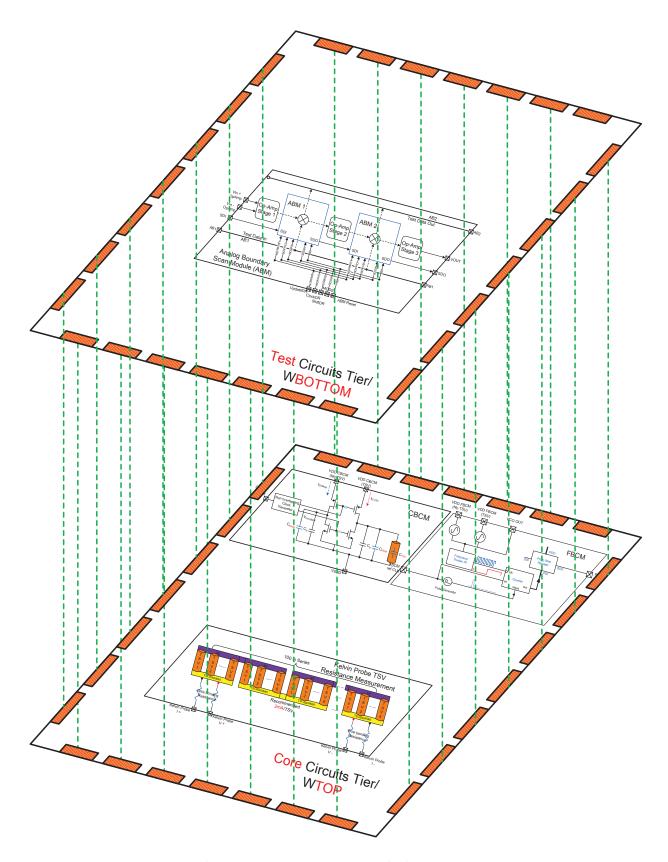

| 3.21 | Two Tiers Of A 3D Chip                                                | 73  |

| 3.22 | Internal Analog Scan                                                  | 75  |

| 3.23 | Modified Analog Boundary Module VS Traditional Analog Boundary Module | 76  |

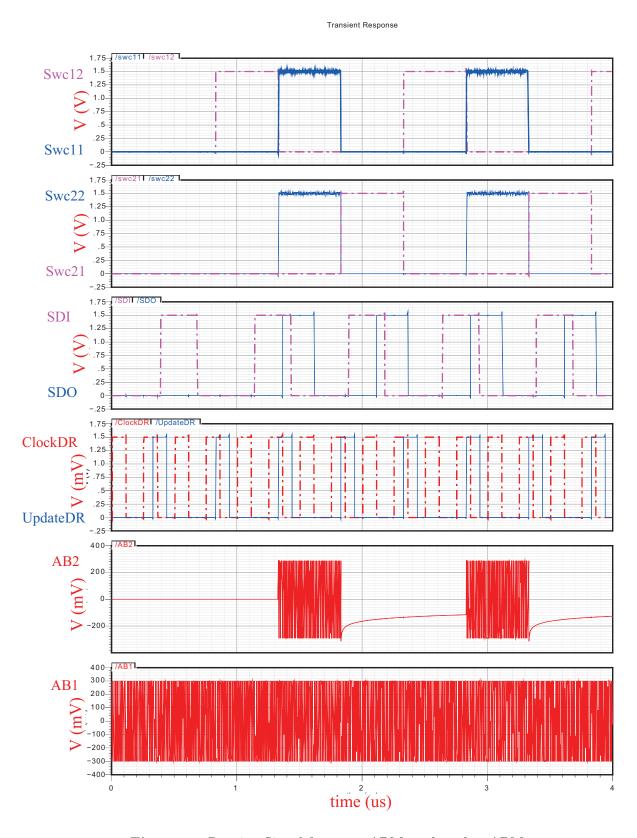

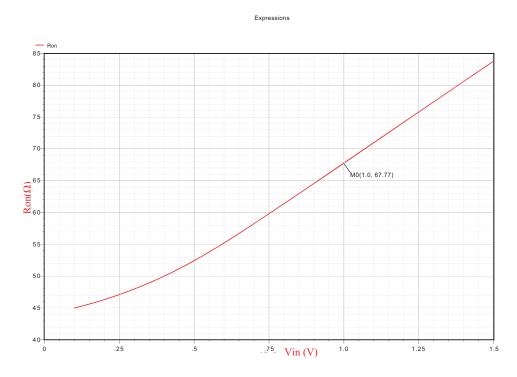

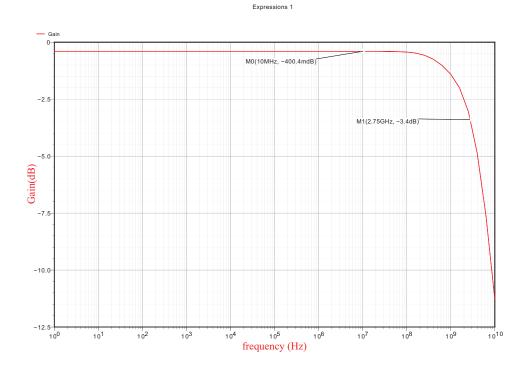

| 3.24 | Modified ABM Time Waveform                                            | 78  |

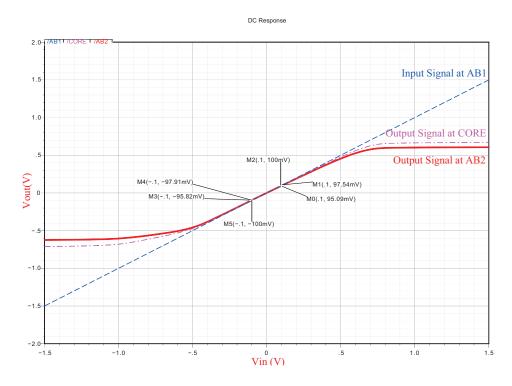

| 3.25 | Analog Switch ON Resistance                                           | 79  |

| 3.26 | Analog Switch Input Range                                             | 79  |

| 3.27 | Frequency Response of Analog Switch                                   | 80  |

| 3.28 | Routing Signal from one ABM to the other ABM                          | 81  |

| 3.29 | ABM Switches' ON Resistance                                           | 82  |

| 3.30 | ABM Switches' ON State Input Range                                    | 83  |

| 3.31 | ABM Switches Frequency Response                                       | 83  |

| 4 1  |                                                                       | 0.0 |

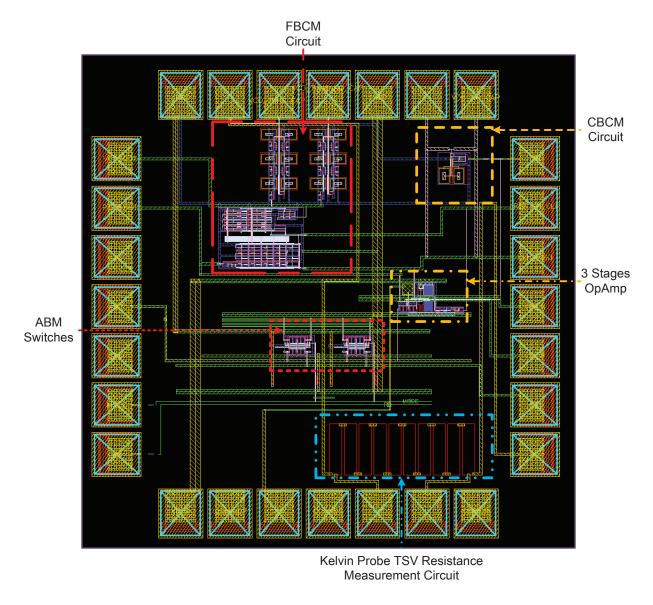

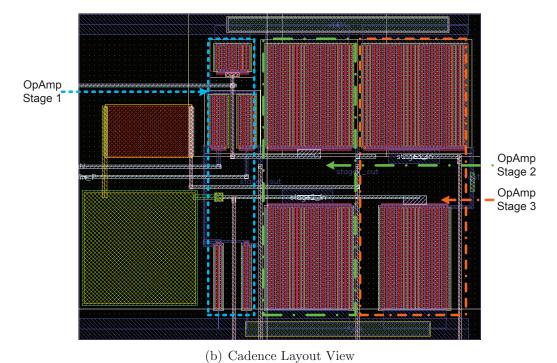

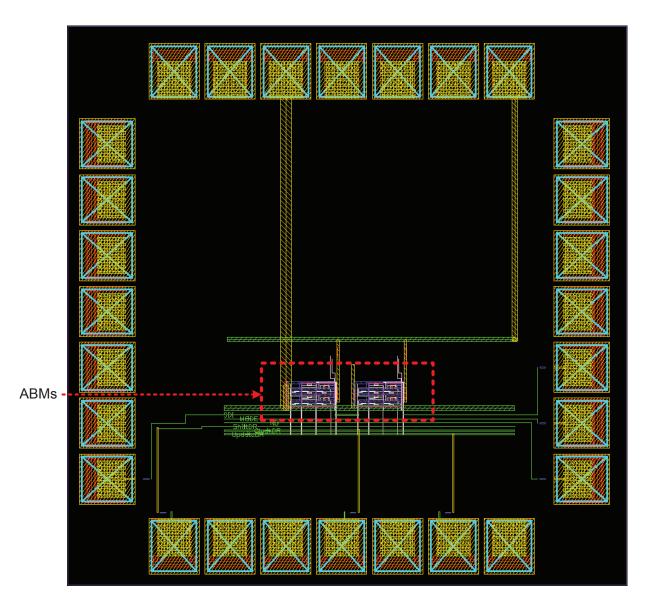

| 4.1  | Two Tier Layout Blocks Diagram                                        | 86  |

| 4.2  | WTOP Tier Layout With Each Circuit Component Identified               | 87  |

| 4.3  | TSV Capacitor Formation                                               | 89  |

| 4.4  | The FBCM Embedded Instrument                                          | 90  |

| 4.5  | The CBCM Embedded Instrument                                          | 91  |

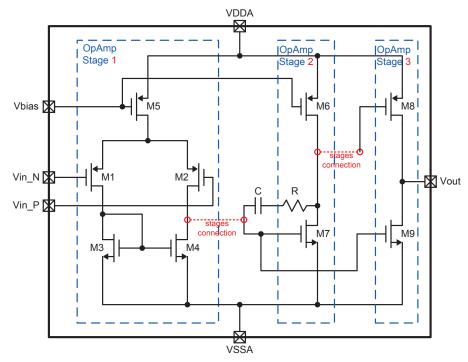

| 4.6  | Three-Stage Op-Amp Circuit                                            | 92  |

| 4.7  | WBOTTOM Tier Layout With Each Circuit Component Identified            | 93  |

| 4.8  | 3D-Chip Pad/Pin Connections                                           | 95  |

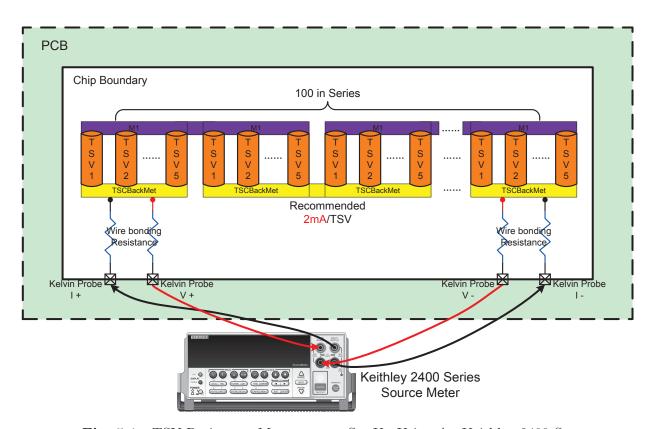

| 5.1  | TSV Resistance Measurement Set Up                                     | 98  |

| 5.2  | Frequency-Based TSV Capacitance Measurement Set Up                    | 100 |

| 5.3  | Charge-Based TSV Capacitance Measurement Set Up                       | 101 |

| 5.4  | Analog Boundary Scan Module Measurement Set Up                        | 102 |

|      |                                                                       |     |

| A.1  | Test Bench for Frequency Based Capacitance Measurement Method         | 107 |

| A.2  | Test Bench for Charged Based Capacitance Measurement Method           | 108 |

| A.3  | Test Bench for Analog Boundary Scan Module                            | 108 |

| A.4  | Test Bench for DC Analysis of ABM Switches                            | 109 |

| A.5  | Test Bench for AC Analysis of ABM Switches                            | 109 |

# List of Tables

| 1.1 | 3D Packaging VS 3D-IC                                            | 8  |

|-----|------------------------------------------------------------------|----|

| 2.1 | Transistor Dimensions For A Five-Stage VDD-Tuned Ring Oscillator | 19 |

| 2.2 | Voltage Buffer Dimensions                                        | 22 |

| 2.3 | Analog Switches Dimensions                                       | 25 |

| 2.4 | Ring Oscillator Output Frequency With Switches In The ON State   | 27 |

| 2.5 | Ring Oscillator Output Frequency With Switches In The OFF State  | 27 |

| 2.6 | NMOS TEE-Switch Parasitics                                       | 29 |

| 2.7 | Comparison Summary Of The One and Two VCO FBCM Implementations   | 33 |

| 2.8 | Transistor Dimensions Of Each Pseudo Inverter Circuit            | 44 |

| 3.1 | Inverter Dimensions                                              | 53 |

| 3.2 | NAND Gate Transistor Dimensions                                  | 54 |

| 3.3 | NOR Gate Transistor Dimensions                                   | 55 |

| 3.4 | Transistor Dimensions For The TSPC DFF Without Reset             | 57 |

| 3.5 | TSPC DFF with Reset Dimensions                                   | 58 |

| 3.6 | EXTEST Test Mode States                                          | 70 |

| 3.7 | Transistor Dimensions Of The TEE-Switch                          | 72 |

| 5.1 | Tezzaron 3D-IC Time Schedule                                     | 97 |

# List of Acronyms

$\operatorname{TSV}$  Through-silicon Via

SoC Systems on Chip

SiP System in Package

PiP Package in Package

PoP Package on Package

DfT Design for Test

PISO Parallel in Shift out

JTAG Joint Test-Action Group

CUT Circuit-under-test

# Chapter 1

### Introduction

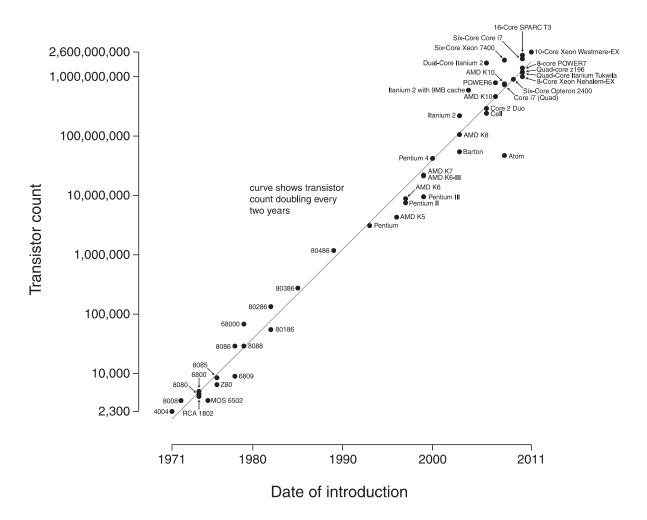

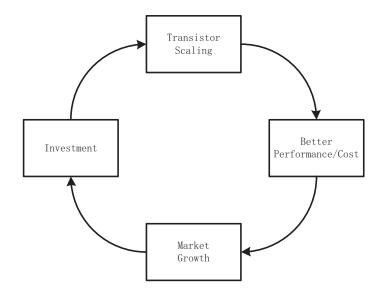

Since the early 70's, the semiconductor industry seems to have doubled the number of transistors integrated on a single monolithic substrate every 18 to 24 months as depicted by Fig. 1.1. Such a phenomena is commonly referred to as *Moore's law*. By reducing the dimensions of a transistor, better performance and lower cost products were introduced into the various electronic markets, resulting in an exponential growth in those markets. Greater revenues, drew more investment, which continues to demand further transistor scaling. Such a relationship between market growth and transistor scaling is illustrated in Fig. 1.2. The virtuous circle of the semiconductor industry has kept the entire semiconductor industry growing in a healthily and steadily manner, until now, where the scaling of a transistor can no longer be performed on account of reaching the atomic scaling limit (i.e., a transistor constructed from a single atom).

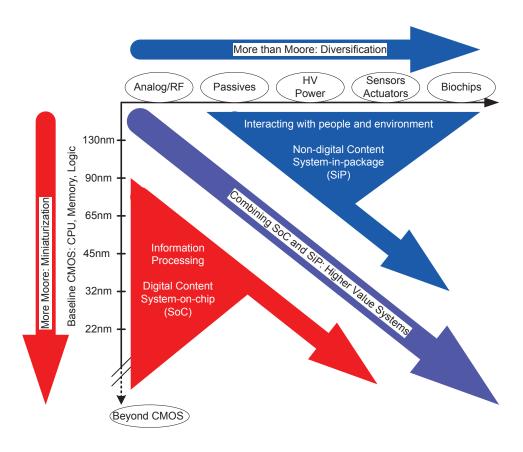

The International Technology Roadmap for Semiconductors (ITRS) divided the trends of miniaturization into two. One is the miniaturization of the digital functions, which is the scaling down of transistor size, also known as *More Moore*. The other is the functional diversification, more functionalities in a single packaged chip, known as *More-than-Moore*, as illustrated in Fig. 1.3.

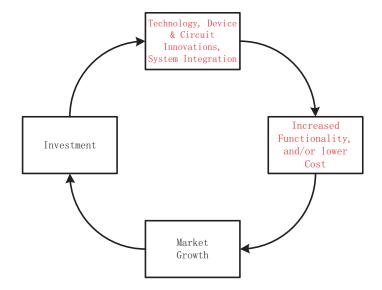

More-than-Moore technologies, which focuses on system integration, have made significant contribution to the semiconductor industry world-wide. A new virtuous circle needs to be created and adapted to relay these industries and their investments, in a manner depicted by that shown in Fig. 1.4. Instead of relying on a transistor scaling paradigm, innovations at all levels must occur, including the system, circuit, device and technology

### Microprocessor Transistor Counts 1971-2011 & Moore's Law

**Fig. 1.1** Moore's Law 2011

Fig. 1.2 The Virtuous Circle of the Semiconductor Industry

levels. Innovations should address both the functionalities and cost of a whole chip. This also encourages the growth of various domains of scientific research, which leads to further opportunities.

#### 1.1 3D IC

While opportunities in a More-than-Moore paradigm are huge, so too are the challenges. The integration of multiple chips in a single package serves as another path to move forward in the More-than-Moore domain. Systems-on-chip (SoC) and System-in-package (SiP) are the two most popular integration types seen in the market today.

#### 1.1.1 SoC and SiP

Systems-on-chip (SoC) packs several functionalities into a single silicon die. It usually includes digital, analog, mixed-signal and even RF intellectual property cores, or IPs for short, in a single chip substrate. However, there are some drawbacks for the single-die SoC. These can be listed in point form as follows:

• All components are placed on the same die using the same process technology.

Fig. 1.3 The Trends In Electronic Miniaturization

Fig. 1.4 Virtuous Circle with More than Moore

• The migration of analog and RF circuit into the same process takes time, thereby extending the product's time-to-market and increasing its engineering costs.

The Systems-In-Package (SiP) approach offers several advantages over SoC. Digital, analog, mixed-signal and RF circuits can be implemented using separate technology processes, thereby optimizing the performance of each. The comparison of SoC and SiP is illustrated in Fig. 1.5. Meanwhile, micro electromechanical systems (MEMS) could also be integrated into the same package; something one is finding in many electronic products today, e.g., iPhone. Fig. 1.6 shows a photograph of twenty-four stacked dies by Amkor Technology. Such an example demonstrates the capability of an SiP approach.

Other packaging alternatives have since been created. These include package-in-package (PiP), where a number of smaller SiPs were mounted on top of one another to form a larger SiP, and package-on-package (PoP), where one SiP was assembled on top of the other SiP. Nonetheless, these technologies offer the advantages that a 3D-IC approach using thrusilicon-vias (TSVs) seems to provide, such as performance, power improvement, density and overall cost of manufacturing.

Fig. 1.5 SoC VS SiP

Fig. 1.6 24 Stacked Dies In A Single Package By Amkor Technology

#### 1.1.2 3D-IC with TSV

Thru-silicon-vias (TSV) is a vertical electrical connection made to pass through the silicon wafer/die in a vertical manner. TSVs are made of copper whose diameters may range from 1 to 30 micrometers. A 3D-IC usually connects two or more dies with TSVs. Depending on the process and numbers of stack dies, commonly referred to as tiers, the 3D-IC may be bonded in back-to-face (B2F) manner such as that shown in Fig. 1.7 or face-to-face (F2F) manner as shown in Fig. 1.8. Bonding between tiers may or may not rely on TSVs. It could be a copper bump instead.

Fig. 1.7 Back-to-face bonding 3D-IC

3D-ICs constructed using TSVs have the following advantages over a stacked-die package arrangement:

- Interconnect between dies are shortened, allowing high-speed performance.

- Big drivers can be eliminated, which will end up saving a lot of power.

- 3D-IC also allows more miniaturization, saving a lot of space; they are ideal for the compact mobile market.

- Re-use of dies increases the manufacturing yield.

Fig. 1.8 Face-to-face bonding 3D-IC

• Beside integration of multiple functions, 3D-IC also shorted the time-to-market, which results in lower cost.

All of these points are summarized in Table 1.1 for easy access.

| Table 1.1 | 3D Packaging | VS 3D-1C |  |  |

|-----------|--------------|----------|--|--|

|           |              | 0D. 1    |  |  |

| Spec              | 3D<br>Packaging | 3D-IC<br>with TSVs |

|-------------------|-----------------|--------------------|

|                   | Fackaging       | WIUII 15VS         |

| Interconnect      | Long            | Short              |

| Performance       | Slow            | Fast               |

| Power Consumption | High            | Low                |

| Density           | Low             | High               |

| Chip Area         | Large           | Small              |

| Yields            | High            | Low                |

| Cost              | High            | Low                |

### 1.2 3D Integration Process

Generally speaking, the 3D integration process follow three main manufacturing steps [1]: (1) Through-silicon via formation, (2) Wafer thinning, and (3) Wafer aligning or die bonding. Each of these steps can be described as follows:

#### 1. TSV Fabrication:

- (a) TSVs were fabricated during the IC fabrication process:

- i. Front-end-of-line (FEOL) TSVs are fabricated before the wiring process in IC fabrication.

- ii. Back-end-of-line (BEOL) TSVs are done during the metal wiring process in the fabrication.

- (b) TSVs were fabricated after the complete ICs were fabricated, which is also known as Post-BEOL TSVs.

- i. TSVs are fabricated before die bonding (vias first).

- ii. TSVs are fabricated after die bonding (vias last).

#### 2. Wafer Thinning:

- (a) The wafers were thinned on temporary handle wafers.

- (b) The wafers were thinned after bonding to the 3D-IC stack.

#### 3. Wafer Aligning or Die Bonding:

- (a) Metal bonding (multiple methods, all create electrical interconnect between layers.)

- i. Direct Cu/Cu, Au/Au, and so on.

- ii. Eutectic CuSn, and so on.

- iii. Hybrid SiO<sub>2</sub>/metal.

- (b) Direct bonding (e.g.  $SiO_2$ - $SiO_2$ ).

- (c) Adhesive bonding.

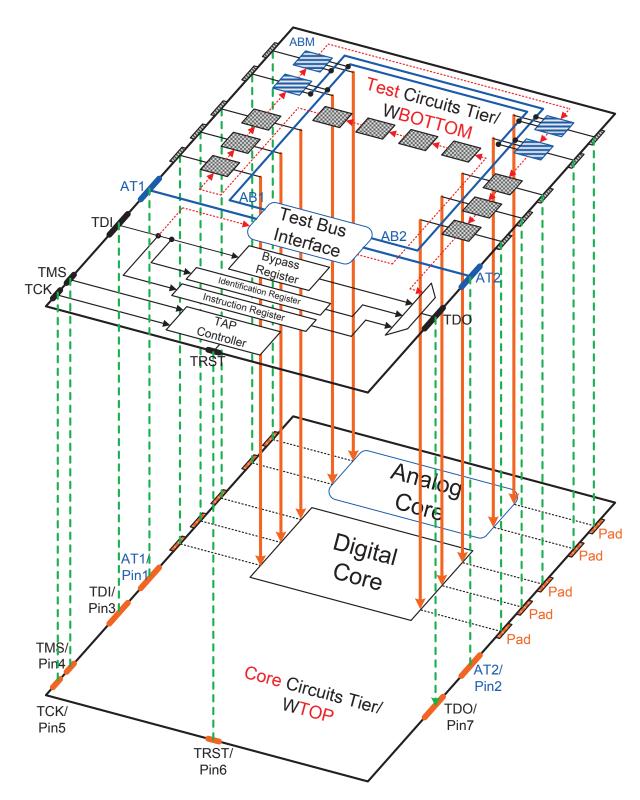

Tezzaron® Semiconductor is one of the world wide leaders in 3D-IC manufacturing, specialized in 3D wafer stacking and TSV processes. Canadian Microelectronics Corporation (CMC) collaborates with Tezzaron, MOSIS and Circuits Multi-Projets® (CMP) to work on 3D-IC prototype design and test. This dissertation is one of the first endeavours into 3D integration within the Canadian university system.

#### 1.3 Tezzaron 3D-IC Technology Description

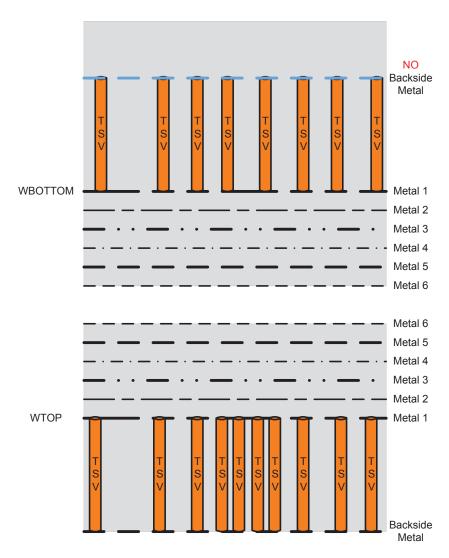

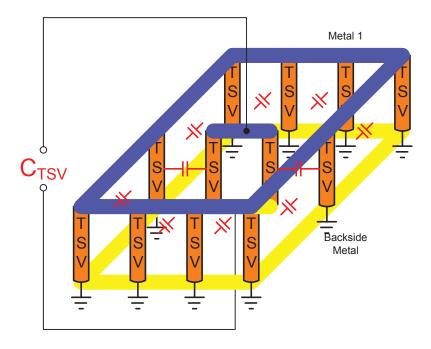

The Tezzaron 3D-IC technique bonds two silicon dies face-to-face with a Cu-to-Cu thermocompression process (referred to as a FaStack®process) as shown in Fig. 1.9. The two dies are named WTOP and WBOTTOM by Tezzaron. Each die or tier has six layers of metal and the ability to integrate thru-silicon vias or TSVs from metal one to the top/bottom of the die where an additional metal layer may be formed. The WTOP tier contains this additional backside metal layer, wheres the WBOTTOM tier does not. This backside metal layer is used to connect signals from within to the chip's I/O. Also seen in the figure, are many TSVs in the WBOTTOM tier. These TSVs are essentially left unconnected and is a by-product of the Tezzaron 3D-IC technique at this time. Future versions of the technology may include a backside metal layer on the WBOTTOM tier. Signals in the WBOTTOM tier will have to be routed through metal layer 6, which is electrically connected to metal layer 6 of the WTOP tier and onwards through out the structure.

### 1.4 Test Challenges

Similar to the conventional single-die IC test, 3D-IC testing should be performed at both the wafer level and after the IC is package. However, there are many more manufacturing steps for 3D-IC, like die stacking and TSV bonding, which requires more tests at the wafer level. Moreover, wafer testing is more challenging than a conventional single-die IC test for the following reasons:

- The probe nowadays can not handle the finer pitch and dimensions of TSV tips.

- The scrub marks left by the probe technology could potentially cause problems for the bonding step.

- Probe needle movement may results in crashes into the various die stacks.

**Fig. 1.9** Illustrating The Metal Layers and TSVS in the WTOP and WBOTTOM tiers of the Teazzaron 3D-IC technology

Also, a 3D-IC process introduces new intra-die defects into the package part on account of wafer thinning or die bonding. Thermal or heating effects are another sources of defects. Mechanical stress can also served as a source of new defects.

The thermo-mechanical reliability of TSV structure has been studied in literatures [2] [3] [4] [5]. Because of the coefficients of thermal expansion (CTE) between different TSV filled materials, copper (Cu) and silicon substrate, the thermo-mechanical stress is induced in the fabrication process. This can affect the device performance or even cause device breakdown. Thus, we need to figure out ways reduce the probing requirements but at the same time provide probe access to 3D-IC chips. The following are the testing issues raised by a 3D-IC technology:

- Is the interconnect TSVs reliable?

- How to probe inside the die stacks?

- Where is the test access? Is primary I/O sufficient?

- How to de-bug and isolate faults?

It is the objective of this dissertation to consider the above questions and identify a possible contender to the conventional wafer probe approach.

#### 1.5 Thesis Overview

This thesis began with an introduction to 3D-IC technology where through-silicon vias and the 3D process was described. Some technology details for the Tezzaron 3D process was also provided in this chapter.

Chapter 2 introduces some modern measurement techniques for characterizing the signal integrity of a TSV in a 3D CMOS process. This will include measurements of its end-to-end series resistance and its corresponding capacitance-to-ground. A frequency-based direct capacitance measurement approach and a charge-based capacitance measurement will be described.

Chapter 3 discusses the DFT techniques used to capture and transfer the information captured by the embedded instruments described in Chapter 2. This chapter will describe a DFT technique that is compatible with the JTAG test bus standard but optimized for a 3D-IC configuration.

Chapter 4 presents the physical details pertaining to the design of the 3D chip made from the Tezzaron technology.

Chapter 5 describes the experimental setup for testing the prototype 3D-chip. This chapter should have provided experimental results as well, but unfortunately, due to manufacturing delays, the chip has not yet returned from fabrication.

Chapter 6 provides the thesis conclusions and some ideas for the future work.

# Chapter 2

## TSV Characterization

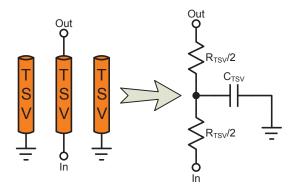

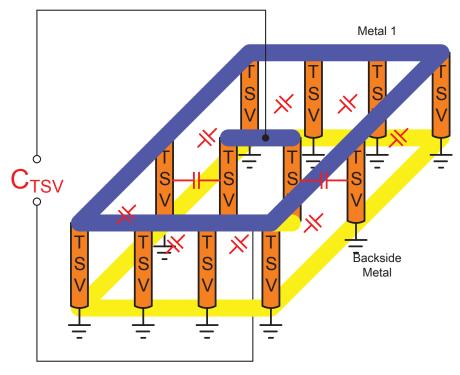

This chapter will introduce some modern measurement techniques for characterizing the signal integrity of a TSV in a 3D CMOS process. This will include measurements of its end-to-end series resistance and its corresponding capacitance-to-ground. In order to control this capacitance, the TSV in question will be surrounded by two separate TSV that are ground at one end as shown in Fig. 2.1. A frequency-based direct capacitance measurement approach and a charge-based capacitance measurement will be described. Looking at the bigger picture, these measurement techniques will be incorporated into a design-for-test (DFT) strategy that attempts to standardize the measurement interface between the IC and its test equipment. We shall delay any detail discussion of the DFT approach until Chapter 3. Here we will focus exclusively on an embedded resistance and capacitance measurement technique.

Fig. 2.1 TSV Lumped RC Model

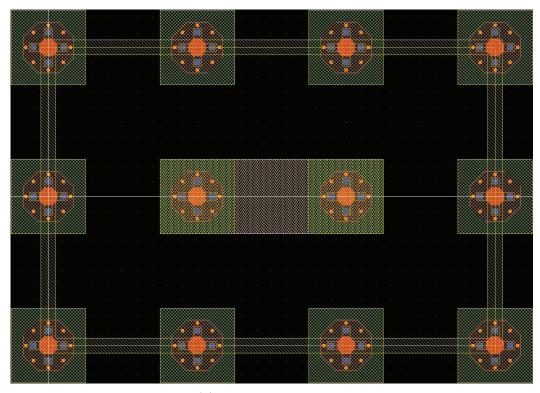

#### 2.1 TSV Resistance Measurement

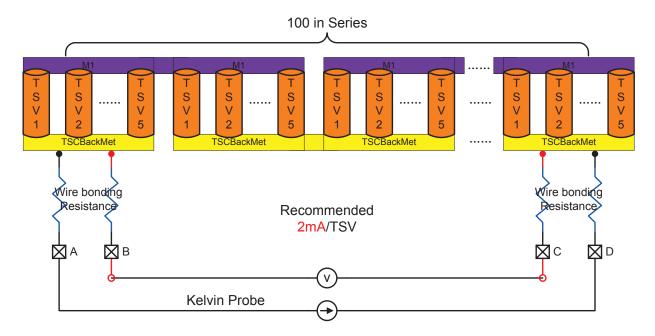

According to [2] [6] [7] the series resistance is approximately 20 m $\Omega$  for a 5  $\mu$ m diameter and 25  $\mu$ m length TSV in the 3D CMOS process created by IMEC. Owing to this very small quantity, making a direct measurement of a single TSV resistance will be subject to many obstacles, such as the influence of other trace resistances, package parasitics, noise, etc. In order to increase this resistance, one hundred TSVs are connected in series, increasing the resistance a 100 fold. However, this resistance was reduced by about a factor of 5, as 5 TSVs were also connected in parallel in order to increase the current capability of the series-parallel circuit combination to about 20 mA. A single TSV from Terrazon Semiconductor has a current carrying limit of 2 mA. Collectively, the increased resistance combined with the higher current limit enables a more accurate measurement.

In order to eliminate the influence of any trace parasitic in series with an instrument off-chip, a Kelvin connection was made to the resistance network. This is shown in Fig. 2.2. Here a DC current is forced into the series circuit through IC pads A and D and the voltage drop across the resistor network is measured off-chip with a voltmeter through another set of internal traces connect to pads B and C. As the current through the voltmeter is very low, the effect of the trace resistance connected to pads B and C are insignificant and a true measurement of the voltage dropped across the resistor network can be made [8].

Assuming all the TSVs are identical, and we have P TSVs connected in parallel and S TSVs in series, a single TSV resistance  $R_{TSV}$  can be found from the following

$$R_{TSV} = \frac{V}{I} \cdot \frac{S}{P} \tag{2.1}$$

where I is the current forced into the resistor network by the current source and V is the voltage measured by the voltmeter. For the case we have defined here, with 5 TVSs in parallel and 100 components in series, the TSV resistance expression becomes

$$R_{TSV} = \frac{100}{5} \cdot \frac{V}{I} \tag{2.2}$$

### 2.2 Measuring Capacitor Mismatch

Measuring small valued capacitances directly on-chip, such as the capacitance shunting the TSV of Fig. 2.1, through an off-chip measurement is highly susceptible to stray capacitances

Fig. 2.2 Kelvin Probe for TSV Resistance Measurement

such as those seen at the bonding pads of the IC. Moreover, as these capacitances are quite small, on the order of 50 fF, they are generally beyond the measurement resolution of any bench-top capacitance meter. Before we tackle the measurement of the absolute value of some small parasitic capacitance, in this section we shall first review several methods used to measure the capacitance mismatch between two supposedly identical capacitors. One method is based on a voltage-based step method [9] applied to a capacitor network, another is based on two independent ramp signals applied to a similar capacitor network [9] [10] and a third method is based on measuring the frequency difference caused by the capacitance mismatch on the load of an oscillator [9].

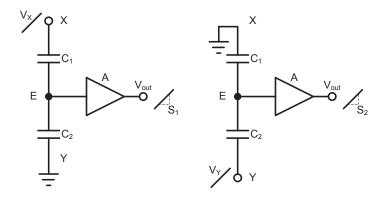

#### 2.2.1 Ramp-Based Capacitor Mismatch Measurement

Consider a test cell whereby two similar capacitors ( $C_1$  and  $C_2$ ) are connect in series. Nominally,  $C_1 = C_2 = C$ , but due to mismatches, they different slightly with magnitude  $\Delta C = |C_1 - C_2|$ . In addition, an amplifier with gain A is connected to the common point of the two capacitors as shown in Fig. 2.3. At each end of each capacitor is a voltage source. During the first phase, a voltage ramp  $V_X$  is applied to one end of the capacitor network while the voltage source at the other end is held at ground potential. The next phase reverses the roles that each voltage source assumes and repeats the measurement at the output of the amplifier. The slopes of the corresponding output signals to these two separate excitations, denoted as  $S_1$  and  $S_2$ , are measured. The relative mismatch between  $C_1$  and  $C_2$  can then be calculated according to

$$\frac{\Delta C}{C} = 2 \cdot \frac{S_1 - S_2}{S_1 + S_2} \tag{2.3}$$

One limitation of this approach is the noise from the amplifier. Measurements should be averaged multiple times for a more repeatable measurement of capacitor mismatch.

Fig. 2.3 Ramp-Based Capacitor Measurement Approach

#### 2.2.2 Frequency-Based Capacitor Mismatch Measurement

In this measurement situation, a voltage-controlled oscillator (VCO) is loaded with two switched capacitive loads assumed to be matched. As the frequency of oscillation is a function of its load capacitance, relative differences in the frequency of oscillation will be proportional to relative capacitive mismatch according to

$$\frac{\Delta f_{out}}{f_{out}} = \alpha \cdot \frac{\Delta C}{C} \tag{2.4}$$

To use this method, the  $\alpha$  term must be identified through some calibration procedure.

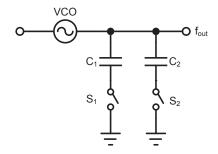

Fig. 2.4 Frequency-Based Capacitor Mismatch Measurement Approach

### 2.3 Frequency-Based TSV Capacitor Measurement

In this section we shall make use of the frequency-based mismatch measurement approach to measure the capacitance of a TSV. This approach was selected as the order of magnitude of the TSV capacitance is similar in magnitude to a capacitor mismatch. For the convenience of this dissertation, this method will be referred to as the frequency-based TSV capacitor measurement approach, or FBCM method for short. Two methods will be provided, one involving a single VCO and the other using two.

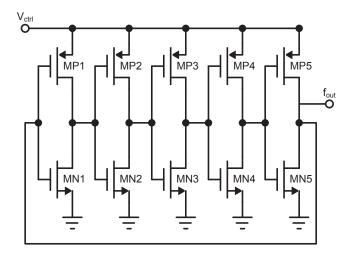

Fig. 2.5 Five-Stage VDD-Tuned Ring Oscillator

The VCO is to be constructed using the 5 stage VDD-tuned ring oscillator shown in Fig. 2.4. This oscillator provides a very small silicon footprint using a regular layout structure. This simple test circuit can reach frequencies as high as 2.5 GHz, which increases the sensitivity to very small capacitances. All like-transistor types (NMOS and PMOS) of the

ring oscillator are identical. A summary of the dimensions of these transistors can be seen listed in Table 2.1.

**Table 2.1** Transistor Dimensions For A Five-Stage VDD-Tuned Ring Oscillator

|             | NMOS | PMOS |

|-------------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 |

| $W (\mu m)$ | 2    | 4    |

As the actual oscillation frequency of the ring oscillator will vary from chip-to-chip on account of process variations, the  $\alpha$  parameter in Eqn. 2.4 must be found for each and every chip. To extract this value, two sets of frequency measurements will be made; one involving the VCO under no-load conditions and the other with the TSV attached. Under such conditions, we can write Eqn. 2.4 as

$$\frac{f_{out,TSV} - f_{out,noload}}{f_{out,noload}} = \alpha \cdot \frac{(C_{TSV} + C_{eff,parasitic}) - C_{eff,parasitic}}{C_{eff,parasitic}}$$

(2.5)

which reduces to

$$\frac{f_{out,TSV} - f_{out,noload}}{f_{out,noload}} = \alpha \cdot \frac{C_{TSV}}{C_{eff,parasitic}}$$

(2.6)

where  $C_{eff,parasitic}$  correspond to the effective parasitic capacitance seen at the output of the VCO under no load conditions and  $C_{TSV}$  is the additional capacitance added when the TSV is connected to the VCO output. Parameters  $f_{out,noload}$  and  $f_{out,TSV}$  are the measured frequencies corresponding to the unloaded and load conditions, respectively. As the objective of the measurement is to find  $C_{TSV}$ , rearranging Eqn. 2.6 and isolating  $C_{TSV}$ , we find

$$C_{TSV} = \frac{C_{eff,parasitic}}{\alpha} \cdot \frac{f_{out,TSV} - f_{out,noload}}{f_{out,noload}}$$

(2.7)

As mentioned earlier, the  $\alpha$  term is unknown and needs to be identified. Also,  $C_{eff,parasitic}$  is also unknown and must be identified. A different approach is therefore required.

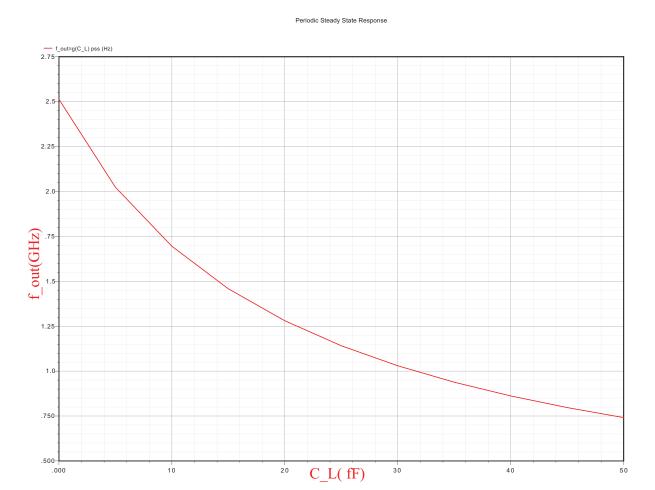

Going back to first principles, the frequency of oscillation  $f_{out}$  of the ring-oscillator can be described in general terms as a function of its load capacitance  $C_L$ , i.e.,

$$f_{out} = g(C_L) (2.8)$$

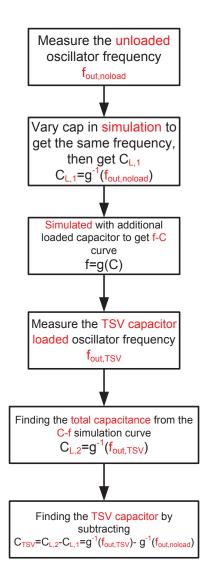

Here the function g() represents any nonlinear expression. The expression  $f_{out} = g(C_L)$  can be illustrated using the graph shown in Fig. 2.6.

**Fig. 2.6** VCO Output Frequency Vs. Load Capacitance  $f_{out} = g(C_L)$  Nonlinear Curve

Now, assuming that this function g() is known and invertible, the load capacitance on the ring oscillator can be determined according to

$$C_L = g^{-1}(f_{out}) (2.9)$$

Operating the VCO under two different load conditions, i.e.,  $C_{L,1} = C_{eff,parasitic}$  and  $C_{L,2} = C_{eff,parasitic} + C_{TSV}$  and measuring the corresponding oscillating frequencies, as previously

identified as  $f_{out,noload}$  and  $f_{out,TSV}$ , allows one to identify the load capacitances as

$$C_{L,1} = g^{-1}(f_{out,noload})$$

(2.10)

and

$$C_{L,2} = g^{-1}(f_{out,TSV}) (2.11)$$

Subsequently, the unknown TSV capacitance  $C_{TSV}$  can then be found from the following expression

$$C_{TSV} = C_{L,2} - C_{L,1} (2.12)$$

The above process is summarized in the flow chart shown in Fig. 2.7.

#### 2.3.1 TSV Capacitor Formation

The TSV-under-test is surrounded with several dummy structures and all are connected directly to ground at each end as shown in Fig. 2.8. These grounded dummy structures isolate the TSV-under-test from the rest of the IC.

#### 2.3.2 FBCM Using The Single-VCO Approach

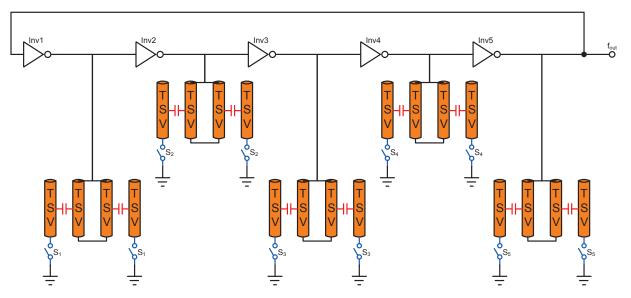

In this measurement case, the FBCM is constructed with a single ring-oscillator VCO and several switchable loads, in much of the same fashion as that depicted in Fig. 2.4. Specifically, the VCO is realized as a cascade of five inverter sections, with each section loaded with a programmable-TSV load, as shown in Fig. 2.9. Here the programmable-TSV consists of a parallel combination of two floating TSVs surrounded by two other TSVs that can be connected to ground through the two analog switches.

#### Output Buffer Design

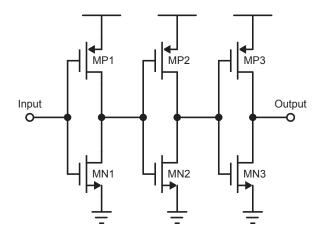

In order to drive the VCO signal directly off-chip for a frequency measurement, a voltage buffer was also constructed as shown in Fig. 2.10. The buffer consists of a cascade of three inverter stages with transistor dimensions seen listed in Table 2.2.

**Fig. 2.7** A Flow Chart Illustrating The Measurement Approach For A Two-VCO Frequency-Based TSV Capacitor Cell

Table 2.2

Voltage Buffer Dimensions

|             | MN1  | MN2  | MN3  | MP1  | MP2  | MP3  |

|-------------|------|------|------|------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 | 0.13 | 0.13 | 0.13 |

| $W(\mu m)$  | 1    | 4    | 16   | 2    | 8    | 32   |

Fig. 2.8 TSV Formation With Grounded Dummy Structures

**Fig. 2.9** A Single-VCO Frequency-Based TSV Capacitor Measurement Circuit with Programmable-TSV Loads

Fig. 2.10 A Voltage Buffer For Driving A Ring Oscillator Signal Off-Chip

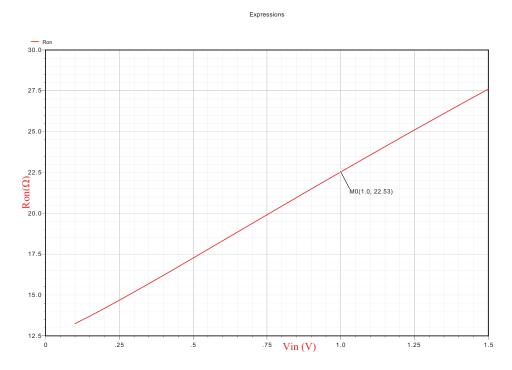

#### Investigating The Impact Of The Analog Switches on FBCM Operation

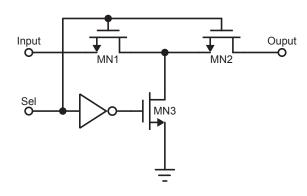

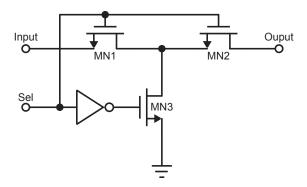

The analog switch is constructed using a grounded TEE-connected arrangement of three transistors driven from a single control port as shown in Fig. 2.11. This particular switch introduces a small amount of parasitic capacitance to ground at each terminals of the switch. This capacitance is the sum of all the capacitance that appears at either the drain or source terminal of a single transistor to ground. Two different implementations of the switch were compared; one where the transistor width of all three transistors making up the TEE-switch was set to 10  $\mu$ m and the other with widths of 90  $\mu$ m each. As a point of reference, these two switch realizations are compared to the situation with the switch either removed in an open or infinite impedance state or closed in a zero impedance state. Using this ideal switch conditions as a point of reference allows one to compare the reduction in performance caused by a real switch.

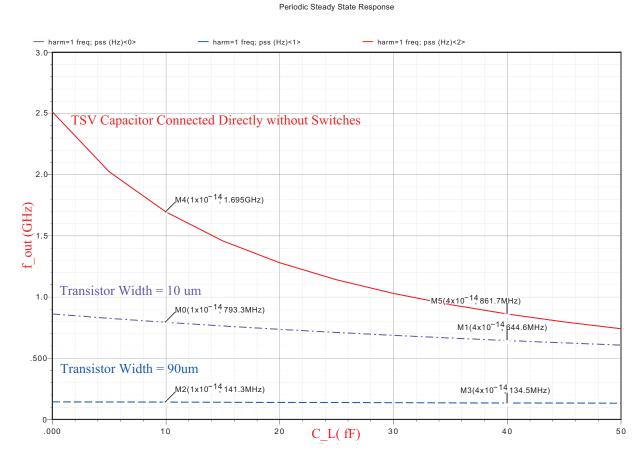

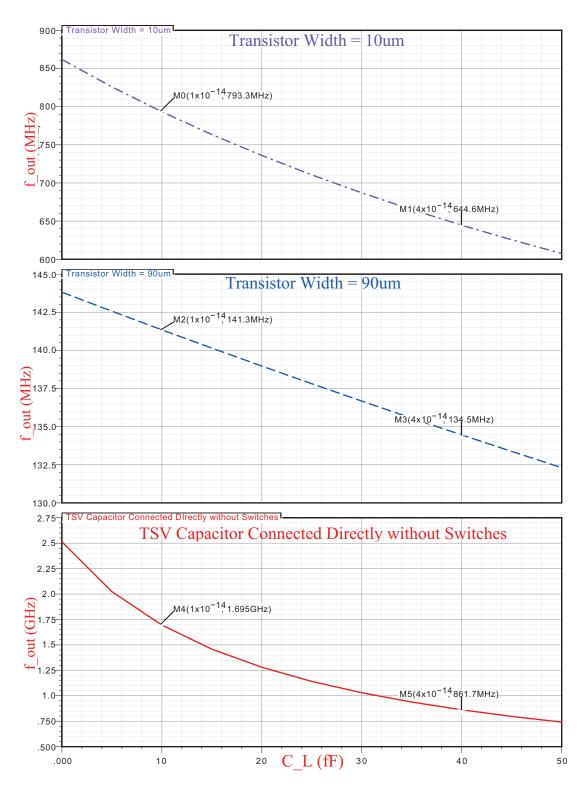

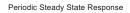

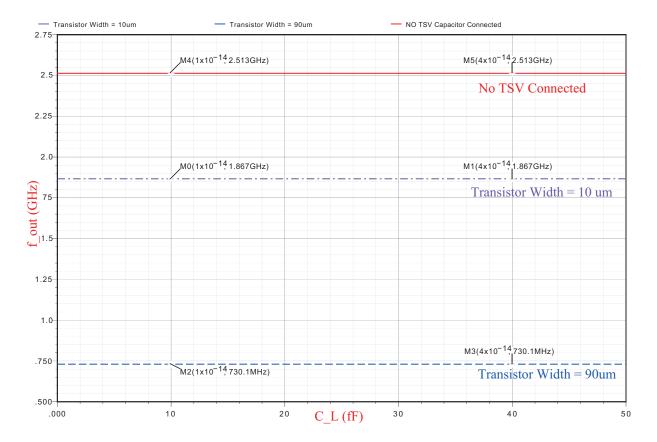

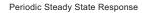

The simulation results for the FBCM arrangement of Fig. 2.9 for the situation when the TSV switches are placed in the closed or ON state are shown in Fig. 2.12 for a 0 to 50 fF effective capacitance load on the FBCM. The load introduced by the TSV was simply modeled as an ideal capacitor. The control voltage  $V_{ctrl}$  is set to 1.4 V. Also shown in this plot are the simulation results for the ideal switch (i.e., replaced by a short circuit). The simulation is repeated but this time with the switches placed in the open or OFF state. The results of these simulations are shown in Fig. 2.14. To summarize these two sets of results, Tables 2.4 and 2.5 lists the output oscillation frequency for TSV capacitive loads of 10 fF and 40 fF, respectively.

Fig. 2.11 Analog Switch

Table 2.3 Analog Switches Dimensions (a) 10  $\mu$ m Analog Switches

|             | MN1  | MN2  | MN3  |

|-------------|------|------|------|

| L (μm)      | 0.13 | 0.13 | 0.13 |

| $W (\mu m)$ | 10   | 10   | 2    |

## (b) 90 $\mu$ m Analog Switches

|             | MN1  | MN2  | MN3  |

|-------------|------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 |

| $W (\mu m)$ | 90   | 90   | 20   |

From Fig. 2.12 to Fig. 2.15, the label M0 indicates the simulation with 10 fF load capacitance and 10  $\mu$ m switch, the label M1 is with 40 fF load capacitance and 10  $\mu$ m switch, the label M2 is with 10 fF load capacitance and 90  $\mu$ m switch, the label M3 is with 40 fF load capacitance and 90  $\mu$ m switch, the label M4 is with 10 fF load capacitance and without switch, and the label M5 is with 40 fF load capacitance and without switch.

Each set of results can also be compared to the ideal switch situation. As is evident from these two tables of results, there is a huge gap between output oscillation frequency of the ideal switch situation and that generated by either the 10  $\mu$ m or 90  $\mu$ m switch implementation. We also notice that the smaller switch realization (i.e., width of 10  $\mu$ m) leads to a higher oscillation frequency. The reason for these differences can be attributed to the switch capacitive parasitics.

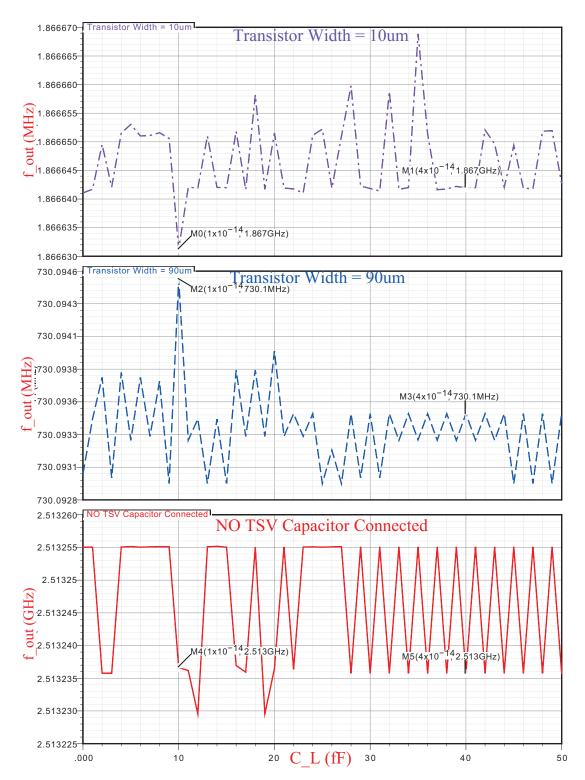

To better understand the reason for this oscillation loss, consider the small-signal model of the TEE-connected switch arrangement of Fig. 2.11 in Fig. 2.16. Here  $R_{sw}$  is the resistance of the switch and  $C_{gs}$ ,  $C_{gd}$ ,  $C_{sb}$ , and  $C_{db}$  represents the small-signal capacitances of the NMOS transistor. Also included is the small capacitance between the source and drain of the transistor  $C_{ds}$  created by an electric field under the channel region of the transistor. Also shown is the capacitance  $C_{TSV}$  that is used to represent the capacitance of the TSV. The output oscillation frequency  $f_{out}$  is inverse proportional to the total equivalent capacitances no matter the switch is ON or OFF. When the switch is ON, the output oscillation frequency  $f_{out}$  is determined by

$$1/f_{out} \propto ((C_{gs} + C_{sb}) + (C_{gd} + C_{db}) + C_{TSV})$$

(2.13)

and while the switch is *OFF*,

$$1/f_{out} \propto ((C_{gs} + C_{sb}) + C_{ds}||((C_{gd} + C_{db}) + C_{TSV}))$$

(2.14)

As can be seen listed in Table 2.6, the various parasitic capacitance of the two switches is also in fF range, which is relatively close to our TSV capacitance value. Thus, the parasitic capacitance of switches cannot be ignored.

# Fig. 2.12 Single-VCO-Based with Switches In ON State Comparison

**Table 2.4** Ring Oscillator Output Frequency With Switches In The ON State

| Frequency (Hz)    | $10\mu m$ Switch | $90\mu\mathrm{m}$ Switch | NO Switch            |

|-------------------|------------------|--------------------------|----------------------|

| $C_{TSV} = 10fF$  | 793.3 MHz        | $141.3~\mathrm{MHz}$     | $1.695~\mathrm{GHz}$ |

| $C_{TSV} = 40 fF$ | 644.6 MHz        | $134.5~\mathrm{MHz}$     | $861.7~\mathrm{MHz}$ |

**Table 2.5** Ring Oscillator Output Frequency With Switches In The OFF State

| Frequency (Hz)   | $10\mu\mathrm{m}$ Switch | $90\mu \text{m}$ Switch | NO Switch            |

|------------------|--------------------------|-------------------------|----------------------|

| $C_{TSV} = 10fF$ | $1.867~\mathrm{GHz}$     | $730.1~\mathrm{MHz}$    | 2.513 GHz            |

| $C_{TSV} = 40fF$ | $1.867~\mathrm{GHz}$     | $730.1~\mathrm{MHz}$    | $2.513~\mathrm{GHz}$ |

Periodic Steady State Response

Fig. 2.13 Single-VCO-Based with Switches In ON State Comparison Details

Fig. 2.14 Single-VCO-Based with Switches In OFF State Comparison

Table 2.6

NMOS TEE-Switch Parasitics

| Parasitics  | ON                       | ON                       | OFF                      | OFF                      |

|-------------|--------------------------|--------------------------|--------------------------|--------------------------|

| Capacitance | $10\mu\mathrm{m}$ Switch | $90\mu\mathrm{m}$ Switch | $10\mu\mathrm{m}$ Switch | $90\mu\mathrm{m}$ Switch |

| $C_{gs}$    | 7.049 fF                 | $63.46~\mathrm{fF}$      | $3.501~\mathrm{fF}$      | 31.51 fF                 |

| $C_{sb}$    | 387.6  aF                | $3.492~\mathrm{fF}$      | $1.769~\mathrm{fF}$      | $16.04~\mathrm{aF}$      |

| $C_{gd}$    | 7.411 fF                 | $66.73~\mathrm{fF}$      | $4.255~\mathrm{fF}$      | $38.30~\mathrm{fF}$      |

| $C_{db}$    | 387.6  aF                | $3.492~\mathrm{fF}$      | $2.651~\mathrm{fF}$      | $24.02~\mathrm{aF}$      |

| $C_{ds}$    | 2.446  fF                | $22.04~\mathrm{fF}$      | 391.2  zF                | $3.545~\mathrm{aF}$      |

| $C_{sd}$    | $1.792~\mathrm{fF}$      | $16.13~\mathrm{fF}$      | $10.99~\mathrm{aF}$      | $99.60~\mathrm{aF}$      |

$\begin{tabular}{ll} \bf Fig.~2.15 & Single-VCO-Based~with~Switches~In~OFF~State~Comparison~Details \\ \end{tabular}$

Fig. 2.16 Parasitics Analysis Of The TEE-Connected Switch

#### 2.3.3 FBCM Using The Two-VCO Approach

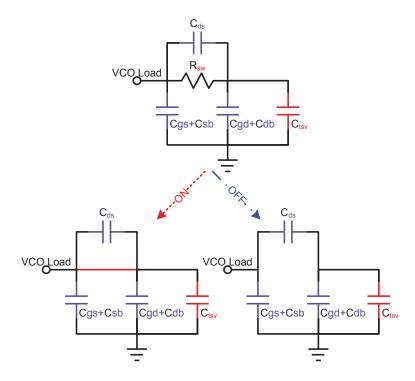

An important limitation of the single or one VCO FBCM implementation method of the previous subsection is the dependence of the oscillation frequency on the switch parasitics and, in turn, the TSV capacitance measurement. In this section, a second approach is provided that is based on a two VCO implementation. Such an implementation provides a higher measurement resolution than the single or one VCO approach and solves the parasitic dependence problem. Fig. 2.17 shows the schematic diagram for the two VCO FBCM measurement approach. On the top part of the figure is a 5-stage ring oscillator with no additional load. On the bottom part is the same 5-stage ring oscillator but loaded with TSVs without the aid of analog switches. This particular arrangement eliminates the analog switches altogether and with it their corresponding parasitic problem. In normal operation the unload VCO will oscillate with frequency  $f_{out,noload}$  and the TSV-loaded VCO will oscillate with frequency  $f_{out,noload}$  and the TSV-loaded VCO will oscillate with frequency  $f_{out,noload}$  and the TSV capacitance would be found using the exact same formula as seen in Eqn. 2.7. In practice, however, transistor mismatches between the loaded and unloaded ring oscillator will introduce errors in the

TSV measurement. It is therefore imperative that the layout of the two VCOs is done in a careful and symmetric manner so as to minimize these types of errors. Using large sized transistors also helps to reduce these mismatches.

Fig. 2.17 Two VCOs Frequency-Based TSV Capacitor Measurement Approach Without Analog Switches

A comparison of the single- or one-VCO approach versus the two-VCO approach can be seen listed Table 2.7. While each approach has its pros and cons, it is believed by the author that the two-VCO approach is better suited to a TSV capacitance measurement and will be the method of choice as a frequency-based measurement approach.

#### 2.3.4 External Access To Frequency-Based Capacitance Measurements

From Eqn. 2.7, we can see that two frequencies are required:  $f_{out,noload}$  and  $f_{out,TSV}$ . If a frequency-to-digital converter (FDC) is used, then the frequency quantity will appear in the form of an integer value expressed in general terms as

$$M = \beta \cdot f \tag{2.15}$$

**Table 2.7** A Comparison Summary Of The One and Two VCO FBCM Implementations

|              | Pros                                                                                                            | Cons                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| One-VCO FBCM | • Single VCO, saving space and power.                                                                           | • Parasitics $R_{sw}$ and $C_{sw}$ introduce measurement error. • Loss of measurement resolution when $C_{sw} \approx C_{TSV}$ . |

| Two-VCO FBCM | <ul> <li>No switch parasitics to care about.</li> <li>Higher sensitivity to the capacitor variation.</li> </ul> | <ul> <li>Mismatch between VCOs introduce the measurement error.</li> <li>Noise from one VCO couples into the other.</li> </ul>   |

where  $\beta$  represents the gain of the FDC. Since the digital count  $M_{out}$  is linear with respect to output frequency  $f_{out}$  as it is derived directly from a counting procedure,  $M_{out}$  will have the same nonlinearity with respect to the load capacitance  $C_L$  except with a different gain factor,  $\beta$ . By combining Eqn. 2.8 with Eqn. 2.15, we can write

$$M_{out} = \beta \cdot g(C_L) \tag{2.16}$$

By defining a new nonlinear function  $G(x) = \beta \cdot g(x)$ , Eqn. 2.12 can be written as

$$C_{TSV} = G^{-1}(M_{out,TSV}) - G^{-1}(M_{out,noload})$$

(2.17)

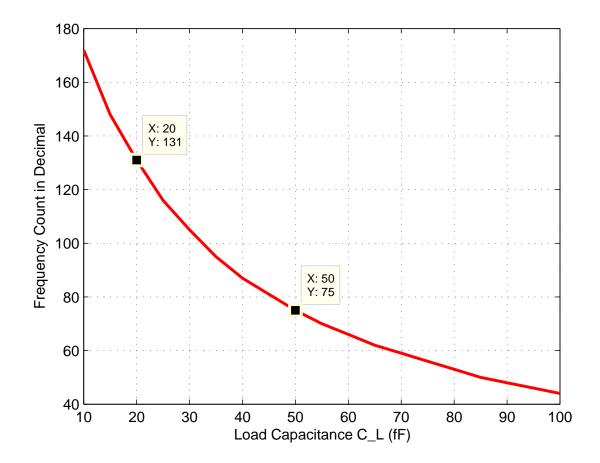

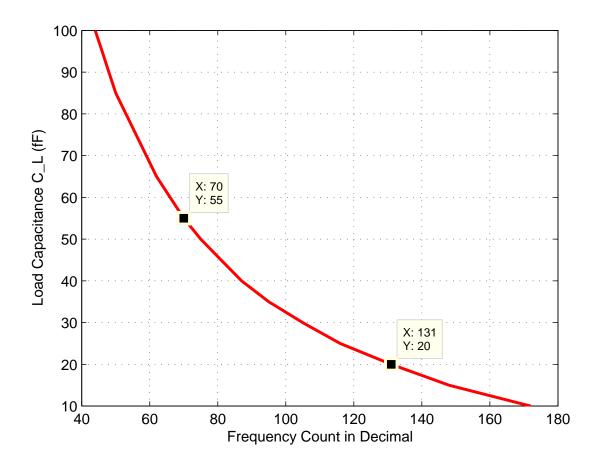

The relation between the frequency count  $M_{out}$  and the load capacitance  $C_L$  is illustrated in Fig. 2.18. Notice that the gain of the FDC does not appear in the computation of the TSV capacitance quantity.

Fig. 2.18 Frequency Count VS Load Capacitance

#### Frequency-To-Digital Converter Principle

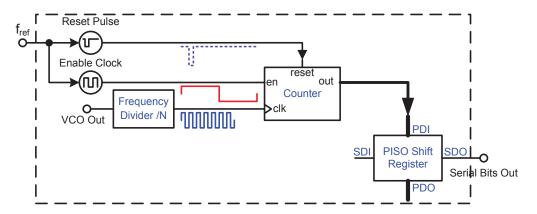

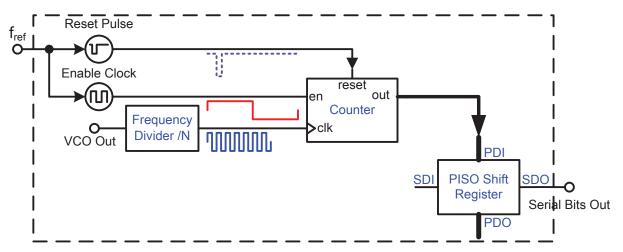

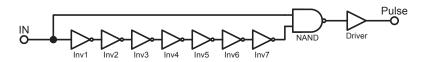

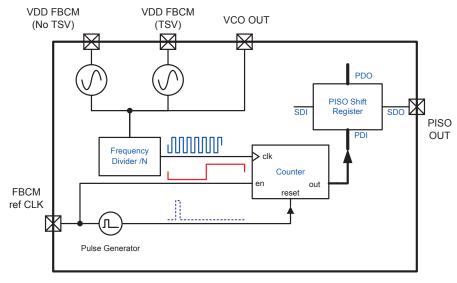

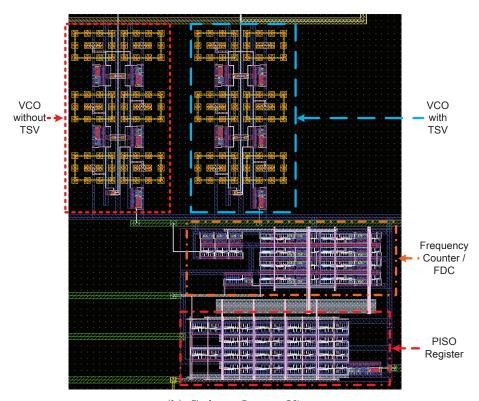

The FDC shown in Fig. 2.19 consists of three parts: frequency divider, counter and reset pulse signal generator. The FDC takes as input a square wave signal from the VCO. This signal is first divided down in frequency using the divide-by-N frequency divider circuit and directed to the clock input of the counter. A second input consisting of the enable signal (START COUNT) initiates the counting cycle. The count completes when the reset pulse is generated (STOP COUNT). The pulse generator is clocked using an off-chip reference signal with frequency  $f_{ref}$ .

Fig. 2.19 Frequency-To-Digital Converter With External Access

The frequency of the incoming VCO signal is then determined from the count value denoted as M according to

$$f_{vco} = 2 \cdot N \cdot M \cdot f_{ref} \tag{2.18}$$

This phase of operation is referred to as the *Counting Phase*. The next phase of operation is called the *Shifting-Out Phase*, whereby the digital count value is passed to the user off-chip. This is explained next.

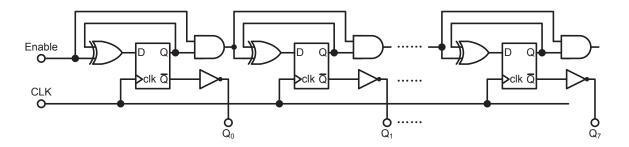

To further improve the on-chip test, a parallel-in-serial-out (PISO) register associate with the frequency counter is included. The serial output requires only a single pin, saving pins for other chip functions. The PISO register is eight-bits wide and an additional eight-ones are added as the flag bits to indicate the start of a word count transmission.

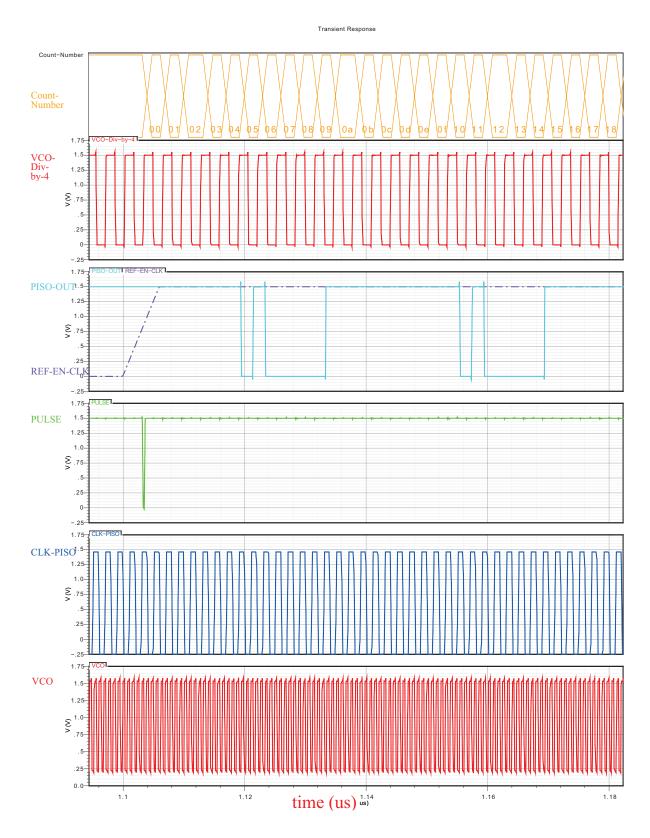

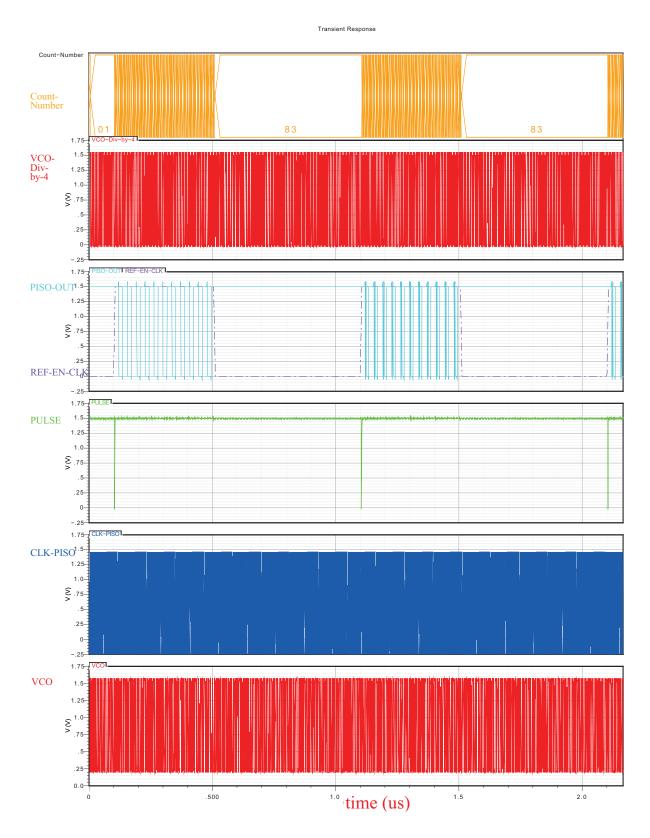

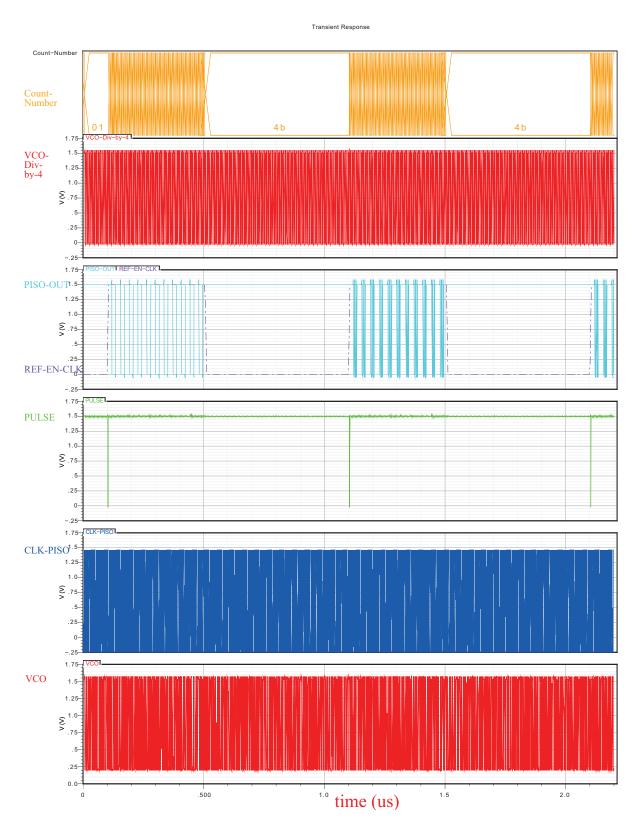

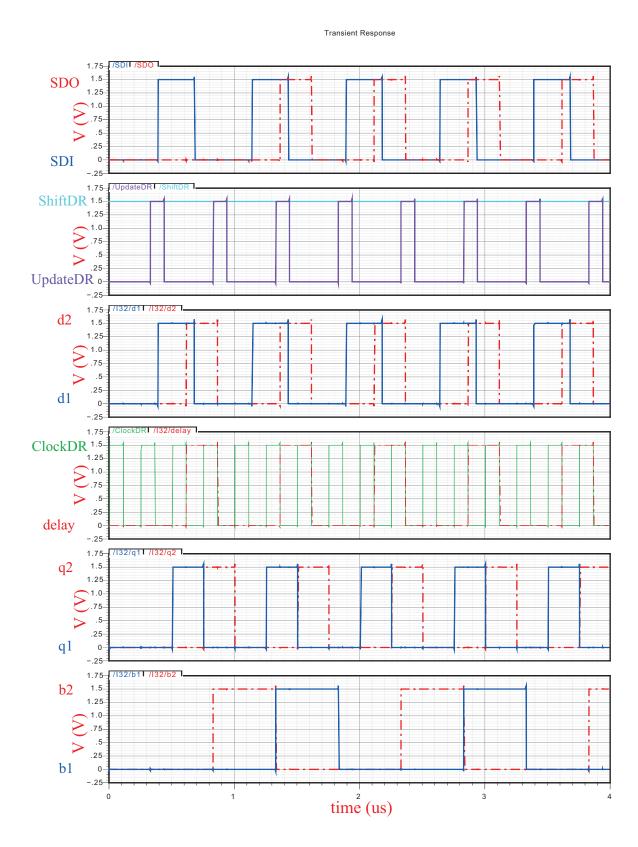

The timing diagram corresponding to the FDC is illustrated in Fig. 2.20. From top to bottom, the first waveform represents the *Count-Number*, the next waveform represents

Fig. 2.20 FBCM Counter and PISO Output Waveform Details

the VCO output after the frequency divider VCO-Div-by-4, the third plot is for the shift register output signal PISO-OUT and the reference clock signal REF-EN-CLK, the forth waveform is for the pulse signal PULSE, the fifth plot is for the clock signal of PISO shift register CLK-PISO and the bottom waveform is for the VCO output signal VCO.

At the beginning of every conversion cycle, the PULSE signal resets the counter to a decimal zero value. The counter is clocked by divide-by-4 output and the counter is allowed to increment only when the reference clock REF-EN-CLK is set high. When the reference clock goes low, the frequency counter stop counting and the PISO register begins to shift out the counter bits with eight redundant ones (as seen in the waveform plot as PISO-OUT).

#### 2.3.5 Example Simulation and Discussion

In this subsection, we are going to show the TSV capacitance extraction procedure using the two-VCO FBCM method through a Spectre simulation. Each VCO will be loaded with a 20 fF parasitic capacitance and the TSV capacitance will be made equal to 30 fF. The timing diagram corresponding to this simulation is shown in Fig.2.21 following the exact same signal format as the previous timing diagram. In this simulation, there are two full counting cycles, one for the unloaded VCO and the other for the TSV-loaded VCO. At the end of each count phase, the shifting-out phase is also shown.

Let us assume the frequency count of decimal 131 with the timing diagram of the FDC process shown in Fig. 2.21 is the measurement result corresponding to an unloaded TSV capacitance. The TSV capacitance calculation is then performed according to the flow chart of Fig. 2.7.

- 1. Find the Count- $C_L$  plot from simulation. (This is shown in Fig. 2.22 as  $C_L$ -Count for ease of use)

- 2. Determine the *unloaded* oscillation frequency output count. In our case here, the top plot of Fig. 2.21 obtain from simulation indicates a count of '83' in HEX or 131 in decimal.)

- 3. Using the Count- $C_L$  curve of Fig. 2.22, for a decimal count of 131,  $C_{eff,parasitic}$  is 20 fF.

Fig. 2.21 FBCM Counter and PISO Output Two Full Cycle Waveform

- 4. Next, repeat the above steps but this time make reference to the TSV-loaded VCO. For the simulation situation of Fig. 2.23, we observe the *loaded* oscillation frequency output count as a HEX value of 4b or a decimal value of 75.

- 5. Using the Count- $C_L$  curve of Fig. 2.22, for a decimal count of 75,  $C_{total}$  is 50 fF.

- 6. The TSV capacitance is simply the difference between  $C_{total}$  and  $C_{eff,parasitic}$  leading to  $C_{TSV}$ =30 fF.

Fig. 2.22 Load Capacitance VS Frequency Count

Fig. 2.23 Timing Diagram Corresponding To An Unloaded And Loaded VCO Output.

# 2.4 Charge-Based TSV Capacitor Measurement

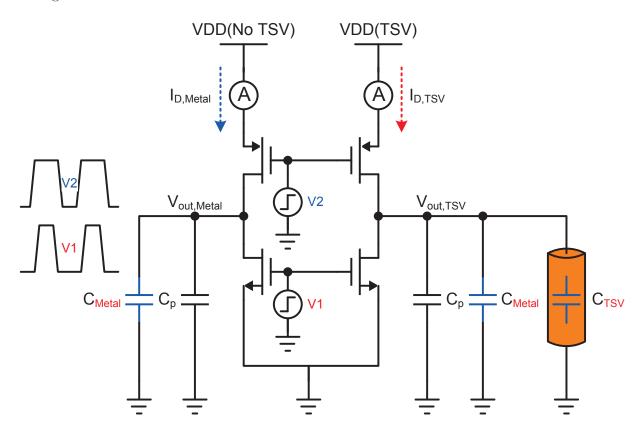

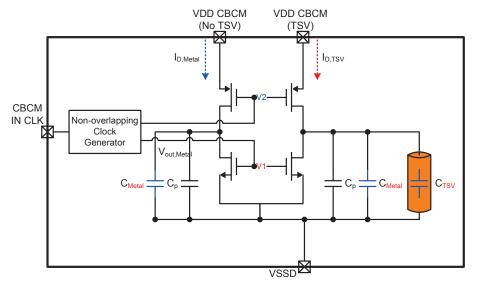

The charge-based capacitor measurement method (CBCM) was first proposed in [11][12]. As showed in Fig. 2.24, there are a pair of NMOS and PMOS transistors connected as a matched pair of *pseudo* inverters. The gate of each inverter is driven with separate inputs. The right inverter is loaded by TSV capacitor, while other inverter does not include the TSV capacitance but includes its parasitic capacitance  $C_P$  and any capacitance included with the metal routing associated with the TSV capacitance, denoted by  $C_{Metal}$ , as illustrated in Fig. 2.8. This cell wil act as the reference cell.

Fig. 2.24 Charge-Based Capacitance Measurement

#### 2.4.1 CBCM Principle

Voltage signals  $V_1$  and  $V_2$  in Fig. 2.24 are two independent control signals used to ensure the NMOS or PMOS transistors are conducting at non-overlapping times. Once the PMOS transistor turns on, charge flow from VDD into the TSV capacitor to charge up the capacitor. The same amount of charge will then be discharged through the NMOS transistors to ground on the other half of the charging cycle. Driving the nodes associated with  $V_1$  and  $V_2$  guarantees separate charging and discharging processes for each of the load capacitors.

Precision ammeters, like the Keithley 2602/2400 Source Meter, are used to measure the charging currents of each inverter with nA measurement accuracy. The ammeter is connected in series between VDD and source of each PMOS transistors to capture the charging current (or between ground and source of NMOS transistors if a discharge current is to be measured).

The charging and discharging process of a capacitor could be characterized in gneral terms using a i-v relationship of a capacitor as

$$i(t) = C\frac{dv(t)}{dt} \tag{2.19}$$

By integrating equation 2.19 over the period of the charging or discharging cycle, we can write

$$I_{ave} = C \cdot VDD \cdot f \tag{2.20}$$

where  $I_{ave}$  is the average current over the whole cycle and f is the frequency of the charging and discharging process.

In the TSV capacitance measuring, we have TSV with associated metal layers connected on the right side combining to form a total capacitance  $C_1$ . While the metal layers without TSV connected on the left side is said to have a total capacitance  $C_2$ . Where each capacitor can be written as

$$C_1 = C_P + C_{Metal} + C_{TSV} (2.21)$$

and

$$C_2 = C_P + C_{Metal} (2.22)$$

With the same VDD and f, the capacitance of the TSV  $C_{TSV}$  can be found from the difference of  $C_1$  and  $C_2$ , i.e.,

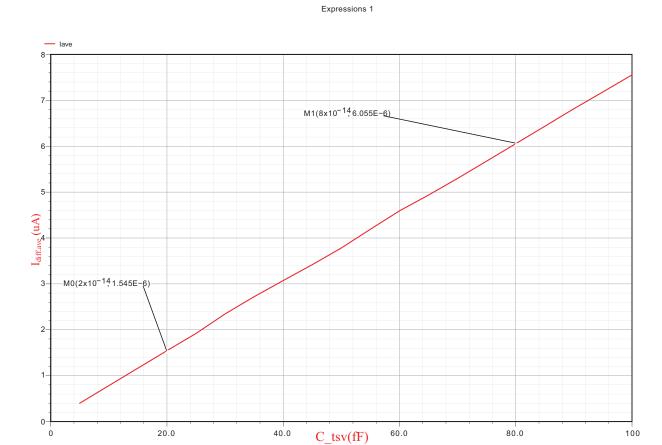

$$C_{TSV} = C_1 - C_2 = \frac{I_{D,TSV} - I_{D,Metal}}{VDD \cdot f} = \frac{I_{diff,ave}}{VDD \cdot f}$$

(2.23)

where  $I_{diff,ave}$  is the difference of the average charging or discharging current of the two sides of the pseudo inverters. Eqn. 2.23 reveals the linear relationship between  $C_{TSV}$  and  $I_{diff,ave}$ . Getting slightly ahead of the reader, Fig. 2.25 illustrates a Spectre simulation of a specific case of the CBCM circuit where we see the average charing current is very much a linear function of the TSV capacitance.

For ease of use, we introduce the slope factor, k, according to

$$k = \frac{I_{diff,ave}}{f} \tag{2.24}$$

This term represents the slope of the  $I_{diff,ave}$  vs f transfer characteristic for a specific supply voltage VDD. We shall make use of this parameter later on when extracting the TSV capacitance from a current measurement.

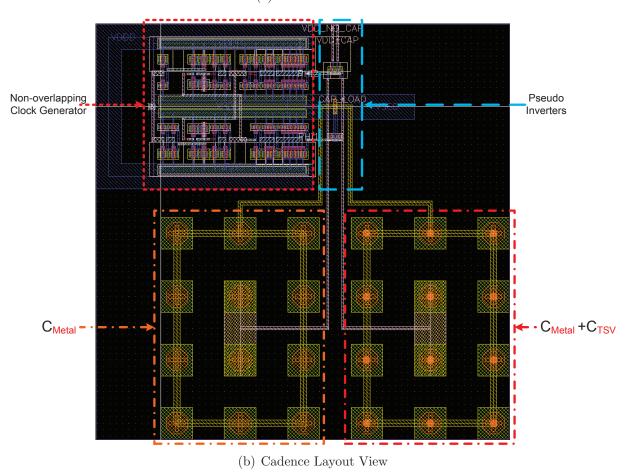

#### 2.4.2 CBCM Method Circuit Design

In the CBCM method, the most critical issues are matching the pseudo inverters and ensuring non-overlapping control signals. We'll discuss these two issues one by one.

#### Pseudo Inverter Design

Since the current difference is very small and sensitive to the load capacitance at the output of each inverter, it is critical that the parasitic capacitance at each *pseudo* inverter output is well matched. By placing each inverter close to one another and using common-centroid layout, mismatches in the parasitics can be minimized.

Also, we recognize from Eqn. 2.20 that the average difference current is a linear function of frequency, f. Hence, a higher operating frequency will result in a larger current difference level, thereby improving the signal-to-noise ratio of any particular measurement. However, to operate at higher frequency (i.e., guarantee a fully charge and discharge process) we must make use of small-sized transistors. The dimensions of the transistors used in the design of the CBCM circuit are listed Table 2.8.

Fig. 2.25 Averaged Difference Current VS TSV Capacitance

Table 2.8

Transistor Dimensions Of Each Pseudo Inverter Circuit

|             | PMOS | NMOS |

|-------------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 |

| $W (\mu m)$ | 0.5  | 0.5  |

#### Non-Overlapping Control Signal Generator Design

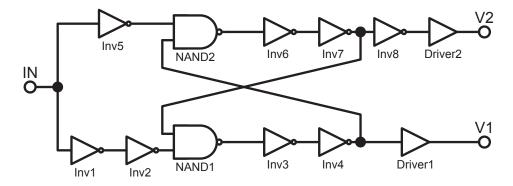

The non-overlapping signal can be generated either on- or off-chip as mentioned in [11][12]. However, in order to get fast rising edges for better measurement accuracy, in this work, the non-overlapping control signal generator was implemented directly on chip. The schematic for this design is shown in Fig. 2.26. Here the inverter chains are used to introduce delays to create non-overlapping signals from the same reference signal. A Spectre simulation of the behaviour of this control signal generator subject to a 50 MHz input clock signal acting as the reference is shown in Fig. 2.27. The bottom waveform represents the input clock signal with a 0.5 ns rise and fall time and the top waveform represents the generated output non-overlapping signal V1 and V2. As is clearly evident from this plot, signals V1 and V2 do not overlap.

Fig. 2.26 Non-Overlapping Clock Signal Generator Schematic

#### 2.4.3 Example Simulation and Discussion

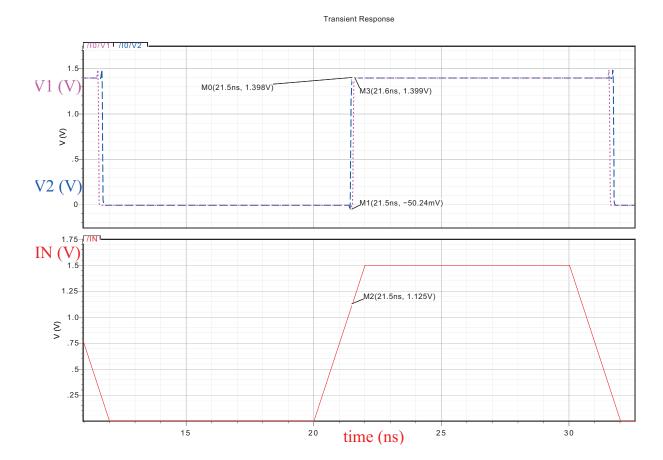

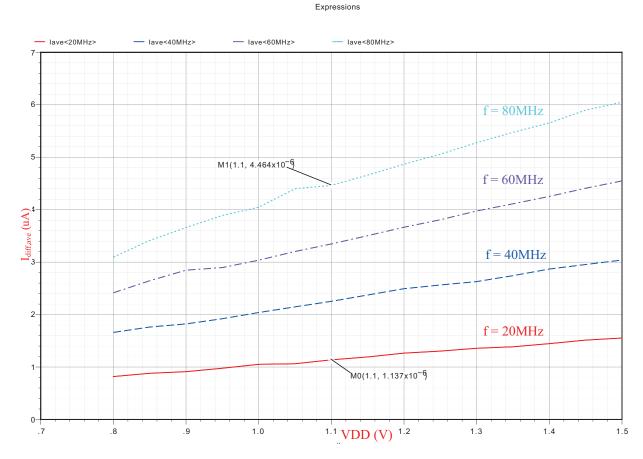

By applying the non-overlapping waveform in Fig. 2.27 to the CBCM circuit of Fig. 2.24, we can measure the average difference current  $I_{diff,ave}$ . Under four separate supply voltage conditions, , i.e., 0.8 V, 1.0 V, 1.2 V and 1.4 V, the  $I_{diff,ave}$  versus f was extracted through a Spectre simulation. The results are shown in Fig. 2.28. For each voltage condition, the TSV capacitance  $C_{TSV}$  can be derived directly from the slope of each curve. For instance, with VDD = 1.4 V, we find  $I_{diff,ave} = 3.553\mu A$  at f = 50MHz, hence using Eqn. 2.24, we find

$$k = C_{TSV} \cdot VDD = \frac{I_{diff,ave}}{f} = 7.106e - 14$$

(2.25)

Fig. 2.27 A Spectre Simulation Of The Non-Overlapping Clock Signals

Subsequently, the TSV capacitance  $C_{TSV}$  is found from Eqn. 2.23 to be

$$C_{TSV} = \frac{k}{VDD} = \frac{7.106e - 14}{1.4} = 50.76fF \tag{2.26}$$

Expressions

Fig. 2.28 Averaged Difference Current VS. Frequency Under Four Different Voltage Supply Conditions

In a similar manner, we can also calculate the TSV capacitance for a supply voltage of 0.8 V. There we see at 50MHz,  $I_{diff,ave2} = 2.036\mu A$ , leading to

$$C_{TSV} = \frac{I_{diff,ave2}}{f_2 \cdot VDD} = \frac{2.036}{50e6 * 0.8} = 50.9fF$$

(2.27)

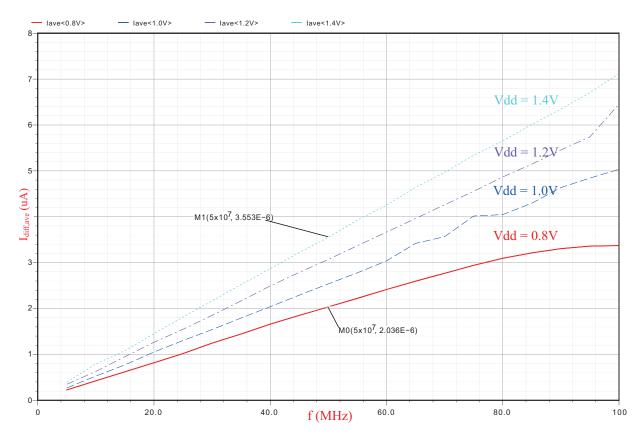

The charging and discharging currents, together with the difference current is shown in Fig. 2.29 for a 1.4 V supply level operating at a frequency of 50 MHz are shown in Fig. 2.29. The outputs of each pseudo inverter is charged to VDD when the control signal  $V_1$  and

Fig. 2.29 Time Domain Charging and Discharging Current With/Without TSV Capacitor

$V_2$  are set low. The plot corresponding to  $IO/VDD\_TSV$  is the current of the TSV loaded cell and the plot of  $IO/VDD\_NO\_TSV$  is the current of the reference cell. The top plot corresponding to Inet is the difference between these two currents. Its time average value (generally averaged over several cycles of the waveform) provides an estimate of  $I_{diff,ave}$ , which in turn is used to estimate  $C_{TSV}$ .

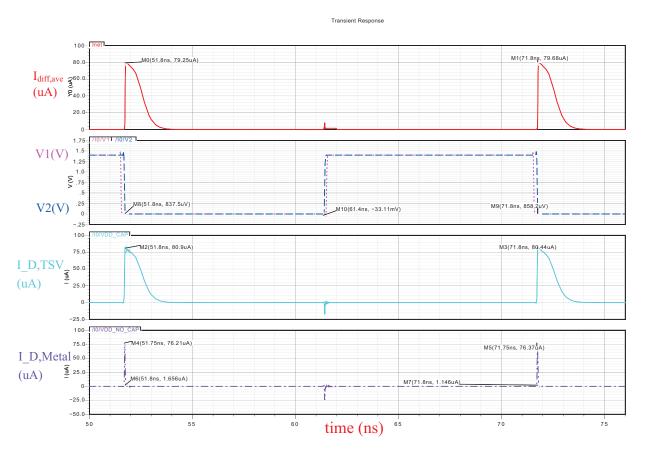

As an aside, the TSV capacitance extraction process described above can be re-developed with respect to variations in the supply voltage. For instance, one can use four different input clock frequencies, say 20 MHz, 40 MHz, 60 MHz and 80 MHz. By sweeping the supply voltage VDD and measuring the difference of the average charging and discharging current  $I_{diff,ave}$ , we can get the plot shown in Fig. 2.30. In this case, the TSV capacitance  $C_{TSV}$  would be derived from the slope of the  $I_{diff,ave}$  versus VDD curve.

**Fig. 2.30** Averaged Difference Current VS. Supply Voltage At Four Different Operating Frequencies

#### 2.5 Conclusion

In this chapter several techniques for characterizing the signal integrity of a TSV in a 3D CMOS process was described. A four-point probe method for measuring the series resistance of a TSV was described. This was then followed by two methods to measure the end-to-end equivalent capacitance of a TSV structure. Each method can be classified as either a frequency-based or charge-based method. In the case of the frequency-based approach, two techniques were described; one involving a single-VCO and the other a two-VCO approach. Here it was shown that the two-VCO approach is less sensitive to switch parasitics and hence the preferred frequency-based method. The charge method is very simple in principle but is subject to mismatches issues. The accuracy of this method improves with supply voltage but, of course, is limited to what the technology can support.

# Chapter 3

# 3D-IC Test Access and DfT Techniques

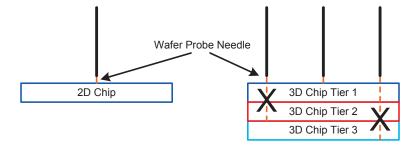

Test access is a popular way to externally stimulate a circuit-under-test (CUT) and extract its response with external instruments. For 2D chips, on-chip circuits can be accessed externally by a wafer probe such as that shown in Fig. 3.1. Here it can be seen that a set of fine needle-like fingers touch down on the surface of a wafer containing many individual dies. Through various metal pads, the probing needles make contact and direct power, control and signalling information to and from each IC. In the case of 3D chips, whereby multiple tiers of dies are stack on top of one another, preventing direct access to dies below the top layer as shown in Fig. 3.2. Here it is shown how the wafer probe can reach tier 1 but not tier 2 and tier 3 of the die stack.

This begs the question, "How does one access the circuits that reside on the various layers of a 3D-chip?" As first mentioned in [13], the use of DfT (Design for Test) techniques had a tremendous impact on the test costs associated with 2D-chip by providing test access through the application of on-chip test circuits. Such an approach is believed to be applicable to 3D-chips are well. This is the subject of this chapter.

DfT refers to adding testability features to microelectronic circuits. When properly implemented, DfT can achieve higher product quality with higher test coverage and lower production costs. Plenty of DfT literature exists for testing digital circuits; very little material can be found on analog or mixed-signal circuits. This chapter will focus on the latter area.

Fig. 3.1 Wafer Probe

$\textbf{Fig. 3.2} \quad \text{Wafer Probe of 2D VS 3D}$

At the core of most, if not all, analog DfT techniques is the conversion between analog and digital signals, generally through the application of analog-to-digital (ADC) or digital-to-analog (DAC) conversion circuits. We'll begin this chapter by first describing the various logic circuits used to capture digital signals. This will then be followed by a discussion of the DfT techniques used for the TSV capacitance measurement techniques described in Chapter 2. Finally, the chapter will close with a discussion of an analog boundary scan technique for accessing internal analog/mixed-signal functions of a 3D-chip.

## 3.1 Digital Logic Gates Designs

Most DfT techniques are implemented using some form of digital logic. This section will describe the basic logic gates used to implement the DfT function of this dissertation.

#### 3.1.1 Inverter Design

The inverter is designed to be simple and have a compact layout. The dimensions of the NMOS and PMOS transistors used in this dissertation are listed in Table 3.1. As is evident, the length of each transistor is assigned the minimum dimension of 0.13  $\mu$ m but the widths are either 1 or 4  $\mu$ m depending on whether it is an NMOS or PMOS transistor. This arrangement provides equal rise and fall times.

Table 3.1 Inverter Dimensions

|             | MN   | MP   |

|-------------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 |

| $W (\mu m)$ | 1    | 2    |

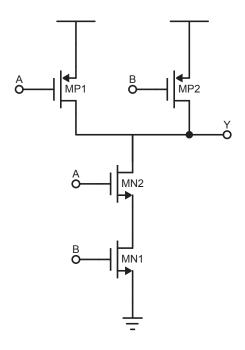

#### 3.1.2 NAND Gate Design

Similar to the inverter design, the NAND gate is also chosen to be simple and have a compact layout. The schematic for the NAND gate is shown in Fig. 3.3. The transistor dimensions are listed in Table 3.2.

Fig. 3.3 NAND Gate

Table 3.2

NAND Gate Transistor Dimensions

|             | MN1  | MN2  | MP1  | MP2  |

|-------------|------|------|------|------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 | 0.13 |

| $W(\mu m)$  | 2    | 2    | 2    | 2    |

#### 3.1.3 NOR Gate Design

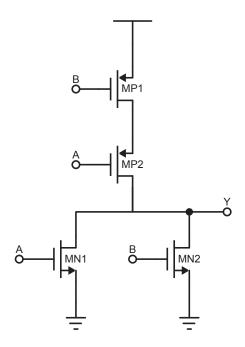

The schematic of the NOR gate can be seen in Fig. 3.4 and the corresponding transistor dimensions are provided in Table 3.3.

Fig. 3.4 NOR Gate

Table 3.3

NOR Gate Transistor Dimensions

|            | MN1  | MN2  | MP1  | MP2  |

|------------|------|------|------|------|

| L (μm)     | 0.13 | 0.13 | 0.13 | 0.13 |

| $W(\mu m)$ | 1    | 1    | 4    | 4    |

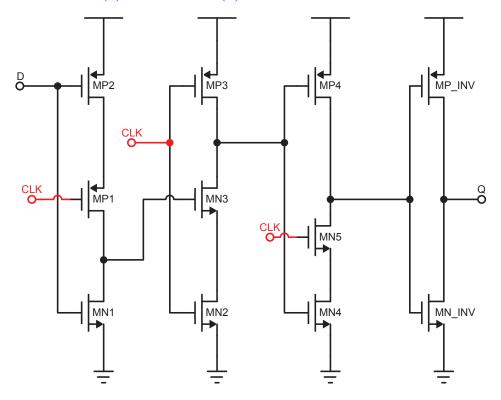

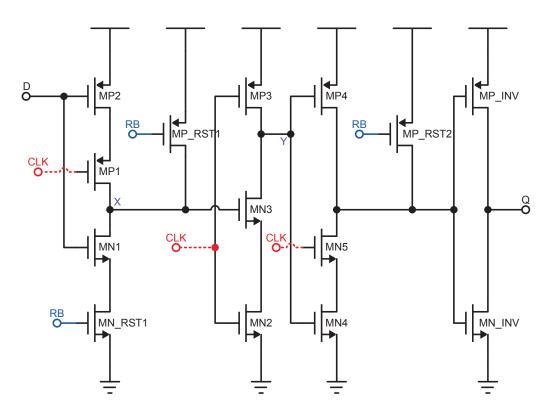

#### 3.1.4 True-Single-Phase Clock D-Type Flip-Flop Design

The true single-phase clock (TSPC) structure [14][15] is used to implement the D-type flip-flop (DFF) used in this work. It provides better performance by introducing a pre-charge stage between stages to speed up the circuit operation. There are two types of TSPC DFFs used in this work; one has a reset function and the other one does not.

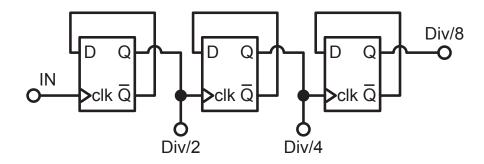

#### TSPC DFF Without Reset

The schematic diagram for the TSPC DFF without reset is shown in Fig. 3.5. This particular DFF will be used as part of a frequency divider circuit. The TSPC DFF without reset will be used to realize a frequency divider circuit. The transistor dimensions can be seen listed in Table 3.4(a) and Table 3.4(b).

Fig. 3.5 TSPC DFF Without Reset

#### TSPC DFF With Reset

The schematic diagram for the TSPC DFF with reset is shown in Fig. 3.6. This particular TSPC DFF will be used in for constructing the counter circuit. The transistor dimensions for this DFF can be seen listed in Table 3.5(a) and Table 3.5(b).

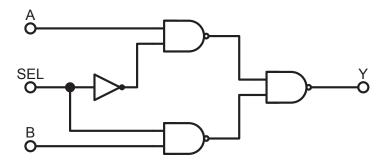

#### 3.1.5 MUX Design

The multiplexer (MUX) acts as a digital switch in order to select the appropriate signal path. It is also used in the implementation of the shift register. The multiplexer is shown

**Table 3.4** Transistor Dimensions For The TSPC DFF Without Reset (a) NMOS Dimensions

| NMOS        | MN1  | MN2  | MN3  | MN4  | MN5  | MN_INV |

|-------------|------|------|------|------|------|--------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 | 0.13 | 0.13 | 0.13   |

| $W(\mu m)$  | 1    | 1    | 1    | 1    | 1    | 1      |

#### (b) PMOS Dimensions

| PMOS       | MP1  | MP2  | MP3  | MP4  | MP_INV |

|------------|------|------|------|------|--------|

| L (μm)     | 0.13 | 0.13 | 0.13 | 0.13 | 0.13   |

| $W(\mu m)$ | 2    | 2    | 2    | 2    | 2      |

Fig. 3.6 TSPC DFF with Reset

**Table 3.5** TSPC DFF with Reset Dimensions (a) NMOS Dimensions

| NMOS        | MN1  | MN2  | MN3  | MN4  | MN5  | MN_RST1   | MN_INV |

|-------------|------|------|------|------|------|-----------|--------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 | 0.13 | 0.13 | 0.13<br>1 | 0.13   |

| $W (\mu m)$ | 1    | 1    | 1    | 1    | 1    | 1         | 1      |

#### (b) PMOS Dimensions

| PMOS        | MP1  | MP2  | MP3  | MP4  | MP_RST1 | MP_RST2 | MP_INV |

|-------------|------|------|------|------|---------|---------|--------|

| $L (\mu m)$ | 0.13 | 0.13 | 0.13 | 0.13 | 0.13    | 0.13    | 0.13   |

| $W (\mu m)$ | 2    | 2    | 2    | 2    | 2       | 0.13 2  | 2      |

in Fig. 3.7 consisting of the previously described logic gates.

Fig. 3.7 Multiplexer

# 3.2 Support Circuits For FBCM

In this section, we'll look at the DfT techniques and support circuits used for FBCM described previously in Chapter 2. This includes the frequency-to-digital converter (FDC) and the PISO shift register design.

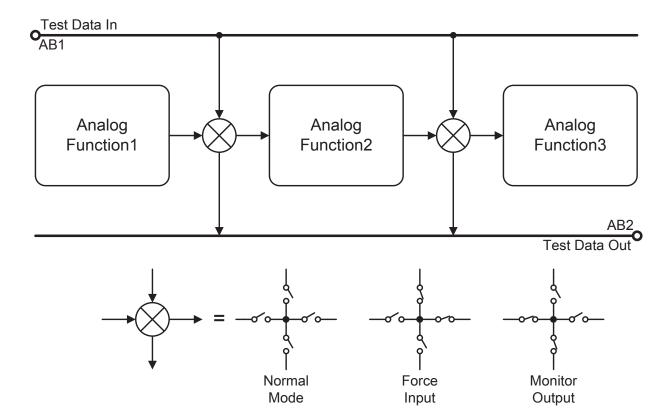

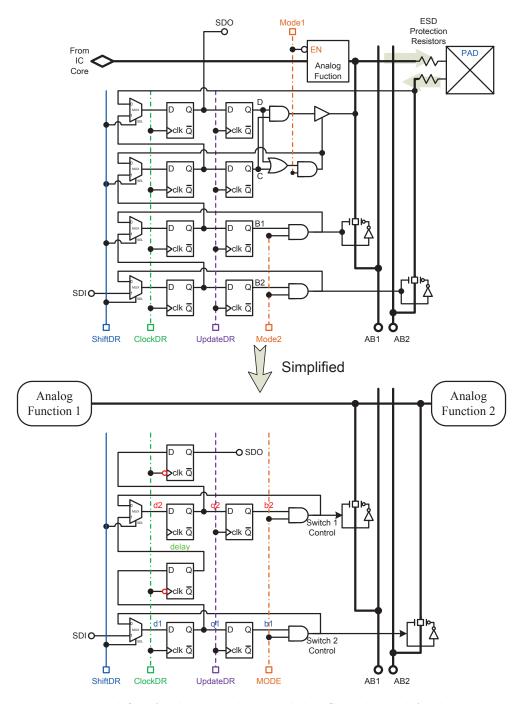

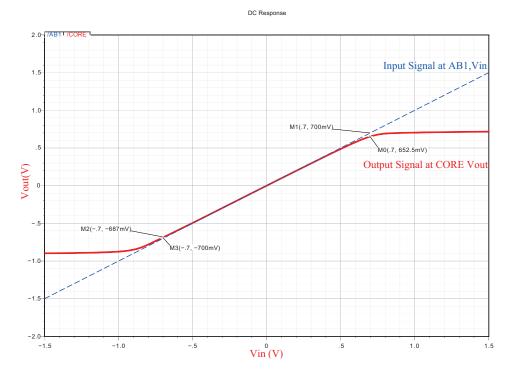

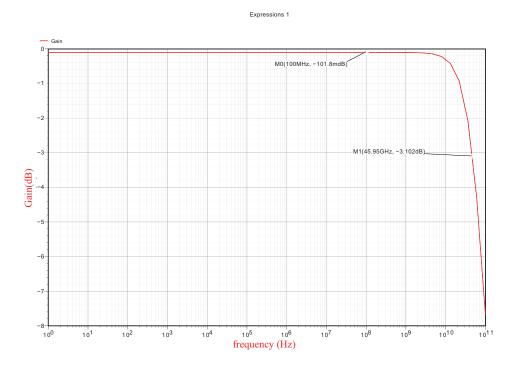

#### 3.2.1 Frequency-to-Digital Converter