# Temperature compensation of oscillators using a phaselocked loop with a thermal feed-back

By

Seyed Ali Gorji Zadeh, M.A.Sc.

Department of Electrical and Computer Engineering

McGill University, Montreal, Quebec, Canada

January, 2023

A thesis submitted to McGill University

In partial fulfilment of the requirements of the degree of

Doctor of Philosophy

©Copyright 2023

All rights reserved.

To whom who knows everything

## **ACKNOWLEDGMENTS**

First of all, I would like to thank my supervisor, professor Mourad El-Gamal who his continuous support made it possible to finish this journey. In addition to insightful technical advice throughout my PhD work, he made invaluable guidance in directing the research and showed me how to see the big picture. In addition to his financial support, the productive environment he provided by creating the Wireless ICs and MEMS Laboratory (formerly known as RFIC lab) at McGill University was a unique opportunity for learning and collaboration with bright minds. These bright minds that I enjoyed friendship, scientific discussions and collaborations with include Karim Alladina, Paul-Vaheh Cicek, Fredrik Nabki, Mahdi Parvizi, Mohannad Elsayed, Rania Mekki, Hani Towfik, Sareh Mahdavi and Tanmoy Saha.

My special gratitude goes to professor Fredrik Nabki who has been a constant help in proceeding in this journey and has given me numerous insightful pieces of advice.

Very importantly, I should thank my family, my wife Maede, my parents Seyed Abbas and Ashraf, my sisters Raheleh and Faezeh and my brother Mohammad. They have given me the meaning of life and the endeavour for achieving in life.

Finally, I would like to thank the Vadasz Family Foundation for the generous contributions in awarding me with the Vedas doctoral fellowship in engineering, which was a great help in starting my PhD studies.

# TABLE OF CONTENTS

| DEDICATION                                                                          | ii   |

|-------------------------------------------------------------------------------------|------|

| TABLE OF CONTENTS                                                                   | V    |

| LIST OF TABLES                                                                      | . xi |

| LIST OF FIGURES                                                                     | xii  |

| Chapter 1 Introduction                                                              | 1    |

| 1.1 Motivation                                                                      | 1    |

| 1.2 Research Goal                                                                   | 2    |

| 1.3 Contributions                                                                   | 4    |

| 1.3.1 Proposing a Temperature Compensation Scheme Using Temperature                 |      |

| Controlled Oscillators in a Phase-Locked Loop Configuration                         | 4    |

| 1.3.2 Modeling and Analysis of Temperature Compensation Capability of the           |      |

| Proposed Scheme                                                                     | 4    |

| 1.3.3 Analysis of the Phase Noise of a Dual Oscillator PLL System                   | 5    |

| 1.3.4 Analysis, Application, and Measurements of the Filtering Effect of the Heater | s    |

| in the Whole PLL System                                                             | 5    |

| 1.3.5 Implementing the Proposed System Along with the Integrated Heaters in         |      |

| CMOS Technology                                                                     | 6    |

| 1.3.6 Feasibility Study of Using the Proposed Temperature Compensation Scheme       |      |

| for MEMS-based Oscillators                                                          | 6    |

| 1.4 Thesis Outline                                                                  | 7    |

|                                                                                  | 8           |

|----------------------------------------------------------------------------------|-------------|

| 2.1 Introduction                                                                 | 8           |

| 2.2 Bandgap Voltage Reference                                                    | 8           |

| 2.3 Bandgap Current Reference10                                                  | 0           |

| 2.4 Temperature Compensation in Sensors10                                        | 0           |

| 2.5 Temperature Compensation in Oscillators1                                     | 1           |

| 2.5.1 Crystal Based and non-Integratable Oscillators1                            | 1           |

| 2.5.2 MEMS-Based Oscillators12                                                   | 2           |

| 2.5.3 All Silicon Oscillators                                                    | 3           |

| 2.6 Summary and Conclusion                                                       | 3           |

| Chapter 3 System Description and Analysis of the Proposed Scheme for Temperature |             |

|                                                                                  |             |

| Compensation14                                                                   | 4           |

| Compensation                                                                     |             |

|                                                                                  | 4           |

| 3.1 Introduction14                                                               | 4           |

| 3.1 Introduction                                                                 | 4           |

| 3.1 Introduction                                                                 | 4<br>4<br>8 |

| 3.1 Introduction                                                                 | 4<br>4<br>8 |

| 3.1 Introduction                                                                 | 4<br>4<br>8 |

| 3.3.1.1 Micro-heater modeling                                                    | 24    |

|----------------------------------------------------------------------------------|-------|

| 3.3.1.2 Heating system replacing the charge pump and the loop filter             | 28    |

| 3.3.1.3 Proportional and integral and higher frequency parts of the heating      |       |

| system transfer function                                                         | 32    |

| 3.3.2 Analysis of the System Response to Step and Ramp of Ambient Tempera        | ture  |

|                                                                                  | 34    |

| 3.4 Effects of Having Two Separate Micro-heaters on the System Performance       | 35    |

| 3.5 Summary and Conclusion                                                       | 39    |

| Chapter 4 Phase Noise of a Dual Loop PLL for Temperature Compensation of Oscilla | ators |

|                                                                                  | 40    |

| 4.1 Introduction                                                                 | 40    |

| 4.2 System Description                                                           | 40    |

| 4.2.1 Temperature Compensation Scheme                                            | 40    |

| 4.2.2 Phase Noise Interaction                                                    | 42    |

| 4.3 System Analysis                                                              | 43    |

| 4.3.1 Linear Approximation                                                       | 43    |

| 4.4 Simulation Results                                                           | 49    |

| 4.4.1 System Response in Simulink                                                | 49    |

| 4.4.2 Phase Noise Simulation in Verilog-A                                        | 51    |

| 4.5 Summary and Conclusion                                                       | 54    |

| ,                                                                                |       |

| Chapter 5 Simulating a Dual Loop PLL for Temperature compensation of MEMS based |

|---------------------------------------------------------------------------------|

| oscillators55                                                                   |

| 5.1 Introduction55                                                              |

| 5.2 System Description55                                                        |

| 5.2.1 MEMS Resonator55                                                          |

| 5.2.2 Temperature Compensation Scheme                                           |

| 5.3 System Analysis59                                                           |

| 5.3.1 Linear Approximation59                                                    |

| 5.3.1.1 Steady State Response of Frequency to Ambient Temperature61             |

| 5.3.1.2 Instantaneous Frequency of Frequency to Ambient Temperature Change      |

| 62                                                                              |

| 5.3.2 Circuit Implementation64                                                  |

| 5.3.2.1 Divider, PFD, and CP65                                                  |

| 5.3.2.2 Loop Filter65                                                           |

| 5.3.2.3 Output Buffer                                                           |

| 5.4 Simulation Results                                                          |

| 5.4.1 System Level Simulation Results66                                         |

| 5.4.2 Circuit Level Simulation Results68                                        |

| 5.4.2.1 Temperature Step Response68                                             |

| 5.4.2.2 Temperature Ramp70                                                      |

| 5.5 Summary and Conclusion                                                       | 71   |

|----------------------------------------------------------------------------------|------|

| Chapter 6 CMOS Implementation of a Dual Loop PLL for Temperature compensation    | of   |

| Silicon based oscillators                                                        | 72   |

| 6.1 Circuit Implementation                                                       | 72   |

| 6.1.1 Micro Heater Structure and Behavior                                        | 72   |

| 6.1.2 Heaters of the Ring Oscillator                                             | 72   |

| 6.1.3 CMOS TCO                                                                   | 76   |

| 6.1.4 Frequency Divider, PFD, CP and Loop Filter                                 | 80   |

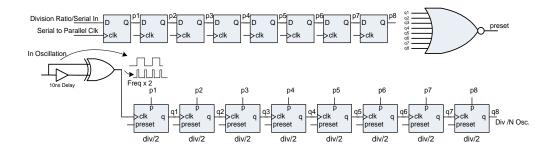

| 6.1.4.1 Frequency Divider                                                        | 80   |

| 6.1.4.2 Phase Frequency Detector                                                 | 81   |

| 6.1.4.3 Charge Pump                                                              | 82   |

| 6.1.4.4 Loop Filter                                                              | 83   |

| 6.1.4.5 Micro-heater Filtering Effect and Circuit Simplifications                | 83   |

| 6.1.5 Output Buffer for Heaters                                                  | 84   |

| 6.2 Measurement Results                                                          | 86   |

| 6.2.1 CMOS Current-Starved Ring Oscillator                                       | 87   |

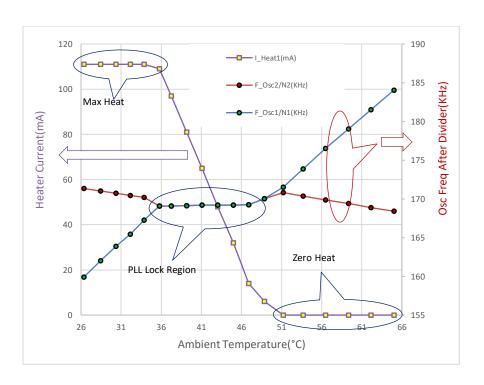

| 6.2.2 Closed-loop Temperature Compensated Results                                | 89   |

| 6.2.3 Heater power and its limiting effect on the range of temperature compensat | tion |

|                                                                                  | 89   |

| 6.2.4 Temperature compensation capability of the system                          | 91   |

| 6.   | .3 Summary and Conclusion                                                      | .94 |

|------|--------------------------------------------------------------------------------|-----|

| Cha  | pter 7 Conclusion                                                              | .95 |

| 7.   | .1 Research Summary                                                            | .95 |

| 7.   | .2 Future Work                                                                 | .98 |

|      | 7.2.1 Implementing One Micro-heater for Both Oscillators                       | .98 |

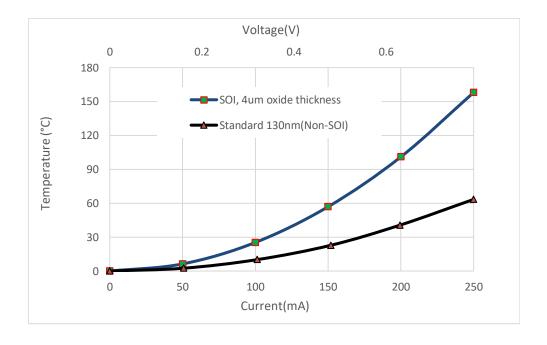

|      | 7.2.2 Implementation in More Heat Preserving Technologies Like SOI             | .98 |

|      | 7.2.3 Using the Current Scheme Concurrently with Other Electronic Temperature  |     |

|      | Compensation Schemes                                                           | .98 |

|      | 7.2.4 Study and Measurements of the Phase Noise of the Oscillators Used in the |     |

|      | Proposed Scheme                                                                | .99 |

| LIST | Γ OF REFERENCES1                                                               | 100 |

# LIST OF TABLES

| Summary of system design values.                                | 65 |

|-----------------------------------------------------------------|----|

|                                                                 |    |

| Output frequency variation of resonator 1 vs. temperature ramps | 70 |

# LIST OF FIGURES

| Figure 2-1. Brokaw bandgap reference voltage circuit 9                                     |

|--------------------------------------------------------------------------------------------|

| Figure 3-1. The difference between the slopes of the two lines produces the feedback       |

| force                                                                                      |

| Figure 3-2. Block diagram of a possible realization of the PLL-based compensation          |

| system17                                                                                   |

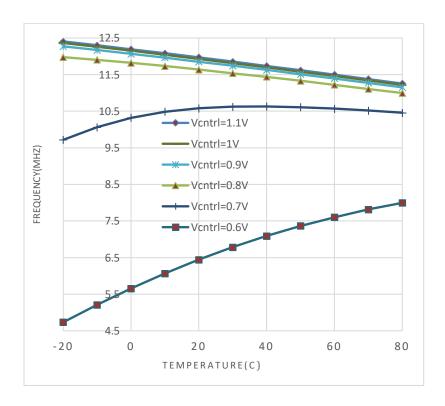

| Figure 3-3. Simulated effect of temperature on the oscillation frequency at different      |

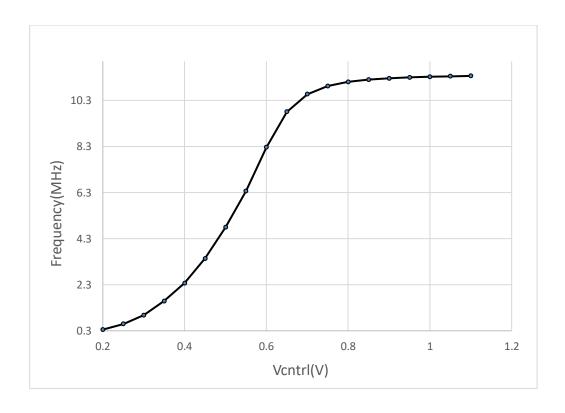

| control voltages (Vcntrl)19                                                                |

| Figure 3-4. Crossing at two points can be avoided by using a higher slope difference       |

| between the two oscillators21                                                              |

| Figure 3-5. Linearized model of the proposed system23                                      |

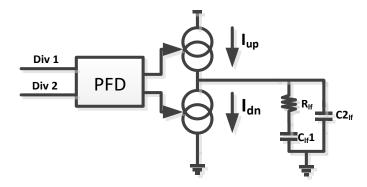

| Figure 3-6. The heating system model and its equivalent electrical circuits24              |

| Figure 3-7. A typical type II PLL has a charge pump and a loop filter with one pole at the |

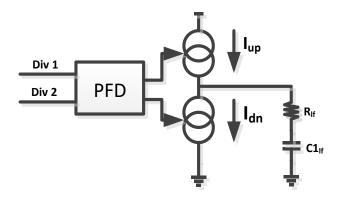

| origin and one zero(a) or a pole-zero pair at higher frequencies for stability reasons27   |

| Figure 3-8. Second order RC circuit modeling the heating system29                          |

| Figure 3-9. Second order modeling of the heating system                                    |

| Figure 3-10. Second order effect of the heating system can produce the effect of the loop  |

| filter31                                                                                   |

| Figure 3-11. A first order model of the heating system plus a gain stage can be good       |

| approximation of the system in the frequencies in the bandwidth of the PLL34               |

| Figure 3-12. Linearized model of the system where each oscillator has a separate mid  | cro- |

|---------------------------------------------------------------------------------------|------|

| heater                                                                                | 36   |

| Figure 3-13. Simplified model of the system with two separate micro-heaters           | 37   |

| Figure 4-1. The difference between the slopes of the two lines produces the feedback  |      |

| force.                                                                                | 41   |

| Figure 4-2. Linearized model of the system.                                           | 42   |

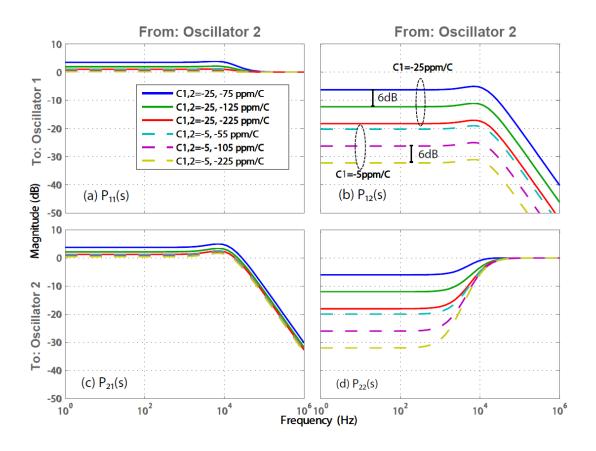

| Figure 4-3. Phase noise contribution by each block of the system                      | 46   |

| Figure 4-4. Transfer functions of the phase noise generated in each oscillator to the |      |

| output of either oscillator.                                                          | 50   |

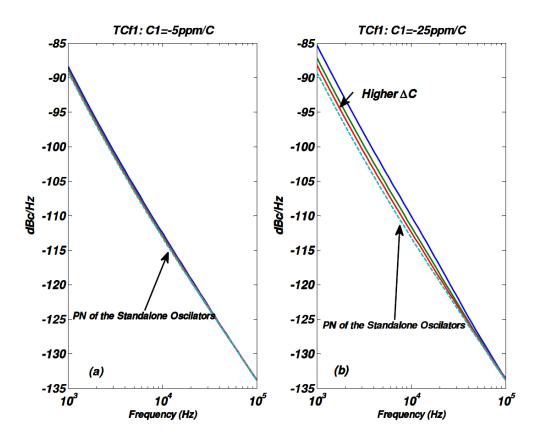

| Figure 4-5. Phase noise observed at the output of Oscillator 1 when both oscillators  |      |

| generate equal phase noise, for $\Delta C$ =50, 100, 200 ppm/°C                       | 52   |

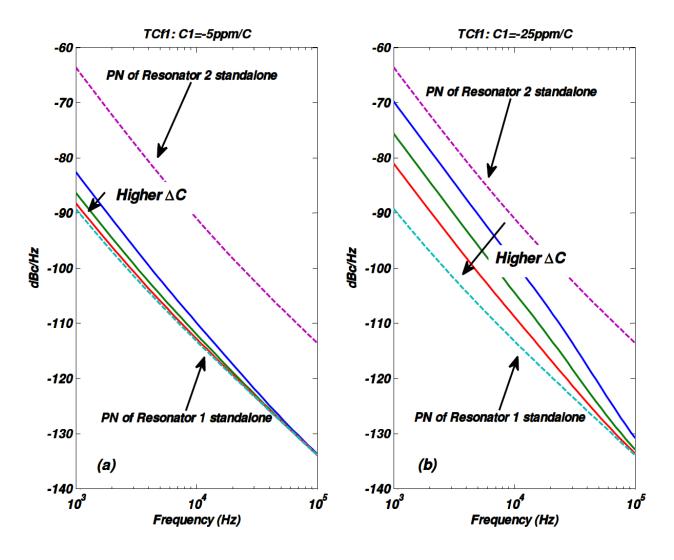

| Figure 4-6. Phase noise generated at the output of Oscillator 1 (MEMS resonator-bas   | ed)  |

| when Oscillator 2 (all CMOS-based) generates a much higher phase noise than           |      |

| Oscillator 1, for $\Delta C$ =50,100,200ppm/°C.                                       | 53   |

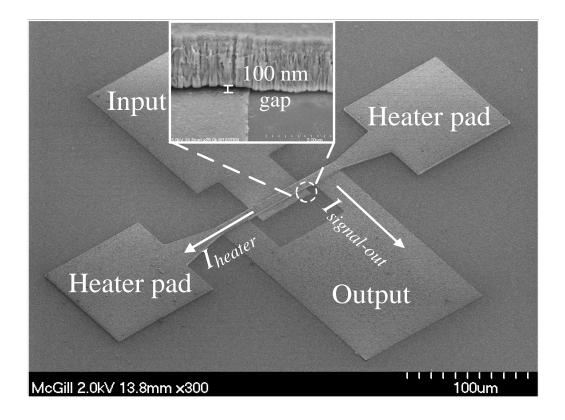

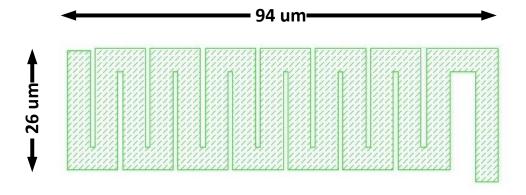

| Figure 5-1. Micrograph of the resonator with a micro-heater                           | 56   |

| Figure 5-2. Block diagram of the compensation system                                  | 58   |

| Figure 5-3. Frequencies at the outputs of both dividers vs. temperature               | 59   |

| Figure 5-4. Linearized model of the proposed system                                   | 60   |

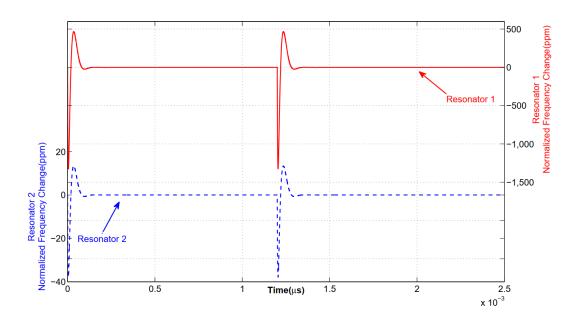

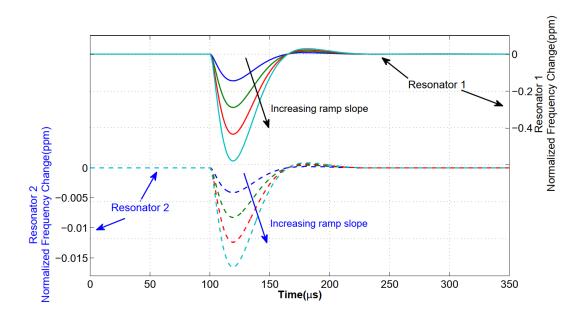

| Figure 5-5. Resonators' frequency change caused by temperature ramps                  | 67   |

| Figure 5-6. Step response of the system simulated in Simulink MATLAB                  | 67   |

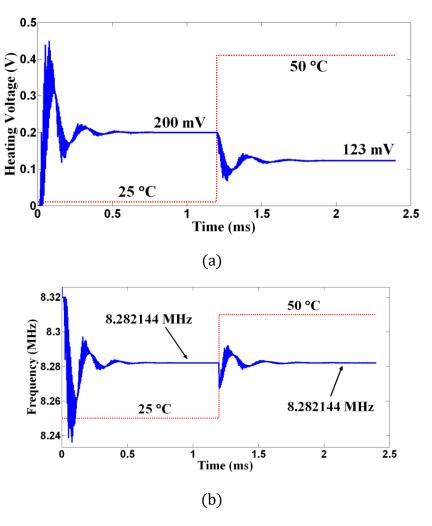

| Figure 5-7. (a) Control voltage and (b) output frequency of resonator 1 in response to a       |

|------------------------------------------------------------------------------------------------|

| step ambient temperature change69                                                              |

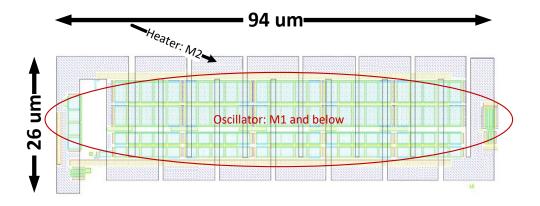

| Figure 6-1 Layout mask of the M2 metal layer the micro-heater is built from73                  |

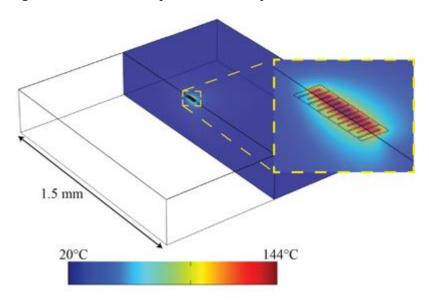

| Figure 6-2 COMSOL Multiphysics is used to obtain an estimation of the micro-heater             |

| behavior on the die74                                                                          |

| Figure 6-3 The layout of the oscillator and the micro-heater on top of it74                    |

| Figure 6-4 Thermal simulation results showing temperature change vs. current biasing of        |

| the micro-heater for both standard bulk and SOI technology75                                   |

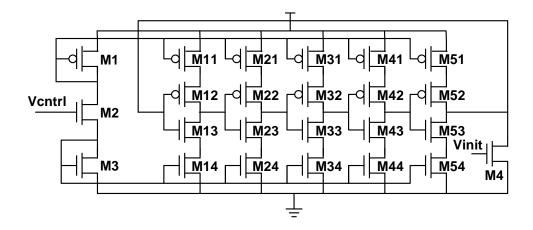

| Figure 6-5 Current-starved CMOS ring oscillator                                                |

| Figure 6-6 Frequency of oscillation vs. starvation control voltages at a temperature of        |

| 87°C                                                                                           |

| Figure 6-7 Simulated effect of temperature on the oscillation frequency at different control   |

| voltages (Vcntrl)                                                                              |

| Figure 6-8. If the slope of the frequency to temperature curves of the two oscillators are     |

| pushed away from each other, the possibility that they can meet each other at two              |

| different points can be removed80                                                              |

| Figure 6-9 Frequency divider and the serial to parallel shift register to receive the division |

| ratio serially81                                                                               |

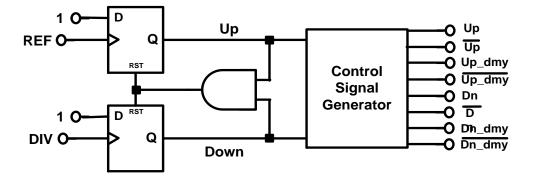

| Figure 6-10 Phase Frequency detector with control signal generator81                           |

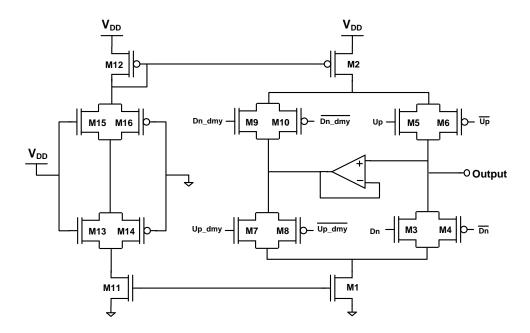

| Figure 6-11 Charge pump used in the circuit implementation82                                   |

| Figure 6-12 The loop filter that can be eliminated in this system.                             |

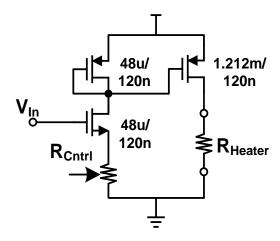

| Figure 6-13. High power buffers for the heater indicating the W/L ratios of all transistors. |    |

|----------------------------------------------------------------------------------------------|----|

| 3                                                                                            | 34 |

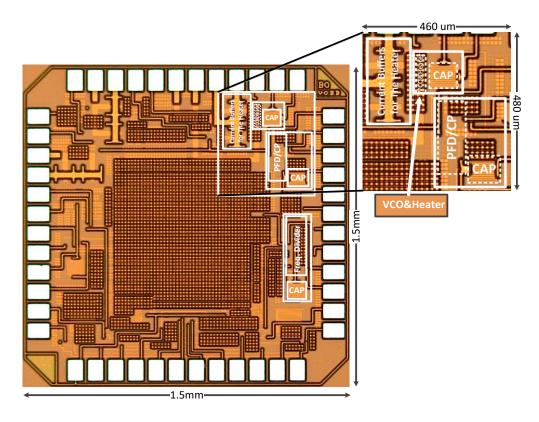

| Figure 6-14. Die micrograph with active area outlined                                        | 36 |

| Figure 6-15. The PCB designed to test the compensation scheme using the fabricated           |    |

| chip                                                                                         | 37 |

| Figure 6-16. Frequency of oscillation vs. current starving control voltages                  | 38 |

| Figure 6-17. How the heater current limits PLL lock region current                           | 90 |

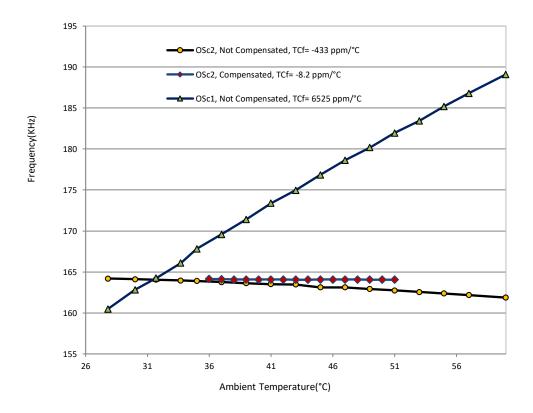

| Figure 6-18. <i>TCf</i> of oscillators with and without compensation                         | 92 |

# LIST OF ABBREVIATIONS

ADC Analog to Digital Converter

CMOS Complementary Metal-Oxide-Semiconductor

CP Charge Pump

CTAT Complimentary to Absolute Temperature

DAC Digital to Analog Converter

IoT Internet of Things

MEMS Micro-Electromechanical Systems

OCXO Oven Controlled Crystal Oscillator

PCB Printed Circuit Board

PFD Phase-Frequency Divider

PLL Phase-locked Loop

PPM Parts Per Million

PTAT Proportional to Absolute Temperature

PVT Process, Voltage, Temperature

Q Quality Factor

SiC Silicon Carbide

SOI Silicon on Insulator

TCF temperature Coefficient of Frequency

TCO Temperature Controlled Oscillator

VCO Voltage Controlled Oscillator

XO Crystal Oscillator

#### **ABSTRACT**

Using an integrated micro-heater and a phase-locked loop (PLL) configuration, a technique to create a temperature-insensitive area on a die is described. The proposed PLL configuration employs thermal feedback through the micro-heater to significantly improve the temperature stability of the die area.

Two oscillators are employed in the PLL to act as temperature sensors to detect the ambient temperature variations and command the thermal loop to compensate them. The temperature stability of these oscillators located in the temperature-compensated die area is improved significantly and can provide a stable timing signal needed for the system. The temperature compensation of oscillators provided by this technique is studied in more detail.

Design methodologies and system-level analysis are presented. An application on temperature compensation of MEMS-based oscillators is studied with analysis and simulations. Based on these preliminary steps, an all-CMOS test-chip for proof-of-concept is designed and fabricated using a standard 130 nm CMOS technology. Analysis and experimental results show that the micro-heating system employed in this technique can provide

a low pass filtering effect enough to replace the electrical low pass filtering effect provided by a charge pump and a loop filter. Therefore, the charge pump and the loop filter existing in the conventional PLL loops can be eliminated in this system.

Test characterization of the realized proof-of-concept chip shows that the temperature stability of the die area can be improved by a factor as large as 50x for an ambient temperature range of 36°C to 52°C. Simulation shows that this range can be improved by many folds using more heat preserving technologies like SOI CMOS instead of bulk CMOS.

# **ABRÉGÉ**

L'invention concerne une technique pour créer une zone insensible à la température sur une puce à l'aide d'un micro-réchauffeur intégré et d'une configuration de boucle à verrouillage de phase (PLL). La configuration PLL proposée utilise une rétroaction thermique à travers le micro-réchauffeur pour améliorer considérablement la stabilité de la température de la zone de la matrice.

Deux oscillateurs employés dans la PLL agissent comme des capteurs de température pour détecter les variations de température ambiante et commander à la boucle thermique de les compenser. La stabilité en température de ces oscillateurs situés dans la zone de matrice à compensation de température est améliorée de manière significative et peut fournir un signal de synchronisation stable nécessaire pour le système. La compensation de température des oscillateurs fournie par cette technique est étudiée plus en détail.

Les méthodologies de conception et l'analyse au niveau du système sont présentées. Une application sur la compensation de température des oscillateurs à base de MEMS est étudiée avec analyse et simulations. Sur la base de ces étapes préliminaires, une puce de test entièrement CMOS pour la preuve de concept est conçue et fabriquée à l'aide d'une technologie

CMOS 130 nm standard. L'analyse et les résultats expérimentaux montrent que le système de micro-chauffage utilisé dans cette technique peut fournir un effet de filtrage passe-bas suffisant pour remplacer l'effet de filtrage passe-bas électrique fourni par une pompe de charge et un filtre à boucle. Par conséquent, la pompe de charge et le filtre de boucle existant dans les boucles PLL classiques peuvent être éliminés dans ce système.

La caractérisation de test de la puce de preuve de concept réalisée montre que la stabilité de la température de la zone de la matrice peut être améliorée d'un facteur aussi grand que 50x pour une plage de température ambiante de 36 ° C à 52 ° C. Il est démontré par simulation que cette gamme peut être améliorée par de nombreux plis en utilisant davantage de technologies de préservation de la chaleur comme SOI CMOS au lieu du CMOS en masse.

# Chapter 1 Introduction

#### 1.1 Motivation

Nowadays, electronic devices are required more than ever to operate in various environmental conditions with little or no degradation in performance. Temperature is one of these environmental conditions that vary in many applications. There have been numerous circuit techniques to compensate for the effect of temperature on the performance of electronic systems. For decades, bandgap reference circuits have been designed specifically to address the need for temperature-stable circuits.

More recently, the ever-growing applications of high-resolution and high-speed data converters, including digital-to-analog converters (DACs) and analog-to-digital converters (ADCs), have demanded high-precision voltage references. This has made temperature compensation techniques for bandgap reference still relevant to the research community [1-5].

Similarly, obtaining stable current references is very important for many mixed-signal applications like current-mode analogue-to-digital converters (ADCs). The research is still conducted to improve these circuits [6-9].

With the introduction and spread of the internet of things (IoT) and sensor networks, more and more sensors are used in electronic circuits and compensation of the effect of temperature on them has been a demanded area for researchers [10-14].

In addition, in digital systems, timing circuits as important components of the system, require reference oscillators that must yield a stable frequency under all operating conditions. Temperature compensation techniques have been proposed and are still being investigated by researchers for all the different types of oscillators, consisting of quartz crystal oscillators [15-18], microelectromechanical systems (MEMS) based oscillators [19-28], and all-silicon integrated oscillators [29-44].

The temperature compensation techniques proposed to date are mostly based on the use of circuits or devices with lower intrinsic temperature sensitivity [24], or the addition of a component with an opposite temperature sensitivity to cancel out the temperature sensitivity of the circuit, mostly in an open-loop fashion [42, 45]. In all of these temperature compensation techniques, it is assumed that the ambient temperature can change the temperature of the system and the circuit under investigation. However, an extra level of temperature compensation can be added on top of these techniques that is maintaining the temperature of the circuits and devices fixed in the presence of ambient temperature variations. In this method, variations in the ambient temperature are sensed, and heating (in some cases, a cooling system) serves to counteract this effect on the system. This is accomplished by providing more heat to the system when the ambient temperature drops and less when the ambient temperature increases. This is the same familiar scheme used at the macroscopic scale to regulate the ambient temperature in living spaces using thermostats in heating systems or air conditioning systems. This scheme has been of interest for the semiconductor circuit research community for a long time. It has been used for temperature compensation of reference signal generators [46-48] and for creating highly stable OCXOs [15, 17]. In addition, more recently, it has been applied to microelectromechanical systems (MEMS)-based oscillators [26, 49-53].

The interesting aspect of this method is that it can be applied to the system concurrently with other temperature compensation methods, which can significantly reduce the temperature sensitivity of the system.

#### 1.2 Research Goal

This research work aims to propose an integrated temperature compensation scheme to counteract the effect of the ambient temperature change on the system. It explores the use of oscillators as temperature sensors to detect ambient temperature variations and compensate for its effect on the oscillators and the die area surrounding them by employing thermal feedback made in a PLL configuration leveraging micro-heaters. Electrothermal integrated circuits have been under study since the 70s [54-56]. Compared to other works using integrated heaters, the work here attempts to bring some added perspective to the

heating system architecture by considering a model similar to a typical PLL and adding new implementation aspects. Notably, a combination of analysis and measurements, including electro-thermal simulation, system-level analysis and simulations, and fabrication results are detailed here and have not been reported before.

In this research, a scheme is proposed for temperature compensation for a CMOS die area. This temperature compensation scheme aims to keep the temperature of the die area fixed while the ambient temperature changes. For this purpose, there is a need for a heating system (or, if possible, a cooling system) to provide heat when it is needed to counteract the effect of the ambient temperature changes. In addition, there is a need for a sensor to sense the ambient temperature variations and send this information through a commanding (possibly feedback) path to the heating system. In short, it can be said that the three main components of this system are the heating system, the sensory one, and the commanding path.

On the other hand, one important issue that oscillators encounter is their temperature sensitivity. Generally, the frequency that an oscillator generates is highly dependent on the temperature it operates in, and efforts to compensate for the temperature sensitivity of oscillators have been going on for decades [29].

Using this property of oscillators as an advantage and using the temperature sensitivity of the oscillators to sense the temperature variations in a temperature compensation system can be a fascinating idea. This way, the temperature sensitivity of an oscillator is used to provide a temperature-stable environment which in turn can place an oscillator that is less affected by the ambient temperature changes.

To use the frequency of an oscillator as a temperature sensor, it needs to be compared with a reference point. One natural candidate for this is using a second oscillator and a phase-locked-loop (PLL) to compare the frequency of the two oscillators feeding it. To use a second oscillator as a reference point, the two oscillators should have different temperature sensitivity. Therefore, when their temperature changes, their frequency changes at a different rate compared to one another. Hence, the PLL can detect this change and generate

a different command signal for the heating system. This will form a feedback system from the oscillators, PLL, and the heating system, which can reduce the temperature sensitivity of the oscillators and the environment this system is affecting.

#### 1.3 Contributions

The contribution of this work can be described in the below categories.

# 1.3.1 Proposing a Temperature Compensation Scheme Using Temperature Controlled

#### Oscillators in a Phase-Locked Loop Configuration

As mentioned, the difference between frequencies of two oscillators with different Temperature Coefficients of frequency (TCf) can create a signal that can be used in a feedback loop to keep the temperature and consequently the frequency of oscillators fixed. A new scheme for temperature compensation of electronic circuits in general and oscillators specifically was proposed based on this idea. This scheme uses a new PLL structure that has not been analyzed before, and it is designed with an integration possibility in mind.

# 1.3.2 Modeling and Analysis of Temperature Compensation Capability of the Proposed

#### Scheme

The proposed temperature compensation scheme is simplified with a linear model, and this linear model is used to analyze the behavior of the system and its temperature compensation capability. Since the system has both electrical and thermal components, mathematical models of both domains are combined, and the insight from the analysis is used for predicting and improving the system.

A simulation verification of the analysis also is performed in this work.

The contributions associated what mentioned in sections 1.3.1 and 1.3.2 are highlighted below [57]. The author's contribution was to generate the main idea of the work and also to design, analyze, the circuit level and system level simulations. The contribution of K. Allidina was

advice on circuit simulation and providing some circuit models for circuit simulation. The contribution of T. Saha, has been in circuit level simulations and the contributions of M.N. El-Gamal and F. Nabki has been in general guidance and advice of the direction of the research.

**S. A. Gorji Zadeh**, T. Saha, K. Allidina, F. Nabki and M. N. El-Gamal, "Electronic temperature compensation of clamped-clamped beam MEMS resonators," *2010 53rd IEEE International Midwest Symposium on Circuits and Systems*, 2010, pp. 1193-1196.

## 1.3.3 Analysis of the Phase Noise of a Dual Oscillator PLL System

To examine the phase noise behavior of the whole system when there are two oscillators with possibly different phase noise, an analysis of the phase noise of a dual oscillator PLL system is performed. A system-level behavior simulation accompanies this analysis for verification purposes.

The contributions associated with this work are mostly highlighted below [49]. The author's contribution was to define the main idea of the work and perform the analysis and run the simulation. The contribution of M.N. El-Gamal and F. Nabki has been in general guidance and advice of the direction of the work conducted.

**S. A. Gorji Zadeh**, M. N. El-Gamal and F. Nabki, "The phase noise of an oscillator employing a dual MEMS resonator temperature compensation scheme," *2010 International Conference on Microelectronics*, 2010, pp. 160-163,

# 1.3.4 Analysis, Application, and Measurements of the Filtering Effect of the Heaters in the Whole PLL System

The heating system used in this design consists of micro-heaters, and they are simplified, and a linear model is analyzed in the system analysis. Based on this analysis, the PLL loop is implemented using the loop filter effect obtained from the heating system. Second-order modeling and analysis of the heating system show that the heating system has a filtering effect in time and frequency domain, which can replace the filtering that a loop filter in a

standard PLL system can provide. Step response tests and measurements are performed on the micro-heater in this work to demonstrate how this filtering effect behaves. All these are new contributions of this work.

## 1.3.5 Implementing the Proposed System Along with the Integrated Heaters in CMOS

## Technology

An integrated implementation of the proposed scheme is performed using IBM CMOS 130nm technology. The system that is designed and implemented for this purpose consists of onchip micro-heaters and all building blocks of PLLs. This includes current-starved ring oscillators, frequency dividers, phase-frequency detectors (PFDs), charge pumps, and the buffers needed for the heaters.

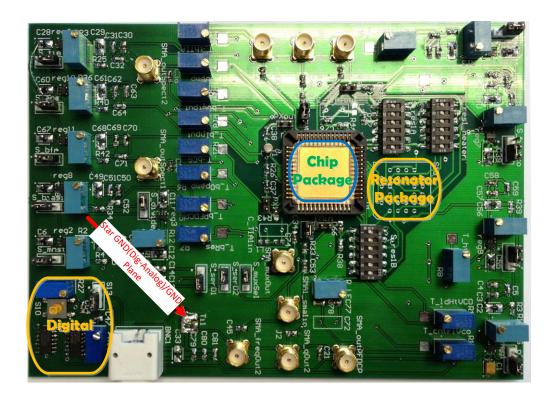

The whole dual oscillator system implemented for this work is tested with a printed circuit board (PCB) designed for this purpose.

## 1.3.6 Feasibility Study of Using the Proposed Temperature Compensation Scheme for

#### **MEMS-based Oscillators**

The possibility of using the proposed structure in an integrated way with MEMS-based oscillators is explored in this thesis. This is performed by examining the temperature behavior of the in-house fabricated MEMS resonators and simulations and analysis.

The contributions associated with the work mentioned in sections 1.3.4 to 1.3.6 are highlighted below [58]. The author's contribution was to generate the main idea of the work, analysis, simulation, and system and circuit design for the proof of concept. To this end, preparing the layout for fabrication of the test chip, designing the PCB for testing the circuit and running measurement are performed by the author. The contribution of K. Allidina was to provide PFD/CP circuits and advice on circuit implementations. The contribution of P. V. Cicek has been in MEMS resonator's behavior description, and COMSOL simulations of heat dissipation in bulk and SOI die

fabrication. The contributions of M.N. El-Gamal and F. Nabki have been in general guidance and advice of the direction of the research conducted.

**S. A. Gorji Zadeh**, K. Allidina, P. V. Cicek, F. Nabki, and M. N. El-Gamal, "CMOS die area temperature compensation using a phase-locked loop with thermal-feedback," Analog Integrated Circuits and Signal Processing, vol. 113, no. 3, pp. 315-329, 2022/12/01 2022.

#### 1.4 Thesis Outline

An overview of schemes for temperature compensation is presented in Chapter II. The proposed scheme of this work is described and analyzed in chapter III. In chapter IV, the phase noise behavior of the system with two oscillators is analyzed, and in chapter V, the possible application of this scheme for temperature compensation of MEMS-based oscillators is analyzed and modeled using simulations. Chapter VI explains the implementation of the proposed temperature compensation for an all-silicon oscillator system and presents the results and discussions, while chapter VII makes the conclusion.

# Chapter 2 Overview of Temperature Compensation in Electronic Circuits

#### 2.1 Introduction

As a warm-blooded creature, human has always needed to keep the variations of the temperature of his body limited in different environmental conditions. The use of cloth and even taking caves as a shelter has partly been due to this need. As warm-blooded creatures, compared to cold-blooded ones, have more robust performance, providing a controlled environment with limited variations helps in getting a steady performance from a system located in that environment.

Obtaining robust and predictable behavior from electronic systems is an objective in most of these systems. To achieve this, one important design aspect for electronic systems is their robust and controlled performance in the presence of temperature variations.

Therefore, numerous ways to compensate temperature sensitivity of electronic systems and their circuits have been introduced. This chapter will introduce an overview of the main electronic systems and circuits used for temperature compensation. The main electronic temperature compensation systems will be discussed in the coming sections.

### 2.2 Bandgap Voltage Reference

Providing a circuit that generates a stable voltage reference is essential for any analog mixed-signal circuits design. The signal generated by this block is used for analog-to-digital converters (ADCs), digital-to-analog converters (DACs), voltage regulators, clock references and sensors [59-62]. Bandgap reference (BGR) voltage generators are the most common types of voltage reference generator circuits intended to provide a signal independent from the process, supply voltage and temperature (PVT).

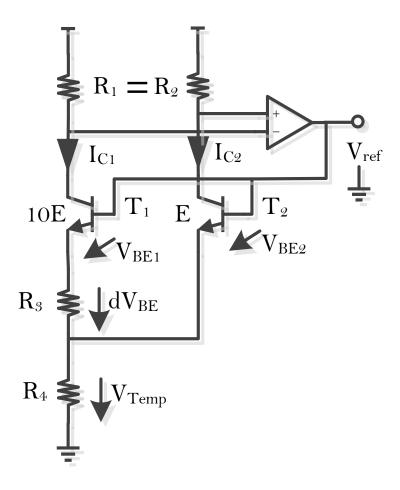

Figure 2-1. Brokaw bandgap reference voltage circuit.

In BGR circuits, two voltages acting opposite each other with respect to temperature cancel out the effect of temperature on the overall voltage generated by the circuit. In these circuits, as shown in one of its simple forms by A. P. Brokaw in [63], and depicted in Figure 2-1, a scaled version of the voltage difference between two p-n junctions with different current densities ( $V_{Temp} = 2 \frac{dV_{BE}}{R_3} R_4$ ), which is proportional-to-absolute-temperature (PTAT), is added to the voltage of a single p-n junction with a constant current ( $V_{BE2}$ ), which is complementary to absolute temperature (CTAT).

As shown, the compensation system used in these circuits does not use any feedback and tries to cancel two opposite effects with each other in an open-loop fashion.

Many aspects of reference voltage circuits like non-linearity over a higher temperature range and precision voltage reference generation, temperature drift and low voltage applications have been the research community's focus in recent years. [4, 7, 64-69].

#### 2.3 Bandgap Current Reference

Current references are also essential blocks in most analog, mixed-signal blocks such as digital-to-analog converters (DACs), digital-to-analog converters (ADSs), amplifiers and phase-locked loops (PLL). Current references designs can be categorized into two main types.

In the first type, the reference current is generated by adding a proportional-to-absolute-temperature (PTAT) current and a complementary-to-absolute-temperature (CTAT) current to each other [7, 8, 70, 71].

In the second type of reference current circuits, a PTAT or CTAT voltage is applied to a PTAT or CTAT resistor to create an insensitive temperature current [6, 71, 72]. This type is used for low power applications like the Internet of things (IoT) [71, 73].

#### 2.4 Temperature Compensation in Sensors

With the prevalence of the internet of things (IoT) and sensor networks, many circuits for sensors have been introduced. These sensors measure various parameters like pressure, humidity, acceleration, inertia and more [74-77].

To obtain a reliable read-out from the sensors in different temperatures is an important specification needed for all the sensory systems and circuits. In general, the temperature compensation of sensors happens in two different ways. One way is hardware compensation, and the other method is software compensation.

In hardware compensation, symmetry is created in the system using circuit elements with opposite sensitivity to temperature [78-80]. Even though the hardware temperature compensation for sensors is rather easy, it lacks high accuracy. Without any feedback, it

cannot adapt to the possible changes in the circuits like process, voltage, and different ranges of temperature (PVT).

In software temperature compensation, as opposite to hardware temperature compensation, the system's temperature is measured. Using digital circuits, a command is sent to the appropriate circuits to compensate for the effect of temperature variations [81, 82]. With the complexity added, higher accuracy and an ability to respond to variation in the circuit condition is added to the system.

### 2.5 Temperature Compensation in Oscillators

Nowadays, electronic devices are required more than ever to operate in various environmental conditions with little or no degradation in performance. Precise timing is a crucial requirement in almost all digital electronic systems, which requires a clock signal to serve as a reference. This reference clock must yield a stable frequency under all operating conditions to ensure consistent operation of the system. In this work, the frequency stability of oscillators in the presence of temperature variations will be explored.

The three main oscillator types used in electronic systems are crystal, MEMS-based, and all-silicon oscillators. Each type exhibits a different degree of frequency stability in the presence of temperature variations.

# 2.5.1 Crystal Based and non-Integratable Oscillators

Crystal oscillators are the most stable of these three types and have essentially had a monopoly on applications requiring high precision and highly stable frequency since 1919 [16]. A basic crystal oscillator (XO) can provide frequency stability of less than  $\pm 50$ ppm without temperature compensation, and a temperature compensated XO (TCXO) can provide frequency stability of  $\pm 2.5$ ppm over a temperature range of 125°C [83]. Oven controlled crystal oscillators (OCXO) can provide even higher stability, and have been demonstrated to have frequency stability in the range of  $\pm 5$ ppb over a range of 75°C [17] and more recently, have shown frequency stability of  $\pm 3$ ppb over a range of 125°C [18]. Although crystal oscillators can provide very good temperature stability and a very high-

quality factor (Q) (and consequently very low phase noise [16, 84]), they suffer from several drawbacks. Their operating characteristics are sensitive to vibration and shock, and they need to be packaged in a vacuum or gas-filled hermetic package to prevent contamination. In addition, the large form factor and technological limitations render crystal oscillators unsuitable for monolithic integration with microelectronics. These drawbacks have led researchers to look for possible replacements for crystal oscillators.

#### 2.5.2 MEMS-Based Oscillators

Research into creating oscillators using MEMS has been conducted ever since the idea of using silicon as a mechanical material for electronics was proposed in the 1980s [85, 86]. Significant effort has been devoted to this research area, and promising results have been achieved [19, 20, 22, 23, 87]. Because the output frequency of MEMS-based oscillators is inherently more sensitive to temperature than that of crystal oscillators, several compensation methods have been proposed, including mechanical compensation by coating the device with a material to cancel its temperature dependence [24, 88, 89], electronic compensation by including a tuning capacitor in the circuit or adjusting the temperature of the devices through heat induction [20, 25, 90, 91], and a combination of mechanical and electronic compensation techniques [26]. Recent work has achieved temperature stability of lower than 1 ppm for MEMS-based oscillators over a temperature range greater than 100°C [23, 28, 92-94].

Research on integrated oscillators has been ongoing in parallel to MEMS-based oscillators since the 1960s [29]. New advances in semiconductor technology in general and CMOS specifically have renewed interest in all-silicon integrated oscillators [30]. Although the high-temperature sensitivity of all-silicon oscillators has been a significant hurdle in their practical use as timing references, recent improvements in this area have been significant. The research community has presented relaxation and RC oscillators [31-36, 95, 96] and ring oscillators [97-100] with temperature stabilities on the order of 400 ppm over a range of up to 130°C [35]. Meanwhile, LC oscillators have been shown to achieve temperature stabilities as low as 200 ppm over a temperature range of 90°C without the need for complex post-processing calibration/compensation techniques [40-44, 101].

#### 2.5.3 All Silicon Oscillators

The majority of the temperature compensation techniques proposed to date are based on the use of circuits or devices with lower intrinsic temperature sensitivity [24], or the addition of a component with an opposite temperature sensitivity to cancel out the temperature sensitivity of the oscillator, mostly in an open-loop fashion [42].

### 2.6 Summary and Conclusion

This chapter highlighted the importance of temperature compensation in electronics circuits and systems by presenting a brief overview of many electronic circuits that use temperature compensation. Bandgap voltage and current references, electronic sensors and oscillators are the main circuits that temperature compensation techniques for them were discussed. In the brief discussion, some literature published in these areas was also presented.

# Chapter 3 System Description and Analysis of the Proposed Scheme for

# **Temperature Compensation**

#### 3.1 Introduction

In this chapter, the proposed temperature compensation scheme is introduced and is analysed. First, the proposed compensation scheme is introduced and then it is modelled using a linear approximation to be able to analyse it. Initially, the analysis is performed on a simplified system. Then practical details and non-idealities are added to the system for a better analysis of the system that can provide a better understanding of its behaviour and predict its functionality. The proposed scheme is described in the next section.

## 3.2 The Proposed Temperature Compensation Scheme

One way to compensate for the ambient temperature change effect on the desired device is to provide a mechanism to keep the temperature of the device fixed independently from the ambient temperature variations. In this method, changes in the ambient temperature can be sensed, and a heating system (and in some cases a cooling system [102]) can be employed to cancel out the effect of this ambient temperature variation on the oscillator. In the system implementing this, a heater is used to push more heat into the system when the ambient temperature drops and less heat is pumped into the system when the ambient temperature increases. This is the same familiar scheme used at the macroscopic scale to regulate the ambient temperature in living spaces utilizing heating and air conditioning systems. This scheme has been of interest to the semiconductor circuit research community for a long time. It has been used for temperature compensation of reference signal generators [46, 47] and for creating highly stable OCXOs [15, 17]. In addition, more recently, the same scheme has been applied to MEMS-based oscillators [26, 49]. Even though there have been suggestions that some MEMS-resonators can be implemented on top of silicon-based integrated circuits [19], an integrated compensation system with MEMS-based resonators using this concept has yet to be presented. However, using this concept is just gaining the research community's attention to be realized on all-silicon oscillators. Recently, an integrated micro-heater was

shown to create a voltage-temperature compensated area on-chip [103]. The current work proposes an integrated compensation scheme that can be used for both MEMS-based oscillators and all-silicon oscillators. This work exposes a different heater structure than the one in [103], and in addition, it provides an analysis of the loop and behaviour of the dual loop PLL created for this purpose. It models the system in its entirety, both with respect to the dual loop PLL and the thermal feedback, and it illustrates its design procedure, metrics, and considerations [58].

The proposed temperature compensation scheme uses integrated micro-heaters built on top of the oscillators to keep the temperature of the oscillators fixed against the ambient temperature variations. The power delivered to the micro-heaters and, consequently, the heat transferred to the oscillators increases when the ambient temperature drops and decreases when the ambient temperature increases. The objective of this compensation technique is to keep the actual temperature of the oscillators fixed and independent from the ambient temperature variations.

To change the amount of heat provided by the micro-heaters in response to ambient temperature variations, a mechanism to detect ambient temperature changes is needed.

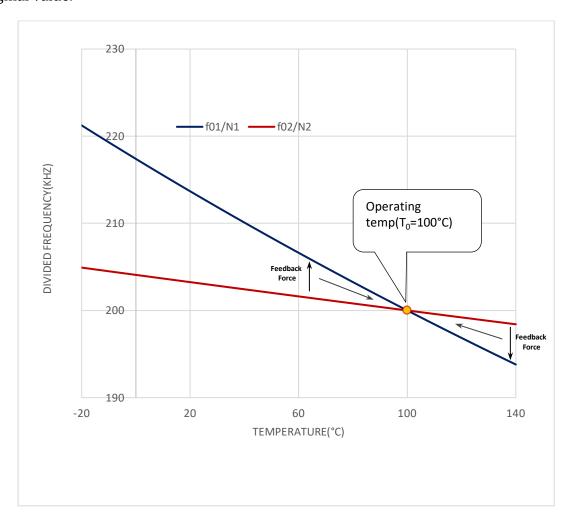

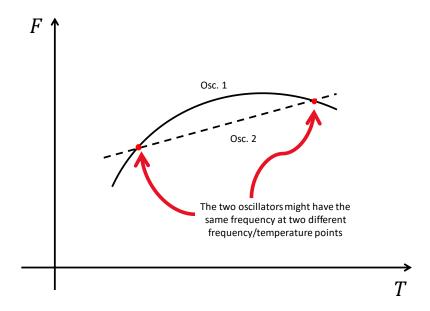

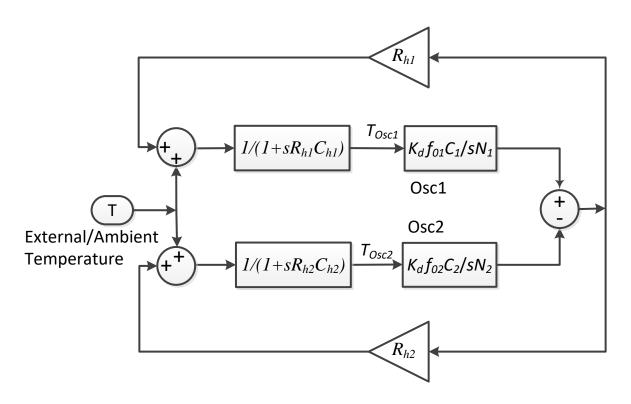

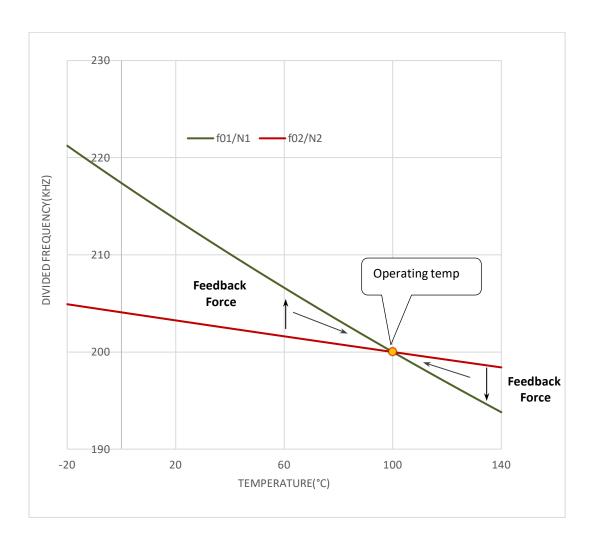

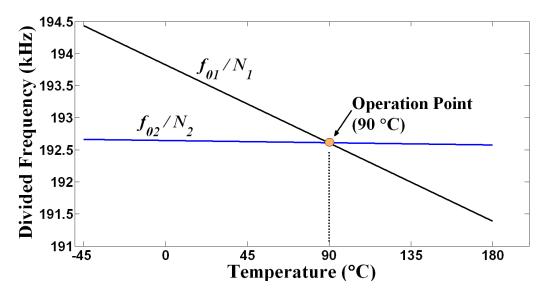

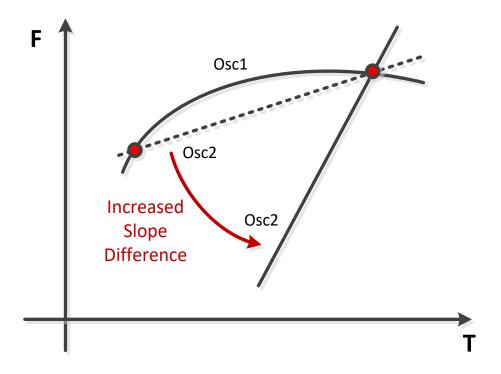

To show how the temperature variations can be detected, let's consider two oscillators whose frequency reacts to temperature differently, as shown in Figure 3-1. In this figure, the frequency of each oscillator divided by a specific number is plotted as a function of its temperature. As Figure 3-1 shows, if the two lines do not have the same slope, they can only meet at one temperature(T0) and frequency point. Therefore, if the system is biased at temperature T0, any temperature change causes the two frequencies to further depart from each other. Thus, this frequency difference can be used as a temperature change indicator in a temperature compensation system. It can be used in a feedback loop to control the amount of heat required to be transferred to the oscillators to push back the temperature to its original value.

Figure 3-1. The difference between the slopes of the two lines produces the feedback force.

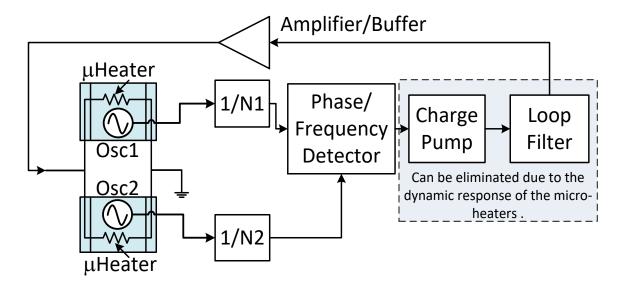

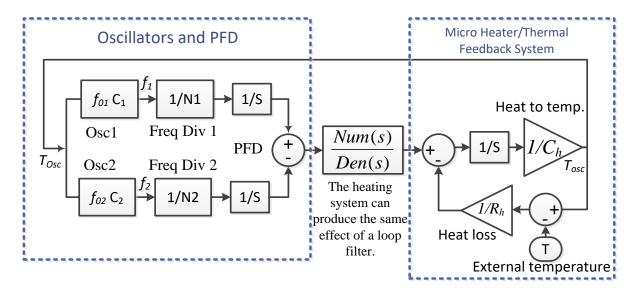

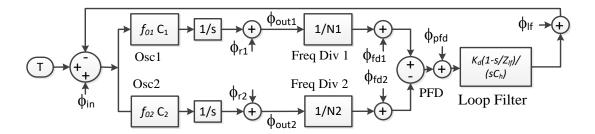

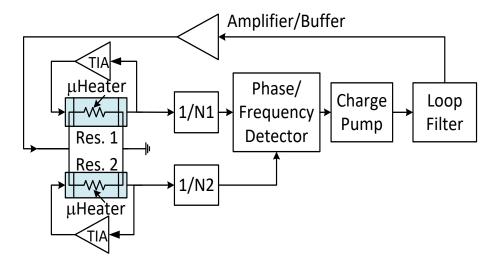

Since frequency comparison and frequency differentiation is needed for this purpose, a PLL structure is a good candidate to perform this job[104]. Thus, a feedback system depicted in Figure 3-2 is proposed for the temperature compensation system.

There are two oscillators equipped with micro-heaters in this system, each feeding one programmable integer frequency divider. The frequency dividers are added to the design to provide the ability to divide down the two oscillators' frequencies and make them closer to each other. This adds the capability to the system to employ two oscillators operating at possibly very different frequencies. By dividing them down to close enough frequencies, they make them suitable phase frequency detector (PFD) block inputs. The division ratio in each path can be adjusted independently to provide an extra degree of freedom in the design.

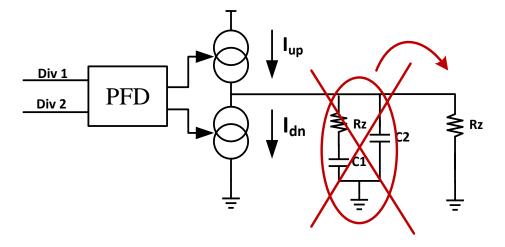

The divided down signals are compared to each other in a phase-frequency detector (PFD), and a signal corresponding to the difference between the two frequencies is generated by the PFD. In this phase-locked loop (PLL) system, the output of PFD can go through a charge pump (CP) and loop filter to provide a clean feedback control signal. However, as it will be shown in the next chapters, the dynamics of the heating system and the micro-heaters can act like a filter and there is a chance that both charge pump and loop filter be eliminated from a PLL system consisting of a heating system.

Figure 3-2. Block diagram of a possible realization of the PLL-based compensation system.

In the proposed system, the heat forces the loop to lock and makes the signal frequencies going into the PFD of the same value. To achieve this, the control signal corresponding to the difference between the two frequencies controls the current mirrored by the current buffer/amplifiers into the micro-heaters built on top of the oscillators. The current amplifier/buffers are necessary to drive the low impedance micro-heaters.

It should be noted that the oscillators in this PLL are temperature-controlled oscillators (TCOs) as opposed to voltage-controlled oscillators (VCOs) used in a conventional system. This is because the frequency of oscillators in this system is controlled by the temperature and the heat generated by the micro-heaters, as opposed to a voltage signal.

## 3.2.1 Temperature to Frequency Function

In Figure 3-1, it has been assumed that for simplicity, a straight line can show the frequency of each oscillator as a function of its temperature. This assumption is quite realistic for MEMS-based oscillators, as shown in [87, 105-109].

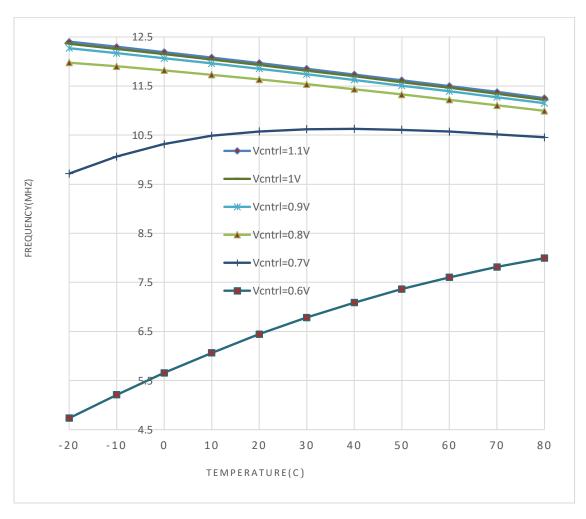

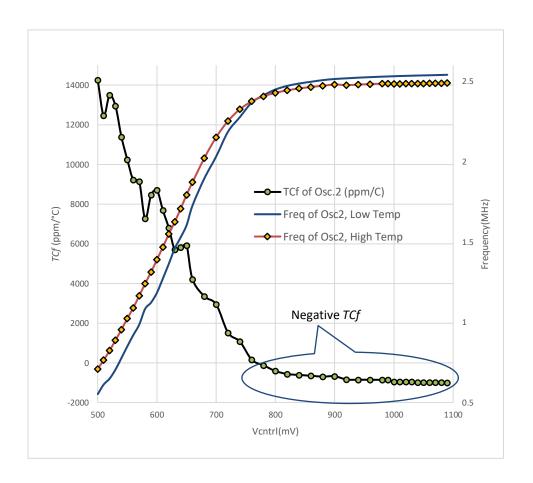

For silicon-based oscillators, the assumption that frequency changes with respect to temperature in a linear fashion is not completely realistic. Figure 3-1 shows the simulated frequency of a current-starved ring-oscillator versus temperature for different control voltage that controls the current going through the inverter chain in the ring-oscillator. This current-starved ring-oscillator is used in the implementation of the system that will be explained in future chapters. From Figure 3-3 it can be noticed that even though at most of the control voltage range, the frequency to temperature curves are straight lines, but there are situations that s straight like cannot represent frequency to temperature variations of the oscillators. When frequency to temperature curves of oscillators are not straight lines, special attention should be paid to designing the temperature compensation system explained in the next section.

# 3.2.2 Implications of not having a straight-line showing frequency versus temperature

### of oscillators

To ensure that the PLL locks at one frequency, in the proposed scheme as shown in Figure 3-1 it is assumed that the frequency to temperature curves of the oscillators meet each other at only one frequency/temperature point. As long as the two curves are straight lines, this assumption is true. However, if these curves are not straight lines, implications in functionality of the system might arise. Let us assume as shown in Figure 3-4.a, the frequency versus temperature curve of one of the oscillators is a straight-line and the other one is not. In this case, these two curves may meet each other at two points, as shown in Figure 3-4.a.

Figure 3-3. Simulated effect of temperature on the oscillation frequency at different control voltages (Vcntrl).

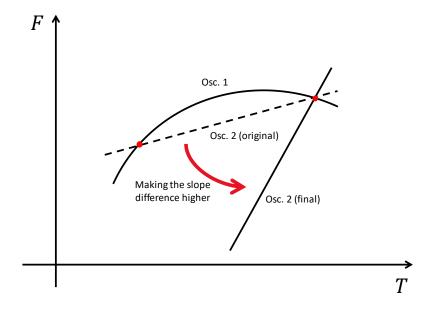

Now, if the slope of one of the two curves (without loss of generality in this case, we assume the slope of the straight-line) is pushed away from the other one, as shown in Figure 3-4.b, the curves only meet each other at one single point.

In general, if the frequency versus temperature of one of the oscillators is always more than the other one, the slope of the difference between the two curves is always positive or negative, which means the difference between the two curves is monotonic. This means it only crosses zero at one point, which means the two curves only meet at one point.

This discussion concludes that enough attention should be paid to the design of the circuit to prevent implications caused by this issue. As mentioned above, if the slope of one curve is always larger than the other one, the two curves can only meet at one point. However, if this is not possible over the whole temperature range, the system can still work over any specific range that this condition is met.

a) There are two frequency/temperature points that both oscillators can meet each other.

b) If the slope of oscillator 2 is increased and pushed away from the slope of oscillator 1, they might only meet each other at one frequency/temperature point rather than two points they crossed at originally.

Figure 3-4. Crossing at two points can be avoided by using a higher slope difference between the two oscillators.

### 3.2.3 Assuming Frequency versus Temperature is a straight-line

Indeed, even if the frequency versus temperature curves of the oscillators are not really straight lines, in a short enough temperature range, they can be assumed to be straight lines. In the following, it is assumed that the two curves are straight lines.

The slope of the frequency to temperature line of the oscillator is used to define the temperature sensitivity of that oscillator (and of the resonator if the oscillator is a resonator-based one). To quantify this frequency sensitivity to temperature, temperature coefficient of frequency or TCf is defined as the normalized variation of frequency to temperature, as shown below.

$$TCf = \frac{\frac{\Delta f}{f0}}{\Delta T} \tag{3.1}$$

, where,  $\Delta f$ =f-f0 and  $\Delta f$ /f0 is the normalized frequency variation and  $\Delta T$  is the temperature variation.

As indicated in Figure 3-1, the PLL achieves lock at an operating temperature of  $T_0$  when the following condition is satisfied:

$$\frac{f_{01}}{N_1} = \frac{f_{02}}{N_2} \tag{3.2}$$

where  $f_{01}$  and  $f_{02}$  are frequencies of each oscillator at  $T_0$ . To achieve this condition, the division ratios of the frequency dividers ( $N_1$  and  $N_2$ ) must be properly selected. It is assumed that oscillators have different and monotonic TCf, and therefore, the PLL can only lock at the only one temperature that meets the relationship in (3.2).

The above analysis assumes that the temperature of both oscillators is the same, which essentially means that the micro-heaters provide the same amount of temperature control/feedback to each oscillator. This condition needs to be adhered to as closely as possible during the design and implementation of the system.

Since the only cooling mechanism available in this system is to stop the micro-heaters from supplying heat, the only way to ensure that the loop locks at all ambient temperatures is to set  $T_0$  above the maximum targeted ambient temperature. For example, if the system is designed to work at an ambient temperature of 85°C, the actual temperature of the oscillators must be set slightly higher than that (e.g. 100°C, as shown in Figure 3-1). A temperature margin is helpful to account for process variations and non-idealities in the system. For instance, a margin would be necessary if the lowest current generated by the output buffer is greater than zero due to leakage currents.

## 3.3 Linear Approximation and System Analysis

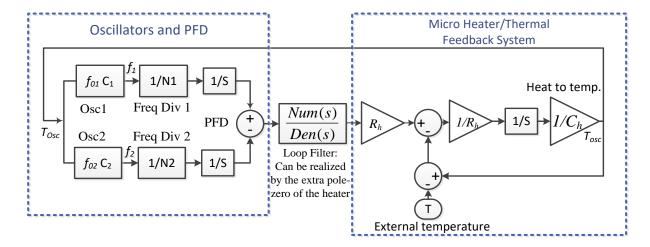

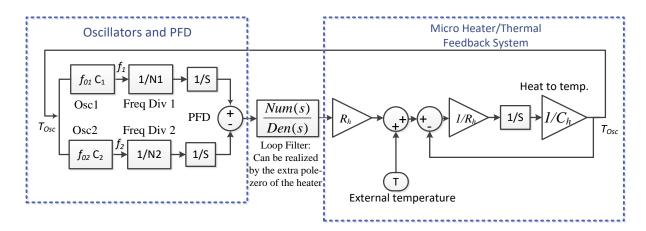

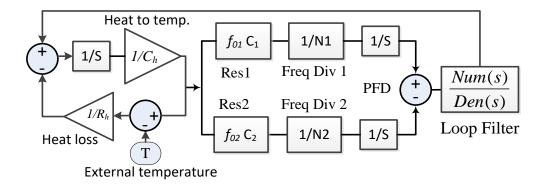

## 3.3.1 Linear Approximation

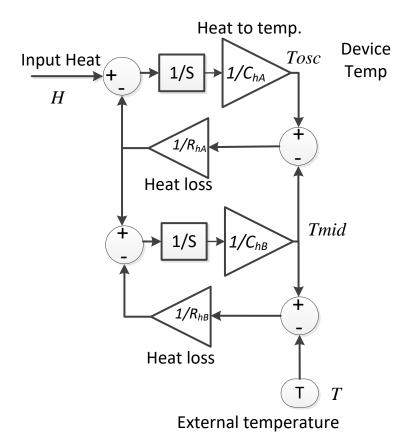

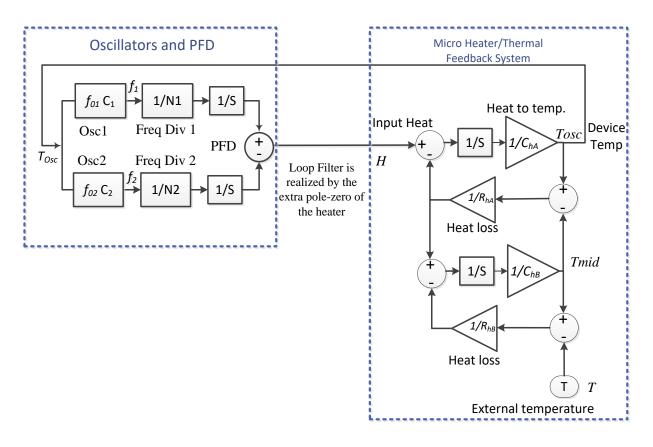

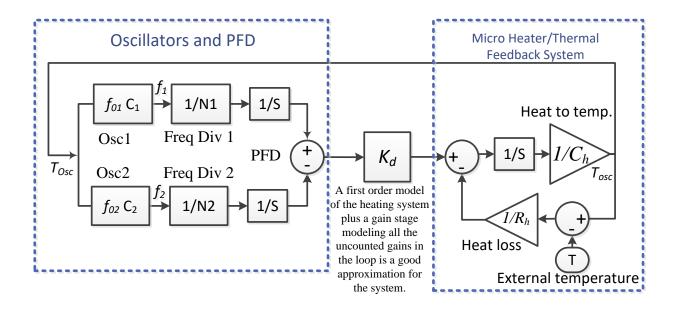

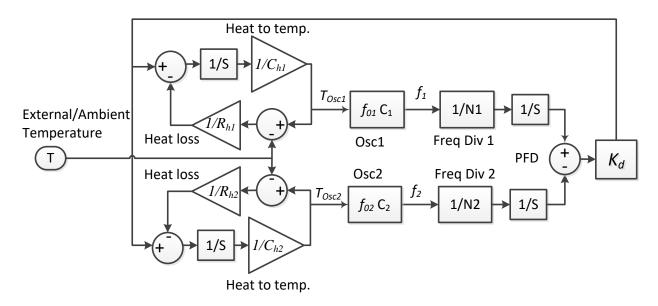

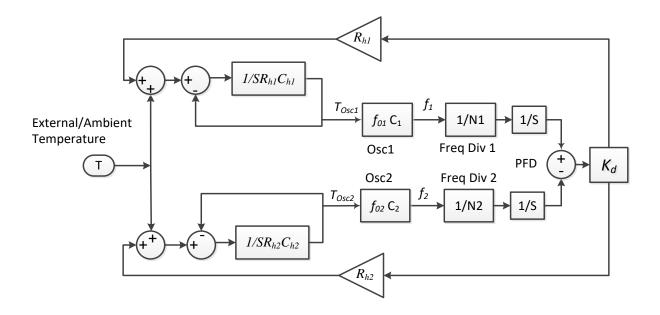

The system can be approximated as a continuous-time linear system to simplify the analysis, and this model is shown in Figure 3-5. The system consists of three main parts. Oscillators and Phase Frequency dividers (PFD), Loop-Filter (will be realized by the heating system) and the heating system. Any changes in the ambient temperature will cause a frequency shift in the oscillator. The PLL feedback loop will adjust the temperature of the micro-heater to

Figure 3-5. Linearized model of the proposed system.

Figure 3-6. The heating system model and its equivalent electrical circuits.

compensate for this shift. It should be noted that this linear approximation is only valid if the loop bandwidth of the system is at least 10 times smaller than the frequency of the signal at the output of the frequency dividers [110].

For each oscillator, a temperature change from the initial temperature  $T_{\rm osc}$  to  $T_{\rm osc}$  causes an oscillation frequency variation from  $f_0$  to f expressed as:

$$f(T_{osc}) = f_0(1 + C(T_{osc} - T_{osc0})),$$

(3.3)

where C (C1 and C2 in Figure 3-5) is the oscillator's temperature coefficient of frequency (TCf). In this system, heat controls the frequency of oscillators through temperature-controlled oscillators (TCO) as opposed to voltage-controlled oscillators (VCO). Hence, the PLL system can be linearized around the initial temperature  $T_{\rm osc0}$  and the frequencies  $f_{01}$  and  $f_{02}$  as depicted in Figure 3-5. Using this model, the variation of the frequency of the output signal of each TCO passes through a linear gain stage, a divider, and an integrator, which converts the frequency variations into a phase variation before being input to the PFD.

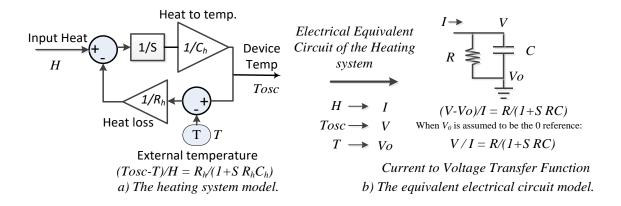

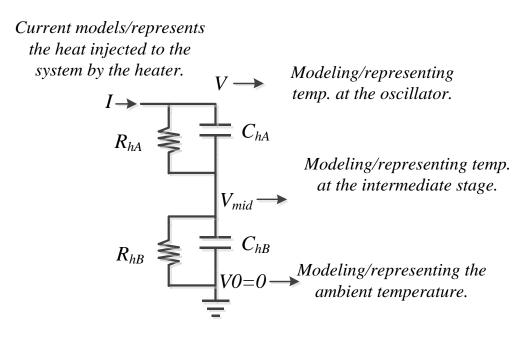

### 3.3.1.1 Micro-heater linear modeling

As shown in Figure 3-6, a simple heating system can be modelled as thermal feedback where heat loss is proportional to the difference between the oscillator and ambient temperatures. Therefore, total heat loss is subtracted from the electrical power injected into the microheaters to yield the net heat delivered to the oscillators. The power to energy conversion can

be modelled as an integrator (1/s in the Laplace domain), and energy is converted to temperature using a coefficient proportional to the inverse of the heat capacity of the system (1/ $C_h$ ). Heat loss, proportional to the temperature difference between the heater and heat dissipation site, scales inversely to the system's heat resistivity (1/ $R_h$ ). Therefore, the heat capacitance and resistance of the system defines its dynamics. Even though the ambient temperature affects the heat capacitance and resistance of the system,  $C_h$  and  $R_h$  are assumed to be constant for the sake of simplicity.

As dictated by general thermodynamics, the heater shows a very slow response to temperature variations compared to the electrical signal variations in the system. Therefore, a simple first-order model of the heater can be considered to add a pole near the origin (given by  $1/R_hC_h$ ) to the open-loop transfer function of the PLL system. As will be shown in the following sections, in addition to this dominant pole in the vicinity of 0 Hz, the heating system can exhibit an extra pole and an extra zero that can enhance the stability of the PLL loop. As a result, the heating system can replace the loop filter.

Considering the model of Figure 3-5, the transfer function for the oscillator temperature variation in response to an ambient temperature change, T, assuming the initial ambient temperature  $T_0 = 0$  and that both oscillators are at the same temperature, can be derived as:

$$H(s) \stackrel{\text{def}}{=} \frac{T_{OSC}}{T}(s) = \frac{sDen(s)}{s^2 R_h C_h Den(s) + s Den(s) + K_0 R_h Num(s)},$$

(3.4)

where  $K_o = \frac{f_{02} C2}{N_2} - \frac{f_{01} C1}{N_1} = \frac{f_{01} \Delta C}{N_1} = \frac{f_{02} \Delta C}{N_2}$ , and  $\Delta C = C_2 - C_1$ . The term  $(1/R_h C_h)$  represents the dominant pole of the heater and Num(s) and Den(s) are the numerator and denominator of the loop filter model  $\frac{Num(s)}{Den(s)}$ . As shown in the next section, the loop filter can be completely removed since the heating system can provide the same functionality needed from a loop filter in a stable type II PLL.

As it is assumed that the frequency of the oscillators is linearly dependent on the temperature, the frequency shift in response to an ambient temperature variation can be written as:

$$H_{f1}(s) \stackrel{\text{def}}{=} \frac{f_1}{T}(s) = \frac{C_1 f_{01} T_{OSC}}{T}(s) = C_1 f_{01} H(s), \tag{3.5}$$

which presents the same dynamics of H(s) with the addition of the gain term  $C_1$   $f_{01}$ .

Type II PLLs are generally employed to achieve a system with zero phase error and no residual error. This means the error between the output of this system and its input is finally reaching zero [104]. The open-loop transfer function of a type II PLL consists of two integrators or poles at the origin.

To be able to obtain a type II PLL from the system shown in Figure 3-5,  $\frac{Num(s)}{Den(s)}$  is chosen to be only a gain factor  $K_d$  and therefore (3.4) can be written as:

$$H(s) \stackrel{\text{def}}{=} \frac{T_{osc}}{T}(s) = \frac{s}{s^2 R_h C_h + s + K_o K_d R_h} = \frac{s}{s R_h C_h \left(s + \frac{1}{R_h C_h}\right) + K_o K_d R_h}.$$

(3.6)

As mentioned before, the pole associated with the heating system is close to the origin, and then it can be assumed that  $1/R_hC_h\rightarrow 0$ . Hence, the transfer function of the system can be shown as:

$$H(s) \stackrel{\text{def}}{=} \frac{T_{osc}}{T}(s) \cong \frac{s}{s^2 R_h C_h + K_o K_d R_h}, \qquad (3.7)$$

which has the same characteristics of a type II PLL.

Typically, a type II PLL consists of oscillators and a PFD and charge pump followed by a loop filter that can be a resistor and capacitor in series as shown in Figure 3-7. a to take charge from the charge pump [111]. The loop filter of such a system can be shown as:

$$F_a(s) = R_{lf} + \frac{1}{s C 1_{lf}} = \frac{1}{C 1_{lf}} \left( \frac{s C 1_{lf} R_{lf} + 1}{s} \right). \tag{3.8}$$

A type II PLL has a system transfer function with two poles at the origin and this means it is susceptible to instability. To increase the stability of such a system, a capacitor is added in parallel to the series resistor-capacitor of the loop filter. This new capacitor, shown as  $C2_{lf}$  in Figure 3-7. b, is at least ten times smaller than  $C1_{lf}$  to add a pole at higher frequencies. Therefore, the loop filter transfer function of this system can be shown below(C):

$$F_b(s) = \frac{1}{\frac{1}{R_{lf} + \frac{1}{sC1_{lf}}} + sC2_{lf}} = \frac{1}{C1_{lf} + C2_{lf}} \frac{1 + sR_{lf}C1_{lf}}{s\left(sR_{lf}\frac{C1_{lf}C2_{lf}}{C1_{lf} + C2_{lf}} + 1\right)}.$$

(3.9)

a) The loop filter has a pole at the origin and a zero.

b) The loop filter has pole at the origin and a pole-zero pair at higher frequencies to have a better stability.

Figure 3-7. A typical type II PLL has a charge pump and a loop filter with one pole at the origin and one zero(a) or a pole-zero pair at higher frequencies for stability reasons.

With the assumption that  $C1_{lf} > 10 * C2_{lf}$ , then (3.8) can be simplified as:

$$F_b(s) \cong \frac{1}{C1_{lf}} \frac{1 + sR_{lf}C1_{lf}}{s(sR_{lf}C2_{lf} + 1)}.$$

(3.10)

In the next section, similarities between the dynamics of the system with the heater and a type II PLL are discussed. It will be shown that the heating system can replace the charge pump and loop filter of a typical PLL while maintaining the characteristics of a type II PLL.

### 3.3.1.2 Heating system replacing the charge pump and the loop filter

As mentioned earlier, a stable type II PLL requires a loop filter consisting of a pole at the origin in addition to a zero and a pole at higher frequencies. Interestingly, it is noted that the micro-heater acts like a system with a pole close to the origin and a pole and zero at higher frequencies. This is like the response obtained from a charge pump and a loop filter, as shown in (3.10), and therefore it can be shown that the micro-heater in this system can eliminate the need for a charge pump and loop filter. To show this, the effect of the heating system is analysed here.

As presented in Figure 3-6.b, a first-order model of the heating system consists of a single-pole parallel RC equivalent circuit. The heat H going into the system is modelled as a current I, and the temperature T as a voltage V. A resistance models the heat loss mechanism of the heating system and capacitance models its heat capacity. The current-to-voltage transfer function of the equivalent electrical circuit is thus

$$\frac{V}{I}(s) = \frac{\frac{1}{C_h}}{s + \frac{1}{R_h C_h}}.$$

(3.11)

Therefore, a simple one-pole heating system with heat loss resistance of  $R_h$  and heat capacitance of  $C_h$  has been modelled with a parallel RC circuit with resistance  $R_h$  and capacitance  $C_h$ .

Since the heater has a very slow response, the pole in (3.11) can be considered to be almost at the origin and therefore, (3.10) can be written as:

$$\frac{V}{I}(s) \cong \frac{\frac{1}{C_h}}{s} \,. \tag{3.12}$$

This has the same effect as an integrator following a charge pump.

Further examination of the heating system shows that extra zero and pole can be modelled to model the system's behaviour at higher frequencies. Interestingly, this helps increase the stability of the system.

To find a more realistic model of the system, a higher order modeling of the system can be performed. A first step for this can be considering the second order effects of the heating system. For this purpose, the physical area between the heater and the outside environment is defined as an intermediate stage. It is assumed that the heater exchanges heat with this intermediate stage, which exchanges heat with the outside environment. This intermediate

Figure 3-8. Second order RC circuit modeling the heating system.

stage represents the entire area of the chip starting from the immediate vicinity of the heater to the boundary of the chip and outside environment. This area is very large and has a very high heat capacity corresponding to a system model with a pole close to 0 Hz. The two-stage system can then be modelled by parallel RC circuits in series, as shown in Figure 3-8.

The transfer function from voltage to current of this system, which represents the oscillator temperature as a function of the heat injected by the heater, can therefore be expressed as

$$\frac{V}{I} = \frac{\frac{1}{C_{hA}}}{s + \frac{1}{R_{hA}C_{hA}}} + \frac{\frac{1}{C_{hB}}}{s + \frac{1}{R_{hB}C_{hB}}} = \frac{A(s - z)}{(s - p_A)(s - p_B)},$$

(3.13)

which represents a system with two poles and one zero.

The second order model of the system can also be equivalently shown as in Figure 3-9.

Figure 3-9. Second order modeling of the heating system.

Figure 3-10. Second order effect of the heating system can produce the effect of the loop filter.

As previously discussed, one of the poles of the heating system can be considered to be almost at 0 Hz  $(1/R_{hA}C_{hA} \cong 0)$  and therefore, (3.13) can be simplified as (3.14).

$$\frac{V}{I} = \frac{T_{OSC}}{H} = \frac{\frac{1}{C_{hA}} \left( s + \frac{1}{R_{hB}C_{hB}} \right) + \frac{1}{C_{hB}} \left( s + \frac{1}{R_{hA}C_{hA}} \right)}{\left( s + \frac{1}{R_{hA}C_{hA}} \right) \left( s + \frac{1}{R_{hB}C_{hB}} \right)} \cong \frac{\left( \frac{1}{C_{hA}} + \frac{1}{C_{hB}} \right) s + \frac{1}{R_{hB}C_{hA}C_{hB}}}{s \left( s + \frac{1}{R_{hB}C_{hB}} \right)} \cong \frac{A(s - z)}{s(s - p)}, (3.14)$$

This is the same filtering effect shown in (3.10) for a type II PLL with added zero-pole for stability. Such a PLL typically consists of a charge pump and an RC loop filter [111, 112]. However, here the heating system adds the same effect by adding a pole at the origin and an extra pole and zero to the system and therefore it can replace the charge pump and the loop filter needed in a type two PLL.

Eliminating the loop filter has the benefit of reducing chip area as integrated loop filters tend to be large, while removing the charge pump can reduce noise caused by issues such as charge sharing and clock feedthrough.

Figure 3-10 shows the system with no loop filter and charge pump, and the heating system provides the functionality of a charge pump and a loop filter.

In addition to the pole close to the origin and a zero, the higher order effects of the heating system add higher frequency poles and zeros to the system. However, these extra poles and zeros are at higher frequencies and can be assumed they are out of the bandwidth of the PLL.

# 3.3.1.3 Proportional and integral and higher frequency parts of the heating system

### transfer function

As explained in [111], the loop filter of a PLL in a general form can be shown as:

$$F(s) = F_{n+i}(s) F_{hf}(s), (3.15)$$

where,  $F_{p+i}(s)$  represents the proportional and integral parts of the loop filter and  $F_{hf}(s)$  represents the high-frequency portion of it.  $F_{hf}(s)$  has its greatest effects at higher frequencies and mostly out of the loop bandwidth of the PLL with the only constraint of it to be having a finite and non zero value at  $F_{hf}(0)$ . The proportional plus integral (P+I) factor of the loop filter, in general, can consist of as many integrators and not just limited to one integrator that is specific to the type II PLL. The general form of  $F_{p+i}(s)$  is shown in (3.16).

$$F_{p+i}(s) = K_1 + \frac{K_2}{s} + \frac{K_3}{s^2} + \cdots$$

(3.16)

In practice, only one integrator is mostly used in Fp+i(s), which creates a type II PLL. The number of integrators in the proportional plus integral part of the loop filter can only sometimes be two and rarely can be more than that [111].

32

Considering the first order model of the heating system shown in Figure 3-6, the transfer function of the heat injected to the system to its temperature variation can be shown as (3.11) and with the notation that pole added by the heating system is very close to the origin  $(1/R_hC_h\cong 0)$ , the transfer function of the heating system can be modeled as an integrator as shown in (3.17).

$$\frac{V}{I} = \frac{T_{Osc}}{H} = \frac{\frac{1}{C_h}}{s + \frac{1}{R_h C_h}} \cong \frac{\frac{1}{C_{hA}}}{s}.$$

(3.17)

This model can provide the proportional plus integral part of the loop filter transfer function of a type II PLL. Similarly, it can be concluded that the higher frequency effects coming from the second order modelling of the heating system can make  $F_{hs}(s)$  of the loop filter and can be eliminated for the frequencies inside the bandwidth of the PLL.

As a result, the heating system can be simplified using a first order model and only a gain stage is added to the system to model the gain obtained from different elements of the system as shown in Figure 3-11.

Therefore, the transfer function of the system can be deducted from (3.4) where  $\frac{Num(s)}{Den(s)} = K_d$ .

Thus,

$$H(s) \stackrel{\text{def}}{=} \frac{T_{osc}}{T}(s) = \frac{sDen(s)}{\left(s + \frac{1}{R_h C_h}\right) s R_h C_h Den(s) + K_o R_h Num(s)} = \frac{s}{\left(s + \frac{1}{R_h C_h}\right) s R_h C_h + K_o K_d R_h}.$$

(3.18)

When the dominant heater pole  $1/R_hC_h$  is close to zero, H(s) can be approximated as in (3.19):

$$H_{aprox}(s) = \frac{T_{osc}}{T}(s) \cong \frac{s}{s^2 R_h C_h + K_o K_d R_h} , \qquad (3.19)$$

which is the transfer function of a type two PLL [111].

# 3.3.2 Analysis of the System Response to Step and Ramp of Ambient Temperature

Further insight into the system can be obtained by analyzing its response to a step and a ramp in the ambient temperature.

Figure 3-11. A first order model of the heating system plus a gain stage can be good approximation of the system in the frequencies in the bandwidth of the PLL.

From the finite value theorem, (3.19) leads to the conclusion that for the proposed system, a temperature step of  $T_s$  produces an actual oscillator temperature change of:

$$\Delta T_{osc}(t \to \infty) = \lim_{s \to 0} sH(s) \frac{T_s}{s} = H(0)T_s = 0$$

(3.20)

Similarly, a temperature ramp having a slope  $\dot{T}_r$  yields:

$$\Delta T_{osc}(t \to \infty) = \lim_{s \to 0} sH(s) \frac{\dot{\tau}_r}{s^2} \cong \frac{\dot{\tau}_r}{\kappa_0 \kappa_d R_h}. \tag{3.21}$$