## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, sub-standard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{n} \times 9^{n}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

**I** MI<sup>®</sup>

# A hardware/software partitioning framework for the codesign of digital systems

## Houria Oudghiri

B.sc, National institute of computer science, (Algeria) 1988 M.sc, National institute of Computer science, (Algeria) 1991

> Department of electrical engineering McGill University, Montréal May1999

"A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfilment of the requirements for the degree of Philosophae Doctor"

© Oudghiri Houria, 1999

# National Library of Canada

#### Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-55368-X

# ABSTRACT

The thesis provides a new approach to the codesign of digital systems. Complex systems tend to have mixed hardware-software components and are often subject to severe cost, performance, and design-time constraints. Our approach is to codesign these systems. The codesign approach allows the hardware and software designs to be tightly coupled throughout the design process. We focus on three key problems of system modeling, system analysis and system hardware-software partitioning.

A key contribution of the thesis is to use hierarchy as it is available in modeling tools to handle complex system models but also during the codesign process to provide different modeling alternatives for the same input system. This use of the hierarchy, during the codesign process, allows the extension of the design space explored to find the final implementation.

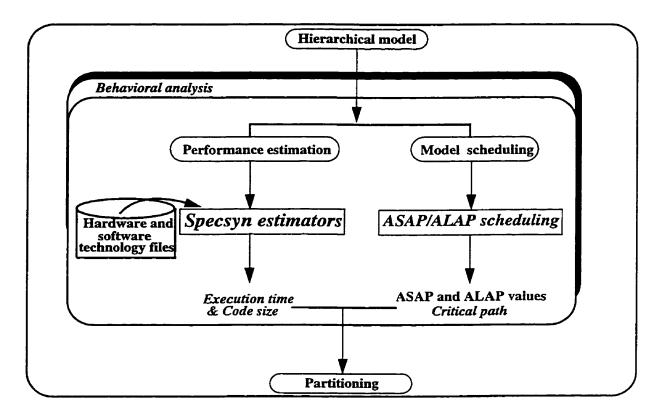

Another key contribution is the analysis of the hierarchical model for any target architecture using automatic estimators and scheduling algorithms. The performance estimation provides information on the performance of each block in the model when it is run on software resources or implemented on hardware. The scheduling algorithm is used to identify critical paths in the system execution and also to identify data dependency between the different model components.

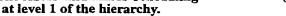

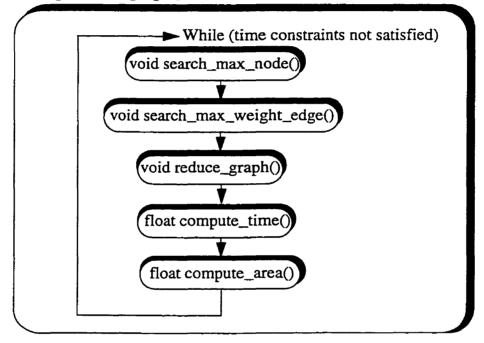

The last main contribution is the hardware-software partitioning algorithm. The proposed algorithm is based on a weighted graph partitioning heuristic. The partitioning algo-

ii

rithm performs into two nested loops. The outer loop is used to select the blocks which take a long time to execute in order to move them to hardware. This selection has the main objective of accelerating the system execution. The inner loop is used to select the neighbors of the block selected in the outer loop. The neighbors which have the most data dependency are first selected in order to minimize the hardware-software communication cost. ٠

We embody all the above concepts in a framework containing tools for hierarchical modeling, system analysis and partitioning. This new framework provides designers with a list of hardware-software implementations corresponding to the different levels in the system hierarchy. These codesign alternatives are provided with their performance and cost measures to allow the designer selecting the final implementation.

## SOMMAIRE

Cette thèse présente une nouvelle approche pour le codesign des systèmes digitaux. Les systèmes digitaux deviennent de plus en plus complexes et ont tendance à contenir des composants hybrides qui peuvent être du logiciel ou du matériel. La conception de tels systèmes est souvent sujette à des contraintes sévères sur le coût, la performance ainsi que sur le temps de conception. On propose, dans cette thèse une approche pour réaliser le codesign de tels systèmes. Cette approche permet de concevoir le logiciel aussi bien que le matériel dans le même processus de conception. Nous nous sommes intéressés, dans cette thèse, surtout à trois problèmes clés dans le domaine du codesign qui sont la modélisation au niveau système, l'analyse de performance ainsi que le problème de partitionnement logiciel-matériel.

L'une des contributions majeures de cette thèse, est l'utilisation de la hiérarchie non seulement pour permettre de modéliser des systèmes très complexes mais aussi lors du processus de codesign afin de fournir différentes alternatives de modélisation pour le même système en entrée. Cette utilisation de la hiérarchie, pendant le processus de codesign, permet d'étendre d'une façon considérable l'espace des solutions qu'on explore afin de trouver la solution finale. En effet, chaque niveau dans la hiérarchie donne un nouveau modèle sur lequel tout le processus de codesign est exécuté afin de trouver une solution logicielle-matérielle. Plusieurs niveaux de hiérarchie vont donc permettre de rechercher une solution pour chaque niveau. Ceci constitue une nette amélioration par rapport aux

iv

travaux classiques où une solution est recherchée pour un seul modèle en entrée.

Une autre contribution concerne l'analyse du modèle hiérarchique pour n'importe quelle architecture cible. Ceci est réalisé en utilisant des outils d'estimation automatique ainsi que des algorithmes d'ordonnancement. L'estimation automatique des performances fournit, d'une façon rapide, des données sur les performances de chaque bloc du modèle lorsque celui-ci est exécuté sur une ressource logicielle ou bien implémenté sur le matériel. Les algorithmes d'ordonnancment servent à identifier les goulots d'étranglement dans l'exécution du système au complet et aussi à déterminer les dépendances en données entre les différents blocs du modèle.

La dernière contribution majeure est l'algorithme de partitionnement logiciel-matériel. L'algorithme proposé est basé sur une heuristique de partitionnement d'un graphe pondéré. Cet algorithme est réalisé en deux boucles imbriquées. La boucle externe sert à sélectionner les noeuds qui sont les plus lents et qui sont déterminants sur la performance finale du système. Cette première sélection sert donc à accélérer l'exécution du système. La boucle interne sert à sélectionner les voisins les plus dépendants du bloc sélectionné par la boucle externe afin de minimiser le coût de la communication entre les partitions logicielle et matérielle.

Toutes ces contributions ont été intégrées dans un environnement de codesign permettant de réaliser une modélisation hiérarchique, une analyse du système en entrée et enfin un partitionnement automatique du système en entrée en deux implémentations, l'une logicielle et l'autre matérielle.

v

### Acknowledgements

I would like to acknowledge my supervisor, Januzs Rajski, for having accepted me as a Ph.D student, supported me and assisted me throughout my doctoral studies.

I would also like to acknowledge my co-supervisor, Bozena Kaminska, for her guidance and assistance throughout my doctoral thesis.

As a member of my supervisory comitte, I acknowledge Prof. Ted Szymanski for his suggestions during the earlier stages of my research work.

I am beholden to all my friends in the VLSI design laboratory at McGill and at the University of Montréal for their assistance. My special thanks to Claude Villeneuve for the pleasant work I had with him.

In addition, I would like to express my thanks to the Algerian Gouvernment for their support during my master and which allows me to continue towards Ph.D.

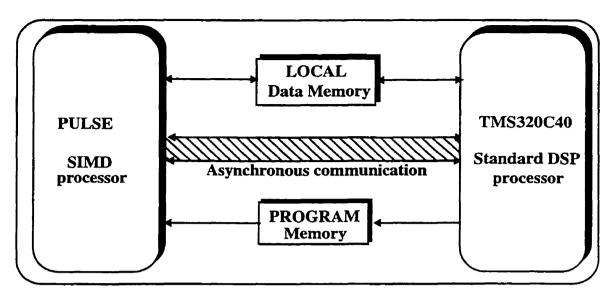

For financial support, I would like to acknowledge Prof. Yvon Savaria, the director of the PULSE project and all the project partners.

Finally, on a more personal level, I am grateful for my parents and to all my family members back home for their support throughout the course of my studies.

# TABLE OF CONTENTS

٠

|   | LIST OF FIGURES x                                         |

|---|-----------------------------------------------------------|

|   | LIST OF TABLES xii                                        |

|   | CLAIM OF ORIGINALITY xiv                                  |

| 1 | INTRODUCTION                                              |

|   | 1.1. Modeling                                             |

|   | 1.2. Performance estimation                               |

|   | 1.3. Partitioning                                         |

| 2 | CODESIGN METHODOLOGY                                      |

|   | 2.1. Motivations for hardware/software codesign10         |

|   | 2. 2. The codesign problem statement                      |

|   | 2.3. A typical codesign flow and tools for codesign       |

|   | 2.3.1       System modeling                               |

|   | 2. 4. Related work16                                      |

|   | 2.4.1Specification and verification172.4.2Co-simulation19 |

|   | 2.4.3 System analysis                  | 19 |

|---|----------------------------------------|----|

|   | 2.4.4 Partitioning                     | 20 |

|   | 2.4.5 Cosynthesis and prototyping      | 22 |

|   | 2. 5. The proposed codesign framework  | 24 |

|   | 2. 6. Summary                          | 28 |

| 3 | SYSTEM SPECIFICATION                   | 30 |

|   | 3.1. Modeling techniques               | 31 |

|   | 3.1.1 Finite State Machines            |    |

|   | 3.1.2 Data flow graphs                 | 32 |

|   | 3.1.3 Communicating processes          | 32 |

|   | 3.1.4 Object-oriented modeling         | 33 |

|   | 3. 2. The proposed model               | 34 |

|   | 3. 3. The model data structure         | 40 |

|   | 3.4. Summary                           | 43 |

| 4 | SYSTEM ANALYSIS                        | 45 |

|   | 4.1. Performance estimation            | 45 |

|   | 4.1.1 Hardware performance estimation  | 46 |

|   | 4.1.2 Software performance estimation  | 47 |

|   | 4.2. The proposed estimation technique | 47 |

|   | 4.2.1 The Specsyn estimators           | 48 |

|   | 4. 3. Scheduling                       | 54 |

|   | 4.4. Summary                           | 58 |

| 5 | SYSTEM PARTITIONING                    | 59 |

|   | 5.1. Problem definition                | 61 |

|   | 5.2. Related work                      | 62 |

|   |       | 5.2.1 The input model                                             | 62             |

|---|-------|-------------------------------------------------------------------|----------------|

|   |       | 5.2.2 The granularity                                             | 63             |

|   |       | 5.2.3 The cost function                                           | 64             |

|   |       | 5.2.4 The partitioning algorithm                                  | 66             |

|   | 5.3.  | The proposed partitioning technique                               | 71             |

|   | 5.4.  | The partitioning algorithm implementation                         | 78             |

|   | 5.5.  | The algorithm complexity                                          | 30             |

|   | 5.6.  | Summary                                                           | 33             |

| 6 | CAS   | SE STUDIES 8                                                      | 35             |

|   | 6. 1. | The target architecture                                           | 36             |

|   | 6.2.  | The FFT example                                                   | 37             |

|   |       | 6.2.1 The high-level description of the FFT transform             | 87             |

|   |       | 6.2.2 The FFT hierarchical modeling                               | 90             |

|   |       | 6.2.3 The performance estimation and scheduling                   | <del>9</del> 2 |

|   |       | 6.2.4 Partitioning alternatives                                   | <del>)</del> 3 |

|   | 6.3.  | The power network simulation algorithm9                           | 9              |

|   |       | 6.3.1 The high-level description of the power network simulation  | <del>)</del> 9 |

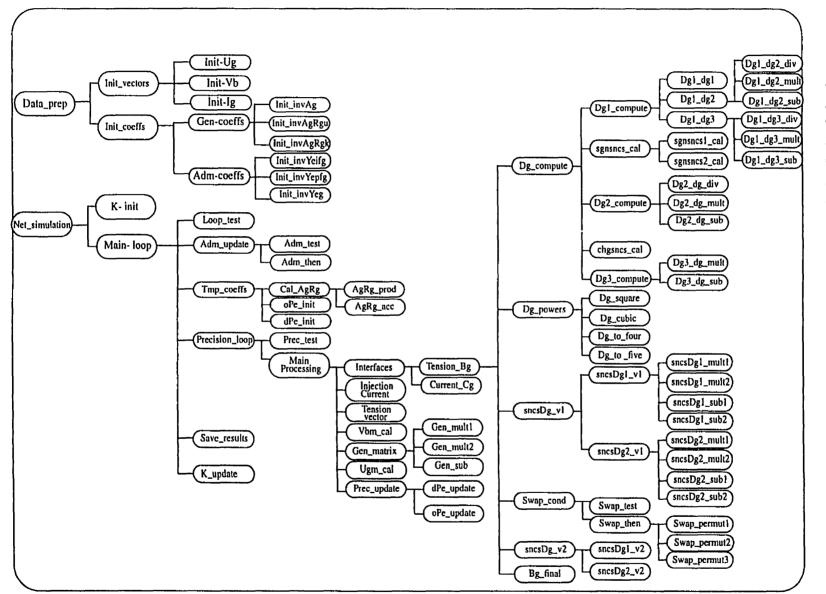

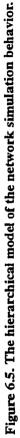

|   |       | 6.3.2 The hierarchical modeling of the power network simulator 10 | )1             |

|   |       | 6.3.3 Performance estimation 10                                   | )3             |

|   |       | 6.3.4 Partitioning alternatives 10                                | )4             |

|   | 6.4.  | Summary10                                                         | 17             |

| 7 | CON   | ICLUSIONS                                                         | 8              |

|   | 7.1.  | Contributions10                                                   | 18             |

|   |       | 7.1.1 Hierarchical modeling                                       | )9             |

|   |       | 7.1.2 System partitioning                                         |                |

|   |       | 7.1.3 System analysis                                             |                |

|   | 7.2.  | Future directions                                                 | 2              |

#### ix

| 7.2.1    | Framework integration                 |     |

|----------|---------------------------------------|-----|

| 7.2.2    | Hardware and software synthesis       |     |

| 7.2.3    | Interface synthesis                   |     |

| APPENDIX |                                       |     |

| Tech     | nolgy files for the system estimation | 115 |

| REFEREN  | NCES                                  |     |

# LIST OF FIGURES

•

| Figure. 1.1 The hardware/software codesign process                                     | 4  |

|----------------------------------------------------------------------------------------|----|

| Figure. 2.1 The typical codesign flow process.                                         | 16 |

| Figure. 2.2 The proposed codesign flow                                                 | 26 |

| Figure. 2.3 Modeling and codesign alternatives                                         | 27 |

| Figure. 3.1 Examples of the different modeling techniques                              | 33 |

| Figure. 3.2 The HDLC entity environment and block digram                               | 36 |

| Figure. 3.3 The hierarchical model of the HDLC entity                                  | 37 |

| Figure. 3.4 The data flow graph models corresponding to different levels of hierarchy. | 37 |

| Figure. 3.5 Possible hardware/software partitioning.                                   | 40 |

| Figure. 3.6 The data structures used to implement the hierarchical model.              | 42 |

| Figure. 3.7 The data structures used to implement the data flow graph                  | 43 |

| Figure. 4.1 The behavioral analysis step                                               | 48 |

| Figure. 4.2 The allocation list for hardware estimation                                | 50 |

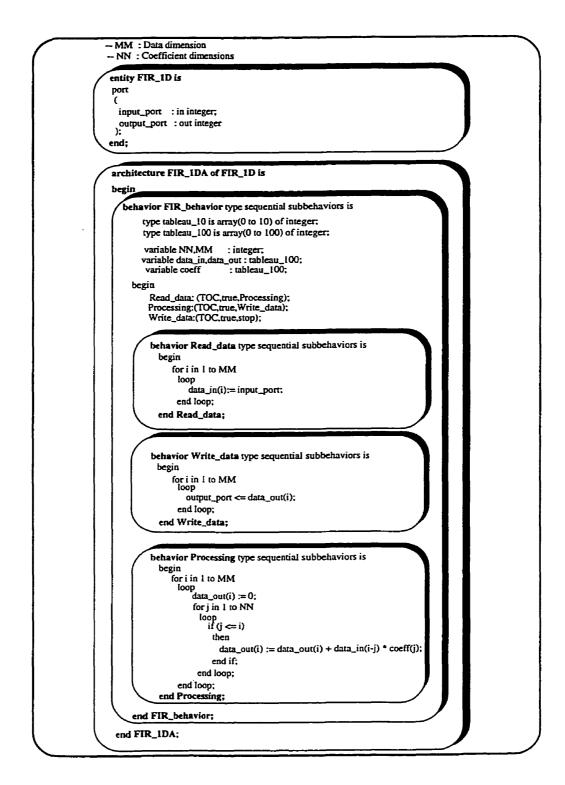

| Figure. 4.3 The SpecChart description of the FIR filter.                               | 51 |

| Figure. 4.4 The list of generic instructions.                                          | 53 |

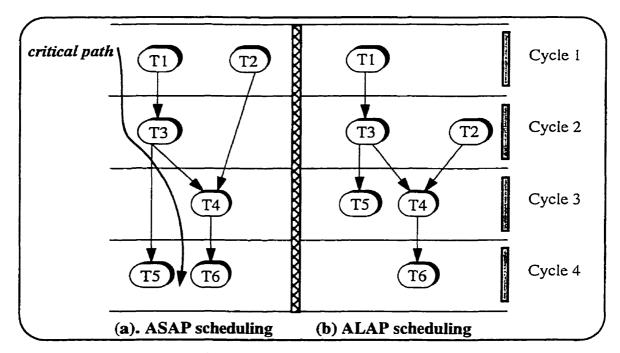

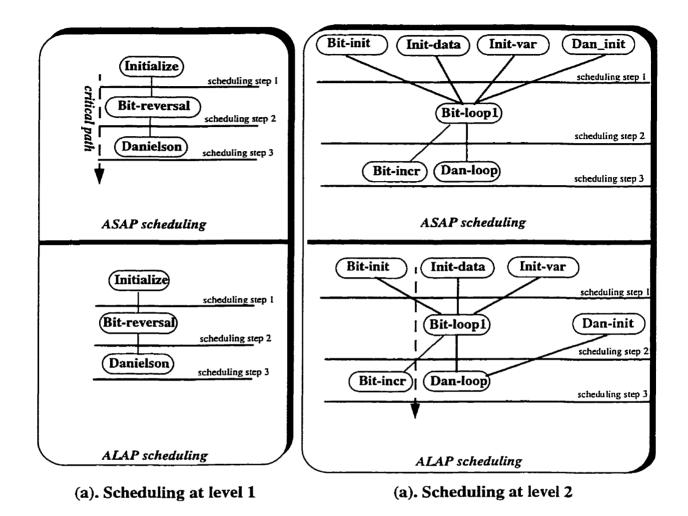

| Figure. 4.5 An example of ASAP and ALAP scheduling                                     | 55 |

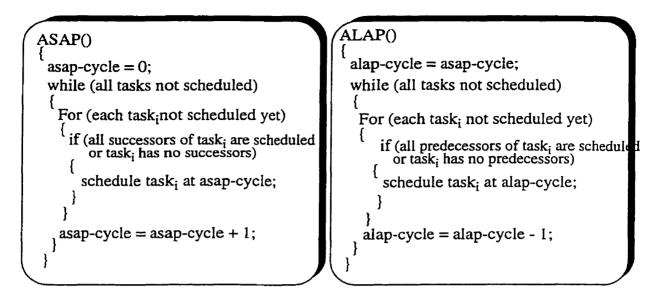

| Figure. 4.6 The ASAP and ALAP scheduling procedures                                    | 56 |

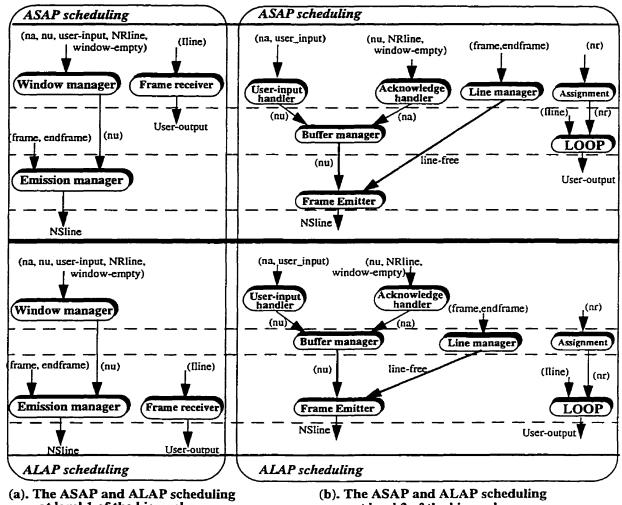

| Figure. 4.7 The task scheduling for different levels in the hierarchy.                 | 57 |

| Figure. 5.1 The proposed hardware-software partitioning procedure                      | 76 |

| Figure. 5.2 The partitioning procedure flow for the HDLC example                       | 77 |

| Figure. 5.3 The procedure to find the critical path in the data flow graph              |

|-----------------------------------------------------------------------------------------|

| Figure. 5.4 The principal procedures used in HAP                                        |

| Figure. 5.5 The complexity of the principal procedures in the partitioning algorithm 82 |

| Figure. 5.6 The search directions in the codesign space exploration                     |

| Figure. 6.1 The codesign target architecture                                            |

| Figure. 6.2 The FFT transform C program                                                 |

| Figure. 6.3 The hierarchical model of the FFT transform behavior                        |

| Figure. 6.4 ASAP/ALAP scheduling at two different levels of the FFT hierarchy           |

| Figure. 6.5 The matlab program of the network simulation algorithm 100                  |

| Figure. 6.6 The hierarchical model of the network simulation behavior                   |

| Figure. A.1 The technology file of the PULSE processor                                  |

| Figure. A.2 The technology file for the C40 processor                                   |

# **LIST OF TABLES**

| Table.2.1 Fields of system design with related work                                         |

|---------------------------------------------------------------------------------------------|

| Table.4.1 Memory size of the base types    54                                               |

| Table.5.1 Comparison of the common partitioning methods.    70                              |

| Table.6.1 Performance estimation of the FFT blocks                                          |

| Table.6.2 The FFT transform partitioning under timing constraints       95                  |

| Table.6.3 Block assignment at different hierarchical levels of the FFT model                |

| Table.6.4 Alternative comparison for the FFT transform                                      |

| Table.6.5 The performance estimation for the power network simulator blocks 104             |

| Table.6.6 Block assignment at different hierarchical levels of the network simulation algo- |

| rithm                                                                                       |

| Table.6.7 Codesign alternatives for the network simulation algorithm                        |

## **Claim of originality**

The author claims originality for the following contributions of the dissertation:

- Chapters 1 through 5 contain reviews in their first sections, although these reviews are original in the sense of providing a new classification of related works according to determinant characteristics in the codesign field.

- Chapter 2 presents a novel codesign flow based on the hierarchy and performance estimation. This flow is reiterated for each level in the hierarchy.

- Chapter 3 develops a new use of hierarchy for models of digital systems described at high-level. The hierarchy is not presented as a new approach for design but is considered in a different way. The majority of modeling tools support hierarchy but only to allow handling complex systems. We exploit this same hierarchy used to simplify the modeling step to provide various input models for the same input system. This use of hierarchy provides an expansion of the modeling space because different input models are available for each level of the hierarchy, but also an expansion of the codesign space because a hardware-software solution may be found for each level of the hierarchy. Our Codesign process consider at each level of the hierarchy a set of blocks with different abstraction when moving through the hierarchy levels.

- Chapter 4 proposes a new analysis methodology for the codesign of digital systems. The analysis is performed in two stages: the performance estimation and the task scheduling. The performance estimation is performed using known automatic estimators but we provide these available estimators with technology files for each resource of our target architecture. The task scheduling is performed to find critical paths and bottlenecks in the system execution. The scheduling step identifies the concurrency between the system tasks in an independent way of the partitioning.

- Chapter 5 proposes a new hardware-software partitioning algorithm based on a dependency graph partitioning. The nodes and edges of the dependency graph are weighted in order to minimize the system execution time and the hardware-software communication overhead. The hardware-software partitioning is performed on the basis of two types of selection, global and neighborhood. The global selection selects the bottlenecks in the system to accelerate the system execution. The neighborhood selection operates on the neighbors of the bottlenecks in order to minimize the hard-ware-software communication overhead.

- Chapter 6 provides extensive experimental verification on two case studies. For each case study, two lists of hardware-software partitioning alternatives are provided: the timing constraint list and the hierarchy list. The timing constraint list gives the list of hardware-software partitioning alternatives obtained for different timing constraints. The hierarchy list provides a list of hardware-software partitioning alternatives for the same timing constraint but at different levels of the hierarchy.

- Chapter 6 also provides a comparison between the hardware-software alternatives obtained for the same timing constraint to show the necessity of a performance-area tradeoff.

# 1

# INTRODUCTION

System-level design usually involves designing an application specified at a highlevel abstraction. A typical design objective is to minimize cost (in terms of area or power) while the performance constraints are usually throughput or latency requirements. The specification at system level is built of basic components called tasks. This specification has two characteristics. First, tasks are at a higher level of abstraction than atomic operations or instructions. This allows for complex applications to be described easily and more naturally. Secondly, there is no commitment to how the system is implemented. Since the specification does not assume a particular architecture, it is possible to generate either a hardware, or a software, or a mixed implementation. This is specially important for the synthesis of complex applications whose cost and performance constraints often demand a mixed hardware-software implementation. For such applications, full-software implementations (program running on a programmable processor) often cannot meet the performance requirements, while custom-hardware solutions (custom ASIC) may increase design and product costs. It is important therefore, not to commit each task in the application to a particular mapping (hardware or software) or implementation when specifying the application. The appropriate implementation for each task can be selected by a global optimization procedure after the specification stage. The task level of abstraction allows this flexibility. Manual development of a lower-level design specification (such as at the RTL level) is quite intense due to the complexity of the applications. As a result, it is desirable to specify the application at the task level and allow a design tool to generate lower levels of implementation from it.

Such a system-level design approach is now viable due to the maturity of lower level design tools and semiconductor technology. Computer-aided design tools that operate at lower levels of abstraction are quite robust. The next step is to use these CAD tools for system-level design. Also, advances in semiconductor manufacturing have made it possible to fabricate a "system on a chip".

Figure 1.1 summarizes the key issues in system-level design. These are system specification, modeling, partitioning, synthesis, simulation and design-space exploration. A system is first specified in a high-level language as a set of tasks. It is then transformed into a model to catch its functionality details at a high-level of abstraction. Several hardware and software implementation options are usually available for each task in the description. The partitioning process determines an appropriate mapping (hardware or software) for each task. A partitioned application has to be synthesized and simulated within a unified framework that involves the hardware and software components as well as the generated interfaces. The software synthesis of a task is to generate the code for the task on a given processor. Finally, the validation of the final implementation is often performed using co-

2

simulation tools. The system-level design space is quite large. Typically, the designer needs to explore the possible options, tools, and architectures, choosing either automated tools or manually selecting his/her choices (feedbacks in Figure 1.1). A design-space exploration framework attempts to ease this process.

The most important aspect of system-level design is the multiplicity of design and modeling options available for every task in the specification. Each task can be implemented in several ways in both hardware and software mappings, and can also be modeled as a big black box, a set of subblocks or a set of basic operations. The partitioning problem is to select an appropriate mapping of each task from a given model. In system-level design, there are a number of such tasks and overall design is to be optimized. Clearly, it is not enough to optimize each task independently. For example, if each task were fed to a highlevel hardware synthesis tool that optimized for speed, then the overall area of the system might be too large. Hardware-software partitioning is the problem of determining an implementation of each task so that the overall design is optimized.

Once the appropriate implementation for each task has been determined, the hardware-software synthesis problem is that of synthesizing the implementation. Implementations for tasks mapped to hardware or software can be generated by feeding the task descriptions to synthesis tools. The hardware synthesis consists of high-level synthesis [McFarland 90] followed by logic synthesis [Brayton90] and layout synthesis [DeMicheli86]. The software synthesis comprises high-level software synthesis [Pino95], followed by compilation and assembly. System-level design is not a black-box process, but relies considerably on user creativity and interaction. For instance, the user might want to experiment with the design parameters. The design process could get quite anwieldy as the

3

user experiments with the design methodology. As a result, an infrastructure that supports design space exploration is also a key aspect of the system-level design process. Tools for design space exploration must include performance estimation tools. Estimation tools give quick predictions on the outcome of applying certain synthesis or transformation tools.

Figure 1.1. The hardware/software codesign process.

Designing systems containing both harware and software components is not a new problem. The traditional design approach has been somewhat hardware first in that the software components are designed after the hardware has been designed and prototyped. This leaves little flexibility in evaluating different design options and hardware-software mappings. With isolated hardware and software design paths, it also becomes difficult to optimize the design as a whole. Such a design approach is especially inadequate when designing systems requiring strict performance and a small design cycle time. The key tenet in codesign is to avoid isolation between hardware and software designs to proceed in parallel, with feedback and interaction between the two as the design progresses. This is accomplished by developing tools and methodologies that support coupled design of hardware and software through a unified framework. The goal of codesigning the hardware and the software components of a system is to achieve high quality designs with a reduced design time.

Our main objective, in this thesis, is to provide efficient solutions to some relevant codesign problems. The main tasks involved in the codesign process have been presented in the above paragraphs. These are the system modeling, the system parformance estimation and the hardware/software partitioning. The techniques used to perform such tasks are determinant on the final hardware/software implementation. We propose new and original techniques to perform these tasks with the objective of providing more efficiency and better design space exploration. The proposed objectives with a statement of originality are presented below for each one of these tasks.

#### 1.1. Modeling

The specification at the system level is often modeled as a set of tasks. These tasks are described at the basic operation level in some modeling framework or at the process level (sequence of basic operations) in some others.

Digital systems are becoming more and more complex and this complexity involves the use of new modeling characteristics, as the hierarchy in order to make the modeling of such complex systems tractable. The hierarchy has been proven to be extremely useful when modeling highly complex systems. The majority of modeling tools include the hierarchy in their modeling approach. In this thesis, we consider the hier-

5

archical model available and we propose a new use of this available hierarchy. The hierarchy is not used only to ease the modeling process but all along the codesign process by considering the different modeling alternatives available in a hierarchical model, each one with a different complexity.

The main objective intended by this use of hierarchy is to have several modeling alternatives and to codesign each one of these alternatives. Many co-implementation alternatives are then provided since a possible hardware/software implementation with its own performance and cost is found for each one of the modeling alternatives. This use of hierarchy is a new and original way to expand the design space exploration which is a key tenet in the codesign process.

#### 1. 2. Performance estimation

In literature, many tools are available for performance estimation on a specific target architecture. The available estimation tools are often tied to a specific architecture and new tools have to be developed if the target architecture is changed. We intend in this thesis to use generic estimation tools that can be tied dynamically to any target architecture. The target architecture resources are first described in a generic way and put into the data base of the estimation tools. Then, the estimators consider any input algorithmic specification and provide performance estimation measures when the input algorithm is run or implemented on the selected resources. The main objective, at this step, is the flexibility to consider many possible target architectures for the same input system specification rather than having one target architecture fixed at the very early stages of the design.

#### 1. 3. Partitioning

Partitioning is the main task in the codesign process since the final hardware/software implementation is tightly dependent on the techniques used to select and map the tasks to hardware or to software. Many automatic partitioning algorithms have been proposed during the past years but without convincing codesigners to adopt the automatic solution. Codesigners have not enough confidence in an automatic solution for partitioning because they want to make the main decisions by themselves.

We propose a partitioning solution which is between the complete automated and manual partitioning. We propose an automatic partitioning technique which attempts to try several task mappings and then provides the desiger with the obtained alternatives and their performance estimations. The automatic partitioning algorithm is in charge of the complex and iterative search process while the decision of selecting the final implementation is left to the designer.

This thesis presents in detail each one of the original proposals presented above. Chapter 2 briefly presents an overview of related work in system design and computer-aided techniques developed for system synthesis, and the general scheme of the proposed codesign framework. The organization of the rest of thesis can be explained by relating it to the organization of our codesign CAD framework. The input to our system is an algorithmic description of the system functionality. The description is compiled into a hierarchical system graph model based on dataflow graphs whose features and properties are described in Chapter 3. Chapter 4 describes performance estimation and analysis techniques used to predict the performances of possible hardware/software implementations. In chapter 5, we define the problem of system partitioning and present an automatic approach to partitioning digital systems for hardware/software cosynthesis. Chapter 6 describes case studies considered for hardware/software codesign and the results obtained after applying our codesign approach. Chapter 7 presents conclusions where the objectives defined above are recalled in the context of obtained results and finally the directions for future research are presented.

•

# 2

# CODESIGN METHODOLOGY

While the CAD tools for the design of individual application specific ICs, or ASICs, are in a fairly mature state, in some application domains it is even possible to completely synthesize an ASIC from a high-level behavioral description in a matter of hours, CAD methodology for dedicated systems have not kept pace. Real-life systems are composed of a mix of software running on general purpose programmable hardware, ASICs and other dedicated hardware, electromechanical components, and mechanical interconnect and packaging, and a unified approach that encompasses the various software, hardware, and mechanical aspects of system design is desirable.

The increased functional and implementation complexity and heterogeneity of systems mean that one cannot just scale and apply chip design techniques to the design of a system. For example, it is difficult and unnatural to represent and simulate an entire system according to a single computation model as is usually done in the case of chips. This simple architecture model of a single controller and a datapath as used for chips is inadequate for most board level systems. Clock synchronous hardware implementation is usually adequate for chip but not for an entire system. Software issues are absent in a chip design as ASICs mostly have hardwired controllers. In short, system level design is more than just a scaled version of chip design.

Since system-level design oversees high-level synthesis, logic synthesis, etc..., decisions made at the system level impact all the layers below it. In other words, if the objective in system-level design is to come up with the "best" system implementation, there are a large number of design options. The system-level designer is faced with the questions of selecting the best design options.

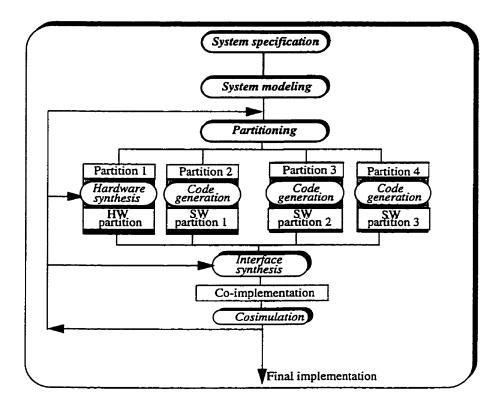

The general design methodology is shown in Figure 2.1. The inputs to the codesign tool include the design specification and the design constraints, and the output is an implementation for the system. This chapter describes the various components of the standard codesign tool. In section 2.2, the codesign problem is stated with all the involved steps. In section 2.3, a typical codesign flow is described and the various tools required in the codesign process are outlined. In section 2.4, we present a list of the most known frameworks related to the codesign of digital systems. In section 2.5, we outline the proposed methodology with the advantages it offers compared to the related works.

## 2. 1. Motivations for hardware/software codesign

Most digital functions can be implemented by software programs. The major reason for building dedicated application-specific hardware (ASICs) is the satisfaction of performance constraints. These performance constraints can be on the overall time (latency) to perform a given task, or more specifically on the timing to perform a subtask and/or on the ability to sustain specified input/ouptut data rates over multiple executions of the system model. The hardware performance depends on the results of operation scheduling and the performance characteristics of individual hardware resources. The software performance depends on the number of instructions the processor must execute and the cycles-per-in-struction metric of the processor. In general, application-specific hardware implementations are faster since the underlying hardware is optimized for the specific set of tasks. However, some parts of the description of an ASIC machine may be well suited to a commonly available reprogrammable processor while others may take too long to execute.

## 2. 2. The codesign problem statement

Hardware software codesign is a complex problem that involves the following subproblems:

1. Modeling the system functionality and performance constraints

System modeling refers to the specification problem of capturing important aspects of system functionality and constraints to facilitate design implementation and evaluation. Among the important issues relevant to mixed system designs are:

- . Explicit or implicit concurrency in the specification.

- . Model of communication- shared memory versus message passing-.

- . Control flow specification or scheduling information.

When the concurrency is implicit, the concurrency information is obtained by performing a dependency analysis for which the complexity depends on the system model used.

- 2. Choosing the granularity of the hardware/software partitions. The system functionality can be handled either at the functional abstraction level, where a certain set of operations is partitioned, or at the process communication level where a system model composed of interacting process models is mapped onto either hardware or software. The former attempts fine-grain partitioning while the later attempts a high-level library binding through coarse-grain partitioning. Each choice has advantages and disadvantages. The first one allows efficient and refined analysis and transformations but at a higher computing complexity. The second one reduces the processing complexity with a loss in design efficiency since blocks or processes are considered instead of basic operations. This reduces the partitioning alternatives compared to those available at the basic operation level.

- 3. Determining the feasible partitions of application-specific and re-programmable components. The blocks in the system functionality are assigned to hardware or to software in such a way that the resulting implementation satisfies the functionality requirements and the constraints. This is a difficult problem because good system-level cost metrics, accurate techniques for estimating the cost, and techniques for reliable performance estimation of system-level hardware and software are required.

- 4. Specifying and synthesizing the hardware, the software and the hardware/ software interface. Each one of the determined partitions is synthesized to obtain the final implementation using the automatic tools available on the mar-

ket. This synthesis is also done under performance and cost constraints.Hardware and software synthesis tools use different specification languages (for example, VHDL for hardware synthesis and C for software synthesis) and thus the resulting partitions must be translated to the specific description language in order to be automatically synthesized.

The next chapters focus on the various aspects of the codesign process with the proposition made for each one of these steps. In the next section, we follow the codesign problem presentation by showing a typical codesign flow in section 2.3. In section 2.4, a list of related works in codesign are classified according to their major characteristics. In section 2.5, our proposed codesign framework is presented.

### 2. 3. A typical codesign flow and tools for codesign

A typical codesign flow is shown in Figure 2.1. A task-level specification is transformed into the final implementation by a sequence of tools. The final implementation consists of custom and commodity programmable hardware components and the software running on the programmable components. The design constraints include the desired throughput and the architectural model (maximum allowable hardware area, memory size, communication model). The design flow describes the sequences of steps that operate on the design data to generate the final implementation. The components of the codesign flow include tools for modeling, analysis, partitioning, synthesis and simulation.

#### 2.3.1 System modeling

Models are often needed in order to avoid creating detailed implementations. A mod-

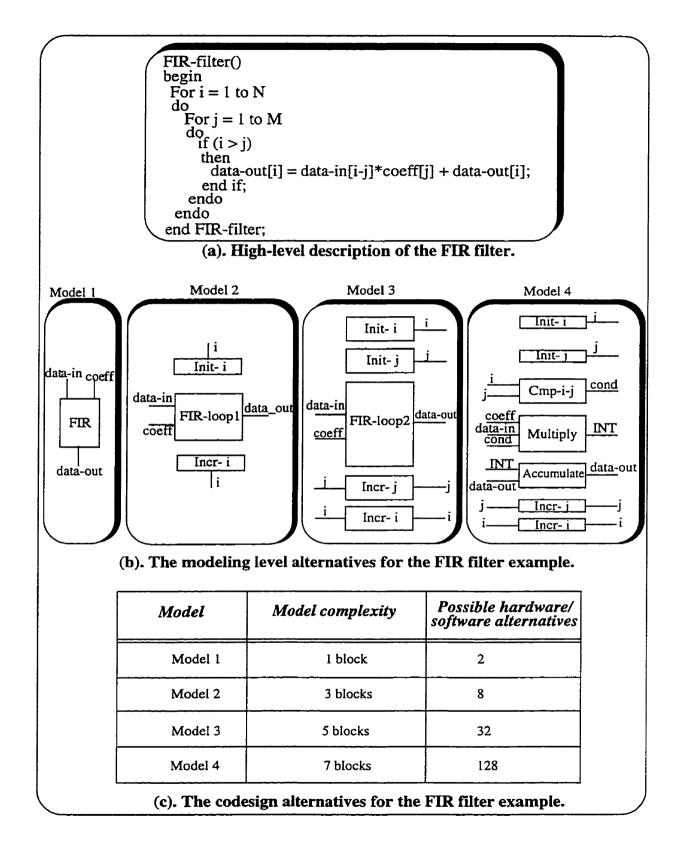

el of a system helps to estimate relevant properties, like area and delay, of its implementations. The model is built from a set of interconnected basic elements. The model complexity depends on the basic element complexity. Indeed, if the basic element is an arithmetic or logical operation, the model may be very complex because the majority of systems are generally constituted of a large set of these simple operations. If the basic element is a task or a process (a set of interconnected basic operations), the model complexity may be reduced considerably. This means that the model complexity depends on the model granularity. The more the granularity is fine the more the model is complex and hard to handle. We propose a modeling technique with a variable granularity that allows the use of a simple model as long as the constraints are satisfied. We handle complex models only when the constraints cannot be satisfied with simple models. In chapter 3, we show the advantages of such a modeling technique.

#### 2.3.2 System analysis

The system analysis involves two main tasks. These are the performance estimation and the scheduling of the model tasks. The performance estimation provides estimates of the implementation metrics (area and execution time requirements) for each of the tasks in the specification when different hardware and software realizations are considered. The scheduling determines the possible execution flows of the different tasks based on their data dependencies. The estimates and task scheduling guide the partitioning algorithm during the task mapping. Details of the estimation and scheduling tools are discussed in chapter 4.

#### 2.3.3 Partitioning

Once the estimates of the area and execution time and the scheduling of the functional

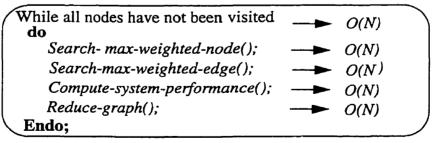

blocks have been performed, the next step in the codesign flow is the partitioning. The goal of the partitioning is to determine, for each task the mapping to hardware or to software while optimizing the overall design. The partitioning is a non-trivial problem. Consider a task-level specification, typically in the order of 50 to 100 tasks or nodes. Each task can be mapped to either hardware or software. Furthermore, within a given mapping, a task can be implemented in one of several options. Suppose there are 5 design options. Thus, there are  $(2 \times 5)^{100}$  design options in the worst case! Although a designer may have a preferred implementation for some p nodes, there are still a large number of design alternatives with respect to the remaining nodes  $(2 \times 5)^{100-p}$ . Determining the best design option for these remaining nodes is, in fact, a constrained optimization problem. In section 5.3, the partitioning algorithm that uses a graph partitioning heuristic is presented. The proposed heuristic is very efficient with the complexity  $O(N^2)$ , where N is the number of tasks in the design specification.

#### 2.3.4 Cosynthesis

Once the application is partiotioned into hardware and software, the individual hardware, software, and interface components are synthesized. The particular synthesis tool used depends on the desired technology. The VHDL code can be generated and passed through synopsys tools to generate the hardware implementation. Similarly, different software synthesis strategies can be used; for instance, the C description may be generated. The interface generation depends on the desired architectural model. There are several published approaches to the problem of synthesizing hardware and software from high-level specification.

#### 2.3.5 Cosimulation

Once the hardware, software, and the interface components are synthesized, a validation/verification step is required. This is often a cosimulation of the different components, hardware, programmable hardware and software. Examples of such cosimulation tools are Ptolemy (Stanford University) and logic modeling [Synopsys95].

We propose a codesign tool as a framework for system-level design. The tool is a unified platform consisting of tools for modeling, analyzing and partitioning of mixed hardware-software systems. Simulation and synthesis tools may be used from those available on the market.

Figure 2.1. The typical codesign flow process.

## 2.4. Related work

Work in the computer-aided approach to system design is relatively new. Recent in-

terest in system synthesis has been stimulated by the success and maturity of chip-level synthesis tools and the emergence of synthesis approaches at levels of abstraction higher than logic-level and RTL-level circuit description. In the follow sections, we briefly review related work that is directly relevant to the codesign problem.

Table 2.1 gives some pointers to fields in system design. A system design typically requires to address all these topics. But the relevance of each topic depends very much on the considered application domain. For example in avionics, the system security and a validated design are of the utmost importance, whereas in digital signal processing the high performance power and the chip complexity are the main design topics.

Achieving performance requires a careful tailoring of the system structure to the requirements imposed by the algorithms. For complex applications, this makes an analysis of the programs necessary to determining the requirements. Analysis tools are required to support this in a an efficient way. Table 2.1 gives the list of some codesign works with the main codesign problems each of them has addressed. In the next paragraphs, these problems are listed with the solutions proposed in literature.

#### 2.4.1 Specification and verification

The input system is specified into a formal language that allows an easy and formal specification with functionality checking and verification facility. This specification is determinant for the next steps in the codesign flow. The more efficient the specification language is, the easier are the analysis and partitioning steps. Some codesign frameworks in literature are dedicated mainly for a strong and efficient formal language for specification and verification.

One of these works is CODES [Buchenrieder92] which stands for COncurrent DES-

17

sign. The system is specified as a set of communicating parallel random access machines (PRAMs). The design process is modeled using Petri Nets which are a well known strong formal modeling technique. The input specification is simulated using StateMate or SDL tools widely used for the communication protocol simulation and verification.

Another work concentrating on the formal specification language is COSMOS [BenIsmail94b]. The main objective of this codesign framework is to provide an intermediate format SOLAR [O'Brien95] which can model system-level constructs in a synthesisoriented manner. The philosophy is to allow the designer to use customized languages to describe different aspects of his system and to provide translators to this intermediate form. SOLAR is able to model and synthesize a wide range of communication schemes between concurrent processes.

Another work related to specification and modeling is the SpecCharts formal language [Gajski93] developped by Gajski et al. at the university of California at Irvine. This formal language is an attempt to build a bridge between hardware and software specifications. The system's behavior is conceptualized as a hierarchy of sequential and concurrent behaviors. The hierarchical structure is described in the language SpecCharts while the basic behaviors are described in VHDL language. This has been a very elegant solution for modeling both hardware and software but raises the question of the need for a standard.

The last work in this category of frameworks concentrating on specification and modeling is the tool developped by Chiodo et al. [Chiodo94]. This tool uses a unified formal specification model called network of Codesign Finite State Machines (CFSMs) to describe control-dominant systems characterized by relatively low algorithmic complexity such as embedded controllers. The modeling tool is also used to describe techniques to realize a

18

CFSM as either a hardware or software FSM, to generate the interfaces between the resulting hardware and/or software FSMs.

#### 2.4.2 Co-simulation

Simulation is a very uselful facility at the starting of the design to check the functionality and at the end of the design to verify the design implementation. The simulation is often used as an alternative to formal verification for complex systems.

The main framework known for system-level simulation is PTOLEMY [Buck94a]. PTOLEMY is a framework for the simulation, prototyping and software synthesis of digital signal processing systems. PTOLEMY's strength is its unified framework that primarily addresses the simulation of specifications as a set of heteregeneous computation models constituting a DSP system. Examples of supported models are synchronous data flow (SDF), dynamic data flow (DDF), discrete events (DE) and signal-level digital hardware (Thor).

In addition to a simulation framework, PTOLEMY also provides code generation abilities for its synchronous data flow (SDF) model using DSP processors, C, Silage or VHDL languages as targets. The strength in heterogeneity by use of diverse computation models in Ptolemy comes at the loss of an analytical handle on system properties when the input system is not from a DSP application...This is particularly true for system specifications that feature a significant amount of control flow. Nevertheless, Ptolemy represents an important step towards simulation of complex systems.

#### 2.4.3 System analysis

The codesign process requires a profiling and a performance analysis of the input

specification in order to find a final implementation for the different system blocks such that the overall system performance is optimized. This analysis phase is determinant for an efficient hardware/software partitioning. Some codesign frameworks emphasize on this apsect as SpecSyn [Vahid92] and CASTLE [Theinbinger94].

SpecSyn is an automatic codesign framework which uses the SpecCharts language for the input specification. The hardware and software performance and area estimation may be determined for a wide range of resources described into technology files. The technology file library contains many standard processors and some custom ASIC types.

CASTLE is a complete cosynthesis environment in which data flow graph (DFG) representation is derived from an array of specification formats as Verilog, VHDL and C. This environment has very efficient profiling and analysis procedures which provide the designer with a wide range of information allowing him to make manually the appropriate mapping of the model's operations.

#### 2.4.4 Partitioning

Several partitioning algorithms have been proposed in literature and are presented with more details in chapter 5. Here, we briefly review some of the codesign frameworks which are mainly intended for partitioning.

COSYMA [Henkel93], CO-SYnthesis for eMmbedded Architectures, performs partitioning of operations at the basic block level with the goal of providing speedup in program execution time using hardware co-processors. Input to COSYMA consists of an annoted C-program. This input is compiled into a set of basic blocks and corresponding Directed Acyclic Graph or DAG-based syntax graphs. The syntax graphs are helpful in performing dataflow analysis for definition and use of variables that helps in estimating communication overheads accross hardware and software. The syntax graphs are partitioned using simulated annealing algorithm under a cost function. This process is repeated using exact performance parameters from synthesis results for a given partition.

The chief advantage of this approach is the ability to utilize advanced software structures that result in enlarging the complexity of system designs. However, selective hardware extraction on potential speedups makes this scheme relatively limited in exploiting potential use of hardware components. Further, the assumption that hardware and software components execute in an interleaved manner (and not concurrently) results in a system that under-utilizes its resources.

Another framework based on the language UNITY for the specification of concurrent systems [Barros94] uses clustering for partitioning. The partitioning scheme associated with it classifies UNITY assignments according to a set of five attributes which identify the degree of data dependency and parallelism between assignments. Associated with each of these attributes is a set of implementation alternatives. A two-stage clustering algorithm then selects assignments to be grouped according to similarity of implementation alternatives, data dependencies, resource sharing and performance. The clustered assignments are scheduled for a given target architecture. Finally, an interface graph is constructed based on clustering results. This process is then reiterated based on satisfaction of design constraints.

The last framework presented here is VULCAN II [Gupta93]. VULCAN II addresses the problem using I/O data rate constraints to partition a description in Hardware C such that a maximal set of operations is implemented as software running on a microprocessor while the remaining operations are mapped to ASICs in a common-memory shared-bus architecture. The partitioning algorithm is greedy and moves non-deterministic delay opera-

21

tions to software in order to meet hardware cost constraints while satisfying performance requirements.

#### 2.4.5 Cosynthesis and prototyping

Once a system has been analyzed and partitioned, the different resulting partitions need to be implemented to obtain the final concurrent hardware/software implementation. This is performed by a synthesis phase of each one of the partitions using two types of techniques, standard synthesis tools or by protototyping each one of these partitions on an existing architecture. Academical examples for the two types are presented below.

From the first class, we present Chinook tool for the cosynthesis of real-time reactive embedded systems [Chou95]. The Chinook system consists of six tools. The first one is a front-end parser of system descriptions in annoted Verilog. The second one is the processor/ device library containing detailed generic specification of the processor device interfaces as well as timing schemas for software run-time estimation. The third tool is the device/ driver synthesizer that compiles the timing diagrams and Verilog devices into a customized code for the given processor. The fourth tool is the interface synthesizer which has the role of allocating I/O resources to connect a processor to the desired peripheral devices and customizing the access routines accordingly. The fifth tool is the communication synthesizer in charge of generating the hardware and software needed from inter-processor communication. The last tool is the scheduler which generates C code to meet real-time constraints in software with all resources allocated.

The chief advantage of this approach is its efficiency in building suitable input/output interfaces for controlling external devices.

The second class is based on prototyping. A typical example is the SIERA tool

[Srivastava95]. SIERA is a framework for rapid prototyping of systems that span across chip and multiprocessor boards in hardware as well as device drivers and operating system kernels in software. This work utilizes chip-level synthesis tools and DSP code synthesis tools to present a framework for performing both activities. A system is specified as a network of concurrent sequential processes in VHDL. The communication between processes is by means of queues. This specification is manually mapped into an architecture template. The main strength of this methodology lies in management of system complexity by using modularity and reusability afforded by existing libraries.

Other codesign aspects have been addressed in literature too. One of them is the code generation for the software synthesis. Typically, flexible processors are used for software implementation. Another codesign interest is related to case studies on specific examples. Applying design automation to real-life problems provides insight into the complexity and requirements demanded by these systems.

The related work review, presented above, is not exhaustive but merely representative of the contemporary work by examining important CAD frameworks for codesign.

| Topics                       | References                                                               |  |  |

|------------------------------|--------------------------------------------------------------------------|--|--|

| Specification & verification | CODES [Buchenrieder92], COSMOS [BenIsmail 94b],<br>SpecCharts [Gajski93] |  |  |

| Simulation                   | PTOLEMY [Buck94b], Insulin [Sutarwala93]                                 |  |  |

| Analysis                     | ADAM [Jain92], SPECSYN [Vahid92], CASTLE [Theibinger94]                  |  |  |

| Partitioning                 | COSYMA [Henkel94], VULCAN II[Gupta93], UNITY[Barros93]                   |  |  |

| Cosynthesis and prototyping  | Chinook [Chou95], SIERA[Srivastava95]                                    |  |  |

| Case studies and             | MPEG[Wilberg96]                                                          |  |  |

| Code generation              | CAPSYS [Auguin94], CodeSyn [Lien94]                                      |  |  |

Table 2.1: Fields of system design with related work

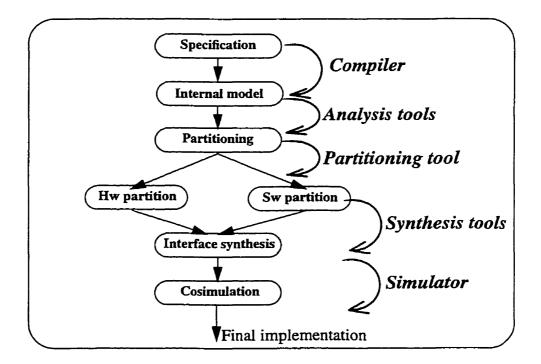

# 2. 5. The proposed codesign framework

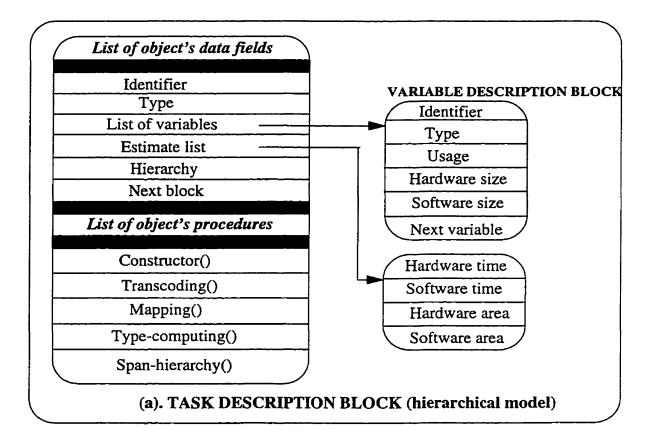

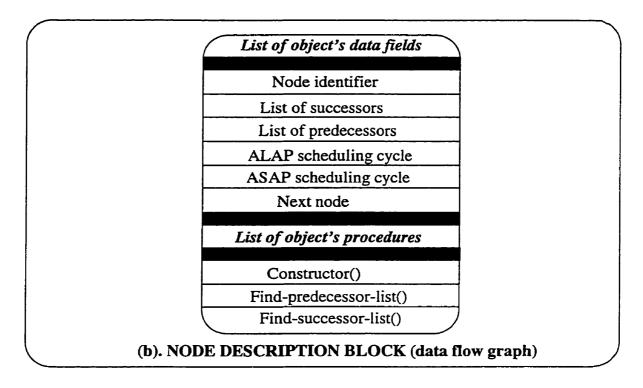

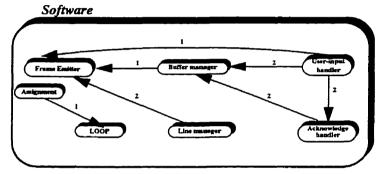

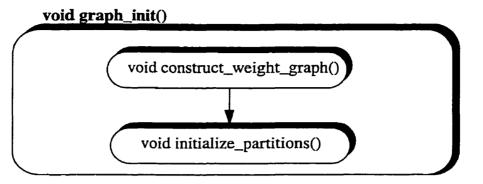

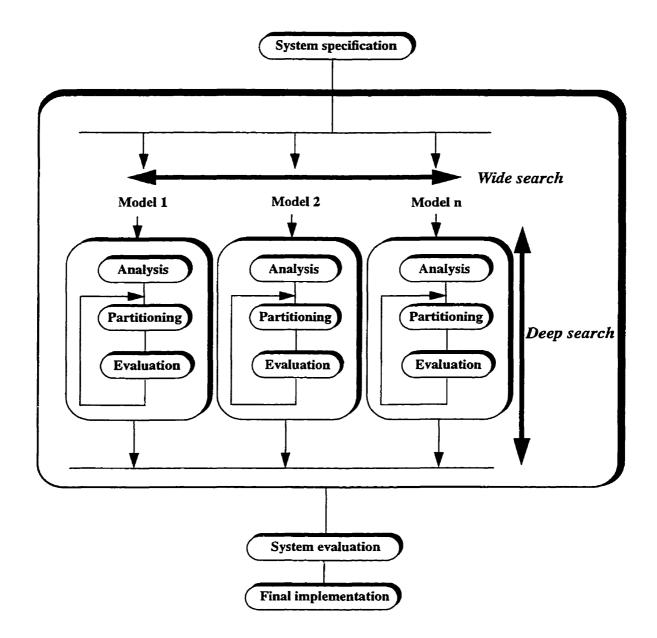

Our proposed methodology is presented according to the codesign problem statement already presented in section 2.1. Figure 2.2 shows the proposed codesign flow. The input specification is described in any HDL or programming language where a certain hierarchy is inherent. This description is then manually translated into a hierarchical model based on data flow graphs. The hierarchical model can also be taken from any modeling tool available on the market. Each element or task in the model is a node in a graph, this node may be a simple basic operation or may be decomposed into a subgraph where sub-nodes may be basic operations or other data flow graphs. Edges between nodes correspond to data dependencies between operations or tasks. The hierarchy of the input system allows the use of a variable granularity rather than a fixed one at the level of basic operations or at the level of tasks.

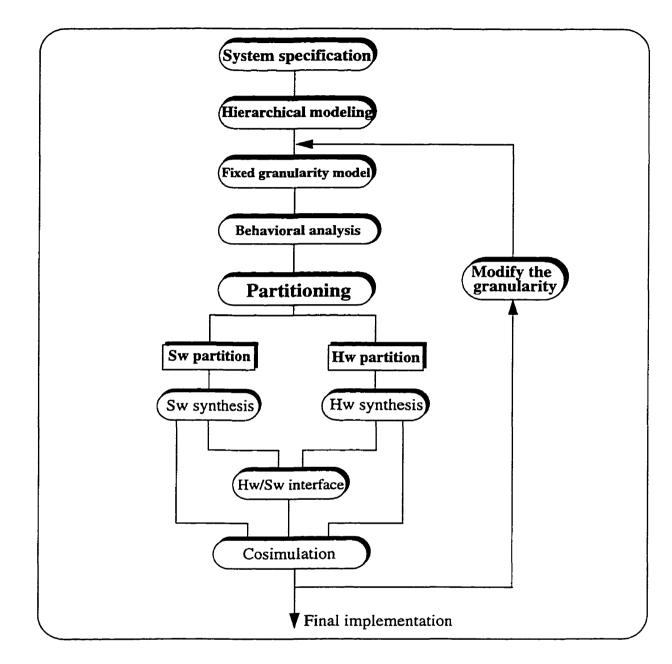

Figure 2.3(b) shows the different modeling views provided by the hierarchy for the FIR filter example described in Figure 2.3(a).

The FIR behavior may be built of one black box with all the inputs and outputs, or of three blocks where the outer loop (the first For loop) is decomposed, or five blocks where the two loops are decomposed or finally of seven blocks corresponding to the assignment, comparison, multiplication and addition basic operations.

This model is then estimated in order to determine for each node in the model the performance and area metrics when implemented into hardware or software using the Specsyn estimators. We provide the technology files of our specific resources to these estimators

24

[Gong95]. The technology files describe the target hardware and software.

The next step is the partitioning. A level of hierarchy or a given granularity is first selected. This results in a set of tasks corresponding to the system model at the chosen granularity. These tasks are then assigned to hardware or to software while minimizing a cost function and satifying a performance constraint. Figure 2.3(c) shows the number of possible hardware/software partitionings for each one of the possible models for the FIR filter. The more the number of blocks increases, the more the number of possible alternatives increases too and the more the partitioning algorithm becomes complex. We will show in the next chapters how the optimal modeling level may be found to satisfy the performance constraints while simplifying the partitioning algorithm.

Once a hardware or a software implementation has been determined for each element, the hardware and software synthesis are performed according to the processor on which the software will be run and to the hardware technology targeted for hardware. The interface between the two partitions is also synthesized. The final implementation is then validated using a cosimulation environement.

One of the main contributions in the proposed codesign framework, shown in Figure 2.2, is the possibility to choose different granularities. The tool starts at the simplest model of the input system by fixing a coarse-grain modeling. The model is built of a small number of components and the partitioning algorithm complexity is of course reduced. If the constraints are not satisfied using this modeling level, the tool may change the granularity towards fine-grain modeling. The number of components increases but the design exploration may be more efficient. We will show later in chapter 6 how the variation of the granularity allows a very efficient design space exploration.

25

Figure 2.2. The proposed codesign flow.

Figure 2.3. Modeling and codesign alternatives.

The proposed codesign approach provides new contributions for the following aspects:

- 1. The proposed use of hierarchy overcomes many of the limitations of modeling techniques. Our approach supports various models from the simplest to the most complex for the same input system. These modeling alternatives are already available in any hierarchical modeling tool but we propose to take advantage of it during the codesign process. A main feature in codesign is to explore the design space efficiently in order to find the best final implementation. Our modeling technique allows an enlargement of the modeling space for the same input system and thus a large choice for the final implementation.

- 2. A model analysis step is performed to estimate the performance of each block and to determine the critical blocks with all the possible concurrency between them. This analysis step provides very important information that will later guide the partitioning algorithm in order to optimize the overall system performance.

- 3. The partitioning algorithms in the literature are various but a non-negligeable number of codesign frameworks perform partitioning manually. Those partitioning algorithms which are automatic consider a limited number of parameters in order to simplify the algorithm complexity. In our proposed algorithm, many parameters may be taken into account (performance requirements, hardware/software concurrency, and communication overhead).

# 2.6. Summary

This chapter showed a typical codesign flow, a review of the most popular codesign frameworks and then the proposed methodology. Our work is not an attempt to implement a complete codesign framework, but we concentrate on specific tasks to improve the standard codesign flow. All our proposed tools and techniques are intended to be integrated into available cosynthesis tools. Developing the compiler which translates the input specification into an internal model and the hardware and software synthesis tools is out of the scope of our work. Compilers and synthesis tools are already available as industrial tools. Our objective is to propose efficient techniques for specific tasks in the codesign flow that can be easily integrated into available codesign frameworks to improve their performance and design exploration techniques. The major improvements provided by our proposition are related to the granularity flexibility that expands considerably the codesign space exploration and the pseudo-automatic partitioning approach. The follow chapters present the different codesign steps in detail with the solutions and approaches adopted in our codesign methodology. The next chapter presents the modeling technique in detail. We also concentrate in chapters 4 and 5 on the partitioning algorithm using a graph partitioning heuristic which takes into account the performance estimation and concurrency between model's tasks.

# 3

# SYSTEM SPECIFICATION

This chapter examines issues in the specification and modeling of system functionality for systems that are the target of hardware/software consynthesis. The essential idea is to capture properties of a system without regard to its implementation.

Specification and design approaches provide many advantages through a designer's lifecycle. First, by creating a test-bench early in the design process and simulating the behavior, functional errors and omissions are detected early and easily corrected. Similar corrections can be extremely difficult to make late in the design cycle. Second, by defining module behavior completely, fewer integration problems are likely to occur after concurrent design of each of the modules. Third, by using a machine readable language, automated estimators and synthesis tools can be applied to reduce the design time or to rapidly evaluate alternative implementations. Finally, by writing a behavioral specification independent of any implementation information, redesign is greatly simplified. A variety of languages have been proposed for behavioral specification, such as VHDL, Verilog, HardwareC, CSP, and

StateCharts. A good language should support a conceptual model useful for the particular system to be specified. Existing languages support conceptual models such as finite-state machines or data flow graphs.

In section 3.1, a list of the modeling techniques generally used in related work is given. In section 3.2, the proposed model is presented on examples to show the efficiency of the modeling technique.

# **3. 1. Modeling techniques**

A model refers to an abstraction over its object, capturing important relationships between components of the object. Models are often needed in order to avoid creating detailed implementation.

A formal model of a design should consist of the following components:

- 1. A functional specification (implicit or explicit relations involving inputs and outputs)

- 2. A set of properties that the design must satisfy.

- 3. A set of performance indexes that evaluate the quality of the design.

- 4. A set of constraints on performance indexes.

Common models used to capture the functionality of digital systems are listed in the next sections. Each one of these models is appropriate for a specific application field. A combination of one or two of these models may be required when using hybrid systems.

# 3.1.1 Finite State Machines

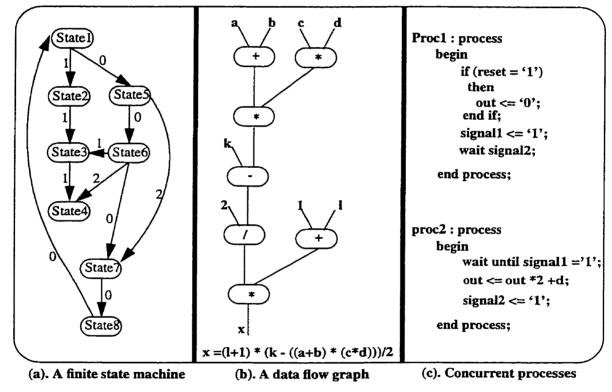

Traditional FSMs are good for modeling sequential behavior, but are impractical for modeling concurrency or memory because of the so-called state explosion. Several specification languages are based on finite-state machines, like StateCharts and SDL [BenIsmail94b]. In order to avoid their limitations, the FSMs are often improved by three characteristics to reduce the state space size: hierarchy, concurrency and non-determinism. Figure 3.1(a) shows an example of a simple FSM state digram. This state diagram shows the system control flow from one state to another or what is called state transitions. The state transitions are the edges on the state digaram. These transitions are initiated by input conditions or environmental events (values on the edges). Several common systems may be modeled as FSMs but these are more appropriate for control-dominated systems because no data processing is specified in the FSM behavior. To overcome such a limitation, extended FSMs have been proposed where the data processing is added to each state definition.

### 3.1.2 Data flow graphs

A program is specified by a directed graph where the nodes represent computations and the arcs represent totally ordered sequences of events. Examples of languages based on data flow graphs are Esterel [Dembinski], HardwareC [Gupta94], and Verilog [Hu94]. Figure 3.1(b) shows a small data flow graph where the nodes are basic arithmetic operations and the arcs shows the sequencing and data dependencies between the operations. The bottom of Figure 3.1(b) shows the arithmetic expression modeled by the data flow graph. This kind of modeling has been shown to be appropriate for data-driven applications especially digital signal processing applications. Data flow graphs have been extended to Control-Data flow graphs in order to support control-driven applications.

## 3.1.3 Communicating processes

The system behavior is described as a set of concurrent processes communicating via

message passing or shared data. This model is appropriate for control-dominated systems with concurrency which is a characteristic supported neither by finite-state machines nor by data flow graphs. An Example from this category is CSP [McFarland92] and VHDL [Eles94]. Figure 3.1(c) shows a VHDL code sample where two processes execute concurrently. The two processors are synchronized using wait statements on common signals (signal1 and signal2). Internally, each process may be modeled as an FSM or a data flow graph.

Figure 3.1. Examples of the different modeling techniques.

#### 3.1.4 Object-oriented modeling

The system behavior is described as a set of objects with their associated procedures and functions. This modeling concept is largely used in software development but its list of users and application fields is continuously increasing. This makes it a future candidate for modeling high-level systems which can be implemented in hardware or in software. An attempt to use the C++ language for high-level systems has been purposed [Forrest92].

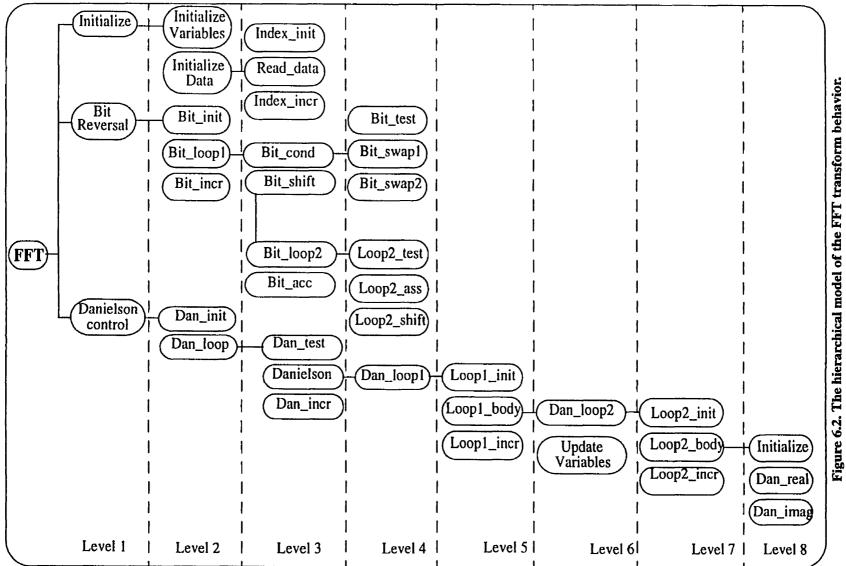

# 3.2. The proposed model

In our codesign framework, we consider the input system as a hierarchical data flow graph. This means that the system behavior is represented as a set of processes or functions, each one described as another set of processes and functions until basic nodes are reached. Basic nodes are simply basic operations like arithmetic or logical operations. Blocks or functions may be the processes from VHDL description or the procedures in a C specification. Then, each block or function is decomposed into subblocks or basic statements. When basic statements are reached, the hierarchy is stopped while non-basic statements are decomposed until their basic statements are reached. Examples of non-basic statements are loops, conditional branches or simply a block of sequential statements. Each level in the hierarchy provides a different model, in terms of complexity, for the same input system.

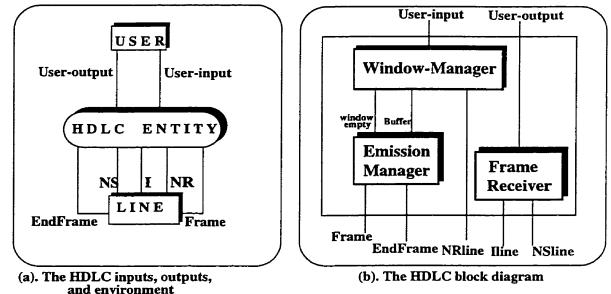

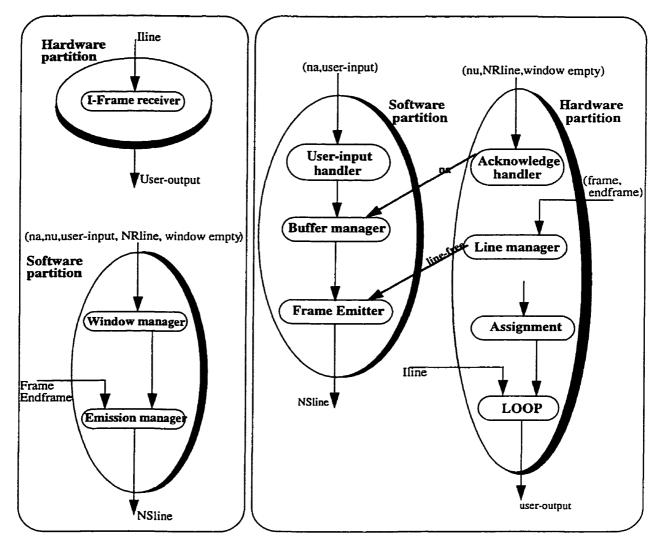

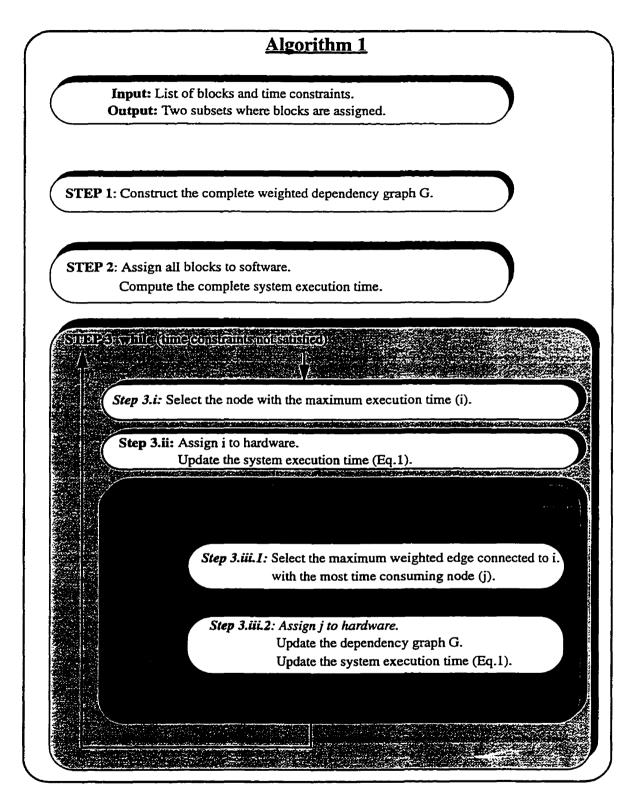

Figure 3.2(a) shows an example from the communications field, the HDLC entity with its environment [Berry91]. An HDLC entity is the set of functions needed to perform the communication between a user and the network, in such a way that all low-level functions related to the network are transparent at the user side. The HDLC entity communicates with the user via the variables, *user-Input*, and *user-output*, and with the network via the variables, *frame*, *endframe*, *iline*, *sline*, and *nrline*. Internally the HDLC functions are structured into three main blocks, the *window manager*, the *emission manager* and the *frame receiver*, as shown in Figure 3.2(b).

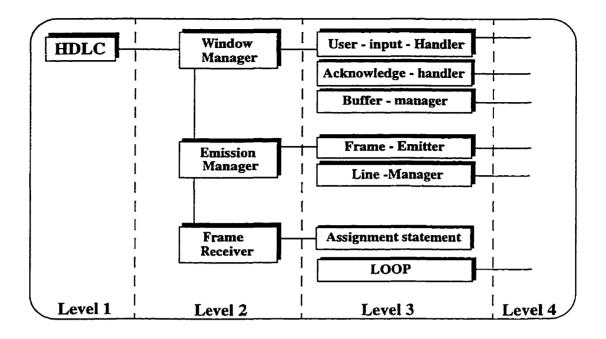

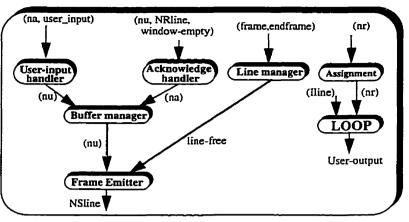

Figure 3.3 shows the HDLC entity as a hierarchy of interacting and dependent ele-

ments. We propose a new use of the already available hierarchy to consider different views of different complexity for the same system functionality. Indeed, level 1 of hierarchy shows the main block, then at level 2 the main block is decomposed into 3 blocks, the *win-dow manager* block, the *emission manager* block, and the *frame receiver* block. At level 3 of the hierarchy, each one of these blocks is decomposed into 3, 2, and 2 subblocks respectively. Note that the *frame receiver* block is constituted at this level of one basic operation (assignment statement) for which no further decomposition is possible, and a loop structure which can be decomposed in the next level as the set of basic operations of the loop body.

This example shows how the behavior is structured from few complex boxes at low levels of hierarchy to the most detailed description which is simply a lot of basic and simple operations at high levels of hierarchy. These different modeling views are available in all modeling languages supporting the hierarchy. Our main contribution is to use each one of these modeling alternatives during the codesign process.

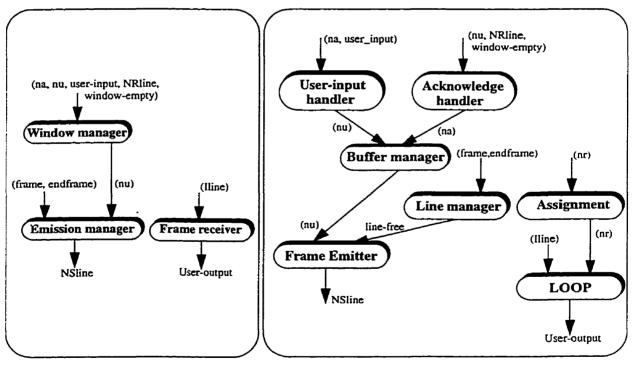

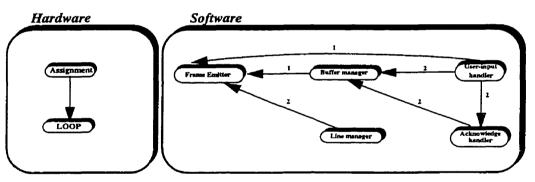

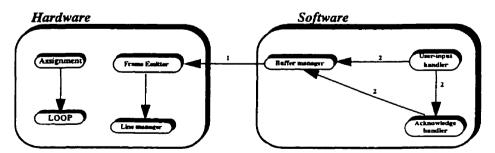

Each level of the hierarchy in the model is described as a data flow graph. Figure 3.4 shows examples of data flow graphs obtained for two different levels in the HDLC hierarchy.

A node in the data flow graph is characterized by its inputs (input edges to boxes), its outputs (ouput edges from the boxes) and the internal functionality of the node. The node may be a simple operation or a pointer to another data flow graph. Edges between nodes in the data flow graph correspond to data dependencies. Nodes that may be executed concurrently do not have any data dependencies as the *user-input handler* and *acknowledge handler* blocks. Dependent nodes have to be executed sequentially as is the case of the *frame emitter* and *line manager* blocks.

35

This data flow graph modeling allows the analysis to identify concurrent and dependent blocks in the model. In Figure 3.4(b), the blocks *acknowledge handler*, *buffer manager* and *frame emitter* have to be executed sequentially because they have data dependencies. The *buffer manager* block waits for the variable *na* which is an output of the block *acknowledge handler* and the *frame emitter* block waits for the variable *nu which is* output by the *buffer manager* block. The blocks *line manager* and *buffer manager* can be executed in parallel since there is no common variable shared by the two blocks.

•

Figure 3.2. The HDLC entity environment and block digram.

Figure 3.3. The hierarchical model of the HDLC entity.

(a). The data flow graph at level 1.

(b). The data flow graph at level 2.

When codesigning the HDLC function, the designer may start to find the best partitioning at level 1. In this case, the partitioning algorithm handles only three functional and interdependent blocks which are *the window manager*, the *emission manager* and the *frame receiver* (Figure 3.4(a)). Each block is assigned to hardware or to software based on its performance estimation determined during the performance estimation step.

The data flow graph at this level shows that the block *frame receiver* is independent of the other two blocks, the *window manager* and the *emission manager*. If the two later blocks were assigned to software and the block *frame receiver* to hardware, there will be no communication overhead because no communication is needed between the two partitions, Figure 3.5(a). Executing the *frame receiver* block concurrently with the blocks *window manager* and *emission manager* reduces the overall execution time. The total execution time is the maximum of two execution times: the *frame receiver* execution time in hardware and the sum of the *window manager* and *emission manager* software execution times.

A complete software solution where all the blocks are assigned to software would execute sequentially all the blocks even if they can be executed in parallel. The total execution time is then the sum of the execution times of the three blocks, *window manager*, *emission manager* and *frame receiver*.