OPTIMIZED ERROR COVERAGE IN BUILT-IN SELF-TEST BY OUTPUT DATA MODIFICATION

5

Yervant Zorian

VLSI Design Laboratory Department of Electrical Engineering McGill University Montreal, CANADA

thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering)

September 1987

©1987 by Y. Zorian

### Abstract

The concept of Built-In Self-Test (BIST) has recently become an increasingly attractive solution to the complex problem of testing VLSI chips. However, the realization of BIST faces some challenging problems of its own. One of these problems is to increase the quality of fault coverage of a BIST implementation, without incurring a large overhead. In particular, the loss of information in the output data compressor, which is typically a multi-input linear feedback shift register (MISR), is a major cause of concern.

In the recent past, several researchers have proposed different schemes to reduce this loss of information, while maintaining the need for a small area overhead.

In this dissertation, a new BIST scheme, based on modifying the output data before compression, is developed. This scheme, called *output data modification* (ODM), exploits the knowledge of the functionality of the circuit under test to provide a circuitspecific BIST structure. This structure is developed so that it can conveniently be implemented for any general circuit under consideration. But more importantly, a proof of effectiveness is provided to show that ODM will, on the average, be orders of magnitude better than all existing schemes in its capability to reduce the information loss, for a given amount of area overhead.

Moreover, the constructive nature of the proof will allow one to provide a simple trade-off between the reduction tolerated in information loss to the area overhead needed to affect this reduction.

#### Résumé

La vérification des circuits intégrés à très grande échelle (VLSI) constitue un problème très complexe. L'approche des tests incorporés (BIST) est une approche récente qui est de plus en plus attrayante. Néanmoins, la réalisation de puces autotestables pose de sérieux problèmes aussi. Un de ces problèmes est d'améliorer la qualité de l'autovérification du circuit sans nécéssiter une trop grande aire supplémentaire de silicium. La perte d'information résultant du verificateur/compresseur de réponse (qui est le plus souvent implémenté sous forme de régistre (Shift Register) à entrées multiples) constitue un des points d'intérêts majeurs de la recherche actuelle dans le domaine.

Récemment, plusieurs chercheurs ont proposés des approches visées à réduire la perte d'information résultant de la compression de la réponse du circuit. En général ces approches ne requiert que peu d'aire de silicium suppléméntaire. La présente dissertation propose une nouvelle approche d'autovérification. Celle-ci est basée sur la modification de la réponse du circuit avant la compréssion. L'approche, appellée "output data modification" (*ODM*), utilise la déscription fonctionelle du circuit afin de réaliser une structure de test propre à un circuit. Cette structure est déveloper afin qu'elle puisse aisément être implémenter pour n'importe quel circuit.

Le plus important est qu'une preuve d'éfficacité est donnée. Celle-ci démontre qu'en général, pour une aire de silicium supplémentaire donnée, l'approche ODM résulte en une diminution de la perte d'information qu'est de plusieurs ordres de grandeur inférieure aux autres approches précédemment proposées.

En outre, la nature constructive de la preuve permet de facilement établir le rapport entre la réduction de perte d'information désirée, et l'aire supplémentaire réquise pour éffectuer cette réduction.

$\bigcirc$ .

# Acknowledgements

I wish to express my sincere gratitude to Professor Vinod K. Agarwal, who as supervisor provided invaluable and instructive guidance, as well as motivation and enthusiasm throughout the course of this research.

- I would also like to extend my thanks to Mr. André Ivanov for his grateful help in writing the french abstract, and making useful comments on the presentation of this material, and Mrs. Maida Kazanjian for her kind participation in preparing the graphics.

• Very special thanks go out to my wife and parents, without whose support and rencouragement would have made the task considerably much more difficult.

Finally, I am grateful also to the National Sciences and Engineering Research Council of Canada and McGill University for providing financial support during the period of this research.

## Statement of Originality and Contribution to the Knowledge

The author of this thesis claims originality for the following contributions:

- The development of a *BIST* scheme, based on the output data modification concept, to optimize the error masking problem, which is one of the major concerns of *BIST*. This scheme provides the best implementation in the quality of *BIST* compared to all the earlier attempts. An analytical proof also developed in this thesis shows that for average cases, it provides tremendous reduction in error masking.

- The development of several designs for sequence generation. These designs are characterized by their capability to generate large numbers of distinct sequences (of length l) using a small amount of hardware (O(log(l))) gates). These designs can also be adopted in various applications other than the output data modification scheme.

- The development of a heuristic algorithm which has the goal of defermining agood approximation to a desired sequence that can be obtained for a given amount of hardware.

- The development of a trade-off concept in *BIST* designs to achieve optimal solutions between the two following constraints: the desired amount of test quality, and a tolerated amount of extra hardware. More specifically, this concept is elaborated for the case where test quality is measured by error masking probability and where the amount of extra hardware is measured in number of cubes.

iv

| ۔<br>م اس        | , '                                   | Table of Content                            | s :                   | к.:                      | ,                 |

|------------------|---------------------------------------|---------------------------------------------|-----------------------|--------------------------|-------------------|

| Conter           |                                       | 2                                           |                       | 2                        | Pages: '          |

| · Abstra         | ct                                    | م <b>ج</b> ور<br>معرج مع مع مع              | • • • • •             | • • • • •                | 1.                |

|                  | e                                     |                                             |                       |                          | <b>N</b> (1)      |

| Acknow           | wledgements 🖓 . 👝 .                   | • • • • • • • • • • • •                     |                       |                          | <u>. j</u> ii     |

| •                | ent of Originality and G              | 1                                           |                       |                          | •                 |

| <b>Table</b> o   | of Figures                            | •••••••••••••••••••••••••••••••••••••••     |                       | · · · `· ·               | <sup>-</sup> viii |

| Chapte           | er 1: Introduction                    | • •                                         |                       |                          | <b>l</b>          |

|                  | 1.1 Background<br>1.1.1 Cost of Testi | ng                                          |                       |                          |                   |

|                  | 1.1.2 Generating a                    | Test Set                                    |                       | 4•••••••                 | 2                 |

| ,<br>- ,         | · •                                   | Test Quality                                |                       |                          |                   |

| I                | ` <b>_</b>                            | out Patterns and Ana                        | _                     | -                        | 1                 |

| I                | 1.2 <i>VLSI</i> Testing Strateg       | *                                           |                       |                          |                   |

|                  |                                       | Testing Strategy .<br>tations of Determinis |                       |                          |                   |

|                  | •                                     | ST Strategy                                 |                       |                          |                   |

|                  |                                       | eral BIST Model and                         |                       | -                        |                   |

| >                |                                       | tations of Universal I                      |                       |                          |                   |

|                  | ,                                     | fic BIST Strategy .                         |                       |                          |                   |

| 1                | 1.3 Error Information Lo              | ss in $BIST$                                | ••••••                | • • - • • •              | <u>·····15</u> ,  |

| 1                | 1.4 Dissertation Outline              | ۰۰۰۰۰ ۰۰۰<br>در                             |                       | ••••••                   | 17                |

| Chapte           | r 2: BIST for Random L                | ogic                                        |                       | ,<br>, , , , , ,         | 19                |

| 2                | 2.1 Preliminaries                     |                                             |                       | · · <sup>j</sup> . · · · | •19               |

|                  | 2.1.1 Linear Feedb                    | ack Shift Registers .                       |                       |                          | 21                |

|                  | 2.1.2 Hardware Co                     | st of BIST                                  |                       |                          | 26                |

| 2                | 2.2 Input Pattern Genera              | tion Process                                |                       |                          | 27                |

| ۰, ۳<br>۰, ۰, ۰, |                                       | est-Based Techniques                        | , <b>"</b>            | ۰                        | 28                |

| 1<br>1           | 2.2.2 Pseudo-Rand                     | om Test-Based Techr                         | nique . <sup></sup> . |                          | . 33              |

')

(

?

•

•

ł

Ċ

| 2.2.2.1 Establishing Pseudo-Random Test Length .<br>2.2.2.2 Random Pattern Resistant Faults                                                                                                                                                                                                                                                                                     |                                       |             | 34<br>36                             |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------|--------------------------------------|------------|

| 2.2 Output Data Compression Process                                                                                                                                                                                                                                                                                                                                             | <br>                                  | •<br>• •    | 44                                   | - ,        |

| Chapter 3: The Error Masking Problem and Output Data Modification                                                                                                                                                                                                                                                                                                               |                                       | . • .       | 51                                   | \$         |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                |                                       | •           | 51                                   |            |

| '3.2 The Error Masking Problem                                                                                                                                                                                                                                                                                                                                                  |                                       |             | 52                                   |            |

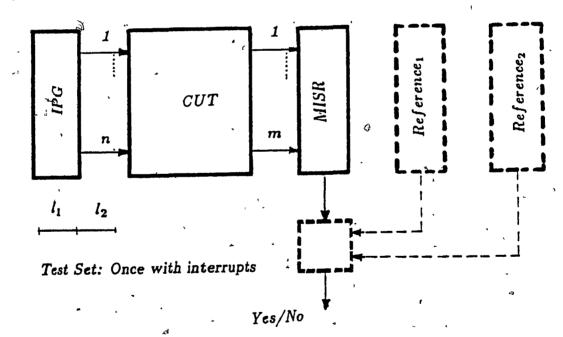

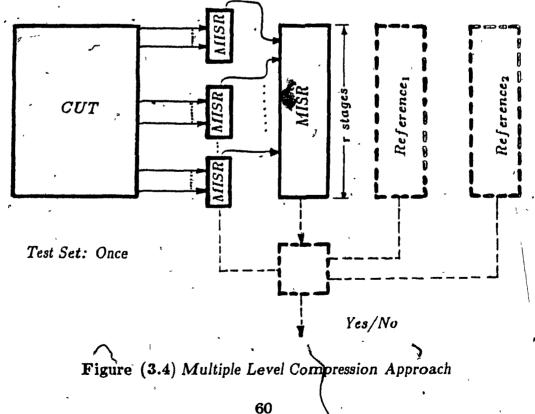

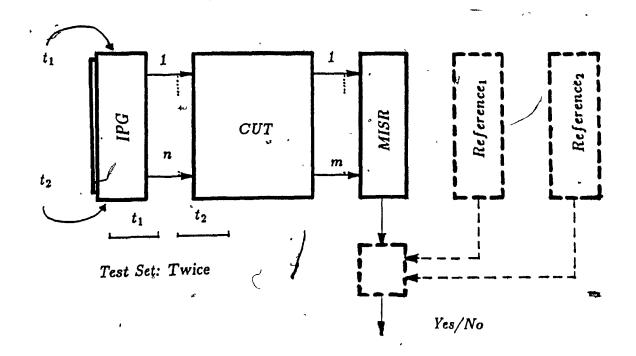

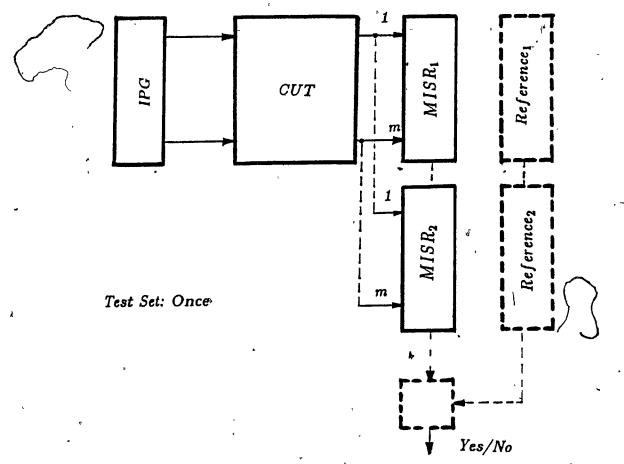

| 3.3 Improving Error Coverage                                                                                                                                                                                                                                                                                                                                                    | · · · · · · · · · · · · · · · · · · · | •<br>•<br>• | 57<br>57<br>58。<br>60<br>61'<br>62   |            |

| 3.3.6 Variable Shift Compression Approach                                                                                                                                                                                                                                                                                                                                       |                                       |             | 64                                   |            |

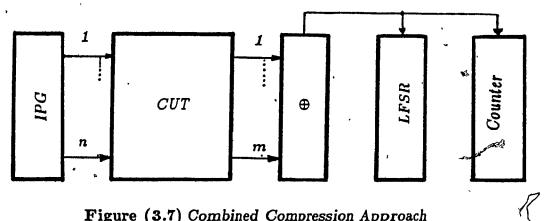

| 3.3.7 Combined Compression Approach                                                                                                                                                                                                                                                                                                                                             | •                                     |             | 64                                   | - 1        |

| 3.4 The ODM Concept                                                                                                                                                                                                                                                                                                                                                             | • • •                                 | •           | 67                                   | /          |

| 3.5 The Proposed ODM Model                                                                                                                                                                                                                                                                                                                                                      |                                       |             | 71                                   |            |

| Chapter 4: Modifier Sequence Generation Methods                                                                                                                                                                                                                                                                                                                                 | •<br>• • •                            | •           | 74                                   |            |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                | • • •                                 | ••          | 74                                   |            |

| 4.2 Methods to Generate a Sequence by Segments         4.2.1 EIS Methods for Modifier Sequence Generation         4.2.1.1 EIS with Single Input and a Single Seed         4.2.1.2 EIS with Single Input and Multi-Seed Possibilities         4.2.1.3 EIS with Double Inputs         4.2.1.4 Further EIS Possibilities         4.2.2 ESS Method for Modifier Sequence Generation | •<br>• • •<br>• ty-, •<br>• • •       | •<br>•<br>• | 75<br>76<br>82<br>84<br>87 . 7<br>89 |            |

| 4.3 A Method to Generate Modifier Sequences by Totality                                                                                                                                                                                                                                                                                                                         | • • • • • •                           | •           | 91                                   |            |

| <b>Chapter 5:</b> Reduction in Deception Volume for Average Sequences                                                                                                                                                                                                                                                                                                           |                                       | •           | 95                                   | <b>5</b> 2 |

| 5.1 Preliminary Calculations                                                                                                                                                                                                                                                                                                                                                    |                                       |             | 95<br>98<br>99                       |            |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                       | Ľ           | •                                    |            |

· `.(

٩,

9

7 à.

vi

| • •          | 5.4 Average Number of k-cubes with Exact Number of Isolated Vertices .              | 102        |

|--------------|-------------------------------------------------------------------------------------|------------|

|              | 5.5 Weight of a k-cube with v Isolated Vertices $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 103        |

|              | 5.6 The Available Cubes and the Reduction in Deception Volume                       | 104        |

| -            |                                                                                     | •          |

| - ~ Chapt    | ter 6: Realization of the ODM Scheme                                                |            |

| ,            | 6.1 The General BIST Design of the ODM scheme                                       |            |

|              | 6.1.1 The Standard Self-Test Facilities                                             |            |

| <b>`</b> ,   |                                                                                     | 109        |

| · .          |                                                                                     | 11)<br>11) |

| ۔<br>م,<br>ع | 6.1.3 The Improved Compressor                                                       | ٢٦         |

|              |                                                                                     | •          |

| x            | 6.2 Circuit-Specific Implementation                                                 |            |

| -            | 6.2.1 A Procedure to Implement the ODM Scheme                                       |            |

| ~            | · · · · · · · · · · · · · · · · · · ·                                               |            |

| •            | 6.3 Conclusive Remarks                                                              | 123        |

| - Chapt      | ter 7: Results and Conclusions                                                      | 13         |

| - Olapi      |                                                                                     | ۰.         |

| •            | 7.1 Introduction                                                                    |            |

| ٥            | 7.2 Simulation Results                                                              |            |

|              | 7.3 Conclusive Remarks on the ODM Scheme                                            | 13         |

|              | 7.4 BIST Schemes Adopting the ODM Approach                                          | 13         |

|              | 7.5 Further Possibilities under $ODM$                                               | 13         |

| ,            |                                                                                     | ,          |

| Refere       | •<br>ences •                                                                        | 14         |

| ,            |                                                                                     | ! •        |

vii 🚽

1 , **T**

# Table of Figures

:0

ŗ.

).

| Figures:     | ۰<br>۰                                                     | P      | ageş:            |      |

|--------------|------------------------------------------------------------|--------|------------------|------|

| Figure 1.1   | A General BIST Model                                       | •••    | - 1°Q            |      |

| Figure 2.1 🔹 | The General Form of an $LFSR$                              | • •    | 22               |      |

| Figure 2.2   | An Illustration of a Polynomial Division                   | •••    | 23               |      |

| Figure 2.3   | An Autonomous LFSR with Maximum Cycle Length               | ••     | 25               |      |

| Figure 2.4   | Pseudo-Exhaustive Input Pattern Generation                 | •••    | - <del>3</del> 2 |      |

| Figure 2.5   | An $LFSR$ as an $ODC$                                      | •••    | 41               | 1    |

| Figure 2.6   | Multi-Input Shift Register (MISR) as ODC . •               | • •    | 42               |      |

| Figure 2.7   | Parity Checker for an Output Data Stream <sup>•</sup>      | . • .* | 45 ≯             | هبسه |

| Figure 2.8   | Count-Based Compression Techniques for Single Output CUTs  | •      | 47               | ,    |

| Figure 2.9   | One's Counting for Multi-Output CUT's                      |        | 49               |      |

| Figure 3.1   | A Representation of an Output Data Compression             |        | 54               |      |

| Figure 3.2   | Extended Compressor Approach                               | ••     | ∘ <b>,5</b> 8    |      |

| Figure 3.3   | Segmented Test Set Approach                                | •      | <b>5</b> 9 ·     | ,    |

| Figure 3.4   | Multiple Level Compression Approach                        | •      | <b>6</b> 0       |      |

| Figure 3.5   | Multiple Test Sets Approach                                | •      | 62               |      |

| Figure 3.6   | Multiple Compressions Approach                             | •      | 63               |      |

| Figure 3.7   | Combined Compression Approach                              | •      | 65               |      |

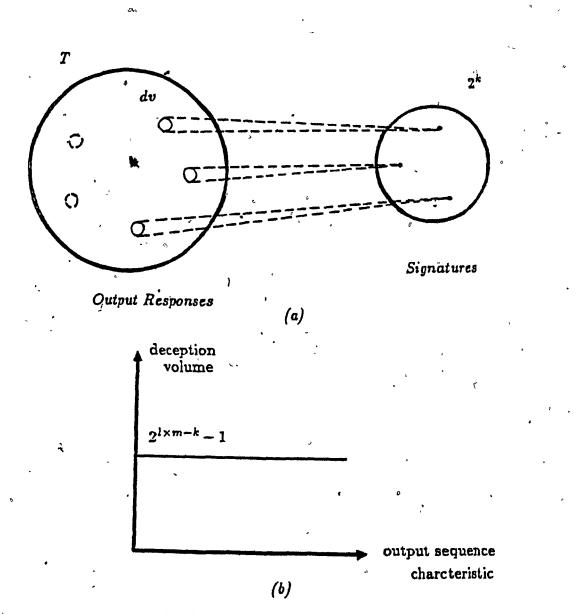

| , Figure 3.8 | Uniform Deception Volume $(MISR)$ $$                       | •      | 68               |      |

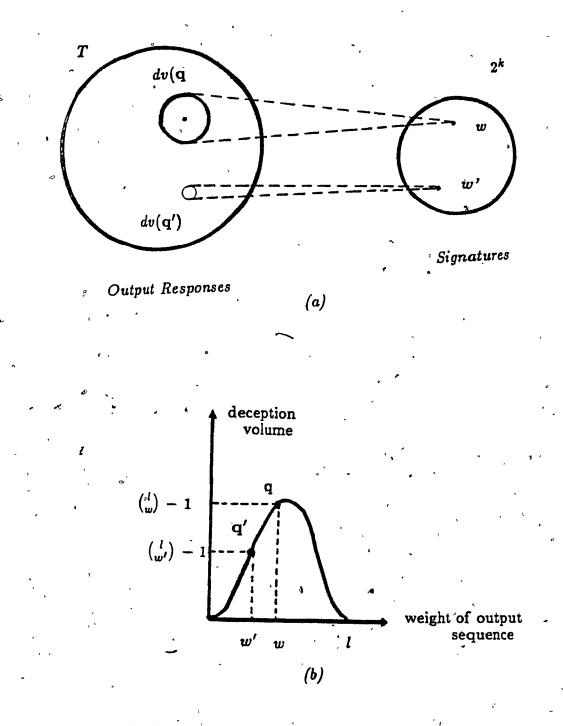

| Figure 3.9   | Non-Uniform Deception Volume (One's Counting) *            | •      | 69               |      |

| Figure 3.10  | The Modification Operation                                 | •      | 70               | ъ    |

| Figure 3.11  | A BIST Model for the ODM Scheme •                          | •      | 72               |      |

| Figure 4.1   | Single Input Method'                                       | •      | 83               |      |

| ⊴Figure 4.2  | Double Input Method                                        | •      | 85               |      |

| Figure 4.3   | Two Level Modification Technique                           | •      | 89               |      |

| Figure 4.4   | Equal Size Segments Method                                 | •      | <b>9</b> 0       | ć    |

| Figure 5.1   | Isolated Vertices in an Essential Çube                     | •      | <b>9</b> 9       |      |

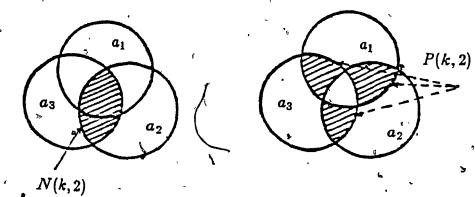

| Figure 5.2   | The States of Three Isolated Vertices in an Essential Cube | •      | 102              |      |

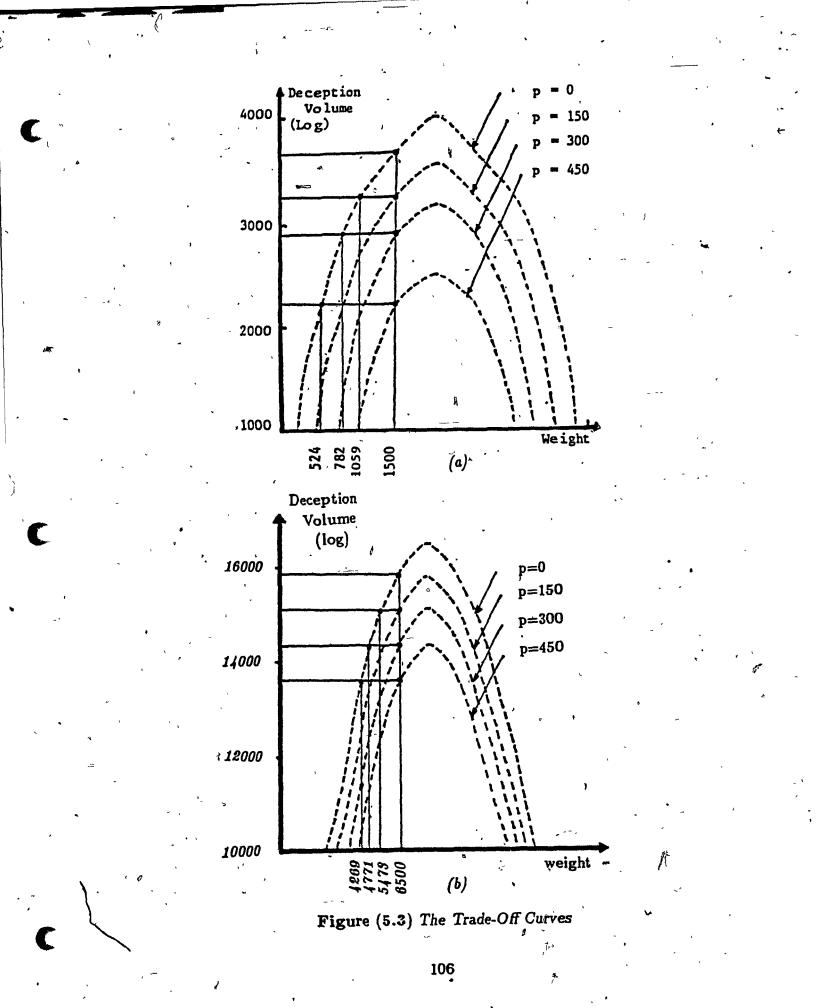

| Figure 5.3   | The Trade-Off Curves                                       | •      | <b>10</b> 6      |      |

viii

යා

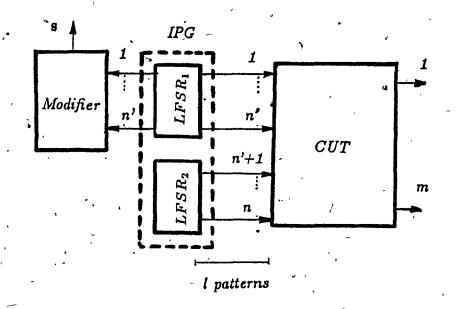

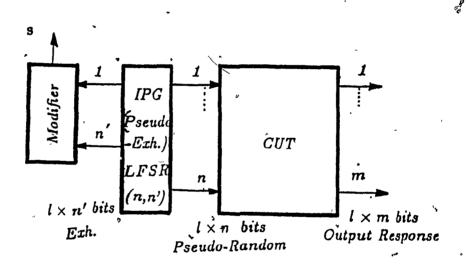

Figure 6.1An JPG Design with Two LFSRs110Figure 6.2An IPG Based on Pseudo-Exhaustive Technique111Figure 6.3The Improved Compressor117Figure 6.4The Hardware Realization of the Modifier Block122

ix

# Chapter 1

Introduction

1.1 Background:

The integrated circuit (IC) technology is continually moving towards higher scale and density factors, hence making possible the fabrication of circuits with a very large number of devices on a single chip. However, increases in circuit complexity, due to these technological improvements, have made testing such circuits a major problem [Williams 83].

Testing is performed in order to determine whether a circuit is operating correctly, or not, i.e. to find out if it is producing identical results to what it is originally designed for.

A testing procedure, in general, consists of three steps: generating a set of input patterns (i.e. test set); applying these to the circuit under consideration; and analyzing the resulting output data. This procedure is usually performed at various levels during the production of a system [Mann 80] [Myers 83]. For instance, the dies are tested during fabrication, the packaged chips before insertion into the boards, the boards after assembly, and finally, the entire system is tested when complete. The complexity of the testing procedure at each level is determined by factors such as the time available for testing, the degree of access to internal circuitry, and the percentage of faults which are required to be detected.

## **1.1.1** Cost of Testing:

As digital systems become more complex, their cost of testing becomes a major part of the cost of a system.<sup>9</sup> Thus, there is much activity in trying to reduce the cost of testing by developing different testing strategies. It is, however, important to mention that the cost of finding a failing component depends, in addition to the testing strategy upon the level of testing (i.e. chip level, board level, ...) as well. In general, since detecting and isolating a fault at the board or higher packaging levels costs more than at the chip level [Williams 83]. To minimize the cost of testing, it is imperative that faults be detected as early as possible. Most of our discussions, throughout this dissertation will be concentrated on chip level testing, although the scheme proposed is applicable to other levels besides chip level testing.

#### **1.1.2** Generating a test set:

The testing procedure, as indicated previously, starts by generating a test set. Such a set is utilized in order to identify the circuits that have become faulty due to physical, failures. The large number of possible failures dictates that a practical strategy to generate a test set should avoid working directly with these physical failures. Since, at the chip level, one is not usually concerned with determining the exact physical failure, what is desired is merely to find out the existence or absence of any failure. Thus, in general, the effects of physical failures are described by a fault model. If a fault model accurately describes all the physical failures of interest, then, one only needs to generate a test set which detects all the faults in the fault model. The most widely-used fault model is that of a single line being permanently stuck-at a logic value of 0 (s-a-0) or 1 (s-a-1).

The presence of a given fault is said to be detected when an appropriate input pattern, applied to the circuit-under-test (CUT), causes an incorrect logic result (that is, error) at one or more output lines of the CUT. Different physical failures/faults may cause the same error under a given pattern. Given a fault model, a test set is considered complete if it detects the entire set of faults in a CUT. Hence; it is essential that for every fault, there must exist at least one pattern by which it will be detected. It will be seen later, that despite its necessity a complete test set is often not easy to obtain for large circuits.

Various algorithms [Goel 81] [Fujiwara 83] have been developed to generate test sets for chip level testing. Conventionally, a test set at this level consists of either deterministic, exhaustive, or randomly generated patterns, depending on the testing strategy adopted. A discussion concerning these strategies will appear later in section 1.2.

## 1.1.3 Measures of Test Quality:

When considering a set of input patterns to test a complex circuit, one should first consider how good it is for detecting the set of faults in the circuit. Usually, the quality

of a test set is measured by the ratio of the faults detected to the total number of faults in the model. This ratio is termed as fault coverage.

Fault coverage is usually determined by a process called fault simulation. This process consists of simulating the application of every pattern in the test set to the set of faulty circuits (corresponding to the circuit to which a fault is injected) and comparing the responses to that of a fault-free circuit. However, such a simulation of the entire set of faults, particularly in large circuits with many tens of thousands of gates may take a prohibitive amount of computing time. As an alternative to simulation, several probabilistic measures have been proposed to estimate the fault coverage [Savir 83a] [Seth 85].

# 1.1.4 Applying Input Patterns and Analyzing Output Data:

\* Once a set of input patterns is generated, it is then applied to the circuit under consideration. Depending on the testing strategy adopted, the source of input patterns is in some cases inside the chip itself, while in others in an external device. This will be discussed more fully in a later section. Similarly, the output data analysis is either performed internally to the chip or via an external device. It needs to be mentioned, that external devices, which serve the functions of generating input patterns and analyzing output responses, are often very expensive and very complex systems.

Whether performed internally or externally, the analysis of output data always consists of consparing the entire output response. or some function of it, with reference values representing the correct responses. Based on this comparison, if the two values differ, the chip is declared faulty or else fault-free. The following section describes in brief some of the testing strategies that are best suited for complex VLSI chips.

## **1.2** *VLSI* Testing Strategies:

Different strategies to VLSI testing have been developed over the years [Williams 83] [Williams 84] [Wang 85]. The purpose of this section is to provide a short description of these strategies, outline their uses, and describe some of their limitations. The first strategy considered is the deterministic testing, which is probably still most common, although it has numerous limitations. One most significant limitation being that, it is heavily dependent on the structural information of the CUT. The second strategy, to be addressed in this section, is universal testing (i.e. CUT's structure-independent), which adopts the concept of building test facilities into a chip. Since the inclusion of test facilities is conventionally known as "built-in self-test" (BIST) [McCluskey 85a], the above mentioned strategy will be termed as the universal BIST. The third strategy, considered in this section, includes a new trend of BIST schemes [Schnurmann 75] [Barzilai 81] [Agarwal 83] [Zorian 84]. These schemes distinguish themselves from the previous schemes by having their self-test facilities adjusted (i.e. programmed) specifically for given circuits. We will classify these under a strategy termed as circuit-specific BIST strategy.

## **1.2.1 Deterministic Testing Strategy:**

As mentioned in the previous section. the first step in the testing procedure consists of generating input patterns for a given CUT. Under the deterministic testing strategy, this step is based on the topological structure of the circuit, and its set of faults. Fo derive an input pattern for a particular fault, a specific structure-dependent computation is needed. The input patterns resulting form these compose a deterministic test set. Such computations are usually performed by one of numerous algorithms known as automatic test pattern generation algorithms [Roth 66], [Goel 81], [Fujiwara 83]. To evaluate the quality of the test set, a fault simulation process is also required [Chang 70] [Armstrong 72] [Bose 82] [Hayes 82] [Levendel 81].

Under the deterministic testing, external test equipments are used to apply generated test sets, as well as to perform the output data analysis [Williams 83].

# **1.2.1.1** Limitations of Deterministic Testing:

The continuous growth in the complexity of chips creates major problems in all three steps of the deterministic testing procedure. Due to these problems, the input pattern generation and application, as well as the output data analysis, have become extremely expensive steps. In order to better understand the magnitude of these problems, the difficulties of each of these three steps is briefly discussed in the following.

The test pattern generation problem under this strategy, is well recognized to be an NP-complete problem [Fujiwara 82] [Ibarra 75] even for combinational circuits. This implies an exponential growth in test generation time with the growth in hardware complexity. Various algorithms [Roth 66] [Goel 81] [Fujiwara 83] have been developed to reach more tractable growth rates for average circuits. An illustration in [Goel 80] shows that the test generation with such an algorithm, in general, consumes CPU time at a rate approximating  $G^2$  (where G is the number of gates in the circuit). While this growth rate is much more tractable than an exponential one, it still is not very attractive for large area chips. [Goel 80] projected upwards of 1000 hours of CPU time

(

to generate tests for a 100,000 gate structure, even assuming an algorithm which could determine tests without backtracking. Obviously, the costs of test pattern generation for complex VLSI chips could quite easily become intolerable.

Another major problem with complex VLSI chips is in performing a complete fault simulation (needed to determine the fault coverage) for a deterministic test set. It is observed that the computer run time is proportional to  $G^2$  to do fault simulation [Williams 79], and is proportional to  $G^3$  for both test generation and fault simulation [Goel 80]. Thus, small increases in gate count will yield to quick increases in run times. Several techniques have been reported to reduce the complexity of fault simulation [Parker 79] [Ulrich 74]. However, it still is a very time consuming, and hence expensive task [Williams 79], particularly for complex chips.

Furthermore, the two other steps in the testing procedure (applying input patterns and analyzing output data), as indicated above, face severe problems with large VLSI chips as well. These problems are in terms of time and volume. More specifically, the amount of time needed to apply a set of deterministic patterns, and to perform the output data analysis, has grown to the extent that it often results in an unacceptable test duration /McCluskey 85a]. In regards to the volume, or number of input patterns and output reference values, it has become too large to be handled efficiently by the test equipment hardware [McCluskey 85a].

Finally, another characteristic of the deterministic testing strategy mentionedearlier, is the dependence of test pattern generation and fault simulation on the structural information of a CUT. This is a limitation simply because a detailed structural (i.e. topological) information of a complex VLSI chip is often hard to obtain and to analyze.

X

## **1.2.2** Universal BIST Strategy:

The limitations of the deterministic testing strategy have led the attention<sup>o</sup> of IC manufacturing and design communities to new methods for testing complex VLSI chips. One such method, which increases the controllability and observability of the circuits, and avoids the inadequacies of deterministic test generation and fault simulation for sequential circuits, is based on the idea of designing circuits for testability. This is realized by adopting some simple built-in testing techniques, known as design for testability techniques [Williams 83] [Mangir 83] [Muehldorf 81]. Conventionally, such techniques are in some cases in the form of general guidelines to be followed. In others, they are design rules to be implemented. Associated with these techniques is their cost of implementation and return of investment [Akers 77] [Eichelberger 78] [Hayes 74] [Funatsu 75].

It is important to mention that most of the design for testability techniques came as a response to the difficulty of deterministic test generation for sequential circuits. Hence, in order to avoid this difficulty, a number of companies including IBM [Eichelberger 77], Sperry Univac [Stewart 77], Nippon Electric [Funatsu 75] and Fujitsu [Ando 80] have developed special techniques commonly known as scan techniques. These techniques suggest estructured design approach in which all sequential elements are organized so that their contents can easily be controlled and observed. Using a scan technique reduces the test generation problem for a sequential circuit to the test generation problem for a combinational circuit alone [Williams 83] [McCluskey 84b]. Usually sequential elements (Juch as latches and flip-flops) tested under these techniques, are first switched from their normal mode of operation to a test mode. During the test mode, these elements become threaded together into one or more shift registers. This makes it possible to first scap in arbitrary test patterns through them, and then scan these patterns out to compare

the output data with the correct response. These techniques are becoming\_commonly accepted methods and therefore increasingly implemented by the manufacturers[].

As a result of adopting a scan-based technique, the sequential testing problem is reduced to one for combinational circuitry only. Hence, the main task remains to develop a testing strategy which solves the problems of deterministic testing for combinational circuits. In other words, the major intent is to provide a testing strategy that eliminates the problems of test generation and fault simulation for combinational circuits, avoids the expensive test equipments, and is also independent of the CUT's structural details.

A new testing strategy promises to realize all the above mentioned intentions by providing a structure-independent and on-chip testing strategy. It is termed as universal BIST strategy. This testing strategy moves some or all of the test equipment functions onto the chip itself, or onto the board on which the chips are mounted. Therefore, it is called a built-in self-test strategy. Furthermore, it is called universal because the structure of its self-test facilities holds a general design, independent of the CUT's structure (i.e. the facilities are not programmed specifically for a given circuit).

Under the universal BIST, various built-in self-test schemes for random combinational logic [McCluskey 85a], PLAs [Treuer 85] and memories [Sun 84] have been developed. Such schemes are useful tools in the testing of complex VLSI chips. More details about these BIST schemes and in particular about BIST techniques used for random combinational logic are described in the first two chapters of this dissertation.

# 1.2.2.1 General BIST Model and Self-Test Operation:

Due to the increasing use of scan-based techniques, the main emphasis of current BIST schemes is to provide close to a 100% testing of the combinational circuitry.

Q

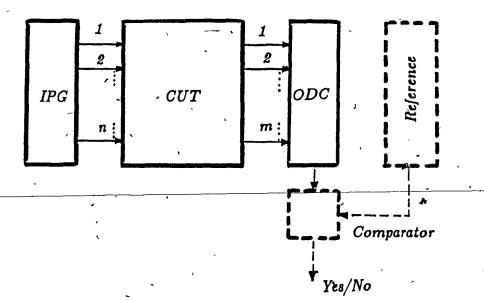

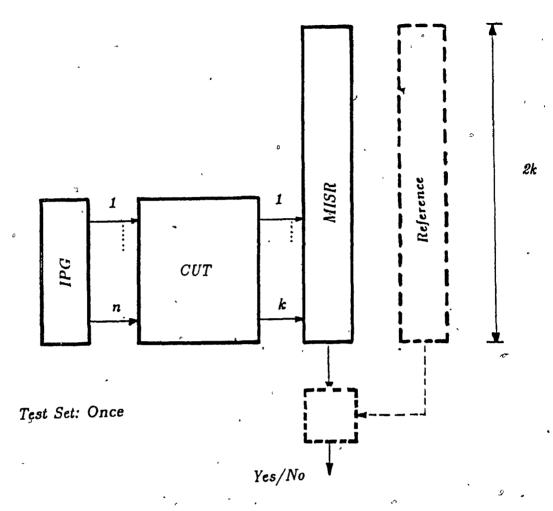

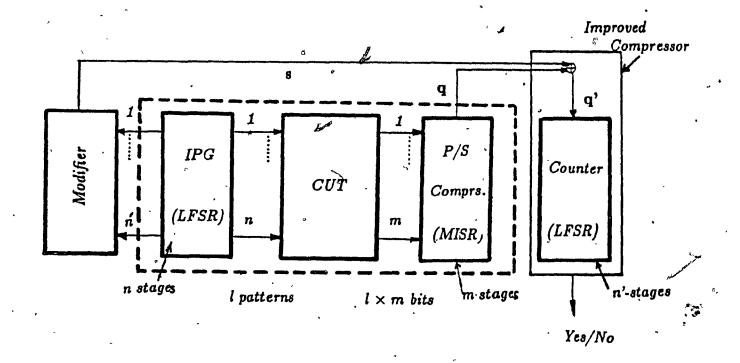

The implementation of a BIST scheme implies the addition of self-test facilities, that enable the resulting structure (i.e. the BISTed design) to apply the input patterns and analyze the output data. Figure(1.1) shows a general BIST model which consists of the combinational CUT itself and the extra blocks for self-testing.

Figure (1.1) A General BIST Model

In a typical BIST model, the extra blocks remain transparent to the user during the normal mode of operation as long as the original circuit functions according to its specifications. During the self-test mode, one of the self-test blocks called IPG (input pattern generator) generates the input patterns internally and applies them to the circuit in question. Conventionally, the test sets used in BIST schemes are either exhaustive, i.e. consisting of all possible input patterns, or pseudo-random, i.e. consisting of pseudorandomly generated patterns. The test patterns for both cases (i.e. exhaustive, or pseudo-random) can be generated internally, as will be discussed in the section 2.2, by simple IPGs during the self-test mode. Hence, there is no need for the difficult test pattern generation processes that are needed under the deterministic testing strategy. Such an internal pattern generation possibility solves also the difficult requirement of

storing the test patterns in advance, and thus avoids a large part of the memory required to store these patterns.

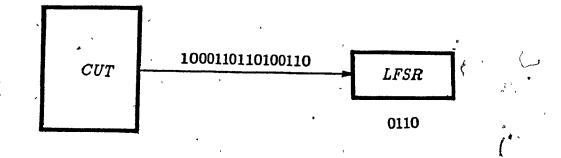

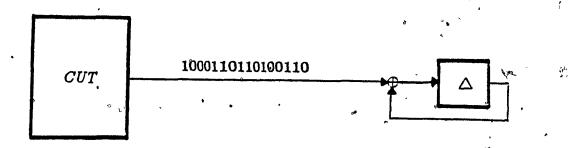

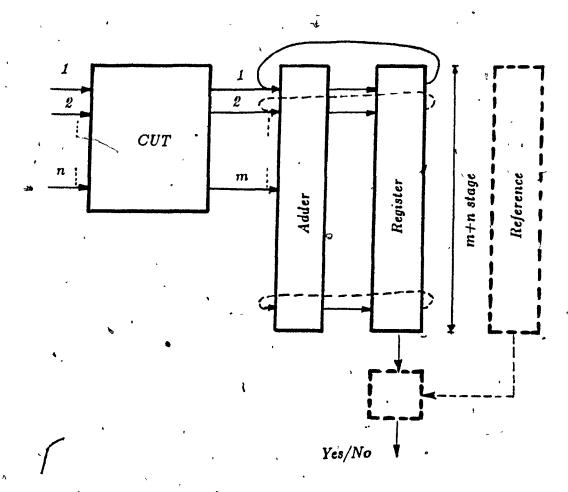

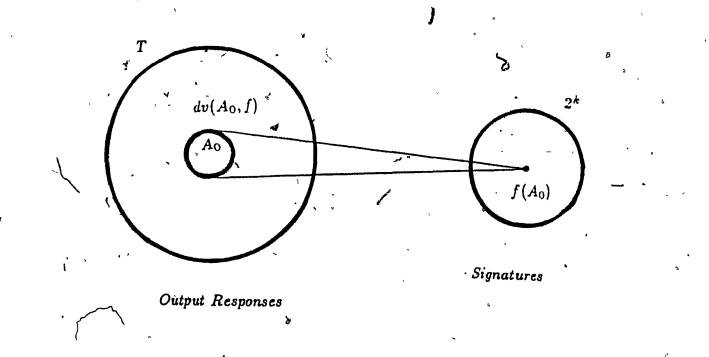

Furthermore, most of the BIST schemes reduce the amount of output data prior to the final step of output data verification. This process of lessening the amount output data is well known as output data compression, and performed by a block termed output data compressor (ODC). This block collects the actual output data of a CUT and compresses it into a signature of the output response. The intent behind this lessening is to reduce the amount of memory required to store the volumnious reference values needed to verify the actual output data of a CUT.

Finally, in order to complete the output data analysis, the last two blocks perform the verification step. Wherein, the observed signature in the ODC is compared by the Comparator with the fault-free value stored in the reference block. Hence, if the two signatures differ, it is safe to predict that the CUT is faulty. And if the two are identical, then the CUT is conventionally declared fault-free. However, identical signatures do not guarantee a fault-free circuit, since a faulty circuit can produce some output combination which gets compressed into the same signature as the fault-free one.

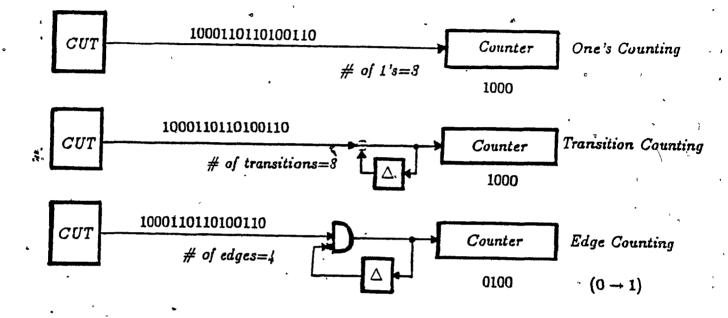

Under various BIST schemes, the self-test blocks in Figure(1.1) are realized by different devices (i.e. circuit structures). It is important to note that these devices are intended to be simple and nonexpensive, so that they require tolerable amounts of hardware. The most commonly utilized IPG consists of an extremely simple device, called linear feedback shift register (LFSR) which has the capability of generating both exhaustive and pseudo-random patterns [Peterson 75]. The output data compression itself is often performed by simple devices as well, e.g. a counter for One's Counting [Savir 80] and Transition Counting [Hayes 76b] techniques, or a multi-input linear feedback shift register (MISR) for another compression technique known as polynomial division

[Benowitz 75].

The characteristics of input pattern generation and output data compression techniques, as well as their specific devices, are presented in more detail in chapter 2. It can be noted that the use of pseudo-random pattern generation followed by compression of output data by polynomial division is being increasingly adopted by many reported BIST schemes [Konemann 79] [Bhavsar 81] [Bardell 82] [Komonytsky 82]. Hence, this use has become an almost standard form of testing in universal BIST. Furthermore, this standard BIST has recently been adopted by several manufacturers in their products [Danniels 81].

# **1.2.2.2** Limitations of Universal *BIST*:

The current universal BIST schemes have different limitations. One of these is that if schemes with exhaustive testing are used for complex VLSI chips, then a circuit with a large number of inputs may require an exceedingly large test set, with its consequent unacceptable test time [Bozorgui-Nesbat 80].

On the other hand, if pseudo-random testing is used, certain faults, known as random pattern resistant faults, may exhibit extreme reluctance to detection by the pseudorandom patterns [Eichelberger 83]. Therefore, such faults may result in unsatisfiable fault coverages.

Yet another drawback with universal BIST is faced if a faulty circuit is declared. as fault-free As mentioned earlier, this may happen when an erroneous output data is compressed by some ODC into a signature identical to the fault-free one. It is obvious that this drawback also affects the quality of test, since it reduces the expected fault coverage of a test set [Smith 80] [Bhavsar 84]. In particular, this phenomenon which

*л*2

occurs under current BIST schemes for random logic using output data compression will be the focus of interest throughout this dissertation.

## **1.2.3** ' Circuit-Specific *BIST* Strategy:

Although an ideal BIST structure should be a completely general one, in the sense that it should be applicable to any CUT, in order to avoid some of the limitations in universal BIST, a new strategy which considers circuit-specific self-test structures is under development [Agarwal 81] [Agarwal 83] [Zorian 84] [Tang 84] [Chin 84]. This new strategy, termed here as circuit-specific BIST strategy, is mainly aimed at optimizing the test quality, while maintaining most of the advantages of universal BIST.

With the above mentioned strategy, a typical BIST scheme utilizes certain information about the CUT in question to program the self-test facilities. This information is generally the functionality (i.e. the functional information) of a CUT. Conventionally, despite that such self-test facilities have a general design, they need to be programmed specifically for given CUTs. Notice that the three limitations of universal BIST mentioned in section 1.2.2.2, can be avoided or reduced by adopting such circuit-specific BIST schemes The overcoming of these limitations by circuit-specific BIST schemes will only be briefly discussed next. More thorough discussions appear in the subsequent chapter.

The first case considers the test length problem for complex VLSI chips under exhaustive testing. Various BIST schemes, known as pseudo-exhaustive testing schemes, appeared recently in the literature [Wang 84] [Tang 84]. They suggest different techniques to reduce this test length problem by adopting circuit-specific IPGs. Such a technique typically exploits the functional information of a CUT to determine the set

, 13 of inputs which drive each output, and then accordingly set a specific IPG that will provide a reduced test length. Several pseudo-exhaustive techniques are described in section 2.2.1.

The second case to illustrate the use of circuit-specific BIST deals with the attempts aimed at detecting random pattern resistant faults, in order to increase the fault coverage of schemes based on pseudo-random test. Some of the attempts, to solve the problem of random pattern resistant faults, suggest ways to modify a regular pseudo-random IPG for a given CUT (see section 2.2.2.2). One modification is to generate unequiprobable (i.e. biased) random patterns. These have been shown to provide higher possibility of detecting the resistant faults [Schnurmann 75] [Chin 84] [Wundelich 87].

Another question of major concern under most of the current BIST schemes for random combinational logic is the problem of declaring a faulty circuit as fault-free due to output data compression [McCluskey 85a] [Williams 84]. This problem can also be reduced by adopting circuit-specific BIST schemes [Agarwal 83] [Zorian 84] [Li 87]. This reduction is realized by exploiting the functionality of the CUT, and accordingly providing circuit-specific IPGs and ODCs. The main issue of the remainder of this dissertation is to introduce, implement and analyze a complete BIST scheme which has the ability of drastically reducing the problem of declaring a faulty circuit as fault-free by modifying the output data [Zorian 84] [Zorian 86c].

It is important to indicate, at this stage, that the circuit-specific BIST strategy in general might be considered as a promising strategy since it tends to maintain the advantages, and avoid the problems of the two previous testing strategies (deterministic and universal BIST). To be more specific, considering implementation costs, the

circuit-specific BIST strategy avoids the large expenses of input pattern generation, fault simulation and test equipments under the deterministic testing strategy, while it tends to maintain the ease of implementing BIST facilities (IPGs and ODCs). In other respects, it avoids the dependence on the structural details of a given CUT needed under the deterministic testing. However, it usually utilizes the functionality of the CUT in question. Finally, such a strategy can improve the test quality of Universal BIST by, minimizing the problems of error information loss and random pattern resistant faults.

## **1.2** Error Information Loss in *BIST*:

As discussed earlier, the compression of a CUT's output response leads, in general, to a loss of error information. Such a loss results in a reduction in the test quality of the overall BIST design, since the number of faults which remain undetected because of this loss, causes a reduction in the expected fault coverage [McCluskey 85a] [Bhaysar 84]. It has to be mentioned that faults in the BIST hardware itself may also lead to information loss. Actually, various BIST schemes including those using standard BIST might reach considerably low fault coverages due to error information loss. Such results are shown for example in [Saxena 85] [Zorian 86b]. Numerous BIST schemes intended to reduce the loss of error information have been reported in the literature [Hassan 83] [Hassan 84a] [Bhavsar 84] [Hiawiczka 86]. However, for the amount of hardware overhead that these schemes require, the reduction rate provided-is limited (analysis found in section 3.3), Consequently, there is no provision to obtain better reduction rates under these schemes [Bhavsar 84].

The objective of this dissertation is a new BIST scheme which not only provides the best implementation in the quality of BIST over all the earlier attempts, but also tends to solve the problem of error information loss by drastically reducing its rate

to insignificant levels. Hence, this scheme provides a very high insurance that if an output data is ever erroneous, then its corresponding signature will differ from the fault-free signature. Such an insurance is particularly suited for very high test quality requirements (1 failure in a 10<sup>5</sup> or 10<sup>6</sup> parts etc...). Moreover, the hardware overhead<sup>3</sup>, required to implement this scheme is not more than that used in the previous attempts.

Importantly, the amount of loss, in error information for a BISTed design depends upon two factors. The first factor is the function adopted for output data compression, whereas the second consists of the CUT's error-free output data itself. None of the previous attempts takes both factors into consideration (see section 3.3). In effect, they suggest improving the effectiveness of the standard form of BIST by optimizing only one of the factors: the output data compression function [Bhavsar 84] [Carter 82a]. The BIST scheme presented in this dissertation utilizes the dependence on both factors. The above mentioned superiority of our scheme is actually the result of properly optimizing both of these factors, and consequently achieving tremendous increases in the effectiveness of standard BIST. The optimizations of both factors, under our scheme, as will be shown in section 3.4, are not independent of each other. In effect, an appropriate function for output data compression will first be determined. Then, accordingly, the output response data will be optimized. This optimization (of the second factor) can be realized by modifying the output data of a fault-free CUT into a modified output data which results in a substantial reduction in error information loss [Agarwal 83]. Moreover, this modification must be done by an easily implementable method. The BIST scheme developed throughout this dissertation utilizes such a modification to optimize its output data [Zorian 86c] by adopting an easily implementable method [Zorian 84] [Zorian 86a]. Hence, this scheme is termed in the remainder of this dissertation as output data modification (ODM) scheme.

The ODM scheme, as will be shown, consists of an adjustable, i.e. programmable, BIST structure (i.e. IPG, ODC, etc...), in order to perform modification of a given output data. Hence, this structure is specific to the CUT in question. Thus, accordingly the ODM scheme is classified under the circuit-specific BIST strategy.

In other respects, the BIST structure itself will be shown to have the ability of being very conveniently implemented for any general circuit. Furthermore, it is analytically proved (in chapter 5) that for any average case, the ODM scheme provides tremendous improvement in test coverage. Moreover, the constructive nature of this proof provides a whole range of trade-offs between the improvement in the desired test quality and the overhead in silicon area needed to affect this improvement.

# 14. Dissertation Outline:

The remainder of this dissertation is organized as follows:

In chapter 2, a review of basic BIST techniques for random logic, used under universal and circuit-specific BIST strategies, is presented. These basic techniques are used for input pattern generation and output data compression processes. Most of these techniques will also be used for the ODM scheme.

In chapter 3, the error masking problem is discussed. An analysis of the existing BIST schemes aimed at reducing this problem is provided. Finally, the output data modification concept is introduced, and its BIST model demonstrated.

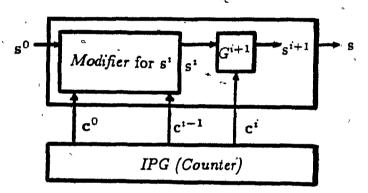

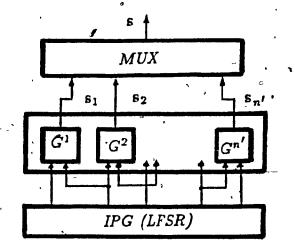

In chapter 4, various methods are developed to generate a specific element of the ODM scheme: the modifier sequence. This sequence, which is based on the functionality of a CUT, is shown to be easily generated by non-expensive circuitry.

In chapter 5, an effectiveness proof of the ODM scheme for average cases is developed. A useful trade-off between the improvement in desired test quality and the area overhead needed to affect this improvement is discussed as well.

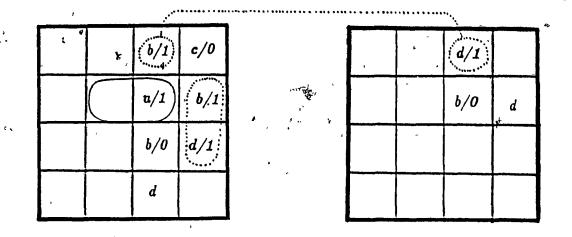

In chapter 6, the realization of the ODM concept as a BIST model is discussed. Then, given a CUT, the implementation of the scheme is demonstrated, and in particular, the circuit-specific programming of its Modifier block is detailed.

Finally, chapter 7 concludes the dissertation with some simulation results and concluding remarks. There it will be shown that the ODM scheme can indeed serve a very useful role in providing high fault coverage through BIST for a minimal increase in the area overhead.

• Chapter 2

## 1 E

**BIST** for Random Logic

## 2.1 Preliminaries:

$c^{N}$

The concept of BIST has in recent years become an invaluable tool in the testing of complex VLSI chips, especially with the outgrowth of scan-based techniques. This is evidenced by the several commercial chips with BIST implementations [Kuban 83] [Gelsinger 86]. Particularly, the current growing usage of application-specific integrated circuits (ASIC) has wrther increased the value of BIST, since the expensive procedure needed for the deterministic testing strategy cannot be justified for the limited production runs of ASICs. Several aspects concerning the importance of BIST and the benchits it provides were demonstrated in chapter 1, along with the differences between its universal and circuit-specific strategies. One of the most useful aspect of BIST is its ability to test deeply embedded logic, PLAs and memories. It has now been established that BIST for regular structures such as PLAs and memories can quite efficiently provide a guaranteed fault coverage [Treuer 85] [Saluja 87] which does not require any fault simulation. On the other hand, BIST schemes for non-regular structures, such as random combinational logic, have not yet evolved to a guaranteed fault coverage environment. For most such schemes, the only ensured coverage is in terms of error coverage, as will be discussed in the following chapter. Various attempts [Hassan 84a] [Bhavsar 84] [Carter 82a] to increase this error coverage in order to increase the certainty of BIST for random combinational circuits have been reported. The ODM scheme, presented throughout this dissertation, has the same objective. However, it provides a tremendous improvement in error coverage at a very low additional cost. In the remainder of this dissertation, only built-in self-test for random combinational logic is treated.

In order to more easily understand the ODM design and its implementational aspects in the following chapters, it is important to illustrate some basic BIST techniques in advance. A review of such techniques and some analysis of their limitations are presented in this chapter. More specifically, the BIST techniques addressed here cover exhaustive and pseudo-random input pattern generation, as well as various output data compression techniques like polynomial division, parity check and count-based techniques. Most of these BIST techniques are utilized by different existing BIST schemes as well as to implément the ODM scheme.

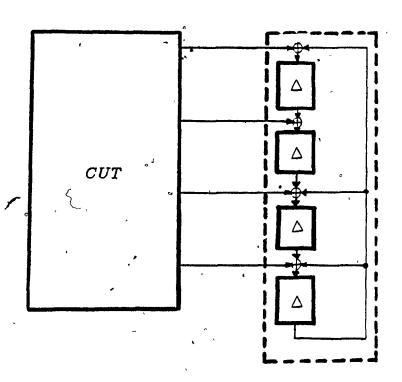

Before reviewing and analyzing the above mentioned BIST techniques, it is helpful to direct one's attention to how these techniques are used by the ODM scheme. A typical input pattern generator under the ODM scheme has to provide two sets of patterns simultaneously: one pseudo-random and the other exhaustive. Thus, it is necessary to

address both pattern generation techniques in this chapter. In regard to the output data compression process under ODM, it is performed by two succeeding steps. The first step uses a polynomial division-based compression technique (i.e. MISR); whereas the second step utilizes a count-based technique. Hence, most of the BIST techniques introduced in this chapter will be useful in the following chapters, where the realization of the ODM scheme is presented. Prior to the illustration of these techniques, a wellknown self-test device, called LFSR, is described.

## 2.1.1 Linear Feedback Shift Registers:

A BIST design, in general, consists of two principal units for self-test purposes (Figure(1.1)). These are an IPG which generates the input patterns and applies them to the CUT inputs, and an ODC which collects and then reduces the large amount of output data prior to its evaluation. These two units are often implemented by a device called a linear feedback shift register (LFSR). Conventionally, LFSRs are used to build pseudo-random generators [Golomb 82], polynomial division-based compressors [Benowitz 75], and store address generators [Hsiao 77] [Wang 82]. In order to well understand the capabilities and the limitations of an LFSR in a BIST structure, a brief description of its operation, structure and characteristics is provided in the following.

The mathematics, upon which an LFSR is based, is essentially the same as the basis for algebraic coding theory. A more detailed treatment of the material in this section kan be found in [Peterson 75]. Coding theory treats binary sequences as polynomials with binary coefficients, where each bit in a sequence is the coefficient of a unique power of x. For example, the 5-bit sequence 11001 is represented by the 4-th degree polynomial  $m(x) = x^4 + x^3 + 1$ . Here, the degree of a polynomial is the largest power of x in a term of the polynomial with a non-zero coefficient. The arithmetic, which must be used in the manipulation of these polynomials, is the arithmetic of the coefficients over the Galois Field of two elements GF(2) [Peterson 75]. Notice the result of dividing, multiplying or adding two binary polynomials also yields a polynomial in x with binary coefficients. For instance, the division of polynomial m(x) by p(x) yields a quotient polynomial q(x) and possibly, a remainder polynomial r(x):

$$\frac{m(x)}{p(x)} = q(x) + \frac{r(x)}{p(x)}$$

(2.1)

5

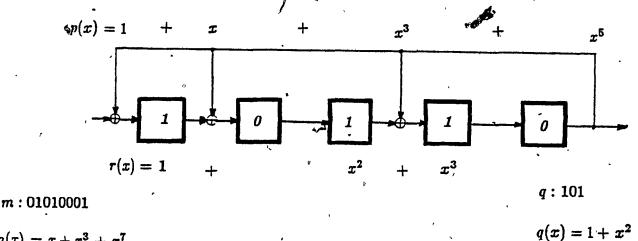

Example (2.1): Suppose that  $m(x) = x^7 + x^3 + x$  is divided by  $p(x) = x^5 + x^3 + x + 1$ , then the quotient polynomial is  $q(x) = x^2 + 1$ , and the remainder is  $r(x) = x^3 + x^2 + 1$ .

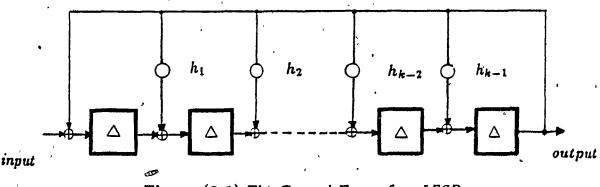

LFSRs can be used to mechanize polynomial division. An LFSR is a linear sequential network [Elspas 59] composed of interconnections of two types of elements: memory elements (e.g. D-flipflops) and Exclusive-OR gates. Figure (2.1) represents the general form of a k-stage LFSR, where memory elements are represented by squares; and Exclusive-OR gates are represented by the symbol  $\oplus$ .

Figure (2.1) The General Form of an LFSR

The memory elements together form a shift register. The output of the last stage of this register is fed back to the inputs of some of these memory elements via Exclusive-OR gates. These gates give the shift register its linear property [Golomb 82]. The feedback connections which characterize an LFSR are represented by a polynomial known as the LFSR's characteristic polynomial p(x):

$$p(x) = 1 + h_1 x + h_2 x^2 + \dots + h_{k-1} x^{k-1} + x^k$$

(2.2)

where  $h_i$  is equal to one if the corresponding feedback path  $h_i$  is a closed circuit; otherwise, it is equal to zero. The external input line shown in Figure(2.1) allows a serial feed of data.

$m(x)=x+x^3+x^7$

# Figure (2.2) An Illustration of a Polynomial Division

The operation performed by an LFSR is equivalent to the process of dividing an `input polynomial m(x) by the characteristic polynomial of the LFSR p(x). Specifically, the polynomial division m(x)/p(x) (equation 2.1) is performed by initializing the LFSR to all 0's, and serially shifting into the LFSR via its input, the input sequence that m(x)represents. Due to this division, a new sequence is shifted out serially from the LFSR output (i.e. the last stage). After the last input bit has been shifted into the LFSR,

a content remains in the LFSR. The new sequence shifted out of the LFSR represents the quotient polynomial of the division, q(x); whereas the LFSR content represents the remainder polynomial r(x), shown in equation (2.1). The polynomial division in Example(2.1) is realized by the LFSR shown in Figure(2.2).

Conventionally, when polynomial division is adopted to perform output data compression in a BIST design, an LFSR is utilized as the ODC. In such cases, the ODC's input sequence (i.e. input polynomial m(x)) is the output sequence from the CUT. After the division process has been performed, the LFSR content (i.e. the remainder of the division r(x)), represents the compressed form of the CUT's output sequence. Generally this remainder is termed as the signature (of the output response). Hence, the LFSR is sometimes called a signature analyzer [Frohwerk 77] [David 78].

Most of the BIST schemes adopt LFSRs for input pattern generation as well. This is possible when a test set of pseudo-random or exhaustive patterns is required. An LFSR that typically serves for input pattern generation is the autonomous LFSR, i.e. the one with no external input string applied to it. The sequence of test patterns generated from such an LFSR consists of its succeeding contents. Therefore, with each transition of state, the new LFSR content serves as the next pattern. Since an LFSR content appears on the outputs of its memory elements, the outputs of these elements can be directly connected to their corresponding CUT inputs. The only activating force of an autonomous LFSR is the feedback connections to the Exclusive-OR gates because there is no external input sequence applied to it (i.e. a constant 0 is applied to the external input). Consequently, given the characteristics of an autonomous LFSR and its initial state, the entire sequence of patterns can be determined in advance.

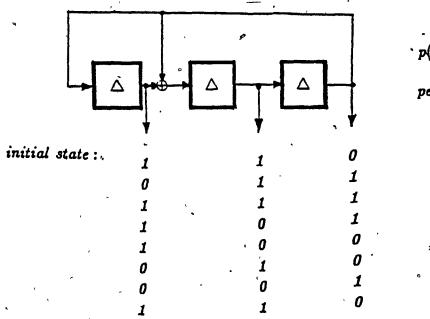

Each autonomous LFSR has a specific cycle, at the end of which the sequence of its patterns repeats. The cycle length (period) of an autonomous LFSR is determined by

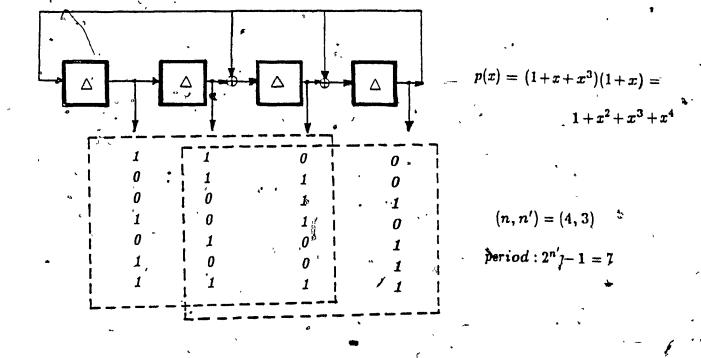

its characteristic polynomial (in some cases, on the initial state as well). The maximum cycle length possible (upper bound) is  $2^k - 1$ . This will consist of all non-zero distinct patterns. This arises provided that the LFSR starts in a non-zero initial state, and that its characteristic polynomial belongs to a certain class [Gschwind 75]. This is the class of primitive polynomials, for which tables can be found in [Golomb 82] [Peterson 75], and many other publications. Figure(2.3) demonstrates an LFSR which generates such a set of patterns.

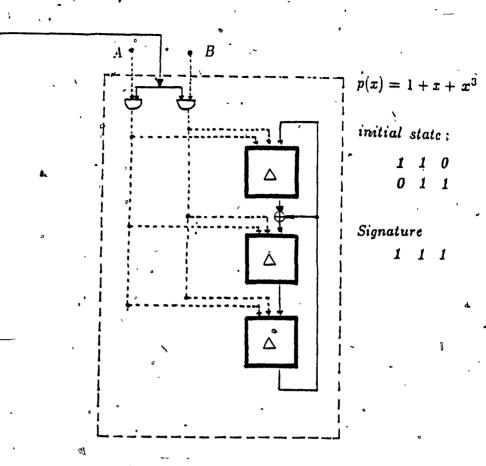

$p(x) = 1 + x + x^3$

$period: 2^n - 1 = 7$

Figure (2.3) An Autonomous LFSR with Maximum Cycle Length

The above mentioned property of generating  $2^{k} - 1$  distinct patterns provides a useful application of LFSR's in BIST. This is the use of maximum cycle length LFSRs as IPGs for BIST schemes with exhaustive testing [Sedmak 79] [McCluskey 81].

Furthermore, the patterns generated by an LFSR with maximum cycle length possess another very useful property which can be observed in the order of the patterns' appearance [Muchldorf 81]. Any segment, out of the entire sequence of patterns gener-

ated holds properties similar to random patterns [Golomb 82]. It must be stated that the generation of these patterns cannot be considered truly random. One of the reasons being that in this case, no pattern is repeatable until all of the other patterns appear. Thence, these patterns are usually termed as pseudo-random patterns.[Golomb 82].

In BIST schemes, the ability of LFSRs to generate pseudo-random patterns is considered to be one of their most appealing properties. This is because it is established that applying pseudo-random patterns in sufficient numbers (but still much smaller than the set of all possible patterns) is often very effective for detecting faults in combinational [Agrawal 75] [McCluskey 85a] [Chin 87] as well as in sequential CUTs [Losq 78].

Moreover, another appealing property of LFSRs characterized by primitive polynomials (i.e. maximum cycle lengths) renders LFSRs useful for output data compression. It has been shown that for ODCs, primitive polynomials are preferable to non-primitive polynomials, because they guarantee the detection of all single-bit errors [Bhavsar 85]. Primitive polynomials are also preferred to non-primitive polynomials because they result in less error information loss. This is true for the case where specific error patterns are considered [Hassan 83], as well as for the more general case with different error occurrence probabilities [Williams 86] [Williams 87]. However, to predict the effect of the choice of a particular primitive polynomial on the fault coverage of a BIST scheme is still an open problem [Ivanov 87].

## 2.1.2 Hardware Cost of BIST:

Ever since the introduction of BIST techniques, the related hardware overhead, and cost of implementation, have been of primary concern [Williams 84]. Conventionally, self-test circuits needed to implement the BIST techniques are either added to

the original CUT, as in [Bhavsar 81], or formed by reconfiguring some of the existing elements in the CUT, like in [Konemann 79]. In both cases, some extra hardware cost arises. Obviously, such a cost depends on the design and implementation of the chosen BIST technique as well as the CUT itself. Various methods have been introduced to investigate the hardware cost of BIST designs [Ohletz 87]. From [Bardell 82] (where three different BIST schemes are described and compared for cost and performance), it appears that a 5% threshold is current practice. Higher levels may be acceptable if test cost is reduced enough. In the implementation of the ODM scheme as well, the hardware cost will be shown in chapter 6 to be of primary concern.

Various BIST schemes use different techniques to design the two principal selftest blocks. The remainder of this chapter treats a number of these techniques. This treatment will serve as a basis to understand the implementational aspects of the ODMscheme in the following chapters.

## **1.2 Input Pattern Generation Process:**

The existing BIST schemet for combinational circuits suggest several techniques to perform input pattern generation. The pattern generation techniques of interest here, can be classified under the two most common types in BIST: exhaustive and pseudorandom. These two types are both of interest because they are needed to implement an . IPG in the ODM scheme.

It is necessary for an IPG to produce a repeatable test set, and for the IPG to send distinct start and stop signals to the ODC. Furthermore, if the CUT and ODC memory elements, it must be possible to repeatably initialize them to a known state before the

start signal is issued. These forementioned requirements are to ensure that for a given circuit, the same signature results for the fault-free CUTs.

#### 2.2.1 Exhaustive Test-Based Techniques:

Exhaustive testing implies the application of all possible  $2^n$  input patterns to a CUT, where n is the number of the input lines. The important advantage of this type of testing is that it is CUT-independent in the sense that no information about the CUT is required, except the number of its input lines.

Several schemes under universal BIST suggest the adoption of exhaustive testing to ensure complete fault coverage [Sedmak 79] [McCluskey 81] [McCluskey 82] [Agarwal 83]. Examples in [Savir 80] and [Barzilai 81] couple exhaustive testing with One's counting as the output data compression technique, while those in [Susskind 81] and [Muzio 82] couple exhaustive testing with the accumulation of Walsh coefficients.

The implementation of an IPG which performs exhaustive testing in a BIST design requires a device capable of generating all possible input patterns. An obvious candidate to perform this task is a binary counter. But since the order of the applied patterns is not important in an exhaustive test set, it is possible to use a maximum cycle length LFSR that generates all but one of the exhaustive patterns. Furthermore, the use of such an LFSR is also more efficient, since its hardware implementation is known to consume less area overhead than a binary counter of the same size. However, for the LFSR to generate the missing all-zero pattern, a modification of the maximum cycle length LFSR is needed. One possible modification is to add a scan path to scan-in the all-zero state through the LFSR [McCluskey 84b]. Another is to add extra gates to autonomously cycle through the all-zero state [McCluskey 86]. Yet another is to adopt

a systemätic technique to design an LFSR which cycles through all the states [Wang 86a] [Wang 86c].

The major concern with exhaustive testing is that circuits with many input lines require a very large number of input patterns which implies a too long testing time. For instance, if a circuit has more than 25 input lines; a 00 nanosecond clock would take more than one second to complete the testing process. Due to this concern, different attempts have been made to reduce the number of input patterns when exhaustive testing becomes infeasible. To notice is that most of these attempts utilize some information about the circuit under consideration, and therefore, produce circuit-specific BIST structures.

In order to reduce the large number of input patterns required, some techniques suggest partitioning the circuit. This implies decomposing the CUT into manageable partitions [McCluskey 81]. Different partitioning techniques are described in [Bozorgui-Nesbat 80], [McCluskey 81] [DasGupta 84] and [Archambeau 84]

Still to reduce the test length and retain the advantages of exhaustive testing, several other BIST schemes suggest techniques which apply exhaustive patterns to portions of the CUT rather than to the entire CUT. This is realized by a back-tracing procedure whereby the actual number of inputs that drive every output is determined [Bottorff 77]. These input pattern generation techniques are known as pseudo-Exhaustive techniques. More specifically, the concept underlying pseudo-exhaustive testing is the following. Since many combinational circuits may have outputs that depend on only a subset of the inputs, it is possible to exhaustively test the entire circuit by applying an exhaustive set of patterns to each subset of inputs, and then to observe the results on each corresponding output [McCluskey 85a]. In fact, to determine the subset of inputs upon which each output depends to design the required circuit-specific IPG, it suffices

to know the functionality of the CUT. It is important to mention that, the implementation of the pseudo-exhaustive techniques does not require any topological modifications to the CUT. The simplest IPG device that efficiently implements pseudo-exhaustive techniques is undoubtedly the LFSR. This is because some LFSRs have the capability of generating exhaustive test sets on some subsets of their outputs [Wang 84]. Such LFSRs require specific adjustments (hardware programming) according to the CUT. Several pseudo-exhaustive techniques are briefly described in the following.

The first pseudo-exhaustive technique appeared in [Barzilai 81]. It suggests the following. Given a CUT with n inputs, check if some of these inputs can share the same test signal. If n - n' inputs (n' < n) can share the test signals with the other n' inputs, then the test length becomes  $2^{n'}$ . A binary counter of size n' is suggested to generate these input patterns. The problem with this technique is that when n' is close to n, the test length may still be too long

To resolve this test length problem, another pseudo-exhaustive technique called verification testing was proposed [McCluskey 82], [Tang 83] [McCluskey 84]. Verification testing is based on the derivation of a constant-weight test set for a circuit without partitioning the circuit The constant-weight test set is shown to be a minimum-length test set for most of the circuits. However, the major problem with this technique is that for circuits which require-higher (m-out-of-n) codes (e.g. a 10-out-of-20 code), constant-weight counters become very costly to implement.

It may be more economical to use an LFSR instead of some form of counter for pseudo-exhaustive testing, even though this sacrifices the minimum test length property. One LFSR-based technique suggests using a combination of LFSR's and shift registers [Barzilai 83] [Tang 84] for input pattern generation. It uses linear codes [Peterson 75] to find the desired generator polynomial for the LFSR. This technique is most useful

when the maximum number of inputs upon which an output depends is much less than n. However, it is difficult to find the suitable generator polynomial. Moreover, the technique usually requires at least two initial states which may have to be stored in a ROM. This storage can become a burden when there are many such circuits to be tested.