#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48108-1346 USA 800-521-0800

# High-Speed/Low-Cost Delta-Sigma Modulation Techniques for Analog-to-Digital Conversion

by John Abcarius, B. Eng. 1995

Department of Electrical Engineering

McGill University, Montréal

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Engineering.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-50588-X

### **Abstract**

As digital electronics becomes increasingly popular, the need for efficient data conversion to provide the link to our analog world grows all the more important. To sustain the current rate of technological advancement, the requirements on the data conversion systems are becoming more stringent. Wireless communication systems demand high speed, high performance analog-to-digital conversion front-ends. Furthermore, consumers demand quality electronics at low cost, which precludes the use of expensive analog processes.

This thesis investigates the potential of  $\Delta\Sigma$  modulation techniques in addressing both of these issues through the design, implementation and experimentation of several prototype integrated circuits. Delta-Sigma modulation has recently become widely recognized for its ability to perform high performance data conversion without the use of high precision components. To extend these benefits to wireless applications, a novel eighth-order bandpass  $\Delta\Sigma$  modulator for A/D conversion will be presented. The modulator design is developed beginning at the signal processing level and realized in a 0.8 $\mu$  BiCMOS process using the switched-capacitor (SC) technique. To address the cost issue, the design of a data conversion system based on the  $\Delta\Sigma$  modulation technique using an economical purely digital CMOS implementation is investigated. The distortion performance of experimental prototypes implemented using switched-capacitor (with capacitors realized using MOSFETs) and switched-current techniques is assessed.

This work therefore contributes to the ongoing drive to improve the performance and applicability of the  $\Delta\Sigma$  modulation technique in meeting modern-day data conversion needs.

### Résumé

Avec la popularité grandissante des circuits électroniques numériques, le besoin de convertir avec efficacité les données pour assurer le lien avec le monde analogique devient de plus en plus important. Afin de maintenir le rythme actuel de développement technologique, les exigences relatives aux systèmes de conversion de données deviennent plus sévèrres. Les systèmes de communication sans fil requièrent des circuits de conversions analogiques-numériques à grande vitesse et haute performance. De plus, les consommateurs exigent des composants électroniques de haute qualité à prix raisonnable, ce qui rend impossible l'utilisation de procédés analogiques coûteux.

Dans cette thèse, le potentiel de la modulation delta-sigma à solutionner les deux problèmes ci-haut mentionnés est étudié à l'aide de la conception, la fabrication et l'expérimentation de plusieurs prototypes de circuits intégrés. La modulation  $\Delta\Sigma$  est récemment devenue largement reconnue grâce à sa capacité de convertir les données avec une grande qualité sans nécessiter de composants de haute précision. Pour étendre ces bénéfices aux applications de communication sans fil, un nouveau modulateur de huitième ordre à bande passante sera présenté. La conception du modulateur est expliquée à partir du niveau de traitement du signal jusqu'à la réalisation utilisant la technique des condensateurs-commutés à l'aide du procédé BiCMOS de 0,8 microns. Afin d'aborder la question du coût, la conception d'un système de conversion basée sur la technique de modulation  $\Delta\Sigma$  qui utilise un procédé numérique est étudiée. Une analyse de la distorsion sur des prototypes expérimentaux employant des condensateurs-commutés (réalisés à l'aide de transistors à effet de champ MOSFETs) et des techniques de courants-commutés est aussi effectuée.

Cet ouvrage contribue donc à l'élan d'amélioration de la performance et de l'utilité des techniques de modulation  $\Delta\Sigma$  dans le contexte des besoins présents de conversion de données.

## Acknowledgements

The work described herein is a result of the generous contribution of knowledge, expertise, and support of several people.

To begin, I would like to express my gratitude to my supervisor, Professor Gordon Roberts. His endless enthusiasm and unparalleled teaching ability are largely responsible for my microelectronics career choice and success of this work. I greatly appreciate his technical insight and unwavering support throughout my degree.

I am grateful for the contributions of, and many useful technical discussions with Loai Louis, Choon Leong, Benoit Dufort, Mourad El-Gamal, Xavier Haurie, Vincent Leong, Benoit Veillette, Arman Hematy and for the good times spent together. I am very fortunate to have had such excellent company during my years at McGill. Nicolas Gagnon and John Walker were of great assistance in the development of the PCB boards. I am thankful for the around-the-clock efforts of the system administrators in keeping the computers running. I am also grateful for the work of the many MACS laboratory alumni who established the infrastructure that made this work possible.

Most of all I would like to thank my wife Shelley for her understanding, patience and support, and that of my family as well throughout my education at McGill. Special thanks to the entire Ducks Utd. team for their continuing friendship, laughter and advise.

Finally, NSERC provided personal financial support and together with Micronet supplied funding for the laboratory equipment.

# **Table of Contents**

| Abstı  | ract   |                                                                 | ii  |

|--------|--------|-----------------------------------------------------------------|-----|

| Résu   | mé     |                                                                 | iii |

| Ackn   | owle   | dgements                                                        | iv  |

| List o | of Fig | ures                                                            | ix  |

|        |        | bles                                                            |     |

| Chap   | pter 1 | : Introduction                                                  | 1   |

|        | 1.1    | Motivation                                                      | 1   |

|        |        | 1.1.1 The need for high-performance, high-speed data conversion | 2   |

|        |        | 1.1.2 The need for using a standard digital CMOS process        | 4   |

|        | 1.2    | Thesis Overview                                                 | 4   |

| Chaj   | pter 2 | 2 : Basic Lowpass Delta-Sigma Modulation                        | 6   |

|        | 2.1    | Background Theory                                               | 6   |

|        |        | 2.1.1 Delta-Sigma Modulation for Data-Conversion                | 6   |

|        |        | 2.1.2 Basic ΔΣ Modulator Operation                              | 9   |

|        |        | 2.1.3 Time Domain Analysis                                      | 11  |

|        |        | 2.1.4 Frequency Domain Perspective: Noise Shaping               | 12  |

|        |        | 2.1.5 A General Modulator Structure                             | 13  |

|        | 2.2    | A Second-Order LowPass ΔΣ Modulator                             | 15  |

|        |        | 2.2.1 Design Specifications                                     | 15  |

|        |        | 2.2.2 SFG-Level Design                                          | 15  |

|        |        | 2.2.3 Switched-Capacitor Realization                            | 18  |

|     |        | 2.2.4 Circuit Implementation                          | . 20 |

|-----|--------|-------------------------------------------------------|------|

|     |        | 2.2.5 Experimental Results                            | . 24 |

|     | 2.3    | Conclusion                                            | . 25 |

| Cha | pter 3 | 3 : A Novel High-Order Bandpass ΔΣ Modulator          | 26   |

|     | 3.1    | The Bandpass Approach                                 | . 26 |

|     | 3.2    | Modulator Design                                      | . 29 |

|     |        | 3.2.1 Design Objectives                               | . 29 |

|     |        | 3.2.2 NTF Design for Desired Specifications           | . 29 |

|     |        | 3.2.3 Selecting a Structure                           | . 31 |

|     |        | 3.2.4 Obtaining the Coefficients that control the NTF | . 37 |

|     |        | 3.2.5 Obtaining the Coefficients that control the STF | . 39 |

|     |        | 3.2.6 Scaling for Maximum Dynamic Range               | . 40 |

|     | 3.3    | Switched-Capacitor Implementation                     | . 42 |

|     |        | 3.3.1 Capacitor Sizing                                | . 42 |

|     |        | 3.3.2 Switch Design                                   | . 45 |

|     |        | 3.3.3 Clock Phasing                                   | . 49 |

|     |        | 3.3.4 Amplifier and Comparator Circuits               | . 50 |

|     |        | 3.3.5 D/A Scheme                                      | 50   |

|     | 3.4    | Layout Considerations                                 | 52   |

|     |        | 3.4.1 The Capacitor Array                             | 52   |

|     |        | 3.4.2 Overall Floorplan                               | 54   |

|     | 3.5    | Design Verification                                   | 55   |

|     |        | 3.5.1 SFG level verification                          | 55   |

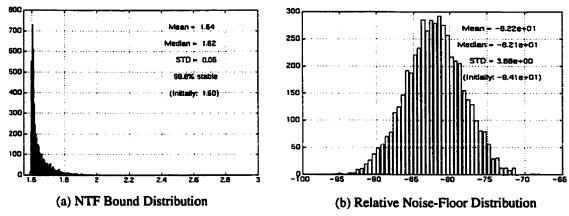

|     |        | 3.5.2 Performance Under Process Variation                    |

|-----|--------|--------------------------------------------------------------|

|     |        | 3.5.3 Simulating the structure using SWITCAP2                |

|     |        | 3.5.4 Using HSPICE to Simulate the Circuit                   |

|     |        | 3.5.5 Verifying the Circuit's Layout                         |

|     | 3.6    | Experimental Results                                         |

|     |        | 3.6.1 The Test Environment                                   |

|     |        | 3.6.2 Experimental Performance                               |

|     |        | 3.6.3 Performance Evaluation                                 |

|     |        | 3.6.4 Performance Limitations                                |

|     |        | 3.6.5 Recommendations for Improvement                        |

|     | 3.7    | Conclusion                                                   |

| Cha | pter 4 | : All-CMOS Data Conversion using $\Delta\Sigma$ Modulation73 |

|     | 4.1    | Introduction                                                 |

|     | 4.2    | The Switched-Capacitor Approach                              |

|     |        | 4.2.1 Using MOSFETS to Realize Capacitors                    |

|     |        | 4.2.2 Reducing the MOS-Capacitor Non-Linearity 87            |

|     |        | 4.2.3 Prototype Filter                                       |

|     |        | 4.2.4 Prototype $\Delta\Sigma$ Modulator                     |

|     | 4.3    | The Switched-Current Approach                                |

|     |        | 4.3.1 Implementation using the SI Technique                  |

|     |        | 4.3.2 Prototype Switched-Current Filter                      |

|     |        | 4.3.3 Prototype Switched-Current ΔΣ Modulator                |

|     |        |                                                              |

| Chapter 5: Conclusion | 11 |  |

|-----------------------|----|--|

| •                     |    |  |

| References            | 12 |  |

# **List of Figures**

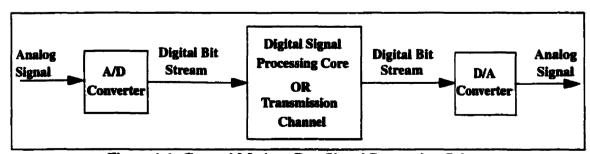

| 1.1  | General Modern-Day Signal Processing Scheme                                   | 1  |

|------|-------------------------------------------------------------------------------|----|

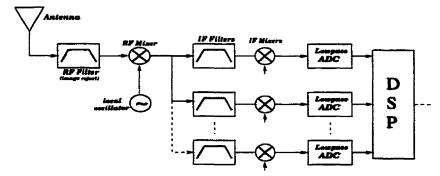

| 1.2  | Simplified Conventional Wireless Receiver (Base Station)                      | 2  |

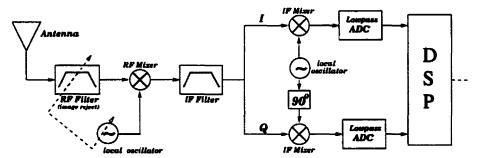

| 1.3  | Simplified Handset Receiver Architecture                                      | 3  |

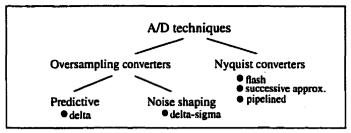

| 2.1  | Main A/D conversion Techniques                                                | 7  |

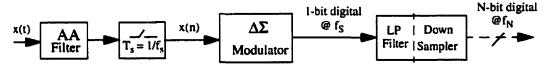

| 2.2  | Elements of a Delta-Sigma Analog-to-Digital Conversion System                 | 8  |

| 2.3  | First-Order $\Delta\Sigma$ modulator with linear model of the quantizer       | 9  |

| 2.4  | Input (sinusoid) and output (PDM) time-domain waveforms of a $\Delta\Sigma M$ | 10 |

| 2.5  | First-order $\Delta\Sigma$ modulator with modified signal flow graph          | 11 |

| 2.6  | Output Noise PSDs corresponding to 1st and 2nd Order LP Modulators            | 12 |

| 2.7  | General ΔΣ Modulator Structure for A/D Conversion                             | 13 |

| 2.8  | Two-Integrator Loop Topology                                                  | 15 |

| 2.9  | SFG level representation of the delayed, delayed combination                  | 16 |

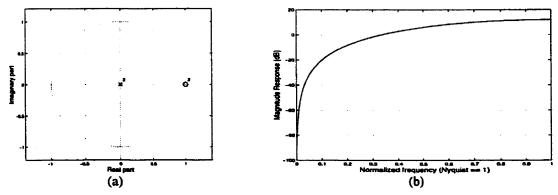

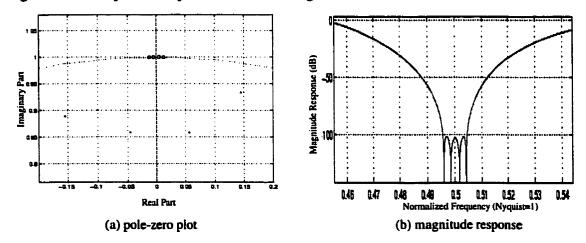

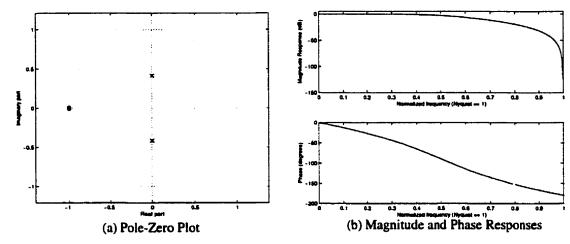

| 2.10 | (a)Pole-Zero and (b) Frequency Response Plots of NTF for a=1, b=2             | 16 |

| 2.11 | Alternate representation of the delayed, delayed combination                  | 17 |

| 2.12 | NTF Behavior for the alternate SFG representation (a=1/4 and b=1/2)           | 17 |

| 2.13 | Results of SFG-Level Simulation using Simulink                                | 18 |

| 2.14 | Lowpass Modulator Implementation                                              | 19 |

| 2.15 | Area-efficient SC Modulator Implementation                                    | 20 |

| 2.16 | Fully-Differential Folded-Cascode OTA with CMFB and Bias Circuity             | 21 |

| 2.17 | Transmission Cell                                                    | 22 |

|------|----------------------------------------------------------------------|----|

| 2.18 | Schematic of Clock Phase Generator                                   | 23 |

| 2.19 | Chip Photomicrograph of Second-Order Lowpass ΔΣ Modulator            | 24 |

| 2.20 | Experimental Results of the Fabricated IC                            | 25 |

| 3.1  | General Modulator Structure                                          | 26 |

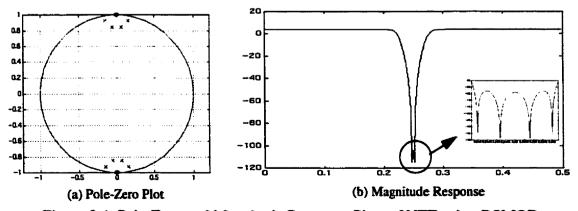

| 3.2  | (a) pole-zero and (b) magnitude response plots of a BP NTF           | 27 |

| 3.3  | Simplified Digital RF Receiver                                       | 28 |

| 3.4  | Pole-Zero and Magnitude Response Plots of NTF using DSMOD            | 30 |

| 3.5  | General Eighth-Order ΔΣ Modulator Structure                          | 31 |

| 3.6  | LDI Two-Integrator-Loop Topology                                     | 32 |

| 3.7  | LDI and modified LDI (parenthesized clock phases) SC topologies      | 33 |

| 3.8  | SC Implementation of the Unit Delay Cell                             | 34 |

| 3.9  | Basic FE Structure                                                   | 35 |

| 3.10 | SC Implementation of the FE Structure                                | 36 |

| 3.11 | SFG-level Structure (based on FE loop)                               | 37 |

| 3.12 | Optimized NTF after 4 of the 8 b's were set to zero                  | 38 |

| 3.13 | Modulator with odd feedforward coefficients set to zero              | 39 |

| 3.14 | Optimized Signal Transfer Function Response                          | 40 |

| 3.15 | Transmission Gate                                                    | 46 |

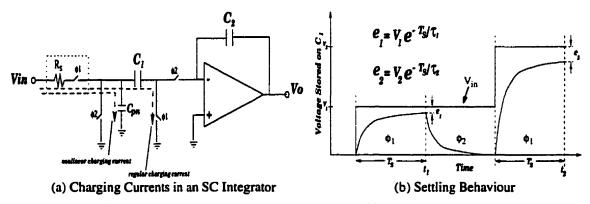

| 3.16 | Analysis of Settling Errors during the Charging Phase in SC circuits | 47 |

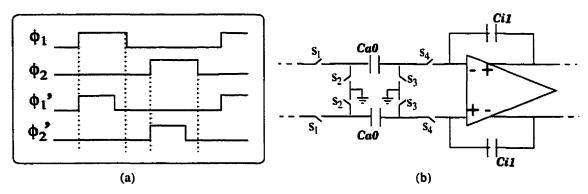

| 3.17 | Four-Phase Clocking Scheme with Example Circuit                      | 49 |

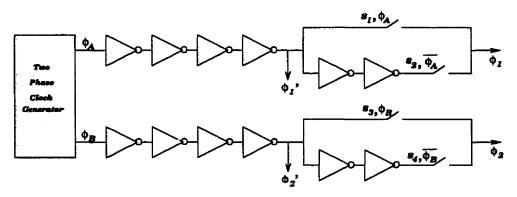

| 3.18 | Digital Circuitry to Generate the Four Clock Phases                  | 50 |

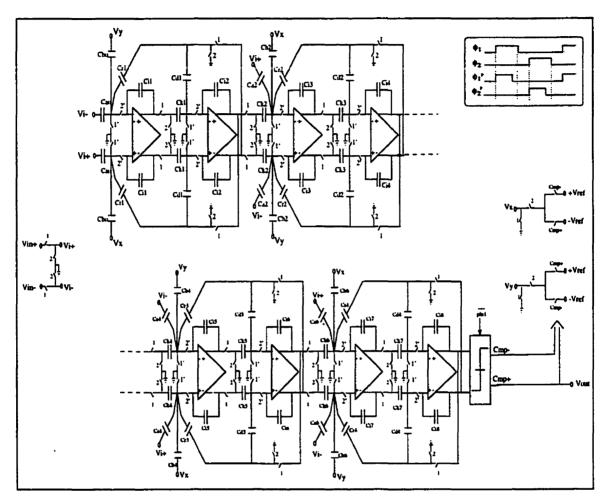

| 3.19 | Complete Switched-Capacitor Circuit Implementation                   | 51 |

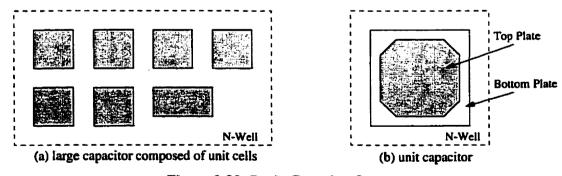

| 3.20 | Basic Capacitor Layout                                                       | 52 |

|------|------------------------------------------------------------------------------|----|

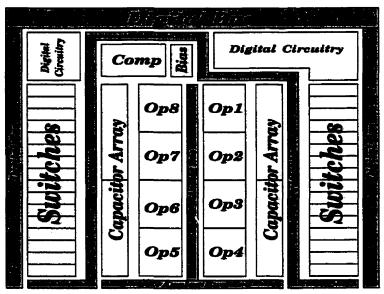

| 3.21 | Overall Floorplan of the Layout                                              | 54 |

| 3.22 | Spectrum of Modulator's Output, Simulated using Simulink                     | 55 |

| 3.23 | Performance Under Process Variation                                          | 57 |

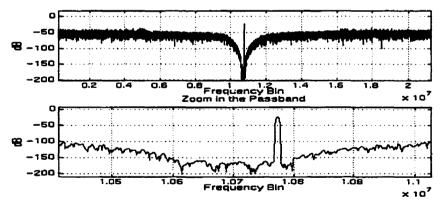

| 3.24 | Spectrum of the Modulator Output, Simulated with SWITCAP2                    | 58 |

| 3.25 | Spectrum of Modulator's output obtained from HSPICE simulation with          |    |

|      | everything ideal except the comparator                                       | 59 |

| 3.26 | Die Micrograph of the 8th-order Bandpass Delta-Sigma Modulator               | 61 |

| 3.27 | Top View of PCB Boards                                                       | 62 |

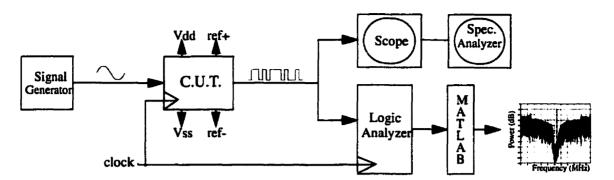

| 3.28 | Experimental Setup used to Test the Modulator                                | 63 |

| 3.29 | Physical Setup used in Diagnosing the Circuit                                | 63 |

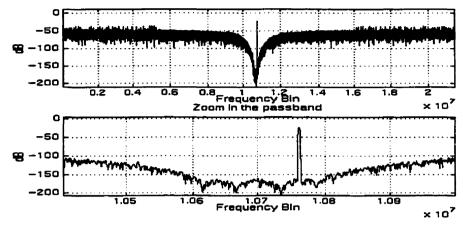

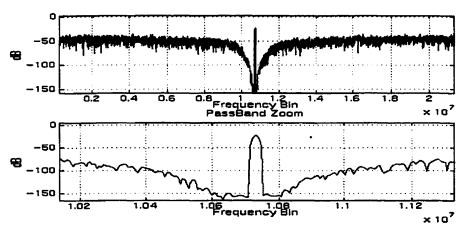

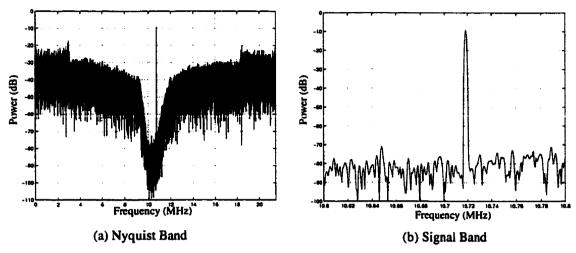

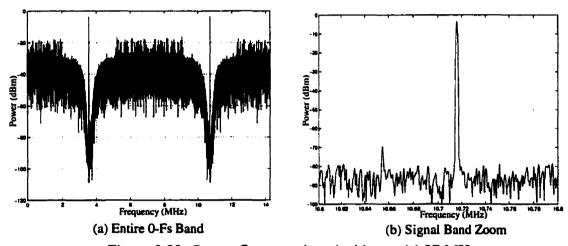

| 3.30 | Output spectra when clocked at 42.8 MHz                                      | 65 |

| 3.31 | IF band when clocked at 44.8 MHz                                             | 66 |

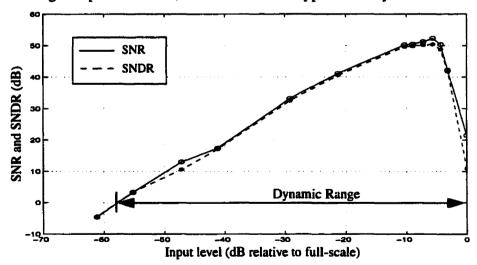

| 3.32 | SNR and SNDR as a function of input level                                    | 66 |

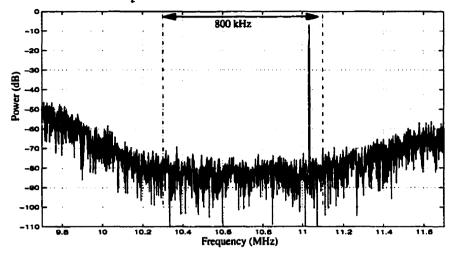

| 3.33 | Output Spectra when clocking at 14.27 MHz                                    | 67 |

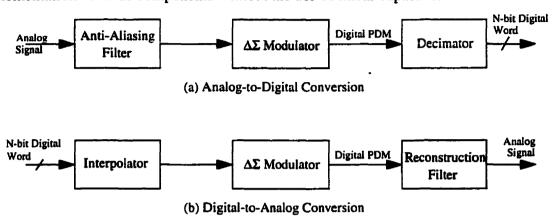

| 4.1  | Basic Elements of Data Conversion systems based on $\Delta\Sigma$ Modulation | 74 |

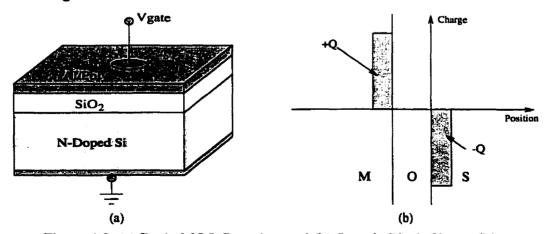

| 4.2  | (a) Basic MOS Capacitor and (b) Sample Block Charge Diagram                  | 76 |

| 4.3  | Charge Fluctuations within a MOS-C structure subject to an AC gate voltage,  |    |

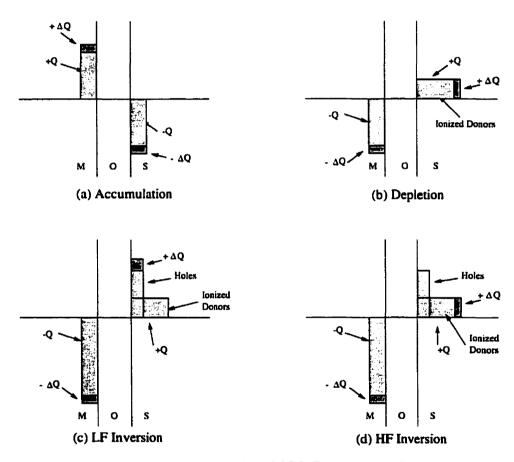

|      | under four different DC bias conditions                                      | 77 |

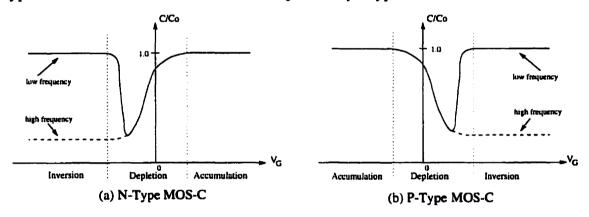

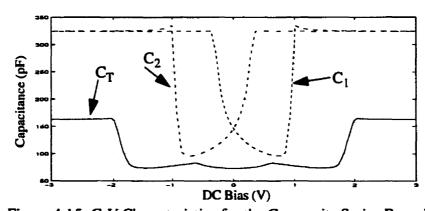

| 4.4  | Capacitance-Voltage Characteristics of N-type and P-type MOS-Cs              | 79 |

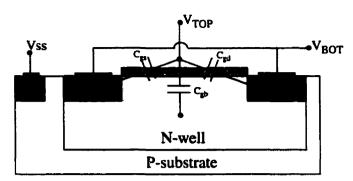

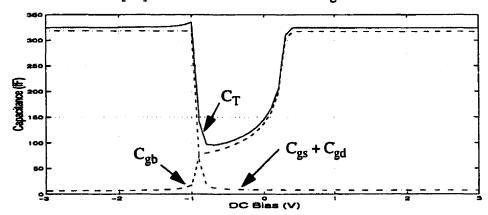

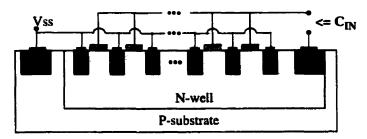

| 4.5  | P-MOSFET Structure used for Capacitor Implementation                         | 80 |

| 4.6  | Capacitance-Voltage Characteristic for the P-MOSFET Structure                | 81 |

| 4.7  | Basic SC integrator to illustrate effect on capacitor non-linearities        | 82 |

| 4.8  | The SC Technique from a Charge Processing Point of View      | 84  |

|------|--------------------------------------------------------------|-----|

| 4.9  | SC Circuit to Demonstrate Linear Charge Processing           | 84  |

| 4.10 | SC ΔΣ Modulator from a Charge Processing Perspective         | 86  |

| 4.11 | Configuration used to Bias PMOS-Capacitors in Accumulation   | 87  |

| 4.12 | Alternate DC Biasing Configuration                           | 87  |

| 4.13 | DC Biasing Scheme for a Differential SC Integrator           | 88  |

| 4.14 | Structures to Reduce Non-Linearity, without DC Biasing       | 89  |

| 4.15 | C-V Characteristics for the Composite Series Branch          | 89  |

| 4.16 | MOSFET Layout to Reduce Non-linearity                        | 90  |

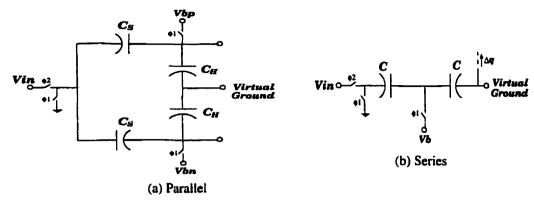

| 4.17 | Composite SC Branches proposed in [46]                       | 91  |

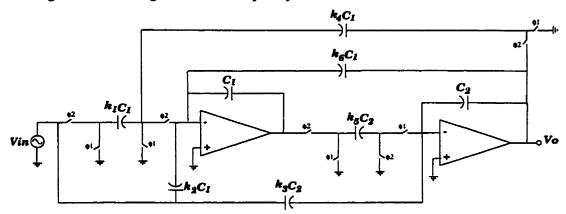

| 4.18 | Second-Order Lowpass SC Filter Prototype                     | 92  |

| 4.19 | Ideal SC Filter Response                                     | 93  |

| 4.20 | Chip Micrograph of SC Circuits employing MOSFET-capacitors   | 94  |

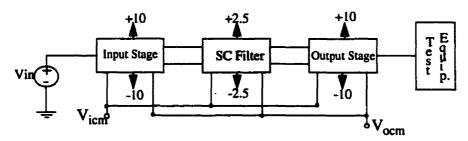

| 4.21 | Overall Filter Test Setup                                    | 95  |

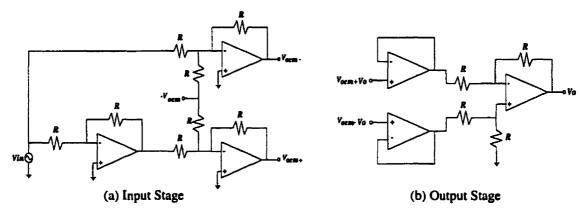

| 4.22 | Input and Output Stages Required in the Overall Test Setup   | 95  |

| 4.23 | Experimental Filter Behavior, employing Poly-Poly Capacitors | 95  |

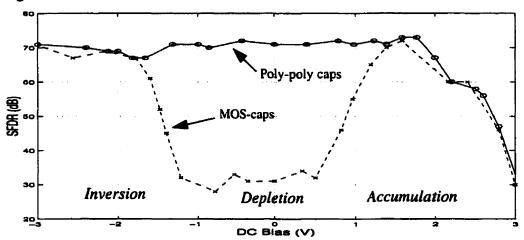

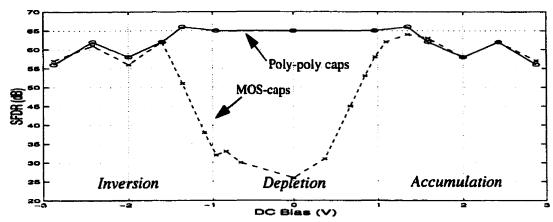

| 4.24 | Effect of Capacitor DC Bias on the Filter SFDR               | 96  |

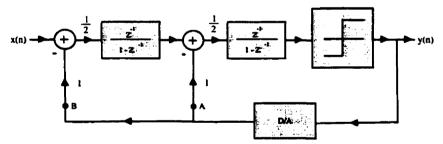

| 4.25 | SFG-Level Structure for Prototype $\Delta\Sigma$ Modulator   | 97  |

| 4.26 | Experimental Performance using Non-Biased MOSFET Capacitors  | 99  |

| 4.27 | Effect of Capacitor DC Bias on the Modulator SFDR            | 100 |

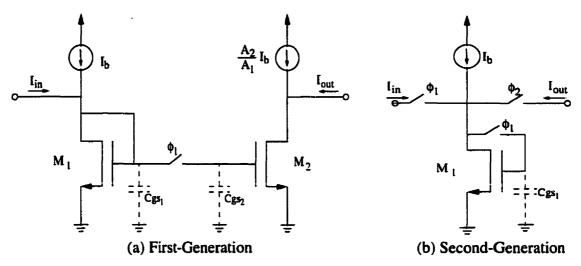

| 4.28 | Basic SI Memory Cells                                        | 102 |

| 4.29 | SI Integrator based on First-Generation Memory Cells         | 103 |

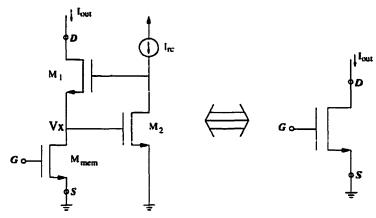

| 4.30 | Regulated Cascode "Super-Transistor"                         | 104 |

| 4.31 | High-Swing Double-Cascode Current Source                 | 106 |

|------|----------------------------------------------------------|-----|

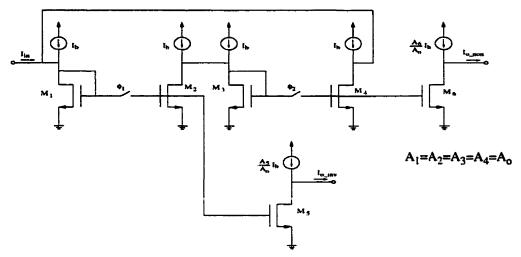

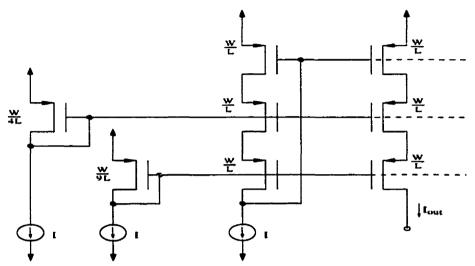

| 4.32 | A Second-Order Lowpass SI Filter Circuit                 | 109 |

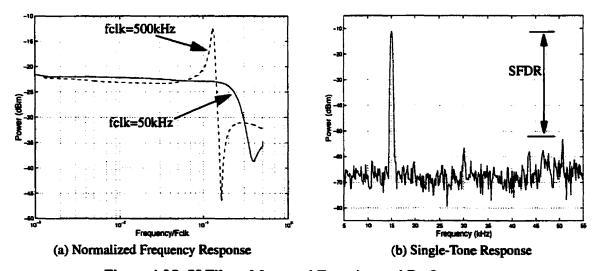

| 4.33 | Simulated Frequency Response of SI Filter using WATSNAP  | 110 |

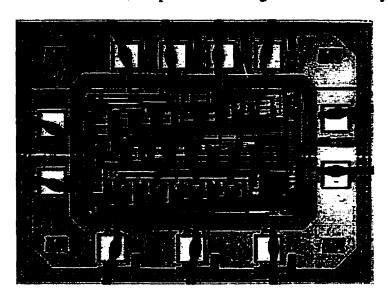

| 4.34 | SI Filter Chip Photomicrograph                           | 111 |

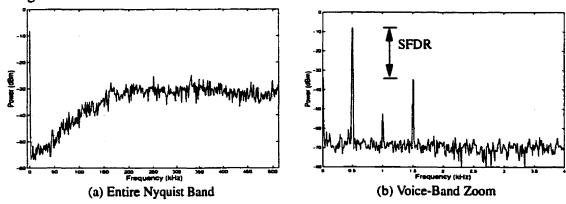

| 4.35 | SI Filter: Measured Experimental Performance             | 111 |

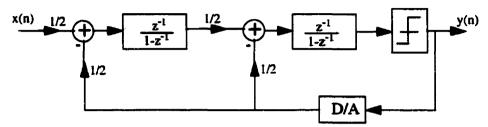

| 4.36 | DSP-level Structure of SI Modulator                      | 112 |

| 4.37 | (a) Quantizer and (b) 1-bit DAC implementations          | 112 |

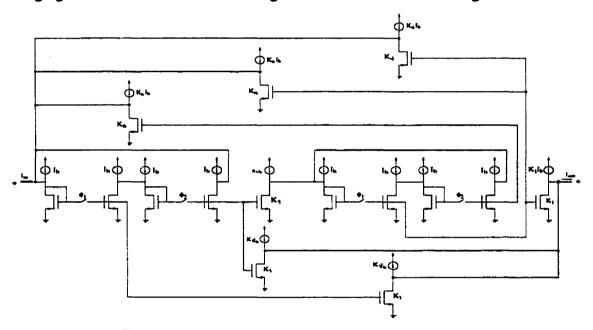

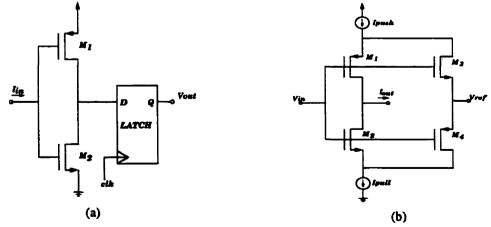

| 4.38 | Simplified SI Delta-Sigma Modulator Schematic            | 113 |

| 4.39 | SI Delta-Sigma Modulator Chip Photomicrograph            | 115 |

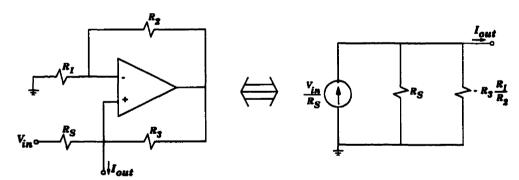

| 4.40 | V-to-I Converter Based on a Negative-Impedance Converter | 115 |

| 4.41 | Experimental Performance of SI ΔΣ Modulator              | 116 |

## **List of Tables**

| 3.1 | Theoretical Modulator Specifications                            | 30  |

|-----|-----------------------------------------------------------------|-----|

| 3.2 | Modulator Coefficients' Values After DR Scaling and Adjustments | 41  |

| 3.3 | Capacitor Values used in the SC structure                       | 45  |

| 3.4 | Summary of Experimental Results                                 | 68  |

| 3.5 | Previously Reported Fabricated Bandpass ΔΣ Modulators           | 69  |

| 4.1 | Dynamic-Range Scaled Coefficient Values for the SC Filter       | 93  |

| 4.2 | Implemented Capacitor Structures and Area Requirements          | 98  |

| 4.3 | Maximum SFDR Attainable with Non-Biased MOSFET Capacitors       | 100 |

| 4.4 | Nominal Design Values for SI Delta-Sigma Modulator              | 114 |

| 4.5 | Summary of Experimental Results for the Four Prototype ICs      | 117 |

### **Chapter 1: Introduction**

This thesis is concerned with the use of delta-sigma modulation as a means of meeting the modern day analog-to-digital conversion (ADC) needs of high-performance and low-cost. This chapter will discuss the driving force behind these two industry demands, and outline how the work of this thesis is organized to address them.

#### 1.1 Motivation

As digital processors are becoming ever more powerful and inexpensive, digital processing of information has replaced much of the traditional analog techniques used in the past. In addition due to the improved signal quality, ease of routing and added versatility, most information transmission in modern-day communication systems is also performed using digital means. In consequence, this has lead to the general processing scheme shown in Figure 1.1 below:

Figure 1.1: General Modern-Day Signal Processing Scheme

#### Chapter 1: Introduction

As real-world signals, such as speech or radio waves, are analog in nature, it is necessary to include A/D and D/A converters at the front and back ends of the system, respectively. These data converters contain both analog and digital components, and form the interface between analog real-world signals and the hardware that processes them.

The above scheme has become increasingly popular, however, it does have two major repercussions associated with it. These two repercussions are the motivating factor behind this work and will be discussed next.

#### 1.1.1 The need for high-performance, high-speed data conversion

As we drive towards higher quality and greater operating speeds, increased demands are placed upon the processing hardware. Continually improving digital processors are paving the way for these increased demands. However, if the data converters shown in Figure 1.1 can not follow suit, they will become the bottle neck in the system. That is, their lower performance will dominate the system performance.

The need for high speed data conversion is further intensified by a growing trend in wireless communications. Systems that rely solely on analog modulation and demodulation schemes are being replaced by digital techniques or by hybrid solutions that allow the use of both analog and digital approaches. Digital systems allow the transfer of data as well as voice, are more easily routed and provide greater security for the user through channel encryption. A conventional (mostly) digital cellular receiver is depicted in Figure 1.2:

Figure 1.2: Simplified Conventional Wireless Receiver (Base Station)

Although not shown in the simplified base station architecture of Figure 1.2, the RF downconversion is typically handled in multiple stages to ease the requirement on the image rejection filter. In the receiver of Figure 1.2, each channel uses an independent dedicated IF strip before the signal is brought down to baseband. Only then do the ADCs convert the signals to the digital domain, where processing can begin. This approach is costly due to the extensive use of analog components. In addition, each channel is fixed, and not adaptable to any changes made in transmission protocols. For these reasons, it is desirable to move the analog-to-digital converters as close to the front-end of the system as possible, ideally converting the entire RF spectrum with one single, wide-band ADC. This would alleviate the need for multiple expensive analog components, and make the system more versatile, as the digital hardware can easily be re-programmed and adapted to any new protocol. This latter approach, however, places extreme requirements on the data converter, in terms of both speed and resolution.

Further incentive for investigating high speed ADC can be understood by considering more closely the demodulation of a single channel, as in the handset receiver of Figure 1.3.

Figure 1.3: Simplified Handset Receiver Architecture

Once down-converted to baseband, the signal is split into in-phase (I) and quadrature (Q) components which are processed by separate channels, leaving the receiver susceptible to mismatch between the two. Furthermore, the lowpass ADC must be designed carefully to avoid DC offset and 1/f noise problems. Alternatively, these shortcomings could be avoided if a bandpass ADC were used to directly convert the IF signal and the I/Q split performed digitally. However, once again this places stringent demands on the data converter.

As will become evident shortly,  $\Delta\Sigma$  modulation offers an attractive approach to realize the high-performance converters required. A major advantage of the  $\Delta\Sigma$  technique is that it

does not require high precision analog circuitry, which is all the more important if one wishes to use a standard digital CMOS process.

#### 1.1.2 The need for using a standard digital CMOS process

As the vast majority of IC's are currently realized using digital processing of information, fabrication processes have been tailored to optimize for digital circuitry. As such, pure digital CMOS, where no additional processing steps have been used, is by far the most economical technology in terms of fabrication cost.

However, analog circuitry often requires high performance features that are not found in a standard digital CMOS process. For example, the high gain and bandwidth associated with a BJT is often desirable, as is the high linearity of poly-poly capacitors. Although these features can be included through additional processing steps, as in current BiCMOS processes, this approach incurs extra costs.

In addition, in many systems, it is often desirable to include the usually small amount of analog circuitry together with the mainly digital core resulting in a mixed-signal IC. This is especially the case for data converters which often contain the only analog circuitry on the entire IC. If the analog circuits can not be designed using a purely digital CMOS process, the entire IC will have to be fabricated in a more expensive BiCMOS technology. Thus, although digital circuits can be produced quite inexpensively on their own, the relatively small amount chip area devoted to analog functions can contribute an unproportionate amount to the overall system cost.

Therefore, any circuit technique that would allow these analog circuits to be manufactured in the same inexpensive CMOS process as the digital core would be very valuable.

### 1.2 Thesis Overview

In Chapter 2, the concept of delta-sigma modulation for analog-to-digital conversion will be introduced. A basic second order lowpass modulator, implemented using the switched-capacitor (SC) technique has been fabricated in a 0.8µ BiCMOS process, and will be used

#### Chapter 1: Introduction

to demonstrate the technique through from specification to a physical IC. This illustration of the basic design process will serve to pave the way for the more elaborate work of Chapter 3, where a more complex eighth-order modulator will be investigated. It will also set the ground work for the  $\Delta\Sigma$  modulator designs of Chapter 4, which are based on variations of the same second-order modulator.

Next, in Chapter 3, the concept of bandpass delta-sigma modulation will be introduced. The chapter illustrates a step-by-step design process for a novel, eighth-order bandpass delta-sigma modulator, designed to address the need for high speed, high performance data-converters discussed in Section 1.1.1. The discussion will detail the design from the DSP-level abstaction complete through to subtle, though crucial, implementation and layout considerations. The strategy used to verify the design at the various stages will also be presented. The design has been fabricated in a 0.8 $\mu$  BiCMOS process producing the first working bandpass prototype of such high-order. Experimental results will be shown to illustrate the performance of the modulator.

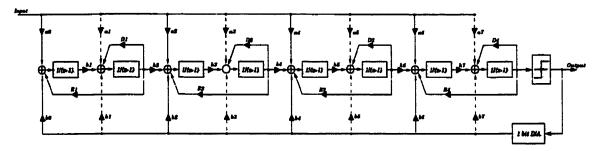

Chapter 4 will be used to address the economic driving force discussed in Section 1.1.2 by studying the use of  $\Delta\Sigma$  modulation in an all-CMOS data conversion system. Specifically, we will investigate sampled-data implementations of the  $\Delta\Sigma$  modulator and filter components using two different circuit techniques that do not require the linear capacitors which are unavailable. One approach is to employ the switched-capacitor technique and use MOSFETs to implement the capacitors. The second approach is to use the technique of switched-currents which inherently does not require explicit capacitors all-together. In each case, an experimental prototype of a second order lowpass  $\Delta\Sigma$  modulator as well as of a biquadratic filter has been fabricated to study the techniques. Experimental results of the four ICs will also be included in the chapter.

The thesis will conclude in chapter 5 with a summary of the work presented.

In this chapter, the concept and background theory of lowpass  $\Delta\Sigma$  modulation will first be introduced. Next, a second-order voiceband  $\Delta\Sigma$  modulator will be used to illustrate the basic design process from initial specification through to a physical IC that has been fabricated in a 0.8 $\mu$  BiCMOS process.

### 2.1 Background Theory

This section will first discuss how the analog-to-digital conversion using the  $\Delta\Sigma$  method compares to other classes of data-conversion techniques. The basic principles of  $\Delta\Sigma$  modulation will then be discussed in terms of both time domain and frequency domain behavior.

#### 2.1.1 Delta-Sigma Modulation for Data-Conversion

The main A/D conversion techniques used today are summarized in Figure 2.1. The main distinction between converter classes is in the rate at which they sample the analog signal. Nyquist rate converters sample a bandlimited continuous-time signal at the Nyquist rate,  $f_N$ , which is twice the bandwidth of the analog signal. The sampling action must be preceded by an analog lowpass filter to avoid any aliasing.

Figure 2.1: Main A/D conversion Techniques

Nyquist rate converters have two main disadvantages [1]. First, the anti-aliasing filter must have a very sharp roll-off which translates into a high-order, quite complex, analog filter. Second, the matching of components becomes a problem when the precision of the converter starts to increase. This is because in VLSI implementations, an N-bit quantizer achieves data-conversion by comparing the analog input signal to a set of reference voltages, and outputting the appropriate digital word. The precision of the converter depends on the spacing between these reference voltages which, from the implementation viewpoint, depends on the matching properties of the resistors or capacitors used. For a quantizer with 16-bit resolution or higher, the spacing of these reference levels must be in the microvolt range. Unfortunately, the matching tolerance of these elements (resistors or capacitors) is much lower than the above requirements. Therefore, unless expensive post-fabrication microsurgery is used, nyquist-rate converters are not well-suited for high-precision data conversion needs.

Oversampled converters sample the analog signal at a much higher rate,  $f_S$ . The amount of oversampling is quantified by the *oversampling ratio*, defined as

$$OSR = f_S/f_N \tag{2.1}$$

This class of converters avoids the aforementioned problems by exchanging the required resolution in amplitude for that in time. Furthermore, by oversampling, the specifications on the anti-aliasing filter are relaxed and a much coarser quantizer can be used. This is because in an oversampled system, the quantization noise will be spread over a much wider range,  $[0,f_S]$  and subsequent filtering can eliminate the noise that is outside the signal band  $[0,f_N/2]$ . This results in an increased signal-to-noise-ratio (SNR). Specifically, the SNR will increase by 3 dB, every time the OSR is doubled [2].

The oversampling technique can be plainly applied to any waveform coding technique. However, coders that use oversampling usually use quantizers with fewer levels and employ an additional approach to reduce the quantization noise apart from pure oversampling. As will be seen in the next section, this is done in delta-sigma modulation by embedding the quantizer within a feedback loop. This allows the quantizer to be even more coarse (as low as one-bit) making these converters quite insensitive to circuit imperfections and component mismatch [3]. Thus, delta-sigma modulation can be viewed as a means of pushing the data-converter beyond component tolerances.

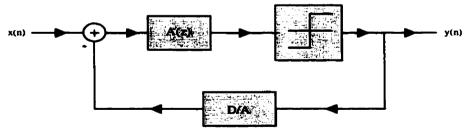

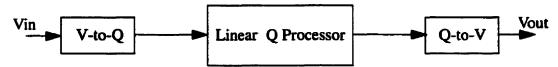

A simplified block diagram of an analog-to-digital converter that uses the delta-sigma modulation technique is shown in Figure 2.2. The analog input is first lowpass filtered to prevent aliasing from occurring when the signal is sampled at the clock rate,  $f_S$ . The delta-sigma modulator operates on the discrete time signal, x(n), producing a single-bit digital representation at the same rate,  $f_S$ . Next, the bit stream is decimated, producing a multi-bit digital word stream at the lower nyquist rate,  $f_N$ , which is now suitable for data storage or to be operated on by a DSP engine.

Figure 2.2: Elements of a Delta-Sigma Analog-to-Digital Conversion System

Next, the  $\Delta\Sigma$  modulator, which forms the core of the data-converter, will be examined in more detail.

#### 2.1.2 Basic $\Delta\Sigma$ Modulator Operation

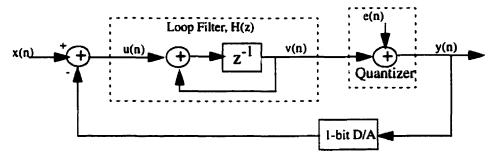

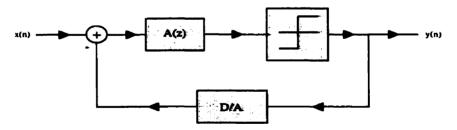

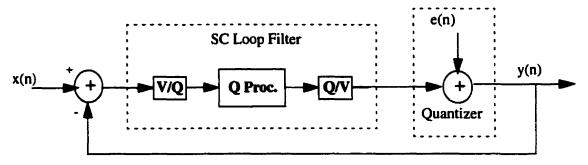

In this section we investigate how a  $\Delta\Sigma$  modulator single-bit output can effectively encode the discrete-time, multi-valued input signal. To begin, consider the DSP-level implementation of a first-order  $\Delta\Sigma$  modulator shown in Figure 2.3.

Figure 2.3: First-Order  $\Delta\Sigma$  modulator with linear model of the quantizer

It consists of an analog delay element,  $z^{-1}$ , and summer stage in an internal feedback loop forming a simple integrator, H(z). This loop filter is followed by a 1-bit quantizer which will output +/-1 depending on whether the input, v(n), is above or below a certain threshold, usually defined midway between the supply rails. This quantizer has been modeled as a simple analog summer, with e(n) representing the error made when approximating the loop filter output, v(n), by the quantizer output, v(n). The quantity e(n) is referred to as the quantization error, and leads directly to the quantization noise, to be discussed shortly.

The quantizer output which also serves as the modulator output is feed back to the input through a 1-bit D/A converter. The feedback level is then subtracted from the modulator input signal to produce u(n), the loop filter input. The 1-bit D/A is necessary so that the subtraction can occur in the same (analog) realm, but does not otherwise affect the basic signal processing.

When employing a simple one-bit quantizer, the output y(n) can be either +/- 1. Consider the simple case for a 0 V DC input, x(n). If the output level is +1, the error u(n) will be negative, and negative values will accumulate in the integrator, producing v(n). Eventually, after enough clock cycles, enough negative values will accumulate, causing v(n) to go neg-

ative and the quantizer to produce y(n)=-1. The overall input-output error has been reduced, when averaged over time, because negative errors will cancel with previous positive ones

Consider next the case for a positive DC input signal, x(n). When y(n)=1, the magnitude of the error, u(n) would be less than when y(n)=-1. Therefore it would take more clock cycles for the integrator to accumulate enough error to cause y(n) to switch from 1 to -1 than from -1 to 1. Therefore, the output y(n) will spend most of it's time at y(n)=1. Similarly, for negative input signals, y(n) will spend most of it's time at y(n)=-1. In fact, when averaged over time, the output bitstream will approximate the DC input voltage, x(n).

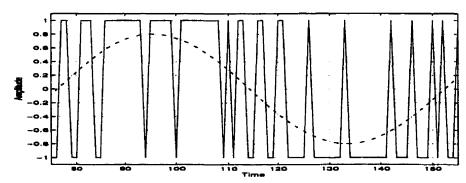

Now, consider the case where x(n) is a sinusiodal input. Following the above reasoning, there should be more high output levels when the input is positive, and more low output levels when the signal is negative. This is confirmed by Figure 2.4 which shows the input-output time domain waveforms of a  $\Delta\Sigma$  modulation system.

Figure 2.4: Input (sinusoid) and output (PDM) time-domain waveforms of a  $\Delta\Sigma M$

With the input signal superimposed on the output signal, we see that the output signal toggles between the zero and one state in such a way that the input signal is encoded into the density of the one's in the output signal. In other words, when the input signal is very near the full scale value, the output is in the high state for many clock cycles. Conversely, when the input is near the other extreme, the output is in the zero state for many clock cycles. In both cases, the local average of the modulator output tracks the analog input. When the input is near the mid-range, the value of the modulator output varies rapidly between the low and high states in almost equal proportion. This type of encoding is referred to as *Pulse Density Modulation* (PDM) [5]. By carefully averaging the output signal over many clock cycles, the input signal can be recovered as a multibit digital signal. This is the task performed by the decimator that was shown in Figure 2.2, resulting in multi-bit digital representation of the analog input.

#### 2.1.3 Time Domain Analysis

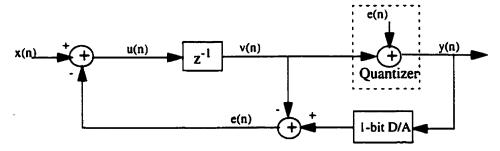

A greater understanding of the modulator operation can be achieved by examining the time domain input-output relation of the structure. This can be easily obtain if the modulator of Figure 2.3 is modified slightly, without changing the functionality what so ever. The resulting signal flow graph is shown in Figure 2.5 below.

Figure 2.5: First-order  $\Delta\Sigma$  modulator with modified signal flow graph

Referring to this modified representation of the modulator, it is easy to see that the quantization error, e(n), is being fed back and subtracted from the input signal. The time domain equation describing the circuit in Figure 2.5 can be easily found to be given by

$$y(n+1) = x(n) + [e(n+1) - e(n)]$$

(2.2)

As can be seen from Eq. (2.2), the output is the sum of the input, delayed by one clock cycle, plus the difference between the quantization error made on the current and previous cycles. Because the  $\Delta\Sigma$  modulator loop is oversampled, adjacent samples of the internal signals will be highly correlated. Therefore, we can expect near perfect cancellation of the quantization errors, improving more so if the oversampling ratio is increased.

If instead of merely feeding back the quantization made on the last clock cycle, but rather a quantity dependent on multiple past errors (i.e. e(n), e(n-1), e(n-2)...) one could obtain a better estimate the sample error that would be made on the next phase. This approach al-

lows superior cancellation of the quantization errors and is the reasoning behind building higher-order modulators. In general, an Nth-order modulator will use N previous values of the quantization error on which to base estimate of the next.

#### 2.1.4 Frequency Domain Perspective: Noise Shaping

Further insight can be obtained if the input-output relation of Eq. (2.2) is moved into the frequency domain by taking the z-transform as follows,

$$Y(z) = z^{-1}X(z) + [1 - z^{-1}]E(z)$$

(2.3)

The z-domain equation is usually analyzed in terms of the separate transfer characteristics experienced by the input signal and quantization noise. The *signal transfer function* (STF) of the above structure is given by

$$STF = \frac{Y(z)}{X(z)} = z^{-1}$$

(2.4)

indicating that the signal is only delayed in time. However, the quantization noise transfer function (NTF) is given by

$$NTF = \frac{Y(z)}{E(z)} = 1 - z^{-1}$$

(2.5)

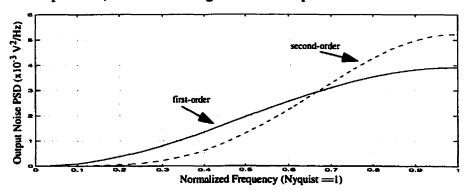

which has a transmission zero at DC. Figure 2.6 illustrates the effect of this zero on the modulator output noise power spectral density (PSD), presented theoretically in [4][8]. It can be clearly seen that the lower frequency components of the noise will be suppressed while those at higher frequencies emphasized. Thus, the noise is "shaped" out of the signal band (at low frequencies) and into the high end of the spectrum.

Figure 2.6: Output Noise PSDs corresponding to 1st and 2nd Order LP Modulators

The dashed line in Figure 2.6 illustrates the output noise PSD when a second order loop filter, H(z), is employed in Figure 2.3. Compared to the first order case, more of the quantization noise is pushed out of the signal band and into higher frequencies. This confirms the intuitive reasoning developed in the previous section. That is, in general, the higher the order of the converter, the more the noise will be shaped in the desired manner [6].

Regardless of the modulator order, the high frequency noise which occurs out of band must be removed in order to maintain signal quality. This is achieved by the subsequent lowpass filtering operation that occurs within the decimator.

As mentioned previously, the resolution of the modulator can be increased by increasing the oversampling ratio, defined in Eq. (2.1). The amount by which the SNR improves depends on the order of the modulator [5]. A general rule of thumb is that for every doubling of the OSR, the SNR will increase by 3 dB, in addition to 6 dB for every integrator in the loop filter [8]. Therefore, doubling the OSR would lead to a 9 dB increase in the SNR for a first order modulator, and 15 dB increase in the SNR for a second order converter.

#### 2.1.5 A General Modulator Structure

To conclude our overview of  $\Delta\Sigma$  modulation, consider the general (N<sup>th</sup> order) modulator of Figure 2.7 consisting of a loop filter, quantizer and DAC in a negative feedback loop.

Figure 2.7: General  $\Delta\Sigma$  Modulator Structure for A/D Conversion

In general, the quantizer need not be restricted to be a simple thresholder, as in the one-bit case. For the same OSR, multibit modulators have lower quantization noise (approximately 6 dB less per extra bit used [23]), are more easily stabilized, and ease the requirements on the decimation filter. Although this approach adds complexity to the quantizer, the major drawback comes from the D/A circuit, which must also be multi-bit to follow suit. Non-

linearities introduced from component mismatch in the multi-bit D/A circuit will lead directly to distortion at the modulator output as these errors, unlike those of the quantizer, will not be shaped by the modulator noise transfer function. Recently, however, research has emerged demonstrating that by using dynamic element matching techniques [74][75], the D/A errors can also be shaped, albeit at the expense of increased hardware. Therefore, although this work focuses on single-bit modulation, it should be noted that the multi-bit approach does show potential as well.

Referring again to Figure 2.7 and modeling the quantizer as an additive noise source allows the signal transfer function within this structure to be written as by

$$STF = A(z)/[1+A(z)]$$

(2.6)

and the noise transfer function as

$$NTF = 1/[1 + A(z)]$$

(2.7)

To design a general modulator using the above structure, one must first determine how many bits of resolution are necessary for the specific application. This can be easily translated into an SNR requirement using Eq. (2.8)[23] below

$$SNR = (6.02 \cdot N + 1.76) \ dB$$

(2.8)

The above SNR requirement will place a constraint on the maximum allowable noise in the signal band. In brief, a mathematical NTF can then be derived that achieves the noise-shaping necessary to obtain the required noise suppression and thus SNR. As will be seen in the novel design presented in Chapter 3, this NTF can then be used in establishing the loop filter, A(z). It should also be mentioned that, especially when a 1-bit quantizer is used,  $\Delta\Sigma$  modulators are highly nonlinear structures. Modeling the quantizer as an additive noise source, as usually done in practice, does not capture all its effects on the circuit. In particular, the stability of  $\Delta\Sigma$  modulators (especially those of high-order) is not well understood and is generally addressed using rules of thumb [14].

Finally, as will be seen in the work that follows, although conceptually sound,  $\Delta\Sigma$  modulators are not usually designed using the simple single-loop topology of Figure 2.7. Instead, multi-loop structures, which are better suited for circuit implementation will be used.

#### 2.2 A Second-Order LowPass $\Delta\Sigma$ Modulator

In this section, a second-order lowpass modulator design will be used as an example to demonstrate the basic  $\Delta\Sigma$  technique through from specification to a physical IC. It will set the stage for the more elaborate eighth-order design that will be investigated in Chapter 3. Furthermore, the work presented herein will also form the backbone of the  $\Delta\Sigma$  designs in Chapter 4, which use the same signal processing-level topology.

#### 2.2.1 Design Specifications

The modulator under investigation is intended for use in a voice-band analog-to-digital converter. The objective is to obtain at least 13-14 bits of resolution (or approximately 80 dB SNR) over the 0-4 kHz band.

The maximum expected SNR for a  $\Delta\Sigma$  modulator can either be derived theoretically by modeling the quantization errors as an additive white noise source, as detailed in [5][8], or through empirical analysis, as described in [6]. Referring to the latter work, it was found that by using a 2nd-order modulator with coincident NTF zeros<sup>1</sup> and OSR of 128, up to 85 dB SNR can be expected. An OSR of 128 with inputs up to 4 kHz requires that the system be clocked at approximately 1 MHz, which is reasonable for the given technology. Therefore, a second-order modulator is well-suited to meet the intended specifications.

#### 2.2.2 SFG-Level Design

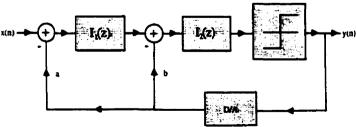

Figure 2.8 shows the most popular topology for a second-order  $\Delta\Sigma$  modulator, which is well documented in the literature [71].

Figure 2.8: Two-Integrator Loop Topology

<sup>1.</sup> Alternatively, the NTF zeros could be spaced throughout the passband, though this will only improve the SNR by approximately 5 dB in the relatively low-order design of this chapter

It consists of two integrator loops with feedback coefficients, a and b, selected in such a way so as to ensure stability. The integrators,  $I_1$  and  $I_2$ , may each either be delayed or non-delayed. Each combination has its own advantages and disadvantages. These will be discussed in the design of Chapter 3, where the implications are more severe. For these relatively low speeds and performance requirements, however, the choice is not crucial and we follow the approach used in [3]. That is, both integrators will be of the delayed type.

The resulting signal and noise transfer functions are given in Eqs. (2.9) and (2.10) below

$$NTF = \frac{(z-1)^2}{z^2 + (b-2)z + (1+a-b)}$$

(2.9)

$$STF = \frac{1}{z^2 + (b-2)z + (1+a-b)}$$

(2.10)

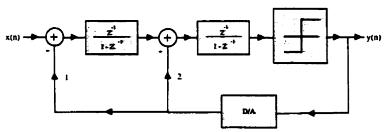

The corresponding SFG block level diagram is shown in Figure 2.9, with a=1 and b=2.

Figure 2.9: SFG level representation of the delayed, delayed combination

With his choice of feedback coefficients, the signal will propagate unaffected through the modulator in two clock cycles, while the quantization noise will be shaped according to the noise transfer function shown in Figure 2.10

Figure 2.10: (a)Pole-Zero and (b) Frequency Response Plots of NTF for a=1, b=2

Although this does produce the desired noise shaping, the structure of Figure 2.9 is not best-suited for implementation. One reason for this is that the signal range required at the outputs of the two integrators is several times the maximum input range. This can represent a problem in VLSI circuit technologies where the dynamic range is limited. This effect can be avoided by slightly modifying the DSP representation to that shown in Figure 2.11 [3]. As will become apparent shortly, this representation also lends itself more easily to implementation than does the original of Figure 2.9.

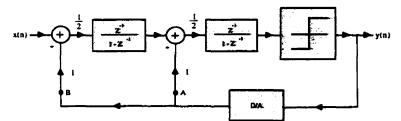

Figure 2.11: Alternate representation of the delayed, delayed combination

Referring to Figure 2.11, note that the feedback from point A to the output passes through one scaling factor of a half. However, the feedback from point B and the input both pass through two scaling factors of a half. Thus the feedback in the branch containing the point A is effectively twice that of the other branch, as in the original representation of Figure 2.9.

Before investigating IC realizations, design of Figure 2.11 was verified using Simulink, a SFG-level simulator. The circuit was stimulated with a sinusoid, whose frequency was carefully choose to ensure coherent sampling. The output PDM bitstream was sampled at a rate of one bit per clock cycle (1.024 MHz), for 32768 (2<sup>15</sup>) cycles. Next, matlab was used to preform the FFT analysis, producing the spectra shown in Figure 2.13(a) with an equivalent resolution of 31 Hz/bin.

Figure 2.13: Results of SFG-Level Simulation using Simulink

The maximum SNR in the 0-4 kHz bandwidth (corresponding to an OSR of 128) was found to be 86 dB.

In addition, this relatively fast simulator was used to investigate the behavior of the modulator for various input levels. The results are summarized in Figure 2.13(b). Initially, as the input level increases, the SNR follows suit, due to the increase in signal power. However, as the input approaches the feedback reference level of 0 dB, the SNR drops off rapidly. This behavior is typical to  $\Delta\Sigma$  modulators and is due to stability problems which occur when large input voltages are allowed to accumulate in the integrators of the loop filter. The plot of Figure 2.13(b) illustrates that the modulator is useful in processing signals within a 90 dB dynamic range, that is the range in which the modulator attains a positive SNR.

#### 2.2.3 Switched-Capacitor Realization

The switched-capacitor (SC) technique was chosen to implement the design due to its robustness, high degree of accuracy, and IC reusability. Because mixed-signal ICs suffer from relatively high noise, a fully differential SC implementation was used as it is less susceptible to electronic noise when compared with the single-ended implementation.

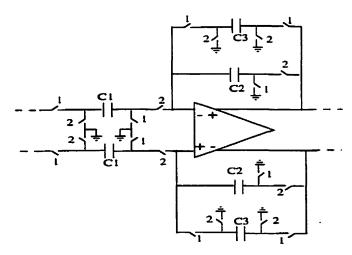

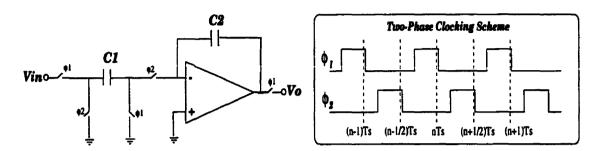

To map the SFG-level structure onto a SC design, each integrator in Figure 2.11 is directly realized by a conventional multi-input, stray-insensitive SC integrator of the delayed (non-inverting) type as shown in Figure 2.14(a).

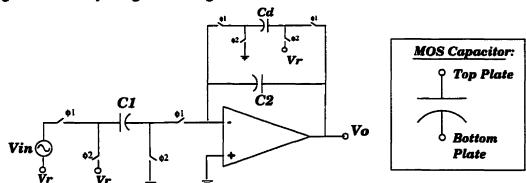

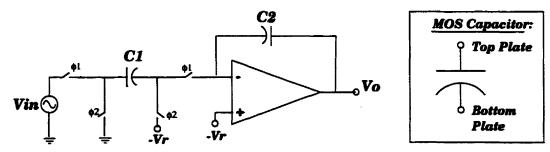

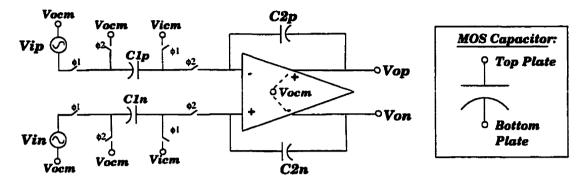

Figure 2.14: Lowpass Modulator Implementation

The switches are controlled by a two-phase non-overlapping clock whose phases are shown adjacently in Figure 2.14(b). The short time where both phases are low is necessary to avoid charge sharing in SC circuits. Feedback is implemented by the shaded sections, where the ratios of  $(C_1/C_2)=1/2$  and  $(C_3/C_2)=1/2$  specify the a and b coefficients respectively. The one-bit D/A block of Figure 2.11 is easily realized by switching in a positive or negative reference voltage, depending on the quantizer output level.

At this point, one advantage of the decision to use two delayed-type integrators in the SFG-level design becomes apparent. In this configuration, the amplifier  $A_1$  is being driven at the beginning of  $\phi_2$ , and has its output sampled at the end of  $\phi_1$ . Therefore, on any given phase, the amplifier  $A_1$  has only to settle an input transient or drive its capacitive load, but never both simultaneously. Had this integrator been non-delayed, the amplifier would have been driven at the beginning of  $\phi_1$ , and the output would have been sampled at the end of that same  $\phi_1$ , placing greater demand on the amplifier speed.

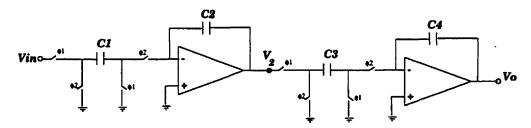

Another benefit of opting for the SFG-level design of Figure 2.11 is that, because  $C_1=C_3$  in the corresponding implementation of Figure 2.14, the SC circuit can be optimized to

make more efficient use of the available silicon area. This can be accomplished by switch and capacitor sharing, as follows. Referring to Figure 2.14 and following the path from the label 'A' to the input of the second amplifier, one sees a switch controlled by  $\phi_2$ , a capacitor of value  $C_1$ , and another switch controlled by  $\phi_2$ , with switches controlled by  $\phi_1$  on either side of  $C_1$ . This is also true when following the path from the label 'B' to the input of this amplifier. Thus the whole feedback structure in the shaded area can be eliminated and node A can be connected to node B. This is also true for the other three shaded feedback structures. In addition, the D/A switches feeding analog  $V_{ref}$  and  $-V_{ref}$  can also be shared since they perform the same function. Combining all of the above changes results in the circuit shown in Figure 2.15.

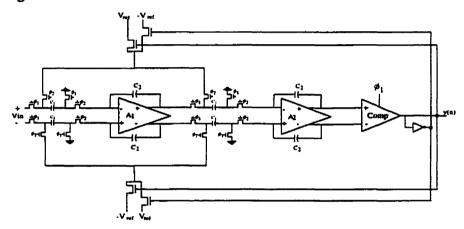

Figure 2.15: Area-efficient SC Modulator Implementation

After verifying the above topology using Switcap[68], a discrete-time simulator, the next task was to implement the SC design at the transistor-level.

## 2.2.4 Circuit Implementation

This section provides a brief discussion of how each of the components used in the schematic of Figure 2.15 is implemented using a BiCMOS technology.

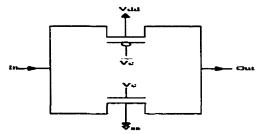

# (i) Amplifier and Comparator Circuits

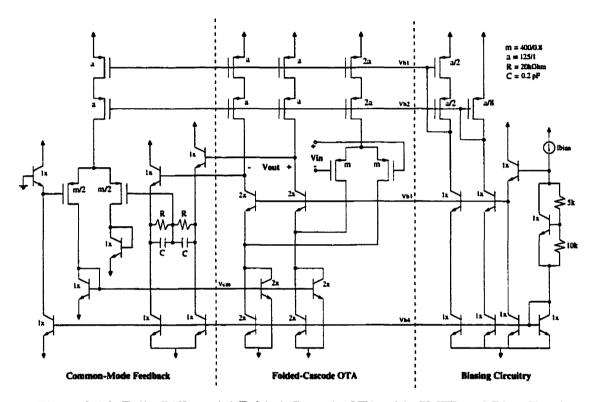

The amplifier used in realizing the SC implementation was obtained from designers at Carleton University, where it was originally used in a similar bandpass application [7]. The

transconductance amplifier schematic is shown in Figure 2.16 where it can be seen that the design uses a folded-cascode topology. The pmos transistors of the input differential-pair provide a high input impedance and low 1/f noise, while the npn cascode transistors set the non-dominant pole near their unity gain frequency. The amplifier uses continuous-time CMFB circuitry to set the output DC level at analog ground. When compensated with 1pF load capacitors, the amplifier achieves a DC gain of 57 dB, a unity-gain frequency of 500 MHz, and a slew-rate of 1000 V/µs.

Figure 2.16: Fully-Differential Folded-Cascode OTA with CMFB and Bias Circuity

The comparator shown in Figure 2.15 can be realized simply by using the opamp in an open-loop configuration, followed by inverters to boost the gain. In addition, a D-type flip-flop can be used to provide the latching mechanism at the quantized output.

The performance of the amplifier is more than sufficient for the 1 MHz speed of this design. For the high-speed design of Chapter 3, however, capacitive loading will become a significant issue and will need to be investigated further.

## (ii) Switches

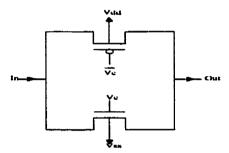

The switches were realized using two-transistor transmission gates as shown in Figure 2.17. One benefit of this approach is that it increases the range of allowable signal levels in the circuit. For example, consider a singular nmos switch with a controlling voltage that swing between the  $\pm$ -2.5 volt rails. If a signal level of 2 V appears at the source of the nmos switch, the V<sub>GS</sub> drop would be insufficient to conduct the signal. However, unlike a simple nmos switch, the transmission cell will always conduct when the controlling voltage (V<sub>C</sub>) is positive. Specifically, if the node voltage at the source is such that the nmos does not conduct, it is guaranteed that the pmos will.

Figure 2.17: Transmission Cell

Another advantage of the transmission gate is that it can be carefully sized to control charge injection (CI). This effect can sometimes have a serious impact on SC circuit performance. However, at the speeds and precision required for this second-order modulator, CI was not a significant issue. Therefore, this topic will be further investigated in the more elaborate design of Chapter 3, where it plays an important role.

The transmission gate was simulated in HSPICE and found to have an on-resistance of 3.5k Ohms and off-resistance of 250 G Ohms. Considering that the capacitors will typically be in the picofarad range, the time constant during conduction will be on the order of nanoseconds. This effect is therefore not a concern in this design which is clocked at a frequency of 1 MHz.

### (iii) Clock Phase Generator

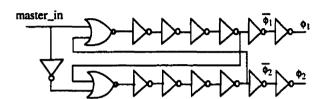

The SC design to be implemented requires 4 clock phases. Of these, two are the non-over-lapping controls,  $\phi_1$  and  $\phi_2$ . In addition, their inverses are also needed to control the transmission gates. To produce these four phases from a single master clock, the well-known structure of Figure 2.18 was used. It is composed of an SR latch stretched out by an even number of inverters after the NOR gates. The length of the non-overlapping period is determined by the number of inverters in the feedback loop of the latch.

Figure 2.18: Schematic of Clock Phase Generator

## (iv) Capacitors

The capacitors were formed by two layers of polysilicon available in the  $0.8\mu$  BiCMOS process used. Therefore, their linearity was not a concern in achieving the accuracy of this design. The actual sizes used were 1 pF and 2 pF for  $C_1$  and  $C_2$ , respectively. They were chosen to be in the wide range where neither settling, charge-injection, or kT/C noise would become a serious issue. The exact choice is not critical at these speeds but will become significant for the high-speed design of Chapter 3, where it will be discussed in detail.

## 2.2.5 Experimental Results

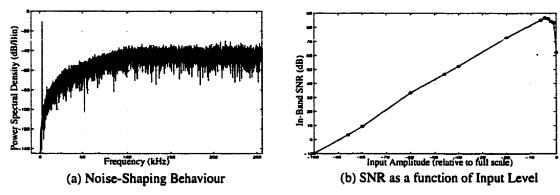

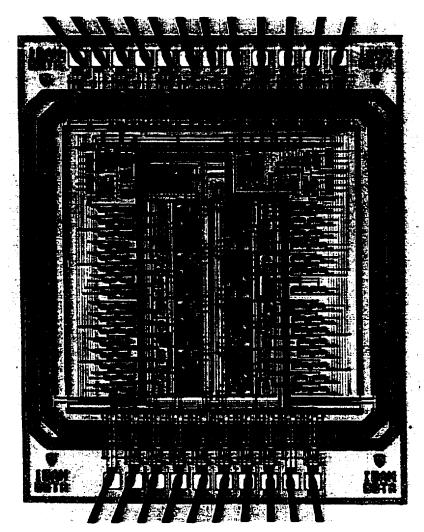

Once the circuit was determined to function correctly through HSPICE simulations, the circuit layout was performed using a 0.8µ BiCMOS technology. The design was fabricated and the chip photomicrograph is shown in Figure 2.19.

Figure 2.19: Chip Photomicrograph of Second-Order Lowpass  $\Delta\Sigma$  Modulator

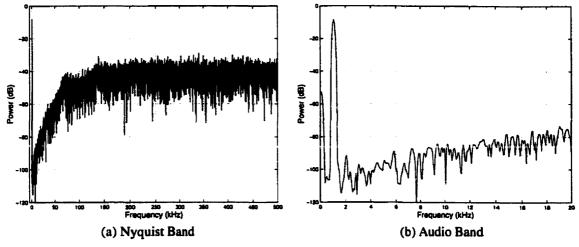

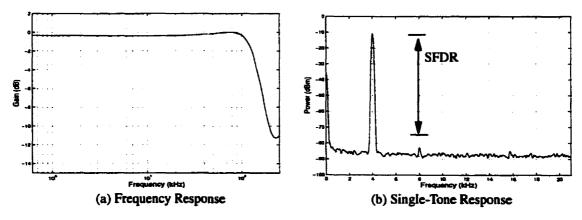

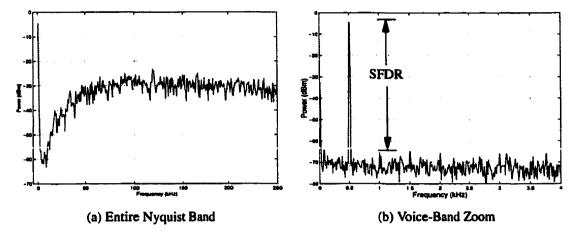

The chip occupies an active area of  $0.51 \mu m^2$  and consumes approximately 75 mW of power when clocked at a frequency of 1 MHz. Figure 2.20 illustrates the experimental results obtained from the prototype IC. A sinusoid in the voice-band was used as stimulus to the circuit and the output bit stream was captured digitally. Matlab was then used to perform a FFT analysis. The Nyquist band plot of Figure 2.20(a) is a result of 16384 (2<sup>14</sup>) point FFT analysis (corresponding to a resolution of 61 Hz/bin) and clearly shows the quantization noise is being shaped as expected. The audio band zoom of Figure 2.20(b) reveals an additional tone at DC resulting from offset voltages in the lowpass modulator. This behavior is

expected and will not adversely affect the converter performance, as audio and voice band applications do not extend in frequency to DC.

Figure 2.20: Experimental Results of the Fabricated IC

Over the voice-band, the peak signal-to-noise ratio (SNR)<sup>1</sup> was computed and found to be 82 dB, equivalent to approximately 13 bits of resolution. For input levels resulting in this peak SNR, the modulator achieves a spurious-free dynamic range (SFDR)<sup>2</sup> of 83 dB, limited by the third harmonic frequency component, visible in the audio-band output spectrum of Figure 2.20(b). The physical modulator therefore meets the design specifications outlined in Section 2.2.1 and is well-suited for the intended voice-band applications.

# 2.3 Conclusion

In this Chapter, the basic concepts of lowpass  $\Delta\Sigma$  modulation for analog-to-digital conversion have been presented. A second-order voice-band modulator has been used to illustrate the basic design process from specification through to layout. Experimental results indicate the modulator is functioning correctly, and meets the desired specifications. We are now well prepared to investigate the novel eighth-order bandpass design of Chapter 3.

<sup>1.</sup> SNR defined as the ratio of the input power to the integrated noise floor over the signal band

SFDR defined as the ratio of the input power to the peak non-signal spectral component in the signal band (0-4kHz)

# Chapter 3 : A Novel High-Order Bandpass $\Delta\Sigma$ Modulator

This chapter begins with an introduction to the bandpass modulation concept and its merits. The step-by-step approach that was used to design an eighth-order bandpass modulator will then be described. Implementation and layout considerations will prove be to key to overall performance and will be examined in detail. The methods used to test the modulator throughout the design process will also be investigated. The chapter will conclude with experimental results from a fabricated prototype.

# 3.1 The Bandpass Approach

Recall from Chapter 2 that a general  $\Delta\Sigma$  modulator has the structure shown in Figure 3.1, repeated here for convenience.

Figure 3.1: General Modulator Structure

In the previous lowpass case, the loop filter, A(z), was chosen so that the NTF shaped the quantization noise outside of the low frequency band. However, A(z) can be conveniently

#### Chapter 3: A Novel High-Performance Bandpass $\Delta\Sigma$ Modulator

chosen to shape the noise out of any desired band of operation. For example, one technique is to apply the lowpass-to-bandpass transformation described by Eq. (3.1) to the loop filter.

$$z \to -z^2 \tag{3.1}$$

This approach can be used without altering the stability characteristics of the modulator whatsoever[7]. That is, if the lowpass modulator is stable, so will be the bandpass equivalent. Applying this to the simple first order lowpass modulator of Section 2.1.3 yields the following signal and noise transfer functions:

$$NTF = (z^2 + 1)/z^2 (3.2)$$

$$STF = -1/z^2 \tag{3.3}$$

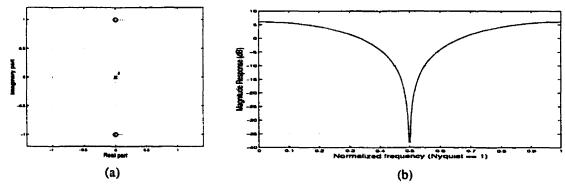

As can be seen, the STF consists only of a a simple inversion and two pure delays. Therefore, it has linear phase and can be easily reconstructed without distortion. The new NTF, however, is vastly different and is shown in Figure 3.2.

Figure 3.2: (a) pole-zero and (b) magnitude response plots of a BP NTF

Note that the NTF zeros are now centered about half the Nyquist frequency, not zero. Therefore, this modulator would be well suited to operate on signals with frequencies of one fourth the sampling rate.

The advantage of choosing a bandpass modulator over its lowpass counterpart comes when working on high frequency signals in a narrow bandwidth. With a bandpass modulator, it is only necessary to remove the noise from the narrow signal bandwidth, keeping the oversampling ratio (defined in Eq. (2.1)) high. This is because noise can be pushed onto both

sides of the band of interest. With a lowpass modulator on the other hand, the noise would need to be shaped out of the entire region  $[0,f_{SIG}]$ . Therefore the operational bandwidth would be much larger and the effective OSR greatly reduced. The only drawback of the bandpass approach is that for the same degree of noise shaping as a lowpass modulator, double the order is required. This is because each NTF pole and zero must have a complex conjugate in order to avoid having complex co-efficients in the loop filter.

In theory, delta-sigma modulators can be extended to an arbitrary high-order [6], to meet the continuously increasing requirements imposed on present-day A/D converters. Provided stability is achieved, high-order modulators have the advantage that the resolution and/or bandwidth obtained is considerably higher than low-order ones. Bandpass modulators allow the extension of these benefits to narrowband signals centered at higher frequencies. They are thus prime candidates for use in receiver front-ends, converting IF signals directly to digital form.

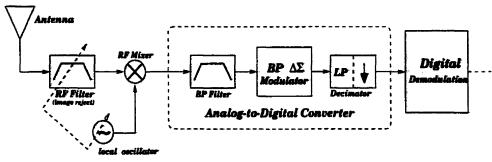

The eighth-order bandpass modulator design of this chapter is intended to meet the A/D conversion needs in the increasingly popular area of digital RF receivers. As depicted in Figure 3.3, the bandpass modulator is the key component in the A/D system that is used to convert the IF signal of a superheterodyne receiver directly to digital form. Any further processing, such as IF filtering and demodulation can now be handled digitally. This scheme makes the system more versatile, as the digital hardware can easily adapt to changing communication protocols. Furthermore, this approach does not suffer from DC offset and low frequency noise problems (when compared to mixing and lowpass conversion) and there is no I/Q mismatch in the quadrature demodulation since this step is performed in the digital domain[10].

Figure 3.3: Simplified Digital RF Receiver

# 3.2 Modulator Design

This section will first briefly outline the specifications and goals of the design. A step-by-step procedure will then be given, outlining the design procedure that was followed.

## 3.2.1 Design Objectives

To address the need of digital radio, the modulator is designed to operate on signals within a 200 kHz bandwidth, centered at the commonly used IF of 10.7 MHz. When the IF signal band is centered at  $f_S/4$ ,  $f_S$  being the clocking frequency, the circuit must be clocked at 42.8 MHz. However, because a high-order modulator is employed, it is also possible to centre the IF band at  $3f_S/4$ , allowing for either one third the clock rate (easing decimation), or processing of signals three times higher in speed (IF band centered at 32.1 MHz) while still achieving excellent results.

To achieve the high resolution required in modern-day wireless systems, an eighth-order modulator was chosen. Combined with the OSR of 107, derived from the above bandwidth and clock speed, a theoretical resolution of over 20 bits should be possible [6].

In addition to obtaining a working prototype of a future application, these ambitious design constraints will serve another purpose as well. The work will verify and further the design methods of high-order modulators; and help to understand and solve some of the problems encountered with them.

## 3.2.2 NTF Design for Desired Specifications

The mathematical expression for the NTF was established using DSMOD, a software tool developed at McGill for the design of  $\Delta\Sigma$  modulators [11]. By specifying the modulator's passband, OSR, and various other parameters, the program produces an optimal NTF (butterworth with optimally placed zeros) which is a compromise between stability and SNR. The resulting NTF is given by Eq. (3.4) below.

$$NTF_{DSMOD}(z) = \frac{N_{DSMOD}(z)}{D_{DSMOD}(z)} = \frac{1 + 3.99926z^2 + 5.99852z^4 + 3.99926z^6 + z^8}{0.396502 + 1.9497z^2 + 3.646z^4 + 3.08274z^6 + z^8}(3.4)$$

#### Chapter 3: A Novel High-Performance Bandpass ∆∑ Modulator

The expected specifications of a modulator characterized by the NTF of Eq. (3.4) are detailed in Table 3.1 which follows:

| Specification           | Value    |  |

|-------------------------|----------|--|

| Order                   | 8        |  |

| Center Frequency        | 0.250000 |  |

| Oversampling Ratio      | 107.000  |  |

| Lower passband Edge     | 0.247664 |  |

| Upper passband Edge     | 0.252336 |  |

| Bound on NTF            | 1.60000  |  |

| Optimal Input Amplitude | 0.50000  |  |

| Maximum NTF Magnitude   | 1.58781  |  |

| Expected SNR (estimate) | 128.276  |  |

Table 3.1: Theoretical Modulator Specifications

One parameter that appears in Table 3.1 which has yet to be introduced is the NTF Bound. It specifies the maximum allowable level of the NTF amplitude. This factor plays an important role in ensuring the overall stability of the modulator. Specifically, the NTF bound is typically limited to a threshold determined by one of the many rules of thumb[6]. The DSMOD design program also attempts various NTF bounds and input signal amplitudes and returns with the NTF, the NTF bound, and the input level that maximize the SNR for the given specifications.

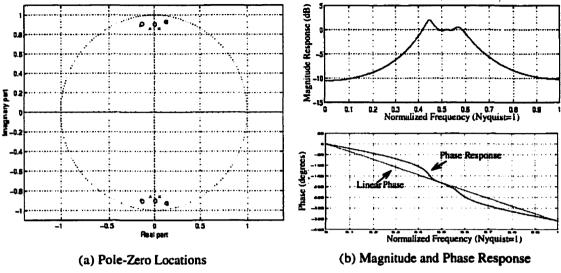

The corresponding pole-zero locations and magnitude response are shown in Figure 3.4, where the four NTF zeros and associated notches are clearly visible.

Figure 3.4: Pole-Zero and Magnitude Response Plots of NTF using DSMOD

It should be noted that the location of the poles in the design of the NTF for  $\Delta\Sigma$  modulators is a compromise between stability and SNR. Placing the poles well inside the unit circle (i.e. close to the origin) will result in deep notches in the signal band (as a result of the zeros) and give excellent noise reduction there. However, remembering that the total noise power is constant, the noise outside the signal band will have to rise and will often exceed the practical stability limit of 2, proposed by Lee in [14] resulting in an unstable modulator. On the other hand, placing the poles too close to the zeros will ensure stability but decrease SNR as the noise in the signal band will rise due to the closely placed poles. Therefore, it is for this reason that an optimal location of the poles and zeros is usually found for a given NTF bound, as with the case of DSMOD.

As the current version of DSMOD is intended for  $\Delta\Sigma$  oscillator applications, the STF returned by DSMOD is unfortunately restricted to be unity. As will become evident, this is neither a necessary nor desirable feature when the modulator is implemented with the SFG-level structure that follows. For this reason, the STF was designed separately as will be discussed in Section 3.2.5. However, the STF, does have the same denominator as the NTF (recall Eq. (2.6)), which considerably restricts the STF design.

## 3.2.3 Selecting a Structure

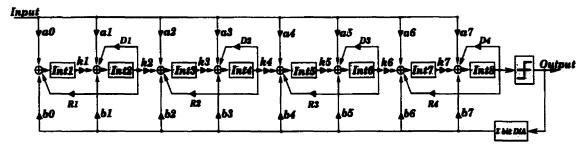

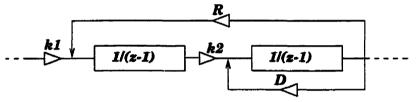

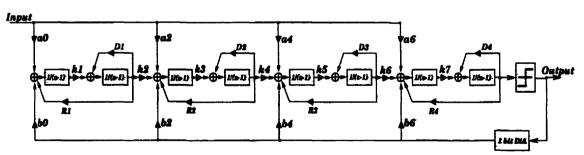

The next step in the design is to determine the physical structure that will implement the theoretical NTF and best meet the demands placed on the hardware such as matching accuracy and speed requirements. To begin, the fourth-order structure given in [12] can be extended to yield the general eighth-order structure shown in Figure 3.5.

Figure 3.5: General Eighth-Order  $\Delta\Sigma$  Modulator Structure

#### Chapter 3: A Novel High-Performance Bandpass $\Delta\Sigma$ Modulator

It is composed of a cascade of resonators, easily realizable in the SC technique, each forming an NTF complex zero pair. The local feedback paths weighted by the  $R_i$  and  $D_i$  coefficients (for i=1...4) specify the locations of these NTF zeros. The remaining feedback paths, from the output of the comparator, scaled by the  $b_i$  coefficients (for i=0, 1,...7) are used in conjunction with the above  $\bf R$  and  $\bf D$  coefficients (boldface is used to denote vector quantities) to define the NTF and STF pole's locations. Finally, the  $\bf a$  coefficients ( $a_0...a_7$ ) are used to establish the STF zeros, while the  $\bf k$  coefficients ( $k_1...k_7$ ) are used in scaling for maximum dynamic range.

One attraction of the above structure is that, being composed primarily of integrators, it lends itself quite easily to SC implementation. However, it has yet to be determined whether the integrators are of the delayed (non-inverting) or non-delayed (inverting) type. As will be discussed next, this small change in phasing can have a major impact on performance.

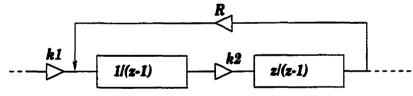

## (i) The Lossless Digital Integrator (LDI) Structure

This popular structure used in [7] is one in which each second order section is composed of a LDI two-integrator-loop topology. That is the first and second integrators would be of the delayed and non-delayed types respectively, as shown in Figure 3.6.

Figure 3.6: LDI Two-Integrator-Loop Topology

Each of the coefficients in Figure 3.6 directly represents a capacitor ratio when the LDI loop is implemented using the SC technique. The transfer function of this second order block is given as:

$$A(z) = \frac{k_1 k_2 z}{z^2 - (2 + k_2 R)z + 1}$$

(3.5)

The poles of this second order section will determine the NTF zeros in the overall structure, and are therefore crucial in achieving a high inband noise suppression. From Eq. (3.5), it

## Chapter 3: A Novel High-Performance Bandpass $\Delta\Sigma$ Modulator

can be seen that the poles will lie on the unit circle, regardless of any capacitor mismatches, represented by  $k_1$  and  $k_2$ . This is advantageous because it ensures that a deep notch will always exist in the overall NTF. However, note that  $k_2$  can affect the phase angle of the poles of A(z), and thus shift the frequency of the notch slightly.

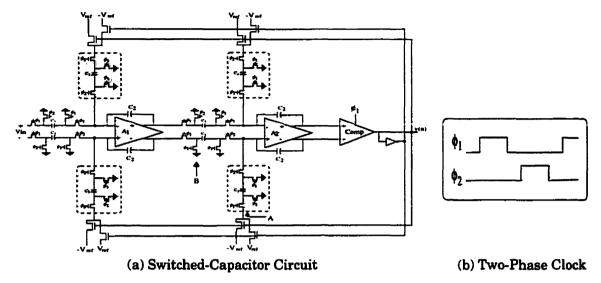

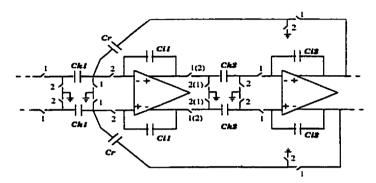

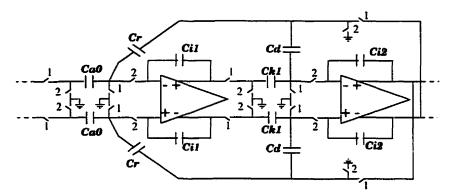

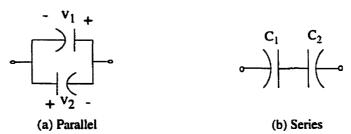

To understand the speed constraints this structure places on the amplifiers, refer to the SC implementation shown in Figure 3.7, ignoring at this point the parenthesized clock phases.

Figure 3.7: LDI and modified LDI (parenthesized clock phases) SC topologies

First note that the structure has a differential implementation, as will all the candidates under study. This is to cancel, to first order, the noise that the digital circuitry adds through the substrate. The integrators used are parasitic insensitive, and switch-sharing has been used in the usual manner. In the above, the capacitor ratio  $C_k/C_{i1}$  forms the coefficient  $k_1$ , the ratio  $C_r/C_{i1}$  forms the ratio R, etc.

Referring to Figure 3.7, it is clear that on clock phase  $\phi_1$ , the first amplifier must drive a load entering the second amplifier, which inturn must simultaneously settle the input transient and drive it's own load. This has a second order transient behavior due to the coupling of the two sections, an thus exhibits very poor settling[7].

# (ii) The Modified LDI Structure

The modified LDI structure attempts to overcome the above mentioned problem associated with the basic LDI topology. There is a subtle change in the second integrator phasing, as seen in Figure 3.7.

#### Chapter 3: A Novel High-Performance Bandpass ΔΣ Modulator