## Lateral Epitaxial Growth of Ge films on Si via a Vapor-Liquid-Solid Mechanism

## Weizhen Wang

Department of Mining and Materials Engineering

Faculty of Engineering

McGill University

Montreal QC Canada

June 19, 2018

A thesis submitted to McGill University in partial fulfilment of the requirements of the degree of Doctor of Philosophy

#### **Abstract**

In recent years, there has been an increasing interest in developing alternative semiconductor materials since traditional Si-based devices have approached their physical limits. Given that Si has many advantages over other materials as substrate, the use of Si wafer is expected to continue. It is therefore important to grow high-quality semiconductor materials, e.g., thin films or nanowires, epitaxially on Si. The past thirty years have seen rapid advances in the field of heteroepitaxial Ge growth on Si because Ge-based devices can add functionality to Si chips and may be the key to enable next-generation computer systems or solar cells. The direct growth of Ge on Si, however, suffers from high-density threading dislocations that are formed during the growth process; these defects act as scattering and recombination centers that degrade the device performance.

In this thesis, a novel growth approach, metal-catalyzed, lateral epitaxial growth, is demonstrated to grow Ge films on Si with reduced threading dislocation density (TDD). In contrast to the traditional blanketed film growth on Si, this technique starts with a small crystal nucleation at a specific position on Si followed by a Ge lateral growth in the horizontal direction. It has been hypothesized that during the lateral growth process the lattice mismatch between Si and Ge can be accommodated by the extension of the preexisting misfit dislocations from the initial growth region or the nucleation of dislocations from the film sidewalls instead of generating additional threading dislocations from the film surface.

In this thesis, SEM and TEM were two primary characterization techniques to study the film morphologies, the growth process, and the relaxation mechanisms. One important finding was that the first nucleation areas of the films often have a higher Si concentration or may be thinner compared to the lateral overgrowth areas. This is important because such differences made it possible to figure out where the first growth occurred in electron microscopy. From here we could compare the dislocation morphologies in different areas. In plan-view and cross-sectional

TEM micrographs, high-density threading dislocations were found to be present in the initial growth areas while the lateral overgrowth areas demonstrated substantially reduced TDD or even defect-free areas. Moreover, the XRD results showed that the Ge films were almost fully relaxed with little Si incorporation. Given that the growth occurred at a low temperature, 375-500 °C, we suggest the presence of new relaxation mechanism since the previous mechanism, dislocation nucleation and glide, would require a much higher temperature to fully relax the lattice mismatch strain. Therefore, we hypothesize that the strain induced by the lattice mismatch can be relaxed by extending the preexisting misfit dislocations and that lateral growth can "build in" dislocations as it grows.

Furthermore, this thesis proposes a simple model to describe the relation between the catalyst (Au) area and the area of the film in plan-view SEM; a film's size can thus be estimated by the size and shape of the Au catalyst. It has been found that a large Au catalyst can absorb more Ge due to its larger vapor-liquid interface, but more Ge is required to saturate the Au. This thesis also presents a study of the optimum growth condition of Ge lateral growth. The results show that high temperature and high GeH<sub>4</sub> partial pressure can boost the growth rate and thus increase the film size within a specified period of time. However, high growth rate can cause more uncatalyzed, vapor-solid Ge growth on Si as well. A relatively lower growth rate and a longer growth time are thus required to simultaneously increase the size of the films and reduce the uncatalyzed growth.

#### **Sommaire**

Au cours des dernières années il y a eu un intérêt croissant dans le développement de matériaux semi-conducteurs alternatifs dans la mesure où les dispositifs traditionnels à base de Si ont atteints leurs limites physiques. Le Si présentant de nombreux avantages par rapport aux autres matériaux en tant que substrat, l'utilisation de supports en Si devrait se poursuivre. Il est donc important de développer des matériaux semiconducteurs de haute qualité, comme par exemple des films minces ou des fils nanométriques, par épitaxie sur Si. Les trente dernières années ont vu des progrès importants dans le domaine de la croissance hétéro-épitaxiale du Ge sur Si, car les dispositifs basés sur le Ge peuvent ajouter une fonctionnalité aux puces au Si et peuvent être la clé pour développer la prochaine génération de systèmes informatiques ou de cellules solaires. Toutefois, la croissance directe de Ge sur le Si est impactée par une forte densité de dislocations vis qui se forment au cours du processus de croissance. Ces défauts agissent comme des centres de diffusion et de recombinaison qui dégradent les performances du dispositif.

Dans ce manuscrit, une nouvelle approche de croissance, la croissance épitaxiale latérale, catalysée par un métal, est démontrée pour la culture des films de Ge sur Si avec une densité de dislocations vis (DDV) réduite. Contrairement à la croissance traditionnelle du film recouvert de Si, cette technique débute par une légère nucléation cristalline à une position spécifique sur le Si suivie par la croissance latérale du Ge dans la direction horizontale. Il est supposé que durant le processus de croissance latérale, la différence entre les paramètres de maille du Si et du Ge peut être compensée par l'extension des dislocations préexistantes de la région de croissance initiale ou par la nucléation de dislocations des parois latérales du film au lieu de générer des dislocations vis supplémentaires à la surface du film.

Dans ce manuscrit, les techniques de caractérisation par microscopie électronique à balayage (MEB) et par transmission (MET) ont été utilisées pour étudier les morphologies du film, le processus de croissance et les mécanismes de relaxation. Il a été démontré que les premières

zones de nucléation des films avaient souvent une concentration de Si plus élevée ou pouvaient être plus minces par rapport aux zones de surcroissance latérale. Ces observations sont importantes car de telles différences ont permis de localiser, par microscopie électronique, la région où la croissance a débuté. À partir de cela, nous avons pu comparer les morphologies des dislocations dans différentes zones. Dans les images prises en MET en vue plan et en coupe, une forte densité de dislocations vis s'est avérée être présente dans les zones de croissance initiale alors que les zones de surcroissance latérale présentaient des zones de DDV sensiblement réduites ou même exemptes de défauts. De plus, les résultats obtenus par Diffraction des rayon X (DRX) ont montré que les films de Ge étaient presque complètement relaxés avec une faible incorporation de Si. Étant donné que la croissance s'est produite à basse température, 375-500 °C, nous suggérons la présence d'un nouveau mécanisme de relaxation puisque le mécanisme précédent, c'est-à-dire la nucléation et le glissement des dislocations, nécessiterait une température beaucoup plus élevée pour relaxer complètement l'élongation du réseau. Par conséquent, nous émettons l'hypothèse que la déformation induite par la différence de mailles peut être relâchée en étendant les dislocations préexistantes et que la croissance latérale peut "générer" des dislocations au fur et à mesure de sa croissance.

De plus, cette thèse propose un modèle simple pour décrire la relation entre la zone du catalyseur (Au) et la surface du film en vue plan par MEB; la taille d'un film peut ainsi être estimée par la taille et la forme du catalyseur d'or. Il a été constaté qu'un catalyseur d'or de grande taille peut absorber plus de Ge en raison de sa plus grande interface vapeur-liquide, mais qu'une plus grande quantité de Ge est nécessaire pour saturer l'or. Cette thèse présente également une étude des conditions optimales pour la croissance latérale du Ge. Les résultats montrent qu'une température et une pression partielle élevées de GeH4 peuvent augmenter le taux de croissance et ainsi augmenter la taille du film dans une période de temps spécifiée. Cependant, un taux de croissance élevé peut également provoquer une croissance vapeur-solide non catalysée de Ge sur le Si. Un taux de croissance relativement plus faible et un temps de croissance plus long sont donc nécessaires pour augmenter simultanément la taille des films et réduire la croissance non catalysée.

### **Acknowledgments**

Firstly, I would like to thank my supervisor Prof. Nate Quitoriano for his continuous support for my PhD study and the research work, for his patience, motivation, and immense knowledge. His guidance helped me all the time during the doctorate study period.

Besides my advisor, I would like to sincerely thank all my research group colleagues, Jerome LeBoeuf, Alexandre Horth, Andrew O'Reilly, Jun Wang, Han Wang, and Moshen Keshavarz, for their important and useful discussion on research, support, and encouragement. My special thanks go to Jerome LeBoeuf, who designed and developed a micro-fabrication process for micro-crucible, and who trained me on the use of the equipment in the McGill Nanotools Microfab.

My sincere thanks also go to Prof. Oussama Moutanabbir, Samik Mukherjee, Simone Assali, and Nima Nateghi, who provided me an opportunity to join their team, and who allowed me to use their MOCVD system and other research facilities. Without their support, it would not be possible to carry out this research.

I also would thank the staff at the McGill Nanotools Microfab, Don Berry, John Li, Sasa Ristic, Zhao Lu, Peng Yang, Alireza Hajhosseini Mesgar, for their advice, support, and knowledge. I also would like to thank David Liu, Nicolas Brodusch, and Frédéric Voisard for their help in electron microscopy.

I would like to thank McGill University and NSERC for funding this project.

Last but not the least, I would like to thank my family: my parents, Zisheng Wang and Min Qin, for supporting me spiritually throughout writing this thesis and my life in general.

## **Table of Contents**

| Abstract                                                | i     |

|---------------------------------------------------------|-------|

| Sommaire                                                | iii   |

| Acknowledgments                                         | v     |

| List of Figures                                         | ix    |

| List of Table                                           | XV    |

| List of Acronyms                                        | xvi   |

| Statement of Originality                                | xvii  |

| Contribution of Authors                                 | xviii |

| Chapter 1. Introduction                                 | 1     |

| 1.1. Motivation                                         | 1     |

| 1.2. Thesis Organization                                | 2     |

| Chapter 2. Ge Based Semiconductor Devices               | 4     |

| 2.1. Why Ge?                                            | 4     |

| 2.2. Ge photodetector for on-chip optical interconnects | 7     |

| Chapter 3. Heteroepitaxial Growth of Ge on Si           | 9     |

| 3.1. Challenges of Ge heteroepitaxial growth on Si      | 9     |

| 3.2. Ge grown directly on Si                            | 13    |

| 3.3. Graded buffers                                     | 14    |

| 3.4. Selective Ge epitaxy                               | 16    |

| 3.5. Epitaxial Layer Overgrowth (ELO)                   | 17    |

| 3.6. Ge lateral growth                                  | 18    |

| Chapter 4. Metal-Catalyzed, Lateral Epitaxial Growth    | 20    |

| 4.1. Chemical Vapor Deposition                          | 20    |

| 4.2. Vapor-Liquid-Solid Growth                          | 22    |

| 4.2.1. Growth Mechanism and Kinetics studies of VLS     | 22    |

| 4.2.2. VLS growth of Ge nanowires                       | 25    |

| 4.2.3. Lateral and guided VLS growth                                     | 28 |

|--------------------------------------------------------------------------|----|

| 4.3. Lateral epitaxial growth of Ge on amorphous substrates              | 34 |

| Chapter 5. Micro-crucible Fabrication                                    | 35 |

| 5.1. Microfabrication Techniques                                         | 35 |

| 5.1.1. Photolithography                                                  | 35 |

| 5.1.2. Electron-beam Deposition and Sputter Deposition                   | 36 |

| 5.1.3. Metal Lift-off                                                    | 37 |

| 5.1.4. Plasma-Enhanced Chemical Vapor Deposition                         | 38 |

| 5.1.5. Wet Etching                                                       | 39 |

| 5.1.6. Reactive Ion Etching                                              | 40 |

| 5.2 Fabrication process of micro-crucibles                               | 41 |

| Chapter 6. CVD Growth of Ge                                              | 43 |

| 6.1. CVD System                                                          | 43 |

| 6.2. CVD Growth Procedure                                                | 44 |

| 6.3. CVD Growth Parameters                                               | 46 |

| 6.4. Growth Reproducibility                                              | 48 |

| Chapter 7. Characterization Techniques                                   | 49 |

| 7.1. Scanning Electron Microscopy                                        | 49 |

| 7.2. Transmission electron microscopy                                    | 51 |

| 7.3. X-ray diffraction                                                   | 56 |

| Chapter 8. Metal-catalyzed, Lateral Epitaxial Growth Process             | 59 |

| 8.1. Results and Discussion                                              | 60 |

| 8.2. Conclusions                                                         | 73 |

| Chapter 9. Laterally Grown Ge Films on Si Using New Relaxation Mechanism | 75 |

| 9.1. Results and Discussion                                              | 76 |

| 9.2. Conclusions                                                         | 83 |

| Chapter 10. TEM Studies of Ge Films Grown Laterally on Si                | 84 |

| 10.1. Results and Discussion                                             | 85 |

| 10.2 Conclusions                                                         | 95 |

| Chapter 11. Conclusions and Future Work | 97  |

|-----------------------------------------|-----|

| 11.1. Conclusions                       | 97  |

| 11.2. Future Work                       | 99  |

| Appendix                                | 101 |

| References                              | 104 |

## **List of Figures**

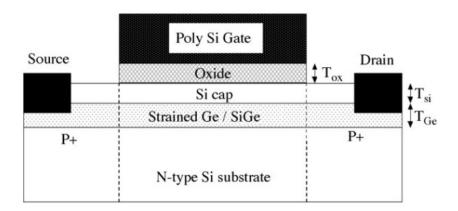

| Figure 2-1. Schematic of high-speed Ge MOSFETs                                                            |

|-----------------------------------------------------------------------------------------------------------|

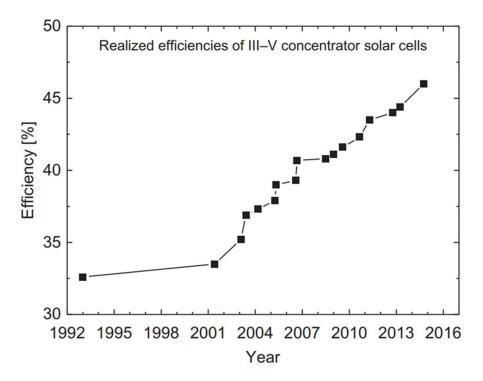

| Figure 2-2. Efficiencies of III-V multijunction PVs                                                       |

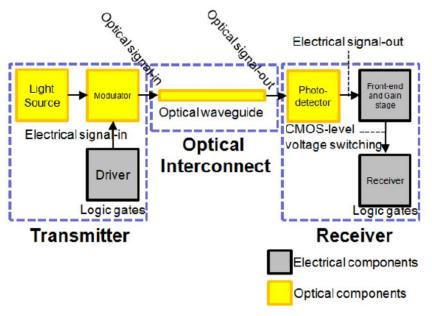

| Figure 2-3. Schematic diagram of optical interconnects                                                    |

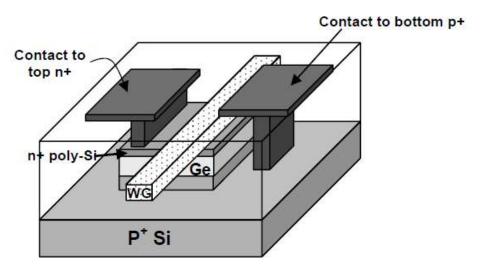

| Figure 2-4. Schematic of a Ge photodetector.                                                              |

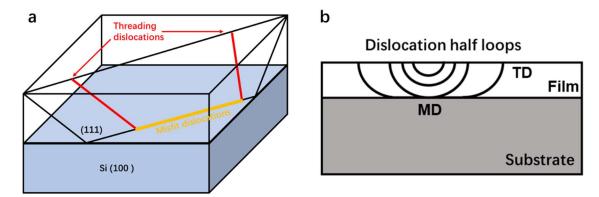

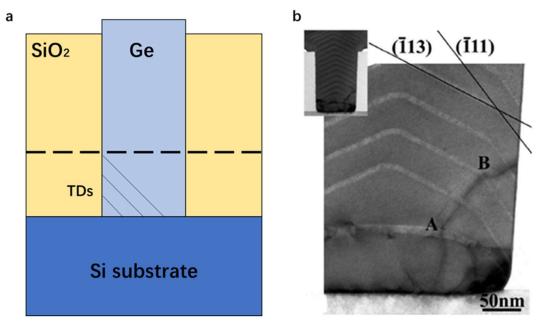

| Figure 3-1. (a) Threading dislocation and misfit dislocation within a Ge film on Si substrate.            |

| (b) Schematic diagram of the relaxation mechanism strained epitaxial layer via the formation              |

| of dislocation loops from the surface                                                                     |

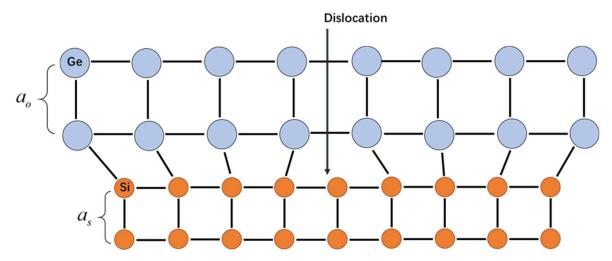

| Figure 3-2. Schematic diagram of crystal lattices at the Si-Ge interface                                  |

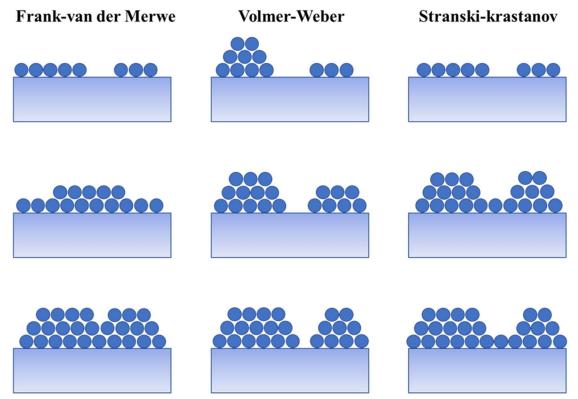

| Figure 3-3. Frank-van der Merwe (FM), Volmer-Weber (VW), and Stranski-Krastinov (SK)                      |

| growth mode                                                                                               |

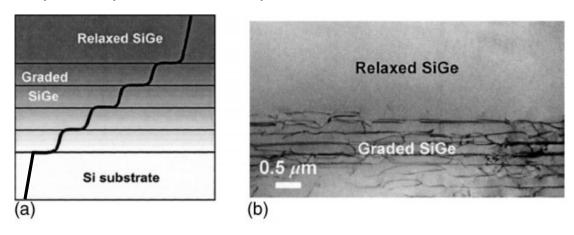

| Figure 3-4. (a) Schematic and (b) Cross-sectional TEM micrograph of graded buffer layers.15               |

| Figure 3-5. (a) Selective Ge epitaxy on Si/SiO <sub>2</sub> . (b) Cross-sectional TEM micrographs showing |

| the redirection of TDs                                                                                    |

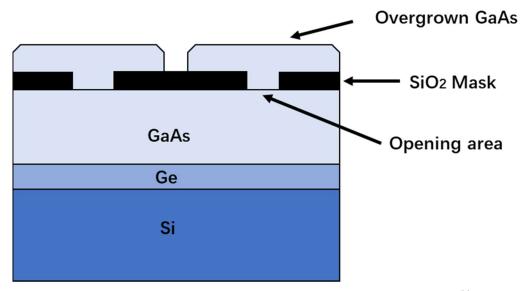

| Figure 3-6. Lateral overgrowth of GaAs on a GaAs/Ge/Si substrate                                          |

| Figure 3-7. The extension of a misfit dislocation in a lateral growth process                             |

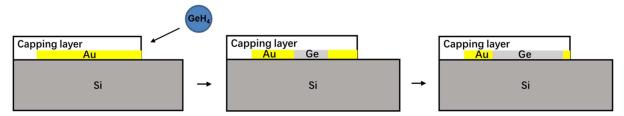

| Figure 3-8. Schematic diagram of the metal catalyzed, lateral growth process                              |

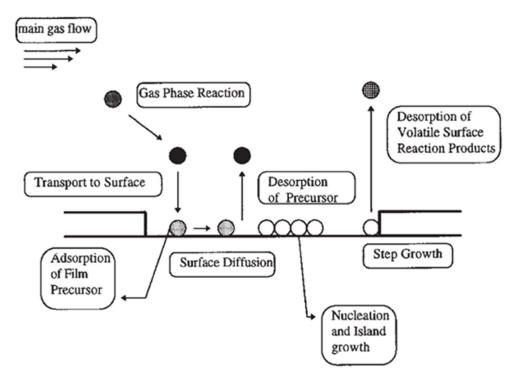

| Figure 4-1. Schematic of CVD process                                                                      |

| Figure 4-2. Schematic diagram of Si nanowire growth via VLS mechanism                                     |

| Figure 4-3. (a) Incorporation-limited where the rate-limiting step is the precursor reactions at          |

| the V-L interface. (b) Crystallization-limited where the rate-limiting step is the deposition at L-       |

| S interface. (c) The effects of temperature and Si partial pressure on the rate-limiting step24           |

| Figure 4-4. (a) TEM micrograph of an initial Si nucleation in a Au nanoparticle. Scale bar, 10            |

| nm. (b) Sizes of several Si nuclei plotted versus growth time t for Au catalysts of different             |

| initial radius R                                                                                          |

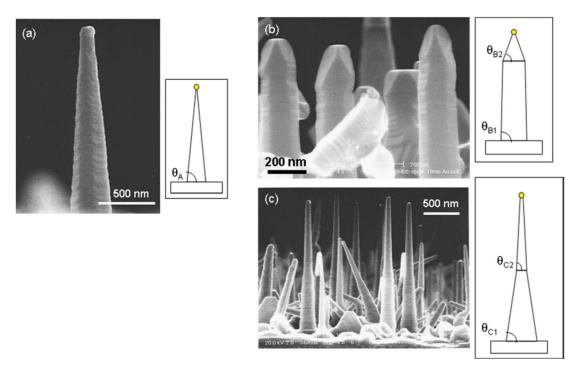

| Figure 4-5. SEM micrographs of Ge nanowires grown on Si (001), showing (a) blocky structure               |

| at 380 $^{\circ}$ C and (b) well-formed structure at 320 $^{\circ}$ C.                                    |

| Figure 4-6. SEM micrographs and respective schematics of Ge nanowires grown at: (a) 380 °C,               |

|                                                                                                           | 27         |

|-----------------------------------------------------------------------------------------------------------|------------|

| Figure 4-7. Schematic of the Si nanowire fabrication process. (a) Blank nanoporous m                      | embrane.   |

| (b) Deposition of thin Ag layer on the back of the membranes. (c) Electrodeposition of                    | of Au into |

| the pores. (d) Chemical etching of the Ag. (e) Si nanowires growth within the pores. (f                   | ) Etching  |

| of the membrane.                                                                                          | 29         |

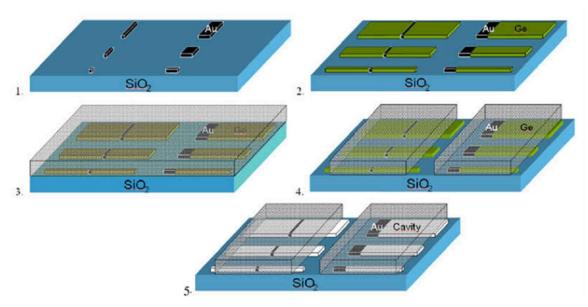

| Figure 4-8. Fabrication process of early micro-crucible structures. (1) Selective depo                    | osition of |

| Au catalysts on SiO <sub>2</sub> . (2) Selective deposition of Ge on SiO <sub>2</sub> which are aligned t | to the Au  |

| catalysts. (3) PECVD of SixOy/SixNy capping layers. (4) Creating openings by lit                          | hography   |

| and RIE. (5) Etching of the Ge layers.                                                                    | 30         |

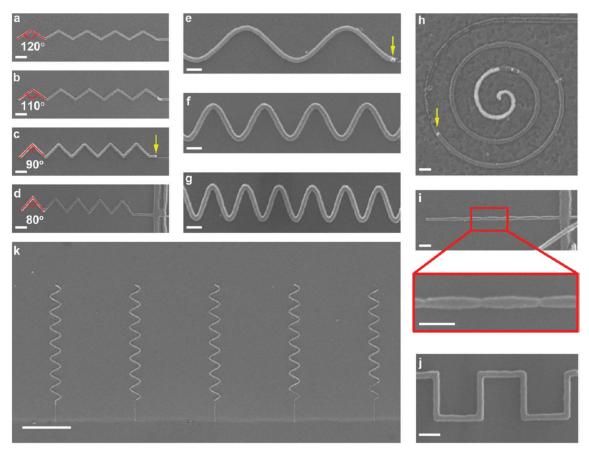

| Figure 4-9. Plan-view SEM micrographs of the laterally grown Si films within ch                           | annels of  |

| different widths (from 200nm to 2µm).                                                                     | 31         |

| Figure 4-10. SEM micrographs of nanowires with different 2D shapes.                                       | 32         |

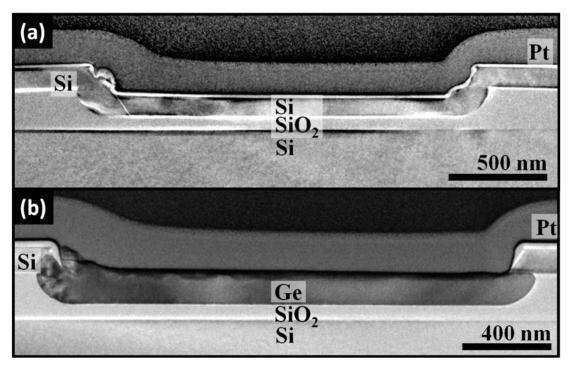

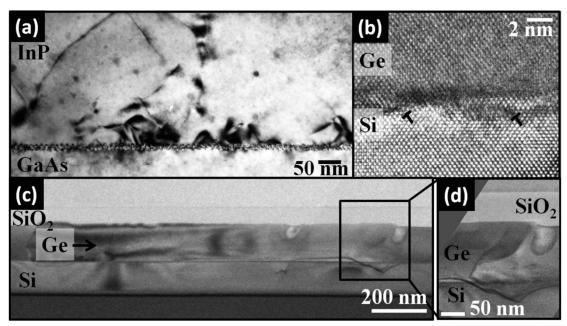

| Figure 4-11. TEM micrographs of Si and Ge nanowires laterally grown on a SiO <sub>2</sub> sur             | rface33    |

| Figure 4-12. (a) TEM micrograph of InP grown on GaAs. (b) TEM micrographs of Ge                           | nanowire   |

| laterally grown on Si                                                                                     | 33         |

| Figure 4-13. Schematic of rapid melting lateral-crystallization.                                          | 34         |

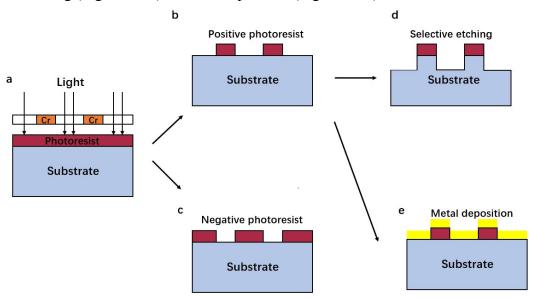

| Figure 5-1. Process flow of the photolithography process.                                                 | 36         |

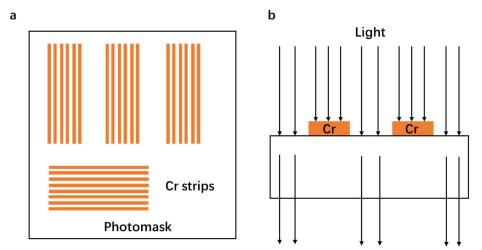

| Figure 5-2. Schematic of a photomask in (a) plan-view and (b) cross-sectional view                        | 36         |

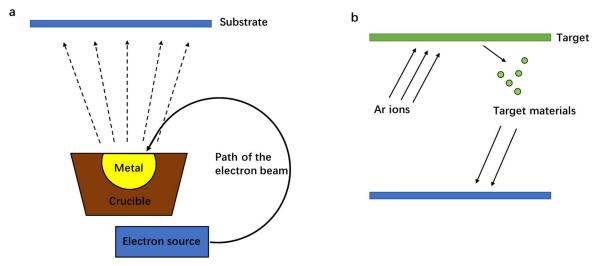

| Figure 5-3. Schematics of the inner structure of (a) an electron beam evaporator (b) a s                  | sputtering |

| chamber                                                                                                   | 37         |

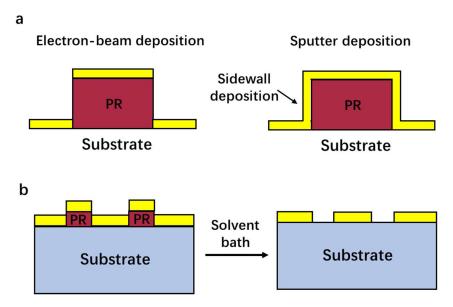

| Figure 5-4. Schematic diagram of the metal lift-off process. (a) Metal deposition on a                    | patterned  |

| photoresist layer by electron-beam deposition and sputter deposition (b) Photoresist layer                | Removal.   |

|                                                                                                           | 38         |

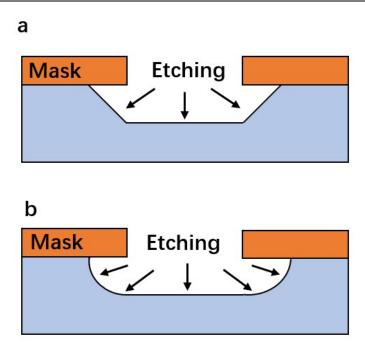

| Figure 5-5. Schematics of wet etching profile in (a) an anisotropic and (b) an isotrop                    | ic etch of |

| a surface.                                                                                                | 40         |

| Figure 5-6. (a) Schematic of the inner structure of a RIE chamber. (b) Schematic of RI                    | E etching  |

| profile                                                                                                   | 41         |

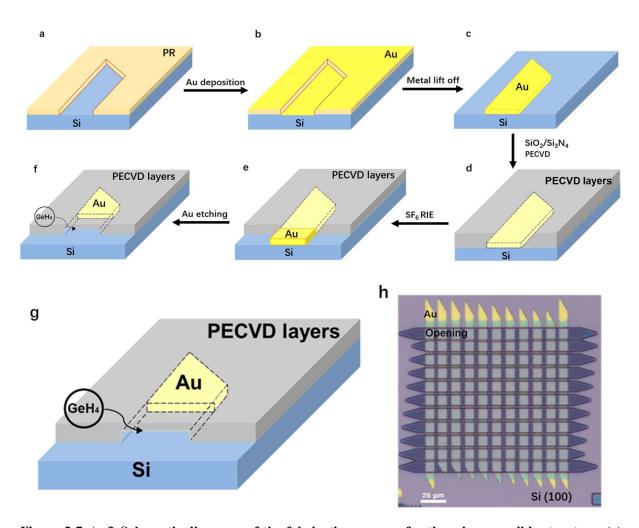

| Figure 5-7. (a-f) Schematic diagrams of the fabrication process for the micro-crucible                    | structure. |

| (g) Schematic diagram of the micro-crucible structure. (h) Optic micrograph of micro-                     | crucibles  |

| on S141                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------|

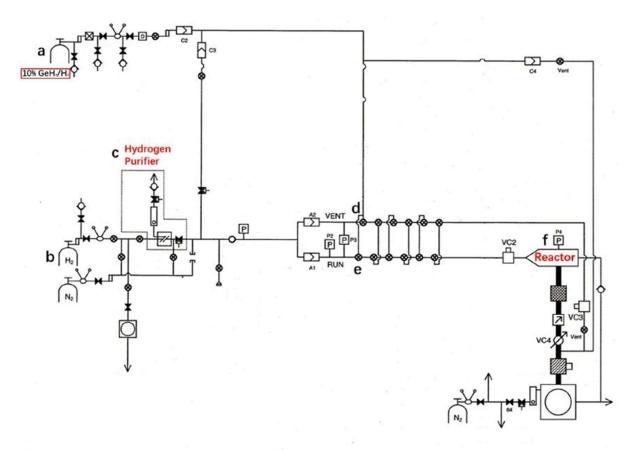

| Figure 6-1. Schematic of the Ge CVD system                                                                      |

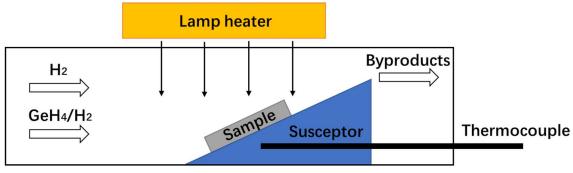

| Figure 6-2. Schematic of the cold-wall CVD reactor                                                              |

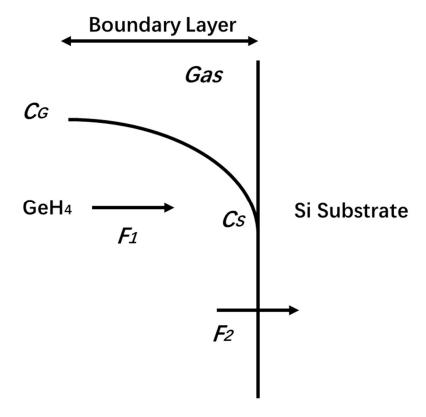

| Figure 6-3. The concentration profile and fluxes of GeH <sub>4</sub> near the Si substrate in a Ge CVD          |

| process                                                                                                         |

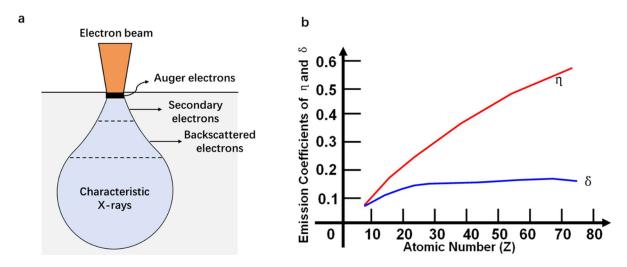

| Figure 7-1. (a) Schematic of the signals that can be generated in SEM. (b) Schematic shows                      |

| emission coefficients of backscattering electrons ( $\eta$ ) and secondary electrons ( $\delta$ ), depending on |

| atomic number (Z)50                                                                                             |

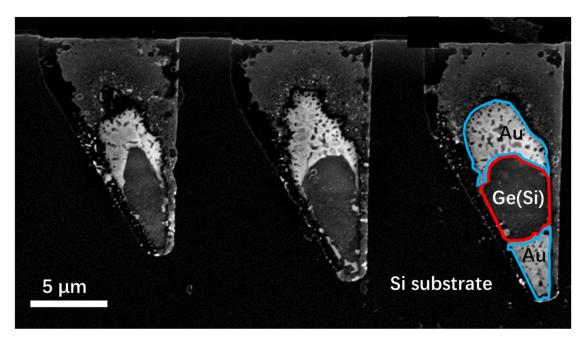

| Figure 7-2. SEM micrograph of micro-crucibles after CVD growth; the film was grown at 375 $^{\circ}\mathrm{C}$  |

| a reactor pressure of 40 mTorr and a total flow rate of 2500 sccm with a GeH <sub>4</sub> flow of 5 sccm        |

| for 1 hour. The red polygon delineates the outline of the Ge(Si) film and the blue polygons                     |

| delineate the outlines of the Au catalysts                                                                      |

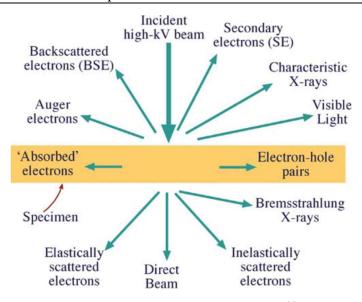

| Figure 7-3. Signals generated in TEM.                                                                           |

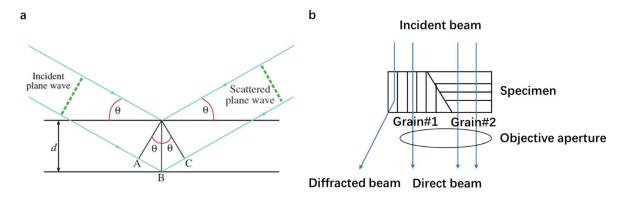

| Figure 7-4. (a) Schematic of a set of crystalline planes that satisfy the Bragg condition to                    |

| generate strong diffraction. (b) Schematic of the basic mechanism of the diffraction contrast in                |

| TEM53                                                                                                           |

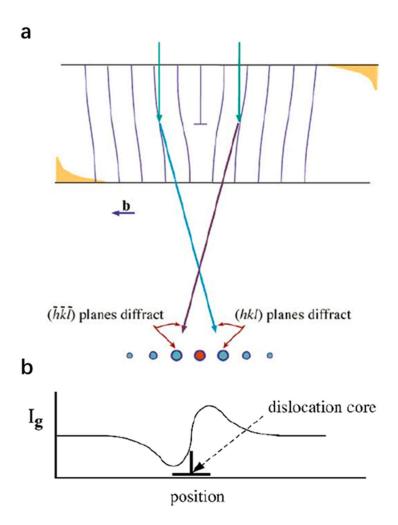

| Figure 7-5. (a) Crystalline planes are distorted because of a dislocation. (b) Diffraction contrast             |

| as a result of a dislocation                                                                                    |

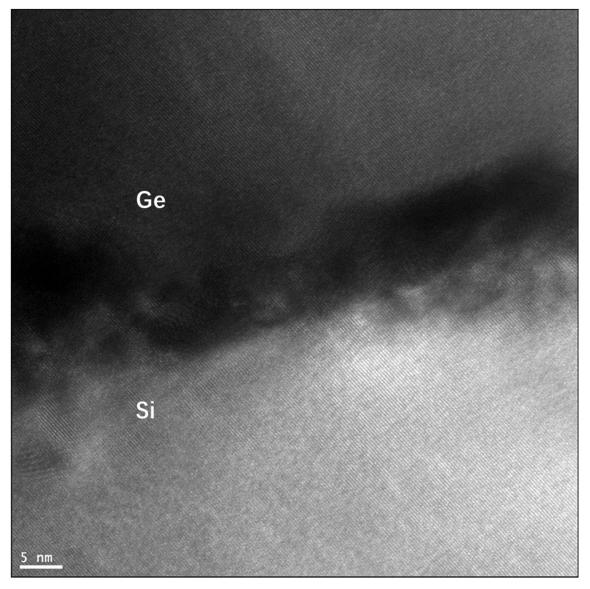

| Figure 7-6. High-resolution TEM micrograph of Ge/Si interface55                                                 |

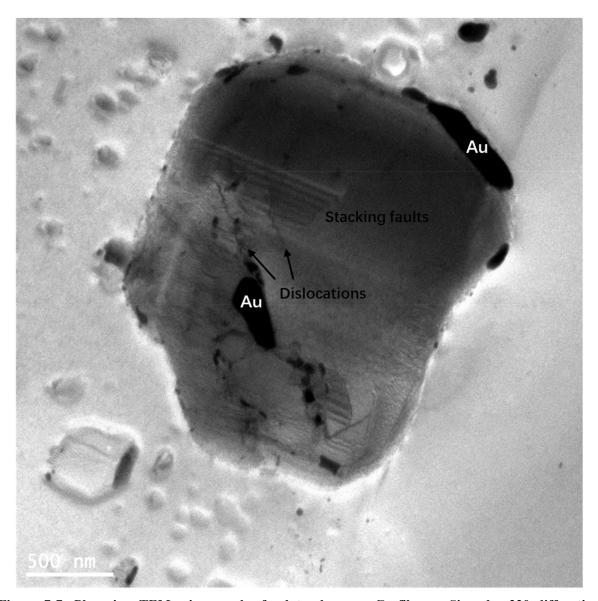

| Figure 7-7. Plan-view TEM micrograph of a lateral grown Ge film on Si under 220 diffraction                     |

| condition                                                                                                       |

| Figure 7-8. Schematic of the Si-Ge interface; the Ge film are (a) fully strained (b) fully relaxed.             |

| 57                                                                                                              |

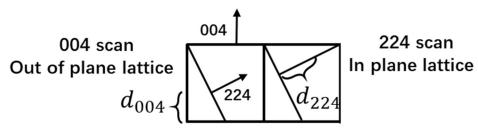

| Figure 7-9. XRD measurements of in-plan and out-of-plane lattices by using 004 and 224 scans.                   |

| 57                                                                                                              |

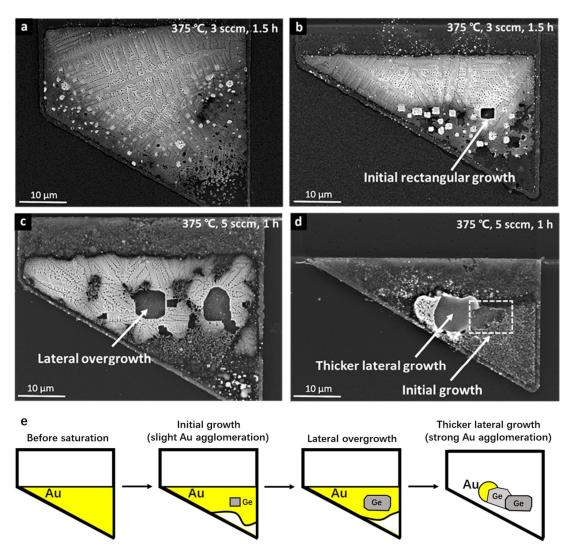

| Figure 8-1. (a-d) SEM micrographs of laterally grown Ge(Si) films on Si which may represent                     |

| different periods of the growth process; films were grown at 375 °C, a reactor pressure of 40                   |

| mTorr and a total flow rate of 2500 sccm under two growth rates: 3 sccm GeH <sub>4</sub> for 1.5 hours          |

| (Figures 8-1a and b) and 5 sccm GeH <sub>4</sub> for 1 hour (Figures 2c and d). (e) Schematic diagrams          |

| of the lateral growth process60                                                                              |

|--------------------------------------------------------------------------------------------------------------|

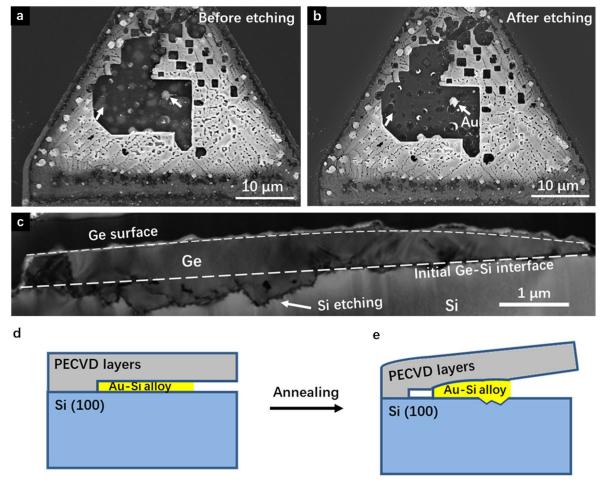

| Figure 8-2. SEM micrographs of laterally grown Ge(Si) films on Si (a) before chemical etching,               |

| (b) after chemical etching. Films were grown at 375 °C, a reactor pressure of 40 mTorr and a                 |

| total flow rate of 2500 sccm for 1 hour and the GeH <sub>4</sub> flow is 5 sccm. (c) Cross-sectional TEM     |

| micrograph of a laterally grown Ge(Si) film on Si. Films were grown at 375 °C for 1 hour and                 |

| the GeH <sub>4</sub> flow is 5 sccm, (d) Schematic diagrams showing the agglomeration of Au on Si during     |

| annealing process                                                                                            |

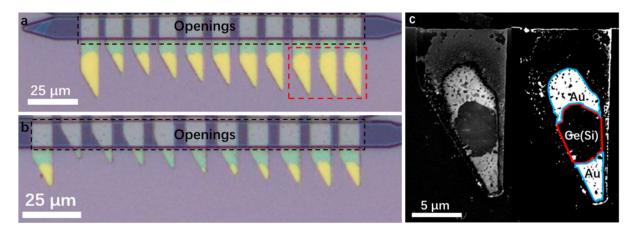

| Figure 8-3. (a) and (b) Optical micrographs of micro-crucibles containing different amounts of               |

| yellow-colored Au catalyst prior to CVD growth; the black dashed-line boxes highlight the                    |

| openings. (c) SEM micrograph of a micro-crucible after CVD growth and the image after being                  |

| processed; the film was grown at 375 °C a reactor pressure of 40 mTorr and a total flow rate of              |

| 2500 sccm with a GeH <sub>4</sub> flow of 5 sccm for 1 hour. The red polygon delineates the outline of       |

| the Ge(Si) film and the blue polygons delineate the outlines of the catalysts. The areas of the              |

| film and the catalysts in plan-view images can be estimated by measuring the areas of the red                |

| and blue polygons64                                                                                          |

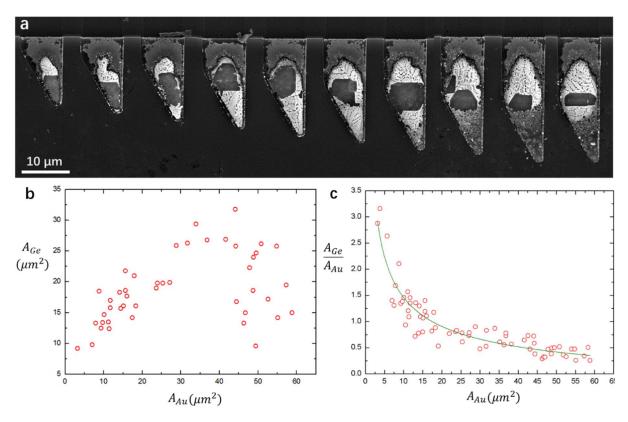

| Figure 8-4. (a) SEM micrographs of laterally grown Ge(Si) films on Si in micro-crucibles of                  |

| varying sizes; the films are grown at 375 °C, a reactor pressure of 40 mTorr and a total flow                |

| rate of 2500 sccm with a GeH <sub>4</sub> flow of 5 sccm for 1 hour. (b) The plot of the Ge film size versus |

| the Au size. The Ge film size and the Au size are measured in plan-view SEM images. (c) The                  |

| plot of $A_{Ge}/A_{Au}$ ratio versus the Au size                                                             |

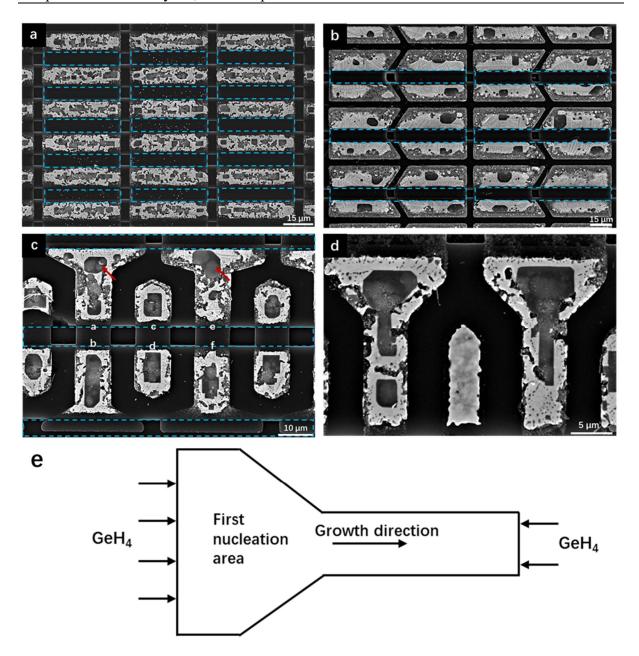

| Figure 8-5. (a-d) SEM micrographs of micro-crucibles with different shapes; films were grown                 |

| at 375 °C at a GeH <sub>4</sub> of 3 sccm for 2 hours, a reactor pressure of 40 mTorr and a total flow rate  |

| of 2500 sccm. The blue dashed-line boxes denote the openings for micro-crucibles and the red                 |

| arrows in (c) highlight the preferential nucleation points. (e) Schematic diagram of an                      |

| asymmetric, two-opening micro-crucible showing the preferential nucleation area and the                      |

| growth direction                                                                                             |

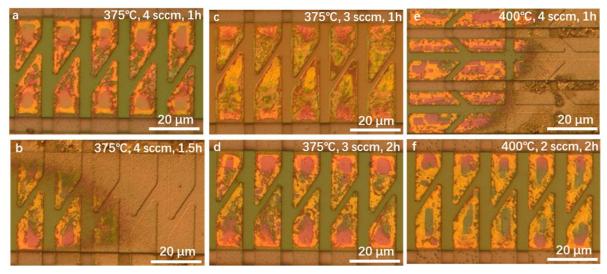

| Figure 8-6. (a-f) Plan-view optical micrographs of laterally grown Ge(Si) films on Si. The films             |

| were grown at a reactor pressure of 40 mTorr and a total flow rate of 2500 sccm. The growth                  |

| variables are the temperature, the GeH <sub>4</sub> flow rate and the growth time70                          |

| Figure 8-7. Schematic diagram of three types of growths (VLS, VS on Si and VS on amorphous                            |

|-----------------------------------------------------------------------------------------------------------------------|

| that may occur in the metal-catalyzed, lateral growth process                                                         |

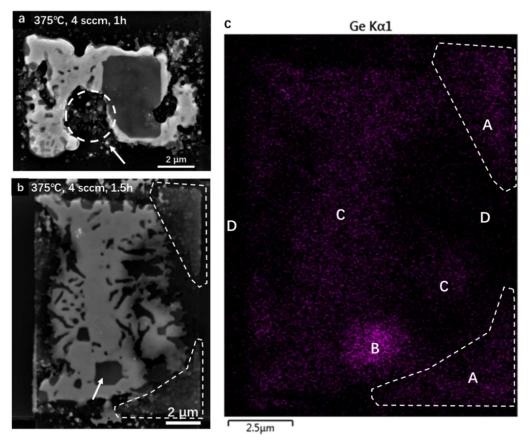

| Figure 8-8. (a) and (b) SEM micrographs of laterally grown Ge(Si) films on Si; films were at                          |

| 375 °C, a reactor pressure of 40 mTorr and a total flow rate of 2500 sccm with a GeH <sub>4</sub> flow of             |

| 5 sccm for 1 hour and 1.5 hours (a) the arrow shows the Ge nanowire growths catalyzed by                              |

| small Au particles, and the circle highlights the Au agglomeration area, (b) the dashed lines                         |

| indicate the uncatalyzed poly-Ge growths on Si and the arrow points to a VLS film growth. (c)                         |

| The EDS mapping of Ge from the area corresponding to the micro-crucible in Figure 8-8b. The                           |

| mapping image is divided into four different regions. A: uncatalyzed growth area. B: VLS                              |

| growth area. C: Au-Si-Ge alloy. D: Si substrate                                                                       |

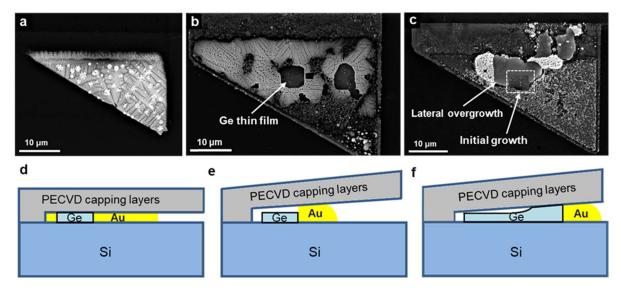

| Figure 9-1. SEM micrographs of Ge(Si) films that were grown in the micro-crucibles which                              |

| have been removed to clearly image the microstructure and schematic representation of the                             |

| agglomeration of Au on Si which leads to thicker Ge film growth. (a) Triangular Au-Si eutectic                        |

| structure without Ge film growth and Au agglomeration. (b-c) Ge(Si) films grew at 375 °C and                          |

| a GeH <sub>4</sub> flow rate of 5 sccm for 60 min. (d-f) Cross-sectional schematic of the agglomeration               |

| of Au76                                                                                                               |

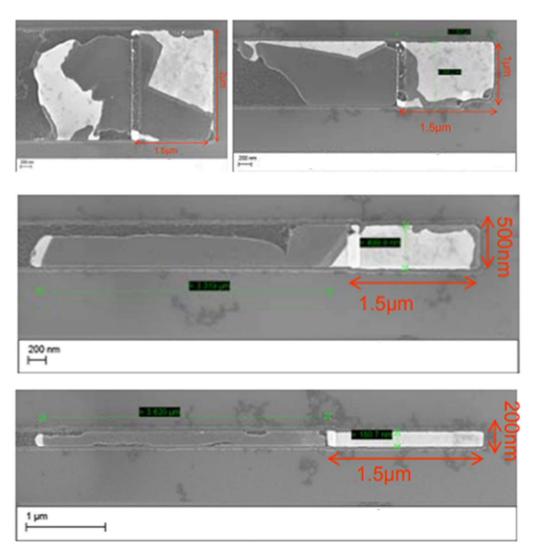

| Figure 9-2. (a) Plan-view SEM micrograph of the Ge(Si) thin film on Si. Ge(Si) films grew at                          |

| 375°C and a GeH <sub>4</sub> flow rate of 5 sccm for 60 min. (b) and (c) Cross-sectional TEM micrographs              |

| under a $g = \langle 220 \rangle$ beam taken through the dashed line (FIB plane) in Figure 9-2a, rectangle            |

| #1 and region #2, respectively. (d) Cross-sectional TEM micrographs of Ge film grown                                  |

| vertically on Si (planar film growth of Ge on Si). (e) Cross-sectional TEM micrographs of Ge                          |

| film grown laterally on Si under a $g = \langle 220 \rangle$ beam                                                     |

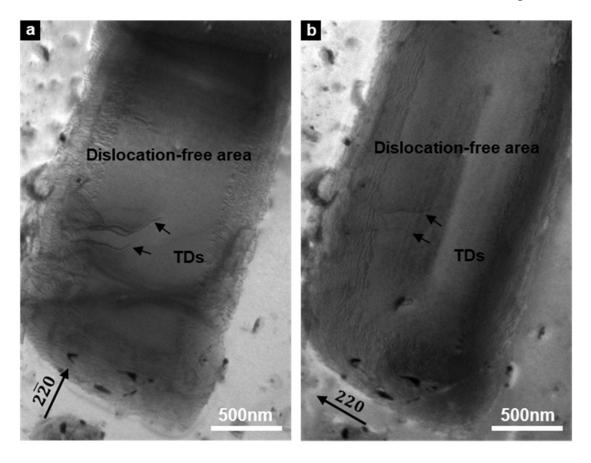

| Figure 9-3. Plan-view TEM micrographs of a Ge(Si) thin film on Si under a $g = \langle 220 \rangle$ beam              |

| (a) and $g = \langle 2-20 \rangle$ beam (b). The film was grown at 500 °C with a GeH <sub>4</sub> flow rate of 4 sccm |

| for 60 min80                                                                                                          |

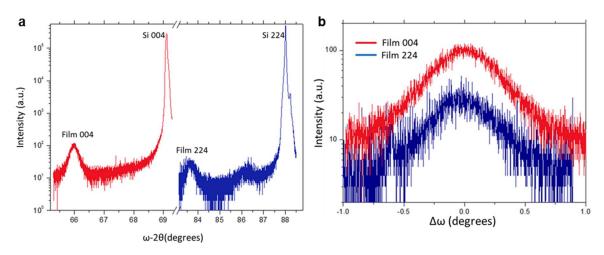

| Figure 9-4. (a) (004) and (224) Omega-2Theta scan of the Ge(Si) films. (films grew at 375 °C                          |

| with a GeH <sub>4</sub> flow rate of 5 sccm for 60 min). (b) 004 and 224 Rocking curves of the Ge(Si)                 |

| films plotted versus relative omega values.                                                                           |

| innis pioticu versus relative omega varues.                                                                           |

| dislocations. (a) the preexisting misfit dislocations which are parallel to the growth direction  |

|---------------------------------------------------------------------------------------------------|

| are elongated to relax the films. (b) the growth front skips a lattice to nucleate misfit         |

| dislocations that perpendicular to the growth direction to relax the films82                      |

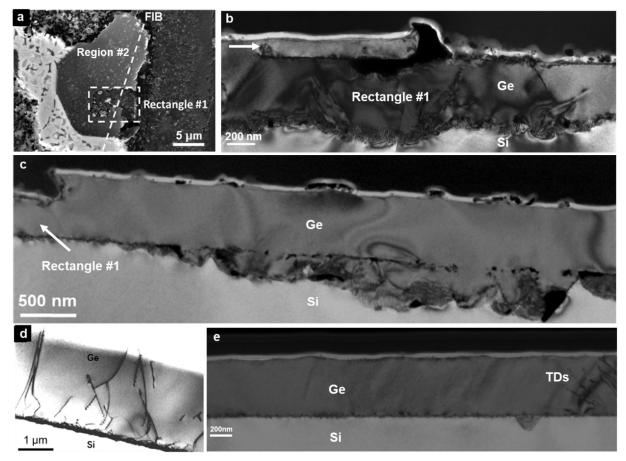

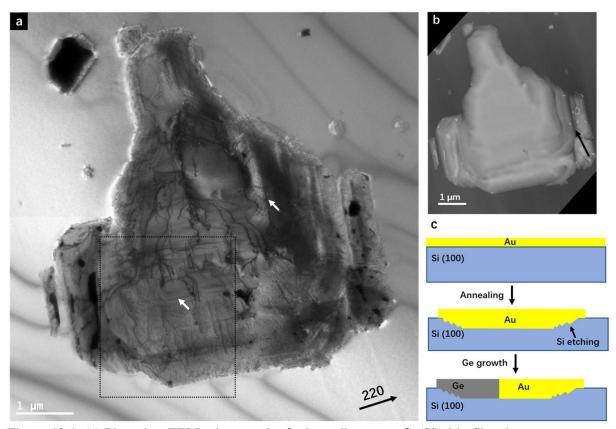

| Figure 10-1. (a) Plan-view TEM micrograph of a laterally grown Ge thin film that was grown        |

| at 375°C under 220 diffraction condition. (b) HAADF image of the same Ge film. (c) Schematic      |

| diagrams of the annealing process and the Ge CVD process in the side view. The schematics         |

| show the possible mechanism for the formation of sloping, rough Si-Ge interface85                 |

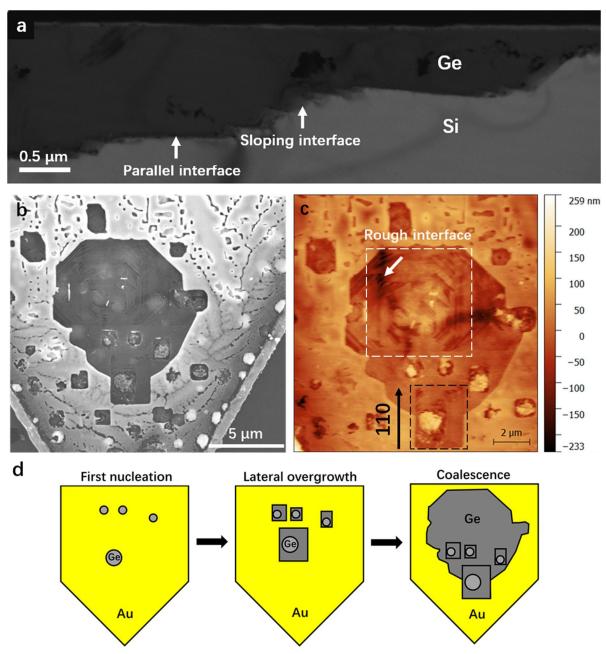

| Figure 10-2. (a) Cross-sectional TEM micrograph showing the parallel interface and sloping        |

| interface underneath a laterally grown Ge film. (b) Plan-view SEM micrograph of a laterally       |

| grown Ge film after CrO3-based wet etching. (c) AFM image of the area demonstrated in             |

| Figure 10-2b. The white arrow indicates the height variations possibly due to the steps in the    |

| sloping interface. The dashed-line box highlights a rectangular crystal that might be grown and   |

| extended from a first nucleation site. 87                                                         |

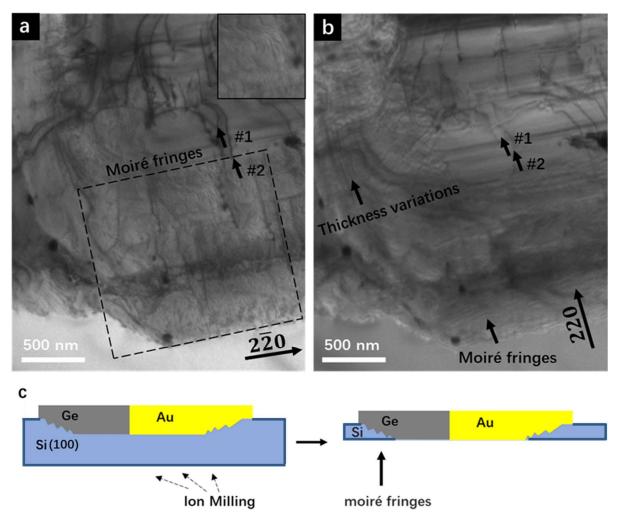

| Figure 10-3. (a) and (b) Plan-view TEM micrograph of the area marked by the dashed-line box       |

| in Figure 10-1a under 2-20 and 220 diffraction condition. The box in the top right corner of      |

| Figure 10-3a shows a magnified image of moiré fringes. (c) Schematic of the ion milling           |

| process and the overlap of Si and Ge that cause the moiré fringes                                 |

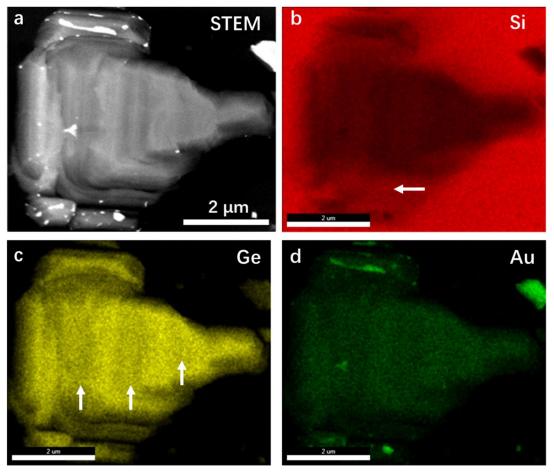

| Figure 10-4. (a) Scanning transmission electron microscopy(STEM) image of the area shown          |

| in Figure 10-1a. (b-d) Energy-dispersive spectroscopy (EDS) mappings of elements Si, Ge, and      |

| Au, respectively90                                                                                |

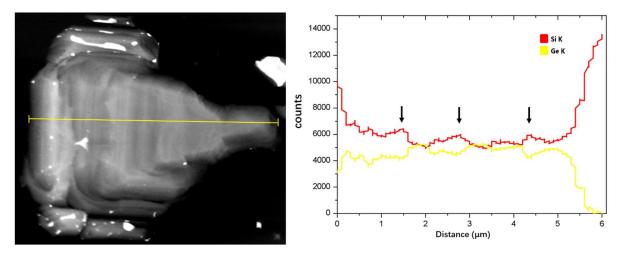

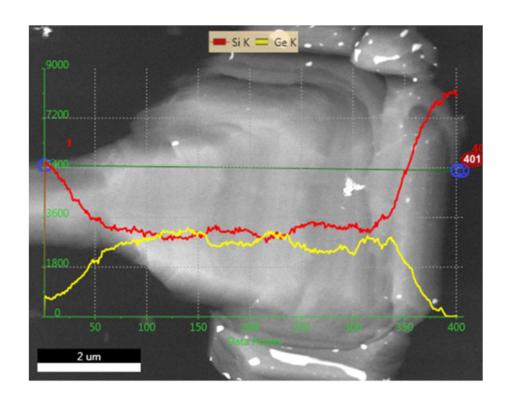

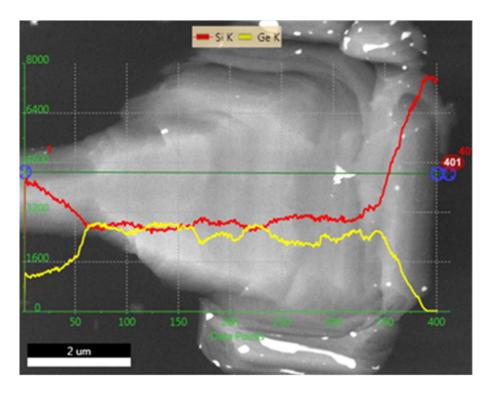

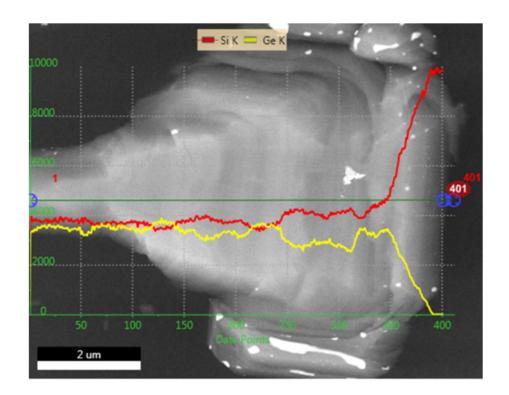

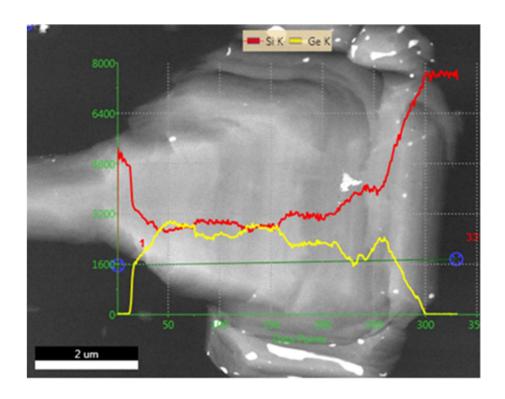

| Figure 10-5. Plan-view TEM micrograph of the film (left) and EDS line scan (right) across the     |

| film along the yellow line in the left image. The arrows in the line scan indicate the Si count   |

| peaks91                                                                                           |

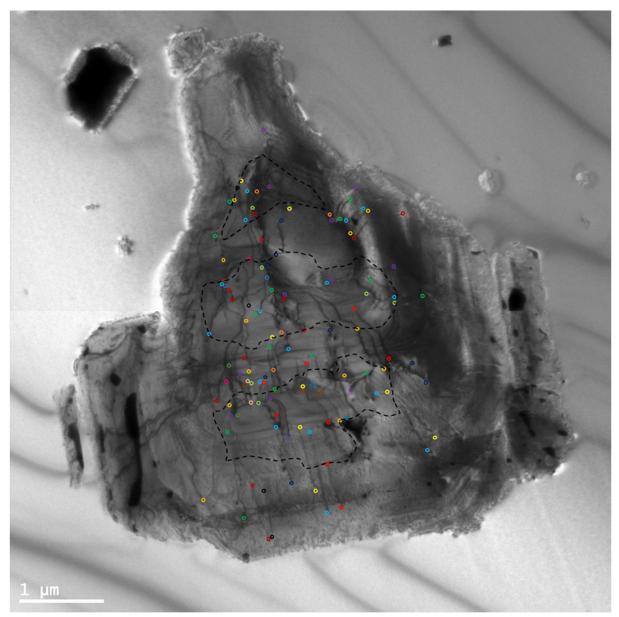

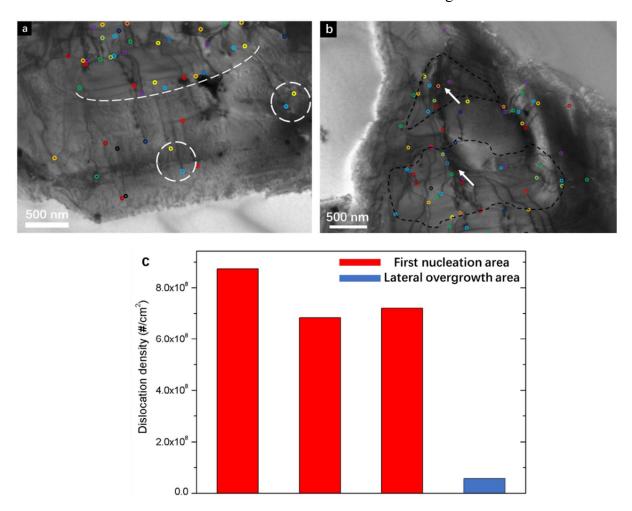

| Figure 10-6. Different colored circles were used to denote the endpoints of the dislocations      |

| within the film shown in Figure 10-1a. In addition, three dashed-line areas highlight the Si-rich |

| areas in the film based on the EDS mapping results                                                |

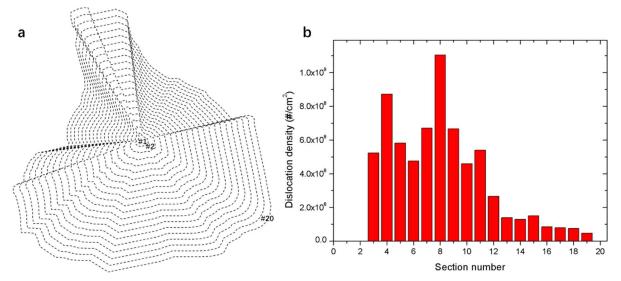

| Figure 10-7. (a) The film shown in Figure 10-1a was uniformly divided into 20 sections based      |

| on the distance from the geometrical center to the edge of the film. (b) A histogram showing      |

| the dislocation density in each section.                                                          |

| Figure 10-8. (a) and (b) Plan-view TEM micrographs showing how the dislocations glid  | ed to |

|---------------------------------------------------------------------------------------|-------|

| the film's edge and the dislocation plie-ups in the Si-rich areas. (c) Dislocation de | nsity |

| histogram of the first growth areas and the lateral overgrowth area                   | 94    |

## **List of Tables**

## **List of Acronyms**

AFM Atomic Force Microscopy

BSE Backscattered Electrons

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical Mechanical Polishing

CVD Chemical-Vapor Deposition

EDS Energy Dispersive Spectroscopy

ELO Epitaxial Layer Overgrowth

FM Frank-van der Merwe

HT High Temperature

LT Low Temperature

MD Misfit Dislocation

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

PECVD Plasma-enhanced Chemical Vapor Deposition

PR Photoresist

PV Photovoltaic

RIE Reactive-ion Etching

SEM Scanning Electron Microscopy

SK Stranski-Krastanov

TEM Transmission Electron Microscopy

TD Threading Dislocation

TDD Threading Dislocation Density

XRD X-Ray Diffraction

VLS Vapour-Liquid-Solid

VLSI Very-Large-Scale Integration

VW Volmer-Weber

### **Statement of Originality**

To the best of my knowledge and belief, the thesis reports for the first time the theoretical and experimental results of lateral Ge film growths on Si using a vapor-liquid-solid mechanism. The original contributions are listed as following:

- 1. Previous studies have reported the lateral growth of Ge films on amorphous substrate by using epitaxial layer overgrowth or rapid-melting-crystallization. These techniques cannot be used to grow Ge directly on Si and sacrifice the epitaxial connection between the film and the underlying substrate. It has been reported that metal-catalyzed Ge nanowires can be grown laterally on Si to reduce the defect density. This thesis adapted this technique for the first time to laterally grow micron-scale Ge thin films directly on Si.

- 2. This thesis presents an unreported study with respect to the comparison of dislocation morphology within the first growth areas and the lateral overgrowth areas of the laterally grown Ge-on-Si films in plan-view and cross-sectional TEM. In addition, the composition and relaxation of the films were characterized by XRD. These results showed that some lateral overgrowth areas, which were found to be defect-free, were nearly pure Ge and fully relaxed. Based on these results, we hypothesized two relaxation mechanisms that enable low-TDD, laterally grown Ge on Si. These new concepts may contribute to high-quality, lattice-mismatched growth on a substrate.

- 3. This thesis presents an unreported study of the metal-catalyzed, lateral epitaxial thin-film growth process. In particular, a model is established in this thesis to determine the final film size. Additionally, growth variables, e.g., growth temperature, are studied to optimize the growth conditions. Based on these results, this thesis provides some original ideals to engineer the lateral thin-film growth on a substrate.

#### **Contribution of Authors**

This thesis was written entirely by Weizhen Wang and reviewed by Nathaniel Quitoriano. The results presented in this thesis (chapter 8, chapter 9, and chapter 10) will be published in scientific journals.

The micro-fabrication process of micro-crucible was designed and developed by Jerome LeBoeuf and Weizhen Wang. Weizhen Wang fabricated the samples, designed a high-density micro-crucible photomask, performed the CVD growth experiments under different growth conditions, prepared the TEM samples, did the SEM, TEM, XRD, AFM characterization, analyzed the results and wrote the paper. Nathaniel Quitoriano prepared FIB samples for TEM, provided guidance, and co-wrote the paper.

## Chapter 1

## Introduction

#### 1.1. Motivation

Decades of research have been devoted to the integration of high-quality semiconductor materials. The technological impacts of integrating these materials together would lead to a paradigm shift in the design of semiconductor devices influencing technologies for solar cells, computer processors, cell phones, and telecommunications<sup>1,2,3,4</sup>. While there have been some advances in materials integration to overcome the difficulties (e.g. high-density dislocations) caused by lattice mismatch<sup>5,6,7,8,9</sup>, especially with bonding and graded buffers<sup>6,7</sup>, a high-quality, direct-growth approach to the integration of semiconductors has always been the technology of choice; it would lead to larger impacts since bonding and graded buffers have limitations<sup>2</sup>.

An innovative way to grow a high-quality, lattice-mismatched film directly onto a substrate, is to start with one nucleation point and laterally grow the crystal over the substrate. In this way, instead of nucleating dislocations from the surface, which is done with both planar film growth and graded buffers, dislocations can be formed and propagated as the growth front moves laterally. Therefore, dislocations remain solely at the interface between the film and substrate and extend from one end of the film to the other, since dislocations must end at a surface. In this manner, the film will be relaxed by a network of misfit dislocations (MDs) without threading dislocations (TDs) intersecting the top, device, surface.

This innovative growth method, first demonstrated here, is made possible by selective, metal-catalyzed Chemical Vapor Deposition (CVD)<sup>10,11,12</sup>. This technique was originally used to grow germanium (Ge) nanowires laterally on Si or SiO<sub>2</sub>. In this thesis, it was adapted to grow high-quality Ge films laterally on a Si substrate, since Ge films on Si have more industrial and proven applications, e.g. Ge photodetectors on Si for optical communication on chip. This project provides an opportunity to advance the understanding of new relaxation mechanisms for heteroepitaxial growth. More importantly, it may contribute to the fabrication of high-performance, low-cost, Ge-based devices.

#### 1.2. Thesis Organization

The objective of this thesis is to develop a metal catalyzed, lateral epitaxial growth technique to grow high-quality Ge films on Si.

This thesis can be divided into three parts. The first part (chapter 1-4) provides a review of literature, which is necessary for the understanding of this thesis. Chapter 1 and Chapter 2 present the motivations of this thesis: it is of interest to develop a novel growth technique (lateral epitaxial growth in this thesis) to grow high-quality Ge thin films on a Si substrate. Chapter 3 gives a brief overview of the research on Ge heteroepitaxial growth on Si and introduces the basic concepts of lateral epitaxial growth. Chapter 4 reviews the research work with respect to metal-catalyzed, lateral epitaxial growth, which is a main growth technique in

this thesis.

The second part of this thesis (chapter 5-7) is concerned with the experimental process in this study. Chapter 5 describes the fabrication process of micro-crucible and introduces the relevant micro-fabrication techniques. Chapter 6 provides a detailed description of a Metal-Organic Chemical Vapor Deposition system (the growth reactor). Chapter 7 presents an introduction of the characterization techniques used in this study.

The third part of this thesis (chapter 8-11) presents the findings of this research work, focusing on the study of thin film morphology, growth variables, dislocation morphology, and thin film composition and relaxation (chapter 8-10). Finally, chapter 11 gives a conclusion of this study and identify the areas for further research.

## Chapter 2

# Ge Based Semiconductor Devices

#### 2.1. Why Ge?

Over the past decades, silicon (Si) has served as the dominant material for semiconductor manufacturing because Si can be easily oxidized to form a stable SiO<sub>2</sub> insulating layer which has many applications in normal semiconductor processing, e.g. the gate material in Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs)<sup>13</sup>. Moreover, silicon has several advantages over other semiconductor materials, such as low cost and high mechanical strength. Today, the micro-fabrication technologies for Si-based semiconductor devices are well-established, e.g. the Si-based Complementary metal-oxide-semiconductor (CMOS) process,

and the Si-CMOS technology is the mainstream technique in very-large-scale integration (VLSI). However, it was predicted that the development of the Si semiconductors may slow down or even end soon since the Si technology is approaching its physical limits 14. The miniaturization of Si MOSFETs, for example, has already met great challenges, e.g. tunneling and dielectric breakdown, especially after the channel length was reduced to below 45 nm<sup>15</sup>. According to Moore's law<sup>16</sup>, the number of transistors on a chip is expected to double approximately every two years; this trend, however, may end in the near future. In addition, the developments of other Si devices, e.g. the traditional Si Photovoltaics (PVs), are also confronted with the bottleneck due to the intrinsic properties of Si. For instance, the theoretical upper limit of the efficiency of single-junction Si PVs was reported to be 31%<sup>17</sup>. Moreover, difficulties arise when an attempt was made to further reduce the manufacturing cost of Si based PVs. The total manufacturing costs of first-generation PVs depends largely on the single crystalline growth of the raw materials, namely, the Si substrates and the purification process of the raw silicon<sup>18</sup>. However, the technologies associated with the production of Si wafers have been highly developed and can hardly be improved to further reduce the cost. As a result, Si PVs currently cannot compete with the traditional grid systems in terms of cost per watt<sup>19</sup>.

Figure 2-1. Schematic of high-performance Ge MOSFETs<sup>15</sup>.

Since the development of the Si-based devices will go through a bottleneck period, there has been an increasing interest in using other semiconductor materials. Ge is one of the most promising alternatives that has many benefits. For example, Ge has higher electron and hole mobilities compared to Si which means that Ge is a potential channel material that can be used to fabricate high-performance MOSFETs<sup>15,20</sup>(Figure 2-1). Since further increases in transistor

density will plateau, if further developments occur they could be through the use of high-mobility channel materials which offer increased performance, though perhaps not increased density. The recent developments of high permittivity (high-k) materials, which can passivate the surface of Ge to form high-k/Ge gate stacks, can contribute to achieving high-performance Ge-MOSFETs as well<sup>21</sup>. Moreover, Ge is commonly used to fabricate highly sensitive near-infrared detectors owning to its excellent short-wavelength absorption and fast responsivity<sup>22</sup>. What is more, Ge-based photodetector fabrication is compatible with the COMS technology, and the CMOS and waveguide integrations of Ge photodetectors have been successfully demonstrated<sup>23,24</sup>. Ge-on-Si photodetectors are believed to be an important component in Si photonics and play a key role in achieving the next-generation interconnects.

Figure 2-2. Efficiencies of III-V multijunction PVs<sup>25</sup>.

Finally, Ge substrate provide an ideal platform for the fabrication of high-efficiency solar cells. Although the Ge band-gap (0.67eV) is far lower than the idea value (1.1eV) for single junction PVs, Ge substrates are lattice-matched with GaAs and thus can be used to grow high-quality GaAs films for the fabrication of Ge-GaAs based III-V Multi-junction PVs. In Figure 2-2, it shows that III-V multijunction concentrator solar cells can reach an efficiency of 45% and it may continue to increase.

#### 2.2. Ge photodetector for on-chip optical interconnects

Silicon photonics is a discipline using silicon as an optical medium in a photonic system for a wide-range of applications, including optical interconnects, optoelectronic integration, biological and chemical sensors, etc<sup>26</sup>.

Figure 2-3. Schematic diagram of optical interconnects<sup>27</sup>.

Today, optical interconnects is a promising area of semiconductor research due to its potential use in next-generation transmission technique, e.g., optical communication circuits can be used to manufacture extremely high-speed computers. On the other hand, the traditional electrical interconnects in integrated circuits has two major problems in practical use<sup>28</sup>. One is the large time delay as a result of electrical interconnects, which reduces the speed of computer systems. In addition, insulator layers must be deposited between multilayered electrical interconnections, which adds complexity to chip fabrication. Fortunately, there will no such issues involved with the use of optical interconnects. Figure 2-3 shows an example of on-chip optical interconnects. As can be seen from this figure, the optical signals are generated from the light source (e.g., multiwavelength laser sources) and transmit through an optical waveguide (e.g., Si optical fiber) and then are collected by the photodetector.

Figure 2-4. Schematic of a Ge photodetector<sup>29</sup>.

In general, optical communication circuits are operated in the infrared because the transmission loss in silicon optical fiber is found to be minimized at the 1.3  $\mu$ m and the 1.55  $\mu$ m wavelength<sup>30</sup>. However, Si-based photodetectors are solely capable of detecting light with a wavelength from 190 nm to 1.1 μm because of the relatively large bandgap of Si<sup>31</sup> (the Si bandgap fails to absorb low-energy, infrared photons). On the other hand, as discussed above, Ge has shown high efficient photodetection capability within this wavelength range in terms of sensitivity and responsivity. Therefore, it is a widely held view that monolithic Ge-based photonics provides a promising option for the optical communications in Si CMOS-compatible circuitry<sup>32</sup>. People typically grow micron-scale or nanoscale Ge films on Si to fabricate Ge photodetectors for onchip optical communications (Figure 2-4). However, this is not a straightforward step since the lattice mismatch between Si and Ge can introduce defects into the films that degrades the film quality. Recently, some growth techniques, e.g. graded buffers<sup>32</sup> and rapid melting growth<sup>33</sup>. were reported to solve this problem and demonstrate the direct fabrication of Ge photodetector on Si; however, these technologies have their own limitations<sup>2</sup>, e.g., graded buffer layers can be too thick. In this thesis, a metal-catalyzed, lateral epitaxial growth technique is used to grow high-quality, micron-sized Ge films on Si by using new relaxation mechanism. This technique has potential to reduce the defect density within the Ge-on-Si films and thus may contribute to the fabrication of high-performance Ge photodetector. More details with respect to the epitaxial growth of Ge on Si are presented in the next chapter.

## Chapter 3

## Heteroepitaxial Growth of Ge on Si

#### 3.1. Challenges of Ge heteroepitaxial growth on Si

It has been shown that Ge has great potential in many fields, e.g. optoelectronics and integrated circuits, and may have great impact on the development of the third generation PVs. However, single-crystalline Ge wafers are known to be expensive and have poor mechanical properties, thus posing challenges for the practical use of Ge-based semiconductor devices. For example, Ge wafers dramatically increase the cost of the Ge-based multijunction PVs and make the PVs less competitive compared to the traditional power grid. To realize the wide applications of Ge devices, people propose to grow Ge thin films epitaxially on low-cost, high-strength Si

substrates. Nevertheless, direct, epitaxial growth of Ge on Si suffers from several drawbacks; the major one is the large lattice mismatch (4%) between Ge and Si that results in the generation of a high-density of dislocations within the Ge film<sup>5</sup>. The lattice misfit is equal to

$$f = \frac{a_s - a_o}{a_o},$$

where  $a_s$  and  $a_o$  represents for the lattice constants of Si and Ge respectively.

Figure 3-1. (a) Threading dislocation and misfit dislocation within a Ge film on Si substrate. (b) Schematic diagram of the relaxation mechanism strained epitaxial layer via the formation of dislocation loops from the surface.

As shown in Figure 3-1a, in general two types of dislocations, misfit dislocation (MD) and threading dislocation (TD), are present within the lattice-mismatched, epitaxial layer. Misfit dislocations reside at the substrate film interface and are necessary to relieve the lattice mismatch of the film. Threading dislocations thread up through the film lying on the (111) plane; they end on the film surface and are somewhat necessary since a dislocation must end at a free interface or grain boundary. Nevertheless, threading dislocations reduce the efficacy of electronic devices, since they act as the recombination and scattering centers for carriers and intercept the top device surface. On the other hand, misfit dislocations are less likely to affect the performance of devices because the top devices are far away from the interface. The misfit dislocations can be doped and then used solely as a conductive path<sup>5</sup>.

Figure 3-2. Schematic diagram of crystal lattices at the Si-Ge interface.

The main nucleation source for both misfit and threading dislocations is considered to be the generation of the surface half-loop dislocations<sup>34,35</sup>(Figure 3-1b). In the initial stage of Ge growth on Si, the Ge film grows coherently on the underlying Si substrate (one-to-one correspondence between a Ge atom and a Si atom). As shown in Figure 3-2, the Ge lattice near the Si-Ge interface is deformed due to the elastic strain caused by the lattice mismatch. As the thickness of the Ge film increases, the elastic strain within the system increases. Beyond a critical thickness<sup>36</sup>, the strain energy is large enough to overcome the energy barrier associated with nucleating dislocation loops from the film surface<sup>5</sup>. Afterwards, the dislocation loops grow and glide to the Si-Ge interface to relax the film (Figure 3-1b). More details regarding the theory of dislocations in strained epitaxial layer can be found in the paper written by Fitzgerald<sup>5</sup>.

The lattice-mismatch between the substrate and the growth film (4% between Si and Ge) provides a large driving force to nucleate numerous surface half-loop dislocations. In most cases, high-density threading dislocations ( $10^6 - 10^9 \,\mathrm{cm}^{-2}$ ) are present within the Ge film grown epitaxially on a Si substrate<sup>37</sup>; this dislocation density is too high for most electrical devices and the most sensitive devices (minority carrier devices, like Bipolar junction transistors and lasers) require a threading dislocation density less than or equal to  $10^6 \,\mathrm{cm}^{-2}$  38.

Figure 3-3. Frank-van der Merwe (FM), Volmer-Weber (VW), and Stranski-Krastinov (SK) growth mode.

Another challenge for the direct epitaxial growth of Ge on Si is the growth of Ge islands caused by the lattice strain near the Si-Ge interface<sup>39</sup>. As shown in Figure 3-3, there are three possible growth modes: Frank-van der Merwe (FM) growth, Volmer-Weber (VW) growth, and Stranski-Krastinov (SK) growth<sup>40</sup>. FM growth is a planar, thin-film growth mode and commonly desirable in the modern semiconductor industry. On the other hand, VW growth is a three-dimension growth mode through the formation of islands. In a lattice-matched system, either FM or VW growth is generally the growth mode depending on the surface energy of the substrate and the growth film. In contrast, in a lattice-mismatched system, a possible scenario is that layer-by-layer planar growth occurs in the beginning stages until the film thickness reaches a critical thickness. Then islands are formed to release the strain energy by the elastic deformation of lattices<sup>41</sup>. This is the process of SK growth mode shown in the Figure 3-3. It has been reported that the Ge-on-Si growth employs the SK growth mode with the formation of a metastable 3D cluster phase<sup>42</sup>. As a consequence, the Ge films grown on Si is expected to have high surface roughness due to the formation of islands and can be a problem for the subsequent device fabrication.

#### 3.2. Ge grown directly on Si

An early attempt to grow high-quality (low-density TDs and flat surface) Ge thin-film directly on Si was reported by L.Colace et al. 43. The growth process includes two steps. In the first step, a thin layer of Ge film (50 nm) was initially grown at a relatively low temperature (300 °C) on Si in an ultrahigh vacuum CVD system. At 300 °C, the Ge island growth (SK growth mode) could be largely suppressed since the formation of islands is a thermally activated process that requires high thermal energy (high temperature) for atomic diffusion. In this stage, it was suggested that the lattice mismatch between the Ge film and the underlying Si substrate was accommodated by misfit dislocations that nucleated from the dislocation half-loops<sup>44</sup>. In order to boost the growth rate and reduce the threading dislocation density, the growth temperature was then increased to 500 °C to grow Ge film over the initial Ge buffer layer. The study found that Ge thin-films with low surface roughness can be grown on Si by using this two-step process; these Ge films were then demonstrated to be used for the fabrication of high-performance Ge photodetector<sup>43</sup>. However, this approach failed to reduce the threading dislocation density to an acceptable level and it was shown that there were  $10^{14}~{\rm cm}^{-3}$  recombination centers within the Ge film. Here, it is reasonable to assume that the density of recombination centers is approximately equal to threading dislocation density, since threading dislocation is the major source for the recombination centers.

In order to further reduce the threading dislocation density (TDD), cyclic thermal annealing was applied after the two-step growth proces<sup>8</sup>. Ge epilayers could be obtained with a threading-dislocation density of  $\sim 10^9$  cm<sup>-3</sup> from the two-step process. Then a cyclic heat-treatment between a high and a low annealing temperature ( $T_H/T_L$ ) was performed to anneal the Ge-on-Si wafers. An average TDD of  $2.3\times 10^7$  cm<sup>-3</sup> was achieved after 10 cycles of annealing between 900 and 780 °C. In addition, it had been shown that in this process the reduction of threading dislocations depends weakly on the annealing time but depends strongly on the number of cycles as well as the annealing temperature. The mechanism behind this phenomenon is believed to be related to thermal-stress induced dislocation glide<sup>8,45</sup>.

In addition, people have been working on further Ge on Si surface roughness reductions to enable the fabrication of nanoscale, Ge-based semiconductor devices. The effects of low temperature (LT) growth, high temperature (HT) growth and HT annealing on the Ge film surface roughness have been investigated and reported by Donghun Choi et al. 46. Interestingly, Ge films grown at 350 °C on Si showed a smooth surface, but post-deposition annealing was found to degrade the surface roughness. On the other hand, Ge films grown by the two-step process (LT growth (350 °C) in the beginning stage and then HT growth (600 °C)) showed a rough surface. The roughness of these films, however, could be reduced by high temperature annealing. The authors suggested that at low temperature the diffusion of Ge atoms was inhibited, but the atoms were not stable and in a "high-energy" state. Then the post-deposition annealing transferred large amounts of heat into the system to activate the Ge atoms and induce the formation of Ge clusters on the surface. This process could reduce the total system energy and increase the surface roughness. In contrast, the Ge atoms were more stable in the films grown at high temperature. The post-deposition annealing boosted the diffusion of Ge atoms, but it was not likely to greatly modify the Ge surface morphology. Thus, the overall consequence was the improvement of the surface planarity. Despite the successful demonstrations of high-quality Ge films directly grown on Si, the wide application of this technology remains doubtful. The process itself is complex, consisting of two-step growth and a time-consuming and high thermal budget cyclic thermal annealing. Besides, although hightemperature annealing can vastly reduce threading dislocation density and improve surface roughness, it can also lead to significant Si out-diffusion and the formation of SiGe<sup>47</sup>.

#### 3.3. Graded buffers

Graded buffers were the first successful technique to reduce the threading dislocation density to a low level in a heterostructure<sup>4</sup>. In this approach, a low Ge content  $Si_xGe_{I-x}$  layer was first grown on Si followed by thin film layer-by-layer epitaxial growths. For the subsequent growths, the Ge content of each additional layer was slightly increased, e.g. 10 - 20 % Ge  $\mu$ m<sup>-1</sup> along the normal direction of the Si substrate<sup>7</sup>, until the composition reached the desirable value. Since the composition difference between a  $Si_xGe_{I-x}$  layer and the layer below it was small, it

was expected that the generation of additional threading dislocations could be suppressed due to the low lattice mismatch between the layers. Note that lattice mismatch is the main cause of the elastic strain field in a heterostructure and a large strain induces dislocation nucleation and therefore additional threading dislocations. As shown in Figure 3-4, during SiGe graded buffer growth, the lattice mismatch between layers were accommodated by the gliding of the preexisting dislocations and therefore the extension of misfit dislocations<sup>48</sup>. The dislocation glide is a thermal activated process; a high growth temperature (> 750 °C), therefore, is necessary to entirely relax each Si<sub>x</sub>Ge<sub>1-x</sub> layer.

Figure 3-4. (a) Schematic and (b) Cross-sectional TEM micrograph of graded buffer layers<sup>48</sup>.

The key point regarding the mechanism of how graded buffers can enable the high-quality growth of lattice-mismatched materials is that the lattice mismatch is largely relieved by the glide of the preexisting dislocations instead of nucleating new dislocation loops. In 1998, Currie *et al.* reported that a chemical-mechanical polishing (CMP) step could be introduced to graded buffers to improve the film quality<sup>7</sup>. It was found that dislocations glide is hindered by the deep trenches in the characteristic cross-hatch pattern. Since the glide of threading dislocation is the main relaxation mechanism for graded buffers, it is necessary to polish the surface to remove the trenches. It has been reported that fully relaxed Ge films could be grown with a threading dislocation density of  $2.1 \times 10^6$  cm<sup>-2</sup> by graded buffers along with the CMP step. The top, low-density TDs surface of Ge or SiGe in graded structure is promising for the fabrication of Ge-based semiconductors, e.g. Ge photodiodes<sup>49</sup>. However, this growth approach suffers from the fact that the graded layers may be excessively thick for the integration of the top devices<sup>50</sup>. It is a tough problem to solve because a low Ge-content increase at each new

layer in the graded buffer is generally required to inhibit the nucleation of additional dislocations, which will inevitably result in thick graded layers.

#### 3.4. Selective Ge epitaxy

In 1989, Fitzgerald<sup>37</sup> investigated the impact of the growth area of lattice-mismatched epilayer on the density of the dislocations within the film. First, it is common sense that the total number of the fixed nucleation sources of dislocations is proportional to the size of the film. Besides, the glide distance of dislocations should not exceed the side length of the film. Therefore, it is expected that dislocation interactions and multiplications that may occur in the process of dislocation slip can be reduced in a small growth area. This is important because dislocation interactions and multiplications are two mechanisms to generate additional dislocations. Furthermore, in a small area, threading dislocations can easily glide to the edge of the film and then can be trapped and eliminated by the sidewalls. In brief, it was found that the number of threading dislocations and misfit dislocations were reduced in a small growth film. It might be attributed to the fact that less dislocation interaction occurred in a small area and threading dislocations were partially annihilated by the sidewall.

Using the similar principle and epitaxial necking, people have developed a technique to improve the crystal quality of the epitaxially grown Ge film on Si, termed as selective Ge epitaxy<sup>9,51</sup>. As shown in Figure 3-5a, a thermally grown SiO<sub>2</sub> film on Si was patterned by lithography and etching processes to predefine the positions (Si surface) to grow Ge. Then Ge was epitaxially grown on Si in a small, predefined window surrounded by SiO<sub>2</sub> sidewalls. It was reported that threading dislocations could be necked out by the SiO<sub>2</sub> sidewalls, and defect-free Ge was grown at the top of the epilayer. In 2007, a study of the mechanism behind the high aspect ratio epitaxial necking was reported<sup>52</sup>. It was found that the defect elimination by the selective Ge epitaxy was owning to the redirection of threading dislocations. During the growth process, threading dislocations were found to be parallel to the growth front normal. Within a high aspect ratio trench, threading dislocations were likely to encounter the (113) facets and then the (111) facets and move towards the sidewalls (Figure 3-5 b). In the end, the dislocations

were trapped and annihilated by the sidewalls. It was an interesting mechanism explaining the reduction of dislocation number in a high-aspect-ratio structure. Hyun-Yong Yu *et al.*<sup>53,54,55</sup> combined this technique with multi-step deposition/hydrogen-annealing cycles for the fabrication of high-performance p-Channel Ge MOSFET and Ge on Si photodiode.

Figure 3-5. (a) Selective Ge epitaxy on Si/SiO<sub>2</sub>. (b) Cross-sectional TEM micrographs showing the redirection of TDs<sup>51</sup>.

#### 3.5. Epitaxial Layer Overgrowth (ELO)

An early example of lateral growth was reported by B-Y. Tsaur *et al.*<sup>56</sup> to reduce the dislocation density within GaAs epilayer from 10<sup>7</sup> cm<sup>-2</sup> to approximate 10<sup>4</sup> cm<sup>-2</sup>. As illustrated in Figure 3-6, lateral overgrowth is a technique similar to selective growth of Ge on Si. However, the Ge selective growth on Si emphasizes on the trapping effects of the SiO<sub>2</sub> sidewalls. On the contrary, for the lateral overgrowth shown in the Figure 3-6, the SiO<sub>2</sub> film was only used as a mask to define the nucleation points on the GaAs substrate. GaAs was initially grown on the predefine areas and then grown laterally over the SiO<sub>2</sub> layer. The study found that the laterally overgrown GaAs films showed no threading dislocations except for the initial growth sections (the opening areas). However, the threading dislocations near the opening areas bent over quickly and did not propagate along the growth direction. It is also believed that this growth technique can be applied to other semiconductor materials to achieve low threading dislocation density within the films.

Figure 3-6. Lateral overgrowth of GaAs on a GaAs/Ge/Si substrate<sup>56</sup>.

#### 3.6. Ge lateral growth

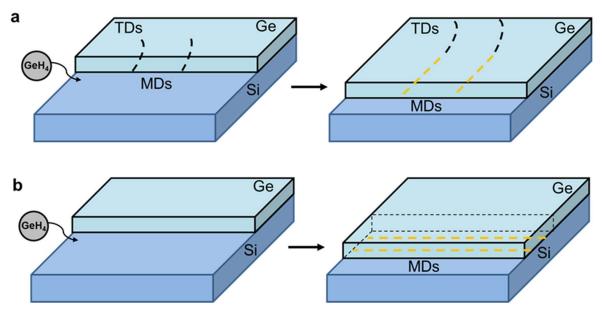

In this thesis, epitaxial layer overgrowth is adapted to grow Ge laterally on Si instead of on an amorphous layer. This lateral growth process provides a pathway for investigating new relaxation mechanisms to accommodate the lattice mismatch between Si and Ge. In a lattice-mismatched, lateral growth process, it is thought that high-density threading dislocations may exist in the first growth section because the initial relaxation mechanism might be the nucleation of surface dislocation loops (Figure 3-7). Nevertheless, with the ongoing lateral growth, the misfit dislocations at the edge of the film might be elongated to release the strain at the interface (Figure 3-7). The new formation of dislocation loops is therefore suppressed since the strain is relaxed by the extension of existing misfit dislocations. In the end, the ratio of the number of threading dislocations to misfit dislocations is expected to decrease along with the lateral growth orientation. As discussed above, threading dislocations are the primary mechanism of device performance degradation in lattice-mismatched semiconductors. The new growth technique, lateral epitaxial growth, therefore has potential for growing high quality, lattice-mismatched thin films.

# Film TD MD First growth section Substrate

Figure 3-7. The extension of a misfit dislocation in a lateral growth process.

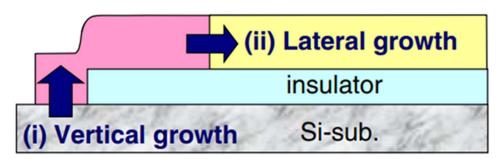

Figure 3-8. Schematic diagram of the metal catalyzed, lateral growth process.

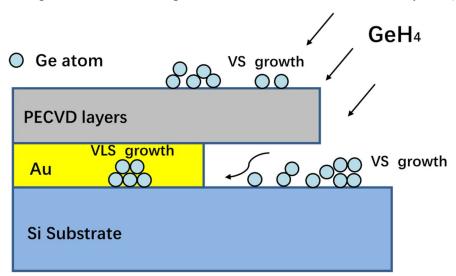

In order to grow the films laterally in predetermined regions, an idea is to use a capping layer to prevent the vertical growth and a metal catalyst to define the nucleation point and engineer the growth direction. In this thesis, a micro-crucible structure <sup>57</sup> was designed for metal-catalyzed, lateral growth and the growth process is depicted in Figure 3-8. As we can see in this picture, the growth of the Ge thin film is confined to a channel underneath the capping layer; small Ge films are initially nucleated in the metal liquid and then grown laterally on Si within the channel. The metal-catalyzed growth method has been extensively used to synthesize semiconductor nanowires, termed as vapor-liquid-solid (VLS) growth <sup>58</sup>; the growth mechanism of VLS is discussed in the next section.

## Chapter 4

## Metal-Catalyzed, Lateral Epitaxial Growth

#### 4.1. Chemical Vapor Deposition

Chemical Vapor Deposition (CVD) is the technique to form a thin film over a substrate by the chemical reactions of vapor precursors. CVD is extensively used in the semiconductor industry and is the basis of vapor-liquid-solid growth. The basic mechanism of CVD is demonstrated in Figure 4-1. It can be seen that a typical CVD process mainly involve gas reactions, the absorption and desorption of gases and multiple surface reactions. Here, the CVD growth of Ge based on the decomposition of germane ( $GeH_4 \rightarrow Ge + 2H_2$ ) is used as an example to illustrate the growth process. First, the CVD precursor(s) (GeH<sub>4</sub>) are transported by a carrier gas (e.g. H<sub>2</sub>) to the reactor chamber. At an elevated temperature, the vapor precursors may chemically react in the gas phase to form intermediate reactants (GeH<sub>3</sub>, GeH<sub>2</sub> or GeH). This is

followed by the adsorption of reactants on the target substrate surface. Afterwards, the reactants may decompose into atoms (Ge) which can diffuse to the growth sites to form a thin film on the substrate. In the end, the by-products are desorbed and transported away from the surface by the carrier gas.

Figure 4-1. Schematic of CVD process<sup>59</sup>.

In 1855, It was reported that tungsten was the earliest metal deposited by CVD<sup>59</sup>. Later in 1909, the first CVD growth of silicon was reported, and this growth method gained further popularity in the 1950s<sup>59</sup>. In the mid-1970s, CVD developed rapidly as a result of the large demand from the semiconductor industry, since CVD could be used to precisely control the uniformity, composition, purity and doping concentration of thin films. Despite its advantages over other thin film growth techniques, CVD suffers from several major drawbacks. First, gas precursors, essential for a CVD process, are generally expensive and toxic. Second, high temperatures are necessary for an epitaxial CVD growth which may cause damage to the temperature-sensitive substrates and increase thermal budget.

#### 4.2. Vapor-Liquid-Solid Growth

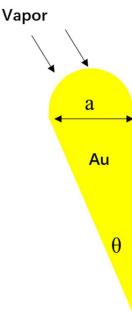

#### 4.2.1. Growth Mechanism and Kinetics studies of VLS

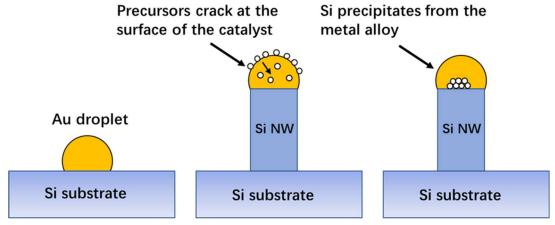

In 1963, Wagner and Ellis first described the unidirectional growth of semiconductors by using metal catalysts and discussed the related growth mechanism<sup>58</sup>. This type of growth was defined as vapor-liquid-solid (VLS) growth<sup>58,60,61,62</sup>. Figure 4-2 shows the growth of a silicon nanowire catalyzed by a gold droplet, demonstrating a typical example of VLS growth<sup>63</sup>. The Au droplet serves as a catalyst on Si substrate to determine the first nucleation site and guide the unidirectional growth of the Si nanowire. In Figure 4-2, the vapor precursors (SiH<sub>4</sub>) tend to decompose at the surface of the liquid droplet rather than the Si substrate due to the catalytic ability of Au and the higher sticking coefficient of the Au/Si eutectic liquid. Once the droplet dissolves a sufficient amount of Si and reaches the supersaturation point, Si starts to precipitate at the liquid-solid interface in the form of a nanowire, dictated by the size of the Au catalyst. Then the system achieves a steady-state and the Si nanowire grows in a specific orientation.

Figure 4-2. Schematic diagram of Si nanowire growth via VLS mechanism.

In 1971, Bootsma and Gassen studied the kinetics of the VLS growths of Si and Ge<sup>64</sup>. It was reported that the VLS growth rates of Si and Ge could be increased by increasing the substrate temperature and the vapor pressures of the hydride precursors (e.g. SiH<sub>4</sub> and GeH<sub>4</sub>). The authors also confirmed that the growth rates of the catalyzed growths were hundreds times higher than that of noncatalyzed growth. Furthermore, it was suggested that the decomposition reactions of the precursors at the Vapor-Liquid surface was the most likely rate-limiting step

since the vapor pressure had impacts on the growth rate. Later, a further study on VLS growth mechanism was given by Givargizov<sup>65,66</sup>. These studies demonstrated that the growth rate of VLS growth decreased abruptly when the diameters of the semiconductor wires was reduced to a critical diameter at 0.1 µm because of the Gibbs-Thomson effect:

$$\Delta \mu = \Delta \mu_0 - \frac{4\Omega \alpha}{d},$$

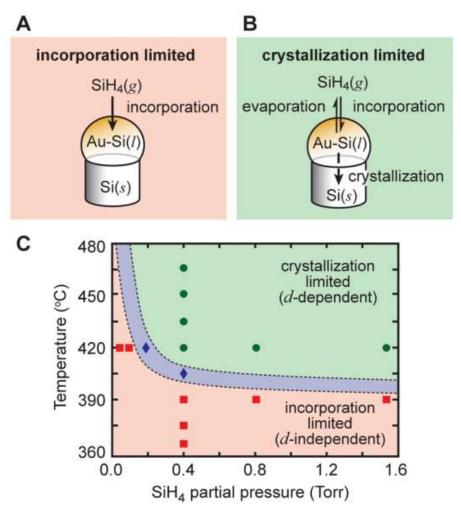

where  $\Delta \mu$  is the effective chemical potential difference of Si in vapor and solid,  $\Delta \mu_0$  is the same chemical potential difference at plane boundary, d is the diameter of Si wire. As can be seen from the equation, when the diameter of the Si wire decreases, the chemical potential difference (the driving force for the VLS growth of Si wire) is reduced correspondingly which would lower the growth rate. However, a study by Nebol'sin et al.<sup>67</sup> reported that the Si VLS growth rate decreases with increasing Si whisker diameter. The authors suggested that a larger Si whisker diameter increases the Si equilibrium concentration in the liquid and thus provides a larger driving force to boost the growth rate. Afterwards, Kodambaka et al. 68 found that the growth rate was independent of the wire diameter, but proportional to the precursor partial pressure. They also proposed that during VLS growth the rate-limiting step is the irreversible dissociative adsorption of the vapor precursors on the liquid surface. In order to resolve the long-term ambiguity with respect to the dependence of nanowire diameter, Pinion et al. 69 performed measurements of Si nanowire growth rates over a range of temperatures, pressures, and diameters. They divided VLS growth into two regimes: (1) an incorporation-limited regime where the rate-limiting step was the precursor reactions at the V-L interface (Figure 4-3a), and (2) a crystallization-limited regime where the rate-limiting step was the deposition at L-S interface (Figure 4-3b). Moreover, it was found that the rate-limiting step depended on growth temperature and Si partial pressure. It was reported that in the incorporation-limited regime the growth rate is independent of the wire diameter, and in the crystallization-limited regime the growth rate depends on the wire diameter (positive correlation).

Figure 4-3. (a) Incorporation-limited where the rate-limiting step is the precursor reactions at the V-L interface. (b) Crystallization-limited where the rate-limiting step is the deposition at L-S interface. (c) The effects of temperature and Si partial pressure on the rate-limiting step<sup>69</sup>.

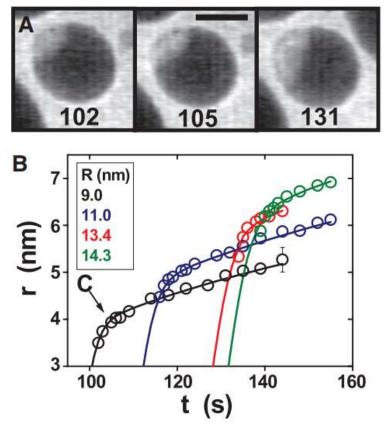

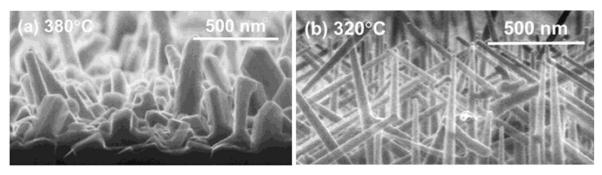

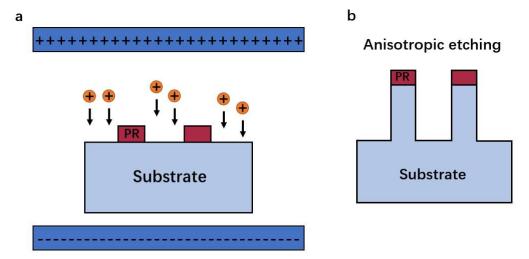

In recent years, transmission electron microscopy was developed to study in situ VLS growth of nanowires; this technique presented a clearer picture of the growth process<sup>70,71,72</sup>. For the VLS growth of Si nanowires on SiO<sub>2</sub>, it had been shown that Si tended to nucleate at the most energy-favorable sites (Figure 4-4a), e.g. the edge of the Au-Si alloy<sup>71</sup>. Once the first crystal seed was formed in the liquid (since it was grown on SiO<sub>2</sub>, the first nucleated crystal was particularly hard to form which caused a large initial supersaturation), the nanowire grew quite fast because of that built up supersaturation and the corresponding increased chemical potential difference. However, after the Si concentration decreased to a near equilibrium value, the growth rate slowed (Figure 4-4b). Note that the growth rate was approximately proportional to the chemical potential difference (proportional to the extent of supersaturation) thus explaining the abrupt reduction in growth rate in Figure 4-4b.