# Layout Effects Modeling for Analog Circuits Design Automation

Henry Hoi Yun Chan

Doctor of Philosophy

Department of Electrical and Computer Engineering

McGill University

Montreal, Quebec

2008-8-31

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Doctor of Philosophy

Copyright ©2007 Henry H. Y. Chan

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-50794-0 Our file Notre référence ISBN: 978-0-494-50794-0

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# DEDICATION

To my dearest Mother, Father, Winnie and Angie

## **ACKNOWLEDGEMENTS**

I am grateful to have Prof. Zeljko Zilic as my research supervisor, who introduced me into microelectronics research at my undergraduate years and provided the equipment and stimulating research environment in the IML at McGill. For the past years, he followed my research closely and critically. His visionary thoughts constantly provided me with inspirations, research techniques and the proper perspective at numerous stages of this work. His encouragements are especially valuable at certain critical points in this research.

I would like to thank Prof. Roni Khazaka and Prof. Dennis Giannacopoulos for their valuable feedback and to be my thesis committee members. Although my name is the only one that is printed on the thesis cover, several individuals contributed either directly or indirectly in bringing this work to its conclusion. I would like to thank Atanu Chattopadhyay, Jean-Francois Boland, Bojan Mihajlovic, Marc Boule, John Storey Bishoff, Robert Armstrong, Terry Thomas and Trent McConaghy for their inspiring discussions, critiques and comments. I thank Stephan Bourduas, Jean-Samuel Chenard, Kahn-Li Lim and Nathaniel Azuelos for the collaborations, excellent French and software support, and Jason McLaren, Zuweina Sood for tools support. I also thank all my past and present colleagues, staff and students in MACS and IML of McGill University, Analog Design Automation Inc., and Synopsys Inc.

Finally, no word would be enough to show my appreciation towards my girlfriend, Angie, for her tremendous sacrifice all along, to be always there when I needed the most. Her unwavering support and patience are the energy sources that propelled me since the beginning to the end of this long, dis-orienting and often difficult journey. Last but not least, every trait that I have, I owe it to my dearest parents and my sister, Winnie, who taught me, encouraged me and supported me since my early years to pursue my dreams, and not to give up without trying my best.

## **ABSTRACT**

Deep sub-micron (DSM) integration brings about aggressive technology scaling to accommodate large and high-speed systems onto a single chip. The integration and migration of mixed-signal systems to smaller process nodes have shortened the traditional analog circuit design cycle and increases performance influence due to parasitic coupling. Current analog optimization tools demonstrate promising results at the schematic netlistlevel, but inherited layout effects are excluded until the physical design is completed. If coupling effects are ignored or poorly modeled, schematic optimization results are no longer accurate with respect to silicon measurements. On the other hand, physical design tools are traditionally guided by geometric constraints. In interconnect-dominated designs, both parasitic-aware circuit optimization and performance-driven physical design are crucial for rapid design closure. This thesis addresses both issues by integrating schematic optimization and the physical design process. Through the use of virtual interconnect parasitic models and light-weight parasitic models, the simulation-based circuit optimizers and placement tools can exchange design and performance information while operating at their full capacities. The interconnect models also provide provisional routing configurations. A novel compaction process for analog layout further refines the block and interconnect positions with respect to DSM effects.

## **ABRÉGÉ**

Les technologies d'intégration submicrométrique profonde (DSM) permettent la réalisation de systèmes complexes à haute vitesse et sur une seule puce. La migration de systèmes à signaux mixtes vers des procédés de fabrication à plus petite échelle raccourcit le cycle de conception traditionnel des circuits analogiques et augmente l'influence des effets parasitiques sur la performance des circuits. Les outils d'optimisation de liste des interconnexions présentent des résultats prometteurs, mais les effets topologiques intrinsèques sont exclus jusqu'à la réalisation physique. Si les effets de couplage sont ignorés ou s'ils sont mal modélisés, les résultats obtenus lors de l'optimisation de la réalisation topologique ne reflèteront pas précisément la réalisation physique. Par ailleurs, les outils automatisant la génération de la réalisation physique et du masque de fabrication du circuit sont traditionnellement guidés par des contraintes géométriques. Pour les réalisations dominées par les interconnexions, une optimisation basée sur les effets parasitiques et sur la performance de la réalisation physique est de très grande importance, pour faciliter la conclusion rapide des projets. Cette thèse adresse les deux points précédents en intégrant l'optimisation des diagrammes schématique avec les procédés de génération du dessin physique. En utilisant des modèles virtuels et simplifiés des effets parasitiques, les logiciels d'optimisation basés sur la simulation peuvent donc communiquer avec les outils de placement sans affecter la performance de la simulation. Les modèles d'interconnexion fournissent aussi des configurations provisionnelles sur le tracé. Une nouvelle approche au processus de compaction, applicable aux topologies analogiques, permet un meilleur raffinement du positionnement des interconnexions en tenant compte des effets DSM.

# TABLE OF CONTENTS

| DED  | ICATIO         | N                                                      |

|------|----------------|--------------------------------------------------------|

| ACK  | NOWL           | EDGEMENTS iii                                          |

| ABS' | TRACT          | iv                                                     |

| ABR  | É <b>G</b> É . |                                                        |

| LIST | OF TA          | BLES ix                                                |

| LIST | OF FIG         | GURES                                                  |

| LIST | OF AE          | BBREVIATIONS xiv                                       |

| 1    | Introdu        | action                                                 |

|      | 1.1            | Problem Description                                    |

|      | 1.2            | Original Contributions                                 |

|      | 1.3            | Claims of Originality                                  |

|      | 1.4            | Thesis Outline                                         |

| 2    | Funda          | mental Concepts and Groundwork                         |

|      | 2.1            | Analog Circuit Design                                  |

|      | 2.2            | Parasitic Effects in Integrated Circuit Design         |

|      | 2.3            | Parasitic Effects in Physical Design                   |

|      | 2.4            | Parasitic Effects Extraction                           |

|      | 2.5            | Sensitivity of Parasitic Effects due to Design Changes |

|      | 2.6            | A Gridless Placement Encoding Scheme                   |

|      | 2.7            | Placement Candidates                                   |

|      | 2.8            | Engineering Change Order                               |

|      | 2.9            | Discretization for Substrate Modeling                  |

|   |       |                                                                      | 37  |

|---|-------|----------------------------------------------------------------------|-----|

|   |       | 2.9.2 Substrate Parasitic Model                                      | 38  |

|   | 2.10  | <b>5</b>                                                             | 43  |

|   |       | 2.10.1 Parasitic Macro-Devices                                       | 45  |

|   |       | 2.10.2 Virtual Interconnect Model                                    | 47  |

|   |       | 2.10.3 Adaptation of Dijkstra's Shortest Path Algorithm              | 53  |

| 3 | Analo | g Design Automation Frameworks                                       | 55  |

|   | 3.1   | Circuit Design Automation                                            | 56  |

|   |       | 3.1.1 Equation-Based Design Automation Methodologies                 | 59  |

|   |       | 3.1.2 Simulation-Based Design Automation Methodologies               | 60  |

|   | 3.2   | Modeling Parasitic Effects in the DSM Performance Space              | 61  |

|   | 3.3   | Existing Automation Approaches with Provisions for Parasitic Effects | 67  |

| 4 | Schei | natic and Placement Co-Optimization                                  | 70  |

|   | 4.1   | Independent Circuit and Physical Design Optimization                 | 71  |

|   | 4.2   | Collaborative Circuit and Physical Design Optimization               | 75  |

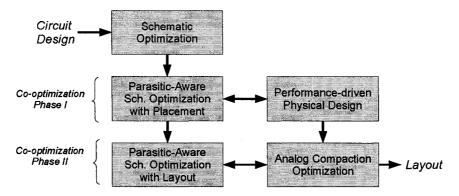

|   | 4.3   | Efficient DSM Analog Circuit Optimization                            | 77  |

|   |       | 4.3.1 Schematic Optimization                                         | 78  |

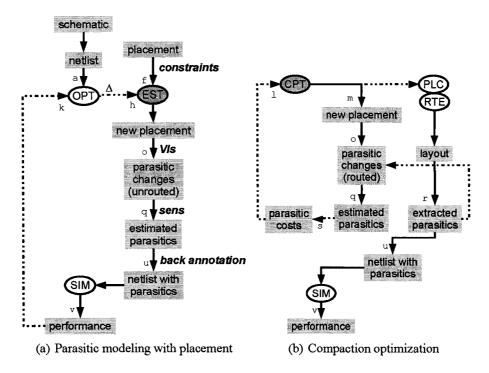

|   |       | 4.3.2 Parasitic-Aware Schematic Optimization with Placement          | 79  |

|   |       | 4.3.3 Analog Compaction Optimization                                 | 80  |

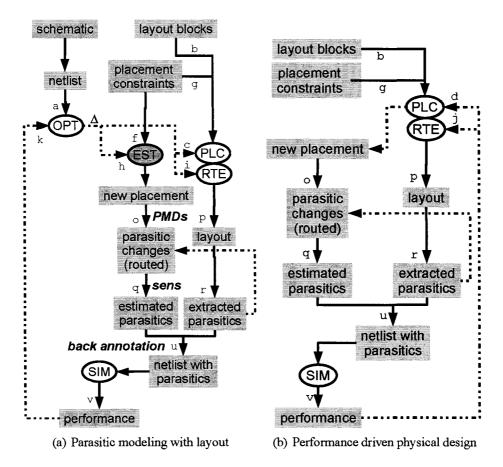

|   |       | 4.3.4 Parasitic-Aware Schematic Optimization with Layout             | 80  |

|   |       | 4.3.5 Performance-Driven Physical Design                             | 81  |

|   | 4.4   | Parasitic-Aware Performance Evaluations                              | 82  |

|   |       | 4.4.1 Sensitivity-Based Performance Variation Estimation             | 83  |

|   |       | 4.4.2 Performance Sensitivity Computation                            | 86  |

|   |       | 4.4.3 Parasitic Sensitivity Computation                              | 88  |

|   | 4.5   |                                                                      | 88  |

|   |       |                                                                      | 90  |

|   |       | 4.5.2 Simulated Annealing                                            | 92  |

|   |       | 4.5.3 Performance Cost Functions                                     | 93  |

|   | 4.6   | Implementation and Experimental Results                              | 94  |

|   |       |                                                                      | 97  |

|   |       |                                                                      | 100 |

|   |       |                                                                      | 105 |

| 5   |       | taneous Switching Noise-Aware PLL Jitter Model for System-on-Chip |     |

|-----|-------|-------------------------------------------------------------------|-----|

|     | Des   | ign Automation                                                    | 109 |

|     | 5.1   | Phase-Locked Loops in SoCs                                        | 110 |

|     | 5.2   | Efficient Modeling of Chip-Level Simultaneous Switching Noise     | 112 |

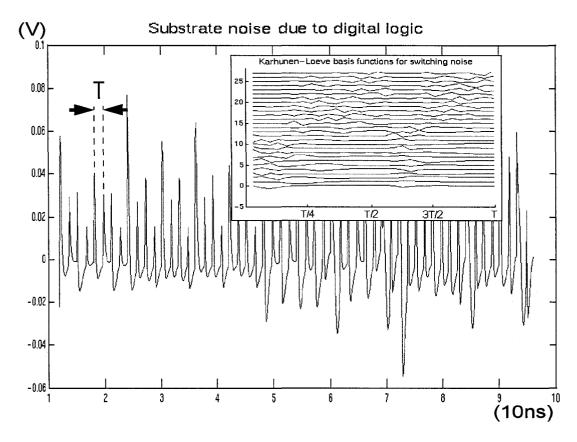

|     |       | 5.2.1 Cyclostationarity                                           |     |

|     |       | 5.2.2 The Karhunen-Loève Basis                                    | 116 |

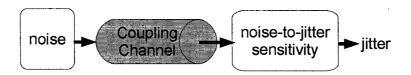

|     | 5.3   | Modeling the SSN Coupling Paths                                   | 119 |

|     | 5.4   | PLL Jitter Analysis                                               | 121 |

|     | 5.5   | Computation of SSN-Induced Jitter                                 | 123 |

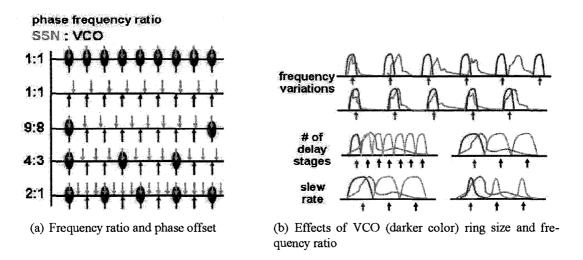

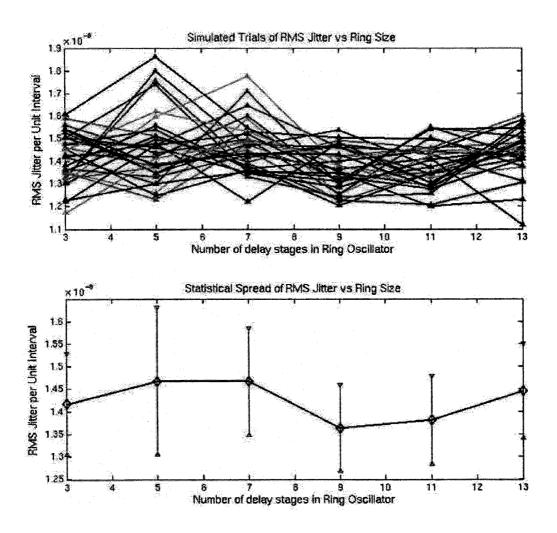

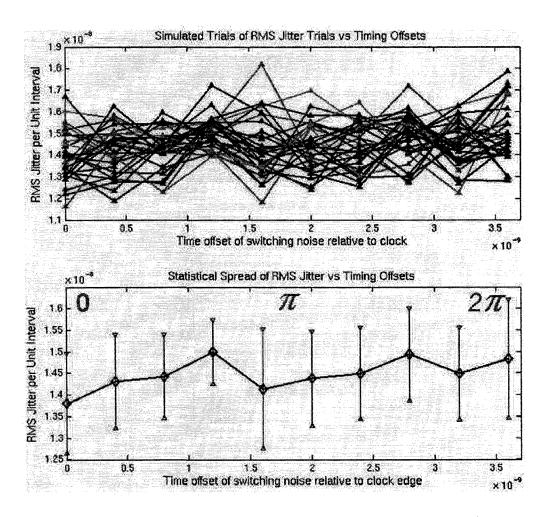

|     | 5.6   | Implementation and Experimental Results                           |     |

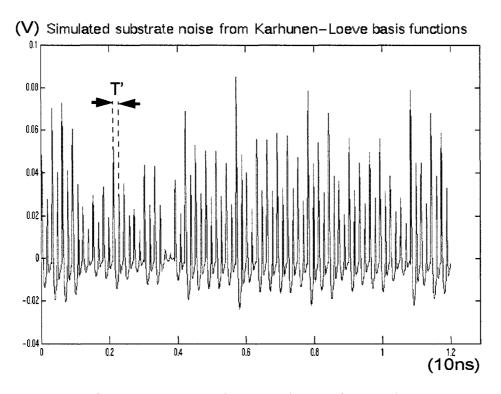

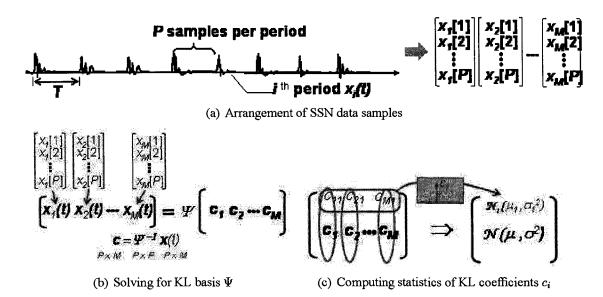

|     |       | 5.6.1 Karhunen-Loève Basis Functions Derivation                   | 126 |

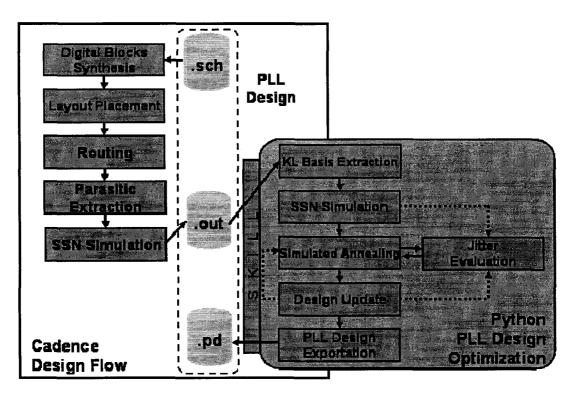

|     |       | 5.6.2 SSN-Aware PLL Design Exploration and Experimental Results   | 127 |

| 6   | Concl | usions and Future Directions                                      | 137 |

|     | 6.1   | Future Work                                                       | 139 |

| 7   | Apper | ndix                                                              | 141 |

|     | 7.1   | Derivation of Instantaneous Phase Lag Equation (5.12)             | 141 |

|     | 7.2   | Derivation of Mean-Square Phase Noise Equation (5.15)             | 142 |

| REF | EREN  | CES                                                               | 144 |

# LIST OF TABLES

| <u> Table</u> |                                                                                                                                         | page |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| 2-1           | Physical Orientations of Parasitic Devices                                                                                              | 19   |

| 4–1           | Types of Parasitic Effects Modeled                                                                                                      | 83   |

| 5–1           | Performance comparison between using the proposed jitter model and running Spectre simulator for computing SSN jitter for a 97MHz VCO . | 134  |

| 5–2           | Substrate coupling-induced jitter statistics for 7-stage ring oscillators after 50 periods over 20 trials                               | 135  |

# LIST OF FIGURES

| Figure       |                                                                                          | page |

|--------------|------------------------------------------------------------------------------------------|------|

| 1-1          | Schematic and placement optimization                                                     | 7    |

| 1–2          | Optimization-based circuit and physical design flow integration                          | 9    |

| 2-1          | Design and modeling hierarchy in IC design flows                                         | 14   |

| 2-2          | Interconnect parasitic models for optimization                                           | 19   |

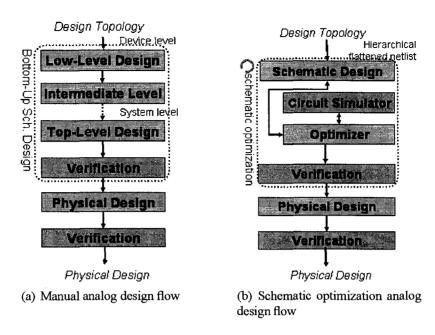

| 2–3          | Analog design flows                                                                      | 22   |

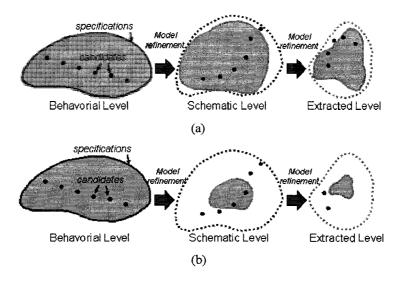

| 2–4          | Impact of parasitic effects on design spaces (a) non-DSM, and (b) DSM design refinements | 23   |

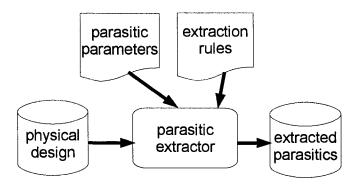

| 2-5          | Parasitic extraction process                                                             | 26   |

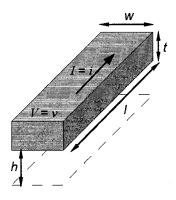

| 2-6          | Parasitic modeling for a simple cuboid object                                            | 27   |

| 2–7          | Interconnect parasitic values update                                                     | 29   |

| 2-8          | Layout template for interconnect sensitivities extraction                                | 30   |

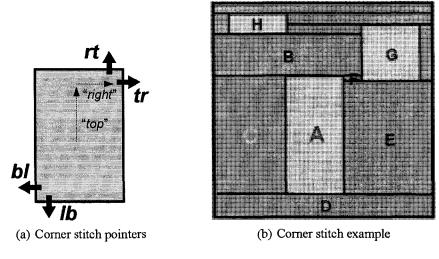

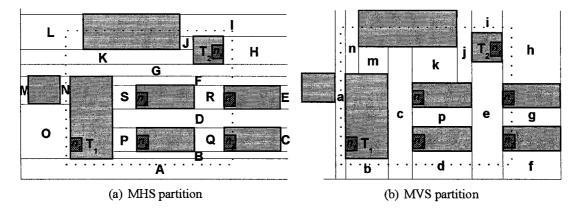

| 2–9          | Maximum horizontal strip partitioning                                                    | 32   |

| 2–10         | Corner stitch encoding scheme                                                            | 33   |

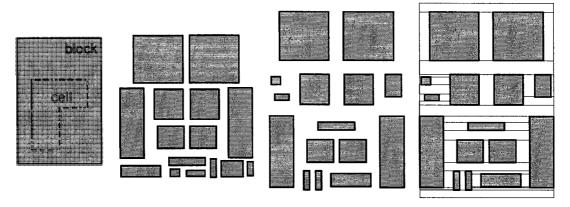

| 2–11         | Block as cell bounding box, block packing, block placement candidates and MHS placement  | 34   |

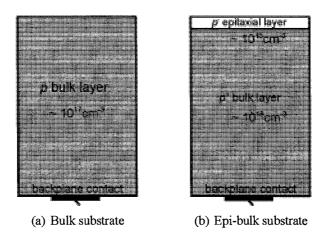

| 2-12         | 2 Cross-sectional diagram of common substrate types                                      | 37   |

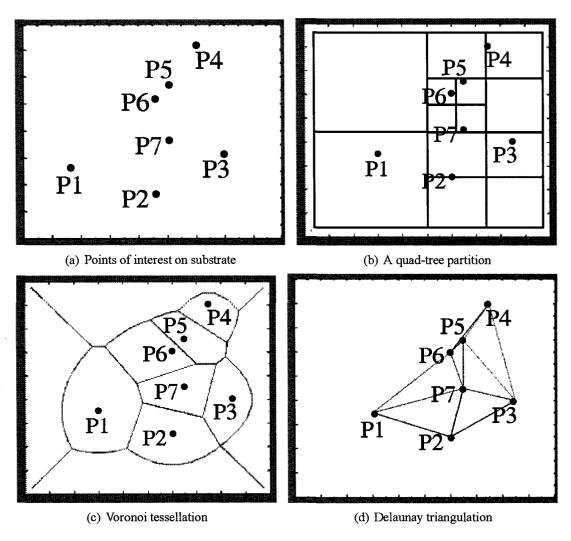

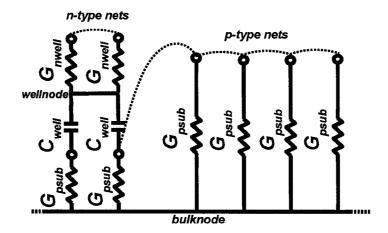

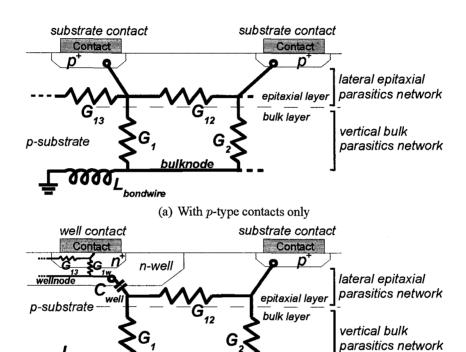

| <b>2</b> –13 | Substrate discretization for parasitic modeling                                          | 39   |

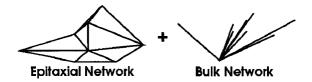

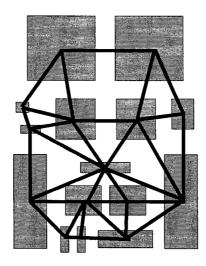

| 2-14         | Parasitic network of the CMOS epi-bulk substrate                                         | 39   |

| 2–15 | Top view of the epitaxial network $(G_{12})$ of the substrate model                                                                                                                                                                                                                                               | 40 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2–16 | Cross-sectional view of the bulk network $(G_1, G_2)$ of the substrate model. The dotted lines denote epitaxial network connections, among $n$ -type, $p$ -type and between $n$ - and $p$ -type substrate port nets                                                                                               | 41 |

| 2–17 | Cross-sectional view of substrate parasitic models                                                                                                                                                                                                                                                                | 42 |

| 2–18 | Interconnect parasitic modeling                                                                                                                                                                                                                                                                                   | 43 |

| 2–19 | Extraction of Parasitic Macro-Devices                                                                                                                                                                                                                                                                             | 44 |

| 2–20 | Parasitic Macro-Devices in a circuit                                                                                                                                                                                                                                                                              | 46 |

| 2–21 | Algorithm: Parasitic macro-device identification                                                                                                                                                                                                                                                                  | 47 |

| 2–22 | Terminals $T_1$ , $T_2$ to be connected, and the geometric partitions                                                                                                                                                                                                                                             | 48 |

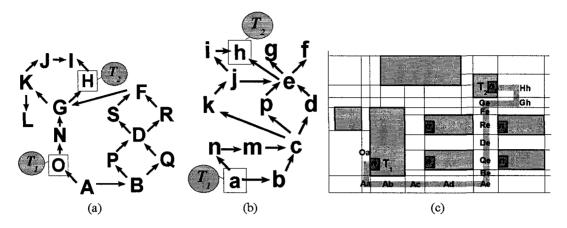

| 2–23 | Vacant tiles adjacency graphs for (a) MHS partition, and (b) MVS partition. (c) Virtual interconnect                                                                                                                                                                                                              | 49 |

| 2–24 | Algorithm: Route finding between terminals $T_1$ and $T_2$                                                                                                                                                                                                                                                        | 50 |

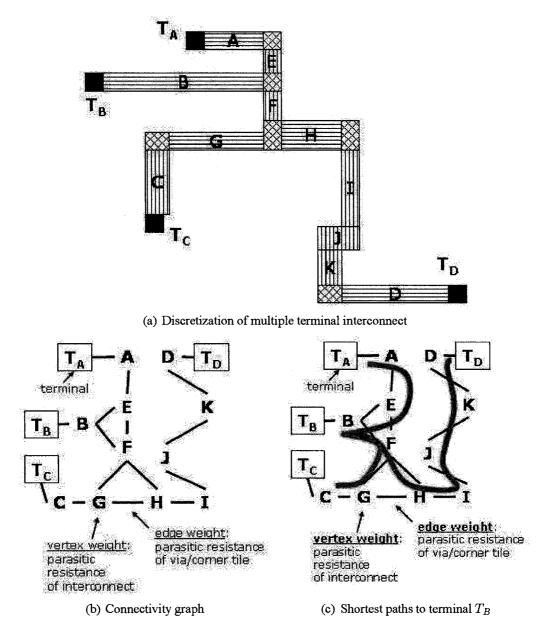

| 2–25 | Finding the shortest paths within a multiple terminal interconnect                                                                                                                                                                                                                                                | 52 |

| 2–26 | (a) Virtual interconnect model (b) Interconnect example                                                                                                                                                                                                                                                           | 53 |

| 2-27 | Algorithm: Dijkstra's shortest path algorithm                                                                                                                                                                                                                                                                     | 54 |

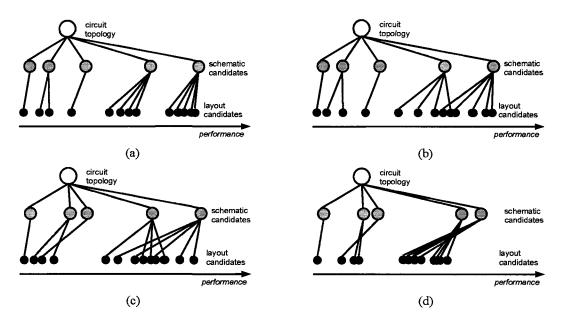

| 3–1  | Scenarios of design candidate performance (a) Type I: Small fabrication effects and small layout spreads, (b) Type II: Small fabrication effects and large layout spreads, (c) Type III: Large fabrication effects and large layout spreads, and (d) Type IV: Large fabrication effects and small layout spreads. | 63 |

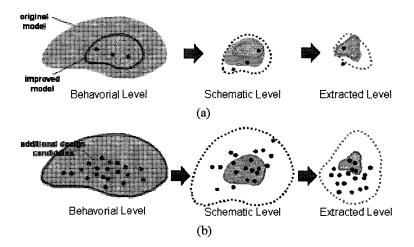

| 3–2  | Remedies of non-linear DSM effects on design spaces (a) more accurate models reflecting DSM effects, and (b) better design space coverage                                                                                                                                                                         | 66 |

| 41   | Simple simulation-based optimization flows                                                                                                                                                                                                                                                                        | 72 |

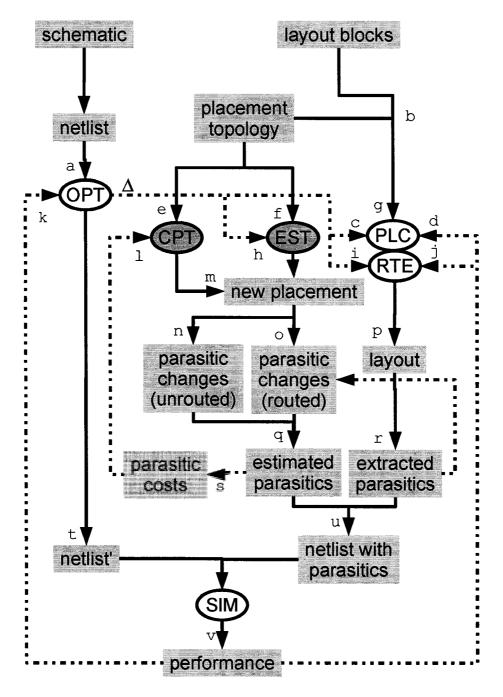

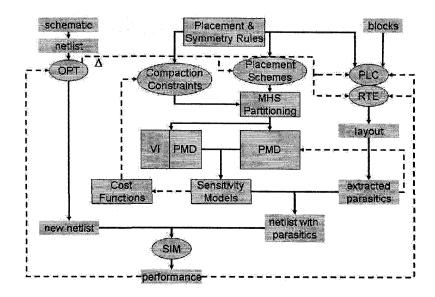

| 4–2  | Circuit and physical design Co-optimization. Solid and dotted arrows represent design advancements and information feedbacks respectively. CPT-Compaction, EST-Parasitic Estimation, OPT-Netlist Optimizer PLC-Placer RTE-Router SIM-Simulator                                                                    | 76 |

| 4–3         | Overall circuit and layout co-optimization flow                                                                                                                                                                | 78         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4-4         | Performance-Driven Physical Design - I                                                                                                                                                                         | <b>7</b> 9 |

| 4–5         | Parasitic-aware Design Automation - II                                                                                                                                                                         | 82         |

| 4–6         | Algorithm: Parasitic-aware schematic optimization                                                                                                                                                              | 84         |

| 4–7         | Algorithm: Parasitic sensitivity calculation algorithm                                                                                                                                                         | 89         |

| 4–8         | (a) Overlapping block placement constraints (b) MHS partition (c) Non-overlapping constraints derived from MHS partition                                                                                       | 90         |

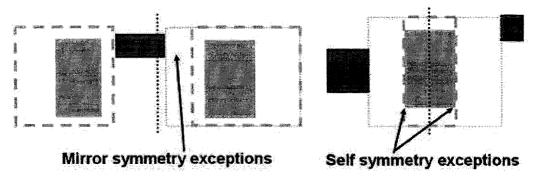

| 4–9         | Mirror- and self-symmetry exceptions on compaction constraints                                                                                                                                                 | 92         |

| 4–10        | Algorithm: Analog layout compaction optimization                                                                                                                                                               | 94         |

| 4–11        | Proposed optimization flow block diagram with standard CAD components: OPT-Netlist Optimizer, PLC-Placer, RTE-Router, SIM-Simulator                                                                            | 95         |

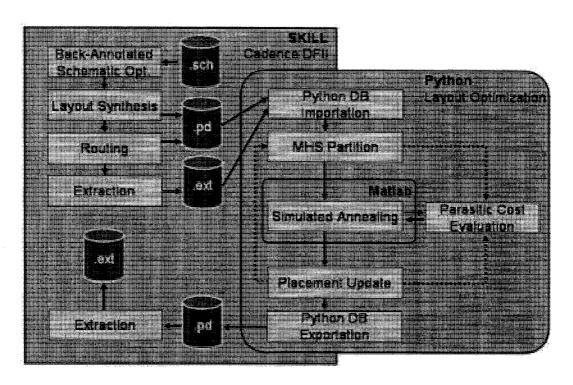

| 4–12        | Proposed optimization flow implemented in Python, SKILL and Matlab .                                                                                                                                           | 96         |

| 4–13        | Circuit data structure implemented in Python                                                                                                                                                                   | 97         |

| 4–14        | Extracted inline resistance and ground capacitance parameters $(Z_{inl})$ for $0.18\mu m$ for various interconnect (a) lengths, (b) widths, and (c) test chip for substrate parameters measurement experiments | 98         |

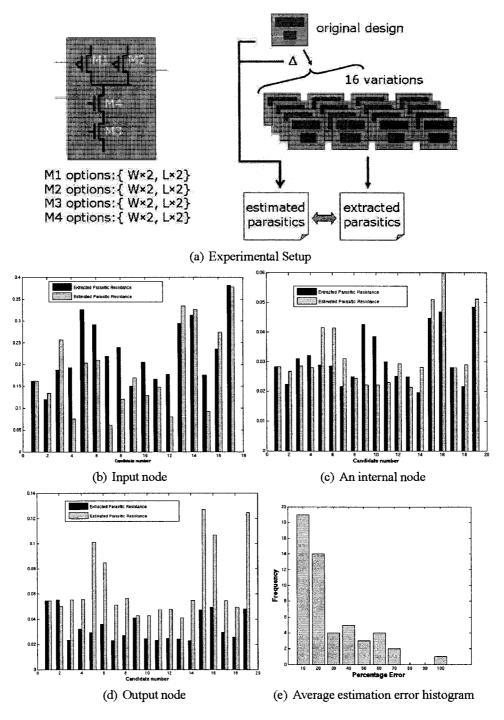

| 4–15        | Comparisons of extracted (dark bars) and estimated (light bars) $Y_{11}$ measured at various nodes                                                                                                             | 99         |

| 4–16        | Comparison of design candidates across multiple objectives in Synopsys Circuit Explorer                                                                                                                        | 101        |

| 4–17        | Query window for block symmetry properties definition                                                                                                                                                          | 102        |

| 4–18        | Comparison of simulated A/D Conversion delay (ns) of different design variables (pMOS W/L) and their average execution time (s) via different circuit models                                                   | 102        |

| <i>1</i> 10 | Completed differential operation amplifier layout                                                                                                                                                              | 10/        |

| 4-20 | $0.18\mu m$ differential OpAmp with and without parasitic modeling information                                                            | 105 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

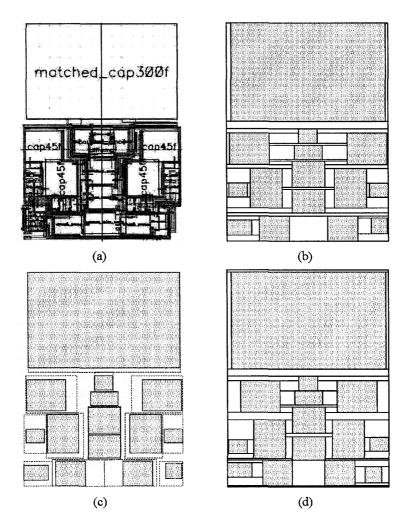

| 4–21 | (a) Placement extraction from layout (b) MHS partition (c) Compaction constraints (d) Optimized placement for OpAmp compaction            | 106 |

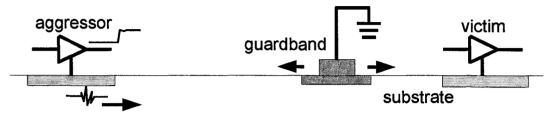

| 4–22 | Guardband placement optimization                                                                                                          | 107 |

| 5-1  | Ring oscillator PLL linear model                                                                                                          | 110 |

| 5–2  | Simulation setup of SSN-induced PLL jitter                                                                                                | 111 |

| 5–3  | Substrate coupling due to digital logic switching activities and its KL basis functions (inset figure)                                    | 114 |

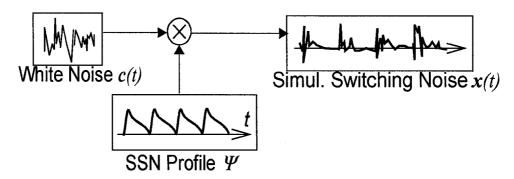

| 5–4  | Equivalent model of SSN generation from noise profiles derived from substrate coupling simulations                                        | 115 |

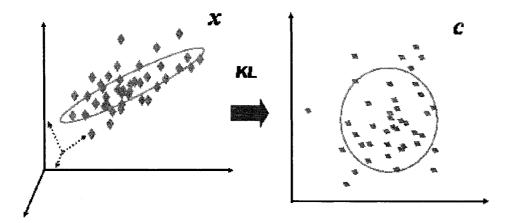

| 5–5  | Dimensional reduction and removal of variable correlations from <i>feature</i> space x to the <i>transform space</i> c through KL mapping | 117 |

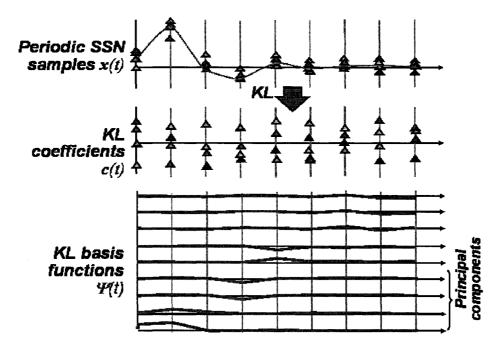

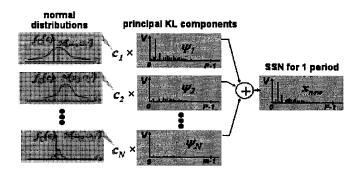

| 5–6  | Example of KL basis extraction and its corresponding distribution of coefficients from data samples                                       | 117 |

| 5-7  | KL model-generated new noise samples                                                                                                      | 118 |

| 5–8  | SSN generation from reduced-order SSN model                                                                                               | 119 |

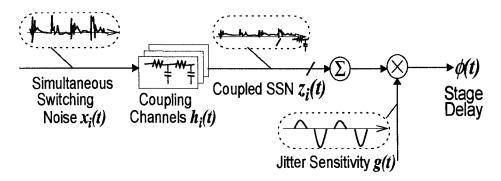

| 5–9  | Noise-to-jitter transfer model                                                                                                            | 120 |

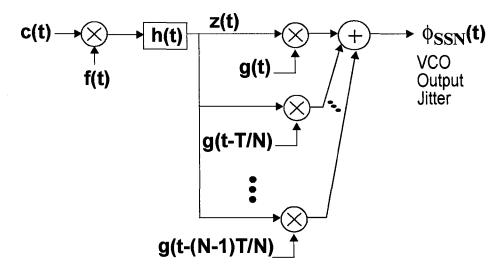

| 5-10 | N-stage ring oscillator output jitter model                                                                                               | 124 |

| 5–11 | Details of KL-based SSN model construction                                                                                                | 128 |

| 5-12 | PLL circuit and physical design co-optimization                                                                                           | 129 |

| 5–13 | Correlations between VCO and SSN in time domain                                                                                           | 129 |

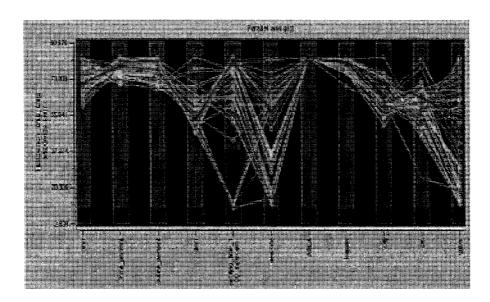

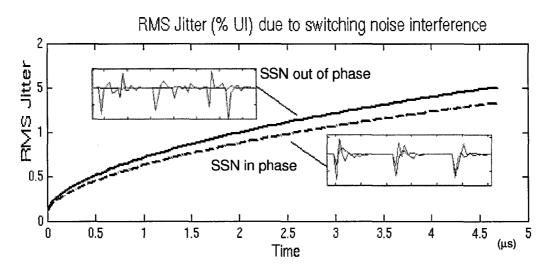

| 5-14 | RMS jitter with various ring sizes                                                                                                        | 131 |

| 5-15 | RMS jitter with respect to phase offset between VCO and SSN                                                                               | 133 |

| 5-16 | RMS jitter with SSN from 2 clock domains with different phase                                                                             | 134 |

## LIST OF ABBREVIATIONS

AC ... Alternate Current

BEM ... Boundary Element method

BJT ... Bipolar Junction Transistor

CAD ... Computer-Aided Design

CDR ... Clock Data Recovery

CI ... CMOS Inverter

CMOS ... Complementary Metal-Oxide Semiconductor

CP ... Charge Pump (PLL component)

DA ... Differential Amplidiers

DC ... Direct Current

DSM ... Deep Sub-Micron

ECO ... Engineering Change Order

EDA ... Electronic Design and Automation

EM ... Electro-magnetic

FEM ... Finite Element Method

HDL ... Hardware Description Language

IC ... Integrated Circuit

KL ... Karhunen-Loève

LF ... Loop Filter (PLL component)

MEMS ... Micro-Electro-Mechanical Systems

MHS ... Maximum Horizontal Strip

MOSFET ... Metal-Oxide Semiconductor Field Effect Transistor

MVS ... Maximum Vertical Strip

OpAmp ... Operational Amplifier

OPC ... Optical Proxmity Correction

OPT ... schematic optimization (Co-optimization flow)

PD ... Phase Detector (PLL component)

PDF ... Probability Density Function

PDK ... Process Design Kit

PLC ... Placement (Co-optimization flow)

PLL ... Phase-Locked Loop

PMD ... Parasitic Macro-Device

PSS ... Periodic Steady State

RF ... Radio Frequency

RMS ... Root Mean Square

RTE ... Routing (Co-optimization flow)

RTL ... Register Transfer Level

SA ... Simulated Annealing

SIM ... Circuit Simulator (Co-optimization flow)

SoC ... System-on-Chip

SSN ... Simultaneous Switching Noise

UI ... Unit Interval

VCO ... Voltage-Controlled Oscillator

VI ... Virtual Interconnect

VLSI ... Very Large Scale Integrated Circuit

## **CHAPTER 1**

# Introduction

The exponential increase in the density of transistors on a silicon chip with time has been a prominent trend in the semiconductor industry. Gordon E. Moore predicted in 1965 that transistor count would increase by a factor of 2 for every 18 months. This is confirmed repeatedly by numerous surveys conducted by *International Technology Roadmap for Semiconductors* (ITRS) [10] and is now known as the *Moore's Law*. It serves as the well-respected basis for predictions of future technology growth trends. The growing number of smaller devices implies that if the accompanying issues of increased design complexity and defects affecting production yield can be overcome without significant cost increase, continual functional and performance improvements of a chip are possible at the same cost. Examples are new system-level design paradigms to take advantage of improved performance, better design and testing tools to handle increasingly complex and dense circuits, lithography techniques with higher resolutions and geometric correction techniques to compensate for optical diffractions, etc.

To reduce packaging cost and long-term reliability issues, digital and analog circuits are often integrated together onto the same silicon die. While such *mixed-signal* systems provide improved performance as packaging and some interconnect parasitics are minimized, new interference issues arise. Analog design must adapt and maintain its robustness towards this new operation environment in order to preserve the data quality of the overall system.

Electronic design automation (EDA) tools are software applications that aid designers in the productivity of designing complex integrated circuit (IC). Until recently, the majority of EDA research and development activities were targeted towards digital designs. Even though more and more circuit functionality is being performed in the digital domain due to its superior robustness against noise and interference, certain analog circuits, such as filters, amplifiers, analog-digital converters, PLL, etc., are irreplaceable and remain an integral part of most systems. On the contrary, advancements towards ubiquitous computing [71] in the fields of wireless and micro-electro-mechanical systems (MEMS) sensor technology will continue to propel the need of analog integration into the foreseeable future. With reduced product lifecycle, shrinking fabrication minimum feature sizes and increasing clock rates, a successful EDA flow must achieve rapid design closure amid strong parasitic influences. Hence, an effective analog EDA flow is crucial for any modern mixed-signal designs to meet the required overall performance objectives efficiently.

A typical IC design cycle involves the following steps:

- System design and verification

- Functional design, partition and verification

- Circuit design and verification

- circuit topology selection

- component selection and simulation

- Circuit verification and noise analysis

- Physical design and verification

- Floorplanning, die size estimation and packaging selection

- Block placement

- Global and detailed routing

- Parasitic extraction and simulation

- Post-extraction verification and noise analysis

- IC fabrication, test, packaging

- Product testing

Each of the above steps can be done manually, automatically or semi-automatically with designers and design aids. The order of these steps are based on a *top-down* hierarchy of models that become progressively more complex. In summary, preliminary functional correctness is first addressed using simple models to simplify the design problem. The design process is repeated again at the next lower level, as more detailed elements and thus design freedom are introduced. Although design processes can occur at functional, circuit and physical levels in the general flow, most of the design processes are performed primarily at one level. The abstraction level where the majority of design processes take place is dictated by the size and complexity of the target system. In the modeling point of view, the predominant IC design paradigm takes the following pattern:

- Design: Perform design processes at the modeling level with the simplest circuit

models (highest modeling level) that is practical and effective to cover the system

properties concerned.

- Implementation: Design refinement towards the physical level with refined circuit models using newly obtained information. Verify if performance is within required specifications.

- Verification: Compare refined performance measures with required specifications.

Additional performance margins may be needed to accommodate subsequent performance degradations due to unencountered effects.

- Re-iteration: If performance degradations exceed margins, back-track to the previous level and attempt an alternative design. The process ends when the performance of an implementable design satisfies the required specifications.

Since lower-level effects are absent from current-level models, the decision of designing circuits at a certain abstraction level implicitly determines which types of effect are significant enough to be revealed and examined and which ones are left to be absorbed by performance margins and verified afterwards. This imposes an important efficiency-accuracy trade-off.

For example, digital systems with billions of gates are designed at the system level. Through abstractions using *Boolean algebra* and various *hardware description languages* (HDLs), large systems can be designed efficiently from the top system level to the *register-transfer level* (RTL) down to the gate level. This system is then *verified* at the circuit and physical levels, via synthesis tools. Performance degradations due to lower-level effects can usually be absorbed by design margins. This is possible due to the wide noise margin.

Otherwise, local design refinements that remedy the violations usually suffice. This is possible due to well-defined signal boundaries between subsystem interfaces. On the other end of the spectrum, *radio frequency* (RF) circuit design requires very detailed modeling of each component used. However, due to its small size, they are often designed directly at the schematic and physical levels.

Curiously, as much as they are different, digital and RF designs share a significant property in the interest of layout parasitic modeling, the *regularity* of the design topology. Dimensions and spacings of digital layout are highly regular in order to facilitate efficient automatic generation. Its noise robustness affords the use of suboptimal, simplified layout design. RF designs also have high degree of conformity from one version to another, due partly to the small number of components and the reliance of test data from previous versions.

Parasitic modeling benefits from predictability of the layout parasitics of both design types. For example, wire-length delay correlations, analytical computations of bus wires crosstalk and reflection [61] are possible due to the uniform widths and signal characteristics. *A priori space mapping* [72] of layout-based RF design is practical due to the layout and parasitic properties being known.

Analog circuit design is usually performed at the circuit, or *schematic*, level with simplified circuit models, which do not adequately capture its layout effects. High performance analog circuits require optimized physical design to attain their performance requirements. It is also too complex for equation-based parasitic modeling except for the very smallest designs. As the differences in actual and predicted performance remain unknown, the limited error margins are maximized to increase design closure probability,

and as a result, counteracting the performance advantage offered by the new technologies. Hence, predicting the layout effects of an irregular and noise sensitive analog circuit design remains a formidable challenge. A better approach is needed in the age of aggressive design specifications where performance margins come at a premium.

#### 1.1 Problem Description

Simulation-based device sizing optimization has been proved successful in efficiently exploring the circuit design space at the schematic-level and delivering a near-optimal solution. As the IC industry continues to adopt advanced fabrication technologies with progressively smaller minimum feature sizes, circuit performance becomes strongly influenced by layout-dependent parasitic effects, in additional to device sizings. This compromises the effectiveness of schematic-level optimization since a well-performing schematic design does not imply robustness towards layout effects. Unfortunately, formal extraction of these parasitic effects is not possible until the physical design is finalized. A new framework that efficiently furnishes layout effects of the candidates during the circuit design process is badly needed. Rutenbar [55] stated that the key criteria for the next-generation analog design automation tool are: (i) the integration of independent point tools, (ii) design constraints extraction, management and reuse, and (iii) system-level design optimization and exploration. This thesis contribute novel concepts and provisions towards solving these issues.

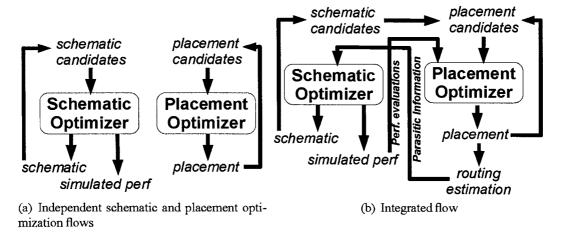

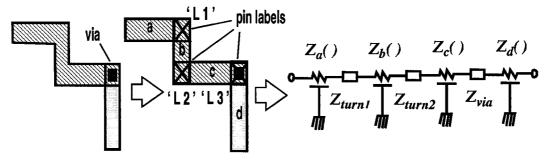

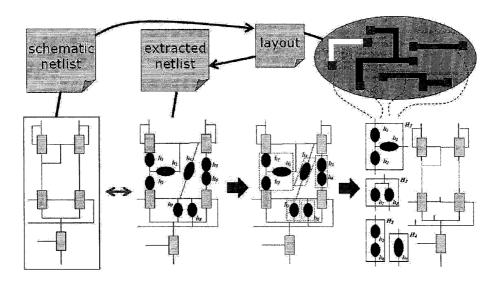

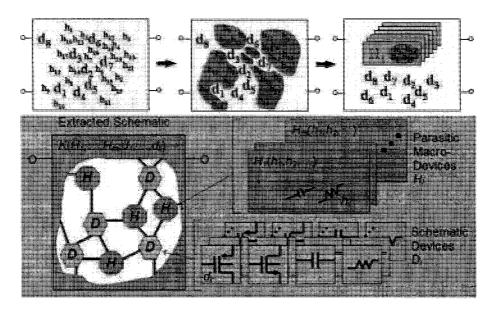

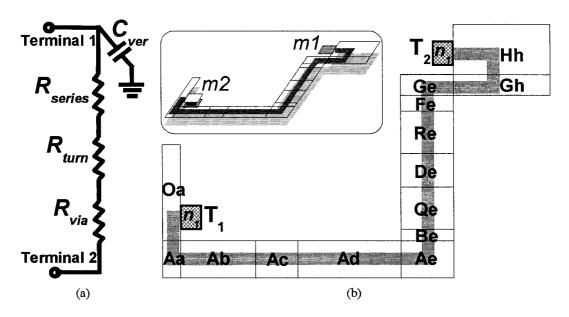

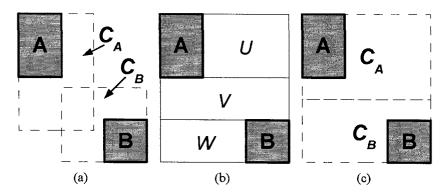

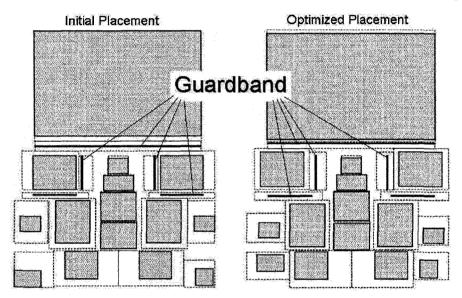

Figure 1–1: Schematic and placement optimization

#### 1.2 Original Contributions

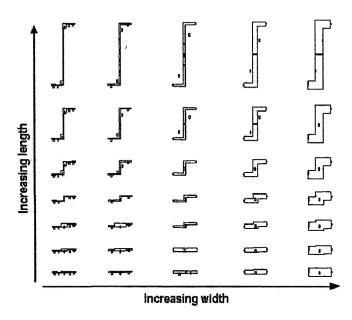

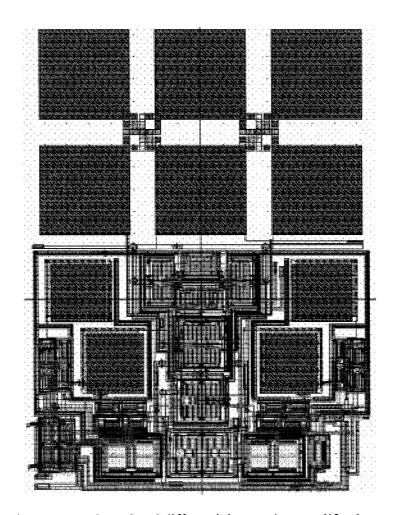

This thesis is based on a series of published research papers on incorporation of parasitic effects in analog design automation [22], [12], [23], [24], [21], [20], [19]. To enable layout-aware circuit optimization for *full-custom* analog designs, this research proposes the integration of currently independent circuit and layout optimization steps (Fig. 1–1(a)) to enhance the convergence among the optimized circuits and their post-extracted performance in the presence of layout parasitic effects. The challenges for next-generation analog design automation tools [55] in the DSM era are addressed in this thesis through careful extraction, exchange and reuse of parasitic and performance information between the circuit and layout optimization loops. As illustrated in Fig. 1–1(b), parasitic information from layout optimization is feedback to the schematic optimizer, in exchange for the performance information of the layout. The improved quality and efficiency of the integrated loop make system-level accurate performance space exploration possible. None of the currently offered optimization techniques encompasses layout effects without involving proprietory cell libraries, thereby compromising design flexibility.

Through a tool-independent and library-independent circuit and physical design cooptimization methodology, the optimization flow proposed here incorporates parasitic estimations in the optimization loop by extrapolating extracted parasitic values according to

anticipated layout modifications. In return, the physical design flow reuses the simulation

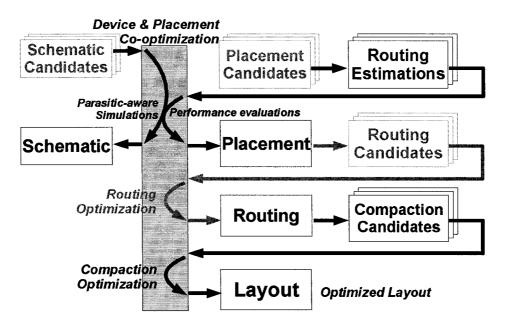

results for performance-driven layout optimization. Fig. 1–2 illustrates the implementation

of the proposed parasitic-aware design automation methodology, compatible with off-theshelf EDA components. Through information exchanged by sharing database and intermediate results, both schematic and layout optimization routines mutually benefit from

each other's optimization results and thus improve their effectiveness. On the left side of

Fig. 1–2, the simulation-based optimization flow tunes device sizes on the schematic at the

presence of layout-effect parasitics. Layout effects are taken into account through annotation of parasitic effects derived from layout optimization. Optimized circuit parameters

and performance data are then fed into the physical optimization flow on the right side.

#### 1.3 Claims of Originality

The thesis has contributed the following new concepts and techniques:

#### Parasitic-Aware Analog Schematic Optimization Algorithm [21][23]

Existing simulation-based schematic optimization engine tunes performance based solely on device sizing. This thesis proposes the back-annotation and estimation of layout parasitics through computation of the block displacement and the change of interconnect geometry of a preliminary layout due to device sizing changes. Layout changes are modeled after the behavior of human designers to yield realistic results. The method has been

Figure 1–2: Optimization-based circuit and physical design flow integration

adopted by research groups for Circuit Explorer of Synopsys Inc. and Creative Genius of Analog Design Automation Inc..

#### Parasitic-Aware Analog Layout Compaction Algorithm [24]

This thesis proposes a performance-driven, parasitic-aware compaction algorithm for analog layout. Current methods are mostly geometric-driven without DSM parasitic insights, such as substrate coupling. The proposed compaction optimization is carried out to fine-tune block placement while balancing the often opposing substrate coupling and interconnect parasitic effects.

#### Parasitic Macro-Device Concept [21][24]

This thesis proposes a novel concept that treats wires and interconnect in a circuit as "devices". An algorithm identifies clusters of parasitic devices in the post-extraction netlist and encapsulate each of them as an n-port Parasitic Macro-Device. Identity of the

corresponding wire or interconnect is stored in its property list. Consequently, the topology of the modified post-extraction netlist circuit graph is consistent from one extraction to another, which enhances the ease of model-building process for parasitic estimation.

#### Simultaneous Switching Noise Models [22]

Simulation of DSM performance of high-performance mixed-signal systems such as *system-on-chips* (SoCs) often involves transient excitations of large number of circuits in order to generate the realistic switching noise level during nominal operations. In Chapter 5, a reduced-order chip-level simultaneous switching noise model is proposed. Model order reduction is achieved through the novel application of *Karhunen-Loève* transformation [38] to capture and reproduce the essence of noise signatures from available noise samples.

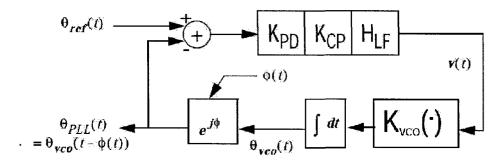

### Cyclostationary Jitter Model [19][22]

PLL jitter simulation is time-consuming, due to the small time resolution needed relative to the simulation time interval. A compact model is derived to estimate the periodic steady-state PLL jitter due to substrate coupling and external interference by exploiting the temporal correlations between noise and the clock signal. This work is cited by [60].

#### 1.4 Thesis Outline

In Chapter 2, fundamental information about parasitic effects in silicon *integrated* circuits (ICs) is given. Resistive, capacitive and inductive parasitic effects are introduced. Several practical approaches, based on either the boundary element method (BEM) or the finite element method (FEM) are explained to extract these effects in ICs. In Chapter 3, the basis of various design automation schemes are presented. Manual schematic-level

design are replaced by optimization-based circuit design methodologies. Complex floorplanning and routing problems also served by search-based physical design automation tools. Parasitic effects, however, are not dealt with until after the physical design process is completed. In Chapter 4, a co-optimization strategy that links schematic and layout optimizations together is presented. The layout optimizer provides accurate parasitic information to the schematic optimizer, while the schematic optimizer gives quantitative performance evaluation results to aid the physical design process. This exchange of crucial information is a major contribution to the improvement of design closure efficiency under the influence of parasitic effects in an automated flow. A detailed example using this proposed co-optimization methodology is presented in Chapter 5. In this chapter, circuit and physical design options are optimized via PLL jitter analysis over design parameters, SoC module and noise barrier placements using *periodic steady state* (PSS) analysis. The scope of design considerations including the effects of aggressive system integration and guardband configurations exceeds the capabilities offered by conventional computer-aided design tools. Finally, the conclusions and implications of this work are discussed in Chapter 6.

## **CHAPTER 2**

# FUNDAMENTAL CONCEPTS AND GROUNDWORK

This chapter consists of two parts. The basic concepts of the conventional circuit design flow, regarding layout-related parasitic effects, the extraction process and how they impact the effectiveness of the IC design flow will be represented. Next, the contributions and implementation of essential components for the proposed co-optimization flow, such as parasitic modeling for placement and routing, sensitivity analysis, representation methods of circuit and the physical design will also be discussed thoroughly.

#### 2.1 Analog Circuit Design

Analog circuitry plays an important role in interfacing between real world information and with signals of complex digital systems. Deep sub-micron (DSM) integration brings about aggressive technology scaling to accommodate sensitive analog and complex digital systems onto a single chip. The mixed-signal systems gain performance advantages by aggressively adopting the latest digital processes. New issues affecting analog circuit development include rapid fabrication process migration, and the sharing of a typically noisy operating environment with digital systems. Specifically, the traditional analog circuit design cycle is being shortened, while the interconnect, packaging and substrate parasitics greater contributions to performance degradation.

A circuit topology is the interconnection of subcircuits and elementary components such as Bipolar Junction Transistors (BJTs), Metal-Oxide Semiconductor Field-Effect Transistors (MOSFETs), resistors (R), capacitors (C) and inductors (L). Traditional analog circuit design begins by drafting the schematic-level topology of the system and then determining the design variables for all components. Circuit design at the schematic level provides good balance between prototyping ease and simulation accuracy. Depending on the size of the system, it can be partitioned into several subsystems, where each part is determined independently. Complex systems can be built hierarchically by encapsulating subcircuit blocks with well-defined interface ports. The topology defines a schematic model of the circuit that designers rely on to evaluate characteristics of the circuit and assign device sizes. The schematic design process is usually carried out through a front-end graphical user interface, where the simulation tool extracts the underlying circuit netlist for simulation. The device sizing of each subsystem at each hierarchical level subcircuit is then performed. The result is a sized schematic of the system.

To simplify a complex circuit design problem, the system concerned is divided into a number of parts, or *subcircuits*. The *design hierarchy* is a set of system partitioning

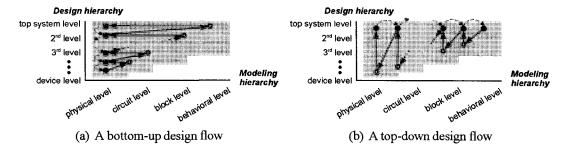

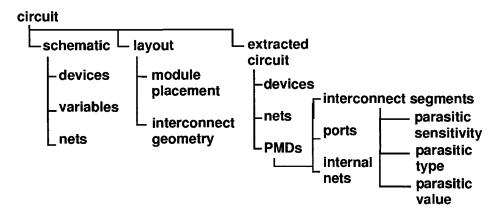

Figure 2-1: Design and modeling hierarchy in IC design flows

schemes that ranges from a collection of subcircuits containing a single device at the bottom level, to containing the entire system at the top. To preserve computation efficiency, modeling details are moderated according to the subcircuit scope. The amount of electromagnetic phenomena involved with even a small subcircuit can be daunting [48], hence only the most significant phenomena are considered if the model scope is large, whereas a more detailed circuit model can be used if the subcircuit under consideration is small. The array of models that describe circuit behaviors from the coarse behavioral to accurate physical models is known as the *modeling hierarchy*. Fig. 2–1 shows how the design and modeling hierarchies interact in the IC design flow. While the modeling hierarchy is always traversed in a top-down manner (right to left in Fig. 2–1), the design hierarchy can either be traversed from the bottom device level up to the top system level, or vice versa.

The *bottom-up* approach starts at the bottom-left corner in 2-1(a) with elementary components or small component groups created independently and then assembled together at a higher design hierarchical level. It progressively selects from the available design options and if these subcircuits pass the evaluation criteria, they are propagated to the next level. At the top level, the completed system is verified. The advantage of this approach is that from device model and sizing parameters upward, lower level details are

known and used in the evaluation at each level, hence no performance approximations or assumptions are needed. Its major drawback is that the overall performance of the eventual system cannot be easily verified and tracked during the intermediate stages with a set of unconnected subsystems.

The *top-down* approach in 2–1(b) begins with the top-level system behavioral model at the upper-right corner. The model is then replaced by a number of lower-level block that satisfy the respective performance specifications. The interface and specifications for each lower-level blocks are then assigned. This refinement process is repeated until all lower-level blocks are replaced by elementary components. While an intact system model is always present during each stage of the model refinement process, these models necessitate performance assumptions in the modeling of lower-level details before they are known. Piecewise functions can model certain non-linear effects within some limits. Exceeding them, accurate models for highly non-linear effects become expensive while evaluations based on simple models can be misleading.

The differences between the top-down and bottom-up flows explain why the top-down design style is effective in digital systems, and that it causes considerable difficulties when applying directly to analog circuits, due to the existence of complex dependencies among design variables and performance measures. Although the bottom-up approach is effective when subcircuit behaviors are inter-related with unknown or ill-defined interfaces, analog and digital component must be refined and verified in tandem in mixed-signal system design. Estimated parasitic-aware circuit models are thus needed to enable a top-down analog flow.

#### 2.2 Parasitic Effects in Integrated Circuit Design

For silicon fabrication, more details of the physical design of the circuit, such as the specific location, shape, dimension and material for every component and interconnect wire, are needed. It begins with floor-planning, followed by determining the dimensions of subsystem blocks. This is then followed by arrangement of the packing configuration of the blocks and the placement of device layout on the die. Finally all necessary nodes are connected corresponding to the given schematic. These steps must all be carried out respecting the given physical design rules and some matching and symmetry constraints, with considerations regarding the consequential fabrication random process variations. Parasitic coupling inherited from the design are extracted from the physical design and evaluated against the required specifications, to ensure that it has not been degraded from that of its schematics. The evaluated information can be used to refine the physical design. Compared to schematic design, physical design is time-consuming, and will typically be performed after its schematic-level performance is satisfactory.

Electrical circuits are interconnections of *electronic devices* that implement certain functions through the interactions of voltage and current among the electrical nodes. Circuits are usually described textually by the connection *netlist* or a graphically by *schematic* drawing. With conventional *very large scale integrated circuit* (VLSI) fabrication technologies, the interconnects are routed through a stack of connected planar metal layers. Below, transistor devices are embedded in, or are on the surface of the silicon substrate, which provides mechanical support to the circuit. The geometric design of this physical implementation is commonly known as the *layout* of the circuit. Parasitic effects are the consequences of the particular implementation of the electronic circuits. This includes the

specific geometry and material choice of the respective layout. These layout-dependent parasitics are created by a special program, the *parasitic extractor*, through examination of the geometry and interaction among all layout shapes. Exact details of the extraction are governed by the *extraction rule deck*, which is a set of rules and other specifications, found in the *process design kits* (PDK). The rule deck varies for different fabrication processes, and changes within a process when either the process properties change or certain parasitic models are refined. The extracted parasitic devices are inserted into the schematic netlist, forming the extracted parasitic netlist or simply the *extracted netlist*.

In the context of this thesis, the term parasitic applies to interactions among circuit nodes that do not belong to the intended idealized schematic design. It includes devices inserted by designers representing the estimated parasitic effects. On the other hand, designers often rely on parasitic effects to implement passive devices. They are considered intentional devices instead of parasitics. Whenever there are potential differences between any two conductors in a network, an electric field is present between them. Analogously, a magnetic field is present around any conductor that carries current. The strength of the fields attenuate over separation distances at rates that corresponding to the properties of the insulating material. Ideally, interconnects are perfect conductors, while disconnected devices and nodes in the circuit are completely insulated from each others. In VLSI, insulations are provided by poor conductors, such as silicon dioxide, air gaps, as well as by means of reverse-biased p-n junction potentials. They reduce most but do not completely eliminate induction among signals. Besides, interconnect wires have small but non-zero resistances that hamper signal propagations. These physical properties are generally known as *layout parasitic effects*. Their consequences of the implemented circuits are

departures from predicted behaviors of their schematic models. However, these parasitic effects also provide several means to integrate on-chip passive devices, such as resistors, capacitors and inductors.

At frequencies greater than a few GHz, the amount of self-inductive effects and signal reflections due to impedance mismatch becomes significant [6]. In these cases, the parasitic effects can be modeled by inline impedances containing inductors. For most analog applications, the operating frequency is usually lower than a few GHz and parasitic inductive effects can be safely ignored.

During circuit operation, a small but measurable amount of charge can leak from one node to another through the insulation. This diversion of charge following the signal paths is known as *leakage current*, and is modeled by auxiliary conducting paths using parasitic resistors. Although the magnitude of leakage current is negligible at its sources in most cases, the combined effect looms as a critical factor with a large number of leakage sites. For instance, consider a multi-million gate microprocessor chip fabricated in 130nm technology with supply voltage of 1.2-1.3V, the total leakage current constitutes 10-30% of its active power [54]. At the 70nm node with supply voltage less than 1.0V, over 50% of the overall power dissipation is due to leakage current [54].

For long wires, signal levels may decrease with distance travelled due to resistance of wire material as it travels further from the driving gate. This effect is known as *IR drop*, and can be modeled by an inline resistor. Along neighboring wires, signal activities may also couple voltages or induce currents across neighboring conductors. These are commonly known as *parasitic coupling*. EM fields are ubiquitous, hence a multiple-port network is needed to describe the parasitic effects between every node pair in general. In

Table 2-1: Physical Orientations of Parasitic Devices

| PARASITIC TYPE                         | ORIENTATION |

|----------------------------------------|-------------|

| Interconnect resistance                | inline      |

| cross coupling capacitance             | lateral     |

| substrate coupling near surface        | lateral     |

| Interconnect capacitance to ground     | vertical    |

| well capacitance                       | vertical    |

| substrate bulk to bulk node resistance | vertical    |

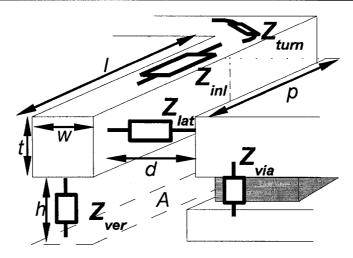

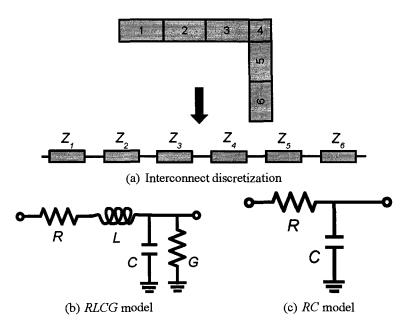

Figure 2-2: Interconnect parasitic models for optimization

practice, the parasitic extractor would determine the significant parasitic effects of the layout, and annotate the circuit netlist with 2-port passive devices. Fig. 2–2 illustrates generic examples of these parasitic device types. They can be modeled by parasitic capacitors and inductors. Layout parasitic effects can be classified into *inline parasitics* that take place *along* the direction of intended signal propagation, *lateral parasitics* that take place *across* the intended signal paths, and *vertical parasitics* that are *perpendicular* to the substrate surface. They respond to layout changes differently. Table 2–1 lists the classification of common parasitics found in CMOS.

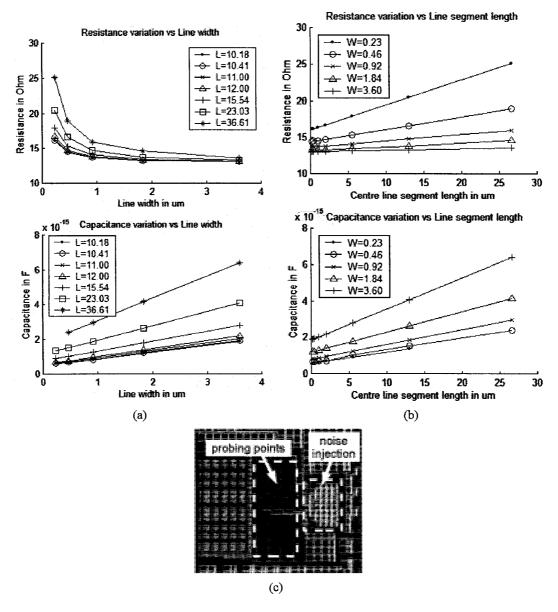

Fig. 2-2 illustrates the generic view of several parasitic device types.  $Z_{inl}(l, w)$  includes interconnect resistances and self-inductances along interconnect segments, it varies according to the length l and width w of the interconnect segment.  $Z_{lat}(p,d)$  refers to lateral cross-coupling capacitances and mutual inductances among neighboring objects of the same layer, it varies with their separation distances d and overlapped length p.  $Z_{ver}(A)$  denotes vertically-oriented capacitance, inductances between interconnects of different layers. Ignoring the fringing effects [61], the capacitance is proportional to the projected area A. Layer thickness t is fixed throughout layout synthesis. Finally,  $Z_{turns}(w)$  and  $Z_{via}$ model respectively the additional impedances for turns and via in the interconnect. These parameters are usually available with the fabrication PDKs. Otherwise, a layout test set containing straight and one-turn wires of variable widths can be set up once for each process technology to obtain the necessary parasitic model parameters  $Z_{inl}$ ,  $Z_{lat}$ ,  $Z_{ver}$ ,  $Z_{turns}$ and  $Z_{via}$ . Additionally, parameter sensitivities with respect to geometric dimensions  $\frac{\partial Z_{inl}}{\partial l}$ ,  $\frac{\partial Z_{lat}}{\partial p}$  and  $\frac{\partial Z_{ver}}{\partial A}$  are also derived for parasitic estimation purposes. Extracted values and sensitivities of resistances and capacitances of various interconnect widths and lengths are discussed in Section 2.5. Discussion of substrate and interconnect discretization for parasitic modeling follows next.

The parasitic effects shown above are functions of physical design geometry and fabrication material characteristics. They may also be functions of signal frequencies. If so, the interconnection is also known as a *dispersive* channel in the field of communication systems. In the era of DSM technologies, spaces separating wires and devices diminish,

signal frequency increases and the amount of parasitic coupling increases. Accurate extraction of parasitic parameters is thus an important step in circuit design. The following sections explain the details of parasitic extraction from physical design geometry.

# 2.3 Parasitic Effects in Physical Design

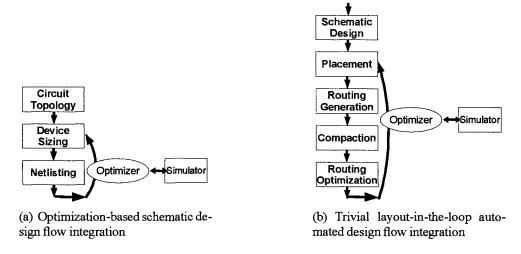

One of the many objectives that constitutes a quality fabrication process is to minimize the performance degradation for all circuits due to their inherited layout parasitics. Sources of performance degradation can be attributed to general layout parasitic effects and fabrication *process variations*. Parasitic effects have been discussed earlier in this chapter. Process variation is due to the systematic and stochastic irregularities on different parts of the wafer causing variations of physical properties. Stochastic irregularities include bleeding, diffraction, thickness and thermal gradients [32], patterns and proximity effects [25]. They are beyond the control of designers, which must rely on accurate models and quality control of the foundry. Systematic process variation can be minimized through robust layout design practices, such as common centroid, inter-digitation and symmetry, etc. [32]. For example, device mismatch is the process that causes time-independent variations of geometric discrepancies of otherwise identically designed devices [50]. Fig. 2–3(a) depicts such design flow. The schematic design begins at the device level, the layout design and parasitic extraction then follow.

Parasitic devices in a post-extracted netlist can be separated into two types, (i) those that are present within device models and parametrized by their design variables, and (ii) those that are extracted from interconnect geometry. While the former are readily available even before layout synthesis, interconnect parasitic effects may not be easily predicted.

Figure 2-3: Analog design flows

Fortunately, for technology nodes over 250nm, they are usually minor and within design margins [43]. In these cases, feasible layout solutions are usually available from top-down modeling hierarchy and schematic-optimized candidates if adequate error margins are given. Fig. 2–3(b) illustrates a circuit optimization flow based on replacing the manual schematic design procedure in Fig. 2–3(a) with the schematic optimizer.

Due to the aggressive push for high performance with existing BJT and MOSFET technologies, available error and noise margins are drastically reduced. While digital logic circuits can tolerate substantial noise in its signal, as long as the voltage level crosses the threshold voltage level within the correct time constraints, analog circuits are sensitive to signal integrity issues in general. Although not crucial for analog implementations, the need for high device density, low power and area in digital designs for high-performance

Figure 2-4: Impact of parasitic effects on design spaces (a) non-DSM, and (b) DSM design refinements

and portable applications has forced analog designs to adopt newer DSM processes for economic reasons.

With high packing density and low supply voltage, influences of parasitic effects and stochastic process variations strengthen. Minute variations of the signal can be amplified to large error, or lead to incorrect logic levels in mixed-signal systems. As supply voltages fall, path delays increase much more dramatically in a 130nm process than they do in a 250nm process [43]. Fig. 2–4 compares the conceptual impact of DSM effects from the circuit designers' point of view. Fig. 2–4(a) illustrates that model refinement throughout the design flow is gentle, and most design candidates pass the post-extraction test. The DSM environment reflects a different situation however. In Fig. 2–4(b), feasible layout solutions are not guaranteed for all candidates that are within specifications at the schematic level. This is because schematic models precede layout design, and are unable to account

accurately for layout effects, while these effects are now more prominent in the DSM era. Failure of design closure will send the design process to backtrack to previous steps for costly re-starts. First-pass success rate in DSM design drops drastically. Since design automation shares the same general tool flow, all flows based on circuit-level performance measures are subject to the same impact. This issue cannot be solved by worst-case models, as performance margins are already slim. Instead, new optimization strategy is thus needed. The dominance of DSM parasitic effects have large implications affecting the implementation of future analog design automation flows.

### 2.4 Parasitic Effects Extraction

Electromagnetic (EM) fields governing the parasitic effects are expressed by Maxwell's equations [41]. In general, they can be solved using numerical EM field solvers. Maxwell's equations either can be expressed in their *differential* form

$$\nabla \cdot E = \frac{\rho}{\epsilon_0}$$

$$\nabla \cdot B = 0$$

$$\nabla \times E = -\frac{\partial B}{\partial t}$$

$$\nabla \times B = \frac{4\pi k}{\mu_0^2 \epsilon_0^2} J + \frac{1}{\mu_0^2 \epsilon_0^2} \frac{\partial E}{\partial t} ,$$

(2.1)

or the integral form

$$\oint \vec{E} \cdot d\vec{A} = \frac{q}{\epsilon_0}$$

$$\oint \vec{B} \cdot d\vec{A} = 0$$

$$\oint \vec{E} \cdot d\vec{s} = -\frac{\partial \Phi_B}{\partial t}$$

$$\oint \vec{B} \cdot d\vec{s} = \mu_0 i + \frac{1}{\mu_0^2 \epsilon_0^2} \frac{\partial}{\partial t} \int \vec{E} \cdot d\vec{A} .$$

(2.2)

In its differential form, the entire physical design in the EM field is first discretized into a mesh that consists of small 2- or 3-dimensional tiles, and the area or volume within each tile is assumed equipotential. The potentials for the mesh at each time step are then solved. Two commonly used approaches are the *finite element* (FE) and the *finite difference* (FD) methods. They differ in whether the variables are expressed as the values of the tiles, or the differences between adjacent tiles. Both approaches effectively replace Maxwell's equations by a system of large but sparse matrix equations. The integral Maxwell's equations are a system of contour integrals of the EM fields of the physical design. Since  $\oint_C \vec{F} \cdot d\vec{s} = 0$  if no sources or sinks of  $\vec{F}$  are present within closed contour C, hence only sources and sinks of the fields are needed to be concerned. The *boundary element method* (BEM) employs this approach via solving *Green's function* to yield a system of small but dense matrices. In general, the FEM and FDM are preferred for large systems, while the BEM is preferred for smaller systems that need higher accuracies.

In practical IC design however, numerical field solvers are too expensive to be used repeatedly for parasitic extraction. Instead, computation results are expressed as parameters

Figure 2–5: Parasitic extraction process

in terms of the material type and geometry, and are stored with other modeling parameters in the PDK technology file. To reduce modeling complexity and improve the matching of accurate parasitic models approved by fabrication foundries, the majority of physical design are realized with rectilinear geometry, except in a few special cases, such as spiral inductors, where 45 degree edges are permitted. Fig. 2–5 shows the parasitic extraction process in the IC design flow. Complex layout objects are first discretized rectilinearly according to the extraction rules. The corresponding parasitic values can then be computed by the width and length of the objects or object segments using the material parasitic properties and layer thickness parameters given in the technology file. This effectively replaces solving (2.2) for complex objects with finding, or *extracting*, the geometric parameters and substituting them into simple formulas to be given next.

Layout parasitic extraction is a crucial step in the IC design process. As a circuit design is fabricated on a silicon die, its practical performance is not only determined by the schematic devices and connections, but also dependent on the qualities and properties of the materials that made up the circuit. Extensive research on fabrication processes and associated sophisticated techniques is carried out in an effort to increase the efficiency

Figure 2-6: Parasitic modeling for a simple cuboid object

of the fabrication material, and to minimize the contributions of these non-ideal effects towards circuit performance. The role of parasitic extraction is to *quantitatively* predict these non-ideal effects from the layout geometry, through the insertion of passive parasitic devices such as resistors, inductors, capacitors and diodes in the extracted circuit netlist. The parasitic properties of simple shapes, such as in Fig. 2–6, can be given analytically

inline resistance:

$$R = \rho \frac{l}{tw}$$

(2.4)

parallel-plate capacitance:

$$C = \epsilon \frac{lw}{h}$$

(2.5)

in terms of the 2-dimensional geometry and various process-related layer thickness parameters and material resistivity  $\rho$  and permittivity  $\epsilon$ . In general, most objects involved in circuit layouts have more complex geometry. Their parasitic values thus do not have closed-form formula and are solved through numerical analysis. To reduce computational and fabrication costs, most layout design rules restrict the drawn layout to contain only shapes with rectilinear edges. Through segmentation, or discretization, of these objects,

their parasitic properties could be computed efficiently using a small set of physical parameters with their geometric dimensions as  $Z_{inl}$ ,  $Z_{lat}$ ,  $Z_{ver}$ ,  $Z_{turns}$  and  $Z_{via}$  in Fig. 2-2.

## 2.5 Sensitivity of Parasitic Effects due to Design Changes

Conceptually, the physical design and parasitic extraction process can be regarded as a mapping of geometric parameters to parasitic values. Except in highly controlled or the simplest cases, this mapping is practically unknown. The sensitivity analysis stems from Taylor series expansion. It offers analytical means to extrapolate complex functions based on known values and moments at certain points. The following equations define the estimation of the new parasitic value Z' with respect to new geometric parameter x', extracted parasitic value Z and known geometric parameter x based on the  $1^{st}$ - and  $2^{nd}$ - order sensitivity analyses respectively:

$$Z' = Z + \frac{\partial Z}{\partial x}(x' - x) \tag{2.6}$$

$$Z' = Z + \frac{\partial Z}{\partial x}(x' - x) + \frac{\partial^2 Z}{\partial x^2}(x' - x)^2.$$

(2.7)

While both estimations can be used interchangeably, (2.7) requires an additional  $2^{nd}$ -order term, but gives better estimate for higher-order functions. The  $1^{st}$ -order sensitivity analysis is used in this work. Further investigation of the Cadence Assura parasitic extraction tool confirms the linearity of parasitic RC values with respect to wire width and length in Fig. 4–14. To derive technology-dependent resistivities and permittivities, Fig. 2–8 depicts the layout template that extracts parasitic values and sensitivity data for interconnects of various length and widths. This procedure is needed to be updated only once for each technology process. For substrate coupling, since the extraction tool used does not facilitate

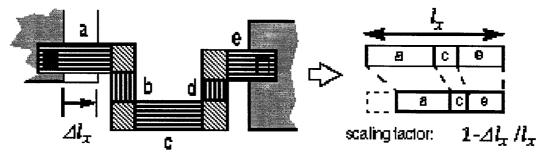

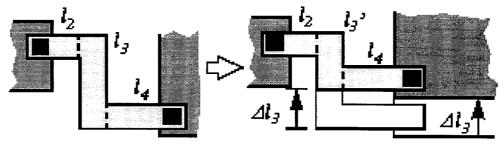

(a) Labeled pin insertion at turns and vias for identification of segments in post-extraction netlist

(b) Resizing of multi-segment interconnect is applied to all segments *parallel* to the resize direction, proportional to their relative length

(c) Resizing an interconnect vertically modifies the shape and parasities of segment  $l_3$ , while horizontal segments  $l_2$ ,  $l_4$ , turns and vias remain untouched

Figure 2-7: Interconnect parasitic values update

Figure 2–8: Layout template for interconnect sensitivities extraction

substrate extraction, the substrate network is derived manually from triangulation scheme. The parasitic values are computed using estimated substrate resistivity values ( $10\Omega cm$  for  $0.18\mu m$  CMOS process) and direct separation distances, or length of the network edges.

Parasitic models for substrate coupling, interconnect and power supply parasitics are crucial for interconnect-dominated DSM designs, as the objective functions rely on them to evaluate and rank the qualities of various placement candidates. During compaction and routing phase, both inline and lateral parasitics vary with block positions. Additionally, the vertical parasitics also vary with the interconnect lengths during the routing phase. The variations of parasitic devices depicted in Fig. 2–2 are given by:

$$Z'_{inl} = Z_{inl} + \frac{\partial Z_{inl}}{\partial l}(l'-l) + \frac{\partial Z_{inl}}{\partial w}(w'-w)$$

(2.8)

$$Z'_{lat} = Z_{lat} + \frac{\partial Z_{lat}}{\partial p}(p' - p) + \frac{\partial Z_{lat}}{\partial d}(d' - d)$$

(2.9)

$$Z'_{ver} = Z_{ver} + \frac{\partial Z_{ver}}{\partial A}(A' - A). \tag{2.10}$$

# 2.6 A Gridless Placement Encoding Scheme