# ΔΣ Digital-To-Analog Converter with Reduced Hardware Requirements using Segmentation

By

Denis Romanov B. Eng. 2018

Department of Electrical Engineering McGill University, Montreal

June 2021

### **Abstract**

Presented in this work is a thorough examination of the use of segmentation in  $\Delta\Sigma$  Digital-to-Analog converters (DAC).  $\Delta\Sigma$  DACs use the principle of negative feedback to recreate an incoming signal and convert it into a pulse modulated density (PDM) signal. This effectively recreates the input signal, with some added quantization noise. Segmentation is a process in which a digital code is split into disparate codes that can then act as separate signals.

In this work, segmentation has been used to relax the requirements on the digital hardware while sacrificing little in the way of performance in terms of Signal-to-Noise ratio (SNR). This was accomplished by having the  $\Delta\Sigma$  DAC split into multiple modulators, each of which dealt with a segment of the original input data. The  $\Delta\Sigma$  modulator dealing with the most significant bits provides the bulk of the response. The remaining  $\Delta\Sigma$  modulators dealing with the least significant bits provide some reprieve from the quantization noise, while also requiring less hardware to implement than the high-performance converter dealing with the most significant bits.

A rigorous mathematical analysis was first performed to demonstrate the effects of segmentation on a segmented  $\Delta\Sigma$  modulator's performance. These established equations gave rise to several design principles, which were then used to create several examples of segmented  $\Delta\Sigma$  modulator designs. This was then followed by several simulations in MATLAB's Simulink environment to back up those findings. Lastly, the simulation designs were mapped on to a field-programmable gate array (FPGA) and tested in a laboratory to confirm the simulations.

### Résumé

Cette thèse présente un examen approfondi de l'utilisation de la segmentation dans les convertisseurs numérique-analogique (DAC)  $\Delta\Sigma$ . Les DAC  $\Delta\Sigma$  utilisent le principe de rétroaction négative pour recréer un signal entrant et le convertir en un signal de densité modulée par impulsions (PDM). Cela recrée le signal d'entrée, avec un bruit de quantification supplémentaire. La segmentation est un processus dans lequel un code numérique est divisé en plusieurs codes qui peuvent ensuite agir comme des signaux distincts.

Dans cette thèse, la segmentation a été utilisée afin d'assouplir les exigences sur le matériel numérique tout en sacrifiant peu de performance en termes de rapport signal/bruit (SNR). Ceci a été accompli en divisant le DAC  $\Delta\Sigma$  en plusieurs modulateurs, chacun d'entre eux traitant un segment des données d'entrée d'origine. Le modulateur  $\Delta\Sigma$  traitant des bits les plus significatifs fournit la majeure partie du comportement du modulateur segmenté. Les modulateurs  $\Delta\Sigma$  restants traitant des bits les moins significatifs offrent un certain sursis au bruit de quantification, tout en nécessitant moins de matériel à mettre en œuvre que le convertisseur haute performance traitant des bits les plus significatifs.

Une analyse mathématique rigoureuse a d'abord été réalisée pour démontrer les effets de la segmentation sur les performances d'un modulateur  $\Delta\Sigma$  segmenté. Ces équations ont donné lieu à plusieurs principes de conception, qui ont ensuite été utilisés pour créer plusieurs exemples de modulateurs  $\Delta\Sigma$  segmentés. Cela a ensuite été suivi de plusieurs simulations dans l'environnement Simulink de MATLAB pour étayer ces résultats. Enfin, les plans de simulation ont été mis en correspondance avec un réseau de portes programmable *in situ* (FPGA) et testés en laboratoire pour confirmer les simulations.

# **Acknowledgements**

Firstly, I would like to give my heartfelt that to Professor Gordon Roberts. Had it not been for his guidance, I would not have considered pursuing this degree to begin with. His insights, enthusiasm, and encouragement played a key role in this whole endeavor. He also helped greatly in writing for a research paper for the IEEE Transactions on Circuits and Systems (TCAS) and gave me many opportunities to work at McGill as a teaching assistant. Professor Roberts also gave me the opportunity to work with the wonderful people at Ciena, and the funding I needed to complete my studies.

I would also like to thank Dr. Ahmed S. Emara, a friend and my senior at McGill University. It is thanks to his own experience that I got the grasp of the principles that I needed to start work on this thesis at all. His encouragements as we both sought to complete our theses were not unappreciated. It was thanks to him that the testing board was developed and used in this thesis. Many thanks to all the members of the Microelectronics and Computer Systems (MACS) Laboratory, especially my cohorts Muhtady Muhsain and Rafid Khan. Special thanks to Sadok Aouini and Soheyl Ziabakhsh (whose seat I now occupy at the laboratory) of Ciena for their insights.

I also acknowledge the contributions of McGill University itself, and the partners I interacted with. I have received funding for my studies through the Mathematics of Information Technology and Complex Systems (MITACS). In addition, I acknowledge that the Canadian Microelectronics Corporation (CMC) has also contributed to my success by granting me access to many of their design tools.

And lastly, I would like to thank my family for all their support and encouragement. There are no words to properly convey the amount of help they have provided me, nor are there words to express my gratitude for that help.

In memory of my grandmother, Nina.

# **Table of Contents**

| Abstract                                                            | i    |

|---------------------------------------------------------------------|------|

| Résumé                                                              | ii   |

| Acknowledgements                                                    | iii  |

| Table of Contents                                                   | v    |

| List of Tables                                                      | ix   |

| List of Figures                                                     | x    |

| List of Acronyms                                                    | xiii |

| Chapter 1: Introduction and Background                              | 1    |

| 1.0. Introduction                                                   |      |

| 1.1. Mixed-Signal Systems                                           | 2    |

| 1.1.1. Defining Mixed-Signal Systems                                | 2    |

| 1.1.2. Motivations to use Mixed-Signal Systems                      | 2    |

| 1.1.3. Relevance of DACs and ADCs to this Thesis                    | 4    |

| 1.2. Background Information                                         | 4    |

| 1.2.1. Basic Principles of Digital-to-Analog Conversion             | 4    |

| 1.2.2. History and Operation of ΔΣ Modulation                       | 5    |

| 1.2.3. The Principle of Segmentation                                | 7    |

| 1.3. Motivation                                                     | 8    |

| 1.3.1. Benefits of ΔΣ Modulation                                    | 8    |

| 1.3.2. Improvements to $\Delta\Sigma$ Modulation using Segmentation | 9    |

| 1.4. Summary                                                        | 10   |

| Chapter 2: Literature Review                                        | 11   |

| 2.0. Introduction                                                | 11 |

|------------------------------------------------------------------|----|

| 2.1. DAC Characteristics                                         | 12 |

| 2.1.1. DC Performance Metrics                                    | 12 |

| 2.1.2. Analog Channel Performance Metrics                        | 15 |

| 2.2. DAC Architectures                                           | 19 |

| 2.2.1. Changeover Switch                                         | 19 |

| 2.2.2. Kelvin Divider DACs                                       | 19 |

| 2.2.3. Thermometer DACs                                          | 20 |

| 2.2.4. R-2R DACs                                                 | 22 |

| 2.2.5. Binary-Weighted DACs                                      | 23 |

| 2.2.6. Pulse-Width Modulation DACs                               | 24 |

| 2.2.7 ΔΣ Modulation DACs                                         | 25 |

| 2.3 Segmented ΔΣ Modulation                                      | 27 |

| 2.3.1. Segmented DACs                                            | 27 |

| 2.3.2. Segmentation in ΔΣ DACs                                   | 28 |

| 2.4 Summary                                                      | 31 |

| Chapter 3: Theory and Design of Segmented ΔΣ Modulators          | 32 |

| 3.0. Introduction                                                | 32 |

| 3.1. Theory of ΔΣ Modulation                                     | 33 |

| 3.1.1. ΔΣ Converter Principles                                   | 33 |

| 3.1.2. General ΔΣ Modulator Structures                           | 33 |

| 3.1.3. General Operation Principles                              | 36 |

| 3.1.4. Performance Properties                                    | 37 |

| 3.2. Two-Segment ΔΣ Modulator Topology                           | 40 |

| 3.2.1. Segmentation Principles                                   | 40 |

| 3.2.2. Incorporating Segmentation into $\Delta\Sigma$ Modulation | 40 |

| 3.2.3. General Operation of a 2-Segment ΔΣ DAC                   | 41 |

| 3.2.4. Maximum Output SNR                                        | 45 |

| 3.3. Extrapolating Beyond Two Segments                           | 46 |

| 3.3.1. General Operation Principles                              | 46 |

| 3.3.2. Maximum Output SNR                                        | 48 |

| 3.4. Summary                                                     | 49 |

| Chapter 4: Synthesis and Design of Segmented ΔΣ Modulators       | 50 |

|    | 4.0. Introduction                                                            | . 50 |

|----|------------------------------------------------------------------------------|------|

|    | 4.1. Design method for 2-Segment ΔΣ Modulators                               | . 51 |

|    | 4.1.1. Noise Constraints for a 2-segment ΔΣ DAC                              | . 51 |

|    | 4.1.2. Selecting Filters for a 2-segment ΔΣ DAC                              | . 53 |

|    | 4.1.3. General Form of the Transfer Functions                                | . 54 |

|    | 4.1.4. Conditions for Realizability.                                         | . 55 |

| ,  | 4.2. Design method for K-Segment ΔΣ Modulators                               | . 56 |

|    | 4.2.1. Noise Constraints for a K-segment ΔΣ DAC                              | . 56 |

|    | 4.2.2. Selecting Filters for a K-segment ΔΣ DAC                              | . 59 |

| ,  | 4.3. Running Examples of Segmented ΔΣ DACs                                   | . 60 |

|    | 4.3.1. 2-Segment Running Example                                             | . 60 |

|    | 4.3.2. 3-Segment Running Example                                             | . 63 |

|    | 4.4. Summary                                                                 | . 69 |

| Cł | napter 5: Mapping Segmented $\Delta\Sigma$ Modulators to Digital Realization | ı 70 |

| ;  | 5.0. Introduction                                                            | . 70 |

| ;  | 5.1. Partitioning Data                                                       | . 71 |

|    | 5.1.1. Considerations on Data Partitioning                                   | . 71 |

|    | 5.1.2. Limits on Data Partitioning                                           | . 72 |

|    | 5.1.3. Remedies to Partitioning Problems                                     | . 75 |

| ;  | 5.2. Transfer Function Mapping                                               | . 77 |

|    | 5.2.1. Direct-Form Realization Topology                                      | . 78 |

|    | 5.2.2. Limitations of direct mapping                                         | . 78 |

|    | 5.2.3. Resonator-Cascade Topology                                            | . 81 |

|    | 5.2.4. A comparison of Direct Mapping and Resonator-Cascade Topology         | . 83 |

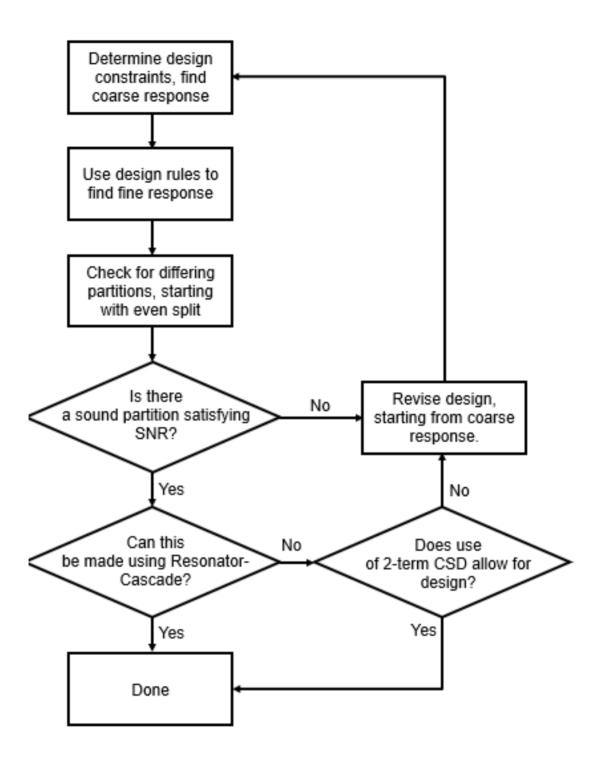

| ;  | 5.3. General method/Flowchart for mapping on to FPGA                         | . 84 |

| ;  | 5.4. Summary                                                                 | . 84 |

| Cł | napter 6: Experimental Validation                                            | . 86 |

| (  | 6.0. Introduction                                                            | . 86 |

| (  | 6.1. Validating Segmented ΔΣ DAC Noise Responses                             | . 87 |

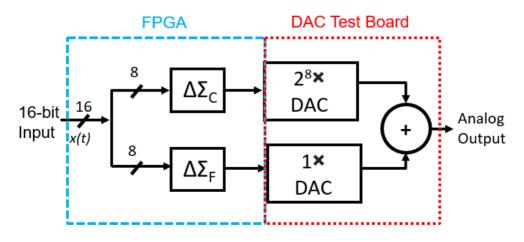

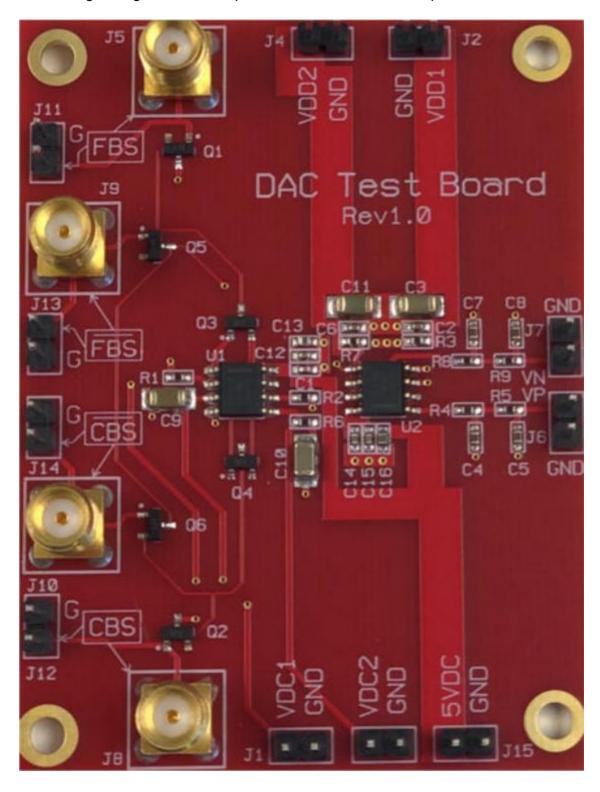

|    | 6.1.1. Hardware Set-up                                                       | . 87 |

|    | 6.1.2. 2-Segment Running Example                                             | . 87 |

|    | 6.1.3. 3-Segment Running Example                                             | . 91 |

| (  | 6.2. Validating Findings on Partitioning                                     | . 92 |

| 6.2.1. 16-Bits Partitioning Example             | 92  |

|-------------------------------------------------|-----|

| 6.2.2. 20-Bits Partitioning Example             | 93  |

| 6.3. Validating Findings on Topology Comparison | 94  |

| 6.3.1. Set-up                                   | 94  |

| 6.3.2. SNR comparison                           | 95  |

| 6.4. Hardware Costs/ Mapping                    | 95  |

| 6.4.1. Hardware Costs for Different Partitions  | 95  |

| 6.4.2. Hardware costs for different topologies  | 97  |

| 6.5. Conclusion                                 | 100 |

| Chapter 7: Conclusion                           | 101 |

| 7.1. Discussion of Results                      | 101 |

| 7.2. Direction for Future Work                  | 102 |

| Bibliography                                    | 104 |

# **List of Tables**

| Table 4.1. A Summary of the Two-Segment $\Delta\Sigma$ DAC<br>Table 4.2. A Summary of the Three-Segment $\Delta\Sigma$ DAC |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Table 6.1. Component Values of the DAC Test Board                                                                          |    |

| Modulator                                                                                                                  | 98 |

| Table 6.3. A Breakdown of Logic Element usage by number of LUT depending on Topology of Modulator                          | •  |

# **List of Figures**

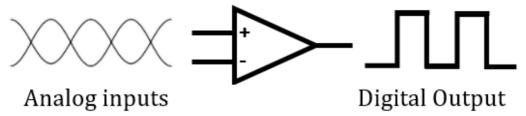

| Fig.1.1. A comparator, using analog inputs and producing a digital output, may be considered a mixed-signal circuit                                                                                                                                      | 2                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

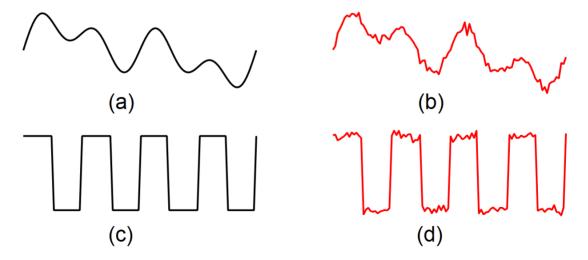

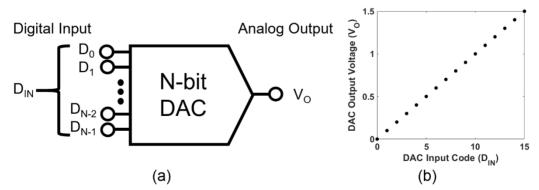

| Fig.1.2. A comparison of an analog signal before and after being subjected to noise (a) and (b) respectively, versus a digital signal before (c) and after noise injection ( Fig.1.3. A diagram of an N-bit DAC (a) and a transfer curve for a 4-bit DAC | se as<br>(d)3<br>5<br>n is |

| Fig.1.5. Various Stages of a 4-bit $\Delta\Sigma$ Modulator for a sinusoidal input. Note the distinction between the Modulator output in green and the DAC output in magenta which the logic high and low are mapped to real voltages.                   |                            |

| Fig.1.6. A comparison of the distance between the frequency band in blue and the imaging frequencies in red for a low sampling frequency (a) and high sampling frequency (b)                                                                             |                            |

|                                                                                                                                                                                                                                                          |                            |

| Fig.2.1. A transfer curve of a non-ideal 4-bit DAC with a best-fit line (a) and endpoi endpoint line (b) both in red                                                                                                                                     |                            |

| Fig.2.2. An example of offset (a) and gain error (b) as compared to the ideal line in                                                                                                                                                                    | red                        |

| Fig.2.3. Example transfer curves of a monotonic DAC (a) and non-monotonic DAC                                                                                                                                                                            |                            |

| Fig.2.4. An example of two different transfer curves with identical best-fit lines                                                                                                                                                                       | 14                         |

| Fig.2.5. An example of quantization and the effective noise it creates                                                                                                                                                                                   | 16                         |

| Fig.2.6. An example of two output frequency spectra displaying symmetric harmon                                                                                                                                                                          | ic                         |

| distortion (a) and asymmetric harmonic distortion (b).                                                                                                                                                                                                   |                            |

| Fig.2.7. An example of Intermodulation Distortion.                                                                                                                                                                                                       | 17                         |

| Fig.2.8. An example of imaging                                                                                                                                                                                                                           | 18                         |

| Fig.2.9. The Changeover Switch 1-Bit DAC: (Single-Pole, Double Throw, SPDT)                                                                                                                                                                              | 19                         |

| Fig.2.10. Kelvin Divider/String DAC                                                                                                                                                                                                                      | 20                         |

| Fig.2.11. Diagram of a thermometer DAC (a) and thermometer DAC with                                                                                                                                                                                      |                            |

| complementary current outputs                                                                                                                                                                                                                            |                            |

| Fig.2.12. R-2R DAC structure for voltage output (a) and current output (b)                                                                                                                                                                               |                            |

| Fig.2.13. Current-Mode Binary-Weighted DAC                                                                                                                                                                                                               |                            |

| Fig.2. 14 A block diagram of a PWM DAC (a) and an example output bitstream (b)                                                                                                                                                                           |                            |

| 3-bit DAC and input of 5                                                                                                                                                                                                                                 |                            |

| Fig.2.15. Structure of a $\Delta\Sigma$ Modulator                                                                                                                                                                                                        | 25                         |

| Fig.2.16. A comparison of DAC output bitstreams using N=3 and input of 4 for a PWN                        |            |

|-----------------------------------------------------------------------------------------------------------|------------|

| DAC (a) and $\Delta\Sigma$ DAC (b)                                                                        |            |

| Fig.2.17. A comparison of DAC output bitstreams using N=3 and input of 4 for a PWN DAC (a) and ΔΣ DAC (b) |            |

| Fig.2.18. Frequency distribution of noise, for an ordinary DAC (a), an oversampling                       | . 23       |

| DAC (b), and a noise-shaping DAC (c)                                                                      | 26         |

| Fig.2.19. Frequency distribution of noise, for an ordinary DAC (a), an oversampling                       | . 20       |

| DAC (b), and a noise-shaping DAC (c)                                                                      | . 26       |

| Fig.2.20. A Block diagram of an early segmented DAC, as described in [9]                                  |            |

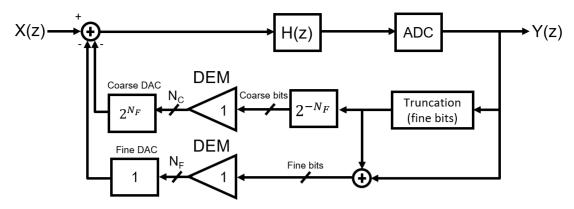

| Fig.2.21. Block Diagram of $\Delta\Sigma$ ADC using segmented DAC, as seen in [10]                        |            |

| Fig.2.22. Block diagram of the architecture proposed in [12], with mismatch error                         |            |

| feedback                                                                                                  |            |

| Fig.2.23. A mismatch-shaped segmented multibit $\Delta\Sigma$ DAC, as shown in [11]                       |            |

| Fig.2.24. Block diagram of the digital noise-coupling technique from [13]                                 |            |

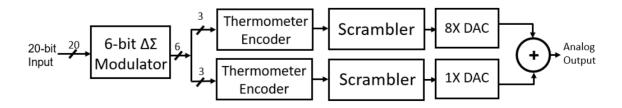

| Fig.2.25. Segmentation combined with scrambling, as seen in [15]                                          | . 30       |

|                                                                                                           |            |

| Fig.3.1 Typical structure of a ΔΣ-based DAC                                                               | . 33       |

| Fig.3.2. Signal flow graph (a) and linear model (b) of a $\Delta\Sigma$ modulator                         |            |

| Fig.3.3. Structure of a $\Delta\Sigma$ Modulator with a unity signal transfer function (STF). The         |            |

| number of bits used for each signal path is identified                                                    |            |

| Fig.3.4. An example of a segmented $\Delta\Sigma$ modulator                                               |            |

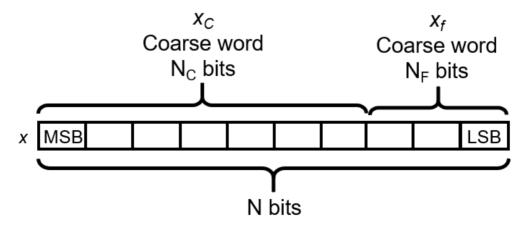

| Fig.3.5. Partitioning of the digital word into two parts: Coarse and Fine                                 |            |

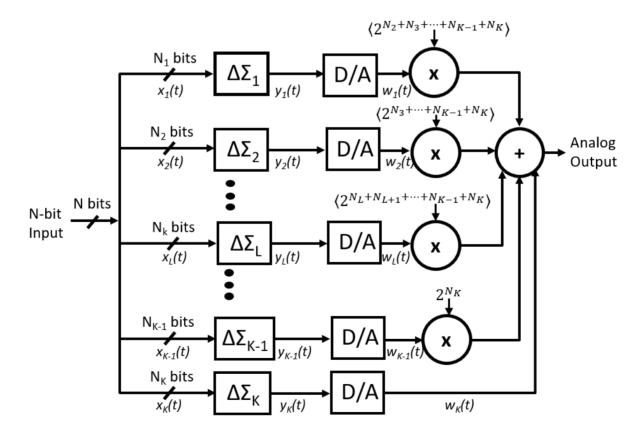

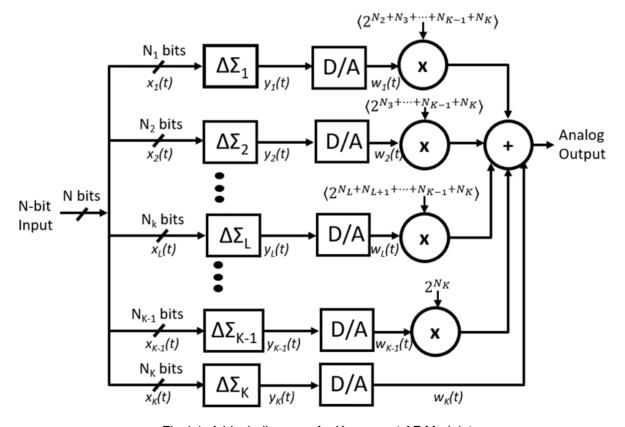

| Fig.3.6. A block diagram of a K-segment ΔΣ Modulator                                                      | . 47       |

| Fig. 4.1. A block diagram of a K aggment AS Modulator                                                     | <b>-</b> 7 |

| Fig.4.1. A block diagram of a K-segment $\Delta\Sigma$ Modulator                                          |            |

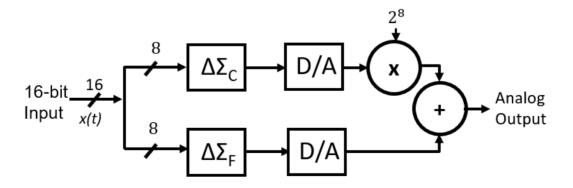

| Fig.4.3. Structure of the 2-segment running example                                                       |            |

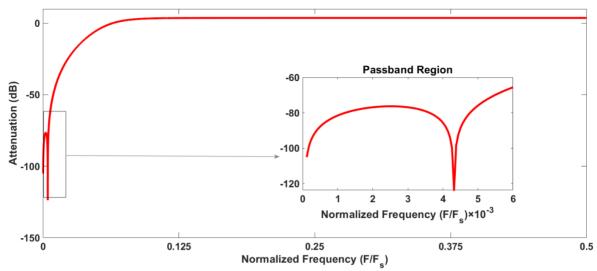

| Fig.4.4. The Noise Transfer Function of the Coarse Segment, shown in the Nyquist a                        |            |

| signal band.                                                                                              |            |

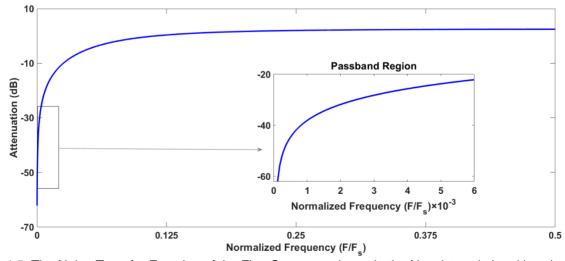

| Fig.4.5. The Noise Transfer Function of the Fine Segment, shown in the Nyquist and                        |            |

| signal band                                                                                               |            |

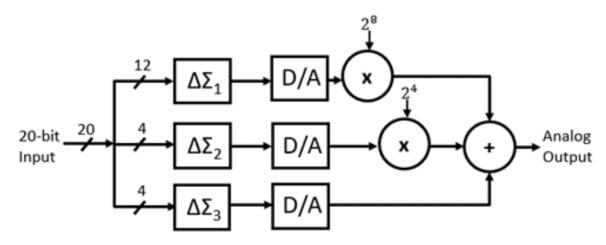

| Fig.4.6. Structure of the 3-segment Example                                                               | . 63       |

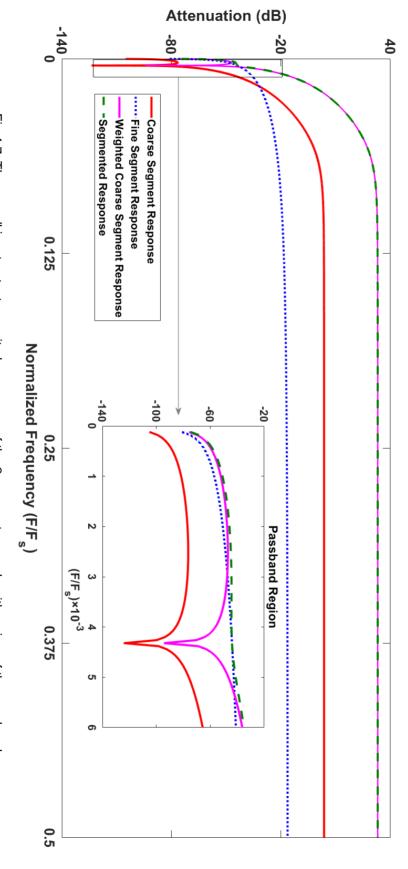

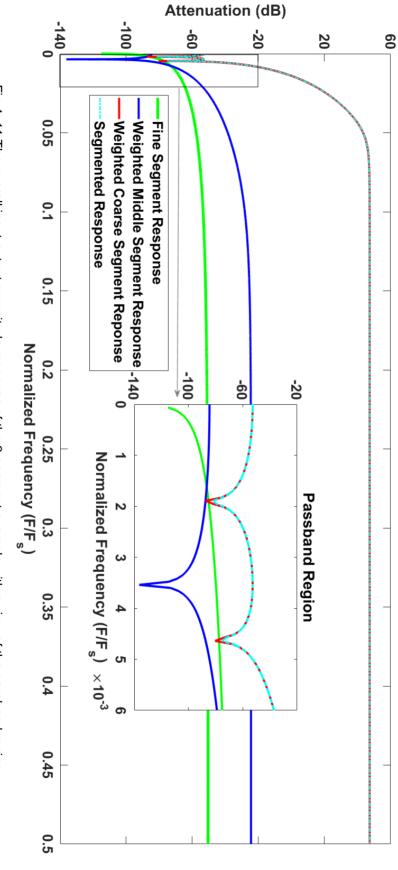

| Fig.4.7. The overall input-output magnitude response of the 2-segment example with                        | а          |

| view of the passband region together with the coarse, weighted-coarse and fine                            |            |

| segment behaviors for comparison purposes                                                                 |            |

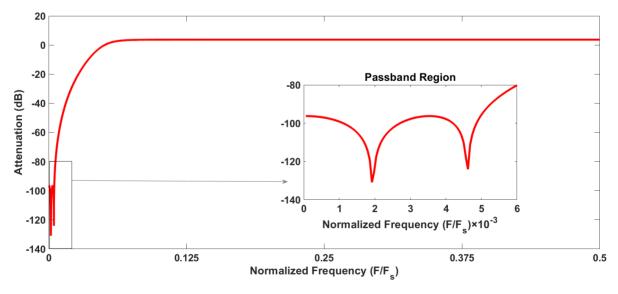

| Fig.4.8. The Noise Transfer Function of the Coarse Segment of the 3-segment exam                          | •          |

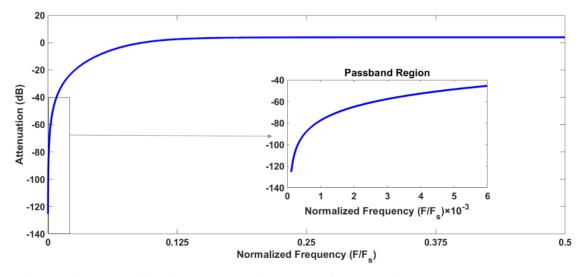

| Fig.4.9. The Noise Transfer Function of the Middle Segment of the 3-segment examp                         |            |

| rig.4.9. The Noise Transfer Function of the Middle Segment of the 3-segment examp                         |            |

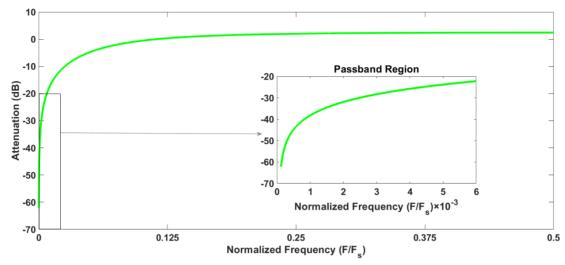

| Fig.4.10. The Noise Transfer Function of the Middle Segment of the 3-segment                              | . 50       |

| example                                                                                                   | 67         |

| Fig.4. 11 The overall input-output magnitude response of the 3-segment example wit                        | h a        |

| view of the passband region together with the coarse, weighted-coarse, weighted                           |            |

| middle, and fine segment behaviors for comparison purposes                                                | . 68       |

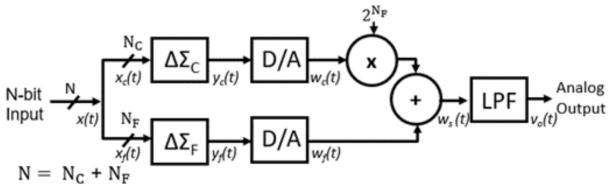

| Fig.5.1. Structure of the segmented $\Delta\Sigma$ DAC                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.5.5. An example of a pre-amplifier used to scale down an input                                                                                                        |

|                                                                                                                                                                           |

| Fig.5.7. An example of a modulator using padding in its operation                                                                                                         |

|                                                                                                                                                                           |

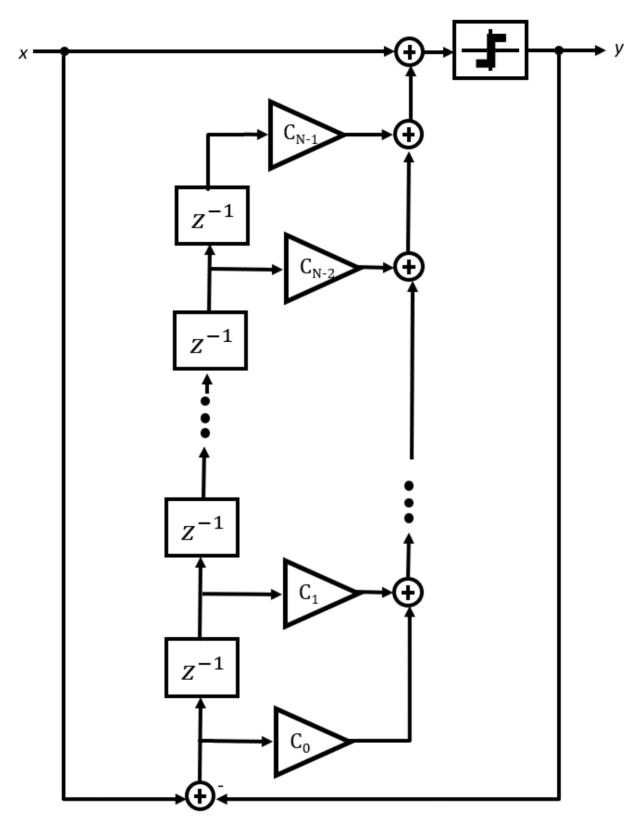

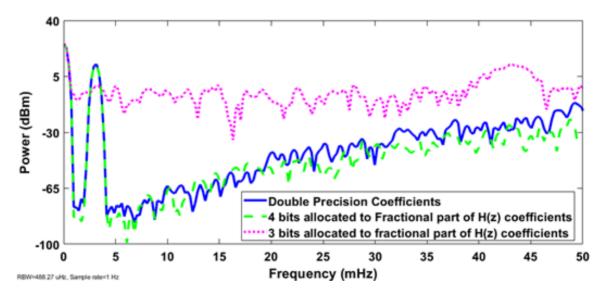

| Fig.5.9. A $\Delta\Sigma$ Modulator with unity STF, using direct form realization                                                                                         |

| precision in the loop filter coefficients                                                                                                                                 |

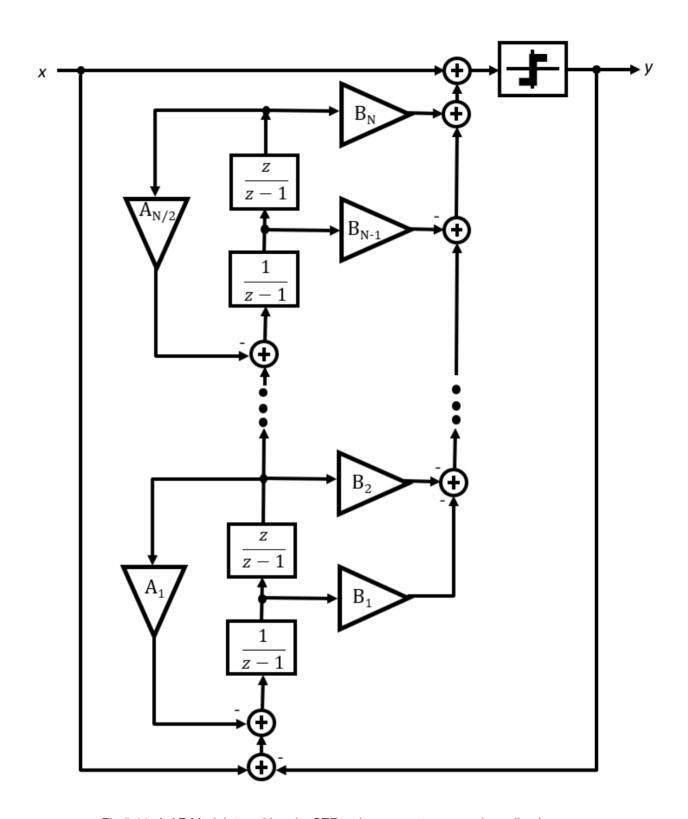

| Fig. 5.11. A ΔΣ Modulator with unity STF, using resonator-cascade realization                                                                                             |

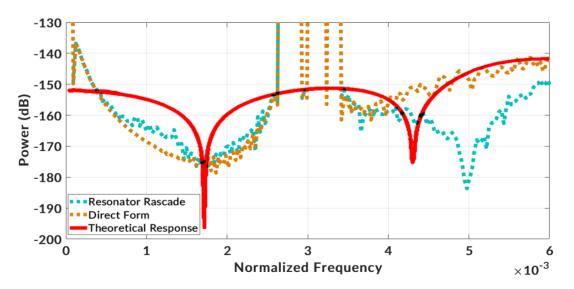

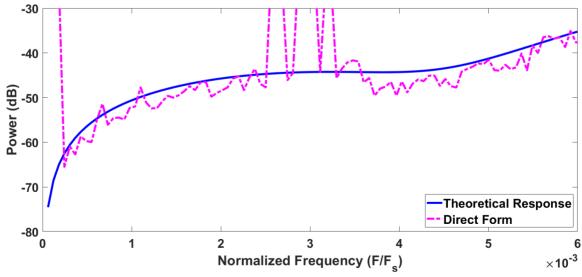

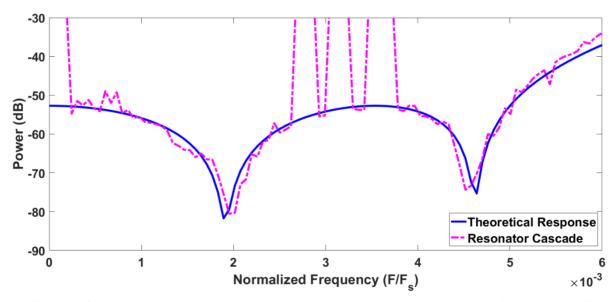

| Fig.5.12. Passband response comparison found through simulation and theory 83 Fig.5.13. Flowchart for the general process for designing a segmented $\Delta\Sigma$ DAC 85 |

| Tig. 3. 13. Flowchart for the general process for designing a segmented AZ DAC 83                                                                                         |

| Fig.6.1. A block diagram of the test set-up                                                                                                                               |

| Fig.6.2. Photograph of the discrete-component reconstruction circuit.                                                                                                     |

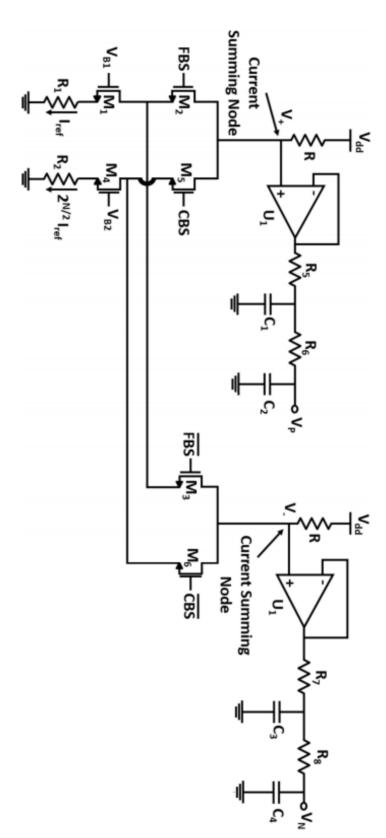

| Fig.6.3. Schematic of the discrete implementation of the reconstruction circuit                                                                                           |

| segment $\Delta\Sigma$ modulator implemented using a direct form topology                                                                                                 |

| segment $\Delta\Sigma$ modulator implemented using a resonator-cascade topology                                                                                           |

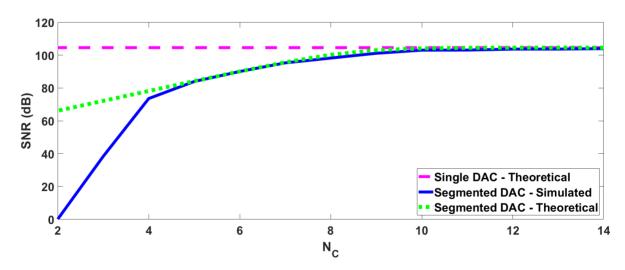

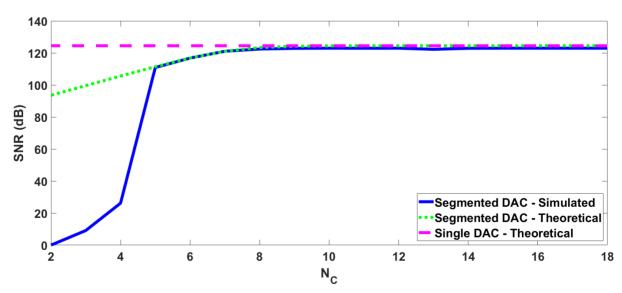

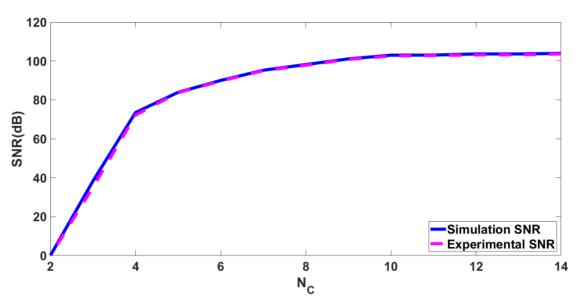

| Fig.6.7. A comparison of the peak SNR vs bit partitioning N <sub>C</sub> between simulations and                                                                          |

| experiment for the 16-bit example in sub-section 5.1.2                                                                                                                    |

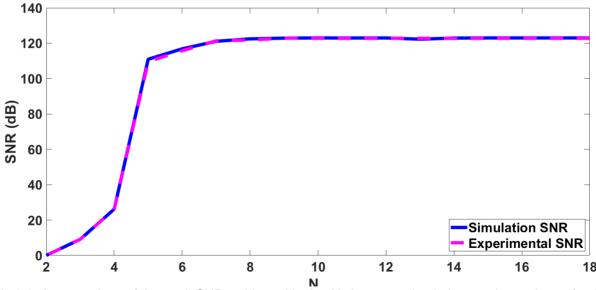

| Fig.6.8. A comparison of the peak SNR vs bit partitioning N <sub>C</sub> between simulations and                                                                          |

| experiment for the 20-bit example in sub-section 5.1.2                                                                                                                    |

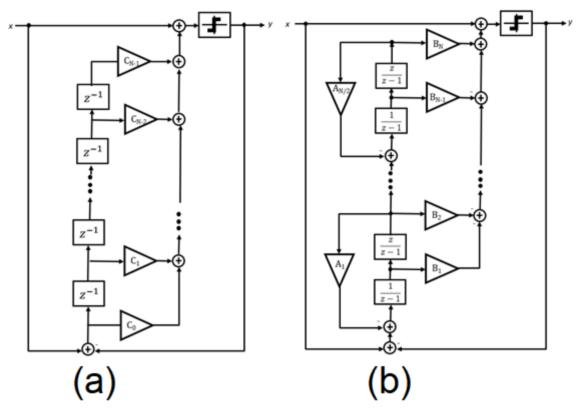

| Fig.6.9. Direct-Form (a) and Resonator-Cascade Form (b) of a ΔΣ Modulator with unity STF94                                                                                |

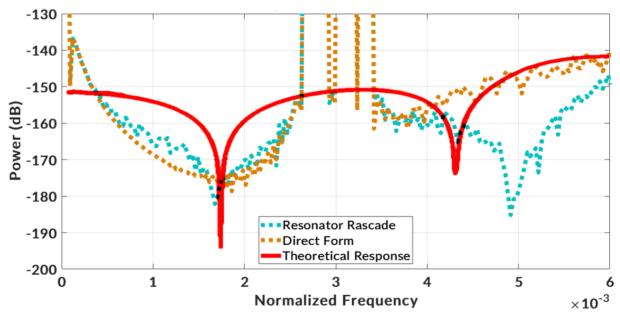

| Fig.6.10. A comparison of PSD for direct form and Resonator-Cascade realizations, as                                                                                      |

| compared to theory                                                                                                                                                        |

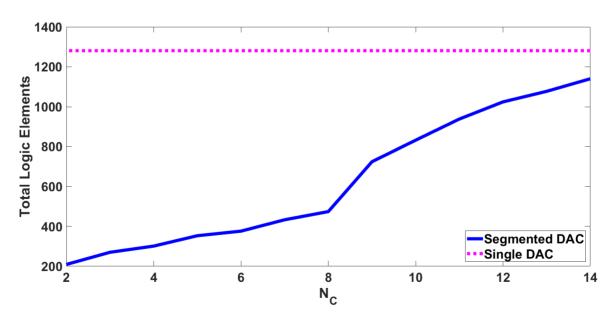

| Fig.6.11. A comparison of total logic elements for different partitioning of data, using the                                                                              |

| 16-Bits Partitioning Example96                                                                                                                                            |

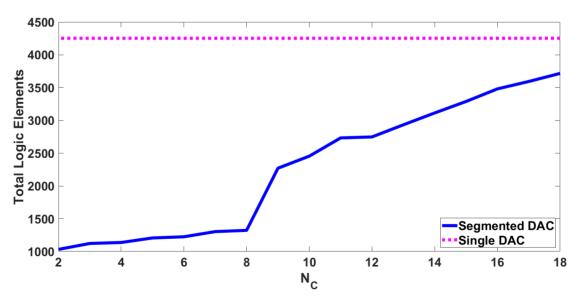

| Fig.6.12. A comparison of total logic elements for different partitioning of data, using the 20-Bits Partitioning Example                                                 |

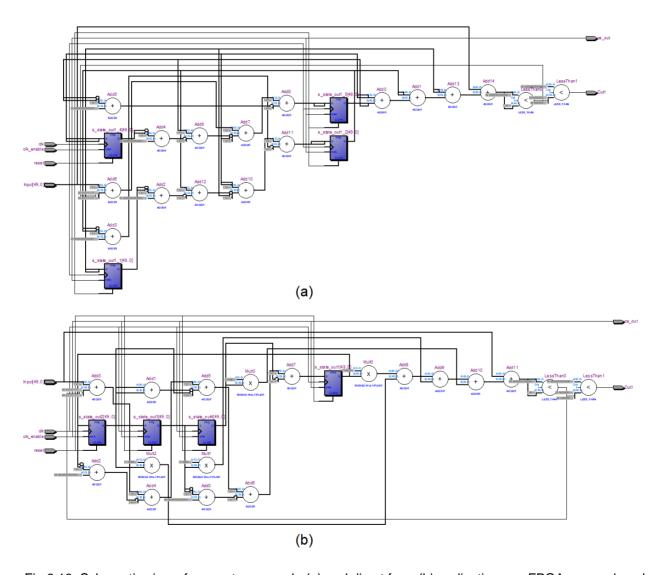

| Fig.6.13. Schematic view of resonator-cascade (a) and direct form (b) realizations on                                                                                     |

| FPGA, as produced by the Quartus RTL viewer99                                                                                                                             |

# **List of Acronyms**

ADC Analog-to-Digital Converter

CBS Coarse Bitstream

DAC Digital-to-Analog Converter

DAQ Data Acquisition System

DDC Digital-to-Digital Converter

DEM Dynamic Element Matching

DNL Differential Nonlinearity

DSP Digital Signal Processing

FBS Fine Bitstream

FPGA Field Programmable Gate Array

INL Integral Nonlinearity

LPF Low-Pass Filter

LSB Least Significant Bit

MSB Most Significant Bit

NTF Noise Transfer Function

Op-Amp Operational Amplifier

PDM Pulse Density Modulation

PWM Pulse Width Modulation

SNR Signal-to-Noise Ratio

STF Signal Transfer Function

TLE Total Logic Elements

# **Chapter 1: Introduction and Background**

### 1.0. Introduction

This chapter will serve as an introduction to the core ideas explored in this thesis, namely the basics of mixed-signal circuit, Digital-to-Analog conversion (DAC), the history and operation of  $\Delta\Sigma$  modulation, and the principle of segmentation in data converters. Lastly, the motivation behind this thesis is explained by introducing the main benefits and shortcomings of  $\Delta\Sigma$  modulation, and how segmentation could be used to remedy the latter.

# 1.1. Mixed-Signal Systems

Firstly, this section will serve as an introduction to mixed-signal systems, as the entire thesis pertains to them.

# 1.1.1. Defining Mixed-Signal Systems

In electronics, one can categorize circuits and the signals associated with them as being either digital or analog. In practice, the signals encountered on a day-to-day basis are analog, such as soundwaves, while general purpose computers and dedicated integrated circuits deal with digital information in the form of binary codes.

A mixed-signal circuit is defined as a circuit which is comprised of both analog and digital components. This definition, while sound, does include certain circuits that many engineers would be hesitant to call mixed-signal circuits, such as the comparator. A comparator has two analog inputs, and one output that indicates which of the two input signals is higher (i.e. a binary output), as shown in Fig. 1.1. For the purpose of this thesis, the mixed signal circuits in question are ones that strictly convert analog electronic signals into digital information or viceversa, which are widely agreed to be true mixed-signal circuits. These are the Analog-to-Digital converter (ADC or A/D) and the Digital-to-Analog converter (DAC or D/A).

# 1.1.2. Motivations to use Mixed-Signal Systems

Since the rise of home computers and especially after the smartphone's meteoric rise in prominence, the importance of mixed-signal circuits and systems

Fig.1.1. A comparator, using analog inputs and producing a digital output, may be considered a mixed-signal circuit

has only continued to grow over the last few decades. While analog signals are what most people deal with on a regular basis, one would be hard pressed to emulate the convenience of digital storage and data manipulation in the realm of analog electronics.

For a great number of applications, electronic systems are designed to accept analog inputs and converted into digital information through the use of sensors such as light detectors and microphones and transferring this information to a computer system.

This information can then be stored, distributed, edited, analysed, or processed with all the convenience and staggering options that digital systems offer. The high levels of integration that can be achieved with digital circuits, combined with the inherent imperviousness to noise that digital signals have as compared to analog signals as shown in Fig. 1.2. The subfigures (a) and (c) show a typical analog and digital signal respectively, while (b) and (d) show those same signals after being exposed to an identical level of noise. It is much easier to reconstruct the intended signal in the digital case, as in the analog case the distinction between noise and signal is not so easily made. The additional insensitivity to variations between parts in digital circuits as apposed to analog components makes the use of digital systems all the more desirable.

Fig.1.2. A comparison of an analog signal before and after being subjected to noise as (a) and (b) respectively, versus a digital signal before (c) and after noise injection (d).

In a mixed-signal system, this information is the converted into an analog signal using actuators such as displays and speakers, to be interpreted by people once again.

The sensors and actuators as mentioned earlier are in fact the ADCs and DACs from section 1.1.1. Both of these circuits have their own purposes, and seldom can an engineer find a complex system that does not employ both.

### 1.1.3. Relevance of DACs and ADCs to this Thesis

This thesis pertains to a specific kind of converter, known as Delta-Sigma ( $\Delta\Sigma$ ). While it can be implemented to use either as a DAC or ADC, this work focuses on the DAC implementation of a  $\Delta\Sigma$  modulator. More specifically, this thesis explores some modifications that can be made to a  $\Delta\Sigma$  DAC and how these modifications affect the converter's performance versus the costs incurred by these changes, as opposed to a more typical converter. Section 1.2. will cover the essentials of  $\Delta\Sigma$ , and data converters in general.

# 1.2. Background Information

This section offers a quick overview of the principles of operation of DACs and  $\Delta\Sigma$  modulators, as well as a brief history of the latter to understand the motivation behind using  $\Delta\Sigma$  modulation. This section will also provide a brief introduction to the principle of segmentation, to better understand the motivation behind this thesis, as covered in section 1.3. A more in-depth look at the operating principles will be presented in chapter 2.

# 1.2.1. Basic Principles of Digital-to-Analog Conversion

The DAC acts as a decoder; it uses a digital input code representing an integer which is then converted into an analog voltage level. The operation can be roughly thought of as a multiplication by some factor to convert to and from the

analog and digital equivalents. Thinking of the output as  $V_{\text{O}}$ , and the input as  $D_{\text{IN}}$ , one can write

$$V_O = G_{DAC} * D_{IN} ag{1.1}$$

where the factor  $G_{DAC}$  is some real-valued constant. Because  $D_{IN}$  pertains to data from a digital system, it is typically an N-bit wide base-2 unsigned integer. It would then be expressed as

$$D_{IN} = D_0 + D_1 * 2^1 + D_2 * 2^2 + \dots + D_{N-1} * 2^{N-1}.$$

(1.2)

Given that the factors  $D_0$  to  $D_{N-1}$  are bits, they will take on values of either 1 or 0, and  $D_{IN}$  will therefore be an integer ranging from 0 to  $2^N-1$ .  $D_0$  is called the least significant bit (LSB) as it has the least impact on  $D_{IN}$ , while  $D_{N-1}$  is considered the most significant bit (MSB) as it has the most impact.

A diagram demonstrating a typical DAC is shown in Fig.1.3. along with an example transfer curve for a 4-bit DAC with G<sub>DAC</sub> of 0.1V. It is plain to see that this results in one-to-one mapping, with the LSB step size (least significant change in voltage) or V<sub>LSB</sub> is equal to 0.1V.

# 1.2.2. History and Operation of $\Delta\Sigma$ Modulation

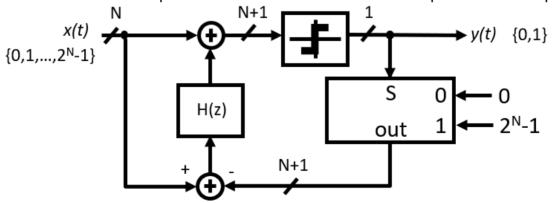

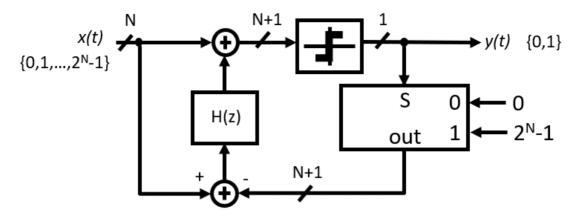

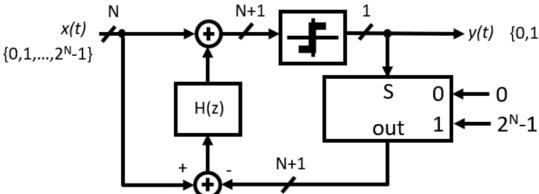

While some variation exists between various implementations of  $\Delta\Sigma$  converters, the principle of negative feedback lies at the core of any and all of them. Fig. 1.4. demonstrates an example of a  $\Delta\Sigma$  DAC structure.

Fig.1.3. A diagram of an N-bit DAC (a) and a transfer curve for a 4-bit DAC

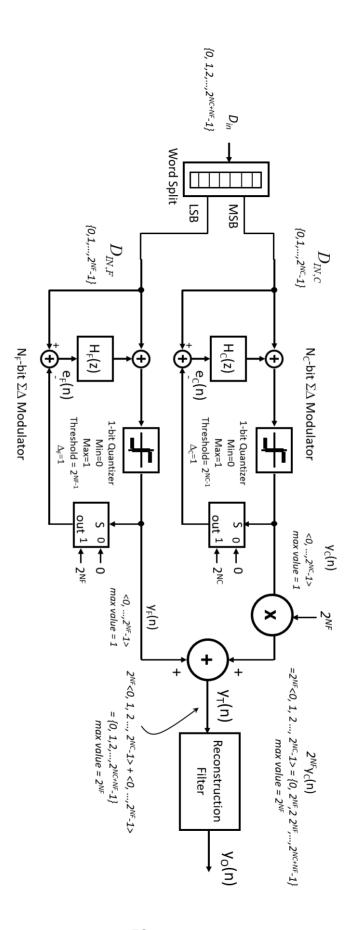

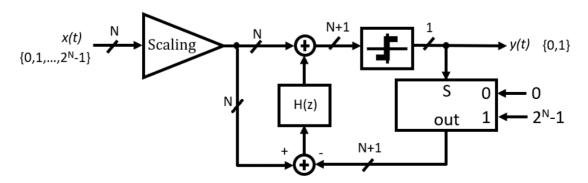

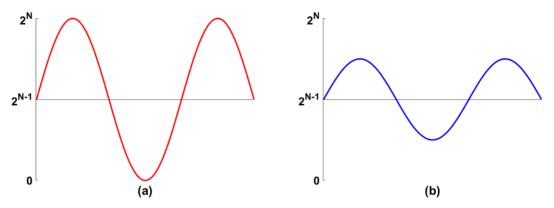

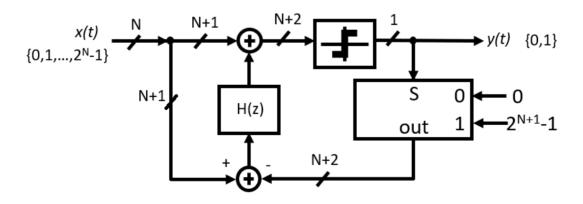

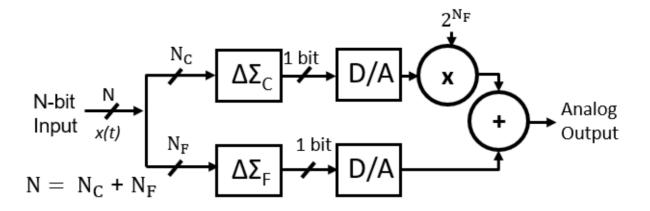

A digital code serves as the input to two difference amplifiers, one into the feedforward path and the other in the feedback path. The feedforward path leads into a comparator, whose output leads into the feedback path via a digital-to-digital converter for scaling purposes. Two of the signal paths are padded with 1 bit, as some operations may cause overflow otherwise. Here a multiplexer with two possible output states of 0 and  $2^{N}-1$  is used to realize this digital-to-digital converter operation. These two integers represent the smallest and largest signal associated with an N-bit data path. This signal then passes into the difference amplifier that leads into the loop filter denoted by H(z).

Over time, a bitstream appears at the output which contains a replica of the original incoming signal x(t) buried in quantization noise. The signal x(t) can be extracted from the bitstream using a lowpass reconstruction analog filter with a corner frequency set to the signal bandwidth of x(t). An example of this is demonstrated in Fig. 1.5. If one were to think of the modulator output in terms of a density of different code levels (i.e. integers), when scaled by the D/A block, the density can now be expressed in terms of a voltage-level pulse modulated density (PDM) signal.

The concept of  $\Delta\Sigma$  modulation dates to 1962, as written by Inose [1]. The motivation for writing this at the time was a drawback in Delta modulation ( $\Delta M$ ) [2], introduced in 1948, which  $\Delta\Sigma$  is itself derived from. The drawback stems from the fact that the pulses produced as the output to the delta modulator carry the information that corresponds to the differentiation of the amplitude of the input

Fig.1.4. Structure of a  $\Delta\Sigma$  modulator. The number of bits used for each signal path is identified.

signal. To put it simply; whether amplitude rises or falls from one sampling pulse to another. To recover the information contained in the input waveform, these pulses must be integrated. As a result, any transmission disturbances (namely noise) will cause an accumulated error in the output signal. This is in contrast to  $\Delta\Sigma$  modulation, which uses what is effectively two opposing operations to achieve a not too dissimilar result.

# 1.2.3. The Principle of Segmentation

The process of segmentation in DACs typically involves the partitioning of input digital data into segments, typically into a segment comprised of the MSBs and another segment comprised of LSBs [3] The outputs of the individuals DACs are then recombined by a process specific to the segmented DAC in question.

There are multiple reasons for which a designer may use a segmented DAC. It may be that the performance requirements a designer faces may dictate specific performance metrics, for which no single architecture may be adequate. It may be that a linear increase in the number of bits leads to an exponential increase of hardware required to create the DAC. As such, segmenting a DAC may be worth it to save on hardware.

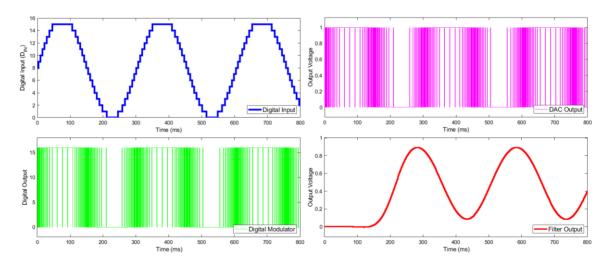

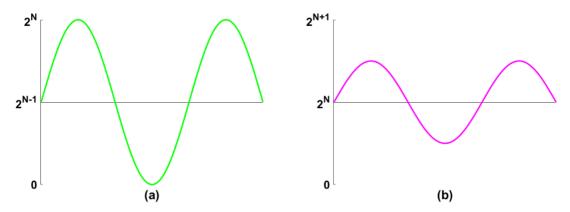

Fig.1.5. Various Stages of a 4-bit  $\Delta\Sigma$  Modulator for a sinusoidal input. Note the distinction between the Modulator output in green and the DAC output in magenta in which the logic high and low are mapped to real voltages.

It is worth noting that segmentation need not send the data segments to separate converters. Indeed, some architectures may allow for data to be treated differently within the same modulator. Examples such as this will be elaborated on in the next chapter.

### 1.3. Motivation

This section covers the motivation behind the use of  $\Delta\Sigma$  modulation, and the motivation behind the research performed for this thesis. Firstly, the benefits of  $\Delta\Sigma$  modulation will be covered. Following this will be a subsection covering the drawbacks and limitations of  $\Delta\Sigma$  modulation and the improvements sought to  $\Delta\Sigma$  modulation through the use of segmentation.

### 1.3.1. Benefits of $\Delta\Sigma$ Modulation

One major advantage of using  $\Delta\Sigma$  DACs is that they are nearly all-digital, as the only true analog component required is the low-pass filter (LPF). This makes it quite compact when implemented on a chip.

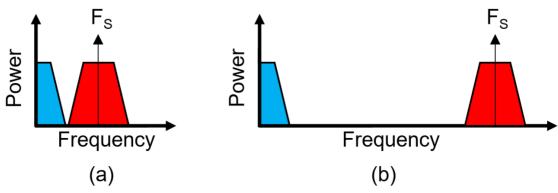

In addition,  $\Delta\Sigma$  modulation possesses highly desirable properties in terms of noise-shaping.  $\Delta\Sigma$  modulators, much like other sampling systems, run on a clock which use a frequency (known as the Sampling Frequency) that is at least double the maximum signal frequency, though this is typically much larger. This has a desirable consequence on imaging effects; the undesirable frequencies are

Fig.1.6. A comparison of the distance between the frequency band in blue and the imaging frequencies in red for a low sampling frequency (a) and high sampling frequency (b).

"pushed" away from the signal band, as shown in Fig. 1.6. This means that not only will there be less interference from aliasing within the input spectrum, but the filter used to reconstruct the signal can also be much simpler as it no longer needs a sharp roll-off.

$\Delta\Sigma$  modulation also holds other advantages where noise is not evenly distributed, but rather pushed to higher frequencies. This is covered in greater detail in sub-section 2.2.7. in comparison to other DACs.

### 1.3.2. Improvements to $\Delta\Sigma$ Modulation using Segmentation

In general, to increase the SNR (and main performance metric) of a  $\Delta\Sigma$  modulator, the hardware and area costs must also increase significantly. A higher order modulator will require far more hardware than one with identical data path width but lower loop filter order. The same is true of an increase in the width of the data path.

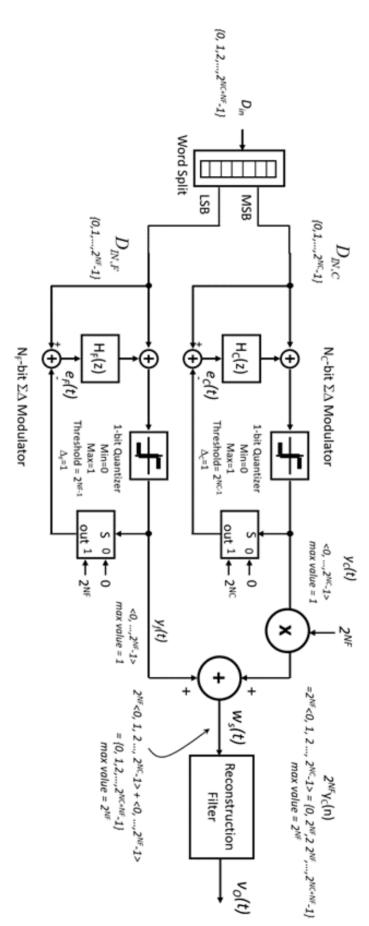

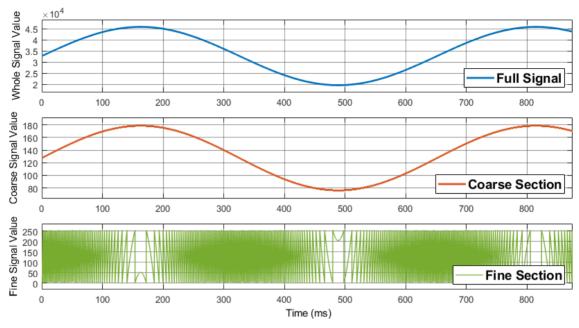

Seeking to remedy this, the work in this thesis aims to use segmentation to create segmented  $\Delta\Sigma$  DACs that uses separate loop filters for the LSBs and MSBs. The idea is that the width of the data path cannot be reduced to meet a certain SNR, but the filters themselves will proportionately require less area to create than a single filter if they are chosen judiciously.

In addition, an increase in resolution for  $\Delta\Sigma$  modulation affects more than just the increase in hardware costs. Consider a  $\Delta\Sigma$  modulator has N bits in its signal path. Any signal created from a N-bit single word requires a full pass of  $2^N$  samples to complete. This means that as the resolution increases, the length of the output bitstream increase exponentially. This presents problems of latency and bandwidth/filter requirements.

In a 2-segment  $\Delta\Sigma$  DAC, however, each segment would have N<sub>C</sub> and N<sub>F</sub> bits, such that the two add up to the original N. Once the outputs are added together after processing, we can expect a significantly shorter output settling time on account of partitioning of the overall resolution of the  $\Delta\Sigma$  modulator.

# 1.4. Summary

This chapter introduced the core ideas of the thesis, offering a quick introduction to mixed-signal systems, Digital-to-Analog conversion, the history and working principles of  $\Delta\Sigma$  modulation, and the principle of segmentation in data converters. This chapter also covered the advantages and limitations of  $\Delta\Sigma$  modulation and introduced the motivation behind applying segmentation of  $\Delta\Sigma$  DACs.

# **Chapter 2: Literature Review**

### 2.0. Introduction

This chapter serves as a review of literature and topics relevant to fully understanding this thesis. Firstly, the metrics relevant to gauging the performance of DACs will be covered. Secondly, various DAC architectures are explored so as to make a point of comparison to  $\Delta\Sigma$  DACs which will be featured prominently in the rest of the thesis. Thirdly, literature concerning various topologies for modulator realization will be covered. Lastly, relevant literature concerning the use of segmentation in  $\Delta\Sigma$  modulation is presented, so as to better understand the purpose and scope of the work in this thesis.

### 2.1. DAC Characteristics

This section covers the essential metrics used to gauge the performance of a DAC. To start, the metrics as they pertain to the DC characteristics are established. Following this, the analog channel performance metrics will be developed on. Most of the information covered here is taken from [4].

### 2.1.1. DC Performance Metrics

While the thesis primarily concerns analog channel measurements, a working DAC must meet certain minimal DC requirements to be considered viable. The description of DACs provided in subsection 1.2.1. makes some assumptions that are rarely true in practice. Often, DACs have several limitations on linearity, as explained here.

### 2.1.1.1. Lines of Comparison

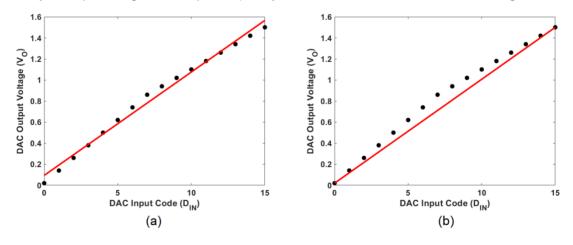

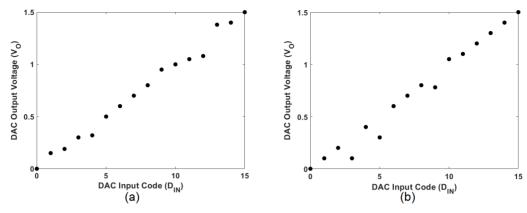

To properly understand the non-idealities characterized by the measurements that will be elaborated on in this sub-section, one must have proper points of comparison. Once data from a DAC is collected, it can be compared against the ideal line to observe how it deviates. Alternatively, one may use different comparison lines; The best-fit line (approximates the data such that total deviation is minimized) and the endpoint-to-endpoint line (approximating the data by interpolating the endpoints) may be used instead, as shown in Fig. 2.1.

Fig.2.1. A transfer curve of a non-ideal 4-bit DAC with a best-fit line (a) and endpoint-endpoint line (b) both in red.

Fig.2.2. An example of offset (a) and gain error (b) as compared to the ideal line in red

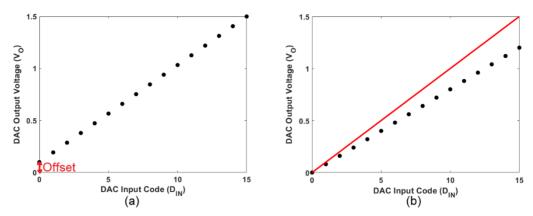

### 2.1.1.2. Offset and Gain Error

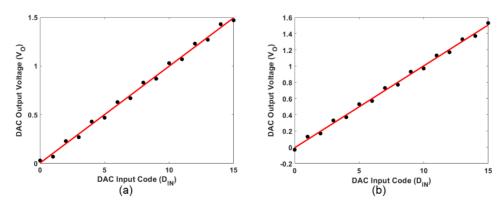

Recall the transfer curve for an ideal 4-bit DAC, as shown in Fig. 1.3. Because the initial code (corresponding to zero) corresponds to an output voltage value of 0, and so an ideal converter is said to have an offset error of 0. In a non-ideal DAC, this output voltage's value is typically non-zero and is defined as the offset, as shown in Fig. 2.2. Offset can be defined as the difference between the measured voltage and some baseline; if not the ideal line, then either the best-fit line or the endpoint-to-endpoint line.

Similarly, gain error compares the gain GDAC from the ideal DAC transfer characteristic against that same gain value derived from either the endpoint-to-endpoint line or the best-fit line. The gain derived this way, rather than at each code transition, is rather insensitive to any one code's location and deviation from the ideal. Because of this, the gain from one of the previously mentioned lines creates the truest representation of the DAC's gain. Gain error is typically expressed as a percentage defined as

$$Gain\ Error\% = \frac{G_{DAC} * G_{IDEAL}}{G_{IDEAL}} \times 100\%. \tag{2.1}$$

# 2.1.1.3. Monotonicity

An ideal DAC is monotonic, as the output voltage derived from any one code is greater than the output voltage produced by the input code immediately preceding it. Denoting the output voltage of a code i as S(i), and the next code's

Fig.2.3. Example transfer curves of a monotonic DAC (a) and non-monotonic DAC (b)

output as S(i+1), one can take the discrete first derivative of the transfer curve, denoted as S'(i) from the formula

$$S'(i) = S(i+1) - S(i). (2.2)$$

For a DAC to be monotonic, the sign of S'(i) must be the same for any given code *i* (i.e. all positive for a rising ramp input or all negative for a falling ramp input). A transfer curve for a monotonic and non-monotonic DAC can be found in Fig.2.3.

### 2.1.1.4. Differential Nonlinearity

One limitation of the previously mentioned metrics is that they characterize a DAC with a single value taken from an average. Notice that in the previous examples concerning monotonicity, the step sizes are not uniform. Two DACs may end up with an identical gain value as derived from their best-fit lines, but different transfer curves, as shown in Fig. 2.4. Note that in (a) the values fall within the ideal range, unlike (b) where the endpoints fall outside of it.

Fig.2.4. An example of two different transfer curves with identical best-fit lines.

Differential non-linearity (DNL) is a figure of merit specifically used to address this issue, as it is used to describe the uniformity of the LSB step sizes between adjacent DAC input codes. DNL represents the error in each step size, expressed in fractions of LSBs. It is computed in a manner not dissimilar from the discrete first derivative, normalizing the result as follows

$$DNL(i) = \frac{S(i+1) - V_{LSB}}{V_{LSB}} LSB. \tag{2.2}$$

As mentioned previously, it is important to keep the V<sub>LSB</sub> value consistent, choosing either the ideal value, or the one derived from one of the linear approximations (endpoints or best-fit).

### 2.1.1.5. Integral Nonlinearity

Integral nonlinearity (INL), much like DNL, is a figure of merit that results in a curve that provides a fuller understanding of a DAC's transfer characteristic. INL is a comparison of the actual DAC transfer curve and one of the three previously mentioned lines; ideal, endpoint-to-endpoint, or best-fit. More specifically, INL is the subtraction of the reference line from the DAC's transfer curve, normalized to be expressed as a fraction of the average LSB step size, or

$$INL(i) = \frac{S(i) - S_{ref}(i)}{V_{LSB}} LSB. \tag{2.3}$$

It is worth noting that while the above formula describes the absolute error if using the ideal line, the INL curve is the integral of the DNL curve, thus its name. DNL is a measurement of the error in step sizes from one code to the next, while INL is the accumulated error for the step sizes.

# 2.1.2. Analog Channel Performance Metrics

The bulk of the thesis is focused on the noise-shaping capabilities of  $\Delta\Sigma$  modulation, and as such this subsection introduces some of the essential performance metrics and sources of non-idealities relevant to  $\Delta\Sigma$  modulation.

### 2.1.2.1. Noise

All practical circuits generate some amount of noise. The source of this noise may be thermal, in the case of resistors, 1/f noise for CMOS transistors, or this noise may be generated from quantization for ADCs and DACs. For the purposes of this thesis, noise will be defined as any signal component other than the primary input test signal.

### 2.1.2.2. Signal-to-Noise Ratio

The primary figure of merit that will be used for characterizing the modulators in this thesis is the Signal-to-Noise ratio (SNR). It is the ratio of the input signal (typically in volts RMS) and the total combined RMS voltage of all the noise sources (frequencies that are do not correspond to the input). Typically, SNR is described in dB as

$$SNR = 20log_{10} \left( \frac{S}{\sqrt{N_1 + N_2 + \dots + N_X}} \right),$$

(2.4)

where S corresponds to the signal, and all N values are the various noise sources.

### 2.1.2.3. Quantization Noise

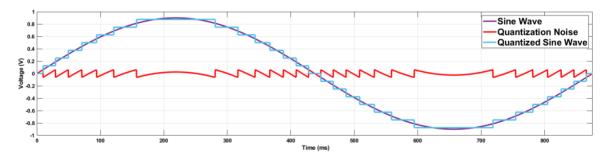

In  $\Delta\Sigma$  converters, one inherent source of noise is quantization. Whenever a signal passes from the digital to analog domains and vice versa, it is not perfectly recreated. If one were to look at the mapping between digital codes and the real-world voltages they represent, there is a loss of information within the realm of LSBs, as shown in Fig. 2.5.

Fig.2.5. An example of quantization and the effective noise it creates.

Fig.2.6. An example of two output frequency spectra displaying symmetric harmonic distortion (a) and asymmetric harmonic distortion (b).

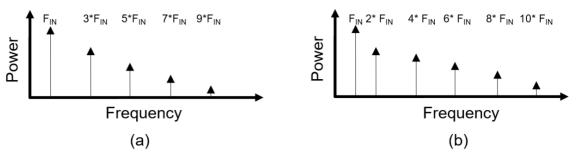

### 2.1.2.4. Harmonic Distortion

Whenever a signal passes through a non-linear circuit, harmonic distortion arises. The output spectrum of a nonlinear circuit does include the frequency components injected at the input, but also frequencies that are integer multiples (harmonics) of those same input frequencies, as shown in Fig. 2.6. Harmonic distortion, if tested on its own, is typically tested with one test frequency at a time. The input test tone's frequency is often referred to as the fundamental tone. Symmetric distortion is called so as it is symmetrical about the x-axis, generating odd harmonics. Conversely, asymmetrical distortion (typically clipping on only one portion of the waveform) adds in even harmonics.

### 2.1.2.5. Intermodulation Distortion

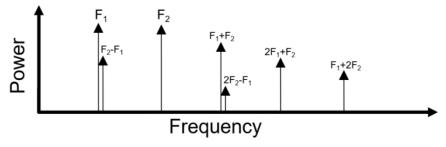

Intermodulation distortion, much like harmonic distortion, involves the injection of output tones that were not present at the input. The main difference between the two is that intermodulation is caused when multiple tones are present at the input. The frequencies may be any sum or difference of any integer multiples of the input tones, as shown in Fig. 2.7.

Fig.2.7. An example of Intermodulation Distortion.

For any two input tones  $F_1$  and  $F_2$  from a multi-tone signal, distortion components of any frequency satisfying

$$|q \times F_1 \pm p \times F_2| \tag{2.5}$$

may appear. The variables q and p are both integers. For intermodulation defined as nth order, the sum of q and p must be equal to n, or

$$q + p = n \tag{2.6}$$

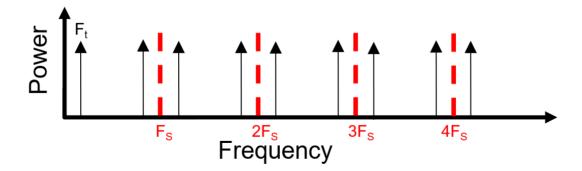

# 2.1.2.6. Imaging

Imaging is a type of distortion that can occur in sampled systems, which makes this quite relevant to the thesis. As a DAC uses a sampling frequency  $F_s$ , an input signal with frequency  $F_t$  is reconstructed at the output, several image tones are introduced. These tones, denoted as  $F_{image}$  will appear the frequencies satisfying

$$F_{image} = n \times F_s \pm F_t \tag{2.6}$$

An example of imaging is shown in Fig. 2.8. As one can surmise, aliasing can be quite an issue if the sampling frequency is quite low or close to the input signal frequency. Oversampling can aid in overcoming this.

Fig.2.8. An example of imaging

Fig.2.9. The Changeover Switch 1-Bit DAC: (Single-Pole, Double Throw, SPDT)

### 2.2. DAC Architectures

This section provides an expeditious summary of several common DAC architectures as reported in the relevant literature; namely the benefits and limitations of each architecture are presented and compared. It should be noted that much of the information presented here is also presented in [3].

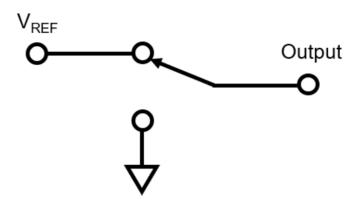

### 2.2.1. Changeover Switch

The changeover switch is also known as a single-pole, double throw (SPDT) switch. It can be thought of as the simplest DAC as it switches the output between two set voltage levels: typically, either between a reference voltage and ground or between a positive reference voltage and a negative voltage with the same magnitude. Fig. 2.9. shows this switch.

The main advantage of this architecture is that it is quite simple to implement, but as a downside it can't effectively be scaled up to accept a multibit input. While quite simple and not needing more discussion in this subsection, the changeover switch is used as a building block in many other DACs.

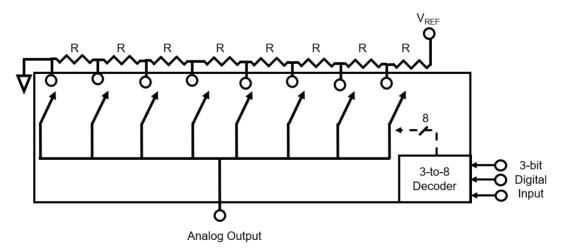

### 2.2.2. Kelvin Divider DACs

The Kelvin Divider DAC, named after Lord Kelvin, is also called the string DAC. Aside from the changeover switch discussed previously, this is the simplest DAC structure (or simplest altogether if considering DACs that accept digital words). A string DAC is composed of  $2^N$  resistors of equal resistance, and an additional  $2^N$  switches. These are allocated such that there is one for each node

of the chain and output. An example of a string DAC is shown in Fig. 2.10. As one can see, the DAC also includes some digital circuitry called a decoder, which takes the N bit input and converts it into 2<sup>N</sup> separate signals of which only one is active. This corresponds to the value of the N-bit input decoded, and as such returns the output voltage.

The architecture itself is quite simple, and the digital circuitry involved in the decoder is quite cheap to implement. In addition, the voltage output is inherently monotonic, as even a short-circuit in one of the resistors cannot cause any particular output code's voltage to exceed the output of the following code.

The major downside lies in the heavy use of analog components. For a linear increase in resolution, one must incur an exponential cost in components. Analog components such as resistors can take up a considerable amount of space and generate a non-negligible amount of heat if they become numerous. Being so dependent on a chain of resistors means that any efforts at trimming said resistors is costly and impractical. This is further exacerbated by their small size.

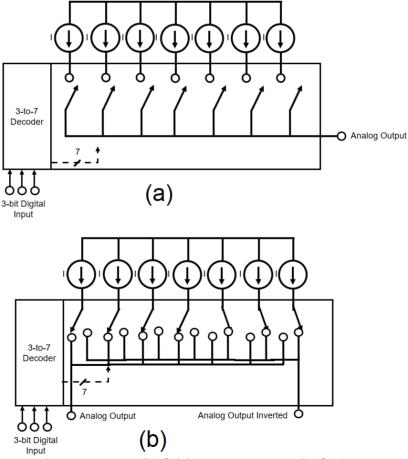

### 2.2.3. Thermometer DACs

Thermometer DACs are also called Fully-Decoded DACs, and are not too dissimilar to string DACs in principle. Once more, an N-bit code serves as the

Fig.2.10. Kelvin Divider/String DAC

input which is passed through a decoder to provide the output. However, the main difference lies in the fact that for whatever input code is used, a number of switches corresponding to that input will be activated. Fig. 2.11. (a) shows a thermometer DAC. Notice here that the number of elements in the chain in  $2^{N}$ -1 rather than  $2^{N}$ .

The primary advantage of such an architecture is similar to that of a string DAC, as the thermometer DAC is inherently monotonic. In addition, since the current sources (or equivalents) are to be of the same value, nonlinearities are quite small. A small modification to the DAC, as shown in Fig. 2.11. (b) in which the switches steer the current sources either to the output node, or another one which acts as its complement. This is quite useful for high-speed applications, as steering a current from one path to another one causes far less glitch than simply turning it on or off.

Fig.2.11. Diagram of a thermometer DAC (a) and thermometer DAC with complementary current outputs

The greatest drawback here, however, is the over-reliance on a large number of analog components; A linear increase in resolution N begets an exponential increase in the number of analog components used, and subtracting one as compared to a string DAC does little to alleviate this.

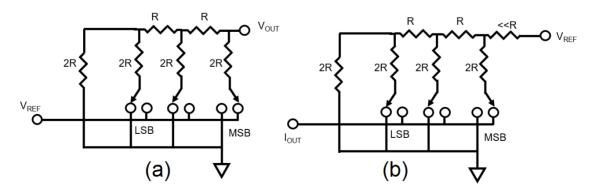

### 2.2.4. R-2R DACs

The R-2R DAC is among the most common building blocks used for DACs. This specific architecture can be used in either a voltage or current mods, as exemplified in Fig. 2.12. It is evident that the converter is named after the ladder network made up of two different resistor values, in a ratio of 2:1. This architecture was first proposed by Smith in 1953 [5]

The main advantage of the R-2R DAC is that a linear increase in resolution only requires a linear increase in the number of resistors used. More specifically, an N-bit R-2R DAC requires 2N resistors. In addition, their relatively low numbers make trimming more appealing. The R-2R ladder also does not need any extra digital circuitry, such as a decoder. Furthermore, the voltage-mode variation presents a constant output impedance, which eases the process of stabilizing any amplifier connected to the output node.

One major disadvantage of the R-2R ladder DAC lies at the input. The switches are required to operate over the voltage range covering VREF to ground, which can be difficult from a manufacturing standpoint. In addition, the input impedance, unlike output impedance, varies drastically over the span of all the input codes that can be used, and so the input must be driven by a low impedance.

Fig.2.12. R-2R DAC structure for voltage output (a) and current output (b)

To add to this, the value  $G_{DAC}$  cannot be readily changed by means of a resistor in series with the voltage reference terminal.

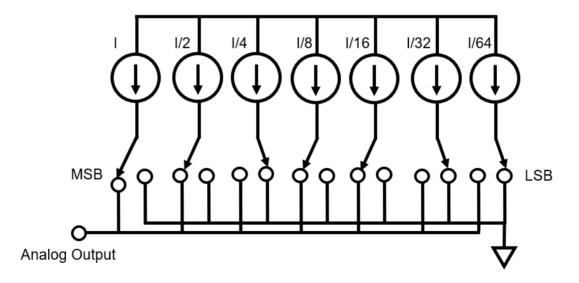

## 2.2.5. Binary-Weighted DACs

All of the previous architectures use very uniform analog components. As the name suggests, binary-weighted DACs use binary-weighted resistors or sources, which are then used to produce the desired analog value from the digital input code switching those sources on or off, as shown in Fig. 2.13. One of the earliest references to binary-weighted DACs can be found in a patent by Paul M. Rainey, dating back to 1921.

The main advantage of the binary-weighted DAC is how few components are needed for a high-resolution DAC. For an N-bit DAC producing 2<sup>N</sup> possible outputs, one needs N sources to create such a DAC.

The greatest downside of binary weighted DACs is the precision required off the components themselves. For example, if one were to take a 7-bit DAC using 7 binary-weighted current sources, the sources responsible for LSB and MSB contributions would need to be matched such that non-linearities are minimized (i.e., a ratio of 64:1). This can quickly become a problem at resolutions of 10 bits or above, as now the ratio between the current sources responsible for

Fig.2.13. Current-Mode Binary-Weighted DAC

the LSB and MSB contributions now result in the former being a fraction of a percent of the latter. This makes components mismatch errors a serious issue.

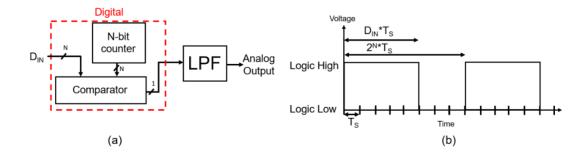

#### 2.2.6. Pulse-Width Modulation DACs

A pulse-width modulated (PWM) DAC is a type of converter is typically constructed using a counter to generate an output voltage proportional to the digital input word. The entire circuit operates off of a sampling clock, which causes an N-bit counter to cycle through all its possible values, compared to the digital input. If the input is greater than the counter's value, a high voltage is produced at the output. Otherwise, a low voltage is produced. This effectively creates a rectangular wave with 2<sup>N</sup> sampling periods each lasting Ts and a duty cycle proportional to the input. This output bitstream must then be passed through a low-pass filter (LPF) to reconstruct the intended. Fig. 2.14 shows a diagram of a PWM DAC, as well as the output bitstream of a 3-bit PWM DAC of an input code of 5.

The primary advantage that PWM DACs provide is the high level of linearity, requiring no calibration. In addition, PWM requires digital components primarily, which are quite economical in their area usage.

The primary disadvantage faced when using PWM is the analog LPF, which consumes a significant silicon area when creating a high-resolution DAC. Since the output is always at a period of 2<sup>N</sup> sampling periods, the filter must be able to remove frequencies that are twice as close to the input frequency range with each additional bit of resolution.

Fig.2. 14 A block diagram of a PWM DAC (a) and an example output bitstream (b) for a 3-bit DAC and input of 5

Fig.2.15. Structure of a  $\Delta\Sigma$  Modulator

#### 2.2.7 ΔΣ Modulation DACs

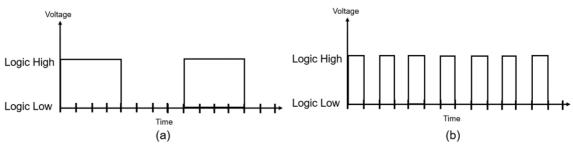

Much like PWM DACs,  $\Delta\Sigma$  DACs produce a bitstream at the output of a digital circuit which is then passed through a LPF to produce the intended signal. The structure of a typical  $\Delta\Sigma$  DAC is shown in Fig. 2.15. The key difference between them is that the bitstream produced by a  $\Delta\Sigma$  DAC is the result of pulse density modulation (PDM), or a much more evenly distributed array of pulses. As an example, consider Fig. 2.16. which shows what output is produced by both a PWM DAC and the simplest  $\Delta\Sigma$  DAC (with the filter replaced with a delay rather than a filter) for a digital input word equal to half of the input range.

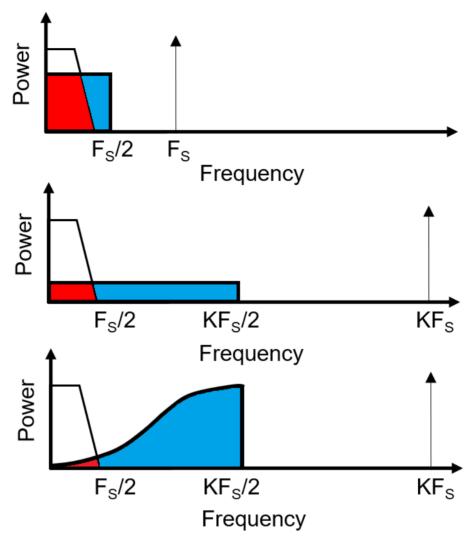

The nature of this output bitstream has several desirable consequences for frequency response. As can be seen in Fig. 2.17. where the red area is quantization noise that remains, with blue being the noise removed by the digital filter. In a typical DAC with sampling frequency  $F_s$ , the quantization noise is concentrated at the lower frequencies and so cannot be adequately dealt with using a low pass filter. With oversampling, that same quantization noise is now spread out all the way to  $KF_s/2$ , drastically reducing the noise observed at the input signal band. Combining this with the noise-shaping properties of the  $\Delta\Sigma$

Fig.2.16. A comparison of DAC output bitstreams using N=3 and input of 4 for a PWM DAC (a) and  $\Delta\Sigma$  DAC (b)

Fig.2.18. Frequency distribution of noise, for an ordinary DAC (a), an oversampling DAC (b), and a noise-shaping DAC (c)

modulator (thanks to the filter in its feedback loop), the noise is further pushed out to the higher frequencies, out of the input signal band. These properties make the  $\Delta\Sigma$  modulator a fantastic low-cost, high-resolution option (24 bits). Its low power and low bandwidth make it a suitable for applications in voiceband and general audio signal processing. It also reduces the need for a costly low-pass filter, thanks to the PDM nature of the output.

There still exist limitations to  $\Delta\Sigma$  modulation, namely the loop filter's component cost rising exponentially with a linear increase in resolution, on top of the worst-case PDM output being on par with the worst case PWM output. These are the issues that this thesis aims to address.

## 2.3 Segmented $\Delta\Sigma$ Modulation

Where the two previous sections covered more general information concerning DACs, this section of the second chapter seeks to address topics more specific to this thesis. In the first subsection, a review of the literature concerning segmentation in DACs will be covered, followed by a review of the use of segmentation in  $\Delta\Sigma$  converters in the second subsection.

### 2.3.1. Segmented DACs

A segmented DAC is a Digital-to-Analog converter whose architecture treats various "segments" of the digital input word differently. In some cases, this may entail using one of the DAC architectures for one of the segments, and a different architecture of another to better exploit their various strengths and shore up their weaknesses.

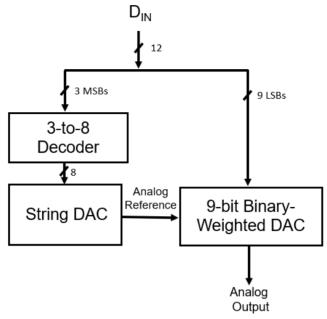

A common use for segmentation uses a thermometer DAC architecture to handle the MSBs (coarse DAC) while employing a binary-weighted DAC to handle the LSBs (fine DAC) as seen in [6, 7]or an R-2R DAC as seen in [6, 7, 8]. This type of architecture provides excellent linearity while mitigating the exponential increase in area consumption. In addition, the second case provides the advantage of only needing one resistor value, making manufacturing much simpler.

It is worth noting that one of the earliest cases of a segmented DAC can be found in [9], back in 1979. The motivation in that case was to make a monotonic DAC with no trimming. By dividing what would have been an ordinary resistor-ladder converter into eight segments, resistors with lower tolerances could be used for each segment for comparable non-linearities to an ordinary R-2R DAC (0.05% versus 0.4%), resulting in a decrease in resistors used by approximately 35%. A diagram of this can be found in Fig. 2.18. The leftmost segment consists of a generator and decoder which create the voltage reference used for the right segment, which uses a binary-weighted segmented 9-bit DAC to create 512 separate voltage levels from the reference fed into it. The "coarse" DAC effectively selects one of 8 current references, and then split using the "fine" DAC, creating

Fig.2.20. A Block diagram of an early segmented DAC, as described in [9]

4096 output voltage levels. The 9-bit DAC is in fact a 4-bit and 5-bit DAC used together, making this example segmented in two ways.

### 2.3.2. Segmentation in $\Delta\Sigma$ DACs

This subsection presents several examples of segmentation being used in  $\Delta\Sigma$  converters and contrasting that with the aim of the structure used later in this thesis. This is done in order to better understand what the thesis is about, as it is vital to understand what this work is not about first.

The use of segmentation in  $\Delta\Sigma$  modulators has previously been adopted for the sake of reducing a  $\Delta\Sigma$  ADC quantizer to reduce the exponential complexity increase of the Dynamic matching element (DEM) and the digital-to-analog converter needed in its construction [10]. While this holds some similarity, this work uses segmentation for the Delta-Sigma converter as a whole, including H(z). Fig. 2.19. includes a simplified diagram of the converter. Notice here that the segmented DACs are being used within a  $\Delta\Sigma$  Analog-to-Digital converter's feedback path, to be fed back into the modulator input. This is in sharp contrast to this thesis, which aims to use segmentation of the modulator itself.

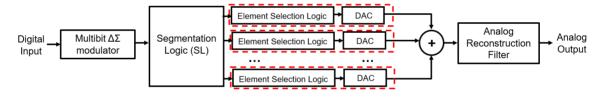

$\Delta\Sigma$  modulator segmentation has also been used to in techniques for segment-mismatch shaping in multi-bit  $\Delta\Sigma$  DACs [11] and ADCs [12] significantly

Fig.2.21. Block Diagram of  $\Delta\Sigma$  ADC using segmented DAC, as seen in [10]

improving the noise-shaping response of the modulator in question. Once again, Fig. 2.20. and Fig. 2.21. include diagrams of these examples, showing here once again that the segmentation takes place within on the component level rather than a system level. In the case of the DAC, segmentation is used in conjunction with element selection logic (ESL) to transform a multibit  $\Delta\Sigma$  modulator output into a vector to control the DACs.

Fig.2.23. A mismatch-shaped segmented multibit  $\Delta\Sigma$  DAC, as shown in [11]

Fig.2.22. Block diagram of the architecture proposed in [12], with mismatch error feedback

Fig.2.24. Block diagram of the digital noise-coupling technique from [13]

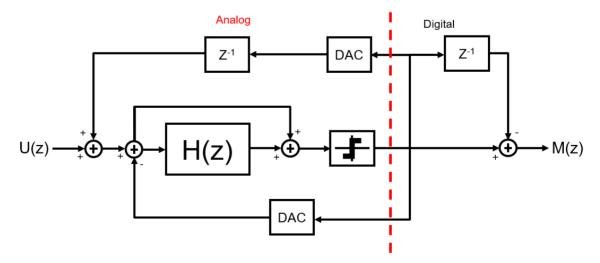

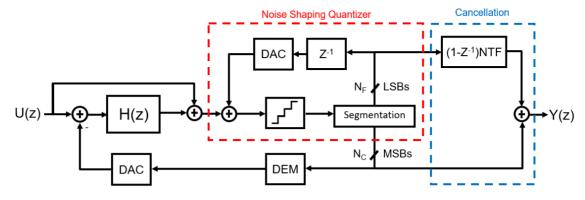

Furthermore, a digital noise-coupling technique for  $\Delta\Sigma$  modulators also made use of segmentation [13], but rather than applying this to the input and modulator proper, the quantizer inputs were segmented instead. The MSBs were led into the modulator output directly, while the LSBs were used for the noise coupling as they approximate the quantization noise introduced by the system. It also helped reduce the area of the auxiliary DAC (treating the LSBs) in the digital noise coupling case, which is not too dissimilar from one of the goals of this thesis. Fig. 2.22 demonstrates this structure. A similar process was used in [14], in this case relaxing the bandwidth and settling error requirements, thanks to the uniform linear settling behavior.

It is also worth noting [15] as it pertains to segmentation with after  $\Delta\Sigma$  modulation has been performed, which stands in contrast to this work where the  $\Delta\Sigma$  modulator is itself segmented. Once again, the structure is shown in Fig. 2.23.

Fig.2.25. Segmentation combined with scrambling, as seen in [15]

# 2.4 Summary

This chapter reviewed the literature relevant to fully understanding the material, context, and goals of the thesis. The essentials of DAC testing and the metrics to gauge performance were introduced in the first subsection, the second subsection compared various DAC architectures to better understand why  $\Delta\Sigma$  was chosen, and in the last subsection literature more specific to segmented  $\Delta\Sigma$  modulation was reviewed to fully understand where this thesis stands and what gap in knowledge it seeks to fill.

# Chapter 3: Theory and Design of Segmented ΔΣ Modulators

## 3.0. Introduction

This chapter will introduce the theory and mathematical analysis needed to describe segmented  $\Delta\Sigma$  digital-to-analog conversion. In the first section, the theory of  $\Delta\Sigma$  is established. In the second section, this theory is used in a mathematical analysis of the 2-segment  $\Delta\Sigma$  converter. In the last section, this analysis is extrapolated to a generalized K-segment  $\Delta\Sigma$  converter.

Fig.3.1 Typical structure of a  $\Delta\Sigma$ -based DAC

## 3.1. Theory of $\Delta\Sigma$ Modulation

This first section covers the principles behind the operation of DS modulation, in order to lay the foundation for the rest of the thesis. First the basic principles of  $\Delta\Sigma$  conversion will be covered, followed by a mathematical analysis of a typical  $\Delta\Sigma$  structure, which leads into the subsection concerning the modulator structure that will be used in this thesis. In the last subsection, the performance properties of this structure will be covered.

### 3.1.1. ΔΣ Converter Principles

The typical structure of an oversampling converter involves three stages as seen in Fig. 3.1. In the case of D/A, the first stage is the  $\Delta\Sigma$  modulator, which provides a sequence of pulses (bitstream) as an output. This is the followed by a 1-bit DAC which converts the two logic values into analog quantities, e.g., voltage level which are then fed into an analog lowpass filter (LPF) to reconstruct the original input.

#### 3.1.2. General ΔΣ Modulator Structures

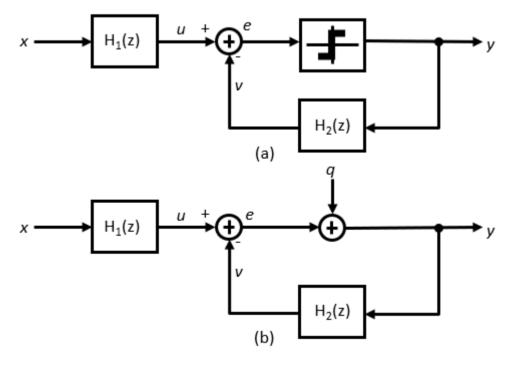

Figure 3.2 shows the signal-flow graph of a typical delta-sigma modulator and the linear model. The main blocks are a pair of linear filters  $H_1$  and  $H_2$ , and the one-bit quantizer. The input x is filtered by the first linear filter, and then negative feedback is applied to the result by way of the second filter, which produces the input to the quantizer, e. The output of the quantizer, y, acts as the output, while being filtered by the second filter block, and sent back to the "sigma" block. This creates a negative feedback loop in an ultimately non-linear system. The quantizer can be modelled as a noise source, as is made apparent in Fig. 3.2. (b). With this

new change, the quantizer output *y* is given via a sum of the original quantizer input e and the associated quantization noise q from the new adder. This noise model allows one to perform a Z-transform on the system, giving the equation

$$Y(z) = \frac{H_1(z)}{1 + H_2(z)} \cdot X(z) + \frac{1}{1 + H_2(z)} \cdot Q(z). \tag{3.1}$$

Thanks to this, there is now a relatively simple way to relate the input, noise, and output in the frequency domain. One can think of the factor being multiplied by X(z) as the signal transfer function (STF)

$$STF(z) = \frac{H_1(z)}{1 + H_2(z)}$$

(3.2)

which determines how the original signal is interpreted at the output Y(z), and the factor multiplying Q(z) as the noise transfer function (NTF)

$$NTF(z) = \frac{1}{1 + H_2(z)}$$

(3.3)

which similarly determines how the noise is interpreted at the output. From here,

Fig.3.2. Signal flow graph (a) and linear model (b) of a  $\Delta\Sigma$  modulator

one can rewrite our original equation for the output as the more general

$$Y(z) = STF(z) \cdot X(z) + NTF(z) \cdot Q(z). \tag{3.4}$$

In the frequency domain, the noise source can be thought of as white noise. This is an approximation, but for any modulator above first order, this is fairly accurate.