## **High-Speed Decoders for Polar Codes**

Pascal Giard

Department of Electrical and Computer Engineering McGill University Montreal, Canada

September 2016

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

© 2016 Pascal Giard

### Acknowledgments

I would like to start by thanking my supervisors, Warren J. Gross and Claude Thibeault. Thanks for their continuous support, mentorship, valuable advice and helpful discussions provided over the years. I am glad that we had such a good relationship that allowed me to freely explore while staying focused on tangible goals.

Many thanks to my friend and colleague Gabi Sarkis. A lot of this work would have been tremendously more difficult to nearly impossible without his help. His algorithmic, software and hardware skills, his vast knowledge, and his insightful comments were all of incredible help. Furthermore, his willingness to cooperate led to very fruitful collaborations stirring both of us up and helping me to remain motivated during the harder times.

I would also like to thank Alexandre J. Raymond, Alexios Balatsoukas-Stimming and Carlo Condo who helped me in one way or another. Thanks to Samuel Gagné, Marwan Kanaan and François Leduc-Primeau for the interesting discussions we had during our downtime.

I am grateful for the financial support I got from the Fonds Québécois de la Recherche sur la Nature et les Technologies, the fondation Pierre Arbour and the Regroupement Stratégique en Microsystèmes du Québec.

Finally, I would like to thank my beautiful boys Freddo and Gouri as well as my wonderful and beloved Joëlle. Their patience, support and indefectible love made this possible. Countless times, Joëlle had to sacrifice or take everything on her shoulders so that I could pursue this degree, and the one before. I am very grateful and privileged that she stayed by my side.

## Abstract

Error detection and correction plays a vital role in modern information storage and communication systems. Polar codes are gathering a lot of attention as they are a class of capacity-achieving error-correcting codes with an explicit construction that can be decoded with low-complexity algorithms. However, their adoption is hindered by the lack of high-speed—high throughput and low latency—hardware and software decoders for codes of practical length and rate.

This thesis presents various solutions to this problem. It introduces modifications to the stateof-the-art low-complexity decoding algorithm to better accommodate low-rate polar codes. It also proposes a code construction alteration process. Hardware implementation results show good latency reduction and throughput improvement with little to negligible coding loss for low-rate moderate-length polar codes.

Then, it presents high-speed software polar decoders. It shows how adapting the decoding algorithm at various levels can lead to significant improvements in latency and throughput, yielding polar decoders that are suitable for high-performance software-defined radio applications on modern desktop processors and embedded-platform processors. These proposed decoders have an order of magnitude lower latency and memory footprint compared to state-of-the-art decoders, while maintaining comparable throughput. In addition, strategies and results for implementing polar decoders on graphical processing units are presented.

Next, it demonstrates that polar decoders can achieve extremely high throughput values and retain moderate complexity. It presents a family of architectures for hardware polar decoders that employ unrolling. The resulting fully-unrolled architectures are capable of achieving a throughput that is two to three orders of magnitude greater than current state of the art while maintaining good energy efficiency. Moreover, the proposed architectures are flexible in a way that makes it possible to explore the trade-off between area, throughput and energy efficiency.

Lastly, while unrolled decoders provide the greatest decoding speed, they are built for a specific, fixed, code i.e. the code length or rate cannot be modified at execution time. Most modern wireless communication applications largely benefit from the support of multiple code lengths and rates. This thesis shows how an unrolled decoder can be transformed into a multi-mode decoder supporting many codes of various lengths and rates. Implementation results show a peak information throughput that is an order of magnitude greater than the state of the art, while showing the best area and energy efficiency.

## Abrégé

La détection et la correction des erreurs jouent un rôle essentiel dans les systèmes modernes de stockage et de communication. Les codes polaires intriguent actuellement beaucoup de chercheurs car ils constituent une classe de codes correcteurs capables d'atteindre la capacité théorique d'un canal avec des algorithmes de décodage de faible complexité tout en proposant une méthode de construction explicite. Cependant, leur adoption est ralentie par le manque d'implémentation matérielle et logicielle de décodeurs hautes vitesses i.e. à faible latence et à haut débit.

Cette thèse propose de multiples solutions à ce problème. Elle introduit d'abord des modifications à l'algorithme de décodage de faible complexité, qui est l'état de l'art, afin d'accommoder les codes polaires à faible taux de codage. Elle propose également une méthode d'altération de la construction des codes polaires. Les résultats d'implémentation matérielle montrent que, pour des codes polaires de longueur moyenne et de faible taux de codage, on obtient une bonne réduction de la latence ainsi qu'une augmentation appréciable du débit au coût d'une perte faible ou nulle en terme de performance de correction d'erreurs.

Puis, elle présente des décodeurs polaires logiciels hautes vitesses. Elle montre, qu'en adaptant l'algorithme de décodage à divers niveaux, on obtient des améliorations significatives en terme de latence et de débit. Il en résulte des décodeurs polaires très intéressants pour les applications de radio logicielle haute performance s'exécutant sur processeur moderne de bureau ou de plate-forme embarquée. Les décodeurs proposés ont une latence et une empreinte mémoire qui est un ordre de grandeur inférieur par rapport à l'état de l'art tout en maintenant un débit compétitif. De plus, des stratégies ainsi que des résultats pour l'implémentation de décodeurs polaires sont présentés pour des processeurs graphiques généralistes.

Ensuite, elle démontre que les décodeurs de codes polaires peuvent atteindre des débits excessivement élevés tout en conservant une complexité modérée. Elle présente une famille d'architecture matérielle pour les décodeurs de code polaire faisant appel à la technique de déroulage. Les architectures complètement déroulées qui en résultent sont capables d'atteindre des débits qui sont de deux à trois fois plus élevés que l'état de l'art tout en maintenant une bonne efficacité énergétique. De plus, les architectures proposées sont flexibles de sorte qu'il est possible d'explorer les compromis entre la surface, le débit et l'efficacité énergétique.

Enfin, bien que les décodeurs déroulés offrent la meilleure vitesse, ils sont construits pour un code spécifique i.e. un code d'une longueur et d'un taux de codage qui ne peuvent être modifiés au

moment de l'exécution. Les systèmes de communication sans-fil modernes bénéficient du support de multiple codes de longueurs et de taux variés. Ainsi, cette thèse montre comment un décodeur déroulé peut être transformé en décodeur multimode supportant plusieurs codes de longueurs et de taux variés. Les résultats d'implémentation montrent un débit nominal qui est un ordre de grandeur plus élevé que l'état de l'art tout en montrant les meilleurs taux d'efficacité en terme de surface et d'énergie.

## Contents

| Co | Contents |               |                                     |  |   | vii |   |   |            |      |

|----|----------|---------------|-------------------------------------|--|---|-----|---|---|------------|------|

| Li | st of I  | Figures       |                                     |  |   |     |   |   |            | xi   |

| Li | st of ]  | <b>Fables</b> |                                     |  |   |     |   |   |            | xiii |

| 1  | Intro    | oduction      |                                     |  |   |     |   |   |            | 1    |

|    | 1.1      | Objectiv      | ves                                 |  |   |     |   | • |            | 3    |

|    | 1.2      | Summa         | ry of Thesis Contributions          |  |   |     |   | • |            | 3    |

|    | 1.3      | Related       | Publications                        |  | • |     |   | • |            | 5    |

|    | 1.4      | Thesis (      | Organization                        |  | • |     |   | • | . <b>.</b> | 7    |

| 2  | Pola     | r Codes       |                                     |  |   |     |   |   |            | 9    |

|    | 2.1      | Constru       | ction                               |  |   |     |   | • |            | 9    |

|    | 2.2      | Tree Re       | presentation                        |  |   |     |   | • |            | 10   |

|    | 2.3      | Systema       | atic Coding                         |  |   |     |   | • |            | 11   |

|    | 2.4      | Success       | ive-Cancellation Decoding           |  | • |     |   | • |            | 12   |

|    | 2.5      | Simplif       | ed Successive-Cancellation Decoding |  |   |     |   | • |            | 13   |

|    |          | 2.5.1         | Rate-0 Nodes                        |  | • |     | • | • |            | 13   |

|    |          | 2.5.2         | Rate-1 Nodes                        |  | • | •   | • | • |            | 13   |

|    |          | 2.5.3         | Rate- <i>R</i> Nodes                |  | • | •   | • | • |            | 14   |

|    | 2.6      | Fast-SS       | C Decoding                          |  | • |     |   | • |            | 14   |

|    |          |               | Repetition codes                    |  |   |     |   |   |            |      |

|    |          |               | SPC codes                           |  |   |     |   |   |            |      |

|    |          | 2.6.3         | Repetition-SPC codes                |  | • |     | • | • |            | 15   |

|   |      | 2.6.4 Other Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16        |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 2.7  | Other SC-based Decoding Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16        |

|   |      | 2.7.1 ML-SSC Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16        |

|   |      | 2.7.2 Hybrid ML-SC Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16        |

|   | 2.8  | Other Decoding Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17        |

|   |      | 2.8.1 Belief-Propagation Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17        |

|   |      | 2.8.2 List-based Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17        |

|   | 2.9  | SC-based Decoder Hardware Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19        |

|   |      | 2.9.1 Processing Element for SC Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19        |

|   |      | 2.9.2 Semi-Parallel Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20        |

|   |      | 2.9.3 Two-Phase Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20        |

|   |      | 2.9.4 Processor-like Decoder or the Original Fast-SSC Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20        |

|   |      | 2.9.5 Implementation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20        |

| 3 | Fast | Low-Complexity Hardware Decoders for Low-Rate Polar Codes 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23        |

| U | 3.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23        |

|   | 3.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -9<br>24  |

|   | 0.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - ·<br>24 |

|   |      | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - ·<br>25 |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26        |

|   | 3.3  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30        |

|   | 3.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33        |

|   | 011  | 3.4.1 Quantization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

|   |      | 3.4.2         Rep1 Node         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2         3.4.2 |           |

|   |      | 3.4.3 High-Level Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35        |

|   | 3.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35        |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35        |

|   |      | 3.5.2 Comparison with State-of-the-art Decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36        |

|   | 3.6  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39        |

| 4 | Low  | -Latency Software Polar Decoders 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41        |

|   | 4.1  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41        |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

## Contents

|   | 4.2 | Impler | nentation on x86 Processors                                              | 43 |

|---|-----|--------|--------------------------------------------------------------------------|----|

|   |     | 4.2.1  | Instruction-based Decoder                                                | 44 |

|   |     | 4.2.2  | Unrolled Decoder                                                         | 47 |

|   | 4.3 | Impler | nentation on Embedded Processors                                         | 54 |

|   | 4.4 | Impler | nentation on Graphical Processing Units                                  | 55 |

|   |     | 4.4.1  | Overview of the GPU Architecture and Terminology                         | 55 |

|   |     | 4.4.2  | Choosing an Appropriate Number of Threads per Block                      | 56 |

|   |     | 4.4.3  | Choosing an Appropriate Number of Blocks per Kernel                      | 56 |

|   |     | 4.4.4  | On the Constituent Codes Implemented                                     | 57 |

|   |     | 4.4.5  | Shared Memory and Memory Coalescing                                      | 58 |

|   |     | 4.4.6  | Asynchronous Memory Transfers and Multiple Streams                       | 58 |

|   |     | 4.4.7  | On the Use of Fixed-Point Numbers on a GPU                               | 59 |

|   |     | 4.4.8  | Results                                                                  | 59 |

|   | 4.5 | Energy | Consumption Comparison                                                   | 61 |

|   | 4.6 | Furthe | r Discussion                                                             | 62 |

|   |     | 4.6.1  | On the relevance of the instruction-based decoders                       | 62 |

|   |     | 4.6.2  | On the relevance of software decoders in comparison to hardware decoders | 62 |

|   |     | 4.6.3  | Comparison with LDPC codes                                               | 63 |

|   | 4.7 | Conclu | ision                                                                    | 64 |

| _ |     |        |                                                                          |    |

| 5 |     |        | ardware Architectures for Polar Decoders                                 | 67 |

|   | 5.1 |        | action                                                                   | 67 |

|   | 5.2 |        | of-the-Art Architectures with Implementations                            | 68 |

|   | 5.3 |        | ecture, Operations and Processing Nodes                                  | 69 |

|   |     | 5.3.1  | Fully Unrolled (Basic Scheme)                                            |    |

|   |     |        | Deeply Pipelined                                                         | 71 |

|   |     | 5.3.3  | Partially Pipelined                                                      | 72 |

|   |     | 5.3.4  | Operations and Processing Nodes                                          | 74 |

|   |     | 5.3.5  | Replacing Register Chains with SRAM Blocks                               | 75 |

|   | 5.4 | -      | nentation and Results                                                    | 76 |

|   |     | 5.4.1  | Methodology                                                              | 76 |

|   |     | 5.4.2  | Effect of the Initiation Interval                                        | 76 |

|    |         | 5.4.3   | Comparison with State-of-the-Art Decoders                            | . 78  |

|----|---------|---------|----------------------------------------------------------------------|-------|

|    |         | 5.4.4   | Effect of the Code Length and Rate                                   | . 80  |

|    |         | 5.4.5   | On the Use of Code Shortening in an Unrolled Decoder                 | . 84  |

|    |         | 5.4.6   | I/O Bounded Decoding                                                 | . 85  |

|    | 5.5     | Conclu  | ision                                                                | . 85  |

| 6  | Mul     | ti-mode | Unrolled Polar Decoding                                              | 87    |

|    | 6.1     | Introdu | uction                                                               | . 87  |

|    | 6.2     | Polar ( | Code Example and its Decoder Tree Representations                    | . 88  |

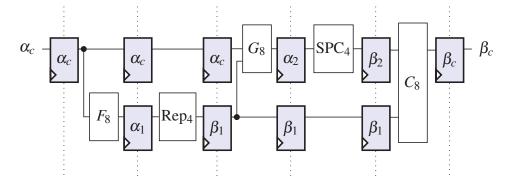

|    | 6.3     | Unroll  | ed Architectures                                                     | . 89  |

|    | 6.4     | Multi-  | mode Unrolled Decoders                                               | . 89  |

|    |         | 6.4.1   | Hardware Modifications to the Unrolled Decoders                      | . 90  |

|    |         | 6.4.2   | On the Construction of the Master Code                               | . 90  |

|    |         | 6.4.3   | About Constituent Codes: frozen bit locations, rate and practicality | . 92  |

|    |         | 6.4.4   | Latency and Throughput Considerations                                | . 93  |

|    | 6.5     | Impler  | nentation Results                                                    | . 94  |

|    |         | 6.5.1   | Error-correction Performance                                         | . 95  |

|    |         | 6.5.2   | Latency and Throughput                                               | . 96  |

|    |         | 6.5.3   | Synthesis Results and Comparison with the State of the Art           | . 97  |

|    | 6.6     | Conclu  | ision                                                                | . 99  |

| 7  | Con     | clusion | and Future Work                                                      | 101   |

|    | 7.1     | Future  | Work                                                                 | . 102 |

|    |         | 7.1.1   | Software Encoding and Decoding on APU Processors                     | . 103 |

|    |         | 7.1.2   | Software Encoding and Decoding on Micro-controllers                  | . 103 |

|    |         | 7.1.3   | High-speed Systematic Encoder                                        | . 103 |

|    |         | 7.1.4   | Multi-mode Unrolled List Decoders                                    | . 104 |

| Li | st of A | Acronyr | ns                                                                   | 113   |

# **List of Figures**

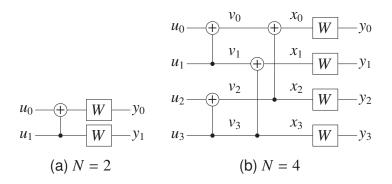

| 2.1 | Construction of polar codes of lengths 2 and 4.                                       | 10 |

|-----|---------------------------------------------------------------------------------------|----|

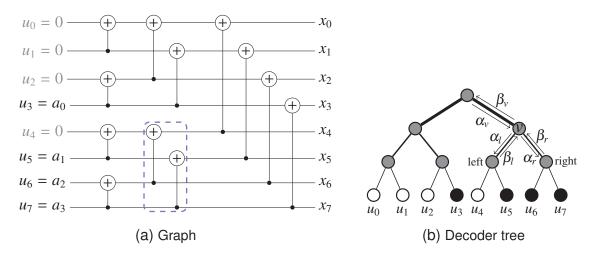

| 2.2 | Non-systematic $(8, 4)$ polar code represented as a graph and as a decoder tree       | 11 |

| 2.3 | Low-complexity systematic encoding of a (8, 4) polar code                             | 12 |

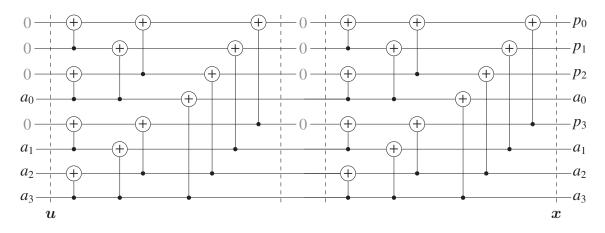

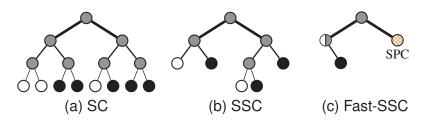

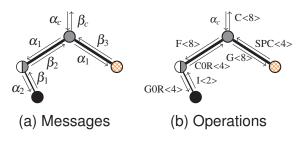

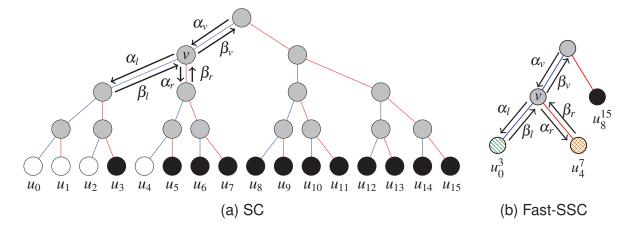

| 2.4 | Decoder trees corresponding to the SC, SSC and Fast-SSC decoding algorithms           | 14 |

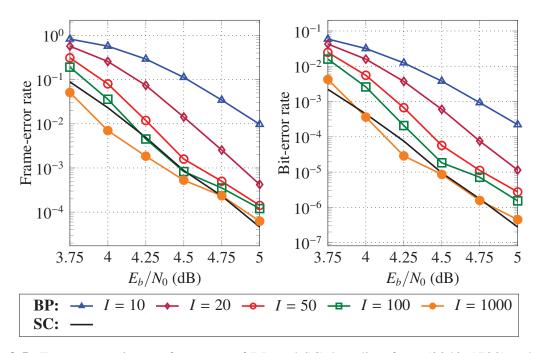

| 2.5 | Error-correction performance of BP and SC decoding for a (2048, 1723) polar code      | 18 |

| 2.6 | Error-correction performance of List, List-CRC and SC decoding of a (2048, 1723)      |    |

|     | polar code versus that of the (1944, 1620) 802.11n LDPC code                          | 19 |

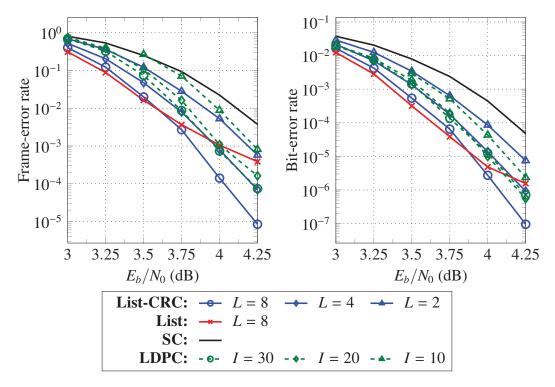

| 2.7 | Architecture of the data processing unit proposed in [8]                              | 21 |

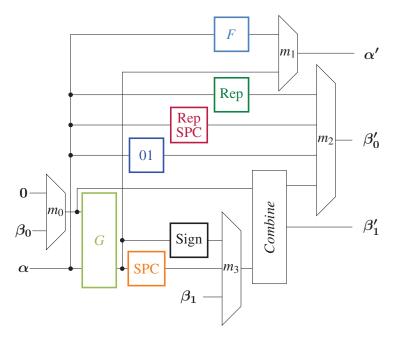

| 3.1 | Decoder tree for the (1024, 512) polar code built using [22] and decoded with the     |    |

|     | nodes and operations of Table 3.1                                                     | 26 |

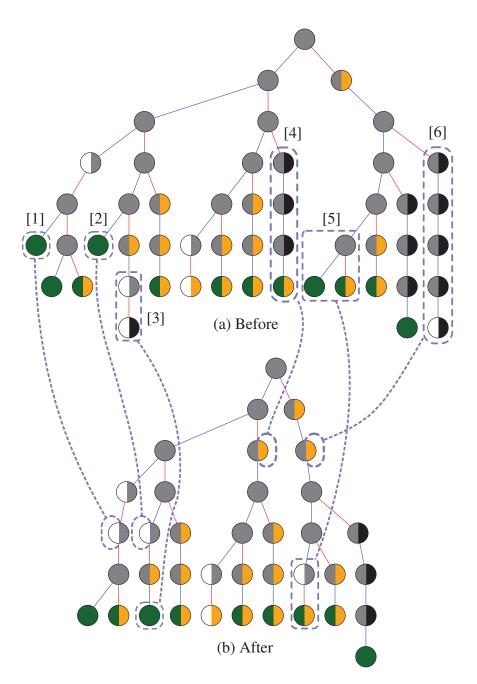

| 3.2 | Decoder trees for two different (512, 376) polar codes, where (a) and (b) are before  |    |

|     | and after construction alteration, respectively.                                      | 29 |

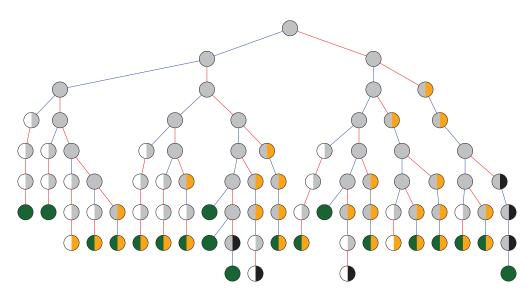

| 3.3 | Decoder tree for the altered (1024, 512) polar code                                   | 30 |

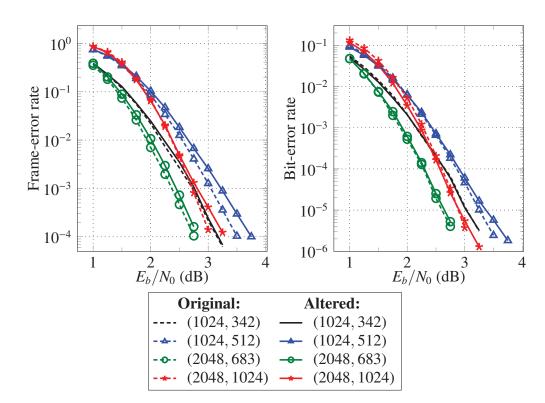

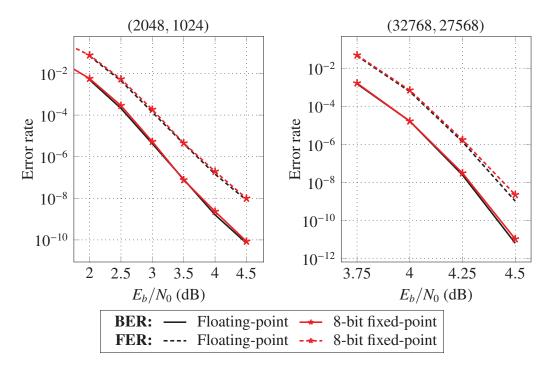

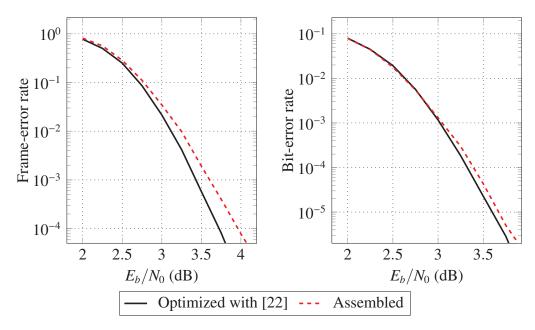

| 3.4 | Error-correction performance of the altered codes compared to that of the original    |    |

|     | codes constructed using the Tal and Vardy method.                                     | 31 |

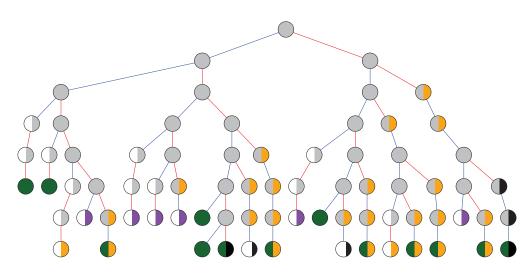

| 3.5 | Decoder tree for the altered polar code with the added nodes                          | 32 |

| 3.6 | Impact of quantization on the error-correction performance of the proposed (1024, 512 | )  |

|     | polar code                                                                            | 33 |

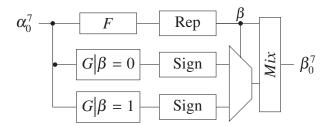

| 3.7 | Architecture of the Rep1 Node                                                         | 34 |

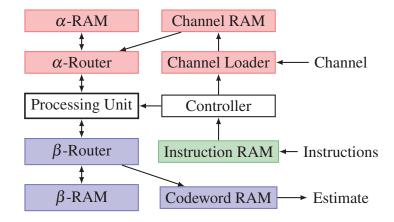

| 3.8 | High-level architecture of the decoder.                                               | 35 |

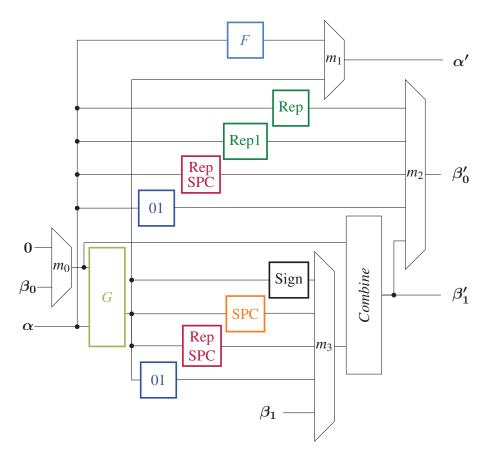

| 3.9 | Architecture of the processing unit                                                   | 36 |

| 4.1 | Effect of quantization on error-correction performance.                               | 45 |

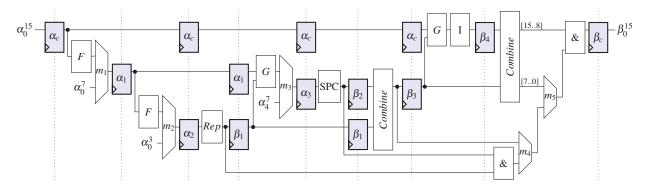

| Dataflow graph of a (8, 5) polar decoder                                                                                                                             | 48                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

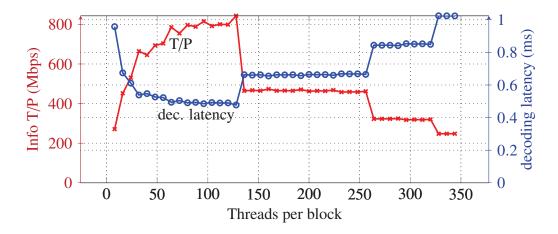

| Polar decoding on GPU: Effect of the number of threads per block                                                                                                     | 56                                                                                                                                                                                                                                                  |

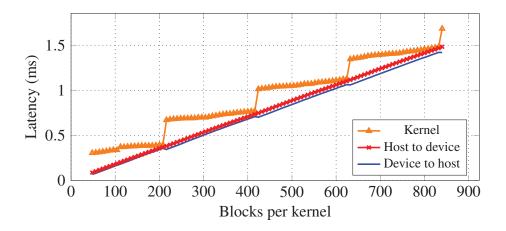

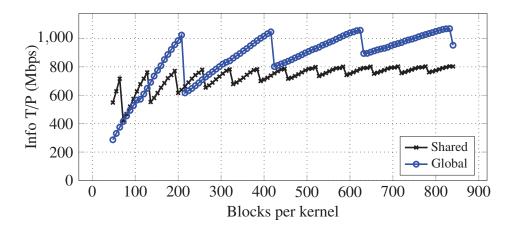

| Polar decoding on GPU: Effect of the number of blocks per kernel                                                                                                     | 57                                                                                                                                                                                                                                                  |

| Polar decoding on GPU: Shared versus global memory                                                                                                                   | 58                                                                                                                                                                                                                                                  |

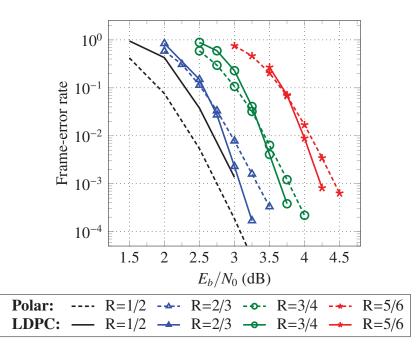

| Polar codes compared with LDPC codes from the 802.11n standard                                                                                                       | 64                                                                                                                                                                                                                                                  |

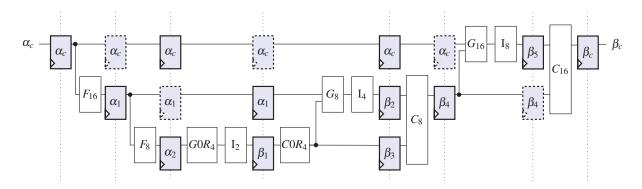

| Decoder trees for an (8,4) polar code decoded with the (a) SSC and (b) Fast-SSC                                                                                      |                                                                                                                                                                                                                                                     |

| algorithms                                                                                                                                                           | 70                                                                                                                                                                                                                                                  |

| Fully-unrolled decoder for a (8, 4) polar code.                                                                                                                      | 70                                                                                                                                                                                                                                                  |

| Fully-unrolled deeply-pipelined decoder for a (8, 4) polar code                                                                                                      | 71                                                                                                                                                                                                                                                  |

| Fully-unrolled deeply-pipelined decoder for a (16, 14) polar code                                                                                                    | 72                                                                                                                                                                                                                                                  |

| Fully-unrolled partially-pipelined decoder for a (16, 14) polar code with $I = 2$                                                                                    | 73                                                                                                                                                                                                                                                  |

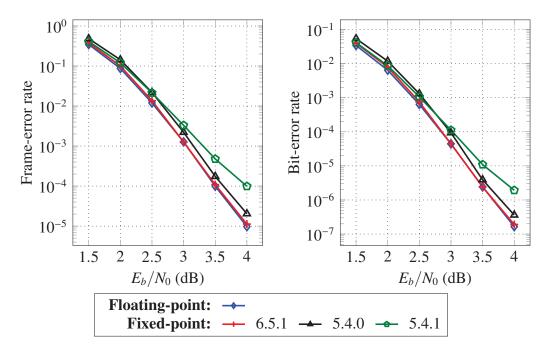

| Effect of quantization on the error-correction performance of a polar code                                                                                           | 77                                                                                                                                                                                                                                                  |

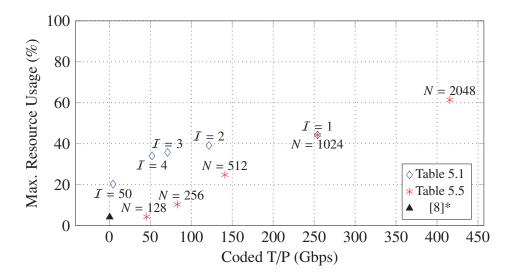

| Maximum FPGA resource usage and coded throughput of unrolled polar decoders.                                                                                         | 84                                                                                                                                                                                                                                                  |

| Decoder trees for SC (a) and Fast-SSC (b) decoding of a (16, 12) polar code                                                                                          | 88                                                                                                                                                                                                                                                  |

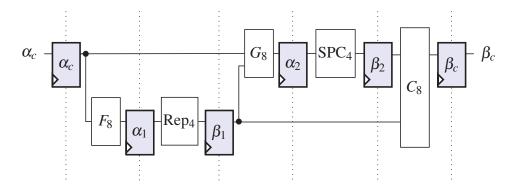

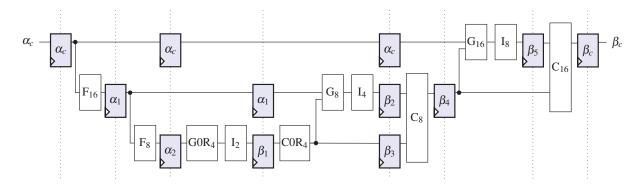

| Unrolled partially-pipelined decoder for a (16, 12) polar code with initiation inter-                                                                                |                                                                                                                                                                                                                                                     |

| $\operatorname{val} \mathcal{I} = 2. \ldots $ | 89                                                                                                                                                                                                                                                  |

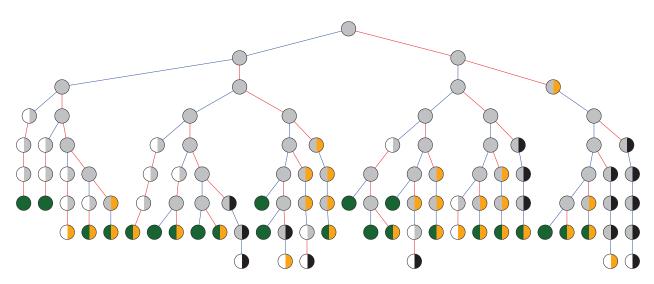

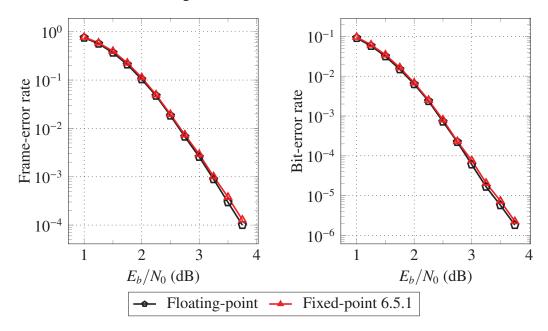

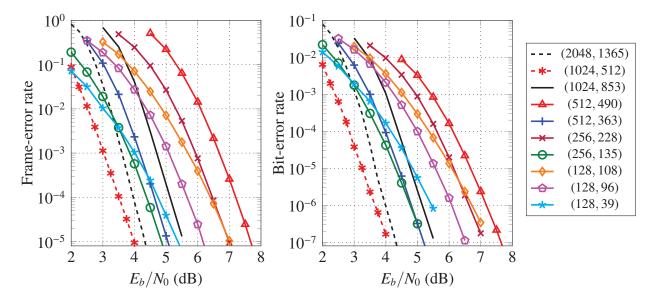

| Error-correction performance of two (2048, 1365) polar codes with different con-                                                                                     |                                                                                                                                                                                                                                                     |

| structions                                                                                                                                                           | 91                                                                                                                                                                                                                                                  |

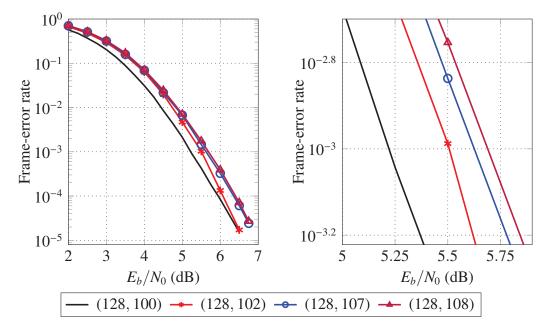

| Error-correction performance of the four constituent codes of length 128 with a                                                                                      |                                                                                                                                                                                                                                                     |

| rate of approximately $\frac{5}{6}$ contained in the proposed (2048, 1365) master code                                                                               | 93                                                                                                                                                                                                                                                  |

| Error-correction performance of the polar codes                                                                                                                      | 95                                                                                                                                                                                                                                                  |

|                                                                                                                                                                      | Polar decoding on GPU: Effect of the number of threads per block Polar decoding on GPU: Effect of the number of blocks per kernel Polar decoding on GPU: Shared versus global memory Polar codes compared with LDPC codes from the 802.11n standard |

## **List of Tables**

| 2.1 | Post-fitting results for SC-based decoder implementations.                         | 22 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Latency and information throughput for SC-based decoder implementations            | 22 |

| 3.1 | Decoder tree node types supported by the original Fast-SSC polar decoder [8]       | 25 |

| 3.2 | New functions performed by the proposed decoder.                                   | 31 |

| 3.3 | Frozen bit patterns decoded by leaf nodes                                          | 32 |

| 3.4 | Post-fitting results for rate-flexible decoders for moderate-length polar codes    | 37 |

| 3.5 | Latency and information throughput comparison for low-rate moderate-length po-     |    |

|     | lar codes.                                                                         | 38 |

| 3.6 | Comparison of state-of-the-art ASIC decoders decoding a $(1024, 512)$ polar code   | 39 |

| 4.1 | Decoding polar codes with the instruction-based decoder                            | 47 |

| 4.2 | Decoding polar codes with floating-point precision using SIMD, comparing the       |    |

|     | instruction-based decoder (ID) with the unrolled decoder (UD)                      | 52 |

| 4.3 | Comparison of the proposed software decoder with that of [49]                      | 53 |

| 4.4 | Effect of unrolling and algorithm choice on decoding speed of the (2048, 1707)     |    |

|     | code on the Intel Core i7-47708                                                    | 54 |

| 4.5 | Decoding polar codes with 8-bit fixed-point numbers on an ARM Cortex A9 using      |    |

|     | NEON.                                                                              | 55 |

| 4.6 | Decoding polar codes on an NVIDIA Tesla K20c                                       | 60 |

| 4.7 | Comparison of the power consumption and energy per information bit for the         |    |

|     | (2048, 1707) polar code                                                            | 61 |

| 4.8 | Information throughput and latency of the polar decoders compared with the LDPC    |    |

|     | decoders of [14] when estimating 524,280 information bits on a Intel Core i7-2600. | 65 |

| 5.1  | Decoders for a (1024, 512) polar code with various initiation interval $I$ imple-                   |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | mented on an FPGA.                                                                                  | 78 |

| 5.2  | Decoders for a (1024, 512) polar code with various initiation interval $I$ imple-                   |    |

|      | mented on an ASIC                                                                                   | 78 |

| 5.3  | Comparison with state-of-the-art polar decoders.                                                    | 79 |

| 5.4  | Comparison with other FPGA implementations                                                          | 80 |

| 5.5  | Deeply-pipelined decoders for polar codes of various lengths with rate $R = 1/2$                    |    |

|      | implemented on an FPGA                                                                              | 81 |

| 5.6  | Deeply-pipelined decoders for polar codes of various lengths with rate $R = 1/2$                    |    |

|      | implemented on an ASIC                                                                              | 81 |

| 5.7  | Partially-pipelined decoders with initiation interval set to $\mathcal{I}_{max}$ for polar codes of |    |

|      | various lengths with rate $R = \frac{5}{6}$ implemented on an FPGA                                  | 82 |

| 5.8  | Partially-pipelined decoders with initiation interval set to $\mathcal{I}_{max}$ for polar codes of |    |

|      | various lengths with rate $R = \frac{5}{6}$ implemented on an ASIC clocked at 1 GHz                 | 82 |

| 5.9  | Deeply-pipelined decoders for polar codes of length $N = 1024$ with common rates                    |    |

|      | implemented on an FPGA                                                                              | 83 |

| 5.10 | Deeply-pipelined decoders for polar codes of length $N = 1024$ with common rates                    |    |

|      | implemented on an ASIC                                                                              | 83 |

| 6.1  | Information throughput and latency for the multi-mode unrolled polar decoders                       |    |

|      | based on the (2048, 1365) and (1024, 853) master codes, respectively with a $N_{\text{max}}$        |    |

|      | of 1024 and 2048                                                                                    | 96 |

| 6.2  | Comparison with state-of-the-art polar decoders.                                                    | 97 |

|      |                                                                                                     |    |

I wanna go fast!

Ricky Bobby

## Chapter 1

## Introduction

Over the last decades we have gradually seen digital circuits take over applications that were traditionally bastions of analog circuits. One of the reasons behind this tendency is our ability to detect and correct errors in digital circuits—circuits making computations with discrete signals as opposed to continuous ones. This ability lead to faster and more reliable communication and storage systems. In some cases it enabled things that we thought might have never been possible e.g. reliable communication with a probe that is located many light years away from our planet.

Right after the second world war, Claude Shannon created a new field—information theory in which he defined the limit of reliable communications or storage. In his seminal work, Shannon defined what he calls the channel capacity [1], the bound that many researchers have tried to achieve or even approach ever since. Shannon's work does not tell us how this limit can be reached.

While Reed-Solomon (RS) and Bose-Chaudhuri-Hocquenghem (BCH) codes have good errorcorrection performance and are in widespread use even today, it's not until the discovery of turbo codes [2] in the 1990s that error-correcting codes approaching the channel capacity were found. Indeed, while Low-Density Parity-Check (LDPC) codes—initially discovered in the 1960s by Robert Gallager [3]—can also be capacity approaching, their decoding algorithm was too complex for the time and thus were not used until they were independently rediscovered by David McKay in 1997 [4].

The discovery of turbo and LDPC codes, greatly rejuvenated the field of error correction. Often used in conjunction with a RS or a BCH code, standards that feature a turbo or a LDPC code are omnipresent. Nowadays, each home contains at least tens of decoders for these codes. They are used in a plethora of applications such as video broadcasting, wireless and wired communications

(e.g. WIFI and Ethernet), data storage and more.

The latest findings on the road to achieving channel capacity are polar codes. Invented by Arıkan in 2008 [5] and further refined in 2009 [6], this new class of error-correcting codes, contrary to LDPC and turbo codes, have an explicit—non-random—construction making the implementation of their encoders and decoders simpler than that of LDPC or turbo codes. Polar codes exploit the channel polarization phenomenon by which the probability of correctly estimating codeword bits tends to either 1 (completely reliable) or 0.5 (completely unreliable). These probabilities get closer to their limit as the code length increases when a recursive construction is used. Under the low-complexity Successive-Cancellation (SC) decoding algorithm, polar codes were shown to achieve the symmetric capacity of memoryless channels as their length tends to infinity.

The complexity of the SC algorithm is low but its sequential nature translates in high-latency and low-throughput decoder implementations. To overcome this, new decoding algorithms derived from SC were introduced, most notably [7] and [8]. These algorithms exploit the recursive construction of polar codes along with the a priori knowledge of the code structure. Fast Simplified Successive Cancellation (Fast-SSC), the algorithm described in [8], integrates the Simplified Successive Cancellation (SSC) algorithm described in [7], thus this work builds upon the former.